# **Western University** Scholarship@Western

**Electronic Thesis and Dissertation Repository**

12-11-2017 11:30 AM

## A Novel AC-DC Interleaved ZCS-PWM Boost Converter

Ramtin Rasoulinezhad The University of Western Ontario

Supervisor Moschopoulos, Gerry The University of Western Ontario

Graduate Program in Electrical and Computer Engineering A thesis submitted in partial fulfillment of the requirements for the degree in Master of **Engineering Science** © Ramtin Rasoulinezhad 2017

Follow this and additional works at: https://ir.lib.uwo.ca/etd

Part of the Power and Energy Commons

#### **Recommended Citation**

Rasoulinezhad, Ramtin, "A Novel AC-DC Interleaved ZCS-PWM Boost Converter" (2017). Electronic Thesis and Dissertation Repository. 5109.

https://ir.lib.uwo.ca/etd/5109

This Dissertation/Thesis is brought to you for free and open access by Scholarship@Western. It has been accepted for inclusion in Electronic Thesis and Dissertation Repository by an authorized administrator of Scholarship@Western. For more information, please contact wlswadmin@uwo.ca.

#### **Abstract**

AC-DC converters with input power factor correction (PFC) that consist of two or more interleaved boost converter modules are popular in industry. PFC is a must in today's AC-DC converters as their input current must meet harmonic standards set by regulatory agencies. With interleaving, the input current of each module can make to be discontinuous and the size of their input inductors since interleaving can reduce the high ripple in each module and produce a net input current with a ripple that is comparable to that achieved with a single boost converter module with a large input inductor.

In high-frequency converters, so as to achieve low harmonic, fast dynamic response, low size, and high-power density the frequency should be increased. The drawback of increasing the switching frequency is increasing the switching losses. This is reason that why soft-switching methods should be used. The focus of the thesis is on zero current switching (ZCS) methods for insulated gate bipolar transistor (IGBT) converters. The auxiliary switch in the proposed converter is activated whenever a main converter switch is about to be turned off, gradually diverting current away from the switch so that it can turn off with ZCS and eliminate the switching losses. In addition, the auxiliary circuit is designed in a way that it can be activated only when the converter is operating with heavier loads and not used when the converter is operating with light load to maximize the overall efficiency.

The operation of the novel converter will then be explained and the mathematical analysis in steady-state will be derived. Based on the results of the analysis, general design guidelines will be provided. Finally, the design procedure will be confirmed by experimental results obtained from the proof of concept prototype.

## Keywords

Power conversion, AC-DC converter, Interleaved boost converter, Zero-current switching, Soft- switching

## Acknowledgments

I would like to express my sincere gratitude to my supervisor, Dr. Gerry Moschopoulos, for his invaluable supervision, encouragement, and continuous guidance throughout my M.ESc research.

I also want to thank my friends, especially; Javad Khodabakhsh, Adel Abosnina, and Neda Rostamzadeh for their great help and contribution during the research work.

I would like to express my deepest gratitude to my parents, Ashraf and Hossein for their constant encouragement and support to continue my higher education and finish this research. I also like to express thanks to my siblings, Reza, Raheleh, and Ramin for all their supports and best wishes. Finally, I dedicate this thesis to my lovely niece and nephew, Negin and Parsa.

# **Table of Contents**

| Abstract                                                            | i    |

|---------------------------------------------------------------------|------|

| Acknowledgments                                                     | ii   |

| Table of Contents                                                   | iii  |

| List of Figures                                                     | vi   |

| Acronyms                                                            | X    |

| Abbreviations                                                       | xi   |

| Chapter 1                                                           | 1    |

| 1 Introduction                                                      | 1    |

| 1.1 General Introduction                                            | 1    |

| 1.2 Semiconductor Devices                                           | 2    |

| 1.2.1 Diodes                                                        | 2    |

| 1.2.2 MOSFETs                                                       | 4    |

| 1.2.3 IGBTs                                                         | 4    |

| 1.3 High Switching Frequency Operation                              | 5    |

| 1.4 Soft Switching                                                  | 7    |

| 1.5 Single-Phase AC-DC Converters (Rectifiers)                      | 9    |

| 1.5.1 The Boost Converter Topology                                  | . 10 |

| 1.5.2 The Interleaved Boost Converter Topology                      | . 12 |

| 1.6 Literature Review                                               | . 16 |

| 1.7 Thesis Objectives                                               | . 24 |

| 1.8 Thesis Outline                                                  | . 25 |

| Chapter 2                                                           | . 26 |

| 2 Modes of Operation of the Novel AC-DC Interleaved Boost Converter | . 26 |

|         | 2.1 Introduction                                                                                    | 26 |

|---------|-----------------------------------------------------------------------------------------------------|----|

|         | 2.2 Modes of Operation                                                                              | 27 |

|         | 2.3 Conclusion                                                                                      | 36 |

| C       | Chapter 3                                                                                           | 37 |

| 3       | Circuit Analysis of the Novel AC-DC Interleaved Boost Converter                                     | 37 |

|         | 3.1 Introduction                                                                                    | 37 |

|         | 3.2 Circuit Analysis                                                                                | 37 |

|         | 3.3 Conclusion                                                                                      | 52 |

| C       | hapter 4                                                                                            | 53 |

| 4       | Design Procedure and Example of the Proposed AC-DC Interleaved ZCS-PWM Converter                    |    |

|         | 4.1 Introduction                                                                                    | 53 |

|         | 4.2 Conditions for ZCS Turn off of all Switches of the Proposed AC-DC Interleated ZCS-PWM Converter |    |

|         | 4.3 Characteristic of the Proposed AC-DC Interleaved ZCS-PWM Converter                              | 57 |

|         | 4.4 Design Example of the Proposed Converter                                                        | 66 |

|         | 4.4.1 Design Procedure for the Main Power Circuit                                                   | 66 |

|         | 4.4.2 Design Procedure for the Auxiliary Circuit                                                    | 72 |

|         | 4.5 Conclusion                                                                                      | 78 |

| C       | Chapter 5                                                                                           | 79 |

| 5       | Experimental Results                                                                                | 79 |

|         | 5.1 Introduction                                                                                    | 79 |

|         | 5.2 Experimental Results                                                                            | 79 |

|         | 5.3 Conclusion from Experimental Results                                                            | 88 |

|         | 5.4 Efficiency Results                                                                              | 89 |

|         | 5.5 Conclusion                                                                                      | 91 |

| $C^{1}$ | Shantar 6                                                                                           | 02 |

| 6 Summary and Conclusion | 92  |

|--------------------------|-----|

| 6.1 Introduction         | 92  |

| 6.2 Summary              | 92  |

| 6.3 Conclusion           | 94  |

| 6.4 Contributions        | 94  |

| 6.5 Future Work          | 95  |

| References               | 96  |

| Appendix A               | 99  |

| Appendix B               | 100 |

| Appendix C               | 101 |

| Appendix D               | 103 |

| Appendix E               | 105 |

| Appendix F               | 107 |

# List of Figures

| Fig. 1.1. (a) Symbol of a diode; (b) actual i-v characteristic; (c) idealized i-v charac | eteristic 3 |

|------------------------------------------------------------------------------------------|-------------|

| Fig. 1.2. Reverse recovery current of a diode                                            | 3           |

| Fig. 1.3. Circuit symbol of an N-Channel power MOSFET                                    | 4           |

| Fig. 1.4. Circuit symbol of an IGBT with an anti- parallel diode                         | 5           |

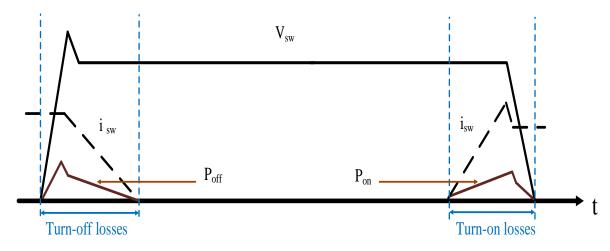

| Fig. 1.5. Typical actual switch voltage and current waveforms                            | 6           |

| Fig. 1.6. Current tail in an IGBT                                                        | 7           |

| Fig. 1.7. Applying ZVS for MOSFET                                                        | 8           |

| Fig. 1.8. Applying ZCS for IGBT                                                          | 9           |

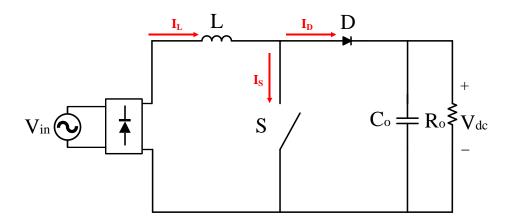

| Fig. 1.9. Topology of a basic AC-DC boost converter                                      | 10          |

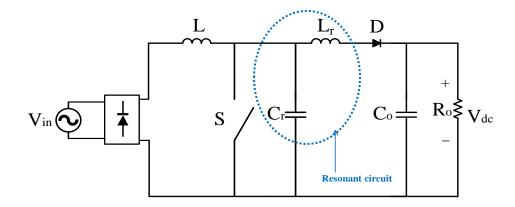

| Fig. 1.10. Topology of a resonant boost converter operating with ZVS                     | 11          |

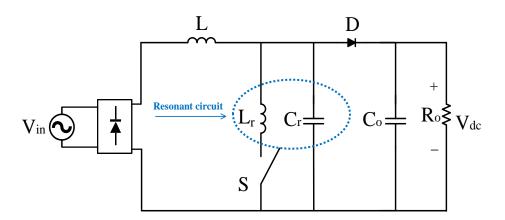

| Fig. 1.11. Topology of a resonant boost converter operating with ZCS                     | 11          |

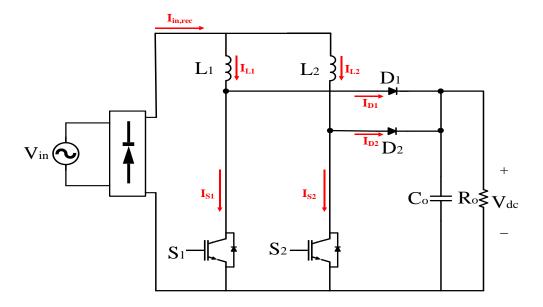

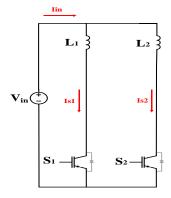

| Fig. 1.12. Topology of a basic AC-DC interleaved boost converter                         | 13          |

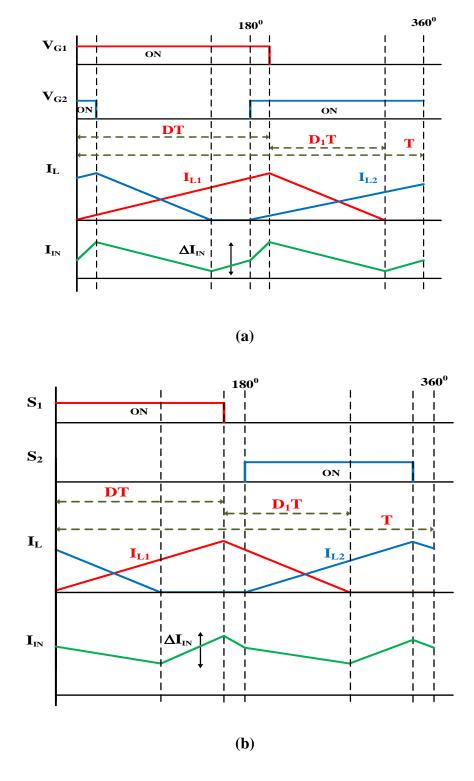

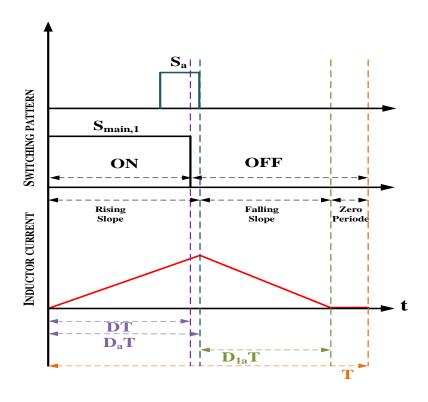

| Fig. 1.13. Inductor current waveforms according to the switching pattern in the DC       | M 14        |

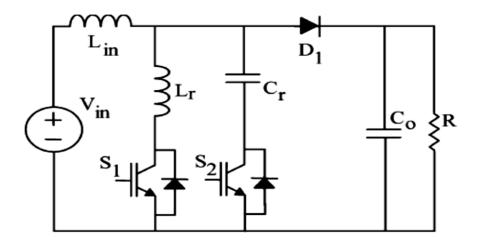

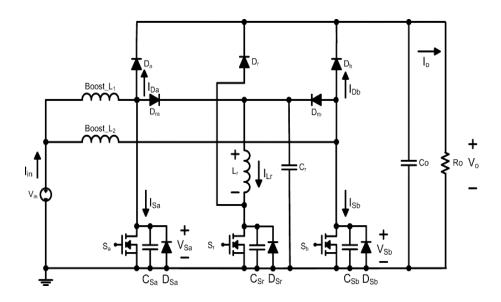

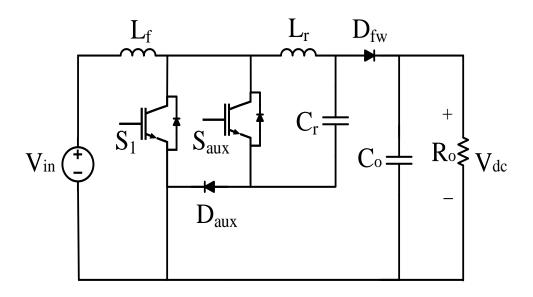

| Fig. 1.14. ZCS boost converter proposed in [19]                                          | 19          |

| Fig. 1.15. ZCS boost converter proposed in [20]                                          | 19          |

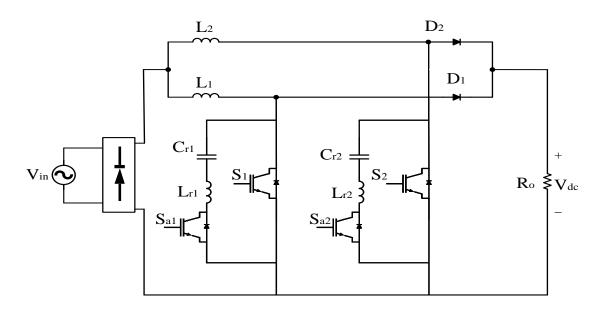

| Fig. 1.16. Interleaved ZCT boost converter proposed in [14]                              | 20          |

| Fig. 1.17. Interleaved ZVS/ZCS boost converter proposed in [16]                          | 21          |

| Fig. 1.18. Interleaved ZVS/ZCS boost converter proposed in [11]                          | 21          |

| Fig. 1.19. Interleaved ZCS boost converter proposed in [17]                              | 22          |

| Fig. 1.20. Interleaved ZCS boost converter proposed in [21]                                                                          | . 23 |

|--------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 1.21. ZCS boost converter proposed in [22]                                                                                      | . 23 |

| Fig. 1.22. Interleaved ZCS boost converter proposed in [18]                                                                          | . 24 |

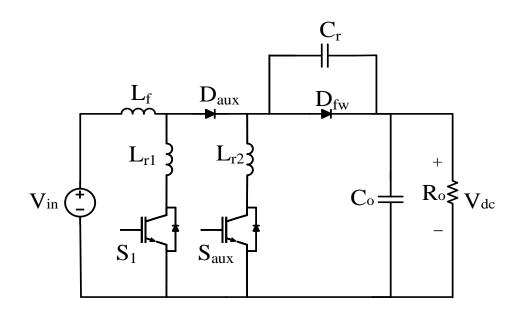

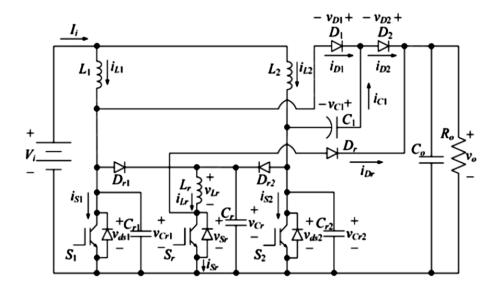

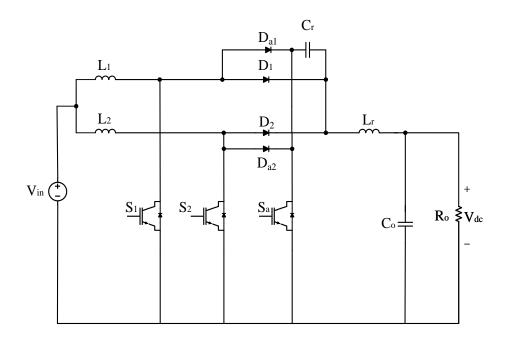

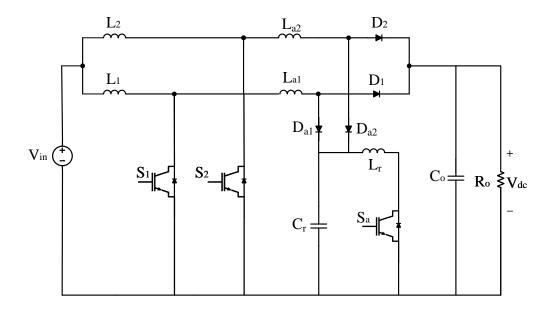

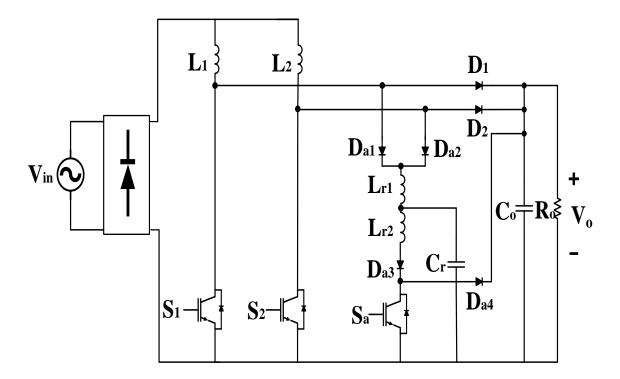

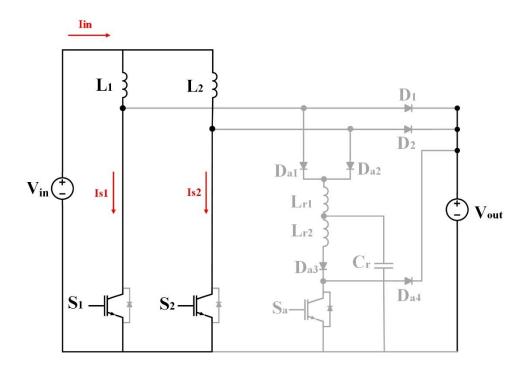

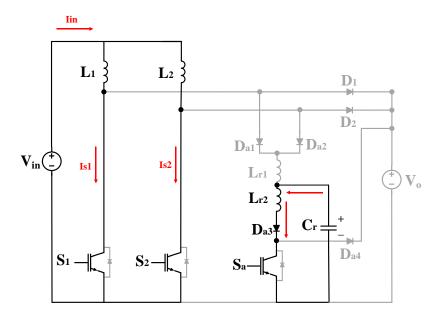

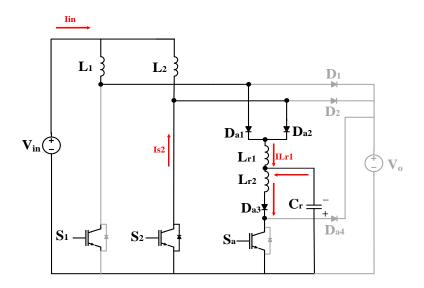

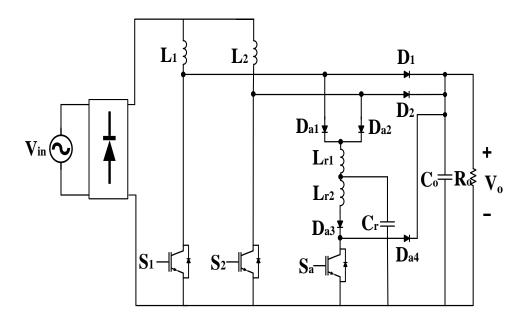

| Fig. 2.1. Proposed interleaved AC-DC ZCS-PWM boost converter                                                                         | . 27 |

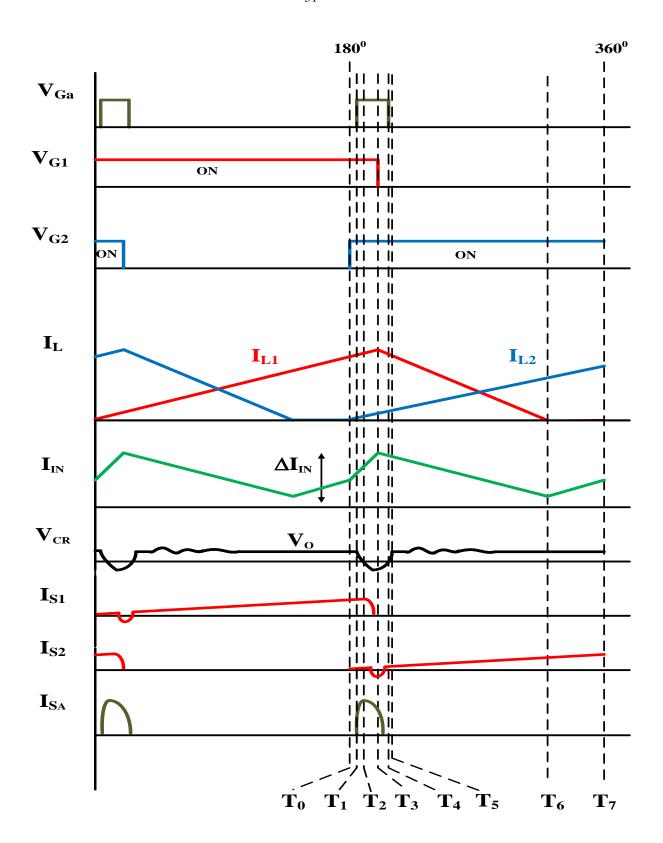

| Fig. 2.2. Voltage and current waveforms of different circuit components of the proposed interleaved boost converter in steady state. | . 31 |

| Fig. 2.3.Current flow in Mode 1                                                                                                      | . 32 |

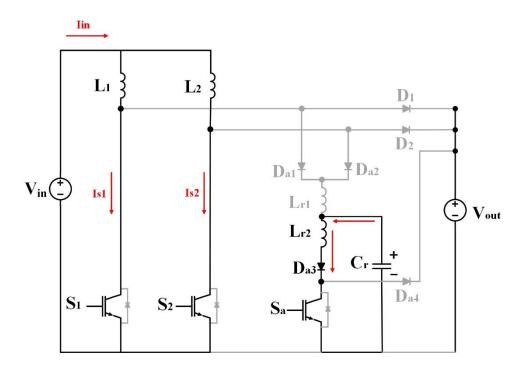

| Fig. 2.4. Current flow in Mode 2                                                                                                     | . 32 |

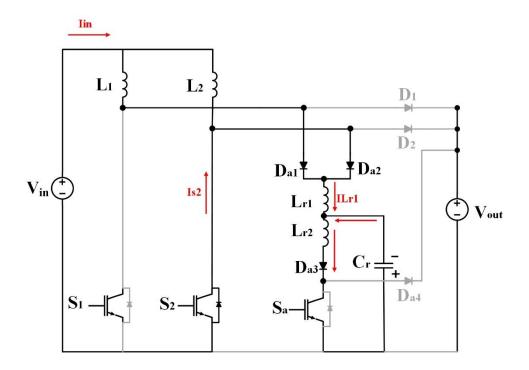

| Fig. 2.5.Current flow in Mode 3                                                                                                      | . 33 |

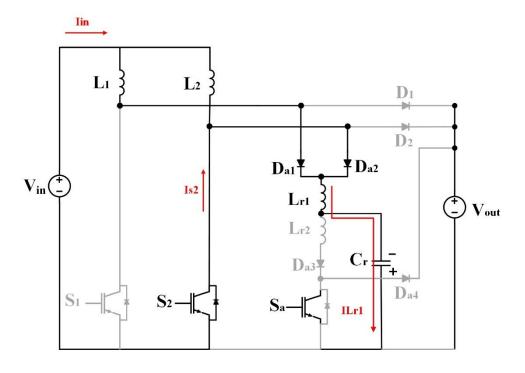

| Fig. 2.6.Current flow in Mode 4                                                                                                      | . 33 |

| Fig. 2.7.Current flow in Mode 5                                                                                                      | . 34 |

| Fig. 2.8.Current flow in Mode 6                                                                                                      | . 34 |

| Fig. 2.9.Current flow in Mode 7                                                                                                      | . 35 |

| Fig. 3.1.Currents flow in Mode 1                                                                                                     | . 38 |

| Fig. 3.2.Reduced equivalent circuit of Mode 1                                                                                        | . 39 |

| Fig. 3.3.Current flow in Mode 2                                                                                                      | . 39 |

| Fig. 3.4. Reduced equivalent circuit of the auxiliary circuit of Mode 2                                                              | . 40 |

| Fig. 3.5. Current flow in Mode 3                                                                                                     | . 42 |

| Fig. 3.6. Reduced equivalent circuit of Mode 3                                                                                       | . 42 |

| Fig. 3.7. Current flow in Mode 6                                                                                                     | . 48 |

| Fig. 3.8. Reduced equivalent circuit of Mode 6                                                                                       | . 48 |

| Fig. 4.1. Proposed interleaved AC-DC ZCS-PWM boost converter                                      | 54   |

|---------------------------------------------------------------------------------------------------|------|

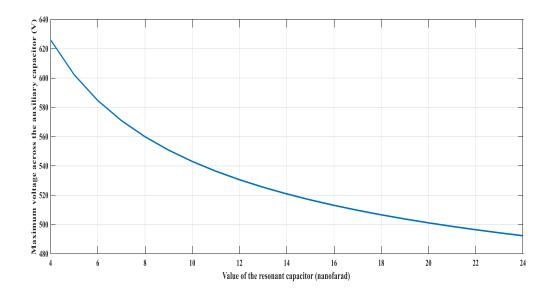

| Fig. 4.2. Characteristic graph of variation of maximum voltage across auxiliary capacitor         |      |

| with the variation of C <sub>r</sub> when other parameters are constant                           | 59   |

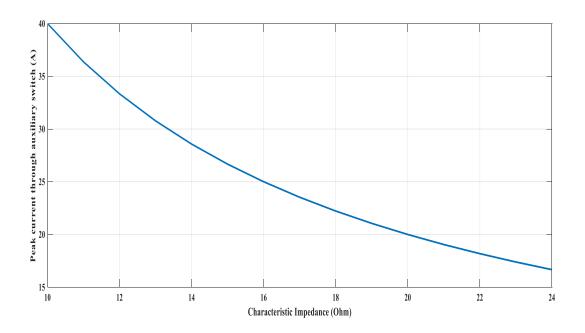

| Fig. 4.4. Characteristic graph of variation of peak current through auxiliary switch with th      | e    |

| variation of resonant capacitor when other parameters are constant                                | 60   |

| Fig. 4.3. Characteristic graph of variation of peak current through auxiliary switch with th      | e    |

| variation of characteristic impedance of the auxiliary circuit                                    | 60   |

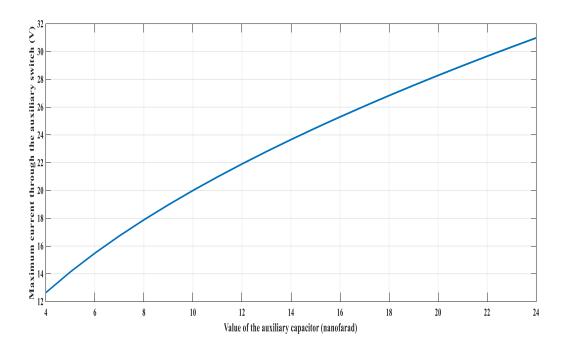

| Fig. 4.5. Characteristic graph of time in which main switch current get reduced to zero wi        | th   |

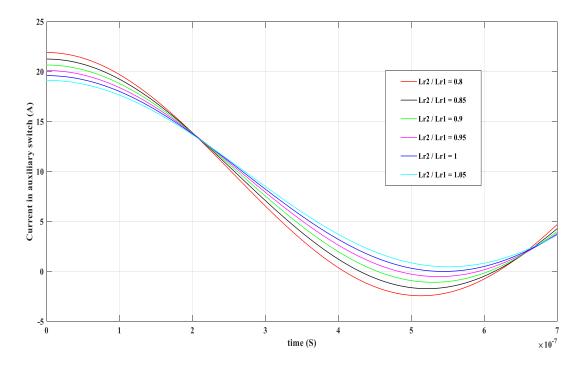

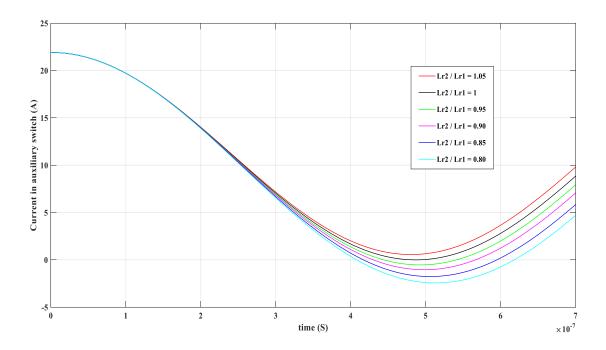

| the variation of L <sub>r2</sub> while other parameters are constant                              | 63   |

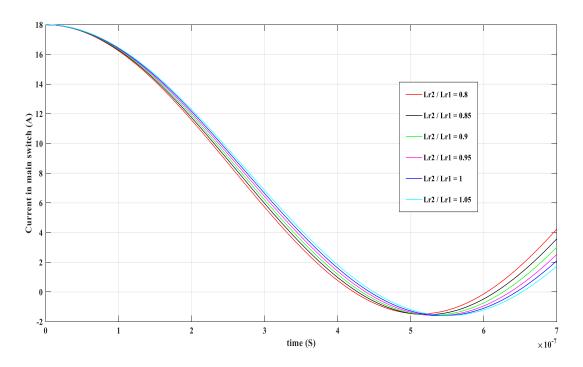

| Fig. 4.6. Characteristic graph of time in which auxiliary switch current get reduced to zero      | )    |

| with the variation of $L_{r2}$ while other parameters are constant                                | 63   |

|                                                                                                   |      |

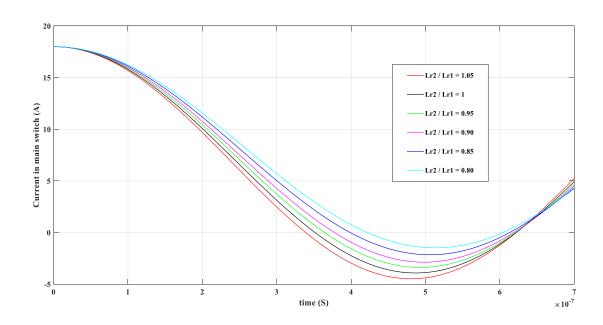

| Fig. 4.7. Characteristic graph of time in which main switch current get reduced to zero with      |      |

| the variation of $L_{r1}$ while other parameters are constant                                     | 65   |

| Fig. 4.8. Characteristic graph of time in which auxiliary switch current get reduced to zero      | )    |

| with the variation of $L_{r1}$ while other parameters are constant                                | 65   |

| Fig. 4.9. Profile of the input inductor phase current according to the switching pattern in       |      |

| DCM                                                                                               | 68   |

| Fig. 4.10. Profile of the input inductor phase current of the proposed interleaved converter      | •    |

| according to the switching pattern in DCM                                                         |      |

| decording to the switching pattern in Delia                                                       | . 00 |

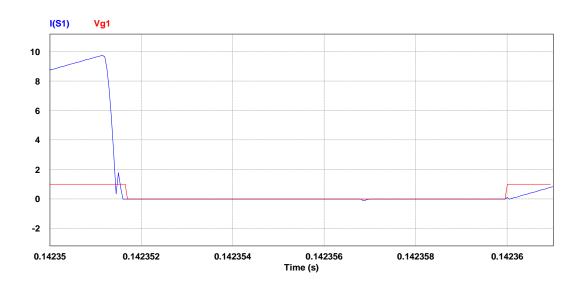

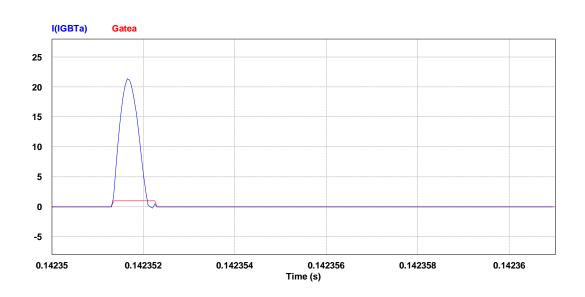

| Fig. 4.11. PSIM simulation of current and gate signal of main switch                              | 75   |

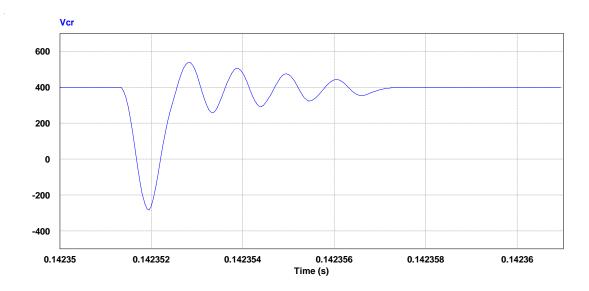

| Fig. 4.12. PSIM simulation of current and gate signal of auxiliary switch                         | 75   |

| Fig. 4.13. PSIM simulation of resonant capacitor                                                  | 76   |

| Fig. 5.1. Proposed AC-DC interleaved ZCS-PWM boost converter                                      | 80   |

|                                                                                                   |      |

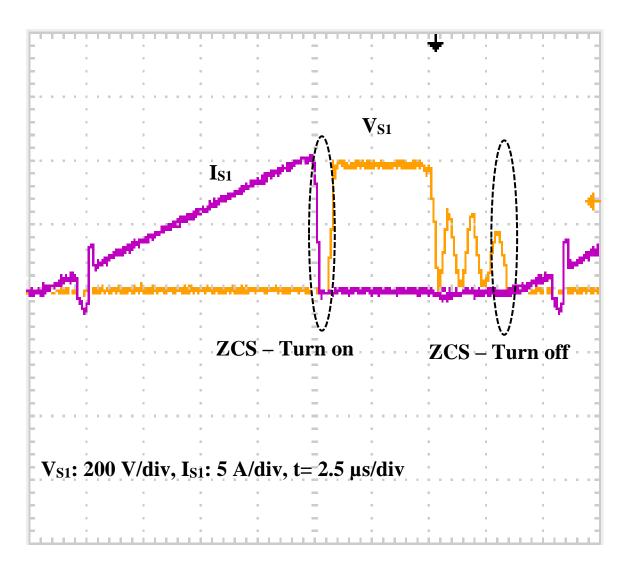

| Fig. 5.2 Main switch S <sub>1</sub> voltage and current waveforms V <sub>c1</sub> I <sub>c1</sub> | 81   |

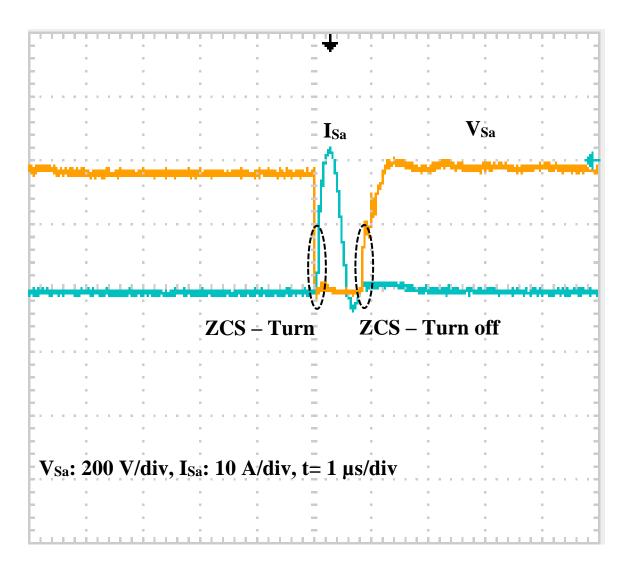

| Fig. 5.3. Auxiliary switch S <sub>a</sub> voltage and current waveforms V <sub>Sa</sub> , I <sub>Sa</sub>             | 82 |

|-----------------------------------------------------------------------------------------------------------------------|----|

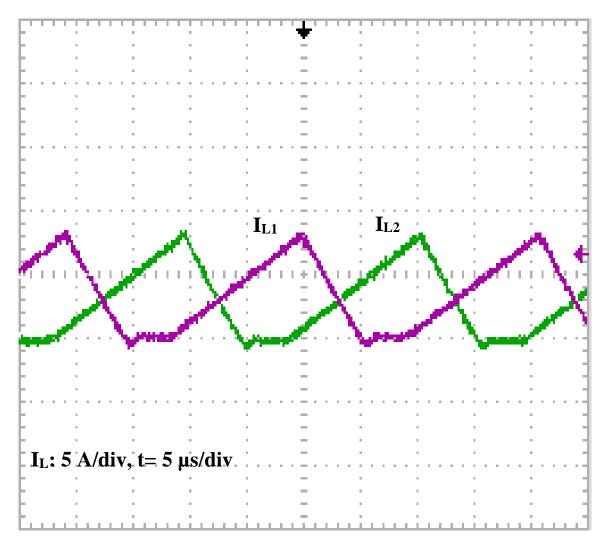

| Fig. 5.4. Main input inductors L <sub>1</sub> and L <sub>2</sub> current waveforms I <sub>L1</sub> , I <sub>L2</sub>  | 83 |

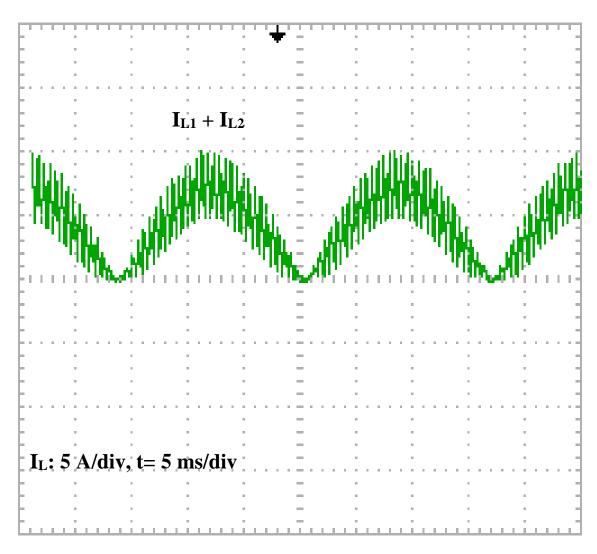

| Fig. 5.5. Rectified input current waveform I <sub>L1</sub> + I <sub>L2</sub>                                          | 84 |

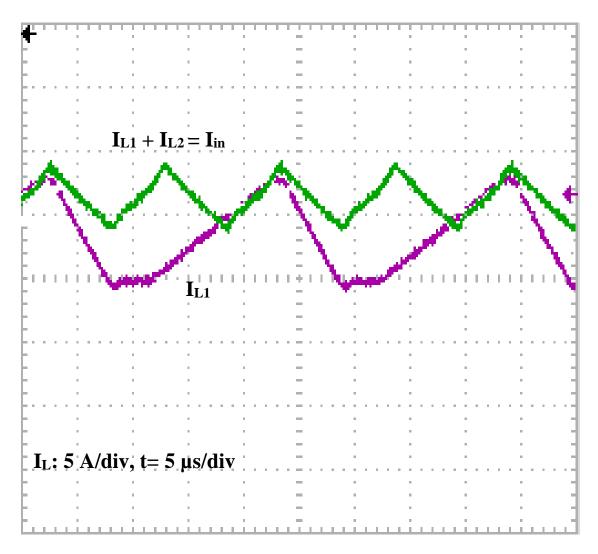

| Fig. 5.6. Rectified input current ripple and I <sub>L1</sub> waveforms                                                | 85 |

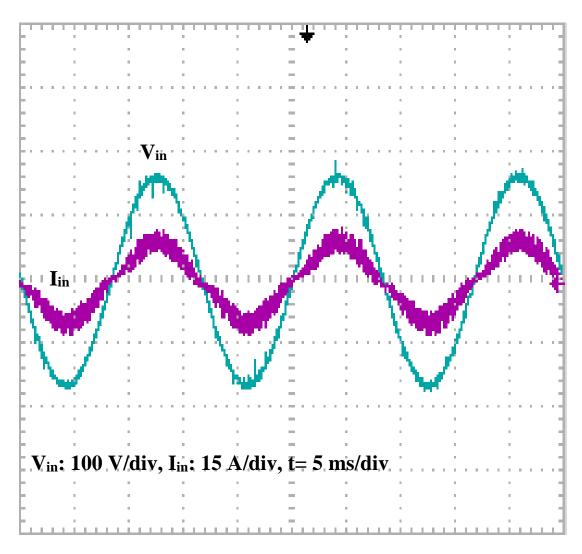

| Fig. 5.7. Input voltage and current waveforms V <sub>in</sub> , I <sub>in</sub>                                       | 86 |

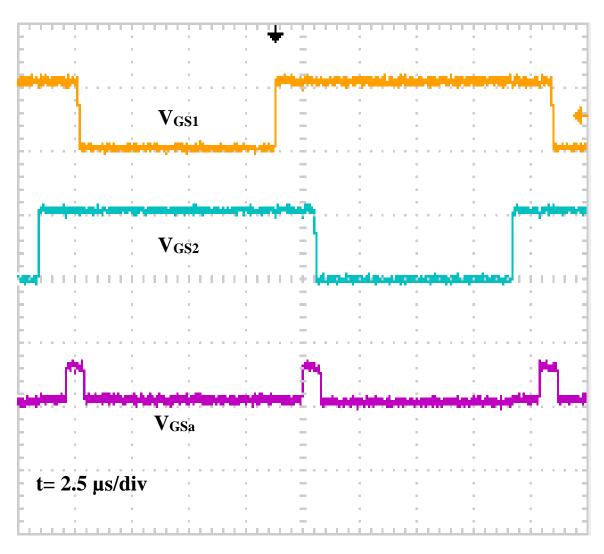

| Fig. 5.8. Gating signals of main switches and auxiliary switch V <sub>Gs1</sub> , V <sub>Gs2</sub> , V <sub>Gsa</sub> | 87 |

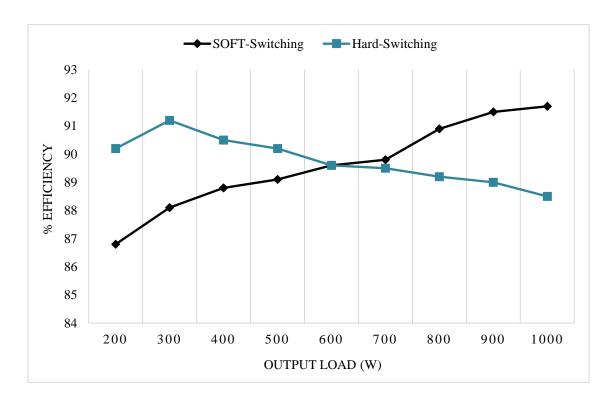

| Fig. 5.9. Comparative of efficiency graphs between soft-switching and hard-switching for                              |    |

| different output loads at input voltage of 110 V and output voltage 400V.                                             | 90 |

## Acronyms

AC Alternative Current

DC Direct Current

EMI Electromagnetic Interference

DCM Discontinuous Current Mode

CCM Continuous Current Mode

KCL Kirchhoff's Current Law

KVL Kirchhoff's Voltage Law

MOSFET Metal Oxide Semiconductor Field Effect Transistor

IGBT Insulated Gate Bipolar Transistor

BJT Bipolar Junction Transistor

RMS Root Mean Square

PWM Pulse Width Modulation

ZCS Zero Current Switching

ZVS Zero Voltage Switching

THD Total Harmonic Distortion

PFC Power Factor Correction

## **Abbreviations**

V<sub>in</sub> Input AC Voltage

V<sub>o</sub> Output DC Voltage

Input Current

I<sub>o</sub> Output Current

V<sub>rec</sub> Rectified AC Voltage

V<sub>dc</sub> DC Voltage

D Duty Cycle

f<sub>sw</sub> Switching Frequency

t Time

C<sub>O</sub> Output Capacitor

R<sub>o</sub> Output Resistive Load

L<sub>1</sub> Input Inductor 1

L<sub>2</sub> Input Inductor 2

$L_{r1} \hspace{1.5cm} Resonant \ Inductor \ 1$

$L_{r2} \hspace{1.5cm} Resonant \ Inductor \ 2$

C<sub>r</sub> Resonant Capacitor

S<sub>1</sub> Main Switch 1

S<sub>2</sub> Main Switch 2

S<sub>a</sub> Auxiliary Switch

D<sub>1</sub> Main Boost Diode 1

D<sub>2</sub> Main Boost Diode 2

D<sub>a1</sub> Auxiliary Diode 1

D<sub>a2</sub> Auxiliary Diode 2

D<sub>a3</sub> Auxiliary Blocking Diode 3

D<sub>a4</sub> Auxiliary Clamping Diode 4

V Volt

A Ampere

μ Micro

k Kilo

H Henry

F Farad

## Chapter 1

#### 1 Introduction

#### 1.1 General Introduction

Power electronics is a field of power engineering that converts and controls input power to the desired output power by using semiconductor devices. The power source can be DC sources such as solar cells, batteries, and fuel cells, or AC sources like different kinds of electric generators. The power source can be single-phase or three-phase based on the application and its frequency is 50 or 60 Hz according to the region in which it operates. For instance, in North America, the frequency should be 60 Hz while in Europe it is 50 Hz. The load can be AC or DC, with or without isolation, single-phase or three-phase. Thus, power electronics converters are classified into:

- DC to DC

- DC to AC

- AC to DC

- AC to AC

A new interleaved boost AC-DC converter is proposed in this thesis. Its modes of operation will be analyzed and relevant mathematical equations for each mode of operation will be derived. The results of the mathematical equations derived for the proposed interleaved converter in the steady-state condition will be used to design the converter. The characteristic curves for the key components of the proposed converter will be presented by using MATLAB simulations based on the derived equations. Then, the value of each component can be determined by using the circuit simulator PSIM in order to satisfy the

key design objectives. Finally, the feasibility of the converter will be confirmed with results obtained from an experimental prototype.

#### 1.2 Semiconductor Devices

In many cases, power converters, which are used to convert the available input power source to the desired output load, consist of passive elements such as inductors and capacitors, controllers to regulate the output voltage and semiconductor devices such as transistors and diodes. The semiconductors are one of the most important parts of any converter and can be classified into uncontrollable and controllable devices.

The diode is an uncontrollable semiconductor device, which should be forward biased to be turned on and conduct the current and reverse biased to be turned off. BJTs (Bipolar Junctions Transistors), MOSFETs (Metal Oxide Semiconductor Field Effect Transistors) and IGBTs (Insulated Gate Bipolar Transistors) are the most common controllable semiconductors. However, at high frequencies, IGBTs and MOSFETs are dominant. Diodes, MOSFETs, and IGBTs are explained in more detail in the following subsections.

#### 1.2.1 Diodes

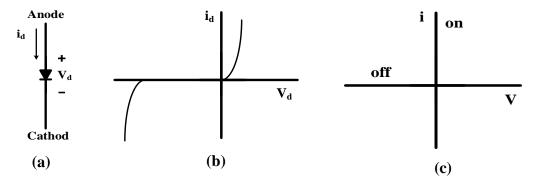

The following figure shows a diode and its current and voltage characteristics. A diode consists of anode and cathode sides when the current,  $i_d$ , is positive (Fig. 1.1.a) the diode is forward biased and conducts the current but when the voltage,  $V_d$ , is negative, it works as an open circuit and does not conduct the current, and this is called reverse biased. Therefore, the current can be flowed in only one direction from the anode to cathode. Fig. 1.1.b and Fig. 1.1c show actual and ideal characteristics of a diode respectively.

As can be seen from Fig. 1.1.c, an ideal diode does not conduct any negative current. However, as is shown in Fig. 1.2, in reality when the current through the diode decreases to zero, for a moment the current goes to negative and then reaches zero. This negative current, called reverse recovery current, and its duration are defined as t<sub>rr</sub>, which is equal to the time that the current takes to reach negative and return to zero.

Fig. 1.1. (a) Symbol of a diode; (b) actual i-v characteristic; (c) idealized i-v characteristic

Fig. 1.2. Reverse recovery current of a diode

It can be seen from Fig. 1.2 that, during t<sub>rr</sub>, voltage and current overlap and therefore reverse recovery current causes power losses in the diode. The other drawback of reverse recovery in a power electronic circuit is EMI (electromagnetic interference), which leads to malfunctions in the system. By increasing the frequency, reverse recovery losses will be increased; thus, power electronic engineers use fast recovery diodes that have a short t<sub>rr</sub>. It should be noted that there is no overlap between current and voltage in the discontinuous mode because the current reaches and stays zero for a predetermined amount of time and reverse recovery loss is eliminated.

#### 1.2.2 MOSFETs

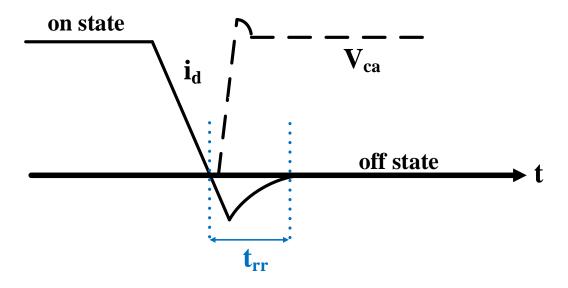

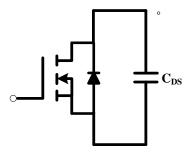

The MOSFET (metal oxide field effect transistor) is one of the most common types of power semiconductor switches and consists of three terminals: gate (G), source (S) and drain (D). In Fig. 1.3, a circuit symbol of a power MOSFET is shown. MOSFETs are the best choice for lower power, higher switching frequency applications (> 100 kHz) for several reasons. The first reason is that their switching speed is fast, the second is that their on-state losses are low when operating with low drain-source voltage, and a third reason is that a small voltage needs to initiate the on/off transition of the forward current (i<sub>DS</sub>) in MOSFETs because of the high impedance gate. Although MOSFETs are controllable semiconductor devices and can block positive drain-source voltage V<sub>DS</sub>, they cannot block negative V<sub>DS</sub> because they have an intrinsic anti-parallel diode. Voltage between the gate and source (V<sub>GS</sub>) should be higher than about 4 V to conduct current. This voltage is called the threshold voltage, and MOSFETs can be considered to be open circuits for voltages less than this value. Therefore, by maintaining the gate voltage at a higher value (close to 10 V), MOSFETs can conduct drain current i<sub>D</sub> and are considered to be on. During an onstate, a real MOSFET has a small resistor between the drain and source R<sub>DS</sub>(on) that leads to conduction losses in the device. This conduction loss is one of the main reasons why MOSFETs are not the best choice for high power applications.

Fig. 1.3. Circuit symbol of an N-Channel power MOSFET

#### 1.2.3 IGBTs

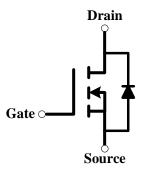

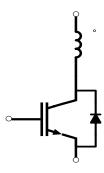

The IGBT (insulated gate bipolar transistor) is a combination of a MOSFET and a BJT (bipolar junction transistor). Its on-state is like that of BJT, while its gate is like that of MOSFET. This device consists of three terminals: a gate (G), an emitter (E) and a collector

(C). In Fig. 1.4, a circuit symbol of an IGBT is shown. Unlike MOSFET, IGBT may or may not have anti-paralleled body diodes.

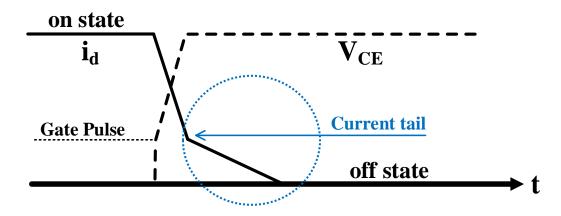

Conduction losses in MOSFETs increase as the amount of current i<sub>D</sub> increases, while those in BJTs are fixed; thus, for higher power applications, BJTs have lower conduction losses than MOSFETs. BJTs, however, are slower devices than MOSFETs because they require continuous base current to operate, and since IGBTs share some of the characteristics of BJTs, IGBTs are slower than MOSFETs. IGBTs turn off more slowly than MOSFETs because they have a current tail due to the fact that they are minority carrier devices. This means that electrons must be removed from these devices before they are turned off so that a significant overlap of voltage and current appears during this switching transition. Switching losses of IGBTs are higher than those of MOSFETs, but IGBTs are preferred over MOSFETs for higher power, lower switching frequency applications (< 100 kHz).

Fig. 1.4. Circuit symbol of an IGBT with an anti- parallel diode

## 1.3 High Switching Frequency Operation

Main energy storage in converters includes capacitors, inductors, and transformers. Usually, the size and weight of a converter depend on its energy storage components, which are necessary for storing and transferring energy. The size of the energy storage can be decreased by increasing the switching frequency of the converter, for instance, capacitors and inductors can store enough voltage and current respectively for a shorter amount of time, which leads to a lighter and smaller converter. Therefore, one of the advantages of increasing the switching frequency is reducing the overall size and weight of the converter.

In ideal switches, during turning on and turning off, there is no overlap between current and voltage and, as a result, there is no power loss.

On the other hand, in actual switches, current and voltage overlap, as shown in the next figure, which leads to power losses. This is one of the restrictions and disadvantages of increasing the switching frequency. In Fig. 1.5, Is and Vs are defined as current through and voltage across the switch respectively.

Fig. 1.5. Typical actual switch voltage and current waveforms

It can be seen from Fig. 1.5 that, in an actual switch, current and voltage overlap during the switching transition from on to off and vice versa. As power losses in switching are related to the multiplication of current and voltage, by increasing the switching frequency, the switching losses increase as well.

The dominant switching losses for a MOSFET happen while turning the switch on because the capacitor, which is placed between the drain and source of the MOSFET, stores the energy, and when the MOSFET is turned on, this capacitor discharges the voltage. Therefore, there is an overlap between current and voltage until the capacitor is discharged completely. However, the main switching losses for an IGBT, as shown in Fig. 1.6, occur while turning the switch off because it has the current tail. Thus, when it is turned off, the current tail and voltage overlap until the current tail goes to zero. These kinds of switching methods are called hard switching in the literature.

Fig. 1.6. Current tail in an IGBT

## 1.4 Soft Switching

Based on the abovementioned discussions, so as to operate a converter in high switching frequency, the problem of hard switching, which leads to power losses, should be solved. This problem can be tackled by soft-switching techniques. The techniques that should be implemented in converters in order to make the switching transition to something more gradual, are called soft-switching in the power electronics literature. Based on these techniques, one of the voltages or currents should be zero during the switching transition time. Therefore, because there is not any overlap between voltage across and current through the switch, switching losses can be almost eliminated. Since the transition is not sudden and is gradual, EMI will be reduced significantly as well.

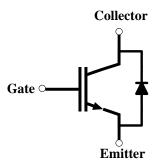

Soft switching techniques can be categorized into two main types: ZVS (zero current switching) and ZCS (zero current switching) methods. Here some general information about these two main approaches is presented. The ZVS principle of operation is based on forcing the voltage to zero just before turning the switch on or off and keeping it zero during the switching transition time. In industry, all the MOSFETs and many kinds of IGBTs have the anti-parallel diode in their body, which allows them to conduct the current in the reverse direction. In other words, by having anti parallel diodes, MOSFETs can conduct current from the source to drain and for IGBTs from the emitter to collector. For IGBTs that have anti-parallel diodes and all MOSFETs, turning on under ZVS can be achieved by conducting the current through the body diode just before the switch is turned

on. As a result, during the switching transition, the voltage of the switch can be assumed to be zero. In addition, when the turning the switch off with ZVS, the rate of voltage rising across the switch should be decreased so as to restrict the overlap between voltage and current during the switching transition time. This can be done by adding a capacitor in parallel with the switch.

On the other hand, the ZCS technique can be achieved by forcing the current through the switch to zero just before the switch is turned on or off and maintain it at zero during the switching transition time. When turning the switch off with ZCS, the current should be diverted from the switch just before the switching. The most common way to do this is to impose a negative voltage across the switch or in a current path of the switch. Also, when turning the switch on with ZCS, the rate of current rising through the switch should be reduced in order to limit the overlap between voltage and the current of the switch during the switching transition time.

As discussed before, MOSFETs have  $R_{DS,on}$  and should be used in high switching frequencies and low current applications. Most often, MOSFETs operate with ZVS as they have a fairly high drain-source capacitance. Therefore, as is shown in Fig. 1.7, MOSFETs are usually turned on and off with ZVS by adding a capacitor in parallel with them.

Fig. 1.7. Applying ZVS for MOSFET

On the other hand, because IGBTs have tail current, they are used in high current and lower switching frequency applications in comparison with MOSFETs. Usually, the soft-switching technique that are used for IGBTs are ZCS as they are minority-carrier devices (as shown in Fig. 1.8). It is worth noting that the most important switching losses for

MOSFETs and IGBTs, which should be eliminated, are turning-on and turning-off losses respectively. In this thesis, soft switching of IGBT under ZCS will be presented.

Fig. 1.8. Applying ZCS for IGBT

## 1.5 Single-Phase AC-DC Converters (Rectifiers)

AC-DC converters are essential in both of low and high-frequency applications. For instance, HVDC (high voltage direct current) is one of the areas in which inverters in the low -frequencies, where the switching frequency is almost the same as the line frequency, should be implemented. However, in this thesis, the focus is on high-frequencies where AC-DC converters can be used at battery chargers, telecommunication power supplies, uninterrupted power sources (UPS), medical devices, personal computers, information technology applications, and so on. One of the most important features that AC-DC converters should possess is that, their power factor should be close to one. In other words, input voltages and currents of these converters should be purely sinusoidal and in phase with each other to meet harmonic standards such as IEC 1000-3- 2 2, IEC-61 000-3-2, IEC 1000-3-4 and IEEE-519-1992. By increasing the power factor, the efficiency of the inverter, in terms of real power, can be increased. Power factor can be written as follows:

$$PF = \frac{P_{ave}}{P_{app}} \tag{1-1}$$

Where,  $P_{ave}$  and  $P_{app}$  are average power and apparent power respectively. It should be noted that, the input power factor of a current-fed converters is higher than a voltage-fed converter. Thus, power factor can be increased by using a current-fed converter.

#### 1.5.1 The Boost Converter Topology

Boost AC-DC converters are used, when an AC input voltage should be stepped-up to meet a DC load voltage, which is higher than the AC source voltage. The topology of a boost AC-DC inverter is shown in Fig. 1.9, where a diode bridge rectifier is used to convert the input AC to DC. Then, four main components are used to boost the DC voltage, including: a semiconductor switch (S) such as MOSFETs and IGBTs in high –frequencies which should be turned on and off periodically, a diode (D), an inductor (L), and an output filter capacitor (C). The output voltage is dependent on the time in which the switch conducts, over the time of the switching cycle, which is the inverse of the switching frequency  $T_S = \frac{1}{f_S}$ . This ratio called duty cycle (D) and can be obtained as follows:

$$D = \frac{T_{on}}{T_{S}} \tag{1-2}$$

When switch is turned on, the current flows through the inductor and can be stored there. At this mode of operation, the output capacitor supplied the load. The voltage across the inductor at this time is equal to the input voltage. When the switch is turned off, the diode is forward-biased, thus the input current flows to the output. Now, voltage across the inductor is equal to  $V_{in}$ - $V_o$ . Since, the output voltage is higher than the input voltage, this value is negative.

Fig. 1.9. Topology of a basic AC-DC boost converter

It should be noted that, ZVS and ZCS for a boost converter can be achieved by using resonant converters or resonant-transition converters frequently. In resonant converters, which use a resonant inductor ( $L_r$ ) and a resonant capacitor ( $C_r$ ), like Fig. 1.10 (ZVS) and Fig. 1.11 (ZCS), there are high peak switch voltage or current stress which leads to high conduction losses.

Fig. 1.10. Topology of a resonant boost converter operating with ZVS

Fig. 1.11. Topology of a resonant boost converter operating with ZCS

On the other hand, since in resonant-transition converter an additional circuitry that is not a part of the main power circuit is used to perform ZCS or ZVS, it does not suffer from high peak switch voltage or current stress, so conduction loss is less than a resonant converter. In this thesis, the main idea is turning the auxiliary switch on only before turning the main switches off and then turning the auxiliary switch off right after it. Therefore, the

auxiliary switch operates for only a small portion of the switching cycle. In other words, the resonant-transition converter operates almost like a conventional converter.

## 1.5.2 The Interleaved Boost Converter Topology

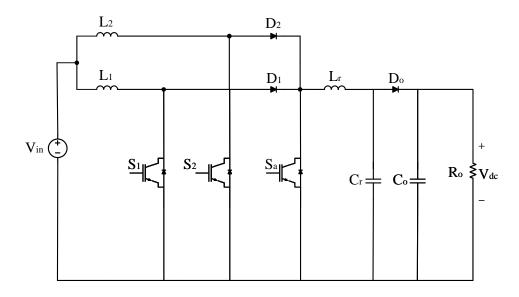

A two-phase boost interleaved technique, applies two boost converters in parallel so as to conduct the current evenly through the two inductors and reduce the size of filter components. As is shown in Fig. 1.12, a boost interleaved converter is consisted of two switches  $S_1$  and  $S_2$ , which are IGBTs in this thesis and need a periodic pulse that should be applied between gate and emitter terminals to turn them on and off periodically, two inductors ( $L_1$ ,  $L_2$ ), and two diodes ( $D_1$ ,  $D_2$ ) which are connected to a common filter capacitor ( $C_0$ ) and load. Therefore, each inductor encounters with half current in comparison with conventional boost converters. Since, switches operate  $180^\circ$  out of phase, the inductors ripple currents are decreased by each other. The effective switching frequency is doubled while the input current is reduced. Thus, peak-to-peak variation in capacitor current is reduced as well which leads to use a smaller filter capacitor in comparison with a single boost converter with the same output voltage ripple. Smaller inductors and capacitor are needed; therefore, price and size of the inductors and capacitor are decreased significantly.

It can be seen from Fig. 1.12 that, voltage across each inductor when its switch is turned on and off is equal to  $V_{in}$  and  $V_{in}$ - $V_{out}$  respectively. These values are exactly the same as the boost converter which was discussed previously. The duty cycle of the switch, D, which relates the width of this periodic pulse to the length of the switching period, determines the ratio of the output to the input voltage. Converters that have this property are called pulsewidth modulated (PWM) converters. If the current through the inductor never drops to zero it would be operated in CCM (continuous current mode). The voltage gain of the boost converter in this condition is calculated as follows:

$$\frac{V_{out}}{V_{in}} = \frac{1}{1-D} \tag{1-3}$$

Fig. 1.12. Topology of a basic AC-DC interleaved boost converter

By using interleaving method, the input current of each module can be designed to be discontinuous (drops to zero) which leads to reduction of the size of the input inductors. This can be done, as interleaving can reduce the high ripple in each module and produce a net input current with a ripple that is comparable to that achieved with a single boost converter module with a large input inductor. In addition, there is less current stress on the converter components since they handle a fraction of the overall current, and the control is easier as more sophisticated control methods, which are needed for continuous current mode (CCM), are avoided.

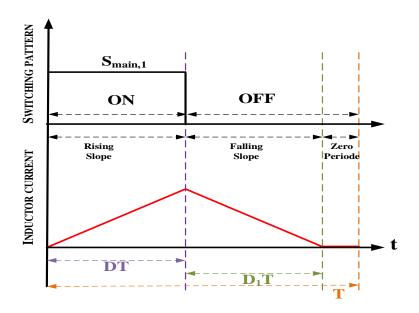

Besides, by operating interleaved boost converter in DCM, switches can be turned on with ZCS, reverse recovery losses of diodes are eliminated, and the small size inductances can also be used. However, the turn- off losses of the switches still exist and should be tackled by soft switching method, which is ZCS in this thesis and will be explained in the next chapter in more details. The inductor current waveforms are shown in Fig. 1.13, according to the switching pattern in the DCM for  $D \ge 0.5$  and D < 0.5.

Fig. 1.13. Inductor current waveforms according to the switching pattern in the DCM.

As can be seen from Fig. 1.13, inductor current ripple is reduced by using interleaved technique. Since an AC input source can be considered to be a DC input source during a very short switching cycle, different equations such as voltage gain can be derived by assuming input source as DC. In the following equations, DT and D<sub>1</sub>T are defined as the switching on-time and the time period in which the phase current becomes zero after DT respectively:

$$\frac{di_{L1,2}}{d_t} = \frac{V_{in}}{L_{1,2}} \quad \text{(rising slope)}$$

(1-4)

$$\frac{di_{L1,2}}{d_t} = \frac{V_{in} - V_{out}}{L_{1,2}} = \frac{-D V_{in}}{L_{1,2} D_1}$$

(falling slope) (1-5)

Voltage gain of the interleaved boost converter is obtained as follows:

$$\frac{V_{out}}{V_{in}} = \frac{D+D_1}{D_1} \tag{1-6}$$

As discussed before, half of the input current flows from each boost converter. Thus, the average diode current is obtained:

$$I_{D1,2} = \frac{1}{2} \left( \frac{V_{in}DT}{L_{1,2}} \right) D_1 = \frac{1}{2} \frac{V_{out}}{R}$$

(1-7)

By rearranging:

$$D_1 = \left(\frac{V_{out}}{V_{in}}\right) \frac{L}{RDT} \tag{1-8}$$

Substituting equ. (1-8) into equ. (1-6) results in:

$$\left(\frac{V_{out}}{V_{in}}\right)^2 - \left(\frac{V_{out}}{V_{in}}\right) - \frac{D^2 RT}{L_{1,2}} = 0 \tag{1-9}$$

In this thesis, by using an additional circuitry that is not a part of the main power circuit, ZCT is performed in an interleaved converter. As discussed previously, in the resonant-transition converter, the auxiliary switch operates only for a small portion of the switching cycle. Before turning each main switch off, the auxiliary switch is turned-on which makes a capacitor in the auxiliary circuit undergoes resonance with the auxiliary inductors. By resonating this capacitor, a negative voltage is imposed across the auxiliary inductor-switch, so the currents of the main switches force to be reduced to zero before the pulses at the gate of main switches are removed. Therefore, main switches can be turned -off with ZCS method. In the next section, some of the soft switching methods which have been proposed in the referred papers for interleaved converter will be presented.

#### 1.6 Literature Review

AC-DC converters with input power factor correction (PFC) that consist of two or more interleaved boost converter (IBC) modules are used widely in industry [1-18]. As it was discussed previously, soft-switching approaches for these converters can either be zero-voltage switching (ZVS) if they are implemented with MOSFETs or zero-current switching (ZCS) if implemented with IGBTs. The main idea of this thesis is performing ZCS condition for turning IGBTs on and off. Most of these use an auxiliary circuit that is activated whenever a main converter switch is about to be turned off, gradually diverting current away from the switch so that it can turn off with ZCS.

ZCS methods in boost converters have at least one of the following drawbacks [13-27]:

- The auxiliary circuit causes the main converter switch to operate with a higher peak current stress that creates a need for a higher rated device for the main switch.

- The auxiliary switch should be turned on for a long time which reduces the efficiency.

- The main switches or auxiliary switch need a floating driver which makes driving more complicated and increase the noise.

- Auxiliary circuit components must be placed in the main part of the converter so that the auxiliary circuit is not completely separated from the main converter. This means conduction losses can be increased and higher current rated components need to be used.

- Each module of an interleaved AC-DC boost converter must have its own ZCS auxiliary circuit to help its main switch to be turned-off with ZCS. This adds cost to the overall interleaved converter.

Now the above-mentioned drawbacks of the previous papers are explained by some sample papers.

ZCS-PWM converters that use an auxiliary circuit to help the main converter switch turnon with ZCS are generally less efficient than hard-switching converters at light loads. The

main reason for this is that the auxiliary circuit losses dominate when the converter is

operating under these conditions. Auxiliary circuit losses include the turning on and off of

the auxiliary switch and additional conduction losses as there can be an increased amount

of circulating current flowing in the converter. ZCS-PWM converters achieve their

improved efficiency over hard-switching converters at heavier loads when the main switch

switching losses that are eliminated - especially the IGBT current tail losses - are greater

than the auxiliary circuit losses.

Ideally, the auxiliary circuit used to achieve ZCS operation in a ZCS-PWM converter should be activated only when the converter is operating with heavier loads and not used when the converter is operating with light load. Operating the converter in such a manner would ensure the optimal efficiency profile over the entire load range. This, however, generally cannot be done with ZCS-PWM converters because of the presence of an inductor placed in series with the main switch. As can be seen in the example converters shown in Figs. 1.14 and 1.15, an inductor is typically placed in series with the main switch so that it can turn on with ZCS. The series inductor slows down the rate of rise in current after the switch has been turned on so that the overlap between voltage and current in this switch can be reduced.

Although the presence of this series inductor in a ZCS-PWM converter is beneficial, it prevents the auxiliary circuit from being disengaged from the main converter when the converter is operating under light load conditions. As long as this series inductor is in the converter, the auxiliary circuit must be used at all times, across the full load range – even when it is not necessary under light load conditions – because failure to do so would result in the damage of the main switch. Given the size of the series inductance, which may be relatively small compared to that of the input boost inductor but is not insignificant, the energy in this inductance would result in the appearance of high voltage spikes across the switch when it is turned off as there would be no path for current to flow through.

There are several possible solutions to the problem of having an inductor placed in series with the main switch, but none of them are truly satisfactory. It may be possible to place a bypass switch of some sort across the series inductor so that when the auxiliary circuit is not needed, the bypass switch would be turned on and current would bypass the inductor, but this would add cost and make the converter more complex.

Another possible solution is to implement the converter with an active auxiliary circuit and a passive snubber. With such a scheme, the active auxiliary circuit would be activated only when the converter is operating with heavier loads and the passive snubber would be used to deal with the series inductor energy when the main converter switch is turned off with the auxiliary circuit is disengaged from the main circuit. This approach would again increase the cost and the complexity of the converter.

If the main switch could somehow be made to turn on with ZCS without having an inductor in series with the main switch, then it would be possible to avoid using the auxiliary circuit when the converter is operating under light load conditions. This is, in fact, possible when the converter is operating with a discontinuous input inductor current. In such a case, the main converter switch would turn on with ZCS as initially there would be no current flowing through the switch. Current through the switch would rise gradually, given the size of the input boost inductor.

Discontinuous current mode operation is advantageous when a boost converter is implemented with two converter modules in parallel and the modules are interleaved with

respect to each other with a phase difference of 180°. Interleaving is commonly used as a means of reducing current ripple in power converters. In the scheme being described, if the individual converter modules are ZCS-PWM converters, then it would be possible to disengage the auxiliary circuit from the main circuit as there would be no need of a series inductance to help the main switch turn on with ZCS.

Fig. 1.14. ZCS boost converter proposed in [19]

Fig. 1.15. ZCS boost converter proposed in [20]

One of the basic topologies, which is shown in Fig. 1.16, has been presented in [14]. The main drawback is that, each module of the proposed interleaved AC-DC boost converter must have its own ZCS auxiliary circuit to help its main switch turn off with ZCS. Since two switches should be used, the price and complexity of the converter are increased. Another disadvantage of this topology is that, the converter in the absence of high-voltage conversion ratio does not have an appropriate ZCS. The next problem is that, each auxiliary switch should not be turned -off exactly after turning its main switch off. It means that, both of auxiliary switches need some time after turning their main switches off to be turned off with ZCS, which increases the conduction losses.

Fig. 1.16. Interleaved ZCT boost converter proposed in [14]

In the auxiliary circuit proposed in [16], main switches are turned on and off with ZVS and ZCS respectively. But one of the drawbacks of this topology is that, the resonant switch operates with hard switching. Besides, as it needs soft switching for turning the main switches on as well, the auxiliary switch should be operated four times in each switching cycle for turning on and off main switches which leads to higher switching losses.

Although the problem of hard switching of the auxiliary switch is solved in [11], yet it works like that of [16], which means that the auxiliary switch should be operated four times in each switching cycle to turn main switches on and off with ZVS and ZCS respectively.

Fig. 1.17. Interleaved ZVS/ZCS boost converter proposed in [16]

Another disadvantage of this topology is that, it needs a bulky clamping capacitor  $C_1$  which is placed in the path of the main power circuit, so the auxiliary circuit is not completely separated from the main converter. Therefore, the auxiliary circuit cannot be disengaged from the main power circuit in the light loads.

Fig. 1.18. Interleaved ZVS/ZCS boost converter proposed in [11]

In some papers such as [17], the auxiliary diodes are in series with the main power circuit. Since, these diodes should tolerate higher average current rating, their price and conduction losses are increased. In addition, maximum voltage across  $D_0$  in [17] is twice the output voltage. Also, as auxiliary inductor is in series with the main circuit path, maximum voltage across the main switches, auxiliary switch and the main diodes are higher than the output voltage.

Fig. 1.19. Interleaved ZCS boost converter proposed in [17]

The auxiliary circuit proposed in Paper [21] can be seen in Fig. 1.20, where voltages across  $D_{a1}$  and  $D_{a2}$  are twice the output voltage. The auxiliary inductor is in the path of the main power circuit therefor voltage across the main switches, auxiliary switch and main diodes are higher than the output voltage.

Since in the auxiliary circuit in [22], two switches do not share the common ground, auxiliary switch needs a floating gate driver, which increases the noise and complexity of the proposed circuit

The authors in [18] have used two inductors in series with the input inductors. Because auxiliary inductors are in the path of the main power circuit, voltage across the main switches and diodes are higher than the output voltage. Voltage across the auxiliary switch is almost two times of the output voltage

Fig. 1.20. Interleaved ZCS boost converter proposed in [21]

Fig. 1.21. ZCS boost converter proposed in [22]

Fig. 1.22. Interleaved ZCS boost converter proposed in [18]

## 1.7 Thesis Objectives

The main objectives of this thesis are as follows:

- To propose a novel AC-DC interleaved ZCS-PWM boost converter that does not have any drawbacks that mentioned for the converters reviewed in this chapter, without adding any new component in the main power path.

- To analyze the steady-state characteristic of the proposed converter by mathematical analysis so that it can be properly designed.

- To derive design procedure for the new interleaved converter which can be used for selecting the proper components

- To confirm the feasibility of the proposed converter proposed in this thesis by computer simulation and experimental results obtained from a proof-of-concept prototype.

#### 1.8 Thesis Outline

The thesis is organized as follows:

- In Chapter 2, the new interleaved boost converter which has a single auxiliary switch to perform ZCS for all switches will be introduced, its modes of operation will be explained and its features will be described.

- In Chapter 3, circuit analysis of the proposed converter will be analysed

mathematically based on the different modes of operation discussed in Chapter 2.

Then equations which describe the voltage and current of the different components

of the converter in steady-state will be derived.

- In Chapter 4, the results of the mathematical equations derived from the proposed interleaved converter in the steady-state condition in Chapter 3, will be used to determine the condition of operating main switches and auxiliary switch with ZCS. The characteristic curves for the key parameters of the proposed converter will be presented by applying the MATLAB simulations according to the steady-state equations. Effects of each key component on the operation of the converter will be discussed. Then, the design procedure will be explained by an example. By using characteristic curves generated by MATLAB program and the circuit simulator PSIM, the value of each component will be determined in order to satisfy the key design objectives. Selected values will be used in the next chapter to build a laboratory prototype.

- In Chapter 5, the design procedure discussed in Chapter 4 will be validated by the laboratory proof-of-concept prototype. The results of the voltages and currents obtained from Oscilloscope will be plotted. The efficiency of the proposed AC-DC interleaved ZCS-PWM boost converter will be compared with the conventional one.

- In Chapter 6, the content of this thesis will be summarized, and the conclusion will be presented. Then the main contributions of this thesis will be stated and suggestions for future works will be presented.

## Chapter 2

## 2 Modes of Operation of the Novel AC-DC Interleaved Boost Converter

#### 2.1 Introduction

As was explained in Chapter 1, interleaving multiple AC-DC converter modules is advantageous as input current ripple can be reduced and smaller input inductors can be used. If soft-switching is desired, then either ZVS or ZCS can be used, depending on what is used for the switching devices. If IGBTs are used, then ZCS is preferred as it eliminates the turn-off current tail that these devices have, which contributes to turn-off switching losses.

Previously proposed interleaved ZCS-PWM AC-DC converters have several drawbacks, including higher cost due to the need for multiple auxiliary circuits to help the main witches turn off with ZCS. A new interleaved ZCS-PWM AC-DC converter that does not have many of the drawbacks of previously proposed converters of the same type is proposed in this chapter. In this chapter, the general operation of the proposed converter is explained, its modes of operation are discussed in detail, and its features are stated.

## 2.2 Modes of Operation

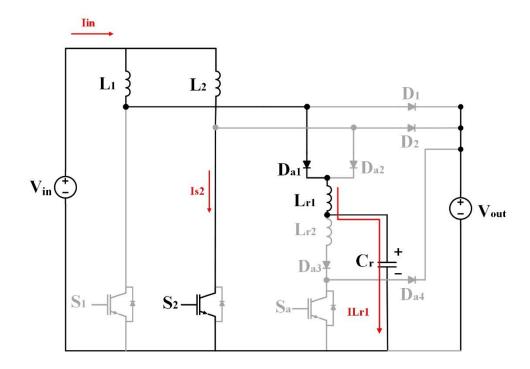

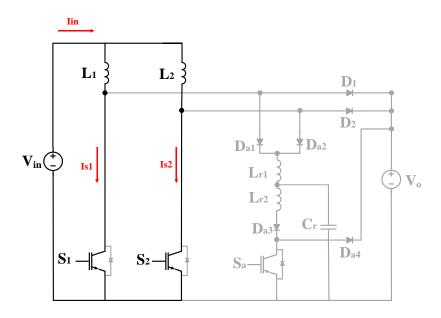

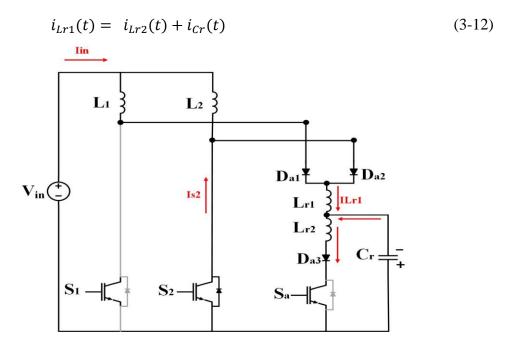

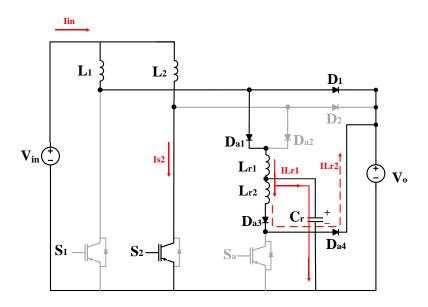

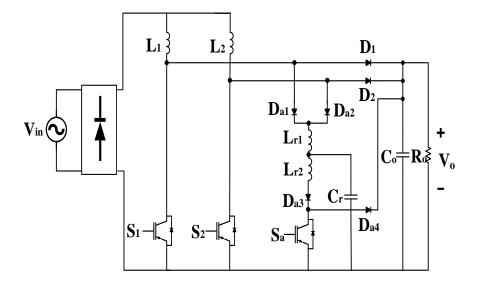

The proposed converter, shown in Fig. 2.1, consists of two boost converter modules, one with  $L_1$ ,  $S_1$ , and  $D_1$ , the other with  $L_2$ ,  $S_2$  and  $D_2$ . The gating signals of the two main switches,  $S_1$  and  $S_2$  are identical but shifted  $180^\circ$  with respect to each other. The currents in  $L_1$  and  $L_2$  are designed to be discontinuous and identical, with  $180^\circ$  phase shift with respect to each other. The two boost modules are connected to the same auxiliary circuit, which consists of interfacing diodes  $D_{a1}$  and  $D_{a2}$ , reverse blocking diode  $D_{a3}$ , switch voltage clamping diode  $D_{a4}$ , resonant inductors  $L_{r1}$  and  $L_{r2}$  and resonant capacitor  $C_{r1}$ . The auxiliary switch needs to be activated whenever one of the two main switches is about to be turned off and is active for only a fraction of the switching cycle.

The various modes of operation that the proposed converter goes through during a switching cycle are explained in this section. The modes of operation are studied for the case when the converter is operating in steady-state, which can be defined as the converter components having the same voltage and current at the end of a switching cycle (and the start of a new one) as thy have at the start of the cycle. In other words, the voltage and

Fig. 2.1. Proposed interleaved AC-DC ZCS-PWM boost converter

current waveforms of all components of the proposed interleaved converter should be identical for every switching cycle when the converter is operating in steady-state.

Typical voltage and current waveforms of the proposed converter are shown in Fig. 2.2 and equivalent circuit diagrams of each mode are shown in Figs. 2.3 to 2.9 for a half switching cycle, for the case when duty cycle  $D \ge 0.5$  and  $S_2$  is turned on and  $S_1$  is turned off. The modes of operation for the other half-cycle when  $S_1$  is turned on and  $S_2$  is turned off are identical. The following assumptions have been made in Figs. 2.3-2.9:

- The proposed circuit has two boost modules that are designed to be operated in DCM so that the input inductor current of each module is discontinuous, but the input current, which is the sum of the inductor currents, is continuous.

- Since the AC input source voltage is equivalent to a DC voltage during a very short amount of time such as a switching cycle, it is considered as a DC input voltage.

- The output filter capacitor, C<sub>o</sub>, is large enough to be considered as a voltage source, V<sub>o</sub>.

- All semiconductor switches are ideal with no parallel output switch capacitor across them.

- All inductors and capacitors are ideal and have negligible resistances.

- All diodes are ideal and have no reverse recovery current.

- The duty cycle D is greater or equal to 0.5.

**Mode 1** (**T**<sub>0</sub> < **t** < **T**<sub>1</sub>): This mode begins when switch  $S_2$  is turned on. The rectified voltage is applied to  $L_2$  and the current through the  $L_2$  linearly increases as does the input current in the input inductor  $I_{in}$ . The slope of the current is  $\frac{V_{in}}{L_2}$ . Since  $I_{in}$  is the summation of the  $I_{L1}$  and  $I_{L2}$ , it will increase with greater slope.

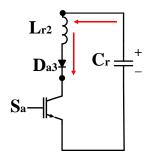

**Mode 2 (T**<sub>1</sub> < t < T<sub>2</sub>): This mode begins when the auxiliary switch ( $S_a$ ) is turned on in preparation to turn off main switch  $S_1$  with ZCS.  $S_a$  turns on with ZCS because  $L_{r2}$  limits the rise of the switch current. After  $S_a$  is turned on,  $C_r$  starts to resonate with  $L_{r2}$  so that the current in  $L_{r2}$  rises while the voltage across  $C_r$  decreases.

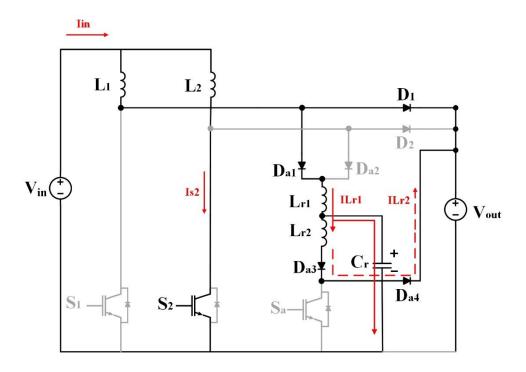

**Mode 3** ( $T_2 < t < T_3$ ): This mode begins when the voltage across  $C_r$ ,  $V_{Cr}$ , is zero. During this mode,  $V_{cr}$  is charged to a negative voltage and  $D_{a1}$  and  $D_{a2}$  start to conduct. The voltage

across  $D_1$  and  $D_2$  is limited to the output voltage. The current through  $L_{r1}$  increases, thus  $I_{L1}$  and  $I_{L2}$  flow through the  $L_{r1}$ . The current in  $L_2$  is less than  $L_1$ , thus the current through  $S_1$  becomes zero and  $S_1$  can be turned off with ZCS. The current through  $S_2$  becomes negative and flows through its body diode.

Mode 4 (T<sub>3</sub> < t < T<sub>4</sub>): This mode begins when the current in  $L_{r2}$  reaches zero because of its resonance with  $C_r$ ;  $S_a$  can then be turned off with ZCS condition. During this mode, energy in  $L_{r1}$  is transferred to  $C_r$ , thus increasing its voltage so that  $V_{Cr}$  becomes less negative and is in the process of eventually becoming positive.

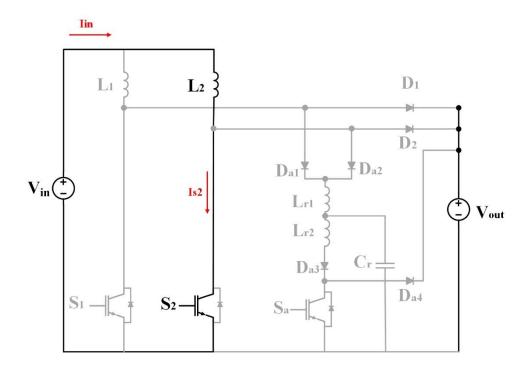

**Mode 5 (T<sub>4</sub> < t < T<sub>5</sub>):** This mode begins when the net voltage across the  $C_r$  and  $L_{r1}$  becomes positive, thus auxiliary diode  $D_{a2}$  stops conducting and  $I_{L2}$  flows through  $S_2$ .  $D_{a1}$  continues to conduct during this mode.

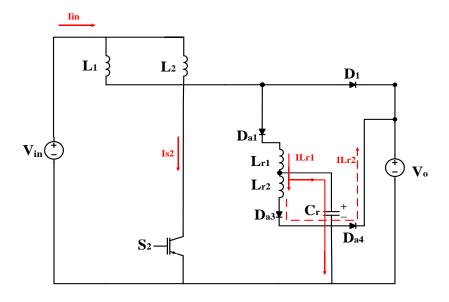

**Mode 6** (**T**<sub>5</sub> < **t** < **T**<sub>6</sub>): This mode begins when  $V_{Cr}$  reaches the output voltage  $V_o$ .  $D_4$  clamps the voltage across the auxiliary switch to  $V_o$  as well and the stored energy in  $L_{r1}$  is transferred to the output so that the current in the  $L_{r1}$  decreases. When the current through  $L_{r1}$  becomes less than  $I_{L1}$ , diode  $D_1$  starts to carry the current difference. The voltage across  $L_1$  becomes ( $V_o$ - $V_{rec}$ ) and the current through  $L_1$  starts to decrease linearly.

**Mode 7** ( $T_6 < t < T_7$ ): This mode begins when the current in  $L_1$  reaches zero. This is the last mode of the half-cycle. The next half-cycle begins when  $S_1$  is turned on under ZCS.

When D is less than 0.5, the modes of operation of the converter are identical to those shown in Figs. 2.3-2.9 except for Mode 1 when only switch  $S_1$  is on.

The proposed converter has the following features:

- (i) All the converter switches turn on and off with ZCS.

- (ii) There is only one active auxiliary circuit for both main switches instead of each main switch needing its own active auxiliary circuit to help it turn off with ZCS.

- (iii) The main switch does not have increased peak and RMS current stresses as it the case with resonant type ZCS auxiliary circuits because no current from the auxiliary circuit flows into the main circuit.

- (iv) None of the auxiliary circuit components are in the main power path so that they only handle a fraction of the current that the main circuit components handle.

- (v) The voltage stress of the auxiliary switch is clamped to the output voltage and does not exceed this voltage.

- (vi) The main boost diodes do not have reverse recovery current as the input inductor currents are discontinuous.

- (vii) The auxiliary circuit does not interfere with the interleaving operation of the converter thus all the advantages of interleaving are maintained.

- (viii) The auxiliary circuit can be deactivated when the converter is operating under light-load conditions, unlike most ZCS methods, where the auxiliary circuit must always be in operation, regardless of the load; thus light-load efficiency is improved because there is no auxiliary circuit component in the main power circuit.

Fig. 2.2. Voltage and current waveforms of different circuit components of the proposed interleaved boost converter in steady state.

Fig. 2.3. Current flow in Mode 1

Fig. 2.4. Current flow in Mode 2

Fig. 2.5. Current flow in Mode 3

Fig. 2.6. Current flow in Mode 4

Fig. 2.7. Current flow in Mode 5

Fig. 2.8. Current flow in Mode 6

Fig. 2.9. Current flow in Mode 7

#### 2.3 Conclusion

In this chapter, the modes of operation of the proposed PWM interleaved AC-DC boost converter which uses only a single active auxiliary circuit to assist all the main converter switches operate with ZCS and operates with ZCS itself was proposed. It was shown that the proposed circuit has fourteen intervals in each switching cycle which can be divided into two identical half cycles. Then seven different modes of operation which are distinct from each other in terms of the voltage across and current through the different components were illustrated. As it was shown, the auxiliary switch works in a very small instant of time in comparison with the switching cycle. Thus, except during a small fraction of the switching cycle, the proposed converter operates as a conventional PWM interleaved boost converter. The modes of operation, which were stated in this chapter, will be used for deriving mathematical equations in the next chapter.

## Chapter 3

# 3 Circuit Analysis of the Novel AC-DC Interleaved Boost Converter

#### 3.1 Introduction

The modes of operations that the proposed AC-DC interleaved ZCS boost converter goes through during a switching cycle were discussed in the previous chapter. In this chapter, mathematical equations of each mode in steady- state are derived to demonstrate the effects of the proposed auxiliary circuit on each component. These equations can be used to determine the parameters that should be met to satisfy the ZCS conditions. Thus, characteristic behaviors of different components are specified so as to use in design analysis. It should be noted that, since during the most intervals, the proposed interleaved converter operates like that of a conventional one, only the equations for the time in which the auxiliary circuit operates will be derived.

### 3.2 Circuit Analysis

The equations are derived based on the following assumptions:

- The input inductor current of each module is discontinuous, while the input current of the converter is continuous.

- The input voltage of the proposed converter can be assumed to be DC. This assumption

is valid as the AC source can be considered to be DC during a switching cycle as the

duration is of this cycle is much shorter than that of the line cycle.

- The output filter capacitor, C<sub>o</sub>, is large enough to be considered as a voltage source V<sub>o</sub>.

- All semiconductor switches are ideal, which means that they have no conduction losses and no parallel capacitor across them.

- All inductors and capacitors are ideal and have negligible resistance.

- All diodes are ideal with negligible reverse recovery time and forward voltage drop.

The analysis in this chapter is done with  $D \ge 0.5$ ,  $S_2$  turned on, and  $S_1$  turned off; the analysis and formulas for the other half-cycle when  $S_1$  is turned on and  $S_2$  is turned off is identical.

The following figure shows the equivalent circuit for Mode 1:

Fig. 3.1. Currents flow in Mode 1

When switch  $S_2$  is turned on, the rectified voltage is applied to  $L_2$  and this leads to a gradual increase of the current through  $L_2$  and the input current in the input inductor,  $I_{in}$ . The slope of  $L_2$ , which is equal to the slope of  $S_2$ , rises according to:

$$V_{in} = L_2 \frac{dIL_2(t)}{dt} \tag{3-1}$$

By integrating from time T<sub>0</sub> to T<sub>1</sub>, the main switch current can be expressed as

$$I_{S2}(t) = \frac{V_{in}}{L_2} (T_1 - T_0)$$

(3-2)

Fig. 3.2. Reduced equivalent circuit of Mode 1

All the input current goes through  $S_1$  and  $S_2$  so that

$$I_{in} = I_{S1} + I_{S2} \tag{3-3}$$

The next mode begins when the auxiliary switch  $(S_a)$  is turned on in preparation for the ZCS turn-off of main switch  $S_1$ . The equivalent circuit diagram at time  $T_2$  is shown in Fig. 3.3. This diagram can be further simplified in order to demonstrate the auxiliary circuit current during this mode of operation as shown in Fig. 3.4.

Fig. 3.3. Current flow in Mode 2

By applying KVL in Fig. 3.4, the following equation can be obtained:

$$V_{Cr}(t) = L_{r2} \frac{d}{dt} i_2(t)$$

(3-4)

Fig. 3.4. Reduced equivalent circuit of the auxiliary circuit of Mode 2

By applying KCL in Fig. 3.4, the following equation can be obtained:

$$i_{Lr2}(t) = i_{Cr}(t) = -\frac{d}{dt} q_{Cr}(t) = -C_r \frac{d}{dt} V_{Cr}(t)$$

(3-5)

By substituting equ. (3-5) into equ. (3-4), the following result can be obtained:

$$V_{Cr}(t) = -L_{r2} C_r \frac{d^2}{dt^2} V_{Cr}(t)$$

(3-6)

In order to solve the above- mentioned equations, the initial capacitor voltage  $V_{cr}(0)$  and the initial auxiliary inductor  $i_{Lr2}(0)$  should be defined.  $V_{cr}(0)$  is assumed to be equal to  $V_{o}$  and  $i_{Lr2}(0)$  is equal to zero in this mode. As a result, the derivative of the capacitor voltage  $dV_{cr}(0)/dt$  can be determined to be:

$$\left[\frac{d}{dt}V_{Cr}(t)\right]_{t=0} = -\left(\frac{1}{C_r}\right)\left[\frac{d}{dt}q_{Cr}(t)\right]_{t=0} = \left(\frac{1}{C_r}\right)\left[i_{Lr2}(t)\right]_{t=0}$$

$$= 0$$

(3-7)

By using equ. (3-7) into equ. (3-6), the following can be obtained:

$$V_{Cr}(t) = V_0 \cos \omega_2 t \text{ for } T_1 < t < T_2$$

(3-8)

Based on the initial conditions of this mode, the following equation can be written:

$$i_{Lr2}(t) = i_{Cr}(t) = -C_r \frac{d}{dt} V_{Cr}(t) = C_r V_o \omega_2 \sin \omega_2 t$$

(3-9)

$$= \frac{V_0}{Z_2} \sin \omega_2 t \qquad \qquad \text{for } T_1 < t < T_2$$

In the above equation,  $\omega_2 = \frac{1}{\sqrt{L_{r2}C_r}}$  and the characteristic impedance of the auxiliary circuit is defined as  $Z_2 = \sqrt{\frac{L_{r2}}{C_r}}$ . Mode 2 is finished when the voltage of the auxiliary capacitor  $V_{cr}$  reaches zero; therefore, the duration of this mode can be calculated by making equ. (3-8), equal to zero as follows:

$$V_{Cr}(t) = V_0 \cos \omega_2 t = 0 \text{ for } t = T_2$$

(3-10a)

where

$$\omega_2 t = \frac{\pi}{2}$$

$$T_2 - T_1 = \frac{\pi}{2} \sqrt{L_{r2}C_r}$$

(3-10b)

Thus the current at  $t=T_2$ , which is the time in which the maximum current flows through the auxiliary circuit, can be determined to be

$$i_{Lr2}(t) = i_{Lr2}(T_2) = \frac{V_o}{Z_2} \sin \omega_2 t$$

(3-11)

$$i_{Lr2}(T_2) = \frac{V_0}{Z_2} \qquad \text{for } t = T_2$$

The next mode begins when the voltage across the resonant capacitor is zero. During this mode,  $V_{cr}$  is charged to a negative voltage and  $D_{a1}$  and  $D_{a2}$  begin to conduct. In Mode 3, current through the main switch  $S_1$  and auxiliary  $S_a$  switch should go to zero or negative before turning them off so that this is done with ZCS.

The equivalent circuit diagram at time  $T_2$  is shown in Fig. 3.5; it can be be further simplified as shown in Fig. 3.6:

Fig. 3.5. Current flow in Mode 3

It can be seen from the Fig. 3.6 that

Fig. 3.6. Reduced equivalent circuit of Mode 3

Initial conditions for Mode 3, which should be derived from the previous mode, show that the initial value of voltage across the auxiliary capacitor  $V_{Cr}$  (t<sub>2</sub>) and current through the auxiliary inductor  $i_{Lr1}$  (t<sub>2</sub>) are zero, while the initial current through the second auxiliary inductor  $i_{Lr2}$  (t<sub>2</sub>) in this mode is equal to

$$i_{Lr2}(T_2) = \frac{V_o}{Z_2} \tag{3-13}$$

Since D<sub>a3</sub> is conducting, the voltage across auxiliary circuit inductor L<sub>r2</sub> is

$$V_{Lr2} = V_{Cr} \tag{3-14}$$

Since  $D_{a2}$  is conducting the voltage across auxiliary circuit inductor  $L_{r1}$  is

$$V_{Lr1} = -V_{Lr2} = -V_{Cr} (3-15)$$

By differentiating equ. (3-12) with respect to time, the following equation is obtained:

$$\frac{d}{dt}i_{Lr1}(t) = \frac{d}{dt}i_{Lr2}(t) + \frac{d}{dt}i_{Cr}(t)$$

(3-16a)

which can be rewritten as

$$\frac{V_{Lr1}}{L_{r1}}(t) = \frac{V_{Lr2}}{L_{r2}}(t) + C_r \frac{d^2}{dt^2} V_{Cr}(t)$$

(3-16b)

By substituting equ. (3-15) into equ. (3-16b), the following result is obtained:

$$\frac{V_{Cr}}{L_{r1}}(t) + \frac{V_{Cr}}{L_{r2}}(t) + C_r \frac{d^2}{dt^2} V_{Cr}(t) = 0$$

(3-16c)

which can be rewritten as

$$\frac{V_{Cr}}{L_{r1}}(t)\frac{L_{r2}}{L_{r2}} + \frac{V_{Cr}}{L_{r2}}(t)\frac{L_{r1}}{L_{r1}} + C_r\frac{d^2}{dt^2}V_{Cr}(t) = 0$$

(3-16d)

$$\frac{V_{Cr}(L_{r1} + L_{r2})}{L_{r1}L_{r2}}(t) + C_r \frac{d^2}{dt^2} V_{Cr}(t) = 0$$

(3-16e)

By defining  $L_{eq} = \frac{L_{r_1}L_{r_2}}{L_{r_1}+L_{r_2}}$ , equ. (3-16e) can be simplified to

$$\frac{V_{Cr}}{L_{eq}}(t) + C_r \frac{d^2}{dt^2} V_{Cr}(t) = 0$$

(3-16f)

which is equal to

$$\frac{V_{Cr}}{L_{eq}}(t) = -C_r \frac{d^2}{dt^2} V_{Cr}(t)$$

(3-16g)

and be rearranged to be

$$\frac{V_{Cr}}{L_{eq}C_r}(t) = -\frac{d^2}{dt^2}V_{Cr}(t)$$

(3-16h)

By defining  $\omega_e = \frac{1}{\sqrt{L_{eq}C_r}}$  and substituting it into equ. (3-16h), the following equation can be obtained:

$$V_{Cr}(t)\omega_e^2 = -\frac{d^2}{dt^2}V_{Cr}(t)$$

(3-16i)

As mentioned previously, the initial voltage of the auxiliary capacitor is zero. The derivative of the initial magnitude of the auxiliary capacitor can be determined to be:

$$\left[\frac{d}{dt}V_{Cr}(t)\right]_{t=0} = -\left(\frac{1}{C_r}\right)\left[\frac{d}{dt}q_{Cr}(t)\right]_{t=0} = -\left(\frac{1}{C_r}\right)\left[i_{Lr2}(t)\right]_{t=0}$$

(3-17)

Substituting equ. (3-13) into equ. (3-17) results in

$$\left[\frac{d}{dt}V_{Cr}(t)\right]_{t=0} = -\left(\frac{V_0}{Z_2C_r}\right)$$

(3-18)

and by using equ. (3-16i), the voltage across capacitor Cr can be determined to be:

$$V_{cr}(t) = -\left(\frac{V_o}{\sqrt{\left(1 + \frac{L_{r2}}{L_{r1}}\right)}}\right) \sin \omega_e t$$

(3-19)

Applying KVL to Fig. 3.6 results in:

$$V_{Lr1}(t) = -V_{Cr}(t) = -V_{Lr2}(t)$$

(3-20a)

Since the voltage across an inductor is generally related to the derivative of the current through it, this can be rewritten as

$$L_{r1}\frac{d}{dt}i_{Lr1}(t) = -L_{r2}\frac{d}{dt}i_{Lr2}(t)$$

(3-20b)

Substituting equ. (3-20a) into equ. (3-20b) results in

$$\frac{d}{dt}i_{Lr1}(t) = -\frac{V_{Cr}}{L_{r1}}(t)$$

(3-20c)

which can be rewritten as:

$$di_{Lr1}(t) = -\left(\frac{V_{Cr}}{L_{r1}}(t)\right)dt$$

(3-20d)

The above equation can be solved by integrating it during the interval of this mode of operation. The initial magnitude of the auxiliary inductor  $I_{Lr1}$ , which is equal to zero, can be derived from the previous mode as shown in Fig. 3.3 and is

$$i_{Lr1}(t) = \left(\frac{V_o L_{eq}}{Z_2 L_{r1}}\right) (1 - \cos \omega_e t)$$

(3-20e)

During this mode of operation,  $I_{S1}$  should go to zero or negative in order to meet the ZCS condition; thus the direction of current through  $S_1$  is changed and flows through its body

diode. Based on Fig. 3.6, the following condition should be satisfied to ensure the soft switching of  $S_1$ :

prerequisite of ZCS of

$$I_{S1}$$

:  $i_{in}(t) - i_{Lr1}(t) \le 0$  (3-21a)

This means that current through  $i_{Lr1}$  should be more than  $i_{in}(t)$ . Substituting equ. (3-20e) into equ. (3-21a) results in

$$i_{in}(t) - \left[ \left( \frac{V_o L_{eq}}{Z_2 L_{r_1}} \right) (1 - \cos \omega_e t) \right] \le 0$$

(3-21b)

By applying KVL to Fig. 3.6, the following expression can be written:

$$V_{Cr}(t) = L_{r2} \frac{d}{dt} i_{Lr2}(t)$$

(3-22a)

which can be rewritten as

$$di_{Lr2}(t) = \left(\frac{V_{Cr}}{L_{r2}}(t)\right)dt \tag{3-22b}$$

Based on equ. (3-13), the initial current through the second auxiliary inductor  $i_{Lr2}$  (t<sub>2</sub>) in this mode is equal to  $i_{Lr2}(T_2) = \frac{V_0}{Z_2}$ . By substituting equ. (3-19) into equ. (3-22b), the current through the  $L_{r2}$  can be determined to be:

$$i_{Lr2}(t) = \frac{V_o}{Z_2} - \left[ \left( \frac{V_o L_{eq}}{Z_2 L_{r2}} \right) (1 - \cos \omega_e t) \right]$$

(3-22c)

As explained in Chapter 2, auxiliary switch  $S_a$  is turned on to help the main switches turn off with ZCS and it should be turned off soon afterwards. At the end of this mode of operation,  $I_{Sa}$  should go to zero or become negative so that it turns off with ZCS as well. It can be seen from Fig. 3.6 that

$$I_{Sa}(t) = i_{Lr2}(t)$$

(3-23)

In order to turn off the auxiliary switch,  $S_a$ , with ZCS,  $i_{Lr2}(t)$  should be zero or negative; this can be expressed as:

prerequisit of ZCS of

$$I_{Sa}$$

:  $I_{Sa}(t) = i_{Lr2}(t) \le 0$  (3-24a)

Substituting equ. (3-22c) into equ. (3-24a) results in

$$\frac{V_o}{Z_2} - \left[ \left( \frac{V_o L_{eq}}{Z_2 L_{r2}} \right) (1 - \cos \omega_e t) \right] \le 0 \tag{3-24b}$$

The voltage across the main diodes,  $V_{D1}$  and  $V_{D2}$ , can be derived based on the KVL in Fig. 3.5 to be

$$V_{D2} + V_o = 0 (3-25)$$

$$V_{D1} - V_{Cr} - V_{Lr1} + V_0 = 0 (3-26a)$$

Based on equ. (3-15) during this mode,  $V_{Lr1} = -V_{Cr}$ , so that equ (3-26a) can be rewritten as

$$V_{D1} + V_0 = 0 (3-26b)$$

The above-mentioned equations show that, in this mode of operation, the voltage across each main boost diodes are equal to the output voltage. This is one of the advantages of this topology that the maximum voltage across the main diodes is equal to the output voltage.