### PERFORMANCE LIMITATIONS IN WIDE

## SUPERSCALAR PROCESSORS

By

### ASWIN RAMACHANDRAN

Bachelor of Engineering in Electronics and Communication University of Madras Madras, Tamil Nadu 2001

Master of Science in Electrical Engineering Oklahoma State University Stillwater, OK 2003

> Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY December, 2008

# PERFORMANCE LIMITATIONS IN WIDE

# SUPERSCALAR PROCESSORS

Dissertation Approved:

Dr. Louis G. Johnson

Dissertation Adviser

Dr. R. G. Ramakumar

Dr. Marvin Stone

Dr. Charles Bunting

Dr. Sohum Sohoni

Dr. A. Gordon Emslie

Dean of the Graduate College

Dedicated to my mother

#### ACKNOWLEDGEMENTS

As Abraham Lincoln quipped, "*It's not the years in your life that count. It's the life in your years.*" My life seemed to attain a meaning only after I met a few wonderful people. As my meager mind realizes, these people not only inspired and motivated me but also shared a portion of their life.

Following a chronological order, the influence my parents and my grandmother have on me is significant. My grandmother's determination to raise four children with modest income and my parents' hard work to provide a good education for their children is something that makes me wonder everyday. My elder brother's excellence in education also induced a spirit of motivation in me – may be this is what is known in animal kingdom as *Sibling Rivalry!* My high school teacher of Chemistry is an epitome of hard work and it is through him that I learned to channelize and try to time myself properly.

Life at Oklahoma State University brought exciting opportunities that I would have never experienced if it were not so. I still remember the day when I walked into Dr. Marvin Stone's sensor lab and the research work that I undertook with interest for the next two years. Just watching him at work is enough to motivate a person. Dr. Rama Ramkumar's witty comments always made me look to the other side of life and Dr. Sohum Sohoni's suggestions always kept me to improve and to achieve more.

Besides research, I experienced a new phase of graduate school when I began to teach! Dr. Charles Bunting's unmatched enthusiasm for students and in research has always been a tremendous inspiration to me. I began to enjoy the art of teaching and continued it for about 9 semesters.

My first chance to meet Dr. Louis Johnson came through the digital VLSI class that I had taken under him. Further, I continued with my *master's* thesis on digital CMOS design. The class on *Superscalar* processors that intrigued me a lot, especially on a rename-register file design. I had suggested some design enhancements then that I never thought that I would later incorporate them in my dissertation work. We would discuss for several hours in his office about design aspects in computer architecture. Later, these discussions formed the basis of my dissertation. Dr. Louis Johnson has a profound impact on my life and will continue to be so for which I'm indebted to him forever.

Apart from growing in my school life, my friends circle also began to grow. Interestingly, as I look back, I have found friends at all ages from 8 to 80 years. I try to work with the international friends' ministry in a local church and also practice taekwondo both of which expanded my circle of friends in the community of Stillwater.

The joy and qualities of some of my friends, Gerard, Simon, Rajaguru, Vijayaraja, Majunu, Aravind, Grisha, Shyam and many others are remarkable. The help from Bob and Bettie through the church ministry played a significant role. I also enjoy the childlike playful times with Robert and inspiration thoughts from Marley and Mei Ling. All these people and many more have made my life meaningful and beautiful.

# TABLE OF CONTENTS

| Chapters                                                  | Page |

|-----------------------------------------------------------|------|

| INTRODUCTION I                                            | 1    |

| 1.1. Performance Studies                                  | 1    |

| 1.2. Motivation                                           | 2    |

| 1.3. Cycle-Accurate Simulation Engine Concept             | 5    |

| 1.3.1 Processing Elements and Signals:                    | 5    |

| 1.3.2 Buffer Design:                                      | 5    |

| 1.4. Implementation of the Clocked Buffer Model           | 7    |

| 1.4.1 Module Interfaces through Port Definitions:         |      |

| 1.4.2 Register and Memory Element Interface Model:        |      |

| 1.4. Organization of this Dissertation                    |      |

| LITERATURE REVIEW II                                      |      |

|                                                           |      |

| 2.1 Simulation                                            |      |

| 2.2 Simplescalar Tools                                    |      |

| 2.3 Liberty Simulation Environment                        |      |

| 2.5. 1 UNISIM                                             |      |

| 2.5.2 .ArchC                                              |      |

| SIMULATOR PERFORMANCE III                                 |      |

| 3.1 Simulator Design                                      |      |

| 3.2 Comparison with Superscalar Designs                   |      |

| 3.3 Comparison of Simulation Speed                        |      |

| 3.4 Discussion                                            |      |

| SUPERSCALAR ARCHITECTURE MODEL IV                         |      |

| 4.1 SUPERSCALAR DESIGN                                    |      |

| 4.2 Store Buffer and Load Dependence Prediction Mechanism |      |

| 4.2.1 Load – Store Address Dependence Prediction          |      |

| 4.3 Summary                                               |      |

| WRITE-BACK BUS MODEL V                                                           | 56  |

|----------------------------------------------------------------------------------|-----|

| 5.1 Related Work                                                                 | 57  |

| 5.2 Write-Back Bus Model                                                         |     |

| 5.2.3. Distribution of Write-Back Bus Size:                                      | 61  |

| 5.3 Write-Back Scheduling Logic                                                  | 63  |

| 5.3.1. First-In First-Out (FIFO):                                                | 63  |

| 5.3.2. Round-Robin (RR):                                                         |     |

| 5.3.3. Priority to Load/Store, Multiply/Divide and ALU instructions (LMA):       | 66  |

| 5.3.4. Priority to the instruction that has Highly Dependent Instructions (PHD): |     |

| 5.3.5. Priority to Program Order Instructions (PO):                              | 70  |

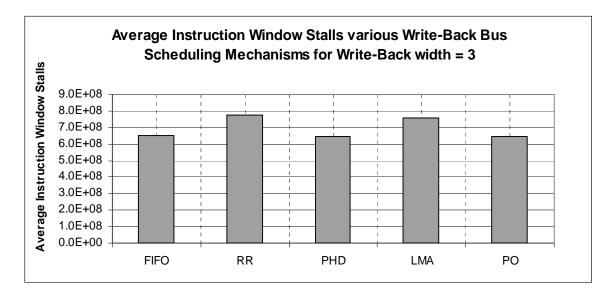

| 5. 4. Simulation Methodology and Implication of scheduler mechanisms             |     |

| 5.4.1. Round-Robin Schedule (RR):                                                |     |

| 5.4.2. FIFO Write-Back Bus Scheduler:                                            |     |

| 5.4.3. Priority to High Dependence (PHD) Write-Back Bus Scheduler:               |     |

| 5.4.4. Load-Multiply-ALU (LMA) Write-Back Bus Scheduler:                         |     |

| 5.5 Summary                                                                      | 76  |

| CONTROL DEPENDENT LIMITATIONS VI                                                 | 77  |

| 6.1 Program Dependencies                                                         | 77  |

| 6.1.1 Higher IPC with Superscalars                                               |     |

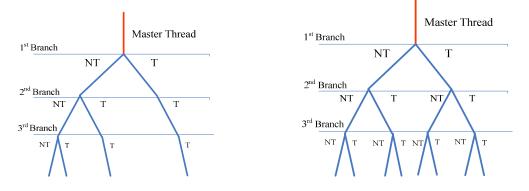

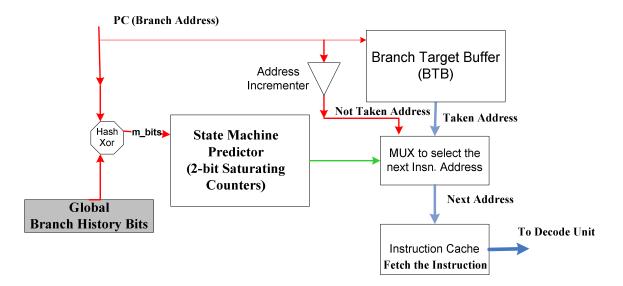

| 6.2 Multi-Path Execution Schemes                                                 |     |

| CONLCUDING REMARKS VII                                                           | 112 |

| REFERENCES                                                                       | 115 |

| APPENDIX                                                                         | 119 |

# LIST OF TABLES

| Table                                                                           | Page |

|---------------------------------------------------------------------------------|------|

| 3.1 Event-Driven Simulation Process                                             | 21   |

| 3.2 Simulation Details of the three different simulation models                 | 29   |

| 4.1. Summary of description on the fields of the Instruction Window             | 39   |

| 5.1 Instruction Wake-Up Frequency Using                                         | 69   |

| Round Robin Write-Back Scheduler                                                | 69   |

| 5.2 Microarchitecture Details of the Simulated Processor                        | 71   |

| 5.3 Improvement in IPC                                                          | 73   |

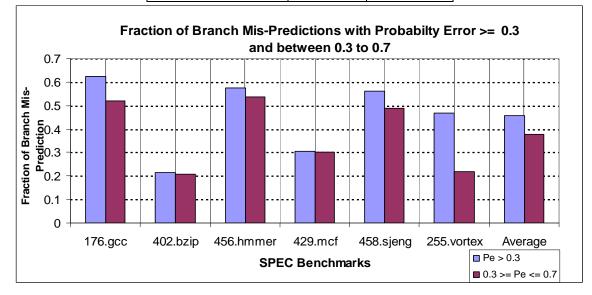

| 6.1 Probability of Misprediction                                                | 79   |

| 6.2 Calculated IPC using equ(6.2) for Branch Prediction                         | 82   |

| 6.3 Probability of Branch Prediction Error for 3 billion Completed Instructions | 84   |

| 6.4 Comparison of fetch policy schemes that are evaluated in this study         | 99   |

| 6.5. Simulation Details of the Multi-Path SMT Architecture                      | 101  |

# LIST OF FLOW CHARTS

| Flow Chart                      | Page |

|---------------------------------|------|

| 4.1 Fetch Functional Module     |      |

| 4.2 Dispatch Logic              |      |

| 4.3 Execute Stage               |      |

| 4.4 Finish Stage Logic          |      |

| 4.5 Complete Stage Logic        |      |

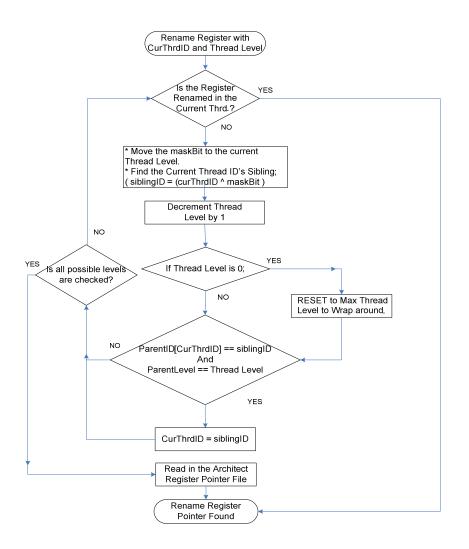

| 6.1 Thread Rename Pointer Logic |      |

# LIST OF FIGURES

| Figure Page                                                                                                |

|------------------------------------------------------------------------------------------------------------|

| 1.1 Structure of a Simple Data Path Representation                                                         |

| 1.2. Relationship between IPCin and IPCout                                                                 |

| 1.3. Pipeline Register Interface Model. A and B are modules defining the functionality of the architecture |

| 1.4. Module Interface                                                                                      |

| 1.5. Improved Mechanism with Global Pointers for Global Data Structures                                    |

| 1.6. Memory Access through Ports                                                                           |

| 1.7. Port Access for a Memory Element 12                                                                   |

| 2.1 Port Communications in Liberty, Vaccharajani et. al. [3], 2002                                         |

| 3.1 Objectives of a Microarchitecture Simulator                                                            |

| 3.2 Module Executions                                                                                      |

| 3.3 Design Flow of Simulation                                                                              |

| 3.4 Performance Comparison between the Simulators for a simple 3-stage scalar MIPS architecture            |

| 3.5 Comparison of Simulator Through-put                                                                    |

| 3.6 Simulated Superscalar Architecture                                                                     |

| 3.7 Comparison of Simulator Performance for a Superscalar Architecture Model                               |

| 3.8. Illustration of Module Port Communication                                                             |

| 4.1 Design of Rename Register Logic                                                                        |

| 4.2 Fields of Instruction Window Entry                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------|

| 4.3. Functional Block Diagram of the Issue Logic 42                                                                                    |

| 4.4. Functional Block Diagram of the Execute Stage                                                                                     |

| 4.5 Load Finish and Store Buffer Models                                                                                                |

| 4.6 No. of Load Forwarding and Memory Recoveries with destination memory address<br>prediction and instruction address (PC) prediction |

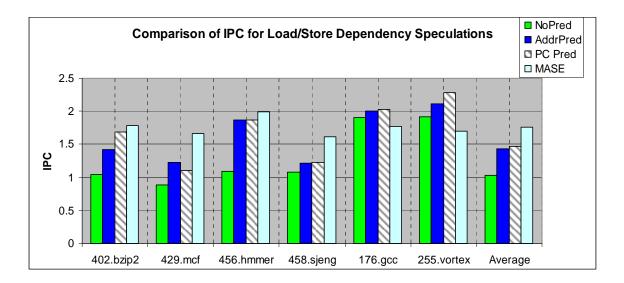

| 4.7 IPC with and without Load-Store Dependence Prediction                                                                              |

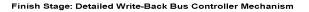

| 5.1. Detailed Architecture Model describing the Write-Back Buses at Finish Stage 60                                                    |

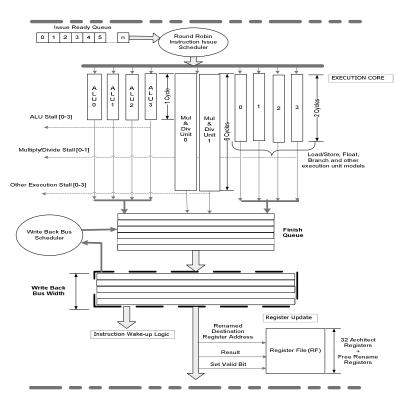

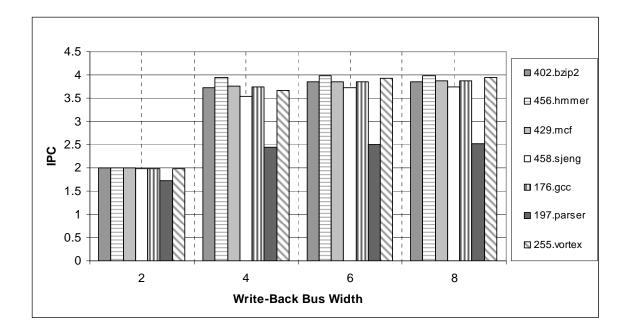

| 5.2. IPC of a hypothetical processor using SPEC CINT 2006/2000 Benchmarks                                                              |

| 5.3. Comparison of IPC for Different Write-Back Bus Widths for fetch width of 4 62                                                     |

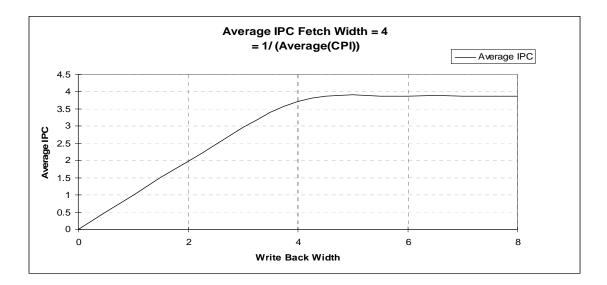

| 5.4. Average IPC for Fetch Width of 4                                                                                                  |

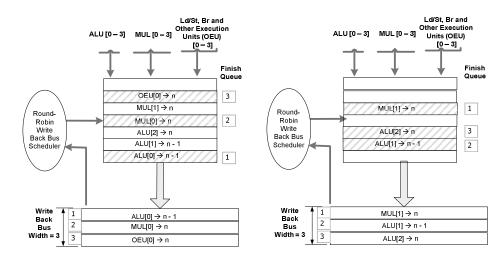

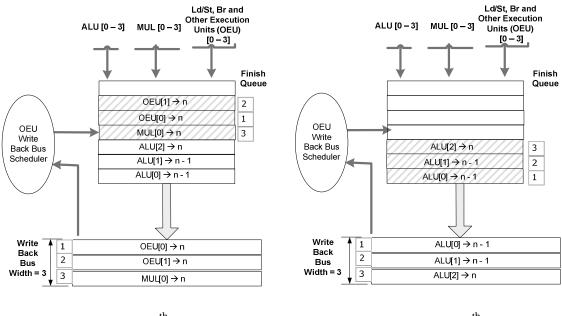

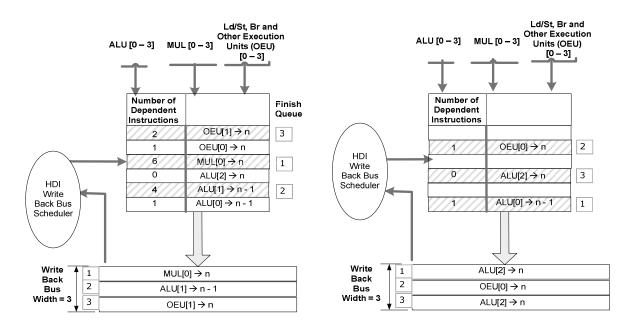

| 5.5 Round-Robin Write-Back Bus Scheduler                                                                                               |

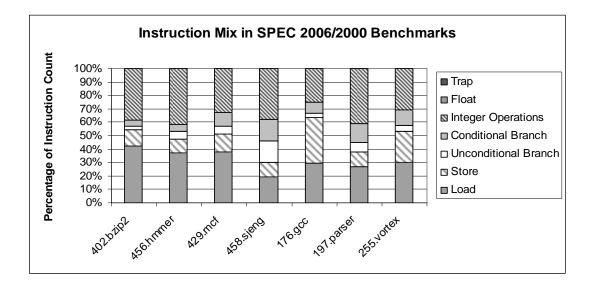

| 5.6 Instruction Mix in SPEC 2006/2000 Benchmark                                                                                        |

| 5.8 LMA Write-Back Bus Scheduler                                                                                                       |

| 5.9 PHD Write-Back Bus Scheduler                                                                                                       |

| 5.9 Chain of Data Dependency in an Instruction Window                                                                                  |

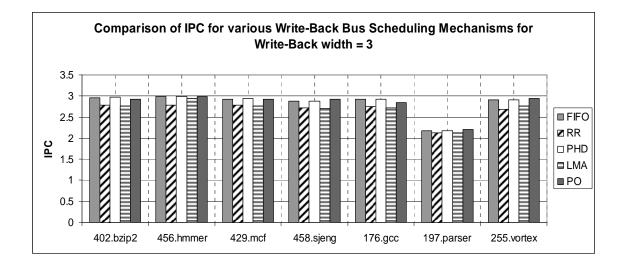

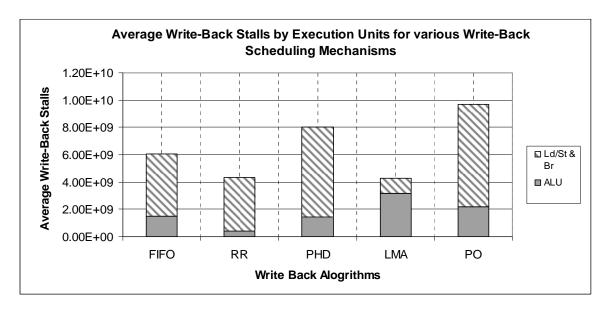

| 5.10 Comparison of IPC over various Write-Back Bus Scheduling Mechanisms                                                               |

| 5.11 Average Write-Back Stalls by Execution Units for various Write-Back Bus<br>Schedulers                                             |

| 5.12 Average Instruction Window Stalls for various Write-Back Bus Scheduling<br>Mechanisms                                             |

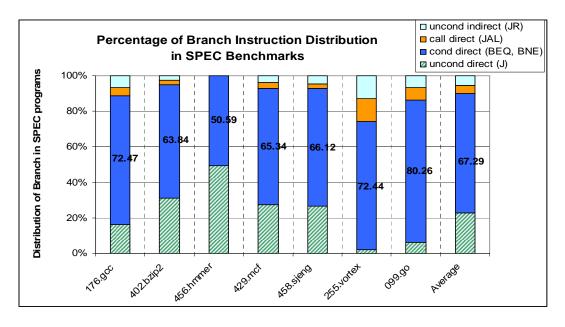

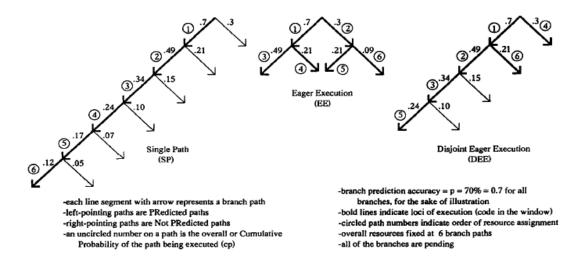

| 6.1 Multi-Path for 3 Unresolved Branches                                                                                               |

| 6.2 Logical Block Diagram of the Branch Prediction in                                                                                  |

| 6.3 Fraction of Branch Misprediction in SPEC benchmarks                                                                                |

| _gshare: Size: 2048 entries; History Bits: 16; BTB: 512 sets with 4-way associative 84                                            |

|-----------------------------------------------------------------------------------------------------------------------------------|

| 6.4 Classification of Branch Instructions in SPEC benchmarks                                                                      |

| 6.5 Comparisons of Execution Strategies (Source: Uht and Sindagi, 1995 [39])                                                      |

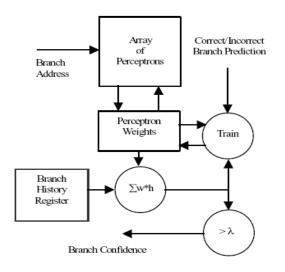

| 6.6 Perceptron based branch confidence estimation by Akkary et el. [2004]                                                         |

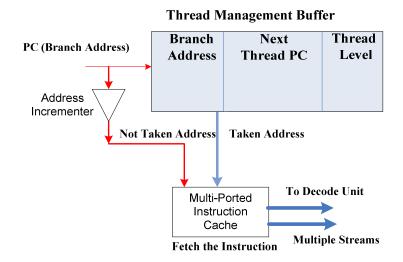

| 6.7 Logical Block Diagram of Fetch-Stage in Multi-Threaded Processor                                                              |

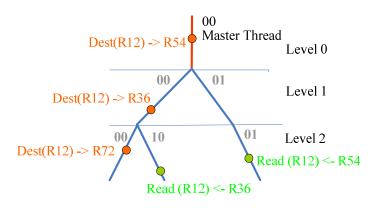

| 6.8 Example of Register Renaming in Multi-Path Design                                                                             |

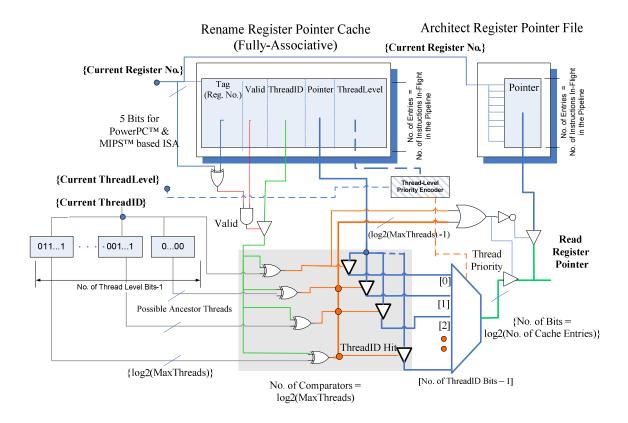

| 6.9. Logical Block Diagram of Register Renaming in Multi-Path Design                                                              |

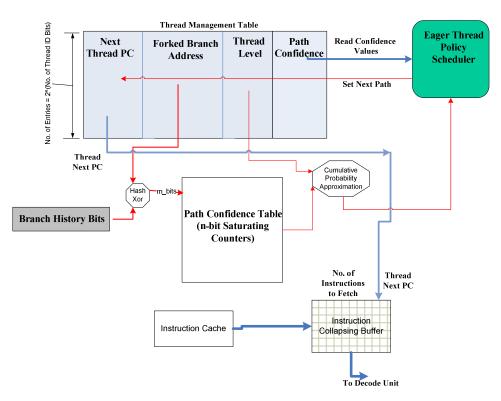

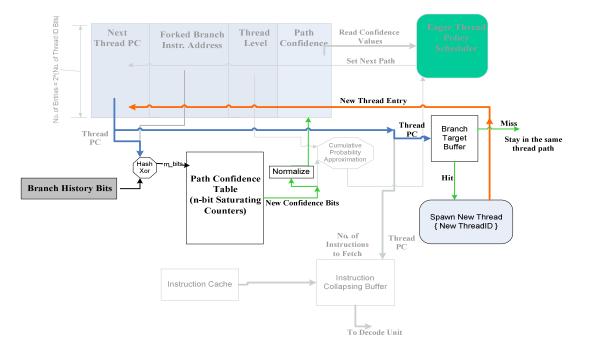

| 6.10 Logical Block Diagram of Fetch Policy using Confidence Estimator                                                             |

| 6.11 Thread Creation Process                                                                                                      |

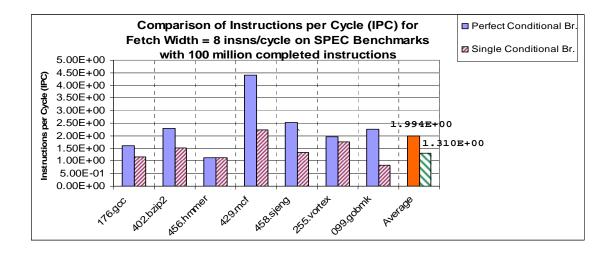

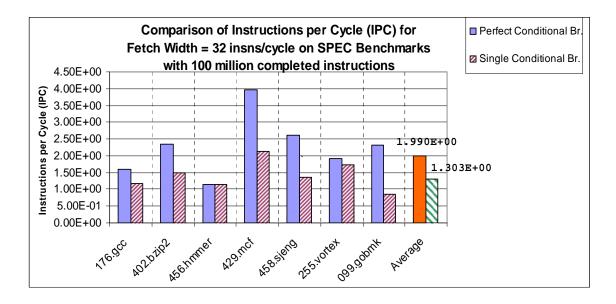

| 6.12 Performance Comparison between Perfect and Single-Threaded Processor 102                                                     |

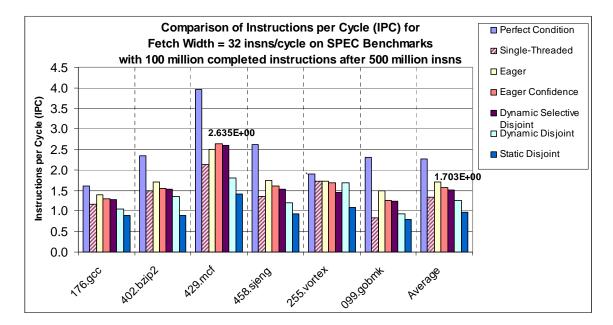

| 6.13 IPC for Fetch Width of 32. IPC for 32-wide fetch is slightly less than 8-wide fetch because of increased latency in recovery |

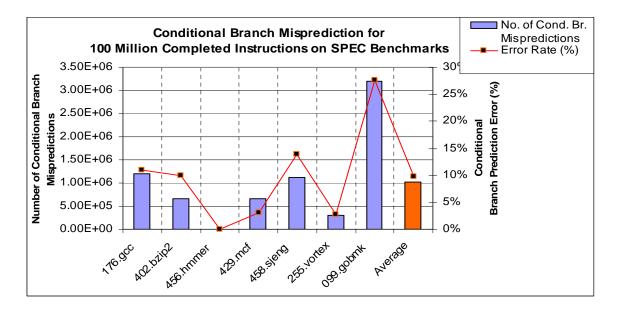

| 6.14 Conditional Branch Error Rate. The plot represents the number of Recoveries due<br>Conditional Branch Misprediction          |

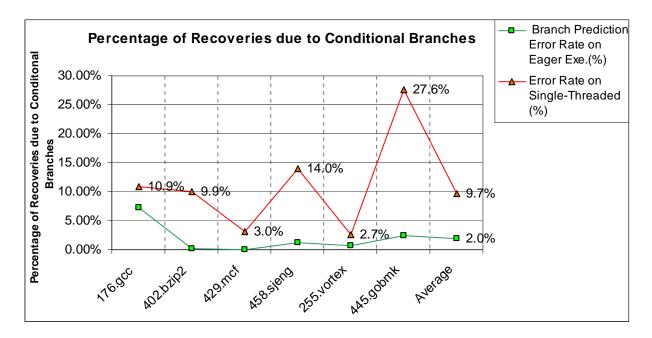

| 6.15 Percentage of Recoveries due to conditional branch misprediction                                                             |

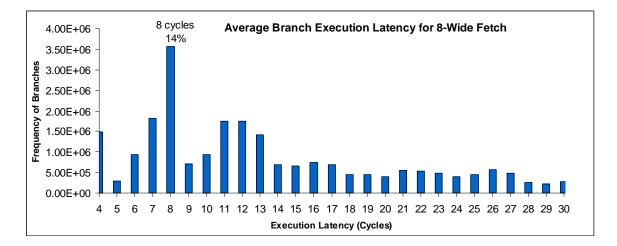

| 6.16 Average Branch Execution Latency for 8-Wide Fetch in the SPEC benchmarks 105                                                 |

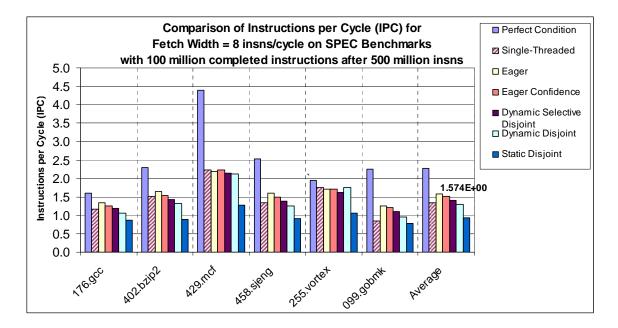

| 6.17 Comparison of IPC for different eager-based polices with single-threaded processor<br>for 8-wide fetch                       |

| 6.18 Comparison of IPC for different eager-based polices with single-threaded processor<br>for 32-wide fetch                      |

| 6.20 Relationship showing how different eager schemes rely on branch prediction and its effect on IPC                             |

| 6.21 Histogram of Active Threads                                                                                                  |

| 6.22 Code Phase Variations in SPEC benchmark                                                                                      |

#### CHAPTER I

#### INTRODUCTION

# **1.1. Performance Studies**

The design space of microarchitecture is bound to grow significantly as multi-threaded and multi-core architectures are investigated by computer researchers. Typically, computer architecture studies can be classified into 2 categories – *Performance Evaluation* and *Performance Estimation* metric studies.

Studies involving Performance Evaluation simulates the entire microarchitecture design and provides an accurate performance metric for the simulated microarchitecture. The simulation of the microarchitecture is cycle-accurate and involves detailed description of the microarchitecture blocks. This method of detailed cycle-accurate performance analysis takes tens of thousands of host machine's clock cycles.

The SPEC CPU benchmark programs have become the de facto standard to evaluate computer architecture designs. However, with the number of instructions in the SPEC benchmarks mounting to more than a trillion instructions, it is not feasible to simulate the complete set of benchmark programs in a reasonable amount of time. For example, to execute 1 trillion instructions (assuming it takes 10,000 machine cycles for a simulated cycle) using a typical CPU operating at 1.5 GHz clock speed and 3 instructions per cycle, it takes about 77 days to evaluate the microarchitecture design. As different design trade-off studies have to be carried out by researchers, such long computing wait time becomes a huge impediment for research. Hence, several techniques have been proposed to circumvent the cost of increased simulation time. Reduced input data-set and trace-driven evaluations are a few of the techniques to reduce simulation time for cycle-accurate simulations. However, the similarities of these simulations with the actual simulation are still under investigation.

On the other hand, *Performance Estimation* models are proposed to probabilistically estimate the performance of the architecture design. The performance estimate of the microarchitecture is determined in a short time and this ensures the possibility of several microarchitecture design trade-off studies. But, the accuracy of the probabilistic model that describes the microarchitecture is debatable. Several assumptions are made to describe the microarchitecture model and such abstraction undermines the results of the performance estimations.

# **1.2. Motivation**

The flow of instructions is measured in instructions per clock,  $IPC_i$ , at some point i in the data path. Usually what we are interested in is the average IPC which can be determined as,

$$IPC_{i} = \frac{1}{N_{c}} \sum_{c} IPC_{i}(c)$$

<sup>(1)</sup>

Chapter I

where, Nc is the total number of clock cycles when running a bench mark program and  $IPC_i(c)$  is the number of instructions passing a point in the data path during clock cycle, c.

High level processor simulations can calculate IPC in this manner, but they are forced to simulate the processor behavior for billions of clock cycles which is very expensive. Instead a stochastic model for IPC can be used which avoids simulating the processor architecture cycle by cycle.

The data path structure and the hazard control logic determine the IPC(c) when hazards occur. Suppose the cycle by cycle simulation calculates N(IPCi = 0), N(IPCi = 1), ...,  $N(IPCi = s_i)$  which is the number of clock cycles that  $IPC_i(c) = 0, 1, ..., s_i$ , where  $s_i$  is the local superscalar width (instruction parallelism) at point *i* in the data path. The IPC model can be made stochastic by defining the probability that  $IPC_i(c) = 0, 1, ..., s_i$  as

$$P(IPC_{i} = n) = \frac{1}{N_{c}} N(IPC_{i} = n) \qquad n = 0, 1, ..., s_{i}$$

(2)

so that,

$$IPC_{i} = \sum_{n=0}^{s_{i}} n \cdot P(IPC_{i} = n)$$

(3)

The same system of equations from the structural model that determines IPC(c) will give a system of equations that can be solved for  $P(IPC_i = n)$  without running a cycle by cycle simulation.

The level of detail of this approach is such that individual instructions are not tracked as they flow through the data path structure. Instead the probability of an instruction flow rate is determined at each point in the data path structure. Many of the hazard control equations require knowledge about certain types of instructions at certain locations during certain clock cycles. The probability of an instruction of a certain type can be determined from instruction frequency analysis of the benchmark programs.

$$P(type = t \ at \ i) = P(type = t \ | \ instruction \ at \ i) * P(instruction \ at \ i)$$

$$= f_t * P(instruction \ at \ i)$$

(4)

The instruction frequency of type t instructions,  $f_t$ , can be reused for performance calculations of many different structural models. The stochastic model determines P(IPCi = n) only. The reuse of instruction frequency data greatly reduces the complexity of the stochastic model.

Calculating the effects of hazards is complicated since hazards are not mutually exclusive and that stalls from different hazards can overlap in time. The same stall can be produced by more than one stall at one time, and we must be careful to avoid counting the same stalls more than once. To apply the *IPC* formula, we must include not only individual hazards, but also all possible combinations of hazards with all possible overlaps in time.

In order to accurately estimate the performance of a complex microarchitecture design, we must understand the dynamic relationship between its instruction flow and the hazards due to structural, control and data dependence through its statistical information. An extremely fast microarchitecture simulator with detailed module descriptions that is closely related to hardware behavior is necessary to gather this statistical information. Hence, *OSU AbaKus* – a cycle-accurate microarchitecture simulator is developed to address this issue.

4

## **1.3.** Cycle-Accurate Simulation Engine Concept

The basic idea behind the cycle-time simulator is that all clocked modules are evaluated for every simulation cycle. This idea is in direct relationship with the pipelined design of the microarchitecture design, as all stages in the pipeline are evaluated similarly for each clock cycle.

#### 1.3.1 Processing Elements and Signals:

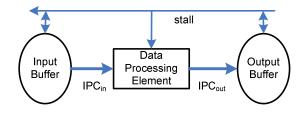

As shown in Figure 1.1, each *Data Processing Element* has an input buffer and an output buffer. The *Data Processing Element* takes the necessary input data for evaluation and produces the output data that is then stored in the output buffer. The flow of data in the buffers is controlled by the *stall signal*. The processing elements can also introduce *forward-propagating stalls* or *bubbles* in the pipelines. The propagation of bubbles in the pipeline occurs when there is insufficient amount of data stored in the input buffers to feed the *processing elements*. The bubbles can be related to the *no-operations* (NOPS) in the microarchitecture design.

Figure 1.1 Structure of a Simple Data Path Representation

## 1.3.2 Buffer Design:

The design of the buffer offers the most discreet part of the simulation engine. It defines both the simulation engine's flexibility as well as its simulation speed. The buffer in the simulation act as information sources and sinks for the *Data Processing*

*Elements*. They maintain the network of connections through which the processing elements communicate with other processing elements in the design.

If the buffer gets filled, it can initiate a *stall signal* that stalls the up-stream buffers. The *IPC* of the processor is directly affected by these stall signals. The stall signals that stall up-stream buffers are called *backward-propagating stalls* or *up-stream stalls*. A major task in designing microarchitecture involves keeping a steady flow of information in the pipeline and to prevent buffers from being filled up.

The  $IPC_{out}$  and  $IPC_{in}$  are related in the eqn (5) and eqn (6) and are illustrated in Figure 1.2, where  $N_b$  is the total number of instructions that the buffer can store,  $s_{in}$  and  $s_{out}$  are the number of instructions that are flowing into and out of the buffer in a clock cycle,  $bubbles_{in}(c)$  is the number of bubbles that come into the buffer at cycle, 'c' and  $bubbles_{out}(c)$  is the number of bubbles that leave the buffer at cycle, 'c'.

$$IPC_{in}(c) = \begin{cases} s_{in} - bubbles_{in}(c) & \text{if stall}_{in}(c) = 0\\ 0 & \text{if stall}_{in}(c) = 1 \end{cases}$$

(5)

$$IPC_{out}(c) = \begin{cases} s_{out} - bubbles_{out}(c) & \text{if stall}_{out} = 0\\ 0 & \text{if stall}_{out} = 1 \end{cases}$$

(6)

Figure 1.2. Relationship between IPCin and IPCout

As defined in section 1.3.1, *bubbles* define the *NOP* instructions. The buffers can both propagate as well as initiate stall signals, *stall<sub>in</sub> and stall<sub>out</sub>*. The condition at which the

buffer is filled initiates the *stall*<sub>in</sub>(*c*) *signal* at cycle 'c'. This is shown in eqn. (7), where  $I_b(c)$  is the number of instructions present in the buffer at cycle 'c'.

$$\operatorname{stall}_{in}(c) = \begin{cases} 1 & \operatorname{if} I_b(c) + s_{in} - s_{out} > N_B \text{ and if } \operatorname{stall}_{out} = 0 \text{ and } I_b(c) > s_{out} \\ 1 & \operatorname{if} I_b(c) + s_{in} > N_B \text{ and if } \operatorname{stall}_{out} = 1 \\ 0 & \operatorname{otherwise} \end{cases}$$

(7)

The state of the buffer for the next cycle can then be calculated and is given in eqn. (7). Thus eqn. (8) describes that the state of the buffer for the next cycle is only defined by the current state of the buffer.

$$I_b(c+1) = I_b(c) + IPC_{in}(c) - IPC_{out}(c)$$

(8)

This simplistic view of the buffer is established from the pipeline model and more succinctly relates to the *Moore State Machine* of the architecture design. Furthermore, for stochastic performance analysis, this step can be extended to a discrete-time *Markov* model and thus future state of the buffer can be estimated.

# **1.4. Implementation of the Clocked Buffer Model**

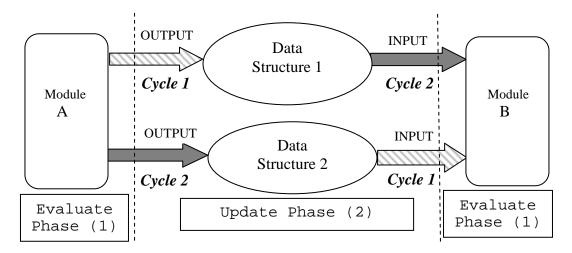

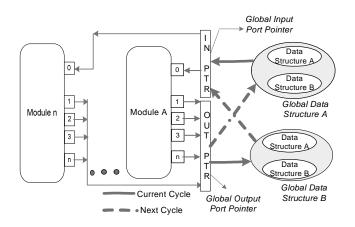

In this section, the implementation of the *buffer model* and the *Data Processing Elements* that are otherwise known as *modules* is discussed. As discussed in section 1.2, it is important that this cycle-accurate simulator is simple and fast. As shown in Figure *1.3*, the functionality of the architecture is defined by the two modules *A* and *B*. Two separate simulation data structures are maintained at its interface. The simulation methodology is a 2-step process.

The first step is to evaluate all the modules in the *evaluate phase*. In the first cycle, module *A* uses *Data Structure 1* as the output while module *B* uses *Data Structure 2* as

the input. The second step, i.e. at the end of the evaluate phase, is the *update phase*. The pointers of *Data Structures A* and *B* are alternated. Hence, during the second cycle module *A* uses *Data Structure 2* as the output while module B uses *Data Structure 1* as the input. This buffer interface mechanism avoids transfer of huge amounts of simulation data during each cycle. This concept is further explained in detail in the following sections.

Figure 1.3. Pipeline Register Interface Model. A and B are modules defining the functionality of the architecture.

#### 1.4.1 Module Interfaces through Port Definitions:

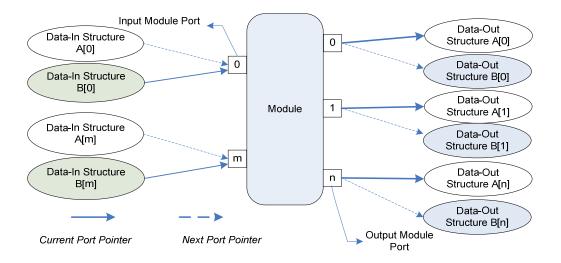

The modules descriptions are based on ISO C++ standard constructs. The modules describe the behavior of the *Data Processing Element*. The functional behavior of the module is described using C++ language definitions as in a sequential programming. However, the difference between sequential and modular programming is brought by *port* definitions that are used to interface with other modules. As a result, as shown in Figure *1.4*, the modularity in the design is achieved through *ports* that are used as communication interfaces between modules and the buffer.

Figure 1.4. Module Interface

Similar to an HDL, *ports* are specified in a module to be an input or output port. In Figure 1.4, each *port* has 2 pointers, the *current port pointer* and the *next port pointer*. The input data to the module is read from the *Data-In Structure* that is pointed by the *current port pointer* while the module's output data is written into the *Data-Out Structure* that is pointed by *next port pointer*. In the following cycle, the pointing location of the pointers is alternated, thus the outputs written during the previous cycle can be read as inputs in the following cycle and vice versa. This simple alternating of pointers avoids the overhead of copying the entire data structure that leads to slow simulations as in OSCI SystemC 2.1.

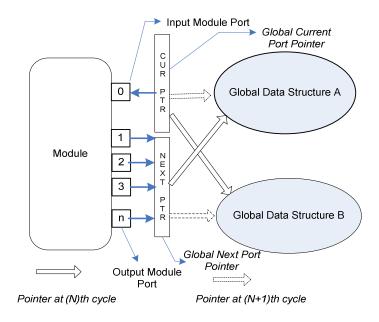

Figure 1.5. Improved Mechanism with Global Pointers for Global Data Structures The number of update operations in alternating pointers between *Data-In and Data-Out Structures* is directly proportional to the number of ports in a module. Hence, to avoid this additional computational cost, two *Global Pointers* for the *Global Data Structure A and B* are created as illustrated in Figure 1.5. Furthermore, the outputs of all the modules in the simulation are referenced to the *Global Next Pointer* and similarly, the inputs of all the modules are referenced to the *Global Current Pointer*. These pointers alternate between the *Global Data Structures A and B* for each clock cycle. Thus, the output data structure at clock cycle 'N' becomes the input data structure at clock cycle 'N+1' and vice versa. This mechanism not only avoids copying data between the *Global Data Structures* but also makes the number of update operations independent of the number of ports in the modules. As a result, it maintains the computational time for updating the pointer locations a *constant*.

#### 1.4.2 Register and Memory Element Interface Model:

The update phase that is shown is Figure 1.3 is also extended to update the registers in the *register file* and other *memory elements*. As shown in Figure 1.6, the data in the memory elements are accessed through *ports* similar to the actual memory access. The location of the *write and read* is determined by the *write and read addresses* respectively. Therefore, a *write data or read data* occurs on the referenced register/memory location depending on the logic.

Figure 1.6. Memory Access through Ports

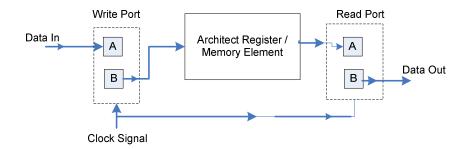

As shown in Figure 1.7, both the *write port* and *read port* have two in-built data structures defined as *Port A* and *Port B*. On the *write port* interface, the data to be stored are written into *write port A*, while the data from the *write port B* are transferred to the *memory element*. Their corresponding pointers are alternated during the *update phase* that is triggered by the clock cycle. Hence in the following cycle, the functionalities of *write ports A* and *B* are interchanged. Similarly, on the *read port* interface, data is read from the *read port A* and the data from the *memory element* is transferred to the *read port B*. The functionalities of *ports A* and *B* are similarly interchanged for each cycle.

Figure 1.7. Port Access for a Memory Element

This functionality of the *write ports* and *read ports* described in this section corresponds to the *D-flip flop register* that is used in the actual hardware design. Hence, designing the memory structures with *port* interfaces provides this simulator the capability to perform both functional as well as timing verifications as in an HDL, and yet with a much greater simulation speed.

# **1.4. Organization of this Dissertation**

Chapter 2 reviews the simulation mechanism on existing simulators. It reveals the benefits and drawbacks of each simulator. Chapter 3 presents the simulation approach of AbaKus simulator and also compares its performance with existing simulators. Chapter 4 discusses the modeling details of the superscalar architecture. It then presents about the load-store dependence prediction schemes used in AbaKus. Chapter 5 presents a case study on register write-back buses and identifies the characteristics of different bus scheduling mechanisms. Chapter 6 presents another case study on control dependencies problem in superscalar cores. Finally, Chapter 7 summarizes the design of AbaKus and limitations of superscalar processors.

12

#### CHAPTER II

#### LITERATURE REVIEW

# **2.1 Simulation**

Hardware simulation is a process of describing the behavior of hardware logic using computer programming languages and verifying the hardware behavior with test input sets. Its use and adaptation depends on the accuracy of the results obtained using simulated hardware compared with actual behavior, speed of simulation and flexibility to design.

Computer architecture simulators are needed for the following reasons:

- Perform extensive design space exploration because it is cheaper to experiment with simulated designs.

- Verify hardware logic with respect to both functionality and timing, and

- Aid in the simultaneous development of support software tools such as compilers and operating systems.

There is a plethora of computer architecture simulators and the next section discusses some of the widely used computer architecture simulators.

#### **2.2 Simplescalar Tools**

Simplescalar tool set (Burger and Austin [1], 1997) has been one of the most widely used computer architecture simulator both in research as well as in class projects. It is an open-source and free-of-charge tool for non-commercial academic users. It provides a baseline out-of-order simulator known as the *sim-outorder* and most of the processor design aspects including the reorder window size, number of functional units and latency of memory ports can be defined at compile time. In addition, it integrates simplistic cache models to its processor and the cache design parameters can also be varied.

Simplescalar package has a set of simulators ranging from simple functional simulator to complex out-of-order processor simulator. It supports MIPS IV based Instruction Set Architecture (ISA) with minor changes to the instruction opcodes and also provides cross-compiler for its ISA to run on host computer machines. The advantage of Simplescalar tool set is its speed of simulation. On *sim-outorder* simulations the simulation speeds can average about 200 K instruction/s on a typical modern day desktop machine. Hence, it has been widely popular to execute SPEC benchmarks with Simplescalar tool sets that would normally be executed on real processors.

One of the main drawbacks of *sim-outorder* is that it is weakly related to the actual hardware behavior. For example, *sim-outorder* does not model the effects of write-back buses in the processor core. The contention among the write-back buses is important as it may increase the latency of dependent instructions. Another weakness of *sim-outorder* is that the actual execution of the instruction is in-order and only the control flow of execution is simulated. The concept of pipeline register timing is not simulated and it is

14

important to maintain accuracy. Besides, code changes in Simplescalar have also proven to be difficult (Vachharajani et. al [2], 2002) and hence it has reduced flexibility.

# 2.3 Liberty Simulation Environment

In order to the address the problems of accuracy in simulations and to reduce the development time for logic design Vachharajani et. al. [3], 2002 developed the Liberty Simulation Environment (LSE). It is free and is a component-based model designed to reuse code usage.

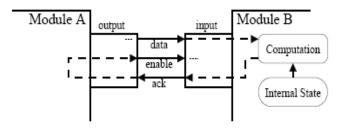

Modularity in module definitions is well enforced by allowing modules to communicate through ports. Each port as shown in Figure 2.1 handles 3 signals: *data, enable,* and *ack.* The *data* is sent forward and the *enable* indicates that the receiving module should process the data. If the receiving module can process the data then an *ack* signal is transmitted. This simulates effectively the pipeline stalls and timing of data in an architecture simulation.

Figure 2.1 Port Communications in Liberty, Vaccharajani et. al. [3], 2002

The advantages of LSE are that it is modular and through the use of a graphical user interface, designers can drag, drop and connect modules. However, the modularity comes at the cost of simulation speed. The number of hand-shaking signals increases with the increase in ports (Vachharajani et. al, 2002].

The order in which the modules are invoked depends on the scheme called *Heterogeneous Synchronous Reactive* (HSR) scheme. It is different for the discrete-event scheduling in that a partial order of module invocation is generated statically using several optimizing scheduling polices and later can change similar to the discrete-event scheduling. In general, the HSR reduces the problem suffered by discrete-event scheduler which invokes repeated module evaluations.

# **2.4 ASIM**

The key feature of ASIM is its modularity (Emer [4], 2002). The performance models in ASIM are mainly developed using C++ and is a proprietary of Intel [4]. Modularity is achieved through ports that are FIFO queues. The model of FIFO ports helps ASIM to simulate the latency between pipeline stages and also wire delays.

ASIM is considered to offer a high degree of module reuse. However, ASIM is likely to suffer in the speed of simulation as it is based on discrete-event scheduler. Although, these schedulers enable designers to simulate realistic hardware signal flow, they suffer from additional computation time. Since, ASIM is considered to be closely related to simulate hardware behavior; an extension of ASIM known as A-Ports (Pellauer et. al. [5], 2008) has been developed to emulate the behavior through FPGAs.

### **2.5 SystemC Based Simulators**

SystemC is a C++ based modeling language with several model libraries for specifying the digital logic of the hardware and has a discrete-event scheduler to simulate the timing

details. The popular version of SystemC is maintained by Open SystemC Initiative (OSCI) [6].

#### 2.5. 1 UNISIM

Unified Simulation environment (UNISIM) is an open-source SystemC add-on that focuses on modularity and code reusability. It also supports cycle-level and transactionlevel models. Several groups such as *Liberty*, *Microlib* (Perez et. al. 2004, [7]) and SystemC model developer are actively involved to develop architecture models of the computer system.

One key feature in UNISIM is its interoperability which means that it is considered to be possible to integrate with different simulation environments. It also supports full system simulation that includes operating systems such as Linux. Virtutech<sup>®</sup> Simics<sup>TM</sup> [8] is another simulation environment that performs full system simulation and supports various operating systems. But the disadvantage of Simics is that it is commercial with source code restrictions. UNISIM currently supports a host of processor model including PowerPC and ARM. The drawback on UNISIM is that it is an even-driven simulation environment and is slower than cycle-time based simulations.

#### 2.5.2 .ArchC

ArchC [9] is an open-source architecture description language based on SystemC. It defines several wrapper class structures to enable designers to specify the architecture parameters instead on the actual module descriptions. Module descriptions are also

possible to extend its model libraries. It supports various models including PowerPC, Intel 8051 and SPARC V8 architectures.

### **2.6 FPGA-based system emulation**

Research Accelerator for Multiple Processors (RAMP) [10] aims to emulate dozens of processor cores in multiple FPGAs whose cells are being densely packed. Validating multiple processors is difficult in simulations because of the increase in the level of simulation as well as the number of test inputs. Emulation using FPGA technologies can lead to significant improvements in validating such architecture designs. However, the cost involved in emulation is also significantly higher compared to computer simulations.

# 2.7 Other Simulators

There are number simulators available for the computer architecture research community to simulate various components of a computer system. Depending on the simulator's characteristic it is the choice of the researcher to select a simulator. Simulators such as M5 (Binkert et. al. 2006, [11]) and SESC [12] model both CPU as well as support network I/Os of a computer system. PTSim (Yourst, 2007, [13]) is an event-based simulation for x86 architectures. Numerous variants of Simplescalar tools such as *sim-mase* (Larson et. al. 2001, [14]) is developed to further increase the level of simulation details in Simplescalar tool set.

# **2.8 Discussion**

Computer architecture simulators available for researchers are abundant. The choice of the simulator comes down to the details of architecture that the researcher is interested to model. The nature of the simulator depends on its modularity/flexibility, speed and accuracy.

Although most of the simulators focus of modularity and reusability, it comes at the cost of simulation speed. Simulation speed is important to enable researcher to test and validate the architecture with numerous test input sets and also to explore more design alternatives.

FPGA based system emulation can provide speed and accuracy but at an increase cost. AbaKus simulator is developed to address the issues of speed, accuracy and modularity and in an affordable way. In the next few chapters, the internals of AbaKus simulation engine and its models are discussed.

#### CHAPTER III

#### SIMULATOR PERFORMANCE

# **3.1 Simulator Design**

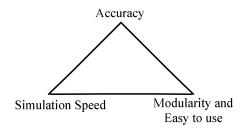

Simulators strive to achieve the three important parameters - accuracy, flexibility and speed in the best possible way as depicted in Figure *3.1*. The simulators described in Liberty [2], MASE [14] and ASIM [4] emphasize on each of these parameters.

Figure 3.1 Objectives of a Microarchitecture Simulator

Microarchitecture functionality can be visualized as a group of modules triggering dependent modules to be evaluated each cycle. In general, it is modeled as a state machine. Therefore, the signals that are generated in a module propagate and modify the state as they traverse through various module structures. The two common types of simulations are considered to explain interface mechanism,

- Event-Driven Simulation

- Cycle-Time Simulation

## Chapter III

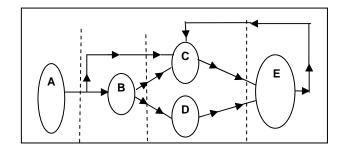

In an event-driven simulation, a process queue maintains a list of modules that are to be evaluated for each cycle. The process queue is updated for each finite simulation cycle time. Consider A, B, C, D and E are hardware functional modules connected as shown in Figure *3.2*.

Evaluation of each module triggers its dependent modules and is added in the process queue. For the structural logic shown in Figure *3.2*, the process queue collects copies of same modules to be evaluated repeatedly as shown in Table *3.1*.

Figure 3.2 Module Executions

| Cycle | Evaluate    | Trigger     | Process<br>Queue |

|-------|-------------|-------------|------------------|

| 1     | А           | B, C        | B, C             |

| 2     | B<br>C      | C, D<br>E   | C, D, E          |

| 3     | C<br>D<br>E | E<br>E<br>C | E, E, C          |

#### TABLE 3.1EVENT-DRIVEN SIMULATION PROCESS

Modules C and E are evaluated multiple times.

Although, this ensures a more realistic hardware logic evaluation, repeated module execution results in a lot of computing time. Simulation kernels of HDLs such as Verilog, VHDL and SystemC are based on this mechanism. Techniques to reduce the number of redundant module executions in SystemC by acyclic scheduling have been proposed by Perez et al. [15]. On the other hand, the cycle-time simulation has a simpler approach. All the modules in the simulation are evaluated only once on each simulation cycle. This provides a more straightforward solution to avoid redundant module evaluations. The functional verification is typically provided by enforcing sequential order of module executions, as in SimpleScalar. The challenge in a cycle-time simulation is to provide both functional as well as timing verification that is provided by the event-driven simulation. There are two cycle-time simulators that are developed in this study.

- [1] OSU SystemC

- [2] OSU AbaKus

#### 3.1.1 OSU SystemC

As SystemC has grown to be one of the frameworks for developing system-level architectures, a new cycle-time simulation model based on SystemC language construct – OSU SystemC – is developed in this research.

The models developed in SystemC v2.1 from Open SystemC Initiative (OSCI) are compared OSU SystemC. SimpleScalar version 3.0 tool-set provides the base-line model to compare the performance of the simulators as it is widely used for academic research and studies. The syntax of OSU SystemC is same as IEEE 1666 standard described for SystemC v2.1, but with restriction on usage of thread modules. The following summarizes the kernel of OSU SystemC,

• The old and new values have pointer that are switched on each delta cycle instead of values being copied [15].

22

• The scheduler is cycle-time based and hence, it evaluates all the modules that are declared with SC\_METHOD in a delta cycle. SC\_THREAD definitions are not handled as it needs synchronization of all thread modules after each delta cycle.

#### 3.1.2 OSU AbaKus Simulator:

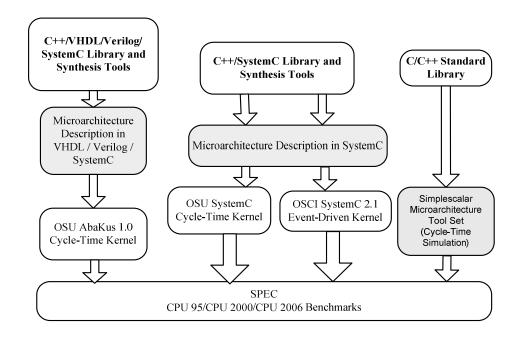

On the other hand, the syntax of OSU AbaKus is in standard C++ and is developed such that it is adaptable to any hardware description language. The OSU AbaKus Microarchitecture Design Simulator is developed to address the issues of flexibility and speed. The design flow for each microarchitecture simulator is illustrated in Figure 3.3.

OSU AbaKus provides a much simplified simulator with a new simulation kernel and is completely different from that of SystemC 2.1 kernel. Thus, by having a new simulation kernel, the redundant codes present in the existing OSU SystemC version and its class hierarchical design is avoided.

Figure 3.3 Design Flow of Simulation

3.1.3 Comparison between OSCI SystemC, OSU SystemC and OSU AbaKus

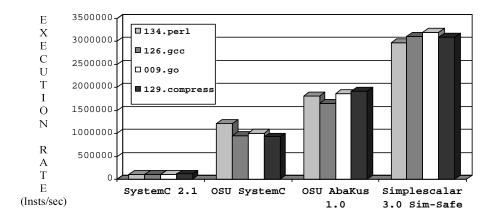

A simple three-stage scalar pipeline model was tested with SPEC 95 benchmark programs on an AMD Duron 750 MHz processor running Linux kernel 2.4.2. As shown in Figure 3.4, the instruction execution rate of the new simulators using the SimpleScalar's instruction-execution engine is 10 times faster than the model developed in *SystemC 2.1*. This results in 25% increase in simulation speed between OSU AbaKus and OSU SystemC. The throughput of the simulators is compared in Figure 3.5. SimpleScalar's sim-safe executes all instructions in a clock cycle i.e. the instruction execution latency is 1 and it represents the most ideal execution engine.

Figure 3.4 Performance Comparison between the Simulators for a simple 3-stage scalar MIPS architecture

OSU SystemC OSU Abakus Simplescalar's sim-safe

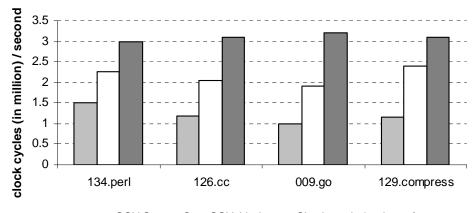

Figure 3.5 Comparison of Simulator Through-put

It is observed from Fig. 3.5 that OSU AbaKus has 40% more throughput than OSU *SystemC*. The simulation kernel differences such as implementation of advanced objectoriented concepts cause the asymmetric distribution of execution rate seen in Figure 3.5. To further investigate the performance of the simulators on complex designs, a superscalar architecture is built using OSU AbaKus.

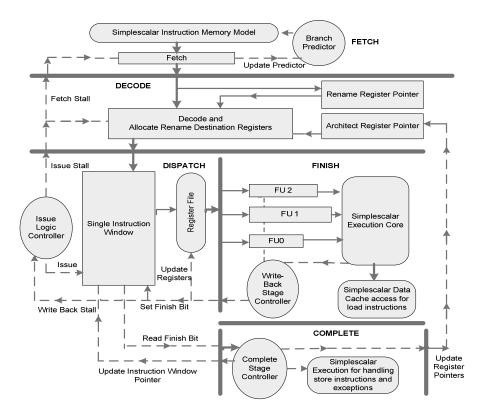

# **3.2** Comparison with Superscalar Designs

A modular description of superscalar architecture design is written to accurately model the functionality of the microarchitecture during each clock cycle. The modules are described in C++ and reuse Simplescalar's execution core and memory models. Figure *3.6* shows the details of the simulated superscalar architecture. It accurately models the stall signals and in addition, the pipeline registers are parameterized to simulate different superscalar architecture widths. The finish stage encompasses the issue logic, instruction execution and write-back buses to update the register file. The microarchitecture is designed to explicitly model the *rename register mechanism* using Rename Register

Pointers and Architect Register Pointers that is not modeled in SimpleScalar's simoutorder *3.0*. Moreover, unlike SimpleScalar *3.0*, all executions are true out-of-order.

As shown in Figure 3.6, the microarchitecture uses SimpleScalar's *memory model* to fetch instructions and to perform memory related operations. The dynamic instruction scheduler with single instruction window includes instruction wake-up logic and out-of-order issue logic. As a test case perfect branch prediction is used to determine the throughput of each simulator and limit the architectural differences between the two simulations. But, it is found that in SimpleScalar, the next program counter is determined at dispatch and hence it encounters conditional stalls even during perfect branch conditions.

Figure 3.6 Simulated Superscalar Architecture

As there is no floating-point unit incorporated in *OSU AbaKus*, it handles floating-point instructions as a precise exception. Due to this simplification, it is expected to have a

lower IPC than SimpleScalar. Instructions that cause exceptions have three-cycle functional unit latency. The recovery mechanism then recovers the processor to the original machine state. However, the number of recovery cycles depends upon the state of the processor at the time of exception and this is not modeled in detail with SimpleScalar *3.0*. Besides, no explicit register rename mechanism is implemented in SimpleScalar *3.0*.

A more detailed out-of-order architecture model is developed in Simplescalar 4.0/MASE [14]. The renaming register logic is included and a distributed reservation station model is incorporated. An in-order execution queue is maintained and hence it does not incur a 2-cycle penalty for perfect branch prediction studies as in Simplescalar 3.0.

Another architecture difference between *Simplescalar* and *OSU AbaKus* is the register write back bus model during the finish stage. This is an important module that defines the number of instructions that can finish in a clock cycle. This aspect is not considered in Simplescalar versions (Vachharajani et. al. 2006, [3]). *OSU AbaKus* solves this problem by providing an explicit parameter for the write-back bus bandwidth and simulates realistic stalls encountered during instruction finish. The pre-compiled SPEC binaries from SimpleScalar and our own compiled binaries with ref and train input data-sets were run to completion. Due to the long running time not all benchmarks are incorporated in the test.

27

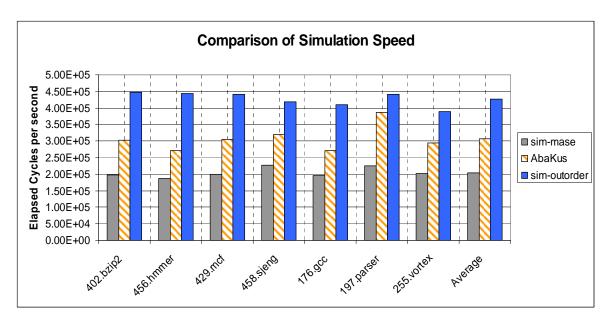

# **3.3 Comparison of Simulation Speed**

Figure 3.7 compares the simulation speed of the three microarchitecture simulators, sim-mase, *OSU AbaKus* and sim-outorder. In order to correctly compare the simulators, every effort is made so that the simulated hardware architectures are as similar as possible. In addition, the processor model that is simulated in the three simulators is designed to have similar average Instructions per clock cycle (IPC). The simulators are compiled with gcc 3.4.5 with the O0 optimization level and are executed in a 64-node cluster each with 3.2 GHZ Intel Xeon<sup>TM</sup> processor running a Linux 2.6.9 kernel. The simulated architecture details are listed in Table 3.2.

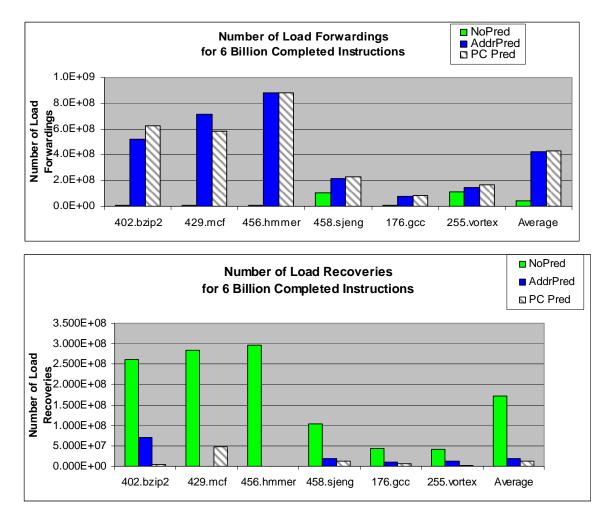

SPEC CPU 2006/2000 integer benchmarks with reference input datasets are used to compare the simulators. A total of *6* billion instructions are executed in each of the selected benchmarks. Only the benchmarks that compiled successfully with Simplescalar's *sslittle-na-sstrix-gcc* are used in this research.

Figure 3.7 Comparison of Simulator Performance for a Superscalar Architecture Model

Due to the inherent dissimilarities between the simulated architectures, it is more pertinent to compare the elapsed simulation *cycles/s* between the simulators instead of instructions/s. Both *sim-mase* and *OSU AbaKus* have more detailed architecture simulation than sim-outorder. As seen in Figure 1, the new simulator *–OSU AbaKus-* is on average *50.27%* faster than sim-mase while sim-outorder is on average *39.04%* faster than OSU AbaKus.

| <b>Design Parameters</b>           | sim-outorder      | AbaKus            | sim-mase<br>4 inst/cycle |  |  |  |

|------------------------------------|-------------------|-------------------|--------------------------|--|--|--|

| Instruction Fetch Width            | 4 inst/cycle      | 4 inst/cycle      |                          |  |  |  |

| Instruction Window Size            | Single Window: 64 | Single Window: 64 | Split Window: 64         |  |  |  |

| Physical Registers                 | 32                | 100               | 100                      |  |  |  |

| Issue Width                        | 8                 | 8                 | 8                        |  |  |  |

| Commit Width                       | 8                 | 8                 | 8                        |  |  |  |

| Branch Predictor                   | Perfect           | Perfect           | Perfect                  |  |  |  |

| Integer ALU units (Latency =1)     | 3                 | 3 3               |                          |  |  |  |

| Mul/Div Unit (Latency = 6)         | 1                 | 1                 |                          |  |  |  |

| Float ALU units                    | 4                 | Exception call    | 4                        |  |  |  |

| Float Mul/Div units                | 1                 | Exception call    | 1                        |  |  |  |

| Write Back Bus Width               | Not Modeled       | 4                 | Not Modeled              |  |  |  |

| Exceptions                         | Not Modeled       | Precise           | Precise                  |  |  |  |

| Memory Latency                     | 1                 | 1                 | 1                        |  |  |  |

| Number of Executed<br>Instructions | 6 Billion         | 6 Billion         | 6 Billion                |  |  |  |

| Average IPC                        | 2.165             | 1.794             | 1.884                    |  |  |  |

| Average Simulation Time            | 6520.1 seconds    | 11268.7 seconds   | 15655.0 seconds          |  |  |  |

TABLE 3.2

SIMULATION DETAILS OF THE THREE DIFFERENT SIMULATION MODELS

Although, other simulators such as publicly available *Liberty* and Intel's *ASIM* also focus on modularity, their over-head time on port communication is significant as the number of signals increase. The 3-way hand-shake port communication in *Liberty* and multiple event-driven executions in ASIM slow the simulations as the complexity of the design increases (Vachharajani et. al. 2002 [2]). In contrast, *OSU AbaKus* is a cycle-time simulator similar to Simplescalar. Thus, the simulation speed of *OSU AbaKus* is compared only to those of Simplescalar 3.0 and MASE. The AbaKus simulator can be succinctly defined as an HDL that is familiar to hardware designers, but with a cycle-time based simulation environment.

The *OSU AbaKus* simulation tool set enjoys the advantages of modularity and simulation speed. Modularity is achieved by writing module descriptions as done in typical hardware description languages such as Verilog or VHDL. Changes to its modules are simplified because the modules are not sequentially dependent as is the case with Simplescalar tools. In the following section, the flexibility of the *OSU AbaKus* simulation tool will be demonstrated by studying the effect of write-back bus widths. The write-back bus is a natural part of our model because of the direct correspondence of simulation modules with real hardware modules; whereas the write back bus is not included in Simplescalar or MASE module descriptions.

# **3.4 Discussion**

Simulation design objectives of AbaKus computer architecture design tool are provided below followed by a brief discussion.

- 1. Modularity: Breaks down performance modeling into different pieces.

- 2. Reusability of modules: Increases productivity and robustness of the software.

#### Chapter III

- 3. Familiarity with HDL programming.

- 4. Fast Simulation Speed.

- 1. Modularity:

All the modules in the simulation are accessed by either the *Global Input Port Pointer* or the *Global Output Port Pointer*. As indicated in Figure 3.8, the data elements the 2 global pointers point are switched for each cycle. Thus the updated values are read by the read ports while the write ports have a temporary data location to write its entries.

Figure 3.8. Illustration of Module Port Communication

## 2. Reusability:

Because our module port implementation is fully synchronous, much less simulation time is required to verify the architecture. The flexibility, i.e. reusability of modular code of the *AbaKus* simulation tool will be demonstrated by studying the effect of write-back bus widths. The write- back bus is a natural part of our model because of the direct correspondence of simulation modules with real hardware modules; whereas the write back bus is not included in Simplescalar or MASE module descriptions. 3. Familiarity of HDL Programming:

The following code structure format is similar to a behavioral HDL that is familiar to

hardware developers.

```

<module_name>(){

OUTPUT* <output_struct_pointer>; // Output Port Definition

INPUT* <input_struct_pointer>; // Input Ports

INPUT_STALL* <input_stall_pointer>; // Propagating Input Stall Signals

/*module descriptions*/

OUTPUT = module_function( INPUT, INPUT_STALL ); // Module Descriptions

}// End of Module

```

4. Fast Simulation Speed:

Both *sim-mase* (Larson et. al., 2001 [14]) and *AbaKus* have similar and more detailed architecture description than *sim-outorder*. The machine state of *AbaKus* and *sim-mase* architectures recovers from exceptions at the complete stage and write-back stage respectively, while *sim-outorder* recovers from exceptions at the dispatch stage. The functional units are matched both in terms of number of units and its latencies. In the Chapter 4, the hardware and software logic of architecture modeling are discussed in detail.

#### CHAPTER IV

#### SUPERSCALAR ARCHITECTURE MODEL

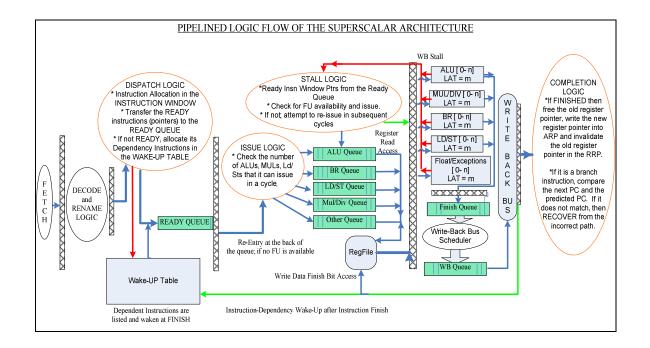

# **4.1 SUPERSCALAR DESIGN**

This chapter describes about the basic structure of AbaKus' superscalar processor models in detail. The models are described in a structure similar to an HDL that is discussed in Chapter 3. The functional description of the modules is in standard C++. The basic modules of the 7-stage pipeline are the fetch, decode, dispatch, issue, finish, write-back and complete. The implementation details of each of these modules follows below,

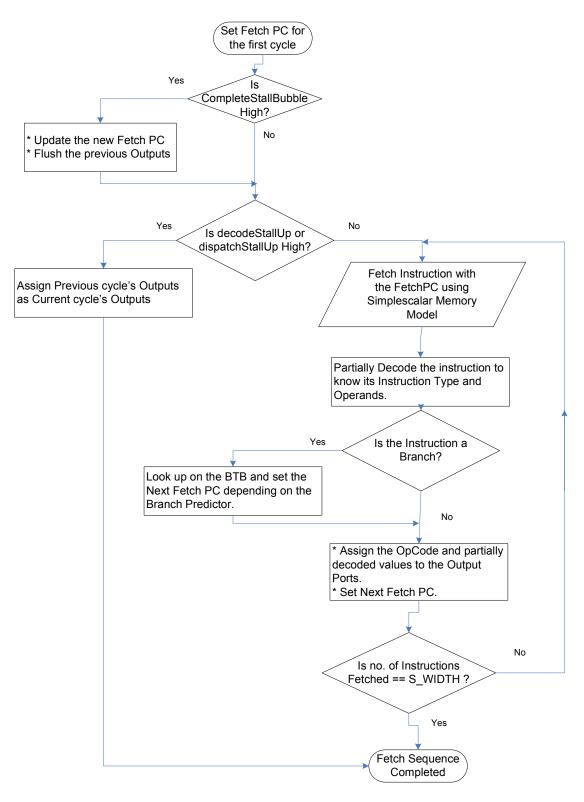

## **Fetch Stage**

In the CPU architecture core, the fetch stage of AbaKus architecture interfaces with the memory. The memory unit can be a cache module or the main memory. In a simple interface model, the fetch is interfaced to the main memory. Although, the memory interface architecture is a weak relationship with the actual CPU-Memory behavior, it can be extended to be interfaced with caches.

The following statement is a macro described in Simplescalar (Burger and Austin, 1997, [1]).

#### MD\_FETCH\_INST(inst, mem, fetchPC);

It is a direct interface to the main memory requiring only 3 arguments, the instruction object, main memory pointer and the Program Counter (PC) to fetch. A cache functional module can replace this statement in the fetch module. However, 2 additional signal arguments are required, if the cache functional module is interfaced, that is shown below, cache\_func(inst, cache\_mem, fetchPC, stallUp\_signal, hit\_signal);

The 2 additional signals, stallUp\_signal and hit\_signal are required to ensure both timing as well as data coherency respectively. Following the instruction fetch of the corresponding PC, the instruction is partially decoded to identify its type and operands. This is done for simulation speed-up and also to balance the work-load.

Since the branch predictor look-up can have a significant adverse effect on the simulation time, it is necessary that only branch instructions need to be searched in the look-up table of the Branch Target Buffer (BTB). Hence, after the type of instruction is known through the partial decoder, only the branch instructions are allowed to access the BTB and the branch predictors. This is described in Flow Chart 1.

The work-load between these stages must be balanced because the *decode stage* has override logic, free-register priority encoder and register renaming where as the *fetch stage* only has the function of instruction fetch interfaced to the main memory. However, depending on the required timing, the fetch stage can be further easily be super-pipelined into instruction fetch and partial decoder stages.

34

Flow-Chart 4.1 Fetch Functional Module

#### **Decode Stage**

As mentioned earlier, the main functionality of this stage as implemented in AbaKus architecture is selecting *free rename register*, *register override logic* and *register renaming logic*.

#### Selecting Free Rename Register:

This functional block selects the next free register available to be renamed. The instruction set architecture registers are renamed to avoid name dependency stalls in the superscalar architectures. Basically, the number of required renamed registers is equal to the sum of instruction window width and instruction fetch width.

Selecting the free register is simple. It only requires determining the bit that is not set from the list of busy bits. The corresponding index of the busy bit is the register pointer for the free register.

#### **Override** Logic:

This is a special case where the operands of one or more subsequent instructions in an instruction decode group refer to the destination register of any of its previous instructions. In this case, the override logic makes sure that the newly renamed register that would only be updated in the next cycle get referenced to the operand that matches its pointer in the same cycle. This logic is discussed by Shen and Lipasti, 2005 [16] and is implemented in the AbaKus architecture model.

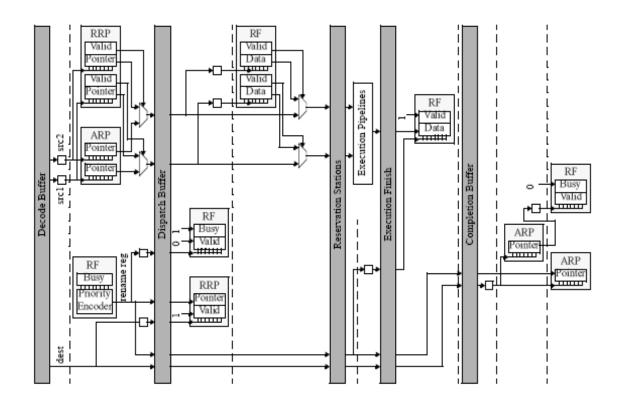

Register Renaming:

Register renaming is done by having 2 register pointer files – Architect Register Pointer File and Rename Register Pointer File. This is best explained with the help of the following diagram in Figure 4.1.

Register File (RF): Holds the values of the computed data.

Architect Register Pointer (RRP): Holds permanent register pointers for the 32, LO and HI registers of the Instruction Set Architecture (ISA). The updates are made at the complete stage.

Figure 4.1 Design of Rename Register Logic

Rename Register Pointer (RRP): Holds temporary register pointers for all the destination registers of in-flight instructions in the pipeline and is updated at the dispatch stage.

Hence, instructions with dependent source operands refer to the RRP at the decode stage to find out the correct dependent register pointers.

## **Dispatch Logic**

Instructions are dispatched to a special instruction window buffer after the decode logic. The number of entries in the instruction window is fixed during compilation time. The fields of the instruction window entry are shown in Figure 4.2.

| busy | completed       | d missp        | ecu    | ulat   | ed     | finishe   | ed issue | d in | Order | exception          | alu         | br          | mult   | L<br>D <sup>re</sup> | eadLO        | rea        | dHI        | wake<br>Up |

|------|-----------------|----------------|--------|--------|--------|-----------|----------|------|-------|--------------------|-------------|-------------|--------|----------------------|--------------|------------|------------|------------|

|      | Insn<br>Address | Insn<br>Opcode | R<br>D | R<br>S | R<br>T | RD<br>old | Pred PC  | NPC  | PC    | Ld_predict<br>Addr | bpre<br>upd | ed_<br>late | Stack_ | _inde                | × STC<br>BUF | DRE<br>FID | LOA<br>BUF | AD<br>FID  |

Figure 4.2 Fields of Instruction Window Entry

The implementation of the instruction window buffer is a choice of the designer. For hardware logic implementations such as FPGA or custom IC, it is efficient to implement the instruction window buffer as a fully-associative memory. On the other hand, for a software simulation it is efficient to implement this special buffer as a direct-mapped cache.

In Figure 4.2, the hashed fields represent a single bit field and the remaining fields are represented by 32 bits in the software implementation. However, the number of bits should be discerned carefully for the hardware implementation depending on the requirement. The summary of description of each field is described in Table 4.1.

| Name of the Field | Description                                  |  |  |  |  |  |

|-------------------|----------------------------------------------|--|--|--|--|--|

| Busy              | Indicates the entry is busy or free.         |  |  |  |  |  |

| ~                 | Indicates the instruction is                 |  |  |  |  |  |

| Completed         | completed/committed                          |  |  |  |  |  |

|                   | Indicates the instruction is misspeculated   |  |  |  |  |  |

| Mis-speculated    | and have to thrown out.                      |  |  |  |  |  |

|                   | Indicates the instruction has finished       |  |  |  |  |  |

| Finished          | execution                                    |  |  |  |  |  |

|                   | Indicates the instruction has its operands   |  |  |  |  |  |

| Issued            | ready and is issued in the issue queue.      |  |  |  |  |  |

|                   | Indicates the instruction enforces order of  |  |  |  |  |  |

|                   | fetch, i.e. the STORE instruction forces all |  |  |  |  |  |

| InOrder           | other instructions fetched before it must be |  |  |  |  |  |

|                   | completed, if no load prediction/memory      |  |  |  |  |  |

|                   | disambiguation is turned on.                 |  |  |  |  |  |

|                   | syscall or any special instructions that is  |  |  |  |  |  |

| Exception         | not implemented in the hardware to be        |  |  |  |  |  |

|                   | treated as an <i>exception</i> .             |  |  |  |  |  |

| ALU               | Indicates an ALU type of instruction.        |  |  |  |  |  |

| D                 | Indicates a BRANCH/JUMPtype of               |  |  |  |  |  |

| Br                | instruction.                                 |  |  |  |  |  |

| lD                | Indicates a LOAD type of instruction.        |  |  |  |  |  |

|                   | Indicates a Multiplication/Division type of  |  |  |  |  |  |

| Mult              | instruction.                                 |  |  |  |  |  |

|                   | Indicates a lower 32-bit of the 64-bit       |  |  |  |  |  |

| readLO            | multiplication result.                       |  |  |  |  |  |

|                   | Indicates a higher 32-bit of the 64-bit      |  |  |  |  |  |

| readHI            | multiplication result.                       |  |  |  |  |  |

|                   | Instruction Address (32-bit) of the          |  |  |  |  |  |

| Insn Address      | instruction                                  |  |  |  |  |  |

TABLE 4.1. SUMMARY OF DESCRIPTION ON THE FIELDS OF THE INSTRUCTION WINDOW

|                    | Instruction Opcode (insn A & insn B) of     |  |  |  |  |  |  |

|--------------------|---------------------------------------------|--|--|--|--|--|--|

| Insn Opcode        | the instruction                             |  |  |  |  |  |  |

| RD                 | Destination Register                        |  |  |  |  |  |  |

| RS                 | Source Operand A                            |  |  |  |  |  |  |

| RT                 | Source Operand B                            |  |  |  |  |  |  |

| Rd_Old             | Old Destination Register                    |  |  |  |  |  |  |

| PC                 | Program Counter                             |  |  |  |  |  |  |

| NPC                | Next Program Counter                        |  |  |  |  |  |  |

| Pred PC            | Predicted Program Counter at the branch     |  |  |  |  |  |  |

| i leu i c          | instruction                                 |  |  |  |  |  |  |

| Ld_Predict Address | Predicted Load Dependent Address at         |  |  |  |  |  |  |

|                    | Fetch                                       |  |  |  |  |  |  |

| Bpred_update       | Branch Update Structure Pointer             |  |  |  |  |  |  |

| Stack_index        | Index of the Branch Stack for a direct jump |  |  |  |  |  |  |

| Stack_Index        | instruction.                                |  |  |  |  |  |  |

| STORE BUF ID       | Index of the top of STORE Buffer            |  |  |  |  |  |  |

| LOAD BUF ID        | Index of the top of LOAD Buffer             |  |  |  |  |  |  |

| Waka Up            | 0 – Indicates both Rs and Rt are not Ready. |  |  |  |  |  |  |

| Wake-Up            | 1 – Indicates either Rs or Rt is Ready.     |  |  |  |  |  |  |

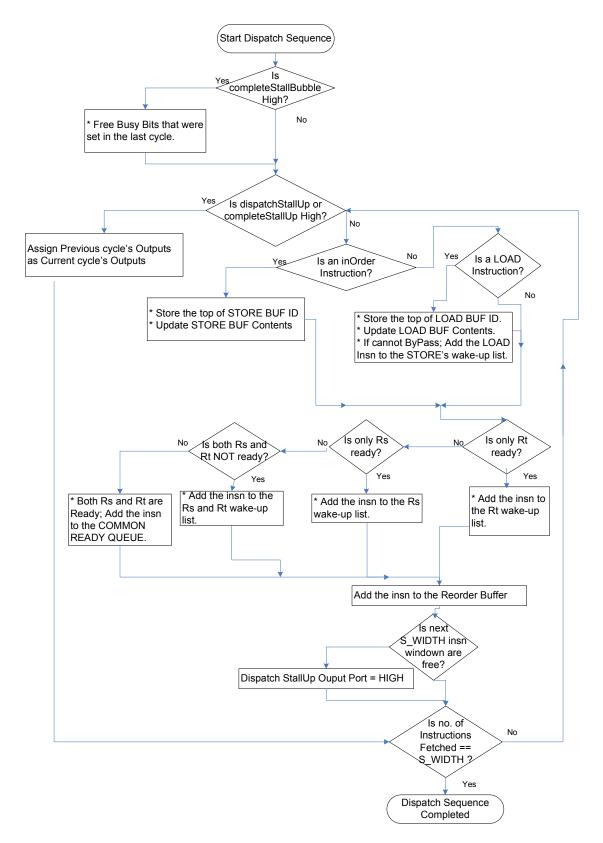

The dispatch logic is described in the Flow Chart 4.2. The head pointer of the instruction window is incremented and it is determined if the next 'S\_WIDTH' of instruction window entries are available. If not, then the output port of the *dispatchStallUp* signal is raised high.

Flow Chart 4.2 Dispatch Logic

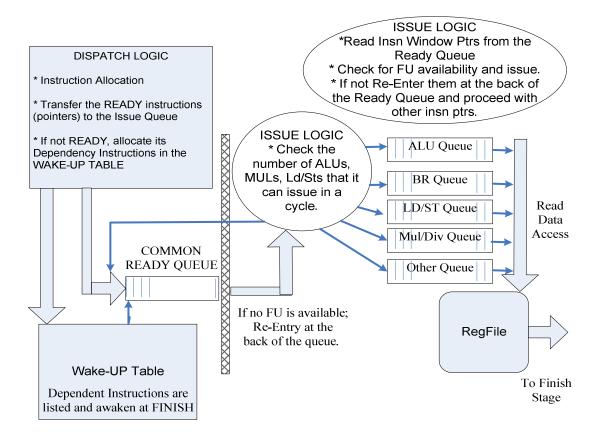

# **Issue Logic**

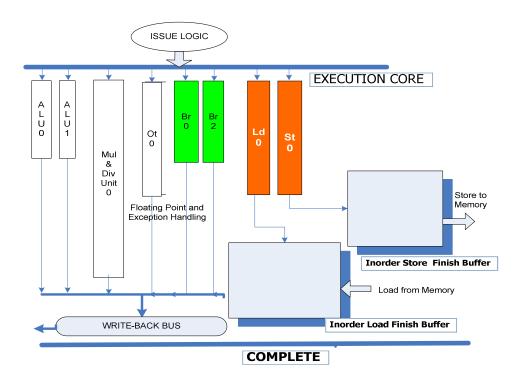

The issue logic reads the instructions in the *Common Ready Queue* and adds it to the separate *issue queue* that is specific for each instruction type. Basically, there are 5 categories of *issue queue* – ALU, BR, LD/STORE, MULT/DIV and Other instructions such as *syscall*, *DLW*, *DSW* and other floating-point instructions. It is important that the instructions have individual queues because a *stall* in one of the functional unit would not stall-up the entire queue. The functional block of the *dispatch logic and the issue logic* is illustrated in Figure 4.3.

Figure 4.3. Functional Block Diagram of the Issue Logic

- [1] The pointer of the ready instruction that is put into the *Common Issue Ready* is read and its corresponding instruction window entry and the instruction type are determined.

- [2] Depending upon the type of instruction, it is then added to the respective instruction issue queue. Step 1 and 2 are continued until all the ready instructions in the *Common Issue Ready* are added into its specific instruction type queues.

- [3] Finally, if there is no *stall-up* signal for the corresponding issue queue then the instruction is assigned to the output ports for issue. Although, the instruction is assigned for issue, it is only finalized, i.e. the *issue bit* is set only in the next cycle because there can be a stall in the *execute stage* that is propagates to the *issue stage* only in the next cycle.

A *Round-Robin priority* issue is implemented in order equally distribute the instruction issue among the different instruction types. The number of instruction issues is set as a compilation parameter in the *sc\_datatypes.h* file. The issue queue stalls due to unavailability of functional units and finalization of the instruction issue are determined in the next stage – *Execute Stage*. The number of entries in the individual issue queue is a compilation parameter and is set equal to the number of entries in the instruction window. Stall-Up signals due to unavailability of issue queue entry is not implemented, however, *the optimal number of entries in the individual issue queue* is a topic of future research.

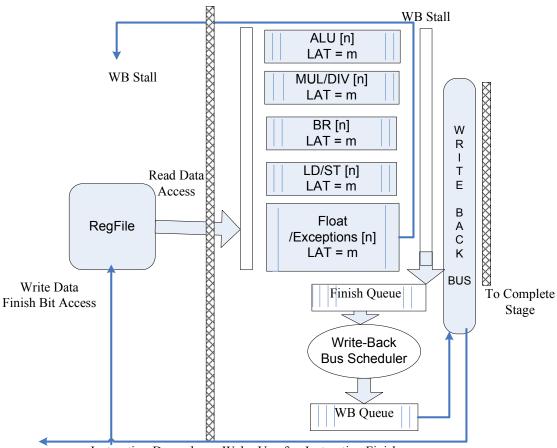

## **Execute Stage**

The execute stage consists of ALU, Mult/Div, BR, LD/STORE and Float/Other instructions functional units. Each of functional units has latency, 'm', which is a compilation parameter. Besides, the number of functional units, 'n', of each instruction type is also a variable that is defined during the program compilation.

Instruction-Dependency Wake-Up after Instruction Finish

Figure 4.4. Functional Block Diagram of the Execute Stage.

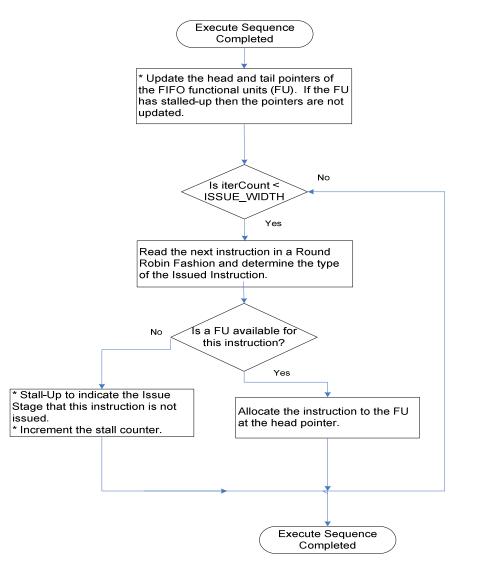

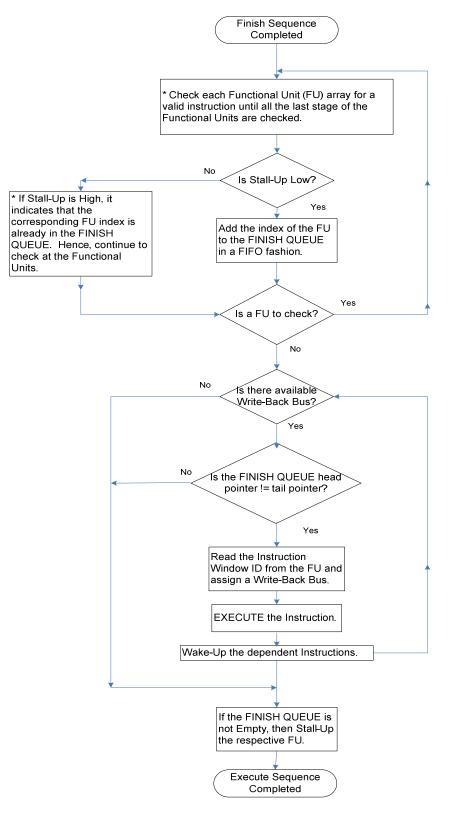

It should be noted that at the execute stage only the latency of the instruction execution is simulated but the actual instruction execution takes place only at the finish/write-back stage. The pipeline stage of the functional unit is implemented as a circular FIFO queue. The head and tail pointers of the queue are updated at each cycle. The instructions are read from the issue queue and are assigned to the corresponding functional units in a round-robin fashion. If no functional units are available then a *stall-up* signal is for the corresponding functional unit is raised high. After a fixed number of cycles, the inserted instructions in the circular FIFO queue at the head pointer propagate to the tail pointer. Once the instruction i.e. the instruction window ID reaches the tail pointer, it is determined to be finished the execution. As shown in Figure 4.4, the instruction is then inserted into the *finish queue*.

Flow Chart 4.3 Execute Stage

## **Finish/Write-Stage:**

The *finish-stage* is an important module as instructions are scheduled to finish by accessing the write-ports of the *Register File*, if required, and also its dependent instructions are waken-up. In addition, the function execution of the instruction takes place at this stage through a subroutine macro call –  $SYM\_CAT()$ . As shown in Figure 4.4, the finished instructions are inserted into the FINISH QUEUE. The order in which the instructions are scheduled into this queue determines the write-back bus scheduling order. By default, the instructions are arranged in the FINISH QUEUE in a FIFO fashion. A more detailed study of scheduling the instructions in the FINISH QUEUE is discussed later in Chapter 5.

The instructions are read from the FINISH QUEUE and assigned a write-back bus, if available. If the write-back bus is not available, then that specific Functional Unit is stalled-up. Once assigned a write-back bus the instruction is set to finish, i.e. the instruction is functionally executed and the results are updated in the register file in the next cycle.

Once the instruction finishes execution, its dependent instructions are found by walking through the dependent list of the wake-up structure. The wake-up structure has a list of instruction window pointers. Either the wake-up bit of the dependent instruction window slot is set to 1 or the instruction is directed to the READY QUEUE depending upon its operands validity. The finish-stage functionality is further illustrated in Flow Chart 4.4.

Flow Chart 4.4 Finish Stage Logic

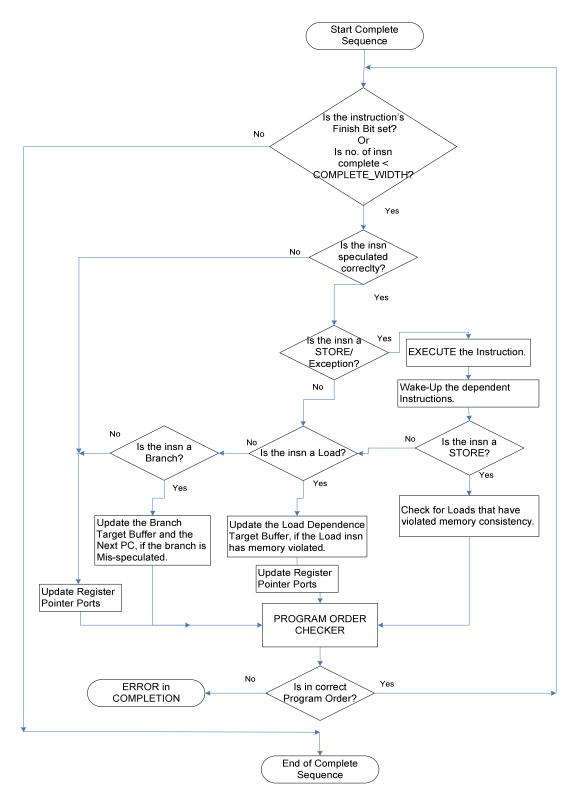

## **Complete Stage**

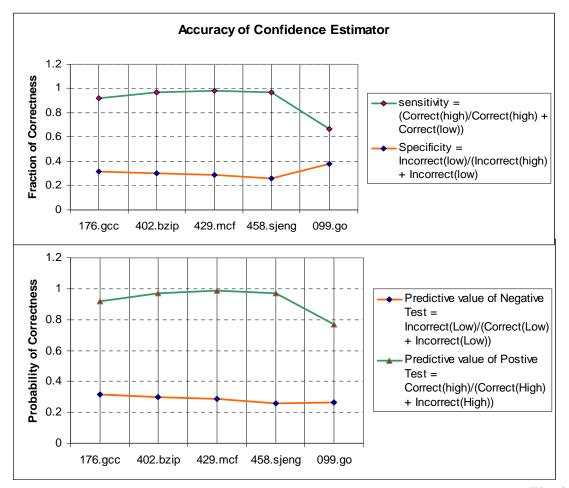

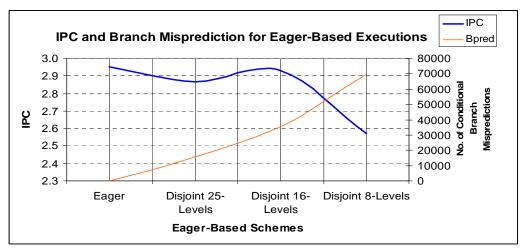

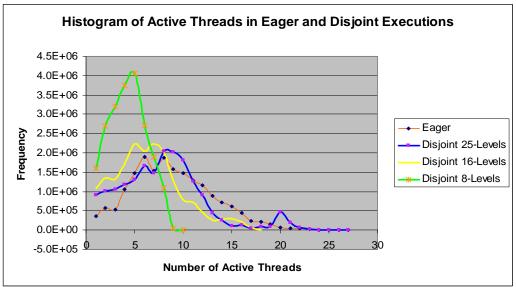

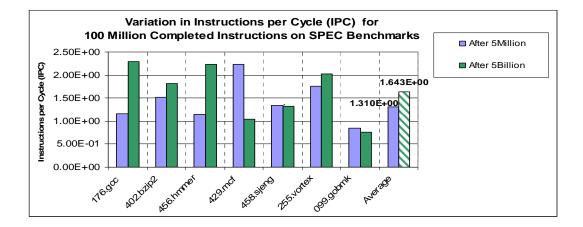

The *complete stage* includes retiring the STORE instructions, executing the FLOAT and exception causing instructions, waking up dependent instructions and resetting the instruction window and register pointer entries. In addition, the complete stage also has *in-order instruction checking mechanism* to ensure that the completing instruction is the instruction in the program order. Apart from these functionalities, the complete stage also takes care of memory disambiguation that is discussed later in this chapter. The instructions are ready for complete, when they have finished execution and assigned for completion based on the program order. The maximum number of instructions that can be completed is defined as COMPLETE\_WIDTH in the *sc\_datatypes.h* header file.