# A PROPOSED 10-BIT HIGH-SPEED

### **TWO-STEP NEURAL-BASED**

# ANALOG-TO-DIGITAL

# **CONVERTER**

By

#### JIE ZHENG

Bachelor of Science

University of Science and Technology of China

Hefei, China

1985

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE December, 1997

# A PROPOSED 10-BIT HIGH-SPEED

# **TWO-STEP NEURAL-BASED**

# ANALOG-TO-DIGITAL

# CONVERTER

Thesis Approved: Chur Milchen Thesis Advisor Anni S. Amn Mayne B Powell

Bean of the Graduate College

ii

### ACKNOWLEDGEMENTS

This study was conducted to propose a new architecture for high-speed (2.5-GHz) and high-resolution (10-bit) A/D converter. The key functional blocks of the proposed architecture were designed, simulated and laid-out for fabrication. The 4-bit flash ADC system were tested.

I wish to express my sincere appreciation to my major advisor, Dr. Chriswell Hutchens for his intelligent supervision, constructive guidance and inspiration. My sincere appreciation extends to my other committee members Dr. Louis G. Johnson and Dr. Scott T. Acton. I would like to thank the Naval Ocean Surveillance Command for providing the research opportunity and financial support to this project.

Moreover, I wish to express my sincere gratitude to my colleagues who provided suggestions and assistance for this study.

I would also like to give my special appreciation to my wife, Xiaojun Chen, for her strong encouragement at times of difficulty, love and understanding throughout this whole process. Thanks also go to my parents for their support and encouragement.

Finally, I would like to thank the Department of Electrical and Computer Engineering for supporting during these years of study.

iii

|  | AC) | 35 |

|--|-----|----|

|  |     |    |

# TABLE OF CONTENTS

| Cl | Papter                                        | age |

|----|-----------------------------------------------|-----|

|    |                                               |     |

| 1. | INTRODUCTION                                  | 1   |

|    | 2                                             |     |

|    | 1.1 Objective                                 | 4   |

|    | 1.2 Organization                              | 4   |

| 2. | LITERATURE REVIEW                             | 6   |

|    | 2.1 High-Speed ADC Architectures              | 7   |

|    | 2.1.1 Flash A/D Converter                     | 7   |

|    | 2.1.2 Multi-Step A/D Converter                | 10  |

|    | 2.1.2.1 Subranging Architecture               | 13  |

|    | 2.1.2.2 Two-Step with Residual Scaling        | 13  |

|    | 2.1.2.3 Subranging with Partial Scaling       | 16  |

|    | 2.1.3 Folding and Interpolation A/D Converter | 18  |

|    | 2.1.4 Neural Network A/D Converter            | 22  |

|    | 2.2 Factors limiting accuracy                 | 25  |

|    | 2.2.1 Static Offset Voltages                  | 25  |

|    | 2.2.2 Dynamic Offset Voltages                 | 26  |

|    | 2.2.3 Noise                                   | 29  |

|    | 2.2.4 DAC Errors                              | 30  |

|    | 2.3 Comparators Amplification Techniques      | .31 |

|    | 2.3.1 Single Pole Amplifier (SPA)             | 31  |

|    | 2.3.2 Multistage Amplifier (MA)               | 33  |

|    | 2.3.3 Regenerative Amplifier (RA)             | 33  |

| 2.4 Digital-to-Analog Converter (DAC)                                |

|----------------------------------------------------------------------|

| 3. 4-BIT FLASH ADC IMPLEMENTATION AND TESTING RESULTS                |

| 3.1 4-Bit Flash ADC System Building Blocks                           |

| 3.1.2 Bubble Detector                                                |

| 3.1.3 Encoder/Latch                                                  |

| 3.1.4 Input Buffer and Output Buffer                                 |

| 3.2 Testing Results                                                  |

| 3.2.1 P and N Transistors Testing Results                            |

| 3.2.2 Functional Blocks Testing Results                              |

| 3.3 Future Design Considerations    79                               |

|                                                                      |

| 4. A PROPOSED TWO-STEP NEURAL-BASED A/D CONVERTER                    |

| 4.1 Hopfield Neural Network A/D Converter                            |

| 4.1.1 HADC with Symmetric Interconnections                           |

| 4.1.2 HADC with Non-Symmetric Interconnections                       |

| 4.1.3 Worst Case Delay of HADC                                       |

| 4.2 Two-Step Neural-Based A/D Converter Building Blocks              |

| 4.3 Voltage-to-Current Converter                                     |

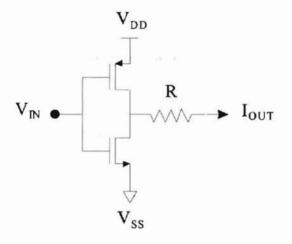

| 4.3.1 Resistor Type                                                  |

| 4.3.2 Switch Type                                                    |

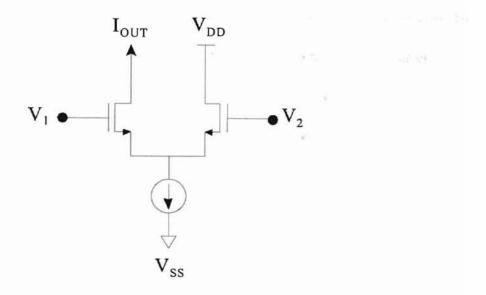

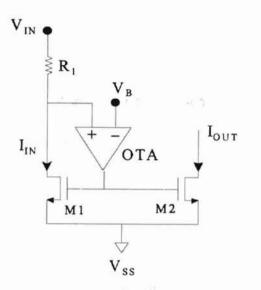

| 4.3.3 CMOTA Type                                                     |

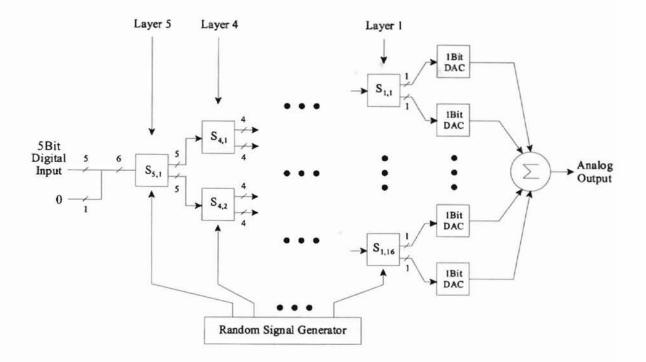

| 4.4 Dynamic Element Matching (DEM) DAC 101                           |

| 4.4.1 DEM DAC System Building Blocks                                 |

| 4.4.2 1-Bit DAC Bank 103                                             |

| 4.4.3 Switching Block                                                |

| 4.4.4 Random Signal Generator                                        |

| 4.5 Performances of Proposed Two Step Neural-Based A/D Converter 107 |

| 4.5.1 Conversion Rate                                                |

| 4.5.2 Accuracy and Bandwidth 109                                     |

| 4.5.3 Area and Power Dissipation<br>4.5.4 Comparison between Two-Step Neural-Based ADC and Two-Step Flash |     |

|-----------------------------------------------------------------------------------------------------------|-----|

| ADC                                                                                                       | 110 |

| 5. CONCLUSIONS AND SUGGESTIONS                                                                            | 112 |

| BIBLIOGRAPHY                                                                                              |     |

| APPENDIX A. FOLDING AND INTERPOLATION A/D CONVERTER                                                       | 121 |

does so that the

the state of the providence of the state

| at Scher et neur Prachetarest Comparator                                  |

|---------------------------------------------------------------------------|

| 5., 3 1.K1 and CLR2                                                       |

| LIST OF FIGURES                                                           |

| 40.40                                                                     |

| Figure Page                                                               |

| 2.1 A Typical Flash A/D Converter System Diagram                          |

| 2.2 Two-Step A/D Converter System Block Diagram                           |

| 2.3 Two-Step Subranging A/D Converter System Block Diagram                |

| 2.4 Two-Step with Residual Scaling A/D Converter System Block Diagram15   |

| 2.5 Subranging with Residual Scaling A/D Converter System Block Diagram17 |

| 2.6 A Folding ADC Architecture 19                                         |

| 2.7 An Interpolation ADC Architecture                                     |

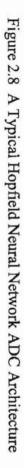

| 2.8 A Typical Hopfield Neural Network ADC Architecture                    |

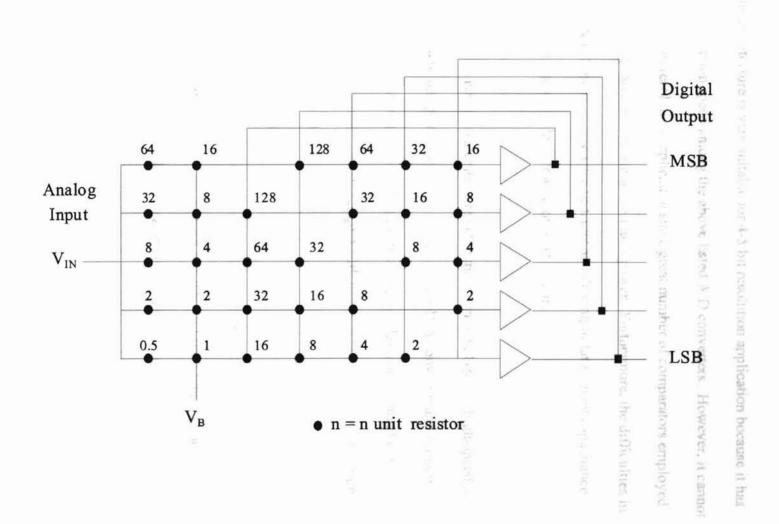

| 2.9 Comparator with Autozeroing Technique                                 |

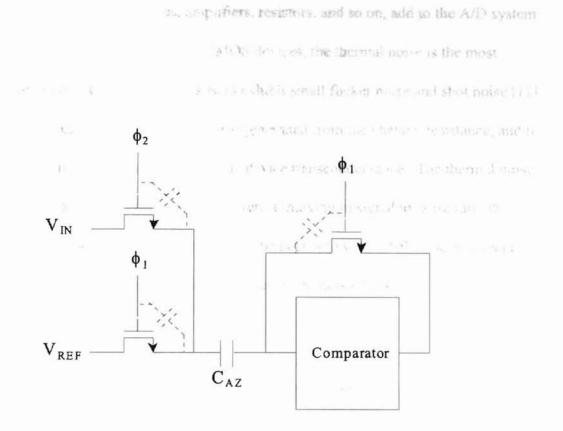

| 2.10 General Approaches to Obtain Amplification in Comparators            |

| 2.11 Three Kinds of Most Commonly Used DAC 36                             |

| 3.1 4-Bit Flash A/D Converter System Block Diagram                        |

| 3.2 (a) Schematics of Regenerative Comparator                        |

|----------------------------------------------------------------------|

| 3.2 (b) Timing of Clock Signals CLK1 and CLK2 43                     |

| 3.3 Small Signal Equivalent Circuit of Setting and Resetting Process |

| 3.4 Simulation Result of Regenerative Comparator 49                  |

| 3.5 Schematic of Bubble Detector                                     |

| 3.6 Schematic of Encoder                                             |

| 3.7 Simulation Result of Encoder                                     |

| 3.8 Schematic of Input Buffer                                        |

| 3.9 Schematic of Output Buffer                                       |

| 3.10 P Transistor Characteristics                                    |

| 3.11 N Transistor Characteristics                                    |

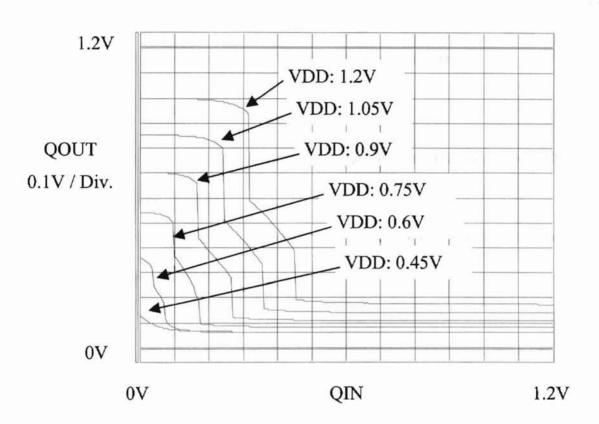

| 3.12 Output Buffer DC Sweep Response                                 |

| 3.13 Pulse Transient Response of Output Buffer                       |

| 3.14 Gate Delay Per Stage Versus Power Supply                        |

| 3.15 Input Buffer DC Sweep Response                                  |

| 3.16 Pulse Transient Response of Input Buffer                        |

| 3.17 Bubble Detector DC Sweep Response                                           |

|----------------------------------------------------------------------------------|

| 3.18 AC Response of Bubble Detector                                              |

| 3.19 Gate Delay Versus Power Supply                                              |

| 3.20 Comparator DC Sweep Response                                                |

| 3.21 Clock Pulse Transient Response of Comparator                                |

| 3.22 Encoder DC Sweep Response                                                   |

| 3.23 Pulse Transient Response of Encoder                                         |

| 3.24 Output Pad Model for Analysis                                               |

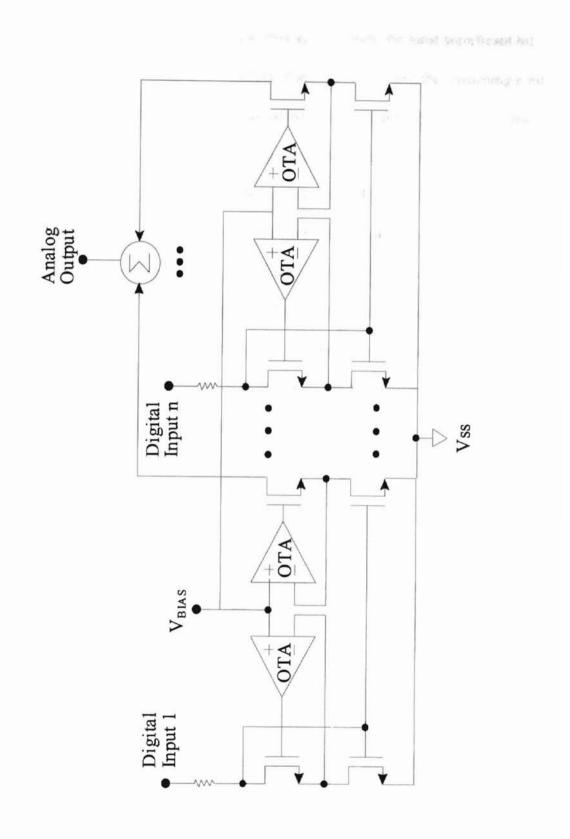

| 4.1 A 5-Bit Non-Symmetric Type Hopfield Neural-Based A/D Converter85             |

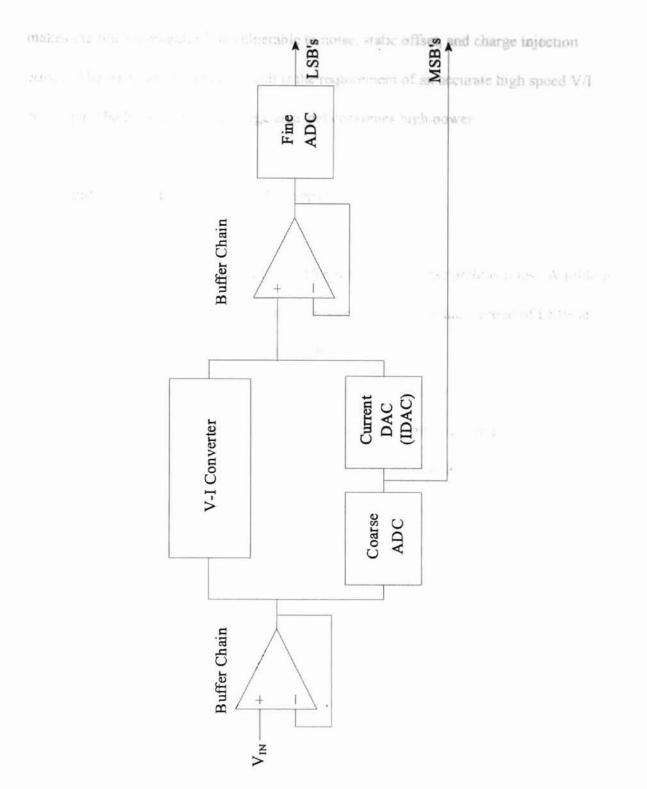

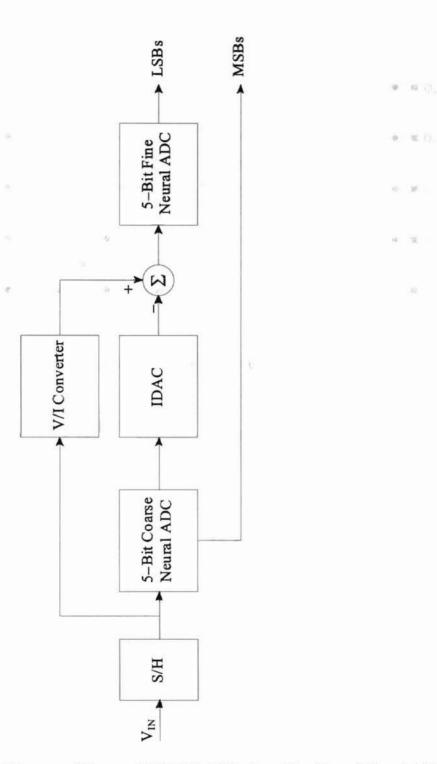

| 4.2 The Block Diagram of Proposed 10-Bit 2.5GHz Two-Step Neural-Based ADC 88     |

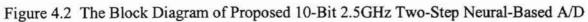

| 4.3 The 5-Bit Neural-Based Coarse A/D Converter                                  |

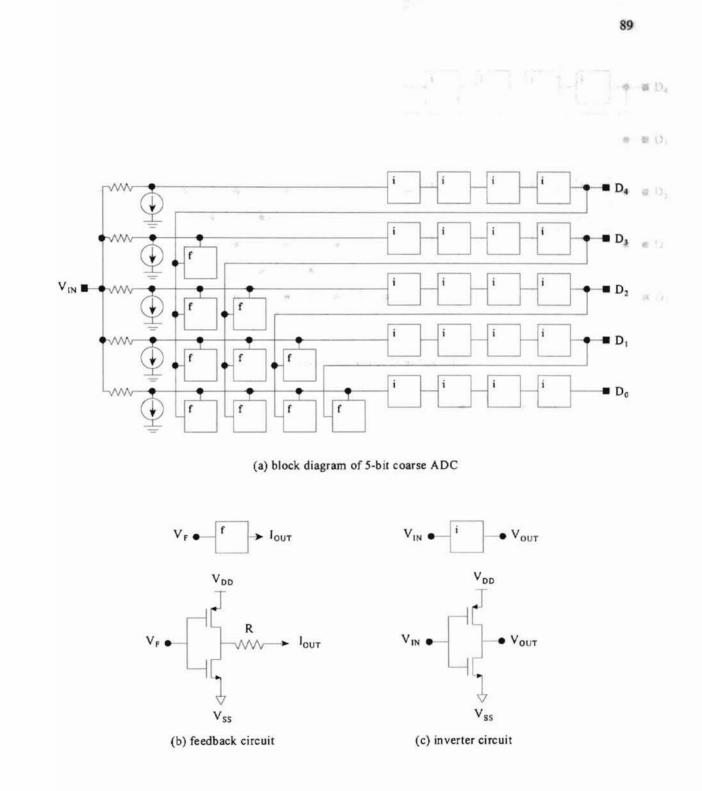

| 4.4 The 5-Bit Neural-Based Fine A/D Converter                                    |

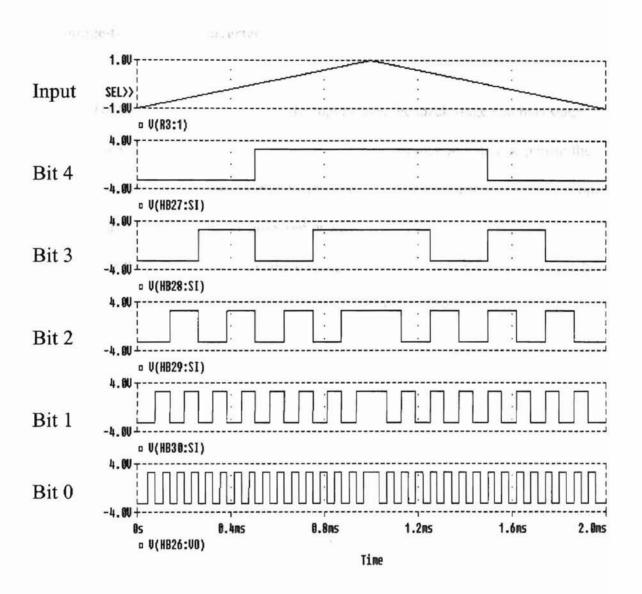

| 4.5 Functional Simulation Result of the 5-Bit Neural-Based Coarse and Fine ADC91 |

| 4.6 Resistor Type Voltage-to-Current Converter                                   |

| 4.7 Switch Type Voltage-to-Current Converter                                     |

| 4.8 Current Mirror with OTA Type Voltage-to-Current Converter                    |

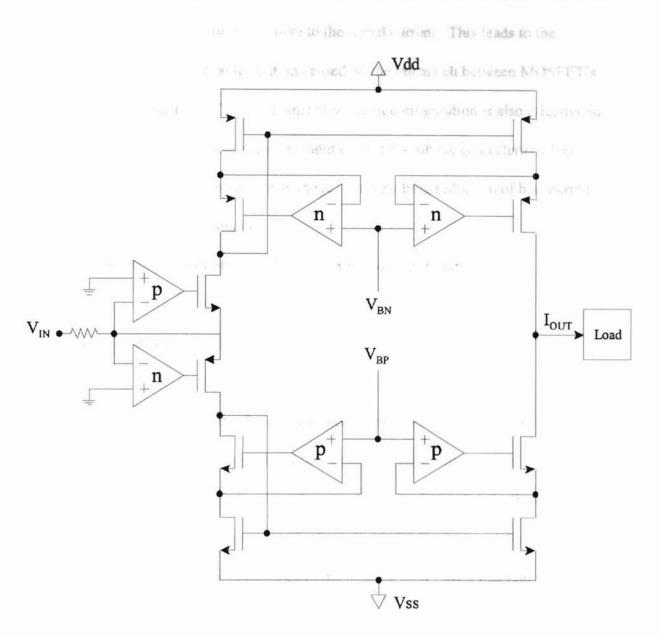

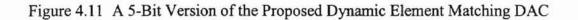

| 4.9 A 10-Bit Accuracy AB Class Type Voltage-to-Current Converter10                |

|-----------------------------------------------------------------------------------|

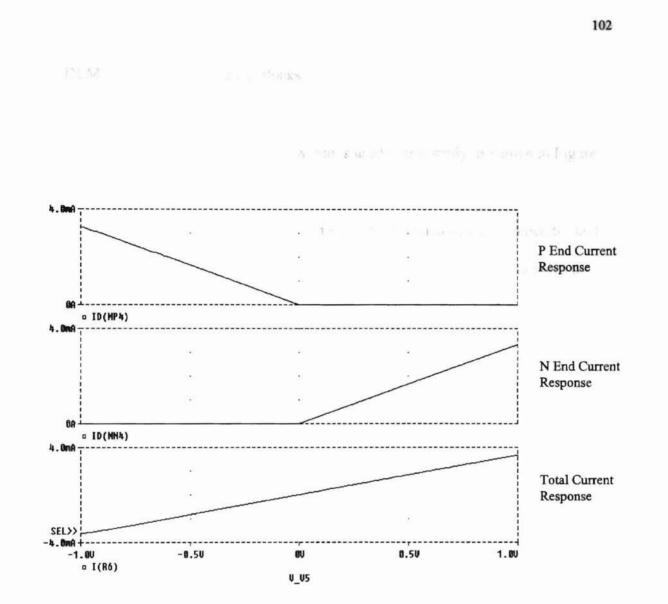

| 4.10 DC sweep simulation result of 10-Bit Accuracy AB Class Type V/I Converter 10 |

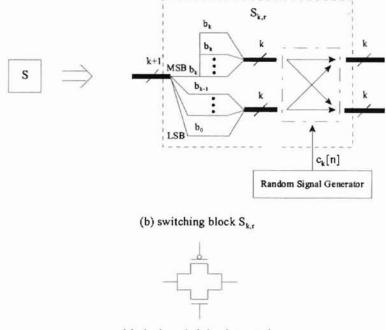

| 4.11 A 5-Bit Version of the Proposed Dynamic Element Matching DAC10               |

| 4.12 10-Bit Accuracy 1-Bit DAC Bank 10                                            |

| 4.13 Pseudo Random Signal Generator 10                                            |

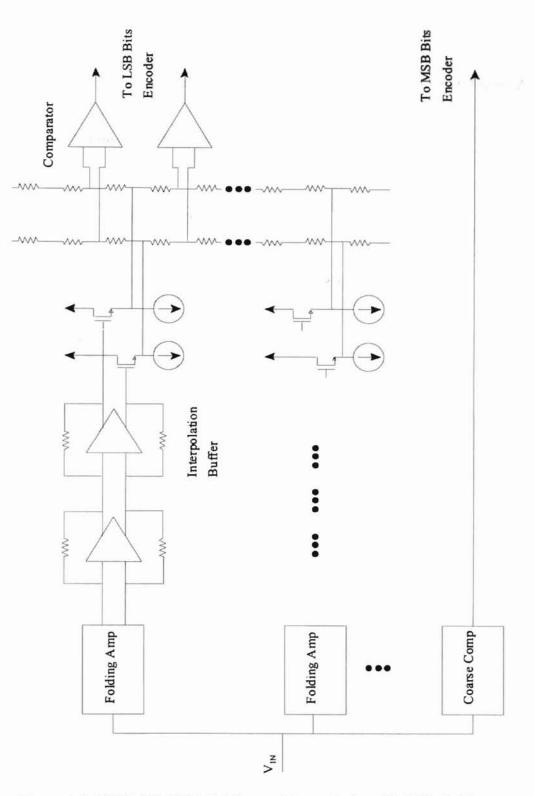

| A.1 10-bit 2.5 GSPS Folding and Interpolation ADC Block Diagram                   |

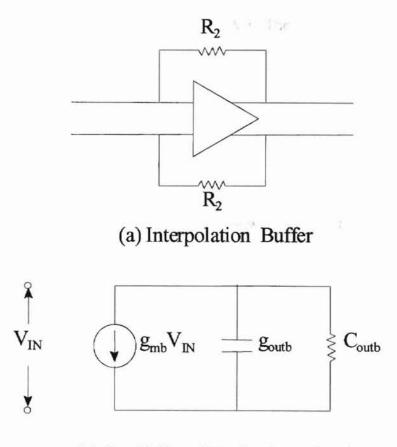

| A.2 (a) Interpolation Buffer (b) Small Signal Equivalent Circuit                  |

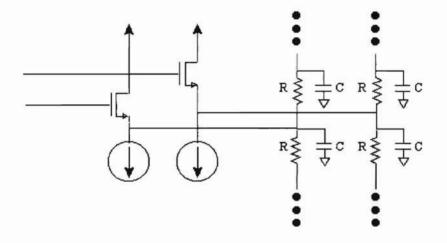

| A.3 Schematic of Source Follower                                                  |

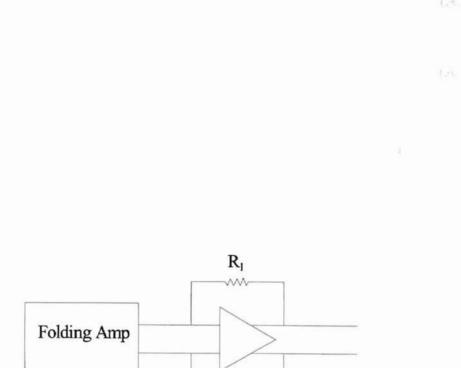

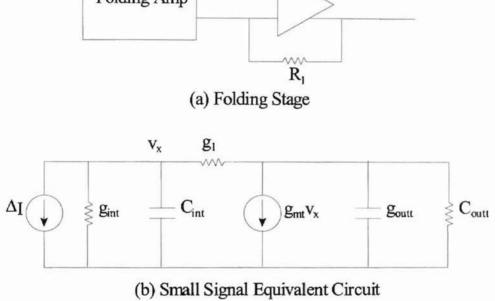

| A.4 (a) Folding Stage (b) Small Signal Equivalent Circuit                         |

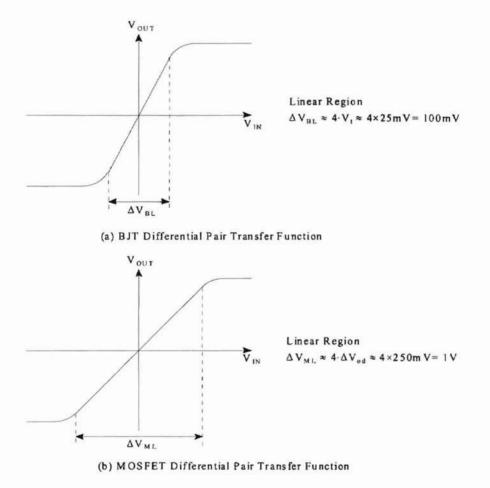

| A.5 Differential Pair Transfer Function (a) BJT (b) MOSFET13                      |

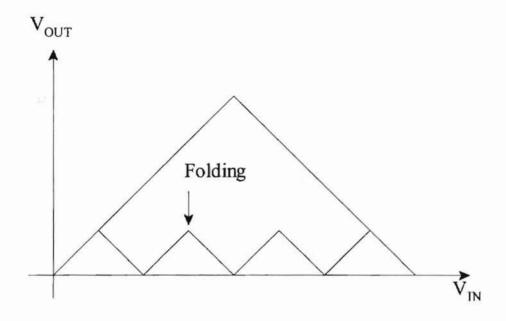

| A.6 Transfer Curve of Folding Circuit                                             |

Construction Marameter

# NOMENCLATURE

- I<sub>D</sub> Drain Current

- V<sub>s</sub> Source Potential

- V<sub>T</sub> Threshold Voltage

- V<sub>TN</sub> NMOS Threshold Voltage

- V<sub>TP</sub> PMOS Threshold Voltage

- k Boltzmans Constant

- T Temperature in Degree Kelvin

- f Frequency

- R Resistance

- C Capacitance

- LSB Least Significant Bit

- MSB Most Significant Bit

- C<sub>L</sub> Load Capacitance

- V<sub>DD</sub> Positive Power Supply

- V<sub>ss</sub> Negative Power Supply

- g<sub>m</sub> Transconductance Parameter

- R<sub>o</sub> Output Impedance

- g<sub>ds</sub> Drain to Source Transconductance Parameter

- V<sub>IN</sub> Input Voltage

- Vout Output Voltage

- V<sub>REF</sub> Reference Voltage

- C<sub>gs</sub> Gate to Source Capacitance

- C<sub>gd</sub> Gate to Drain Capacitance

- C<sub>ds</sub> Drain to Source Capacitance

- CLK Clock Signal

- ΔV Gate Overdrive Voltage of MOSFET

- $\omega_{T}$  Unity Gain Frequency

- $\tau_x$  Time Constant of X

- t<sub>d</sub> Delay Time

- GBP Gain Bandwidth Product

- Vos Offset Voltage

- W/L Width to Length Ratio for the Transistor

- μ Transistor Self Gain

- V<sub>FS</sub> Full Scale Voltage

- HADC Hopfield Neural Network Analog-to-Digital Converter

- V/I Voltage-to-Current Converter

- DEM Dynamic Element Matching

- CMOTA Current Mirror with OTA

I'v or zhep flach and a start of CHAPTER 1 ones of realizing high speed, high rasion to the first of the West Conversion rates approaching balf those of fully parallel A finance of the state of each transpoorders a relatively small most capacitance **INTRODUCTION**

provide a state of the second second bold concern.

Analog-to-digital (A/D) converters provide the interface between the analog signal domain and the binary digital computational domain. The development of digital signal processor (DSP) technology has increased the use and importance of the A/D converter. A 10 bit A/D converter with a high conversion frequency of over 2.5 GHz is needed for the applications of digital signal processing in telecommunication, networks, image processing, medical engineering system and consumer products. However, the maximum conversion frequency of the existing 10 bit A/D converter still remains in the order of 50-200 MHz [1][2][3].

Without doubt, the flash A/D converter (full parallel converter) gives the best conversion frequency performance. The negative attributes of this converter type are the large die size, high power dissipation and large input capacitance. Flash converter uses 2<sup>n</sup>-1 comparators and 2<sup>n</sup> matched resistors for n-bit resolution. Thus, the 1023 comparators, which are needed for a 10 bit application, result in large area, high power consumption as well as large input capacitance. Moreover, the input bandwidth is limited if the input is to be driven by a  $50\Omega$  signal due to the large buffer needed to drive the ADC's large number of comparators. Even with state-of-the-art technologies the flash architecture is clearly not an acceptable approach for a 10 bit 2.5 GHz A/D converter.

Two-step flash architectures are an effective means of realizing high speed, high resolution A/D converters. With conversion rates approaching half those of fully parallel A/D converter's, this type of architecture provides a relatively small input capacitance together with low power dissipation due to the reduced number of comparators required to achieve the high resolution. A two-step architecture uses a sample and hold circuit together with a high speed A/D – D/A coarse quantizer subtraction circuit. As a part of the effort it was determined that the sample and hold circuit requires a 1590 GHz process bandwidth for 10-bit 2.5GHz application. Such a high-performance sample and hold function is clearly not feasible with existing CMOS technology and is beyond the scope of this effort.

The folding and interpolation architecture, successfully used in high speed and high resolution bipolar A/D converter [1][4], employs considerable fewer comparators than a fully parallel converter and in addition does not require a sample and hold. The result is a high speed, low power dissipation converter with small die area. While incorporating the folding and interpolation scheme with MOS devices, this type converter suffers from an inherent limitation associated with the linearity of velocity saturated MOS devices. The folding factor number is as small as two due to the soft non-linearity of MOSFET differential pair transfer function (see Appendix A). This restriction results in folding CMOS architecture have a large number of comparators and large power consumption as well as matching difficulties. It was also found that the required 2.5GHz bandwidth for a folding architecture with MOS devices is also well beyond the reach of any current process.

1.1 O Neural networks behave essentially like analog nonlinear circuits.

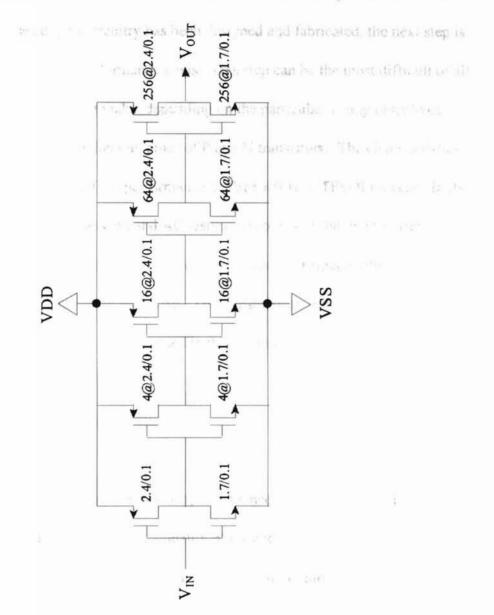

Interconnections between neurons (the elementary processing units) permits one to obtain high parallel computational capabilities, which potentially ensure high speed conversion. The Hopfield neural network is one of the most popular networks for electronic neural computing due to the simplicity of the network architecture and quick convergence in the time domain. Hopfield neural-based A/D converters have several advantages over conventional A/D converters. For a 10 bit Hopfield A/D converter only 45 neurons and 10 voltage to current converters are required. Thus, this architecture has a significantly smaller area than the fully flash A/D converter which employs 1023 comparators in the 10 bit case. By adjusting the contribution values between the amplifiers with a learning rule, the adaptive A/D converter with linear A/D conversion performance can be made. The adaptability of a neural-based A/D converter can be useful to compensate for initial device mismatches or long-term characteristic drifts. However, the conversion rate performance is constrained by the worst case delay of LSB (Least Significant Bit) when neural-based architecture applies to 8 ~ 10 bit resolution. The worst case delay happens when the variation of input signal causes the digital output to be changed from 100...00 to 011...11, or from 011...11 to 100...00. Moreover, the great size differences (up to 64 ~ 256) between neurons used in 8 ~ 10 bit application makes their matching very difficult to meet the resolution requirements. Therefore, the neural-based converter is suitable for the  $4 \sim 5$  bit resolution application and as previously noted has many advantages over the 4-5 bit flash A/D converter.

1.1 Objective and an functional testing subcells, which were fabricated on the IBM ten SCI SOS process, ore also presented.

The objective of this thesis is to investigate and propose a new type A/D converter architecture for high speed and high resolution application and has resulted in a two-step neural network-based A/D converter. This research presented here is based on a review of two-step flash A/D converters, analysis of the folding and interpolation scheme, and Hopfield neural network A/D converters. The analysis and testing results of 4-bit flash A/D converter cells are also used to support this proposal.

Incorporating the Hopfield neural network architecture into the two-step combines the advantages of both neural and two-step ADC. It is potentially a solution and currently the best choice for a 10 bit 2.5 GHz A/D converter although a high speed track and hold circuit is still needed for this architecture.

#### **1.2 Organization**

Chapter 1 has introduced the background and the purposes for this study.

Chapter 2 reviews the architectures of high-speed and high-resolution A/D converters: flash ADC, two-step ADC, folding and interpolation ADC, and neural-based ADC. The critical block functions of A/D converter, i.e., comparators, D/A converters, are also reviewed. The factors limiting accuracy are presented in this chapter.

Chapter 3 includes one architecture of 4-bit flash A/D converter system. The analysis, circuit simulations and test results have shown that high speed performance could be reached with proper laid-out and fabrication. The testing results of this 4-bit

ADC system and six functional testing subcells, which were fabricated on the IBM 0.1µm SOI/SOS process, are also presented.

Chapter 4 presents a Hopfield neural network A/D converter. The conversion rate, which is correlative with worst case delay of LSB, is calculated and confirmed by simulation. Three kinds of voltage-to-current converters, the key function block used in Hopfield neural network A/D converter, are analyzed. Based on the above work, the twostep neural-based A/D converter is proposed and its performance is estimated.

Chapter 5 summarizes the results of the study, conclusions, and recommendations.

Appendix A includes the analysis of a folding and interpolation architecture for velocity saturated CMOS process. The simulations support the result that the limitation of soft non-linearity of MOSFET differential pair restricts the maximum folding number while applying MOS devices to this architecture. For each of three stages: folding, buffer, and comparator, the requirements of matching and offset are described. The bandwidth requirement of process is analyzed and power dissipation of comparators is discussed.

# 1.4 High-speed ADC Architectur CHAPTER 2

will acculote the new of four commonly used high-speed

# LITERATURE REVIEW

test since i liefe anthronium shows a

Traditional analog-to-digital converter designs have used a flash architecture to obtain high conversion rate and a sigma-delta architecture to obtain the high resolution. For the resolutions greater than 8 bits, the fully flash A/D converter suffers from severe disadvantages. Not only the large area (exponential growth) and power dissipation but also the performance limitations due to a highly nonlinear input capacitance and reference mismatching problems have stimulated the development of multistage A/D converters, folding and interpolation A/D converters, and neural network-based A/D converters.

The first section of this chapter reviews the flash A/D converter followed by three different kinds of architectures for realizing high-speed and high-resolution analog-to-digital converters: two-step, folding and interpolation, and the Hopfield neural network. The second section reviews the factors limiting the accuracy of ADC systems. The third section presents three kind of comparators as well as their performances and limitations. The digital-to-analog converter, an essential block function for multistage ADC, is reviewed in the last section.

#### 2.1 High-Speed ADC Architectures

In this section, we will see a brief overview of four commonly used high-speed A/D converters, i.e., flash, multi-step, folding and interpolation and Hopfield neural network, as well as their performances. The best-known flash architecture shows a excellent speed performance. However, this architecture requires 2<sup>N</sup> -1 comparators to achieve an N-bit resolution. The alternatives to a full-flash architecture are the multi-step, folding and interpolation, and neural network A/D conversion principles. These architectures are capable of achieving a large analog bandwidth and high resolutions without incurring the power and area penalties associated with the flash architectures.

#### 2.1.1 Flash A/D Converter

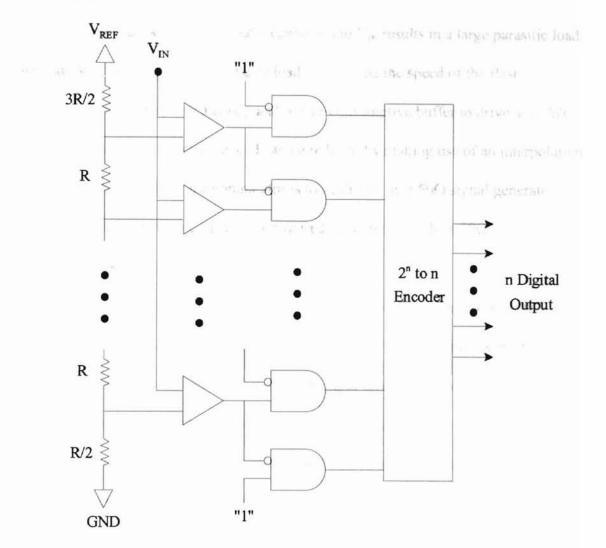

Flash converters are the standard approach for realizing very-high-speed converters, as seen in some publications [15][16][17]. The input signal in a flash converter is fed to 2<sup>n</sup>-1 comparators in parallel, as shown in Figure 2.1. Each comparator is also connected to a different node of the resistor string. Any comparator connected to a resistor string node where  $V_{REF}$  is larger than  $V_{IN}$  will have a '1' output while those connected to nodes with  $V_{REF}$  less than  $V_{IN}$  will have a '0' outputs. Such an output code word is commonly referred to as a thermometer code since it looks quite similar to the mercury bar in a thermometer. Note that the top and bottom resistors in the resistor string have been chosen to create the 0.5 LSB offset in an A/D converter. words of the univertant design issues that should be addressed when building high-

sellor forskill an arts i klinned as folker

```

· 新生生生的新闻的新闻的"

```

Figure 2.1 A Typical Flash A/D Converter System Diagram

Some of the important design issues that should be addressed when building highspeed flash A/D converters are outlined as follows. The amplifier circuits to control • Input Capacitance Load

The large number of comparators connected to  $V_{IN}$  results in a large parasitic load at the node  $V_{IN}$ . Such a large capacitance load often limits the speed of the flash converter and usually requires a strong and power-consumptive buffer to drive  $V_{IN}$ . We shall see that this large capacitance load can be reduced by making use of an interpolation architecture. Specifically, if the comparator is to be driven by a 50 $\Omega$  signal generator,  $C_{IN}$ should be less than  $1/(2\pi R\omega)$ , where  $\omega$  is required bandwidth and R is 50 $\Omega$ .

#### • Reference Resistor String Nonideality

A primary factor determining the basic DC linearity of any flash ADC is the matching that is obtained in the elements of the resistor divider. Uniform reference levels must be established without being affected by the input drive requirements of the bipolar inputs or the setup time of the capacitor levels during the autozero interval. Matching of the resistor ladder elements depends partially on the patterning techniques that are used in the fabrication process. It is also dependent on geometry, which is dictated by the layout and the particular process. The accuracy of reference resistor string is limited to 5-6 bit [31].

### Sampling Clock Jitter

The sampling clock jitter, a function of the sample/hold (S/H) circuit noise, is critical in determining the maximum frequency that can be converted by an ADC system. Therefore, it must be designed to be very small. Internally, a small rise or fall time of the

sampling clock avoids additional jitter caused by noise of the clock amplifier circuits. This requires large geometry transistors to be used in the amplifier circuits to control

thermal or kT/C noise ( $\Delta t = \frac{\sqrt{kT/C}}{\pi f_{CLK} V_{FS}}$ , or for comparator switches at 1GHz,  $\Delta t = 0.09$ ps). Furthermore, crosstalk with the other circuits in the vicinity must be minimized to avoid modulation of the sampling clock.

Clock Skew and Input Signal

Even very small differences in the arrival of clock or input signals at the different comparators can cause errors. For a high speed input signal, it would only take very small time to change through 1 LSB ( $\Delta t < \frac{1}{\pi f_B 2^{n+1}}$ , or at 1GHz,  $\Delta t < 5ps$  and 0.16ps for

5 bit and 10 bit respectively). If there is a clock skew between comparators greater than 1 LSB, the converter will then produce a false logic function. One means of easing this problem is to precede the converter by a sample-and-hold circuit. However, accurate high-speed sample-and-hold circuits can be more difficult to realize than the flash converter itself. It should also be noted that the delay differences may not be caused just by the routing differences of clock and  $V_{IN}$  signals, but could also be caused by process variation of drives, switches and capacitance loading.

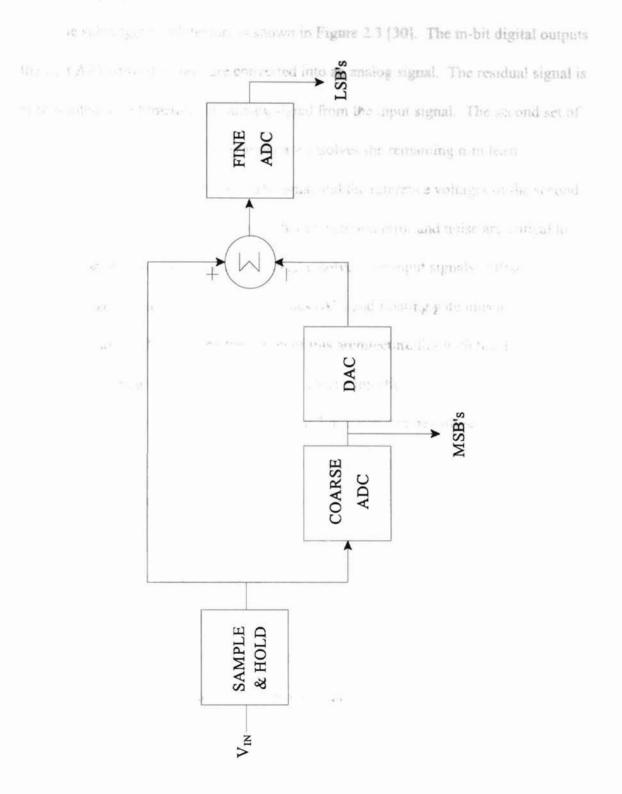

#### 2.1.2 Multi-Step A/D Converter

To avoid some of the problems encountered with a full-flash converter the multistep architecture was developed [21-24]. Multi-step A/D converters employ much fewer comparators than the flash ADC with insignificant sacrifice of conversion rate. Since three or more stages have the difficulties of complex sample and hold circuits with little additional reduction in area, the two step has become the prevalent solution for high speed A/D converter with a resolution of 8-10 bits. Specifically, two-step converters require less silicon area, dissipate less power, have less input capacitance load, and the voltage which the comparators need to resolve are less stringent than for flash equivalents. However, two-step converters do have a larger latency delay, although their throughput approaches that of flash converters. The general block diagram for a two-step converter is shown in Figure 2.2.

The operation of this two-step converter is as follows. The m-bit MSB A/D determines the first m MSBs of n bit digital output. To determine the remaining LSBs, the quantization error is found by reconverting the m-bit digital signal to an analog value using the m-bit D/A and subtracting that value from the input signal. With this approach, rather than requiring 1023 comparators as in a 10-bit flash converter, only 62 (2<sup>m</sup>+2<sup>n-m</sup>-2, here m=5, n=10) comparators are required for a two-step A/D converter. However, this straightforward approach would require all the components to be at least 10-bit accurate. Furthermore, two-step converters require accurate DAC conversion and a summing circuit.

Based on the different approaches to process the residual signal, the two-step flash A/D converter is categorized into three kinds of architectures: subranging, two step with residual scaling and subranging with partial scaling. These architectures, as well as their performances and limitations, are presented as follows [30].

2.1 Subrangers, Vicin secure

G. .

Figure 2.2 Two-Step A/D Converter System Block Diagram

#### 2.1.2.1 Subranging Architecture

The subranging architecture is shown in Figure 2.3 [30]. The m-bit digital outputs of the first A/D converter stage are converted into an analog signal. The residual signal is then computed by subtracting this analog signal from the input signal. The second set of comparators referred to as the fine comparator resolves the remaining n-m least significant bits by comparing the residual signal and the reference voltages of the second stage. Static and dynamic offset voltage, charge injection error and noise are critical to the fine comparator stage operation, as it must resolve finer input signals. Offset voltage can be minimized using autozeroing techniques (AZ) and floating gate injector trimming (Fowler tunneling) [12][29]. The limitation of this architecture lies with the difficulty of designing fine comparators whose noise floor, charge injection/redistribution, and static errors must be maintained below 1/2 LSB. This limitation can be mitigated by the use of a residual amplifier at the cost of an increase in settling time associated with the linear gain amplifier as in the following two step architecture.

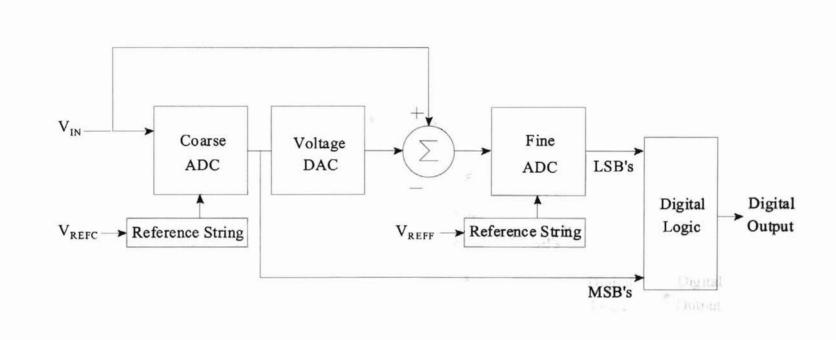

#### 2.1.2.2 Two-Step with Residual Scaling

A two-step residual scaling architecture is shown in Figure 2.4 [30]. The residual signal is obtained by subtracting the reconstructed analog signal from the input signal and amplifying it 2<sup>m</sup> times. The same set of reference strings and comparators can optionally be used in the second stage to resolve the fine bits. This approach eliminates matching requirements between them but increases settling speed and complexity. As the input signal can be quite large for both stages and comparators often need not be autozeroed.

PAR

How you a break settings those associated with the constant scaling amplifier makes it

Reverse international ender

were respect is our man investive.

Figure 2.4 Two-Step with Residual Scaling A/D Converter System Block Diagram

However, a longer settling time associated with the residual scaling amplifier makes it less attractive, since a high conversion speed is our main objective.

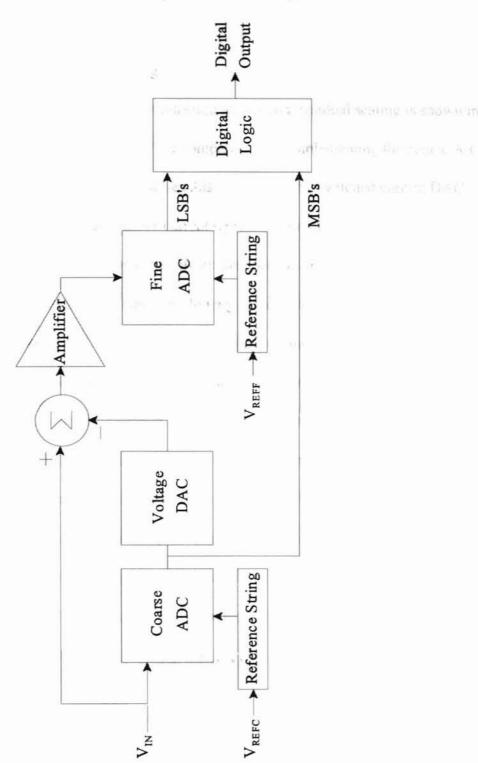

2.1.2.3 Subranging with Partial Scaling

A two-step subranging ADC architecture with partial residual scaling is shown in Figure 2.5 [30]. The first stage uses 2<sup>m</sup> - 1 comparators for implementing the coarse A/D converter to generate the MSB's and passes this result on to the switched current DAC. Note that the DAC generates a negative current representation of the coarse signal. Current mode summing is then applied to obtain the residual signal. This approach potentially reduces the conversion speed by lowing the parasitic capacitance while providing a means to control the time constant by selecting the summing node resistor R<sub>SUM</sub>. This comes with a high price in area and power to maintain accurate high bandwidth voltage to current conversion. Voltage to current converter (VIC) is required to convert the input voltage signal to its current equivalence before summing across  $R_{\text{SUM}}$ in developing the residual voltage signal. This residual signal is scaled as much as m times to ease the accuracy and noise requirements of the fine comparators and then buffered to reduce the parasitic capacitance (or settling time) of the summing node. The use of m scaling means the fine comparators are required to resolve only m times the 0.5mV differences (  $m \frac{V_{FS}}{2^{n+1}}$  ). This method offers a means to overcome the large

amplifier settling time associated with the fully residual scaling by: (1) partial scaling of the residual signal, and (2) buffering to ease the settling time of the summing node due to the distributed parasitic capacitance. As previously noted partial residual scaling also

Figure 2.5 Subranging with Residual Scaling A/D Converter System Block Diagram

makes the fine comparator less vulnerable to noise, static offset, and charge injection errors. The weakness of this approach is the requirement of an accurate high speed V/I converter which takes up a very large area and consumes high power.

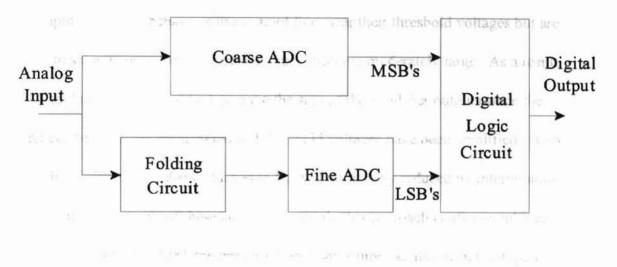

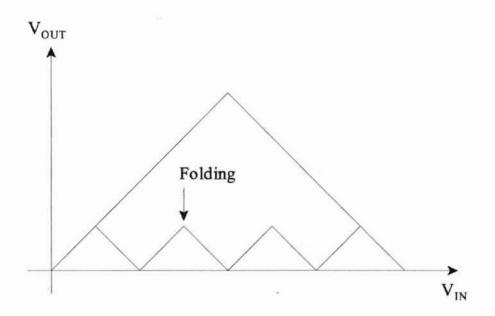

2.1.3 Folding and Interpolation A/D Converter

Folding and interpolation are two different A/D converter architectures. A folding A/D converter is similar in operation to a two-step converter in that a group of LSBs are found separately from a group of MSBs, as shown in Figure 2.6. However, while a twostep converter requires an accurate D/A converter, a folding converter determines the LSB set more directly through the use of nonlinear analog preprocessing and simultaneously determines the MSB set. Also note that no sample-and-hold is required in this system implementation[6][20]. The architecture uses analog preprocessing to transform the input signal into a repetitive (the folding in time) output signal to be applied to the fine converter. In this system the most significant bits are determined by the coarse quantizer, which determines the number of times a signal is folded. The fine bits are determined by the fine quantizer which converts the preprocessed "folded" signal into the fine code. In this way, it is possible to obtain an 10-bit resolution with only 62 comparators (5-bit coarse and 5-bit fine). Furthermore, the sampling of the analog signal at the same clock edge does not require the need for a sample-and-hold amplifier. The low component count results in a small die area and a reduction in power. One drawback, however, is the higher repetition rate of the folded input signals that can result in rounding-off the tips of the folded signal [28]. This rounding-off problem can result in a

reading an at the heigh frequency and a true input spectrum in the conversion

to taken of the convertient of second amplifices, as shown in Figure 2.7.

(a) A typical folding system diagram

(b) Folding circuit: output signal as a function of input signal

Figure 2.6 A Folding ADC Architecture

loss of resolution at the high-frequency end of the input spectrum in the conversion process.

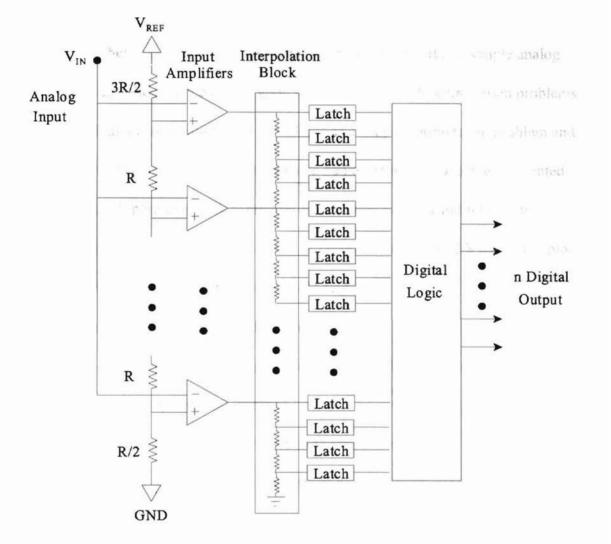

The interpolation converters make use of input amplifiers, as shown in Figure 2.7. These input amplifiers behave as linear amplifiers near their threshold voltages but are allowed to saturate once their differential inputs become moderately large. As a result, noncritical latches only need to determine the sign of the amplifier outputs since the differences between the input signal and threshold voltages have been amplified. Also, the number of input amplifiers attached to  $V_{IN}$  is significantly reduced by interpolation between adjacent outputs of these amplifiers. While this approach is often combined with a folding architecture [6][28], the interpolation architecture has also been used quite successfully by itself [4].

Incorporating the interpolation technique into the folding topology, the folding and interpolation architecture has the advantage of both folding and interpolation. The advantage is that the large number of comparators can be significantly reduced through creating only a small number of folding signals and deriving the remaining folding signals by the resistive interpolation between the outputs of two adjacent signals. A linear interpolation between the two adjacent signals with an accuracy less than 0.5 LSB of the interpolated system is required. In this case, the 32 folding signals necessary for the 5 least significant bits are derived from a four times interpolation between eight output signals of the folding encoder. Thus, this architecture is very suitable for highresolution converters which require a large analog bandwidth.

The folding and interpolation architecture has been successfully used in bipolar process [4][5][6]. Nevertheless, as stated in the Appendix A, the inherent limitation of

these show are addited SFET differential must be structs its potential application to the

and Att to a second

10

Figure 2.7 An Interpolation ADC Architecture

soft non-linearity of MOSFET differential pairs restricts its potential application to the subthreshold MOS processes.

2.1.4 Neural Network A/D Converter

It has been shown [8] how highly interconnected networks of simple analog processors can collectively compute good solutions to difficult optimization problems. Analog-to-digital conversion can be considered as a simple optimization problem and thus several A/D conversion systems based on neural-networks have been presented [8][9][10]. A Hopfield network composed of one-layer neurons and fully connected feedback resistors can be used to realize an A/D converter. Figure 2.8 shows the block diagram of typical Hopfield neural-based A/D converter.

In this Hopfield network, simple decision-making amplifiers and a resistive network are used. Each noninverting amplifier has a sufficient voltage gain to function as a comparator with output digital levels of 1 or -1. The amplifier outputs are fed back to the amplifier inputs with the densely connected resistive network.

Due to the inherently simple architecture and massively parallel processing capability, the neural-based circuits will potentially play an important role in the next-generation A/D converter systems.

The high-speed ADC architectures, fully flash, multi-step, folding and interpolation, and neural network, are summarized as follows.

I

CITCH STREET STATE

Flash ADC

#### an aminate the configurement for high socilizing component

This architecture is very suitable for 4-5 bit resolution application because it has the highest conversion speed among the above listed A/D converters. However, it cannot be used for 8-10 bit resolution application since great number of comparators employed result in a very large area and consume too much power. Furthermore, the difficulties in matching of great number of reference resistors and driving of large input capacitance also restrict its application in high resolution A/D system.

Multi-Step ADC

Currently, the two-step architecture is the most common type for high-speed and high-resolution (8-10 bit) ADC application. An accurate D/A converter and summing circuit are needed in this architecture. Moreover, it requires high-speed and high-resolution sample/hold circuit. The subranging with partial scaling type requires high accurate V/I converter additionally.

Folding and Interpolation ADC

It has been successfully used for A/D converter in bipolar process. The number of comparators needed in this architecture is much less than full flash type and no sample/hold circuit is needed. Both the area and power are much smaller than that of flash ADC. Nevertheless, this architecture has its limitation in MOS process due to the soft non-linearity of MOSFET (see Appendix A).

Neural Network ADC

This architecture is potentially an important implementation for high-speed ADC since its simplicity in circuit and fast conversion process. In theory, neural network ADC

offer an on-board trim to eliminate the requirement for high accuracy component y AV, matching. The worse case delay in LSB restricts its application for 8-10 bit resolution ADC. In Chapter 4, a new two-step neural-based ADC will be proposed to achieve highspeed and high-resolution performances, which incorporates neural-based ADC into a two-step ADC.

#### 2.2 Factors limiting accuracy

Among the sources of A/D converter errors, the static offset voltage, dynamic offset voltage, and thermal noise are three major sources affecting the system accuracy. This section presents and discusses these major sources of error as well as the critical design issues and parameters. The DAC error sources as well as reference errors will then be discussed in this section.

The second s

## 2.2.1 Static Offset Voltage

Input amplifiers, output amplifiers, and comparators in practical circuits inherently have a built-in offset voltage. This offset voltage is caused by the finite matching of components primarily and is referred to as the static offset voltage, which is given by [11]

$$\mathbf{V}_{\rm os} = \left[\pm \Delta \mathbf{V}_{\rm T} \pm \frac{1}{2} \cdot \left(\frac{\Delta\beta}{\beta}\right) \cdot \Delta \mathbf{V} \pm \frac{1}{2} \cdot \frac{\Delta\beta}{\beta} \cdot \Delta \mathbf{V}_{\rm T}\right] \cdot \sqrt{\mathbf{N}_{\rm P}}$$

(2.1)

States & Children R.

where  $V_T$  and  $\beta$  represent the threshold voltage and transconductance respectively,  $\Delta V_T$ and  $\Delta\beta$  are the variations in the threshold voltage and transconductance respectively, and  $N_p$  is the number of transistor pairs, i.e., differential pairs and current mirrors.

The static offset voltage is very important for system DC performances. Note that Fowler trimming or an autozero procedure [12] can be used to remove the static offset in a system. Furthermore, care must be taken during the layout of the circuit. The static offset voltage can be minimized by using common centroid geometry and multiple transistor fingers layout scheme in conjunction with inter-digitation.

### 2.2.2 Dynamic Offset Voltage

The charge injection mismatch resulting from channel inversion and clock feedthrough creates an offset voltage referred to as dynamic offset voltage. The charge injection mismatch due to channel inversion is caused by the redistribution of charge. When a switch is closed, the switching transistor is made conductive by mobile carriers that are attracted into the channel by the gate voltage. For charge equilibrium, the total charge of the mobile carriers in the channel must be equal to the total charge stored in the gate. The redistributed charge on the gate in strong inversion is given by:

$$Q = C_{gs} \left( V_{gs} - V_{T} \right) \tag{2.2}$$

The redistribution of this charge is a function of terminal impedance on both ends of the switch. Therefore, any mismatching in switch transistor dimensions, input or output

impedance, parasitic capacitance and threshold voltages can result in what is referred to as dynamic offset voltage.

F

The clock feedthrough error is caused by the mismatch charge absorption when autozeroing technique is used in comparators. This error voltage is given by:

$$V_{os} = \frac{\Delta Q}{C_{AZ}} \cdot \frac{(g_{mc} + g_{ml})}{g_{mi}}$$

(2.3)

where  $\Delta Q$  is the channel charge mismatch of switches,  $C_{AZ}$  is the input sampling or autozero storage capacitor, and  $g_{mc}$ ,  $g_{ml}$ ,  $g_{mi}$  are the transconductance value of the comparator, load, and input circuit, respectively (see Figure 2.9).

The dynamic offset voltage must be kept below 1/2 LSB of the A/D system by proper design and layout. Several guidelines can be used to minimize the dynamic offset voltage [11]. First, the large load capacitance will significantly reduce the clock feedthrough but at the expense of slowing down the setting time and reducing the bandwidth. Second, the large  $V_{GS}$  will minimize the threshold voltage mismatch but at the expense of increased power consumption due to decreased headroom. Third, small clock voltage swing to the point where the switch just turns on and off reduces the clock voltage coupling effect. Fourth, a good common mode rejection ratio of fully differential pairs with good matching reduces the clock feedthrough voltage since clock signal appears, to the first order, as a common mode signal.

: switch parasitic capacitance

Figure 2.9 Comparator with Autozeroing Technique

and a rescaled in this section, only the static offset voltage of

Noise of current sources, amplifiers, resistors, and so on, add to the A/D system errors. Among the noise sources in CMOS devices, the thermal noise is the most significant one since the MOS transistors exhibit small flicker noise and shot noise [11]. The thermal noise in an MOS transistor is generated from the channel resistance, and its magnitude is inversely proportional to the device transconductance. The thermal noise exhibits itself as a deviation from the theoretical maximum signal to noise ratio that an ideal converter can have. Therefore, it must be kept below 1/2 LSB. The mean-square noise values of the thermal noise sources in an MOS transistor is

Noise Power =

$$\frac{8kT\Delta f}{3g_m}$$

(2.4)

where k is the Boltzmann's constant, T is the absolute temperature, and  $\Delta f$  is the noise bandwidth. Taking both bandwidth and signal to noise ratio requirements into consideration, the constrains on  $g_m$  and  $C_L$  can be determined based on the following equations:

$$g_m > (\frac{8kT\Delta f}{3}) \cdot \frac{(2^{n+1})^2}{V_{FS}^2}$$

(2.5)

and

$$C_{L} > \left(\frac{16kT}{3\pi}\right) \cdot \frac{(2^{n+1})^{2}}{V_{FS}^{2}}$$

(2.6)

where  $V_{FS}$  is the full scale voltage of the A/D system.

Among the error sources presented in this section, only the static offset voltage of the comparator can be cancelled using autozero techniques or Fowler trimming. Since the dynamic offset voltage and thermal noise can not be canceled, they must be kept below an LSB of the A/D system by proper design, layout and trimming. Dynamic offset voltage can be minimized by using the fully differential circuit and large load capacitor while the thermal noise can be mitigated by large capacitor. However, a large capacitor will result in the large size and large power consumption as well as and increased settling time for the system.

## 2.2.4 DAC Errors

DAC is a critical component in two-step ADC architecture and its errors will greatly affect the ADC system performances. In the actual DAC circuit, the mismatch in reference resistors, reference capacitors, and reference current, introduces the static offset. Furthermore, the clock feedthrough of the analog switch causes the dynamic offset voltage. The thermal noise in reference resistors and reference current sources also contributes its error to the DAC and must be kept 1 to 1.5 LSB below the signal.

A special dynamic element matching (DEM) technique can be used in DAC to increase signal-to-noise ratio and this technique will be discussed in Chapter 4.

## 2.3 Comparators Amplification Techniques

This section reviews the comparator amplification techniques and their applications in the coarse and fine comparators. Functionally, the comparator needs to ensure that digital output levels can be generated based on small differences of two input signal levels. Therefore, amplification is the basic function of comparator. Since the comparator amplification need not be linear, it can be implemented by using nonlinear gain stages.

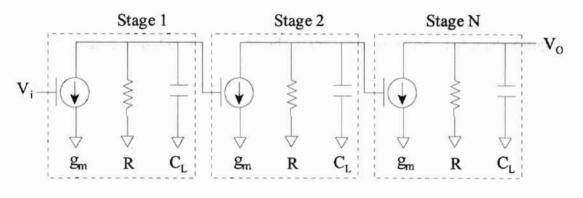

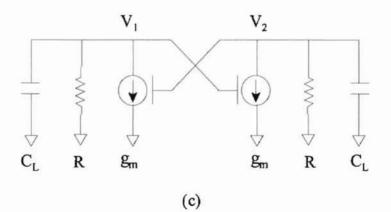

The comparator amplification techniques can be categorized into three generic approaches. A single-pole amplifier (SPA) is the simplest form of comparator. A multistage amplifier (MA), comprised of a cascade of N identical SPA's, provides higher gain than SPA. A regenerative amplifier (RA), implemented using positive feedback, has the best speed performance among these approaches[13]. Figure 2.10 shows the small signal equivalent circuit for each of these amplification techniques.

2.3.1 Single pole amplifier (SPA)

Assumed that a step waveform is applied at the input of comparator. The equivalent amplification factor A for this circuit is defined as the ratio of the output  $V_0$  to the input step amplitude  $V_i$  (see Figure 2.10(a)) after an amplification time  $T_a$ . If the MOSFET output impedance are quite large, the relationships between  $T_a$  and A for the SPA is simply

(b)

(a) Single pole amplifier (SPA)

(b) Multistage amplifier (MA)

(c) Regenerative amplifier (RA)

32

(2.7)

$$T_a = \frac{C_L}{g_m} \cdot A$$

(2.7)

where  $g_m$  is the transconductance of the amplifier stage,  $C_L$  is the load capacitance at the output node, and A is the small signal DC gain which equals  $g_m R_0$ .

2.3.2 Multistage amplifier (MA)

Multistage amplifier is just a cascade of the identical SPAs. The relationship between  $T_a$  and A for MA is given by[13]:

$$T_a = \frac{C_L}{g_m} \cdot (A \cdot N!)^{\frac{1}{N}}$$

(2.8)

where N is the number of the amplifier stages. For the MA, there exists an optimum number of stages  $N_{op}$ , for which  $T_a$  is minimized. The relationship between  $N_{op}$  and A is approximated by [13]

$$N_{on} \approx 1.1 \cdot \ln(A) + 0.79$$

(2.9)

for A < 1000.

## 2.3.3 Regenerative amplifier (RA)

As stated previously, a positive feedback amplifier can also be used as a comparator. The equivalent amplification factor A of such a amplifier is defined as the ratio of the differential output,  $V_1(t)-V_2(t)$ , to the initial differences,  $V_1(0)-V_2(0)$ , after a

regeneration time period of  $T_a$ . Again assume the MOSFET output impedance is very large, the amplification time  $T_a$  is then related to A by

1

$$T_a = \frac{C_L}{g_m} \cdot \ln(A)$$

(2.10)

For the SPA and MA configurations, the amplification gain is limited by the low frequency gain of the individual SPA stages. However for RA, the gain A is limited only by the noise floor and the power supply voltage. From the above equations (2.7),(2.8), and (2.10), it can be seen that the amplification time  $T_a$  in a comparator is best obtained by means of regeneration technique. However, for a practical implementation this may be difficult to accomplish as in case of MOS comparators due to the relatively large offsets within the sense amplifier. Therefore, the regenerative amplifier is generally preceded by a preamplifier [14]. The preamplifier also eliminates the "kick back" voltage which introduce error source into reference resistor chain.

The previous discussions in this section described three comparator amplification techniques. In two-step A/D architectures, the SPA and MA are generally used in the first level of the ADC to conserve power, whereas the RA is used in the second stage where it has to resolve small voltages in the range of 0.5mV to 2mV. In general, the RA is used in high-speed ADCs to achieve the fastest speed performance.

the re-conversion of the

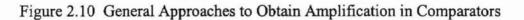

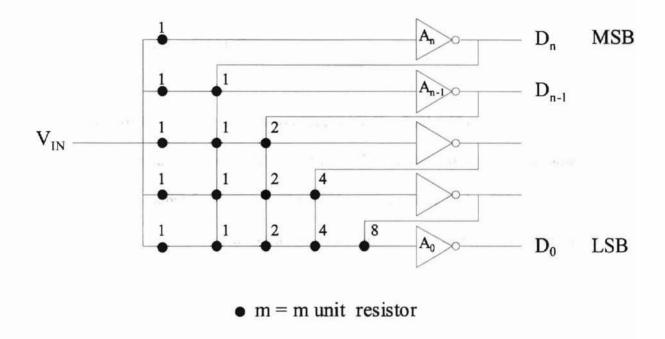

## 2.4 Digital-to-Analog Converter (DAC)

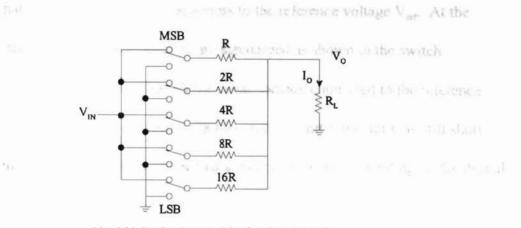

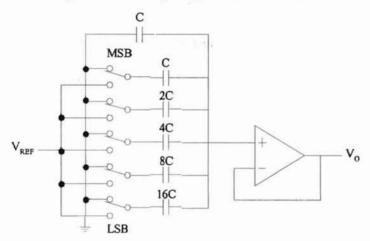

All two step A/D architectures require the intermediate re-conversion of the MSBs to an analog equivalent by a DAC. The typical digital-to-analog converter consists of three major elements: (1) some type of resistor or capacitor network, (2) a means of switching either a reference voltage or current to the proper input terminals of the network as a function of the digital value of each digital input bit, and (3) a reference voltage or current. For high-speed applications in a two-step A/D converter system, the most commonly used DACs can be categorized into three types: resistor network DAC, capacitor network or charge redistributed DAC, and current reference source DAC. Figure 2.11 shows these three kinds of DAC.

Resistor Network DAC

Figure 2.11(a) shows a 5-bit DAC using a weighted-resistor network. The size of each resistor is inversely proportional to the weighted value of the particular digital bit that it converts.

Since delay of the DAC is proportional to the resistance of R, the R must be small enough to decrease the RC time constant. Nevertheless, it is difficult to obtain matching resistors for 10 bit accuracy [31] at low resistance value in a CMOS process. This disadvantage limits its application in high speed A/D systems.

Capacitor Network DAC

In Figure 2.11(b) an example of a binary weighted capacitor D/A converter system is shown. The system consists of n binary weighted capacitors, an additional

The strength of a first of the processional amplitude used as a follower, and a set

(a) a 5-bit DAC using a weighted-resistor network

(b) a 5-bit DAC using a weighted-capacitor network

(c) a 5-bit DAC using reference current sources network

Figure 2.11 Three Kinds of Most Commonly Used DAC

capacitor with the unit capacitance, an operational amplifier used as a follower, and a set of switches that connect the weighted capacitors to the reference voltage  $V_{ref}$ . At the beginning of the conversion all capacitors are discharged as shown in the switch configuration of Figure 2.11(b). Then all the capacitors are connected to the reference voltage to perform a precharge condition. In this case the unit capacitor C is still shortcircuited to ground. When the conversion starts, every capacitor, depending on the digital input information, is connected to ground or remains in the reference position. During the conversion, the charge is redistributed over the capacitors and a binary-weighted D/A conversion is obtained for the generated output voltage. The accuracy of this type DAC can be 10-bit [31]. The limitation of this DAC is that it requires the precharge process, which slows down the conversion speed.

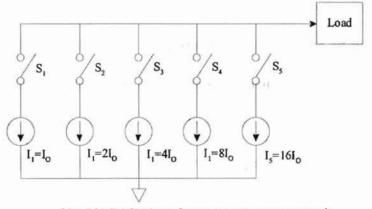

## • Current Reference Source DAC

Sometimes it is necessary to obtain a current DAC with high accuracy in an A/D converter system. Figure 2.11(c) shows a example of binary-weighted current reference source DAC. The digital input code is applied at the control end of switch. Each reference current source  $I_i$  is switched to the output node  $I_{out}$  by the bit switches  $S_1 \sim S_5$ . Since current reference source can be implemented by using high accuracy current mirror (OTA type), its accuracy can be 10-bit [31]. Therefore, this kind of DAC can be employed in the high-speed and high-resolution A/D system, as stated later.

Among the three different kinds of DAC described previously in this section, the resistor network DAC has the simplest form but it suffers from resistor matching

difficulty when applied in high resolution application in a CMOS process. The capacitor network DAC needs an accurate and high-speed OTA to achieve high resolution and speed performances. The current reference source DAC is the best choice in this proposal due to its achievable high accuracy as well as high speed performances although it has larger area than the previous two DACs. This kind of DAC, along with current mirror with OTA technique, will be discussed in Chapter 4.

The dynamic element matching (DEM) DAC is very suitable for high accuracy application [25][26]. By reducing the correlation among successive error sources, DEM DAC can achieve high signal-to-noise ratio performance up to 12 bit [25]. The DEM DAC will be discussed in Chapter 4.

THE CARDON REPORT OF A REAL ASSAULTERS OF

encodes in a set of the set of th

the the value of the detected

# **4-BIT FLASH A/D CONVERTER**

## IMPLEMENTATION AND TESTING RESULTS

as some buffys fine

The parallel A/D architecture, commonly referred to as flash A/D conversion, provides the fastest possible approach to quantizing an analog signal. All of the possible quantization levels are simultaneously compared to the analog input signal. Figure 2.1 represents the architecture of a generic flash A/D converter.

In order for an analog signal to be quantized, its voltage level must be within the end points of the reference voltage divider. Comparators for which the analog input level is greater than the respective reference levels will output digital logic '1'. Likewise, the comparators that have reference levels that are greater than the analog input will output logic '0' as a result of the comparison process. The appearance of the  $2^{N}$ -1 bit digital word that results from the simultaneous comparisons gives rise to the thermometer analogy. A continuous string of 1's should appear up to the quantization level that is nearest to the input level. Beyond this point, a continuous string of zeros results. The height of the string of 1's can be read, as the mercury in a thermometer, to yield the quantized measurement of the analog input. In actual implementation, digital logic, referred to as bubble detector or thermometer decoder, is used to evaluate the results of adjacent comparators in order to find the '1'/'0' boundary condition. The bubble detector

will produce only one output that is true, thus providing a unique digital code to the  $2^{N}$ :N encoder in the last stage. The active signal acts as an address line to the encoder which enables the output of a single N-bit word equivalent to the value of the detected quantization level.

In this chapter, the first section will present the schematics of five functionality blocks, i.e., comparator, bubble detector, encoder, input buffer, and output buffer. The SPICE simulations are also presented. The testing results will be included in section two. The characteristic curves of P transistor and N transistor reveals the performances of IBM 0.1µm process. The DC screen and AC response testing results of five functional blocks on the wafers are displayed later. Finally, the future design considerations are shown in section three based on the practical testing results.

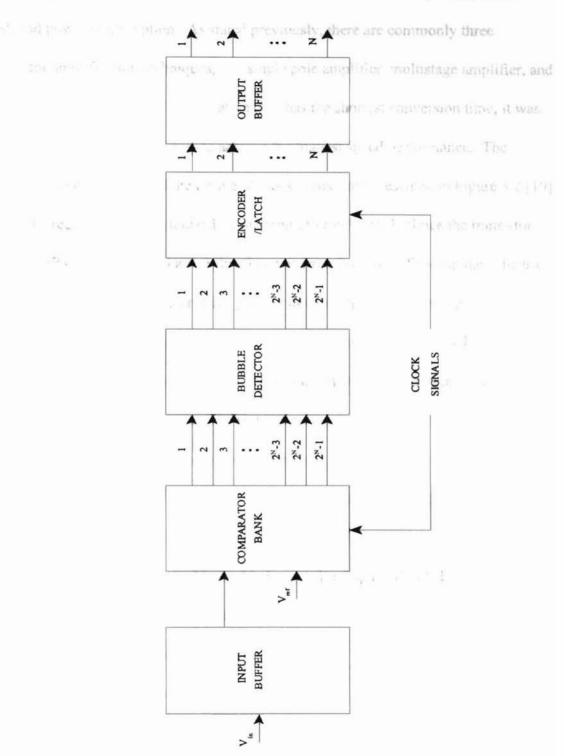

## 3.1 4-Bit Flash ADC System Building Blocks

The block diagram of practical 4-bit flash A/D converter in this study is shown in Figure 3.1. An input buffer is employed to drive the large input capacitance of 15 comparators while an output pad driver is used for the 4-bit system to drive the output pads.

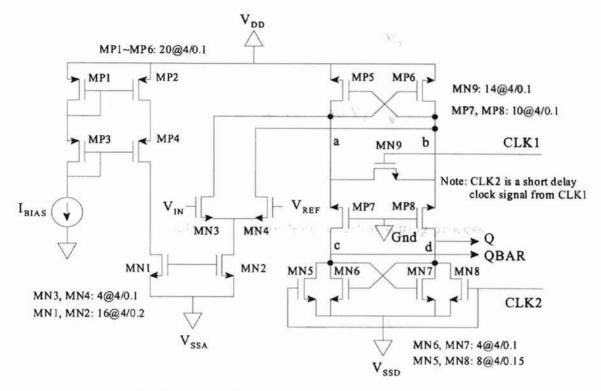

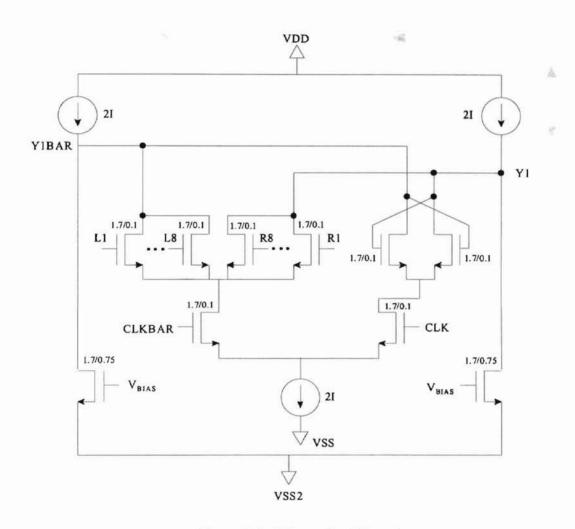

## 3.1.1 Comparator

The function of the comparator is a crucial, and often a limiting component in the

ingle-spectral is the energy systems due to its finite accuracy, comparison

Figure 3.1 4-Bit Flash A/D Converter System Block Diagram

design of high-speed A/D conversion systems due to its finite accuracy, comparison speed, and power consumption. As stated previously, there are commonly three comparator amplification techniques, i.e., single pole amplifier, multistage amplifier, and regenerative amplifier. Since regenerative type has the shortest conversion time, it was employed in this 4-bit A/D system to achieve the highest speed performance. The schematics of comparator and the timing of clock signals are presented in Figure 3.2 [19].

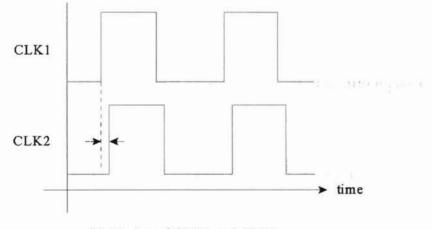

The regeneration is initialized by opening of switch MN9. Since the transistor MP7 and MP8 isolate the N-channel flip-flop pair from P-channel flip-flop pair, the use of two clocks performs the regenerative process in two steps. The first step of regeneration is within the short time slot between CLK1 getting high and CLK2 getting high. The P-channel flip-flop regenerates the voltage differences between nodes a and b. The second regeneration step starts when CLK2 getting high. The voltage differences between node c and d is quickly amplified to a voltage swing equal to the logic levels.

The first regeneration step is very important, not only in raising the regeneration speed but in reducing the total input offset voltage. The differential errors caused by the mismatches in MP7 and MP8, and in the N-channel flip-flop are divided by the amplification gain in the first regeneration step, when referred to the input as an equivalent offset voltage. Therefore, their contribution to the total equivalent input offset voltage can be neglected for sufficiently high gain.

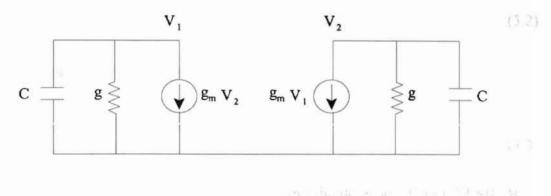

The comparison mechanism has to be closely explored in order to optimize speed and accuracy. For each step regeneration, the small signal equivalent circuits of the setting and resetting processes are shown in Figure 3.3. For the setting process, the following two differential equations are derived as follows:

1

(a) Schematic of regenerative comparator

(b) Timing of CLK1 and CLK2

Figure 3.2 (a) Schematics of Regenerative Comparator

(b) Timing of Clock Signals CLK1 and CLK2

(a) Small signal equivalent circuit of setting process

(b) Small signal equivalent circuit of resetting process

Figure 3.3 Small Signal Equivalent Circuit of Setting and Resetting Process

for Each Step Regeneration

(a) Setting process (b) Resetting process

443

(3.1)

$$g_{m}v_{2} + gv_{1} + C\frac{dv_{1}}{dt} = 0$$

(3.1)

$$g_{m}v_{1} + gv_{2} + C\frac{dv_{2}}{dt} = 0$$

(3.2)

Solving (3.1) together with (3.2) gives

$$\frac{g_m - g}{c} \cdot t$$

$$v_1 - v_2 = v_{IC} \cdot e \quad C \quad (3.3)$$

where  $V_{IC}$  is initial voltage difference of  $V_1$  and  $V_2$ , and should be less than 1/2 LSB. By assuming  $g_m >> g$ , this equation can be simplified as follows.

$$\frac{g_{m}}{v_{1} - v_{2}} = v_{1C} \cdot e^{\frac{C}{C}}$$

(3.4)

This equation is applicable for both first step and second step regeneration. Thus, for the first step regeneration, we have

$$\mathbf{v}_{01} = \mathbf{v}_{1C1} \cdot \mathbf{e}^{\frac{\mathbf{g}_{mps}}{C}} \cdot \mathbf{t} \approx \mathbf{v}_{1C1} \cdot \mathbf{e}^{\frac{\mathbf{t}}{\tau_{p}}}$$

(3.5)

where  $V_{01}$  is the first step regeneration output voltage,  $\tau_p$  is the time constant of first step regeneration (P transistor pair). For the second step regeneration, its initial voltage is the voltage  $V_{01}$  of the first step regeneration. Thus, we have

$$\mathbf{v}_{02} = \mathbf{v}_{01} \cdot \mathbf{e}^{\frac{\mathbf{g}_{mn6}}{\mathbf{C}}} \cdot \mathbf{t} \approx \mathbf{v}_{1C1} \cdot \mathbf{e}^{\frac{\tau}{\tau_{p}}} \cdot \mathbf{e}^{\frac{\tau}{\tau_{n}}} = \mathbf{v}_{1C1} \cdot \mathbf{e}^{\frac{\tau}{\tau_{p}}} + \frac{\mathbf{t}}{\tau_{n}}$$

(3.6)

where  $\tau_n$  is the time constant of second step regeneration (N transistor pair).  $V_{02}$  is the output voltage of second step regeneration and also is the output voltage of this comparator circuit. When  $t = t_{set}$ ,  $V_{02}$  equals to  $V_{OH}$ , which is the logic high level voltage.

Then, t<sub>set</sub> can be derived as follows.

$$t_{set} = \frac{1}{\frac{1}{\tau_{p}} + \frac{1}{\tau_{n}}} \cdot \ln \frac{V_{OH}}{V_{IC1}}$$

(3.7)

Based on the P and N transistor characteristics testing data, we can assume that  $\tau_p = 1.5$  $\tau_n$ . Then, equation (3.7) can be simplified as follows.

$$t_{set} = \frac{3}{5} \cdot \tau_n \cdot \ln \frac{V_{OH}}{V_{ICI}}$$

(3.8)

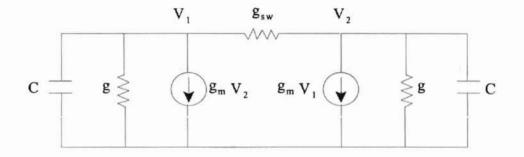

For the resetting process, we can derive the following two differential equations.

$$g_{m}v_{2} + gv_{1} + C\frac{dv_{1}}{dt} + (v_{1} - v_{2}) \cdot g_{sw} = 0$$

(3.9)

$$g_{m}v_{1} + gv_{2} + C\frac{dv_{2}}{dt} + (v_{2} - v_{1}) \cdot g_{sw} = 0$$

(3.10)

Solving these two equations gives

$$\frac{\mathbf{g}_{m} - \mathbf{g} - 2 \cdot \mathbf{g}_{sw}}{C} \cdot \mathbf{t}$$

$$\mathbf{v}_{1} - \mathbf{v}_{2} = \mathbf{v}_{OH} \cdot \mathbf{e} \qquad C \qquad (3.11)$$

where  $V_{OH}$  is the initial voltage difference of  $V_1$  and  $V_2$  for resetting process. When t =  $t_{reset}$ ,  $V_1 - V_2$  should be reset to less than  $V_{IC1}$ . By assuming  $g_m >> g$ ,  $t_{reset}$  can be derived as follows:

$$t_{\text{reset}} = \frac{C}{g_{\text{m}} - 2 \cdot g_{\text{sw}}} \cdot \ln \frac{V_{\text{IC}}}{V_{\text{OH}}} = \frac{C}{2 \cdot g_{\text{sw}} - g_{\text{m}}} \cdot \ln \frac{V_{\text{OH}}}{V_{\text{IC}}}$$

(3.12)

Then the total delay of this comparator is determined by adding  $t_{set}$  and  $t_{reset}$ ,

$$\mathbf{t}_{d} = \mathbf{t}_{set} + \mathbf{t}_{reset} = \frac{3}{5} \cdot \frac{C}{g_{mn6}} \cdot \ln \frac{\mathbf{v}_{OH}}{\mathbf{v}_{IC1}} + \frac{C}{2 \cdot g_{sw} - g_{mn6}} \cdot \ln \frac{\mathbf{v}_{OH}}{\mathbf{v}_{IC1}}$$

$$=\frac{2}{5}\frac{C}{g_{mn6}} \cdot \ln \frac{v_{OH}}{v_{IC1}} \cdot \frac{3 \cdot \frac{g_{sw}}{g_{mn6}} + 1}{2 \cdot \frac{g_{sw}}{g_{mn6}} - 1}$$

(3.13)

where C and  $g_{\text{mn6}}$  are shown below,

$$C = W_{n6} \cdot L \cdot C_{OX} + \frac{W_{sw} \cdot L \cdot C_{OX}}{2}$$

(3.14)

$$g_{m} = \frac{W_{n6} \cdot \Delta V \cdot \mu_{sat} \cdot C_{OX}}{L}$$

(3.15)

Define k and  $k_w$  as follows,

$$k = \frac{\mu_{sal}}{\mu_{sw}}$$

(3.16)

$$k_{w} = \frac{g_{sw}}{g_{mn6}} = \frac{W_{sw}}{W_{n6}} \cdot \frac{\mu_{sw}}{\mu_{sat}} = \frac{W_{sw}}{W_{n6}} \cdot \frac{1}{k}$$

(3.17)

Solving equations (3.13), (3.14), (3.15), (3.16) and (3.17) gives

$$t_{d} = \frac{2}{5} \cdot \frac{L^{2}}{\mu_{sal} \cdot \Delta V} \cdot \ln \frac{V_{OH}}{V_{IC}} \cdot (1 + \frac{k_{w} \cdot k}{2}) \cdot \frac{3 \cdot k_{w} + 1}{2 \cdot k_{w} - 1}$$

$$= \frac{2}{5} \cdot \frac{L^{2}}{\mu_{sal} \cdot \Delta V} \cdot \ln \frac{V_{OH}}{V_{IC}} \cdot \frac{(2 + k_{w} \cdot k)(3 \cdot k_{w} + 1)}{2(2 \cdot k_{w} - 1)} \cdot$$

(3.18)

The optimized comparator delay is approached by

$$\frac{dt_{d}}{dk_{w}} = 0$$

Thus, the equation for k<sub>w</sub> is derived as follows.

$$6 \cdot k_{w}^{2} \cdot k - 6 \cdot k_{w} \cdot k - k - 10 = 0$$

(3.19)

If

$$k = \frac{\mu_{sat}}{\mu_{sw}} = 0.7 \tag{3.20}$$

From equations (3.19) and (3.20), we have  $k_w = 2.17$  and

$$\frac{W_{sw}}{W_{n6}} = k_w \cdot k = 1.52$$

(3.21)

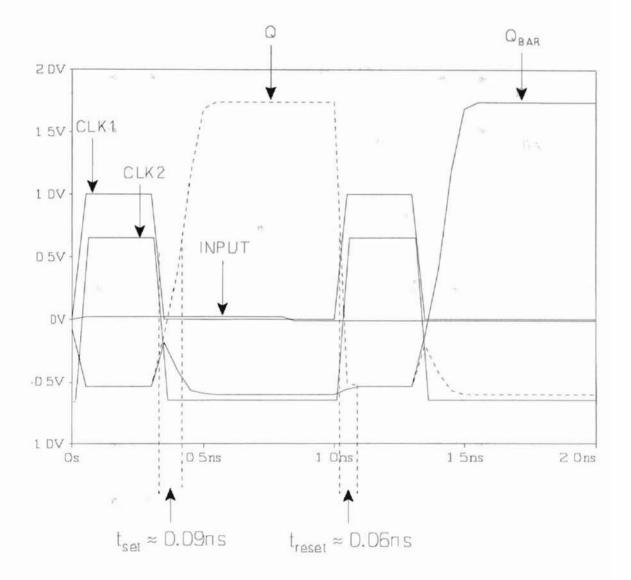

The simulation results of this comparator is shown in Figure 3.4.

## 3.1.2 Bubble Detector

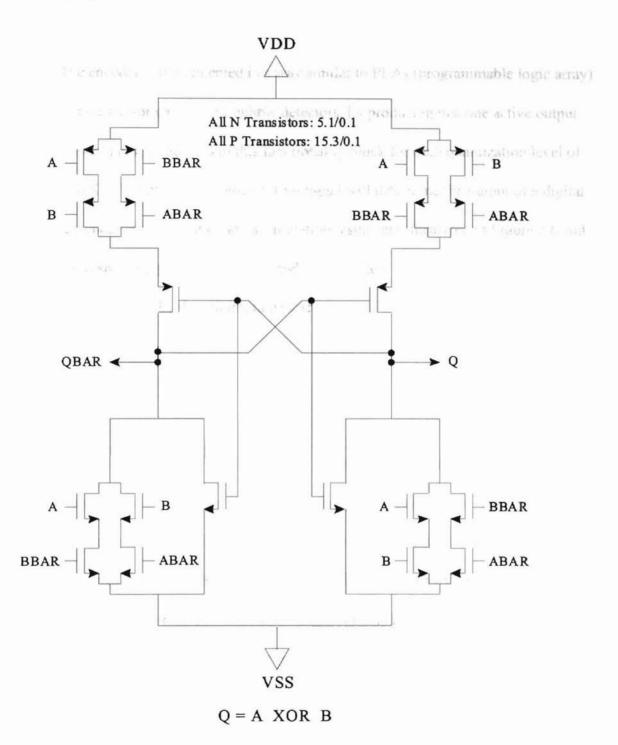

The digital output of the comparators should represent a thermometer code, as described previously. The boundary between the '1's and '0's must be detected in order to establish the segment of the quantization range in which the input lies. Figure 3.5 illustrates the schematics of the bubble detector. Exclusive-or gate is used here to detect the '1'/'0' boundary condition. The bubble detector geometry is three times large than the encoder to achieve the best speed performance.

Figure 3.4 Simulation Result of Regenerative Comparator

3 Tal. Mer

-

Figure 3.5 Schematic of Bubble Detector

The encoder is implemented in a way similar to PLAs (programmable logic array) [7]. The exclusive-or gates in the bubble detectors, by producing just one active output signal, deliver a unique address to this functionality block for each quantization level of the flash ADC. Therefore, the unique active signal will determine the output of a digital word. The encoder schematics and its simulation results are illustrated in Figure 3.6 and Figure 3.7, respectively. To achieve the highest speed and bandwidth performance, the encoder is designed to be the minimum geometry.

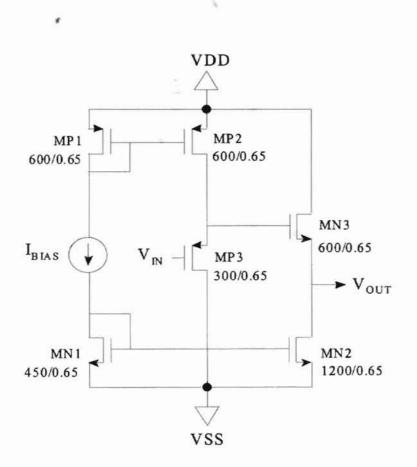

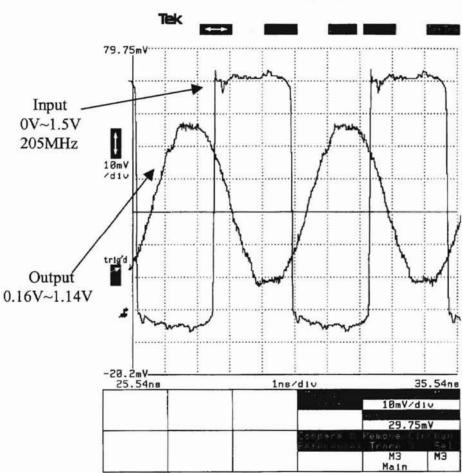

## 3.1.4 Input Buffer and Output Buffer

At the output of the 4-bit ADC system, the minimum size transistors of encoder is not able to drive the output load, which usually has a large capacitance. The inverter chain, which also function as a buffer, is used in the 4-bit ADC system as a pad driver. At the other extreme, the width of bubble detector is scaled up by four times to keep the effect load of encoder small and maintain a maximum bandwidth. For the same reason, the comparator is scaled up by four time again with the added benefit of reducing the noise floor. Thus, in this 4-bit flash ADC system, input of the 15 comparators produce a very large capacitance, which could reduce the input bandwidth. To avoid bandwidth reduction, an input buffer must be employed to drive this large load. In this design solution, a source follower is used in the 4-bit ADC system. Figure 3.8 and Figure 3.9 display the schematics of input buffer and output buffer.

1

dia.

Figure 3.6 Schematic of Encoder

T

Figure 3.7 Simulation Result of Encoder

Figure 3.8 Schematic of Input Buffer

#### 1.1 Contrary Breath

11

at the solution texture selected based on a thorough examination of

Figure 3.9 Schematic of Output Buffer

## **3.2 Testing Results**

After a flash A/D system has been selected based on a thorough examination of specifications and the support circuitry has been designed and fabricated, the next step is to perform tests to verify the performance goals. This step can be the most difficult of all, and there are many approaches to take, depending on the particular testing objectives. This section first shows the testing outcomes of P and N transistors. The characteristics of P and N transistor will reveal the performance of IBM's 0.1µm TFSOI process. In the second part, DC screenings, transient and AC testing responses of the input buffer, output buffer, comparator, bubble detector, and encoder are illustrated respectively. The gate delay, rise/fall time and bandwidth are tested. The transmission line effect and load capacitance effect on testing are also included in this section.

#### 3.2.1 P and N Transistors Testing Results

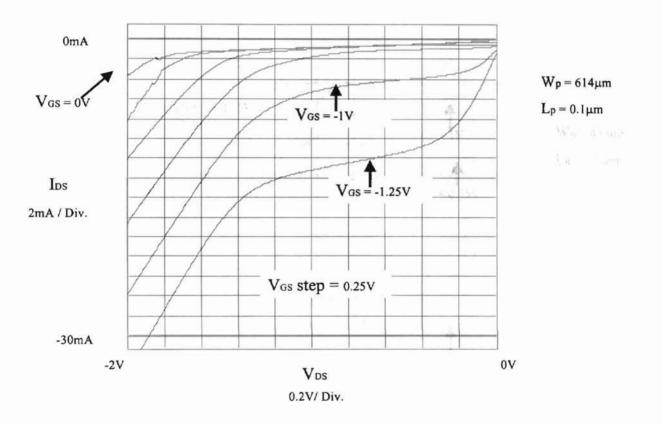

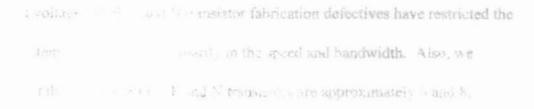

The transistor characteristics show the performances of process and allow one to determine the performances of each functionality block and 4-bit ADC system. Typical P and N transistor characteristics are shown in Figure 3.10 and Figure 3.11, respectively.

The testing results reveal that P transistor suffered from avalanche when  $V_{DS}$  goes beyond 1.1V. Thus, it limited the maximum power voltage which can safely be applied in the circuit. It also can be seen from the testing data that N transistor has a recognizable large leakage current when  $V_{GS}$  equals to 0. This means that the N transistor has a very

Figure 3.10 P Transistor Characteristics

E.

Figure 3.11 N Transistor Characteristics

low threshold voltage. Both P and N transistor fabrication defectives have restricted the anticipated system performances, primarily in the speed and bandwidth. Also, we determined that the self gain of the P and N transistors are approximately 6 and 8, respectively.

## 3.2.2 Functional Blocks Testing Results

This section displays the DC, AC and transient testing results of all the five functional blocks implemented in 4-bit A/D system, i.e., output buffer, input buffer, bubble detector, comparator and encoder.

For the DC function verification, the test setup uses an HP 4155A to sweep one of the input signals and test the output voltage level to confirm the logic, gain, offset, etc. For the pulse transient response testing, the high frequency pulse signal is applied to the input via a Model 10 high speed probe. The output is tested using a Model 34A or Model 10 probe. For AC response testing, the test setup is similar to that of the transient except for that the input signal applied is sinusoid rather than pulse. The following observations were made.

## • Output buffer

First of all, the DC sweep testing results of the output buffer is illustrated in Figure 3.12. The DC transfer function of this output buffer showed that it can produce a logic function while it has two problems, a bad transfer curve in transition region and limited output voltage at a logic high. The first problem is due to the avalanche voltage

(in not say entrient of N transistor, A second space 3, 13. The testing sub-conduct second beent, for

F

Figure 3.12 Output Buffer DC Sweep Response

of the P transistor and the second one comes from the leakage current of N transistor.

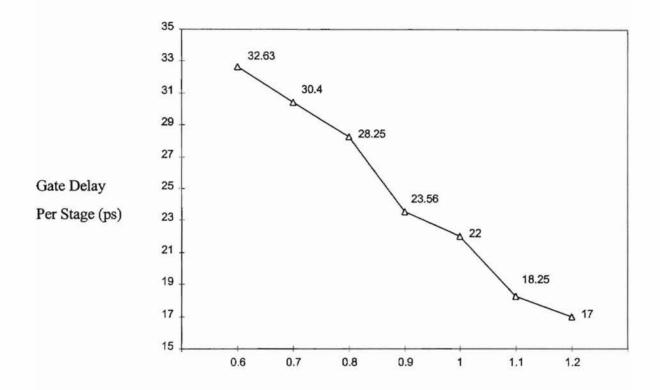

The pulse transient response of output buffer is shown in Figure 3.13. The testing data show that the delay for the first four stages of output buffer is 300ps and 260ps, for the rise and fall edge respectively. Therefore, the average delay per stage is given as

$$t_{d} = \frac{300ps + 244ps}{2 \cdot 4} = 68ps \tag{3.22}$$

Since the inverter chain is scale up by four, the effective gate delay is

$$t_d = \frac{68ps}{4} = 17ps$$

This is commonly referred to as gate delay per stage. This result is closed to the IBM testing data, which is 22ps [18].

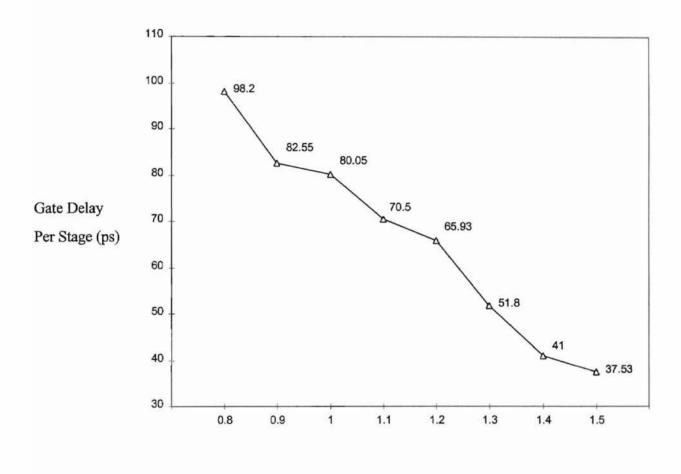

The relationships between gate delay and power supply for output buffer are tested and illustrated in Figure 3.14.

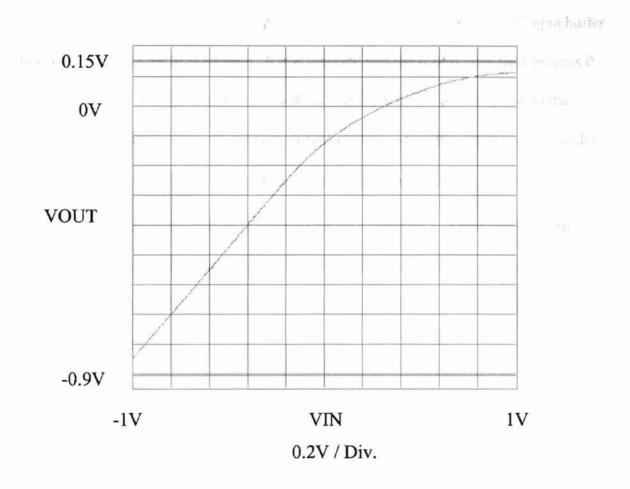

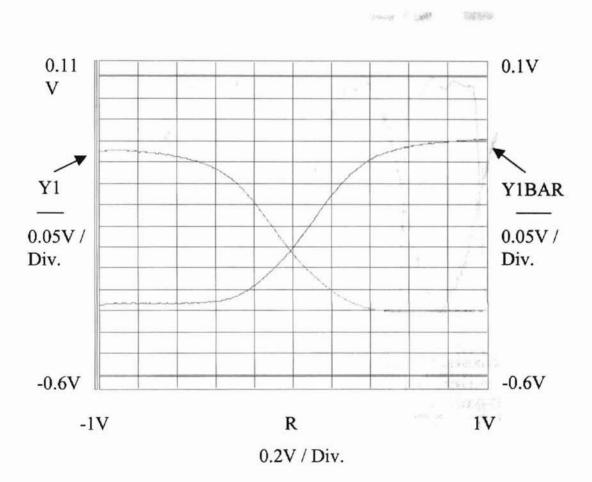

## • Input buffer

A typical DC screening of the input buffer is presented in Figure 3.15. The DC gain is limited to be 0.4 to 0.75. This performance can be verified by the analysis in the following. The DC gain of a source follower is given by:

$$A = \frac{g_{m}}{g_{m} + g} = \frac{1}{1 + \frac{g_{p} + g_{n}}{g_{m}}} \approx \frac{1}{1 + \frac{2 \cdot g_{ds}}{g_{m}}} = \frac{1}{1 + \frac{2}{\mu}}$$

(3.23)

where  $\mu$  is the self gain of transistor. The total DC gain of the input buffer shown in Figure 3.8, which composed of two source followers, is given by

Figure 3.13 Pulse Transient Response of Output Buffer

Figure 3.14 Gate Delay Per Stage Versus Power Supply

rand the final N transistor

Assess to a set of input

Figure 3.15 Input Buffer DC Sweep Response

$$A_{T} = A^{2} = \frac{1}{\left(1 + \frac{2}{\mu}\right)^{2}}$$

(3.24)

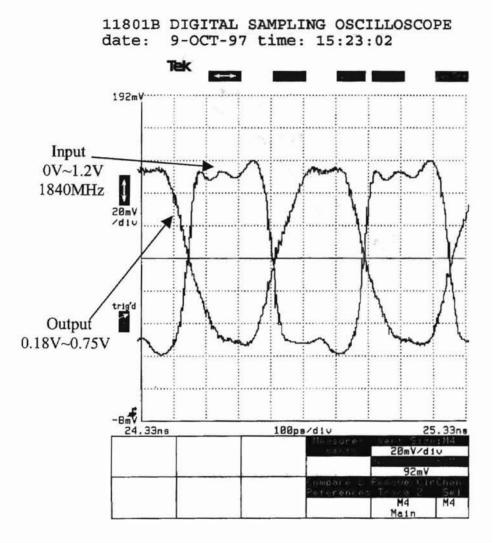

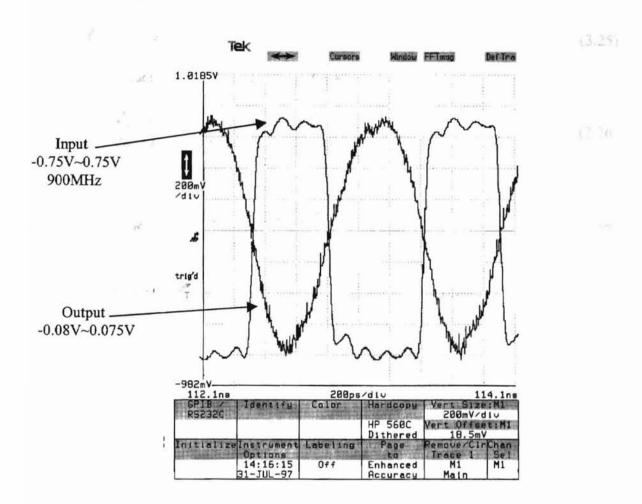

When self gain  $\mu$  is 6 ~ 8, A<sub>T</sub> is 0.56 ~ 0.64. This analysis using the P and N transistor data agrees with the tested results of Figure 3.15. The pulse transient response of input buffer is presented in Figure 3.16.

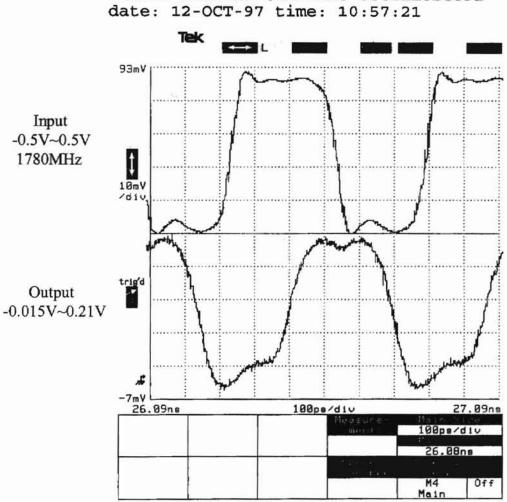

The AC response testing of input buffer showed that the bandwidth of input buffer is around 0.75GHz for SOS process. It was reported that the  $f_T$  of 0.1µm IBM process P transistor is 67GHz [18]. The limited bandwidth of input buffer is mainly due to the following restrictions. First, the 0.65µm length of transistor in this input buffer, which is not the minimum length, reduces the bandwidth by a factor of 6.5. Second, the low  $g_m$  of P transistor (Figure 3.10) reduces the bandwidth by a factor of 2. Third, the load effect reduces the bandwidth by a factor of 2. The MOSFET source resistance could also contribute to the degradation of bandwidth. The input buffer is redesigned to achieve 5.6GHz bandwidth.

## Bubble detector

The basic function of bubble detector is the exclusive-or. To verify the DC function, we can connected one of A or B to ground and sweep the other one. The DC sweep test of the bubble detector is displayed in Figure 3.17. The DC function of bubble detector is confirmed by the testing. The problems that existed here are similar to that of output buffer since both of them are CMOS logic blocks. The P transistor's avalanche voltage causes a logic transition problem and the N transistor's leakage current results in a limited output voltage swing.

11801B DIGITAL SAMPLING OSCILLOSCOPE

Figure 3.16 Pulse Transient Response of Input Buffer

ľ

Figure 3.17 Bubble Detector DC Sweep Response

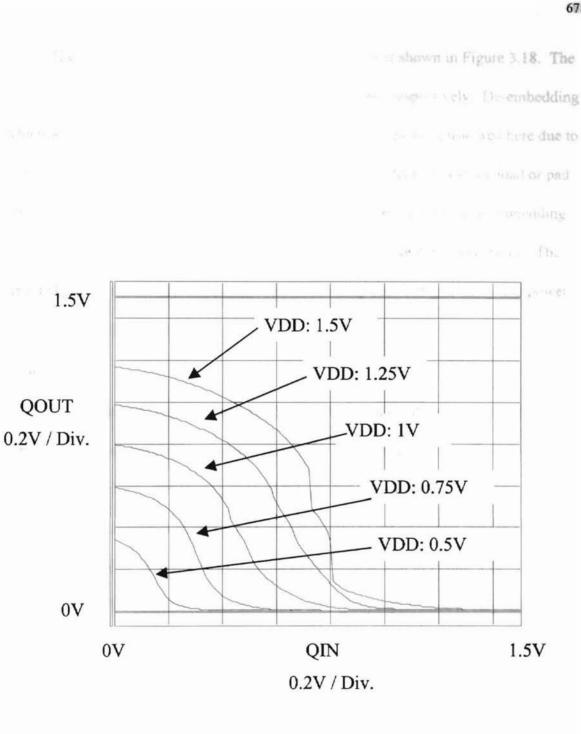

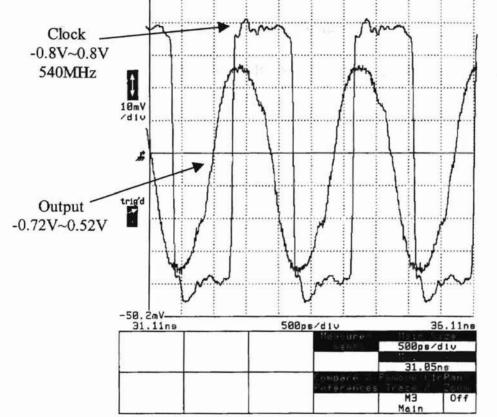

The pulse transient response of the bubble detector is shown in Figure 3.18. The rise time and fall time of the output are 1340ps and 1350ps, respectively. De-embedding (which will be discussed later in pad capacitance section) must be considered here due to the great difference between the gate capacitance of bubble detector and the load or pad capacitance. The effective gate delay is estimated to be 37ps based on a de-embedding factor 36:1, which includes a factor of three due to the series switched resistance. The expected gate delay is about 22ps [18]. The relationship between gate delay and power supply is shown in Figure 3.19.

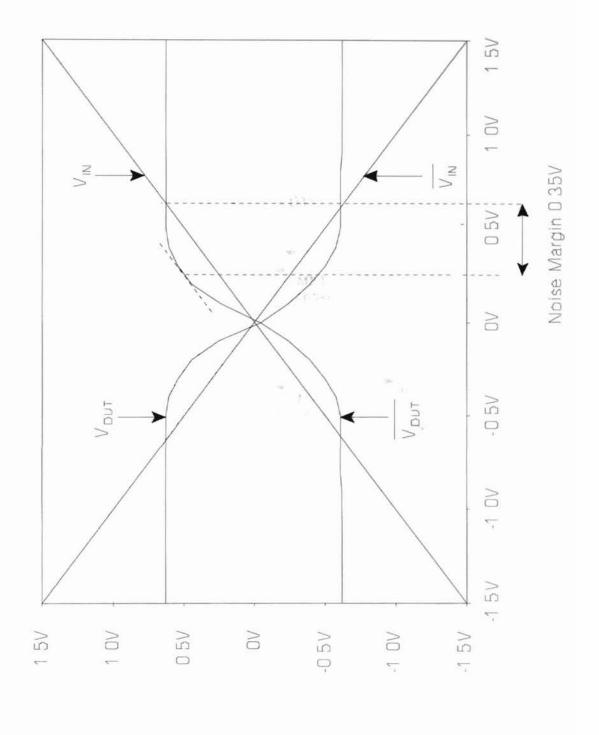

## Comparator

The function of comparator is verified by sweeping input and applying the clock signals to the clock terminals simultaneously. The DC sweep response of comparator is shown in Figure 3.20. The testing verified the DC functionality of comparator. The offset voltage measured is 30 mV while the sensitivity of the changing state is 10 mV.

The transient response of the comparator is represented in Figure 3.21. Deembedding must be considered here also since load (pad) capacitance is very large while the transistors in comparator is very small. The de-embedding factor is 15:1. Therefore, the equivalent rise and fall time are 32ps and 30ps, respectively. The simulation demonstrated a rise and fall time of 60ps.

## • Encoder

Each encoder has 16 inputs signals with half of them (8 inputs) on each side. In the single encoder testing layout, seven of eight inputs on each side had been tied to the negative power supply. Therefore, the basic function of this encoder testing circuit is

Figure 3.18 AC Response of Bubble Detector

11801B DIGITAL SAMPLING OSCILLOSCOPE date: 9-OCT-97 time: 22:40:51

Power Supply (Volts)

Figure 3.19 Gate Delay Versus Power Supply

Figure 3.20 Comparator DC Sweep Response

Figure 3.21 Clock Pulse Transient Response of Comparator

and and the second s

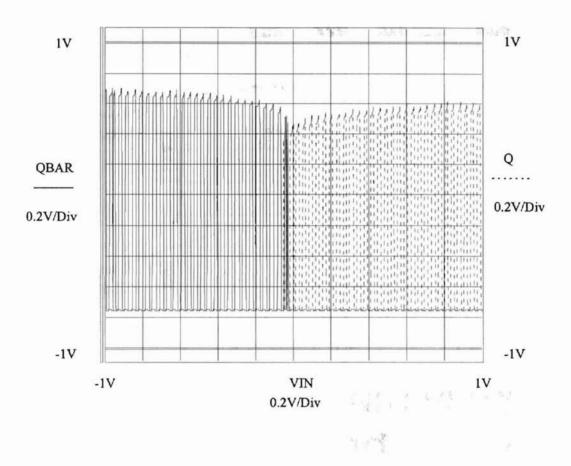

simply an inverter. The DC sweep testing of encoder is illustrated in Figure 3.22. The limited output logic high voltage is due to the N transistor leakage current.

The pulse transient response of encoder is displayed in Figure 3.23. The large pad capacitance limited its rise and fall time performance. The pad de-embedding factor is 87. The encoder was redesigned to achieve the expected 60ps delay performance.

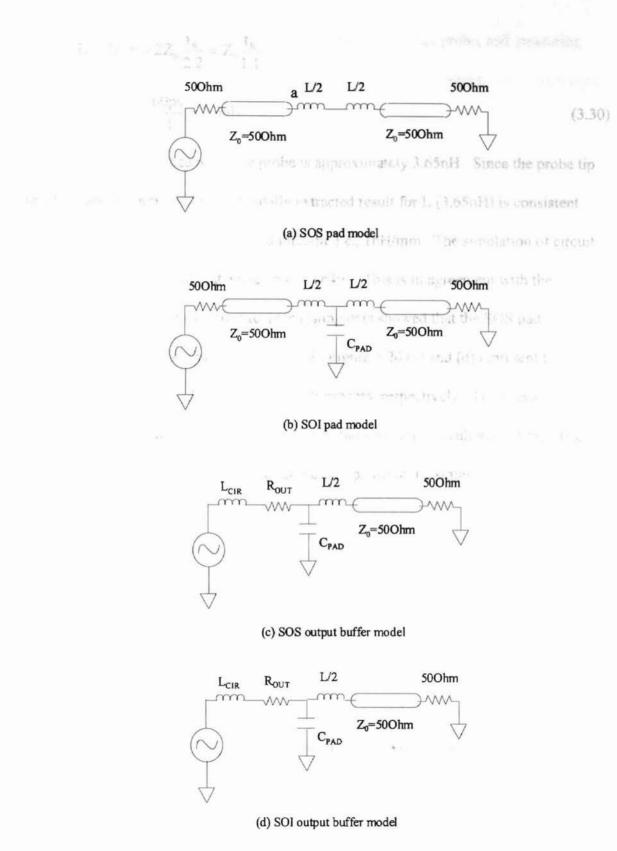

## • Pad capacitance

The pad capacitance measured was too large to be ignored. The 200 $\mu$ m by 200 $\mu$ m pad capacitance was measured at 0.07pF for the SOS process, 1.56pF for the SOI and 3.29pF for the BULK.