## FIRST ORDER QUASI STATIC MOSFET CHANNEL

## CAPACITANCE MODEL

By

## SAMEER SHARMA

Bachelor of Science in Electrical Engineering Punjab Engineering College Chandigarh, India 1994

Master of Science in Electrical and Computer Engineering Oklahoma State University Stillwater, Oklahoma December, 2003

> Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY May, 2008

# FIRST ORDER QUASI STATIC MOSFET CHANNEL

## CAPACITANCE MODEL

Dissertation Approved:

Dr. Louis G. Johnson

Dissertation Adviser

Dr. George Scheets

Dr. James E. Stine, Jr.

Dr. H. K. Dai

Dr. Gordon Emslie

Dean of the Graduate College

# TABLE OF CONTENTS

| CHAPTER PAG |                                                              |    |

|-------------|--------------------------------------------------------------|----|

| I. INTRO    | DUCTION                                                      | 1  |

| 1.1         | MODELING PROCESS                                             | 1  |

| 1.2         | SCOPE                                                        | 4  |

| 1.3         | OUTLINE                                                      | 5  |

| II. LITE    | RATURE REVIEW                                                | 7  |

| 2.1         | MEYER'S MODEL                                                | 8  |

| 2.2         | CHARGE BASED MODELS                                          | 11 |

| 2.3         | TRANS-CAPACITIVE MODEL                                       | 15 |

| 2.4         | MEHMET MODEL                                                 | 15 |

| III. FIRS   | T ORDER QUASI-STATIC CHANNEL CAPACITANCE MODEL               | 18 |

| 3.1         | STEADY STATE OPERATION                                       | 18 |

| 3.2         | QUASI-STATIC OPERATION                                       | 19 |

| 3.3         | MODELING EQUATIONS                                           | 21 |

| IV. MOS     | FET POWER                                                    | 27 |

| 4.1         | SOURCES OF POWER DISSIPATION                                 | 28 |

| 4.2         | POWER AND ENERGY MODELING ISSUES                             | 29 |

| 4.3         | POWER MEASUREMENT TECHNIQUES                                 |    |

| 4.4         | POWER EQUATIONS                                              |    |

| 4.5         | ENERGY FUNCTION CALCULATION                                  | 37 |

| V. FIRST    | <b>FORDER CURRENT COMPONENTS AND CAPACITANCE CALCULATION</b> | 40 |

| <b>CHAPTER F</b>                                                      |                                        |    |  |

|-----------------------------------------------------------------------|----------------------------------------|----|--|

| 5.1                                                                   | FIRST ORDER CURRENT COMPONENTS         | 40 |  |

| 5.2                                                                   | CAPACITANCE DERIVATION                 | 42 |  |

| 5.3                                                                   | EQUIVALENT CIRCUIT                     | 47 |  |

| VI. COM                                                               | /PARISON AND DISCUSSION                | 49 |  |

| 6.1                                                                   | MODEL VERIFICATION AND ADVANTAGES      | 49 |  |

| 6.2                                                                   | ENERGY PUMPING                         | 50 |  |

| 6.3                                                                   | TOTAL FIRST ORDER POWER                | 52 |  |

| 6.4                                                                   | SIMULATION EXAMPLE                     | 52 |  |

| VII. DEPENDENCE OF THE BSIM ABULK PARAMETER ON THE SOURCE POTENTIAL56 |                                        |    |  |

| 7.1                                                                   | EVALUATION OF EXTRA CURRENT COMPONENTS | 57 |  |

| 7.2                                                                   | SIMULATION EXAMPLE                     | 58 |  |

| 7.3                                                                   | CONCLUSION                             | 63 |  |

| REFERENCES                                                            |                                        |    |  |

| APPENDICES                                                            |                                        |    |  |

# LIST OF TABLES

| TABLE                                                    | PAGE |

|----------------------------------------------------------|------|

| Table 3.1 NMOS Zero and First Order Charges and Currents | 25   |

| Table 4.1 Power Equations                                | 37   |

| Table 4.2 Energy Function                                | 39   |

| Table 5.1: Storage and Dissipative Current Components    | 42   |

| Table 5.3: Total Capacitances.                           | 44   |

| Table 5.4: Conserved Capacitances                        | 45   |

| Table 5.5: Dissipative Capacitances                      | 46   |

# LIST OF FIGURES

| FIGURE                                                                       | PAGE |

|------------------------------------------------------------------------------|------|

| Figure 1.1: Energy Imbalance                                                 | 3    |

| Figure 2.1: Meyer Capacitance Model                                          | 8    |

| Figure 2.2: Channel Current Calculations                                     | 9    |

| Figure 2.3: Current Representation in Meyer's Model                          | 11   |

| Figure 2.4: Channel Charge approximation using Ward's Model                  | 12   |

| Figure 2.5: Trans-capacitance Approximation                                  | 15   |

| Figure 2.6: Small Signal Representation of Mehmet's Model                    | 17   |

| Figure 3.1: Bulk and SOI CMOS Structures                                     | 18   |

| Figure 3.2: Voltage, Charge and Current Waveforms                            | 20   |

| Figure 3.3: Four terminal MOSFET Structures                                  | 22   |

| Figure 4.1: Leakage Current Components                                       | 28   |

| Figure 4.2: Dynamic Power                                                    | 30   |

| Figure 4.3: Transient Waveforms                                              | 31   |

| Figure 4.4: Capacitor based Power Measurement Technique                      | 34   |

| Figure 4.5: Power Dissipation in MOS Transistor                              | 34   |

| Figure 4.6: MOS Channel Power Calculation                                    | 35   |

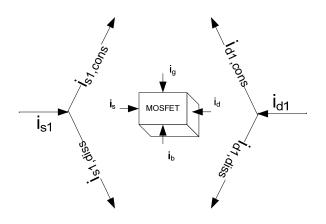

| Figure 5.1: First order dissipative and conserved current components         | 41   |

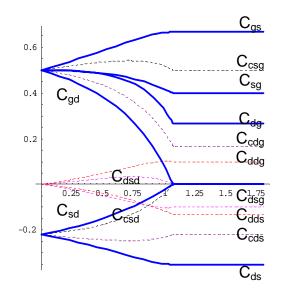

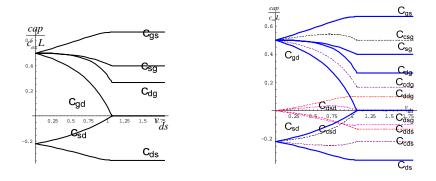

| Figure 5.2: Total, Conserved and Dissipative Capacitances vs v <sub>ds</sub> | 44   |

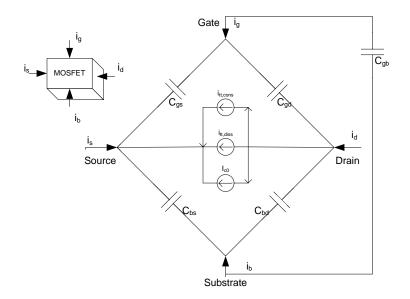

| Figure 5.3: Equivalent Circuit                                               | 47   |

## FIGURE

## PAGE

| Figure 6.1: Terminal capacitances vs v <sub>ds</sub>              | 50 |

|-------------------------------------------------------------------|----|

| Figure 6.2: Capacitance vs v <sub>ds</sub>                        | 50 |

| Figure 6.3: Gate pumping action                                   | 51 |

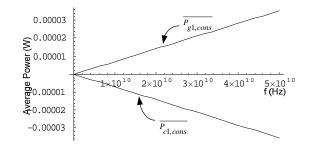

| Figure 6.4: Average conserved gate and channel power vs frequency | 51 |

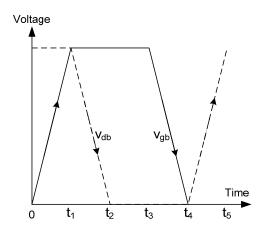

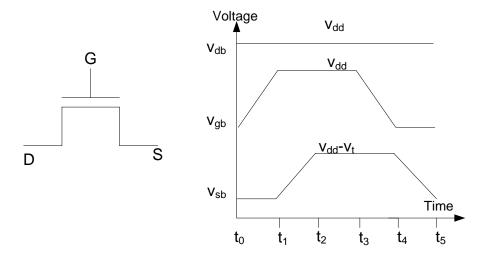

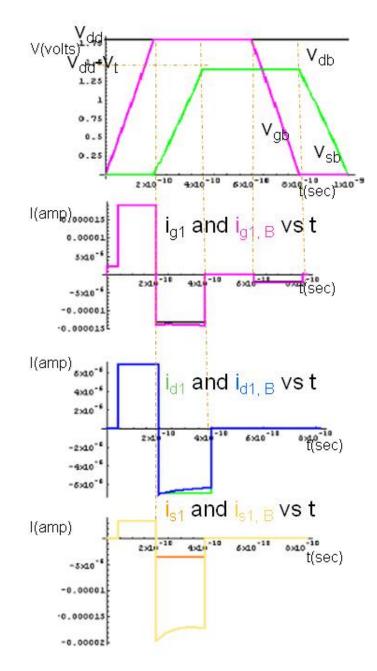

| Figure 6.5: Idealized voltage waveforms                           | 53 |

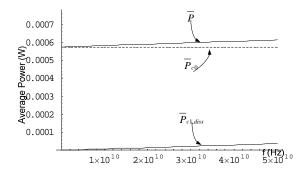

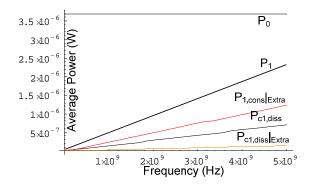

| Figure 6.6: Total power vs. frequency                             | 54 |

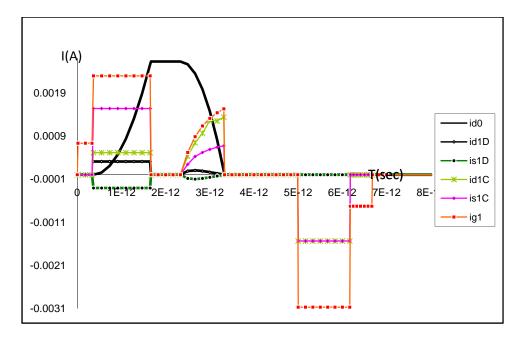

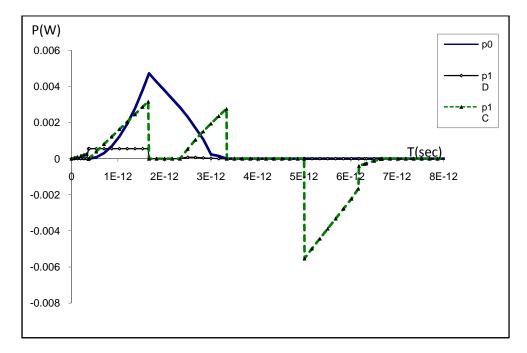

| Figure 6.7: Current plots                                         | 55 |

| Figure 6.8: Power plots                                           | 55 |

| Figure 7.1: Terminal capacitances vs v <sub>ds</sub>              | 59 |

| Figure 7.2: Extra power dissipation                               | 60 |

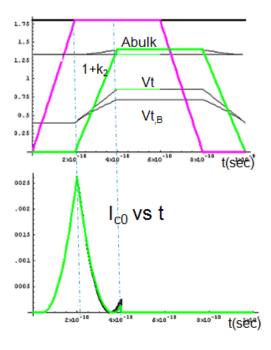

| Figure 7.3: Threshold voltage and bulk charge parameter           | 61 |

| Figure 7.4: Zero order currents                                   | 61 |

| Figure 7.5: First order currents                                  | 62 |

## LIST OF SYMBOLS

| SYMBOLS         |  | NAMES                                      |

|-----------------|--|--------------------------------------------|

| $q_{c}$         |  | channel charge per unit length             |

| $q_{c0}$        |  | zero order channel charge per unit length  |

| $q_{c1}$        |  | first order channel charge per unit length |

| $q_s$           |  | source charge per unit length              |

| $q_{d}$         |  | drain charge per unit length               |

| $q_g$           |  | gate charge per unit length                |

| L               |  | channel length                             |

| W               |  | channel width                              |

| $c_{ox}$        |  | oxide capacitance per unit length          |

| <sup>v</sup> fb |  | flat band voltage                          |

| $v_{t0}$        |  | threshold voltage at zero source bias      |

| v <sub>t</sub>  |  | threshold voltage                          |

| $\phi$          |  | fermi potential                            |

| $t_{ox}$        |  | oxide thickness                            |

| <sup>v</sup> cb |  | channel terminal voltage                   |

| <sup>v</sup> gb |  | gate terminal voltage                      |

| vsb             |  | source terminal voltage                    |

| SYMBOLS                |   | NAMES                                  |

|------------------------|---|----------------------------------------|

| <sup>v</sup> db        |   | drain terminal voltage                 |

| $k_1$                  |   | body effect coefficient                |

| $k_2$                  |   | body effect coefficient                |

| <i>I</i> <sub>c0</sub> |   | zero order (static) current            |

| $I_D$                  |   | static drain current                   |

| IS                     |   | static source current                  |

| $I_{G}$                |   | static gate current                    |

| I <sub>B</sub>         |   | static substrate current               |

| I(t)                   |   | total channel current                  |

| <sup>i</sup> d1        |   | first order drain current              |

| i <sub>s1</sub>        |   | first order source current             |

| i <sub>g1</sub>        |   | first order gate current               |

| i <sub>b1</sub>        |   | first order substrate current          |

| i<br>d1,con            | s | first order conserved drain current    |

| i<br>s1,cons           | s | first order conserved source current   |

| i<br>d1, diss          | 5 | first order dissipative drain current  |

| i<br>s1, diss          |   | first order dissipative source current |

| $\overline{P_{c0}}$    |   | average power                          |

| Р                      |   | total instantaneous power              |

| P <sub>c</sub>         |   | instantaneous channel power            |

| $P_{c0}$               |   | static power                           |

| SYME                 | BOLS | NAMES                                  |

|----------------------|------|----------------------------------------|

| P <sub>c1,dist</sub> | s    | first order dissipative channel power  |

| P <sub>c1,con</sub>  |      | first order conserved channel power    |

| P <sub>g1,cor</sub>  | 1.5  | first order gate power                 |

| $C_L$                |      | externally load capacitor              |

| $C_{gb}$             |      | gate to bulk capacitance               |

| $C_{gs}$             |      | gate to source capacitance             |

| $C_{gd}$             |      | gate to drain capacitance              |

| C <sub>sb</sub>      |      | source to bulk capacitance             |

| C <sub>sg</sub>      |      | source to gate capacitance             |

| C <sub>sd</sub>      |      | source to drain capacitance            |

| $C_{db}$             |      | drain to bulk capacitance              |

| $C_{dg}$             |      | drain to gate capacitance              |

| $C_{ds}$             |      | drain to drain capacitance             |

| C <sub>csb</sub>     |      | conserved source to bulk capacitance   |

| C <sub>csg</sub>     |      | conserved source to gate capacitance   |

| C <sub>csd</sub>     |      | conserved source to drain capacitance  |

| C <sub>cdb</sub>     |      | conserved drain to bulk capacitance    |

| C <sub>cdg</sub>     |      | conserved drain to gate capacitance    |

| C <sub>cds</sub>     |      | conserved drain to drain capacitance   |

| C <sub>dsb</sub>     |      | dissipative source to bulk capacitance |

# SYMBOLS NAMES

| $C_{dsg}$            |                  | dissipative source to gate capacitance      |

|----------------------|------------------|---------------------------------------------|

| $C_{dsd}$            |                  | dissipative source to drain capacitance     |

| C <sub>ddb</sub>     |                  | dissipative drain to bulk capacitance       |

| $C_{ddg}$            |                  | dissipative drain to gate capacitance       |

| $C_{dds}$            |                  | dissipative drain to drain capacitance      |

| P <sub>c1, dis</sub> | s, B             | BSIM first order dissipative channel power  |

| P <sub>c1, con</sub> | ns, B            | . BSIM first order conserved channel power  |

| P<br>g1,com          | ns, B            | . BSIM first order gate power               |

| P<br>g1,con          | $s\Big _{Extra}$ | . extra first order channel conserved power |

| P <sub>c1,diss</sub> | Extra            | extra first order channel dissipative power |

| $P_{1,cons}$         | Extra            | extra first order conserved power           |

## ACKNOWLEDGMENTS

I would like to express sincere thanks to my advisor Dr. Louis G. Johnson for his guidance, encouragement and the research opportunity. I would also like to extend appreciation to my committee members Dr. George Scheets, Dr. Yumin Zhang, Dr. James E. Stine Jr. and Dr. H. K. Dai for their invaluable knowledge and guidance.

Additional thanks go to all my colleagues in VLSI Design Group for helpful discussions on circuit simulation, device modeling and power estimation. Finally, I would like to acknowledge the support from my wife Srijana and two daughters Vidhi and Tanya for their patience and encouragement throughout my studies.

## **CHAPTER I**

## **I. INTRODUCTION**

#### 1.1 MODELING PROCESS

Modeling is a process of accurately representing the behavior of a device to be used in a circuit simulator. Designers need these reliable and accurate models for circuit development. With the growth of CMOS technology, MOSFET modeling has taken a centre stage and the accurate modeling of MOS transistor channel capacitance has been an ongoing effort. First, Meyer's [1.1] reciprocal gate-capacitive model, then Ward's [1.2] charge-based, non-reciprocal capacitance model have been used. Many papers have also been written on the comparison of these models. Some [1.3-1.6] claim that Meyer's model fails due to charge non-conservation which justifies the usage of charge-based models while others claim [1.7-1.9] that the charge non-conservation is mainly due to the faulty mathematical modeling of the simulation software. As pointed out by Fossum [1.10], it is not clear whether we have explored all other possibilities. We may be able to achieve a better result with a different channel partition or may be with no partition at all. Recent papers on field-dependent mobility [1.33] and laterally asymmetrical doping [1.34] have now shown inconsistencies in Ward's model, which artificially partitions the channel charge into the source and the drain components. Many ideas have also been suggested for estimation of energy and power taking into consideration the input slew dependency [1.11], propagation delay [1.12], short circuit power [1.13] and supply current measurements [1.14-1.16].

One of the most popular and widely adapted, <u>Berkeley Short-Channel I</u>GFET (BSIM) Capacitive <u>Model</u> [1.17, 1.18] has tried to include many of the above mentioned modeling techniques to estimate the behavior of Insulated Gate Field Effect Transistors (IGFET). However, the BSIM

~1~

capacitive model fails to include the first order trans-capacitive currents due to the charge redistribution in the channel that causes the actual output waveform and the delay to deviate from the BSIM stimulation results [1.19]. In reality, the MOS device is a highly nonlinear four terminal device and modeling it as a simple energy storage device leaves a lot to be desired. When the inversion layer is formed, the I-R drop from the resistive components and charge redistribution current causes power dissipation in the channel. This makes the assumption that the capacitive model does not contribute any net power dissipation in the channel inconsistent for use in energy prediction.

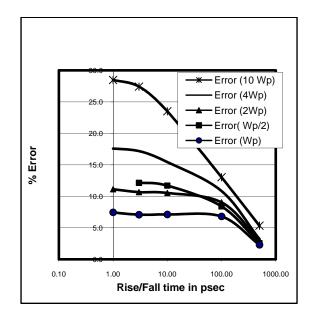

If the BSIM model is not consistent, one may ask as why it is still being used? The reason is: the BSIM quasi-static models are analog friendly, continuous and have good I-V characteristic. These I-V models are derived from the channel charge that is calculated correctly to the first order. Power is also derived from the channel charge. The problem, however, is that the power is derived only to zero order. In other words, the BSIM capacitive model calculates static power dissipation, which is nothing but the multiplication of zero order current and steady state voltage. Though the BSIM capacitive model includes first order corrections in dynamic power calculation, it leaves out some important terms. We can think the process of dynamic power calculation of the BSIM model as being nothing but an easy way of calculating the zero order power by using the change in the energy of the capacitors during charging and discharging. The BSIM capacitive model assumes that the first order terms are the energy storage terms (like capacitors and inductors) that do not dissipate energy, which in reality is not the case. Hence it is not appropriate to look at the change in the energy of the capacitors in the channel as there is no energy function for the channel. It causes an error and gives a different number for power from the supply power than the dissipated power from all the devices, clearly a violation of energy conservation principles. This effect is pointed out in Fig. 1.1 which is a plot of switching frequency and the energy imbalance for different width ratios of transistors in a inverter. As seen, for higher switching frequencies (small rise/fall times) the energy imbalance is more pronounced.

~2~

In reality, it is very difficult to estimate the usefulness of SPICE simulation in the power estimation of a real circuit. In digital applications, it is well known that the glitches can contribute half the power, and how accurately we can predict the power spike depends on how accurately we can predict the glitches. Therefore, it did not make a whole lot of difference, as SPICE was not predicting the power accurately anyway. Even if it were able to predict the power, it is not possible to extrapolate to a real circuit with glitches that are not exactly the same as SPICE calculated. However, in the world of Pentiums [1.20], Core Duos [1.21] and Quanti-Speed Architecture processors [1.22], where the gates are switching around 300 billion times a second [1.23], it becomes essential to calculate the higher order transients to accurately predict the device power and switching dynamics.

Figure 1.1: Energy Imbalance

It should also be pointed out that scholars working in the MOS device-modeling are aware of the transport current components flowing in the channel. Many papers [1.24 -1.27] and chapters [1.28-1.30] have been written about the charging and transport current components. However, all of them assume that it is not possible to separate the dissipative and energy storage components and have come up with many theories and models to envision the transient effects. One of the models by Lim-Fossum [1.31, 1.32] has the first order transient trans-capacitive current and

suggests the difference between non-reciprocal capacitive elements to be responsible for these transport currents. This however has some drawbacks. First, if these were the total trans-capacitive currents, its product with the drain to source voltage should have been the total dissipative power, which is not the case. Second, Lim-Fossum used Ward's charge partition model to find the source and drain charge components, which makes their model dependent on the accuracy of the charge partition.

#### 1.2 SCOPE

The object of the research is to realize the inconsistency in the current MOSFET modeling and develop efficient models for accurate intrinsic capacitance and power dissipation estimation. An ideal model would be to consider all non linear effects and solve a complete non-linear differential equation for the channel in three dimensions. In that case, we see a packet of charge traveling down the channel as a function of time. Although such models are valuable, from the simulation perspective, the process is ineffective as the simulation times are very long. To be computationally efficient, we need compact models that describe the electrical behavior analytically and are able to represent the non-linear channel in a reasonable time without sacrificing modeling accuracy. Furthermore, the fast scaling of frequency for semiconductor integrated circuits that was seen in the last few decades has been saturating. One of the reasons is the increase in power dissipation. Power limits the scaling. The high power dissipation due to small device geometry has thrown off course the roadmap of future development of semiconductor technologies. When the devices are switching rapidly, the power dissipation per unit area goes up causing excessive heating. Unless a sophisticated cooling system is implemented, the device may no longer be operational. The reality is: we have reached a power limited scaling regime. Scaling now is no longer determined by the device size, but by how much power the chip can dissipate at a particular working frequency. However, the lack of suitable device models to measure this power dissipation has provided a plethora of research avenues. The conventional MOSFET models have some inherent issues and are not consistent for power and energy prediction as they:

~4~

- Fail to include the first order power dissipation due to channel charge redistribution

- Give a net non-zero power in the channel that has no physical basis from the terms that should be conserved

This makes the MOSFET modeling very important going forward into the nanometer regime. Given that the accuracy of the simulation depends on the physical representation of the device, it is very important that we have a reliable mathematical model that is able to represent the device behavior. Designers need these accurate models for circuit development.

#### 1.3 OUTLINE

The outline of the dissertation is as follows:

Chapter 2 describes the conventional MOSFET models used in transient analysis and computer simulation. The analysis of these models gives a general overview and a good background on device modeling. Some of these models are still being used for device simulation. The Meyer's model, Ward's charge partition model, Mehmet model and Trans-capacitance models and its effectiveness are considered. Some of the advantages and the shortcomings are also discussed.

Chapter 3 describes a one dimensional MOSFET current model with current continuity equations. These equations have been used to compute the channel currents and channel charges as well as currents at the source and the drain terminals for a charge conserving, quasi-static, channel capacitance model. The calculation of channel currents without charge partition allows the computation of the instantaneous channel power, which further helps in separating the dissipating and energy conserving current components.

Chapter 4 describes the details of power estimation. Zero and the first order instantaneous power is computed by integrating the power density over the entire channel. This leads to the derivation of closed-form analytical expressions for the conserved and dissipative current components from the first order drain and source currents. The energy function calculations from the first order conserved power components are also shown.

Chapter 5 describes the derivation of capacitances from the first order drain ( $i_{d1}$ ) and source ( $i_{s1}$ ) current components. These capacitances are then separated into conserved and dissipative components. An improved equivalent circuit is also developed by following the method used by Lim-Fossum.

The results are verified using the BSIM Capacitive and Lim-Fossum fully depleted SOI models for currents and charges in chapter 6. Even though these models used a charge partition instead of solving exactly as we have, all models predict the same source and drain currents, and hence the same terminal capacitances. However, we are able to separate out these capacitances into conserved and dissipative components.

Chapter 7 describes the inconsistencies of the BSIM capacitive model for energy and power prediction. We have shown that the dependence of the BSIM bulk charge parameter on the source potential causes extra power dissipation in the channel that has no physical basis. This leads to an inconsistent power model where energy supplied from the gate does not balance out with the energy generated at the channel.

### **CHAPTER II**

### **II. LITERATURE REVIEW**

This chapter describes some of the MOS models that have been used in circuit simulators to analyze the transient response. Historically, MOS devices have been modeled with capacitor and over the last few decades, many such capacitive models have been proposed to effectively represent the charges at the four terminals of a FET device. The problem however is the difficulty in representing the terminal charges by a single model. This is because; MOS transistors not only conduct current in a steady state but also conduct when the terminal voltages are varying. The time dependence of currents and voltages of a MOSFET makes representation using steady state (DC) conditions insufficient. A solution is possible by superimposing zero order steady state DC (I-V) representation over a capacitance (C-V) model to characterize the transients as

$$I(t) = I_{c0}(v) + i_{c1}(v, \frac{dv}{dt})$$

where  $I_{c0}(v)$  is the steady state (DC) current and depends only on the instantaneous terminal voltages.  $i_{c1}(t)$  is the transient transport component and is zero under steady state conditions. For simulation purposes, the capacitance (C-V) model is developed by expanding the transient current as

$$i_{c1}(t) = \frac{dq}{dt} = c\frac{dv}{dt}$$

In the subsequent sections, some of these models have been discussed in chronological order of the history of device modeling.

#### 2.1 MEYER'S MODEL

In 1971, Meyer [2.1] proposed the first large signal model for MOS transistors in terms of physical device parameters.

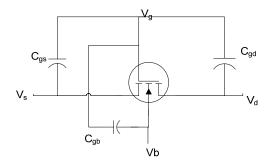

Figure 2.1: Meyer Capacitance Model

The model represents the charge storing property of MOS transistors using three nonlinear voltage dependent capacitors, as shown in Fig. [2.1]. These capacitors are defined in terms of the total gate charge  $Q_g$ . Meyer's model is a simple charge conservation model as it restricts the sum of the gate charge  $Q_g$  and channel charges  $Q_c$  o be zero, and is based on the following five assumptions.

- The total gate charge Q<sub>g</sub> is a function of the terminal voltage under steady state conditions.

- The gate capacitances are found as:

$$C_{gs} = \frac{\partial Q_g}{\partial v_{gs}} \qquad C_{gd} = \frac{\partial Q_g}{\partial v_{gd}} \qquad C_{gb} = \frac{\partial Q_g}{\partial v_{gb}}$$

(2.1)

$$C_{gg} = C_{gs} + C_{gd} + C_{gb}$$

Where  $v_{gs}$ ,  $v_{gd}$  and  $v_{gb}$  are the gate to source, gate to drain and gate to bulk voltages.

• The drain to bulk, source to bulk and drain to source capacitances are assumed to be zero.

$$C_{ds} = C_{db} = C_{sb} = 0$$

$$C_{sd} = C_{bd} = C_{bs} = 0$$

It is assumed that the capacitance matrix is symmetrical, which is necessary to conserve energy.

$$C_{gd} = C_{dg}$$

$C_{gs} = C_{sg}$   $C_{gb} = C_{bg}$

• The total source, drain and bulk capacitances are calculated as:

$$C_{dd} = C_{ds} + C_{dg} + C_{db}$$

$$C_{ss} = C_{sg} + C_{sd} + C_{sb}$$

$$C_{bb} = C_{bs} + C_{bd} + C_{bg}$$

These five assumptions give the capacitance matrix as shown below;

$$\begin{bmatrix} C_{gd} + C_{gs} + C_{gb} & -C_{gd} & -C_{gs} & -C_{gb} \\ -C_{gd} & C_{gd} & 0 & 0 \\ -C_{gs} & 0 & C_{gs} & 0 \\ -C_{gb} & 0 & 0 & C_{gb} \end{bmatrix}$$

To calculate the total gate charge (  $\mathcal{Q}_{g}$  ), a gradual channel approximation is used. The charge

per unit area at any position x along the channel is given in by

$$Q(x) = C_{ox}(V_{gb} - V_t - V(x))$$

Figure 2.2: Channel Current Calculation

where  $V_{gb}$  is the gate voltage,  $V_t$  is the threshold voltage, V(x) is the potential at position x along the channel, and  $C_{ox}$  is the gate oxide capacitance per unit area. The steady state drain current  $I_{c0}$  is found using

$$I_{c0} = WQ(x)\mu \frac{dV(x)}{dx}$$

where W is the channel width and  $\mu$  is the mobility. Integrating from source (x=0) to drain (x=L);

$$I_{c0} = \mu C_{ox} \frac{W}{2L} (V_{gs}^2 - V_{gd}^2)$$

(2.2)

where *L* is the channel length. Gate charge is given by

$$Q_{g} = \frac{2}{3} WLC_{ox} \left[ \frac{(V_{gd} - V_{t})^{3}}{(V_{gd} - V_{t})^{2} - (V_{gs} - V_{t})^{2}} - \frac{(V_{gs} - V_{t})^{3}}{(V_{gd} - V_{t})^{2} - (V_{gs} - V_{t})^{2}} \right]$$

(2.3)

Using (2.1) and (2.2), capacitances are calculated as

$$C_{gs} = \frac{2}{3} WLC_{ox} \left[ 1 - \frac{(V_{gd} - V_t)^2}{(V_{gs} - V_t + V_{gd} - V_t)^2} \right]$$

(2.4)

$$C_{gd} = \frac{2}{3} WLC_{ox} \left[ 1 - \frac{(V_{gs} - V_t)^2}{(V_{gs} - V_t + V_{gd} - V_t)^2} \right]$$

(2.5)

$$C_{gb} = 0$$

Finally, current through each capacitor is computed as

$$I_{gs} = C_{gs} \frac{dV}{dt} \qquad I_{gd} = C_{gd} \frac{dV_{gd}}{dt} \qquad I_{gb} = C_{gb} \frac{dV_{gb}}{dt}$$

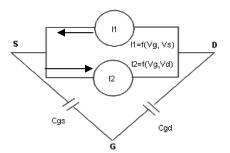

Fig. 2.4 shows the current representation of Meyer's model. Currents I1 and I2 in the channel are assumed to be bidirectional, one being dependent on gate-to-source and other being dependent on gate-to-drain. This is also known as "Two-current-source MOS model".

Figure 2.3: Current Representation in Meyer's model

The major drawback of Meyer's model is the exclusion of the source to bulk and drain to bulk capacitances resulting from substrate charges.

#### 2.2 CHARGE BASED MODELS

Ward [2.2-2.4] claimed that Meyer's model failed the charge conservation test for circuits that required charge storage. They identified the presence of nonlinear reciprocal capacitances and exclusion of the source to bulk and drain to bulk capacitances as being the source of charge non-conservation in the circuit simulation. They based their findings using current equation

$$i(t) = C(v) \frac{dV}{dt}$$

(2.6)

Here the capacitance term is dependent on the terminal voltages of the source, drain and the gate and has been evaluated at some appropriate voltage i.e. C(v) is not defined as a time dependent variable and can follow any path and as a result may lead to some arbitrary charge value. The best possible solution with average value of capacitor taken at two time intervals may also lead to an incomplete charge prediction. Integrating from the present time point  $t_0$  to the next time point  $t_1$  equation (2.6) can be written as

$$\int_{t_0}^{t_1} i(t)dt = \int_{v(t_0)}^{v(t_1)} C(v)dv$$

(2.7)

If C(v) is considered a constant, equation (2.7) reduces to

$$\int_{t_0}^{t_1} i(t)dt = C(v)[V(t_1) - V(t_0)]$$

(2.8)

The capacitance value for C(v) that's been used here is computed at time  $t_0$ . Ward assumes this being the reason for charge pumping, as there may be some residual charge at time  $t_0$ . He suggests that even if the capacitive values are calculated at time  $t_1$  or smaller time steps, it will not guarantee charge conservation. To overcome the assumed charge neutrality limitations, he suggested the charge-partition model [2.2].

The charge-partition model is based on the fixed charge distribution in the MOSFET terminals. The model tries to split the total channel charge  $Q_c$  into source ( $Q_s$ ) and drain ( $Q_d$ ) charges rather than splitting the total distributed capacitance into reciprocal gate-to-source and gate-to-drain capacitances. The current is then computed as the derivative of charge as

$$i(t) = \frac{dQ(t)}{dt}$$

Using similar integration approach as equation (2.7)

$$\int_{t_0}^{t_1} i(t)dt = Q(t_1) - Q(t_0)$$

(2.9)

Though  $Q(t_0)$  and  $Q(t_1)$  are complex functions of time, it can be obtained at any time by terminal voltage at that instant.

Figure 2.4: Channel Charge Approximation using Ward's model

The emphasis of the charge model was the use of charge as a state variable for the computation of charge at the MOSFET terminals. Ward was also able to put in perspective a current continuity

equation

$$\frac{\partial I(y,t)}{\partial y} = -W \frac{\partial Q(y,t)}{\partial t}$$

with the boundary conditions on  $V(y)$  as  $V(0) = V_s$  and  $V(L) = V_d$

to calculate the source and drain charges together with the source and drain currents, and the transport current. Using the current continuity equation, the current at any point y on the channel is evaluated as

$$I(y,t) - I_{s}(t) = -W \int_{0}^{y} \frac{\partial Q(y,t)}{\partial t} dy$$

(2.10)

where  $I_s(t) = I(0,t)$  is the source current, and L is the length of the channel. Considering only drift current for I(y,t) and solving for  $I_s(t)$ , equation (2.10) reduces to two current components

$$I(y,t) = -\mu WQ(y,t) \frac{\partial V(y,t)}{\partial y} \text{ and}$$

(2.11)

$$I_{s}(t) = -\frac{W}{L} \int_{0}^{L} \mu(y,t)Q(y,t)\frac{\partial V(y,t)}{\partial y}dy + \frac{d}{dt} \left[ W \int_{0}^{L} (1-\frac{y}{L})Q(y,t)dy \right]$$

(2.12)

Substituting y=L to obtain the drain current

$$I_{d}(t) = -\frac{W}{L} \int_{0}^{L} \mu(y,t)Q(y,t)\frac{\partial V(y,t)}{\partial y}dy + \frac{d}{dt} \left[ W \int_{0}^{L} (\frac{y}{L})Q(y,t)dy \right]$$

(2.13)

Since the drain and source current can be assumed to have transport and charge components, they can be represent using

$$I_{s}(t) = -I_{T}(t) + \frac{dQ_{s}(t)}{dt}$$

(2.14)

$$I_{d}(t) = I_{T}(t) + \frac{dQ_{d}(t)}{dt}$$

(2.15)

From equations (2.13) (2.14) and (2.15),

$$Q_s = W \int_0^L (1 - \frac{y}{L})Qdy$$

(2.16)

$$Q_d = W \int_0^L (\frac{y}{L}) Q dy$$

(2.17)

Many modifications have been made since Ward proposed the original charge model in 1981. Almost all these models consider "charge" as a state variable and use non-reciprocal capacitors. Some models have partitioned the channel charge into drain and source components in the ratio of 40/60 while others use a 50/50 model. However, none of these models addresses the actual cause of charge non-conservation. Yang, Berton and Chatterjee [2.5], while investigating the charge conservation problem, observed that the non-conservation of charge in circuit simulator SPICE is due to the integration problem independent of device physics. They think the error is due to the choice of voltage as a state variable for simulation, and also due to the nonlinearities in the MOS capacitances and its dependence on four different terminal voltages.

Sakallah, Yen and Greenberg [2.6] also support the view that the charge non-conservation in the Meyer capacitance model has nothing to do with the device physics or a faulty capacitive model, *"rather by the mathematical error of characterizing a multidimensional function by an incomplete subset of its partial derivatives."* They conclude that the charge non-conservation can be eliminated if circuit simulators are given non trivial models. They also followed modeling using Ward's approach and proceeded by splitting total channel charge into source and drain instead of splitting total distributed capacitance between the gate and the channel into reciprocal gate-to-source and gate-to-drain capacitances. As mentioned earlier, the charge splitting techniques have been revised many a time, and have been classified into two groups with respect to the bulk charges included in the model [2.7] for efficient MOSFET modeling. They are

I. Depletion Charge Model (DSM)

II. Simplified Charge Model (SCM)

In DCM, bulk charge is considered to be proportional to the square root of a voltage, while SCM is a more simplified DCM model, with slight compromise in bulk to drain and bulk to source capacitances.

Although charge-based models provided an alternate way to model MOSFET's, it was still not able to explain the charge non-conservation of the Meyer capacitance model. Roots and Hughes [2.8] in 1988 and Snider [2.9] in 1995 suggested a trans-capacitance model, which came close in identifying the conservation problem.

~14~

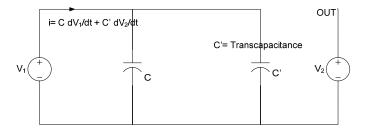

#### 2.3 TRANS-CAPACITIVE MODEL

Roots and Hughes [2.8] in 1988 and later Snider [2.9] was able to explain the charge nonconservation of the Meyer capacitance model using the concept of trans-capacitance. According to them, a capacitive gate to source MOS elements that depends on both gate to source and gate to drain voltages would transport a non-zero charge. They predicted the violation of charge conservation due to the omission of recharging effect of capacitances and tried to compensate the charge by adding an extra element in the circuit and called it a trans-capacitance element. Their model concluded that:

1. Current equation  $I = C \frac{dV}{dt}$  alone does not account for all the currents in MOS transistors

as capacitances are controlled by more than one source.

2. These capacitances appear to dissipate energy if trans-capacitance terms are ignored.

Figure 2.5: Trans-capacitance Approximation

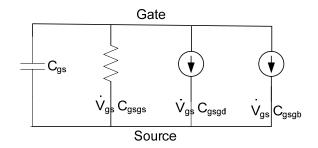

#### 2.4 MEHMET MODEL

In 1989, Mehmet A. Cirit [2.10] was able to show the root cause of charge non-conservation in the gate-capacitance model proposed by Meyer. He points out that the "*Meyer model is a first-order inaccurate approximation to MOS capacitances.*" Since the MOS capacitance is dependent on several variables, faults in the modeling of such an element causes the SPICE simulator to neglect non-linear first order capacitive terms.

Considering the gate to source transient current equation

$i_{gs} = C_{gs} \,\partial_t v_{gs}$

its partial derivative gives

$$i_{gs} = C_{gs} \delta^V_{gs} + \delta C_{gs} \delta^V_{gs} .$$

(2.20)

Since gate capacitance is dependent on gate to source, gate to drain and gate to bulk voltages, including these effects, equation (2.20) can be modified as

$$\delta i_{gs} = C_{gs} \delta^V_{gs} + V_{gs} \frac{\delta C_{gs}}{\delta V_{gs}} \delta V_{gs} + V_{gs} \frac{\delta C_{gs}}{\delta V_{gd}} \delta V_{gd} + V_{gs} \frac{\delta C_{gs}}{\delta V_{gb}} \delta V_{gb}$$

(2.21)

If  $\alpha$  is 1/h, where h is the time interval, and voltage varies by an amount  $\delta V$ , the corresponding change in its time derivative  $\overset{\bullet}{V}$  can be estimated as  $\delta \overset{\bullet}{V} = \alpha \delta V$ . Substituting these values in equation (2.21), equation (2.21) can be rewritten as

$$\delta i_{gs} = C_{gs} \alpha \delta V + V_{gs} \frac{\delta C}{\delta V_{gs}} \delta V_{gs} + V_{gs} \frac{\delta C}{\delta V_{gd}} \delta V_{gd} + V_{gs} \frac{\delta C}{\delta V_{gb}} \delta V_{gb}$$

(2.22)

Similarly, gate to drain and gate to substrate current can be written as

$$\delta i_{gd} = C_{gd} \alpha \delta V + V_{gd} \frac{\delta C_{gd}}{\delta V_{gs}} \delta V_{gs} + V_{gd} \frac{\delta C_{gd}}{\delta V_{gd}} \delta V_{gd} + V_{gd} \frac{\delta C_{gd}}{\delta V_{gb}} \delta V_{gb}$$

(2.23)

$$\delta i_{gb} = C_{gb} \alpha \delta V + V_{gb} \frac{\delta C_{gb}}{\delta V_{gs}} \delta V_{gs} + V_{gb} \frac{\delta C_{gb}}{\delta V_{gd}} \delta V_{gd} + V_{gb} \frac{\delta C_{gb}}{\delta V_{gb}} \delta V_{gb}$$

(2.24)

The first term in (2.22-2.24) is frequency dependent, while rests of the terms are due to non-linear capacitances and look like resistors in the channel. As circuit simulators only considered the frequency dependent terms for circuit evaluation, Mehmet assumed that this incomplete representation was the root cause of charge pumping in circuit simulators, and proposed a model to include ignored non-linear terms that caused an extra charge in the channel.

Figure 2.6: Small Signal Representation of Mehmet Model

Fig. 7 shows a small signal representation of Mehmet model for  $C_{gs}$  where

$$C_{gsgs} = \frac{\delta C_{gs}}{\delta V_{gs}} \qquad C_{gsgd} = \frac{\delta C_{gs}}{\delta V_{gd}} \qquad C_{gsgb} = \frac{\delta C_{gs}}{\delta V_{gb}}$$

(2.25)

$$C_{gdgs} = \frac{\delta C_{gd}}{\delta V_{gs}} \qquad C_{gdgd} = \frac{\delta C_{gd}}{\delta V_{gd}} \qquad C_{gdgb} = \frac{\delta C_{gd}}{\delta V_{gb}}$$

(2.26)

$$C_{gbgs} = \frac{\delta C_{gb}}{\delta V_{gs}} \qquad C_{gbgd} = \frac{\delta C_{gb}}{\delta V_{gd}} \qquad C_{gbgb} = \frac{\delta C_{gb}}{\delta V_{gb}}$$

(2.27)

Mehmet used this model in the circuit simulator Lspice and observed the charge conservation. He concluded that the Meyer gate capacitance model can be made to conserve charge by considering all first order terms. He also pointed out that the substrate charges might be easily included in the Meyer capacitance model to simulate the MOS devices more accurately.

It should be noted that in any MOSFET model, charge or capacitance, the charge neutrality condition is built into the derivation [2.11] and may seem unreasonable to come up with a charge non-conservation problem. Whichever modeling techniques are used, the main goal is to come up with an analytical description of MOS device behavior with emphasis on equations that are continuous in all regions of device operation.

### **CHAPTER III**

### **III. FIRST ORDER QUASI-STATIC CHANNEL CAPACITANCE MODEL**

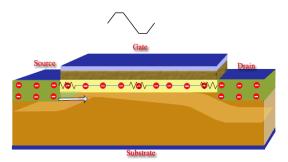

This chapter describes the mathematical equations used to analyze the MOS transistor for the research work. The current continuity equations are presented without the channel charge partition to compute the steady state and dynamic current components. These currents then become the basis for I-V and C-V models to be used in the circuit simulators.

#### 3.1 STEADY STATE OPERATION

In the steady state, the gate and substrate are assumed to have no direct conductive path to the channel. Leakage through the gate oxide as well as recombination current between the substrate and the channel are neglected.

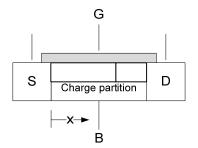

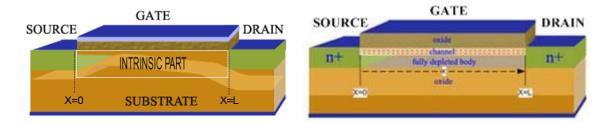

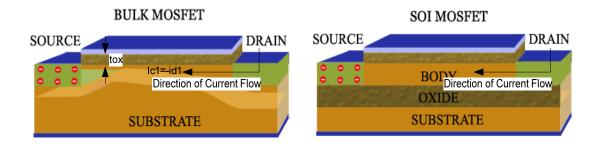

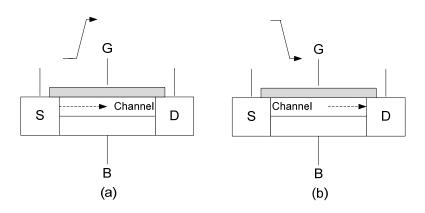

Figure 3.1: BULK and SOI CMOS Structures

It is very important that the body charges are properly modeled [3.1, 3.2, 3.3] and its effects are included for steady state and the transient simulations. These effects cause an uneven distribution of channel charge between the source and the drain regions, and the regions in between, which in turn causes uneven distribution of the gate and substrate charges. To model all these skewed distributions, it will be convenient to describe the charges by its density per unit length. Considering only the intrinsic part of the MOS transistor, which is responsible for all the transistor action, the zero order charge per unit length at the terminals can be written as

$$q_{jb0} = f(v_{gb}, v_{cb}) \text{ where } j = g, c$$

(3.1)

In terms of drift current, current flow in the device can be seen due to the transport of electrons from the source to the drain terminal. Taking steady state values,

$$I_{c0} = I_D \tag{3.2}$$

$$I_S = -I_D \tag{3.3}$$

$$I_G = 0 \tag{3.4}$$

$$I_B = 0$$

(3.5)

where  $I_{c0}$  is the steady state channel current, which becomes  $I_D$  at the drain end and  $-I_S$  at the source end. The steady state gate  $I_G$  and substrate currents  $I_B$  are zero as the transistors are assumed to be leakage free. These terminal currents can be expressed as some function of terminal voltages and can be written as

$$I_{c0} = f(v_D, v_G, v_S, v_B)$$

(3.6)

#### 3.2 QUASI-STATIC OPERATION

Equation (3.4) was calculated with the assumption that the terminal voltages were steady. In a real circuit, transistors operate under dynamic conditions where terminal voltages are varying. To calculate the charge under such conditions, quasi-static operations are assumed. The voltages are allowed to vary slowly in quasi-static operation. Though the gate, substrate and the channel charges are still the functions of instantaneous voltages and can be represented using equation (3.1), however, the currents can not be predicted using equation (3.6). With similar assumption of leakage free gate oxide and negligible recombination current, the first order gate ( $i_{g1}$ ) and substrate ( $i_{b1}$ ) currents are no longer zero. They are given at any location x along the channel by the gate ( $q_q$ ) and bulk ( $q_b$ ) charge densities as:

$$i_g(x,t) = \frac{d}{dt}q_g(x,t)$$

(3.7)

$$i_b(x,t) = \frac{d}{dt}q_b(x,t)$$

(3.8)

In the quasi-static operation, even though the charge distribution in the channel remains the same, there exists a conducting path between the source and the drain terminals. Charge enters from the source terminal and leaves the drain terminal, which makes channel partition schemes misleading to understand the device physics. It is also challenging to represent the channel charge and compute the first order source ( $i_{s1}$ ) and drain ( $i_{d1}$ ) terminal currents due to two reasons:

- It is unrealistic to consider the charges in the channel as being partitioned between source and drain and

- Charge redistribution causes extra dissipation in the channel.

The unrealistic partition can be resolved by solving for the total charge in the channel instead of separating it into source and drain charges.

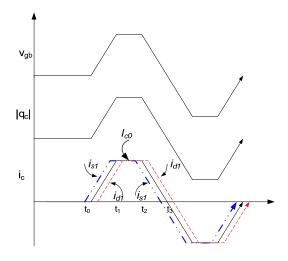

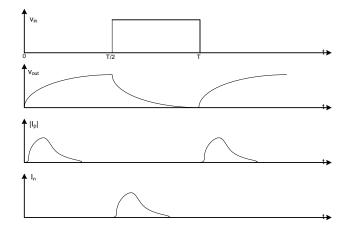

Fig. 3.2 shows a voltage, charge magnitude and current waveforms. The current waveforms show a pair of first order components together with a steady state DC component. The origin of these first order components not predicted by DC operation can be explained using a test quasi-static voltage at the gate terminal.

Figure 3.2: Voltage, Charge and Current Waveforms

A rising input at the gate terminal from time  $t_0$  to  $t_1$  causes the first order currents. Compared to first order drain current ( $i_{d1}$ ), first order source current ( $i_{s1}$ ) is more in this interval as more electrons are pumped from the source terminal and fewer electrons are removed from the drain. Between the intervals  $t_1$  to  $t_2$ , current settles into a steady state value of  $I_{c0}$ . On the other hand, for a falling waveform between the interval  $t_2$  to  $t_3$ , first order drain current becomes more than the first order source current as more electrons are sucked out from the drain terminal. These transients that show up during the switching are also responsible for the channel charge redistribution, which in turn also contributes to power dissipation. To properly analyze the MOS transistors and develop C-V models to be used in circuit simulators, we then need to consider these first order currents together with the steady state values. As mentioned above, the charge redistribution also contributes to the power dissipation, which suggests the presence of first order dissipative and conserved components. We have been able to identify and separate out these components. This is explained in detail in chapter 4 with derivations.

#### 3.3 MODELING EQUATIONS

In order to obtain an analytical solution, the current flow is considered in one dimension parallel to the surface of the device. The equations for both Bulk and SOI processes are developed with some assumptions. The body charge is assumed to have square root dependence for the Bulk process, while the charge expressions for SOI MOSFET assumes that the region under the channel is completely depleted of mobile charges. These simplified assumptions helps us to make use of a linear relationship between the body and the surface potential to compute the energy function without partitioning the channel charge. The linear body-surface relation also provides a simplified charge model and terminal currents. It should be noted that solving the model involves complicated algebraic calculations that are practically impossible without modern mathematics tools like "Mathematica" [3.4].

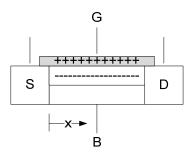

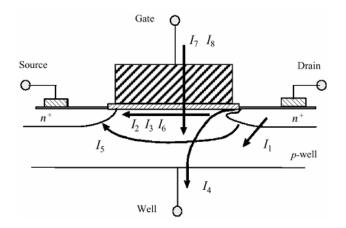

Figure 3.3: Four terminal (a) BULK NMOSFET and (b) SOI NMOSFET Structure

Fig. 3.3 shows NMOS BULK and SOI transistors. The charge per unit length  $(q_c)$  at a position x along the channel is given by

$$q_{c}(x) = -c_{ox}(v_{gb} - v_{fb} - v_{cb}(x) - \phi + q_{b}(x)/c_{ox})$$

(3.9)

Similarly, the bulk charge (back gate) per unit length (  $q_b$  ) at x can be written as

$$q_{b}(x) = \begin{cases} -c_{ox}(k_{1} + k_{2}v_{cb}(x)), & SOI \\ -c_{ox}(k_{1}\sqrt{\phi + v_{sb}} + (Abulk - 1)(v_{cb}(x) - v_{sb})), & BULK \end{cases}$$

(3.10)

where  $v_{fb}$ ,  $v_{gb}$  and  $v_{cb}$  are flat band, gate and channel voltages with respect to the body. *Abulk* [3.13] is the bulk charge coefficient,  $k_1$  and  $k_2$  are body effect coefficients.  $c_{ox} = w (c_{ox}/A)$  is the oxide capacitance per unit length and w is the channel width. The bulk charge is approximated using first two terms of Taylor's expansion around the source terminal  $v_{sb}$ . The linear dependence of back gate for a fully depleted SOI MOSFET is included in the  $k_1$  term. Charge conservation is insured by defining the gate charge per unit length  $q_g$  as

$$q_g = -(q_b + q_c) \tag{3.11}$$

It will be convenient to define the channel charge per unit length at the source (*x*=0)  $q_s$  and the drain (*x*=*L*)  $q_d$  and their time derivatives as

$$q_s = -c_{ox} v_{gst} \text{ and}$$

(3.12)

$$\frac{d}{dt}q_s = -c_{ox}\frac{d}{dt}v_{gst}$$

(3.13)

where

$$v_{gst} = v_{gb} - v_t - v_{sb}$$

(3.14)

In equation (3.14),  $v_t$  is the threshold voltage. The body effect parameters are included by considering the dependence of source terminal on the threshold voltage [3.5, 3.6] by defining

$$v_t(v_{sb}) = \begin{cases} v_{t0} + k_2 v_{sb}, & SOI \\ v_{t0} + k_1 (\sqrt{\phi + v_{sb}} - \sqrt{\phi}), & BULK \end{cases}$$

(3.15)

where

$$v_{t0} = \begin{cases} v_{fb} + k_1 + \phi, & SOI \\ v_{fb} + k_1 \sqrt{\phi} + \phi, & BULK \end{cases}$$

(3.16)

At the drain end,

$$q_d = -c_{ox} v_{gdt} \quad \text{and} \tag{3.17}$$

$$\frac{d}{dt}q_d = -c_{ox}\frac{d}{dt}v_{gdt} \qquad \text{where} \tag{3.18}$$

$$v_{gdt}(x) = \begin{cases} v_{gb} - v_t - v_{sb} - (1 + k_2)(v_{db} - v_{sb}), & SOI \\ v_{gb} - v_t - v_{sb} - Abulk(v_{db} - v_{sb}), & BULK \end{cases}$$

(3.19)

It is assumed that positive current flows into the drain and velocity saturation effects are neglected. The derivative of *Abulk* with  $v_{sb}$  is assumed to be negligible. These assumptions are necessary for energy conservation [3.7] and simplified capacitance equations [3.8]. Even though the equations are simplified, accuracy is not significantly compromised [3.8]. The results are expected to be accurate for a substrate referenced system [3.9]. Drift current at a distance x along the channel can be written as

$$i_{c}(x,t) = q_{c}(x,t)\mu \frac{d}{dx}v_{cb}(x)$$

(3.20)

Charge conservation is assured using the continuity equation

$$\frac{d}{dx}i_{c}(x,t) = -\frac{d}{dt}q_{c}(x,t)$$

(3.21)

where  $q_c = q_{c0} + q_{c1}$

In equation (3.21),  $q_{c0}$  is a function of terminal voltages and  $q_{c1}$  is a function of first order time derivatives of terminal voltages. Using (3.20) in (3.21) gives

$$\frac{d}{dx}[q_c(x,t)\mu\frac{d}{dx}v_{cb}(x)] = -\frac{d}{dt}q_c(x,t)$$

(3.22)

Taking the spatial derivatives of charge per unit length as a function of potential along the channel, equation (3.9) and (3.10) reduces to

$$\frac{d}{dx}q_c(x,t) = C_c \frac{d}{dx}v_{cb}(x); \quad C_c = c_{ox}K; \quad K = \begin{cases} (1+k_2), & SOI\\ Abulk, & BULK \end{cases}$$

(3.23)

Substituting  $\frac{d}{dx}v_{cb}(x)$  in (3.22) and rearranging terms gives

$$\frac{d}{dx}[q_c(x,t)\frac{d}{dx}q_c(x,t)] = -\frac{C_c}{\mu}\frac{d}{dt}q_c(x,t)$$

(3.24)

Equation (3.24) can be solved iteratively to compute the current and the charge in the channel. In terms of the steady state (zero order) charge per unit length at any position x along the channel, equation (3.24) reduces to

$$\frac{d}{dx}(q_{c0}\frac{d}{dx}q_{c0}) = 0$$

(3.25)

Performing integration from source(x=0) to drain (x=L), zero order charge along the channel becomes

$$q_{c0} = -\sqrt{(q_s^2(1-x/L) + q_d^2 x/L)}$$

(3.26)

and the steady state drift current component simplifies to

$$I_{0} = \frac{\mu}{C_{c}} q_{c0} \frac{d}{dx} q_{c0}$$

(3.27)

Equation (3.27) gives the usual equation for static current neglecting velocity saturation, which is shown in Table 1. The first order current and charge can be found by keeping terms of first order in time derivatives in equation (3.24)

$$\frac{d}{dx}(q_{c0}\frac{d}{dx}q_{c1} + q_{c1}\frac{d}{dx}q_{c0}) = -\frac{C_c}{\mu}\frac{d}{dt}q_{c0}$$

(3.28)

Rearranging the terms, equation for the first order channel charge simplifies to

$$q_{c1} = -\frac{C_c}{\mu} \frac{1}{q_{c0}} (\frac{d}{dt} \int (\int q_{c0}[x]dx)dx) + c1x + c0$$

(3.29)

and the first order channel current reduces to

$$i_{c1} = \frac{\mu}{C_c} (q_{c0} \frac{d}{dx} q_{c1} + q_{c1} \frac{d}{dx} q_{c0})$$

(3.30)

Finally, equation (3.30) can be solved to compute the first order channel current at the source  $i_{s1} = i_{c1}$  (*x*=0) and the drain  $i_{d1} = -i_{s1}$  (*x*=L) ends in all regions of operation. We have assumed pinch-off saturation which occurs when  $q_d = 0$ . The drain voltage at saturation can now be estimated by

setting

$$v_{gdt}(x) = 0$$

to get  $v_{ds} \ge \frac{v_{gst}}{K}$  as a boundary between the linear and the saturation regions.

In the cut-off, it is assumed that the channel current is zero, which is made possible by setting both the charge densities  $q_d$  and  $q_s$  to zero. Table 1 summarizes the charge and current in all regions of operations. These results obtained without partitioning the channel charge are in agreement with Lim-Fossum [3.10] and the BSIM capacitive model [3.11, 3.12] which were obtained using Ward's [3.2] partition. Therefore, we have verified that Ward's partition is correct when the voltage dependence of Abulk is ignored.

|            | Linear                         | Saturation       | Cut-Off                  |

|------------|--------------------------------|------------------|--------------------------|

| Conditions | $q_{c}$                        | $q_{c}^{} < 0$   | $q_{_{\mathcal{C}}} = 0$ |

|            | $v_{gdt} > 0$<br>$v_{gst} > 0$ | $v_{gdt} = 0$    | $v_{gdt} = 0$            |

|            | $v_{gst} > 0$                  | $v_{gst} > 0$    | $v_{gst} = 0$            |

| $q_{s}$    | $-c_{ox}v_{gst}$               | $-c_{ox}v_{gst}$ | 0                        |

| $q_d$      | $-c_{ox}v_{gdt}$               | 0                | 0                        |

Table 3.1: NMOS Zero and First Order Charges and Currents

| I <sub>c0</sub> | $\frac{\mu c_{ox}}{2L(1+k_2)} (v_{gst}^2 - v_{gdt}^2)$                                                                                                                              | $\frac{\mu c_{ox}}{2L(1+k_2)}v_{gst}^2$  | 0 |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---|

| i <sub>s1</sub> | $\frac{2c_{ox}L}{15(v_{gdt}+v_{gst})^3} [2v_{gdt}(\frac{d}{dt}v_{gdt})(v_{gdt}^2+3v_{gdt}v_{gst}+v_{gst}^2) + v_{gst}(\frac{d}{dt}v_{gst})(8v_{gdt}^2+9v_{gdt}v_{gst}+3v_{gst}^2)]$ | $\frac{2}{5}c_{ox}L\frac{d}{dt}v_{gst}$  | 0 |

| <sup>i</sup> d1 | $\frac{2c_{ax}L}{15(v_{gdt}+v_{gst})^3} [v_{gdt}(\frac{d}{dt}v_{gdt})(3v_{gdt}^2+9v_{gdt}v_{gst}+8v_{gst}^2) + 2v_{gst}(\frac{d}{dt}v_{gst})(v_{gdt}^2+3v_{gdt}v_{gst}+v_{gst}^2)]$ | $\frac{4}{15}c_{ox}L\frac{d}{dt}v_{gst}$ | 0 |

# **CHAPTER IV**

# **IV. MOSFET POWER**

This chapter discusses the origin of MOS transistor leakage and describes the power computation techniques for conserved and dissipative components without the channel charge partition. The existence of an energy function is also validated. The conserved and dissipative power components then become the basis of conserved and dissipative current components in chapter 5.

The fast scaling of operation frequency for semiconductor integrated circuits that was seen in the last few decades cannot continue. One of the reasons is the increase in power dissipation. Power limits the scaling. The high power dissipation due to small device geometry has thrown off course the roadmap of future development of semiconductor technologies as predicted in the International Technology Roadmap for Semiconductors [4.1].

When the devices are switching rapidly, the power dissipation per unit area goes up causing excessive heating. Unless a sophisticated and expensive cooling system is implemented, the device may no longer be operational. The reality is: we have reached a power limited scaling regime. Scaling now is no longer determined by the device size, but by how much power the chip can dissipate at a particular working frequency. However, the lack of suitable device models to measure this power dissipation has provided a plethora of research avenues. The conventional MOSFET models have some inherent issues and are not consistent for power and energy prediction as they:

• Fail to include the first order power dissipation due to channel charge redistribution,

Give a net non-zero power in the channel that has no physical basis from the terms that should be conserved.

This makes the MOSFET modeling very important going forward into the nanometer regime for low power design techniques and power-aware architectures [4.3]. Given that the accuracy of the simulation depends on the physical representation of the device, it is very important that we have a reliable mathematical model that is able to represent the device behavior. Designers need these accurate models for circuit development.

#### 4.1 SOURCES OF POWER DISSIPATION

There are three sources of power dissipation in the MOS transistor [4.3-4.6]. The first source of power dissipation is due to the transistor switching that is related to the charging and discharging of the external load capacitors. The second source is from the short-circuit power due to the current flow from the supply to the ground. These two dissipations are related to the transitions at the gate [4.7]. The third source is the leakage power. Transistor scaling has reduced the threshold voltage and increased the gate leakage resulting in higher static power. Fig. 4.1 shows all these leakage sources that are taking up the power budget. Some of these sources have dominant effects on the transistor performance in the nano-meter regime [4.7, 4.8].

Figure 4.1: Leakage Current Components [4.5]

| 11 | PN junctions reverse bias current |

|----|-----------------------------------|

| 12 | Subthreshold leakage              |

| 13 | Drain Induced barrier lowering    |

| 14 | Gate-Induced drain leakage        |

| 15 | Punchthrough                      |

| 16 | Narrow width effect               |

| 17 | Gate oxide tunneling              |

| 18 | Hot carrier injection             |

#### 4.2 POWER AND ENERGY MODELING ISSUES

Meyer [4.9] was the first to present a capacitive model. Ward and Dutton [4.10] pointed out the assumed charge non conservation problems in Meyer's model. To solve these problems in transient simulation, they proposed a charge partitioning scheme with a charge conservation constraint. Sheu et al. [4.11] and Chung [4.12] made many improvements later to better derive I-V and C-V characteristics. One of the industry standards, the BSIM capacitive model includes many of these models to estimate the behavior of MOS transistors. The BSIM model assumes that the MOSFET capacitance is an energy storage device and uses the conserved charges (to first order) to predict the currents and voltages at different nodes. The same charge (to zero order) is also used to predict the channel power. This makes the BSIM capacitive a zero order, quasi-static power dissipation model. The model

- Assumes that the first order terms only contribute to energy storage

- Uses channel charge partition scheme and the bulk charge parameter has a non-linear dependence on the source potential.

Both these ideas leave a lot to be desired. First, the dissipative power has some higher order terms due to the charge redistribution. These higher order dissipative components become significant at higher frequencies and modify the total power dissipated in the channel [4.13]. This is explained later in section 4.5. Second, the non-linear dependence of *Abulk* on  $v_{sh}$  does not

~29~

allow the derivation of energy function from all of the conserved components [Appendix A7.2]. These effects causes the BSIM capacitive model to predict a different number for instantaneous power measured from the supply than the power dissipated in the device, clearly a violation of energy conservation principles.

If an analytical closed form solution for the stored energy function is desired using non-reciprocal capacitors, the FET charge equation has to be solved for a linear source dependence of the bulk without the channel charge partition. These inconsistencies make the current BSIM capacitive model non-ideal for energy estimation.

#### 4.3 POWER MEASUREMENT TECHNIQUES

Many models have been suggested for the estimation of power, like using supply current measurements [4.14], input slew dependency [4.15], propagation delay [4.16], short circuit power [4.17] and non-conventional capacitor-based methods [4.18]

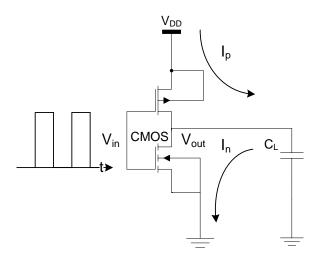

Figure 4.2: Dynamic Power

Fig 4.2 shows one of simplest techniques used to calculate the transistor power consumption. Power is consumed when the gate drives the output  $V_{out}$  to a new value. Assuming that the input  $V_{in}$  changes very fast, only one transistor turns on at a time. When the output goes high, the current flows through the PFET and goes only to the capacitor. The current component that goes down the NFET has been neglected. Similarly when the output settles to a low value, it is assumed that the current goes through the NFET. Though the PFET is not quite turned off yet, the current that is coming through the PFET is neglected.

Figure 4.3: Transient Waveforms

Fig 4.3 shows the transient waveforms. The output looks more like a RC time constant due to the presence of the capacitance, charging up the output from 0 to T/2 and then discharging from T/2 to T. If we look at the corresponding current plots for falling input transient, it is only the PFET that is providing the capacitor current  $I_p$ . For the rising input transient, capacitor current  $I_n$  is through the NFET. It should be noted that the currents mentioned above are the magnitudes of the drain current. The instantaneous power dissipation is then calculated by solving for I and V and multiplying them together. It is also assumed that the capacitors are purely energy storage devices and does not contribute to net power dissipation. Hence, during the falling input transition, power dissipation is only in the PFET. Similarly during the rising input transition, power dissipation is only in the NFET.

Using these assumptions, the average power  $\overline{P_{c0}}$  for a complete cycle is computed using

$$\overline{P_{c0}} = \frac{1}{T} \begin{bmatrix} T/2 \\ \int U_p V_{DSp} dt + \int U_p V_{DSn} dt \end{bmatrix}$$

(4.1)

where  $V_{DSp}$  and  $V_{DSn}$  are the outputs at the PFET and NFET respectively. During the falling transition as PFET charges the capacitor, actual positive current flows from the device to the capacitor. This makes the PFET drain current  $I_p$  negative.

$$I_p = -(C_L \frac{dV_{out}}{dt})$$

(4.2)

where  $C_{L}$  is the output load. The corresponding output voltage at the PFET,  $V_{\rm DSp}$  becomes

$$V_{DSp} = V_{out} - V_{DD} = -(V_{DD} - V_{out})$$

(4.3)

where  $V_{DD}$  is the supply voltage. From (4.2) and (4.3), power dissipated in the PFET,  $P_{PFET}$  is computed using

$$P_{PFET} = \int_{0}^{T/2} I_p V_{DSp} dt$$

(4.4)

Similarly, the current through the NFET,  $I_n$  is negative of the capacitive current.

$$I_n = -(C_L \frac{dV_{out}}{dt})$$

(4.5)

and the corresponding output voltage,  $V_{\rm DSn}$  is

$$V_{DSn} = V_{out} \tag{4.6}$$

From (4.5) and (4.6), power dissipated in the NFET,  $P_{\rm NFET}$  is given by

$$P_{NFET} = \int_{T/2}^{T} I_n V_{DSn} dt$$

(4.7)

The average power,  $\overline{P_{c0}}$  for a complete cycle is estimated using equations (4.4) and (4.7) as

$$\overline{P_{c0}} = \frac{1}{T} [P_{PFET} + P_{NFET}]$$

(4.8)

Substituting  $I_n$ ,  $I_p$ ,  $V_{DSn}$  and  $V_{DSp}$  in equation (4.8), the average power equation reduces to

$$\overline{P_{c0}} = \frac{1}{T} \begin{bmatrix} T/2 \\ \int \\ 0 \end{bmatrix} C_L \frac{dV_{out}}{dt} (V_{DD} - V_{out}) dt + \int_{T/2}^{T} (-C_L \frac{dV_{out}}{dt}) V_{out} dt]$$

(4.9)

Because of the fact that the transistor currents are related to the charging and discharging of the currents of the capacitor, the power integrals can be replaced from integrals over dt to an integral over dv. This gives a closed form expression for the dynamic power independent of i(t) and v(t).

$$\overline{P_{c0}} = f C_L V_{DD}^2$$

(4.10)

There are, however, some issues in regards to the dynamic power equation (4.10). These issues are:

- The MOS channel is not purely an energy storage device and has no energy function.

For an energy function to exist, second order partials have to be equal. This is shown in the Appendix [A4.5-A4.7].

- The MOS capacitors dissipate power and the trans-capacitive terms used in the charge model includes both dissipative and conserved components. Therefore, it is not appropriate to look at the change in the energy of the external load capacitor  $C_L$  in the channel as a true measure of power. Dynamic power predicted using equation (4.10) is in fact an easy way of computing the zero order power by looking at the change in energy during charging and discharging of external capacitors.

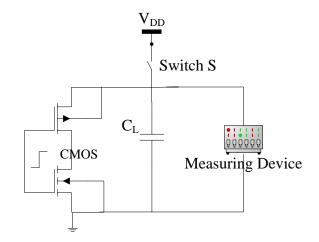

Fig. 4.4 shows another capacitor based technique used for power measurement. In this type of power measurement, switch S is closed and the load capacitor  $C_L$  is allowed to attain the supply voltage  $V_{DD}$ . The switch is then opened and the CMOS gate is allowed to undergo a transition. This causes some energy consumption in the circuit, which is captured by the measuring device as a decrease in supply voltage ( $\Delta v$ ). Energy dissipated in the circuit can now be estimated using

$$Energy = \frac{1}{2}C_L V_{DD}^2 - \frac{1}{2}C_L (V_{DD} - \Delta v)^2$$

(4.11)

where  $\frac{1}{2}C_L \Delta v^2$  is the energy consumed by the circuit. This method of energy prediction is very

accurate [4.18]. However, this energy prediction is not possible during the design phase. Hence,

there is a need for a verification tool that can simulate the real world behavior of the transistor during the design phase.

Figure 4.4: Capacitor based Power Measurement Technique

This makes the next and subsequent sections of power derivation one of the most important findings of our research, where the energy function is derived from a symmetrical charge conserving FET models. Before going through the derivation, it however, becomes important to discuss the extra source of transistor power dissipation that was not included in section 4.1. It also becomes important to check the validity of the quasi-static approximation in the model derivation.

Figure 4.5: Power Dissipation in MOS Transistor

When the gate undergoes a transition, from  $v_{ss}$  to  $v_{dd}$  or  $v_{dd}$  to  $v_{ss}$ , the resistive drop (IR) and the charge redistribution cause the power dissipation in the channel. Usually, the zero order steady state current is used to determine the power dissipation. The additional power dissipation from

the channel charge redistribution is ignored. This is because, in the quasi-static model, charge redistribution is assumed to happen instantaneously with no propagation delays. However, the channel charge density still changes as an indirect function of time through the dependence on time varying terminal voltages. This allows the use of the quasi-static model to predict the charge redistribution and the associate power dissipation as long it satisfies  $t_R > 20 T_0$  [4.19] where  $t_R$  is the waveform rise time and  $T_0$  is the time taken by electrons to reach the drain from the source terminal (transit time). Moreover, the conventional charge model is based on the assumption that the MOSFET capacitors do not contribute any net power dissipation in the channel. But, as shown in Appendix [A4], it is not the case. The channel capacitances are not energy conserving. They do have some power dissipative terms due to the charge redistribution in the channel. These higher order dissipative terms become significant at higher frequencies, which make it necessary to include their effects on total power for efficient power dissipation prediction.

### 4.4 POWER EQUATIONS

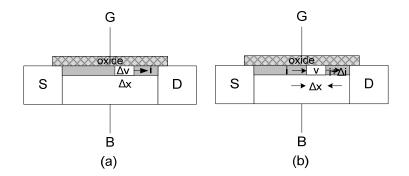

Fig: 4.6: MOSFET Channel Power Calculation

Fig 4.6 shows a MOS device. Considering a slice of thickness  $\Delta x$ , MOS channel can be thought of having two power components, due to:

• Fig. 4.6 a: The current i(x) flowing through the slice of thickness  $\Delta x$  having a potential  $\Delta v$

, which looks like a series resistance and results in the power dissipation of  $i\Delta v$ .

Fig. 4.6b: The rate of change of charge that is building in the slice due to the difference in current Δ*i*. This power change *v*Δ*i* is the energy stored in the charge at the potential *v*(*x*).

The instantaneous power going into the transistor channel  $P_c$  can then be estimated using

$$P_{c} = \int_{0}^{L} \frac{d}{dx} (i_{c}(x)v_{cb}(x)) dx = \int_{0}^{L} (\frac{d}{dx}i_{c}(x))v_{cb}(x)] dx + \int_{0}^{L} i_{c}(x)(\frac{d}{dx}v_{cb}(x))] dx$$

(4.12)

where the first integral represents change in stored energy and second term represents power dissipation. Keeping non-zero terms to first order in time derivatives, equation (4.13) can be expanded as:

$$P_c = P_{c0} + P_{c1,diss} + P_{c1,cons}$$

where

$$P_{c0} = \int_{0}^{L} I_{co}(\frac{d}{dx}v_{cb0}(x)) dx$$

[Appendix 4.1] (4.13)

$$P_{c1,diss} = \int_{0}^{L} i_{c1} (\frac{d}{dx} v_{cb0}(x)) dx$$

[Appendix 4.2] (4.14)

$$P_{c1, cons} = \int_{0}^{L} v_{cb0}(\frac{d}{dx}i_{c1}) dx$$

[Appendix 4.3] (4.15)

The total instantaneous power P into the transistor is the sum of channel power  $P_c$  and gate

power

$$P_{g1,cons}$$

.

$P = P_c + P_{g1,cons}$

where the gate power is

$$P_{g1,cons} = i_{g1}v_{gb} \tag{4.17}$$

(4.16)

where  $i_{g1}$  (Appendix: A3.3) is the first order gate current component.

Equation (4.13) represents the usual zero order power dissipation. Equation (4.14) represents the first order power dissipation due to the trans-capacitive transient current components and equation (4.15) represents the first order conserved power in the channel. Since the gate power estimated in equation (4.17) is assumed to be purely reactive and leakage free, it becomes necessary to add its contribution together with the conserved components from the channel to obtain a closed form solution for the stored energy function. Table 2 summarizes the power components and Appendix (A4) shows the derivation of these equations. We have used  $v_{gbt0} = v_{gb} - v_{t0}$ .

| Power                  | Linear Region                                                                                                                                                                                                         | Saturation                                                     | Cut-off |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------|

|                        |                                                                                                                                                                                                                       | Region                                                         | Region  |

| <i>P</i> <sub>c0</sub> | $\frac{\mu c_{ox}}{2LK} v_{ds} (v_{gst}^2 - v_{gdt}^2)$                                                                                                                                                               | $\frac{\mu c_{ox}}{2LK} v_{ds} v^2_{gst}$                      | 0       |

| P <sub>c1,diss</sub>   | $\frac{c_{ox}L}{30(v_{gdt}+v_{gst})^3}v_{ds}(v_{gst}-v_{gdt})[3v_{gdt}^2\frac{d}{dt}v_{gdt} + 3v_{gst}^2\frac{d}{dt}v_{gst} + 7v_{gdt}(\frac{d}{dt}v_{gdt} + \frac{d}{dt}v_{gst})v_{gst}]$                            | $\frac{\frac{c}{\partial x}L}{10} v_{ds} \frac{d}{dt} v_{gst}$ | 0       |

| P <sub>c1,cons</sub>   | $\frac{-\frac{c_{ox}L}{6K}[-3(v_{gdt}\frac{d}{dt}v_{gdt}+v_{gst}\frac{d}{dt}v_{gst})+}{4(v_{gdt}\frac{d}{dt}v_{gdt}(v_{gdt}+2v_{gst})+v_{gst}\frac{d}{dt}v_{gst}(2v_{gdt}+v_{gst}))(v_{gbt}0)}{(v_{gdt}+v_{gst})^2}]$ | $-\frac{c_{ox}L}{6}\frac{d}{dt}v_{gst}$ $(v_{db}+3v_{sb})$     | 0       |

| Table 4. | 1: Power | Equations |

|----------|----------|-----------|

|----------|----------|-----------|

### 4.5 ENERGY FUNCTION CALCULATION

Energy is defined as *the capacity to do work*. In a MOSFET, work is done to transfer the charge from the source to the drain terminal. However, energy prediction is very tricky for MOS devices

as it is difficult to separate the charging (effective work) and the dissipative components of the electrons. This makes it difficult to predict how much energy is lost in the channel and how much energy is used as the effective work. To make the matter worse, the bias at the gate terminal forces these charge movements.

For the model derivation, the gate is assumed to be leakage free. It is also assumed that there is no net charge transfer from the gate to the channel. However, energy is still supplied from the gate to drive the channel charges. It then becomes necessary to add the contribution from the gate together with the channel charges. As these charges are conserved over a complete cycle, it is possible to derive a closed form analytical solution for an energy function from these conserved charges. The separation of conserved components make it possible to estimate total power dissipation by leaving out energy storage terms that do not contribute to power dissipation, making the solution simple, straightforward and computationally efficient.

The conserved component of channel power was given by equation (4.15). It can also be written as:

$$P_{c1,cons} = \frac{dE}{dt} = \sum_{V} \frac{\partial E}{\partial V} \frac{dV}{dt}$$

(4.18)

Equation (4.18) can be expanded to represent channel power in the form of energy as

$$P_{c1,cons} = \frac{\partial E_c}{\partial v_{gb}} \frac{dv_{gb}}{dt} + \frac{\partial E_c}{\partial v_{db}} \frac{dv_{db}}{dt} + \frac{\partial E_c}{\partial v_{sb}} \frac{dv_{sb}}{dt}$$

(4.19)

where  $E_c$  is some function of voltages  $v_{gb}$ ,  $v_{sb}$ ,  $v_{db}$ . Since the channel receives energy from the gate during switching transient, it can be shown [APPENDIX A4.5] that the energy from the channel alone is not conserved. Hence an energy function is not possible in equation (4.19).

Taking similar approach, gate power is represented using

$$P_{g1,cons} = \frac{\partial E_g}{\partial v_{gb}} \frac{dv_{gb}}{dt} + \frac{\partial E_g}{\partial v_{db}} \frac{dv_{db}}{dt} + \frac{\partial E_g}{\partial v_{sb}} \frac{dv_{sb}}{dt}$$

(4.20)

where  $E_g$  is also some function of  $v_{gb}$ ,  $v_{sb}$ ,  $v_{db}$ . Since gate is supplying the energy to the channel, it can also be shown that the gate alone has no energy function [APPENDIX A4.6]. An Energy function is possible only when the conserved components are combined [APPENDIX A4.7].

$$P_{cons} = P_{g1,cons} + P_{c1,cons}$$

(4.21)

Using equations (4.19), (4.20) and (4.21)

$$\frac{\partial E}{\partial v_{jb}}(v_{gb}, v_{sb}, v_{db}) = \frac{\partial E_c}{\partial v_{jb}} + \frac{\partial E_g}{\partial v_{jb}}; j = g, s, d$$

(4.22)