# FRONT END OF A 900MHz RFID FOR BIOLOGICAL

## SENSING

By

# **REHAN AHMED**

Master of Science in Electrical and Computer Engineering Oklahoma State University Stillwater, Oklahoma 2009

> Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY December, 2015

# FRONT END OF A 900MHz RFID FOR BIOLOGICAL

SENSING

Dissertation Approved:

Dr. Chriswell G. Hutchens

Dissertation Adviser

Dr. James E. Stine, Jr.

Dr. Weihua Sheng

Dr. R. Russell Rhinehart

## ACKNOWLEDGEMENTS

I would like to first thank my advisor Dr. Chris Hutchens for giving me this great opportunity to work toward a Ph.D degree under his supervision. It has been a privilege to do research under his guidance. His constant guidance and encouragement provided me a clear path for my study, and I have truly enjoyed working with him over these years of acquiring knowledge and wisdom that will help me in future. I am equally grateful to my committee members. Dr. James E. Stine, Dr. Weihua Sheng and Dr. R. Russell Rhinehart

I feel very fortunate to have worked together with all my colleagues Srinivasan Venkatarman, Ran liao, Guanglei An, Zhe Yuan, Aniket, Kanishka de, Arpit and many thanks goes to them.

At last I want to thank my parents Borhan Uddin Ahmed and Luthfanessa Ahmed and my sister Shabnam Ahmed for their love and support.

Acknowledgements reflect the views of the author and are not endorsed by committee members or Oklahoma State University.

## Name: REHAN AHMED

## Date of Degree: DECEMBER, 2015

## Title of Study: FRONT END OF A 900MHz RFID FOR BIOLOGICAL SENSING

## Major Field: ELECTRICAL ENGINEERING

Abstract: This thesis presents the front end of a 900MHz passive RFID for biological sensing. The components blocks of the front end consist of power harvester, switch capacitor voltage regulator, phase lock loop and a modulator and demodulator. As the RFID is passive so the power resource is limited hence the main focus while implementing all the block was low power and high efficiency power conversion. All the individual block were optimized to provide maximum efficiency. For the harvester to achieve high efficiency and high output voltage a design approach is discussed by which the device sizes are optimized and the values of the matching network components are solved. The efficiency achieved with this approach is 34% while supplying  $74\mu A@1.2V$ .

The switch capacitor voltage regulator would supply power to the digital core of the RFID, which will operate at subtheshold or moderate inversion. The switch capacitor implemented in this work is a adaptive voltage regulator, as I intend to use the dynamic supply voltage scaling technique to compensate for the reduction in reliability of performance of the circuit due to variation of  $V_{TH}$  across process due to random doping effects and temperature in subthreshold.

The phase lock loop (PLL) block in this front end provide the system clock synchronized with the base station to all the backend blocks like the digital controller, memory, and the analog to digital converter ADC and the switch capacitor voltage regulator. The PLL is a low power with jitter of 24nsec and is capable of clock data recovery from EPC gen 2 protocol format data and consumes  $3\mu$ W of power

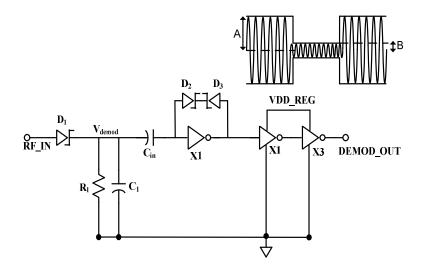

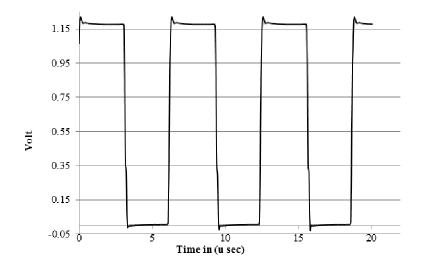

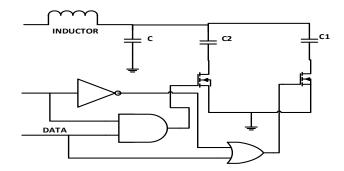

Finally a ultra low power AM (amplitude modulation) demodulator is presented which is consumes only 100nW and is capable of demodulating a double-sideband amplitude modulated (DSB-AM) signal centered at 900MHz and the modulating frequency is 160KHz. The demodulator can demodulate signal having as low as -5dBm power and 50% modulation index. The modulation for transmitting signal is achieved by BPSK(back scatter phase shift keying).

# TABLE OF CONTENTS

| Chapter                                                                 | Page |

|-------------------------------------------------------------------------|------|

| I. INTRODUCTION                                                         | 1    |

| 1.1 Introduction                                                        | 1    |

| 1.1.1 Active RFID                                                       |      |

| 1.1.2 Passive RFID                                                      | 2    |

| 1.2 Research objective                                                  | 3    |

| 1.3 Dissertation Organization                                           |      |

| II. POWER HARVESTER                                                     | 8    |

| 2.1 Introduction                                                        | 8    |

| 2.1.1 Near field                                                        |      |

| 2.1.2 Far field                                                         | 9    |

| 2.2 Objective of far field harvester design approach                    |      |

| 2.3 Matching network                                                    |      |

| 2.3.1 L matching network                                                |      |

| 2.4 Harvester Design                                                    | 20   |

| 2.4.1 Harvester design optimization                                     |      |

| 2.5 Results and discussion                                              |      |

| III. ADAPTIVE SWITCH CAPACITOR POWER REGULATOR                          |      |

| 3.1 Introduction                                                        |      |

| 3.2 Critical path monitoring                                            |      |

| 3.2.1 Synchronizer                                                      |      |

| 3.2.2 Critical path replicas                                            | 40   |

| 3.2.3 Time to digital converter                                         |      |

| 3.2.3 Controller                                                        | 40   |

| 3.2.3 CPM role                                                          | 40   |

| 3.3 DC-DC power converter                                               | 43   |

| 3.3.1 Linear regulator                                                  |      |

| 3.2.2 Switch mode power converter                                       |      |

| 3.3.2 a) Switch inductor converter                                      | 47   |

| 3.3.2 b) Switch capacitor converter                                     | 48   |

| 3.4 Design consideration for implementation of scalable switch capacito |      |

|                                                                         | 49   |

| Chapter                                                             | Pag    |

|---------------------------------------------------------------------|--------|

| 3.4.1 Output voltage                                                | 50     |

| 3.4.2 Efficiency                                                    | 50     |

| 3.4.3 Output voltage ripple                                         | 56     |

| 3.4.4 Number of capacitor                                           | 57     |

| 3.5 Step-down voltage conversion using switch capacitor DC-DC conve | rter57 |

| 3.5.1 Implementation of different converter gain                    | 60     |

| 3.6 Voltage regulation technique                                    | 63     |

| 3.6.1 Pulse frequency modulation                                    | 64     |

| 3.6.2 Converter gain control                                        |        |

| 3.6.3 Switch width modulation                                       | 64     |

| 3.6.4 Pumping capacitor modulation                                  |        |

| 3.7 Voltage control circuit                                         | 65     |

| 3.7.1 Controller algorithm                                          |        |

| POWER CONVERTER                                                     |        |

| 4.1 Optimization of power loss                                      | 60     |

| 4.2 Simulation results                                              |        |

| V. PHASE LOCK LOOP                                                  | 78     |

| 5.1 Introduction                                                    | 78     |

| 5.2.1 Phase frequency detector                                      | 80     |

| 5.2.2 Charge pump                                                   |        |

| 5.2.3 Loop filter                                                   |        |

| 5.2.4 Voltage controlled oscillator                                 |        |

| 5.3 Loop characteristics                                            |        |

| 5.4 Noise analysis of PLL                                           |        |

| 5.5 Clock data recovery circuit                                     |        |

| 5.5.1 CDR operation                                                 |        |

| 5.6 Lock circuit                                                    |        |

| 5.7 Results                                                         |        |

| 5.8 Conclusion                                                      | 96     |

| VI. DEMODULATOR AND MODULATOR                                       | 97     |

|                                                                     | 07     |

| 6.1 Introduction                                                    | 9/     |

| <ul><li>6.1 Introduction</li><li>6.2 Demodulator</li></ul>          |        |

| VI. CONCLUSION                                                 | 102 |

|----------------------------------------------------------------|-----|

| REFERENCES                                                     | 105 |

| APPENDICES                                                     | 111 |

| Appendix A. MATLAB program for rectifier                       | 111 |

| Appendix B. Switch capacitor power loss optimization in MATLAB | 115 |

# LIST OF TABLES

| Table     |                                                                 | Page |

|-----------|-----------------------------------------------------------------|------|

| Table 1.1 | Some of the published RFID tag features                         | 4    |

| Table 2.1 | Power budget for the micro neural RFID                          | 11   |

| Table 2.2 | Efficiency of the Harvester at different width of the rectifier | 30   |

| Table 2.3 | Comparison of various RF_DC architectures                       | 31   |

| Table 3.1 | Control output and V <sub>ref</sub> selected                    | 43   |

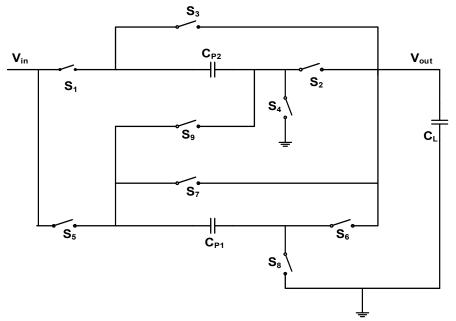

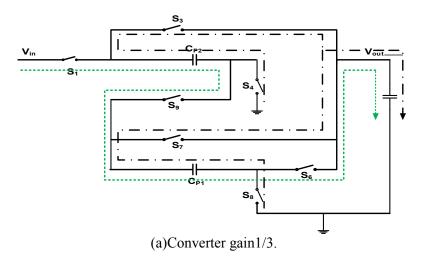

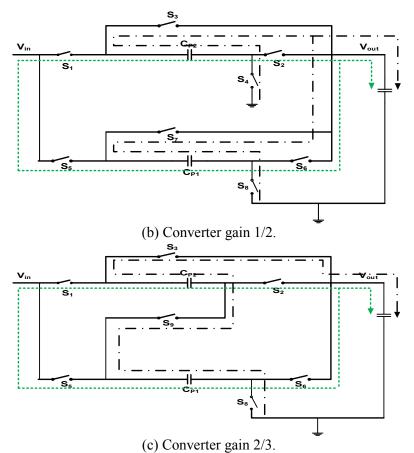

| Table 3.2 | Switch control signal for all the CGs in figure 3.15            | 63   |

| Table 4.1 | Coefficients value for different converter gains                | 71   |

| Table 5.1 | The value of the different PLL parameter                        | 88   |

| Table 5.2 | Measured Jitter                                                 | 95   |

| Table 5.3 | Measured PLL power consumption                                  | 95   |

| Table 5.4 | Measured PLL lock time                                          | 96   |

| Table 6.1 | Comparison of present demodulator with other similar works      | 100  |

|           |                                                                 |      |

# LIST OF FIGURES

# Figure

# Page

| Figure 1.1  | RFID system working principle                                                        | 3   |

|-------------|--------------------------------------------------------------------------------------|-----|

| Figure 1.2  | Block diagram of the total RFID system                                               | . 6 |

| Figure 2.1  | Three different matching network Block diagram of the total RFID                     | .13 |

| Figure 2.2  | The L matching network adopted allow to exploit circuit parasitic                    |     |

| -           | constructively                                                                       | .15 |

| Figure 2.3  | Low-pass L matching network with inductor and capacitor resistance                   |     |

|             | shown explicitly                                                                     | .16 |

| Figure 2.4  | Different voltage rectifier                                                          |     |

| Figure 2.5  | Schematic of one stage modified Dickson Charge pump                                  | .22 |

| Figure 2.6  | fT versus VGS plot for a minimum length and different width                          |     |

|             | geometry transistor                                                                  |     |

| Figure 2.7  | Rectifier current waveform in steady state from MATLAB                               | 25  |

| Figure 2.8  | Plot of harmonic efficiency $\Delta i/\Delta P$ vs the component (harmonic)          |     |

|             | number                                                                               | .26 |

| Figure 2.9  | Nth stage of the rectifier where Cp is the sum of all the parasitic capacitor        | .25 |

| Figure 2.10 | Rin versus transistor width Block diagram of the total RFID                          |     |

| Figure 2.11 | Q factor of the versus the transistor width                                          |     |

| Figure 2.12 | Efficiency n vs NMOS width from Matlab model and cadence simulation                  | .29 |

| Figure 2.13 | Vout vs $I_L$ plot with $P_{in}$ = -6dBm                                             | .32 |

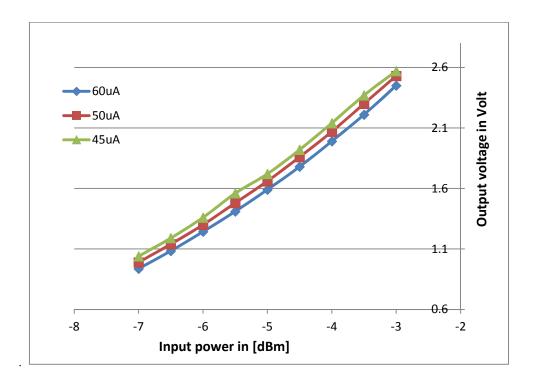

| Figure 2.14 | Vout vs Input power for different load current                                       |     |

| Figure 2.15 | Layout of the harvester with matching cap and LDOs                                   | .32 |

| Figure 3.1  | Plot of $I_D$ vs $V_{GS}$ at constant $V_{DS}$ =800mV for NMOS of four different     |     |

| -           | die,W/L=220nm/180nm at room temperature                                              | .35 |

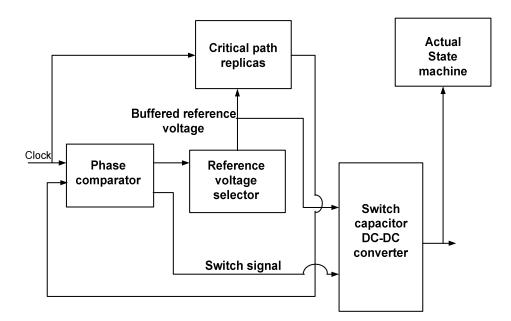

| Figure 3.2  | Block diagram of the adaptive voltage regulation process                             | .38 |

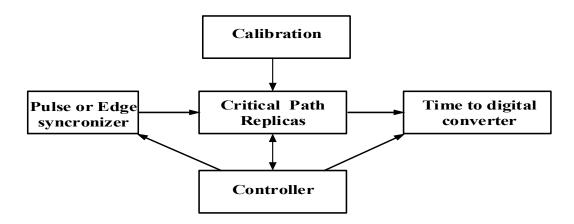

| Figure 3.3  | Block diagram of critical path monitoring system                                     |     |

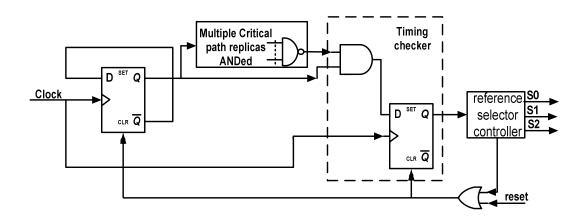

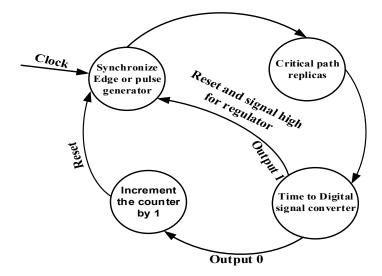

| Figure 3.4  | Schematic of critical path monitoring circuit                                        | .41 |

| Figure 3.5  | State diagram of the critical path monitoring circuit                                | .41 |

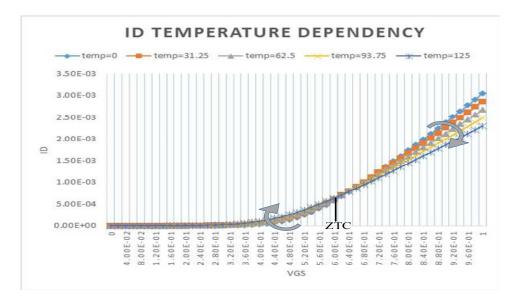

| Figure 3.6  | Id dependency on temperature for subthreshold and velocity saturation                | .42 |

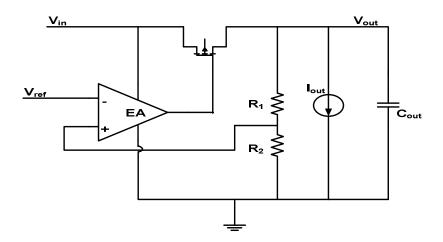

| Figure 3.7  | Low dropout Linear regulator                                                         | .45 |

| Figure 3.8  | a)Power stage topology of Switch mode buck b) Power stage topology of 2-to           |     |

|             | switched capacitor converter                                                         | .47 |

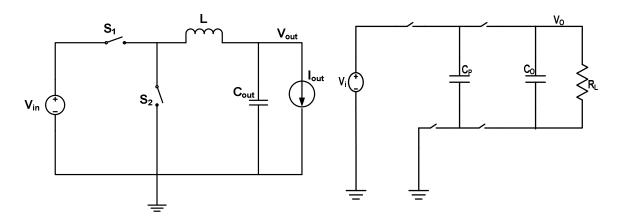

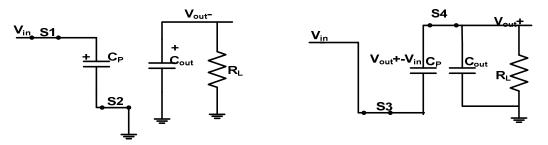

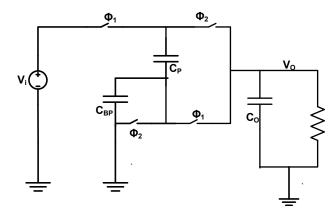

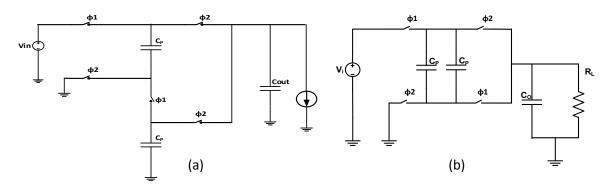

| Figure 3.9  | Switch Capacitor of CG=1/2                                                           |     |

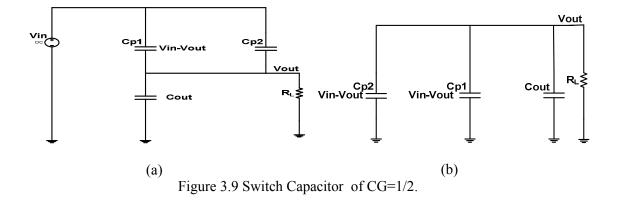

| Figure 3.10 | Power loss only due to switching loss for CG 1/2 configuration                       |     |

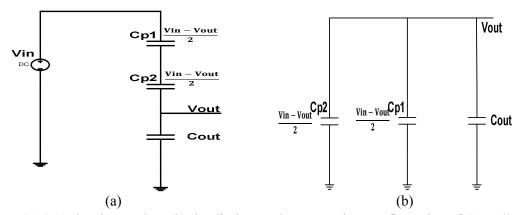

| Figure 3.11 | Charge states before and after the charge redistribution between $C_P$ and $C_{out}$ | 54  |

# Figure

| Figure 3.12                | A 2:1 SC converter with bottom plate parasitic capacitor                                                                                          | 56 |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

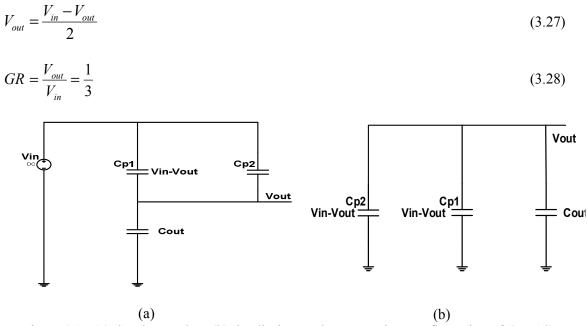

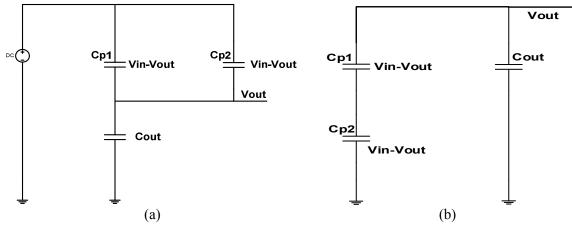

| Figure 3.13                | a)regular series parallel topology for CG 1/2 b)improved series parallel topol for CG 1/2.                                                        |    |

| Figure 3.14                | (a) the charge phase(b) the discharge phase capacitor configuration of GR=1/3                                                                     | 60 |

| Figure 3.15                | (a) the charge phase(b) the discharge phase capacitor configuration of $GR=1/2$                                                                   | 61 |

| Figure 3.16                | (a) the charge phase(b) the discharge phase capacitor configuration of GR=2/3                                                                     | 62 |

| Figure 3.17<br>Figure 3.18 | Switch capacitor power stage with reconfigurable multiple step-down GRs .<br>Charge and discharge path of the multiple GR with the reconfigurable | 65 |

| 1 igule 5.10               | Sc power stage                                                                                                                                    | 63 |

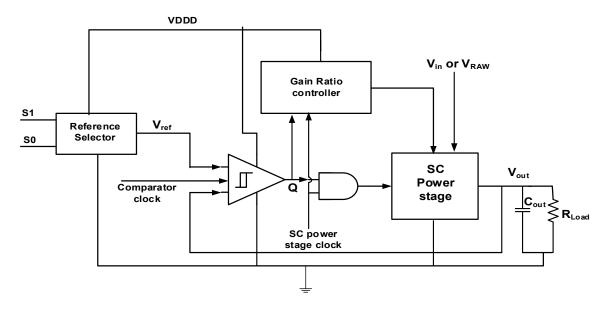

| Figure 3.19                | Block diagram of the control circuit                                                                                                              | 66 |

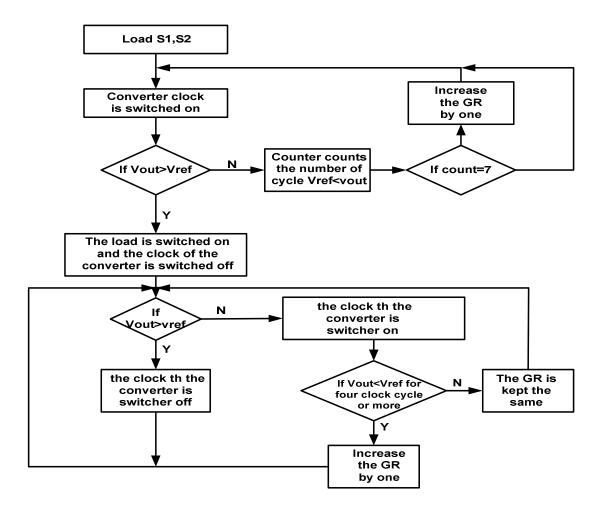

| Figure 3.20                | Control algorithm of the converter                                                                                                                |    |

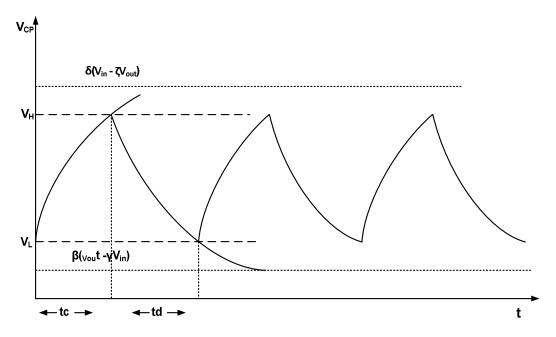

| Figure 4.1                 | Typical voltage wave form observed across pumping capacitor C <sub>P</sub>                                                                        |    |

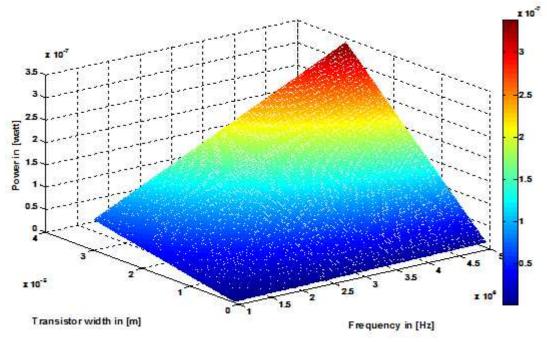

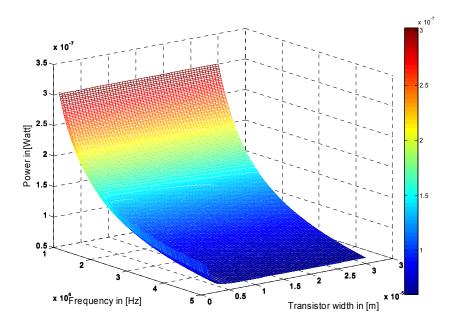

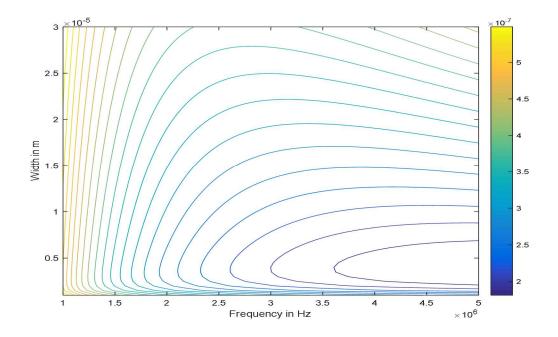

| Figure 4.2                 | Plot for equation 4.13 for CGs 1/2                                                                                                                |    |

| Figure 4.3                 | Contour plot of equation (4.15) which is total power loss with respect to $f_s$ and width W                                                       | 73 |

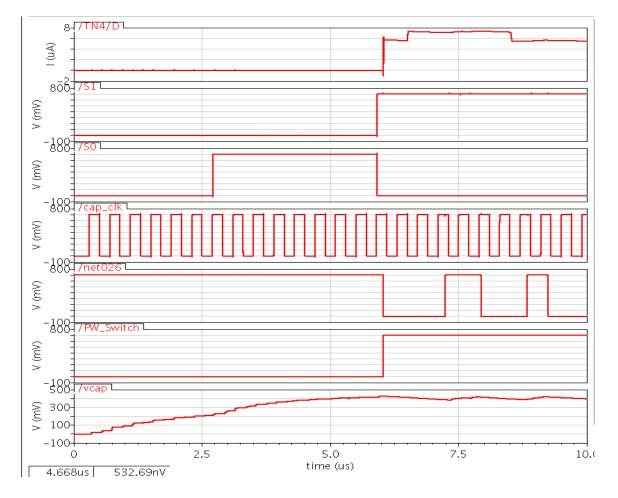

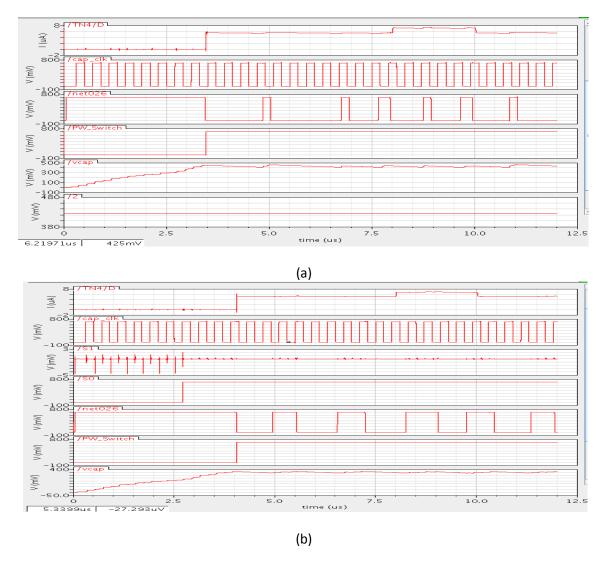

| Figure 4.4                 | Simulation results of the load regulation of the converter                                                                                        | 74 |

| Figure 4.5                 | Simulation results of the a)SS corner b)FF corner load regulation of                                                                              |    |

|                            | the converter                                                                                                                                     |    |

| Figure 4.6                 | Simulation results of the line regulation of the converter                                                                                        |    |

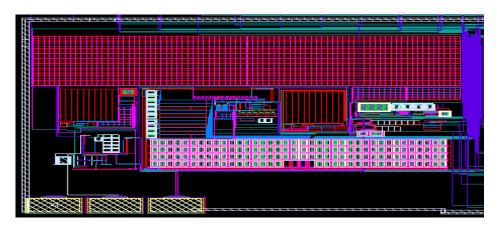

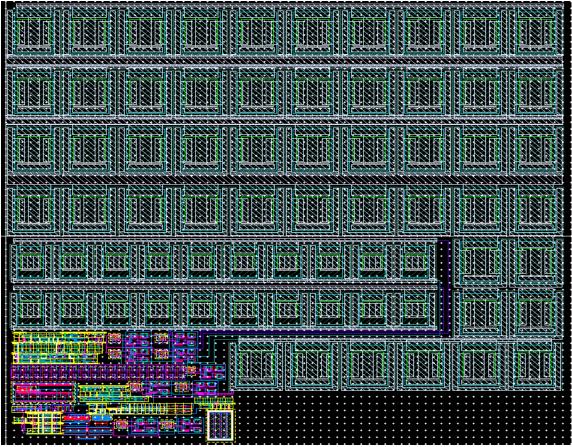

| Figure 4.7                 | Layout of the Switch capacitor voltage regulator                                                                                                  |    |

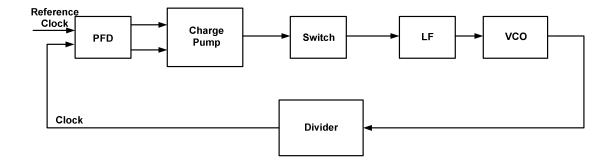

| Figure 5.1                 | Basic PLL block diagram                                                                                                                           |    |

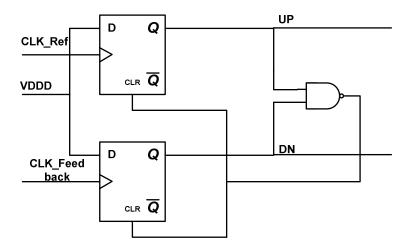

| Figure 5.2                 | Phase frequency detector schematic                                                                                                                |    |

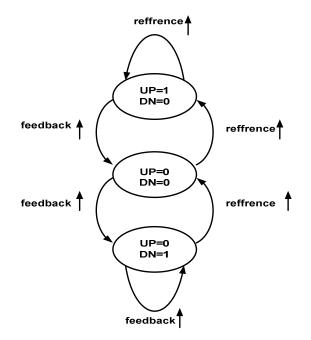

| Figure 5.3                 | Phase frequency detector state diagram                                                                                                            | 81 |

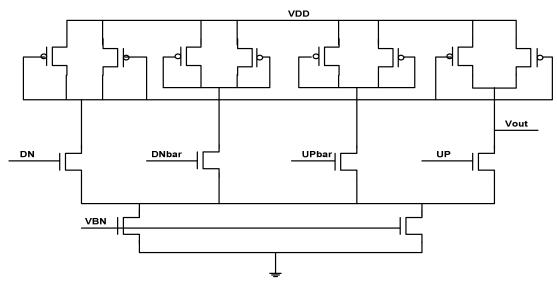

| Figure 5.4                 | Charge Pump Schematic                                                                                                                             | 82 |

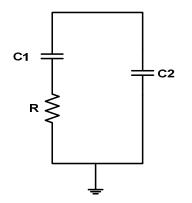

| Figure 5.5                 | Loop filter Schematic                                                                                                                             | 83 |

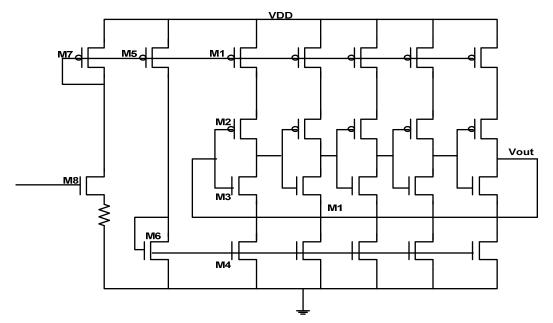

| Figure 5.6                 | Voltage controlled oscillator schematic                                                                                                           |    |

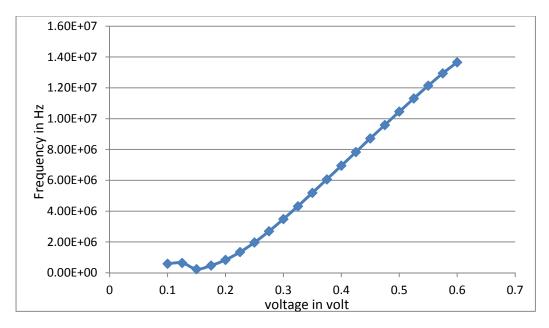

| Figure 5.7                 | Simulated transfer curve of VCO                                                                                                                   | 86 |

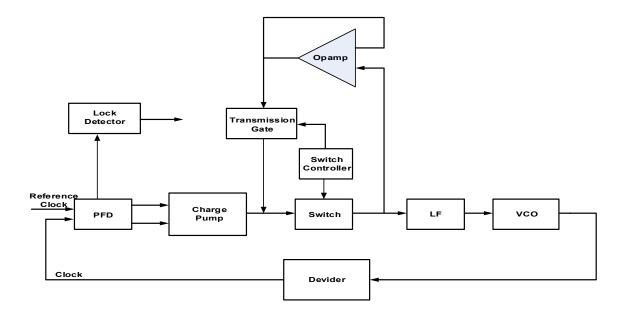

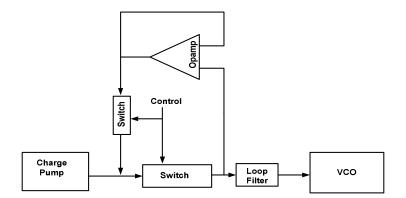

| Figure 5.8                 | Block diagram of the total PLL circuit with the CDR                                                                                               | 90 |

| Figure 5.9                 | Block diagram of switch configuration                                                                                                             | 91 |

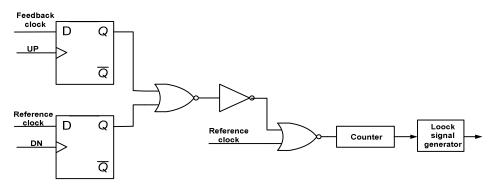

| Figure 5.10                | Block diagram of the Lock detection circuit                                                                                                       | 92 |

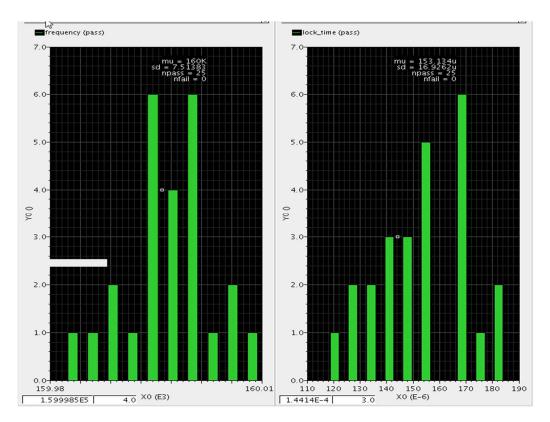

| Figure 5.11                | Montecarlo simulation for the lock time and the frequency deviation                                                                               | 93 |

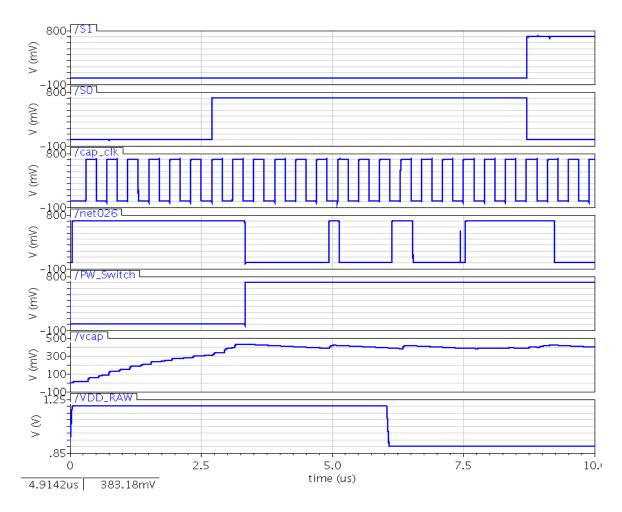

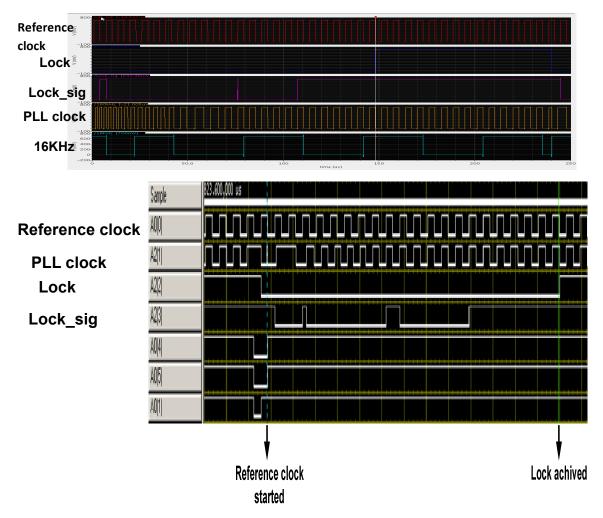

| Figure 5.12                | PLL transient simulation and measurement with reference                                                                                           |    |

| C                          | clock only and no data                                                                                                                            | 94 |

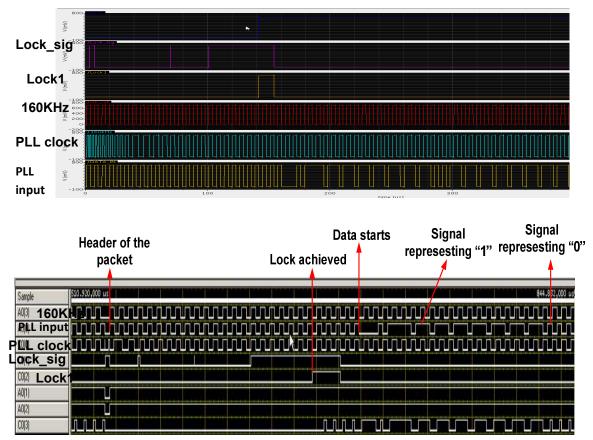

| Figure 5.13                | PLL transient simulation and measurement with reference clock header and then data                                                                | 94 |

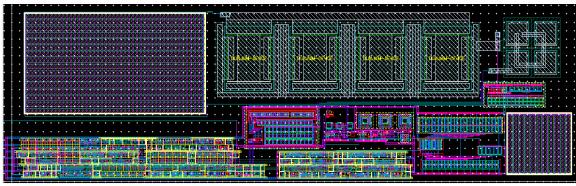

| Figure 5.14                | Picture of PLL layout                                                                                                                             |    |

| Figure 6.1                 | Demodulator schematic                                                                                                                             |    |

| Figure 6.2                 | Modulated signal is of -5dBm Power and 50% modulation                                                                                             |    |

| 1 15010 0.2                | from cadence simulation                                                                                                                           | 00 |

| Figure 6.3                 | Measured result of the demodulator with a modulated signal                                                                                        |    |

| rigure 0.5                 | of -5dBm and modulation index of 50%                                                                                                              | 00 |

|                            |                                                                                                                                                   | "  |

| Figure 6.4 | Modulator Schematic                  |  |

|------------|--------------------------------------|--|

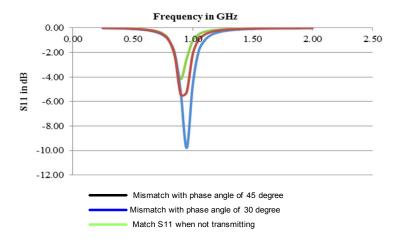

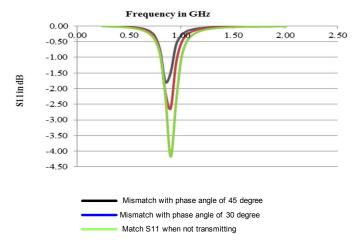

| Figure 6.5 | Simulated S11 When Transmitting a"0" |  |

| Figure 6.5 | Simulated S11 When Transmitting a"1" |  |

## CHAPTER I

#### INTRODUCTION

#### **1.1 Introduction**

The term radio frequency identification is commonly known as RFID refers to a very broad spectrum of devices which are used to automatically identify or gather important information about objects, location and individual without any need of manual intervention and then transmitting that information to a computing system wirelessly. RFIDs have been around since 1970 [1] and until recently were used mainly for object tracking, identification, inventory, and detection of a wide variety of objects [2]. The RFID technology has a number of improvements over the barcode technology as they can be used to track a variety of objects in real time, do not have the constraint of line of sight, they have longer range of operation and can operate and withstand harsh environment. Hence this usage of tracking or identifying are extensively used in supply chain management where low cost passive UHF RFID tags are used to track and keep inventory of a variety of stored items. Due to advancements in technologies including, low power circuit design, innovative circuit architectures and high efficiency antennas, RFIDs can now be combined with a sensory system, which open the path for a variety of applications. Passive smart RFIDs with enhanced signal processing and greater functionality are becoming more accessible to the end user. Emerging smart RFID applications beyond the field of inventory and security are

applied to record storage environment data for temperature sensitive food and medicine during transport [3, 4], continuously monitor health of a structure to detect any damage to verify performance and/or safety of the structure [5], use to gather home and work environment data to make smart energy efficient homes [6, 7]. RFIDs can also be used in medicine and health care where RFID can be used as a implantable or wearable device to collect information or monitor bio-signals wirelessly and unobtrusively. Bio-signals examples include; temperature, blood pressure, heart rate, blood glucose level, and neural activity which can be used to study complex biological systems, effect of various disease and treat or monitor patients [8, 9]. These are some of the many applications playing a critical role in promoting smart passive RFID research and development.

From a power prospective an RFID can be categorized in two basic forms.

- a) Active

- b) Passive

**1.1.1 Active RFID** tags have an integrated power source (internal battery) and behave the same manner as passive devices but with increased performance. The integrated battery increases the cost of the tag, limits the tag life time, limits the size of the tag and also raises safety concern in case of bio-implant. These disadvantages of the active transponders limit the applications where these tags can be used.

**1.1.2 Passive RFID** tags are without an internal power source (battery) and harvest their own power. The source of their power supply can be acoustic, thermal, solar, mechanical or the RF field generated by the reader. Most of the RFIDs used come under this category. Compared to the

former by being battery free these RFIDs are more cost effective, smaller in size, greater in lifespan, and safer for bio-implantation. For sensor network and tracking applications the main advantage of being battery free is the cost, size, and safety. In case of biomedical applications these RFID must have low power consumption, high power conversion efficiency, long life span, and they must be unobtrusive to the user.

#### **1.2 Research Objective**

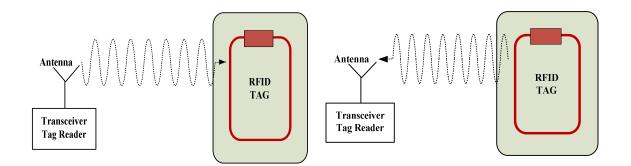

The basic working principle of the RFID is presented in Figure 1.1. The passive RFID system as presented in the figure consists of a Reader and a Tag. The Reader or Transceiver is the unit acting as the master and supplies the RFID tag with energy via the RF field and initiates the communication signals to command the tag to execute the requested action to be executed. The reader control can be either via a computer terminal or a mobile device.

Figure 1.1 RFID system working principle.

The Transponder or Tag act as the identification device, receives and decodes RF signals coming from the reader. In this thesis the front end for a analog dominant passive RFID working at 900MHz is presented to be used for biological sensing. The RFID has the capability of addressability and also follows EPC gen 2 protocol. The RFID will have a band pass amplifier, a

8bit analog to digital converter (ADC), digital controller with memory will be capable of amplifying and processing the bio-signals and communicating with the base station. Since the research published by Karthaus [10], a very influential and widely cited paper in 2003, there has been a tremendous advance in research on passive smart RFIDs. A number of the previous works which has some commonality with this work are reviewed below and summarized in table 1.1

| Author      | Power Consumption | Sensors      | Technology | Clock   |

|-------------|-------------------|--------------|------------|---------|

| Daniel [11] | 9μA@1V            | Amp+8bit ADC | 130µm      | 3MHz    |

| Cho [12]    | 3.5µA@1.5V        | Temperature  | 250µm      | 330KHz  |

| Shen [13]   | 15.4µA@1.2V       | 8bit ADC     | 350µm      | -       |

| Kim [14]    | 15µA@2V           | Temperature  | 250µm      | -       |

| Barret [15] | 2.75uA@1.5V       |              | 130µm      | 1.28MHz |

Table 1.1Some of the published RFID tag features

The work presented by Daniel, et al.[11] is similar to our work, they were the first to implement EPC gen 2 protocol in smart RFID. The RFID was developed for the purpose of biological sensing, having a chopper amplifier of less than 1 KHz bandwidth and 8bit ADC. The sensors presented by Cho, et al. [12] and Kim, et al. [14] respectively were both developed for environmental sensing both the RFIDs had temperature sensor and light sensor in them while the RFID developed by Cho was completely passive; the RFID by Kim was semi-passive. The RFID developed by Shen, et al [13] was also for the purpose of environmental monitoring it contained a temperature sensor and a low power successive approximation 8bit ADC with a sampling rate of 120 KHz however it does not follow the EPC gen 2 protocol. This work presents the front end of a passive smart RFID consisting of RF-DC rectifier, PLL, adaptive switch capacitor voltage regulator, demodulator and modulator. As a smart passive RFID going to be used for biological

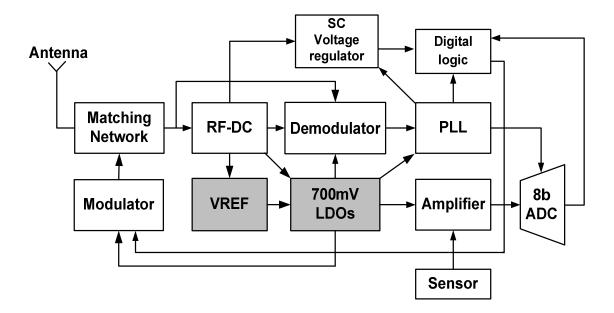

sensing, so must harvest its own power. The main focus in this work is to lower power consumption and achieving higher efficiency and reduce system size. To meet this goal each of the block presented in this circuit were individually optimized so that the efficiency of the total front end is improved and the area minimized. The RF DC rectifier is optimized to maximize the harvested voltage with a single stage to attain greater SNR-BW/Watt while attaining greater power harvest efficiency. With this design approach, the RF front harvester achieved an efficiency of 34% at -6dBm while supplying 70µA@1.2V. The generated DC voltage is unregulated as the incoming RF energy is variable, hence its needs to be regulated and limited before it can be used as the supply voltage for the Analog Front End (AFE) circuitry, logic and communications system blocks the AFE consists of 8bit ADC, Amplifier and voltage references. The power regulation is performed by a LDO for the analog and for the digital block, supply voltage is regulated by an adaptive switch capacitor (SC) voltage regulator. The SC voltage regulator is capable of supplying voltage between 350mV and 500mV. The adapting capability of the SC regulator compensates for the Vth (threshold voltage variation) across process and temperature. While supplying  $6\mu A@400$  mV the SC regulator achieves a conversion efficiency of 86% with +/-12mV ripple. The tag needs to process the data received and the data to be transmitted to the receiver. As a result there must be a digital controller, memory storage and a packet forming pie coder for communication. The clock for the controller and the memory are provided by the PLL. The PLL presented in this work is low power and perform clock and data recovery from pie encoded data while it consumes  $3.1\mu W$  and provides a systems clock frequency of 5.12MHz. Finally for both inbound and outbound communication we have a demodulator and modulator. The demodulator presented operates with as little as -5dBm and a 50% modulation index while consuming only 0.1µW The block diagram of the whole smart RFID is presented in figure 1.2

Figure 1.2 Block diagram of the total RFID system.

#### **1.3 Dissertation Organization**

Chapter 2 discusses the RFID power harvester. The power harvester consists of two significant pieces beyond the antenna, the matching network and the RF to DC rectifier. In this chapter different matching network options and their pros and cons are psesented. After the matching network the rectifier is discussed in detail different types of rectifier are reviewed. The sizing of the rectifying devices is dealt with in detail. Finally simulation results are presented along with comparison of other wireless power harvester works.

Chapter 3 presents the adaptive switch capacitor power regulator which supplies regulated power to the digital controller block. Digital control is designed to operate at or near subthreshold voltage. In this chapter the problems due to the variation of  $V_{th}$  for digital circuitry operating nesr subthreshold are discussed in detail. To resolve the problem of system failure or yield issues due to  $V_{th}$  variation a adaptive switch capacitor voltage regulator is developed and presented. In adaptive voltage regulator first a critical path monitoring circuit to determine the appropriate

supply voltage for the proper functioning of the digital block is presented. After which a over view of the different types of voltage regulator are discussed along with their advantages and disadvantages. Among different types of regulator, the switch capacitor regulator is chosen for it high efficiency.

Chapter 4 presents the optimization process of the power loss in switch capacitor voltage regulator and the different simulation results.

Chapter 5 presents the system phase lock loop (PLL). The primary function of the PLL is to provide data recovery and a system clock to the RFID tag synchronized with the base station clock. As power efficiency is of utmost important for passive RFIDs, the PLL presented is a low power PLL. The different blocks of the PLL; phase frequency detector (PFD), charge pump, low-pass filter, voltage controlled oscillator (VCO), frequency divider is discussed in detail. The PLL clock data recovery circuit capable of extracting the embedded clock from the EPC gen 2 protocol data is also discussed in detail in this chapter. The chapter concludes with the presentation of simulation and measured data of the PLL, Finally power and jitter performance are compared with previous works.

Chapter 6 presents the AM (amplitude modulation) demodulator and the BPSK (binary phase shift keying) modulator of the tag which are the critical block to receiving and transmitting data to and from the reader. As previously mentioned power is a premium. A 100nW demodulator is presented. The BPSK modulator presented does not actively transmit radio signal however, it reflects back the incident energy from the reader by BPSK, this is also known as signal back scattering.

Chapter 6 presents the conclusion of this work and suggests future research areas concentrations.

## CHAPTER II

#### POWER HARVESTER

#### **2.1 Introduction**

In this work we present an implantable smart passive RFID, passives RFID have no internal power and must harvest power to perform any measurement and data transport task. There are various method of power or energy harvesting including solar, mechanical, piezoelectric or acoustic, thermal via the Sebeck effect and finally electromagnetic or electrostatic of radio frequency energy. An implantable neural RFID must be unobtrusive so it needs to be wireless and battery free making it low volume, safe and assists in avoiding repeated surgery for battery replacement. There are three main approaches for wireless power transfer (WPT) a) inductive coupling, b) electrostatic coupling which are used in near-field WPT and c) electromagnetic coupling in for far field WPT. The boundary that separates near field and far field is  $\lambda/2\pi$  where  $\lambda$  is the wavelength of the concerned wave, for 900MHz which is approximately (5.3cm in air or 76mm in neural tissue) [16]. Beyond this boundary the near reactive field degrades rapidly.

**2.1.1 Near Field**: Due to its simplicity and safe, transmission inductive coupling is popular for near field WPT. In inductive coupling the primary and the secondary coil are tuned to resonate at the desired frequency. Coils having identical resonant frequencies are strongly coupled and power is transferred via magnetic resonance induction. The limitation of inductive coupling is that power transfer ratio degrades rapidly beyond  $\lambda/2\pi$  and although this approach works well at close

proximity it requires accurate coplanar alignment. Also the near field harvesters mainly operate in the lower frequency range of tens of megahertz, as lower carrier frequencies results in reduced power loss in the media. As a result of low carrier frequencies the passive LC components required to implement inductive coupling become large in volume and the data rates low as well. Inductive coupling WPT was first commercialized successfully by the medical electronics industry [17, 18]. This harvesting approach is used to charge "pads", cell phones, laptops, as well as medical appliances [19].

2.1.2 Far filed: In case of far field the power is transferred from a transmitting antenna to a receiving antenna via radiating electromagnetic (EM) wave. For far field operation the transmitter typically emits the EM wave in the ISM band 900MHz-950MHz [20] and in case of microwave applications at 2.42GHz or 5.725GHz. WPT by far field does not require precise alignment as in near field. High power levels are limited in the far field approach due to potential health hazard from EM radiation [21], neural tissue heating, and also to avoid interference with other wireless system in proximity. To confine tissue heating within safety power limits transmitted power densities must be limited to ensure less than a 1C° /cm<sup>3</sup> rise in neural tissue. According to power absorption and temperature changes reported by authors Sun Mingui et al .in [22], Ibrahim et al.in [23] and Kennedy in [24]; the safe limit of incident power is 3mW before a rise of 1°C/cm<sup>3</sup> in neural tissue temperature occurs. The maximum average specific absorption rate (SAR) allowed by FCC commissions is 1.6 W/kg in 1 gram of tissue [25, 26]. A study of an ingestible wireless device by Xu and Meng considering conductivity and permittivity of the human body tissue [27] reported an acceptable SAR level of  $0.89W/Kg (\approx 0.89mw/ cm^3)$  for an input power level of 25mW at 430MHz. The work further demonstrates that the deeper the device is implanted in tissue less signal is received by the device. The SAR distribution further illustrates that in close proximity to the transmitting antenna greatest electromagnetic power absorption occurs. All the above studies demonstrate that with RF power along with today's circuit technology the

biomedical community has the capability to develop passive RFIDs capable of harvesting useful power from a far field source and sufficient to perform a variety of functions like temperature, pressure measurement, heart rate, blood glucose level and acquiring neural signal, amplify that and digitizing the acquired signal for finally communication to the base station. Key advantageous of far field harvesting are; small antenna size, high data rates and standoff distance. The efficiency of the harvester is determined by the efficiency of the components including the matching network, the rectifier. The safe power levels determines the maximum distance the harvester can operate. In next section of the far-field electromagnetic energy harvester is addressed.

#### 2.2 Objective of the far field harvester designing approach

Most of the passive RFIDs can be classified into two groups. The first category are used for inventory control, carry out read or write of memory primarily responding to base station or reader interrogation with an identification number and are used mainly for identification or tracking. The power requirements of these RFIDs are a few micro watts [28, 29]. The second category of RFIDs known as smart RFIDs, are capable of sensing, processing and acquiring a signal along with communication sensor data. These RFIDs frequently consists of multiple system blocks beyond power harvesting; they consist blocks for power management, voltage references, amplification, and an Analog to digital converter (ADC) for digitizing the signal. These blocks together are referred as the Analog front end (AFE); they also include a PLL (also near constant current load), digital controller and circuits for in bound and out bound communication (very light loading). The power requirements of smart RFIDs are thus frequently dominated by the (AFE) which require a near constant current and require greater power compared to the first category of RFID, where load varies with the task as these are dominated by the digital state machine power requirement [30]. A summary of the power budget for the implantable smart neural RFID presented in this thesis is in table 2.1. Designing a power

harvester for implantable passive smart RFID is a challenging task first due to the high power requirement of smart RFID compared to an inventory RFID. Second due to the limit on the incident power allowed for ensuring a safe SAR level. To overcome the above disadvantages high efficient harvesters are essential to minimizing the incident power and preventing tissue damage and also to increase the depth of field of operation.

| Block name        | Supply<br>Voltage (V) | Quiescent<br>current(µA) | Power<br>Consumed(µW) |

|-------------------|-----------------------|--------------------------|-----------------------|

| RF-DC converter   | Input power           |                          | 250                   |

| Voltage reference | 0.9                   | 9.85                     | 8.865                 |

| LDO1              | 0.9                   | 4.05                     | 3.645                 |

| LDO2              | 0.9                   | 1.27                     | 1.143                 |

| PLL               | 0.7                   | 4.43                     | 3.1                   |

| Demodulator       | 0.7                   | 0.138                    | 0.096                 |

| Modulator         | 0.7                   | 0.107                    | 0.075                 |

Table 2.1 Power budget for the micro neural RFID

In case of digital CMOS circuits the power consumption is written as in (2.1)

$$P_{TOT} = Leakage Power + Dynamic Power$$

(2.1)

$$P_{TOT} = I_L V_{DDD} + C V_{DDD}^2 f$$

(2.2)

$$P_{TOT} = V_{DDD} (I_L + CV_{DDD} f)$$

(2.3)

Where  $P_{TOT}$  is the total digital power  $V_{DDD}$  is the digital supply voltage and  $I_L$  is the leakage current, C and f are the total or effective switched capacitance load and switching frequency

respectively. From (2.3) power consumption of the digital circuits can be minimized by reducing the  $V_{DDD}$  supply voltage while meeting the switching speed of the circuit. In case of analog circuit which are constrained by bandwidth (BW) and signal to noise ratio (SNR) of the system. The bandwidth and SNR are given by (2.4) and (2.5) respectively

$$I_D = BWnU \ _{T}C_C$$

$$I_D \propto BWC_C$$

(2.4)

$$SNR = \frac{V_{DDA} - 10U_T}{\sqrt{\frac{kT}{C_C}}}$$

$$\propto (V_{DDA} - 10U_T)\sqrt{C_C}$$

(2.5)

In the above equations I<sub>D</sub> is the load current, n is the ideality factor, U<sub>T</sub> is the thermal voltage and Cc is the amplifier compensation capacitance for the multiplying digital to analog converter MDAC, voltage reference, PLL, LDO blocks etc. and V<sub>DDA</sub> is the analog supply voltage. The  $10U_T$  values preserves headroom to avoid signal clipping or distortion. From (2.5) we see scaling V<sub>DDA</sub> by 2 more than doubles SNR. An equal improvement in SNR can also be achieved by increasing the C<sub>C</sub> by four times, however supply current would need to be increased four times to meet the bandwidth requirements. Thus increasing C<sub>C</sub> would increase power consumption quadratically while increasing V<sub>DDA</sub> linearly achieves the same result. Given a desired SNR and BW V<sub>DDA</sub> should be increased verses increasing C<sub>c</sub> to optimize power savings. It is concluded for smart RFIDs being AFE power consumption dominant, achieving as high a harvested voltage within the limits of the process is desired. A higher harvested voltage allows a higher V<sub>DDA</sub>, and thus a lower analog load current and a greater SNR-BW/Watt. The efficiency of a power harvester is presented as in (2.6) where P<sub>hav</sub> is the power loss in the harvester due to the diode drop loss, and P<sub>out</sub> is the output power.

$$\eta_{hav} = \frac{P_{out}}{P_{in}} = \frac{P_{out}}{P_{hav} + P_{out}}$$

(2.6)

The harvester efficiency depends on a) harvested voltage, b) harvester load or harvester currents, c) matching network efficiency d) bandwidth of the rectifier switches, and e) available input power level. Higher voltages are preferred over lower currents for mixed signal RFIDs while for inventory or WORM/ROM/EPROM based RFID are power optimized at lower VDDs and constrained by their maximum current.

#### 2.3 Matching Network

From the maximum power transfer theorem the harvester impedance must match the antenna impedance to ensure maximum power transfer from the antenna to the harvester. Other than the impedance matching some of the other requirements of matching network for this work are voltage boosting, setting up the bandwidth requirement and finally help in outbound communication by BPSK modulation. First we will discuss about the different types of matching network with their pros and cons and then decide which one to select.

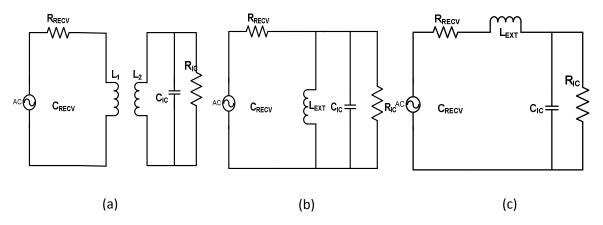

Figure 2.1 Three different matching network.

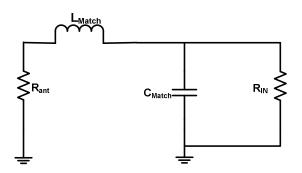

There are simple three methods of impedance matching networks a) transformer matching b) shunt matching c) series inductor matching all of which are shown in figure 2.1(a), (b) and (c)respectively.

**Transformer matching**: The transformer matching is suitable when the antenna is a differential nature such as a quarter wave dipole while the rectifier rectifies the whole full wave that is both positive half and the negative half of a cycle. The advantage of this full wave rectification is they have less ripple (1/2). In transformer matching to achieve high input voltage at the input of rectifier, the ratio between primary and secondary needs to be high resulting in both large inductor values and area. Hence this matching network has a larger foot print and in addition a lower Q. The resulting area and low Q efficiency makes on chip integration both difficult and in efficient. Other than this matching also requires close proximity and alignment of the primary and the secondary for good performance both of which are more easily and efficiently achieved off chip.

**Shunt matching**: In case of shunt matching as in figure 2.1(b) the added shunt inductor combined with the effective shunt capacitor tunes the circuit to the desired resonance frequency. Shunt matching provides a DC short for low frequency. This results in excellent ESD performance, but in case of shunt matching because of the absence of real part transformation there is little or no voltage boosting. In absence of any voltage boosting the input power and the antenna impedance would need to be high enough to develop sufficient voltage to turn on the rectifying devices and develop enough output voltage for RFID to work. One other disadvantage of this matching network is that it requires the antenna and the rectifier to be designed simultaneously as in absence of any impedance transformation they cannot be matched separately.

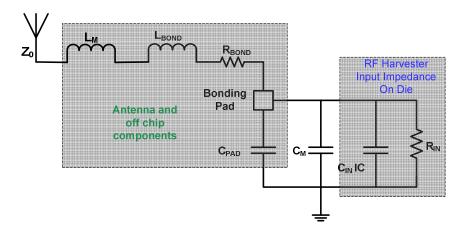

**Series matching**: Finally in case of the series matching network of figure 2.1(c) the series inductor resonates out the effective capacitor. This type of matching provides us with a voltage boosting when the antenna impedance is low relative to the rectifier impedance. This will be explained in detail later. One other advantage of this matching network is that it gives freedom to design the antenna and the rectifier independent of each other and their impedance can be matched using this network. In general this is not recommend as optimization across the system though more difficult is more optimal when considering the antenna, matching, rectifier and the load type. Among different topologies of series matching network like T,  $\pi$  and the L match network is prefered as it provides better efficiency compared to the other two [31] while boosting the input voltage of the rectifier by Q, where Q is quality factor of the network. Other benefit of using an L matching network is that it helps in absorbing the inductance of the bond wire, L<sub>BOND</sub>, and the capacitor C<sub>Pad</sub> of the pad in a constructive manner as shown in the figure 2.2. In figure 2.2 R<sub>BOND</sub> is the bonding wire resistance, C<sub>M</sub> is the tuning capacitor, C<sub>IN</sub> is the effective capacitor of the rectifier and R<sub>IN</sub> is the effective load.

Figure 2.2 The L matching network adopted allow to exploit circuit parasitic constructively.

#### 2.3.1 L matching network

There are two basic L matching, low pass and high pass which are used to step up and step down load impedance respectively depending which port is connected to the source and which one is connected to the load [32, 33]. The L matching network is shown in figure 2.3 where  $R_{IN}$  is the load resistance due to the input impedance of the rectifier and  $R_{ant}$  (Zo<sub>ant</sub> the lossless impedance of the antenna) is the antenna impedance.  $L_{Match}$  is the sum of tuning inductor  $L_M$  and bondwire inductor  $L_{BOND}$ . The capacitor  $C_{Match}$  is the sum of  $C_{PAD}$  tuning capacitor  $C_M$  and rectifier equivalent capacitor  $C_{IN}IC$ . From the maximum power transfer theorem the network has to match the impedance connected to the right hand port to the impedance at the left hand port [31, 34] hence.

Figure 2.3 Low-pass L matching network with inductor  $L_{Match}$  and capacitor  $C_{Match}$  shown explicitly.

$$R_{ant} + jX_L = \frac{1}{\frac{1}{R_{IN}} + \frac{1}{jX_C}}$$

(2.7)

Where  $X_L$  is the impedance due to  $L_{Match}$  and  $X_C$  is the impedance due to capacitor  $C_{Match}$  so equating the real and the imaginary parts

$$R_{ant} = \frac{R_{IN} X_C^2}{R_{IN}^2 + X_C^2}$$

(2.8)

$$X_{L} = \frac{R_{IN}^{2} X_{C}}{R_{IN}^{2} + X_{C}^{2}}$$

(2.9)

$$Q_{s} = \frac{X_{L}}{R_{ant}} = \frac{R_{IN}^{2} X_{C}}{R_{IN} X_{C}^{2}} = \frac{R_{IN}}{X_{C}} = Q_{p} = Q$$

(2.10)

# From equation (2.10) and (2.9)

$$R_{ant} = \frac{X_L}{R_{IN}} X_C = \frac{X_C}{R_{IN}} \left( \frac{R_{IN}^2 X_C}{R_{IN}^2 + X_C^2} \right)$$

(2.11)

Dividing both the numerator and denominator by  $X_{c}\ensuremath{^{\sim}\!2}$  we get

$$R_{ant} = R_{IN} \frac{1}{\left(\frac{R_{IN}^2}{X_C^2} + 1\right)} = R_{IN} \left(\frac{1}{Q^2 + 1}\right)$$

(2.12)

$$Q = \sqrt{\left(\frac{R_{IN}}{R_{ant}} - 1\right)}$$

(2.13)

$$\frac{X_C}{X_L} = \frac{Q^2 + 1}{Q^2}$$

(2.14)

In the above equations  $X_L$  and  $X_C$  are the series and shunt reactance of the inductor and capacitor respectively. At resonance condition with the Q>>1 for the transformation the match reactance are  $X_C \approx X_L$ .

$$\eta_{mn} = 1 - \frac{Q}{Q_L}$$

$$= 1 - \frac{\sqrt{\left(\frac{R_{IN}}{R_{ant}} - 1\right)}}{Q_L}$$

(2.15)

Where  $\eta_{mn}$  is the network efficiency,  $R_{IN}$  is the real part of the rectifier impedance seen from the antenna side and  $R_{ant}$  is the antenna impedance seen from the rectifier side. From equation 2.15 the efficiency of the matching network depends on the ratio of Q and Q<sub>L</sub> [33]. To achieve higher efficiency high quality inductors are required. Therefore an off chip inductor is needed to be used in series matching network to achieve high efficiency. As mentioned in section 2.2 the series matching network provides Q times boost to the input voltage thus

$$Q = \frac{V_{\text{max}}}{V_{in}}$$

(2.16)

In the above equation  $V_{max}$  is the peak input voltage at input of the rectifier and  $V_{in}$  is the peak voltage at the antenna,  $I_{DC}$  is the DC current, using the maximum power transfer theorem where  $P_{in}$  is the input power and  $R_{ant}$  is the antenna impedance, the defining RFID equation are

$$P_{in} = \frac{V_{in}^2}{4R_{ant}} = \frac{1}{2\eta} V_{out} I_{DC}$$

(2.17)

$$Q \approx \sqrt{\frac{R_{IN}}{R_{ant}}} = \frac{\omega L_{Match}}{R_{IN}}$$

(2.18)

$$R_{IN} = \alpha \frac{V_{out}}{I_{DC}}$$

(2.19)

$$\omega = \frac{1}{\sqrt{L_{Match} C_{Match}}}$$

(2.20)

In the above equation and value of  $\eta$  is the efficiency and  $\alpha$  is a constant to mimic diode drop given by The above equation (2.17) and (2.18) depicts for a particular P<sub>in</sub> and R<sub>ant</sub> peak input voltage V<sub>max</sub> varies linearly with Q. Another factor which is affected by Q in a resonance circuit is its bandwidth which is

$$2Q < \frac{f}{\Delta f} \tag{2.21}$$

Where  $\Delta f$  is the bandwidth and f is the resonance frequency. This band width requirement must also satisfy capacitance variation across process, which puts a limit on the Q value that can be utilized. To achieve high harvester efficiency we need to maximize the Q to the allowable limit and R<sub>IN</sub> by determining the optimum NMOS width for the rectifier and the R<sub>ant</sub> while maintaining the desired bandwidth as communication protocol demands. For a smart RFID; P<sub>in</sub>,  $\omega$ , Q, and I<sub>DC</sub> are typically known. Solving (2.17-2.20)

$$V_{out} = 2\eta \frac{P_{in}}{I_{DC}}$$

(2.22)

$$R_{ant} = \eta \,\alpha \frac{2P_{in}}{I_{DC}^2 Q^2} \tag{2.23}$$

$$L_{match} = \frac{2\alpha\eta P_{in}Q}{I_{DC}^2 \omega}$$

(2.24)

$$C_{match} = \frac{I_{DC}^2 Q}{2\alpha \eta P \omega}$$

(2.25)

Where the constants  $\eta$  and  $\alpha$  must be solved/optimized by simulation. Observe that for a passive smart RFID V<sub>out</sub> solve for by setting I<sub>DC</sub> as opposed to a digital dominant RFID setting V<sub>out</sub> and achieving a maximum I<sub>DC</sub>

#### 2.4 Harvester design

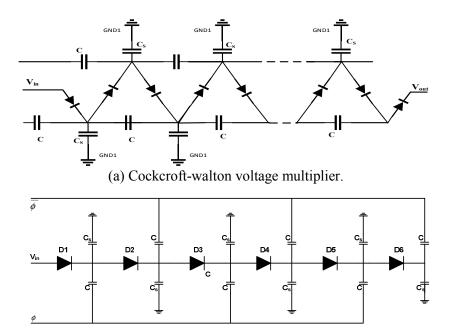

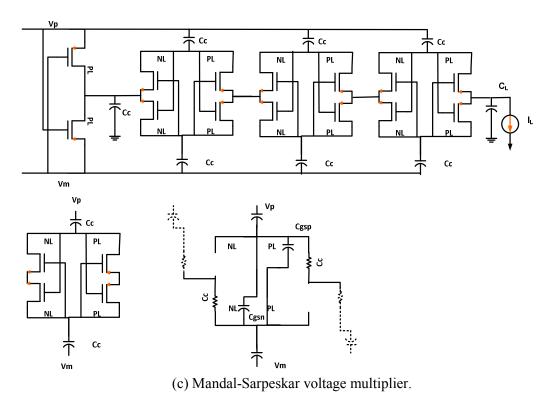

To harvest energy from the Radio frequency wave by far field approach the RF energy radiated from the base station is converted in to DC power, for which we need the rectifier. The rectifier power efficiency directly affects the performance of the system. There are various different design technique for voltage rectifier some of which are a) Cockcroft-walton voltage multiplier [35], b) Dickson Voltage multiplier [36] c) Mandal-Sarpeskar [37] voltage multiplier and d) Bergeret voltage multiplier [38]. For this work the harvester used is a modified Dickson charge pump topology. The regular Dickson voltage multiplier with diode is presented in figure 2.4. Dickson voltage multiplier is simple in architecture and its advantage over the Cockcroft Walton voltage multiplier is that in Dickson multiplier both the coupling capacitor C and the stray capacitor  $C_8$  are driven by the RF signal and all the stray capacitor are connected in parallel. Where as in Cockcroft the stray capacitors are connected in series with the coupling

(b) Dickson Voltage multiplier.

Figure 2.4 Dickson voltage multiplier with diodes.

capacitors, this affects the efficiency greatly when C<sub>S</sub> and C become comparable.

While designing the harvester the fundamental requirement we need to consider for having efficient harvester are a)  $I_{ON} >> I_{OFF}$  that is the on current of the rectifier device must be much higher than the off or leakage current, b) The Q of the matching network need to be high at least greater than 6 to 8 but constrained by the communication bandwidth, c) bandwidth of the rectifying devices must be high to support harmonics of the rectified current. d) it is preferable to operate the rectifying device in subthreshold as in this region as current varies exponentially with the overdrive voltage. The  $g_m$  efficiency decreases as one moves from subthreshold to moderate inversion to strong inversion where the current varies as linear of the over drive voltage. Hence strong inversion is the least preferred region of operation. The rectifying device used in the harvester can be either a Schottky barrier diode (SBD), or diode connected MOS. The preferred device is the one which supports greater  $f_T$  and greater log slope. In [10, 39] the rectifier is

implemented with Schottky barrier diodes (SBD) which offers very good performance, as it has fast switching and low substrate leakage. The main limitation of the schottky diode is that all CMOS process do not support SBD and those that do are typically more costly.

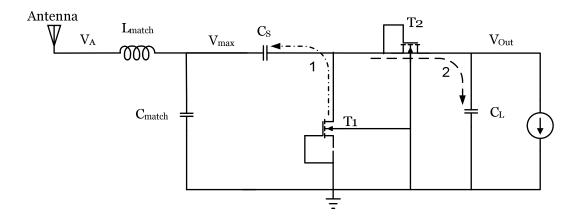

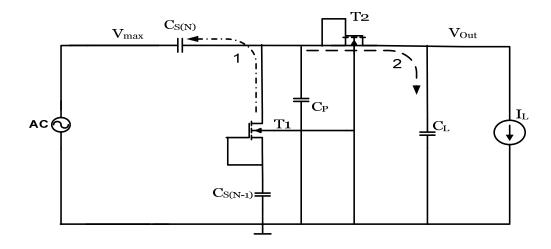

Figure 2.5 Schematic of one stage modified Dickson Charge pump.

To avoid SBD problem one solution is to use the diode connected MOSFET in place of the SBD. At 180nm or shorter node geometries the choice of the device depends on the availability. In this thesis the switches or diode are implemented using NMOS "diode" connected transistors as presented in figure 2.5. The multiplication action of the charge pump can be described as follows, in the negative half cycle C<sub>s</sub>, the coupling capacitor, where C<sub>s</sub>>>C<sub>match</sub> charges through T<sub>1</sub> to  $(V_{max}-V_d)$ . In the positive cycle a voltage equal (2\*V<sub>max</sub>-V<sub>d</sub>) turn on T<sub>2</sub> and charges capacitor C<sub>L</sub> to  $V_{out} = 2*(V_{max} - V_d)$ . Where V<sub>d</sub> is the minimum transistor turn on voltage at *f<sub>C</sub>* the carrier frequency. In case of a N stage Dickson charge pump the steady state voltage is given by

$$V_{out} = 2N(V_{max} - V_d) \tag{2.26}$$

Where  $V_{out}$  is output voltage of the rectifier  $V_{max}$  is the amplitude of input sinusoid at the rectifier input and N the number of stages. Equation 2.26 portrays that to have higher  $V_{out}$  a lower turn on

voltage  $V_d$  is needed and also  $V_{max}$  needs to be higher. One of the fundamental requirement of an efficient harvester is  $f_T$  as expressed earlier in this section. The  $f_T$  of the MOS diode can be expressed as

$$f_{\text{TNMOS}} \approx \frac{1}{2\pi} \left( \frac{\text{ID}}{\text{nU}_{\text{T}} \text{C}_{\text{gg}}} \right)$$

(2.27)

$$= \frac{1}{2\pi} \left( \frac{\text{I}_{\text{S}} e^{\left(\frac{\text{V}_{\text{G}} - \text{V}_{\text{TN}}}{\text{n} \text{U}_{\text{T}}}\right)}}{\text{n} \text{U}_{\text{T}} \text{C}_{\text{gg}}} \right)$$

$$= \frac{\mu_{\text{n}} \text{U}_{\text{T}}}{\pi \text{L}^{2} \text{C}_{\text{OX}}} \left( e^{\left(\frac{\text{V}_{\text{G}} - \text{V}_{\text{TN}}}{\text{n} \text{U}_{\text{T}}}\right)} \right) =$$

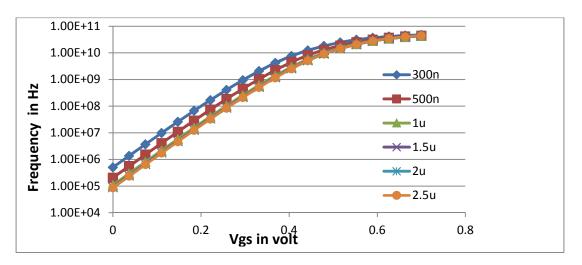

The significant things to notice from 2.27 are; the  $f_T$  is independent of the width and is inversely proportional to square of the length. To depict the dependence of  $f_T$  on  $V_{GS}$  a plot of  $f_T$  vs  $V_{GS}$  is presented in figure 2.6. The plot shows to support a particular  $f_T$  one cannot go below a certain  $V_{GS}$  and also  $f_T$  increases log linearly in the subthreshold region. As mentioned previously in the beginning of this section that to achieve high efficiency we need to have low  $V_{GS}$ . This dictates a low  $V_T$  as well but still high enough to ensure an acceptable  $I_{OFF}$ .

Figure 2.6 f<sub>T</sub> versus V<sub>GS</sub> plot for a minimum length and different width geometry transistor

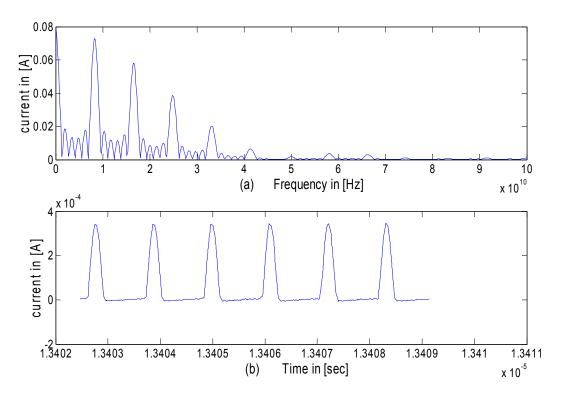

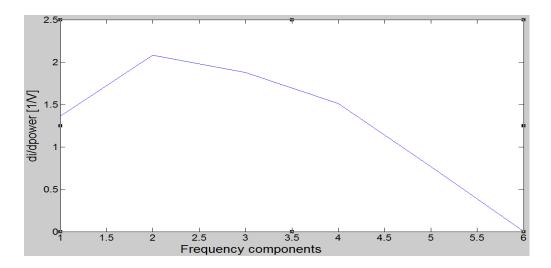

During steady state harvesting the average charge harvested per cycle is constant. The average area under a single current pulse during steady state will thus remain constant, so current pulse amplitude varies inversely with the device width and the duty cycle increases with the device width. When a FFT is performed on the current train pulses it is observed that greater amplitude and narrow pulses support higher frequency components than shorter and wider pulses. A plot of the steady state current train pulses and its FFT is presented in figure 2.7. From 2.6 to support an additional seven harmonics V<sub>d</sub> must increased by  $2nU_T$ . A plot of harmonic efficiency  $\Delta i/\Delta P$  vs the component (harmonic) number is presented in figure 2.8 where  $\Delta i$  is the increment in current due to the nth harmonic and  $\Delta P$  is the incremental power cost of harvesting the nth harmonic. From figure 2.8 we observe harvest efficiency increases with transistor width until the current pulse is such that 2 to 3 harmonic components are harvested after which we cross a point of diminishing returns. Current harmonics continue to be harvested but at a higher and higher cost. Thus we should increase the width of the device so that the resulting  $V_d$  in steady state support 2 to 3 harmonics. As presented in the power budget table, this smart RFID requires around 50µAof load current at a DC voltage of 900mV or higher. High efficiency of harvesters allows for a greater depth field of operation. As efficiency is dependent on  $V_d$  we select the device sized with minimum length, L<sub>min</sub> but sufficiently wide enough to support the desired current density and the required "MOS diode" bandwidth.

The L matching network provides voltage boost to the harvester input voltage by a factor of Q, given by (2.16) where  $R_{IN}$  is the input resistance of the rectifier and  $R_{ant}$  is the antenna impedance. To achieve high harvester efficiency we need to maximize the Q, and  $R_{ant}$  by determining the optimum NMOS geometry for the rectifier and the  $R_{ant}$  while maintaining the desired communication bandwidth. The communication bandwidth standard must be satisfied across process capacitance variation.

Figure 2.7 (a) MATLAB FFT of the rectifier current during steady state.

(b) Rectifier current waveform in steady state.

Figure 2.8 Plot of harmonic efficiency  $\Delta i/\Delta P$  vs the component (harmonic) number.

### 2.4.1 Harvester design optimization

The objective is to maximize Q and R<sub>ant</sub>, to maximize Vout and thus obtain higher harvester voltage while avoiding device breakdown. The maximum Q is constrained by the band width of the tuning circuit so R<sub>ant</sub> and Q are used in concert to maximize  $V_{max}$ . Also in equation (2.26) in section 2.4 while calculating  $V_{out}$  the effect of the parasitic capacitances were not taken in to account. The schematic of the Nth stage of a N stage rectifier is shown in figure 2.9 with parasitic capacitor taken in to consideration. As indicated in figure 2.9 taking into account the parasitic capacitors of the rectifying devices equation 2.26 can be rewritten as

Figure 2.9 Nth stage of the rectifier where  $C_p$  is the sum of all the parasitic capacitor.

$$V_{out} = 2N \left[ V_{\max} \left( \frac{C_s}{C_s + C_p} \right) - V_d \right]$$

(2.28)

The above equation indicates that the V<sub>out</sub> decreases with the increase in parasitic capacitor so if  $C_P$  becomes comparable to  $C_S$  efficiency would be affected. Although  $C_S >> C_P$  the size of the transistor must be optimize to achieve maximum efficiency.

Rectifiers are nonlinear even in the steady state condition. Therefore to optimize we need a current equation valid in all the regions of device operation. The EKV model [40] provides accurate current modeling in all regions, as a result the EKV model is used to estimate rectifier transistor  $I_D - V_{GS}$  characteristic as follows:

$$I_{D}(V_{GS}) = I_{S}\left[\ln^{2}\left(1 + e^{\frac{V_{p} - V_{GS}}{2U_{T}}}\right) - \ln^{2}\left(1 + e^{\frac{V_{p}}{2U_{T}}}\right)\right]$$

where  $V_{p} = \frac{V_{G} - V_{th}}{n}$

and  $I_{S} = 2nK_{p}\frac{W}{L}U_{T}^{2}$  (2.29)

In the above equations  $I_S$  is the specific current,  $U_T$  is the thermal voltage, Vth is the threshold voltage and  $V_p$  is the pinch off voltage.

From the efficiency equation 2.6 one can write

$$\eta = \frac{1}{\frac{P_{hav}}{P_{out}} + 1} = \frac{1}{\frac{V_{GS} \ i_{O}(t)}{V_{out} \ I_{DC}} + 1} \approx \frac{1}{\frac{V_{GSon} \ I_{DC}(T)}{V_{out} \ I_{DC}} + 1}$$

$$\approx \frac{1}{\frac{\left(V_{GSon} \ (f_{C}) + nU_{T} \ \ln\left(\frac{mI_{on}}{Is}\right)\right)mI_{DC}}{V_{out} \ mI_{DC}} + 1}$$

$$\approx \frac{1}{\frac{\left(V_{GSon} \ (f_{C}) + nU_{T} \ \ln\left(\frac{mI_{on}}{Is}\right)\right)}{V_{out}} + 1}$$

$$\approx \frac{1}{\frac{\left(V_{GSon} \ (f_{C}) + nU_{T} \ \ln\left(\frac{mI_{on}}{Is}\right)\right)}{V_{out}} + 1}$$

where  $V_{GSon}(f_C)$  is the minimum  $V_{GS}$  for NMOS turn on at the carrier frequency  $f_c$  and  $I_{on}$  is the average drain current at  $V_{GS}$ . Equation (2.30) shows that efficiency is maximized by having a greater harvest voltage,  $V_{out}$  and lower load current  $I_{out}$ ,  $V_{out}$  is the output voltage which directly varies with Q. As the objective of optimization is to have higher harvested voltage with lower load current and achieving greater harvester efficiency so to perform the optimization we need to

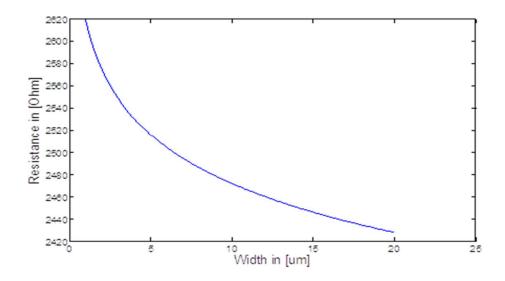

calculate the  $R_{in}$  and Q for which we modeled the rectifier in MATLAB. The value of  $R_{in}$  is calculated from the rms voltage and current across the diode connected transistor. A plot of the  $R_{in}$  while varying the width W is presented in figure 2.10

Figure 2.10 Rin versus transistor width.

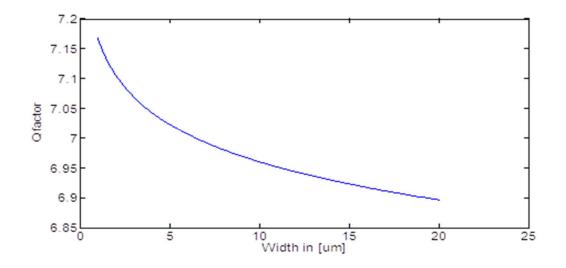

From the above figure 2.10 it is observe that  $R_{in}$  decreases with increase in width of the transistor and it is nonlinear. After calculating the Rin, the Q values are also calculated using equation

Figure 2.11 Q factor of the versus the transistor width.

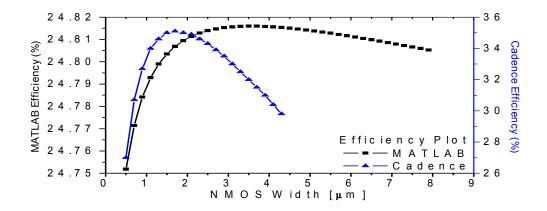

(2.11) while calculating the value of Q, the  $R_{ant}$  is considered as 50 $\Omega$  for convenience of RFID testing. Other values may be taken as required to maximize V<sub>max</sub> while maintaining BW. A plot of Q with varying width is presented in figure 2.11. Figure 2.10 and 2.11 demonstrate that Rin and Q decrease with increases in width of the transistor. On the other hand V<sub>GS</sub> or in this case V<sub>d</sub> decreases with increase in width of transistor for constant drain current. Therefore considering (2.13), (2.16), (2.28) and (2.29), there exists a optimum width which would achieve maximum efficiency with maximum Vout and given load current. To find this optimal geometry harvester efficiency is simulated to find an estimate of the device geometry for maximum efficiency and  $V_{out}$  using a MATLAB program. The values of the matching network components are also determined from the Q values obtained in simulation. The efficiency plot from MATLAB is presented in figure 2.12. From figure 2.12 it is observed that maximum efficiency occurs in the range of 500 nm to 5 um of transistor width. The value of the inductor Lmatch is calculated to be 60 nH and the C<sub>match</sub> value is 520 fF for a Q value of 6.5 To get an fabrication value for maximum efficiency a parametric sweep of device in the estimated width range is performed using Cadence Spectre with results presented in figure 2.12. In Cadence the resulting maximum efficiency device width is 1.75µm.

Figure 2.12 Efficiency  $\eta$  vs NMOS width from Matlab model and cadence simulation.

### 2.5 Results and discussion

In this case considering the resonance frequency as 900MHz the value of  $L_{match}$  comes to 60nH and the value of  $C_{match}$  is 521fF.With the above values of L and C a parametric sweep of the "diode" width is performed in Cadence where efficiency is plotted in Fig 2.11. This results in a maximum efficiency around a device width of 1.75µm, which supports our estimation with MATLAB of 2µm. Table 2.2 show the result of parasitic extracted simulation in cadence spectre for different width W with N equal to one at 900MHz, constant load power and a fixed input power of -6dbm in the 0.18µm IBM process. The desired power is maximum VDD i.e. 1V at 50µA. From the table one can see that the efficiency achieved are close to the plot in figure 2.12.

| Frquqency | MOS area         | Pin   | L    | С    | Output      |                       | Efficiency |

|-----------|------------------|-------|------|------|-------------|-----------------------|------------|

| (MHz)     |                  | (dbm) | (nH) | (fF) | voltage (V) | current<br>range (µA) | (%)        |

| 900       | 2μm X .18μm      | -6    | 74   | 422  | 1.16        | 74                    | 34.3       |

| 900       | 3μm X .18μm      | -6    | 74   | 422  | 1.08        | 74                    | 31.9       |

| 900       | 3.5μm X<br>.18μm | -6    | 74   | 422  | 1.02        | 74                    | 30.2       |

| 900       | 4μm X .18μm      | -6    | 74   | 422  | 0.970       | 74                    | 28.7       |

Table 2.2 Efficiency of the Harvester at different width of the rectifier device

Table 2.3 shows the comparison of our harvester to other similar harvesters. It is worth noting that all of the recently mentioned harvesters report a much lower load current than the proposed work. Also the output voltages are given as range and not as the voltage at the reported load current and as mention previously efficiency is highly dependent on both the load and output voltage. In comparison to the other harvester in our case the P<sub>in</sub> minimum is higher by 4 to 16dBm

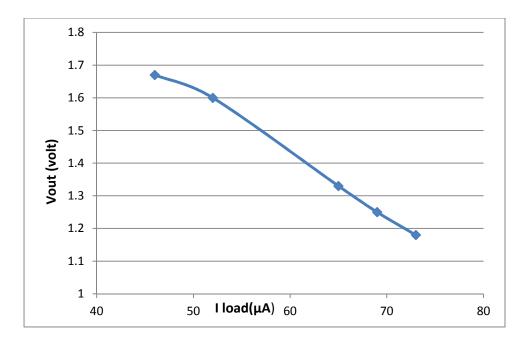

To show the dependence of total efficiency on the load current and the input power along with the harvester efficiency two plots figure 2.13 and figure 2.14 are presented. The plot presented in figure 2.13 is of the voltage  $V_{out}$  at the output of RF-DC converter versus the load current with constant input power of -6dBm. As the peak load current for the simulation was 73µA, the unregulated voltage developed is 1.18V which suggest that we can go below -6dBm as minimum  $V_{out}$  required is 900mV. Figure 2.14 is a plot of output voltage versus the input power for different load current. The plot clearly shows that the output voltage increases with the increase in input power and it also increases with the decrease in load current.

| Author             | Frequency<br>(MHz) | Process        | Matching<br>type | Switch<br>type    | No. of<br>stages | Output<br>voltage<br>(V) | Load<br>current<br>range | Efficiency<br>(%) |

|--------------------|--------------------|----------------|------------------|-------------------|------------------|--------------------------|--------------------------|-------------------|

|                    |                    |                |                  |                   |                  |                          | (µA)                     |                   |

| Barnett<br>[41]    | 900                | 0.18µm<br>Bulk | Shunt            | Schottky<br>diode | 16               | 0-3                      | 1-8                      | 4-8               |

| Curty [42]         | 915                | 0.5µm SOI      | Series           | MOS diode         | 3                | 0-5                      | 1                        | 0-10              |

| Sarpeshkar<br>[37] | 950                | 0.18µm<br>Bulk | Shunt            | MOS diode         | 2                | 0-5                      | 4                        | 16-23             |

| Shameli<br>[43]    | 920                | 0.18um<br>Bulk | Series           | MOS diode         | 4                | 0-1                      | 2                        | 5-10              |

| Kotani<br>[44]     | 953                | 0.18um<br>Bulk | Series           | MOS diode         | 1                | 0-2                      | 31.5                     | 67.5              |

| Scorcini<br>[45]   | 928                | 0.18um<br>Bulk | Series           | MOS diode         | -                | 0-1.5                    | 8.95                     | 45                |

| Triet [46]         | 915                | 0.18um<br>Bulk | Series           | MOS diode         | -                | 0-1.5                    | 1.26                     | 30                |

| Kuhn [47]          | multiband          | РСВ            | Series           | Diode             | -                | 0.9                      | 18.25                    | 52                |

| This work          | 900                | 0.18µm<br>Bulk | Series           | MOS<br>diode      | 1                | 0-1.2                    | 74                       | 34.3              |

Table 2.3 Comparison of various RF DC architectures

Figure 2.13 Vout vs  $I_L$  plot with  $P_{in}$ = -6dBm.

Figure 2.14 Vout vs Input power for different load current.

Figure 2.15 Layout of the harvester with matching cap and LDOs.

# CHAPTER III

# ADAPTIVE SWITCH CAPACITOR POWER REGULATOR

# **3.1 Introduction**

The active power in a digital circuit varies quadratic with the supply voltage hence digital circuits uses supply voltage scaling to reduce power consumption [48-50], when this supply voltage is less than the threshold voltage of the transistor, the circuit is said to operate in subthreshold. Different leakage mechanism in a transistor are [51] a) subthreshold leakage, b) gate oxide tunneling, c) gate edge diode leakage and d) gate-induced diode leakage. In subthreshold the circuit consumes less energy for active operation due to supply reduction and the quadratic relation with the supply voltage. In addition static power is reduced due to DIBL effect on I<sub>off</sub>, and the strong effect of supply voltage on gate oxide tunneling and gate oxide drain leakage [52]. In recent years with the rise in application of wireless network, and new process technology subthreshold circuit designing has gain much more favor. Circuits at subthreshold consumes less power and can now support bandwidth which is sufficient for RFID applications. In severely energy constrained systems such as passive smart RFIDs, where conserving energy is the primary objective subthreshold or near threshold circuits are ideal. In weak inversion the transistor channel is not inverted and current flow is by diffusion where the current maybe written

$$I_{D} = I_{S} \frac{W}{L} e^{\frac{V_{GS} - V_{TH}}{nU_{T}}} (1 - e^{\frac{-V_{DS}}{U_{T}}})$$

(3.1)

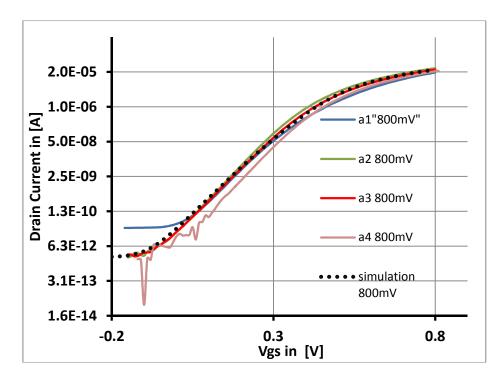

Figure 3.1 Plot of  $I_D$  vs  $V_{GS}$  at constant  $V_{DS}$ =800mV for NMOS of four different die, W/L=220nm/180nm at room temperature and  $V_{th}\approx$ 450mV.

So we observe from equation (3.1) and the plot in figure 3.1  $I_D$  varies exponentially with the (V<sub>GS</sub> – V<sub>TH</sub>). To summarize in deep submicron processes operating in near threshold the issues that affects V<sub>TH</sub> are

- short channel effect, reverse short channel effect [53].

- narrow channel effect and reverse narrow channel effect [54].

- DIBL effect.

- Variability and matching.

- V<sub>TH</sub> variation with temperature.

All these cause variation in  $V_{TH}$ . This  $V_{TH}$  variation causes the variation of  $I_{ON}$  and  $I_{OFF}$  ratio, which affects the switching speed of a circuit. One can also observe from equation (3.1) the drain current  $I_D$  varies exponentially with  $V_{TH}$  in subthreshold so the effect of  $V_{TH}$  variation is more profound in subthreshold and near threshold. Put things in perspective, under classical logic operation we would expect compensation for

$V_{TH}$  variation with temperature typically +/- 90mV +/- 120mV (Tempco equal 0.5 to 1.5mV/C), lot-to-lot and die-to-die

- Commercial -20C to 70C

- Industrial -40C to 85C,105C

- Military -55C to 125C

- Automotive -40°C to +150°C Soon to be 175C or 200C

- Oil field -40°C to +200°C OR -40°C to 225°C

$$\frac{I_D(T)}{I_D(T_0)} = \left(\frac{\mu n(T)}{\mu n(T_0)}\right) \left(\frac{T}{T_0}\right)^2 e^{\int_{U_T}^{U_T} \left(V_{GS}(T_0) - e^{\left(-\frac{V}{U_T}\right) \left(\frac{V_{GS}(T) - V_T(T)}{T} - \frac{V_{GS}(T_0) - V_T(T_0)}{T}\right)}\right)}$$

(3.2)

$$V_{GS}(T) = \frac{T}{T_0} V_{GS}(T_0) + \left(1 - \frac{T}{T_0}\right) \left(V_T(T_0) + \alpha_{VT}(T_0) + nU_T \ln\left(\frac{I_D(T)T^{\alpha}}{I_D(T_0)T_0}\right)\right)$$

(3.3)

$$V_T(T) \approx V_T(T_0) + \alpha_{VT}(T - T_0)$$

(3.4)

where  $\alpha_{VT}$  =-0.5mV/C t0 -4mV/C

- Supply voltage +/- 0.1VDD or higher as on LDOs readily afford regulation ro better than 2%.

- Mobility  $\mu n(T) = \mu n(T_0) (T/T_0)^m$  where m = -1.5 OR 1.2 to 2

- Process +/- 70mV

- Threshold variability  $AvT/\sqrt{2WL} \approx 2-3mV-um/\sqrt{2WL}$  90 to 10nm.