#### **INFORMATION TO USERS**

This was produced from a copy of a document sent to us for microfilming. While the most advanced technological means to photograph and reproduce this document have been used, the quality is heavily dependent upon the quality of the material submitted.

The following explanation of techniques is provided to help you understand markings or notations which may appear on this reproduction.

- 1. The sign or "target" for pages apparently lacking from the document photographed is "Missing Page(s)". If it was possible to obtain the missing page(s) or section, they are spliced into the film along with adjacent pages. This may have necessitated cutting through an image and duplicating adjacent pages to assure you of complete continuity.

- 2. When an image on the film is obliterated with a round black mark it is an indication that the film inspector noticed either blurred copy because of movement during exposure, or duplicate copy. Unless we meant to delete copyrighted materials that should not have been filmed, you will find a good image of the page in the adjacent frame.

- 3. When a map, drawing or chart, etc., is part of the material being photographed the photographer has followed a definite method in "sectioning" the material. It is customary to begin filming at the upper left hand corner of a large sheet and to continue from left to right in equal sections with small overlaps. If necessary, sectioning is continued again-beginning below the first row and continuing on until complete.

- 4. For any illustrations that cannot be reproduced satisfactorily by xerography, photographic prints can be purchased at additional cost and tipped into your xerographic copy. Requests can be made to our Dissertations Customer Services Department.

- 5. Some pages in any document may have indistinct print. In all cases we have filmed the best available copy.

University Microfilms International

300 N. ZEEB ROAD, ANN ARBOR, MI 48106 18 BEDFORD ROW, LONDON WC1R 4EJ, ENGLAND

8012282

### JAMES, DONALD WILLIAM

### ENHANCED HIGH SPEED SERIAL DATA TEST SYSTEM

The University of Oklahoma

D.ENGR.

1979

University Microfilms International 300 N. Zeeb Road, Ann Arbor, MI 48106 18 Bedford Row, London WC1R 4EJ, England

# THE UNIVERSITY OF OKLAHOMA GRADUATE COLLEGE

# ENHANCED HIGH SPEED SERIAL DATA TEST SYSTEM

•

### A DISSERTATION

### SUBMITTED TO THE GRADUATE FACULTY

# in partial fulfillment of the requirements for the

## degree of

### DOCTOR OF ENGINEERING

BY

### DONALD W. JAMES

ENHANCED HIGH SPEED SERIAL DATA TEST SYSTEM

APPROVED BY Kenya DISSERTATION COMMITTEE

#### ACKNOWLEDGMENT

To my wife, Jo, to whom I owe a great deal of gratitude for her encouragement and support during the course of my study. I also wish to thank her for her able assistance in editing and typing the manuscript.

Sincere thanks are due Professor William T. Cronenwett, Thesis Adviser and Chairman of my Doctoral Committee, for his interest, guidance and encouragement. I would also like to acknowledge Professor Samuel C. Lee, Professor William L. Kuriger, and Professor John C. Thompson, the other members of my Doctoral Committee.

I would like to thank my good friend and colleague, John Perry, President of Ra-Nav Laboratories, for allowing me the opportunity to design the system. In addition, thanks are extended to Randell Smith, Ra-Nav engineer, and Danny Grant, Ra-Nav technician, for their efforts in building, debugging, and testing my design.

Finally, I would like to express my appreciation to my associates at Magnetic Peripherals Incorporated for their encouragement. Special thanks are due to Mr. D. C. Bowman, Vice President of Engineering at MPI, for his assistance in getting my thesis printed.

iii

## TABLE OF CONTENTS

|       |      |                                           |                      |                   |                   |               |            |        |    |            |            |             |        |             |        |        | rage                  |

|-------|------|-------------------------------------------|----------------------|-------------------|-------------------|---------------|------------|--------|----|------------|------------|-------------|--------|-------------|--------|--------|-----------------------|

| list  | OF   | TABLE                                     | s.                   | ••                | •                 | •             |            | •      | •  | •          | •          | •           | •      | •           | •      | •      | v                     |

| LIST  | OF   | ILLUS                                     | TRAT                 | ION               | S                 | •             |            | •      | •  | •          | •          | •           | •      | •           | ٩      | •      | vi                    |

| ABST  | RACI | ſ                                         | • •                  |                   | •                 | •             |            | •      | •  | •          | ٠          | •           | •      | •           | •      | •      | x                     |

| Chapt | ter  |                                           |                      |                   |                   |               |            |        |    |            |            |             |        |             |        |        |                       |

| I.    | II   | TRODU                                     | CTIO                 | N.                | •                 | •             | • •        | •      | •  | •          |            | •           | •      | •           | •      | •      | 1                     |

|       |      | Scope<br>GGM-1<br>GGM-2<br>DMG a<br>Desig | 6 Fe<br>1 Fe<br>nd D | atu<br>atu<br>SA  | res<br>res<br>Fea | ;<br>;<br>itu | ires       |        |    | 1 E        |            |             | cen    |             |        |        | 1<br>2<br>4<br>6<br>9 |

| II.   | D    | IGITAL                                    | MES                  | SAG               | ΕC                | GEN           | IER/       | ATC    | DR | •          | •          | •           | •      | •           | •      | •      | 14                    |

|       |      | Physi<br>Logic<br>Input                   | Des                  | scrî              | .ptj              | Lon           | L,         | • •    |    |            | •          | •<br>•<br>• | •<br>• | •<br>•      | •      | •      | 14<br>29<br>40        |

| III.  | D    | IGITAL                                    | SIC                  | SNAL              | . Al              | NAL           | YZ]        | ER     |    |            | •          | •           | •      | •           | •      | •      | 46                    |

|       |      | Physi<br>Logic                            |                      |                   |                   |               |            | n .    | •  | •••        | •          | •           | •      | •           | •      | •      | 46<br>57              |

| IV.   | P    | ROM PR                                    | OGRA                 | MME               | R                 | •             | •          | •      | •  |            | •          | •           |        | •           | •      | •      | 75                    |

|       |      | Physi<br>Logic<br>Firmw                   | Des                  | scri              | pt:               | ior           | 1          | •      | •  | •••        | • •        | •           | •      | •<br>•      | •<br>• | •<br>• | 75<br>78<br>92        |

| v.    | C    | ONSTRU                                    | CTIC                 | ON A              | ND                | TI            | EST        | IN     | G  | •          |            | •           | •      |             | •      | •      | 93                    |

|       |      | Logic<br>Probl<br>Descr<br>Descr          | lems<br>ipt:<br>ipt: | End<br>ion<br>ion | ou<br>of<br>of    | nte<br>Ur     | ere<br>nit | d<br>C | on | st:<br>Wi: | ruc<br>rir | ti<br>ng    | .on    | •<br>•<br>• | •<br>• |        | 93<br>96<br>98        |

|       |      |                                           | omh                  | 1100              |                   |               |            |        |    |            |            |             | re     | s.          | •      | •      | 120<br>120            |

| VI.   | C    | ONCLUS                                    |                      |                   | •••               | •             | •          | •      | •  | •          |            | •           | •      | •           | •      | •      | 131                   |

| BIBL  | JOG  | RAPHY                                     |                      | •                 |                   |               |            | •      |    | •          |            |             |        |             | •      |        | 136                   |

.

# LIST OF TABLES

| TABLE |                                                              | Pa | ıge |

|-------|--------------------------------------------------------------|----|-----|

| I.    | AVAILABLE BAUD RATES FOR THE GGM-16 .                        | •  | 4   |

| II.   | MEMORY ADDRESS FOR PROM                                      | •  | 23  |

| III.  | AVG DISTORTION FOR VARIOUS TYPES & PERCENTAGES OF DISTORTION | •  | 70  |

| IV.   | STATE DIAGRAM FOR CONTROL COUNTER<br>SEQUENCES               | •  | 83  |

| v.    | MICROPROCESSOR ADDRESS DECODES                               | •  | 86  |

## LIST OF ILLUSTRATIONS

.

.

| FIGURE |                                                  | Pa | age |

|--------|--------------------------------------------------|----|-----|

| 1.     | Types of Distortion                              | •  | 3   |

| 2.     | Low-Power Schottky vs CMOS Power<br>Requirements | •  | 12  |

| 3.     | CMOS Rise, Fall, and Propagation Time            | •  | 13  |

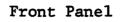

| 4.     | Front Panel of the DMG                           | •  | 15  |

| 5.     | Switched Bias Distortion                         | •  | 17  |

| 6.     | ASCII Code Table                                 | •  | 20  |

| 7.     | Baudot Code Table                                | •  | 22  |

| 8.     | Back Panel of the DMG                            | •  | 26  |

| 9.     | Power Supply Schematic Diagram for the DMG       | •  | 28  |

| 10.    | Digital Message Generator Block<br>Diagram       | •  | 30  |

| 11.    | 2X Clock Period                                  | •  | 34  |

| 12.    | 2X Clock and 20X Clock                           | •  | 35  |

| 13.    | 32K Pseudo-Random Pattern Generator .            | •  | 37  |

| 14.    | I/O Drivers                                      | •  | 42  |

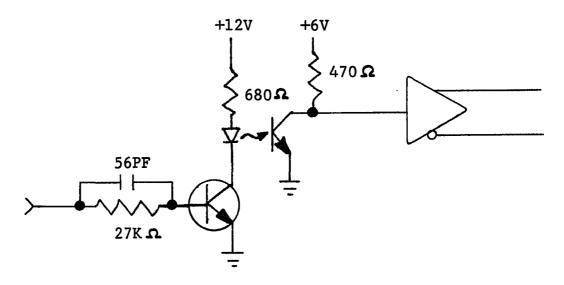

| 15.    | Typical Circuit for Input/Output                 | •  | 43  |

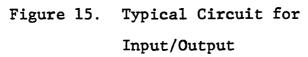

| 16.    | Generator Offset Voltage (Vos)<br>Measurement    |    | 43  |

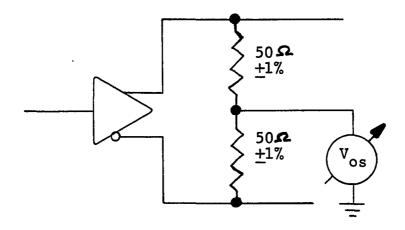

| 17.    | Transformer Coupled High Level<br>Data Output    |    | 44  |

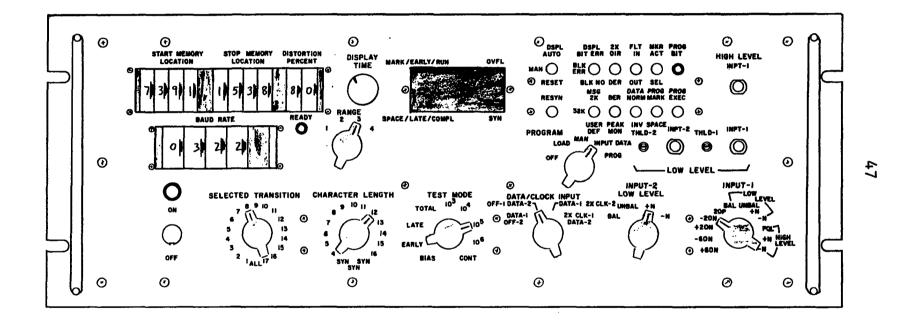

| 18. | Front Panel of the DSA 47                                                 |

|-----|---------------------------------------------------------------------------|

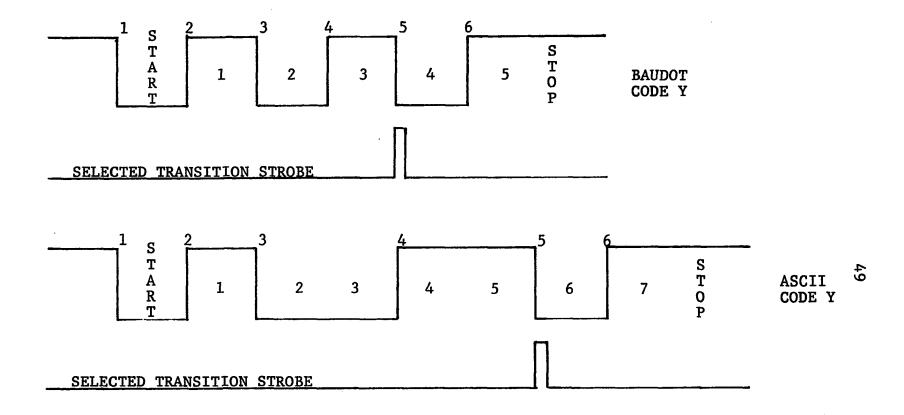

| 19. | Selected Transition Strobe when<br>Selected Transition Switch Set to 5.49 |

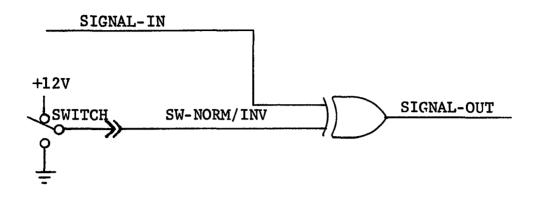

| 20. | Normal or Inverted Controls 53                                            |

| 21. | Truth Table for Two Input Exclusive<br>OR Gate                            |

| 22. | Back Panel of the DSA                                                     |

| 23. | Start/Stop Switch Controls 58                                             |

| 24. | Bit, Bit Error, Block, Block<br>Error Counters 62                         |

| 25. | Block Diagram Average Distortion<br>Circuit                               |

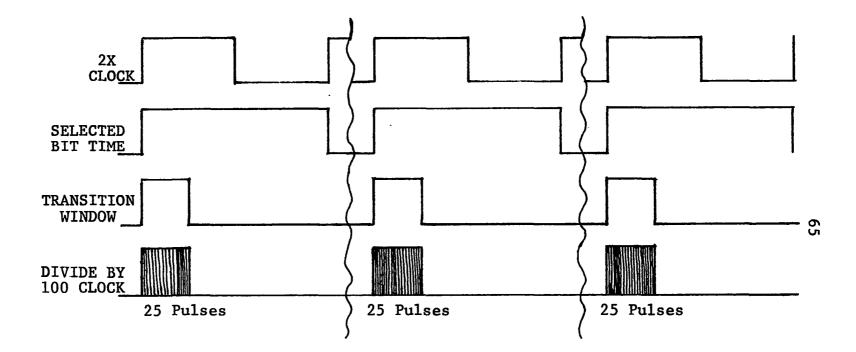

| 26. | 25% Early Distortion 65                                                   |

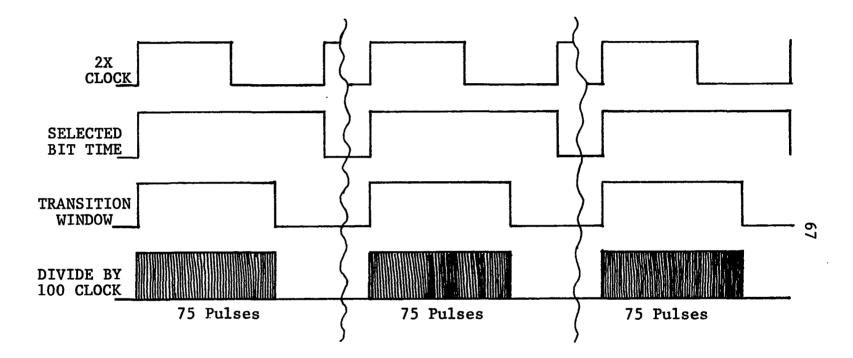

| 27. | 25% Late Distortion 67                                                    |

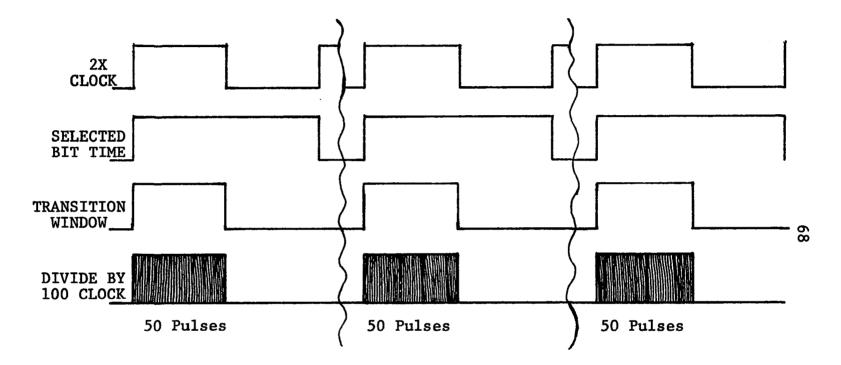

| 28. | 0% Distortion                                                             |

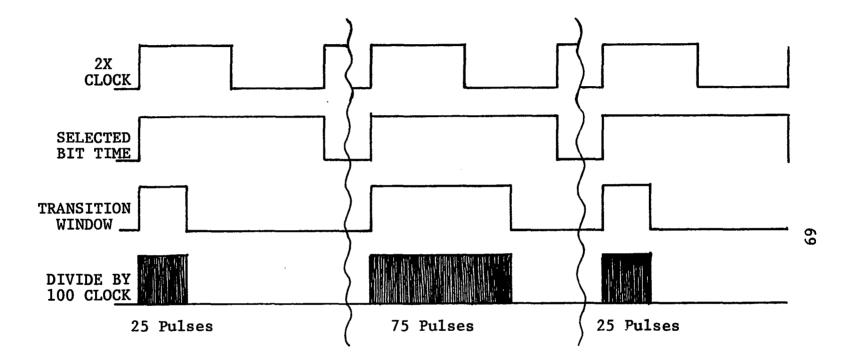

| 29. | 25% Switched Distortion 69                                                |

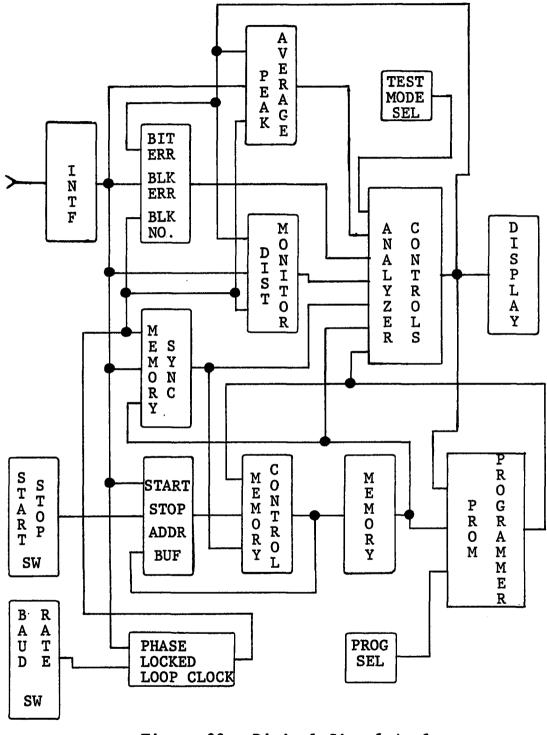

| 30. | Digital Signal Analyzer Block Diagram . 74                                |

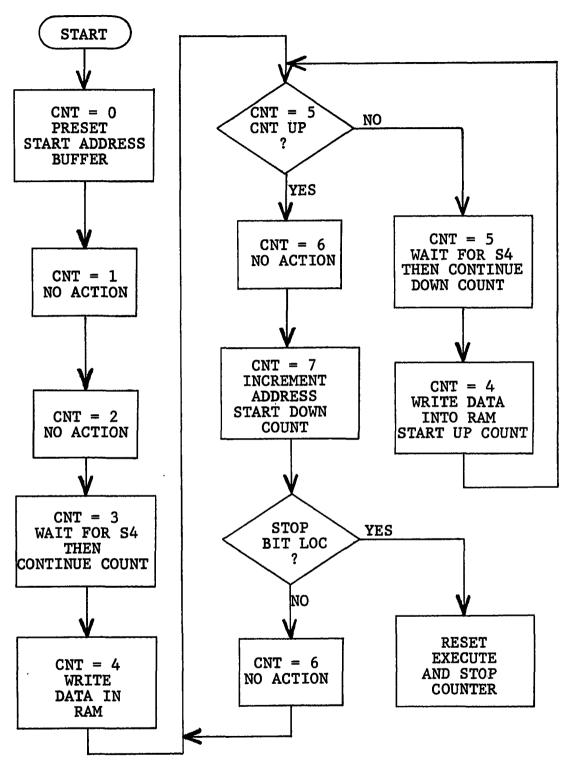

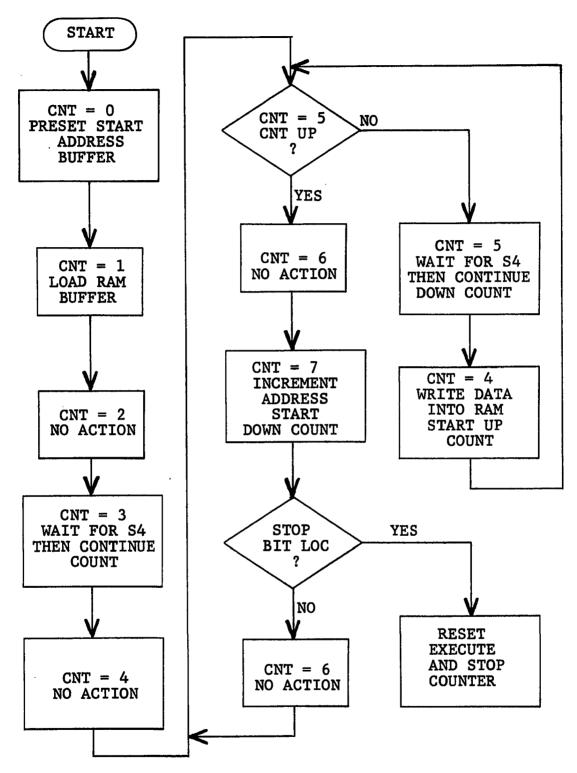

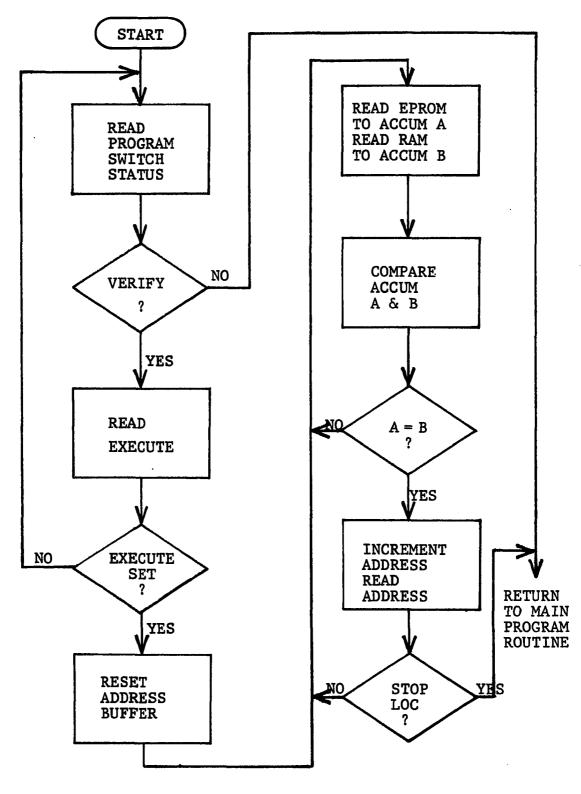

| 31. | Flowchart of Counter Sequences for OFF. 79                                |

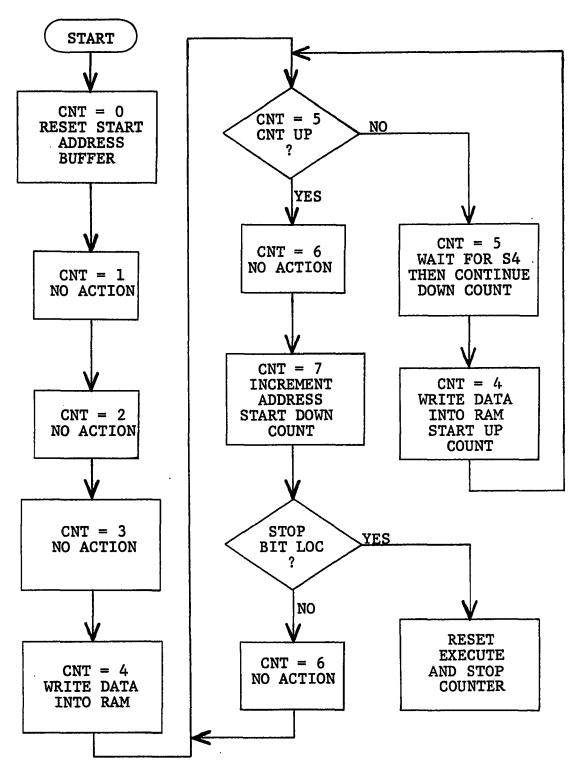

| 32. | Flowchart of Counter Sequences for<br>LOAD                                |

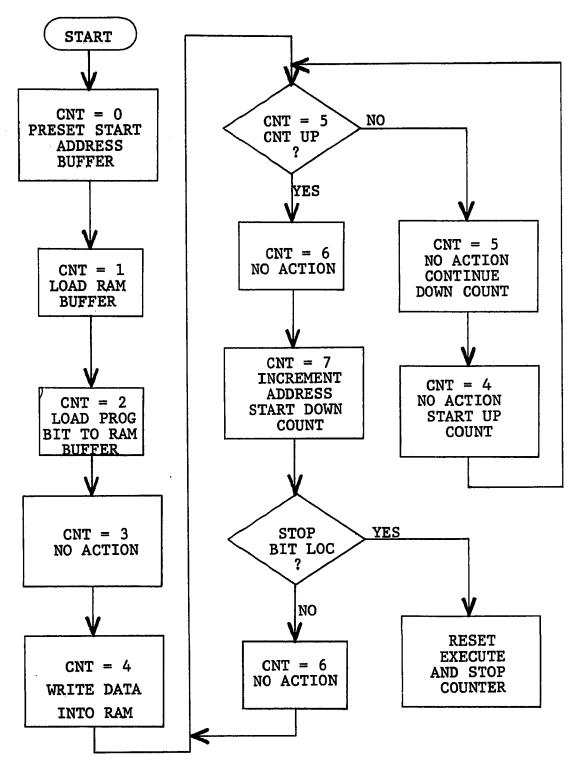

| 33. | Flowchart of Counter Sequences for<br>MANUAL                              |

| 34. | Flowchart of Counter Sequences for<br>INPUT DATA                          |

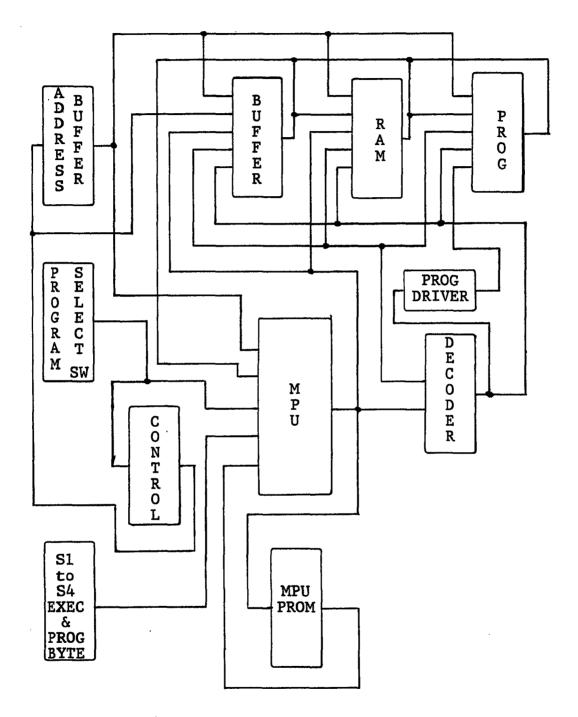

| 35. | PROM Programmer Block Diagram 84                                          |

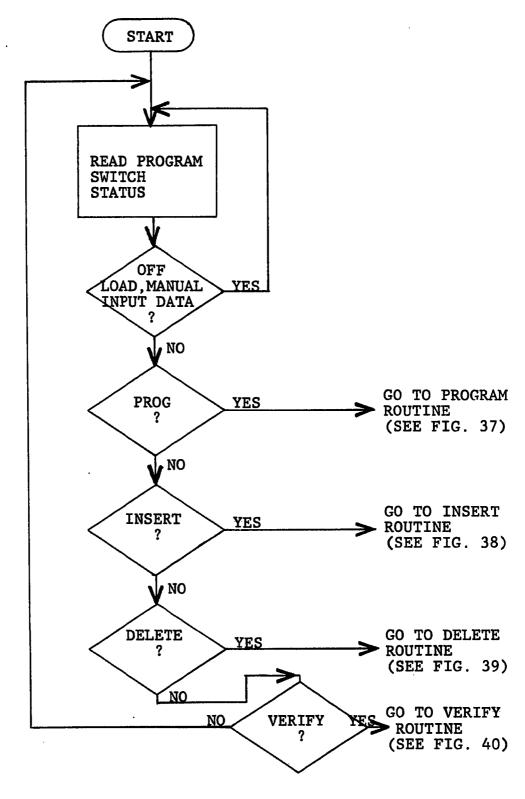

| 36. | Main Program Routine                                                      |

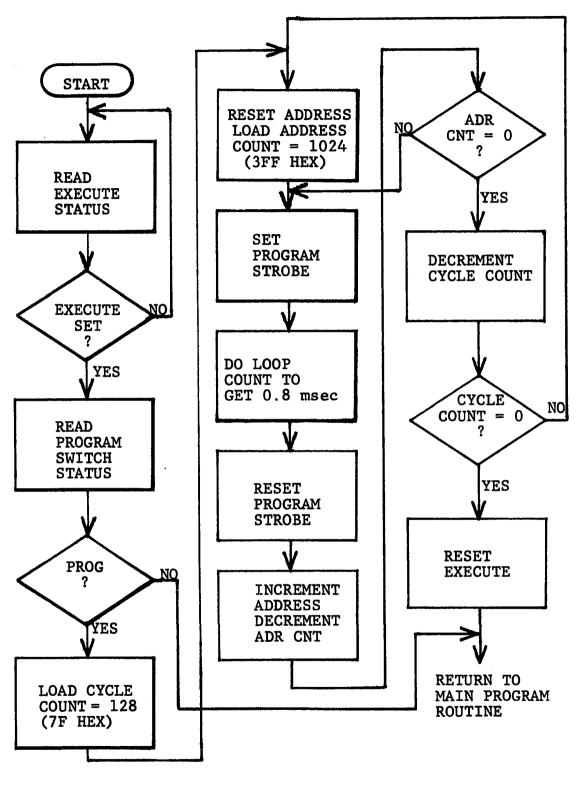

| 37. | Flowchart for Program Routine 88                                          |

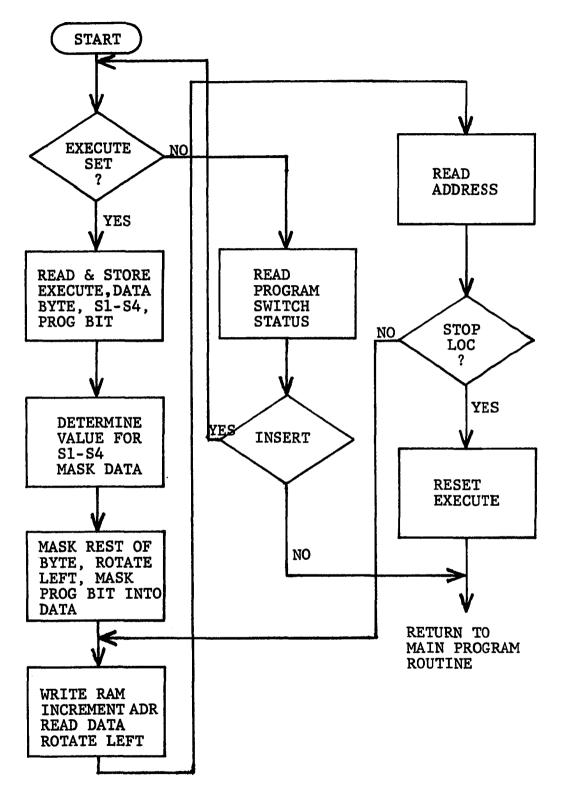

| 38. | Flowchart for Insert Routine 89                                           |

| 39. | Flowchart for Delete Routine 90                                           |

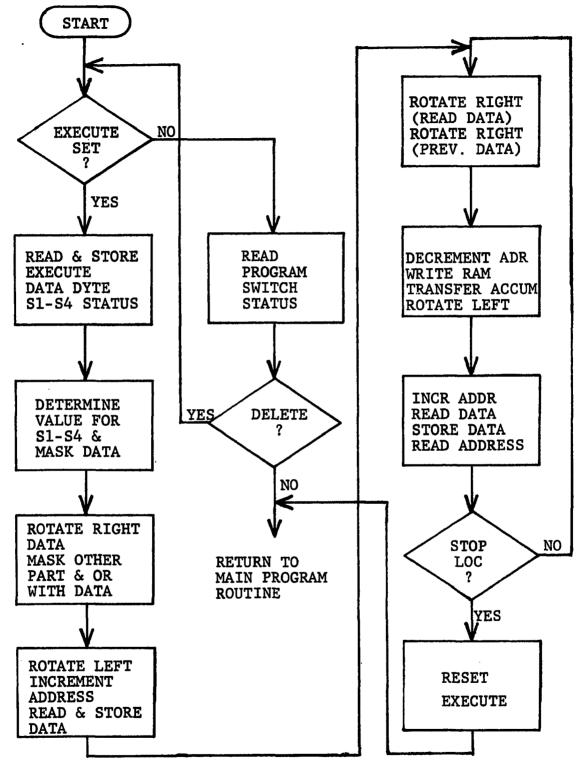

| 40. | Flowchart for Verify Routine 91                                           |

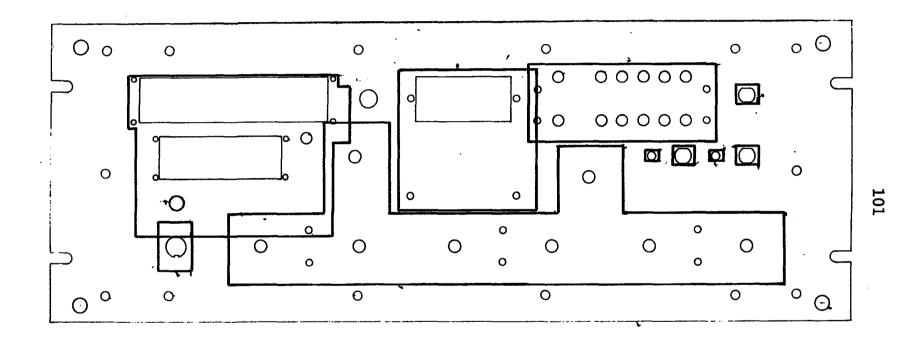

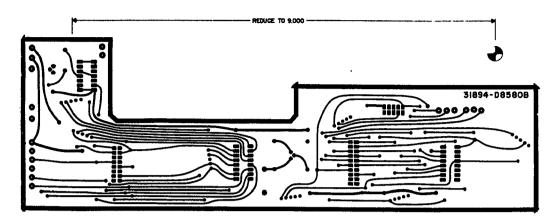

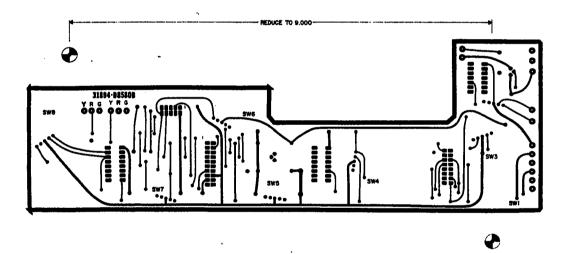

| 41. | Outline of Front Panel PWA on the DSA                                    | 101 |

|-----|--------------------------------------------------------------------------|-----|

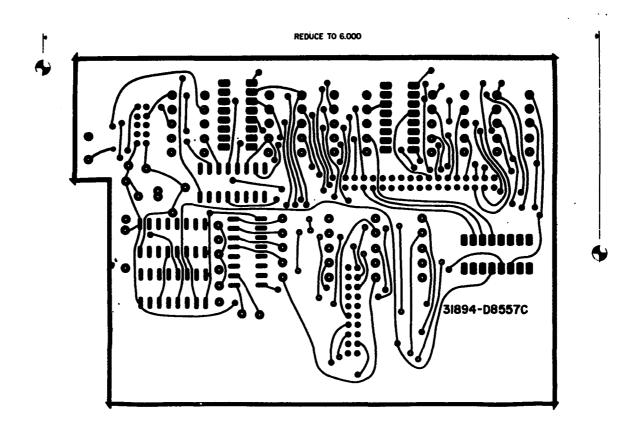

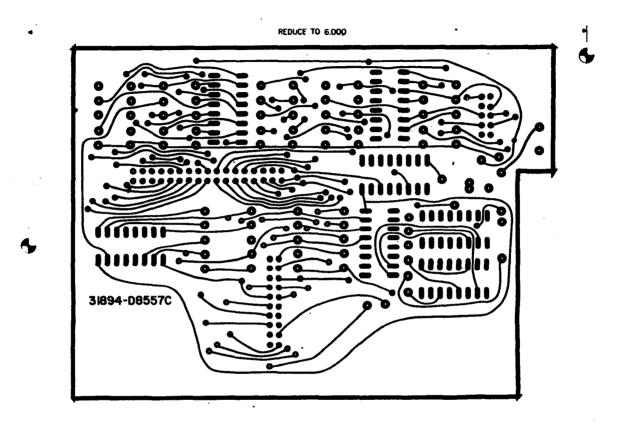

| 42. | Front Side Artwork for the DMG Front<br>Panel Thumbwheel Switch Assembly | 102 |

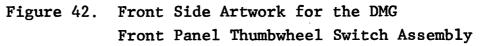

| 43. | Back Side Artwork for the DMG Front<br>Panel Thumbwheel Switch Assembly  | 103 |

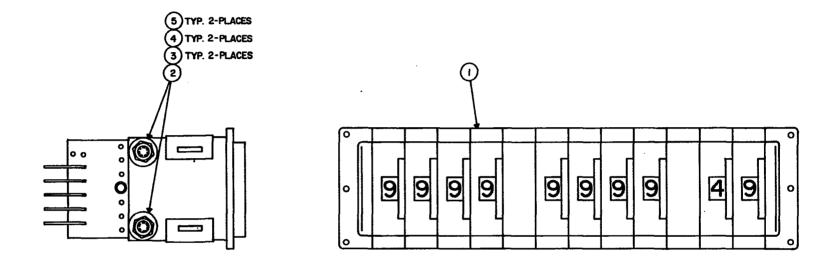

| 44. | Front Panel Thumbwheel Switch<br>Assembly for the DMG                    | 104 |

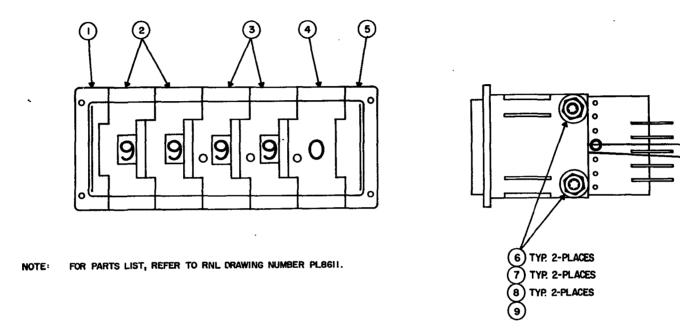

| 45. | Memory Location and Distortion<br>Thumbwheel Switch Assembly             | 105 |

| 46. | Baud Rate Thumbwheel Switch Assembly.                                    | 106 |

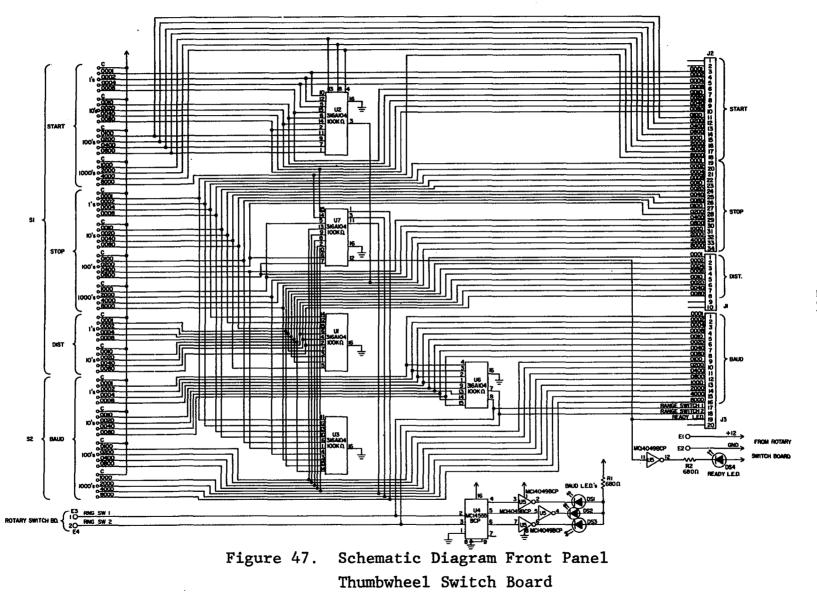

| 47. | Schematic Diagram Front Panel<br>Thumbwheel Switch Board                 | 107 |

| 48. | Back Panel Assembly for the DSA                                          | 108 |

| 49. | Front Side and Back Side Artworks<br>for Rotary Switch Assembly          | 109 |

| 50. | Front Panel Rotary Switch Assembly for the DMG                           | 110 |

| 51. | Front Panel Toggle Switch Assembly for the DMG                           | 111 |

| 52. | Schematic Diagram Toggle Switch<br>Assembly                              | 112 |

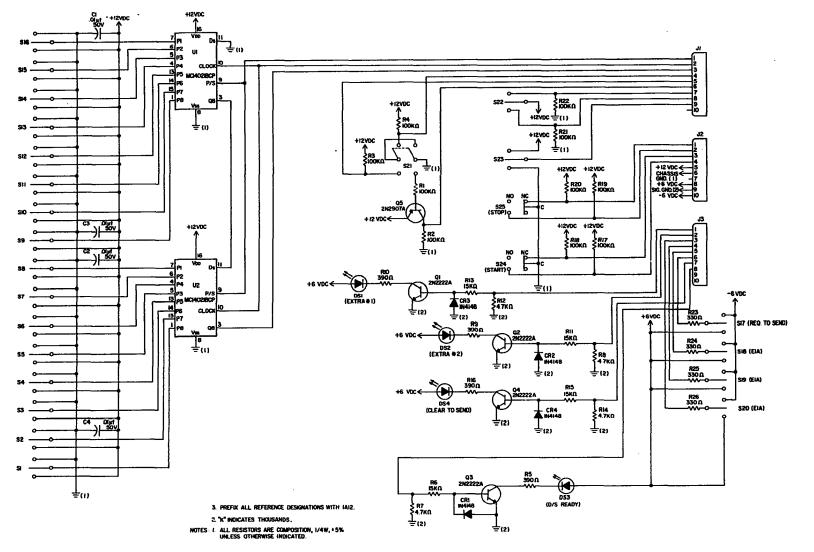

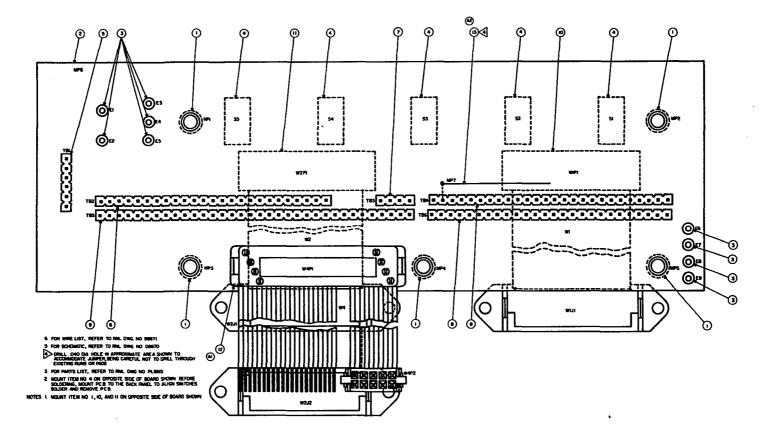

| 53. | Back Panel Switches and Input/Output<br>Assembly for the DMG             | 113 |

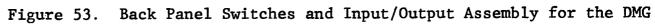

| 54. | Schematic Diagram Back Panel<br>Switches and I/O                         | 114 |

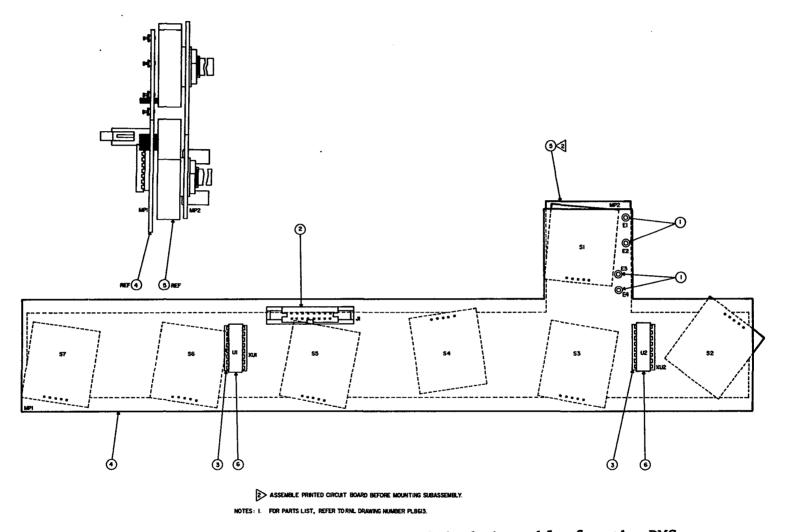

| 55. | Typical Arrangement of Assemblies                                        | 116 |

| 56. | PWA Arrangement in DMG                                                   | 117 |

| 57. | PWA Arrangement in DSA                                                   | 117 |

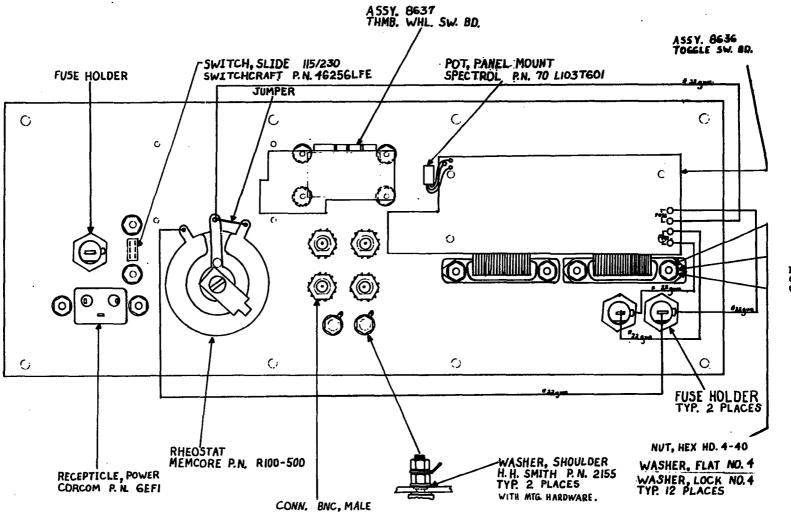

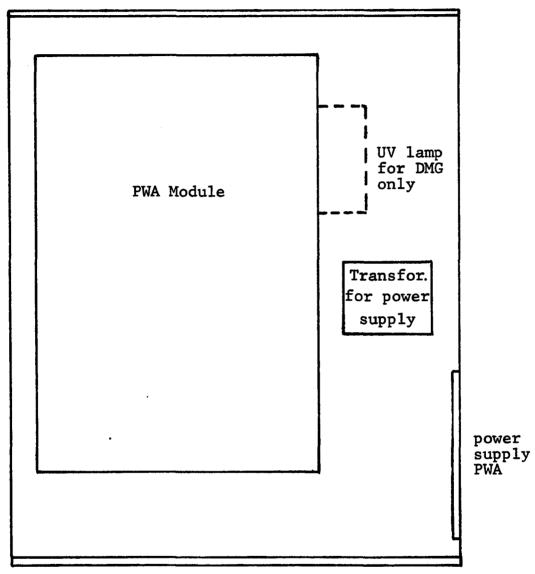

| 58. | Power Supply Assembly for the DMG                                        | 118 |

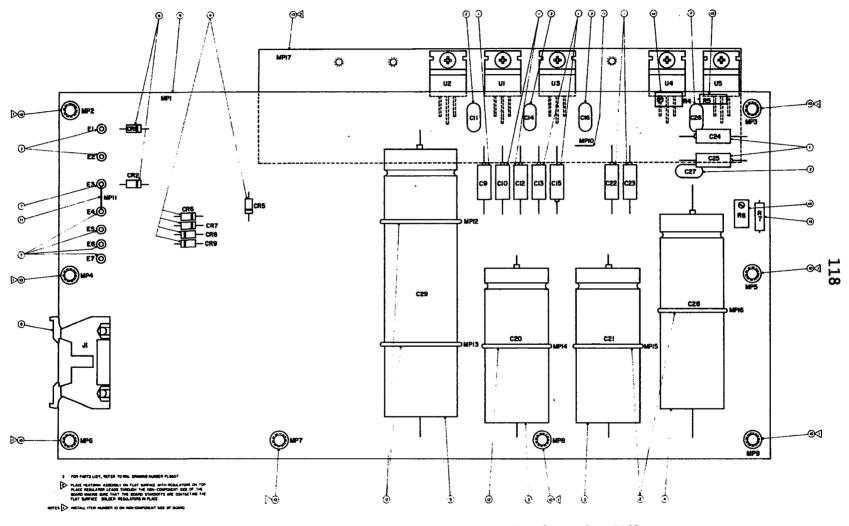

| 59. | Heatsink Assembly Power Supply Board<br>in the DMG                       | 119 |

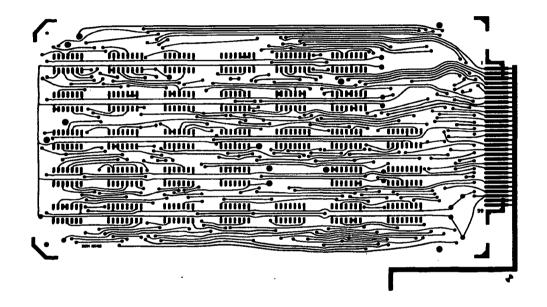

| 60. | Typical PWA Artwork Front Side                                           | 121 |

.

.

.

| 61. | Typical PWA Artwork Back Side                   | 122 |

|-----|-------------------------------------------------|-----|

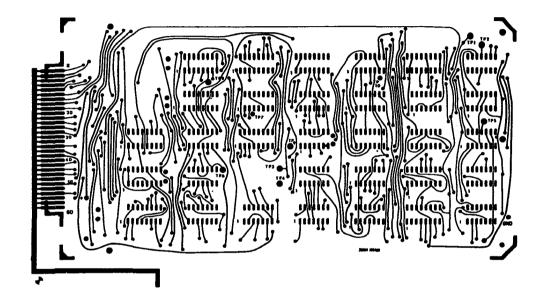

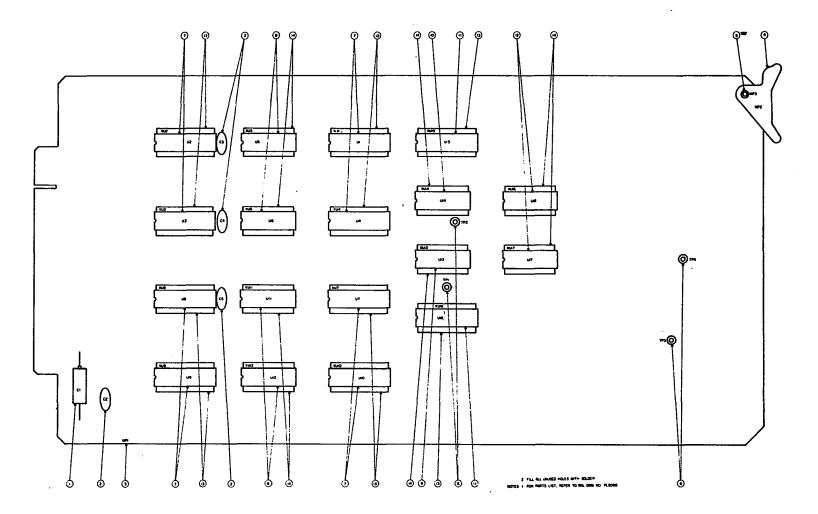

| 62. | Start/Stop Address PWA Assembly                 | 123 |

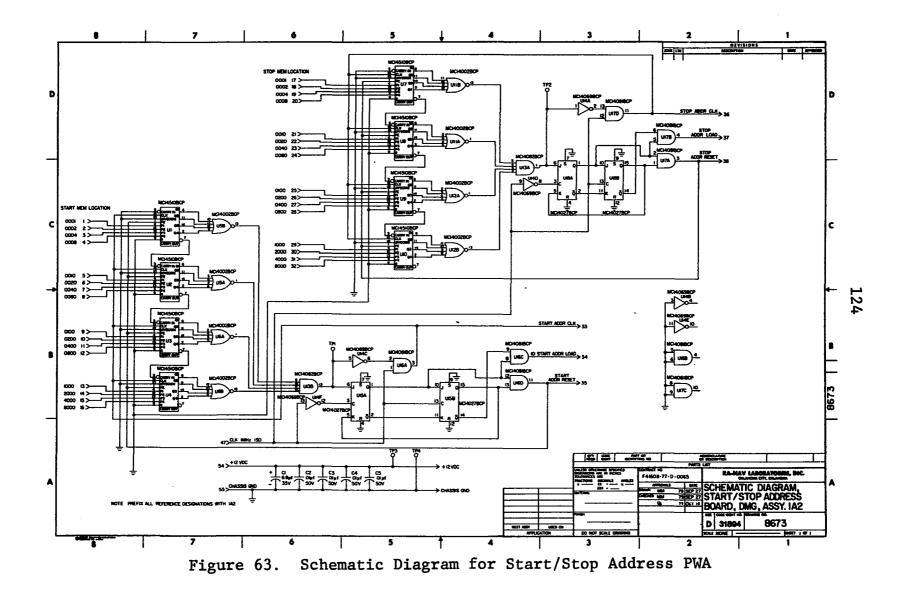

| 63. | Schematic Diagram for Start/Stop<br>Address PWA | 124 |

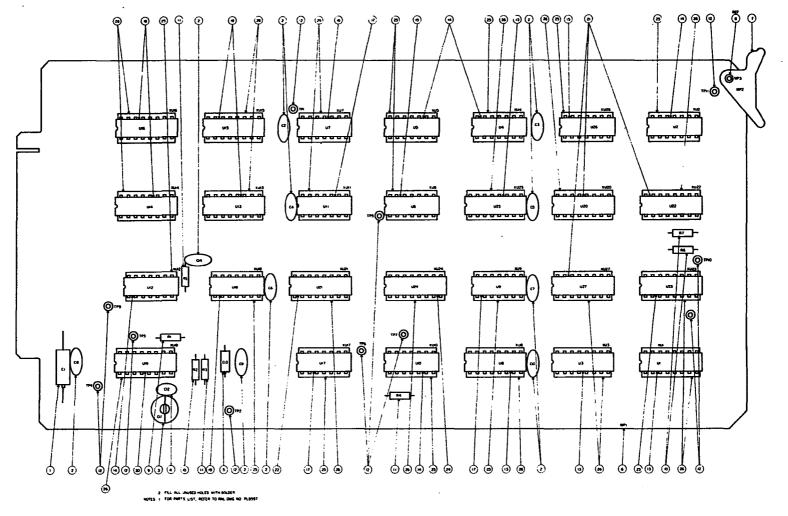

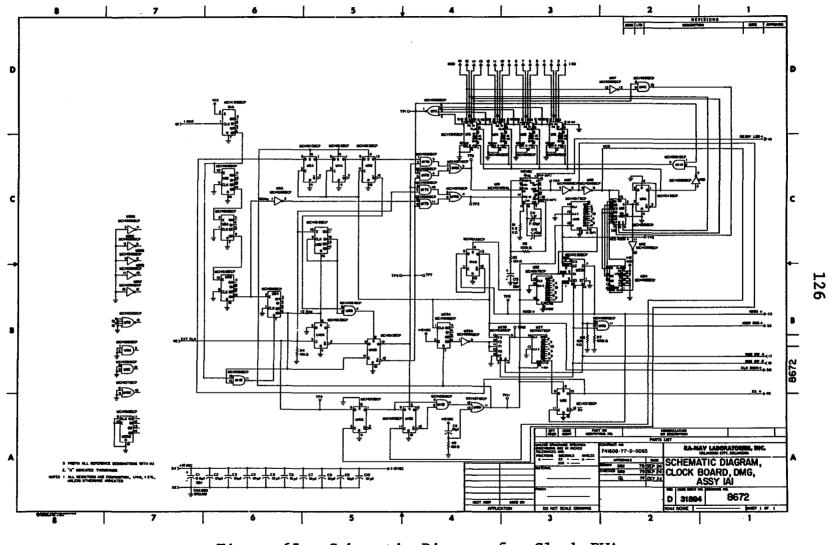

| 64. | Clock PWA Assembly                              | 125 |

| 65. | Schematic Diagram for Clock PWA                 | 126 |

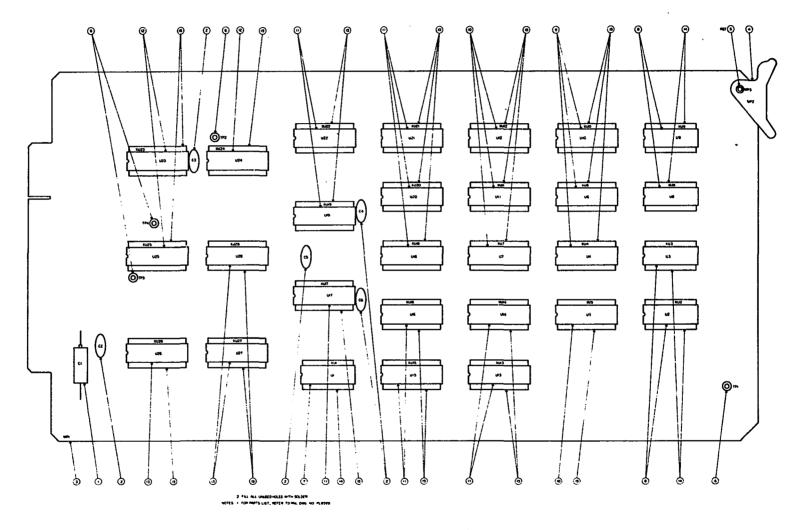

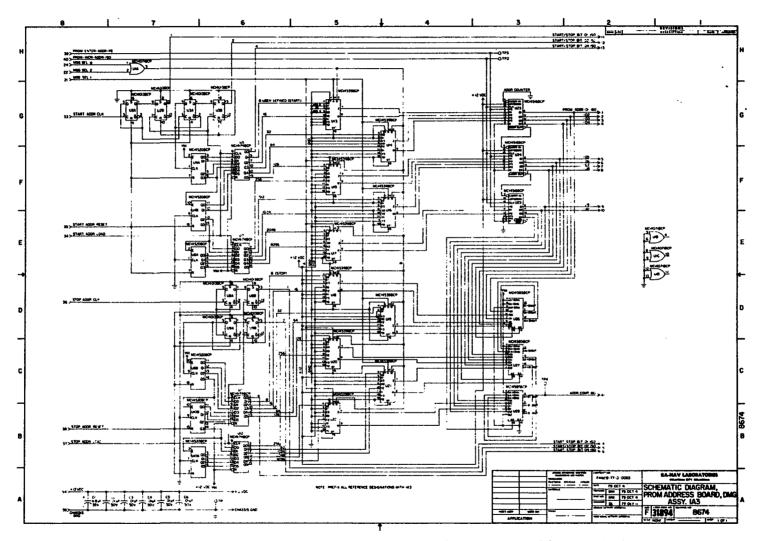

| 66. | PROM Address PWA                                | 127 |

| 67. | Schematic Diagram for PROM Address<br>PWA       | 128 |

| 68. | Extender PWB                                    | 129 |

#### ABSTRACT

This project was initiated as a United States Army contract, F41608-77-D-0065, which was awarded to Ra-Nav Laboratories. As a personal favor to John Perry, President of Ra-Nav Laboratories, I designed the logic for the Digital Data Analysis System. This is a high-speed serial data test system. This proposed design was presented and approved by my Doctoral Committee at the University of Oklahoma as partial fulfillment of the requirements for the degree of Doctor of Engineering in Electrical Engineering.

Before the design work started, there were preliminary meetings with the management of Ra-Nav Laboratories to discuss and define the interpretations of the design specifications. It was evident from the first meeting that the Army specifications were very vague. The management of Ra-Nav Laboratories felt that it was essential to begin the design work and would inform the Army Engineer of the problems at the monthly progress review meeting.

At the preliminary meetings between Ra-Nav and myself the structure of the design evolved. I proposed using either low-power Schottky TTL or CMOS logic to meet Ra-Nav requirements for no cooling fans. I also suggested using a

х

microprocessor which at the onset was rejected by Ra-Nav, but later was incorporated because of the changes in the specifications by the Army Engineer.

By the first monthly progress review meeting the Digital Message Generator logic was nearly completed. It was at this meeting that the Army Engineer was asked to clarify the specifications. Based on his suggestions, the following system was developed. One box would be the Digital Message Generator (DMG), while the second would be the Digital Signal Analyzer (DSA). The DSA was to include a PROM programmer. To meet the PROM programmer requirement, Ra-Nav planned to sell them a Data I/O PROM programmer.

This design was presented to and disapproved by the Army Engineer at the second monthly progress review meeting. The Army Engineer wanted the PROM programmer contained within the DSA. When Ra-Nav suggested repackaging the Data I/O programmer into the DSA, the Army Engineer again disapproved. He pointed out the following problems: The Data I/O was a word-structured PROM programmer, while he wanted a bitstructured programmer. He claimed that the hexadecimal addressing would cause problems for the testers and wanted a decimal address structure. It was at this time that Ra-Nav requested a change in the specifications to reflect the currently agreed upon changes in order that the design would have well defined goals.

The negotiations for the changes in the specifications

xi

took over ten months due to 88 pages of changes to the original 33-page specifications. During these negotiations work was continued in order not to delay the project any longer than necessary. The building of the prototypes was completed, along with most of the debug of the logic design and the printed circuit card artwork.

At the final negotiating session a new Army engineer inserted additional requirements for the PROM programmer. At this point I assessed his requests to determine whether or not they could be included in the design and proposed the following plans to Ra-Nav. The first plan was for a quickfix with minimum impact on schedule and projection, while the second would be the approach that would make the best possible system. The first method consisted of redesigning one printed wiring assembly by inserting a microprocessor. This method left all functions in the logic the same except for the programming function of the PROM programmer. The second method was to redesign three printed wiring assemblies into one or two, allowing the microprocessor to handle all the PROM programming features and some of the DSA operations.

Ra-Nav choose to use the first method, based on what they felt was the most economical solution from their position. They estimated that the cost to them to build one prototype printed wiring assembly was in the range of \$1200 to \$1500. They felt that the first method allowed them some return on their investment. It was agreed that, should

xii

another order be placed for additional units, Ra-Nav would propose the second method as a cost reduction. In doing this they could negotiate a cost reduction program and would receive one half the cost saving to use in the development of the new printed wiring assemblies.

It may sound as though this project was an association of problems generated by the original specifications; however, it is very representative of a typical project in industry. Problems are generated because the person who writes the specification has his own ideas and interpretations which are often different from those of the designer. In most situations a third party checks the designer's system against the specifications bringing about a third interpretation. I have experienced similar problems in projects at Magnetic Peripherals Incorporated.

My last project at MPI would appear to have been an ideal situation. I personally wrote the specifications for the system; the customer reviewed the specifications and made changes. I then designed the system to the specifications, tested it, and presented it to the customer. When he tested the system, however, he found that it did not perform as he had envisioned it would. Therefore, he requested specification changes which resulted in major system changes. Thus, even the most ideal situations result in some specification changes.

It is not my intent to belabor the problems which

xiii

were encountered in designing this system, but rather to describe the Digital Message Generator (DMG), the Digital Signal Analyzer (DSA), and the PROM programmer (a unique part of the DSA), with emphasis on their enhancements, functions, and unique problems. The design principles used and problems encountered are discussed in the chapter on construction and testing.

The first article (first ten units of the contract) has been built and the first system has completed acceptance testing by the Army engineers. This first system exceeded all specification requirements during acceptance testing. The rest of the first article units are now in acceptance testing and are performing satisfactorily.

During the final presentation to my doctoral committee a demonstration of the system was given which consisted of a DMG connected to an ASR-33 teletypewriter. The demonstration featured some of the modes of operation using the stored message (the quick brown fox) and the selected character. These modes of operation used the message release feature which included a single message, single character, and continuous message. The DMG was demonstrated by intermittently adding a single error to the message while it was printing. The distortion feature was demonstrated by changing the percent of distortion until the teletype failed to print the correct character. The last feature demonstrated the use of the DMG to punch a paper tape of the stored message

xiv

by changing the parity select switch on the DMG. Three tapes of the stored message were punched using odd parity, even parity, and mark parity. The three tapes were then comapred to show the difference in the parity bit positions.

#### I. INTRODUCTION

#### Scope and Purpose

This design was a test system for the United States Army under Contract No. F41608-77-D-0065 entitled Digital Data Analysis System. The contract had provisions for sixty units to be built. There were provisions for an additional fifty units for other branches of the services (Marines, Air Force, or Navy). The contract was based around the acceptance by the Army of ten qualification units. The first unit has now been built and is currently being tested for the first of ten qualification units.

The system will consist of two units: the Digital Message Generator (DMG) and the Digital Signal Analyzer (DSA). The equipment is to be used mainly in the test, repair, and evaluation of teletype machines, cryptograph equipment, and other terminal devices. The subsystems have evolved from previous test systems. They included features from their predecessors, enhancements, and new features. The DMG and DSA are related to the GGM-16 and GGM-21 test systems. The DSA and DMG contain most of the features from the GGM-16 and GGM-21, plus enhanced and new features, some

of which were beyond the state of the art when the GGM-16 and GGM-21 were designed.

GGM-16 Features

The GGM-16 was designed in 1969 using mostly discrete transistors with some SSI circuits. The GGM-16 has the following features:

- A 2047 bit (2<sup>11</sup> 1) pseudo-random pattern generator.

- One stored message in 5 bit Baudot code. The message is the "Quick Brown Fox" which is often used in typing drills.

- A series of bit reversal patterns which are

1:1, 2:2, 6:1, 1:6.

- 4. A selected character generated by setting the bit levels on switches on the front panel. The character will be generated from 4 to 8 bits in start/stop mode while it will be 16 bits in the synchronous mode.

- 5. The GGM-16 baud rates are shown in Table I.

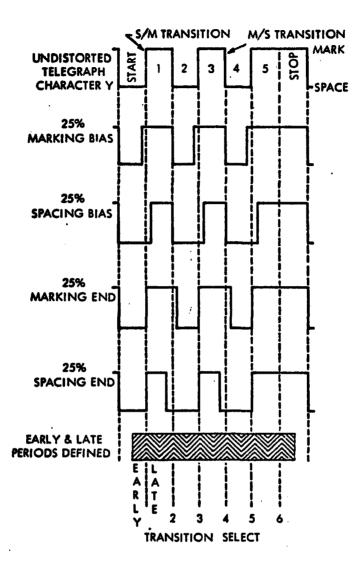

- Telegraph distortion generation and measurement was from 0% to 49% in 1% increments. Telegraph distortion is defined as transition displacement as shown in Figure 1 (see page 3).

- 7. Generates and measures the following types of telegraph distortion (transition displacement): marking and spacing bias; marking and spacing end;

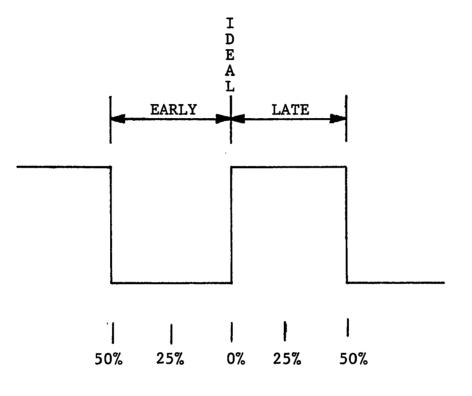

Figure 1. Types of Distortion

| TABLE : |

|---------|

|---------|

| AVAILABLE | BAUD | RATES       | FOR | THE | GGM-16 |

|-----------|------|-------------|-----|-----|--------|

| Low       |      | <u>High</u> |     |     |        |

| 37.5      |      | 150         |     |     | 1200   |

| 45.45     |      | 300         |     |     | 2400   |

| 50.0      |      | <b>600</b>  |     |     | 4800   |

| 60.12     |      |             |     |     | 9600   |

| 74.2      |      |             |     |     |        |

| 75.0      |      |             |     |     |        |

total peak; early peak; late peak. These types of distortion are shown in Figure 1.

. ....

8. Two types of inputs and outputs. One is the polar/neutral isolated inputs and outputs. This is for operation at 300 volts polar or 150 volts neutral at 100 milliamperes maxium loop current. The second is low level MIL-STD 188B input and output for operation at ±6 volts or ±12 volts with 20 milliamperes loop current.

9. Front panel display is a Nixie tube readout.

#### GGM-21 Features

The GGM-21 was designed in 1972 using SSI circuits with some functions built into LSI chips. These LSI special circuits were used for the 32k bit pseudo-random generators and ROM type memory. The GGM-21 has the following features:

1. A 32,768 bit pseudo-random pattern generator.

- Two stored messages, one in 5 bit Baudot code and the second in 8 bit ASCII code. The messages are the "Quick Brown Fox".

- 3. The GGM-21 has a series of bit reversal patterns which are 1:1, 2:2, 6:1, and 1:6. It has a switch control for constant mark and constant space.

- 4. A selected character can be generated by setting the bit levels on switches on the front panel. The character can be generated either from 1 to 16 bits in start/stop mode, or 1 to 16 in synchronous mode.

- The baud rates on the GGM-21 is from 30.0 in

1.0 increments to 9,999.0.

- Telegraph distortion (Figure 1) generation, and measurement is from 0% to 49% in 1% increments.

- 7. Generates and measures the following types of telegraph distortion (transition displacement): marking and spacing bias; marking and spacing end; total peak; early peak; late peak. These types of distortion are shown in Figure 1.

- 8. Two types of inputs and outputs. One is the polar/neutral isolated inputs and outputs. This is for operation at 300 volts polar or 150 volts neutral at 100 milliamperes maximum loop current. The second is low level MIL-STD 188B inputs and outputs for operation at +6 volts or +12 volts

with 20 milliamperes loop current.

9. Seven-segment LED display on the front panel.

#### DMG and DSA Features and Enhancements

The DMG and DSA systems include the features of the GGM-16 and the GGM-21 with enhancements, additional memory, and a PROM programmer. The following are the features of the DMG and DSA:

- Two pseudo-random pattern generators. One is 2047 bit like the GGM-16, but will be stored in EPROM memory. The second is 32,768 bit like the GGM-21, designed in digital logic.

- 2. Three stored messages:

- (a) A 8 bit ASCII code Quick Brown Box like the GGM-21.

- (b) A 5 bit Baudot code Quick Brown Fox like the GGM-16.

- (c) A user definable message anything that the user wishes to have.

- 3. A bit reversal pattern which is 1:1 (the other reversal patterns of the GGM-21 were deleted because they were never used), and either a constant mark or constant space.

- 4. A selected character generated by setting the bit levels on switches on the front panel. The character can be generated either as 4 to 16 bits in the start/stop mode or as 4 to 16 bits in the

synchronous mode.

- 5. The baud rate on the DMG and DSA is from 30.0 in increments of 0.1 baud to 9,999.0 and from 10,000 in increments of one baud to 99,990.

- 6. Telegraph distortion (Figure 1) generation, and measurement is from 0% to 49%. For baud rates from 30.0 to 9,999.0 the distortion is in 1% increments. For baud rates from 10,000 to 99,990 the distortion is in 5% increments.

- 7. Generates and measures the following type of telegraph distortion: marking and spacing bias; switch bias; total peak; early peak; late peak.

- 8. Two types of inputs and outputs. One is the polar/neutral isolated inputs and outputs. This is for operation at 300 volts polar or 150 volts neutral at 100 milliamperes maximum loop current. The second is low level MIL-STD 188B inputs and outputs for operation at ±6 volts with 20 milli-amperes loop current. There is a switch control-lable 2 kHz low pass input filter. This filter can be switched in or out from 30.0 up to 199.9 baud. It is automatically switched out at 200 baud and above.

- 9. Seven-segment LED display on the front panel.

- 10. A PROM programmer is contained in the DSA capable of programming 2708 EPROMs. The programmer has

the following features:

- (a) A copy mode of operation where a previously programmed EPROM can be copied.

- (b) A manual mode of operation where any single bit or group of bits in memory can be changed by operation of a switch. There is a display for viewing contents of that bit.

- (c) An auto-in mode where a data stream can be programmed into bit locations defined by the start and stop address switches.

- (d) The memory is designed so that the unprogrammed area may be programmed without erasing and reprogramming the entire memory.

- 11. There are three additional features designed into the PROM programmer at the request of the Army engineer which are not currently shown in the design specifications:

- (a) A delete mode where any bit or bits can be deleted from memory and the programmed bits above moved downward leaving the unprogrammed area at the top.

- (b) An insert mode where any bit or bits can be inserted into memory and the previously programmed bits above moved upwards into unprogrammed area of memory.

- (c) A verify mode where the contents of an

EPROM can be verified against another EPROM or the EPROM that has just been reprogrammed.

12. The memory is accessible from any specified bit location to any other specified bit location. This area of memory is defined by the start/stop switches. An additional requirement is that no bits in memory will be unusable.

The most significant enhancement to the GGM-16 and GGM-21 is the PROM programmer and all its modes of operations as described in items 10, 11 and 12 above. This enhancement-itself a system--represents a large portion of the DSA and a full discussion is provided in Chapter IV. While the PROM programmer is the largest single enhancement, many of the other features of the GGM-16 and GGM-21 were enhanced in the DMG and DSA.

Item 1 which is the pseudo-random pattern generators from the GGM-16 and GGM-21 had minor enhancements; namely, the addition of a 2708 EPROM memory and the storage of the 2047 pseudo-random pattern in the EPROM.

Item 2(c) is an enhancement to the messages. This enhancement adds versatility to the test system by allowing the tester to use any message he desires up to 8k bits.

Items 5 and 6 represent another significant enhancement, that of increasing the speed of the data by a factor of 10 while keeping distortion measurements at the same percentage. The baud rate for the DMG and DSA are specified

as two ranges. The first range is the same as for the GGM-21 and includes those specific baud rates of the GGM-16 as shown in Table I; therefore, the second range is the enhancement.

The last enhancement is in item 8, that of the 2 kHz low pass input filter. The filter is controlled by a switch (in or out) up to 199.9 baud and is automatically switched out for any baud rate greater than 200 baud.

### Design Preparations

A large amount of the preparation for the design required reviewing several logic data books to optimize the logic design. Among these were the CMOS handbooks,<sup>1,2</sup> Low-Power Schottky data handbook,<sup>3</sup> and microprocessor handbook.<sup>4</sup> In addition to these I reviewed some text books on the design of phase-locked loops<sup>5,6</sup> and data transmission.<sup>7</sup> Other

<sup>4</sup>Motorola Technical Information Center, <u>The Complete</u> <u>Motorola Microcomputer Data Library</u>, Series A (Phoenix: <u>Motorola Incorporated, 1978)</u>, pp. 1-36 - 1-55.

<sup>5</sup><u>RCA COS/MOS Integrated Circuits</u>, pp. 150-153.

<sup>6</sup>Motorola Technical Information Center, <u>Motorola CMOS</u> <u>Integrated Circuits</u>, pp. 7-124 - 7-128.

<sup>&</sup>lt;sup>1</sup>Motorola Technical Information Center, <u>Motorola CMOS</u> <u>Integrated Circuits</u>, Series C (Phoenix: Motorola Incorporated, 1978), pp. 4-3 - 5-5.

<sup>&</sup>lt;sup>2</sup><u>RCA COS/MOS Integrated Circuits</u> (Somerville, N.J.: RCA Corporation, 1977), pp. 34-49.

<sup>&</sup>lt;sup>3</sup>Motorola Technical Information Center, <u>Motorola Low-</u> <u>Power Schottky TTL</u>, Series B (Phoenix: Motorola Incorporated, 1977), pp. 1-2 - 2-8.

<sup>&</sup>lt;sup>7</sup>William R. Bennett and James R. Davey, <u>Data Trans</u>-<u>missions</u> (New York: McGraw-Hill, 1965), pp. 260-267.

reference sources included application notes.<sup>8,9</sup> This was my first design using CMOS logic. Since completing this design, I have used Low-Power Schottky in designs at MPI. I shall describe later in this chapter my reasons for choosing to use the CMOS logic.

The first step in the design required the selection of the logic family from which the system would be designed. The choice of logic family appeared to be one of three: one was  $T^2L$  Low-Power Schottky circuits; the second was CMOS; the third was the LSI type of  $I^2L$  (Ion Injection Logic) which would make the logic special purpose, similar to some of the circuits in the GGM-21. The  $I^2L$  was dropped due to the cost per system and lead time requirements for this design. The contract was for 60 units; thus, cost effectiveness could not be met with the  $I^2L$ .

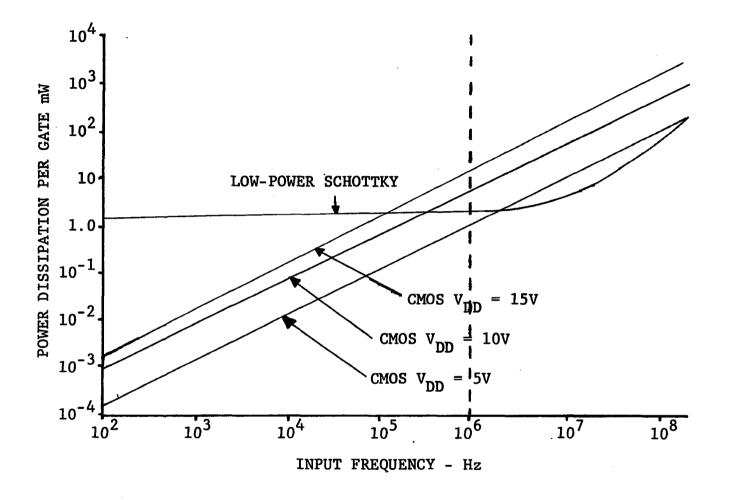

A secondary consideration was a clause regarding heat inside the units. Should the logic consume too much power, the units would require a cooling fan. This would also increase the cost of the units. Figure 2 (page 12) is a graph of power dissipation comparing Low-Power Schottky to CMOS. The maximum frequency in the system will be 10<sup>6</sup> Hz. Only a small amount of the logic would be required to run at

<sup>&</sup>lt;sup>8</sup>Marvin K. Vander Kooi, ed., Linear Applications, Vol. 1 (Santa Clara, Calif.: National Semiconductor Corporation, 1973), pp. AN46-1 - AN46-12.

<sup>&</sup>lt;sup>9</sup>Forest L. Sass, ed., <u>Linear Applications</u>, Vol. 2 (Santa Clara, Calif.: National Semiconductor Corporation, 1976), pp. LB30-1 - LB30-2.

Figure 2. Low-Power Schottky vs CMOS Power Requirements

this frequency. Thus, assuming some Gaussian distribution of frequencies, the CMOS would require less power.

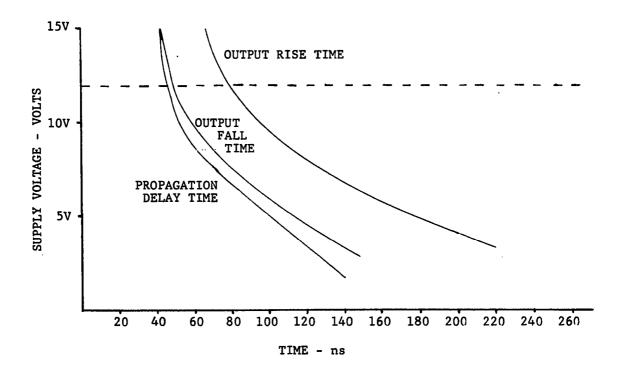

The CMOS has a disadvantage in regard to rise, fall, and propagation time. Figure 3 (shown below) is a graph of time delays for a typical gate of CMOS. From Figure 3 the operating voltage of +12 volts was chosen. In the +12 V range the rise, fall, and propagation times are near ideal values for CMOS. An advantage of CMOS is the larger scale of integration and larger selection of complex functions. This advantage allowed a reduction in number of chips, thus reducing the number of printed wiring assemblies (PWAs) needed in the units.

Figure 3. CMOS Rise, Fall, and Propagation Time

#### **II. DIGITAL MESSAGE GENERATOR**

#### Physical Description

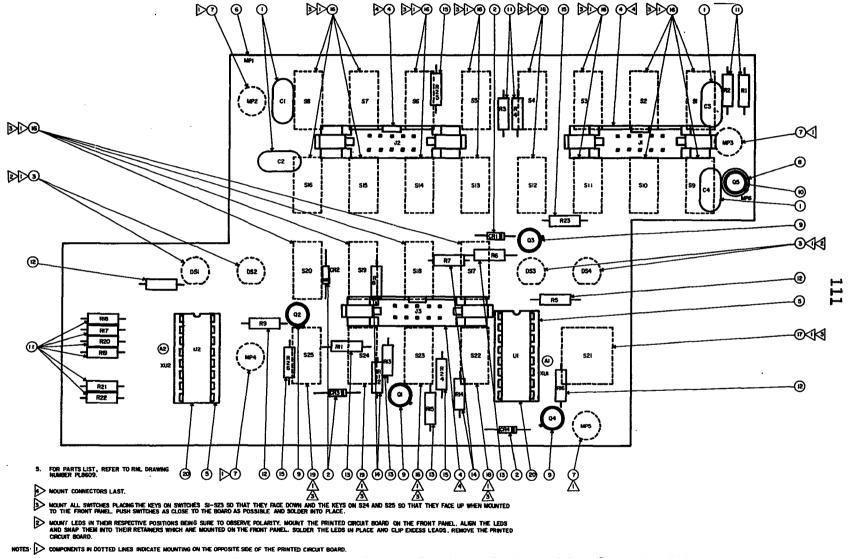

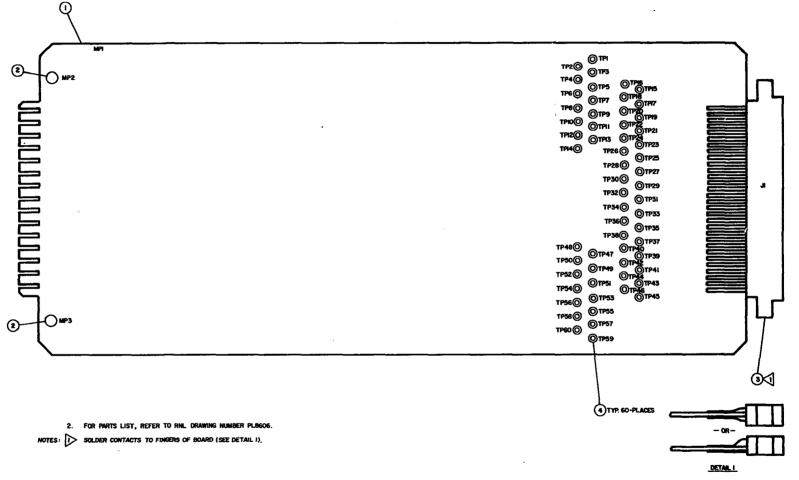

The DMG has nine printed wiring assemblies (PWAs) inside the unit. These PWAs are five inches high and ten inches long with a 60 pin connector on one end. These PWAs can have a maximum of 34 integrated circuits. (The DSA has twelve of these PWAs.)

The PWAs were made this size in order that they could slide into a PWA rack inside the seven inch high unit. The front panel of the unit is hinged which enables it to drop forward in order that the PWAs can be replaced if necessary, or placed on an extender card for testing.

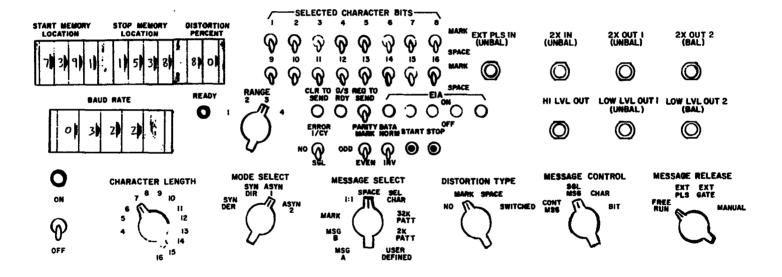

Figure 4 (page 15) is the front panel for the DMG. The switches on the panel are all mounted on printed wiring boards (PWBs). The PWAs are then mounted to the front panel. The PWAs have mass termination connectors in order that the ribbon cable can be routed to the logic. The thumbwheel switches are for the start memory location, stop memory location, and the distortion percent. The first four thumbwheel switches are the START ADDRESS. These are valid for decimal numbers from 0000 to 8191. Any setting beyond the 8191 is an invalid address. The STOP ADDRESS switches are

.

.

Figure 4. Front Panel of the DMG

the next four switches. Their function is similar to the start switches except they are the stop address. The start/stop switches together define the portion of the memory which is to be used for generation of test data.

The next two thumbwheel switches are the DISTORTION PERCENT switches. These determine the percentage of distortion (from 0 to 49%) that the output signal has had added to the ideal output signal. The type of distortion is determined by the distortion type switch. There are four positions on this switch to select the following types:

- NO This selection will cause no distortion in the generated signal.

- 2. MARK This will cause mark bias distortion (Figure 1) to be induced into the generator output signal to the percentage shown on the thumbwheel switches.

- 3. SPACE This will cause space bias distortion (Figure 1) to be induced into the generator's output signal to the percentage shown on the thumbwheel switches.

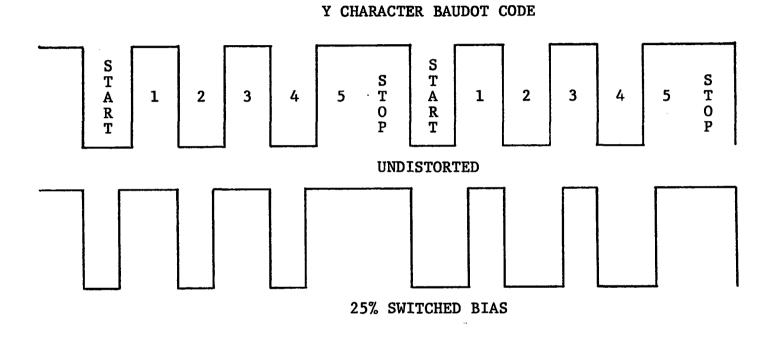

- 4. SWITCHED This will cause switched bias distortion to be induced into the generator signal to the percentage shown on the thumbwheel switches. Switched bias is first one character with mark bias then one character with space bias. Figure 5 (page 17) shows

.

.

Figure 5. Switched Bias Distortion

.

how two characters would be affected by switched bias.

The last set of thumbwheel switches are the BAUD There are five switches which determine the RATE switches. baud rate of the master clock. In conjunction with the thumbwheel switches is the RANGE switch which is a multiplier for the thumbwheel switches. The baud rate is specified to operate between 30 and 99,990 baud; however, the logic will operate at any baud rate set on the switches. The lower baud rates below 30 baud are considered error conditions and are not required to meet clock jitter requirements. To aid the test technician LEDs are mounted inside and near the bottom of each thumbwheel switch. The RANGE switch logic illuminates the correct LED for a decimal point. Thus, the technician can take a direct reading of the baud rate selected by both the thumbwheel switches and the range rotary switch.

The LED between the BAUD RATE switches and the RANGE switch is the "Ready" indicator. This illuminates when the conditions on the front panel have been satisfied by the logic. If the "Ready" LED has not illuminated within 20 seconds, some setting on the panel is incorrect.

The sixteen toggle switches are the SELECTED CHARACTER BITS. These are set for the desired bit pattern for a character and when the MESSAGE SELECT switch is in "Sel Char" the bit pattern is transmitted. The character can be from

4 bits to 16 bits long depending on the setting on the CHARACTER LENGTH switch. These work either in the asynchronous (start/stop) mode or in the synchronous mode. The mode is determined by the setting on the MODE SELECT switch. The synchronous mode is a continuous stream of bits. There are two types of synchronous modes. One is a direct (external) 2X clock while the second is a derived (internal) 2X clock. These are indicated by "Syn Dir" for the external 2X clock and "Syn Der" for the internal 2X clock. The asynchronous (start/stop) mode has two choices. The first, "Asyn 1", has only one stop bit. The second, "Asyn 2", has two stop bits.

The message switches are the controls for the pattern that will be generated by the DMG. The message select switch defines the message to be generated into a data stream. The switch has nine positions and has the following names.

First, the "Msg A" position is a message used as a typing drill which uses all the characters in the alphabet. The message is called the "Quick Brown Fox." The message will print on the teletype or printer as follows:

(carriage return line feed)

TEST DE (7 "deletes" 5 "spaces")

(carriage return line feed)

THE QUICK BROWN FOX JUMPS OVER THE LAZY DOG

(3 "spaces") 1234567890 TIMES END (20 "spaces") Message A is an eight bit ASCII code as shown in Figure 6

| BIT 7 |           |             | •        | •   | 1        |       |          |       |       |

|-------|-----------|-------------|----------|-----|----------|-------|----------|-------|-------|

| BIT   |           | •           |          | •   | BIT 1    | BIT 2 | BIT 3    | BIT 4 | BIT 5 |

|       | NULL      | SP          | (â)      |     |          |       |          |       |       |

|       | SOH       | 1           | A        | a   | ٠        |       |          |       |       |

|       | STX       | 10          | В        | b   |          | •     |          |       |       |

|       | ETX       | 7           | C        | С   | •        | •     |          |       |       |

|       | EDT       | 5           | D        | d   |          |       | •        |       |       |

| •     | ENQ       | %           | E        | е   | •        |       | •        |       |       |

|       | ACK       | 8           | F        | f   |          | •     | •        |       |       |

|       | BELL      | 1           | G        | g   | •        | •     | •        |       |       |

|       | BS        | (           | Н        | h   |          |       |          | •     |       |

|       | HT/SK     | )           | 1        | i   | •        |       |          | •     |       |

|       | LF        | *           | J        | i   |          | •     |          | ٠     |       |

|       | VT        | +           | K        | k   | •        | •     | [        | •     |       |

|       | FF        | 1           | L        |     |          | [     | •        | •     |       |

|       | CR        | -           | M        | m   | •        |       | •        | •     |       |

|       | SO        |             | N        | n   |          | •     | •        | •     |       |

|       | S1        | 17          | 0        | 0   | •        | •     | •        | •     |       |

|       | DLE       | 0           | P        | Р   |          |       | I        |       | •     |

|       | DCI       | T î         | Q        | 9   | •        |       |          |       | ٠     |

|       | DC2       | 2           | R        | r   | <u> </u> | •     |          |       | •     |

|       | DC3       | 3           | S        | 5   | •        | •     | <u> </u> |       | ٠     |

|       | DC4(STOP) | 4           | T        | t   | ľ        |       | •        |       | •     |

|       | NAK       | 5           | U        | U   | •        |       | •        |       | •     |

| •     | SYNC      | 6           | V        | V   |          | •     | •        |       | •     |

|       | ETB       | 7           | W        | w   | •        | •     | •        |       | •     |

|       | CAN       | 8           | X        | ×   |          |       |          | •     | •     |

|       | EM        | 9           | <u>Y</u> | Ιy_ | •        |       |          | •     | •     |

|       | SUB       |             | Z        | Ż   |          | •     | L        | •     | •     |

|       | ESC       | L           |          | 1   | •        | •     | 1        | •     | •     |

|       | FS        | <           |          |     |          |       | •        | •     | •     |

|       | GS        |             |          | )   | •        |       | •        | •     | ٠     |

|       | RS        | <u>&gt;</u> |          | ~   |          | •     | •        | •     | ٠     |

|       | US        | ?           |          | DEL | •        | •     | •        | •     | •     |

ASCII CODE

• is Mark or 1

Figure 6. ASCII Code Table

(page 20) and is stored in the PROM. The PROM addresses are selected by the selection of the "Msg A" position on the MESSAGE SELECT switch.

Message B is the same "quick brown fox" message; however, it is in five-bit Baudot code (see Figure 7, page 22). Again the message is stored in the PROM and the addresses are selected by the positioning of the MESSAGE SELECT switch to "Msg B". The next three positions are test signals. "Mark" is a continuous mark. The length of the mark is controlled by the CHARACTER LENGTH switch with start and stop bits in the asynchronous mode. "1:1" is a string of reversals; that, one mark followed by a single space followed by another mark. The length is determined by the CHARACTER LENGTH switch. The start and stop bits are inserted in the asynchronous mode. In the asynchronous mode the CHARACTER LENGTH switch will determine when the stop and start bits are generated. The third position is "Space" which is a continuous space just like the "Mark" described above.

The last three positions on the MESSAGE SELECT switch are patterns. The first, a 32k pseudo-random pattern  $(2^{15} \text{ bits})$ , is generated by logic. The second, a 2k pseudorandom pattern  $(2^{11} - 1 \text{ bits})$ , is in the PROM and the addresses are selected by the logic. The last position is "User Defined". "User Defined" is the portion of the PROM addresses above the location of the message A, B, and 2k

| UPPER          | LOWER       | BIT | BIT | BIT      | BIT   | BIT |

|----------------|-------------|-----|-----|----------|-------|-----|

| CASE           | CASE        | 1   | 2   | 3        | 4     | 5   |

| CASE           |             |     |     | 3        | 4     |     |

|                | A           | •   | •   |          |       |     |

| ?              | B<br>C      | •   |     |          | •     | •   |

| <u> </u>       | <u> </u>    |     | •   | •        | •     |     |

| <u>\$</u><br>3 | D           | •   |     |          | •     |     |

|                | E           | •   |     |          |       |     |

|                | F           | •   |     | •        | •     |     |

|                | G           |     | •   |          | •     | •   |

| STOP           | H           |     |     | •        |       | •   |

| a              |             |     | •   | •        |       |     |

| 1              | J           | •   | •   |          | •     |     |

| <u> </u>       | ĸ           | •   | . • | . •      | •     |     |

|                | L           |     | •   |          |       | •   |

|                | M           |     |     | •        | •     | •   |

| ,              | N           |     |     | •        | ٠     |     |

| 9              | 0           |     |     |          | •     | •   |

| 0              | Р           |     | •   | • •      |       | •   |

| 1              | Q<br>R<br>S | ٠   | •   | •        |       | •   |

| 4              | R           |     | •   |          | •     |     |

| BELL           | S           | •   |     | ٠        |       |     |

| 5              | T           |     |     |          | :<br> | •   |

| 7              | υ           | •   | •   | •        |       |     |

|                | V           |     | •   | •        | ٠     | •   |

| 2              | W           | •   | •   | L        | :     | •   |

| 1              | X           | •   | · · | •        | •     | •   |

| 6              | Y           | •   |     | •        | •     | •   |

|                | Z           | •   | L   |          | İ     | •   |

| BLANK          | BLANK       |     |     |          |       |     |

| C.R.           | C.R.        |     |     |          | •     |     |

| L.F.           | L.F.        | L   | •   | <u> </u> |       |     |

| SPACE          | SPACE       | i   |     | •        |       |     |

| LTH SHIFT      | LTH SHIFT   | •   | •   | •        | •     | •   |

| FIG SHIFT      | FIG SHIFT   | •   | •   | 1        | •     | •   |

# BAUDOT CODE

• is Mark or 1

Figure 7. Baudot Code. Table

pattern. They are selected from the start/stop switches as described in Table II (shown below). "User Defined" can be any or all of the PROMS. This position allows special PROMS to be installed with special messages or test patterns which the test technician wishes to use for his tests. A detailed description of this function is included in the PROM programmer chapter.

## TABLE II

### MEMORY ADDRESS FOR PROM

| Msg Sel<br><u>Sw Positions</u> | Start Byte<br><u>Address</u> | Stop Byte<br><u>Address</u> | Start Sw<br>Setting | Stop Sw<br><u>Setting</u> |

|--------------------------------|------------------------------|-----------------------------|---------------------|---------------------------|

| Message A                      | 0                            | 127                         | 0                   | 1023                      |

| Message B                      | 128                          | 207                         | 1024                | 1663                      |

| 2k Pattern                     | 208                          | 719                         | 1664                | 5759                      |

| User Defined                   | 720                          | 1023                        | 5760                | 8191                      |

The MESSAGE CONTROL switch is used to control the method by which the message will be generated. It also works in conjunction with the MESSAGE RELEASE switch. The MESSAGE CONTROL switch has four modes. The first is "Cont Msg" (continuous message) which causes a repeat of the message each time it has cycled through the programmed length. The second is "Sgl Msg" (single message). Only one complete message is generated each time the switch is pushed or one of the MESSAGE RELEASE switch options is used. The third position is "Char" (character). Only a single character is generated for each operation. The fourth position is "Bit". This releases a single bit for each operation.

The MESSAGE RELEASE switch is used to determine the method by which the MESSAGE CONTROL is started. "Free Run" is the first position and causes the logic to run unrestricted. The "Ext Pls" (external pulse) position allows the message to start when an external pulse is applied. The "Ext Gate" (external gate) allows the message to run while the gate signal is high. The last position, "Manual", allows the start and stop buttons to be operated for a message to be generated.

There are some special function switches on the front panel used for different types of tests. The ERROR 1/CY (error one per cycle) switch is a three position switch which induces a single error, no error, or errors at the rate of one per each cycle. The down position will induce a single error in the message data stream. The up position causes an error to be induced with each cycle. The error is induced once for each message or once per character when the MESSAGE SELECT switch is in the "Sel Char" (selected character) position. The center position causes no errors to be induced in the data stream.

The second switch is also a three position switch used for parity. The center position is for "Odd" parity while the down position is for "Even" parity. The up

position is called "Mark" which causes a mark to be transmitted for the parity bit. The last special switch is the DATA switch. The up position is "Norm" (normal data); in the down position the data stream is "Inv" (inverted).

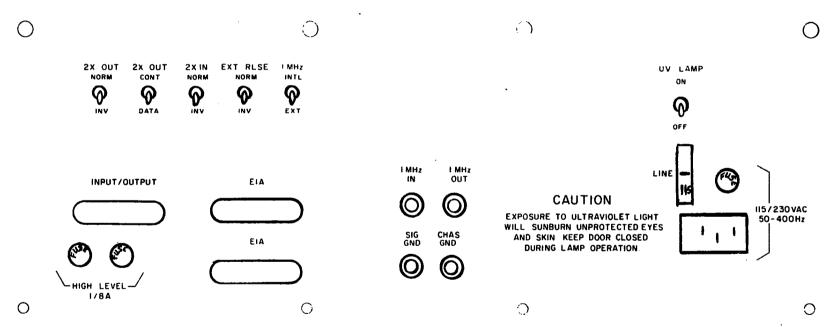

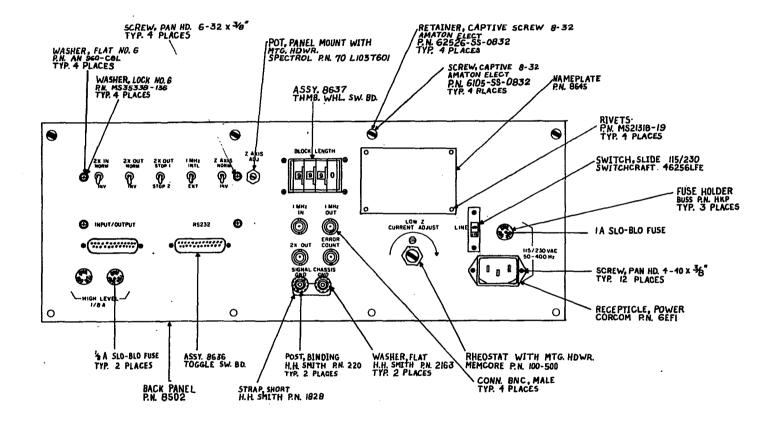

Figure 8 shows the back panel of the DMG. The switches at the top are for the system clocks. The bit rate clock is called the 2X clock while the master clock is 1 MHz (one Megahertz). The switch 2X OUT in either "Norm" or "Inv" position causes the 2X clock output signal on the front panel jack to be normal for "Norm" or inverted for "Inv". The second 2X OUT switch in the "Cont" position selects the bit rate clock or in the "Data" position selects the data stream to be the output. The 2X IN switch in "Norm" or "Inv" indicates which way the input 2X signal is used, either normal ("Norm") or inverted ("Inv"). The EXT PLSE switch in "Norm" or "Inv" indicates the normal ("Norm") or inverted ("Inv") pulse used to trigger events in the generator. The last switch, 1 MHz, selects the master clock either internal ("Intl") or external ("Ext").

The back panel is hinged for inserting a PWA inside the generator when the ultraviolet lamp is used to erase the EPROMs. The EPROMs are placed inside the DMG cabinet, the back panel is closed, and the UV lamp is turned on. After twenty minutes the EPROMs will have completed the erasure process and are ready for programming.

The power input is 115 VAC or 230 VAC from 50 to

# PLEASE NOTE:

| way | all cases this material has been filmed in the best possible<br>from the available copy. Problems encountered with this<br>ument have been identified here with a check mark <u>/</u> . |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.  | Glossy photographs                                                                                                                                                                      |

| 2.  | Colored illustrations                                                                                                                                                                   |

| 3.  | Photographs with dark background                                                                                                                                                        |

| 4.  | Illustrations are poor copy                                                                                                                                                             |

| 5.  | Print shows through as there is text on both sides of page                                                                                                                              |

| 6.  | Indistinct, broken or small print on several pages throughout                                                                                                                           |

| 7.  | Tightly bound copy with print lost in spine                                                                                                                                             |

| 8.  | Computer printout pages with indistinct print                                                                                                                                           |

| 9.  | Page(s) lacking when material received, and not available from school or author                                                                                                         |

| 10. | Page(s) seem to be missing in numbering only as text follows                                                                                                                            |

| 11. | Poor carbon copy                                                                                                                                                                        |

| 12. | Not original copy, several pages with blurred type                                                                                                                                      |

| 13. | Appendix pages are poor copy                                                                                                                                                            |

| 14. | Original copy with light type                                                                                                                                                           |

| 15. | Curling and wrinkled pages                                                                                                                                                              |

| 16. | Other                                                                                                                                                                                   |

. .

University Microfilms International

300 N. ZEEB RD., ANN ARBOR, MI 48106 (313) 761-4700

Figure 8. Back Panel of the DMG

.

.

26

١

.

400 Hertz. The input power is selectable on the switch; down is 115 VAC and up is 230 VAC. The switch has the numbers 115 or 230 visible for the position in which the switch is operated. The switch connects to the taps of the transformer, and when the AC is present, the proper transformer tap is selected. The power supply is similar for both the DMG and the DSA. The same transformer and power supply PWA is used in each unit, but the power supply PWA has the unused regulators left off when installed in the DMG.

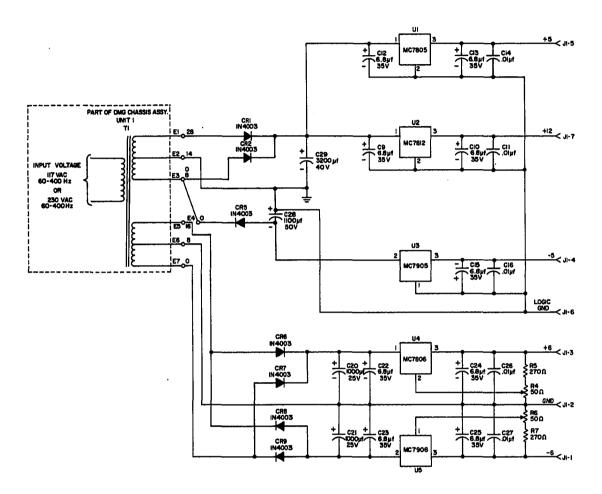

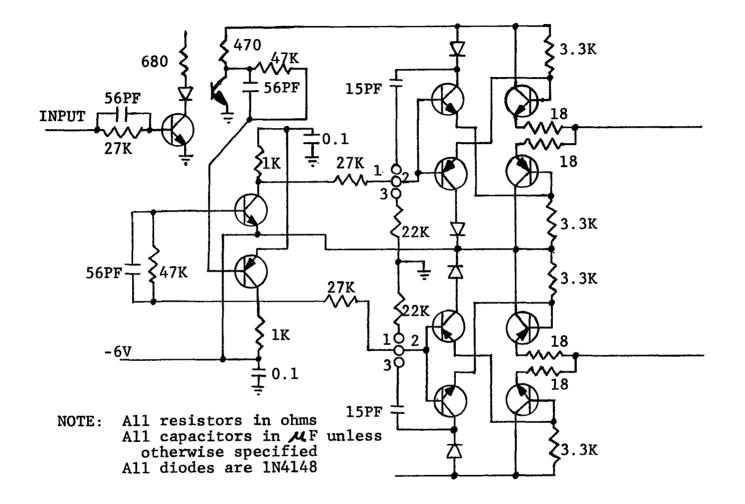

Figure 9 is the schematic diagram of the DMG power supply. The power supply is a typical transformer, rectifier, filter and integrated circuit regulator. The +12volt regulator and the +5 volt regulator are isolated from the frame of the generator or analyzer and mounted on a heat sink. The -5 volt supply is used only for the 2708 EPROMs, thus requires a very low current. The +6 volt and -6 volt supplies are used for the I/O and require a maximum of only 20 milliamps per output. The +5 volt supply in the DMG is used for the 2708 EPROMs and interface logic to the EPROMs. The +12 volt supply has two functions. One is to power the logic and the 2708 EPROM; the second is to power the LED indicators. The UV lamp switch is used to turn the UV lamp on or off. Above the AC input plug is the input power fuse, a 1 ampere slow-blow type fuse.

In the lower left corner are the I/O connectors. These connectors are wired directly to the front panel jacks

NOTE: PREFIX ALL REFERENCE DESIGNATIONS, EXCEPT TI, WITH IAIS.

# Figure 9. Power Supply Schematic Diagram for the DMG

and use a twisted pair wire for the I/O signal. Telephone type tip and ring plugs are needed for the front panel. Below the connectors are 1/8 ampere fuses for the two high level outputs. These will be discussed in the I/O circuits later in this text.

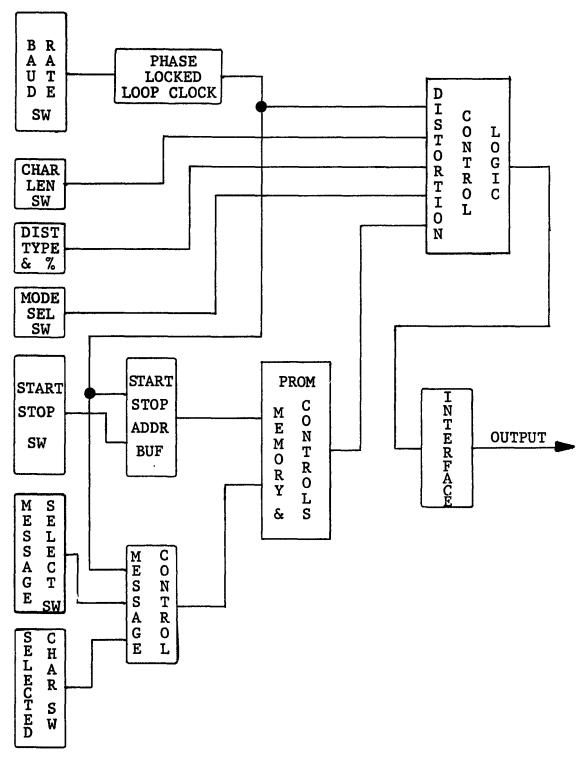

### Logic Description

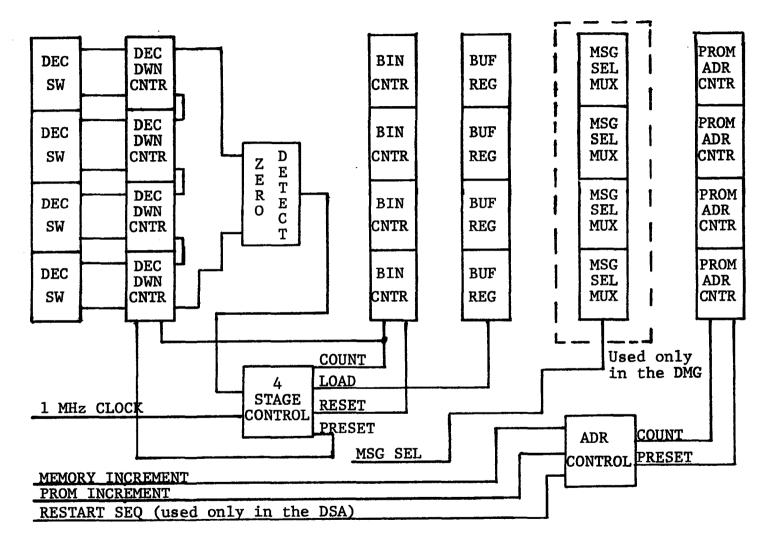

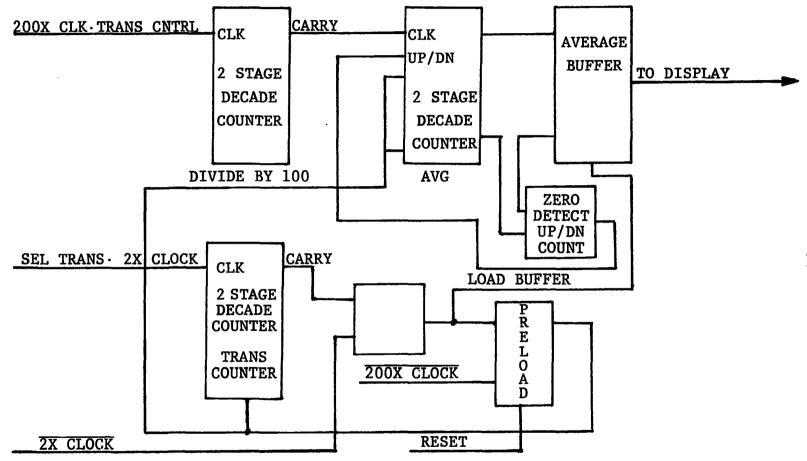

Figure 10 is the major block diagram for the DMG. The master clock in the system is a 1 MHz signal, derived from a 4 MHz oscillator. The clock for generating the baud rates is a phase-locked loop (PLL) which creates a 2X clock which is used as the baud rate clock, a 20X clock which is ten times the baud rate clock, and a 200X clock which is 100 times the baud rate. The value of the baud rate switches is used to preset the counters, which are used as a scaler in the PLL circuit. The circuit is a typical PLL circuit using a voltage controlled oscillator (VCO) and counters for the scaler. The reference frequency--the 100 Hertz reference frequency for the MC14046--is developed from the 4 MHz crystal oscillator using flip-flops and decade counters. The output of the VCO clocks the baud rate switch counters to produce a 200X clock. The VCO output is used also as a clock to a two stage decade counter to create a 20X clock. The RANGE switch is decoded as the select lines of a oneof-four multiplexer. The output of the counters is the input to the multiplexer. The RANGE switch selects the multiplexer inputs for either the 10 times or 100 times baud

Figure 10. Digital Message Generator Block Diagram

rate clock. The 100 times baud rate clock (200X clock) is used for the three lower ranges 0 to 100, 100 to 1k and 1k to 10k. For the 10k to 100k range the 10 times baud rate clock (20X clock) is used. This meets the specifications and allows the logic to have a minimum of a 10 phase clock (ten 1 MHz cycles are generated for each of the highest baud rate clocks). The same clock circuit is also used in the DSA unit.

One of the features of the system is to be able to use an external clock. The external clock could be a 1 MHz standard clock used to test the jitter of the phase-lock loop oscillator and also to verify the logic response to an external master clock. The external 2X clock can be used from another unit in testing either distortion or transmission delays.

The three major clocks in the unit are the 1 MHz master clock, the 2X (baud rate) clock, and either the 200X or the 20X (depending on the selected range) clock. All signals are synchronized to the 1 MHz clock. The baud rate clocks can be derived from the phase-locked loop clock. The 2X clock is used as the bit rate clock and the 200X or 20X clock is used in generating the distortion measuring signals.

The distortion control logic, as shown in Figure 10, is the logic that pulls all the other blocks in Figure 10 together to create the output signal. In asynchronous mode (MODE SELECT switch in "Asyn 1" or "Asyn 2") the start and

stop bits are added by this logic. The distortion control needs inputs from the message control and memory control, from which it constructs the data signal. The input from the CHARACTER LENGTH switch is encoded from a 1 of 16 switch to four-bit binary code and loaded into a binary down counter. Each time the counter reaches zero a character length pulse is generated and the counter is reloaded for the next character cycle. The character length pulse is used in generating the stop and start bits in the asynchronous mode. The MODE SELECT switch determines if the mode is either synchronous or asynchronous with one or two stop bits.

The block called DIST TYPE and % SELECT are the inputs that select the type of distortion and the amount of distortion. Mark distortion is an early transition, while space distortion is a late transition. The switch distortion is a J-K type flip-flop with its output tied back to its input. This causes the distortion to be mark distortion for one cycle, then space distortion for the next. The clock to the switched distortion flip-flop is the character length pulse; thus, every other character has either an early or late transition. The inputs from the DISTORTION PERCENT switches are one set of inputs to two four-bit magnitude comparators cascaded in series. The other input to the comparators is the output from the distortion counter. Thus. the output of the comparators is active when the distortion in the counter is equal to the setting on the DISTORTION

PERCENT switches.

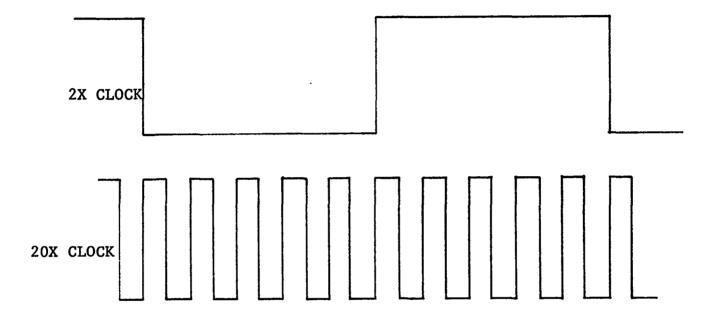

Figure 11 shows the 2X clock period with distortion types and percentages. The falling edge of the 2X clock starts the cycle. The next falling edge of the 2X clock completes this cycle and starts the next. The distortion counter is a two stage up-down decade counter. The counter is preloaded to fifty at the falling edge of the 2X clock. The 200X (or 20X) clock is used as the counter clock. The counter counts down until it reaches zero, which occurs at the rising edge of 2X clock. The counter control is changed to up count and the counter counts up to fifty. The distortion type control enables the comparators during the portion of the bit cycle either early or late as shown in Figure 11. When a compare results, the output signal is gated to allow a transition, if required.

When the 20X clock is selected, only the tens stage of the counter and comparators is active. The low order bit is used and converts the unit's digit output to either zero or five. The distortion is in 5% increments in this range. Figure 12 shows the relationship of the 2X clock to the 20X clock. If the RANGE switch is set from 1 to 3 the 200X clock would be used. For each pulse in Figure 12 there would be 10 pulses.

The next block in Figure 10 would be the PROM memory and controls. This includes the EPROM, the 32k pseudorandom pattern generator and the controls for both. The

Figure 11. 2X Clock Period

Figure 12. 2X Clock and 20X Clock

.

.

MESSAGE SELECT switch determines which of the following will be selected: the 32k pseudo-random pattern generator, the SELECTED CHARACTER BITS switches, or the START/STOP switches which control the EPROM addresses. The MESSAGE SELECT switch is decoded to the various start and stop addresses for the message A, ("Msg A"), message B ("Msg B"), 2047 pseudorandom pattern ("2k Patt"), and the "User Defined". The decode is performed as the select lines of a one-of-four multiplexer.

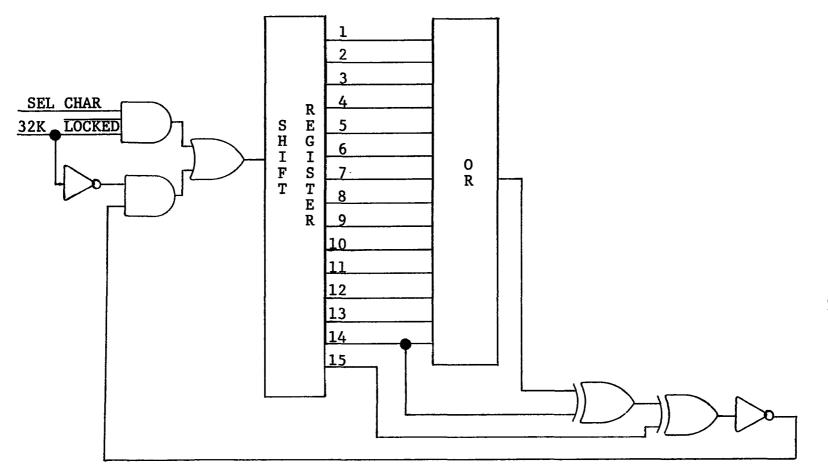

The SELECTED CHARACTER BITS switches, when selected by the MESSAGE SELECT switch, are transmitted per the conditions of the MESSAGE CONTROL switch. The 32k (15 bit) pseudo-random pattern was designed as a 15 bit shift register with exclusive-OR of the outputs as follows. The first 14 outputs are all ORed together so that when any of the outputs are ones, the result would be a one. Output 14 is exclusive-ORed with this result. The output of this logic is then exclusive-ORed with the output of bit 15. The output of this combination logic of 14 and 15 is inverted and fed back as the input to the shift register. The control to the shift register is a counter which counts to 16 then locks the feedback to the input. Before the circuit locks to the feedback signal, the SELECTED CHARACTER BITS switches are the input to the shift register. Figure 13 shows a representative block diagram of the 32k pseudo-random pattern generator.

Figure 13. 32K Pseudo-Random Pattern Generator

•

A requirement for the START/STOP switches was for the logic to automatically follow the address on the switches whenever they are changed. An additional specification requirement was that every bit in the EPROM be addressable making every bit accessible to the test technician. The address display for each bit must be decimal, requiring a decimal-to-binary conversion and a counter stage which can be incremented by the logic.

The start and stop thumbwheel switch output is parallel loaded into a four stage decade down counter. Using the 1 MHz clock, it is down counted to zero. While the decade counter is counting down a stage of binary up counters is counting up. When the decimal down counter reaches zero the binary up counters are loaded into a buffer. The down counter is then parallel loaded to the value of the switches, the binary counter is reset to zero. This circuit is used for both the start and stop switches for the DMG and the DSA The difference in the start and stop is the buffer. units. The buffer in the start circuit is a binary up counter, while the buffer for the stop circuit is a register. Since the stop is always the value from the switches, these outputs are the input to a set of cascaded magnitude comparators.

The start buffer is a counter; therefore, the logic can control the sequencing of the addresses. The reset and preset are also controllable from the logic. The start address must be incremented when generating a message or

programming a PROM. The start control logic must be capable of preloading in order to loop through a set of addresses. The logic uses a compare of the stop switches for the trigger to start a new cycle if the MESSAGE CONTROL is in "Cont Msg".

The MESSAGE SELECT switch is encoded to the start and stop switch buffer. The message A starts at address  $\emptyset \emptyset \emptyset \emptyset$ and ends with address  $\emptyset 127$ . Message B starts at address  $\emptyset 128$  and ends at address  $\emptyset 2 \emptyset 7$ . The 2047 bit pseudo-random pattern starts at address  $\emptyset 2 \emptyset 8$  and ends at address  $\emptyset 463$ . The user definable area starts at address  $\emptyset 464$  and ends at the top address of the EPROM of 1 $\emptyset 23$ . See Table II (page 23) for the bit address which the test technician must use.

The last part of the PROM memory and control is a register and an eight-to-one demultiplexer. The three loworder bits on the start address switch buffer constitute the bit position for the present bit of the EPROM word. The data from the EPROM is stored in a register. To get the selected bit out of the register a counter circuit develops the signals labeled S1, S2, S3, and S4. S1-S3 are the three low-order outputs of a binary counter. S4 is the last output and used to trigger another cycle of EPROM data. S1 to S3 are the controls of the demultiplexer. The data register is the input to the demultiplexer and the output becomes the selected bit. The timing is done at the rising edge of the 2X clock for counting; this allows the data bit to be ready

even if there is 49% distortion, which would be the next rising edge of the 200X clock pulse.

The logic timing to get the next EPROM data byte into the register is used to complete the address changes (either increment or reload the start address) during the last half of the 2X clock cycle when the counter is equal to seven. The address to the EPROM is either incremented, reset, or preset to the next address. This operation happens after the falling edge of the 2X clock, using the 200X or 20X Thus, the address is settled and the EPROM data is clock. presented to the register by the time the next rising edge of the 2X clock occurs. When the counter reaches S4 on the rising edge of the 2X clock, it is either asynchronously reset for the first bit of the next data byte, or preset to the start bit for restarting the message or pattern. There is a single flip-flop in the distortion controls that stores the data signal until the distortion control releases The data flip-flop is loaded by the falling edge of the it. 2X clock, using the falling edge of either the 200X or 20X clock pulse. No matter what the percentage of distortion, the data bit is always ready. Thus, on the next rising edge of either the 200X or the 20X clock, the data flip-flop can be loaded.

#### Input-Output Description

The data flip-flop is then put into the I/O circuits. Both the data and the 2X clock signals are fed into optical

couplers. These are used for the low level output and the RS-232-C<sup>10</sup> interface. The optical couplers drive the pushpull type circuits shown in Figure 14. The circuits in Figure 14 are the RS-422<sup>11</sup> and RS-423<sup>12</sup> type circuits which meet the MIL-STD-188-114. Figure 15 shows a typical circuit representation of the output. The RS-422 and RS-423 type output generators are available in integrated circuits; however, the MIL-STD-188-114 requirements for  $V_{os}$  prevents the use of the RS-422 type integrated circuit drivers. Figure 16 illustrates the method of measuring  $V_{os}$ . The RS-422 specification states that the magnitude of  $V_{os}$  shall not be greater than 3.0 volts when measured between center point of test load and ground. MIL-STD-188-114 states that the magnitude of  $V_{os}$  is less than or equal to 0.4 volts when measured between center point of test load and ground. Thus, the circuit meeting MIL-STD-188-114 also meets the RS-422, but RS-422 does not meet the MIL-STD-188-114.

The data signal and the 2X clock signal are also used as high level outputs. These are transformer coupled for isolation and are shown in Figure 17 as a typical circuit.

<sup>&</sup>lt;sup>10</sup>Electronic Industries Association, <u>EIA Standard</u> <u>RS-232-C</u> (Washington D. C.: Electronics Industries Association, 1969), pp. 4-18.

<sup>&</sup>lt;sup>11</sup>Electronic Industries Association, <u>EIA Standard</u> <u>RS-422</u> (Washington D. C.: Electronics Industries Association, 1975), pp. 3-12.

<sup>&</sup>lt;sup>12</sup>Electronic Industries Association, <u>EIA Standard</u> <u>RS-423</u> (Washington D. C.: Electronics Industries Association, 1975), pp. 4-15.

Figure 14. I/O Drivers

Figure 16. Generator Offset Voltage (V<sub>os</sub>) Measurement

Figure 17. Transformer Coupled High Level Data Output

There are two inputs into the DMG on the front panel. They are the 2X IN (UNBAL) and the EXT PLS IN (UNBAL). These are both RS-423 type inputs. The receiver used for these is the MC3486 (Quad RS-422/423 Line Receiver). The 2X clock has another type of input, the EIA Standard RS-232-C type, on the back panel connector. The 2X IN and the CLR TO SEND are received by MC1489 (Quad RS-232-C Line Receivers).

### III. DIGITAL SIGNAL ANALYZER

## Physical Description

The Digital Signal Analyzer (DSA) is different from the DMG. The DMG is used solely to generate a data signal. The DSA's function is to analyze the input signal and report any errors. Errors are indicated either when the input signal exceeds the setting on the front panel, or when the data polarity is wrong. The DSA also has a second function to perform, that of a PROM programmer.

Figure 18 shows the DSA front panel. Some of the switches perform the same functions as in the DMG. The BAUD RATE switches and the RANGE switch are the same in both the The DSA START/STOP switches have some cir-DSA and the DMG. cuits similar to the DMG START/STOP switches. However, in the DSA there are more functions to be performed by the START/STOP switches, and they have no message select encoding (as in the DMG). The DISTORTION PERCENTAGE switches perform a different function than in the DMG. In the DMG the DISTORTION PERCENTAGE switches acted as the trigger to release the bit, while in the DSA any bit change occurring outside the limits of the distortion switches must be declared an error.

Figure 18. Front Panel of the DSA

The CHARACTER LENGTH switch is another that is the same as in the DMG. However, the SELECTED TRANSITION is unique to the DSA. The SELECTED TRANSITION switch is used to generate a strobe for an oscilloscope trigger. The SELECTED TRANSITION switch has 18 positions, 17 for each possible transition of a 16 bit data stream and an "All" position. When a position from 1 to 17 is selected, on that specific transition a strobe is generated to the Z axis output. Figure 19 shows how each selection would cause a strobe. The "All" position will generate a strobe with each transition. It should be noted that the only way 17 transitions could be generated is for a sixteen bit data stream to alternate ones and zeros in asynchronous mode.

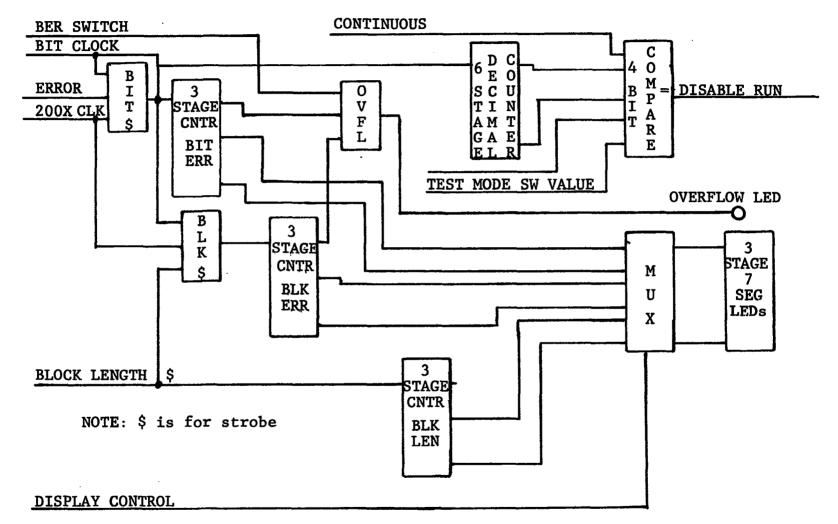

The rest of the switches and displays are different from the DMG. The DSA has a display of three digits. The digits are seven-segment LEDs and around the display are other individual LEDs to represent the following functions. On the top of the display is MARK which represents a bit whose level is a one. The next, EARLY, is the mark bias indicator for the distortion (Figure 1). The third is RUN which indicates that a test is in progress. The final LED on the top is OVFL which is the overflow indicator for the display. This represents a number larger than 999 which is the largest number that can be shown on the display. The bottom of the display has the following indicators. SPACE indicates a zero level bit in the data

Figure 19. Selected Transition Strobe when

:

Selected Transition Switch Set to 5

stream. LATE indicates space bias for distortion measurements (Figure 1). COMPL indicates that a test has been completed and no more data sampling will occur. The last one on the bottom is SYN which illuminates when the test mode selected is synchronous. The SYN LED will be off when using the start/stop mode (asynchronous mode).

The display has two control switches. The DISPLAY TIME is an adjustable switch which causes the time on the display reset signal to vary from two seconds to twenty seconds. The other switch controls the mode of the display. The DSPL AUTO is used with the DISPLAY TIME switch which allows the automatic resetting and loading of the display based on the adjustment of the switches. MAN is the center position and requires manual operation of the switch to reset the display. The manual reset is spring loaded and the switch returns to the center position when released.

The RESYN switch is used to restart the synchronizing logic, allowing the data pattern to be synchronized with the pattern generator data or the memory data. This switch is used when starting test or when preparing to start a new series of tests. During the resyn cycle the distortion is not measured until the READY light glows. The group of ten switches next to the MAN and RESYN switches are controls for the display and data stream. The last two are part of the PROM programmer, and they will be described with the PROM programmer.