#### UNIVERSITY OF OKLAHOMA

### GRADUATE COLLEGE

# LEARNING ASSISTED DECOUPLED SOFTWARE PIPELINING (LA-DSWP)

A THESIS

### SUBMITTED TO THE GRADUATE FACULTY

in partial fulfillment of the requirements for the

Degree of

MASTER OF SCIENCE

By

LUCIA R. FITZMORRIS Norman, Oklahoma 2018

# LEARNING ASSISTED DECOUPLED SOFTWARE PIPELINING (LA-DSWP)

# A THESIS APPROVED FOR THE SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING

BY

Dr. Ronald D. Barnes

Dr. Jon G. Bredeson

Dr. Joseph P. Havlicek

© Copyright by LUCIA R. FITZMORRIS 2018 All Rights Reserved. Ut in omnibus glorificetur Deus

### Acknowledgements

I would like to thank my committee chair, Dr. Ronald Barnes, for his support during the completion of this thesis. I cannot express how happy I have been to work in your lab and share in your passion for computer architecture. I would also like to thank the other members of my Master's thesis committee, Dr. Jon Bredeson and Dr. Joseph Havlicek, for providing the tools necessary for my success.

To my peers in the Soonergy Lab, especially Sonya Wolff, without you I never would have made it through this program. You have helped me grow as an engineer and as a person. I will value our friendship always.

To my parents, thank you for showering me with your love and for instilling in me a curiosity to explore the world. And to my little brother, you always can brighten my day with your uncanny sense of humor and your kind heart. I would also like to thank the sisters at Joseph Monastery. There is nothing like having 16 women ask you every week "Are you done yet?" to put the fire under you to finish a degree program.

Finally, some of the computing for this project was performed at the OU Supercomputing Center for Education & Research (OSCER) at the University of Oklahoma (OU). This material is based upon work supported by the National Science Foundation under Grant No. 1018771.

# Table of Contents

| Acl  | knowledgements                                 | iv        |

|------|------------------------------------------------|-----------|

| List | t of Tables                                    | vii       |

| List | t of Figures                                   | viii      |

| Ab   | stract                                         | ix        |

| Cha  | apter 1. Introduction and Motivation           | 1         |

| 1.1  | Motivation                                     | 2         |

|      | 1.1.1 Moore's Law                              | 2         |

|      | 1.1.2 The Power Wall and Communication Latency | 3         |

|      | 1.1.3 Multi-Core Processors                    | 5         |

|      | 1.1.4 Hardware Optimization Transparency       | 5         |

| Cha  | apter 2. Related Work                          | 9         |

| 2.1  | DOALL                                          | 9         |

| 2.2  | DOACROSS                                       | 10        |

| 2.3  | DOPIPE                                         | 11        |

| 2.4  | DSWP                                           | 12        |

| Cha  | apter 3. Modern Processor Design               | 16        |

| 3.1  | Out-of-Order Pipeline                          | 16        |

| 3.2  | Memory System                                  | 19        |

| 3.3  | Inter-Core Communication                       | 21        |

| Cha  | apter 4. Transform Implementation              | <b>23</b> |

| 4.1  | Software Details                               | 23        |

| 4.2  | Program Dependency Graph Building              | 24        |

|      | 4.2.1 Data Dependencies                        | 25        |

|      | 4.2.2 Memory Dependencies                      | 26        |

|      | 4.2.3 Control Dependencies                     | 27        |

| 4.3  | Directed Acyclic Graph Building                | 28        |

| 4.4  | Determine Partitions Using Machine Learning    | 29        |

| 4.4.1 Reinforcement Learning                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| 4.4.2 Learning Method and Policy                                                                                                             |

| 4.4.3 Problem Space $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 34$                                                      |

| 4.5 Transform Source Code                                                                                                                    |

| 4.5.1 Move Instructions into New Partition Functions $36$                                                                                    |

| 4.5.2 Adding Flows to Partitions                                                                                                             |

| 4.5.3 Insert Functions into Code                                                                                                             |

| 4.5.4 Learning Information                                                                                                                   |

| Chapter 5. Experimentation 42                                                                                                                |

| 5.1 Kernels                                                                                                                                  |

| 5.1.1 Motivation $\ldots \ldots 42$                             |

| 5.1.2 Kernel Definitions $\dots \dots \dots$ |

| 5.2 Hardware Setup $\ldots \ldots 46$                    |

| 5.3 Experiment 1 Setup $\ldots \ldots 46$                       |

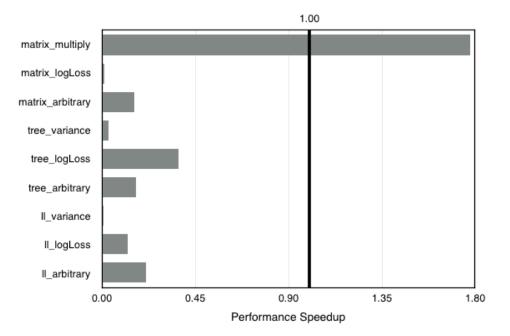

| 5.4 Experiment 1 Results $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 47$                                          |

| 5.5 Experiment 2 Setup $\ldots \ldots 49$                                     |

| 5.6 Experiment 2 Results                                                                                                                     |

| Chapter 6. Conclusion 54                                                                                                                     |

| 6.1 Future Work                                                                                                                              |

| Bibliography 57                                                                                                                              |

| Appendices                                                                                                                                   |

| Appendix A.Notation and Nomenclature62                                                                                                       |

| Appendix B.Selected Code Snippets63                                                                                                          |

| B.1 Inter-Partition Flow Structure                                                                                                           |

| B.2 DSWP Flow Library Header                                                                                                                 |

| B.3 ML Timing Library                                                                                                                        |

| B.4 Linked List Variance Kernel                                                                                                              |

| B.5 Arbitrary Algorithm Calculations                                                                                                         |

| B.6 Latency Calculation Code                                                                                                                 |

# List of Tables

| 4.1 | State and Action Definitions for DSWP ML | 34 |

|-----|------------------------------------------|----|

| 5.1 | Experiment Loop Summary Information      | 45 |

| 5.2 | Experiment 1 Results                     | 48 |

# List of Figures

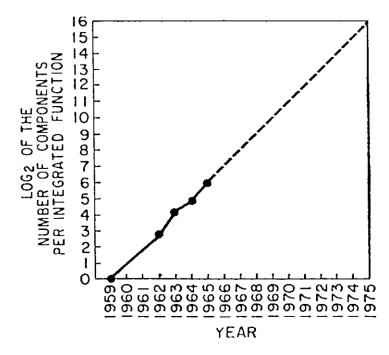

| 1.1  | Reprint of Moore's Original Plot © 1998 IEEE [27]        | 3  |

|------|----------------------------------------------------------|----|

| 2.1  | Program Execution Before and After DOALL Parallelization | 10 |

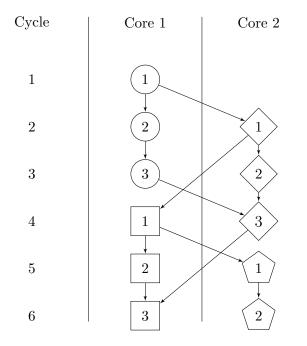

| 2.2  | Program Execution After DOACROSS                         | 11 |

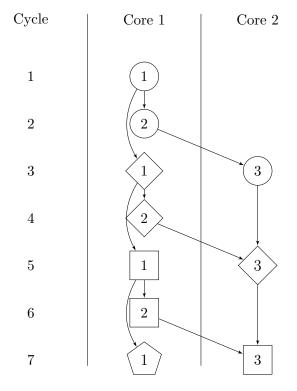

| 2.3  | Program Execution After DOPIPE Parallelization           | 12 |

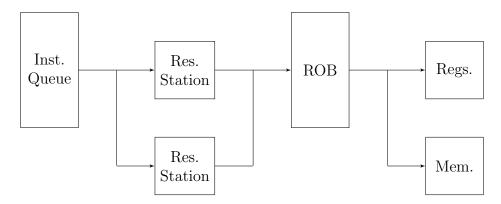

| 3.1  | Simplified Out-Of-Order Pipeline                         | 17 |

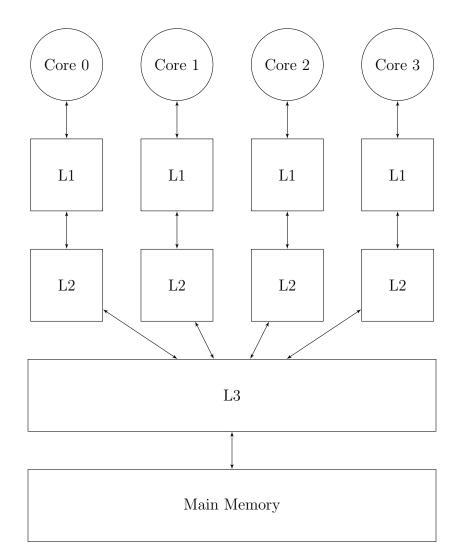

| 3.2  | Modern Processor Memory Hierarchy                        | 20 |

| 4.1  | Example Code Snippet for Data Dependence                 | 25 |

| 4.2  | Example Code Snippet for Memory Dependence               | 26 |

| 4.3  | Example Code Snippet for Control Dependence              | 27 |

| 4.4  | Example Control Dependence within PDG                    | 28 |

| 4.5  | Example Code Snippet for PDG and DAG                     | 29 |

| 4.6  | Example PDG for Code Snippet                             | 29 |

| 4.7  | Example DAG Condensation of PDG                          | 30 |

| 4.8  | Example Q-Tables for SARSA                               | 31 |

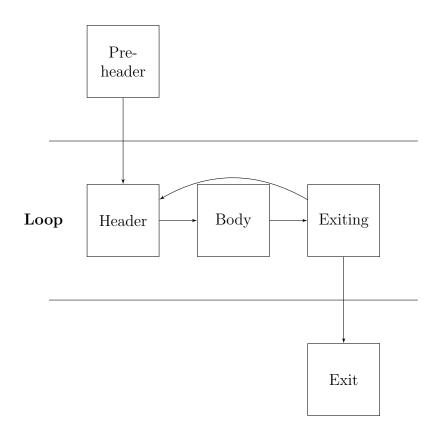

| 4.9  | Loop BB Structure                                        | 37 |

| 4.10 | Pseudo-BB to Inject DSWP Partitions                      | 40 |

| 5.1  | Experiment 1 Results                                     | 49 |

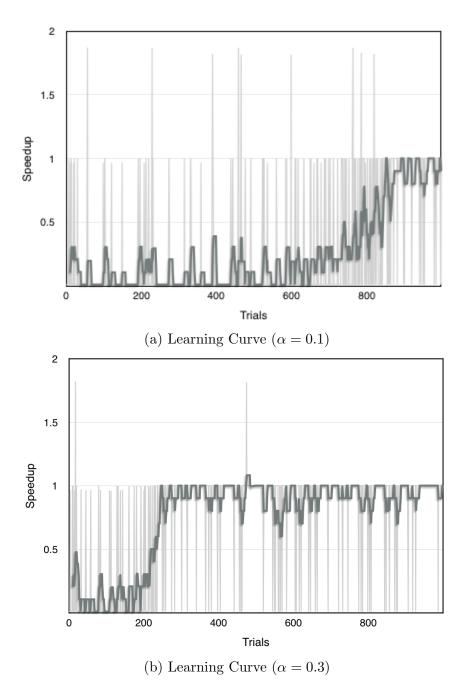

| 5.2  | Matrix Arbitrary Learning Curves                         | 52 |

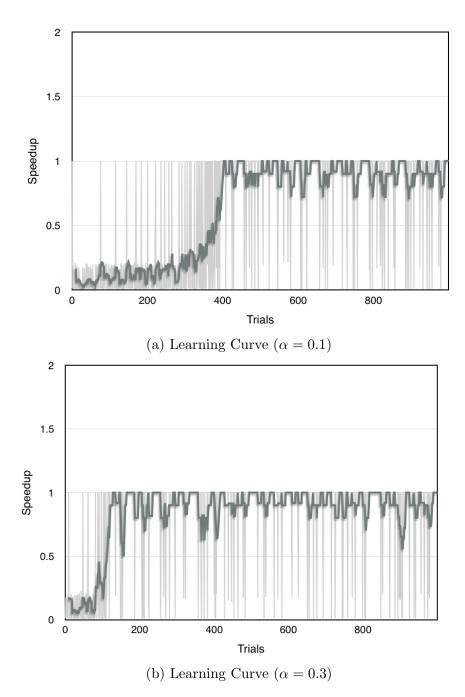

| 5.3  | Matrix Multiply Learning Curves                          | 53 |

### Abstract

### LEARNING ASSISTED DECOUPLED SOFTWARE PIPELINING (LA-DSWP)

Lucia R. Fitzmorris, M.S. The University of Oklahoma, 2018

Supervisor: Dr. Ronald D. Barnes

In this thesis, I introduce and implement an extension to the Decoupled Software Pipelining (DSWP) algorithm proposed by Rangan et al. [34]. This new extension is named Learning Assisted Decoupled Software Pipelining (or LA-DSWP) as it applies reinforcement learning to the partitioning problem found within DSWP. Through experimentation, the viability of DSWP and LA-DSWP as optimizations that produce significant program speedup is tested and measured.

As computer architects strive to keep up with public expectations for processor performance growth, they are increasingly turning to processor designs which utilize multiple independent cores on a single chip. Unlike most prior hardware innovations, computer programs must be written or compiled with multiple threads in mind to take advantage of these new hardware innovations. Automatic thread-extraction using Decoupled Software Pipelining seeks to extract multiple threads from a single-threaded program [28]. This is done by allowing loops within the program to execute on multiple cores on a single processor chip simultaneously without programmer intervention. DSWP focuses on splitting large recursive data structure's traversal loops into multiple threads in an attempt to increase overall program performance.

Unlike prior implementations of DSWP, this research uses a hardware and language independent implementation of DSWP using the LLVM framework. Rather than relying on custom-built hardware to facilitate communication between program threads, this implementation uses Intel's Thread Building Blocks library to create queues in the shared memory between the various onchip processor cores. As this thesis will show, this design setup relies heavily on the memory subsystem of the targeted processors and is greatly impacted by the actual design of the memory subsystem.

Another novel addition to DSWP explored in this thesis is the application of machine learning to the partitioning process. Instead of partitioning the nodes of a loop's program dependency graph using predefined heuristics, this thesis seeks to apply reinforcement learning to allow the DSWP agent to make more informed decisions when optimizing a given loop. The DSWP agent is able to collect and analyze data about each node of a program's loop to partition the loop on a node-by-node basis. This addition constitutes LA-DSWP.

Through experimentation on modern Intel processors, this thesis tests the feasibility of LA-DSWP on current hardware. Multiple kernel programs were written to search for program patterns that can achieve performance increases using DSWP partitioning. Experiments were run using the partitioning methods discussed in earlier papers along with the proposed method utilizing machine learning.

### Chapter 1

### Introduction and Motivation

Since the earliest days of computing, programmers have preferred writing computer code sequentially [32]. The process of creating a sequential list of instructions for the computer to follow is not only easily understood by a human programmer, but it also mimics the way older computer processors execute the program. In older processors, a program's instructions are fetched from memory and executed in the exact order given by the program [31]. To keep increasing processor performance, computer architects have changed this model of program execution within the processor in such a way that masks the pipeline's alterations from the programmer [13]. This model of "invisible hardware optimizations" has reached its end, and now computer architects rely on processor designs that require programmers to explicitly write code that will perform better on a given hardware configuration.

In 2004, Rangan et al. proposed a method of automatic thread extraction from single-threaded program loops named Decoupled Software Pipelining or DSWP [28,34]. This optimization was created to allow programmers to easily take advantage of new multi-core, single chip processor architectures without having to explicitly write programs using multiple, independent threads. This thesis proposes an extension to the DSWP process by optimizing thread extraction within DSWP using machine learning. This new extension of Rangan's optimization is named Learning Assisted Decoupled Pipelining or LA-DSWP. Through a hardware independent implementation of LA-DSWP, this thesis attempts to discover the expected performance increase for programs running on current hardware after they have been optimized using LA-DSWP.

#### 1.1 Motivation

Before expounding on the definition of implementation of LA-DSWP, the remainder of this chapter is used to discuss the motivation for exploring DSWP based optimizations.

#### 1.1.1 Moore's Law

The idea that a computer is outdated as soon as it has been purchased is a common sentiment expressed by everyone from computer scientists to casual web-surfers. This sentiment is ofter ascribed to Moore's law; however, Moore's law does not directly apply to performance increases. Instead, Moore's law refers to the fact that processor complexity will double every year [16,27]. While Moore's law has since been reduced to a doubling of processor complexity every 18 months, his original prediction from only five data points – shown in Figure 1.1 – was remarkably accurate. This increased processor complexity has translated into a massive performance increase in the years since his original prediction.

While there is some disagreement over how exactly to measure performance, a commonly accepted measurement method is by comparing the execution time of an agreed upon set of programs which mimic a normal user's workload [18]. Sets of programs designed to be representative of these workloads are used as benchmarks, with one of the most popular sets being the Standard Performance Evaluation Corporation (SPEC) benchmarks [31]. SPEC was created in 1989 by a conglomerate of vendors and is updated every few years to

Figure 1.1: Reprint of Moore's Original Plot © 1998 IEEE [27]

include programs that represent the common classes of computing. As measured with a comparison against the Vax-11/780 using the SPEC benchmarks, processor performance increased by roughly 50% every year from 1986 to 2003 [17]. In contrast, Moore's law only calls for a processor complexity increase of 35% each year, showing that computer architects were able to increase processor performance at a higher rate than processor complexity. This rate of processor performance growth has slowed considerably since 2003, however, caused by what is known as "the power wall."

#### 1.1.2 The Power Wall and Communication Latency

For a large portion of the history of processors, computer architects focused on designs and optimizations that allowed them to increase two primary aspects of their processors: frequency and IPC (Instructions Per Cycle) [2]. The speed at which a processor can execute instructions is primarily limited by these two aspects. Processor pipelining and memory cache structures were just a few of the major developments during the tail end of the 20th century that allowed computer architects to continue increasing processor performance by close to 50% per year [17]. These strategies came to an end in the early 2000's.

One major constraint that architects began to struggle with is what is now called the power wall. The very laws of physics that allow CMOS logic to function, also enforce an important relationship between power consumption and the frequency at which the MOSFET transistors switch. This relationship is expressed by:

$$P \propto \frac{1}{2} V_{DD}^2 f \tag{1.1}$$

where P is the power consumed by the processor,  $V_{DD}$  is the supply voltage, and f is the operating frequency of the processor [39]. In addition, energy consumption is directly proportional to the heat production of a processor.

Pushing frequency into the GHz, computer architects have bumped into the threshold where they are no longer able to feasibly cool their chips. Even with the steady decline of processor voltage from 5V in the earliest processors to almost 1V for today's processors, the power wall makes continuing to increase processor frequency at pre-2000 rates impossible [2, 13]. Compounding the effect of the power wall has been the move to mobile consumer products. Users demand smart devices and laptops that have long battery life and stay reasonably cool [31]. The power wall has, in effect, largely stalled the increase of processor frequencies.

Another effect compounding the power wall in the relationship that as frequency increases, the number of instructions executed every cycle tends to decrease [2]. Electricity can only travel at a finite speed, so as frequencies increase, data is unable to travel as far through the processor. So as computer architects have pushed frequency higher and higher, they must also work to not cause the IPC to drop and cause the overall performance increase to be negligible.

#### 1.1.3 Multi-Core Processors

Another important rule that has held true in processor design has been Pollack's Rule [14]. Pollack's Rule states that if the complexity of a circuit is doubled, gain will be limited to at most a 50% improvement. This rate of increase corresponds to the 50% increase in processor performance discussed in early sections. After 2004, however, performance gains were impeded by the power wall. This decrease in performance gains forced the industry to change the way in which they designed processors; hence the age of the multi-core processor was born [17].

A multi-core processor is a integrated circuit that contains multiple smaller processors (or cores) that can execute completely independent threads. By including multiple cores on a single IC, Pollack's Rule should hypothetically be mitigated by allowing a performance speedup of 100% while only doubling the complexity of the chip [14]. Since roughly 2006, processor manufactures have embraced the CMP (Chip Multi-Core) revolution as a way to meet demand and continue to grow processor performance. Intel, for example, has pushed CMPs for personal computers that can have up to 6 cores in a single chip [17]. Processors used for servers can even have considerably more cores: for example, the Intel Phi processor has up to 72 cores [20].

#### 1.1.4 Hardware Optimization Transparency

Until the rise of CMP's, the innovations in processor design that allowed steady performance increases were mostly invisible to typical computer programmers. Most programmers work in high level languages (such as C++ or Python) and therefore are unaware of the many optimizations that are performed on their code by compilers and the hardware itself. In this manner, programmers are able to continue writing software the same way it has always been written, yet are able to reap the benefits of continued processor performance growth [13].

Take, for example, computer architects' innovations for branch prediction. Most processors since the mid 1980s have taken advantage of instruction pipelining. In a pipelined processor, many different instructions can execute inside a processor simultaneously, with each instruction being in a different "stage" of the processor [31]. Therefore, new instructions must be fetched from memory before all of the preceding instructions have been fully executed. This can cause major problems with branch instructions. Since a new instruction must be fetched from memory before a given branch has finished executing, the processor must predict the value to which the program counter should be changed to to continue fetching instructions for proper program execution. If a processor mis-predicts the program counter, for example guessing that a branch will update the PC to the next consecutive instruction in memory when it should have actually jumped to a new block of code, the processor pipeline must be flushed to remove the incorrect instructions from the data-path. Accurate branch predictions are important for processor performance since flushes can cause very long delays in program execution. Early methods of handling branch prediction such as static predictions (for example, always predicting that all branches will jump to a new block of code) were only about 62.5%accurate [40]. Later methods using small state-machines and look-up tables were able to increase correct prediction rates to 97% and now small neural networks, known as perceptrons, are used to reach prediction rates of close to

100% [23, 40]. All of these innovations have taken place to improve processor performance without programmers even needing to know that there has been a change in the hardware.

Creating hardware improvements that are invisible to the software does not extend to multi-core processors easily. Since the first assembly programs, software has almost always been written in a very sequential way: first the computer should do this, then add this, and finally store this [32]. High level languages like Fortran or C were able to abstract away the smaller steps and combine multiple machine level instructions into a single line of code, but the sequential manner of programming was unchanged. Even today's object oriented languages such as Python or C# rely on the fact that the order that instructions are performed in is important and should remain unchanged. These instructions may be scheduled by the hardware to execute in a different order by the processors using out-of-order execution, but they must always keep memory and registers consistent to match a processor working in-order. This once again keeps innovations in processor design invisible to the programmer [17].

Multi-core processors require programmers to break this sequential way of thinking. To achieve performance increases with these new processors, programers must split their programs into multiple threads that all execute at the same time. Communication between the threads is slow (limited by communication through usually the L2 or L3 cache) so programers must limit the communication between the threads along with limiting the amount of shared memory between the two [6, 22]. Enforcing memory consistency between two processors is slow so data shared between the two processors can cause many issues for the processor's cache and memory buses [13]. Most programming languages have almost no native support for the structures and processes needed to handle this new parallel way of programming, which in turn, causes programmers to be slow to adapt their code to match multi-core hardware. Institutions using legacy code that in the past have been able to benefit from "Moore's Bounty" (the increase in performance with no change to software) are no longer able to benefit from these new improvements in performance [24].

### Chapter 2

### **Related Work**

Many new methods have been introduced to try to automatically harness parallelism in loops to allow them to be run across many different processor cores. Some new methods have been harnessed to give huge speedups for scientific computing, but those methods usually carry strict requirements to ensure proper code execution. In this section, we will focus on loop parallelization methods.

#### 2.1 DOALL

The easiest method to understand is DOALL parallelization. A loop that is DOALL parallel is one that has no dependencies from one iteration of the loop to the next [30]. This can be a very strict definition for a loop to meet, but if a loop meets this condition every iteration of the loop can be done in parallel. This obviously has potential to give a huge gain in performance if there are many cores to execute the different iterations such as in a GPU. An example of how a loop could be broken with DOALL parallelization to be run across 4 different cores can be seen in Figure 2.1. Notice that since there are no dependencies between loop iteration, no communication is needed between the threads which means DOALL loops performance increases are independent of communication latency between threads. Hypothetically the parallelization shown in the figure could give nearly a 4X speedup compared to the non-parallelized code.

|               | Cor           | re 1:          |              |

|---------------|---------------|----------------|--------------|

|               | Iterat        | tion 1         |              |

|               | Iterat        | tion 2         |              |

|               | Iterat        | tion 3         |              |

|               |               |                |              |

|               | Iterat        | ion N          |              |

|               | (a) Before P  | arallelization |              |

| Core 1:       | Core 2:       | Core 3:        | Core 4:      |

| Iteration 1   | Iteration 2   | Iteration 3    | Iteration 4  |

| Iteration 5   | Iteration 6   | Iteration 7    | Iteration 8  |

| Iteration 9   | Iteration 9   | Iteration 10   | Iteration 11 |

|               |               |                |              |

| Iteration N-3 | Iteration N-2 | Iteration N-1  | Iteration N  |

|               |               |                |              |

(b) After Parallelization

Figure 2.1: Program Execution Before and After DOALL Parallelization

### 2.2 DOACROSS

The next type of parallelization is DOACROSS. Just like in DOALL, DOACROSS splits iterations of the loop between multiple cores. Each iteration is completely executed by a single core. This is shown in Figure 2.2 which illustrates a DOACROSS parallelization of a loop that has 3 instructions per iteration where each iteration's instructions are given a unique shape. DOACROSS differs from DOALL in that data dependencies across iterations are allowed [30]. These are shown by the edges in Figure 2.2 pointing from one core to another. Figure 2.2 assumes a latency of 1 cycle to communicate from one core to another. This figure also shows that DOACROSS can be very sensitive to intra-core communication latency. A latency of 3 would cause this parallelization to have no performance increase because each core would be executing while the other was waiting for the value it depended on [29].

Figure 2.2: Program Execution After DOACROSS

### 2.3 DOPIPE

DOPIPE is very different from the two previous examples of code parallelization. In both DOALL an DOACROSS each iteration of the loop is executed completely on a single core. DOPIPE instead breaks a single iteration of a loop into multiple steps and executes each step on a different core [29]. Figure 2.3 shows an example of the same program as in Figure 2.2, but parallelized using DOPIPE. Notice that the first two instructions of every iteration occur in core 1 and the last instruction is executed in core 3. This can allow for far less communication between the two cores if the code is broken in the correct places. The primary constraint that makes DOPIPE unfeasible for most loops is that it does not work if there are any extra control dependencies inside of the loop. So for example, if the loop contains an if statement or another loop, it is no longer a candidate for DOPIPE [30].

Figure 2.3: Program Execution After DOPIPE Parallelization

#### 2.4 **DSWP**

Decoupled Software Pipelining (DSWP) was created to relax the control dependency restraints of DOPIPE. DSWP was originally formulated at Princeton University in 2004 [34]. The researchers noticed that many programs have loops that traverse very large recursive data structures (RDS). In a typical loop there are two main paths of instructions that are executed: traversal and computational. The traversal path is the one that traverses through memory to load each node of the RDS. The second path does the actual computations that are returned at the end of the traversal. So for instance, if a program is looking for the average value of a linked list, the traversal path loads the pointers that allow the program to move from each index in the list to the next. The computational path is the instructions that are using the values at each index to find the overall average.

DSWP seeks to split RDS loops, and other loops like them, into two separate threads that are mostly independent from each other. Not only does DSWP allow speedups by allowing multiple instructions to execute in parallel, it can also produce better behavior from the memory system of the processor. RDS's can result in poor cache performance because they usually have poor locality within memory. Repetitive cache misses degrade performance and force processors to stall for long periods of time. Ideally, the processor would fetch as many instructions along the traversal path and begin loading data from memory so that some of the latency caused by cache misses would be hidden by the fact that many of the load instructions read times from memory would overlap. This, unfortunately, is not how current processors operate; even out-oforder processors fetch and issues instructions in program order and so the loads of the traversal path have to wait on the instructions of the computational path to be fetched. DSWP helps alleviate this problem by having all traversal instructions on one core and computational instructions on another. This allows the processor to queue many of the traversal load instructions together which can greatly help the memory behavior of the processor [34].

Like DOACROSS and DOPIPE, DSWP relies on low-latency communication between multiple cores to pass data and control dependencies between the two loop threads. The original DSWP work relied heavily on what was termed the "synchronization array" to achieve this low latency communication between cores [34]. The synchronization array is a set of hardware queues that enable separate cores to both pop and push register values with a latency of 1 cycle between the two cores. The synchronization array works well in simulation and helps minimize overhead, but currently only exist on simulated hardware and therefore unable to be used for anything outside of theoretical proof of concepts. Another constraint of the original DSWP algorithms is that their automatic partitioning of loops into threads was done with a straight cut using heuristics they found experimentally. Their heuristics were usually able to find the best split for their threads, but occasionally would perform miserably, even slowing the loop, while the best hand-tuned split was able to give a respectable increase [28].

DSWP was later extended to use other methods to allow it to scale more reasonably with the number of cores available. The first of these methods was SpecDSWP [37]. Speculation has been used for both DOALL and DOACROSS loops in the past and helps relax some of the constraints on a given loop [30]. Speculation allows the processor to guess if a certain condition is expected to be a single value and so lets the compiler ignore a dependency. For instance, a loop could have only one control dependency created by an error-detection ifstatement. This control dependency would need to be passed from one thread to another and could create more overhead for a DSWP partitioning. The compiler could instead choose to speculate that this value will always be false (assuming the programmer did not make many mistakes) and so this communication could be ignored and a queue from core 1 to 2 would no longer be needed. Extra mechanisms are needed to handle instances where the processor mis-speculates a given edge [37].

Another extension of DSWP combines both DOALL and DSWP into a single method called PS-DSWP or Parallel-Stage Decoupled Software Pipelining [33]. PS-DSWP splits loops into two separate threads of execution, but it then applies DOALL to the newly created threads. This allows DSWP to be easily scalable and to take advantage of large numbers of cores. PS-DSWP has been shown to give a much better speedup then DSWP alone, but still uses heuristics to find its partitions and has only ever been implemented on simulated hardware.

### Chapter 3

### Modern Processor Design

Modern processor design differs greatly from the simple architectures in undergraduate textbooks. As discussed in Chapter 1, modern processors use a pipeline model allowing multiple instructions to execute at once inside a processor. This pipeline organization allows the high clock frequencies seen in today's processors by allowing the work of a single instruction to be done in multiple short clock cycles, rather than one long clock cycle. Processor pipelines, currently, have also been harnessed to allow instructions to complete out of program order, but still in a valid sequence. These features, along with a complex memory system, have allowed modern processors to keep up with the growing pressure to increase hardware performance.

### 3.1 Out-of-Order Pipeline

In a a typical in-order processor, instructions are fetched from memory in program order, executed in program order, and then retired in program order. This pattern of execution is easiest to understand and design and was the typical design of early processors. This method, however, is not the most efficient strategy for a processor to follow. For example, a program might contain a long latency instruction followed by a set of short latency instructions that do not depend on the long latency instruction. In an in-order processor, the processor waits until the long latency instruction has finished executing before it starts to execute subsequent instructions. An out-of-order processor could instead execute

Figure 3.1: Simplified Out-Of-Order Pipeline

the subsequent instructions while it is waiting on the long latency instruction to finish execution. In doing this, out-of-order processors are better able to harness instruction-level-parallelism by executing instructions as soon as they have all of the data they need to execute, even if a preceding instruction has not yet been executed. In executing instructions as soon as their data is ready, the processor has more opportunities to allow multiple instructions to execute at once.

Figure 3.1 illustrates a simplified out-of-order pipeline. In an out-of-order pipeline, instructions are fetched from memory in program order and stored in the instruction queue, which is a FIFO (first-in-first-out) buffer. Instructions are then issued from the instruction queue to different reservation stations depending on what sub-system of the processor they need for execution. For instance, memory instructions may be stored in one reservation station, while instructions using the integer ALU may be sent to another. During a clock cycle, each reservation station checks to see if it contains instructions that have all the data needed for execution, and if so, it dispatches the instruction to be executed. This allows multiple instructions to execute at once, as long as the processor subsystems are available. After an instruction finishes executing, it is sent to be held in the reorder buffer (ROB). The reorder buffer is a queue used to keep the state of memory and registers consistent with a processor that is running in-order. To do this, the ROB only allows instructions to retire (make changes to memory and the registers) in program order, meaning it stores instructions in a queue and only allows them to pop from the front if all preceding instructions in program order have already left the ROB [17].

Since all instructions must move through the ROB before they are retired, it can become a bottleneck in the pipeline. Take for example the Intel Haswell architecture whose ROB is 192 instructions long and can have 72 load instructions executing at once [22]. As will be discussed later, a load instruction requiring main memory can take roughly 200 cycles to execute and will stay in the ROB that entire time. A program could likely exist that has two load instructions that require main memory spaced 200 instructions apart. If both instructions could be executed at the same time, some of the latency of the second load could be masked because it would overlap with the execution time of the first load instruction. This, however, will never occur because the ROB will fill up with the first load instruction and the 191 subsequent instructions. This will cause the second load not to be fetched until the first load is retired from the ROB. DSWP tries to alleviate this problem by moving all load instructions into a single core, pushing as many of the other instructions as possible into a second core. This allows the ROB of the core with mostly loads to not be diluted with non-memory instructions. Ideally this will allow many of the load instructions' executing times to overlap, thus increasing overall performance.

### 3.2 Memory System

All modern processors rely heavily on their memory hierarchy to perform well. Accessing main memory implemented as Random Access Memory (RAM) can require hundreds of CPU cycles. If processors dispatched load instructions to main memory one at a time and waited for them to be fulfilled before moving on, the processors would slow to a crawl compared to modern processor architectures. The primary way they are able to mask this latency is by using a cache hierarchy.

A cache is a small, very fast memory structure that exists on-chip with the main processor. Caches can be organized many ways, but the goal is to keep them full of the data the program will most likely use next. When a program loads data from memory, it first checks the L1 cache and if the data is found (termed a cache hit), it is given to the processor without having to contact main memory. If the data is not found (a cache miss) the next level of cache is queried. This continues until either the data is found in a cache or, as a last resort, main memory. The typical latency today for a L1 cache hit is on the scale of 5 cycles and an L2 cache hit being about double that [17]. This shrinks the latency of a memory load from the point of view of the processor to tens of cycles instead of hundreds allowing it to have a much improved overall performance. The trick, however, is how to choose what information should be stored in the caches.

Software usually accesses memory in a combination of two different patterns which form the idea of data locality. The first type of locality is spatial locality, which is the idea that if data is loaded from a given memory location, data from nearby will most likely be loaded next. An example of this fact is iterating through an array. Caches are structured to take advantage of this idea

Figure 3.2: Modern Processor Memory Hierarchy

by loading data in blocks. Instead of only loading the data that is needed by the processor, a cache will load and store an entire block of data [31]. The processor used in this research, for example, always loads data into its caches as 64 byte blocks. Using this method, the data that is needed by the processor is loaded into the cache along with the bytes around it so they will already be in the cache if they are needed later [22]. The second type of locality is temporal locality, which is the idea that data that has been recently used will most likely be used again. Caches take advantage of this principle by evicting data from the cache that has been used the least recently.

### **3.3** Inter-Core Communication

In the original formulation of DSWP, a Synchronization Array (SA) was used to facilitate inter-core communication [34]. Instead of requiring the creation of a new piece of hardware, my work focuses on implementing DSWP on preexisting hardware. Intel and AMD, the two largest manufactures of processors, currently use two different approaches to allow inter-core communication, but both do agree on using a shared L3 cache as is illustrated in Figure 3.2.

Intel places the L3 cache in the Uncore, the structures of the processor that don't belong to a single core [22]. In the Uncore, the L3 cache is composed of cache slices, with each slice being tied to a core. The slices are arranged into a ring of at most 8 slices that are overseen by an agent. Each slice is fully inclusive of the data held in its processor's higher level caches and uses a write-back policy. Unlike a typical cache, Intel describes the shared cache as having a clean hit and a dirty hit. A clean hit is one in which the data needed is contained within the querying core's cache slice. A dirty hit is one in which the data is found in another core's L3 cache and so the agent must facilitate a transfer of data from the supplying core to the querying core. Because of the ring configuration, depending on the location of the slice providing the data, the latency of the cache hit can be variable [22].

AMD took a slightly different approach with their Ryzen processors. Like Intel, AMD uses cache slices that are tied to a given core. Instead of using a ring of slices, however, these slices are fully connected in sets of 4 slices [6]. Also, instead of being fully inclusive, the L3 slices are victim caches. This configuration of the L3 cache allows AMD to have the same latency to access another core's L3 cache slice as a core's own slice [3].

In both cases, inter-core communication is tied directly to the memory subsystem of each processor. Two cores will never be able to communicate with a latency of less than a L3 dirty hit. This latency is a significant hurdle for DSWP to overcome and is one of the main reasons the original research relied instead on using the Synchronization Array [34].

### Chapter 4

### **Transform Implementation**

This implementation of the DSWP follows the algorithm described by Ottoni and others [28]. This algorithm can be summarized as follows:

- 1. Build Program Dependency Graph (PDG)

- 2. Contract PDG to Form Directed Acyclic Graph

- 3. Determine Partitions Using Machine Learning

- 4. Create Partitions in Software

Steps 1 and 2 are largely unchanged from the process original DSWP given by Ottoni and are implemented with a strong reliance on built-in LLVM transform passes, as discussed in the next section. Machine learning has been added to Step 3 to try to achieve a larger speedup across all benchmarks. Finally, Step 4 has been updated to partition code to run on commonly found hardware instead of relying on hardware with the custom designed Synchronization Array to allow thread communication [34].

### 4.1 Software Details

The DSWP transform was completed implemented in C and C++ along with a few bash scripts to facilitate machine learning training. The majority of the code was created to interface with the LLVM framework. LLVM is a compiler created at the University of Illinois at Urbana-Champaign [25]. Since its first release in 2003, LLVM has expanded in use and is currently the default compiler for all OS X machines. It was created to help facilitate the analysis and transformation of code by using an internal code representation (IR) that reads much like a RISC assembly language, but is hardware independent [1]. This IR is able to capture much of the original high level information that is useful for optimizations during the entire lifetime of the software. The IR is generated by the LLVM front-end, transformations are then run on the IR, and finally the IR is passed onto the LLVM linker and back-end to be turned into machine specific executables. This modular framework facilitates researchers to create generic transformations that operate on the LLVM IR without having to focus on language or machine specific limitations. The following figures in this section are given as LLVM IR.

The DSWP transformations used in this paper were all written as LLVM Loop Transformation Passes so that they could use all of the analysis capabilities included in LLVM. This includes using LLVMs analysis passes such as natural loop discovery, memory analysis, and post-dominator tree creation.

The other library used by this project is Intel's Thread Building Block library [19]. This library was created by Intel to facilitate parallel programming in multiple ways, but this project uses its thread safe queues to form the synchronization arrays outlined for the DSWP algorithm. These queues are non-blocking, fine-grained locking queues that can be safely accessed by multiple threads at once.

### 4.2 Program Dependency Graph Building

After a candidate loop has been found by LLVM, the first step of the DSWP algorithm is to construct its program dependency graph or PDG. The PDG

| 1 % x = load % x.addr          |  |

|--------------------------------|--|

| <sub>2</sub> %y = load %y.addr |  |

| $_{3}$ %sum = add %x, %y       |  |

Figure 4.1: Example Code Snippet for Data Dependence

is constructed to enumerate all data, memory, and control dependencies in a given loop [10]. Within the PDG each instruction composing the target loop is a node within the graph, and all dependencies are directed edges between the instruction nodes.

#### 4.2.1 Data Dependencies

The first of these dependencies, data, is almost trivial to enumerate in LLVM IR because it is in Static Single Assignment (SSA) form [8]. Data dependencies are caused when one instruction uses the value created by another instruction. For example, in the code snippet in Figure 4.1, there is a data dependence between the first and third instructions because the third instruction uses the value created in the first instruction. In a SSA form, each variable is only assigned a single time. So for instance in the code snippet shown in Figure 4.1, the value %y will only be assigned by the above load instruction in the given scope. Because of this, %y can be thought of as a label for the load instruction itself. This relationship is expressed in LLVM IR by the fact that instruction operands can be constants or other instructions. So for the example code snippet, %x is not just a value in LLVM IR, it is equivalent to the load instruction itself. This makes data dependencies very easy to find; the DSWP transform can simply inspect the operands of a given instruction and add dependencies between it and any of its operands that are also instructions.

```

1 %x = load %x.addr

2 %x2 = load %x.addr

3 %y = load %y.addr

4 store %s, %y.addr

```

Figure 4.2: Example Code Snippet for Memory Dependence

#### 4.2.2 Memory Dependencies

The next kind of dependency, memory, is far more complex to find. Memory analysis is a complex subject and is outside the scope of this research, so the built-in LLVM memory analysis passes were used to facilitate this step of PDG building. This project used all of the memory analysis passes that are built into the LLVM framework. The data from these passes is then used to make alias sets. Each alias set is comprised of memory pointers that could possibly alias (refer to the same location in memory). If an alias set only contained pointers that were used to read from memory, then the set was discarded with no change to the PDG. This was done because the set only contained RAR (Read After Read) dependencies which are not true dependencies and so can be reordered as needed.

An example of this is shown in Figure 4.2 between the first two instructions. Both instructions load from the same location, but they can occur in either order without affecting program execution. If an alias set contained pointers that were given to functions that wrote memory or were used in a store instruction, the set was used to create memory dependencies between the instructions in the PDG. An example of this would be the last two instructions shown in Figure 4.2. If the store instruction was to happen before the last load instruction, it would most likely change the outcome of the program and so is marked as a dependency in the PDG.

```

1 IF_COND:

2 br %x, 0, %IF_BODY, %IF_END

4 IF_BODY:

5 store %x, %x.addr

6 br %IF_END

7

8 IF_END:

9 %y = load %y.addr

```

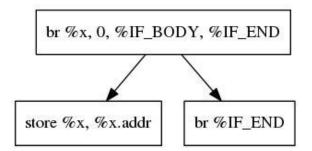

Figure 4.3: Example Code Snippet for Control Dependence

#### 4.2.3 Control Dependencies

The final type of dependency that must be added to the PDG is control dependencies. These occur when an instruction can control whether or not another instruction will execute. An example of a control dependence is shown in Figure 4.3. The first "br" instruction can control whether or not the value of %x will be stored into memory, therefore this dependency needs to be added to the PDG of the example program. These control dependencies can most easily be found using a post-dominator tree (PDT). This project used LLVM to build the PDT which uses the algorithm outlined by Lenguer and Tarjan [26]. The PDT is built with the basic blocks (BB) of the loop as its nodes and the edges showing the post-dominance relationship between the different BB's. A node, D, is post-dominated by another node, E, if the program cannot reach the end of the loop starting at D without traveling through E [10]. For example, in Figure 4.3, the program cannot reach IF\_END without going through the IF\_COND block, therefore IF\_END is post-dominated by IF\_COND.

Once the PDT has been found, it can be used to find control dependencies between BB's. A control dependency from basic block D to E iff D is not postdominated by E and there is a path from D to E in which all BB's (that aren't

Figure 4.4: Example Control Dependence within PDG

D or E) are post-dominated by E. This relationship can be seen in Figure 4.3; IF\_COND is not post-dominated by IF\_BODY, and since there are not other nodes in the path between the two BB's the second condition is also met.

These control dependencies are shown within the PDG by adding an edge from each instruction in a basic block to the terminator of the controlling block. For example, for Figure 4.3, an edge would be added between the br % x,  $0, \% IF\_BODY, \% IF\_END$  instruction and both instructions in the IF\_BODY basic block as shown in Figure 4.4.

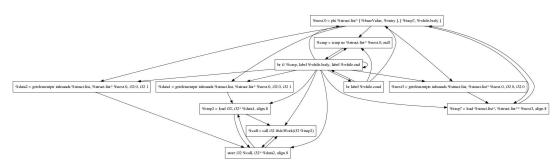

## 4.3 Directed Acyclic Graph Building

A requirement for DSWP is that all data flows must be unidirectional: data cannot flow in and out from the same thread in a valid partitioning [34]. A normal program dependency graph will have many cycles which are usually formed by program loops. To facilitate DSWP partitioning the PDG is condensed by contracting all instructions that are strongly connected components (SCC) into a single node. The search for SCC's in the PDG is done using LLVM's built in scc\_iterator which uses Tarjan's strongly connected components algorithm [36].

The contraction of the SCC will condense the PDG into a directed acyclic graph (DAG) that can be used for DSWP partitioning. The DAG will not

```

1 while (next != 0x00)

2 {

3     int data = next->data;

4     data = doWork(data);

5     next->data = data;

6     next = next->next;

7 }

```

Figure 4.5: Example Code Snippet for PDG and DAG

Figure 4.6: Example PDG for Code Snippet

contain any cycles that can cause problems during the later DSWP partitioning. An example of this contraction can be seen in Figure 4.7; it is the contraction of the PDG in Figure 4.6 which was generated from the code in Figure 4.5. All instructions in a strongly connected component will be partitioned into the same thread. This is similar to the partitioning of SCCs to cores used in a hardware approach to pipelining, Two Pass Pipelining [4,5].

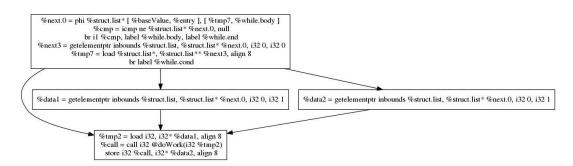

## 4.4 Determine Partitions Using Machine Learning

Previously, DSWP research has used different heuristics to choose which nodes of a loop's DAG should be assigned to each DSWP partition [28] [33] [37]. Usually these heuristics were able to create partitions that gave a decent speedup and were able to match the best partition found iteratively. Sometimes, however, the heuristics would perform very poorly on a few loops and would slow down the code greatly. This project sought to use machine learning (ML) to better handle

Figure 4.7: Example DAG Condensation of PDG

different types of loops and so hopefully perform well on a broader spectrum of loops.

#### 4.4.1 Reinforcement Learning

Reinforcement Learning (RL) provides a system to define a problem that needs to be solved in some statistical manner. Unlike many forms of machine learning, reinforcement learning is not a supervised learning method: the exact correct solution for the problem in not known [15]. RL is instead used to solve problems where only the "goodness" of a solution is measurable. In RL an agent makes decisions in its environment to try to solve a problem. To help define the problem, an RL solution can be broken into 5 basic subelements:

- States : S

- All configurations the environment could possible be in.

- Actions : A

- A set of all actions that the agent can take.

- Policy :  $\pi : S \to P(A = a|S)$

- A mapping from states to actions that describes the probability that

|                    | $\begin{bmatrix} Q \\ Q $                  | $(s_0, a)$<br>$(s_1, a)$<br>$\vdots$<br>$(s_m, a)$ | $(u_0) \\ (u_1) \\ (u_1) \\ (u_0) \\ (u_0$ | $Q(s_0, a_1)$ $Q(s_1, a_1)$ $\vdots$ $Q(s_m, a_1)$ | ····<br>···<br>··. | $Q(s_0, Q(s_1, g)) = Q(s_1, g)$ $\vdots$ $Q(s_m, g) = Q(s_m, g)$ | $\begin{bmatrix} a_n \\ a_n \end{bmatrix}$ |     |

|--------------------|------------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------|------------------------------------------------------------------|--------------------------------------------|-----|

|                    |                                                                                    |                                                    | (8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | a) Generic Q                                       | -Tabl              | le                                                               |                                            |     |

| Γ1                 | 3                                                                                  | 6                                                  | 8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                    | Γ.                 | 1 3                                                              | 5.88                                       | 8 ] |

| 4                  | 2                                                                                  | 5                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                    | 4                  | 4 2                                                              | 5                                          | .76 |

| 1                  | 6                                                                                  | 8                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                    | -                  | 16                                                               | 8                                          | 2   |

| 4                  | $     \begin{array}{c}       3 \\       2 \\       6 \\       -3     \end{array} $ | 10                                                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                    | 4                  | 4 - 3                                                            | $5.88 \\ 5 \\ 8 \\ 10$                     | 5   |

| (b) Q-Table Before |                                                                                    |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                    | (c) Q-7            | Table A                                                          | fter                                       |     |

Figure 4.8: Example Q-Tables for SARSA

the agent will take an action given the state the environment is currently in.

- Reward Function:  $R: (s, a) \to \mathbb{R}$

- A mapping from state-action pairs (the action taken by the agent from a given state) to a numeric value that measures the *short-term* "goodness" of an action.

- Value Function:  $Q: (s, a) \to \mathbb{R}$

- A mapping from state-action pairs to a numeric value that measures the *long-term* "goodness" of an action.

Notice that the subelements do not describe a solution to a given problem, but merely act as a framework that can be used to describe the problem [35].

### 4.4.2 Learning Method and Policy

The solution chosen for this research to solve the DSWP partitioning problem is State-Action-Reward-State-Action (SARSA) with an epsilon-greedy policy. SARSA seeks to create and update a table of Q-values until it converges on the true Q values for a given set of states and actions. After the table converges the learner can then exploit the learned values to take actions that will give it the most long term rewards [38]. A generic Q-table for a state space with states  $s_0$ to  $s_m$  and an action space with actions  $a_0$  to  $a_n$  is shown in Figure 4.8a. This table is initialized to some set of values and then needs to be updated to reach the true Q values for the current policy. This update is done iteratively by the learner as it explores its environment. For each time-step, t, the agent takes some action  $a_t$  from its current state  $s_t$  and will receive some reward from the environment  $r_{t+1}$ . This then moves the agent into a new state  $s_{t+1}$  where it will again take a new action  $a_{t+1}$  and receive another reward  $r_{t+2}$ . Each time the agent takes an action it will update its Q-table using the following formula:

$$Q(s_t, a_t) \leftarrow Q(s_t, a_t) + \alpha * [r_{t+1} + \gamma * Q(s_{t+1}, a_{t+1}) - Q(s_t, a_t)]$$

(4.1)

In the formula,  $\alpha$  is the learning rate (which is usually very small, but always between 0 and 1) and  $\gamma$  is the discount factor (which is also always between 0 and 1) [35]. A large learning rate can speed up the learning process but can also make the agent very sensitive to noise. A large gamma favors long term rewards over short term rewards.

An example of an agent moving through states by taking different actions can be seen in Formula 4.2.

$$\mathbf{s_0} \to_{a_2} \mathbf{s_1} \to_{a_3} \mathbf{s_3} \to_{a_1} \mathbf{s_0} \tag{4.2}$$

An example of how the Q-Table for this agent would be before and after the three actions is shown in Tables 4.8b and 4.8c, respectively. After the first action,  $a_2$  in this case, the agent moves from state  $s_0$  to  $s_2$  and is given some

reward; for this example it will get a reward of 4. For formula 4.1 these values can be filled in for  $s_t$ ,  $s_{t+1}$ ,  $a_t$ , and  $r_{t+1}$  as follows:

$$Q(0,2) \leftarrow Q(0,2) + \alpha * [4 + \gamma * Q(s_1, a_{t+1}) - Q(0,2)]$$

(4.3)

Next the agent takes its next action to go from  $s_1$  to  $s_3$  using action  $a_3$  and gets a reward of 1. This allows the values of  $a_{t+1}$  to be added. Also for this problem  $\alpha$  will be set to 0.1, and  $\gamma$  will be set to 0.8. Now the formula is the following:

$$Q(0,2) \leftarrow Q(0,2) + 0.1 * [4 + 0.8 * Q(1,3) - Q(0,2)]$$

(4.4)

Next the original Q-Table (Figure 4.8b) is used to fill in values for the Q(0, 2)and Q(1, 3) arguments.

$$Q(0,2) \leftarrow 6 + 0.1 * [4 + 0.8 * 1 - 6] \tag{4.5}$$

Solving we find the new value of Q(0,2) is 5.88. This is done once again to update the value at Q(1,3) and the final Q-table is shown in Figure 4.8c.

The policy used by the agent to choose which actions to take from a given state is the epsilon-greedy policy. In this policy the agent chooses to take a random action with probability  $\epsilon$  and chooses the to take the action with the highest Q value with probability  $1 - \epsilon$ . Epsilon-greedy tries to balance both exploration and exploitation of a given environment to achieve the highest rewards over time. An  $\epsilon$  close to 1 will create a learner whose actions are almost completely randomly and so will explore most of the state space. An agent with an  $\epsilon$  close to 0 will always try to exploit its knowledge by choosing the action with the Q value but may miss actions that have much better reward by never exploring them and so never updating its Q-value to acknowledge the higher rewards.

Table 4.1: State and Action Definitions for DSWP ML

| Cycle Ratio  | Latency       | Flows        | Slack         | Percent   | Actions |

|--------------|---------------|--------------|---------------|-----------|---------|

| [0.00, 0.20) | [0, 10]       | [0, 0]       | [0, 50]       | [0, 10]   | ABOVE   |

| [0.20, 0.30) | (10, 30]      | [1,1]        | $(50,\infty)$ | (10, 20]  | BELOW   |