# A LOW POWER LOW MODULATION INDEX ASK DEMODULATOR DESIGN FOR RFID APPLICATIONS

By

## HALADY ARPIT RAO

Bachelor of Engineering in Electronics

Mumbai University

Mumbai, Maharashtra, INDIA

2014

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE December 2016

# A LOW POWER LOW MODULATION INDEX ASK DEMODULATOR DESIGN FOR RFID APPLICATIONS

Thesis Approved:

Dr. Chris Hutchens

Thesis Adviser

Dr. Jim West

Dr. Martin Hagan

Acknowledgements reflect the views of the author and are not endorsed by committee members or Oklahoma State University.

# ACKNOWLEDGEMENTS

I would first and foremost like to thank my parents who have constantly supported me during the good times and the bad.

During my time at Oklahoma State University I was fortunate to come in contact with my advisor Dr. Chris Hutchens who took me under his guidance without much of a fuss, I sincerely thank him for his patience and time. He not only helped me in this effort but throughout my time as a Graduate student.

A special thanks to my Thesis Committee members Dr. West and Dr. Hagan who lent their insights into refining and enriching this work.

During my time as a Masters student I came across some wonderful people helped me in my academic endeavors, these people include Dr. Rehan Ahmed, Mr. Cheng Hao, Mr. Aniket Kulkarni and Mr. Kaniska De.

Also I am grateful to all the individuals that contributed their work to the academic community whose work I was fortunate to not only learn from but build on in this effort.

#### Name: HALADY ARPIT RAO

#### Date of Degree: DECEMBER 2016

# Title of Study: A LOW POWER LOW MODULATION INDEX ASK DEMODULATOR DESIGN FOR RFID APPLICATIONS

## Major Field: ELECTRICAL ENGINEERING

Abstract: In the era of the Internet of Things (IoT) there is a tremendous increase in portable wireless devices utilized in our day to day working. One such example is the Radio Frequency Identification tag. The primary challenge in designing passive RFID tags is reliable functionality over extreme temperature and environmental conditions with low power operation. An important component of the RFID tag architecture is the demodulator which is tasked with interpreting the incoming data and extracting the reference clock for the Phase Locked Loop. A novel ASK demodulator architecture that functions across a temperature range of -25°C to 125°C is designed, analyzed and optimized for the worst and best case semiconductor process variations. The incoming RF frequency is selected as 900MHz based on the EPC GEN2 protocol and the baseband signal is set at 450 KHz with a modulation index of 5%. MOS transistor operation and variability in semiconductor processes is explored and a better understanding of how these concepts effect and shape our design decisions is established. A design objective is setup and steps to achieve these design objectives are presented. The design of the ASK demodulator is completed with the help of the Cadence Virtuoso tool, utilizing the IBM 0.18µm (CMOS 7RF) process. In order to test our design we have used the Monte Carlo analysis and all the significant DC parameters of the design have been tested for 10,000 samples owing to the high variability associated with modern semiconductor processes. On the other hand Monte Carlo simulations for the transient simulations have been done for 30 samples in accordance with the Central Limit Theorem. The results of the design are compared with other ASK RFID demodulator designs in the past and a comparison is made by utilizing a Figure of Merit from literature. The design is among the best ASK demodulator designs found in literature. Throughout this effort there is emphasis on MOS transistor operation and variations in semiconductor processes. The design takes all pertinent challenges such as extreme temperature, environment conditions and the reliability of the design. Through this work an attempt is made to try and simplify the work of the reader and expose them to the challenges associated with ASK demodulator design.

# TABLE OF CONTENTS

| Chapter                                              | Page |

|------------------------------------------------------|------|

| I. INTRODUCTION                                      | 1    |

| 1.1 Introduction to IoT                              | 1    |

| 1.2 Introduction to RFIDs                            | 2    |

| 1.3 Ultra-Low Power Requirement                      | 4    |

| 1.4 Pulse Interval Encoding                          | 5    |

| 1.5 Matching Network and Harvester Circuits          | 7    |

| 1.5.1 Matching Network                               |      |

| 1.5.2 Harvester Circuit                              |      |

| 1.6 Research Objective                               |      |

| 1.7 Thesis Organization                              |      |

| II. MOS Transistors Characteristics and Variability  | 14   |

| 2.1 Subthreshold/Near Threshold Designing            | 14   |

| 2.1.1 Advantages of Operating in Subthreshold Region | 18   |

| 2.1.2 Drawbacks of Operating in Subthreshold Region  | 20   |

| 2.1.3 Subthreshold Operating Limits                  | 21   |

| 2.2 Process Variation                                |      |

| 2.2.1 Random Dopant Fluctuation (RDF)                | 22   |

| 2.2.2 Line Edge Roughness (LER)                      | 24   |

| 2.2.3 Random Telegraph Noise (RTN)                   | 25   |

| 2.2.4 Influence of Neighbors                         | 26   |

| 2.2.5 Small Dimension Effects                        | 26   |

# Chapter

# Page

| 2.2.6 Effects of Process Variation                                                | 31  |

|-----------------------------------------------------------------------------------|-----|

| 2.2.7 Global Variation (Systematic/Process Variation)                             | 32  |

| 2.2.8 Local Variation                                                             |     |

| 2.2.9 Monte Carlo                                                                 | 35  |

| 2.2.10 Process Corners                                                            |     |

| 2.2.11 Lot-to-Lot and Wafer-to-Wafer Variation                                    | 37  |

| 2.3 Temperature Variation                                                         |     |

| 2.3.1 Effect of Temperature Change in Weak Inversion                              |     |

| 2.3.2 Effect of Temperature Change in Strong Inversion                            |     |

| 2.3.3 Zero Temperature Coefficient Point (ZTC)                                    |     |

| 5.2.2 Amplifier Second stage DC Monte Carlo results                               |     |

| 2.4 Supply Voltage Variation                                                      |     |

| 2.5 PVT (Process, Voltage and Temperature) Corners                                |     |

| 2.5.1 Weak Inversion PVT corners                                                  |     |

| 2.5.2 Strong Inversion PVT corners                                                |     |

|                                                                                   |     |

|                                                                                   |     |

| III. ASK DEMODULATORS                                                             | 46  |

|                                                                                   |     |

| 3.1 Digital Modulation                                                            |     |

| 3.2 ASK Demodulators                                                              |     |

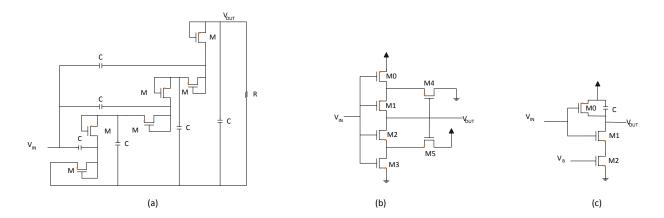

| 3.2.1 Voltage-Mode ASK Demodulators                                               |     |

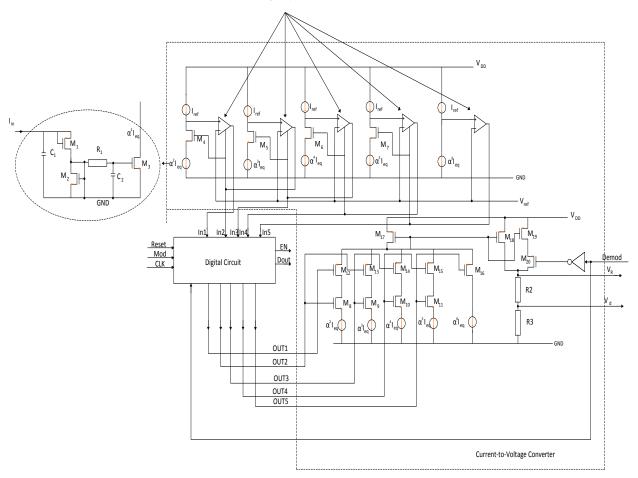

| 3.2.2 Current-Mode ASK Demodulators                                               |     |

| 3.2.3 Mixed-Mode ASK Demodulators                                                 |     |

| 3.3 Tabular Comparison of ASK Demodulators in the past                            | 57  |

| IV. Design Implementation                                                         | 60  |

|                                                                                   | - 0 |

| 4.1 Input to the ASK Demodulator                                                  |     |

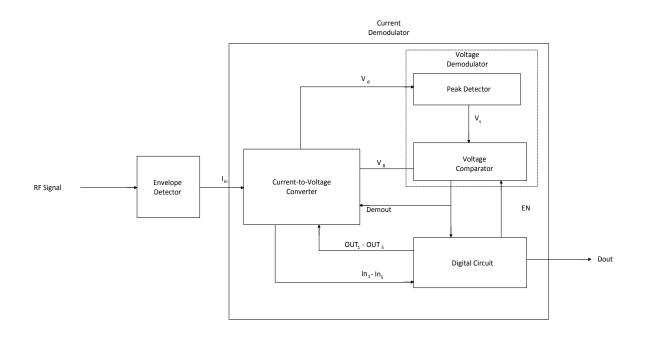

| 4.2 Block Diagram of Front End of the RFID                                        |     |

| 4.3 The Envelope Detector                                                         |     |

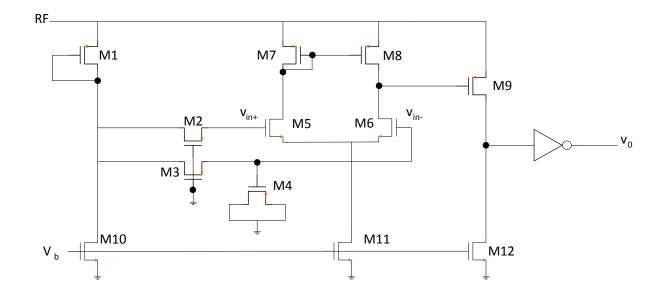

| 4.4 The Filter-Amplifier                                                          |     |

| 4.4.1 Feedback Resistor                                                           |     |

| 4.4.2 First stage amplifier Working                                               |     |

| 4.4.3 Second Stage amplifier                                                      |     |

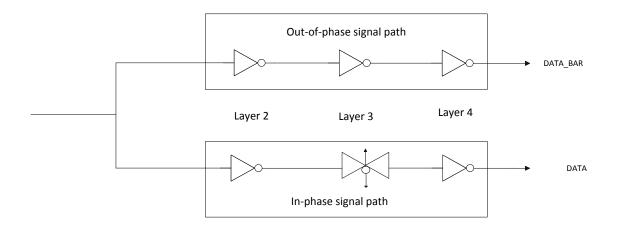

| 4.5 Phase Splitter                                                                |     |

| 4.6 Design Objective                                                              |     |

| 4.6.1 Bandwidth of the first and Second stage amplifier                           |     |

| 4.6.2 The Offset of the first and second stage amplifier: $V_{os1}$ and $V_{os2}$ |     |

| 4.6.3 Gain of the first and second stage amplifier                                |     |

| 4.6.4 Total Power                                                                 |     |

| 4.6.5 Demodulator Design Specifications                                           | 91  |

| V. | Simulation Results                                          |     |

|----|-------------------------------------------------------------|-----|

|    | 5.1 Transient Simulations                                   | 92  |

|    | 5.2 DC Monte Carlo Results                                  | 96  |

|    | 5.2.1 Amplifier First stage DC Monte Carlo results          | 97  |

|    | 5.2.2 Amplifier Second stage DC Monte Carlo results         |     |

|    | 5.3 Monte Carlo Transient Simulations for $N = 30$          |     |

| VI | . Conclusion                                                | 110 |

|    | 6.1 Important parameters in Formulating the Figure of Merit | 110 |

|    | 6.2 Figure of Merits in the past                            |     |

|    | 6.3 Future Scope                                            |     |

|    | 6.4 Conclusion                                              |     |

|    |                                                             |     |

| APPENDICES | <br> | <br> | , |

|------------|------|------|---|

# LIST OF TABLES

| Table                                                          | Page |

|----------------------------------------------------------------|------|

| 3.1 Design Parameters of ASK Demodulators designed in the past | 58   |

| 4.1 Characteristics of RR Polysilicon Resistor R <sub>1</sub>  | 65   |

| 4.2 Demodulator block Characteristics                          |      |

| 4.3 Demodulator transistor geometries                          | 84   |

| 4.5 Performance of the Designed ASK Demodulator                | 90   |

| 6.1 Performance Comparison Table                               | 112  |

|                                                                |      |

# LIST OF FIGURES

# Figure

# Page

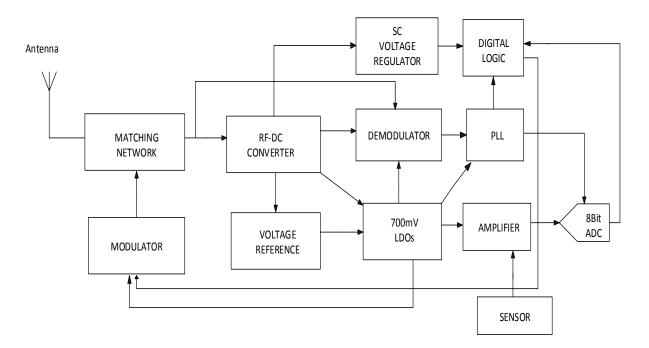

| 1.1 Complete Block Diagram of a "smart" RFID tag                                          | 4 |

|-------------------------------------------------------------------------------------------|---|

| 1.2 Baseband waveform of Pulse Interval Encoding                                          |   |

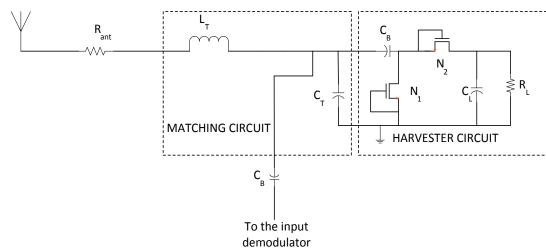

| 1.3 Front End Circuit of the RFID                                                         |   |

| 1.4 L match network                                                                       |   |

| 1.5 Basic Harvester Circuit                                                               |   |

| 1.6 Negative half cycle of the Input at the Harvester10                                   |   |

| 1.7 Negative half cycle of the Input at the Harvester10                                   |   |

| 2.1 Log of inversion layer charge vs the gate-to-body voltage for a two terminal MOS      |   |

| device                                                                                    | 5 |

| $2.2 \ln(I_D) vs V_{GS}$ plot                                                             | 7 |

| $2.3 \frac{gm}{I_D} vs V_{GS}$ plot                                                       |   |

| 2.4 Transition frequency vs gate-to-source voltage for a diode connected NMOS             |   |

| transistor                                                                                | 0 |

| 2.5 Sources of Variation                                                                  | 2 |

| 2.6 Atomistic simulation demonstrating RDF and LEF                                        | 3 |

| 2.7 Impact of Random Dopant Fluctuation on $\sigma_{VTH}$ with change in channel length24 | 4 |

| 2.8 Lithography Wavelength for different process nodes                                    |   |

| 2.9 Threshold voltage vs Width of a 1µm long NMOS diode connected transistor              |   |

| (V <sub>GS</sub> =700mV)                                                                  | 2 |

| Figure                                                                            | Page      |

|-----------------------------------------------------------------------------------|-----------|

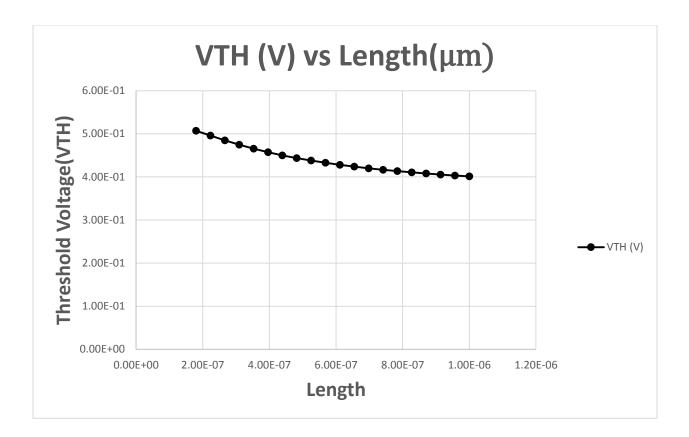

| 2.10 Threshold voltage vs Length of a 1µm wide NMOS diode connected transist      | or        |

| (V <sub>GS</sub> =700mV)                                                          | 30        |

| 2.11 The effects of Variation                                                     | 31        |

| 2.12. Radial gradient on wafer                                                    | 33        |

| 2.13 Stochastic perspective for Random and Systematic Variation of Threshold ve   | oltage of |

| a device                                                                          | 35        |

| 2.14 Lot-to-Lot Variation                                                         | 37        |

| 2.15 Wafer-to-Wafer Variation                                                     | 38        |

| 2.16 Drain Current Dependence on Temperature and the ZTC Point for a minimum geom | netry     |

|                                                                                   |           |

| NMOS                                                                              | 42        |

|                                                                                   |           |

| 2.17 Drain Current Dependence on Temperature and the ZTC Point for a minimum geom | netry     |

| PMOS                                                                              | 43        |

| 2.18 Weak inversion PVT corners                                                     | .44 |

|-------------------------------------------------------------------------------------|-----|

| 2.19 Strong inversion PVT corners                                                   | .45 |

| 3.1 Binary ASK modulated bit stream                                                 | .46 |

| 3.2 Basic implementation of a demodulator                                           | .47 |

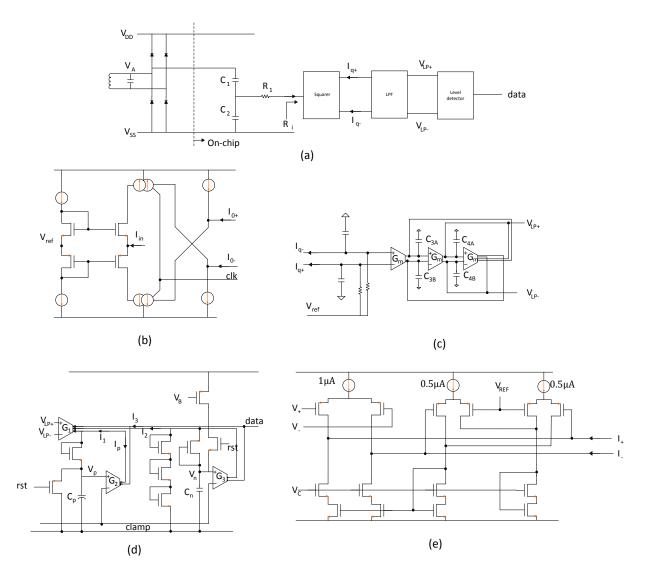

| 3.3 Bouvier et al Circuit Diagram                                                   | .50 |

| 3.4(a) Envelope Detector circuit by Mendizabel et al[1]                             | .51 |

| 3.4 (b)Dokic Schmitt Trigger circuit [2]                                            |     |

| 3.4 (c) Integrator Circuit[1]                                                       | .51 |

| 3.5 Block Diagram of LIU et al[3]                                                   |     |

| 3.6 Current to voltage Converter by [3]                                             | .54 |

| 3.7 (a) Block Diagram of Gudnason[4] (b) Squarer circuit[4] (c) The differential LP | ΥF  |

| implementation[4] (d) The peak detector and data signal extraction circuit[4] (e) A |     |

| single-output filter transconductor, with CMFB circuit[4]                           | .55 |

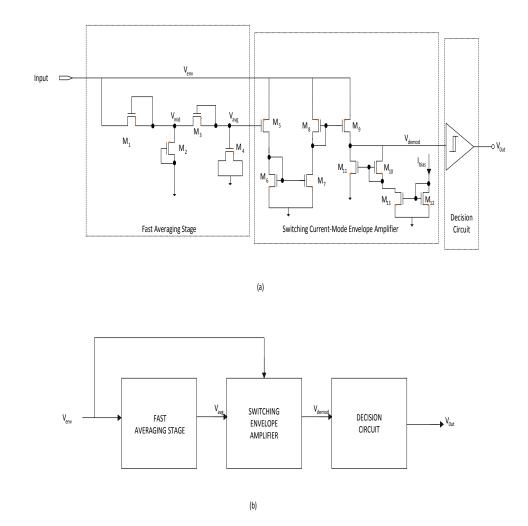

| 3.8 (a) Mousavi et al circuit diagram (b) equivalent block diagram[5]               |     |

| 4.1 DSB-AM Waveform                                                                 | .60 |

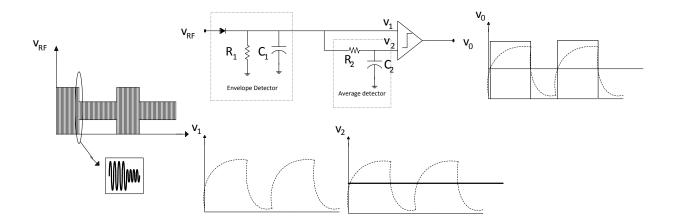

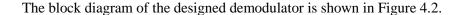

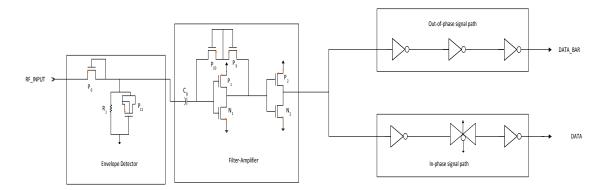

| 4.2 Block Diagram of the Designed ASK Demodulator                                   | .63 |

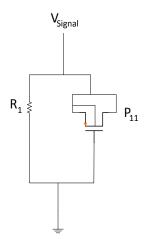

| 4.3 Combination of the Resistor R1 and the MOS capacitor P11                        | .64 |

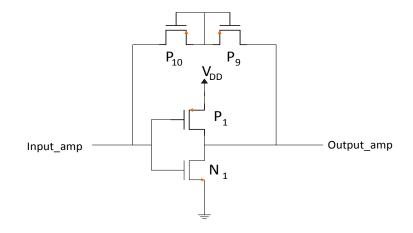

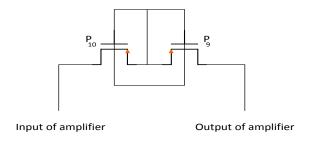

| 4.4 Complementary Common Source amplifier with feedback resistor                    | .66 |

| 4.5 Feedback resistor network                                                       |     |

| 4.6 Small signal equivalent of the feedback                                         | .67 |

| 4.7 Test setup to observe the frequency response of the feedback network            | .69 |

| 4.8 Frequency response of the feedback resistor network                             | .70 |

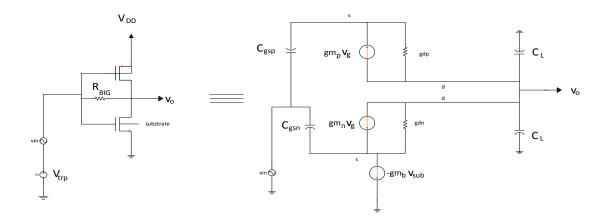

| 4.9 (a) shows the amplifier circuit and (b) Depicts its equivalent circuit70                         |    |

|------------------------------------------------------------------------------------------------------|----|

| 4.10 Small signal equivalent of the amplifier                                                        |    |

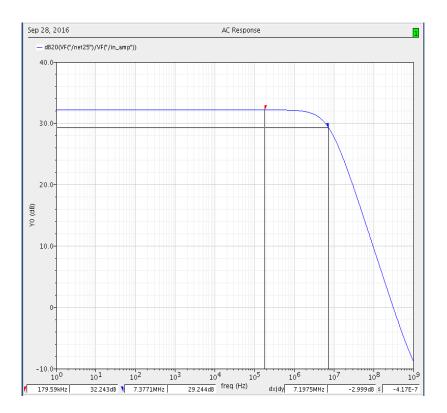

| 4.11 Bode plot of the AC response of the Complementary C-S amplifier                                 |    |

| 4.12 Phase splitter block diagram                                                                    |    |

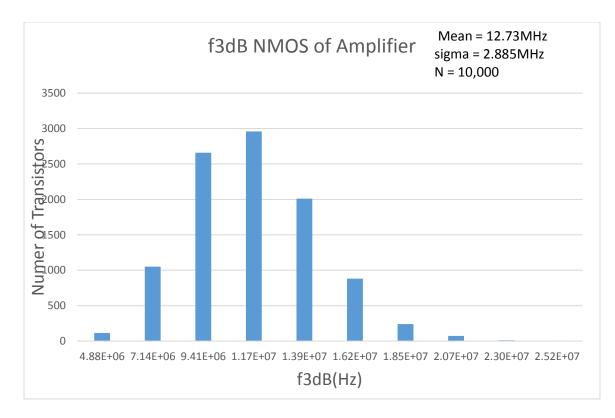

| 4.13 Monte Carlo data for f3dB of the NMOS transistor in the Complementary C-S                       |    |

| amplifier                                                                                            |    |

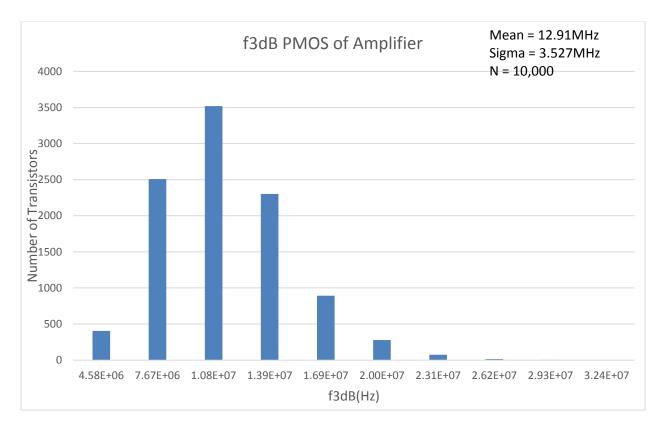

| 4.14 Monte Carlo data for f3dB of the PMOS transistor in the Complementary C-S                       |    |

| amplifier                                                                                            |    |

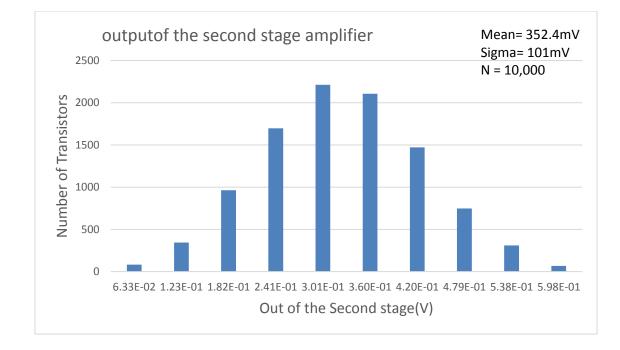

| 4.15 Voltage at the Output of the second stage complementary C-S amplifier                           |    |

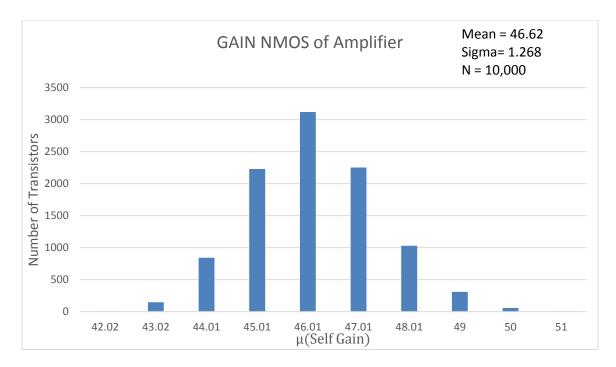

| 4.16 Monte Carlo results for the Self gain of the NMOS transistor in the Complementary               | y  |

| C-S amplifier                                                                                        |    |

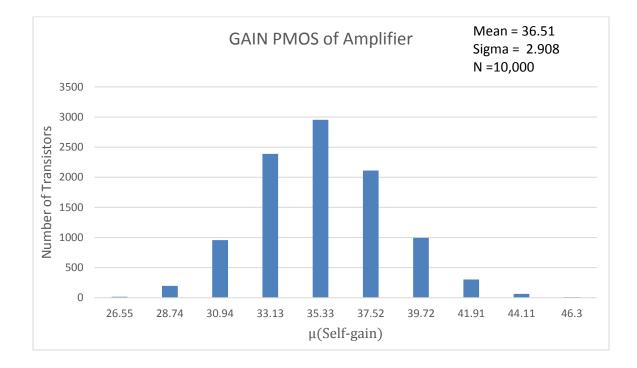

| 4.17 Monte Carlo results for the Self gain of the PMOS transistor in the Complementary               | 1  |

| C-S amplifier                                                                                        |    |

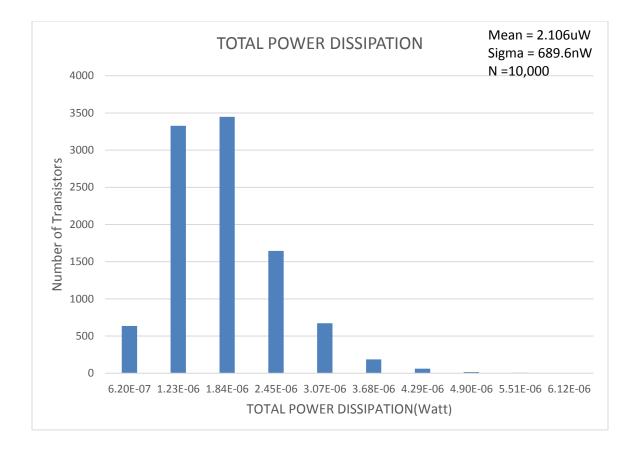

| 4.18 Monte Carlo results for Total Power Consumption                                                 |    |

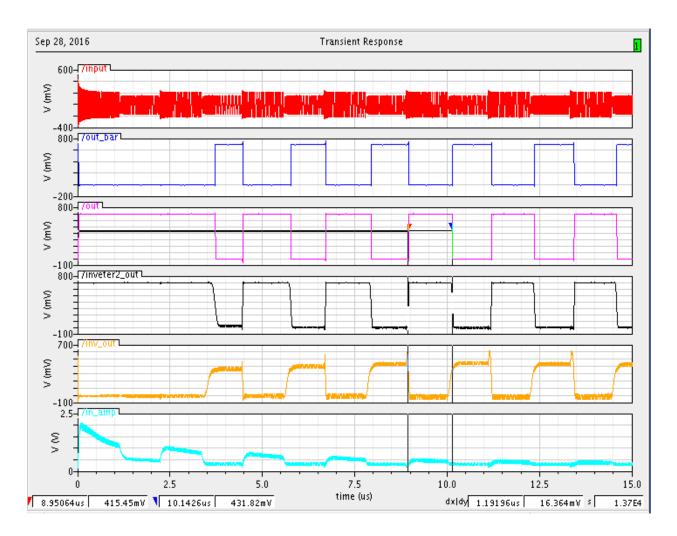

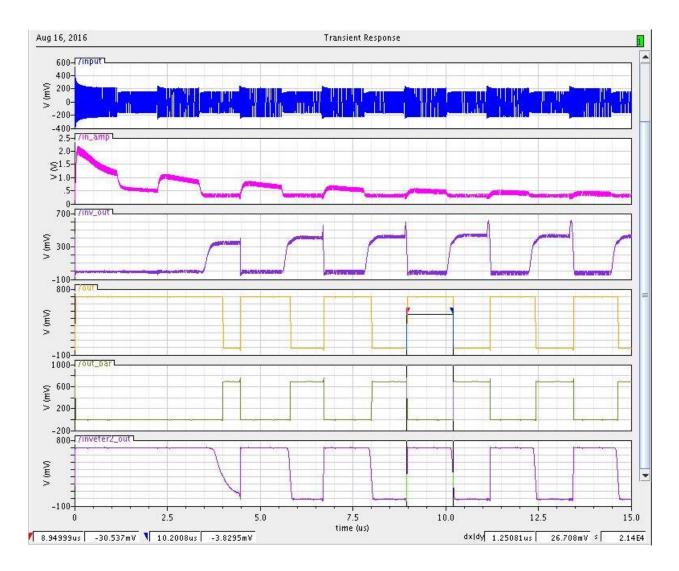

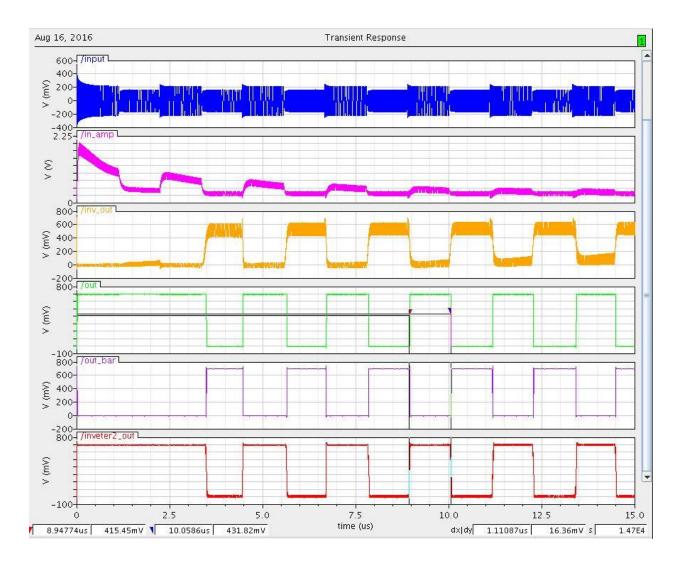

| 5.1 Transient simulations for typical-typical process @ 27°C94                                       |    |

| 5.2 Transient simulations for slow-slow process @ -25°C                                              |    |

| 5.3 Transient simulations for fast-fast process @ 125°C                                              |    |

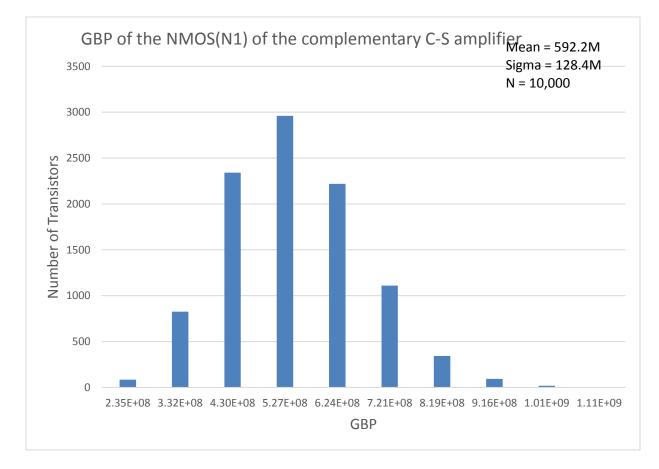

| 5.4 GBP of NMOS (N1) in the first stage of the complementary C-S amplifier97                         |    |

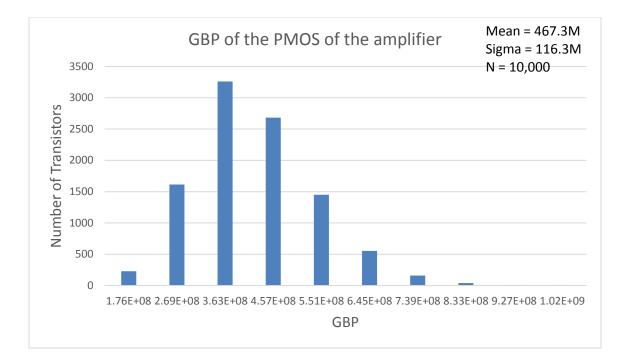

| 5.5 GBP of PMOS in the first stage of the complementary C-S amplifier                                |    |

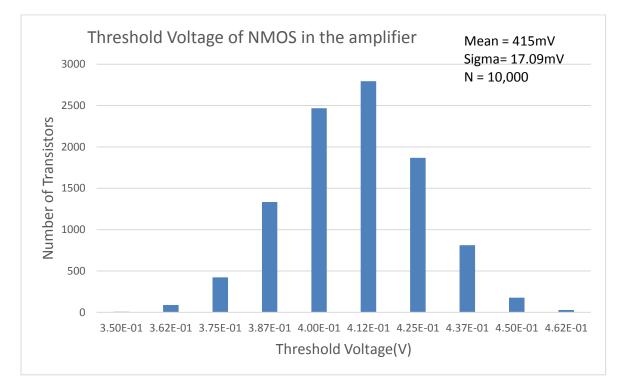

| 5.6 Threshold Voltage of the NMOS transistor in the first stage of the complementary C               |    |

| S amplifier                                                                                          |    |

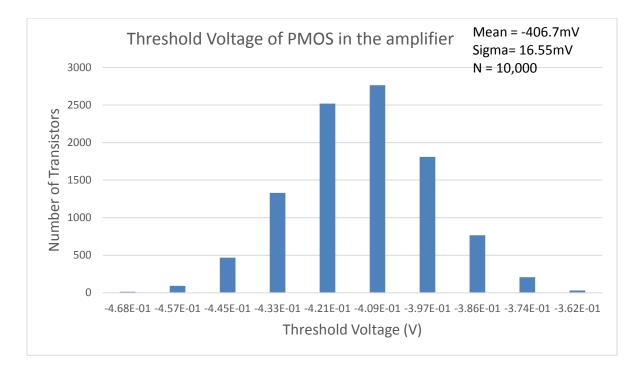

| 5.7 Threshold Voltage of the PMOS transistor in the first stage of the complementary C               | -S |

| amplifier                                                                                            |    |

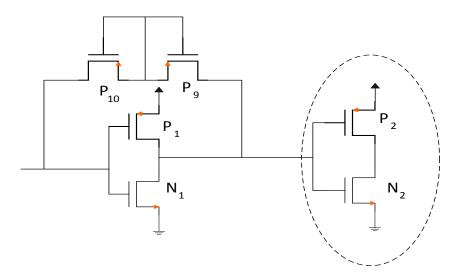

| 5.8 second stage Complementary C-S amplifier in the dashed Ellipse100                                |    |

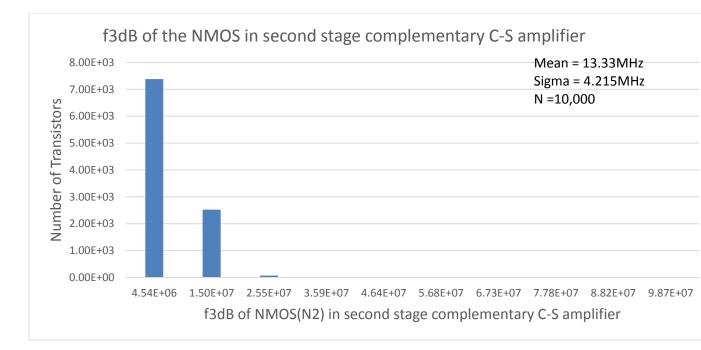

| 5.9 f3dB of the NMOS (N2) in the second stage complementary C-S Amplifier101                         |    |

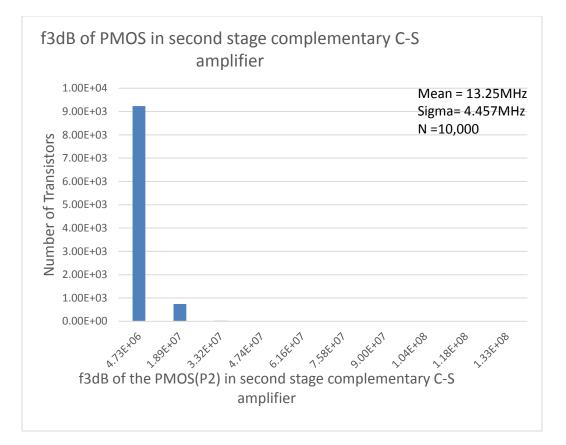

| 5.10 f3dB of the PMOS (P2) in the second stage complementary C-S Amplifier102                        |    |

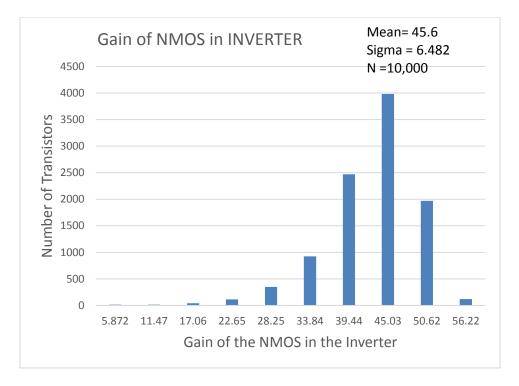

| 5.11 Gain of the NMOS in the Second stage of the Complementary C-S amplifier .103                    |    |

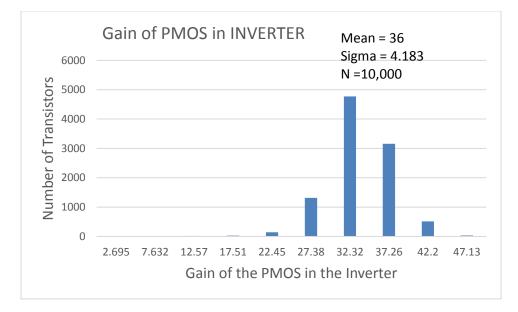

| 5.12 Gain of PMOS in the Second stage of the Complementary C-S amplifier103                          |    |

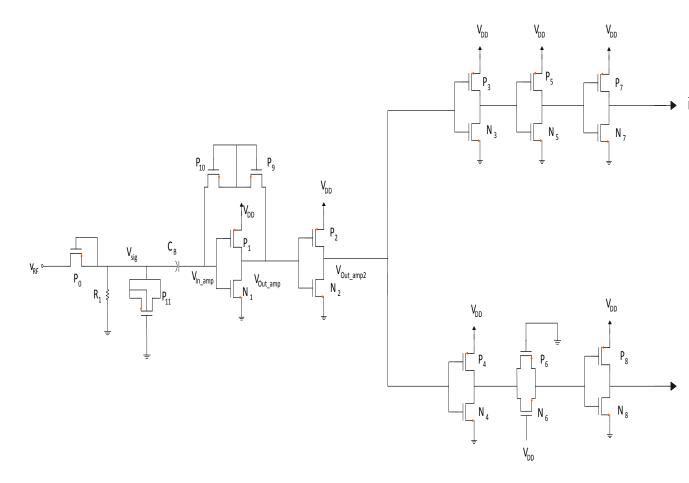

| 5.13 Demodulator circuit diagram                                                                     |    |

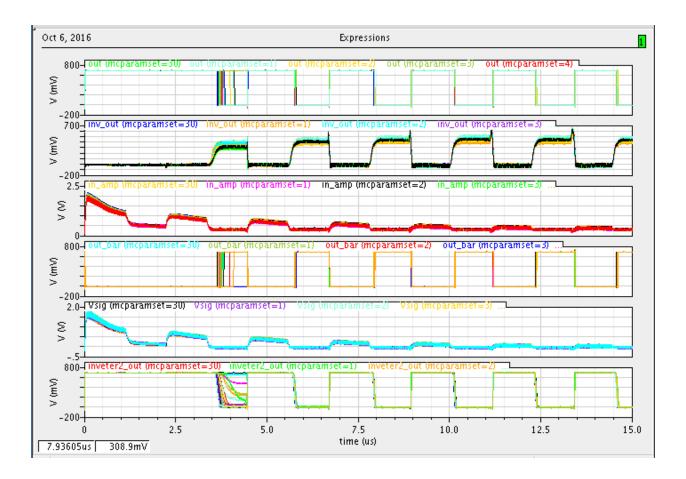

| 5.14 Monte Carlo Simulations for 30 samples105                                                       |    |

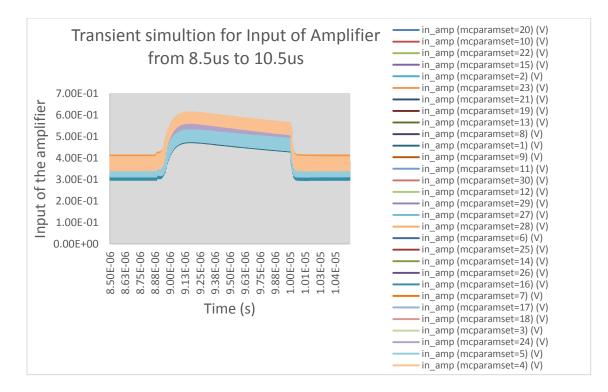

| 5.15 Transient Simulation of Input of the first stage of the Amplifier from 8.5µs to 10.5µ           | μs |

|                                                                                                      |    |

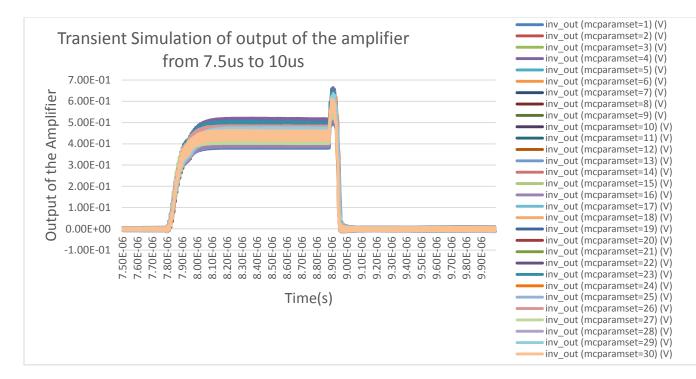

| 5.16 Transient Simulation of Output of the first stage of the Amplifier from $7.5 \mu s$ to $10 \mu$ | JS |

|                                                                                                      |    |

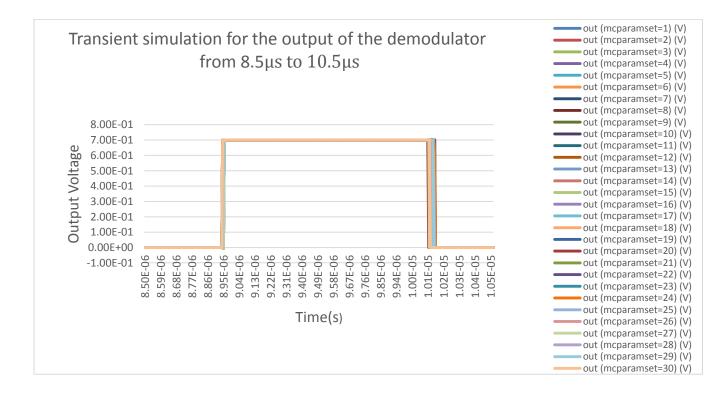

| 5.17 Transient simulation of Output of the Demodulator from 8.5µs to 10.5µs107                       |    |

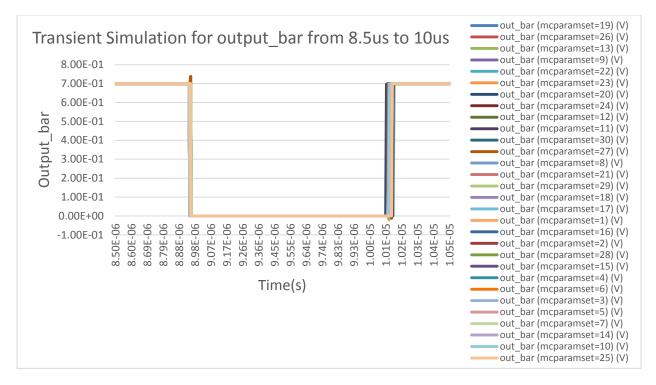

| 5.18 Transient Simulation of Inverse of the Output of the Demodulator from 8.5µs to                  |    |

| 10.5µs                                                                                               |    |

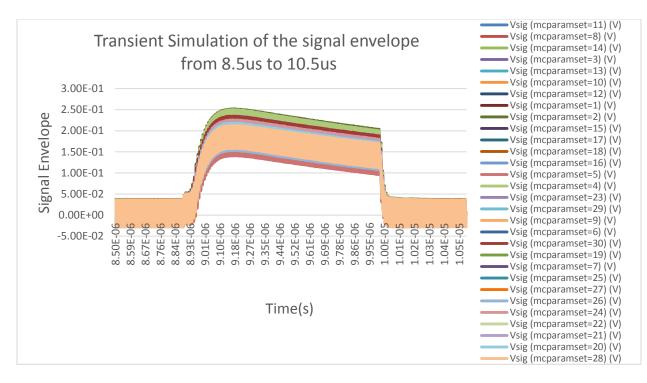

| 5.19 Transient Simulation of Voltage at the output of the Envelope Detector from 8.5µs               |    |

| to 10.5µs                                                                                            |    |

# CHAPTER I

#### INTRODUCTION

## 1.1 INTRODUCTION to IoT

The term IoT refers to the Internet of Things which is a term used to describe the advent of the innumerous wireless systems that are connected to the internet. The Internet of Things has a bright future and will be ubiquitous in the near future [6]. The growth of the internet of things is revolutionary and the number of devices connected to the internet grew to 12.5 Billion in the year of 2010 while the world population at that time was about 6.8 Billion, which implies that the number of connected devices per person was more than  $1(\approx 2)$  at the time. In the future it is predicted that the number of devices connected to the internet should approach 50 Billion in the year 2020 while the population would be approximately 7.6 Billion[7]. This trend suggests that these IoT devices are going to not only outnumber the number of human beings but will be commonplace. One such example is the Apple watch which has instant internet connection on the go, other applications of such devices include[8]:

- Medical- monitoring, safety and quality control

- Personal wearables with real time medical assistance

- Industrial Robots and automation

- Supply Chain-Real time data analysis

- Infrastructure integrity monitoring systems-road and railway transportation

- Homes-Cameras, HVAC, lighting and security.

With so many devices simultaneously accessing the internet there is going to be a crunch in the spectrum available for these devices to communicate hence the communication would need some sort of data distribution network. With greater data rates and an with increase in distances of transmitted data the expenditure of power is going to be extremely high.

In designing IoT devices there is a great emphasis of low power consumption. Lower power consumption extends the battery life of these devices and their usable lifetime increases. These IoT devices have to function satisfactorily in extremes of temperature and environment conditions, as the temperature of the environment increases the semiconductor chips in these devices heat up leading to addition power loss. For the commercial IoT market, the devices have to be designed in order to function efficiently for a temperature range of 0°C to 90°C whereas wireless microsystems that find applications in the military or the automotive industry need to perform satisfactorily for a temperature range of -40°C to 150°C.

### **1.2 INTRODUCTION TO RFIDs**

The numerous IoT devices on the market includes the Radio Frequency Identification (RFID) tag. RFIDs find widespread applications such as object tracking, identification, inventory, data loggin, and supply chain management and data acquisition. RFIDs first found their bearings in the 1970s and since then have evolved to a great extent [9].

These RFID devices are classified into two categories

- Active RFID

- Passive RFID

Active RFID consist of on-chip integrated power source (battery). The luxury of an internal battery improves performance significantly. The drawback of having an internal battery is that these devices have a limited life time, cost more and are less bio compatible. The on-chip battery ensures that there is an abundance of power that can be utilized by the tag for its functioning. Due to the abundance of battery power the communication range for active RFIDs is >100m.

Just the opposite is true of their active counterpart, passive RFIDs have no internal battery and must harvest the power from an input RF signal, solar, acoustic or thermal source for the entire time that they are operational. This stipulation of not having an on-chip battery means that there is a scarcity of available power which the tag can utilize for not only function, i.e. data acquisition and/or storage but also for communicating. Passive RFIDs are smaller in size, have a greater life span and are safer for bio-implantation, and generally lower cost which tips the scales in its favor. However, passive RFIDs are generally limited to near field communication and may extend to a few meters. The drawbacks of using passive RFIDs is that there is greater emphasis on low power consumption, and near field operation. Hence each block in the circuit architecture must be optimized for low power consumption. This is often challenging. This work is limited to passive RFIDs and throughout this effort there will an emphasis on low power design techniques.

#### 1.3 Ultra-Low Power Requirement Dictates Weak Inversion

The complete block diagram of a passive RFID is shown in Figure 1.1

Figure 1.1 Complete Block Diagram of a "smart" RFID tag

As we can see there are many active blocks that may consume large amounts of power such as the Amplifier, Analog to Digital Converter, Voltage Reference, Demodulator, Phase Locked Loop, Low Dropout Regulator, etc. The greatest power offenders include the Low Dropout Regulators, Demodulator, Voltage Reference circuits, Analog-to-Digital converter and the amplifier. It is therefore imperative that each of these blocks are designed in such a manner that their overall power consumption is as efficient as possible. Such low power operation can be achieved by choice of circuit architectures and region of operation (weak inversion). Weak inversion operation benefits us by affording us greater bandwidth per watt compared to strong inversion. The time constraints on the RFID operation is relaxed as the bandwidth requirement of the physical world enables us to opt for weak inversion operation.

The concept of weak inversion and its low power capability is elaborated in Chapter 2. The average input power to an RFID is dependent on the modulation scheme used, for most passive RFIDs the most prevalent modulation scheme is the Pulse interval encoding scheme.

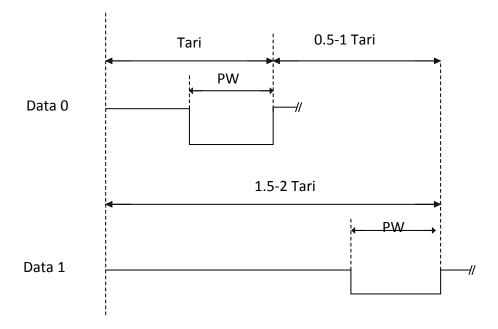

### 1.4 Pulse Interval Encoding

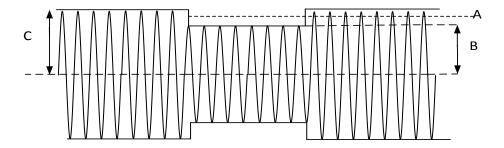

The protocol widely used for passive RFID tags that incorporate backscatter is EPC GEN 2, which is the protocol that was standardized by EPCglobal for passive RFIDs. All passive RFID devices that incorporate the EPC Gen 2 have to conform to a minimum set of rules or minimum standards. A detailed list of these requirements can be found in [10]. Pulse interval encoding is the encoding scheme preferred while communicating from the interrogator to a passive RFID tag in the EPC class-1 generation-2 UHF RFID protocol[10]. This is attributed to the fact the pulse interval encoding scheme maximizes the amount of power flow to the tag while communicating both binary 1's and 0's. The scheme is characterized by a long full power pulse for the binary 1 with a short power off pulse terminating it whereas the binary 0 starts with a short full power pulse and is terminated by the same short power off pulse[11]. The PIE baseband waveform is shown in Figure 1.2. The term Tari is an abbreviation of Type A Reference Interval. It is a unit of time duration that ranges from 6.35µs to 25µs and results in a communication bandwidth requirement approaching 1.5 MHz. The time duration for which the binary 1 and 0 experience a power off pulse is between 0.265 Tari and 0.525 Tari [4].

Figure 1.2. Baseband waveform of Pulse Interval Encoding[11]

One of the drawbacks of the scheme is that the data rate is data-dependent since the duration for binary 0 is shorter than the duration for a binary 1. The worst case in terms of power flow to the tag would be a series of binary 0s whereas the worst case data rate would be caused by a series of binary 1s. A series of 1s requires the greater bandwidth. To increase the average power to the RFID one possible solution is to reduce the modulation index of the incoming signal in order to increase the power levels for the binary 0s, this reduced modulation index imposes tighter specifications on the demodulator design which we would explore in detail in Chapter 4. Although the power at the input is increased, it is up to the matching and harvester circuits to make that input power available to the other parts of the RFID, we explore these circuits in the following sections.

#### 1.5 Matching Network and Harvester Circuits

The front end circuit of the RFID is shown in Figure 1.2.

ANTENNA

Figure 1.3 Front End Circuit of the RFID.

#### 1.5.1 Matching Network

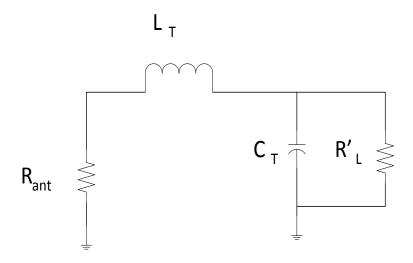

In order to maximizing harvesting of the power in the input RF signal we need to match the source impedance of the antenna to the input of the RFID in order to have maximum power transfer to the input of the harvester. Series matching is selected since it provides us with a voltage boost equal to the Q of the network [12]. This means that the incoming waveform voltage is multiplied by the Q of the matching circuit and the input to the harvester is now  $V_{IN,HAR} = Q * V_{IN}$ . The choice of series matching topologies is limited to the T,  $\pi$  and the L match networks to minimize complexity. The L match is the preferred choice since it offers greater efficiency compared to the T and the  $\pi$  [13] while presenting a voltage boost. The equivalent circuit for the matching network is shown in Figure 1.4.

Figure 1.4 L match network

We need to match the  $R_{ant}$  in series with the inductor impedance  $X_L$  to the parallel impedance of  $R'_L$  and  $X_C$ .

$$R_{ant} + jX_L = \frac{1}{\frac{1}{R'_L} + \frac{1}{jX_C}}$$

$$Q_s = \frac{X_L}{R_{ant}} = \frac{{R'_L}^2 X_C}{{R'_L} X_C^2} = \frac{{R'_L}}{X_C} = Q_p = Q$$

$Q_{s}$  is the quality factor of the inductor  $L_{T}$  whereas  $Q_{p}$  is the quality factor of the capacitor  $C_{T}$

Solving Further

$$Q = \sqrt{\frac{R'_L}{R_{ant}} - 1} \approx \sqrt{\frac{R'_L}{R_{ant}}} \approx \sqrt{\frac{R_L}{R_{ant}}} = \sqrt{\frac{V_{Har}/I_{DC}}{R_{ant}}}$$

A higher Q is advantageous to the RFID operation yet the communication bandwidth limits the maximum applicable Q [12]. The values for  $V_{Har}$  and  $I_{DC}$  are known, as a result the  $R_{ant}$  value is adjusted in order to match the antenna to the load. For the EPC GEN 2 standard the

communication Q around 0.9 to 2.5 GHz approaches 30 to 80. This is effectively reduced to  $(25\rightarrow 66)$  by the process variation of +/- 20% in the tuning capacitance,  $C'_T$

Resonant frequency is given by:

$$f_0 = \frac{1}{2\pi\sqrt{L_T C'_T}}$$

The choice of the load capacitor value is application dependent. The matching network design is not part of this effort hence we do not discuss it any further though a good reference can be found in [12]. As a result acceptable Qs may range between  $6\rightarrow 25$  at 900 MHz.

1.5.2 Harvester Circuit

The incoming RF wave has to be converted to DC power in order to power the entire RFID, for which there is a need for a rectifier. The overall power efficiency of the harvester circuit is critical as it directly impacts the performance of the entire RFID.

Harvester Working:

A more general/simplifed depiction of the harvester is shown in Fig 1.6.

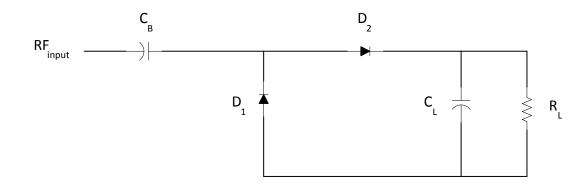

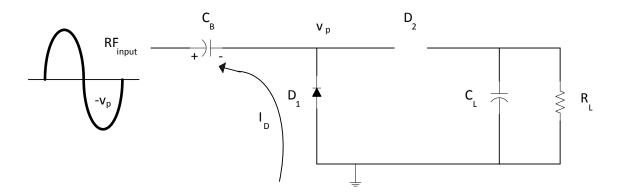

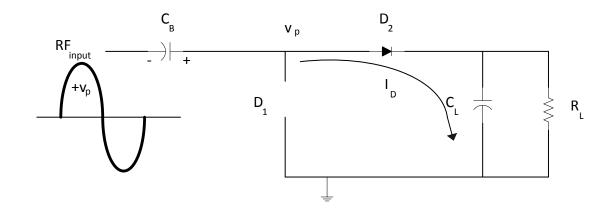

Fig 1.5 Basic Harvester Circuit

In the negative half cycle of the input waveform the diode  $D_1$  becomes forward biased and conducts current which charges the capacitor  $C_B$  to  $V_{peak}$  (peak voltage value of the RF waveform), during this time the diode  $D_2$  remains in the reverse biased mode and is off. This phenomenon is shown in Figure 1.6

Figure 1.6 Negative half cycle of the input at the Harvester

On the positive half cycle of the input the reverse takes place where the diode  $D_2$  is on and the diode  $D_1$  shuts off. Diode  $D_2$  would charge the load capacitor  $C_L$  to  $2V_{peak}$ , as the initial voltage at the capacitor was already  $V_{peak}$  at the moment the input waveform turned positive, it is added to the  $V_{peak}$  value of the incoming input to charge up to  $2V_{peak}$ . This occurrence is presented in Figure 1.7

Figure 1.7 Positive half cycle of the input at the Harvester

The voltage output for N stage harvester circuit is given by

$$V_0 = 2N(V_P - V_d)$$

Where  $V_d$  is the total voltage drop due to the diode losses, LDO losses and parasitic losses at the carrier frequency and  $V_P$  is the peak amplitude of the incoming signal.

The design of the harvester circuit is not undertaken in this effort, complete design and optimization of the harvester can be found in [14], LDO loss numbers can be found at [15]. The output voltage of the harvester is assumed to be at 1V with a DC or average load current of 50µA hence the load resistor at the output of the harvester is given by

$$R_L = \frac{V_0}{I_L} = 20K\Omega$$

As seen in Figure 1.1 and 1.2 the demodulator and the harvester share the same input node which is the output node of the matching network, this implies that we need to ensure that the demodulator does not load the harvester output causing the output harvester voltage to reduce. A reduction in the harvester output voltage reduces the harvester power efficiency. It is important that the impedance looking into the demodulator is greater than approximately 20\*R<sub>L</sub> such that the demodulator has little or no effect on the performance of the harvester. Alternately stated dissipates insignificant power. This constraint has a direct impact on the design of the ASK demodulator effort presented in Chapter 4.

#### 1.6 Research Objective

Demodulation is a process in which the digital baseband data is extracted from a modulated analog waveform which is at a higher frequency called the carrier frequency[11]. The demodulator is a vital cog in the circuit architecture of the RFID as it is responsible for faithfully reproducing the input signal RFID commands which control the RFID state machine. The modulated input contains the clock embedded within it, and the demodulator has the task of decoding the data stream bit s(0 or 1) and in turn providing the embedded reference clock to the PLL. This effort is aimed at designing a power efficient low modulation index Amplitude Shift Keying (ASK) demodulator for RFID applications for a temperature range of -25°C to 125°C making use of a voltage supply of 700mV. For the design, the IBM CMOS7RF 0.18µm process is used and simulations are carried out using Cadence Virtuoso. Design objectives are presented and all design trade-offs and challenges are stated, steps to overcome them are demonstrated and an analytical approach to designing and optimizing the RFID Demodulator is presented. Throughout this effort there is emphasis on the operation of the MOS transistor in subthreshold region and the effects of change in temperature and process on transistor operation. The primary aim of this effort is to design a robust ASK demodulator for extreme of temperature conditions consuming minimum power. The designed ASK demodulator is compared with similar works by using a Figure of Merit[5].

#### 1.7 Thesis Organization

In Chapter 1 the motivation for low power consumption was established, the circuits interacting with the ASK Demodulator were summarized along with their implications on the ASK demodulator design and finally the research objective of this effort was put forth.

Chapter 2 introduces subthreshold/weak inversion design and the effect of process and temperature variation on MOS operation. The chapter then goes on to describe supply voltage variation and concludes by establishing PVT (process, temperature and supply) corners for MOS transistors in weak and strong inversion regions of operation.

Chapter 3 will look at ASK demodulators for RFID applications implemented in the past and make a comparison table which would be used in Chapter 6 to put together a Figure of Merit.

Chapter 4 introduces the designed RFID demodulator and its working and goes on to establish a design objective and discusses the steps taken to achieve such an objective.

Chapter 5 will consist of the circuit simulations results and the DC Monte Carlo simulation results along with the transient working results of the circuit.

Chapter 6 will first look at possible parameters that should be considered towards establishing a Figure of Merit and will go on to establish such a Figure of Merit [5]. Concluding this effort the chapter will look at the Future Scope in an effort to identify best opportunities for improving efficient power usage on a block by block bases.

#### CHAPTER II

#### MOS TRANSISTOR CHARACTERISTICS AND VARIABILITY

This chapter is divided into three sections, the first section would introduce subthreshold operation of the MOS Transistor, and second section would explain in detail the origins of process variation and their consequences and the third section would explore temperature effects in subthreshold and velocity saturation on MOS operation.

#### 2.1 Subthreshold/Near Threshold Designing

In our discussion of the MOS transistor we are going to be utilizing elements of both the EKV model and the BSIM3v3 model to understand the working of the transistor in various regions of operation. Conduction of current in MOS transistor takes places in two ways, one is through drift and the other through diffusion of charge carriers, the drift currents are dominant in the strong inversion regime while the diffusion current is associated with the weak inversion regime [16]. There are many models used to characterize the behavior of the MOS transistor such as the BSIM3[16] model which is a surface potential based model whereas the EKV model is a charge based models. In our discussion about subthreshold operation we are going to use the EKV model to illustrate subthreshold operation. The MOS transistor operation has three modes of operation when the channel is inverted i.e. weak, moderate and strong inversion operation.

The EKV model is a body referenced model which is useful in order to model the MOS transistor operation in weak inversion [16]. These modes of operation are classified based on the inversion coefficient which is defined by [17] as

$$IC = \max\left(i_f = \frac{I_F}{I_{spec}}, i_r = \frac{I_R}{I_{spec}}\right)$$

$I_F$  is the forward current in the channel,  $I_R$  is the reverse current and  $I_{spec}$  is the specific current which is given by  $I_{spec} = 2n \,\mu C_{ox} \frac{W}{L} \, U_T^2$  the current used to normalize  $I_F$  and  $I_R$  at the current level at which  $I_F$  or  $I_R$  changes from weak to strong inversion[17]

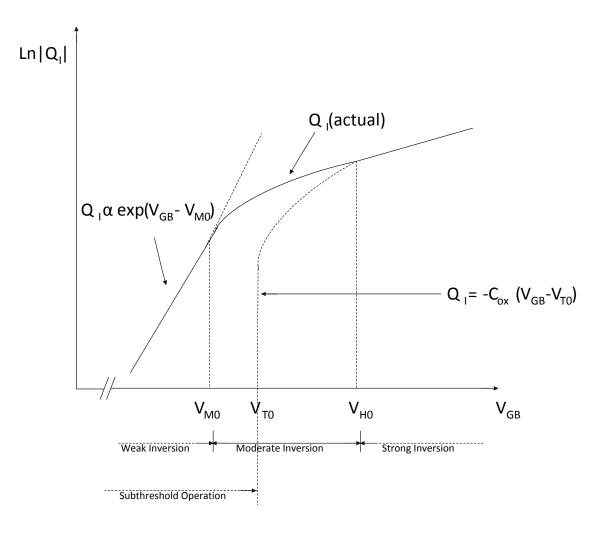

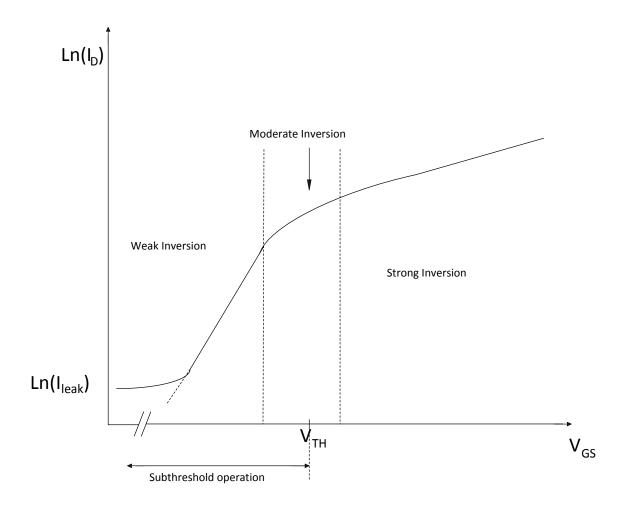

Weak inversion takes place for IC<<1, moderate for IC $\cong 1$  and strong inversion for IC>>1. Fig 2.1 shows the plot of log of the inversion charge vs the gate-to-body voltage in a two terminal MOS structure which establishes the notion of the threshold voltage[16]. Where  $V_{M0}$  is the extrapolated voltage that represents the onset of moderate inversion and V<sub>H0</sub> the onset of strong inversion. V<sub>GB</sub> is the gate-to-body voltage in a two terminal structure and Q<sub>I</sub> is the inversion layer charge. The extrapolated threshold voltage  $V_{T0}$  (ignoring the body effect) is the voltage for which the MOS transistor is said to turn on based on the strong inversion model. Moderate inversion is not well modelled as both weak and strong inversion model fail as the current flowing through the transistor in moderate inversion constitutes both drift and diffusion currents. In a four terminal MOS device subthreshold operation is considered to take place when the gate-to-source bias on a MOSFET is lower than the extrapolated threshold voltage of that MOSFET. This means that any MOS transistor biased below its threshold voltage is said to operate in the subthreshold regime. In terms of regions of inversion subthreshold operation spans weak inversion and part of the moderate inversion regime of operation. A much simpler depiction is presented in Fig 2.2 which plots the ln of the drain current v/s the gate-to-source voltage of a MOS transistor for a source referenced model.

Fig 2.1. Log of inversion layer charge vs the gate-to-body voltage for a two terminal MOS

device[16]

Fig 2.2  $\ln(I_D)$  vs  $V_{GS}$  plot

The following sections will evaluate performance in the subthreshold regime by stating the advantages, disadvantages and limits of designing circuits in the subthreshold region.

The drain current equation in weak inversion is given by[17] as

$$I_D = I_S e^{\frac{V_G - V_{T_0}}{nU_T}} \left( e^{\frac{-V_S}{U_T}} - e^{\frac{-V_D}{U_T}} \right)$$

And can be approximated [11]as

$$I_D = I_{D0} e^{\frac{V_{GS} - V_T}{nU_T}} \left( 1 - e^{\frac{-V_{DS}}{U_T}} \right)$$

#### 2.1.1 Advantage of Operating in Subthreshold Region

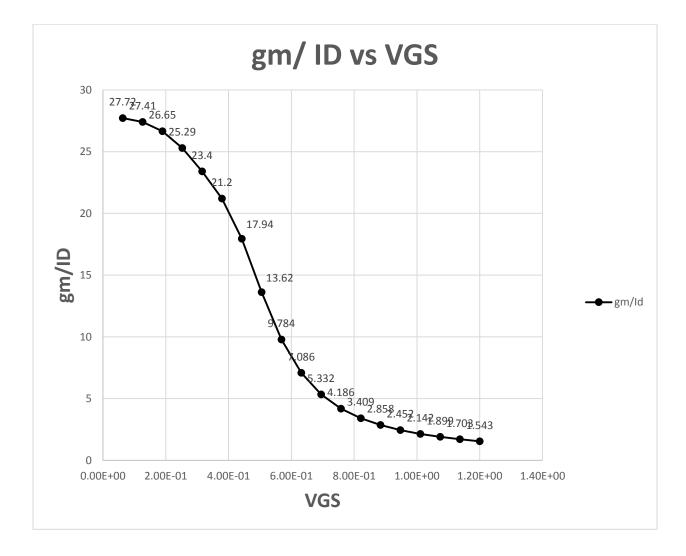

High gm/ID efficiency: When the MOS transistor operates in the subthreshold region the  $g_m/I_D$ is higher than that for above threshold operation where the  $g_m/I_D$  saturates for high gate-tosource voltages. The gm/ID efficiency for a single finger minimum geometry diode connected NMOS device is shown in Fig 2.3. As seen in Fig 2.3 the gm/ID efficiency reduces as the gate-tosource voltage is increased above threshold. The threshold voltage of transistor is at 426mV at 27°C. Around the threshold voltage the gm/Id efficiency is about 18 while it reduces to 9 at 100mV above threshold and to 5 at 200mV above threshold. A higher gm/Id efficiency translates to a higher achievable gain for a lower drain current. The power consumed by an analog circuit is given by*Power* =  $V_{DD} * I_D$ , hence a lower drain current implies the power consumption would be lesser compared to above threshold design for the same gain.

Low Power Consumption: Considering digital circuits it is beneficial to operate circuits in the subthreshold or near subthreshold region for low power consumption while providing the required bandwidth. The latest technologies have ample bandwidth at their disposal and to incorporate subthreshold designs in order to reduce power consumption. This concept is explained through the equation for total power consumption.

The total power consumption is given by

$P_{Total} = P_{static} + P_{static}$

$P_{Total} = V_{DD} * I_{leak} + C * V_{DD}^2 * f$

$P_{Total} \alpha I_{leak} + C * V_{DD} * f$

Where f is the operating frequency and C is the capacitance that is charged or discharged. The term I<sub>leak</sub> is the current flowing through the device when the device is said to be off. If we were to operate in subthreshold the contribution to the total power would be dominated by the static power which is a linear function of the supply voltage whereas the dynamic power is a quadratic function of the supply voltage, hence dynamic power makes a negligibly contribute to the overall power. Subthreshold design consumes low power for the required bandwidth, hence most passive RFIDs these days operate in the subthreshold region as the bandwidth achievable in weak inversion is feasible.

Figure 2.3.  $\frac{gm}{I_D}$  vs V<sub>GS</sub> plot

### 2.1.2 Drawbacks of Operating in Subthreshold Region

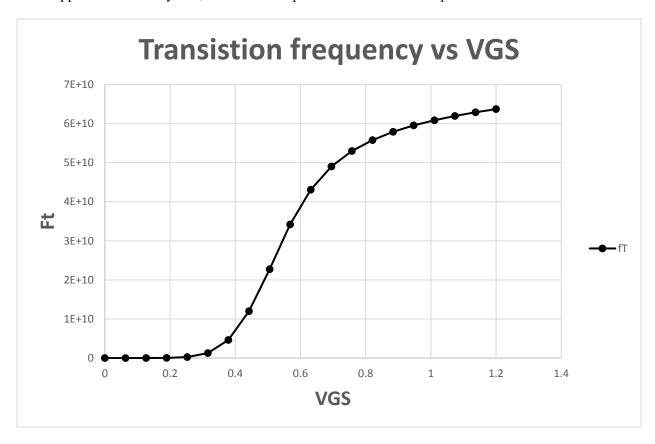

Low Bandwidth: Subthreshold operation is helpful in reducing the power consumption but the frequency of operation is drastically reduced compared to operating above threshold. The bandwidth achievable in the weak inversion regime is lower than that achievable in strong inversion as seen in Figure 2.4, although we are able to achieve a high gm/ID efficiency the magnitude of currents produced are fairly low causing the bandwidth of operation to be low. The transition frequency vs gate-to-source voltage for a minimum geometry diode connected NMOS is shown in Fig 2.4. The transition frequency rises rather abruptly as the gate-to-source voltage is increased beyond the threshold voltage. Since the bandwidth of operation required for passive RFID applications is fairly low, subthreshold operation is still a viable option.

High Variability: The variability associated with the current is high due to the fact that the current is an exponential function of the threshold voltage in weak inversion. The threshold voltage of the device is highly variable and will be discussed in Section 2.2 in detail.

### 2.1.3 Subthreshold Operating Limits

When dealing with subthreshold design it is important to ensure that the  $I_{ON}/I_{OFF}$  ratio is high. This condition ensures that the active drain current used for circuit operation is much greater than the off state leakage current flowing through the device. If the off-state current is comparable to the on-state current, it could lead to a loss of state in a digital circuit and the circuit would not function as required. Also when operating in deep subthreshold ( $V_{GS} \ll V_{TH}$ ) it is important to understand that as the gate-to-source voltage tends towards zero the model predicts that the drain current would also tend to zero yet the data provided by the IBM CMOS RF 7 0.18µm process shows that the leakage or off-state current is comparable to the drain current as shown in Fig 2.2. For the IBM 0.18µm process used for this effort the models incorporated in the simulator are BSIM3v3 or PSP intrinsic models. A designer needs to thoroughly understand the process and how it models the behavior of the MOS transistor in order to successfully predict and optimize any design effort.

#### 2.2 PROCESS VARIATION

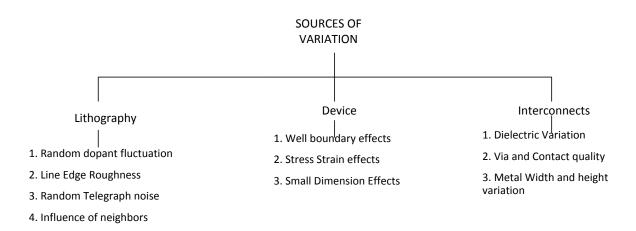

Every semiconductor chip applicaton (die) has specifications to achieve across extremes of temperature and environment conditions. Having said that a chip may be deemed a bad die if it is unable to meet the required specifications and the die may be destroyed or discarded. The semiconductor fabrication process is less than perfect, hence there is a standard deviation of the electrical parameters from their desired designed values. There are various sources of parametric variation associated with all semiconductor processes in general. These common sources of

21

variation are listed in Fig 2.5. The most important electric parameter of transistor in terms of variation is its threshold voltage, in this Sec we focus on transistor threshold variation caused by the process.

Fig 2.5. Sources of Variation[18]

### 2.2.1 Random Dopant Fluctuations

To get more performance out of transistors the industry has relentlessly followed Moore's Law by shrinking device dimensions every few years. The scaling of the device length and width causes a drastic reduction in the number of dopant atoms in the depletion region. For example considering W,L = 100nm for a device, the doping concentration is  $N_A = 10^{18} cm^{-3}$  whereas the depletion width is 35nm, the number of acceptor atoms is given by  $N = N_A * L * W_{Dom} = 350$  atoms [19]. At 32nm the number of dopant atoms is approximately 36. The extrapolated voltage expression for a two terminal device is given by[16].

$$V_{T0} = \phi_{ms} - \frac{Q_0}{C_{ox}} + \phi_0 + \frac{\sqrt{2q\epsilon_s N_A \phi_0}}{C_{ox}}$$

Where the gate to substrate work function is  $\phi_{ms}$ ,  $Q_0$  is the interface charge between the oxide and channel, q is the electron charge and  $\phi_0$  is the surface potential. The number of dopants vary from device to device and their standard deviation follows a Poisson's distribution due to its discrete statistical nature[19, 20]. Therefore the threshold voltage standard deviation due to random dopant fluctuations is given by[18] as

$$\sigma_{\Delta V th} = \left(\sqrt[4]{2q^3 \epsilon_{si} N_A \phi_0}\right) * \left(\frac{t_{ox}}{\varepsilon_{ox}}\right) * \frac{1}{\sqrt{3WL}} \cong \frac{A_{VT}}{\sqrt{WL}}$$

The threshold voltage is a continuous function and its standard deviation is modelled using a Normal distribution. The term  $A_{VT}$  is a constant referred to as the Pelgroms coefficient for the threshold voltage and is process technology dependent[21].

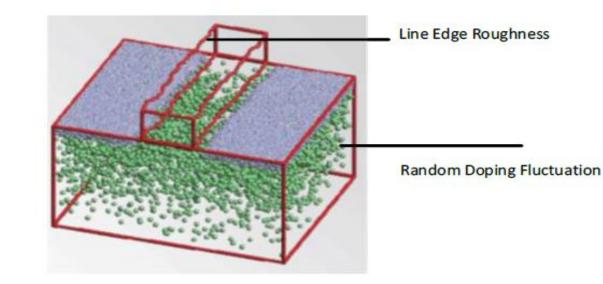

A small variation in this number can have substantial variation of electrical characteristics between devices which would ultimately lead to errors. Fig 2.6 shows the simulated RDF,LER by [19].

Fig 2.6. Atomistic simulation demonstrating RDF and LEF [18, 19]

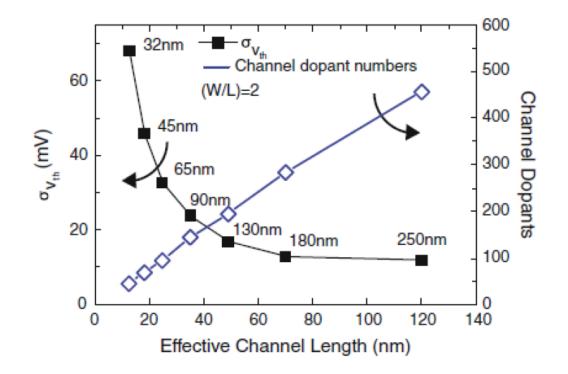

The green spheres depict the dopant atoms. The effect of RDF on threshold voltage with change in device length is illustrated in Fig 2.7.

Fig 2.7. Impact of Random Dopant Fluctuation on  $\sigma_{VTH}$  with change in channel length [18, 19,

21-23]

#### 2.2.2 Line Edge Roughness

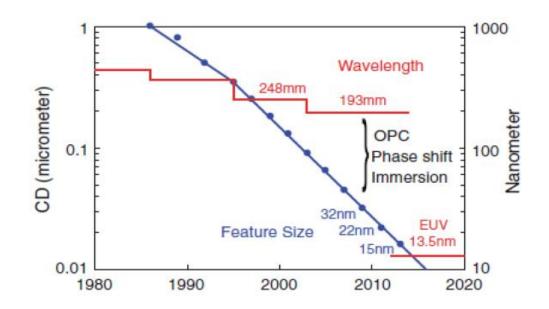

Line edge roughness is caused due to improper patterning of the device dimensions such as the gate length. As the physical dimensions of the transistors is shrinking with every new process node the lithography wavelength has decreased from 500nm to 193nm for gate patterning. Optical lithography and enhancement techniques are used for process nodes 180nm and lower, these techniques employ aperture improvement using OPE (Optical Proximity effects) and immersion technology [18, 19, 24-26]. The optical proximity effects are major contributors to variation

which dictate the smallest feature size fabricated in a node generation. For process nodes below 50nm the LER is a significant contributor to the overall threshold variation [18, 19, 24-26]. Fig 2.8 shows the lithography wavelength for different process nodes.

Fig 2.8. Lithography Wavelength for different process nodes[26]

#### 2.2.3 Random Telegraph Noise (RTN)

Telegraph noise or flicker noise is not very well modelled, this noise or inaccuracy originates due to the scattering of the charge carriers in the channel. Since both the lateral and longitudinal fields effect the direction of carrier path, sometimes the carriers are trapped into the oxide region and accumulate there which reduces the overall channel charge effecting a higher threshold voltage. Once the amount of charge trapped in the oxide is extremely high, charge breaks free from the trap and all the previously trapped carriers are released leading to an increase in the surface potential causing a reduction in threshold voltage. This fluctuation of threshold voltage causes many errors in the circuit and is modelled as a discrete statistical model. The impact of telegraphic or 1/f noise on the threshold voltage is given by [18, 27, 28]

$$\Delta V_{TH,1/f} = \frac{q}{W_{eff} * L_{eff} * C_{ox}}$$

RTN possesses a Gaussian long tail behavior which has critical implications beyond  $\pm 3\sigma$  [19].

#### 2.2.4 Influence of neighbors

Since Optical lithography is the primary method of lithography employed in the semiconductor industry there are many effects that are undesirable such as influence of the neighbors. In a die there may be many circuits designed that have their layouts in close proximity, the optical profile of one circuit can have an impact on the other adjacent circuit. Any variation in the lithography on one circuit can prove to be detrimental to the entire die. For this reason circuit layouts are isolated by either adequately spacing them apart or employing dummy circuits that are sacrificed in order to protect the circuits of requiring more significance[29] accuracy.

#### 2.2.5 Small Dimension Effects

As we have seen the random doping is the prominent cause of variability when the dimensions of the width and the length of the transistors are small, there are other second order effects associated with the device dimensions that are process dependent and their effects vary from one process node to another. These effects include the Narrow Width, Inverse Narrow Width, Short Channel and Reverse Short Channel Effects.

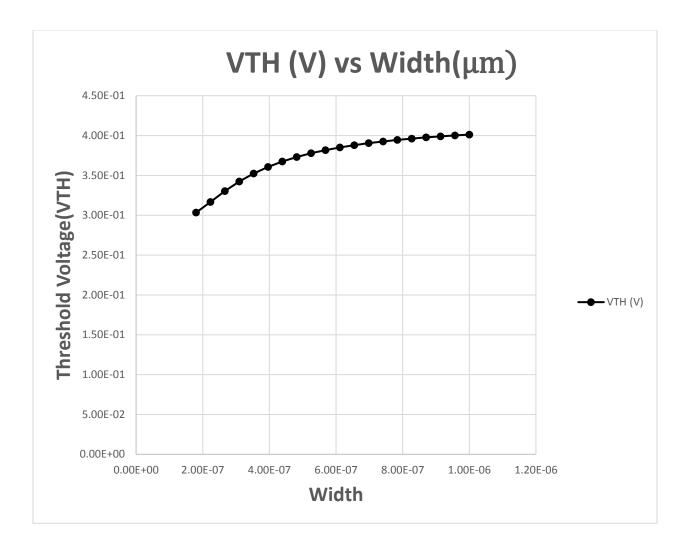

• Narrow Width and Inverse Narrow Width Effect.

Modern CMOS sub-micron(below  $0.25\mu$ m) processes often encounter the issues associated with the Narrow Width and the Inverse Narrow Width effects which are connected to the change of width of the device. When the width of the device has the same order of magnitude as the depletion depth, that device is said to have a narrow width [30]. The Narrow Width Effect causes an increase in  $V_{TH}$  with a decrease in the width. This phenomenon is encountered often in processes that use non and semi recessed isolation such as the Local oxidization of silicon (LOCOS) CMOS process [30]. The LOCOS process was widely used for the processes having channel lengths of  $0.25\mu$ m and greater [16]. For channel lengths  $0.18\mu$ m and lower the processes usually use a Shallow-Trench Isolation (STI) which employs fully recessed isolation. The devices fabricated using the STI process encounter the Inverse Narrow Width effect wherein the  $V_{TH}$ decreases with the decrease in the channel width [31]. The IBM  $0.18\mu$ m CMOS 7RF process is a CMOS STI process and encounters the Inverse Narrow Width effect[32]. To illustrate the same a plot of threshold voltage of a 1µm long NMOS transistor in the diode connected configuration vs change in width is shown in Fig 2.9.

Fig 2.9. Threshold voltage vs Width of a  $1\mu m$  long NMOS diode connected transistor

$$(V_{GS} = V_{DS} = 700 \text{mV})$$

The root cause of the inverse narrow width effect is the fringing fields originating at the gate and terminating at the sides of the channel. For a larger width these fringing fields are a small percentage of the total fields but at narrow widths these vertical fields deplete the region below the thin oxide increasing the surface potential. This increase in surface potential lowers the  $V_{GS}$  required for the onset of inversion which implies a reduction in the threshold voltage of the device [16]. These same fringing fields cause the narrow width effect in LOCOS processes, the fringe fields in LOCOS processes get wasted on the sides of the channel due to which the channel itself experiences a smaller field leading to an increase in threshold for narrow devices. In order

to negate the Narrow and Inverse Width Effects the unit width of a transistor should be kept higher than minimum geometry width (about 500nm at 180nm) and any increase in width should be realized through increasing the number of fingers, i.e. select a unit finger width of 260 to 300nm.

• Short Channel Effects and Reverse Short Channel Effects

Short channel effects are observed in processes where halo implants are absent (halo is a demarcation indicated for implant regions[16]), the resultant  $V_{TH}$  is decreased as the channel length is decreased. This is caused due to the S/D junction horizontal field penetrating into the channel and depletes the Si under the gate, hence a lesser gate-to-source voltage is required to achieve inversion effecting a reduction in the  $V_{TH}$  [32]. For processes that employ halo implants the scenario is just the opposite this is because the S/D halo regions are so close for short channel lengths that they overlap which increases the average channel length [32]. The IBM CMOS7RF 0.18µm incorporates halo implants and follows the reverse short channel effect which can be seen in Fig 2.10 which plots the threshold voltage vs channel length for a 1µm wide NMOS device[32].

Fig 2.10 Threshold voltage vs Length of a 1µm wide NMOS diode connected transistor

$(V_{GS} = V_{DS} = 700 \text{mV})$

When considering non-fingered devices, the PMOS device experiences a lower impact from the INWE and RSCE compared to the NMOS [32]. Also the mobility of the PMOS is lower compared to the NMOS, in an attempt to match their mobility through change in transistor widths we can make use of both INWE and RSCE to our advantage.

• Drain Induced Barrier Lowering or DIBL

As the drain voltage across a transistor is increased there is a phenomenon called drain induced barrier lowering which causes a decrease in threshold voltage. The drain induced barrier lowering or DIBL effect causes the current to increase and the channel inversion increases. This effect is observed mainly in short channel devices when the drain and source are in close proximity due to which their depletion regions approach each other, there is a two-dimensional field on the carriers in the channel. Since there is a field from the source towards the drain and vice-versa the surface potential increases causing the carriers in the channel to move towards the drain for a lower gate-to-source voltage[16]. This phenomenon is extremely important when dealing with transistors operating in weak inversion since a reduction in threshold can causes an increase in inversion charge leading to moderate or strong inversion operation.

As all the sources effecting threshold voltage are uncorrelated, The total threshold voltage standard deviation is expressed by[19]

$$\sigma_{VTH} = \sqrt{\sigma^2_{VTH,RDF} + \sigma^2_{VTH,LER} + \sigma^2_{VTH,other}}$$

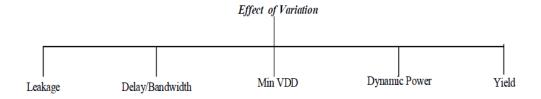

2.2.6 Effects of Process Variation

The effects of process variation are summarized in Fig 2.11.

Fig 2.11. The effects of Variation[18]

Variation primarily effects Bandwidth, Dynamic Power, Leakage, Minimum supply voltage and the overall yield.

• Delay/Bandwidth: The current through a device can be represented as

$$I = C * \frac{dV}{dt} \cong C * \frac{\Delta V}{\Delta t}; \ \Delta t = \frac{C}{I} * \Delta V$$

Where C is the parasitic capacitance and  $\Delta t$  is the time delay for the current to charge the capacitance C to  $\Delta V$  voltage. As the current is dependent on the threshold voltage, any variation in threshold voltage causes variations in delay time which severely impacts performance.

- As stated in Sec 2.1.1 the total power dissipation is dependent on the leakage current and since the leakage current is a weak inversion current, variation in threshold brings about an exponential change in the leakage current which is one of the reasons weak inversion is characterized by high variability. This added leakage current can be detrimental in terms of power consumption when leakage from all devices is accounted for in a circuit.

- The minimum supply voltage for a stack of transistors will be decided primarily by the threshold voltages of the devices, for cold temperatures the threshold voltage of a device will increase which will put a limitation on the minimum supply voltage, this phenomenon of threshold change with temperature will be explored in Sec 2.3. This limitation on the supply voltage also effects the dynamic power dissipation as it is directly proportional to the square of the supply voltage.

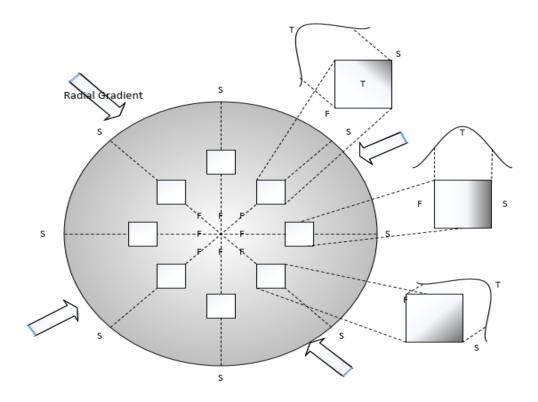

#### 2.2.7 Global Variation (Systematic/Process Variation)

The silicon wafer is circular in shape and many dies are placed on a single wafer, these dies are rectangular in shape. Misalignment in lenses and irregular lithography conditions causes die parameters to vary in dies that are placed closer to the circumference of the wafer compared to the center. The fabrication accuracy is high at the center of the wafer and all the dies in the center are efficient and faster compared to the remaining dies on the wafer. As die location moves towards the circumference of the wafer the dies are poorer in performance (higher threshold), this is attributed to the fact that the wafer is circular whereas the dies are rectangular in shape hence the dies close to the circumference do not experience the same process environment as at the center of the die. This variation of performance from the center of the die to its circumference is

modelled as a random probability function that has a spatial correlation and is referred to as process gradient or process variation. This radial variation is illustrated in Fig 2.12, as seen the center of the wafer is marked F which denotes that the performance of the dies in this region is faster (or superior) than the dies placed away from the center. The intermediate dies which are between the center and the circumference are marked T which denotes that they have a typical value which is the targeted performance and the dies close to the circumference are S which denote that these dies are slow and have poorer performance than desired. The process gradient affecting a single die is diagonal, left to right, bottom to top and vice versa. The process variation cannot be countered by any design techniques however the foundry provides test results that guide the designer to predict the process variation.

Fig 2.12. Radial gradient on wafer[18]

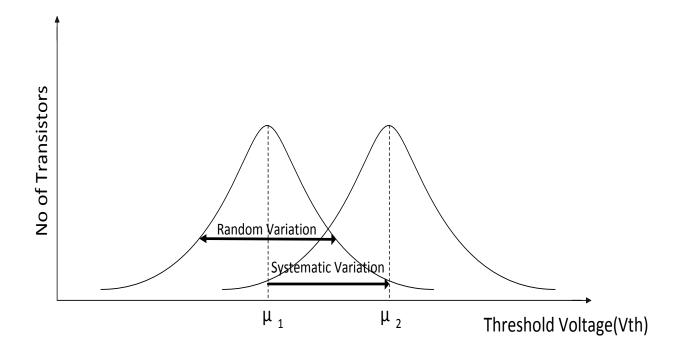

#### 2.2.8 Local Variation

Apart from Global variation that plagues the wafer as a whole, semiconductor die are also affected by local variation that is variation in electric and chemical parameters within a limited or contained area within a die. This variation is caused due to the non-uniform doping illustrated in Sec 2.2.1, this variation is found between devices that are in close proximity to each other which is most commonly referred to as mismatch. Since the doping levels are random, one device may be doped with fewer or greater dopants than a device adjacent to it. This type of variation is detrimental to circuits which require uniform performance for devices that are kept close to one another such as differential amplifiers, current mirrors, comparators, etc. Within a fixed area the local mismatch is dominant over the global mismatch, this area is about 200µm X 200µm for the IBM CMOS 7 RF process[33]. The distribution of threshold voltage of a device due to local variation has a random distribution while its mean value varies with its position on the wafer (gradient), this phenomenon is illustrated in Fig 2.13. In a case where the size of a die is smaller than 200µm X 200µm, the parameter variations between dies will follow the local variation and this kind of variation is commonly referred to as Die-to-die variation. The RDF from Sec 2.2.1 causes a variation in the threshold voltage leading to DC voltage errors in the circuit, this type of error is commonly referred to as DC offset or offset. The offset is of great importance to this design effort since it limits the Signal to Noise ratio and dictates the transistor sizing and power consumption in order to achieve accuracy as well as robustness. Considering a minimum geometry NMOS device (220nm/180nm) and making use of the data indicated as  $\pm 3\sigma$  provided by the semiconductor fabrication vendor we have

$$V_{osn} = \frac{A_{VTN}}{\sqrt{(W - K_{vtw})}(L - K_{vt})} = \frac{12mV.\,\mu m}{\sqrt{(0.22 + 0.58) * (0.18 - 0.58)}\,\mu m} = \pm 40mV$$

Where  $A_{VT}$ ,  $K_{Vtw}$ ,  $L_{Vtl}$  are process defined constants for the threshold voltage.

It is clear from the offset equation that the fix to reduce the offset is to increase the width and the length. Increasing the length will cost us bandwidth, hence the design technique used is to have maximum length that fulfils the bandwidth requirement and subsequently increase the width to reduce the offset such that it is tolerable. Increasing the width and length after a certain value  $\approx 5 - 10$  ( $W_{min}$  and  $L_{min}$ ) at that point the global variation is dominant over the local variation[32].

Fig 2.13. Stochastic perspective for Random and Systematic Variation of Threshold voltage of a

device[18]

## 2.2.9 Monte Carlo

Monte Carlo is the technique used to sample the device parameters such as Length, Width, Threshold voltage, gate length, etc. These device parameters are assigned all the possible random values within the corner limits and the behavior of the entire circuit is analyzed based on the distributions of the circuit specifications such as gain, bandwidth, offset, etc. The design is generally tested for  $\pm 3\sigma$  from the target specification. Memory design on the other hand may require accuracy up to  $\pm 6\sigma$  which is challenging to achieve. The tool used for this effort is Cadence Virtuoso which provides inbuilt Monte Carlo functionality which has been used to analyze the design performance for this effort. Through Monte Carlo simulations we are able to estimate the yield of a fabrication run. The yield of a fabrication run is the percentage of number of chips that meet the most relaxed specifications ( $\pm 3\sigma - \pm 6\sigma$ ) that deem a chip to be just about workable.

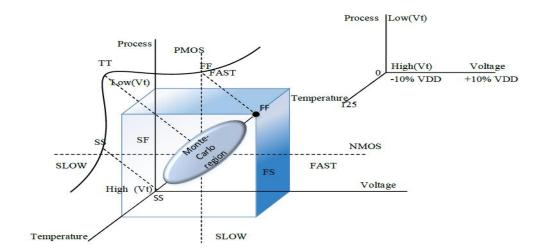

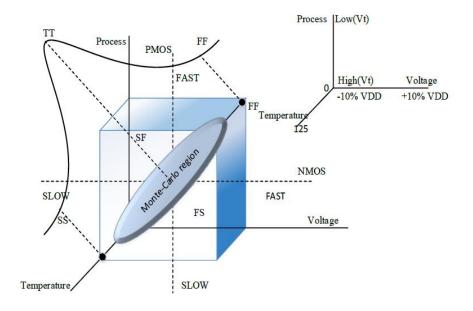

#### 2.2.10 Process Corners

Process corners are certain conditions which demonstrate the limits of process, temperature and other design parameters that guide a designer to check the robustness of the design. The corners that are predominant when analyzing any design are SS (Slow NMOS, Slow PMOS), FF (Fast NMOS, Fast PMOS), TT (Typical NMOS, Typical PMOS), FS (Fast NMOS, Slow PMOS) and SF (Slow NMOS, Fast PMOS). For sophisticated processes there may be many more corners but these are the most widely used. The corner SS means that we randomly test a NMOS and PMOS within a die that is placed spatially at a location where the process is slow for a circuit specification for example clock rate. We then check if the clock rate meets our requirement, if not that die is either discarded or sold for less. The same is done for process corners FF and TT. All die specifications are tested for all these process corners to check robustness of the design. We do not demonstrate the process corners SF and FS, since it is not possible for one die to have a Fast NMOS and Slow PMOS no matter where that die is located on the wafer. Considering that there are many dies on the wafer and a spatial shift in the process variation it is impossible to practically explain the scenarios where the SF and FS corners become relevant. SF and FS corners are just checkpoints that guarantee that the design is robust even for a non-occurring event, hence any additional design effort to achieve performance to satisfy these design corners is

36

nothing but overdesigning. To avoid overdesigning in this effort we have neglected the SF and FS design corners and focused on the SS, TT and FF corners.

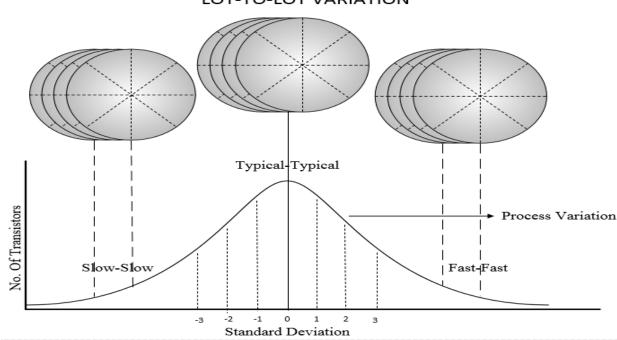

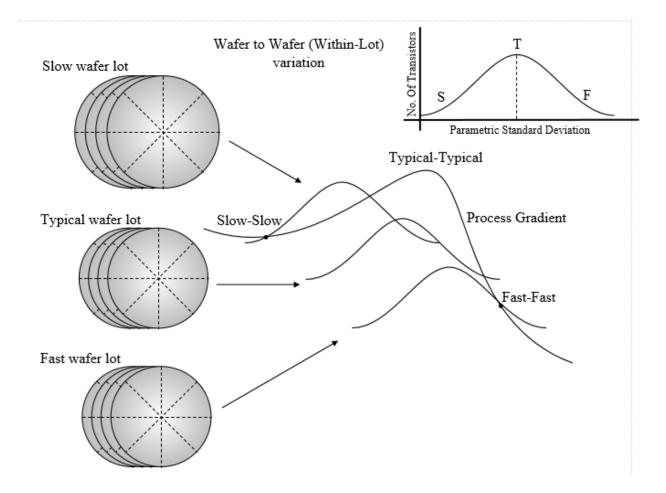

# 2.2.11 Lot-to-Lot and Wafer-to-Wafer Variation

Now that we have an understanding of what corners are we can explore the lot-to-lot and waferto-wafer variation. In a fabrication process multiple wafers are fabricated together and their collection is referred to as a lot. The variation between each lot is referred to as lot-to-lot variation which originates due to physical changes in mechanical and fabrication processes. Lot-to-Lot variation has a normal distribution such that the lots are segregated into Slow, Fast and Typical lots. Within each lot there would be a SS, TT and FF corners which implies that within that lot one wafer would be slow, typical and fast. This variation is referred to as wafer-to-wafer variation. Fig 2.14 shows the Lot-to-Lot variation while Fig 2.15 depicts Wafer-to-Wafer variation.

LOT-TO-LOT VARIATION

Fig 2.14 Lot-to-Lot Variation[18]

Fig 2.15. Wafer-to-Wafer Variation[18]

# 2.3 TEMPERATURE VARIATION

Temperature variation is a major factor when it comes to semiconductor chips. The environment condition temperatures can reach extremes and cause IC (Integrated chip) failures. Many a time when the cooling mechanism in the chip is not robust, the power generated by the chip itself can cause the internal temperature of the chip to rise to alarming levels as well as fluctuate over time.

This section will address the effects of temperature on the drain current in a circuit.

The mobility of electrons depends on the temperature as follows

$$\mu_n(T) = \ \mu_n(T_0) \ \left(\frac{T}{T_0}\right)^m$$

Where T is the environmental temperature and  $T_0$  is the reference temperature and m is the temperature coefficient of mobility. The coefficient m ranges from -1.2 to -2, often m=-1.5[11]. m is a process dependent parameter.

Threshold voltage of a MOS transistor is given by

$$V_T = V_{T0} + \gamma \left( \sqrt{V_{SB} + 2\phi_F} - \sqrt{2\phi_F} \right)$$

Where  $V_{SB}$  is the source-body voltage and  $\phi_F$  is the Fermi potential which is given by

$$\phi_F = U_T \ln\left(\frac{N_A}{n_i}\right)$$

$N_A$  is the acceptor atom doping and  $n_i$  is the concentration of intrinsic carriers in silicon.  $Ø_F$  is a strong function of temperature hence the threshold voltage also varies with temperature.  $V_T(T)$  decreases linearly with temperature as follows[16]

$$V_T(T) = V_T(T_0) + \alpha_{VT}(T - T_0)$$

Where  $V_T(T_0)$  is the threshold voltage at temperature T and  $\alpha_{VT}$  is the temperature coefficient of the threshold voltage. The typical value of the threshold voltage ranges from -0.5mV/°C to - 4mV/°C [11].

Hence we observe that both the electron mobility and threshold voltage both decrease with increase in temperature though both have opposite effects on the current flowing through the transistor. When the threshold voltage of a transistor reduces the current flowing through it increases whereas for a decrease in the electron mobility the current reduces.

## 2.3.1 Effect of Temperature Change in Weak Inversion

Restating the weak inversion drain current equation

$$I_D = I_{D0} e^{\frac{V_{GS} - V_T}{n U_T}} \left( 1 - e^{-\frac{V_{DS}}{U_T}} \right)$$

$$I_{D0} = 2n \frac{W}{L} \mu_n C_{ox} U_T^2$$

n is the subthreshold slope and ranges from 1-2.

Since the threshold voltage is in the exponential term it has a stronger influence on the current when compared to the mobility of the electrons which only linearly effects the current. When the temperature of the transistor is increased the current flowing through it increases since the threshold has reduced. When the temperature of the transistor is reduced the threshold voltage is increased causing a lower drain current to flow even though electron mobility has increased. This implies that the best case scenario for a transistor biased in the weak inversion regime is maintaining a high temperature on the other hand a low temperature would be the worst case scenario to effect a high drain current.

#### 2.3.2 Effect of Temperature Change in Strong Inversion

For the 0.18µm process the velocity of the carriers is saturated for their shorter channel lengths hence we are going to limit the strong inversion discussion to velocity saturation. When the longitudinal field in the channel is very high due to the small channel length the MOS transistor experiences carrier mobility degradation hence the slope of the carrier velocity decreases with increasing longitudinal field. Scatter effects in the channel close to the surface are the root cause of velocity saturation[16].

The drain current flowing through a transistor biased in strong inversion velocity saturation is given by[34]

$$I_D = \frac{\mu_n C_{ox}}{2\left(1 + \frac{V_{GS} - V_T}{\varepsilon_c L}\right)} \frac{W}{L} (V_{GS} - V_T)^2$$

Where  $\varepsilon_c$  is the critical field when the carrier mobility with a high horizontal field is half of the carrier mobility if the field applied was low according to [34]. The vertical field effect causes the mobility degradation due to the coulomb and phonon scattering effects[16]. The vertical and horizontal fields both contribute to the velocity saturation of the carriers, the assignment of the critical field  $\varepsilon_c$  is based on either fields horizontal or vertical as both have their critical limits. To avoid confusion, both the vertical and horizontal fields effect mobility and cause velocity saturation of the carriers as [16] associates the symbol  $\varepsilon_c$  as the critical field with the longitudinal field whereas [34] associates it to the horizontal field.

As both the carrier mobility and the threshold are linear terms of the current equation in such a case the dependence of the current would be a stronger function of carrier mobility than the threshold voltage w.r.t temperature change. Hence the current would reduce at higher temperatures as the mobility would go down dominating the effect of the reduced threshold voltage. Conversely at lower temperatures the current would be high in spite of an increased threshold voltage. The MOS transistor biased in the velocity saturated regime would therefore be slower at higher temperatures and faster at lower temperature which is completely opposite to what the MOS transistor experiences in the subthreshold region. The effect of temperature on the drain current in square-law operation is similar to the velocity saturated behavior.

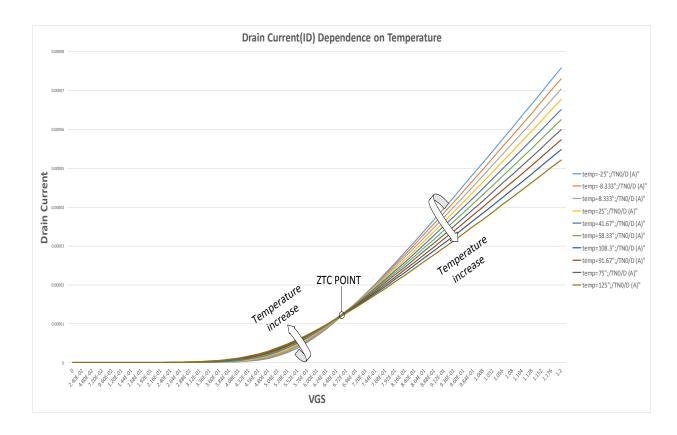

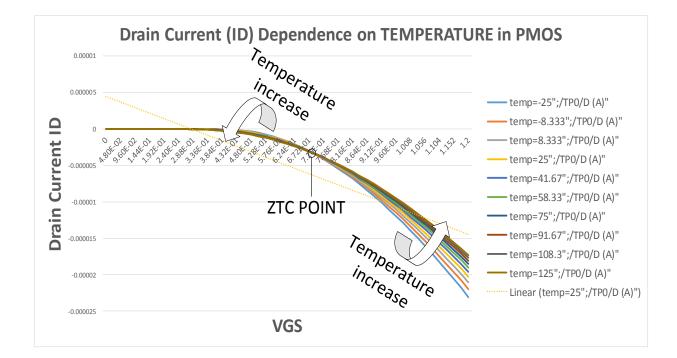

#### 2.3.3 Zero Temperature Coefficient Point (ZTC)

From sections 2.3.1 and 2.3.2 we have seen that the effect of temperature on the drain current through a MOS transistor is governed by the region of operation. The region of operation of a transistor is dependent on the gate-to-source voltage applied to the transistor. There exists a particular gate-to-source voltage for which the drain current is independent of temperature, where the effect of mobility and threshold voltage w.r.t temperature cancel each other. This value of  $V_{GS}$  for which the drain current is independent of temperature-

Coefficient Bias Point or more commonly referred to as the ZTC point. In Fig 2.16 we investigate this ZTC point by sweeping the bias voltage of a single finger minimum geometry (220nm/180nm) NMOS in a diode configuration and varying the temperature from -25°C to 125°C while recording the drain current flowing through it. The same has been done for the PMOS transistor and is shown in Fig .17.

Fig 2.16. Drain Current Dependence on Temperature and the ZTC Point for a minimum geometry NMOS

# Fig2.17. Drain Current Dependence on Temperature and the ZTC Point for a minimum geometry PMOS

Fig 2.16,17 both show the contrasting effects of MOS operation in weak and strong inversion when the temperature is increased.

## 2.4 Supply Voltage Variation

The supply voltage to a die is variable which is due to many reasons such as power supply noise, crosstalk, IR drops, etc. The performance of the die is proportional to the supply voltage, hence a higher supply voltage facilitates a greater drain current which corresponds to higher speed. The supply voltage variation is modelled at about  $\pm 10\%$  of the typical voltage value. Newer designs have a much tighter budget of  $\pm 5\%$  [35] off the target supply voltage. The impact of variation in supply voltage is masked by the detrimental effects of process and temperature variation in IC designs.

#### 2.5 PVT (Process, Voltage and Temperature) Corners

Form the discussions in Sec 2.2, 2.3 and 2.4 we have a good understanding of the impact of process, temperature and supply voltage variations on the operation of MOS transistors, now we take a look on how these three effects combine and their implications on the worst case and best case scenarios. The design of a circuit is tested for the worst case and best case PVT corners, given that the performance of that design is satisfactory for the best and worst cases it would be safe to say that the design will work for any other PVT corners within that range of operation.

#### 2.5.1 Weak Inversion PVT corners

As seen in Sec 2.2.10 a die would have a poor performance at the SS corner, while Sec 2.3.1 established that a transistor slows down when the temperature is low when the device is biased in weak inversion. Putting these two conditions together and considering the proportional dependence of the voltage on the drain current we state that the transistor performance that would be the worst case PVT corners would be the SS @ -25°C for 90% of the supply voltage. Conversely the best case would be FF@125°C for 110% of the supply voltage.

Fig 2.18. Weak inversion PVT corners[18]

Fig 2.18 represents the corners on three axis, process, temperature and voltage. The center of the graph represents the worst case whereas the best case is located in the 3-D plane and all other possible conditions are limited within these two extremes.

# 2.5.2 Strong Inversion PVT corners

The PVT corners for strong inversion is different from the weak inversion in terms of the temperature corner as seen in Sec 2.3. Hence the worst case PVT corner for the strongly inverted device would be SS@125°C at 90% supply voltage whereas best case corner would be FF@-25°C at 110% supply voltage. Fig 2.19 shows the corners for the strong inversion device.

Fig 2.19. Strong inversion PVT corners[18]

# CHAPTER III

#### ASK DEMODULATORS

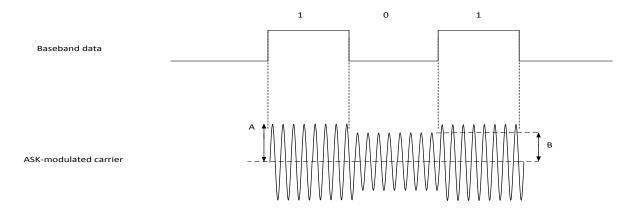

#### 3.1 Digital Modulation

The most prominent digital modulation schemes are Amplitude Shift Keying (ASK), Frequency Shift Keying (FSK) and Phase Shift Keying (PSK). ASK modulation is the most widely used modulation schemes for passive wireless microsystems due to the fact that the modulator and demodulators are simple to configure and their power consumption[11]. In this work we focus on the ASK modulation, the FSK and PSK modulation schemes can be found in [11]. Figure 3.1 depicts the waveform of a binary ASK modulated bit stream[11].

Figure 3.1 Binary ASK modulated bit stream [11]