# A MATRIX MODEL OF DIGITAL SYSTEMS AND ITS

## APPLICATION TO AUTOMATIC

## TEST GENERATION

By

## CHARLOTTE COUCH ACKEN

Bachelor of Science University of Arkansas Fayetteville, Arkansas 1969

Master of Science University of Arkansas Fayetteville, Arkansas 1971

Master of Science Oklahoma State University Stillwater, Oklahoma 1977

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY May, 1982

A MATRIX MODEL OF DIGITAL SYSTEMS AND ITS

# APPLICATION TO AUTOMATIC

TEST GENERATION

Thesis Approved:

ma Thesis Adviser en. a and

Dean of the Graduate College

### ACKNOWLEDGMENTS

My sincere appreciation is extended to Dr. Ronald P. Rhoten, chairman of my doctoral committee and my thesis adviser, for his invaluable assistance throughout the course of my graduate education in electrical engineering. I am grateful to the other members of my doctoral committee, Dr. C. M. Bacon, Dr. M. E. Daniel, Dr. J. W. Maxwell, and Dr. R. J. Mulholland, for their critical reviews of the manuscript and for their encouragement and friendship.

Financial support for this research has been provided by Sandia National Laboratories. Sandia management directly involved in providing me the opportunity to conduct this work were D. M. Olson, D. M. Schuster, C. W. Gwyn, A. A. Lieber, M. E. Daniel, and W. F. Roherty. Their exhibited confidence in my abilities are much appreciated.

Special thanks are extended to the staff of the Sandia National Laboratories technical library, word processing center, and graphic arts division for their assistance. The typing of the final copy was performed by Charlene Fries, to whom I am most grateful.

Well deserved gratitude is extended to my parents, whose personal sacrifice, encouragement, and understanding have inspired me throughout my education. I am thankful for my wonderful husband, John, who has provided loving encouragement and enthusiastic confidence in me during the preparation of this thesis.

iii

# TABLE OF CONTENTS

| Chapte | r Pa                                           | ige                        |

|--------|------------------------------------------------|----------------------------|

| ١.     | INTRODUCTION AND BACKGROUND                    | 1                          |

| 11.    | REVIEW OF RELATED LITERATURE                   | 6                          |

|        | Introduction                                   | 6<br>6<br>16<br>22         |

| 111.   | MODELING DIGITAL SYSTEMS                       | 23                         |

|        | Notation                                       | 23<br>23<br>26<br>39<br>42 |

| ١٧.    | MODEL CHARACTERISTICS AND EXTENSIONS           | 45                         |

|        | Combinational Circuit Matrix Complexity        | 45<br>45<br>53<br>54<br>56 |

| ۷.     | A MATRIX APPROACH TO AUTOMATIC TEST GENERATION | 57                         |

|        | · · · · · · · · · · · · · · · · · · ·          | 57<br>57<br>75<br>83       |

| VI.    | CONCLUSIONS AND RECOMMENDATIONS                | 85                         |

|        |                                                | 85<br>86                   |

| A SELE | CTED BIBLIOGRAPHY                              | 91                         |

# LIST OF TABLES

| Table | e                                         | Page |

|-------|-------------------------------------------|------|

| ١.    | Boolean Difference Identities             | 19   |

| 11.   | Truth Tables for "AND" and "OR" Functions | 25   |

# LIST OF FIGURES

| Figu | re                                                                    | Page |

|------|-----------------------------------------------------------------------|------|

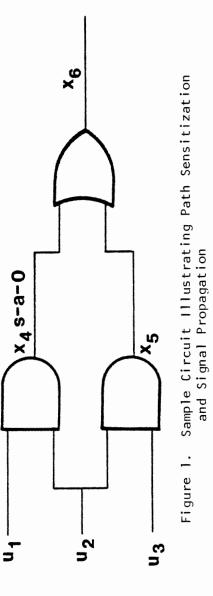

| 1.   | Sample Circuit Illustrating Path Sensitization and Signal Propagation | 10   |

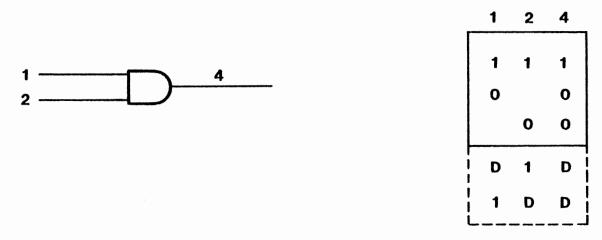

| 2.   | An AND Gate With Its Singular Cover and D-Cubes                       | 11   |

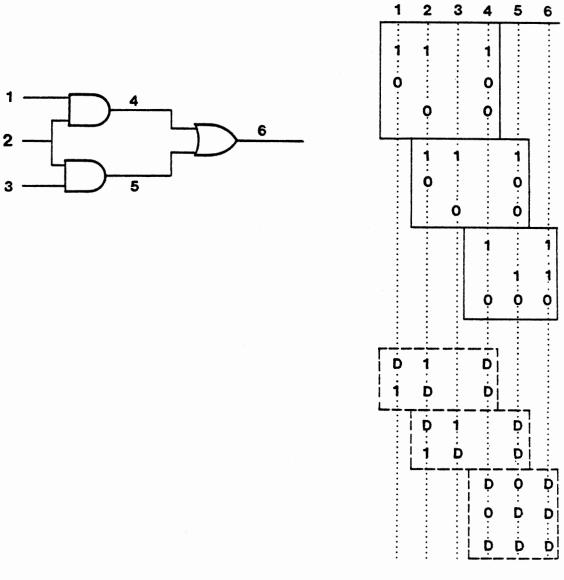

| 3.   | A Simple Combinational Circuit With Its Singular Cover<br>and D-Cubes | 13   |

| 4.   | Sequential Circuit Modeled as an Iterative Combinational<br>Array     | 17   |

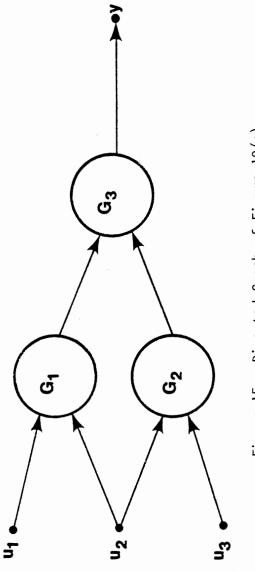

| 5.   | Circuit Viewed as Composite Functions                                 | 21   |

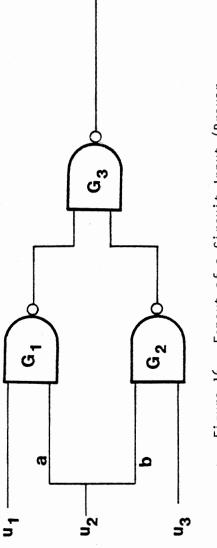

| 6.   | Labeled Generic Logic Diagram                                         | 27   |

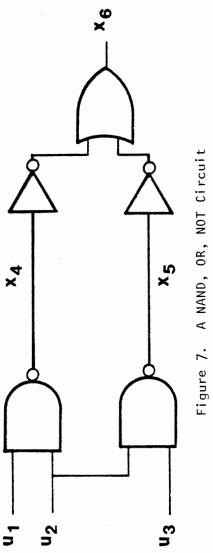

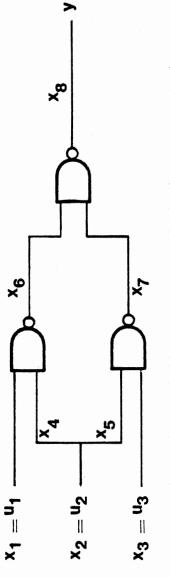

| 7.   | A NAND, OR, NOT Circuit                                               | 29   |

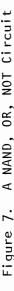

| 8.   | Model Representation of Logic Gates                                   | 32   |

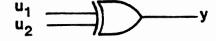

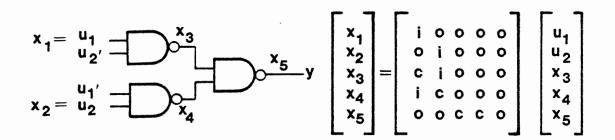

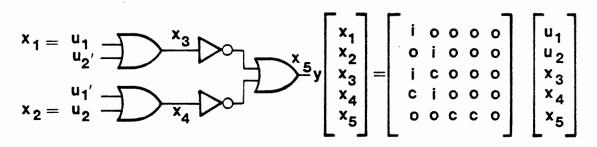

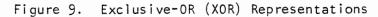

| 9.   | Exclusive-OR (XOR) Representation                                     | 34   |

| 10.  | Combinational Circuit Modeling                                        | 35   |

| 11.  | NOT and OR Gates Represented in Terms of NAND Gates                   | 37   |

| 12.  | Compact Matrix Formulation                                            | 38   |

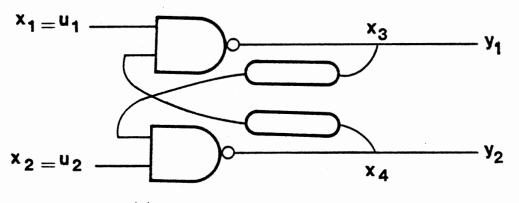

| 13.  | Sequential Circuit Modeling                                           | 40   |

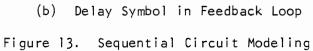

| 14.  | Clocked D-Flip Flop                                                   | 43   |

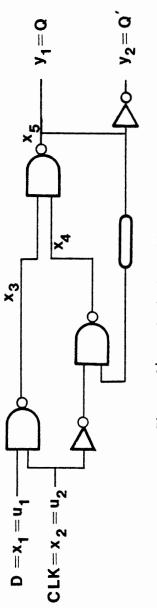

| 15.  | Directed Graph of Figure 10(a)                                        | 47   |

| 16.  | Fanout of a Circuit Input                                             | 51   |

| 17.  | Labeling Extended to Forks in a Fanout Path                           | 52   |

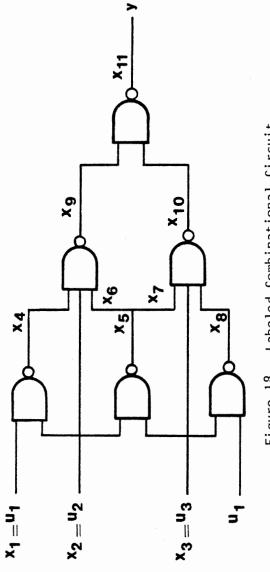

| 18.  | Labeled Combinational Circuit                                         | 60   |

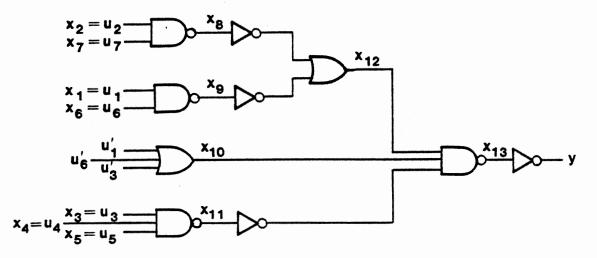

| 19.  | Combinational Circuit                                                 | 63   |

| 20.  | Schneider's Example                                                   | 67   |

| F  | igure                                                                                                                                          |   |   |   |   | Ρ | age |

|----|------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|-----|

| 2  | 1. Circuits With Undetectable Faults                                                                                                           |   | • | • | • |   | 69  |

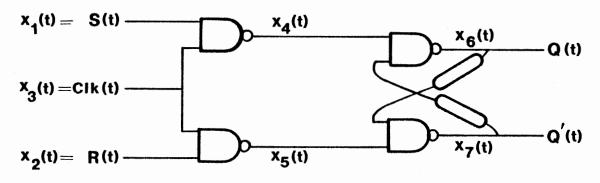

| 22 | 2. Gate Level Representation of a Clocked S-R Flip Flop                                                                                        | • | • | • | • | • | 72  |

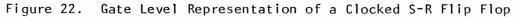

| 2  | <ol> <li>Flow Diagram for Combinational Circuit Test Genera-<br/>tion Using Single Path Sensitization and the Acken<br/>Matrix Model</li></ol> | • | • | • | • | • | 74  |

| 24 | 4. Example Circuit for Illustrating Boolean Difference                                                                                         | • | • | • |   | • | 78  |

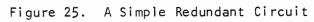

| 25 | 5. A Simple Redundant Circuit                                                                                                                  | • |   |   |   |   | 88  |

.

#### CHAPTER I

## INTRODUCTION AND BACKGROUND

Physical faults can occur at any point during the life of a digital system. Generally speaking, a fault can be defined as anything which causes the system to operate in a manner other than that for which it was designed. Faults can originate during the manufacture, assembly, storage, and/or service phase of the system life. Open circuits, short circuits, and incorrect impedance are example faults. Those which alter the magnitude of a circuit parameter with a resultant modification in circuit speed, current, or voltage are termed parametric faults. Faults which alter the logical behavior of the system are termed logical faults. Because faults can, and do, occur at any time during the life of a digital system, it is necessary to determine, via some testing procedure, the operational status of the device.

A test for a logical fault is defined to be a set of inputs (or input sequences) for which a faulty system will exhibit an unintended logical behavior. Only tests for logical faults will be considered in this research.

The advent of large-scale integration (LSI) and very large-scale integration (VLSI), as well as the increased complexity of digital integrated circuits (ICs), has made manual test generation extremely timeconsuming, unreliable, and physically difficult. For this reason, automatic test generation (ATG) algorithms are desirable. However, most ATG

algorithms are also constrained by the size and complexity of present day ICs. An obvious algorithm for ATG for combinational circuits is to generate all possible input combinations and compare the output of the device under test (DUT) with a known output. This procedure detects all possible logical faults within the system. The disadvantage to this approach becomes apparent as the number of primary inputs, n, increases. Assuming a testing system with a stimulus/response cycle of 1 microsecond, it would take 1 second to exhaustively test a combinational logic circuit with 20 primary inputs. The amount of time required rises exponentially as the number of primary inputs increases, and for n = 50, the time required becomes 35 years!

One approach to narrowing the problem to feasible limits is to consider a subset of all possible faults whose detection will result in a high confidence that all likely faults of interest have been detected. The fault subset is generally defined via a logical fault model.

There are three basic requirements of any logical fault model. The model should indicate what effect the fault will impose upon the operation of the circuit, how many such faults are assumed to be present at one time, and how long the fault is present. The most common logical fault model (also to be utilized in this research) is the single permanent stuck-at model. This model assumes that only one primary input/ output or internal signal line in the circuit will be permanently stuck at logical zero or logical one during the duration of any test.

If a circuit has n primary input lines and p internal signal lines (including primary outputs), then the total possible number of single faults (i.e., occurring one at a time) is 2 (n + p) since each line could be stuck-at-zero or stuck-at-one.

If two or more of the signal lines are simultaneously faulty, there are a total of  $3^{n+p}$  - 1 such multiple faults to consider. Because this number tends to become large as circuits increase in size, this multiple fault model becomes intractable. Even though the multiple fault model is a valid model, it has not been utilized in practical implementations because of the exponential growth in the number of faults that have to be considered.

One method of generating tests for logical faults is to have a test engineer determine input vectors which would cause a change in signal value on every signal line in the device under test. To achieve this, as well as try to minimize the test length and perform fault location simultaneously, would require a lot of detailed and repetitive work-the type of work that is more efficiently done by a computer.

Automatic test generation refers to the process of generating a set of inputs to an integrated circuit via a computer algorithm. Most algorithms utilize information about the system topology and/or behavior and the faults for which tests are being generated. Almost all automatic test generation methods are based upon models of the digital circuit in addition to fault models, some of which were discussed earlier.

Many digital system models exist. The two utilized most extensively for automatic test generation are the gate level logic diagram and the register-transfer level (RTL) diagram. The gate level logic diagram characterizes the system as an interconnection of one or more of the basic logic gates (AND, OR, NOT, NAND, NOR). An RTL diagram characterizes the circuit as an interconnection of functional blocks such as registers, counters, or ALUS. Functional level test generation utilizes an RTL circuit model and attempts to generate tests which will detect

whether or not the functional blocks are performing the function for which they were designed (shifting, counting, ect.). Modeling the circuit at the register-transfer level tends to decrease the execution time and memory requirements for ATG, compared to that required for ATG algorithms which utilize a gate level circuit description. However, functional level test generation methods lack the ability to isolate faults to a gate or signal level, may generate invalid tests, and suffer from a lack of adequate fault models.

The efficiency of ATG algorithms which utilize a gate level circuit description depends upon how much information concerning the circuit behavior and topology is passed and how concisely the information is formulated for use in the algorithm. Completely random ATG formulates no information about the circuit behavior and topology to guide it in generating tests. Other algorithms formulate the behavior and/or topological information in various ways.

Chapter II is a review of some of the best known and most widely used gate level automatic test generation methods. The manner in which the behavior and/or topological information is formulated and utilized by each is reviewed, and the advantages and weaknesses of each method and its underlying mathematical formulation are pointed out.

A matrix formulation for digital integrated circuits is introduced in Chapter III. This representation contains the information about the logical behavior and topology of a circuit necessary for gate level automatic test generation. The concise matrix formulation can be easily stored in and manipulated by a computer. Characteristics of and extensions to the formulation are given in Chapter IV.

Chapter V illustrates several ways in which the matrix representation can be utilized to automatically generate tests. Approaches using path sensitization and Boolean equation manipulation for test generation are presented.

Along with the thesis conclusions, Chapter VI contains suggestions for other possible uses of the matrix representation of a digital system. These include the analytical detection of circuit redundancy and the use of the matrix model as a structure in which to perform testability analysis.

Numerous examples are included in Chapters III through VI to illustrate concepts and techniques.

## CHAPTER II

# REVIEW OF RELATED LITERATURE

# Introduction

The first ATG algorithms were based upon gate level circuit models and the single permanent stuck-at fault model. Boolean equation manipulation was an early ATG technique followed by path sensitization approaches. Most of today's gate level ATG algorithms are based upon one or a combination of both these procedures.

In order to fully understand why certain characteristics of digital system models such as topology, behavior, and compact representation are essential to ATG, a close look at digital circuit test generation methods is necessary. Two path sensitization approaches are reviewed, the Dalgorithm (Roth, 1966) and critical path sensitization (Thomas, 1971). One equation manipulation technique, the Boolean difference approach (Sellers, Hsiao, and Bearnson, 1968) is outlined. Emphasis will be placed on the type of circuit information needed for the technique and the way the information is formulated.

# Path Sensitization

The D-algorithm (Roth, 1966) has formed the basis for most of the ATG programs in use today because it introduced the fundamental concept of path sensitization. Variants of the original path sensitization procedure have proven to be successful.

As it was originally conceived, path sensitization was to be performed on a gate level model of the circuit and generate tests for stuck-type faults. Others have used the idea of path sensitization on partitioned blocks of logic circuitry and on higher level primitives such as registers, counters, etc. (Breuer and Friedman, 1980; Bennetts, Brittle, Prior, and Washington, 1975). Other fault models have also been used in conjunction with the D-algorithm (Breuer and Friedman, 1976).

The basic idea of path sensitization will first be explained, followed by a description of two path sensitization algorithms and their associated model formulation. The advantages and disadvantages to these two techniques and their models will be pointed out.

We first explain the concepts of line justification and error propagation. A value of  $j \in \{0,1\}$  on the output to gate G is justified by assigning values to the gate inputs which, when applied to G, will result in the value j. For example, the value 1 on the output of an AND gate can be justified by assigning the value 1 to each of the gate inputs. Similarly, the value 0 on the output of an AND gate can be justified by assigning the value 0 to any one or more of the inputs to the gate. Hence, justifying a 0 output to a 2-input AND gate allows three choices. If the inputs are  $u_1$  and  $u_2$ , we may choose  $u_1 = 1$ ,  $u_2 = 0$ ;  $u_1 = 0$ ,  $u_2 = 1$ ; or  $u_1 = u_2 = 0$ .

Adopting the symbolism of (Roth, 1966) the letter D will be used to represent the value of a signal line which has the value 1 in the normal (fault-free) circuit and 0 in the faulty circuit, and D' to represent the value of a signal line which has the value 0 in the fault-free

circuit and 1 in the faulty circuit. Hence, if a line has value D, it is stuck-at-0 and D' represents the stuck-at-1 condition.

The error signal D on an input line of gate G is propagated through the gate by assigning values to the other inputs of gate G which will result in a D or D' on the gate output. For example, if an input to an AND gate is assigned the error value D, it will be propagated to the output of the gate only if all other inputs are assigned the value 1. If any other input to the AND gate takes the value 0, the output will be zero and the error value cannot be propagated. To propagate an error signal (either D or D') through an OR gate, all other inputs must be zero; through a NAND gate, all other inputs must be one; through a NOR gate, all other inputs must be zero. Hence, no choice in assignments exists in fault propagation for a given gate type.

The path sensitization procedure for combinational circuits can be described as follows:

Step 1. Select a fault (stuck-at-j, jɛ{0,1}) and fault site (some signal line, a).

Step 2. Justify the value j' on the signal line a by assigning values to the primary inputs. This justification step may require some choices when assigning values to signal lines and/or primary inputs.

Step 3. Propagate the faulty signal value to a primary output along one path or simultaneously along multiple paths through the circuit. Note that a choice of paths may exist. Propagation of a signal value will require assignments to be made along the chosen path; however, as noted earlier, these assignments are never arbitrary.

Step 4. Justify the assignments made in Step 3 so that they are consistent with the assignments made in Step 2. If a consistent

assignment is not possible, then no test exists for the specified fault.

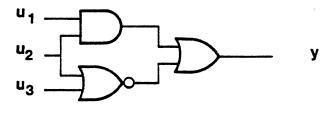

The following example illustrates the path sensitization procedure. Figure 1 is a simple combinational circuit. Assume line  $x_4$  is stuck-at-0. According to Step 2, we wish to justify a 1 on line  $x_4$ , and this is done by setting input  $u_1 = 1$  and  $u_2 = 1$ . Next we wish to propagate the fault through the OR gate to line  $x_6$ , a primary output. This is done by assigning  $x_5 = 0$ . Step 4 involves justifying  $x_5 = 0$  consistent with the other values already assigned.  $x_5$  will equal zero if  $u_2 = 0$ ,  $u_3 = 1$ ;  $u_2$ = 1,  $u_3 = 0$ ; or  $u_2 = u_3 = 0$ . We must choose  $u_2 = 1$ ,  $u_3 = 0$  to be consistent with the assignment made in Step 2. Thus our test consists of the input  $u_1 = 1$ ,  $u_2 = 1$ ,  $u_3 = 0$ .

It is apparent that there are two items of information about the circuit necessary to perform path sensitization. The topology, i.e., the gate interconnection or network information, is needed to determine the path through the circuit. In addition, the behavior of each gate must be known. For example, the information that an AND gate output is 1 only if both inputs are 1, and 0 only if at least one input is 0, is essential.

Path sensitization procedures differ in the manner in which the topological and behavioral information is stored and manipulated to generate tests. The D-algorithm uses "cubes" to pass behavioral information. An operation called intersection of cubes is performed to establish a chain or path through the circuit. Figure 2 illustrates the cube concept. The inputs to the AND gate are labeled 1 and 2, and the output line is labeled 4. At the right in Figure 2 is a table whose heading has the input/output labels. The first row specifies that the output is 0 when both inputs are 1, and the second and third, that the output is 0

Figure 2. An AND Gate With Its Singular Cover and D-Cubes

when either input is 0. This is termed the singular cover of the function, and each row in the singular cover is called a cube. Below the singular cover is the error propagation information for the function. These are called D-cubes of a failure. The first cube indicates that a fault on input 1 can be propagated to output 4 if input 2 is 1. These five cubes contain the behavioral information of an AND gate needed to generate a test in a circuit containing an AND gate.

Figure 3 repeats the circuit of Figure 1 showing its singular cover and, within dashed lines, D-cubes. This example is by Roth (1966). The intersection of two cubes determines how circuit conditions specified by the two cubes can be simultaneously satisfied. If the intersection does not exist, the two conditions assign different values to the same line, implying that the conditions are inconsistent. The intersection of cube  $A = (a_1, a_2, \ldots, a_n)$  with cube  $B = (b_1, b_2, \ldots, b_n)$  designated as  $C = (c_1, c_2, \ldots, c_n) = A + B$  is defined as

c<sub>j</sub> = a<sub>j</sub>

if  $a_j = b_j$  or if  $b_j$  is unspecified. If  $a_j \neq b_j$  for some j, then the intersection C does not exist.

The algorithm itself involves intersecting the D-cubes in a trial and error fashion until a chain is formed from the site of the fault to a primary output. Selected node fanin and fanout information is saved as the algorithm progresses so that the topology of the network is progressively learned. Nodes not specified in the D-cube intersecting phase are assigned by intersecting the incomplete test cube with cubes from the singular cover until all lines for which it is possible to assign values have received them. The entire process may require a

Figure 3. A Simple Combinational Circuit With Its Singular Cover and D-Cubes

.

great deal of backtracking. A detailed description of the algorithm appears in Breuer and Friedman (1976, pp. 46-49). Detailed examples are also given in the former reference as well as in Roth's original paper (Roth, 1966).

In its most general form, the D-algorithm can always find a test if one exists. If the fault is undetectable, the procedure proves that no test exists.

Schneider (1967) has shown that in some cases it may be necessary to sensitize several paths simultaneously in a reconvergent fanout network to detect a fault. (A network has reconvergent fanout if at least one primary input and/or gate output branches out to two or more gates whose outputs lie on paths through the circuit which later reconverge as inputs to a single gate.) While multiple path sensitization is possible with the D-algorithm, Breuer (1981) asserts that multiple path sensitization cases are rare, and that practical implementations of the D-algorithm are often restricted to single path sensitization in order to reduce computation time.

The cube notation and calculus used by the D-algorithm is adequate with respect to behavioral information and is expressed in a format that is easily stored and manipulated by a computer. The representation of the behavioral information suffers from a lack of compactness, however. The need for so much backtracking in the algorithm execution is an indication that a lack of adequate topological information is available in the circuit model. Paths are discovered and problems such as those encountered in circuits containing reconvergent complemented fanout cannot be avoided due to a lack of topological information. (Reconvergent complemented fanout is defined and discussed in Chapter V.)

A variant of the D-algorithm, critical path sensitization, was introduced by Thomas (1971) and is employed in the stimulus generation section, STIMGN, of the D-LASAR system. The procedure involves first selecting a primary output line and assigning to it a critical 1 (0) value. Using sensitizing cubes, this value is driven back toward the primary inputs as in the justification procedure of the D-algorithm. Whenever a choice exists, one alternative is selected. In order to consider all possibilities, the other choices are reserved and used later by backtracking to the site of the choice and making an alternate assignment. For each choice of assignments, all implications of that choice are made. Each line assignment that is critical to the justification procedure is marked as it is generated, and all critical lines are driven back, all noncritical lines are justified using primitive cubes. When an inconsistency arises, making it impossible to justify a critical value by using a sensitizing cube, one can backtrack and use a primitive cube. This procedure is then repeated for each primary output.

The critical path test generation procedure is outlined in detail with examples in Breuer and Friedman (1976). It may fail to generate a test for a fault which requires multiple path sensitization but detects many faults along a sensitized path in one pass. This later characteristic makes it a fault-independent algorithm.

The D-LASAR system models all circuits in terms of their NAND gate equivalent network. This decreases the amount of behavioral information required, thus compacting that information. The disadvantages in modeling everything in terms of NAND gates are twofold. The number of gates in the circuit model can be significantly greater than in the original network. More storage may be required for the network description but

less for the cube description. The NAND gate equivalent description has been criticized because it is an abstraction of the original circuit and there may not be a one-to-one correspondence between the stuckat faults on the signal lines in the model and those of the original circuit.

The significant amount of backtracking and arbitrary assignment of line values when choices arise indicate here, as in the D-algorithm, that not enough topological information is contained in the model. Paths are discovered, as in the D-algorithm, by intersecting cubes to form a long path through the circuit.

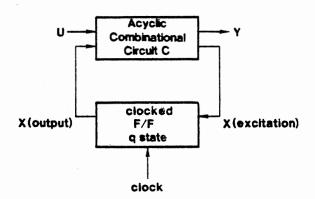

Both the D-algorithm and D-LASAR utilize the iterative combinational array to model sequential circuits. In this model, the feedback loops are cut and the circuit reproduced into cells corresponding to an assigned time frame (see Figure 4). The feedback lines form pseudo outputs of time frame j in cell j and pseudo inputs to time frame j+l in cell j+l. The test generation procedure results in a sequence of input vectors for each fault. Due to the memory characteristic of sequential circuits, it is desirable to obtain a test sequence that is independent of the initial circuit condition since initialization sequences may be difficult or sometimes impossible to generate. In addition, the presence of a fault in the circuit may invalidate an initialization sequence.

#### Equation Manipulation

The final test generation procedure to be reviewed is the Boolean difference algorithm. The Boolean difference approach to ATG is a faultdependent Boolean equation manipulation procedure which utilizes the stuck-at fault model. As a mathematical concept, difference methods can

Combinational Array (Breuer and Friedman, 1976)

be traced to G. Boole in 1872. The elegant mathematical formulation of the Boolean calculus was first introduced by Akers (1959). The use of this calculus to derive tests for logic faults in digital circuits was first suggested by Professor E. Stabler to L. W. Bearnson at Syracuse University (Bearnson, 1965). Further development of the idea appeared in a paper by Sellers et al. (1968) and has since undergone extensive development. It is considered to be the classical equation manipulation approach to ATG.

Assume that a combinational circuit with inputs  $u_1, u_2, \ldots, u_n$ realizes the function  $f(u_1, u_2, \ldots, u_n)$ . Let  $f_i(0) = f(u_1, \ldots, u_{i-1}, 0, u_{i+1}, \ldots, u_n)$  and  $f_i(1) = f(u_1, \ldots, u_{i-1}, 1, u_{i+1}, \ldots, u_n)$ . These represent the condition when input  $u_i$  is stuck-at-0 and stuck-at-1, respectively. The objective in test generation is to find an input vector  $U = (u_1, u_2, \ldots, u_n)$  that causes f(U) and  $f_i(0)$   $(f_i(1))$  to take on different values so that the presence of the fault will be detectable at the primary output. Equivalently, we wish to solve the equation  $f(U) \oplus f_i(0) = 1$   $(f(U) \oplus f_i(1) = 1)$  for U.

By Shannon's expansion algorithm, we have

$$f(U) \bigoplus f_{i}(0) = [u_{i}f_{i}(1) + u_{i}'f_{i}(0)] \bigoplus f_{i}(0)$$

$$= [u_{i}f_{i}(1) + u_{i}'f_{i}(0)] f_{i}'(0)$$

$$+ f_{i}(0)[u_{i}f_{i}(1) + u_{i}'f_{i}(0)]'$$

$$= u_{i}f_{i}(1) f_{i}'(0) + u_{i}f_{i}'(1) f_{i}(0)$$

$$= u_{i}[f_{i}(1) \bigoplus f_{i}(0)]$$

The factor  $f_i(1) \oplus f_i(0)$  is referred to as the Boolean difference of f with respect to u<sub>i</sub> and is given the symbol df/du<sub>i</sub>. This symbol should

not be confused with the derivative notation in the calculus. The test for  $u_i$  stuck-at-0 is the input vector (or vectors) U that satisfy the equation

$$u_i \frac{df}{du_i} = 1$$

.

Similarly, it can be shown that a test for  $u_i$  stuck-at-1 is the solution of the equation

$$u_i^{\prime} \frac{df}{du_i} = 1$$

.

The circuit of Figure 1 realizes the Boolean function  $f(u_1, u_2, u_3) = u_2(u_1 + u_3)$ . The test for  $u_1$  stuck-at-0 is the solution of  $u_1[f(0, u_2, u_3) \oplus f(1, u_2, u_3)] = u_1[u_2u_3 \oplus u_2] = 1$  or  $u_1u_2u_3' = 1$ . The solution is (1,1,0) which tests for  $u_1$  stuck-at-0 (see Table 1).

### TABLE I

BOOLEAN DIFFERENCE IDENTITIES

| $\frac{df'(U)}{du_i} = \frac{df(U)}{du_i}$                                                                                                                    | (1) |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| $\frac{d[f(U) \cdot g(U)]}{du_{i}} = f(U) \cdot \frac{dg(U)}{du_{i}} \oplus g(U) \frac{df(U)}{du_{i}} \oplus \frac{df(U)}{du_{i}} \cdot \frac{dg(U)}{du_{i}}$ | (2) |

| $\frac{d[f(U) + g(U)]}{du_{i}} = f'(U) \cdot \frac{dg(U)}{du_{i}} \oplus g'(U) \frac{df(U)}{du_{i}} \oplus \frac{df(U)}{du_{i}} \cdot \frac{dg(U)}{du_{i}}$   | (3) |

| $\frac{d[f(U) \oplus g(U)]}{du_{i}} = \frac{df(U)}{du_{i}} \oplus \frac{dg(U)}{du_{i}}$                                                                       | (4) |

The use of the identities listed in Table I reduces the amount of algebraic manipulation required in order to determine  $df/du_i$ . If one of the functions, say g(U), is independent of the variable  $u_i$ , then  $dg/du_i = 0$ . When this situation exists, Equations (2) and (3) simplify as follows:

$$\frac{d[f(U) \cdot g(U)]}{du_{i}} = g(U) \frac{df(U)}{du_{i}}$$

(2a)

$$\frac{d[f(U) + g(U)]}{du_{i}} = g'(U) \frac{df(U)}{du_{i}}$$

(3a)

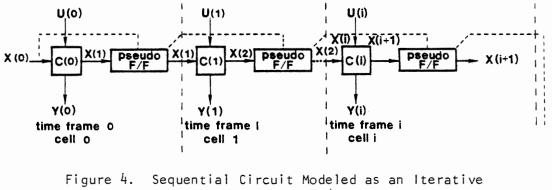

In its original formulation, the Boolean difference approach could generate tests for stuck-at faults on primary input lines only. The concept of a chain rule to enable the computation of composite Boolean differences from the partial Boolean differences of the component functions was introduced by Marinos (1971). For example, the circuit of Figure 5 may be thought of as a composite of the functions f and g, where  $f = x_1 = u_1u_2$  and  $g = x_3 = f + u_3u_4$ . To generate a test for  $x_1$  stuck-at-0, we solve

$$x_{1} \frac{dx_{3}}{dx_{1}} = u_{1}u_{2} \frac{d(x_{1} + u_{3}u_{4})}{dx_{1}} = u_{1}u_{2}(u_{3} + u_{4}) = 1.$$

The tests are (1,1,0,x) and (1,1,x,0), where x represents a "don't care" value.

If each circuit element is considered to be a separate subcircuit, the method resembles the path sensitization procedure. A general form of the chain rule was derived by Chang, Reed, and Banes (1972). Their formula is closely related to the multiple path sensitization concept. Applications of the Boolean difference approach for fault detection in

both asynchronous and synchronous sequential machines exist (Prior and Bennetts, 1974; Hsiao and Chia, 1971).

The Boolean difference approach derives all possible tests which detect a given fault. Since the equation for the circuit is needed, the time and memory requirements for generation of the circuit equations may be excessive for large circuits. Computers are not known to be particularly efficient at manipulation of symbols and simplification of equations.

#### Summary

The fundamental concepts involved in two basic approaches to automatic test generation have been presented. The path sensitization procedure introduced in Roth's D-algorithm (1966) and later modified for use in D-LASAR (Thomas, 1971) is performed by representing the behavior of a circuit by cubes. A path is traced through the circuit by intersecting the cubes according to the rules of the cube calculus. It was noted that in both instances, the behavioral information was adequately supplied to make the algorithm efficient; however, lack of adequate topological information in the cubical representation led to time consuming backtracking in the algorithms.

The Boolean Difference procedure was shown to be an elegant mathematical concept which generates all possible tests for stuck-type faults. However, since it requires the Boolean equation of the circuit, time and memory requirements for generating the equation for large circuits may be excessive.

#### CHAPTER III

#### MODELING DIGITAL SYSTEMS

### Introduction

Automatic test generation algorithms based upon a gate level circuit model can benefit from both topological and behavioral information. The efficiency of the algorithm depends, to a large extent, on the mathematical formulation of this information. The mathematical model should be capable of simultaneously describing the gate level interconnection structure and the logical behavior of each individual gate in a concise mathematical representation suitable for easy storage in and manipulation by a computer.

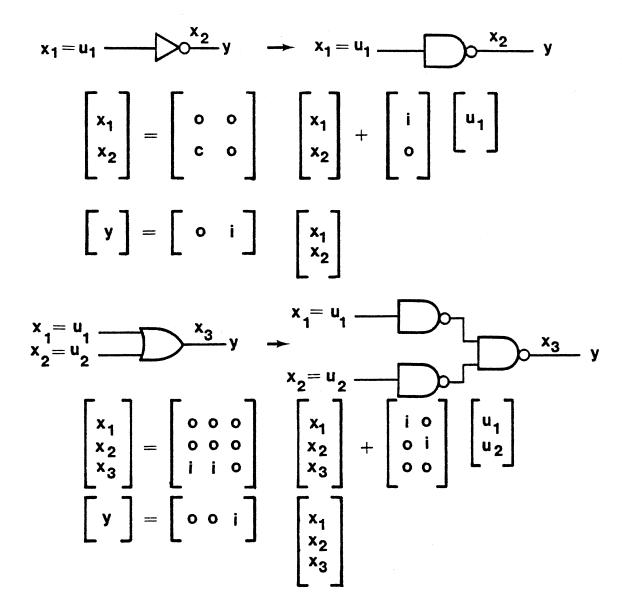

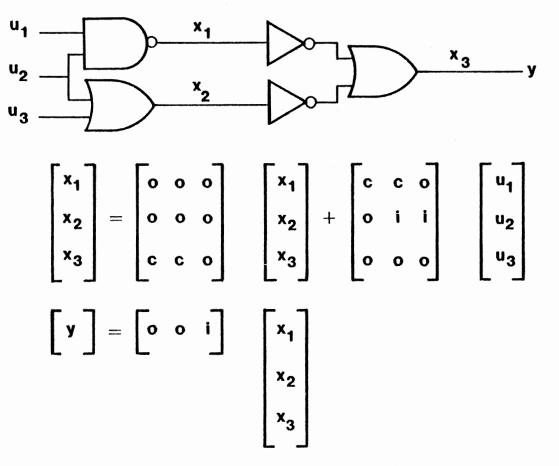

In this chapter, a mathematical model of digital systems is introduced. The model represents a digital system as a set of discrete time Boolean equations expressed in matrix notation. The emphasis of this chapter is to illustrate how the model is formulated from a gate level circuit diagram and to illustrate the representation of behavioral information. The following chapter emphasizes the features of the model pertaining to the network topology and to the machine storage complexity of the model itself.

#### Notation

A Boolean function is a function f with domain  $\{0,1\}^n = B^n$  and range  $B = \{0,1\}$ , where n is an integer and  $B^n$  represents the n-fold

Cartesian product of the set B with itself. A set of m Boolean functions  $f_1, f_2, \ldots, f_m$ , each of which maps  $B^n$  into B, can be represented by a single function f whose domain is  $B^n$  and whose range is  $B^m$ .

There are exactly four Boolean functions from B into B. These functions are:

| ldentity         | $f_i(x) = x$   |

|------------------|----------------|

| Complement (NOT) | $f_c(x) = x'$  |

| Constant Unit    | $f_{u}(x) = 1$ |

| Constant Zero    | $f_{0}(x) = 0$ |

for  $x \in B$ . The notation can be simplified by dropping the f and the parentheses from the functional notation.

| Identity         | ix = x   |

|------------------|----------|

| Complement (NOT) | c× = ×'  |

| Constant Unit    | ux = 1   |

| Constant Zero    | ox = 0 . |

Two other very important functions are the Boolean AND and Boolean OR functions whose truth tables are exhibited in Table II. These functions are used so frequently that a shorthand notation exists for them:  $f_{OR}(x_1,x_2) = x_1 + x_2$ ,  $f_{AND}(x_1,x_2) = x_1 \cdot x_2$ . One canonical representation of a Boolean function is the disjunctive normal form (DNF) which is formed by composition of the AND, OR, and NOT functions. Because every Boolean functions can be represented through functional composition of the three functions AND, OR, and NOT, these three functions form a basis set for the set of all Boolean functions. Other basis sets exist, e.g., {OR, NOT} and {AND, NOT}. When the two functions AND and NOT are composed, the resulting composition function is called the NAND (NOT)

AND) function. Similarly, the NOR (NOT OR) function arises from the composition of the OR and NOT functions. Each of these functions also forms a basis for the set of all Boolean functions.

# TABLE II

TRUTH TABLES FOR "AND" AND "OR" FUNCTIONS

| ×ı | ×2 | $f_{AND}(x_1, x_2) = x_1 \cdot x_2$ | ×ı | ×2 | $f_{0R}(x_1, x_2) = x_1 + x_2$ |

|----|----|-------------------------------------|----|----|--------------------------------|

| 0  | 0  | 0                                   | 0  | 0  | 0                              |

| 0  | 1  | 0                                   | 0  | 1  | 1                              |

| 1  | 0  | 0                                   | 1  | 0  | 1                              |

| 1  | 1  | 1                                   | 1  | 1  | 1                              |

Let  $C = \{i, o, c, u\}$  be the set of functions from B into B and F be the set of all mxn matrices whose entries are functions from the set C. The elements of F are called transformations from  $B^n$  into  $B^m$ . In particular for  $U = (u_1, u_2, \ldots, u_n)^T \varepsilon B^n$ , we define the mxn transformation matrix A operating on U as

$$AU = \begin{bmatrix} a_{11} & \cdots & a_{1n} \\ \vdots & & \vdots \\ \vdots & & \vdots \\ a_{1m} & \cdots & a_{mn} \end{bmatrix} \begin{bmatrix} u_{1} \\ u_{2} \\ \vdots \\ u_{n} \end{bmatrix} = \begin{bmatrix} a_{11} & u_{1} + a_{12} & u_{2} + \cdots + a_{1n} & u_{n} \\ \vdots & \vdots & \vdots \\ a_{m1} & u_{1} + a_{m2} & u_{2} + \cdots + a_{mn} & u_{n} \end{bmatrix}$$

The set F contains an  $(n \times n)$  identity transformation  $I_n = (a_{kj})$ , where  $a_{kj} = i$  when k = j and  $a_{kj} = 0$  when  $k \neq j$ . The identity transformation

maps every vector  $X \in B^n$  into itself. The (m x n) zero transformation,  $0_{m,n} = (a_{ij})$ , is the matrix, all of whose entries are  $o \in C$ . The zero transformation maps every  $X \in B^n$  into an m-vector, all of whose elements are zero.

If A,  $B \in F$  and X,  $U \in B^n$  then AX +  $B U \in B^m$ , where addition is understood to be the Boolean OR operation on vectors in  $B^m$ .

A transformation  $T \varepsilon F$  is, in general, nonlinear. This can be easily proven by exhibiting a counter example. Let  $T:B^3 \rightarrow B^2$  be the transformation  $T(u_1, u_2, u_3)^T = (cu_1, o)^T$ . Then  $T = \begin{bmatrix} c & o & o \\ o & o & 0 \end{bmatrix}$  in matrix form. For  $\alpha$ ,  $\beta \varepsilon B$ ,

$$T(\alpha U + \beta V) = \begin{bmatrix} c \circ o \\ o \circ o \end{bmatrix} \begin{bmatrix} \alpha u_1 + \beta v_1 \\ \alpha u_2 + \beta v_2 \\ \alpha u_3 + \beta v_3 \end{bmatrix} = \begin{bmatrix} c(\alpha u_1 + \beta v_1) \\ o \end{bmatrix} = \begin{bmatrix} (c\alpha + cu_1)(c\beta + cv_1) \\ o \end{bmatrix}$$

$\neq \alpha TU + \beta TV$ .

Combinational Circuit Model

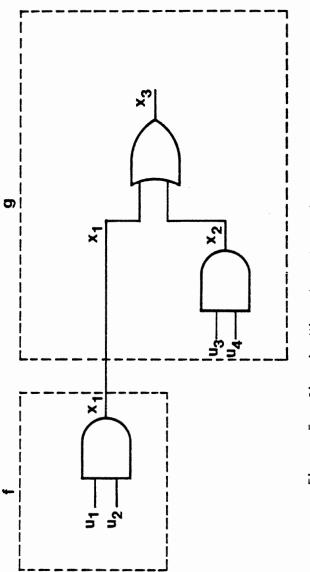

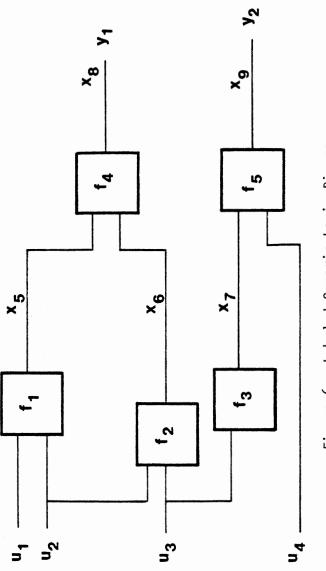

Logic circuits physically realize Boolean functions through composition of functions from the basis set {AND, OR, NOT}. The gate level logic diagram of a combinational circuit describes the interconnection of basic logic gates which represent the Boolean functions AND, OR, NOT, NAND, and NOR. Given a gate level logic diagram, we adopt the following line labeling convention: Primary inputs are labeled  $u_1, u_2, \ldots, u_n$ , and the internal lines are labeled  $x_j$ , where the subscript j must be greater than n and greater than the subscript of any line label on any path between the primary inputs and the line  $x_i$ . Figure 6 is a labeled

•

generic logic diagram where  $f_i$  represents one of the Boolean functions AND, OR, NOT, NAND, or NOR.

The logic diagram can be thought of as a graph of the chain of Boolean function compositions. For example, in Figure 6

$$x_{1} = iu_{1}$$

$$x_{2} = iu_{2}$$

$$x_{3} = iu_{3}$$

$$x_{4} = iu_{4}$$

$$x_{5} = f_{1}(x_{1}, x_{2})$$

$$x_{6} = f_{2}(x_{2}, x_{3})$$

$$x_{7} = f_{3}(x_{3})$$

$$x_{8} = f_{4}(x_{5}, x_{6})$$

$$x_{9} = f_{5}(x_{4}, x_{7})$$

where  $x_1$  through  $x_4$  represent data steps, and  $x_5$  through  $x_9$  represent computation steps. This is called a 9-step chain. (See Savage [1976] for a definition of k-step computation chains.)

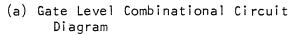

If we restrict the logic diagram to contain only gates which represent the Boolean functions NAND, OR, and NOT, the computation chain takes on a linear-looking form. The circuit in Figure 7 contains only NAND, NOT, and OR gates. The original circuit was an AND,OR circuit. The output lines of NOT gates inserted during modeling are not labeled. The computation chain of the modeled circuit is as follows:

$$x_1 = iu_1$$

$x_2 = iu_2$

$x_3 = iu_3$

DATA STEPS

$$\begin{array}{l} x_4 = cx_1 + cx_2 \\ x_5 = cx_2 + cx_3 \\ x_6 = cx_4 + cx_5 \end{array}$$

COMPUTATION STEPS

In matrix notation the set of equations is written:

where the entries in the matrices are functions from the set  $C = \{i, o, c, u\}$  of Boolean functions of one variable.

In general, the equations describing the behavior of a digital combinational logic circuit with n primary inputs  $u_1, u_2, \ldots, u_n$ ; p logic gates of the type AND, OR, NOR, NAND, NOT, whose outputs are labeled  $x_{n+1}, x_{n+2}, \ldots, x_{n+p}$ ; and m primary outputs  $y_1, y_2, \ldots, y_m$  can be expressed in the form

$$X = AX + BL$$

$Y = DX$

where  $X = (x_1, x_2, \ldots, x_{n+p})^T \varepsilon B^{n+p}$ ,  $U = (u_1, u_2, \ldots, u_n)^T \varepsilon B^n$ , and  $Y = (y_1, y_2, \ldots, y_m)^T \varepsilon B^m$ . The matrix  $A \varepsilon F$  is an (n+p, n+p) matrix which can be partitioned into submatrices.

$$A = \begin{bmatrix} 0 & | & 0 \\ n, n & | & n, p \\ \hline A & | & A \\ 1^{p, n} & | & 2^{p, p} \end{bmatrix}.$$

The matrix  $B \epsilon F$ , a (n+p,n) matrix, can also be partitioned into submatrices.

$$B = \begin{bmatrix} I_n, n \\ 0 \\ p, n \end{bmatrix}.$$

$D\epsilon F$  is an (m,n+p) matrix. Because of the labeling convention, the A matrix is lower triangular, as is the matrix  $A_2$ .

During modeling, all circuit gates are represented in terms of NAND, OR, and NOT gates to achieve the linear-looking equations. Three guestions arise:

- How difficult is it to model a circuit in terms of these gates only?

- 2. What relationship does the signal line in the model have to the actual gate level circuit description?

- 3. What effect does modeling with NAND, OR, and NOT gates have on test generation for stuck-at faults?

The first two questions will be addressed simultaneously. Figure 8 shows how easily each circuit element can be represented in terms of the NAND, OR, NOT gates. There is a one-to-one correspondence between the signal lines in the standard representation and the model representation since the output to inserted inverters are not labeled.

A test for the output of an AND (OR) gate stuck-at-1 is also a test for the output of a NAND (NOR) gate stuck-at-0. When an ATG algorithm tries to generate tests for all stuck-at-1 and stuck-at-0 faults in the

circuit model, the test derived will also test for the stuck-at-faults in the original circuit. Knowledge of the fact that ANDs are modeled with NANDs followed by inverters and NORs as ORs followed by inverters, and knowledge of the above facts concerning the relationship between stuck-at faults in the modeled circuit and the actual circuit enables a straightforward fault location and diagnosis procedure.

Figure 9 illustrates the modeling process using an exclusive-OR (XOR) gate. Two ways to model it are shown. The matrix equation associated with each model appears on the right.

To further illustrate the modeling procedure for combinational circuits, Figure 10 shows a gate level diagram of a circuit and the representation from which a transformation matrix can be written. The matrix equation is

The modeling of all logic gates in terms of NAND, OR, and NOT gates is an intermediate step between the logic circuit described with AND, OR, NOT, NAND, NOR, and XOR gates and that proposed by Thomas (1971) of using only NAND gates. While the NAND gate model can also be represented in the matrix formulation, the complexity of modeling is slightly

$y = u_1 \oplus u_2$

(b) Gate Level Transformation

larger. Figure 11 shows the OR gate and NOT (inverter) modeled as NAND gates. The matrix representations, however, have the same dimensions.

It is possible to use the idea of computation chains to model the combinational circuit and omit the data steps. When this is done, a smaller-dimensioned representation is obtained; however, it is not as useful in ATG as the one presented. For completeness, however, Figure 12 illustrates the labeling procedure and matrix representation for the same circuit as Figure 10. Note that the matrix operating on the U vector in Figure 12 is the same as the submatrix A<sub>1</sub> in the representation for Figure 10.

Before introducing the sequential circuit model, one other interesting observation is made. It is possible to represent a Boolean function in the matrix representation, independent of a gate level diagram. For example, if

$$f(u_1, u_2, u_3) = u_1 u_2 u_3' + u_2' u_3,$$

let

| $ \begin{array}{l} x_1 = u_1 \\ x_2 = u_2 \\ x_3 = u_3 \end{array} $      | DATA STEPS        |

|---------------------------------------------------------------------------|-------------------|

| $ x_4 = cx_1 + cx_2 + ix_3 $                                              | COMPUTATION STEPS |

| $\begin{array}{c} x_5 = i x_2 + c x_3 \\ x_6 = c x_4 + c x_5 \end{array}$ |                   |

an d

$y = ix_6$ .

Figure 11. NOT and OR Gates Represented in Terms of NAND Gates

•

Figure 12. Compact Matrix Formulation

In matrix form

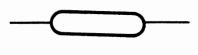

#### Sequential Circuit Model

The sequential circuit will be modeled as an iterative combinational array (Breuer and Friedman, 1976). The matrix formulation achieves a concise representation for this model. The delay symbol pictured in Figure 13 will be incorporated into the gate level diagram in feedback loops to denote the time frames (not to be confused with clock pulses in synchronous sequential circuits or with actual circuit delay).

The computation chain for the circuit of Figure 13b is

$$x_{1}(t) = u_{1}(t)$$

$$x_{2}(t) = u_{2}(t)$$

$$x_{3}(t) = cx_{1}(t) + cx_{4}(t-1)$$

$$x_{4}(t) = cx_{2}(t) + cx_{3}(t-1)$$

The computation chain is shown in matrix form on page 41. In general, a sequential circuit can be represented in the form

$$X(t) = AX(t) + BU(t) + CX(t-1)$$

$$Y(t) = DX(t)$$

| x <sub>1</sub> (t)               | ο | 0 | 0 | 0 | $\left[ x_{1}^{\prime}(t) \right]$ | [;    | 0 | [u <sub>1</sub> (t)] | 0 | 0 | 0 | 0 | $\begin{bmatrix} x_{1}(t-1) \\ x_{2}(t-1) \\ x_{3}(t-1) \\ x_{4}(t-1) \end{bmatrix}$ |

|----------------------------------|---|---|---|---|------------------------------------|-------|---|----------------------|---|---|---|---|--------------------------------------------------------------------------------------|

| x <sub>2</sub> (t)               | o | 0 | 0 | o | x <sub>2</sub> (t)                 | 0     | i | u <sub>2</sub> (t)   | 0 | о | 0 | 0 | ×2(t-1)                                                                              |

| $\left  x_{3}^{(t)} \right ^{=}$ | с | 0 | о | o | ×3(t)                              | +   o | 0 |                      | 0 | O | o | c | ×3(t-1)                                                                              |

| ×4(t)                            | 0 | с | 0 | 0 | $\left[ \times_{4}^{(t)} \right]$  | o     | 0 |                      | 0 | 0 | с | 0 | [×4(t-1)]                                                                            |

|                                  | _ |   |   | _ |                                    |       |   |                      |   |   |   |   |                                                                                      |

| $\left[ y_{1}^{(t)} \right] =$   | 0 | 0 | i | 0 | $\left[ x_{l}(t) \right]$          |       |   |                      |   |   |   |   |                                                                                      |

$\begin{bmatrix} y_{1}(t) \\ y_{2}(t) \end{bmatrix} = \begin{bmatrix} o & o & i & o \\ o & o & o & i \end{bmatrix} \begin{bmatrix} x_{1}(t) \\ x_{2}(t) \\ x_{3}(t) \\ x_{4}(t) \end{bmatrix}$

41

.

where A, B, C, and  $D\varepsilon F$ , t is an integer time step, U(t)  $\varepsilon B^{n}$ , Y(t)  $\varepsilon B^{m}$ . A and B can be partitioned as in the combinational case and the matrix C can be partitioned

$$C = \begin{bmatrix} 0_{n,n} & 0_{n,p} \\ 0_{1^p,n} & 0_{2^p,p} \end{bmatrix}$$

Figure 14 is a labeled gate level diagram of a clocked D-flip flop. The matrix representation for this synchronous sequential flip flop is shown on page 44.

#### Summary

Mathematical matrix representations which describe the behavior of digital systems have been derived. The gate level logic diagram is represented in terms of NAND, OR, and NOT gates and a k-step computation chain is formed. The coefficients of each variable in the computation chain is a Boolean function from the set  $C = \{o, i, c, u\}$ . Sequential circuits are represented as iterative combinational arrays and represented in the matrix format through the introductions of a delay element in each feedback loop. Mathematically, the delay is represented by an integer, t, which corresponds to the iteration number.

Figure 14. Clocked D-Flip Flop

| $\left[ x_{1}(t) \right]$                | 0 | 0 | 0 | 0 | 0 | x <sub>1</sub> (t) |   | ſ | 0 | - | u <sub>1</sub> (t) |   | 0 | 0 | 0 | o | 0 | [× <sub>1</sub> (t-1)]                                                 |

|------------------------------------------|---|---|---|---|---|--------------------|---|---|---|---|--------------------|---|---|---|---|---|---|------------------------------------------------------------------------|

| x <sub>2</sub> (t)                       | ο | 0 | 0 | o | 0 | ×2(t)              |   | 0 | i |   | u2(t)              |   | 0 | 0 | o | 0 | 0 | $\begin{bmatrix} x_{1}(t-1) \\ x_{2}(t-1) \\ x_{3}(t-1) \end{bmatrix}$ |

| $ x_3(t)  =$                             | с | с | 0 | 0 | 0 | ×3(t)              | + | 0 | 0 |   |                    | + | 0 | 0 | 0 | 0 | 0 | ×3(t-1)                                                                |

| ×4(t)                                    | 0 | i | 0 | 0 | 0 | ×4(t)              |   | 0 | 0 |   |                    |   | 0 | 0 | 0 | 0 | с | ×4(t-1)                                                                |

| × <sub>4</sub> (t)<br>× <sub>5</sub> (t) | 0 | 0 | с | с | 0 | × <sub>5</sub> (t) |   | 0 | 0 |   |                    |   | 0 | 0 | o | o | 0 | $\begin{bmatrix} x_4(t-1) \\ x_5(t-1) \end{bmatrix}$                   |

$$\begin{bmatrix} y_{1}(t) \\ y_{2}(t) \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 & i \\ 0 & 0 & 0 & 0 & c \end{bmatrix} \begin{bmatrix} x_{1}(t) \\ x_{2}(t) \\ x_{3}(t) \\ x_{4}(t) \\ x_{5}(t) \end{bmatrix}$$

#### CHAPTER IV

## MODEL CHARACTERISTICS AND EXTENSIONS

## Introduction

The logical behavior of digital systems is a dominant feature of digital circuits when generating tests for logical faults. Because it is necessary in automatic test generation to derive an input to the circuit which allows one to observe a fault on an internal signal line at a primary output, most fault-dependent algorithms have taken the path sensitization approach. Locating and tracing specific paths through the circuit requires some topological information. Both the logic behavior and topological information must be presented in a concise, efficient manner that is amenable to computer storage and manipulation.

Characteristics of the matrix model of digital circuits as they relate to the topology of the system will be given in this chapter. Other features of the circuit contained in the matrix description will be pointed out, and the relationship between the size of the describing matrix and circuit size will be presented. The original model will be extended to include variables associated with each fork in a fanout path in the circuit so that complete coverage of single permanent stuck-at faults can be achieved.

Combinational Circuit Topology

A combinational circuit can be thought of as a directed graph whose

vertices consist of the primary inputs and logic gates and whose edges are represented by the signal lines. A directed graph corresponding to Figure 10(a) is given in Figure 15. The adjacency matrix associated with a directed graph G having n vertices and no parallel edges is an  $n \times n$  binary matrix  $A_{G} = (a_{ij})$  such that

- a<sub>ij</sub> = 1 if there is an edge directed from the ith vertex to the jth vertex, and

- = 0 otherwise

(Deo, 1974). The adjacency graph for Figure 15 is

|                  |                | u۱ | <sup>u</sup> 2        | u'<br>3 | Gl | <sup>G</sup> 2 | G <sub>3</sub> |  |

|------------------|----------------|----|-----------------------|---------|----|----------------|----------------|--|

|                  | u۱             | 0  | 0                     | 0       | 1  | 0              | 0              |  |

|                  | <sup>u</sup> 2 | 0  | 0                     | 0       | 1  | 1              | 0              |  |

| ۰                | <sup>u</sup> 3 | 0  | 0                     | 0       | 0  | 1              | 0              |  |

| A <sub>G</sub> = | G۱             | 0  | 0                     | 0       | 0  | 0              | 1              |  |

|                  | G2             | 0  | 0                     | 0       | 0  | 0              | 1              |  |

|                  | G <sub>3</sub> | 0  | 0<br>0<br>0<br>0<br>0 | 0       | 0  | 0              | 0              |  |

It can be seen by inspection that the transpose of  $A_{G}$  and the A matrix for Figure 10 have corresponding entries. In particular, every nonzero entry in A corresponds to a nonzero entry in the transpose of  $A_{G}$ . This direct correspondence indicates that the network connection (topological) information is contained in the A matrix of the model. Since the network interconnection information is present in A, the fanin (fanout) of the individual vertices (primary inputs and logic gates) can be computed by counting the number of nonzero entries in the row (column) associated with that vertex.

In particular, define  $r_i$  equal to the number of nonzero entries in row i of the A matrix and  $k_j$  equal to the number of nonzero entries in column j of the matrix A. Then  $r_i$  is the fanin of the gate with output labeled  $x_i$ , and  $k_j$  is the fanout of the gate with output labeled  $x_j$  or of a primary input  $u_j$ . The vectors  $R = (r_i)$  and  $K = (k_j)^T$  will be referred to as the fanin and fanout vectors, respectively.

The famin vector for the network of Figure 15 is  $R = (0,0,0,2,2,2)^{T}$ . The famout vector is  $K = (1,2,1,1,1,0)^{T}$ .

## Combinational Circuit Matrix Complexity

Define the complexity,  $\gamma$ , of a matrix to be the number of nonzero elements in the matrix. In the adjacency matrix of a graph, G, the integer  $\gamma$  equals the number of edges in G. The matrix parameter  $\gamma$  is related to the amount of computer storage necessary to represent the matrix.

For conciseness, the system of equations

X = AX + BU

will be rewritten as

$$X = M \begin{bmatrix} U \\ X_p \end{bmatrix}$$

where

$$M = \begin{bmatrix} I & I & 0 \\ -A_1 & I & A_2 \end{bmatrix}$$

and

$$X_{p} = (x_{n+1}, x_{n+2}, \dots, x_{p})$$

.

This formulation takes advantage of the fact that  $x_i = u_i$  for i = 1, 2, ..., n. For example, for the circuit of Figure 10,

$$M = \begin{bmatrix} i & 0 & 0 & 0 & 0 & 0 \\ 0 & i & 0 & 0 & 0 & 0 \\ 0 & 0 & i & 0 & 0 & 0 \\ c & c & 0 & 0 & 0 & 0 \\ 0 & i & i & 0 & 0 & 0 \\ 0 & 0 & 0 & c & c & 0 \end{bmatrix}$$

The matrix M will be referred to as the defining matrix for the system since it contains both the behavioral and topological information. It can be easily seen that the number of nonzero elements in M

$$\gamma = n + \sum_{n+1}^{n+p} r_i = n + \sum_{j=1}^{n+p} k_j .$$

The lower limit of the first summation is n+1 because the first n rows of A contain only the null element o. The complexity measure,  $\gamma$ , corresponds to the number of primary inputs plus the sum of all fanin (fanout) connections in the circuit including primary outputs. For the circuit of Figure 10,  $\gamma = 3 + 6 = 9$ . The upper limit on  $\gamma$  is  $\gamma_{max} = n + \min \{p \cdot (r_i)_{max}, (n+p)(k_i)_{max}\}$ .

A measure of the sparsity of a matrix is given by its density. The density is defined to be the number of nonnull elements divided by the total number of matrix elements. The density of M is

$$d = \frac{\gamma}{(n+p)^2}$$

The density of the defining matrix M for Figure 10 is d = 9/36 = 0.25.

## Model Extensions

To completely test a combinational circuit for single permanent stuck-type faults, fanout on primary input signals and at the output of internal gates must be considered. Figure 16, an example from Breuer and Friedman (1976), illustrates the necessity to differentiate between the different forks on a signal path. The input signal  $u_2$  fans out to gates  $G_1$  and  $G_2$ . This signal may appear normal at one gate and faulty on the other. If  $u_2$  is stuck-at-1, then both a and b are also 1 and the output y becomes  $u_2 + u_3$ . However, the fault in which the input lead a to  $G_1$  is stuck-at-1 but the signal b still corresponds to  $u_2$  results in the output  $y = u_1 + u_2u_3$ . Similarly, if the input lead b to  $G_2$  is stuck-at-1 while signal a still corresponds to  $u_2$ ,  $y = u_1u_2 + u_3$ .

This situation can be included in the model by labeling each fork in a fanout path. With this expansion, note that p is no longer equal to the number of gates in the circuit, but is equal to the number of gates plus the number of newly labeled forks. Figure 17 illustrates the labeling procedure for the circuit in Figure 16. The computation chain becomes

$$x_{1} = u_{1}$$

$$x_{2} = u_{2}$$

$$x_{3} = u_{3}$$

$$x_{4} = x_{2}$$

$$x_{5} = x_{2}$$

$$x_{6} = cx_{1} + cx_{4}$$

$$x_{7} = cx_{3} + cx_{5}$$

$$x_{8} = cx_{6} + cx_{7}$$

>

Figure 17. Labeling Extended to Forks in a Fanout Path

.

In matrix form

|   | [×] |   | [ i | 0 | 0 | 0 | 0 | 0 | 0 | 0  | u j            |  |

|---|-----|---|-----|---|---|---|---|---|---|----|----------------|--|

|   | ×2  |   | 0   | i | 0 | 0 | 0 | 0 | 0 | 0  | <sup>u</sup> 2 |  |

| , | ×3  |   | 0   | 0 | i | 0 | 0 | 0 | 0 | 0  | <sup>u</sup> 3 |  |

|   | ×4  |   | 0   | i | 0 | 0 | 0 | 0 | 0 | 0  | ×4             |  |

|   | ×5  | = | 0   | i | 0 | 0 | 0 | 0 | 0 | 0  | ×5             |  |

|   | ×6  |   | с   | 0 | 0 | с | 0 | 0 | 0 | 0  | ×6             |  |

|   | ×7  |   | 0   | 0 | с | 0 | с | 0 | 0 | 0  | ×7             |  |

|   | ×8  |   | 0   | 0 | 0 | 0 | 0 | с | с | 0  | ×8_            |  |

|   | [y] | = | [0  | 0 | 0 | 0 | о | 0 | 0 | ;] | Х              |  |

The dimension of M is increased by 2 rows and 2 columns, the density of M is 0.17 compared to d = 0.25 before the extension, and  $\gamma$  = 11 compared to  $\gamma$  = 9 prior to the extension. It is expected that when more details of the circuit are modeled, the complexity of the model will increase.

The fanout vector  $K = (1,2,1,1,1,1,1,0)^T$  indicates explicitly that  $x_2 = u_2$  is the line which forks. In general, when  $k_j > 1$ , the defining matrix will contain  $\sum_{j=1}^{n+p} k_j$ , more elements than the nonextended matrix. The maximum increase in complexity,  $\Delta_{max}$ , due to extending the model is equal to  $(k_j)_{max}$  times the number of gates plus primary inputs. The maximum complexity of the extended model is equal to the maximum complexity of the extended model is equal to the maximum complexity of the plus  $\Delta_{max}$ . This quantity is linear in the number of gates plus primary inputs.

## Sequential Circuit Topology

The adjacency matrix for the circuit in Figure 13 (not including

the delay symbols as vertices) is

|            | Го | 0 | 1 | 0] |  |

|------------|----|---|---|----|--|

| <u>۸ –</u> | 0  | 0 | 0 | 1  |  |

| ∽g −       | 0  | 0 | 0 | 1  |  |

|            | Lo | 0 | 1 | 0  |  |

In the model, topological (directed interconnections) information is contained in both A and C. The entries in the transpose of  $A_{G}$  correspond to entries in A + C, where addition in C is defined by the table:

| + | 0 | i | с | u |

|---|---|---|---|---|

| 0 | ο | i | с | u |

| i | i | i | u | u |

| с | с | u | с | u |

| u | u | u | u | u |

and matrix addition in F is defined as in ordinary matrix algebra, i.e., A + B =  $(a_{ij}) + (b_{ij}) = (a_{ij} + b_{ij})$ .

In particular, A + C for the model of Figure 13 is given by

$$A + C = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ c & 0 & 0 & c \\ 0 & c & c & 0 \end{bmatrix}$$

For sequential circuits, the fanin (fanout) vectors are found by counting the number of nonzero elements in the rows (columns) of A + C. The fanin vector for the above example is  $R = (0,0,2,2)^{T}$  and the fanout vector is  $K = (1,1.1,1)^{T}$ .

Sequential Circuit Matrix Complexity

The defining matrix for a sequential circuit is defined to be

where the submatrices  $A_1$ ,  $A_2$ , and  $C_2$  are submatrices of A and C. The general equation can now be expressed as

$$X(t) = M \begin{bmatrix} U \\ X_{p}(t) \\ X_{p}(t-1) \end{bmatrix}$$

where  $X_p = (x_{n+1}, x_{n+2}, \dots, x_{n+p})$ . For the circuit of Figure 14,

|     | [ i | 0 | о | о | 0 | 0 | 0 | [ہ |  |

|-----|-----|---|---|---|---|---|---|----|--|

|     | 0   | i | 0 | 0 | 0 | 0 | 0 | 0  |  |

| M = | c   | c | 0 | 0 | 0 | 0 | 0 | 0  |  |

|     | 0   | i | о | 0 | о | 0 | о | с  |  |

|     | Lo  | 0 | с | с | 0 | 0 | 0 | ړه |  |

and the equation is written as

For the defining matrix, M, the complexity of the matrix is defined identically as for the combinational defining matrix. The complexity of M above is  $\gamma = 2 + 6 = 8$ . The density is again defined as the number of nonzero elements divided by the total number of elements in the matrix. In general, for a sequential circuit,

$$d = \frac{\gamma}{(n+p)(n+2p)}$$

In situations where lines fan out in a sequential circuit, the model can be extended as in the combinational case.

#### Summary

The matrix representation for both combinational and sequential circuits contains the network interconnection information such as node adjacency, fanin, and fanout. The number of elements in the defining matrix of a system corresponds to the number of primary inputs plus the sum of all fanin (fanout) connections in the circuit, including primary outputs and feedback lines in sequential circuits.

### CHAPTER V

# A MATRIX APPROACH TO AUTOMATIC TEST GENERATION

## Introduction

In this chapter, the matrix model of digital systems forms the framework in which the path sensitization approach of Roth is carried out. Behavioral and topological features of the model enable tests to be generated for several faults at once. When choices arise as to line assignments during path sensitization, the model contains enough information to make the assignments intelligently, thus reducing the requirement for backtracking. Self-initializing test sequences for sequential circuits can be generated and untestable faults flagged.

The application of the model in the context of automatic test generation using the Boolean difference method is also exhibited. An algorithm for deriving Boolean equations for each internal line in terms of primary inputs is presented. The Boolean difference of sums of complemented and uncomplemented variables is very straightforward. Because the matrix model represents lines in this manner, differences are quickly and easily calculated when needed, thus saving the computer storage space once necessary for storing the differences.

### Path Sensitization Using the Matrix Model

The matrix model introduced in Chapters III and IV represents each internal line in terms of the sum (OR) of complemented and/or uncomplemented

variables. The variables may be either primary inputs or internal lines. The flow of behavioral information proceeds through the matrix model from inputs to outputs by data steps followed by computation steps.

Line justification and error propagation for the Boolean OR operation is reviewed again at this point for reference. If  $x_4 = x_2 + x'_3$ , then  $x_4 = 1$  can be justified by the assignment  $x_2 = 1$  or  $x_3 = 0$ . To justify  $x_4 = 0$ , the assignment  $x_2 = 0$  and  $x_3 = 1$  is required. To propagate the fault  $x_2 = D$  to line  $x_4$  requires that  $x'_3 = 0$  ( $x_3 = 1$ ). To propagate the fault  $x_3 = D$  to line  $x_4$  ( $x_4 = D'$ ), it is necessary that  $x_2 = 0$ .

In general, to justify a 1, at least one uncomplemented summand must be 1, or at least one complemented variable in the sum must be 0. To justify a 0, all uncomplemented summands must be 0 and all complemented summands, 1. To propagate an error signal (D or D<sup>1</sup>), each uncomplemented variable in the sum must be 0 and each complemented variable, 1.

The path sensitization approach outlined in Chapter II involved first deciding on a fault and fault site. The fault-free value of the faulty variable is immediately justified at a primary input and the error signal is then propagated to a primary output. The last step involves the consistent justification of line values assigned during the justification and propagation steps.

The manner in which this procedure is carried out within the matrix model can best be understood by illustration. Examples showing the basic path sensitization method for combinational circuits, multiple path sensitization, the undetectable fault case, and self-initialization

procedures for sequential circuits are presented. A flow diagram generalizing the procedure follows the illustrations.

The combinational circuit of Figure 18 has matrix representation:

| [×1            |   | [i o o o o o o o o o o ] [u, ]          |       |

|----------------|---|-----------------------------------------|-------|

| ×2             |   | 0 i 0 0 0 0 0 0 0 0 0   u <sub>2</sub>  |       |

| ×3             |   | 0010000000   u <sub>3</sub>             |       |

| ×4             |   | ссооооооо   × <sub>4</sub>              |       |

| × <sub>5</sub> |   | 0 C C O O O O O O O O X5                |       |

| ×6             | = | ooooioooooo x <sub>6</sub>              | (5.1) |

| ×7             |   | 0000i000000 x <sub>7</sub>              |       |

| ×8             |   | cocoooooo x <sub>8</sub>                |       |

| ×9             |   | 0 c o c o c o o o o o x <sub>g</sub>    |       |

| ×10            |   | 0 0 C 0 0 0 C C 0 0 0   × <sub>10</sub> |       |

| [×11           |   | [ • • • • • • • • • • • • • • • • • • • |       |

A test will first be generated for line  $x_4$  stuck-at-0. As in the D-algorithm, the letter D will indicate the value of a line that is 1 in a fault-free circuit, but has taken the value 0 due to the presence of a fault (D = 1/0).

On the right-hand side of Equation (5.1), replace  $x_4$  by the value D. This substitution is labeled as Step 1 in Equation (5.2).

Column 4 indicates that line  $x_4$  connects to line  $x_9$  and the error propagation rules indicate that each of the other nonnull variables in row  $x_9$  must take the value 1. These values ( $x_2 = u_2 = 1$ ,  $x_6 = 1$ , and  $x_9 = D^1$ ) are entered in the right-hand vector and labeled Step 2.

The error signal has been propagated to line  $x_9$ . Column 9 indicates that line  $x_9$  connects to primary output  $x_{11}$  and the error propagation rules indicate that the nonnull variables,  $x_{10}$ , in row 11, take the value 1. These values ( $x_{11}$  = D and  $x_{10}$  = 1) are entered in the right-

hand vector and labeled Step 3. Due to the nature of the propagation procedure, the variables  $x_9$  and  $x_{11}$  will not require justification and can be removed from the list of variables to be justified.

The justification procedure now begins. The signal  $x_4 = 1$  (the fault-free value on the faulty signal line) is justified if  $x_1 = 0$  or  $x_2 = 0$ . Since  $x_2 = 1$  has been previously assigned, we choose  $x_1 = 0$ . This assignment is labeled Step 4.

To ensure consistency, the implications of this assignment are made immediately. Column 1 indicates that  $x_1$  connects to  $x_4$  and  $x_8$ . Since  $x_1 = 0$  and the entry in row 8, column 1 is c, then  $x_8$  must equal 1. This implication is entered as Step 5. The implication assignment of  $x_8 = 1$  implies that  $x_8$  has been justified (since  $x_1 = 0$ ); thus  $x_8$  can be removed from the list of variables which need to be justified.

The justification procedure is continued by justifying  $x_6 = 1$ . The justification rules indicate that  $x_5 = 1$  (Step 6).

The implication of this assignment is made by investigating column 5 which leads to  $x_7 = 1$  (Step 7).  $x_7$  can now be removed from the list of variables requiring justification. Only  $x_{10}$  and  $x_5$  remain to be justified.

The value  $x_{10} = 1$  is now justified. The rules indicate that either  $x_3 = 0$ ,  $x_7 = 0$ , or  $x_8 = 0$ . Since  $x_7 = x_8 = 1$  has already been assigned, the zero value is given to  $x_3$  (Step 8). Implications of the assignment  $x_3 = 0$  indicate that  $x_5 = 1$ ,  $x_8 = 1$ , and  $x_{10} = 1$ . It is noted that  $x_8 = x_{10} = 1$  is consistent with previous assignments, and  $x_5$  is removed from the list requiring justification.

The test derivation is complete. The test T =  $(u_1, u_2, u_3) = (x_1, x_2, x_3) = (0, 1, 0)$  is a test for  $x_4 = D$  (i.e.,  $x_4$  stuck-at-0). In

addition, it will detect the faults  $x_9 = D'$  and  $x_{11} = D$ .

Column No. = 1 2 3 4 5 6 7 8 9 10 11 T

| [x, ]          | 1   | ٦i | 0 | 0 | ο | 0          | 0 | ο | ο | 0 | о | ٦ | Í | 07 | Step | 4 |  |       |

|----------------|-----|----|---|---|---|------------|---|---|---|---|---|---|---|----|------|---|--|-------|

| × <sub>2</sub> |     |    |   |   |   |            |   |   |   | 0 |   | 0 |   | 1  | Step |   |  |       |

| ×3             |     | 0  | 0 | i | 0 | 0          | о | 0 | 0 | 0 | 0 | 0 |   | 0  | Step | 8 |  |       |

| ×4             |     | c  | с | 0 | 0 | 0          | 0 | 0 | 0 | 0 | 0 | 0 |   | D  | Step | 1 |  |       |

| × <sub>5</sub> |     | о  | с | с | 0 | 0          | 0 | 0 | 0 | 0 | 0 | 0 |   | 1  | Step | 6 |  |       |

| × <sub>6</sub> | . = | 0  | 0 | 0 | 0 | <b>i</b> - | 0 | о | 0 | о | 0 | 0 |   | 1  | Step | 2 |  | (5.2) |

| × <sub>7</sub> |     | 0  | 0 | 0 | 0 | i          | о | 0 | 0 | 0 | 0 | 0 |   | 1  | Step | 7 |  |       |

| ×8             |     | c  | 0 | с | 0 | 0          | 0 | 0 | 0 | 0 | 0 | 0 |   | 1  | Step | 5 |  |       |

| ×9             |     | 0  | с | 0 | с | 0          | с | 0 | 0 | о | 0 | 0 |   | D' | Step | 2 |  |       |

| ×10            |     | 0  | 0 | с | 0 | 0          | 0 | С | с | 0 | 0 | 0 |   | 1  | Step | 3 |  |       |

| ×11            | ·   | 0  | 0 | 0 | 0 | 0          | 0 | 0 | 0 | с | С | 0 |   | D  | Step | 3 |  |       |

|                | •   | -  |   |   |   |            |   |   |   |   |   | _ |   |    |      |   |  |       |

In the above example, we were "lucky" because in instances where choices had to be made, the values could be uniquely determined (Steps 4 and 8). The next example illustrates the procedure when choices must be made.

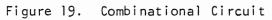

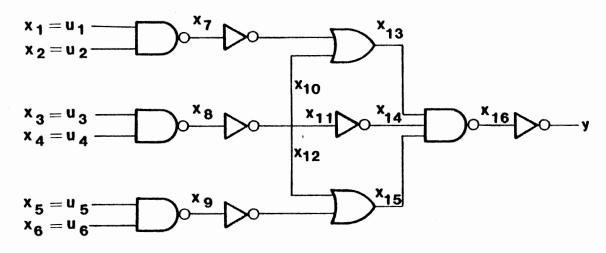

Figure 19 is a small combinational circuit whose matrix representation is given by Equation (5.3) (see page 63).

Derive a test for  $x_9$  stuck-at-0 (Step 1 in Equation [5.4]). Propagate the fault  $x_9 = D$ . Column 9 indicates that  $x_9$  connects to  $x_{12}$  and the fault is propagated if  $x_8 = 1$  (Step 2). Propagate  $x_{12} = D^{1}$ . Column 12 indicates that  $x_{12}$  connects to the primary output variable  $x_{13}$  and the fault is propagated if  $x_{10} = 1$  and  $x_{11} = 0$  (Step 3).

The justification procedure begins by justifying  $x_9 = 1$ . This is true if  $x_1 = 0$  or  $x_6 = 0$ . Which should we choose? Column 1 indicates that  $x_1$  fans out to line  $x_{10}$  as well as  $x_9$ . Check to see if  $x_1 = 0$ would interfere with the value already assigned to  $x_{10}$ . It does not; in fact, it will justify  $x_{10} = 1$ . Therefore, the assignment  $x_1 = 0$  is

62

)

| [× <sub>1</sub> ] |        | Γi | 0 | 0 | 0 | 0 | о | 0 | 0 | 0 | 0 | 0 | 0 | 0  | [u]            |  |

|-------------------|--------|----|---|---|---|---|---|---|---|---|---|---|---|----|----------------|--|

| ×2                |        | 0  | i | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | <sup>u</sup> 2 |  |

| ×3                |        | 0  | 0 | i | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | <sup>u</sup> 3 |  |

| ×4                |        | 0  | 0 | 0 | i | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | u <sub>4</sub> |  |

| × <sub>5</sub>    |        | 0  | 0 | 0 | 0 | i | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | <sup>u</sup> 5 |  |

| ×6                | н<br>1 | 0  | 0 | 0 | 0 | 0 | i | 0 | 0 | 0 | 0 | 0 | 0 | 0  | <sup>u</sup> 6 |  |

| × <sub>7</sub>    | =      | 0  | 0 | 0 | 0 | 0 | 0 | i | 0 | 0 | 0 | 0 | 0 | 0  | <sup>u</sup> 7 |  |

| ×8                |        | 0  | с | 0 | 0 | 0 | 0 | с | 0 | 0 | 0 | 0 | 0 | 0  | ×8             |  |

| ×9                |        | с  | 0 | 0 | 0 | 0 | с | 0 | 0 | 0 | 0 | 0 | 0 | 0  | ×9             |  |

| ×10               |        | с  | 0 | с | 0 | 0 | с | 0 | 0 | 0 | 0 | 0 | 0 | 0  | ×10            |  |

| ×11               |        | 0  | 0 | с | с | с | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | ×11            |  |

| ×12               |        | 0  | 0 | 0 | 0 | 0 | 0 | 0 | с | с | 0 | 0 | 0 | 0  | ×12            |  |

| [×13]             |        | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | с | i | с | 0_ | ×13_           |  |

ż.

(5.3)

made. It turns out in this case that the assignment  $x_6 = 0$  is also valid because column 6 indicates that  $x_6$  also connects to  $x_{10}$  as well as  $x_9$ , and the same argument would hold for assigning it the value 0. Once a value that "works" is found, however, the search is abandoned. Therefore, we assign the value  $x_1 = 0$  (Step 4) with no fear of conflicts later.

Next justify  $x_8 = 1$ . A choice between  $x_2 = 0$  or  $x_7 = 0$  exists. Column 2 indicates that  $x_2$  only fans out to  $x_8$  and its assignment will not affect any other variable. Hence, we make the assignment  $x_2 = 0$ (Step 5).

Next justify  $x_{11} = 0$ . We have no choice here. We must assign  $x_3 = x_4 = x_5 = 1$  (Step 6).

Since no other unjustified values remain, the test is complete. The unassigned inputs,  $u_6$  and  $u_7$ , are treated as "don't care" variables. The test  $(u_1, u_2, u_3, u_4, u_5, u_6, u_7) = (0, 0, 1, 1, 1, x, x)$  detects the faults  $x_9$  and  $x_{13}$  stuck-at-0 and  $x_{12}$  stuck-at-1.

Column No. = 1 2 3 4 5 6 7 8 9 10 11 12 13 T

| [× <sub>1</sub> ] |   | ۲i | 0 | 0 | 0 | 0 | 0 | о | 0 | 0 | 0 | о | 0 | 0 | 0  | Step | 4 |       |   |

|-------------------|---|----|---|---|---|---|---|---|---|---|---|---|---|---|----|------|---|-------|---|

| ×2                |   | 0  | i | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | Step | 5 |       |   |

| ×3                |   | 0  | 0 | i | 0 | 0 | 0 | 0 | 0 | 0 | о | 0 | 0 | о | 1  | Step | 6 |       |   |

| ×4                |   | 0  | 0 | 0 | i | 0 | 0 | 0 | 0 | 0 | о | о | 0 | 0 | 1  | Step | 6 |       |   |

| × <sub>5</sub>    |   | 0  | 0 | 0 | 0 | i | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1  | Step | 6 |       |   |

| ×6                |   | 0  | 0 | 0 | 0 | 0 | i | 0 | 0 | 0 | 0 | 0 | 0 | 0 |    |      |   |       |   |

| × <sub>7</sub>    | = | 0  | 0 | 0 | 0 | 0 | 0 | i | 0 | 0 | 0 | 0 | 0 | 0 |    |      |   | (5.4) | ) |

| ×8                |   | 0  | с | 0 | 0 | 0 | 0 | с | 0 | 0 | 0 | 0 | 0 | 0 | 1  | Step | 2 |       |   |

| ×9                |   | c  | 0 | 0 | 0 | 0 | с | 0 | 0 | 0 | 0 | 0 | 0 | 0 | D  | Step | 1 |       |   |

| ×10               |   | c  | 0 | с | 0 | 0 | с | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1  | Step | 3 |       |   |

| ×11               |   | 0  | 0 | с | с | с | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | Step | 3 |       |   |

| ×12               |   | 0  | 0 | 0 | 0 | 0 | 0 | 0 | с | с | 0 | 0 | 0 | 0 | D' | Step | 2 |       |   |

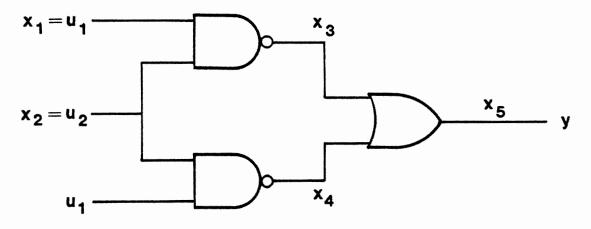

| _×13_             |   | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | с | i | с | 0 | D  | Step | 3 |       |   |