# IMPACTS OF CMOS SCALING ON THE ANALOG DESIGN

## By

## **XUNYU ZHU**

Bachelor of Engineering University of Science and Technology Beijing Beijing, China 1995

Master of Engineering University of Science and Technology Beijing Beijing, China 1998

> Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY July, 2005

# IMPACTS OF CMOS SCALING ON THE ANALOG DESIGN

| Thesis Approved:             |

|------------------------------|

|                              |

| Dr. Chris Hutchens           |

| Thesis Advisor               |

| Dr. Louis G. Johnson         |

|                              |

| Dr. Yumin Zhang              |

|                              |

| Dr. Jack Cartinhour          |

|                              |

| Dr. A. Gordon Emslie         |

| Dean of the Graduate College |

#### **ACKNOWLEDGMENTS**

The completion of this dissertation marks the end of my formal education. Throughout my life, I have been unconditionally and lovingly supported by numerous people. At this moment, I will take this opportunity to express my sincere gratitude to each and every one who have supported and loved me all along.

First and foremost, I sincerely would like thank my parents for their unconditional love and support throughout my life. Their concern and caring always extends to the deepest of my heart. Six years in the U.S., I would not able to achieve this milestone of my life without expressing my sincere gratitude to my Dad and my Mom.

Especially, I would like to express my deep appreciation to my wife, Xuehan Zhang, who has mentally encouraged me in all aspects of my life all these years. Her encouragement and support were the driving force for the write-up of this dissertation.

Living in Mixed-Signal VLSI Lab has definitely been a lot of fun, and an unforgettable part of my experience. I probably leaned as much in the MSVLSI as I did in the classroom. I would like to thank all the members of the MSVLSI past and present, especially Dr. Liu. He taught me everything from the basic schematic drawing to using test instruments. Narendra, did you still remember the days you slept on the floor of the

lab? I'll never forget you guys, Sameer, Jianning, Venket, Ansuhman, Vinay, Vijay, Bharath, Srinivasan, Ira, and Prasanna.

I would also like to thank the faculty of the ECEN Department at OSU, especially Dr. Louis G. Johnson, Dr. Yumin Zhang, and Dr. Jack Cartinghour of Electrical Engineering Technology for being on my Graduate Committee. I am also indebted to Dr. Weili Zhang who has helped me numerous times in the dicing and bonding room. In addition, I am grateful to Space and Warfare (SPAWAR) Systems Command (formerly NRaD), San Diego, CA for its support of this project.

Finally, I would like to thank my advisor, Dr. Chris Hutchens. I appreciate all of the opportunities and assistance he has provided me over the past six years from the English grammar to the design knowledge. His numerous guidance and advice have deeply enhanced my chances for success at OSU and my subsequent career and life. Thank you!

# TABLE OF CONTENTS

| Chapter                                                    | Page          |

|------------------------------------------------------------|---------------|

| Chapter 1                                                  | 1             |

| Introduction                                               | 1             |

| 1.1 Background                                             | 1             |

| 1.2 Research goals                                         | 3             |

| 1.3 Organization                                           | 4             |

| Chapter 2                                                  | 5             |

| Challenges to the Analog Design with CMOS Scaling          | 5             |

| 2.0 Introduction to the CMOS scaling                       | 5             |

| 2.1 Challenges to the analog design in the scaling process | 8<br>11<br>21 |

| 2.2 Promising new device — FinFET                          | 24            |

| Chapter 3                                                  | 30            |

| CMOS Scaling Affects to the Analog Design                  | 30            |

| 3.0 Introduction                                           | 30            |

| 3.1 CMOS scaling impacts to the analog design              | 30            |

| 3.2 Power settling product efficiency                      | 38            |

| 3.3 Analog scaling rule                                    | 46            |

| 3.4 Conclusion                                             | 48            |

| Chapter 4                                                  | 49            |

| Power Efficiency Analysis of OTA Architecture              | 49            |

| 4.0 Introduction                                           | 49            |

| 4.1 Introduction of the SC circuit               | 52  |

|--------------------------------------------------|-----|

| 4.2 Folded-cascode OTA                           | 54  |

| 4.3 Two stage miller compensation OTA            | 60  |

| 4.4 Nested gain-boosting cascode OTA             | 65  |

| 4.5 Nested G <sub>m</sub> -C compensation OTA    | 67  |

| 4.5 Nested cascode miller compensated (NCMC) OTA |     |

| 4.6 Conclusion                                   |     |

| Chapter 5                                        | 76  |

| Low-Voltage Low-Power Pipelined ADC Design       | 76  |

| 5.1 Introduction to pipelined ADC                | 76  |

| 5.2 Accuracy requirements                        | 77  |

| 5.2.1 OTA gain error                             | 77  |

| 5.2.2 OTA settling error                         |     |

| 5.2.3 Components mismatch errors                 |     |

| 5.2.4 Thermal noise                              |     |

| 5.3 Stage scaling                                |     |

| 5.4 Modeling pipelined ADC in Simulink           |     |

| 5.4.1 Pipelined ADC Simulink library overview    |     |

| 4.2 Pipelined ADC components                     |     |

| 5.5 Design example                               |     |

| 5.5.1 Specifications of the pipelined ADC        |     |

| 5.5.2 2-bit/stage architecture                   |     |

| 5.5.3 Nested cascode OTA                         |     |

| 5.5.4 boot-strap clock generator                 |     |

| 5.5.5 Comparator                                 | 107 |

| 5.6 Summary                                      | 109 |

| Chapter 6                                        | 111 |

| Conclusion and Future Work                       | 111 |

| 6.1 Conclusion                                   | 111 |

| 6.2 Pagammandad futura wark                      | 112 |

# LIST OF FIGURES

| Figure                                                                                                      | Page                |

|-------------------------------------------------------------------------------------------------------------|---------------------|

| Figure 1.1 The block diagram of a typical wireless application                                              | 2                   |

| Figure 2.1 ITRS roadmap acceleration continues — gate length trends                                         | 7                   |

| Figure 2.2 Component of the gate leakage current.                                                           | 12                  |

| Figure 2.3 Measured and simulated I <sub>G</sub> -V <sub>G</sub> characteristics under inversion condition  |                     |

| the nMOSFET's. The dotted line indicates the 1 A/cm <sup>2</sup> limit for leakage current                  |                     |

| 22]                                                                                                         |                     |

| Figure 2.4 The dashed lines represent the DIBL leakage and the solid one represent                          | ent the             |

| gate leakage                                                                                                |                     |

| Figure 2.5 The sub-threshold leakage current, where $V_{DS}=1V$ , m=1.1, $\mu$ =300 cm                      |                     |

| T=300K.                                                                                                     |                     |

| Figure 2.6 Leakage current in the sample and hold.                                                          |                     |

| Figure 2.7 Maximum off-state leakage current versus sampling frequency, ass                                 |                     |

| $V_{\text{signal(rms)}}=1V$ , sampling frequency duty =0.5, $T=300K$ .                                      | _                   |

| Figure 2.8 Supply voltage and threshold voltage scale with the channel length [10].                         |                     |

| Figure 2.9 The 3-D structure of the FinFET.                                                                 |                     |

| Figure 2.10 The electron micrograph of the FinFET, whose width is 50nm, len                                 |                     |

| 35nm [SPAWAR, San Diego].                                                                                   | _                   |

| Figure 2.11 Short-channel effect in bulk, thin-film SOI (TFSOI) and FinFET n-cl                             |                     |

| devices                                                                                                     |                     |

| Figure 2.12 The $I_{DS}$ vs. $V_{GS}$ curve biasing in the low $V_{DS}$ =25mVand high $V_{DS}$ =0.5V        |                     |

| dash lines are projected I <sub>DS</sub> when using Mo doped gate to raise the threshold vo                 |                     |

|                                                                                                             | _                   |

| Figure 2.13 Unit current gain of the 80nm length FinFET.                                                    |                     |

| Figure 2.14 The low frequency noise of the FinFET for L=120nm, W=4.2um                                      |                     |

| Figure 2.15 Average equivalent gate voltage noise as a function of gate voltage [43]                        |                     |

| Figure 3.1 V <sub>DSsat</sub> vs. the device channel length for over-drive voltage of 0.2V and              | μ <sub>eff</sub> of |

| 150 cm <sup>2</sup> /V·s. The solid line is V <sub>DSsat</sub> voltage considering velocity saturation;     |                     |

| the dashed line is the ideal V <sub>DSsat</sub> voltage for a long channel device                           | 31                  |

| Figure 3.2 Saturation voltage for the weak inversion. μ <sub>eff</sub> is assumed 300 cm <sup>2</sup> /V·s, | which               |

| is measured from the FinFET and $v_{\text{sat}}$ is $2*10^7$ cm/s.                                          |                     |

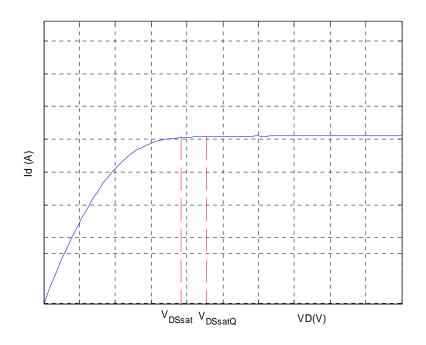

| Figure 3.3 The concept of V <sub>DSsat</sub> and V <sub>DSsatQ</sub>                                        |                     |

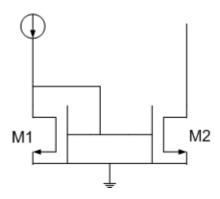

| Figure 3.4 The schematic of a simple current mirror                                                         | 35                  |

| Figure 3.5 The schematic of a wide swing current mirror.                                                    | 36                  |

| Figure 3.6 Analog circuit operation space.                                                                  | 37                  |

| Figure 3.7 The output swing. $V_{out\text{-swing}} = 2*V_{DD} - 4\cdot\Delta V$ .                           | 38                  |

| Figure 3.8 OTA block diagram with input referred noise                                                      |                     |

| Figure 3.9 Normalized the efficiency factor versus the power supply, $\Delta V=0.2V$ . Rec                  | d lines             |

| are for the square law range and blue lines for the weak-inversion range                                    |                     |

| Figure 3.10 Normalized the efficiency versus the power supply, N=4.                                         |                     |

| Figure 3.11 Switched-capacitor gain stage schematic.                                                        |                     |

| Figure 3.12 Normalized $\Pi$ versus $f$ for $\alpha=1/2$ , and $\gamma=4$ .                                 | 46                  |

| Figure 3.13 Scaling overdrive voltage and normalized power efficiency factor vs. su                                   |        |

|-----------------------------------------------------------------------------------------------------------------------|--------|

| voltage                                                                                                               |        |

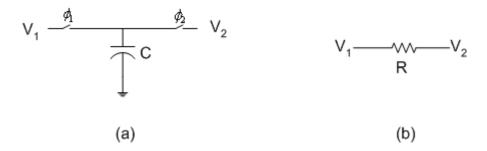

| Figure 4.1 Switched capacitor equivalence of a resistor. (a) Switched-capacitor ci                                    |        |

| (b) Resistor equivalent.                                                                                              |        |

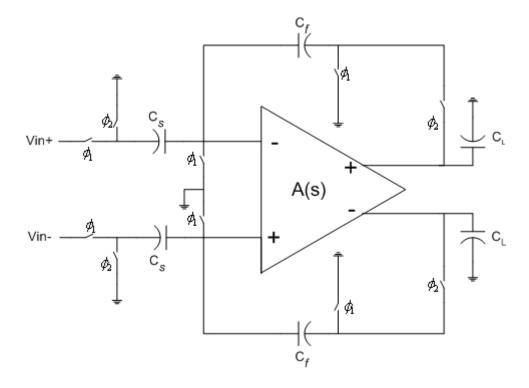

| Figure 4.2 Fully-differential SC gain stage                                                                           |        |

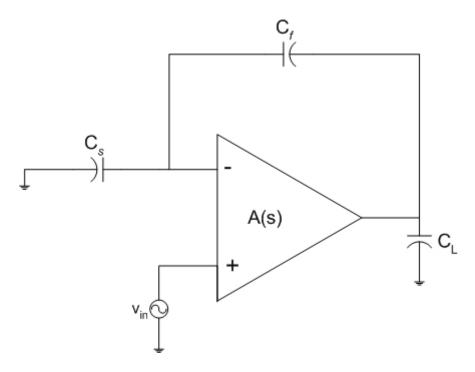

| Figure 4.3 The equivalent schematic of an SC gain stage.                                                              |        |

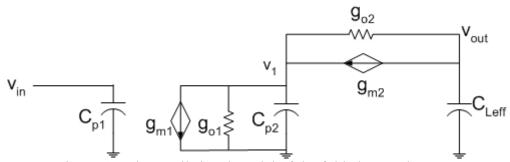

| Figure 4.4 The schematic of the classical folded-cascode OTA                                                          |        |

| Figure 4.5 The small signal model of the folded-cascode OTA                                                           |        |

| Figure 4.6 The small signal model of the close loop folded-cascade gain stage                                         |        |

| Figure 4.7 The small signal model of close loop with feedback factor analysis                                         |        |

| Figure 4.8 Schematic of the two stage miller compensated OTA.                                                         |        |

| Figure 4.9 The small signal model of the two stage miller compensated OTA                                             |        |

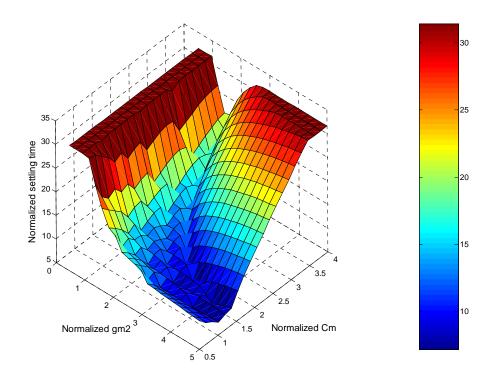

| Figure 4.10 Normalized settling time versus normalized the g <sub>m2</sub> and C <sub>m</sub> , when se error is 0.1% |        |

| Figure 4.11 Comparison of the normalized power settling product efficiency of the r                                   | miller |

| compensated two stage and folded-cascode topologies.                                                                  | 64     |

| Figure 4.12 Concept of nested gain-boosting cascode OTA                                                               | 65     |

| Figure 4.13 The small signal model of closed loop 2-level nested gain-boosting OTA                                    |        |

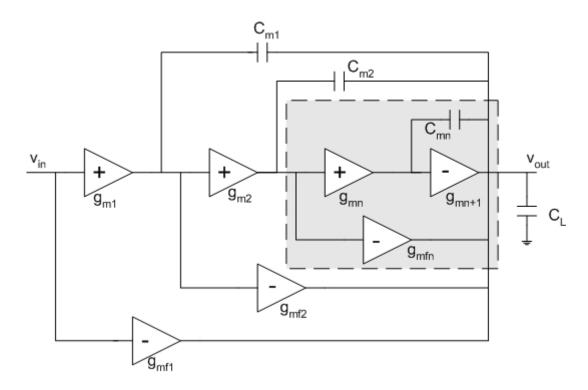

| Figure 4.14 Block diagram of the NGCC concept. The shadow dashed block is the                                         | basic  |

| module of the topology.                                                                                               | 68     |

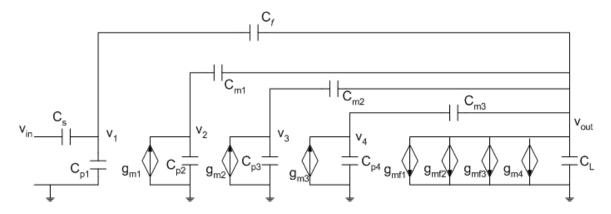

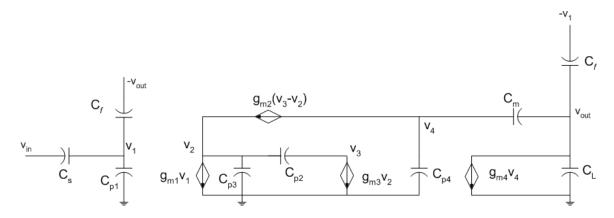

| Figure 4.15 The small signal model of the close loop form of 4-stage NGCC OTA                                         | 68     |

| Figure 4.16 the schematic of the nested cascode miller compensated OTA                                                | 71     |

| Figure 4.17 the small signal model of the nested cascode miller compensated OTA                                       | 72     |

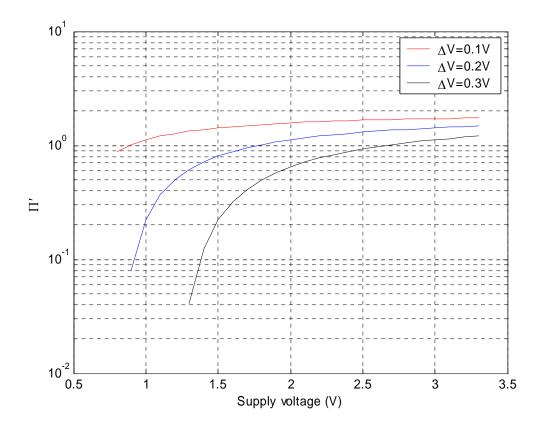

| Figure 4.18 Comparison of the normalized power efficiency factor of NCMC OTA                                          | A and  |

| nested gain boost cascode OTA topology, where $\Pi' = \frac{\prod_{nested\_cascode}}{\prod_{NCMC}}$                   | 7.4    |

| nested gain boost cascode O1A topology, where $11 = \frac{-}{\Pi_{\text{Vol.}6}}$                                     | /4     |

| Figure 4.19 Comparison of the normalized power efficiency factor of NGCC OTA                                          |        |

| rigule 4.19 Comparison of the normalized power efficiency factor of NGCC OTA                                          | 1 and  |

| nested gain boost cascode OTA topology, where $\Pi' = \frac{\prod_{nested\_cascode}}{\prod_{NGCC}}$                   | 74     |

| $\Pi_{NGCC}$                                                                                                          |        |

| Figure 5.1 Pipelined ADC block diagram                                                                                | 76     |

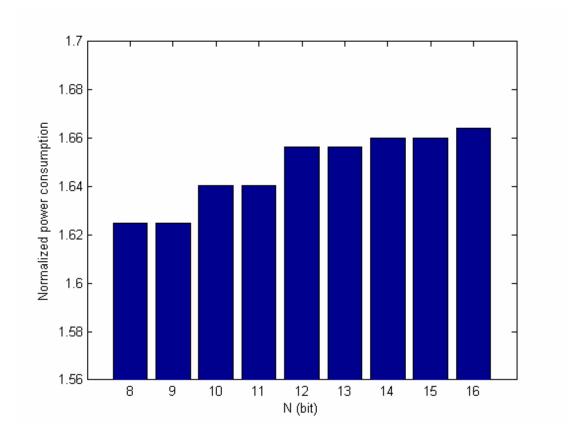

| Figure 5.2 The normalized power consumption vs. resolution                                                            |        |

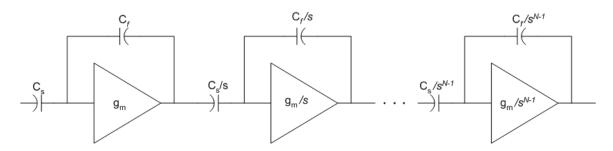

| Figure 5.3 Pipelined ADC block diagram after scaling                                                                  |        |

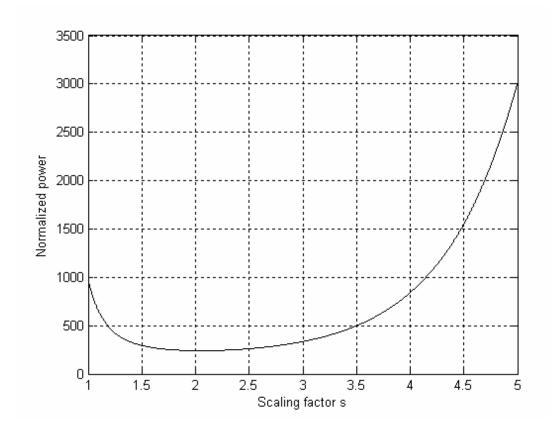

| Figure 5.4 Normalized power versus scaling factor s for 12-bit pipelined ADC, who                                     |        |

| which equals to 1, is the output bits per stage                                                                       |        |

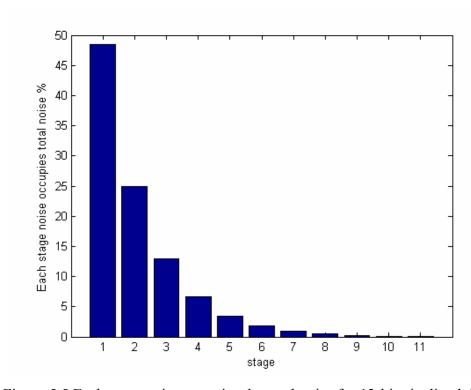

| Figure 5.5 Each stage noise occupies the total noise for 12-bit pipelined ADC                                         | 87     |

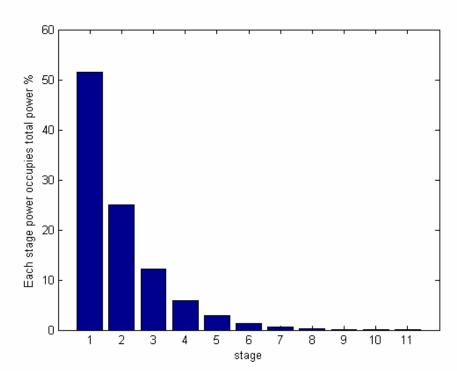

| Figure 5.6 Each stage power occupies the total power for 12-bit pipelined ADC                                         |        |

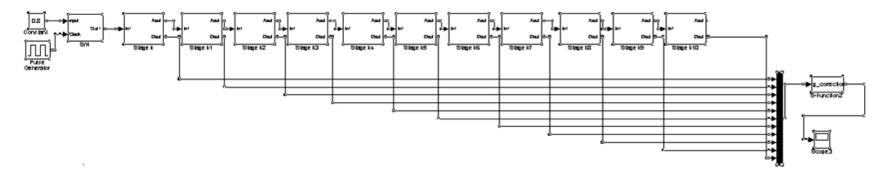

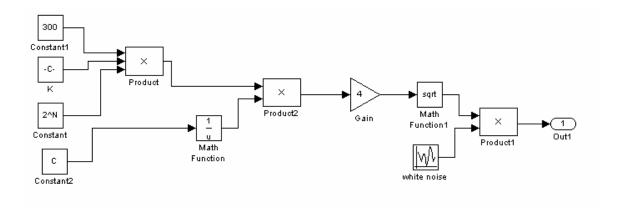

| Figure 5.7 Pipelined ADC in Matlab Simulink                                                                           |        |

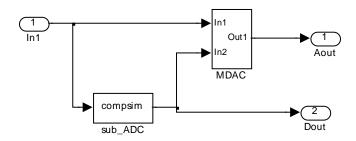

| Figure 5.8 Simulink block diagram of each stage                                                                       |        |

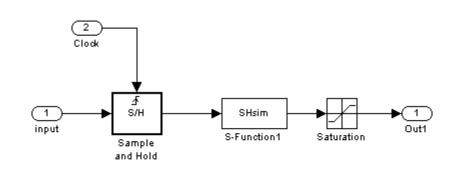

| Figure 5.9 Sample and hold circuit.                                                                                   |        |

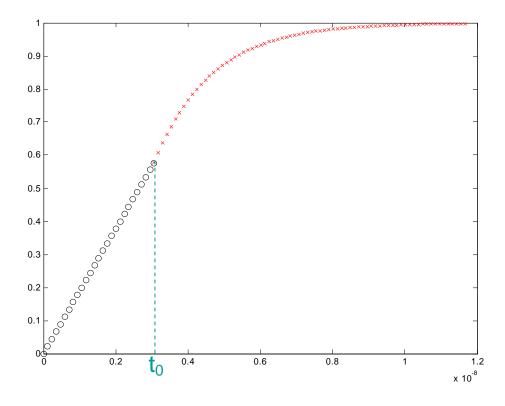

| Figure 5.10The conceptual of the settling combined with the occurrence of OTA s                                       | signal |

| slewing. Note the o's represent slewing while the +'s represent linear settling                                       | _      |

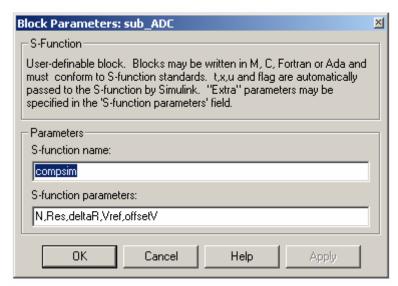

| Figure 5.11 Definition of sub-ADC function.                                                                           |        |

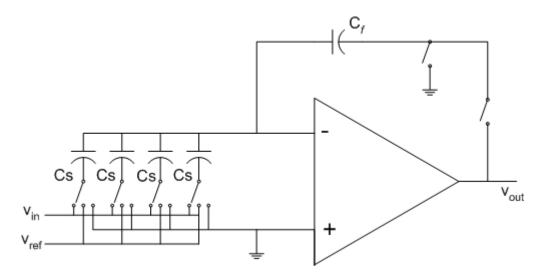

| Figure 5.12 Schematic of a MDAC.                                                                                      |        |

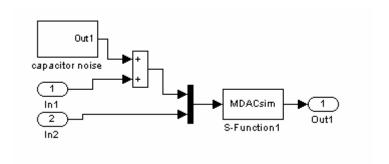

| Figure 5.13 Simulink model of MDAC.                                                                                   |        |

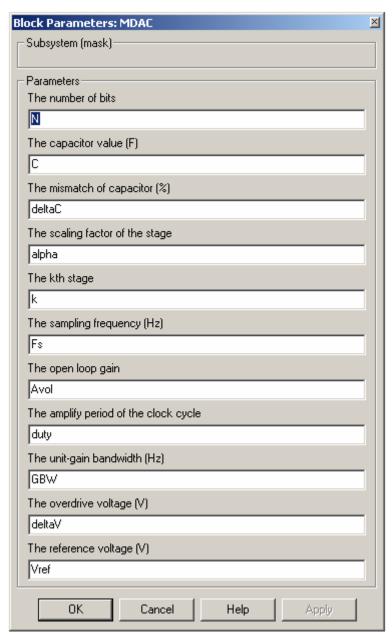

| Figure 5.14 Input parameters window of MDAC.                                                                          | 97     |

| Figure 5.15 Si | mulink model of thermal noise voltage                             | 98            |

|----------------|-------------------------------------------------------------------|---------------|

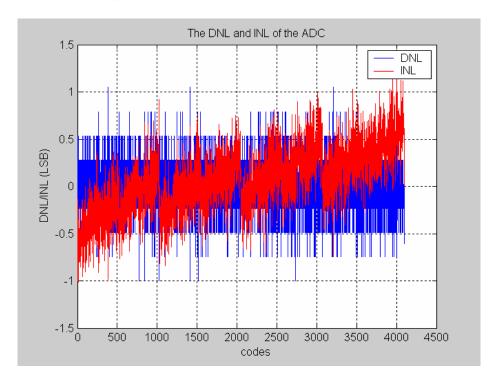

| Figure 5.16 Th | he DNL and INL of a pipelined ADC Simulink simulation             | 100           |

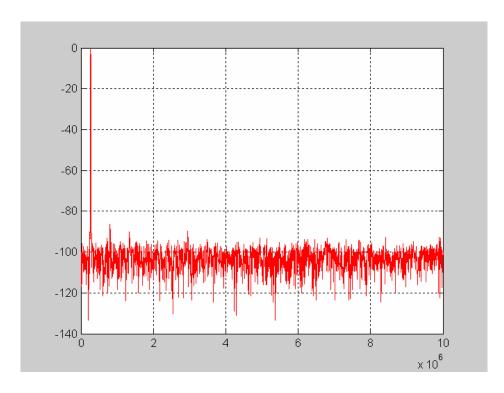

| Figure 5.17 Th | he spectrum of the ADC FFT test Simulink simulation results.      | 101           |

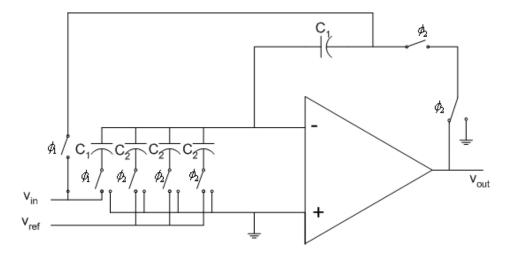

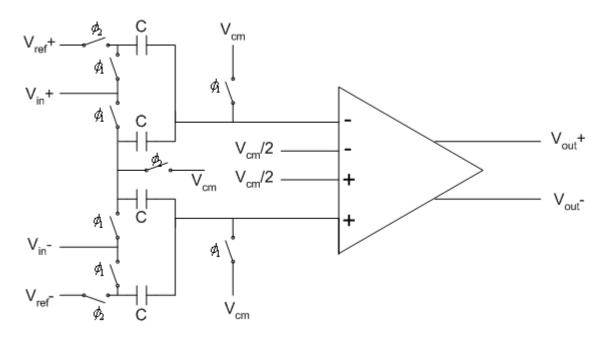

| Figure 5.18 Th | he block diagram of 2-bit MDAC, C <sub>2</sub> =1/2C <sub>1</sub> | 102           |

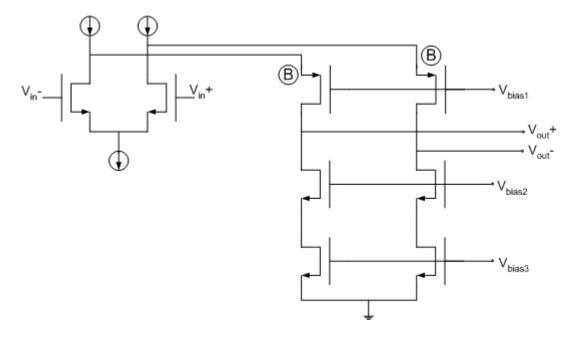

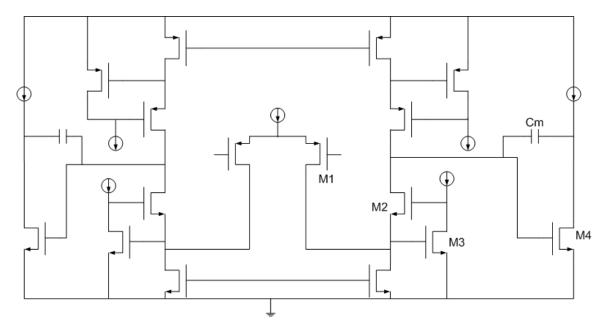

| Figure 5.19 Th | he schematic of the nested cascode OTA                            | 103           |

| Figure 5.20 Th | he schematic of the boosted stage.                                | 103           |

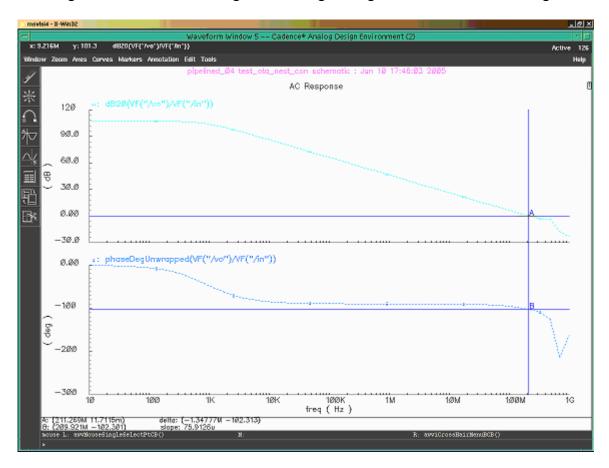

| Figure 5.21 F  | requency response of the open loop OTA, with DC gain = 1          | 107dB, Phase  |

| margin =       | 78°, GBP = 211MHz                                                 | 104           |

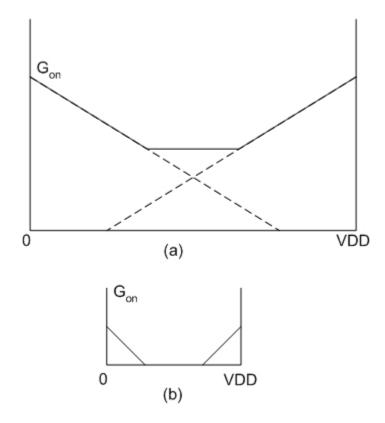

| Figure 5.22 Sv | witch on-conductance (a) under high voltage supply; (b) under     | r low voltage |

| supply         |                                                                   | 105           |

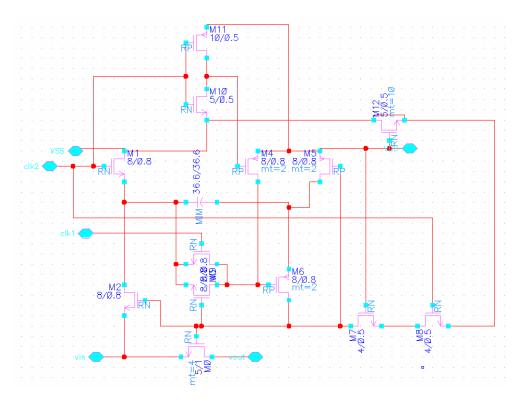

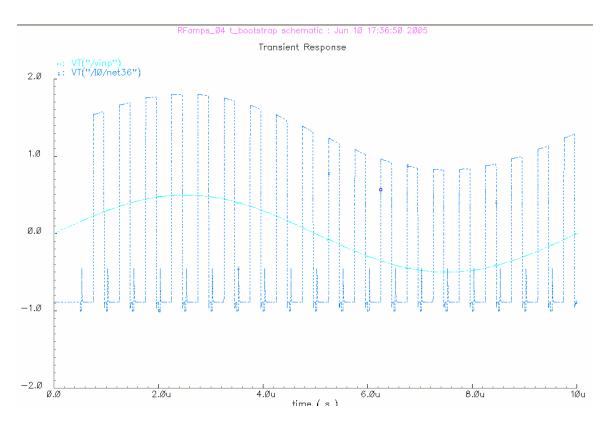

| Figure 5.23 Th | he schematic of boot-strapping circuit.                           | 106           |

| Figure 5.24 Si | mulation of boot-strapping clock versus input signal              | 107           |

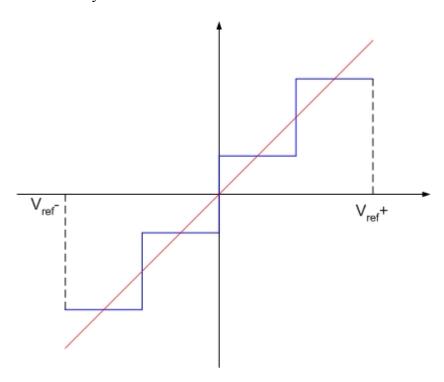

| Figure 5.25 In | put-output transfer curve of 2-bit quantizer.                     | 108           |

| Figure 5.26 Co | onceptual comparator                                              | 109           |

| Figure 5.27 Th | he schematic of the regenerative amplifier.                       | 109           |

|                |                                                                   |               |

# LIST OF TABLES

| Table                                                             | Page |

|-------------------------------------------------------------------|------|

| Table 2.1 Scaling rules for CMOS                                  | 5    |

| Table 2.2 ITRS roadmap 2002                                       | 6    |

| Table 5.1 Optimized scaling factor s versus output bits per stage | 87   |

| Table 5.2 Specifications of the object ADC                        | 101  |

## NOMENCLATURE

ADC Analog to digital converter

A<sub>c</sub> Close loop DC gain

A<sub>o</sub> Open loop DC gain

B Quantizer number of bit

B Resolution bits

BTBT Band-to-Band Tunneling

BW Bandwidth

C<sub>F</sub> Feedback/Integration capacitance

C<sub>gs</sub> Gate to source capacitance

C<sub>gd</sub> Gate to drain capacitance

C<sub>L</sub> Load capacitance

C<sub>Leff</sub> Effective load capacitance

C<sub>m</sub> Miller capacitance

CMFB Common mode feedback

C<sub>ox</sub> Gate oxide capacitanceC<sub>S</sub> Sampling capacitance

D Duty cycle

DIBL Drain-Induced Barrier Lowering

DNL differential non-linearity

DR Dynamic range

$\Delta L$  Mismatch of the channel length  $\Delta W$  Mismatch of the channel width

$\Delta V$  Drain to source saturation voltage needed at the operation point

$E_g$  Barrier of height assuming a triangular barrier

ENOB Effective number of bits

$E_p$  Electric field at the junction

ε Component mismatch

f Feedback factor

$f_B$  Base-band frequency

FFT Fast Fourier Transform

$f_{max}$  Power gain frequency

$f_s$  Sampling frequency

$f_T$  Unit current gain frequency

$\Phi_s$  Potential at the surface

GBP Gain bandwidth product

GIDL Gate-induced drain leakage

g<sub>ds</sub> Drain to source conductance

g<sub>m</sub> Mutual transconductance

*ħ* Modified Planck's constant

INL Integral non-linearity

ID Darin current

$J_t$  Tunneling current density

k Boltzmann's constant  $(1.38 \times 10^{-23} J/_{K^{\circ}})$

K<sub>p</sub> transconductance parameter

Ksps Kilo samples per second

L Channel length

L<sub>eff</sub> Effective channel length

LSB Least significant bit

MOSFET Metal oxide semiconductor field effect transistor

μ Self-gain of the transistor

N<sub>A</sub> Substrate doping levelNCMC Nested cascode miller compensated

NGCC Nested Gm-C compensated

OTA Operational transconductance amplifier

Π Power settling product efficiency

R<sub>in</sub> Input resistance

R<sub>on</sub> Transistor on resistance

rms Root mean square

S Sub-threshold slope

SC Switched capacitor

SCE Short channel effect

SFDR Spurious free dynamic range

SH Sample and Hold

$S_i$  Noise current spectrum

SINAD Signal to noise and distortion ratio

SNR Signal to noise ratio

SOI Silicon on insulator

SOS Silicon on sapphire

SR Slew Rate

q Electron charge  $(1.6 \times 10^{-19} C)$

T Kelvin temperature degree

t<sub>f</sub> Fall time

t<sub>ox</sub> Oxide layer thickness

t<sub>r</sub> Rise time

$t_s$  Sampling period  $U_T$  Thermal voltage

V<sub>cm</sub> Common mode voltage

VCO Voltage controlled oscillator

$V_{DS}$  Drain to source voltage

V<sub>DSsat</sub> Drain to source saturation voltage

$V_{GS}$  Gate to source voltage  $V_{GS}$  Gate to source voltage

$V_{in}$  Input voltage  $V_{n}$  Noise voltage

V<sub>ref</sub> Accurate reference voltage

$V_{res}$  Residue voltage  $V_{os}$  Offset voltage

V<sub>out</sub> Output voltage

$v_{sat}$  Saturation velocity of an electron or hole

$V_T$  Threshold voltage

W Channel width

W<sub>dm</sub> Maximum depletion width

x<sub>s</sub> Low-doped width

## **Chapter 1**

## Introduction

## 1.1 Background

In recent years, advances in micro electronics makes the wide application of wireless technology possible, changing the way people work, live, and entertainment [1]. For instance, cellular phone, Global Positioning System (GPS), and RF ID all have become a part of our daily routine. These products require wider bandwidth, higher resolution, smaller size, and demand less power consumption [1-3].

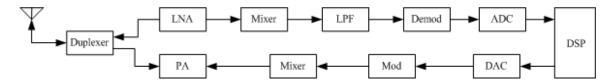

Figure 1.1 is the block diagram of a typical wireless application. Briefly speaking, circuits from the antenna to mixer are referred to as the RF analog circuitry; while circuits from the modulator to the ADC/DAC are referred to as the baseband analog circuit. Conventionally, CMOS technology dominates in the digital circuits, and bipolar and/or SiGe technology dominates the RF circuit for their extremely high  $f_{\text{max}}$ . Thanks to the continuous device dimension scaling, CMOS technology can also achieve  $f_{\text{T}}$  up to 95 GHz [4] and  $f_{\text{max}}$  up to 150 GHz [5]. In order to minimize the power and manufacture

cost, and increase the circuit reliability, it highly desirable to integrate the entire system into a single chip (System on Chip) resulting in lower power demands, lower manufacturing cost and less weight. From this point of view, it seems that CMOS technology is the most favorite choice.

Figure 1.1 The block diagram of a typical wireless application

CMOS SOI technology first emerged for the radiation harden and later for high temperature environment applications [6]. In the recent years, SOI is becoming a mainstream technology having almost the same fabrication process and costs as CMOS. The total dielectric isolation leads to the elimination of the latch-up, and to lower parasitic capacitance and lower leakage current. In addition high Q inductors are now available on the SOI chip as a direct result of the insulation layer allowing for low loss (high resistitvity substrates) from the substrate [7]. This enables or even favors SOI technology for RF applications. A final result of full dielectric isolation is the extension of CMOS for use at ultra high temperatures in excess of 240 °C.

On the other hand, continuous scaling decreases the per unit manufacturing cost while increasing circuit speed [8]. This places an ever increasing burden on the analog RF and baseband designers as more restrict conditions are faced – lower supply voltage, less self gain, and less consistent device parameters. At the same time, device scaling itself encounters more and more problems, such as short-channel effect, and larger

leakage current [9]. SOI technology gives a promising solution to these emergent problems especially the FinFET or dual gate process [8].

## 1.2 Research goals

What is the impact of the CMOS scaling to the analog design and analog circuit topology? This research is attempting to answer these question by investigating the analog design limits as a result of the scaling impact on the device performance and on the circuit performance. A more general goal of this research is to develop guidance with regard to the power efficiency analog circuit design under the scaling scenario. In the context of these goals, some key research results are summarized below:

- $\bullet$  Demonstrate the minimum threshold voltage  $V_T$  for analog design is larger than 300mV; the minimum  $V_{DSsatQ}$  is approximate 100mV; and the minimum supply voltage is around 1.1V.

- Figure of merit Power settling product efficiency (Dynamic range / (Power · Settling time) is proposed as a guide to choose an OTA in the approach to analog design in the presents of device scaling.

- For the first time, all the classical OTA topologies are analyzed in the close loop form in a single document and compared by using the power settling product efficiency as the criteria as the supply voltage scales. Nested gain boost topology is demonstrated as an optimum topology especially for operation in the weak inversion.

Designed a low-voltage, low-power pipelined ADC. Spice and Simulink simulation demonstrating both its feasibility and the power settling product figure of merit approach.

## 1.3 Organization

In Chapter 2, the impact of CMOS scaling to the device performance is discussed. In Chapter 3, the analog design limits are investigate as the CMOS scales and power settling product efficiency figure of merit is proposed. In Chapter 4, different topologies are compared by their power settling product efficiency as the supply voltage and overdrive voltage scale. Optimum topology is given under different specific supply voltage and overdrive voltage. In Chapter 5, a low voltage pipelined ADC is designed as an example. A Matlab Simulink library for the pipelined ADC is built, and the behavior simulation is completed. Components of the pipelined ADC simulation are done in the spice environment.

## Chapter 2

# **Challenges to the Analog Design with CMOS Scaling**

## 2.0 Introduction to the CMOS scaling

The silicon CMOS architecture has successfully become the dominant technology in the integrated circuits [10], as a result of the closely matched device mobility (1.5 to 3), quality native oxide, and its scalability providing decreased power consumption at enhanced performance levels. CMOS gate lengths have reduced from 10um in the 1970's to the present day geometry of less than 0.09um under the guideline set by the Dennard et al [11], which is based on the constant electric field in the device, shown in the Table 2.1.

Table 2.1 Scaling rules for CMOS

| Device Parameters                                    | Scaling Factor |

|------------------------------------------------------|----------------|

| Device dimension t <sub>ox</sub> , L, W,             | 1/κ            |

| Doping concentration N <sub>A</sub> , N <sub>D</sub> | κ              |

| Voltage V                                            | 1/ κ           |

| Current I                                            | 1/ κ           |

| Capacitance C <sub>gs</sub>                          | 1/ κ           |

| Delay time VC/I                                      | 1/ κ           |

| Power consumption VI                                 | $1/\kappa^2$   |

| Electric field of in the device E                    | 1              |

Table 2.2 ITRS roadmap 2002

| YEAR OF PRODUCTION                                    | 2003 | 2004 | 2005 | 2006 | 2007 |

|-------------------------------------------------------|------|------|------|------|------|

| DRAM ½ Pitch (nm)                                     | 100  | 90   | 80   | 70   | 65   |

| MPU ½ Pitch (nm)                                      | 107  | 90   | 80   | 70   | 65   |

| MPU Printed Gate Length (nm)                          | 65   | 53   | 45   | 40   | 35   |

| MPU Physical Gate Length (nm)                         | 45   | 37   | 32   | 28   | 25   |

| $V_{DD}(V)$                                           | 1.0  | 1.0  | 0.9  | 0.9  | 0.7  |

| $T_{ox}$ Equivalent oxide thickness (electrical) (nm) | 2    | 2    | 1.9  | 1.9  | 1.4  |

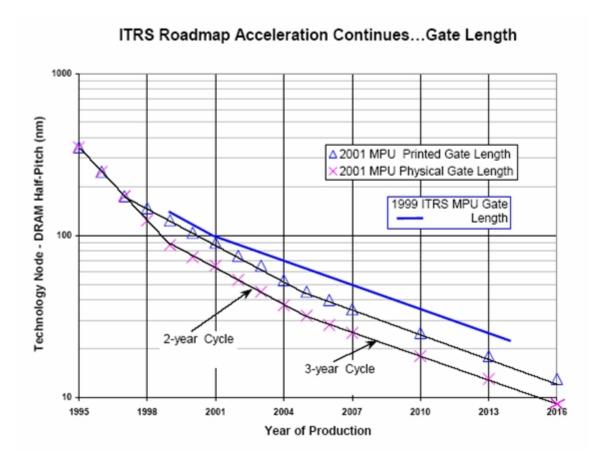

The international Technology Roadmap for Semiconductors (ITRS) [12] points out that the CMOS gate length will continue scaling to below 50nm (Table 2.2 Figure 2.1) in 2005. However, ITRS focuses heavily on the digital applications performance ignoring analog applications. As to analog or mixed-signal design, device scaling imposes more challenges to the analog engineers, when compared to their digital colleagues, in order to maintain the circuit performance.

Figure 2.1 ITRS roadmap acceleration continues — gate length trends.

This chapter first presents an overview of the problems induced by the CMOS scaling, focusing on the challenges in analog circuit design. Then, the FinFET device is introduced, as it is believed to be the most promising device to replace the traditional planar CMOS devices in the next decade, for it alleviates many of the problems faced in process scaling.

## 2.1 Challenges to the analog design in the scaling process

#### 2.1.1 Threshold voltage

The MOSFET threshold voltage should scale at the same rate as the other device parameters according to the scaling theory. However, it scales at a reduced rate, which is clearly understood when taking standby power consumption into consideration for digital applications [13]. The off-state leakage current increases 10 times for every 0.1V decrease in the threshold voltage. Additionally, threshold voltage rolls off as the gate length shrinks due to the loss of gate voltage control over the depletion charge [9], which is referred to as short-channel effects (SCE). SCE is more apparent when the device scales down below sub-100nm, which is one of the main sources of the leakage current increase in deep submicron (DSM) devices [14].

The minimum threshold voltage is determined by considering the acceptable subthreshold leakage current in the digital circuits under the maximum operating temperature and supply voltage conditions simultaneously with maximum  $I_{Don}$ . The sub-threshold leakage is the dominant contributor to the stand-by power in the 0.1um process [10]. Stand-by power occupies 0.01% of the active power in a 1um process while occupying 10% in a 0.1um process. In order to control the stand-by power, the sub-threshold slope should be as large as possible along with an adequate threshold voltage. Presently, the sub-threshold swing of the FinFET is 64-67mV/decade (Figure 2.12). Assuming sub-threshold occupies 4-5 decade (resulting in an on to off ration approaching  $10^5$ ), the minimum threshold voltage should be greater than  $0.25 \sim 0.3$ V. With a threshold

temperature coefficient of -1mV/°C and a maximum operation temperature of 90°C, a threshold voltage of 300mV would ensure an acceptable on/off ratio for digital logic.

The variation of the threshold voltage is another concern for both the digital and analog design. The fluctuation of the threshold voltage results in the fluctuation of the propagation delay, leading to intolerable clock skews and low circuit yields [15]. At the same time, it results in a problematic offset voltage in analog processing, such as comparators of ADCs. In the [16], Wong revealed that the fluctuation is not only related to the fluctuation of the number of the dopants, but also to the distribution of the dopants. For the uniformly doping, the standard deviation of the threshold voltage is

$$\sigma_{V_T} = \frac{q}{C_{ox}} \sqrt{\frac{N_A W_{dm}}{3LW}} \tag{2.1}$$

While for the retrograde doping,

$$\sigma_{V_T} = \frac{q}{C_{ox}} \sqrt{\frac{N_A W_{dm}}{3LW}} (1 - \frac{x_s}{W_{dm}})^{3/2}$$

(2.2)

where  $N_A$  is the substrate doping level,  $C_{ox}$  is the gate oxide capacitance,  $W_{dm}$  is the maximum depletion width,  $x_s$  is the low-doped width.

However, for the ultra-thin films used in fully depleted (FD) SOI or dual gate (DG) FinFET devices, the conventional approach via highly doped film to control the threshold voltage is not viable because the threshold voltage is severely sensitive to the gate oxide and the film thickness variations [17]. Therefore, to improve on threshold performance un-doped film is proposed to achieve good control of the threshold voltage

while improving channel mobility and potentially improving noise performance as well. Trivedi [17] found for the sub-30nm ultra-thin, lightly doped devices, the variation of the threshold voltage is affected by the quantum mechanical (QM) as

$$\sigma_{V_T}^2 \cong \frac{S}{(kT/q)\ln 10} \cdot \frac{0.3763}{(m_x/m_0)t_{gi}^2}$$

(2.3)

where S is the sub-threshold slope,  $m_x/m_0$  is the ratio of the carrier effective mass in the direction of the confinement to the free electron mass. For the mismatch current caused by the mismatch of the threshold voltage, (2.4.a) and (2.4.b) are for the device operation in the strong inversion and the weak inversion respectively.

$$\frac{\sigma^2(I_{ds})}{I_{ds}^2} = \frac{4\sigma^2(V_T)}{(V_{GS} - V_T)^2}$$

(2.4.a)

$$\frac{\sigma^2(I_{ds})}{I_{ds}^2} = \frac{\sigma^2(V_T)}{(nU_T)^2}$$

(2.4.b)

where,  $(nU_T)^{-1}$  is the slope of the  $I_{DS}$ - $V_{GS}$  curve in weak inversion plotted in a log scale.

From (2.2-2.4), we can find that under the same electric field scaling rule, the mismatch of the current is inverse proportional to the scaling factor for the retrograde doping or the square of the scaling factor for the un-doped film. This means in order to get the same offset result from the fluctuation of the threshold voltage,  $\kappa^2$  time's area and power consumption are paid as price for the latter case.

#### 2.1.2 Leakage current

As to the logic and memory applications, the most important performance gauges are On/Off ratio (leakage current), delay, power and reliability [18]. Leakage current will not only disrupt the dynamic nature of the pass transistor logic but increase the stand-by power consumption as well. Leakage current includes two parts: one is the gate leakage current; the other is the Drain to the Source leakage current (off-state leakage).

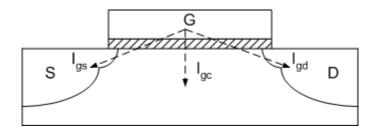

## 2.1.2.1 Gate leakage current

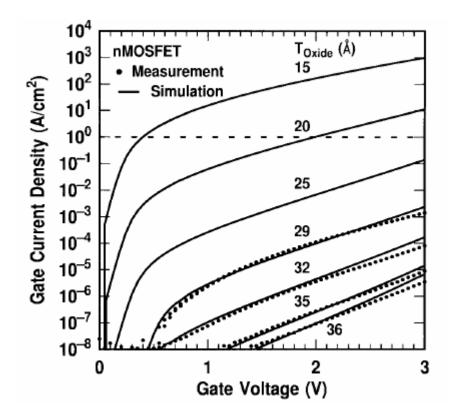

Gate leakage results from the gate silicon dioxide tunneling phenomenon. As the devices scale, gate oxide thickness scales as well to keep the transistor short-channel performance. When gate oxide is sufficiently thin, there is substantial current flowing from the gate to the channel even under the low voltage operation conditions shown in Figure 2.2.  $I_{gs}$  and  $I_{gd}$  is the tunneling current between the source-drain extension (SDE) and the gate overlap, which is called edge direct tunneling (EDT).  $I_{gc}$  is the tunneling current to the channel. Gate leakage current increases exponentially with the decrease of the gate oxide thickness [13, 19, 20].  $I_{gc}$  is the dominant leakage current when  $V_g > 0$ , while EDT is dominant when  $V_{fb} < V_g < 0$  [21]. For the digital circuit, the dissipation power associated with the gate leakage is acceptable until gate oxide thickness reduces less than 2nm Figure 2.3 [13, 22]. This is under the assumption that the maximum tolerable gate leakage current is less than  $1A/cm^2$  or  $10nA/um^2$ . When high  $\kappa$  materials are used as the gate insulator in later generation devices, gate leakage currents are projected to become greatly reduced.

Figure 2.2 Component of the gate leakage current.

Figure 2.3 Measured and simulated  $I_G$ – $V_G$  characteristics under inversion conditions of the nMOSFET's. The dotted line indicates the 1 A/cm<sup>2</sup> limit for leakage current [13, 22].

## 2.1.2.2 Off-state leakage current

The off-state current is composed of 1) the surface Band-to-Band Tunneling (BTBT) or gate-induced drain leakage (GIDL); 2) the bulk BTBT [23]; 3) the subthreshold leakage current; and 4) leakage current due to short-channel effects owing to the Drain-Induced Barrier Lowering (DIBL).

## a) GIDL leakage current

GIDL leakage is the leakage current occurring in the deep depletion layer in the gate-drain overlap region due to the band-to-band tunneling. It can be expressed as [24]

$$I_{GIDL} = AE_s \exp(-B/E_s)$$

$$E_s \approx \frac{V_{DG} - 1.2}{3T_{ox}}$$

(2.5)

where  $E_s$  is the vertical electric field at the silicon surface, A is a preexponential constant and B=21.3MV/cm [24]. A band bending of 1.2eV is the minimum potential for band-to-band to occur [24]. For the sub-100um device, the GIDL effect can be ignored for supply voltages less than 1.2V according to the ITRS roadmap.

#### b) Substrate BTBT leakage current

The substrate BTBT is the junction leakage current occurring in the Drain/Source depletion area with the substrate. The tunneling current density can be expressed as [25]

$$J_{t} = \frac{\sqrt{2m^{*}q^{3}E_{p}V_{a}}}{4\pi^{3}\hbar^{2}\sqrt{E_{g}}} \exp\left(-\frac{4\sqrt{2m^{*}E_{g}^{3/2}}}{3q\hbar E_{p}}\right)$$

(2.6)

where  $m^*$  is the electron effective mass and  $V_a$  is the reverse bias voltage across the p-n junction,  $E_g$  is the barrier of height assuming a triangular barrier,  $E_p$  is the electric field at the junction,  $\hbar$  is the modified Planck's constant.

The substrate BTBT current is critical dependant on the substrate doping concentration [23, 26]. Following the rule described in Table 2.1, substrate BTBT current will increase dramatically as the device scales to sub-100nm. We will find in the later,

this can be solved by new device — the FinFET, which uses nearly intrinsic Si as the substrate resulting in substantially less substrate BTBT current.

## c) DIBL leakage current

DIBL leakage is a surface punch-through phenomenon occurring in the short channel device due to the barrier lowering at the source junction by the drain field and the band-bending under the effect of the gate-induced surface space charges [27].

$$I_{off} = W_{tot}I_o \exp(\frac{qm|V_{ds}|}{kT})/L_{eff}$$

$$I_o \propto \exp(\frac{-E_g + q\phi_s}{kT})$$

(2.7)

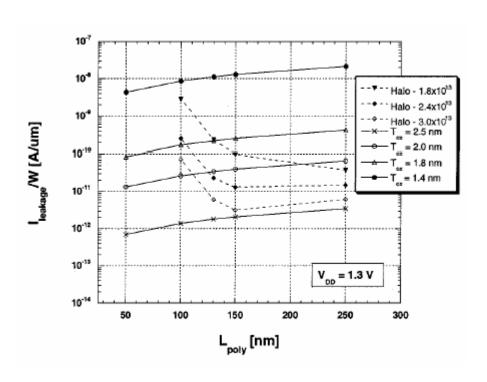

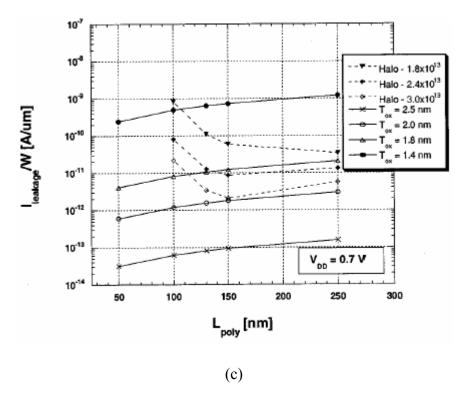

where m is a dimensionless factor,  $W_{tot}$  is the total off-state device width, and  $L_{eff}$  is the effective channel length,  $E_g$  is the bandgap, and  $\phi_S$  is the potential at the surface [27]. The DIBL leakage with the relationship of channel length and supply voltage is shown in Figure 2.4 [28].

(a)

(b)

Figure 2.4 The dashed lines represent the DIBL leakage and the solid one represent the gate leakage.

Although Figure 2.4 cannot be used to represent the actual general leakage current values, it does demonstrate the trends. When channel lengths are less than 150nm, the DIBL leakage increases dramatically.

## d) Sub-threshold leakage current

The channel current will not abruptly become zero when the gate voltage is below the threshold voltage. In the sub-threshold region, the channel current is dominated by the diffusion current. It can be expressed as [29]

$$I_{ds\_sub} = \mu C_{ox} \frac{W}{L} (m-1) \left(\frac{kT}{q}\right)^2 \exp\left(\frac{V_g - V_T}{mkT/q}\right) \left(1 - \exp\left(-\frac{V_{ds}}{kT/q}\right)\right)$$

(2.8)

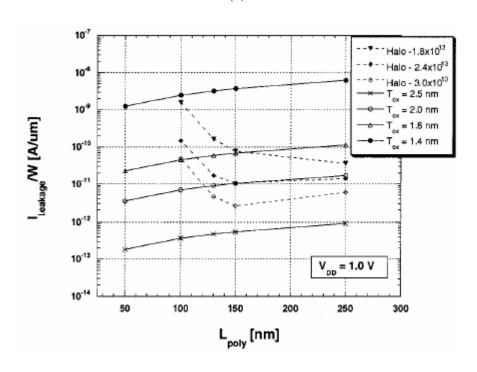

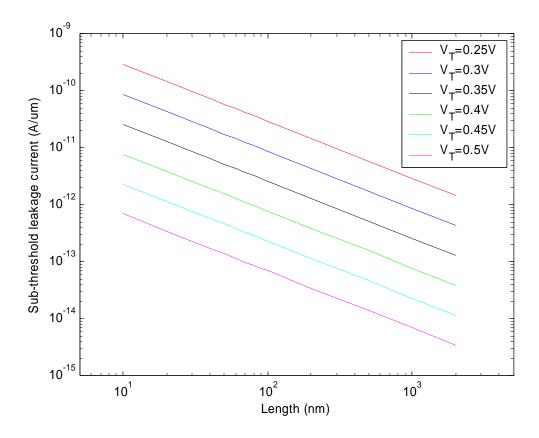

Sub-threshold leakage current versus channel length and threshold voltage is shown in Figure 2.5.

Figure 2.5 The sub-threshold leakage current, where  $V_{DS}$ =1V, m=1.1,  $\mu$ =300 cm<sup>2</sup>/V·s, T=300K.

From Figure 2.5, we can find the sub-threshold leakage current increases with the reduction of the channel length and threshold voltage.

As mentioned above, during the device scaling, GIDL and BTBT current can be ignored by lowering the supply voltage or adopting the FinFET device. However, DIBL and subthreshold voltage will increase dramatically. For the digital applications, GIDL and BTBT current will increase the off-state power or stand-by power with the device scaling. From the analog point of view, it will affect the sampled voltage accuracy on the

capacitor in the SC (switched-capacitor) circuit during the switch hold period. It will be revealed in the next section.

## 2.1.2.3 The leakage current impact on the SC circuits

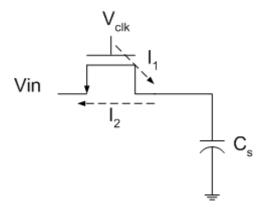

SC circuits are widely used in the data acquisition system. Leakage current has a heavy effect on the resolution. In Figure 2.6 it shows half of a differential sample and hold circuit in the hold period, in which,  $I_1$  is the gate leakage current, and the  $I_2$  is the sum of off-state leakage current. Leakage will result in a differential voltage error  $V_{error}$  because of the differential nature of analog voltages used in analog signal processing. The total voltage error result from the leakage is found as

$$V_{error} = \frac{I_{Lk}\Delta t}{C_s}$$

(2.9)

$$I_{LK} = I_1 W L + I_2 W$$

Where  $C_s$  is the sampling capacitor,  $\Delta t$  is is the hold period of the switch,  $I_{Lk}$  is the total leakage current.

Figure 2.6 Leakage current in the sample and hold.

For data acquisition applications,  $\,C_{\scriptscriptstyle S}\,$  is set by the desired dynamic range or noise floor

$$V_{n(rms)} = \sqrt{\frac{kT}{C_s}} < \frac{V_{signal(rms)}}{2^{B+1}}$$

(2.10)

where  $V_{n(rms)}$  is the thermal noise voltage. Low-frequency noise is ignored here for simplicity. B is the resolution bits of the application. In order to prevent leakage current degrading the resolution,

$$V_{error} < V_{n(rms)} \tag{2.11}$$

or

$$I_{Lk} < \frac{\sqrt{kTC_s}}{\Delta t} < \frac{kT2^{B+1}}{V_{signal(rms)}D} f_s$$

(2.12)

where D is the duty cycle, and  $f_s$  is the sampling frequency.

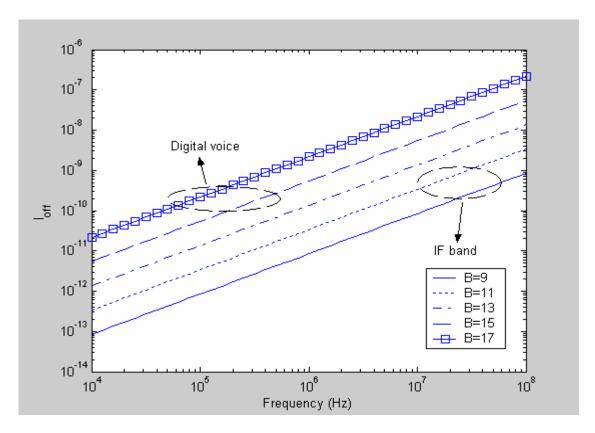

The maximum off-state leakage current is plotted verses sampling frequency for the desired resolution bits B equal 9 to 17 and is shown in Figure 2.7

Figure 2.7 Maximum off-state leakage current versus sampling frequency, assuming  $V_{\text{signal(rms)}}=1V$ , sampling frequency duty =0.5, T=300K.

Here, we observe that a lower resolution requires a smaller leakage current. This seems to contradict with our normal concept. This is a direct result of greater resolutions requiring larger capacitors to maintain the dynamic range or lower noise floor.

Because the physical characteristic is very different for each process, it is very difficult to estimate the leakage current value for a specific size transistor. Here we use data of Figure 2.3 to estimate how much the gate leakage current affects the circuit accuracy. Assuming the width of the device is 0.5um and length is 0.1um, a 2nm gate oxide will result in 5nA gate leakage current. This will result in a SH error larger than 15-bit resolution allows when sampling at 1MHz or 9-11bit resolution sampling at 100MHz.

This means that the leakage current sets the lowest sampling frequency for the specific accuracy objective in the SC application. As to the low frequency applications, oversampling has to be adopted resulting in more power consumption than they may have historically. One of those applications is the audio ADCs with the 10-12 bits resolution.

#### 2.1.3 Noise of the MOS transistor

#### 2.1.3.1 Noise sources of the MOS transistor

The noise sources of the MOS transistor include: 1) Channel thermal noise; 2) Gate noise; 3) 1/f noise; 4) shot noise. The noise induced by parasitic resistances is not considered here. From the frequency domain perspective, the noise sources can be classified into two types: white noise (independent of the frequency), which includes channel thermal noise and shot noise, and 'colored' noise (dependent of the frequency), which includes gate and 1/f noise. Because of the small amplitude of shot noise, it has little effect on the dynamic range, and is not considered here [30]. Gate noise results from the charge in the channel fluctuating due to the channel thermal noise and as a result gate noise is correlated to the channel thermal noise. In this section, the effect of scaling on device noise behavior only considers the channel thermal noise and 1/f noise.

## 2.1.3.2 Channel thermal noise (Simplified to thermal noise)

As noted above, thermal noise is white in nature with an extremely wide bandwidth. It is the dominant noise source when considering many baseband and RF applications. For long-channel devices, the noise current spectrum of the thermal noise is [31]

$$S_i = 4kT \frac{\mu_{eff}}{L^2} Q_{inv} \tag{2.13}$$

where  $Q_{inv}$  is the total inversion layer charge. In particular, (2.13) can be simplified to (2.14) based on the device region of operation, triode or saturation.

$$S_i = 4kTg_{ds}, V_{DS} = 0 (2.14a)$$

$$S_i = \frac{8}{3}kTg_m,$$

$V_{DS} > (V_{gs} - V_{th})$  (2.14b)

Recently, for the deep sub-micro devices, researchers have observed that thermal noise increased [32-36] as a result of the hot carriers [36] or velocity saturation [32, 35] or both [33]. The measurement data shows that the thermal noise power increases by the factor of two for the 0.25um channel length devices [33, 34]. To maintain an equivalent SNR, gm and in turn device power must be increased by a factor of 2.

## 2.1.3.3 1/f noise

1/f noise dominants the low frequency bandwidth as it rolls off with the increase in frequency. In baseband application, 1/f noise can be reduced to the near thermal levels by techniques, such as chopper stabilization, and correlated double sampling [37]. However, for the RF application, it affects the phase noise of the nonlinear circuits, such as mixers and VCOs, resulting from the up-conversion to the high frequency giving rise to a 1/f³ sideband around the carrier frequency[38].

1/f noise origins are from the carrier number fluctuation and the mobility fluctuation [39]. With the device scaling, CMOS process are projected to transfer to the SOI processes especially in the RF application, not only as a result of the lower sub-

threshold leakage currents, but also due to the availability of the high Q on-chip inductor, high resistivity substrates and reduced substrate cross talk. The increase or decrease of 1/f noise spectral density with the device scaling is still a contradicted issue. Several groups report an increase [38, 40, 41], while the others report a decrease for the reduced the gate oxide [42]. The reasons for this may be that 1/f noise is heavily dependent on the Si-SiO2 interface quality and as a result immature processes make comparisons difficult. However, all agree on one thing — the minimum size device-to-device noise fluctuation becomes worse and worse along with scaling. This is a direct result of the smaller gate area and finite number of traps which leads to greater dispersion.

### 2.1.4 Supply voltage scaling

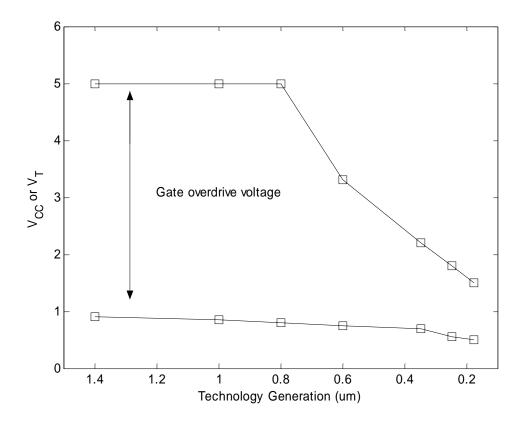

Supply voltage scales with the gate oxide scaling to prevent too large of an electrical field across the oxide. On the other hand, besides the architectural innovation, the most effective way to save the active power is to reduce the power supply voltage [19]. However, threshold voltage does not scale proportionally to the supply voltage scaling as shown in Figure 2.8 due to the leakage current consideration. The dramatic decrease of the  $V_{CC} - V_T$  voltage degraded the device performance greatly.

Figure 2.8 Supply voltage and threshold voltage scale with the channel length [10].

Another direct result of supply voltage scaling is the reduction of the signal swing in the analog circuit, which means more power needed to achieve the same signal-to-noise ratio at an identical bandwidth and. This will be discussed in detail in chapter 3.

# 2.2 Promising new device — FinFET

### 2.2.1 Introduction of FinFET

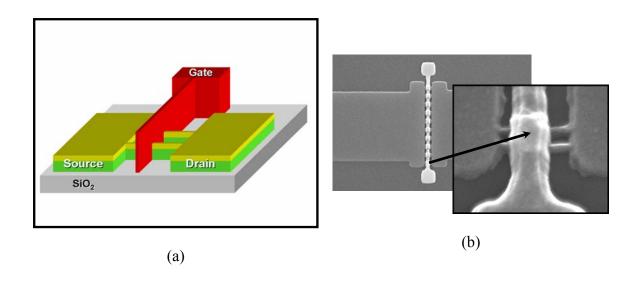

The structure of the FinFET is shown in Figure 2.9.

Figure 2.9 The 3-D structure of the FinFET.

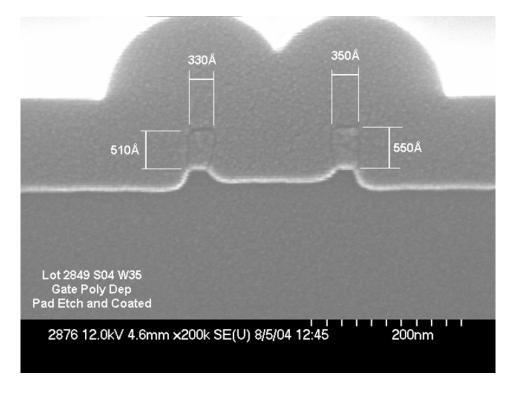

In Figure 2.9, the red represents the gate, blue is drain and source. The device sits on the silicon dioxide, which is white in the plot. The current is flowing parallel to the surface of the SO<sub>2</sub>. The Figure 2.10 is the electron micrograph of the FinFET.

Figure 2.10 The electron micrograph of the FinFET, whose width is 50nm, length is 35nm [SPAWAR, San Diego].

The FinFET provides excellent control of the short-channel effects. Furthermore, the adoption of lightly or even un-doped silicon film achieves higher mobility [14].

### 2.2.2 Performances of the FinFET

### 2.2.2.1Suppression SCE

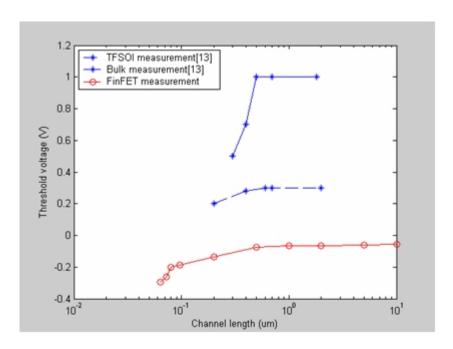

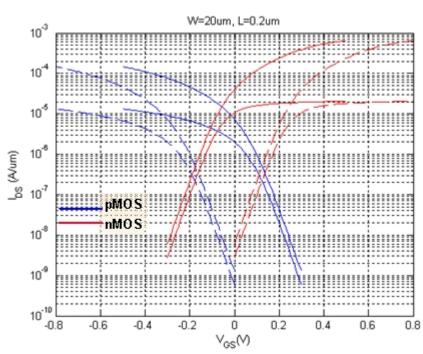

Because a double gate is used to control the channel and ultra-thin film used, SCE is greatly suppressed. Excellent control of the SCE of FinFET is shown in Figure 2.11, where threshold voltage rolling off with the decreases of the channel length is compared between bulk, TFSOI, and FinFET devices. This is also shown in Figure 2.12, in which the solid lines are measured ID-VG curve at low VD (VD=0.025V) and high VD (VD=0.5V) biasing, and the dashed ones are projected curves. A low subthreshold swing of 63-67mV/dec was achieved, which indicated that SCE is well controlled by the FinFET.

Figure 2.11 Short-channel effect in bulk, thin-film SOI (TFSOI) and FinFET n-channel devices.

Figure 2.12 The  $I_{DS}$  vs.  $V_{GS}$  curve biasing in the low  $V_{DS}$ =25mVand high  $V_{DS}$ =0.5V. The dash lines are projected  $I_{DS}$  when using Mo doped gate to raise the threshold voltage.

### 2.2.2.2 Application in the subthreshold range

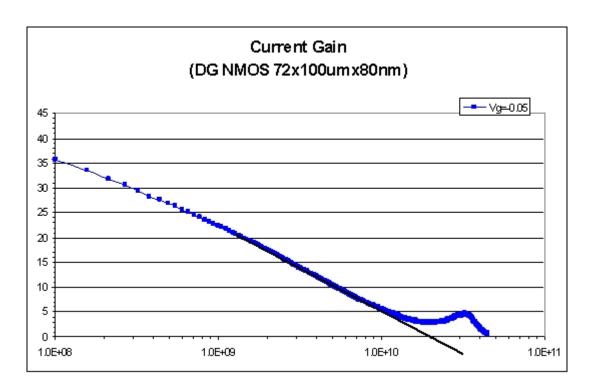

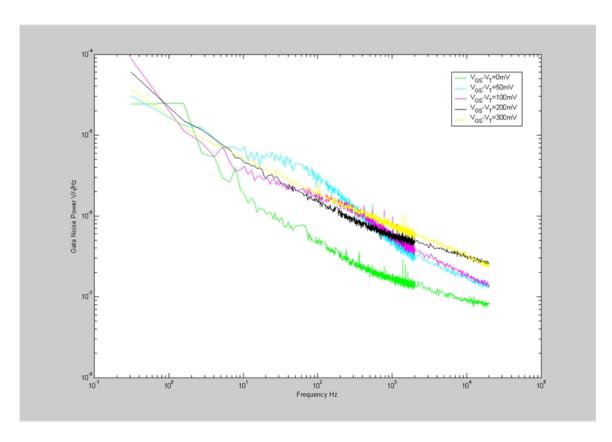

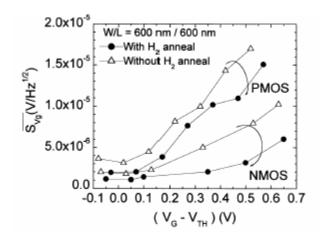

FinFET inherits the benefits of the devices scaling — increase of the  $f_{\rm T}$  (unit current gain bandwidth). Figure 2.13 is the measured  $f_{\rm T}$  of 80nm FinFET, which goes up to 20GHz at the 50mV overdrive voltage. As a rule of thumb, the operation bandwidth is  $1/10\,f_{\rm T}$ , which means the device may be considered for designs in the 2-3GHz application for the transistors working in the moderate inversion. The FinFET also demonstrated less low-frequency noise in weak inversion than in the strong inversion Figure 2.14 and 2.15 [43].

Figure 2.13 Unit current gain of the 80nm length FinFET.

Figure 2.14 The low frequency noise of the FinFET for L=120nm, W=4.2um.

Figure 2.15 Average equivalent gate voltage noise as a function of gate voltage [43]

The FinFET demonstrates good control of the SCE result in less off-state leakage current as a result of the lessoning the TOX requirements compared to planar device of equivalent length. With the high  $\kappa$  material used in the gate, gate leakage problem can also be alleviated further. It also can operate in the weak-inversion range for most state-of-art applications due to its high  $f_T$ . Operation in the weak inversion reduces the overdrive voltage, which alleviate the signal swing problem. Less 1/f noise in the weak-inversion enable it good choice in the RF application. All above advantages enable FinFET an excellent candidate for the sub-100nm devices.

## **Chapter 3**

# **CMOS Scaling Affects to the Analog Design**

## 3.0 Introduction

In the previous chapter, the impact of scaling on single CMOS device performance was discussed. In this chapter the impact of CMOS scaling on analog design will be discussed in detail. Finally concept of a power settling product efficiency is introduced as criteria to choose the optimum process or topologies in design of sampled analog circuits under the circumstance of CMOS scaling.

## 3.1 CMOS scaling impacts to the analog design

#### 3.1.1 Saturation voltage, $V_{DS}$

The voltage saturation of  $V_{DS}$  is an important parameter in analog design for it determines output stage overhead, and headroom directly affecting output swing and circuit efficiency. For a long-channel device, as the drain voltage  $V_{DS}$  increases, the drain current increases as well until channel pinch-off appears at the drain side. This  $V_{DS}$  voltage is referred to as the saturation voltage.

$$V_{DSsat} = \frac{V_{gs} - V_{th}}{m} \tag{3.1}$$

where m is the body-effect coefficient.

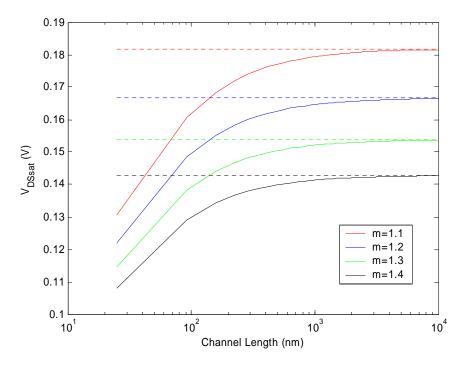

However, when the device is scaled down to the deep sub-micro range, carrier velocity saturation effects must be considered. For operation in the strong inversion under the constraint of velocity saturation, the saturation voltage should be modified to [1]

$$V_{DSsat} = \frac{2\Delta V / m}{1 + \sqrt{1 + 2\mu_{eff} \cdot \Delta V / (mv_{sat}L)}}$$

(3.2)

where  $v_{\text{sat}}$  is the saturation velocity of an electron or hole.  $V_{\text{DSsat}}$  versus the channel length with and without considering velocity saturation are plotted in Figure 3.1 to demonstrate the effect of velocity saturation on the saturation voltage.

Figure 3.1  $V_{DSsat}$  vs. the device channel length for over-drive voltage of 0.2V and  $\mu_{eff}$  of 150 cm<sup>2</sup>/V·s. The solid line is  $V_{DSsat}$  voltage considering velocity saturation; while the dashed line is the ideal  $V_{DSsat}$  voltage for a long channel device.

In the Figure 3.1, the saturation voltage falls away the ideal saturation voltage as channel length approaches the sub-micro range. As the channel length enters the sub-100nm range, the difference in saturation voltage can be as high as 40mV.

Effect of the velocity saturation is only discussed for strong-inversion operation in [29]. Next, we will discuss the effect of the velocity saturation for the weak-inversion operation. For operation in the weak-inversion, drain current equation for long device is expressed as [29]

$$I_{DS} = \frac{\mu_{eff} W}{L} \sqrt{\frac{\varepsilon_{si} q N_a}{2\psi_s}} \left(\frac{kT}{q}\right)^2 \left(\frac{n_i}{N_a}\right)^2 e^{q\psi_s/kT} \left(1 - e^{-qV_{DS}/kT}\right)$$

(3.3)

where  $\psi_s$  is the surface potential, Na is the acceptor impurity density,  $n_i$  is the intrinsic carrier density, and  $\epsilon_{si}$  is the silicon permittivity.

In (3.3), kT/q is approximate to 26mV at the 27°C. As  $V_{DS}$  is larger than 100mV, the value in the right bracelet is almost equal to 1, that is,  $I_{DS}$  is almost constant. From this point of view, saturation voltage of long channel device for operation in weak-inversion is referred to 100mV. However, when considering velocity saturation, (3.3) can be similarly as (3.1) modified to

$$I_{DS} = \frac{\mu_{eff}(W/L)}{1 + \frac{\mu_{eff}V_{DS}}{v_{sat}L}} \sqrt{\frac{\varepsilon_{si}qN_a}{2\psi_s}} \left(\frac{kT}{q}\right)^2 \left(\frac{n_i}{N_a}\right)^2 e^{q\psi_s/kT} \left(1 - e^{-qV_{DS}/kT}\right)$$

(3.4)

where  $v_{sat}$  is the carrier saturation velocity.

In order to determine the saturation voltage, the derivative of  $I_{DS}$  w.r.t.  $V_{DS}$  is set equal to zero and solved for  $V_{DS}$ ,

$$\frac{dI_{DS}}{dV_{DS}} = K' \frac{1 - e^{-qV_{DS}/kT}}{1 + \frac{\mu_{eff}V_{DS}}{v_{sat}L}} = 0 \Rightarrow \frac{1}{U_T} e^{-V_{DS}/U_T} \left(v_{sat}L + \mu_{eff}V_{DS}\right) - \left(1 - e^{-V_{DS}/U_T}\right)\mu_{eff} = 0 \tag{3.5}$$

where  $U_T$  is equal to kT/q.

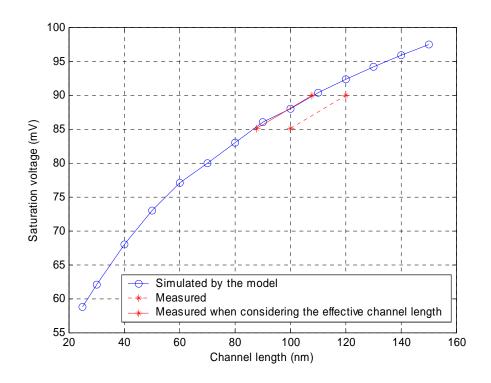

Unfortunately, (3.5) cannot be solved symbolic. It can only be solved numerically. The simulation or numerical results are compared to the measured results for the FinFET device saturation voltages in Figure 3.2. In the Figure 3.2, the saturation voltage is found to be slightly lower than the theoretical value when compared to the long channel device.

Here we define

$$V_{DSsatQ} = V_{DSsat} + V_{sm} = \Delta V \tag{3.6}$$

where  $V_{sm}$  is the safe margin voltage. The concept of  $V_{DSsatQ}$  is shown in Figure 3.3. From above, The minimum saturation voltage of  $V_{DS}$  may or should still be 100mV or greater than  $4U_T$  when considering the safety margin.

Figure 3.2 Saturation voltage for the weak inversion.  $\mu_{eff}$  is assumed 300 cm<sup>2</sup>/V·s, which is measured from the FinFET and  $\nu_{sat}$  is  $2*10^7$  cm/s.

Figure 3.3 The concept of  $V_{DSsat}$  and  $V_{DSsatQ}. \label{eq:vDSsatQ}$

### 3.1.2 Minimum threshold voltage for the analog design

Threshold voltage is another important parameter in the design of analog circuits for it directly determined the minimum supply voltage. In chapter 2, minimum threshold voltage is discussed based on digital application and from  $I_{ON}/I_{OFF}$ . Next, the minimum threshold voltage is now discussed from the analog design perspective. The current mirror circuit is a basic cell for the analog or mixed signal application. A simple current mirror circuit is shown in Figure 3.4.

Figure 3.4 The schematic of a simple current mirror.

Because saturation voltage of  $V_{DS}$  in strong-inversion is larger than that in the weak-inversion, in order to determine the minimum threshold voltage, M1 in Figure 3.4 is assumed to operate in weak-inversion for this analysis. As a result

$$V_{gs1} - \delta V_T(T) \cdot \Delta T = V_{DSsatO1} > 100 mV$$

(3.7)

Where  $\delta V_T(T)$  is the Temperature co-efficiency, which is 0.8-1.2mV/°C;  $\Delta T$  is the temperature fluctuation, and  $V_{sm}$  is the safe margin voltage required to ensure  $V_{DSsat}$  and in the presents of effective threshold variability. For  $V_{gs1}=V_T-50mV$  (operation in the weak-inversion),  $\delta V_T(T)=1$  mV/°C,  $\Delta T=150$ °C, (3.7) simplifies to

$$V_T > 300mV \tag{3.8}$$

For the wide swing current mirror of Figure 3.5, the analysis results in (3.9).

Figure 3.5 The schematic of a wide swing current mirror.

$$V_{gs1} = V_T - 50 - \delta V_T(T) \cdot \Delta T > V_{DSsatQ1} + V_{DSsatQ3} = 2 \cdot 100$$

$$\Rightarrow V_T > 250 + \delta V_T(T) \cdot \Delta T = 400 mV$$

(3.9)

From (3.8) and (3.9), the minimum threshold voltage required by analog applications is larger than 300mV.

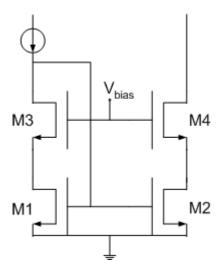

### 3.1.3 Analog circuit operation space

From the discussion in Chapter 2, we know that as the CMOS is scaled, 1) the thermal noise floor is increasing; 2) the increasing leakage current requires the sampling frequency  $f_s$  to be increased; 3)  $f_T$ , current unit-gain bandwidth, is increasing with shrinking channel length; 4) Signal swing reduces as the supply voltage reduces. All these effects can be graphically represented as Figure 3.6. The sampling frequency must increase faster than  $f_T$  as a result of the exponential nature of gate leakage with oxide scaling. The author believes that analog supply voltage scaling will likely stall at 1V.

As shown in Figure 3.6, the shaded area is the analog circuit operation space. With the device scaling, the shaded area representing the analog design space becomes smaller and is pushed to the higher frequencies. In the following section, it will be shown that to achieve the same dynamic range and bandwidth, more power is needed as a result of scaling.

Figure 3.6 Analog circuit operation space.

## 3.2 Power settling product efficiency

As shown above, with CMOS scaling, the analog designer will face a more and more restrictive design space. Substantial amount of power is required to maintain the same dynamic range and bandwidth. In the case of the battery technology, further scaling provides no great improvement. Power is expensive in this portable era. Power settling product efficiency is proposed as a means to give the analog designer guidance as to which OTA structure or parameter is the better choice for the deep sub-micro device applications.

### 3.2.1 Introduction of the power settling product efficiency

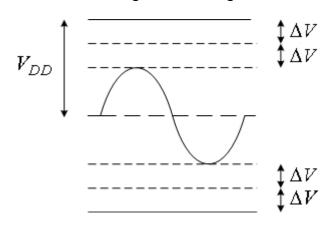

For the analog designer, scaling of the supply voltage means the output swing decreases for the same over-drive voltage shown in Figure 3.7.

Figure 3.7 The output swing.  $V_{out\text{-swing}}=2*V_{DD}-4\cdot\Delta V$ .

The output swing is

$$v_{out-swing} = 2V_{DD} - N \cdot \Delta V \tag{3.10}$$

where the N is the circuit topology factor, by example N=2, 4 and 5 represent a common source, cascode stage and telescopic stage respectively. Where a symmetrical power supply equal to  $\pm V_{DD}$  volts has been assumed.

From (3.10), one direct result of voltage scaling is the potential reduction of the Signal-to-Noise Ratio (SNR) for the same noise floor. In order to evaluate the performance limitations due to the device scaling, the power efficiency K is defined in [44]

$$K = \frac{kT \cdot \Delta f \cdot SNR}{P} \tag{3.11}$$

where k is the Boltzmann's constant, T is the temperature in Kelvin degrees,  $\Delta f$  is the signal bandwidth, and P is the consumption power.

However, in the SC circuit or discrete time application, settling time is more important than the bandwidth for wider bandwidth may not mean less settling time. Similar as power efficiency K, power settling product efficiency is defined as

$$\Pi = \frac{kT \cdot SNR}{P \cdot t_{southe}} \tag{3.12}$$

This is used to estimate how much SNR at the unit power settling time product.

Most analog circuits operated in the Class A mode whose power consumption power can be expressed as

$$P = mI_{bias}(2V_{DD}) \tag{3.13}$$

where m is a dimensionless factor, determined by the circuit topology;  $I_{bias}$  is the input transistor biasing current.

Function (3.13) can be rewritten as

$$P = m \cdot g_m \cdot \Delta V \cdot V_{DD} \tag{3.14}$$

$$P = 2mg_m \cdot n \cdot U_T V_{DD} \tag{3.15}$$

operation in the strong-inversion or weak-inversion, where  $(nU_T)^{\text{-}1}$  is the subthreshold slope.

The main noise sources are 1/f noise and broadband thermal noise. 1/f noise can be reduced to near negligible levels by circuit techniques such as chopper stabilization [45]. Only thermal noise considered here. SNR is defined

$$SNR = \frac{V_{out-swing}^2}{V_{n(rms)}^2(f) \cdot f_n}$$

(3.16)

where  $f_n$  is the noise bandwidth,  $V_{n(rms)}^2(f)$  is the noise spectral density.

For the baseband applications, most circuits can be readily represented as a single or dominant-pole system. As to the multi-poles system, it will be discussed in detail in the Chapter 4. For a single pole system, the settling time is proportional to the bandwidth, which is

$$t_{settle} = \frac{k}{\omega_{3dB}} = \frac{k \cdot C_L}{A \cdot g_m}$$

(3.17)

where  $C_L$  is the effective load capacitor,  $g_m$  is the system transconductance, A is the system gain and k is constant which is related to the settling error.

In order to give a clear and analysis expression of the power settling product efficiency, two examples are given in the later.

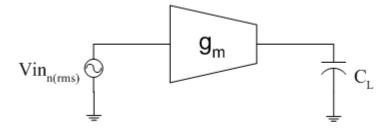

#### 3.2.2 Power settling product efficiency of the OTA

As shown in Figure 3.8, the noise of the OTA is determined by the load capacitor. The output noise voltage is

$$V_{n(rms)}^2 = \gamma kT/C_L \tag{3.18}$$

where  $\gamma$  is a constant determined by the circuit process and topology.

Figure 3.8 OTA block diagram with input referred noise

Combining (3.14), (3.16), (3.17), the power efficiency factor for the square law operation is,

$$\Pi = \frac{A(2V_{DD} - N \cdot \Delta V)^2}{km\gamma \cdot \Delta V \cdot V_{DD}}$$

(3.19)

and for the weak-inversion operation is

$$\Pi = \frac{A(2V_{DD} - N \cdot \Delta V)^2}{km\gamma \cdot nU_{T_A} \cdot V_{DD}}$$

(3.20)

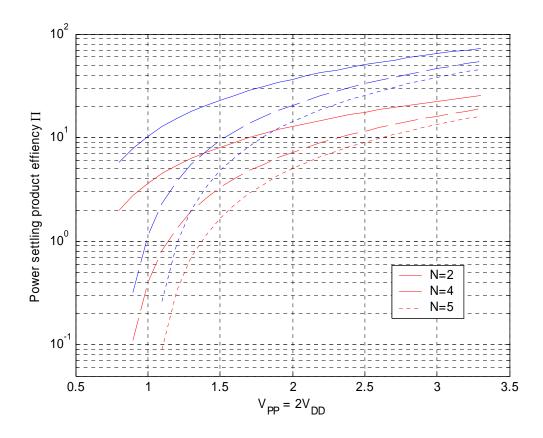

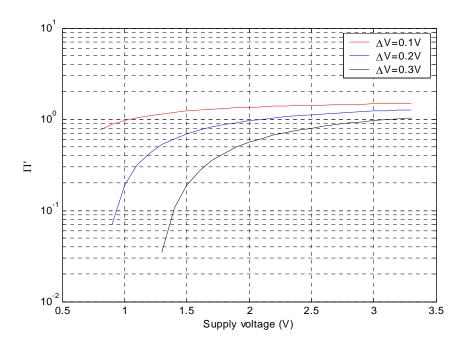

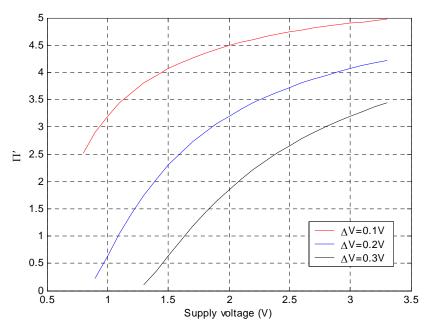

The impact of the scaling of the supply voltage to the normalized power settling product efficiency versus the topology at the constant overdrive voltage is revealed in Figure 3.9. Power settling product efficiency of N=2 (i.e. Common Source structure) topology is affected least in the three topologies. In Figure 3.9, the overdrive voltage was set to 0.2V to demonstrate that the larger overdrive voltage will cause the power consumption to dramatically increase at the low supply voltages. For the plots even it is idealistictly assumed that Vdssat is equal  $\Delta V$  to make the point. N equal 4 and 5 type structures can be represented by folded and telescopic cascode topologies. Figure 3.10

predicts that future analog circuit supply voltages based on DMS scaled devices will typically be greater than 1 V and be restricted to N type 2 to 4 devices.

Figure 3.9 Normalized the efficiency factor versus the power supply,  $\Delta V$ =0.2V. Red lines are for the square law range and blue lines for the weak-inversion range.

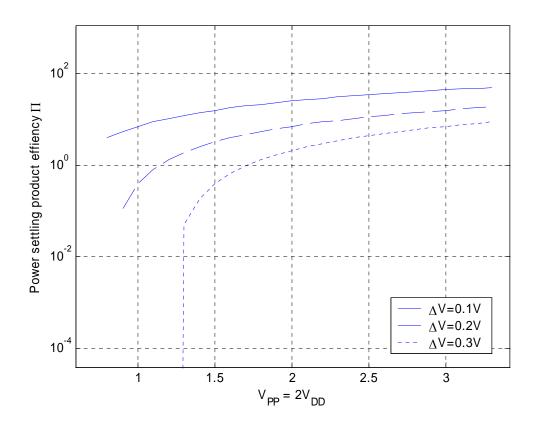

Figure 3.10 is the plot of (3.20) with the normalized power settling product efficiency versus the power supply voltage in the cascode topology, resulting in efficiency plots independent to the process. From Figure 3.10, we observe that when  $V_{PP}$  less than 1.3V, the power increases dramatically for 0.3V overdrive voltage when N=4, which means that high overdrive voltages are not suitable for use in the cascode topology when considering low supply voltage application. It is apparent from Sections 2.2 that future DSM devices will operate in velocity saturation or subthreshold to achieve both low  $V_{dssat}$ , 75 to 150mV, and low 1/f noise. As a result the relevant plots are for  $\Delta V$  are in

the 0.1 to 0.2V range. From Figures 3.9 and 3.10 one concludes that power efficient analog circuits (N=4) must operate with 1.0 to 1.2V supplies for 100 mV and 200mV  $V_{dssats}$  respectively. However, the price of 1.5V supplies is potential increase in DIBL and the return of GIDL. Given assuming a 1.1 Volt supply and  $V_{dssats}$  equals 100mV, N=2 through 4 circuits will be feasible, while if only a 200mV  $V_{dssat}$  can be achieved the bulk of analog circuits will be N=2 for non-weak inversion operation.

Figure 3.10 Normalized the efficiency versus the power supply, N=4.

### 3.2.3 Power efficiency factor of the switched-capacitor gain stage

A representative switched-capacitor gain stage is shown as Figure 3.11. Its noise power is composed of two parts: thermal noise induced by the switches and OTA itself. The thermal noise induced by the switches is

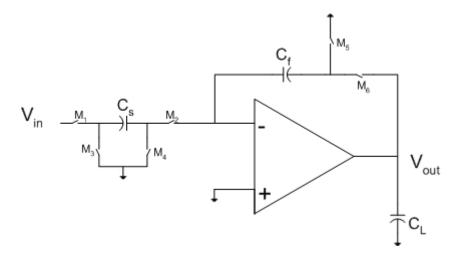

Figure 3.11 Switched-capacitor gain stage schematic.

$$V_{n1}^2 = \frac{2kT}{C_s} {(3.21)}$$

$$V_{n2}^2 = \frac{kT}{C_f} {(3.22)}$$

$$V_{n3}^2 = \frac{kT}{C_L} \tag{3.23}$$

where  $V_{n1}^2$  is the switches  $M_1$ - $M_4$ , generated the noise;  $V_{n2}^2$  is the top switch  $M_5$  generated noise,  $V_{n3}^2$  is  $M_6$  generated noise. Ignoring 1/f noise contributions, the total noise at the output of the gain stage is

$$V_{n_{\_switch(rms)}}^{2} = \frac{2kT}{C_{s}} \cdot \left(\frac{C_{s}}{C_{f}}\right)^{2} + \frac{kT}{C_{f}} + \frac{kT}{C_{L}} = \frac{(1-f)kT}{fC_{s}} \left(\frac{2-3f}{f}\right) + \frac{kT}{C_{L}}$$

(3.24)

where

$$f = \frac{C_f}{C_f + C_s}$$

.

If assuming  $C_s = \alpha C_L$ , (3.24) can be simplified to

$$V_{n\_switch(rms)}^{2} = \frac{kT}{C_{I}} \left( \frac{(1-f)(2-3f)}{f^{2}\alpha} + 1 \right)$$

(3.25)

The total noise is

$$V_{n(rms)}^{2} = \frac{kT}{C_{L}} \left( \frac{(1-f)(2-3f)}{f^{2}\alpha} + 1 + \gamma \right)$$

(3.26)

The settling time of the gain stage is

$$t_{settle} = \frac{k \cdot C_L}{A \cdot g_m} = \frac{f \cdot k \cdot C_L}{(1 - f) \cdot g_m}$$

(3.27)

Combining (3.14), (3.16),(3.26), and (3.27), the power settling product efficiency for the saturation range is

$$\Pi = \frac{(1-f)(2V_{DD} - N \cdot \Delta V)^2}{mk \cdot \Delta V \cdot V_{DD} \cdot f(\frac{(1-f)(2-3f)}{f^2 \alpha} + 1 + \gamma)}$$

$$= \frac{(2V_{DD} - N \cdot \Delta V)^2}{mk \gamma' \cdot \Delta V \cdot V_{DD}}$$

(3.28)

For the same feedback factor, (3.28) is almost the same as the (3.19).  $\gamma$ ' is the same as the  $\gamma$  representing the configuration factor independent of process. From (3.28), similar conclusions will be derived as (3.19). Furthermore, for the same  $\alpha$ ,  $\beta$ ,  $\gamma$ ', different stage gains or feedback factor vs. the normalized  $\Pi$  is shown in Figure 3.12.

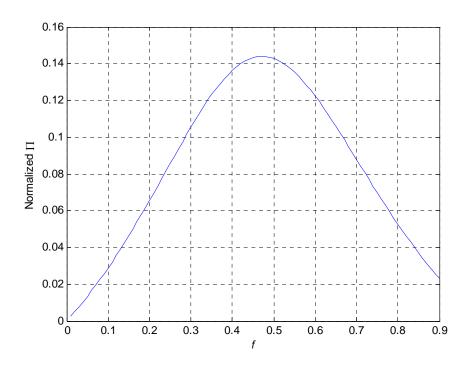

Figure 3.12 Normalized  $\Pi$  versus f for  $\alpha = 1/2$ , and  $\gamma = 4$ .

From the Figure 3.12, we can get one important conclusion that, there is maximum power settling product around feedback factor around 1/2. This point is very important in the later pipelined ADC design.

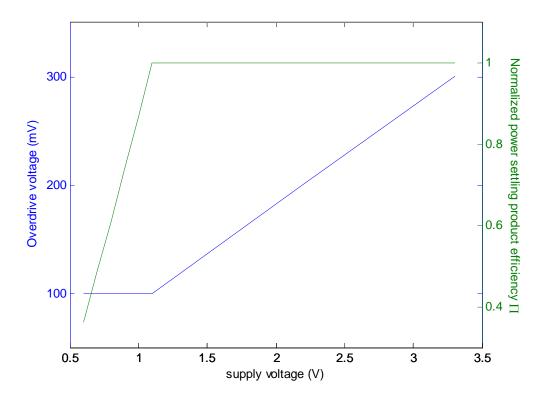

# 3.3 Analog scaling rule

From the Figure 3.10, we observe that the power settling product efficiency reduces with the scaling of the supply voltage for the same overdrive voltage. We also find that the reduction of the overdrive voltage can improve the power settling product efficiency with the reduction of the supply voltage. Here we defined the analog scaling rule as follows; the overdrive voltage should scale at the same the rate or faster than the

supply voltage to keep the power efficiency constant or improving. This is readily observed from the (3.19) and (3.20).

If one uses a 300mV overdrive voltage and assumes a 3.3V technology as a reference, the overdrive voltage will scale down to 100mV for a 1.1V supply voltage to keep the power efficiency constant. From the above analysis and measured data, this is achievable. When the supply voltage scales below 1.1V, the transistors may have to operate in the weak-inversion range to maintain power efficiency but at a reduced bandwidth. Scaling overdrive voltage and normalized power settling product efficiency vs. supply voltage is shown in Figure 3.13. This implies a future mixed signal supply corner will be 1.1V+/-100mV.

Figure 3.13 Scaling overdrive voltage and normalized power efficiency factor vs. supply voltage.

## 3.4 Conclusion

CMOS scaling down to sub-100nm device not only affects single device performance, but also impacts on the topology choice of analog design. In this chapter, we determined that the final scaled value of the supply voltage when considering saturation voltage, threshold voltage, subthreshold, velocity saturation and know process technologies for analog design is 1.1V, and that threshold voltages must be greater than 300mV. In order to give guidance to the topology and parameters choice in the analog design, power settling product efficiency concept is proposed as criteria and analog scaling rule is proposed. In the context of the following conclusions the "low" supply voltage is assumed to be less than 1.1V. Supply voltage and overdrive voltage scaling effects on an analog circuits' performance were presented with following conclusions. 1) With the supply voltage scaling, lower overdrive voltage topologies will have greater power settling product efficiency. 2) Cascode topology may not be suitable for the low supply voltage design as a result of the poor power settling product efficiency. 3) N=5 topology is unsuitable for DSM scaling. 4) Overdrive voltage should always scale at the same or greater rate than the supply voltage to keep the same or better power settling product efficiency. 5) Supply voltages less than 1.1V supply voltage are not suitable for the portable analog applications. 6) Analog circuits are quite feasible supply levels less than 1.1V, however a dramatic power consumption penalty must be paid.

# Chapter 4

## **Power Efficiency Analysis of OTA Architecture**

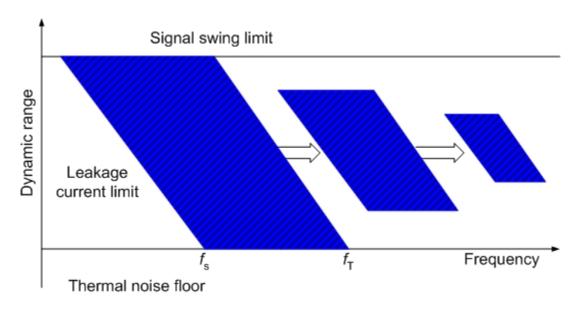

### 4.0 Introduction

Bandwidth (or settling time), accuracy (offset, noise, and gain), and power consumption are three of the most important properties of the analog design. However, they cannot be satisfied simultaneously. In order to achieve higher bandwidth (or less settling time), accuracy is often sacrificed and more power consumed. It is the analog designer's task to make the trade offs between bandwidth and accuracy at minimum power consumption. Less power is especially important in this "portable" era.

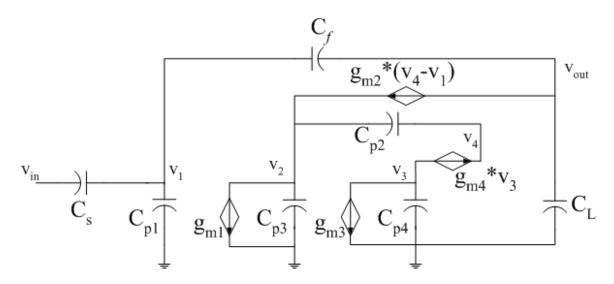

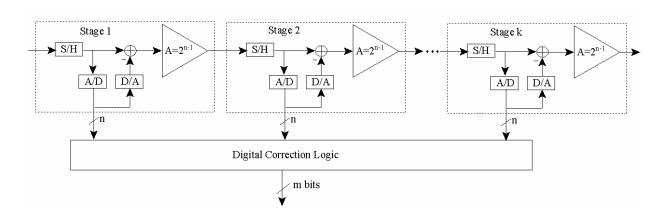

As mentioned in the Chapter 3, CMOS device scaling has continued to pursue higher bandwidth while at the same time not sacrifice transistor performance. One direct result is that supply voltage scales from 3V to sub-1V [12] for the stability considerations due to the thin gate oxide even for the long channel devices. More power is needed to obtain the same dynamic range. The other result of the scaling is the reduction of the transistor output impedance which results in less gain  $(g_m \cdot r_o \text{ or } 2V_A/\Delta V = \mu)[46]$ , where  $\mu$  is the transistor intrinsic gain. The cascode or miller compensated two-stage topologies,

typically used in the high gain applications with long channel devices, are no longer suitable in many applications especially with the sub-100nm transistors. On the other hand, end users typically demand higher and higher quality electronics products, with lower distortion for music, motion pictures, and cell phone voice etc. These applications typically demand greater than 16-bit resolution ADCs for the music compression and decompression and/or 10-12 bits 20-40Msps ADC for the cell phone IF conversion [47]. To achieve 12-bit resolution, an OTA with 75-80dB of DC gain is required for the pipelined ADC topology. This requires  $\mu^4$  or  $\mu^5$  to achieve the desired gain from a device with an intrinsic gain around 20dB. Adequate gain can only be realized by multi-stage topologies.

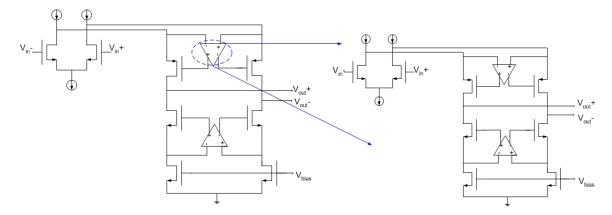

Multi-stage topologies are realized by "vertical" boosting via boosted OTAs [48] or nested boosted OTAs [49]. On the other hand, multi-stage in the "horizontal" direction includes miller compensated OTAs [50], or NGCC (Nested Gm-C Compensation) OTA [51, 52], in which each stage can be a cascode or a simple common-source stage.

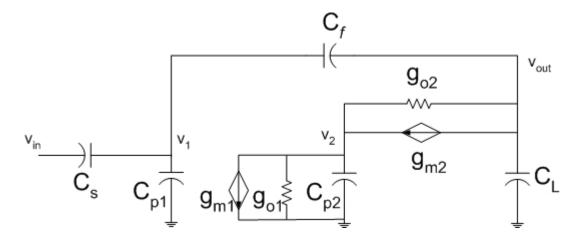

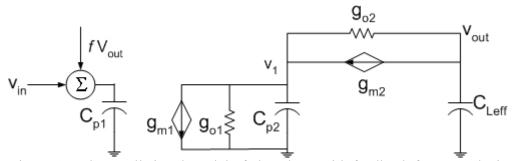

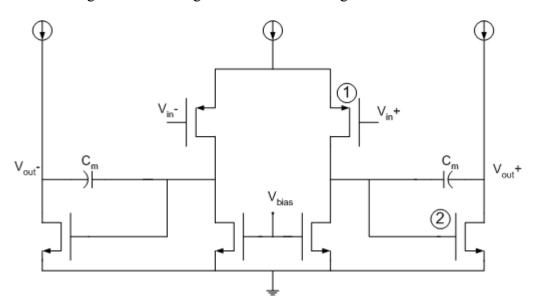

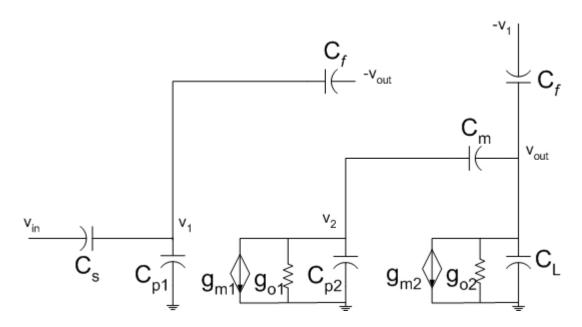

As mentioned at the beginning of this chapter, power consumption must be considered when selecting the OTA topology. However, in people's analysis of OTAs, most considerations are limited to bandwidth, or settling time and stability. The worse is that lots of works [48, 50-52] have only analyzed the open loop transfer function of the above topologies. Although several[53, 54] have analyzed the close loop, the effects of zeros are ignored due to the feed-forward signal through the bilateral feedback path.