# VLSI COMPLEXITY OF PARALLEL FOURIER TRANSFORM ALGORITHMS

BY

## TARANEH BARADARAN SEYED

Bachelor of Science Aryamehr University of Technology Tehran, Iran 1976

Master of Science Oklahoma State University Stillwater, Oklahoma 1981

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY May, 1989

TALBIS 1989D BOD3V Cop. 2

## Oklahoma State Univ. Library

# VLSI COMPLEXITY OF PARALLEL FOURIER TRANSFORM ALGORITHMS

Thesis Approved:

Thesis Advisor

Doorpust

Reid a. Pergue

Dean of the Graduate College

#### ACKNOWLEDGEMENT

I would like to thank my major advisor Dr. Louis G.

Johnson for his graceful attitude during the hardship, his thoughtful advice, and support and encouragement. I deeply owe the acheivements in my life to my husband Bijan who never compromised his love and support. My outmost gratitude to Dr. Donald Fisher for continous support and inspiration during my years at OSU. I would also like to thank the members of my advisory committee Dr. Hedrick, Dr. George, and Dr. Teague for helpful advice and support.

## TABLE OF CONTENTS

| Chapte | r                                               | Page  |

|--------|-------------------------------------------------|-------|

| ı.     | INTRODUCTION                                    | . 1   |

| II.    | FOURIER TRANSFORM COMPUTATION                   | . 4   |

|        | Discrete Fourier Transform                      | . 4   |

|        | Fast Fourier Transform                          | . 4   |

|        | Parallel Processing of DFT                      |       |

|        | N-Cell DFT Pipelines                            |       |

|        | N**2-Cell DFT Networks                          |       |

|        | Fast Fourier Transform Networks                 |       |

|        |                                                 | -     |

|        | Cascade Implementation                          |       |

|        | The FFT Network                                 | . 32  |

|        | The Perfect-Shuffle Implementation of           |       |

|        | FFT                                             | . 34  |

|        | The Mesh Implementation of FFT                  | . 39  |

| III.   | NEW PARALLEL ALGORITHMS FOR FOURIER TRANSFORM . | . 43  |

|        | N-Cell Linear Pipelines                         | . 44  |

|        | On-line Systolic DFTs                           |       |

|        | In-place Systolic DFTs                          | . 52  |

|        | N-Cell Mesh-Connected Network                   |       |

|        | N**2-Cell Mesh-Connected Network                |       |

| IV.    | VLSI COMPLEXITY OF FOURIER TRANSFORM            | . 91  |

|        | Introduction                                    | . 91  |

|        | VLSI Model of Computation                       |       |

|        | Notations and Metrics                           |       |

|        | Assumptions                                     |       |

|        | The Area-Time Performance of Basic              | . ,   |

|        |                                                 | . 102 |

|        | Components                                      | . 102 |

|        | VLSI Complexity of Parallel Fourier             | 100   |

|        | Transform Algorithms                            | . 106 |

|        | Linear Pipeline Architectures                   |       |

|        | Fourier Transform Networks                      | . 128 |

|        | N-Cell Mesh-Connected                           |       |

|        | Architectures                                   |       |

|        | Fast Fourier Transform Networks                 |       |

|        | N**2-Cell Mesh-Connected Network .              | . 140 |

| v.     | CONCLUSIONS AND RECOMMENDATIONS                 | . 147 |

| REFERE | NCES                                            | . 148 |

## LIST OF TABLES

| Table | <b>e</b>                                                                       | Page |

|-------|--------------------------------------------------------------------------------|------|

| 1.    | Physical Characteristics of the New Parallel Fourier Transform Algorithms      | 88   |

| 2.    | Computational Characteristics of the New Parallel Fourier Transform Algorithms | 89   |

| 3.    | Area and Time Complexity of the Basic Components                               | 107  |

| 4.    | Physical Characteristics of the Linear Pipeline Architectures                  | 124  |

| 5.    | Computational Characteristics of the Linear Pipeline Architectures             | 125  |

| 6.    | Approximated Area and Time Measures for Linear Pipeline Architectures          | 127  |

| 7.    | Physical Characteristics of the Mesh-Connected Networks                        | 133  |

| 8.    | Computational Characteristics of the Mesh-Connected Networks                   | 134  |

| 9.    | Approximated Area and Time Measures for Mesh Connected Networks                | 135  |

| 10.   | Physical Characteristics of the Fourier Transform Networks                     | 141  |

| 11.   | Computational Characteristics of the Fourier Transform Networks                | 142  |

| 12.   | Approximated Area and Time Measures for Fourier Transform Networks             | 143  |

| 13.   | Comparative Analysis of Different Fourier Transform Architectures              | 145  |

## LIST OF FIGURES

| Figu | re                                                                                            | Page |

|------|-----------------------------------------------------------------------------------------------|------|

| 1.   | Matrix-Vector Representation of DFT                                                           | 5    |

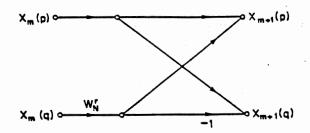

| 2.   | Two-Point Butterfly                                                                           | 7    |

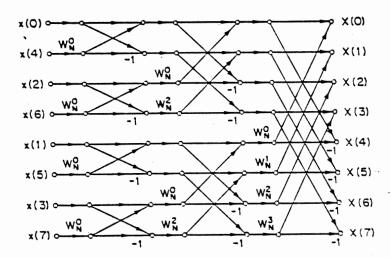

| 3.   | Flow Graph of 8-Point FFT Using the Butterfly of Figure 2                                     | 7    |

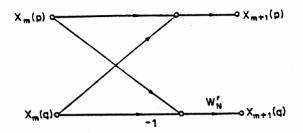

| 4.   | Butterfly for Decimation-in-Frequency Decomposition                                           | 9    |

| 5.   | Flow Graph of Complete Decimation-in-Frequency Decomposition                                  | 9    |

| 6.   | The Structure and Operation of right(a) and Left (b) Cells in 2N-1 Cell DFT Pipeline          | 12   |

| 7.   | The Structure and Operation of the Middle Cell in a (2N-1) Cell DFT Pipeline                  | 13   |

| 8.   | A Sequence of Operations of a (2N-1) Cell Pipeline for a 3-point DFT                          | 15   |

| 9.   | The Structure and Operation of Basic Cell and the Structure of the Pipeline for Recursive DFT | 18   |

| 10.  | (a) Matrix Arrangement of a one Dimensional Signal (b) Resultant Matrix                       | 20   |

| 11.  | The Input/Output Format for an N-element Mesh Connected DFT (Zhang)                           | 22   |

| 12.  | The Structure and Operation of the Basic Cell for N-Cell Mesh-Connected DFT                   | 23   |

| 13.  | Mesh-Connected DFT Network (Zhang)                                                            | 24   |

| 14.  | The Modified Design for Mesh-Connected Network .                                              | 27   |

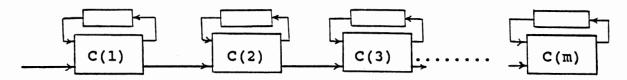

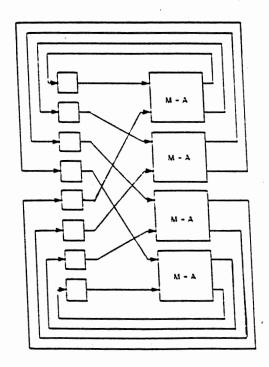

| 15.  | The Structure of the Pipeline for Cascade Implementation of FFT                               | 30   |

| 16.  | The Structure and Operation of the ith Cell in Cascade Implementation of FFT                  | 30   |

| Figu | re                                                                                                                        | Page |

|------|---------------------------------------------------------------------------------------------------------------------------|------|

| 17.  | The FFT network (Thompson 80)                                                                                             | 33   |

| 18.  | The Structure and Operation of the Basic Cell in the mth level of the FFT Network                                         | 35   |

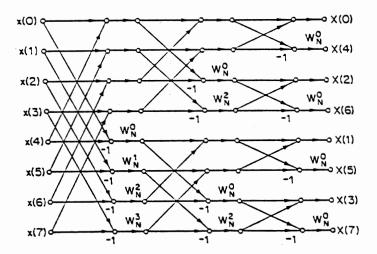

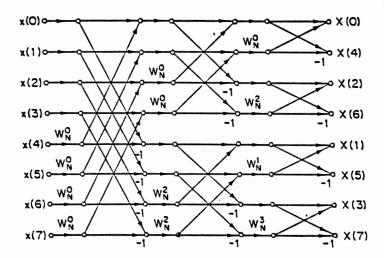

| 19.  | A Shuffle-Exchange Network for 8-point FFT (Stone 71)                                                                     | 35   |

| 20.  | The Flow Diagram of FFT Algorithm for an 8-point Signal with Input in Normal Order and Output in Bit-reversed Order       | 37   |

| 21.  | The Input Flow Through Perfect-Shuffle Network .                                                                          | 38   |

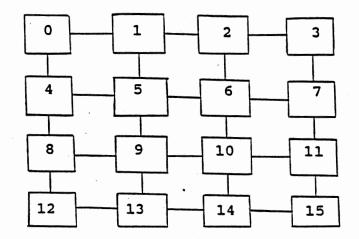

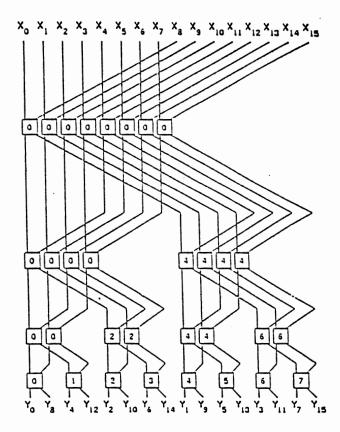

| 22.  | A Mesh Arrangement of a 16-Element Sequence                                                                               | 40   |

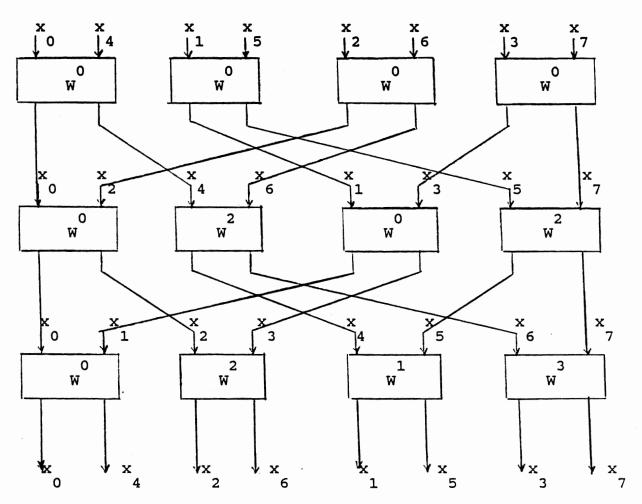

| 23.  | A 16-point FFT Network (Thompson 80)                                                                                      | 40   |

| 24.  | Fourier Transform as Vector Summation                                                                                     | 46   |

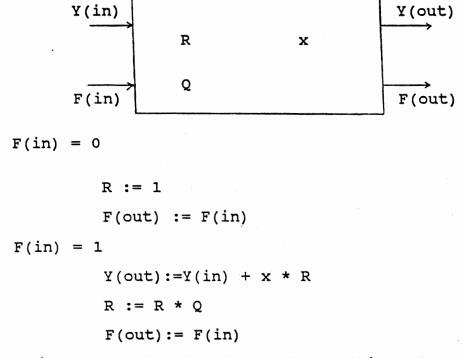

| 25.  | The Structure and Operation of a Basic Cell (a) and the Structure of the Pipeline for the On-line Systolic DFT            | 49   |

| 26.  | The Structure and Operation of Basic Cell (a) and the Structure of the Pipeline (b) for the Modified On-line Systolic DFT | 53   |

| 27.  | A List of Values of R(i,i)s and Q(i)s for Different Values of i                                                           | 57   |

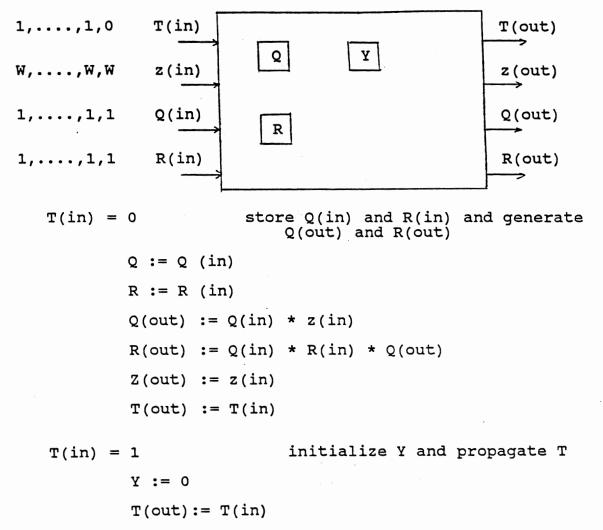

| 28.  | The Structure and Operation of the Basic Cell to Generate Q(i)s and R(i,i)s                                               | 59   |

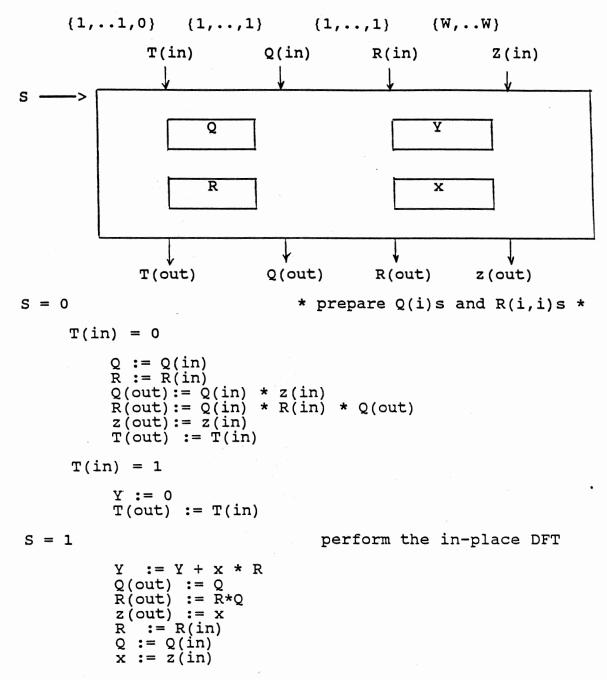

| 29.  | Structure and Operation of a Basic Cell for In-place Systolic DFT                                                         | 61   |

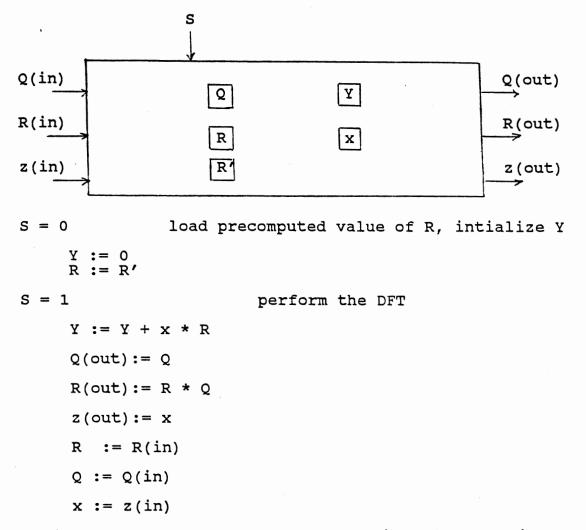

| 30.  | The Structure and Operation of the Basic Cell for Dedicated In-place DFT                                                  | 62   |

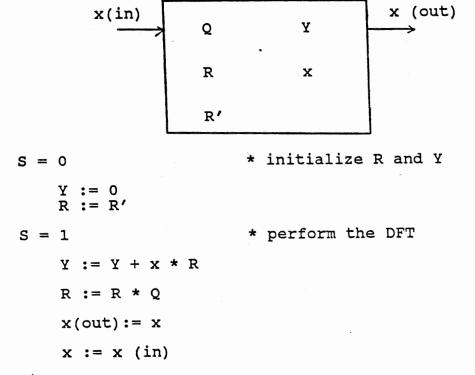

| 31.  | The Set of Coefficients Used at each Cell for N=4                                                                         | 64   |

| 32.  | The Structure and Operation of the Basic Cell for In-place DFT with Minimum Communication Lines                           | 65   |

| 33.  | The Sequence of Coefficients Used by Cells in a 4-cell Design                                                             | 66   |

| 34.  | The Structure and Operation of a Basic Cell for the bi-directional In-place Systolic DFT Pipelin                          | e 69 |

| rigu | re                                                                                                       | Page |

|------|----------------------------------------------------------------------------------------------------------|------|

| 35.  | The Structure and Operation of the Modified Cell for the Bi-directional In-place Systolic DFT Pipeline   | 70   |

| 36.  | The Structure and Operation of the Basic Cell for Linear Non-circular DFT pipeline                       | 72   |

| 37.  | The Structure of the Pipeline for the Linear Non-circular DFT                                            | 72   |

| 38.  | The Structure and Operation of the Basic Cell                                                            | 74   |

| 39.  | The Modified Basic Cell to Direct the Output Back to the Pipeline                                        | 75   |

| 40.  | The Structure and Operation of the Basic Cell for the Mesh-connected DFT Network                         | 79   |

| 41.  | The Structure of N-cell Mesh-connected DFT Network                                                       | 80   |

| 42.  | The Structure and Operation of the Cell (i,j) for the Modified Mesh Connected DFT Network                | 82   |

| 43.  | The Structure of the Modified N-cell Mesh Connected Network                                              | 83   |

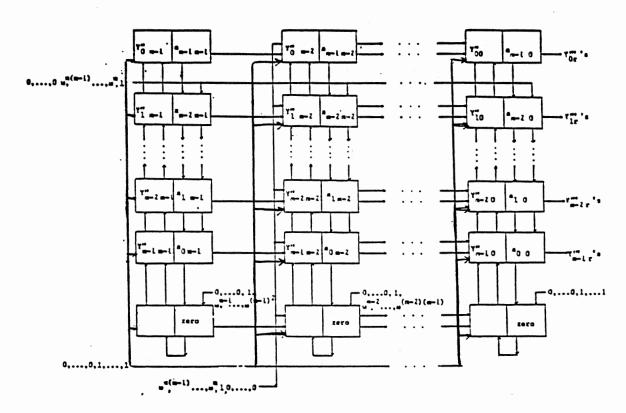

| 44.  | The Structure and Operation of Basic Cell and the Structure of the Network for the N**2-cell DFT Network | 86   |

| 45.  | An Amplifier Chain to Drive a Wire of O(K)                                                               | 98   |

| 46.  | Planar Embedding of the Perfect-Shuffle Connections                                                      | 140  |

#### CHAPTER I

#### INTRODUCTION

The Discrete Fourier Transform (DFT) is one of the most widely used transforms in signal processing, image processing and computer vision. The computationality of Fourier transform however has always been one of the major issues for users and researchers. The time complexity of the sequential algorithm for calculating the discrete Fourier transform of an N-element signal is proportional to N .

Cooley [Cooley 65] proposed a faster method for serial computation of the discrete Fourier transform known as Fast Fourier Transform or FFT. The FFT algorithm is based on the divide-and-conquer paradigm and reduces the time complexity of the computation of an N-element sequence to NlogN.

Over the last two decades a large body of knowledge has been dedicated to the processing aspects of DFT and FFT.

Researchers have persued different approaches and techniques to increase the speed of the computation of the Fourier transform. Since the speed of serial computation of the Fourier transform is machine dependent, many researchers aimed at designing dedicated hardware [Gold 73], [Despain 79]. Reducing the computation time by employing faster circuitry for basic operations used in Fourier transform,

namely, complex addition and multiplication is another approach persued by Taylor [Taylor 85], Cozzens [Cozzens 85], and Troung [Troung 86].

Significant advances in VLSI in recent years, which started a new era in massive parallelism, has opened yet another line of research in parallel processing of the Fourier transform [Thompson 80], [Despain 79], [Stone 71], [Bongiovanni 83], [Zhang 84], [Wold 84], [Gertner 87], and [Troung 88].

The serial and parallel processing of Fourier transform have been studied in two different contexts, namely, direct Fourier transform and fast Fourier transform. Each method offers certain degree of freedom and suffers certain restrictions on the size of the sequence, form of the input/output, and the size and capability of the basic computational units and the interconnections between them.

The area-time trade-off as a common measure for algorithmic and VLSI complexity has been used to approximate the goodness of the algorithms and their associated VLSI implementation. Thompson [Thompson 80] has derived a set of assumptions and rules for the analysis of the VLSI complexity of circuits. He has also derived a lower bound for the area-time complexity of VLSI design of circuits which solve an N-element Fourier transform problem.

In Chapter II, a detailed description of the techniques used to calculate an N-element Fourier transform is presented. Chapter III presents a set of new methods

proposed by this study. In Chater IV the set of assumptions and rules used in the analysis of VLSI complexity of circuits are presented. Also different area-time measures and their applicability are discussed. Based on these assumptions, different layouts for the basic circuitry used in the VLSI design of Fourier transform solving circuitry and their area and time complexity are analyzed. And finally, an in depth analysis of the VLSI complexity of all methods under different area-time measures is presented.

#### CHAPTER II

#### FOURIER TRANSFORM COMPUTATION

Fourier transform computation is based on two different paradigms, the Discrete Fourier transform and the fast Fourier transform. This chapter is dedicated to the description of these methods and the detailed explanation of the parallel techniques to implement them.

#### Discrete Fourier Transform

The Direct Fourier transform of a finite sequence  $\{x(n), n=0,1,\ldots,N-1\}$  may be expressed as  $\{Y(n), n=0,1,\ldots,N-1\}$  where

$$Y(k) = \sum_{n=0}^{N-1} x(n) W 0 \le k \le N-1$$

(2.1)

and W = EXP (-2nj/N). DFT may also be represented in a N matrix-vector multiplication form as depicted in Figure 1.

The direct computation of Fourier transforms using matrix2 vector multiplication has a time complexity of O(N).

#### Fast Fourier Transform

Cooley [Cooley 65] has reformulated equation 2.1 and proposed a new method based on the divide-and-conquer para-

| Y                |   | 1 | 1             | 1                    | 1             | (x )             |

|------------------|---|---|---------------|----------------------|---------------|------------------|

| Y                |   | 1 | W             | 2<br>W               | N-1<br>W      |                  |

| Y 2              |   | 1 | <b>2</b><br>W | <b>4</b><br>W        | 2 (N-1)<br>W  | x 2              |

|                  | = |   | _             |                      |               |                  |

|                  |   |   | •             | •                    | :             | 1.               |

| •                |   |   | •             | •                    | •             | :                |

| •                |   | • | •             | •                    | •             |                  |

| Y <sub>N-1</sub> |   | l | W-1           | w <sup>2 (N-1)</sup> | W (N-1) (N-1) | x <sub>N-1</sub> |

Figure 1. Matrix-Vector Representation of DFT.

digm. This method is called the Fast Fourier Transform or FFT. The FFT is based on the decomposition of the DFT into successively smaller DFTs. Algorithms based on the decomposition of  $\{x(n)\}$  are called decimation-in-time algorithms [Oppenheim 75].

The principle of decimation-in-time algorithms is best m presented by considering the special case of N=2 . Since N is an even number  $\{ x(n) \}$  may be separated into two N/2-point sequences consisting of even-numbered elements in  $\{ x(n) \}$  and odd-numbered elements in  $\{ x(n) \}$ . Equation 2.1 is thus rewritten as:

$$Y(k) = \sum_{n \text{ even}} x(n) \overset{nk}{W} + \sum_{n \text{ odd}} x(n) \overset{nk}{W} \qquad 0 \le k \le N-1$$

Then by exploiting the characteristics of W , the equation  $$\rm N$$  may be rewritten as

$$Y(k) = \sum_{r=0}^{N/2-1} x(2r) W + W \sum_{r=0}^{k} x(2r+1) W (2.2)$$

$$= G(k) + W H(k)$$

where G(k) is the N/2-point DFT of the even-numbered points of  $\{x(n)\}$  and H(k) is the N/2-point DFT of the odd-numbered points of  $\{x(n)\}$ .

Therefore, the computation of an N-point DFT may be decomposed into two computations of N/2-point DFT. If N =  $^{\rm m}$ 2, then the decomposition may further be applied m times until a simple 2-point DFT is reached. The 2-point DFT known

Figure 2. Two-point Butterfly

Figure 3. Flow Graph of 8-point FFT

Using the Butterfly of

Figure 2

as a butterfly computation is presented in Figure 2. The results of 2-point DFTs are then combined to calculate the 4, 8, ..., N point DFTs. The complete flow graph of an 8-point DFT using decimation-in-time algorithm is presented in Figure 3 [Oppenheim 75]. The computation is completed after logN (base 2) steps and each step requires N/2 butterfly operations. Therefore, a complete FFT computation of an N-point FFT has (N/2)logN computational steps which yeilds an O(NlogN) time complexity. The input data appears in bit-reversed order, but the output is in natural order. Oppenheim [Oppenheim 75] presents alternative formulations of decimation-in-time algorithms.

Another class of FFT algorithms, namely, decimation-in-frequency algorithms are based on the decomposition of {Y(n)} in the same manner. Figure 4 represents the butterfly operation for decimation-in-frequency algorithm. Figure 5 represents a complete flow graph of the computation for an 8-point sequence using decimation-in-frequency algorithm.

Recent advances in massive parallel processing promises faster computation of Fourier transforms. The following two sections are dedicated to the detailed description of parallel techniques to evaluate the Fourier transform of an N-element sequence based on the DFT and FFT respectively.

#### Parallel Processing of a DFT

The parallel computation of a DFT is mainly based on Equation 2.1. The symmetrical nature of the matrix of the coefficients shown in Figure 1 and the relationship between

Figure 4. Butterfly for Decimation-in-Frequency

Figure 5. Flow Graph of Complete Decimation-in-Frequency Decomposition.

the elements of this matrix inspired many parallel techniques [Kung 80], [Mead 80], [Zhang 84], [Thompson 80].

The difference between these approaches stems from the assumptions on the size of the sequence and the number of processing elements used in the design. The detailed description of each technique is presented in the following section. The VLSI complexity of these techniques along with others are analyzed in Chapter IV.

## N-cell DFT Pipelines

Kung and Leiserson [Mead 80] were the first to propose a pipeline of processing elements to compute the DFT of an N-element sequence. The pipeline has 2N-1 cells to compute the DFT of an N-element sequence  $\{x(n)\}$ . Cells operate on 50 percent duty cycle. The input sequence enters the pipeline from the leftmost cell with a 50 percent duty cycle. Zerovalued  $\{Y(n)\}$  enters the pipeline from the rightmost cell again with a 50 percet duty cycle. No operation is performed for the first N-1 cycles or until both x(0) and Y(0) reach the middle cell.

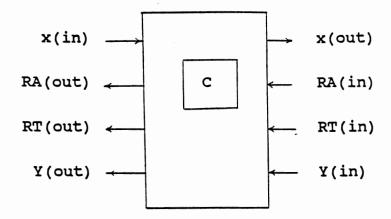

The middle cell is a special cell and it generates all the coefficients required by the transform. Coefficients are then propagated to both the right and the left cells. Register C in each cell is dedicated to the coefficient and is updated by the values that are generated by the middle cell and propagated by other cells. These values are labeled RA and RT.

the elements of this matrix inspired many parallel techniques [Kung 80], [Mead 80], [Zhang 84], [Thompson 80].

The difference between these approaches stems from the assumptions on the size of the sequence and the number of processing elements used in the design. The detailed description of each technique is presented in the following section. The VLSI complexity of these techniques along with others are analyzed in Chapter IV.

## N-cell DFT Pipelines

Kung and Leiserson [Mead 80] were the first to propose a pipeline of processing elements to compute the DFT of an N-element sequence. The pipeline has 2N-1 cells to compute the DFT of an N-element sequence  $\{x(n)\}$ . Cells operate on 50 percent duty cycle. The input sequence enters the pipeline from the leftmost cell with a 50 percent duty cycle. Zerovalued  $\{Y(n)\}$  enters the pipeline from the rightmost cell again with a 50 percet duty cycle. No operation is performed for the first N-1 cycles or until both x(0) and Y(0) reach the middle cell.

The middle cell is a special cell and it generates all the coefficients required by the transform. Coefficients are then propagated to both the right and the left cells. Register C in each cell is dedicated to the coefficient and is updated by the values that are generated by the middle cell and propagated by other cells. These values are labeled RA and RT.

## a) Structure of Left Cells

b) Structure of right cells

### OPERATION

Figure 6. The structure and Operation of right (a) and left (b) cells in 2N-1 Cell DFT Pipeline.

### OPERATION

Figure 7. The Structure and Operation of the Middle Cell in a (2N-1) Cell DFT Pipeline.

When cell i is active, it receives Y from its right neighbor and x from its left neighbor and RA and RT from its left/right neighbor based on whether cell i is located at the right/left of the middle cell. Then it performs the multiply-add operation and sends Y to its left neighbor and x to its right neighbor.

The structure and the operation of cells are depicted in Figure 6. Figure 6a represents the structure of the cells to the left of the middle cell. Figure 6b represents the structure of the cells to the right of the middle cell.

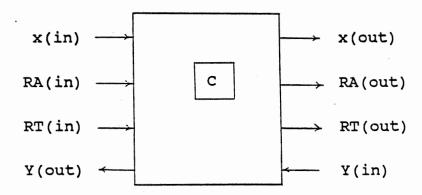

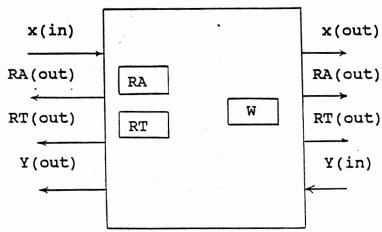

The structure and operation of the middle cell is special and different from other cells. This cell generates and propagates the appropriate coefficients to all other cells. The structure and operation of the middle cell is depicted in Figure 7. Registers RA and RT in the middle cell are initially one and the register labeled W contains EXP(-20 j/N). A sequence of the operations of the pipeline for a 3-point DFT is depicted in Figure 8. Each cell is labeled with its current value of x, y, and C, the coefficient used in multiply-add operation is circled. After 2N-1 cycles through the pipeline, Y(0) is out, Y(1) will be out after 2 more cycles, and finally, it takes 2N-2 more steps after the compeletion of Y(0) to output Y(N-1). Therefore, 4N-3 cycles are required to compute an N-point DFT. Each step requires two multiplications and one addition.

There are 2N-2 simple cells, each containing a register C, a multiplier and an adder. The middle cell performs five multiplications and an addition at each step. A faster

Figure 8. A Sequence of Operations of a (2N-1) Cell Pipeline for a 3-point DFT.

multiplier or several multipliers may be provided in the middle cell to avoid a slow down throughout the pipeline. Each cell requires four input and four output lines.

Basically, this design employs 2N-1 cells each containing a multiply-add circuitry and a register. This approach reaches a 4N-3 cycles of computation for an N-element DFT. The pipeline time (elapsed time between the input of two consecutive sequences) is also 4N-3 since a new computation may not start unless the previous computation is completed.

Kung [Kung 80] has proposed another linear pipeline implementation based on the recursive formulation of the DFT. Given the input sequence  $\{x(n)\}$ , the computation of the Fourier transform of the sequence,  $\{Y(n)\}$ , can be viewed as that of evaluating the polynomial

$$N-1$$

$N-2$   $x(N-1)P + x(N-2)P + .... + x(1)P + x(0)$

At P = 1, W, W, W, ...., W. The polynomial can be rewritten as:

$$(\ldots((P x(N-1) +x(N-2))P + x(N-3))P + \ldots + x(1))P + x(0)$$

The recurrence formula can be rewritten as follows:

$$0 \ Y (i) = x(N-1)$$

$0 \le i \le N-1$

$$k$$

$k-1$   $i$   $Y$   $(i) = Y$   $(i)$   $P + x(N-1-k)$   $1 \le k \le N-1$

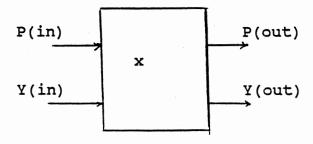

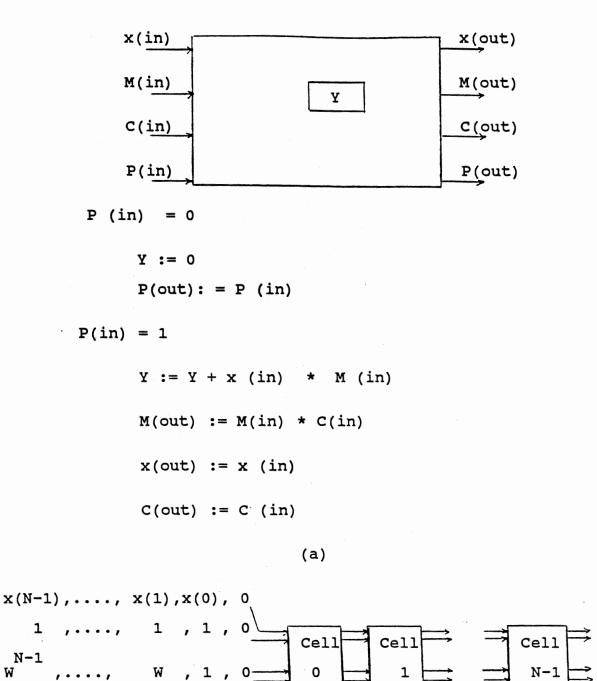

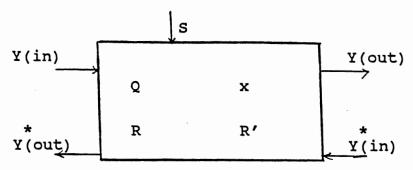

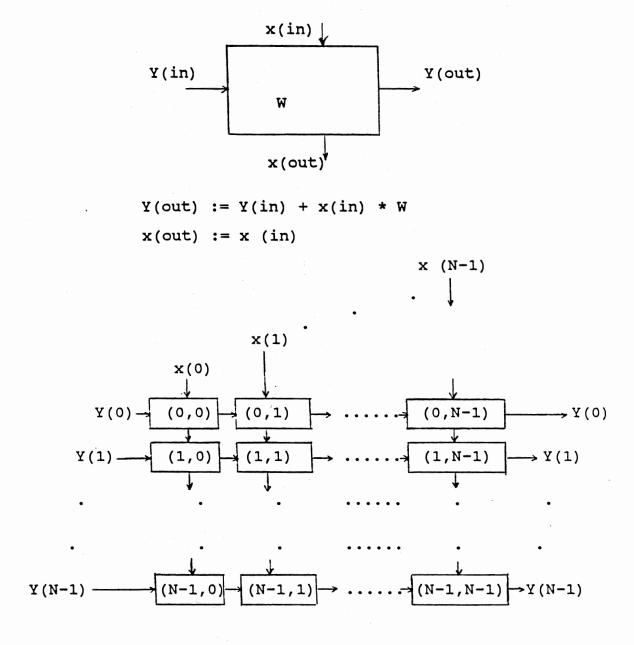

Then Y(i) = Y (i). The structure of a basic cell, its operation, and the structure of the pipeline is depicted in Figure 9.

The full pipeline consists of N-1 cells. The inputs Y(in) and P(in) to the leftmost cell are x(N-1) and some power of W respectively. Y(0) leaves the pipeline after N-1 cycles from the rightmost cell and Y(N-1) will leave the pipeline after N-2 more cycles. Therefore, the processing time of a sequence is 2N-3 cycles. A new sequence may start its load and computation after N cycles or immediately after Y(N-1) has left the leftmost cell. Therefore, the pipeline time is N.

The basic cells in the pipeline require a register and a multiply-add circuitry. It also needs two input and two output lines. Inter-cell connections are near-neighbor.

A set of new linear pipeline approaches proposed in this research will appear in chapter III. The main advantage of linear approaches lie on the fact that the implementation is not restricted by the input size. In other words, for any given N, a linear pipeline could be constructed which solves the Fourier transform problem for any sequence {x(m)} given m <= N and assuming that appropriate P values are provided.

It is possible to decompose the DFT of a sequence  $\{x(n)\}$  to smaller DFTs and then combine the results into  $\{Y(n)\}$ . Gold and Bially [Gold 73] outlined a method to

$$P(out) := P(in)$$

$Y(out) := Y(in) * P(in) + x$

Figure 9. The Structure and Operation of Basic Cell and the Structure of the Pipeline for Recursive DFT.

factor a T-point sequence into a two-dimensional matrix. If T is a composite number, it can be factored into a product of integers. If T is a prime number, the original signal can usually be augmented with zeroes to obtain a composite number.

Let  $T = M \times L$  be the number of elements in the input sequence. Then  $\{x(n), n=0,1,\ldots,T-1\}$  may be rearranged into a two-dimensional matrix with M rows and L columns as shown in Figure 10a. The computational steps required to calculate the Fourier transform of a one-dimensional sequence rearranged into a matrix are as follows:

- 1) Calculate the DFT of each row individually, the  $$\rm L$$  kernel of these transforms is W  $_{\rm T}$

- 2) Multiply each term in the resultant matrix by W where i and j are the row and column indices of each term respectively,  $0 \le i \le M-1$ ,  $0 \le j \le L-1$

- 3) Calculate the DFTs of each column individually, the  $$\rm M$$  kernel of this DFT is W  $_{\rm T}$

The resultant matrix is shown in Figure 10b.

Since steps 1 and 3 are performed in parallel, the computation time is proportional to M+L. Given T = MxL, M+L 1/2 will be minimized if M=L or M = T. Therefore, the matrix arrangement of a one-dimensional signal is most effective when T is a complete square.

Zhang [Zhang 84] was the first to propose an N-cell

(b)

Figure 10. (a) Matrix arrangement of a one dimensional signal (b) resultant matrix.

mesh-connected network for DFT. His approach is based on the above formulation. Kung's recursive DFT is used to compute individual row and column DFTs.

The N-element sequence, N = m, is rearranged into an  $m \times m$  matrix. The format of the rearranged input is shown in Figure 11a. Figure 11b represents the format of the output from the network. Neither the input nor the output have the natural form.

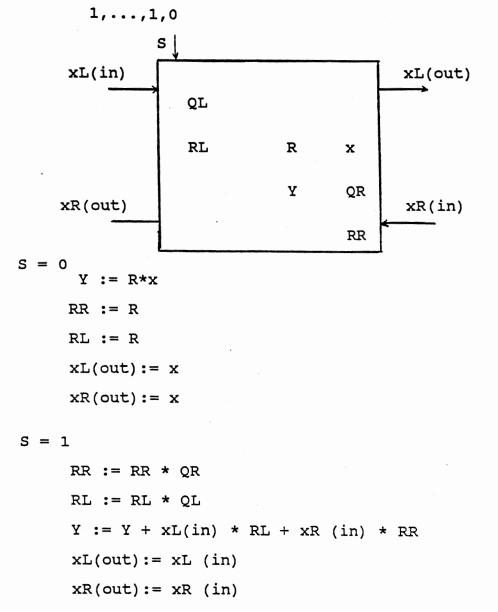

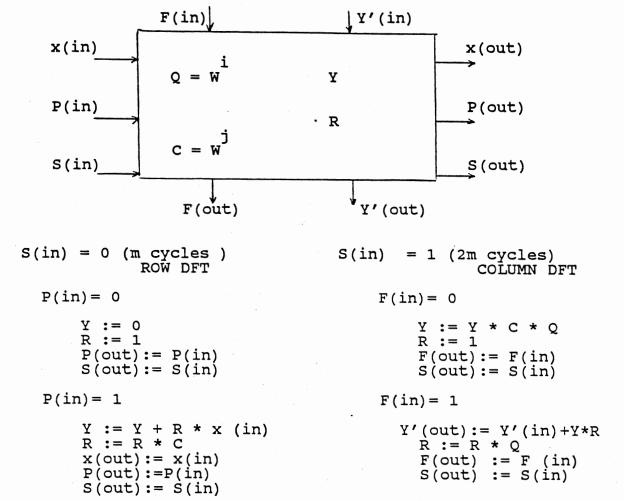

The basic cell in Kung's recursive formulation is modified to allow both row and column DFTs. The structure and operation of the basic cell is represented in Figure 12. A control signal S is used to distinguish column and row DFTs.

Process starts with calculating column DFTs. After m-1 cycles the first element of the Fourier transform is out.

This output and the following outputs are multiplied by appropriate W and shifted back to the same column to be used in row DFTs. Register x in the basic cell is used for shift operation. An extra cell is added to the end of each column pipeline as the last row of the matrix which is used to multiply the output of the pipeline by W and shift it back to the pipeline.

After m more steps, column DFTs are complete and row DFTs may be initiated which will be complete after 2m-2 steps. The complete process requires 4m-2 cycles.

The complete structure of the m x m mesh-connected network is shown in Figure 13. The network has mxm basic cells and an extra row of cells to accomplish local

$$\begin{bmatrix} x(m-1,m-1) & x(m-1,m-2) & \dots & x(m-1,0) \\ x(m-2,m-1) & x(m-2,m-2) & \dots & x(m-2,0) \\ \vdots & \vdots & \ddots & \vdots \\ x(0,m-1) & x(0,m-2) & \dots & x(0,0) \end{bmatrix}$$

(a) input

$\begin{bmatrix} Y(0,m-1) & Y(0,m-2) & \dots & Y(0,0) \\ Y(1,m-1) & Y(1,m-2) & \dots & Y(1,0) \\ \vdots & \vdots & \vdots & \vdots \\ Y(m-1,m-1) & Y(m-1,m-2) & \dots & Y(m-1,0) \end{bmatrix}$

(b) output

Figure 11. The Input/Output Format for an N-element Mesh-connected DFT (Zhang).

Figure 12. The Structure and Operation of the Basic Cell for N-cell Mesh-connected DFT.

Figure 13. Mesh-connected DFT Network (Zhang).

multiplications. Two multipliers generate the appropriate Ps used in the recursive formulation of DFT for the column and row DFTs. The output of these multipliers are input to the cells in the second row of the network (for the column DFTs) and the second column of the network (for the row DFTs). M ij more multipliers are needed to generate the W s, one for each column of cells. Therefore, the complete design 1/2 requires N basic cells and N +2 multipliers. The basic cell as depicted in Figure 12 requires two registers x and \*x , and a multiply-add circuit. Each cell has 6 input and 6 output lines.

The design of the basic cell and the network as appeared in [Zhang 84] using a single local control signal S is incorrect. According to the specifications, the control signal S should remain 1 for 2m cycles to guarantee the correct calculation of the column DFTs and their shift back to the cells. Therefore, one-valued S must be input to the cells in the second row of the matrix from the first cycle until the last cycle of the column DFTs or for 2m consecutive cycles. At this point S must be changed to zero in all cells to inhibit any further shift and propagation of (results of the column DFTs). Therefore, S must be a global signal (connected to all cells). Otherwise if S is set to zero, while directly connected to the last row of cells, other cells are still receiving the value of one and propagating the calculated x s which will result in a faulty outcome.

In summary, in order for this design to work correctly, S must be directly connected to all cells. The consequence of the direct connection of S to all cells is an increase in the area of the design which has a negative effect on its performance. The modified mesh-connected network with S directly connected to all cells is represented in Figure 14.

A new N-cell mesh-connected network using a different formulation and mechanism for row and column DFTs is presented in Chapter III as a part of this study.

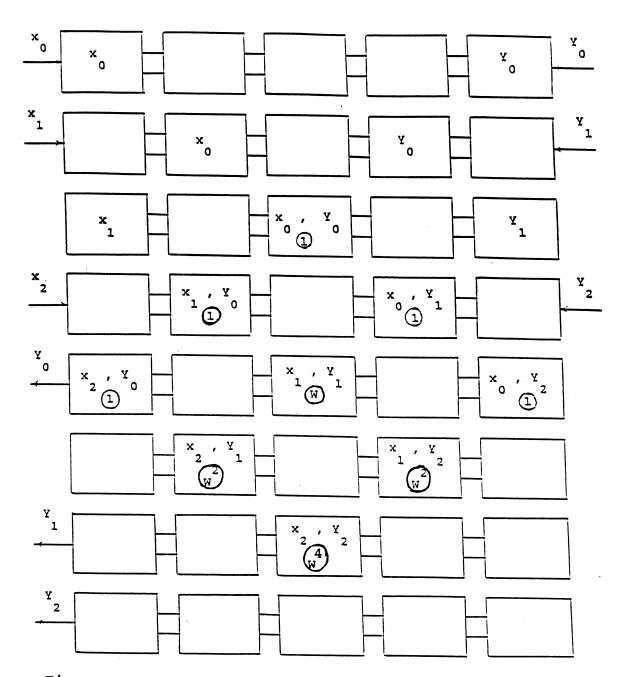

## N -Cell DFT Networks

Another approach to the calculation of DFT may employ a multitude of pipelines of N cells to boost the time efficiency by avoiding the recirculation of the intermediate results. Thompson [Thomson 83] refers to such a design. In this design the non-recursive linear pipeline proposed by Kung is used as the basic computational approach. 4N-3 basic pipelines constitute the complete design which unrolls the computation onto 4N-3 rows of 2N-1 cells. There are actually 2 about 8N cells in this N -cell design. Thompson suggests the possibility of some reductions in the size which leaves 2 2N cells in the network. In Chapter III a new mechanism using only N cells along with detailed description is presented.

The Fast Fourier transform is shown to calculate the Fourier transform more efficiently on a single processor system. Many authors have proposed hardware implementations consisting of many processing cells based on this algorithm.

Figure 14. The Modified Design for Mesh-connected Network.

#### Fast Fourier Transform Networks

There are a number of versions of the FFT algorithm [Oppenheim 75]. The FFT algorithms mainly differ in the order of input, output and the coefficients used. Two algorithms, decimation—in—time and decimation—in—frequency are presented in this chapter. Either algorithm has a time complexity of O(NlogN) on a uni—processor system. Several dedicated, multi—cell designs based on the FFT are presented in the following sections.

## Cascade Implementation

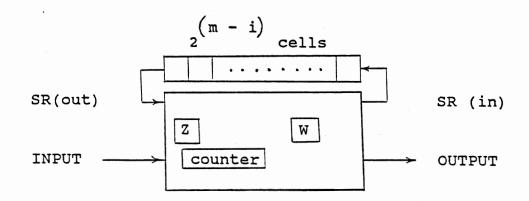

The cascade implementation was first proposed by

Despain [Despain 79]. It is based on the decimation-in

frequency algorithm. The flow graph for an 8-point FFT based

on decimation-in-frequency with inputs in normal order and

outputs in bit-reversed order is presented in Figure 5. This

flow graph is used to describe the details and the mechanism

of the cascade implementation.

register with one cell. Cells are arranged as a pipeline. The structure of the pipeline is depicted in Figure 15.

Each cell has two input and two output lines. The output line SR(in) is connected to the input of the associated shift register, while the other output line OUTPUT is connected to the next cell in the pipeline. One of the two input lines of each cell, SR(out), is connected to the output of the associated shift register while the other input line INPUT is connected to the output of the previous cell. INPUT to the leftmost cell is the line where the input signal enters the cascade and the OUTPUT line of the rightmost cell sends the results of the calculation out. Each cell saves the input values or the intermediate results until the associated input value or intermediate result is input to the cell for butterfly calculation. For example, in a case of 8-point FFT whose flow graph is represented in Figure 5, the leftmost cell C(1) inputs x(0), x(1), x(2), and x(3). and shifts them into the shift register of length 4. When x(4) appears on the INPUT line of C(1), its butterfly correspondent x(0) appears on SR(out), at this point the butterfly operation is performed. x(0)+x(4) is sent to the next cell while (x(0)-x(4))W is sent to the shift register. In the following step, the butterfly operation is performed on x(1) and x(5) and x(1)+x(5) is sent to the next cell while (x(1)-x(5))W is sent to the shift register. The next step generates (x(2)+x(6)) and (x(2)-x(6)) W . At this point the shift register of C(2) is full and SR(out) in C(2) has (x(0)+x(4)) where combined with

Figure 15. The Structure of the Pipeline for Cascade Implementation of FFT.

leftmost-bit of counter = 0

SR(in) := INPUT

OUTPUT := SR (out)

leftmost-bit of counter = 1

OUTPUT := SR(out) + INPUT

SR(in) := (SR(out) - INPUT) \* Z

Figure 16. The Structure and Operation of the ith Cell in Cascade Implementation of FFT.

(x(2)+x(6)) performs the topmost butterfly operation of the second column of Figure 5. During the next phase, the second butterfly from the top on the second column of Figure 5 is performed whose result combined with (x(0)+x(4)) + (x(2)+x(6)) stored in the single register of C(3) generates X(0) which leaves the system on the OUTPUT line of C(3).

Therefore, each cell C(i) performs 2 butterfly (m-i) operations every 2 cycles. During the first 2 cycles, cells accumulate the results of the previous cycles until their associated butterfly couples are generated, then (m-i) during the following 2 cycles the butterfly operations are performed. In general, C(1) performs the butterfly operations at the first column of Figure 5, C(2) performs those in the second column and C(3) performs the ones in the third column.

In order to keep track of cycles associated with each cell there is a (m-i)-bit counter. As long as the leftmost bit of the counter is zero, the cell simply accumulates its input values and sends the output of its shift register to the next cell. As soon as the leftmost bit of the counter (m-i) becomes one and as long as it remains one (2 cycles) it performs the butterfly operations. The structure and operation of cell C(i) is presented in Figure 16.

One of the advantages of using a decimation-infrequency algorithm is the ease of generating coefficients for the butterfly operations. Each cell has a register Z containing 1 initially, which is multiplied by W at every cycle. At the time of butterfly operation, this register contains the appropriate value.

A new sequence of input values may enter the cascade as soon as a slot becomes open in the shift register of the left-most cell or N cycles after the first element of the previous sequence has entered the leftmost cell. Therefore, the pipeline time of the cascade is proportional to N. The processing time of a sequence however is proportional to 2N. To this time the time needed to shift the intermediate results within the shift registers must be added. The total length of shift registers for an N-element implementation of cascade is N. The longest shift register, connected to C(1) contains N/2 cells. Therefore, the time required to shift N/2 elements must be added to the processing time of each computational step. The time required to convert the output sequence from bit-reversed order to normal order must also be added to the processing time of this design.

The cascade implementation of an FFT uses a pipeline of m=logN processing elements. However, the amount of memory used for the shift registers approaches N. Thus, although the number of processing cells is very small, the shift registers occupy an O(N) area.

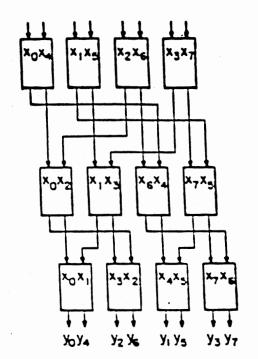

## The FFT Network

One of the methods to implement FFT in hardware is to lay out the flow graph of an FFT computation as depicted in Figure 3 in hardware providing a distinct cell for every butterfly computation. Consequently, the design consists of

Figure 17. The FFT Network [Thompson 83].

N/2 logN cells which could be laid out in logN rows of N/2 cells. Figure 17 adopted from [Thompson 83] represents the FFT network for N=8.

The input is in bit-shuffled order and the output is in bit-reversed order. This order seems to minimize the area required for row interconnections [Thompson 83]. Each cell performs a butterfly operation on its two inputs and coefficients are stored in a register in the cell. The basic structure and operation of an FFT network cell in the mth row is depicted in Figure 18. Additional circuitry is required to convert the input from normal order to bit-shuffled and to convert the output from bit-reversed to normal order.

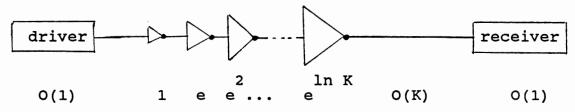

The interconnection between consecutive rows occupy wire areas. Thompson [Thompson 83] shows that in general, the connections emerging from the Kth row  $0 \le K \le \log N - 1$ , K+1 occupy N/(2) tracks. Consequently, a total of N-1 horizontal tracks are required to lay out the inter-row connections.

The processing time of the FFT network is logN cycles. To this time the time for inter row data transmission must be added. The pipeline time performance of the FFT network is one cycle, since a new problem can enter the network immediately after the previous problem leaves the first row.

## The Perfect-Shuffle Implementation of FFT

Stone [Stone 71] was the first to point out the

Figure 18. The Structure and Operation of the Basic Cell in the mth level of the FFT Network.

Figure 19. A Shuffle-Exchange Network for 8-point FFT (Stone 71).

importance of the perfect-shuffle connection in multiprocessing systems. One of the most important applications

of the perfect-shuffle network is in the implementation of

the decimation-in-time algorithm for FFT. Figure 19

represents the general form of the perfect-shuffle network

for an 8-point FFT.

The input to the perfect-shuffle network is in bit-shuffled order and the output is in bit-reversed order requiring extra hardware to rearrange the input and output to the normal order. The network consists of N/2 cells, each designed to perform a butterfly operation. The flow graph of FFT computation for perfect-shuffle arrangement is presented in Figure 20. The flow of inputs through the network is represented in Figure 21.

The perfect-shuffle network consists of N/2 cells each capable of performing a butterfly operation. LogN coefficients for butterfly operations, one for each stage of the computation are stored in each cell. As it is shown in Figure 21, the connection between cells is regular and unlike the FFT network it is independent of the stage of the computation. Data items circulate through N/2 cells for logN cycles before the output is ready. Therefore, the processing time of the FFT of an N-element sequence N=2, is proportional to m=log N. The time required for data recirculation must be added to this time to reflect the actual processing time. The problem of data recirculation and associated area and time complexity is addressed in chapter IV. The pipeline time for perfect-shuffle the FFT

Figure 20. The Flow Diagram of FFT Algorithm for an 8-point Signal with Input in Normal Order and Output in Bit-reversed Order.

Figure 21. The Input Flow Through Perfect-Shuffle Network.

network is equal to its processing time since new sequence can enter the network only after the computation of the current sequence is completed.

## The Mesh Implementation of the FFT

The mesh implementation of an FFT was first proposed by stevens [Stevens 71] for the ILLIAC IV architecture.

2m

Assuming N=2 and using the decimation-in-frequency algorithm, the N-element sequence is arranged into a mesh m m structure of 2 x2 elements in a row-major order. Figure 22 represents a mesh arrangement of a 16-point sequence. In order to simplify the description of the mesh implementation of the FFT algorithm, the data flow will be shown on a 16-point FFT network given in Figure 23.

As it is shown in Figure 23, at each stage of the computation N/2 butterfly operations are performed. At the first stage, the butterfly operations are performed on x(0) and x(8), x(1) and x(9), ...., and x(7) and x(15). Cell 0 receives x(8) and performs the butterfly operation, then it keeps one of the results and sends the other to cell 8. Cells 1 through 7 receive inputs from cells 9 through 15. If the difference between cell numbers is considered as the communication distance, there is an distance-8 communication between cells before the first set of butterfly operations are performed. At the completion of butterfly operations at cells 0 through 7, each cell sends one of its outputs to cells 0-3 and the other to cells 8-11. Therefore, there are

Figure 22. A Mesh Arrangement of a 16-Element Sequence.

Figure 23. A 16-point FFT Network (Thompson 80).

4 distance-8 and 8 distance-4 communications. Note that cells 8-15 are idle at the first stage. After completion of butterfly operations in the second row of the FFT network, cells 0-3 and 8-11 have 4 distance-4 and 8 distance-2 communications. And finally, after the third stage, there are 4 distance-2 and 8 distance-1 communications.

A careful study of Figure 22 reveals that distance-8 communications can be performed in parallel between row 1 and 3 and 2 and 4 through rows 2 and 3. If routing between near neighbors is considered to be unit routing, then distance-8 communication requires 2 unit routing. Distance-4 communication is between near neighbors on consecutive rows, therefore, it requires a unit routing. Distance-2 communication occurs between columns 1 and 3 and 2 and 4 which requires 2 unit routing. Finally, distance-1 communication is between near neighbors on columns.

The total time taken by the data movement during an FFT can be expressed in terms of unit routing performed. Thompson [Thompson 80] shows that in general in an N-cell k mesh, a distance-(N/2) communication is performed before and after the kth stage in the FFT network. The sum of the time contributions of all stages to routing will be the total routing time of the mesh.

There are logN stages in FFT network, each corresponding to a computational step in mesh. There are also 2 distance-k (N/2) communication per stage, one before and one after the computation. If K < 1/2 logN, the mesh's vertical interconnections are used for routing, otherwise the

horizontal connections are used. It is shown [Thompson 80] \$1/2\$ that the total routing time is proportional to N  $% \left( 1\right) =1/2$  .

The processing time consists of logN cycles of butterfly computations and routing which is mainly dominated 1/2 by routing. Thus it is considered to be proprtional to N . The pipeline time of mesh implementation of an FFT is also 1/2 N since a new sequence can start computation only after the current FFT is completed.

The cells in this design are not simple cells but complete processors, since data routing and stage determination and also storage for coefficients are all handled by the cells themselves, requiring larger area for basic cells.

#### CHAPTER III

# NEW PARALLEL ALGORITHMS FOR DISCRETE FOURIER TRANSFORM

Chapter II covers the existing parallel algorithms for calculating the Fourier transform of a sequence. In this chapter, a set of new parallel algorithms are presented. These algorithms are based on the direct computation of the Fourier transform. The main computational paradigm employed is a pipeline and the designs are based on systolic arrays of cells.

The idea of systolic arrays was first proposed by Kung [Kung 79]. It is based on the decomposition of a problem into smaller problems of the same nature. A small processing cell is designed to solve the smaller instance of the problem. The cells are connected appropriately to propagate the intermediate results to the other cells in order to generate the final result. The cell interconnections are assumed to be simple and regular.

The main concept behind the idea of systolic arrays is to simplify and modularize the dedicated design of a circuit to make it amenable for VLSI implementation. The simplicity and regularity of inter-cell connections inhibits extensive wire area and complicated control. Several pipeline systolic approaches to calculate the Fourier transform of a sequence are presented in chapter II. The new approaches proposed in this chapter are mainly inspired by certain properties of the matrix of coefficients in the matrix-vector multiplication representation of Figure 1.

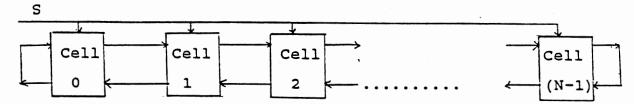

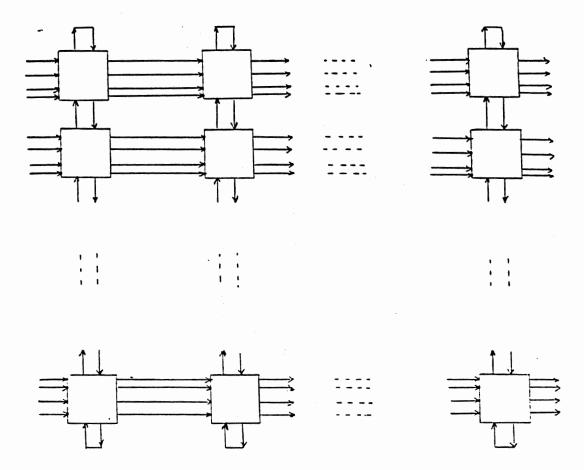

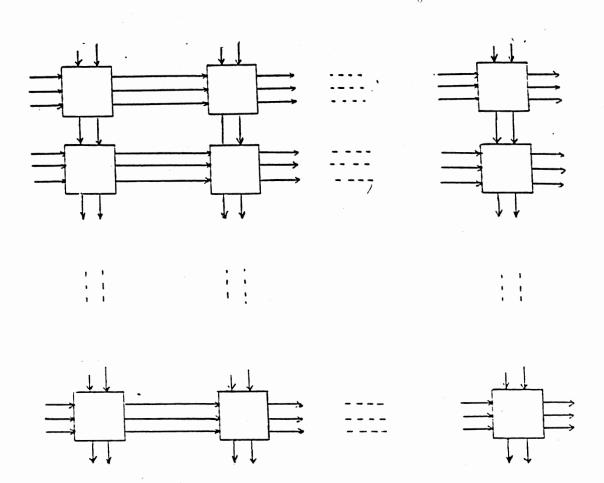

The new pipeline systolic approaches are divided into three categories: N-cell linear, N-cell mesh-connected, and 2 N -cell mesh-connected. The N-cell linear designs resemble the linear pipelines proposed by Kung, but they differ in the formulation, input/output format, and the structure of the basic cell. The N-cell mesh-connected design is based on these new approaches and the rearrangement of an N-element signal into an m x m matrix, N=m, as discussed in chapter 2 II. The N -cell design shows an improvement over the structure proposed by Thompson [Thompson 83]. This chapter is divided into three sections, each covering the details of the designs in each category. The VLSI area-time complexity of these designs along with others presented in chapter II is presented in chapter IV.

### N-Cell Linear Pipelines

The N-cell linear pipeline designs are based on the idea of N basic cells connected as a pipeline. These approaches are divided into two categories based on the form of the entry of the input sequence  $\{x(n)\}$  to the pipeline. The first category called On-line systolic DFT in this study, is based on the serial input of  $\{x(n)\}$  overlapped

with the computation. The second category called In-place systolic DFT in this study, assumes the existence of the input sequence in the pipeline, one element per cell of the pipeline.

## On-Line Systolic DFTs

These approaches are based on the serial input of the sequence to the pipeline from the left-most cell, one element at a time starting with the first element of the sequence  $\{x(n)\}$ , namely, x(0). Y(i)'s or the elements of the Fourier transform of the sequence  $\{x(n)\}$  reside in the registers in the processing cells, Y(0) in the leftmost cell or cell 0, Y(1) in the next cell or cell 1, and finally, Y(N-1) in the rightmost cell or cell N-1.

The elements of  $\{x(n)\}$  sweep the pipeline from left to right, visiting each cell, contributing appropriately to the value of Y(i) residing in that cell. The coefficients by which the elements of  $\{x(n)\}$  contribute to the elements of  $\{Y(n)\}$  are the variables of this approach whose pattern of change may be studied by careful examination of the matrix of coefficients.

The matrix-vector multiplication of Figure 1 may be rearranged as the vector summation of Figure 24. This rearrangement represents the vectors of the values by which x(i) contributes to the elements of  $\{Y(n)\}$ . These vectors are the columns of the matrix of coefficients. The idea may be expressed as follows:

$$\begin{vmatrix} Y_{0} \\ Y_{1} \\ \vdots \\ Y_{N-1} \end{vmatrix} = X_{0}\begin{vmatrix} 1 \\ 1 \\ 1 \end{vmatrix} + X_{1}\begin{vmatrix} 1 \\ W \\ W \end{vmatrix} + X_{2}\begin{vmatrix} 1 \\ W^{2} \\ W^{2} \end{vmatrix} \dots + X_{N-1}\begin{vmatrix} 1 \\ W \\ W^{(N-1)} \end{vmatrix}$$

Figure 24. Fourier Transform As Vector Summation.

$$\frac{1}{Y} = \sum_{i=0}^{N-1} x \frac{M}{i}$$

0<= i <= N-1 (3.1)

Where  $\overline{M}$  is the ith column of the matrix of coefficients. A i careful study of M 's shows that

Let M (j) denote the jth element of M , then i

Therefore, if appropriate W s are generated outside the pipeline and are input to the pipeline along with the corresponding x(i), then a simple multiplication by W will generate the coefficient of x(i) for the next cell.

Let C denote W used to generate M (j+1) using M (j).

i i

Then at each step through the pipeline, a cell receives

x(i), M (j) and C. The contribution of x(i) to Y(j) is made

and then the coefficient for the next step is calculated by

multiplying M (j) by C.

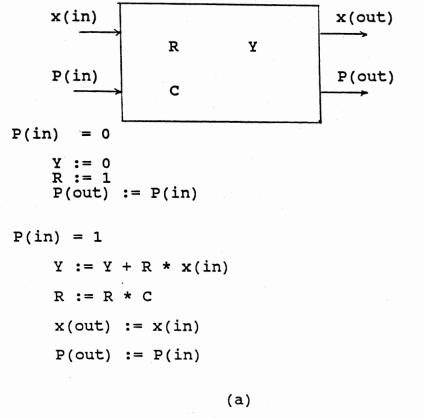

Let x(in) denote the element of {x(n)} that enters a cell, M(in) denote its corresponding coefficient, and C(in) i denote W . These three values are the inputs to a cell at each stage. After the operation is performed, x(in) is propagated to the next cell through a line called x(out),

M (j+1) is propagated on a line called M(out), and finally, i C(in) is propagated unchanged on a line called C(out). A control signal P is added to the design to initialize Y to zero before x(0) enters the cell. The structure and operation of a basic cell and the structure of the pipeline is depicted in Figures 25a and 25b.

Figure 25a represents the structure and the operation of the basic cell. Each computational step requires two multiplications and one addition. The cell contains a single register Y to accommodate the value of the Fourier transform of the signal. Four input and four output lines are needed.

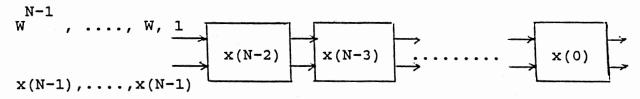

The pipeline requires N cells, each containing a multiplier, an adder, and a register. After N cycles, Y(0) is complete and after N-1 more cycles, the computation is completed. Therefore, this approach requires 2N-1 computational steps. If Y(i)'s are output immediately after

Figure 25. The Structure and Operation of a Basic Cell (a) and the Structure of the Pipeline for the On-line Systolic DFT.

(b)

, 1 , 0

1

they are completed, another sequence may start its computation after N cycles. Therefore, although the processing time of the pipeline involves 2N-1 cycles, its pipeline time may be boosted to N cycles.

In this design data entry to the system overlaps the computation. Data entry is assumed to be serial, requiring the minimum space for wires. Another feature of this design is its modularity. All cells have the same structure and function. The variable of the design, namely, C(in), is an input to the system, rather than being a built-in parameter. Therefore, an N-cell pipeline may be used to calculate the Fourier transform of any sequence of length M, M <= N as long as correct W,  $(W = EXP (-2 \pi j/M))$  is fed to the system and the sequence is padded with zeros to the length of N. It is also possible to expand a pipeline of N-cells to a pipeline of T cells, T >= N by simply connecting the outputs of the rightmost cell of the first module to the inputs of the leftmost cell of the second module. Yet another feature of this pipeline is that Y(i)'s reside in the cells and with slight enhancement of the cells many useful operations such as filtering followed by inverse Fourier transform can be performed in-place without requiring the sequence to leave the pipeline and enter again.

One of the disadvantages of this approach is the multitude of input/output lines in the basic cell. Although this feature adds to the flexibility and modularity of the design, it causes delays due to input/output and increases

the processing time. If the coefficients and the multiplicative factors used to generate them can be stored in the cells instead of being propagated, the processing time may be boosted at the cost of slightly larger cells.

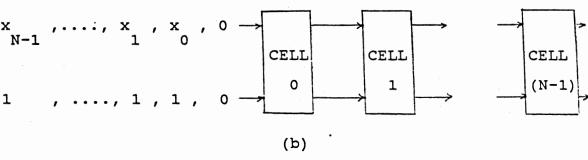

In order to maintain multiplicative factors in the basic cells, the multiplicative factors by which  $\{x(n)\}$  contributes to Y(j) should be analyzed. Another look at the matrix of multiplicative factors of Figure 1 reveals another interesting property of this matrix. The ith row of this matrix represents the multiplicative factors used by the elements of  $\{x(n)\}$  to calculate Y(i). Let R(i) represent the ith row of the matrix of coefficients and x represent the vector representation of  $\{x(n)\}$ , then

$$Y(i) = R \times X$$

0 <= i <= N-1

Therefore, while the elements of {x(n)} are flowing through the pipeline, the values of R may be generated in each i cell. A careful study of R reveals that:

$$\frac{}{R} = \{ W, 0 \le j \le N-1 \}$$

0<= i <= N-1

Let R (j) denote the jth element of R , then i

Let R denote a register in the basic cells to hold the i present value of R and let C denote W, then the number of i input lines to the basic cell may be reduced to one consisting only of the input value x. The control signal P is still needed to initialize Y to zero and R to 1. The structure and the operation of the basic cell and the structure of the pipeline is presented in Figure 26.

The control signal P follows the { 0,1,1,...,1 } sequence, initializing R and Y to one and zero respectively.

Register C is fixed for the design at value W for the ith cell. Each cell contains three registers, a multiplier and an adder, an input and an output data line, and a local input and a local output control line.

The basic operation involves two multiplications and one addition, an input and an output. The processing time for the evaluation of the complete DFT is 2N-1 cycles and the pipeline time can be N if {Y(n)} is output as it becomes ready. The input/output time is reduced from three input/output per basic operation to one.

## In-place Systolic DFTs

Kung [Kung 80] was the first to propose an in-place systolic DFT pipeline. This approach is discussed in detail in chapter II. In this section four new in-place DFT pipelines are introduced which are different from Kung's approach. In all in-place methods, it is assumed that the sequence  $\{x(n)\}$  is already loaded into the pipeline, one

Figure 26. The Structure and Operation of Basic Cell (a) and the Structure of the Pipeline (b) for the Modified On-line Systolic DFT.

element per cell. In Kung's approach, the sequence is loaded from right-to-left, leaving x(N-1) as the input to the leftmost cell, x(N-2) at the left-most cell, and finally, x(0) at the right-most cell. Therefore, requiring only N-1 cells for an N-element DFT.

In the new approaches presented in this section, data is loaded to the pipeline of N cells in natural order, x(0) in the left-most cell, x(1) in the second cell, and x(N-1) in the right-most cell. The structure of the basic cell for the new approaches are different from Kung's approach and the number of cycles is less than Kung's approach by a factor of 1/2 for the first two designs. This reduction in the number of cycles however is at the cost of slightly larger cells. The details of these techniques are presented in the following paragraphs.

The first in-place approach in this section is based on calculating  $\{Y(n)\}$  stored one element per cell in natural order by allowing x's to sweep the cells and contribute to Y in each cell. Therefore, initially x(i) and Y(i), 0 <= i <= N-1 are stored in the ith cell. During the first step x(i) contributes to the value of Y(i) in the ith cell. Then x(i) is propagated to the (i+1)th cell to contribute to the value of Y(i+1). The pipeline is designed to be circular so that the output of cell (N-1) may enter the cell 0. The values of  $\{x(n)\}$  circulate through the pipeline sweeping all the cells and contributing to the Y(i)'s stored in the cells. Therefore, the operation is completed after a complete sweep or N cycles.

Since this design is based on the complete sweep of the cells by  $\{x(n)\}$  stored in the cells, the coefficients by which the input values at each step contribute to the value of Y stored in the cell is different from the previous approaches.

At the first step of the computation, x(i) contributes to the value of Y(i). The coefficients used for this step are the elements of the diagonal of the matrix of coefficients of Figure 1. This sequence may be represented as:

The coefficients used in the second step are the values by which x(i) contributes to  $Y(\ (i+1)\ MOD\ N\ )$ , 0 <= i <= N-1, or the elements under the diagonal and the element at the Nth column and the first row of the matrix of coefficients. This sequence may be represented as:

Let R(i,j) represent the value by which x(i) contributes to Y(j) and Q(i) represent the multiplicative factor to generate R(i,j+1) or the coefficient by which x(i) contributes to Y(j+1). A careful study of these components reveals an interesting pattern. As shown before, the values of R(i,i) or the sequence of the contributions of x(i)s to

Y(j)s is as follows:

Q(i) or the value used to generate R(i,j+1) from R(i,j) is i W for 0 <= i <= N-1. A list of the values of R(i,i) and Q(i) for 0< =i <= N-1 is given in Figure 27.

These values may be pre-computed and stored in each cell or calculated on-the-fly before the actual DFT computation starts. On-the-fly computation adds to the flexibility of the design since W = EXP(-2 J/N) may be changed to accommodate the pipeline for the calculation of any sequence of length M <= N. It also increases the modularity of the design. However, the flexibility and modularity is attained at the price of the overhead of the added computation time.

Figure 27 shows the "on-the-fly" pattern of the computation of R(i,i)s and Q(i)s using the values of R(i-1,i-1) and Q(i-1). Basically, the following computational steps may be carried out through the pipeline to calculate and store R(i,i) and Q(i) in each cell:

$$Q(0) = 1$$

$$Q(i) = Q(i-1)*W 1 <= i <= N-1$$

$$R(0,0) = 1$$

$$R(i,i) = R(i-1,i-1)*Q(i-1)*Q(i) 1 <= i <= N-1$$

Therefore, by initializing the Q(0) and R(0,0) to 1 and

| <u>i</u> | R(i,i)                          | <u>Q(i)</u> |

|----------|---------------------------------|-------------|

| 0        | 1                               | 1           |

| 1        | W                               | ₩ .         |

| 2        | 4<br>W                          | 2<br>W      |

| 3        | 9<br>W                          | 3<br>W      |

| 4        | 16<br>W                         | 4<br>W      |

| :        | •                               | •           |

| N-2      | w (N-2) <sup>2</sup>            | w (N-2)     |

| N-1      | w <sup>(N-1)</sup> <sup>2</sup> | w(N-1)      |

Figure 27. A List of values of R(i,i)s and Q(i)s for Different Values of i.

inputting W = EXP(-2 J/N) to the leftmost cell, the above systolic process may generate and store Q(i) and R(i,i) in the ith cell.

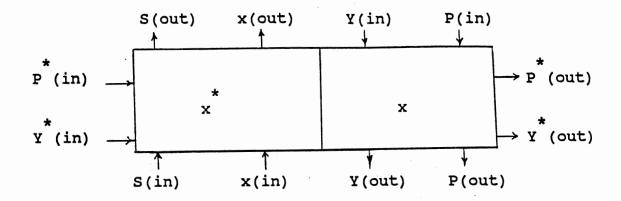

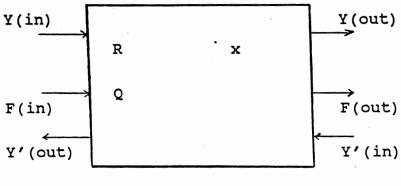

Let Q(in) and R(in) representing Q(i) and R(i,i) and z(in) representing W=EXP(-2\subseteq IJ/N) be the set of inputs to the cell at each instance. Let Q(out) and R(out) representing Q(i+1) and R(i+1,i+1) be the set of outputs from the cell. Then the above systolic operation may be performed at each stage to generate the values of Q(i) and R(i,i). Registers Q and R in each cell are dedicated to the values of Q(i) and R(i,i). A local control signal T is added to each cell to inhibit further operations in the cells where Q and R are already computed. This signal is also used to initialize Y to zero. The structure and operation of the basic cell to generate Q(i)s and R(i,i)s is presented in Figure 28. After Q(i)s and R(i,i)s are calculated, the in-place DFT may start.

Assuming a circular pipeline of cells (last cell is directly connected to the first cell), x(i) is multiplied by R(i,i) and accumulated in Y(i). The next step is to calculate R(i,i+1) which is accomplished by multiplying R(i,i) by Q(i). Then x(i), R(i,i+1) and Q(i) are propagated to the next cell. After N iterations, Y(i) 0 <= i <= N-1 contains the ith element of  $\{Y(n)\}$  or the Fourier transform of  $\{x(n)\}$ .

The structure and operation of a complete cell to calculate the coefficients and to perform the DFT is

Figure 28. The Structure and Operation of the Basic Cell to Generate Q(i)s and R(i,i)s

presented in Figure 29. A global signal S is used to differentiate the coefficient preparation process from the actual computation. The preparation process requires N cycles, and the calculation process requires N more cycles which yields a 2N step process for a complete DFT calculation.

The basic cell contains four registers, a multiplier, an adder, four input/output data lines and two control lines. The main reason for this added space is to attain flexibility and modularity by inputting  $W = EXP(-2\Pi J/N)$  which makes the design independent of N. Sequence  $\{Y(n)\}$  resides in the pipeline after the completion of the process.

The number of computational steps may further be reduced if Q(i) and R(i,i) are pre-computed and stored in each cell, eliminating the preparation process and reducing the number of control signals to one. The global signal S may be used to initialize Y to zero and to load the pre-computed value of R (S=0) and then to invoke the DFT process (S=1) which is completed after N steps. The structure and operation of the basic cell for the dedicated in-place DFT is presented in Figure 30.

Although storing the pre-computed values in the cells eliminates the need to prepare the coefficients, it does not eliminate the need for propagating the values R and Q, since these values are related to the x's which are floating through the pipeline.

In order to reduce the data transfer rate between the cells, we may investigate the coefficients used during the

Figure 29. Structure and Operation of a Basic Cell for In-place Systolic DFT

Figure 30. The Structure and Operation of the Basic Cell for Dedicated In-place DFT

process by floating values of x in correspondence with a given Y. The set of coefficients used during the four stages of the computation in each cell for N=4 is presented in Figure 31.

Obviously, these sequences have the initial value of { R(i,i) } studied in previous paragraphs. The sequence used in the second step of the computation may be generated from the first sequence by multiplying each element by W . This generalization is true for all the following steps.

Therefore, by storing W instead of W in Q(i) the need for propagating R(i,i) and Q(i) is eliminated.

A basic cell for this approach consists of three -i registers Q containing W , R' containing the initial value of R or R(i,i), and R which holds the current value of R(i,j). Registers x and Y are used to hold the values of the sequences  $\{x(n)\}$  and  $\{Y(n)\}$ . x registers may be eliminated from the cell if parallel input of the sequence to the cells during the initial load is available.

The operation of the basic cell is the same as the dedicated design. The only difference is in the fact that R and Q are going to hold the values of the coefficient and multiplicative factor at all times, therefore, eliminating the need for their propagation.

The structure and operation of the basic cell for this approach is presented in Figure 32. As it is shown, the number of input/output data lines is reduced to one which in turn reduces the input/output time. The processing time of

| STEP | Cell 0 | Cell 1  | Cell 2 | Cell 3 |  |

|------|--------|---------|--------|--------|--|

| •    | O      | Y       | Y<br>2 | У 3    |  |

| 1    | 1      | W       | 4<br>W | 9<br>W |  |

| 2    | 1      | 1       | 2<br>W | 6<br>W |  |

| 3    | 1      | 3<br>.W | 1      | 3<br>W |  |

| 4    | 1      | 2<br>W  | 6<br>W | 1      |  |

Figure 31. The Set of Coefficients Used at each Cell for  $N\!=\!4\,.$

Figure 32. The Structure and Operation of the Basic Cell for In-place DFT with Minimum Communication Lines.

|      | Cell 0    | Cell 1              | Cell 2              | Cell 3      |

|------|-----------|---------------------|---------------------|-------------|

|      | O         | Y                   | Y<br>2              | У 3         |

|      |           |                     |                     |             |

| STEP | (RL , RR) |                     | A                   | 9           |

| 1    | 1         | W                   | 4<br>W              | W           |

| 2    | (0,1)     | (1,W <sup>2</sup> ) | 2 6<br>(W ,W )      | 6<br>(W ,0) |

| 3    | (0,1)     | (W,W)               | (1,W <sup>8</sup> ) | 3<br>(W ,0) |

| 4    | (0,1)     | 2 4<br>(W ,W )      | 2 10<br>(W ,W )     | (1,0)       |

Figure 33. The Sequence of Coefficients Used by Cells in a 4-cell design.

this design is N cycles. The pipeline time is also N cycles.

The pipelines for the two previous designs are circular pipelines. The disadvantage of circular pipeline is that the wire connecting the rightmost cell to the leftmost cell is in general a long wire with an O(N) length which imposes long delay and slows down the entire process. It is intresting to investigate the possibility of the float of the x's in both directions to eliminate the need for a long connection.

In order to allow x's to flow in both directions, the techniques used in the previous two designs are combined. Thus at the expense of larger cells and two more input/output lines, the long wire connection which adds to the space and the time complexity of the design is avoided. The values of the {x(n)} which are stored in the cells of the pipeline are now allowed to propagate to both the right and the left neighboring cells. Therefore, two sets of coefficients need to be maintained and manipulated in each cell, one for the x being input from the left neighbor xL and another for the x being input from the right neighbor xR.

The multiplicative factors associated with xL and xR -i i are W and W respectively. The sequence of coefficients used at each step by cells 0-3 in a 4-cell design is represented in Figure 33.

The left input to the leftmost cell and the right input to the rightmost cell are set to zero to inhibit incorrect computations. At the first step of the computation, x(i) is

multiplied by R(i,i) and added to Y(i). Then x in each cell is propagated to both the right and the left neighboring cells and two x's are input to the cell, one from the left neighbor and another from the right neighbor. The coefficient for the xL and xR, RL and RR, are multiplied by -i i

W and W respectively to attain their new values. Both coefficients are initially set to R(i,i). Then xL is multiplied by RL and added to Y. And finally, xR is multiplied by RR and added to Y.

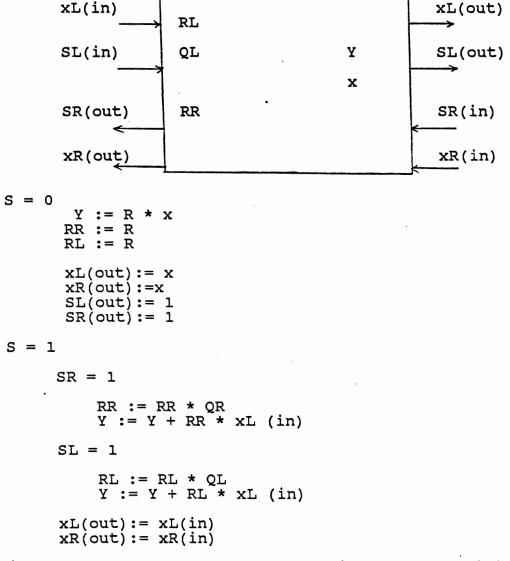

The structure and operation of the basic cell for the design is presented in Figure 34. Registers QL and QR are in infixed for the design at values W and W respectively. A global control signal S is used to initialize Y,RL, and RR and to allow x's stored in cells contribute to associated Y's (S=0) and to start the flow of x's and the computation (S=1).

It is apparent that although all the cells are fully functional at the first step, only a portion of the cells will be fully functional in the following steps. For example, the leftmost and the rightmost cells do not receive meaningful inputs on the xL and xR in the following steps and cells 1 and N-2 are not going to receive meaningful inputs on their xL and xR input lines after the second step. Therefore, in order to inhibit meaningless multiplications, two local control signals SL and SR may be added to the design to avoid multiplication by zero. SL and SR are set to 1 initially. SL(in) for the leftmost cell and SR(in) for the

Figure 34. The Structure and Operation of a Basic Cell for the Bi-directional In-place Systolic DFT Pipeline.

S

Figure 35. The Structure and Operation of the Modified Cell for the Bi-directional In-place Systolic DFT Pipeline.

appropriate coefficients in cell i is W 0<= i <=N-1. Therefore, using Q and R registers in each cell to represent the multiplicative factor and the coefficient, Q has a fixed V and R is initialized to W .

After N iterations, Y(0) is complete and is fed back to the pipeline, while Y(N-1) enters cell 0 for further computation. After N-1 more computational steps, {Y(n)} is completed and stored in cells 0 through N-1 respectively. The structure and operation of the basic cell for the linear in-place DFT pipeline is presented in Figure 36. Figure 37 represents the structure of the pipeline.

This pipeline consists of N cells, each containing four registers, two input/output data lines and one control line, a multiplier and an adder. There is no long data lines and the connections are all near neighbor. The processing and the pipeline time of this design are both 2N cycles.

Yet another technique may be used to avoid long wires by allowing zero-valued Y(i)'s to enter the pipeline from the leftmost cell and sweep the pipeline from left to right. Thus each cell should generate the sequence of the coefficients corresponding to the x(i) stored in the ith cell. These sequences are the columns of the matrix of coefficients. The ith sequence may be represented as:

i

Therefore, if W is stored in each cell, and the initial

Figure 36. The Structure and Operation of the Basic Cell for Linear Non-circular DFT Pipeline.

Figure 37. The Structure of The pipeline for Linear Non-circular DFT.

value of the sequense is set to 1, then the following elements of the sequence may be generated by multiplying its previous value by W .

Let Q and R denote the registers containing W and the element of the sequence. Let Y(in) denote the value of Y that enters the cell and Y(out) denote the value that exits the cell. Then the basic operation of the cell is to multiply R by x and add it to Y(in) and then generate the new R by multiplying it by Q.

The structure and operation of the basic cell is represented in Figure 38. To assure the correct operation of the pipeline, a local control signal F is added to the design to initialize R to 1 (F=0) and to start the computation at each cell as needed (F=1).

After N iterations, Y(0) is out from the rightmost cell. If it is desired to route the result back to the pipeline, then two data lines may be added to the cells to route the output back to the pipeline by connecting the output of the rightmost cell back to itself. The modified basic cell is represented in Figure 39.

The processing time of this pipeline is 2N-1 cycles. If the resulting sequence  $\{ Y(n) \}$  leaves the pipeline, a new sequence may start evaluation immediately after the last element of the current sequence leaves the leftmost cell. In this case the pipeline time will be N cycles.

#### N-Cell Mesh-Connected Network

The idea of an N-cell mesh-connected DFT network was

Figure 38. The Structure and Operation of the Basic Cell.

Figure 39. The Modified Basic Cell to Direct the Output Back to the Pipeline.

first introduced by Zhang [Zhang 84]. This approach is discussed in detail in Chapter II. The idea is based on the rearrangement of a one-dimensional sequence  $\{x(n)\}$  into a two-dimensional matrix given N=m.

Zhang's approach has many drawbacks. The proposed design uses an (m+1) x m network of mesh-connected cells. Input and output have an irregular form. The first row and the first column of the cells have a different form solely because of the form of Kung's recursive linear pipeline used for the basic DFT computation. A total of m multipliers are required to generate different sequences of W. And finally, a global signal S (connected to all cells) is required to assure the correct function of the network. The area used and the delay imposed by the multipliers and global signal and also excessive number of input/output lines per cell are the undesirable features of this design.

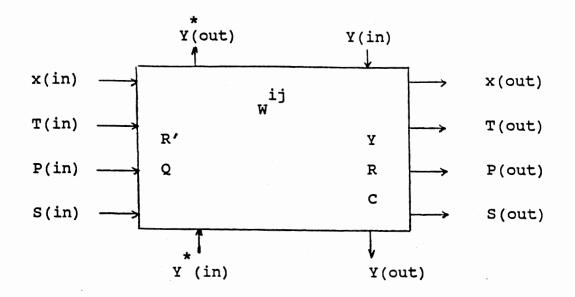

A new mesh-connected network based on the linear pipeline techniques discussed in previous sections is presented in the following paragraphs. The aim is to reduce the time and the space complexity of the design by reducing the input/output lines and avoiding the long distance connections.

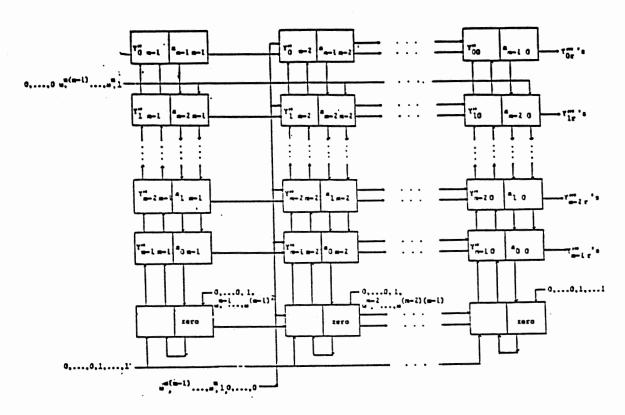

The input sequence is arranged into an m x m matrix, m

1/2

= N as represented in Figure 11. The computation is

divided into three phases:

#### 1) compute the row DFTs

- 2) multiply the results by W  $0 \le i,j \le m-1$

- 3) compute the column DFTs

Phase 2 is combined with the initialization phase of the column DFT computation. The on-line linear DFT of Figure 26 is used for the row DFT computation. This technique allows data entry to overlap the computation. It also requires the minimum amount of input/output lines per cell.

After m iterations the Fourier transform values for column zero of the cells is computed. At this point the column DFT of column zero may start. For the column DFTs, one of the non-circular linear in-place DFTs may be used to avoid long distance connections of the other in-place DFT techniques. After 2m-1 cycles, the column DFT of column zero is complete. The computation for the entire sequence is completed after m-1 more cycles. Thus, the processing and the pipeline time of this design is 4m-2 cycles. A control signal T is added to the basic cell to stop the operation after the completion of the column DFTs at each column.

The structure and operation of the basic cell using the non-circular linear in-place DFT cell of Figure 36 is presented in Figure 40. The control signal P is used in both row column DFTS. For row DFTs, control signal P has the values {0,1,...,1}. It is set to zero to initialize the values of Y and R. It is changed to one immediately and it remains one for m cycles otr until row DFTs are completed. During this phase S is zero to indicate row DFTs. After m