## A NEW DESIGN METHODOLOGY FOR

## **HIGH QUALITY DESIGN**

By

## NAHREEN MAHERUKH

Master of Science

University of Dhaka

Dhaka, Bangladesh

1996

Submitted to the Faculty of the Graduate College of the Oklahoma State University In the Partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE May, 2004

## A NEW DESIGN METHODOLOGY FOR

# HIGH QUALITY DESIGN

Thesis Approved:

.

fam aben ý Thesis Advisor 01 un al he La

of Graduate College

### ACKNOWLEDGEMENTS

I wish to express my sincere appreciation to my advisor, Dr. John M. Acken, for his constructive guidance, support and encouragement. His intelligent suggestions and guidance have made this thesis feasible. His tolerance, patience, motivation and advice have been a constant source of inspiration and motivation that helped me to gain confidence. I also thank my other committee members, Dr. C. Latino and Dr. L.G. Johnson, for their assistance.

I like to sincerely thank my husband, Farhad Milki, for his unconditional love, support and endless encouragement.

I wish to thank my parents, A. Mannan Chowdhury and Fatema Chowdhury for their love, encouragements and blessings.

I dedicate this thesis to my dearest daughter, Nubaira Milki, who is the reason I have worked so feverishly to complete this project.

# **TABLE OF CONTENTS**

# Chapter

# Page

| I. Introduction                                     |    |

|-----------------------------------------------------|----|

| Introduction/ Objective                             | 1  |

| Proposal -BIST and RSP Combined                     | 2  |

| Design Project Description And Proposed Methodology | 3  |

| II. Background                                      | 6  |

| Rapid System Prototyping                            |    |

| The Throw-Away Approach                             |    |

| The Evolutionary Approach                           |    |

| Digital System Testing                              |    |

| General Idea About Testing                          |    |

| Production Testing                                  |    |

| Scan Based Stuck at Fault Test                      |    |

| Functional Test                                     |    |

| IDDO Test                                           | 12 |

| Signature Analysis                                  |    |

| Built in Self Test (BIST)                           |    |

| Exhaustive Testing                                  |    |

| Pseudorandom Testing                                |    |

| Pseudo-Exhaustive Testing                           |    |

| Linear Feedback Shift Register (LFSR)               |    |

| Biometrics For Identification                       |    |

| Summary                                             |    |

|                                                     | 22 |

| III. Software Prototype                             |    |

| Introduction/ Objective                             |    |

| Design Description                                  |    |

| Equations Used For Calculations                     |    |

| Analysis Of Results                                 |    |

| Conclusions                                         | 34 |

# Chapter

| IV. Microcontroller Prototype                         | 25 |

|-------------------------------------------------------|----|

| Introduction                                          |    |

| Brief Description About 6811 Microcomputer            |    |

| Design Description                                    |    |

| Results                                               |    |

| Conclusions                                           |    |

| V. Final Implementation                               | 46 |

| Introduction/Objective                                |    |

| Design Description                                    |    |

| Conclusions                                           |    |

| VI. Conclusions                                       | 50 |

| Conclusions                                           | 50 |

| Recommendations                                       | 51 |

| References                                            | 52 |

| Appendices                                            | 54 |

| Appendix A                                            | 54 |

| Fortran Source Code                                   |    |

| Appendix B                                            | 63 |

| Three Sets Of Database                                |    |

| Calculations With Three Sets Of Data Base             | 65 |

| Appendix C                                            | 71 |

| 6811 Access Program                                   | 71 |

| Appendix D                                            |    |

| Verilog Program                                       | 83 |

| Appendix E                                            |    |

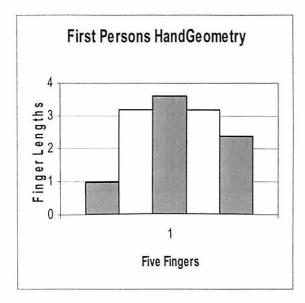

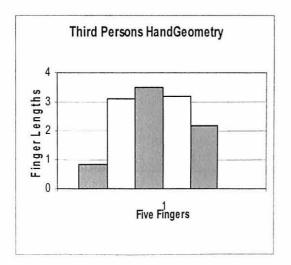

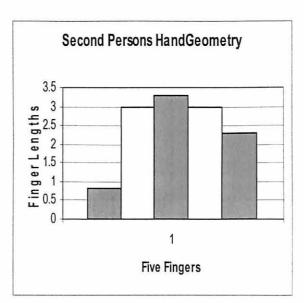

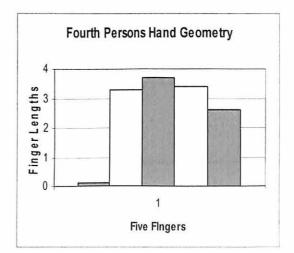

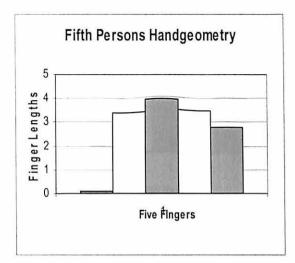

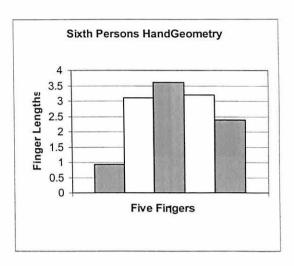

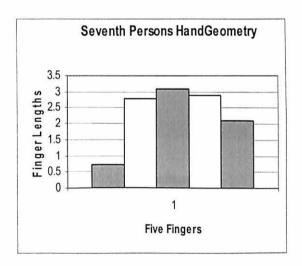

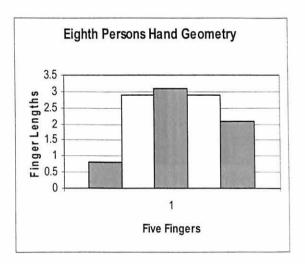

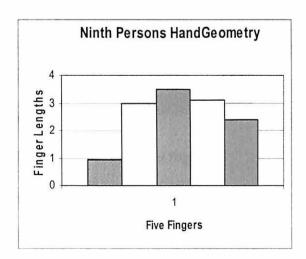

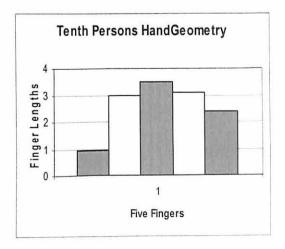

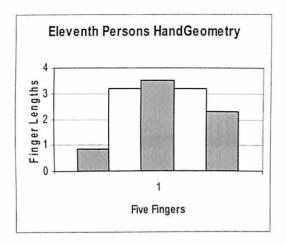

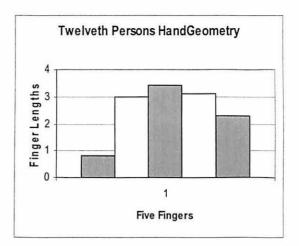

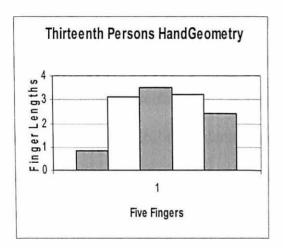

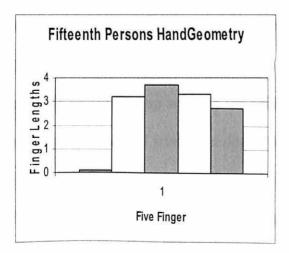

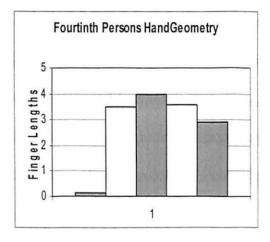

| Graphs Showing The Hand Geometry Of Each Person       | 93 |

| Appendix F                                            | 96 |

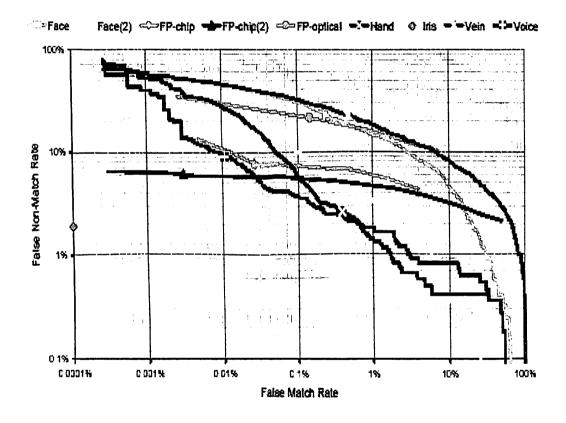

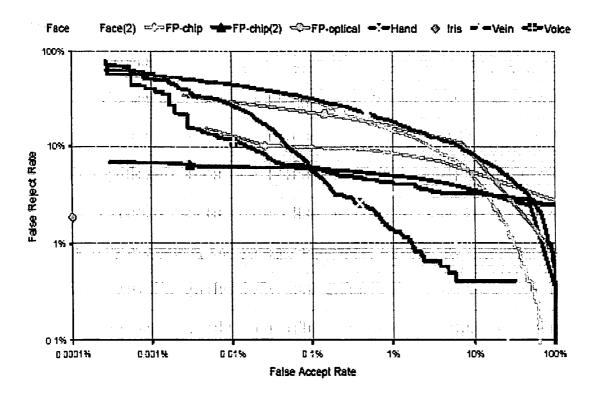

| Summary of The Biometric Product Testing Final Report | 96 |

# LIST OF TABLES

| Table                                                               | Page |

|---------------------------------------------------------------------|------|

| I. Range of FMR (False Match Rate) for the three sets of data       | . 33 |

| II. Range of FNMR (False Non-Match Rate) for the three sets of data | 34   |

| III. Calculated Values With Input Dataset 1                         | 65   |

| IV. Calculated Values With Input Dataset 2                          | 67   |

| V. Calculated Values With Input Dataset 3                           | 69   |

## **LIST OF FIGURES**

| Figure                                                     | Page |

|------------------------------------------------------------|------|

| 1. Traditional Functional Testing                          | 11   |

| 2. Built-In Self-Test with LFSR Circuit                    | 13   |

| 3. An 8 bit LFSR Circuit                                   | 19   |

| 4. Signature analysis with BIST                            | 27   |

| 5. Flow chart for the Fortran Programming and Calculations | 28   |

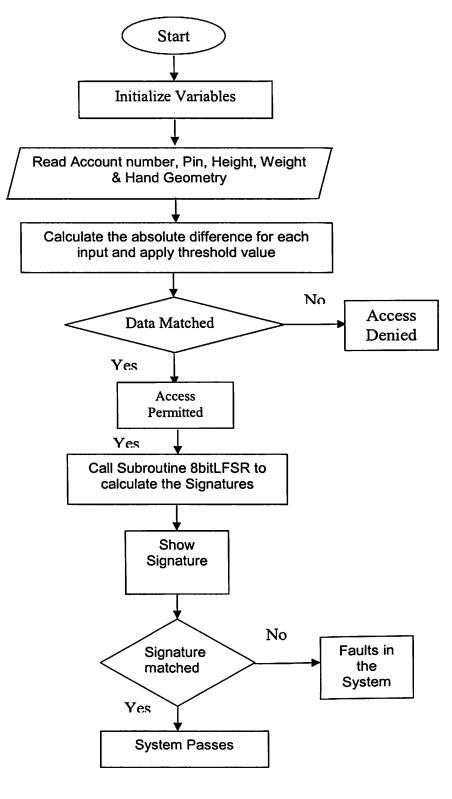

| 6. The Flow chart for the 6811 program                     | 38   |

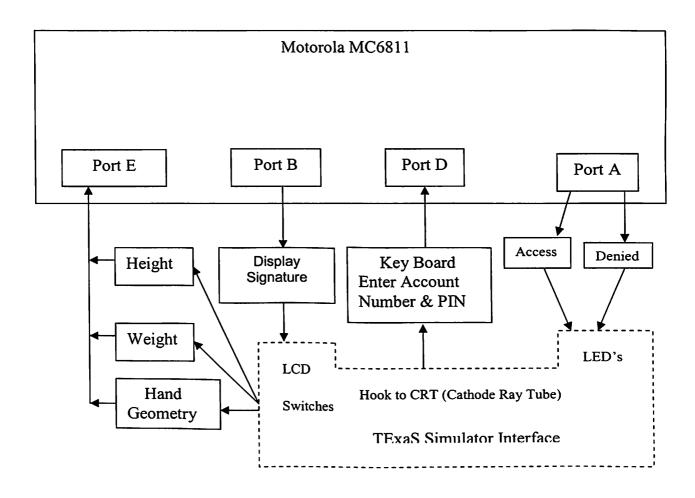

| 7. Block Diagram for the Simulation with Motorola MC6811   | 39   |

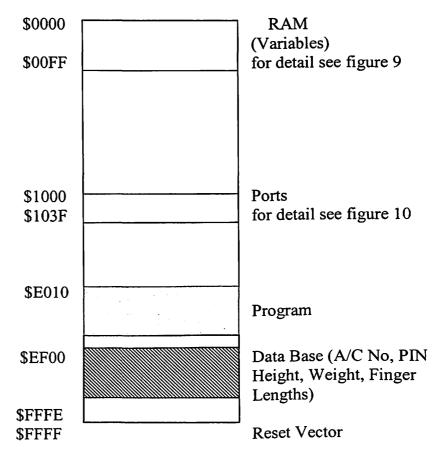

| 8. Memory map for 6811                                     | 40   |

| 9. Memory map for the variables in RAM                     | 42   |

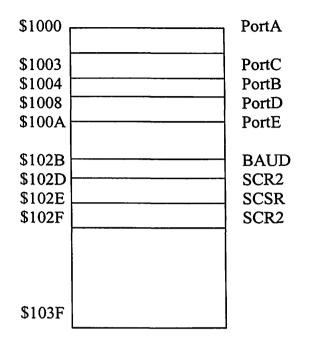

| 10. I/O ports of 6811                                      | 43   |

| 11. Block Diagram of the Access System                     | 47   |

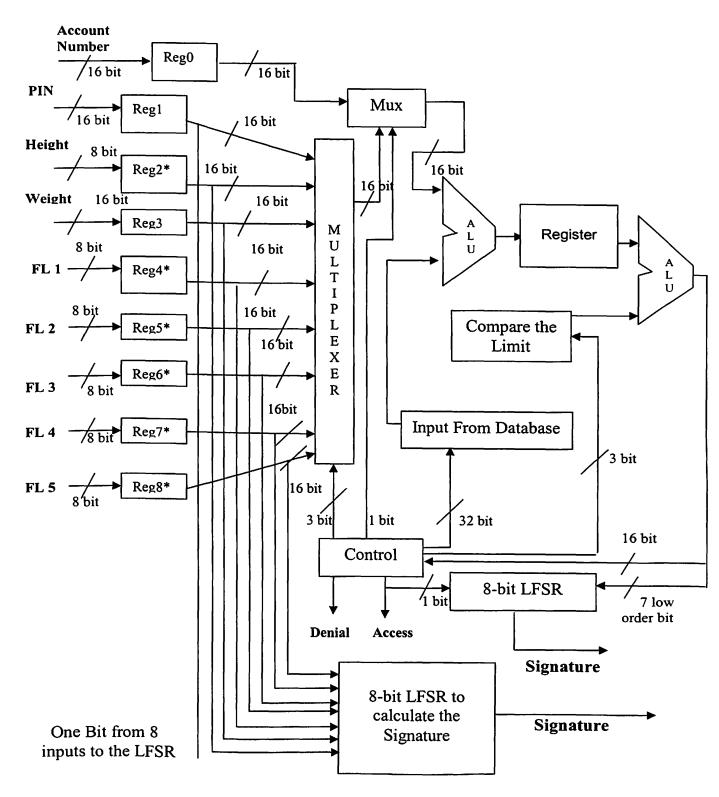

| 12. Detail Block Diagram of The Access System              | 48   |

| 13. Detection error trade-off: FMR vs. FNMR                | 100  |

| 14. Detection error trade-off: FAR vs. FRR                 | 101  |

## **CHAPTER I**

#### **INTRODUCTION**

## Introduction/Objective

The design process utilizes prototyping to evaluate design decisions. In the final product, quality is improved by including production testing solutions during the design process. Security provided by identity verification is widely used in our daily life. Password, PIN (Personal Identification Number), mothers maiden name are just different kinds of identity verification. With Automated Teller Machines (ATM) people use their card with a PIN to get access to their money. This project aims at demonstrating improved access verification by including biometrics. The prototypes are used to statistically evaluate the improvement. Every card member's body weight, height and length of each finger will be stored in the database along with the account number and PIN. At the time of requesting access, the person's height, weight and the finger's length will be measured.

A system is developed that will crosscheck the measured values with the ones stored in database. Statistical analysis of prototype equations is used to determine the match rates and margin of error that can be tolerated. The combination of account number, PIN, height, body weight and fingers length would ensure higher security with less expense. The inclusion of a testing component ensures increased quality in the final system.

# Proposal – Built-In Self-Test (BIST) and Rapid System Prototyping (RSP) Combined

Prototyping is a development approach that promotes the implementation of a pilot version of the intended product. A prototype is an executable model of a system that accurately reflects a chosen subset of its properties, such as display formats, computed results or response times. Rapid system prototyping refers to the capability of creating a prototype with significantly less time than it takes to produce an implementation for operational use. The goal of Rapid System Prototyping (RSP) is to quickly deliver a product that tests ideas, demonstrates feasibility, and refines requirements. Testing done during manufacturing is called manufacturing or production testing. These tests determine whether each product contains manufacturing defects. In order to achieve high quality, a good test strategy usually consists of a variety of test types. The capability of a circuit (chip, board, or system) to test itself is known as Built-In Self-Test (BIST). When Built-In Self-Test is incorporated in the system, at that point test is a part of the design. The ultimate in testable design is to make the design test itself. The BIST approach is the testing technique that is least dependent upon internal design details and is useful in a prototyping environment. This is valuable because in prototyping, the implementation details can always be changed. A prototype also helps to get feedback early in the development process. Adding Built-In Self-Test (BIST), a standard production test technique, to RSP is a method to add quality without slowing the product delivery.

In our access verification system we will use rapid system prototyping in order to evaluate different matching equations. Also, the prototype is used to evaluate how close the values should be matched to allow the access. We will incorporate the BIST

2

technique in the prototyping that will help to test the system in its early phase in less time, and the prototype will benefit from testing used to determine whether the device meets the specification.

## **Design Project Description And Proposed Methodology**

To get access to the system each person will be asked to enter the account number, PIN, and then the height, weight and hand geometry (the length of each finger) will be measured. These are the measured data. In our system the inputs i.e. account number, PIN, height, weight and hand geometry are selected based on their commonality of use. Practically, the individual hand geometry measurements should be combined into one number but that is outside the scope of this research. Also five inputs (account number, PIN, height, weight and hand geometry) are used to increase the reliability of the system. To verify the match of the measured data some equations will be used. With these different equations the deviations of the measured data from the stored data, the ratios of these two values, the root mean square value will be determined. From these equations the one that has the lowest error rate will be chosen. The equation that best fits will be used in designing our second system prototyping. In the system there will be a database, which is a collection of data and a set of rules that will organize data by specifying certain relationship among data. In the database each person's height, weight, and hand geometry, account number and the PIN (Personal Identification Number) will be stored. Let us assume that the data that we have in the data base are the stored data which is denoted by S.D. and the input data (account number, PIN, height, weight and hand

3

geometry) that are measured to get access to the system are the measured data M.D. The modulus of the difference of these two values represents the absolute difference.

Absolute Difference =

$$|$$

S.D. – M.D

For all the inputs (account number, PIN, height, weight and hand geometry) the above equation will be used. The account number is unique here. For the account number and PIN the absolute difference has to be zero. For other three inputs if the absolute difference are zero then it is obvious that the data matched. If the differences are not zero then based on how close the measured data are to the stored data, the percentage of likelihood to get access to the system will be determined.

Another way is to use the ratio of the stored value to the measured value.

$$Ratio = \frac{S.D}{M.D}$$

For the account number and PIN the ratio always has to be one.

The square of the stored data and the measured data will be add together and the average of the value will be taken. Then the square root of the value will give the root mean square value of that particular data.

$$R.M.S = \sqrt{\frac{((S.D)^2 + (M.D)^2)}{2}}$$

It is possible that for the same person sometimes the height or weight or hand geometry can differ from the stored value, where the difference may be small. If we design our system where all the measured data (inputs) have to match with the stored data exactly then it may not always be possible for a person to get access to his/her own account. That's why we need to define adjustable threshold for each input. This will help a person to get access even with small differences between the stored and the measured data. As the account number is a unique number for every single person it ensures that even with the same height or weight one cannot automatically get access to the other person's account.

Variations in biometrics depend upon age. Younger people have increases in height and weight. Injuries can change hand geometry. Weight change can vary greatly with diet and exercise. All of these variations require that the database be updated regularly. Still normal variations of a ....of 1% for finger lengths and up to 10% for weight changes requires setting a matching threshold value for each biometrics.

The software prototype will be done using Fortran software. Absolute difference, ratios and RMS values will be calculated using three different input datasets and results will be compared. The equation that gives the best match rate results using the software prototype will be chosen. The system will be prototyped using the Motorola 68HC11A8 processor with the TExaS simulator to evaluate implementation decisions. Then the system will be design in verilog and will be tested. In all three steps signature will be calculated as a part of BIST.

## **CHAPTER II**

#### BACKGROUND

This thesis describes a new methodology based upon combining established ideas. This Background chapter summarizes the concept and terminology for Rapid System Prototyping (RSP), Production Testing and Biometrics.

## **Rapid System Prototyping**

The IEEE defined prototyping as "A type of development in which emphasis is placed on developing prototypes early in the development process to permit early feedback and analysis in support of the development process", [4].

A prototype is an executable model of a system that accurately reflects a chosen subset of it properties, such as display formats, computed results or response times. Prototypes are useful for formulating and validating requirements, resolving technical design issues and supporting Computer Aided Design (CAD) for both software and hardware components of proposed systems. Rapid prototyping refers to the capability of creating a prototype with significantly less time than it takes to produce an implementation for operational use.

A prototype may not satisfy all of the constraints on the final version of the system. For example, the prototype may provide only subset of all the required functions, and may be expressed in a more powerful or more flexible language than the final version. It may be less efficient in both time and space than the final version, and may have limited capacity. Full facilities for error checking and fault tolerance may not be included in prototyping. Such simplifications are often introduced to make the prototype easier an faster to build. To be effective, a partial prototype must have a clearly defined purpose that determines what aspects of the system must be faithfully reproduced and which ones can safely be neglected. Prototypes must be constructed and modified rapidly, accurately and cheaply. They do not have to be efficient, complete or robust and they do not have to use the same hardware, system software or implementation language as the delivered system. Software for rapid and inexpensive construction and modification of prototypes makes RSP feasible. The main reason for using prototypes is to get early design feedback economically. Prototype versions of most systems are much less expensive to build than the final versions. Prototypes should be used to evaluate proposed systems if acceptance by the customer or the feasibility of development is in doubt. The need for prototyping has become more urgent as systems being developed have grown more complex, more likely to have requirements errors, and more expensive to implement.

Rapid System Prototyping allows experiments on what will be hardware and what will be software. Prototypes facilitate the requirements phase for any type of software or hardware. Prototypes can demonstrate the system to the affected parties as a way to collect criticisms and feedback for update requirements, detect deviations from user expectations early, trace the evolution of the requirements, improve the communication and integration of the users and development personnel, and provide early warning of mismatches between proposed architectures and conceptual structure of requirements.

7

## The Throw-Away Approach

The Throw-Away approach is most appropriate in the project acquisition phase where the prototype is used to demonstrate the feasibility of a new concept and to convince a potential sponsor to fund a proposed development project. The advantage of throw-away approach is that it enables the use of special purpose languages and tools, even if they introduce limitations that would not be acceptable in an operational environment or even if they are not capable of addressing the entire problem. In throw-away approach prototypes are usually built with a specific language for simulations. Refinements on the throw-away prototype mainly concern requirements [7]. The throw-away approach can be a stopgap for an inadequate level of technology and is most appropriate for rough system mock-ups used at the very early stages of a project.

The most apparent disadvantage of throw-away prototypes is spending implementation effort on code that will not contribute directly to the final product. The throw-away prototyping approach has been used in industry for about three decades. Prior to a large project, a study is performed to evaluate the feasibility and cost of the real system. Sometimes the project is canceled based on these studies.

## The Evolutionary Approach

The Evolutionary Approach produces a series of prototypes in which the final version becomes the product. This approach depends on special tools and techniques because it is usually not possible to put a prototype into production use without significant changes to its implementation to optimize the code and to complete all of the details. In the evolutionary approach, support for automated program construction of systems is needed

8

and such tools can be very useful in this context, even if the resulting program are not very efficient. Refinements on the evolutionary prototype concern the product itself, functions, speed, memory, consumption etc [7]. Precise specification for the components of a prototype and clear documentation of its design are critical for effective software prototyping, as are tools for transforming and completing designs and implementations.

## **Digital System Testing**

## **General Idea About Testing**

The process of determining whether a product is functioning correctly or is defective (i.e. broken or faulty) is called testing. When a product is manufactured or assembled it may require testing before being sold or used. Each copy of the product to be tested is called the Device Under Test (DUT). The device could be a system, a board or a chip. The goal of testing is to identify which devices contain failure. Between two test sets, the one detecting more faulty devices while passing more fault free devices is better. The procedure of identifying defective units is called testing. The design verification testing verifies the correctness of the design. A test verifies correct operation against the circuit specifications combines two objectives: Verification that the design of the circuit correctly implements its specification and Verification that the manufacture of the circuit correctly implements the design. It is usually necessary to achieve these two objectives by separate procedures, [9]. The inputs used to verify the design typically do not produce a thorough enough manufacturing test. The manufacturing process is checked by applying test vectors to the physical piece of equipment, and the design process is checked by the simulating the design. The simulation process is called design verification

and uses a set of input vectors chosen specifically to verify the design meets the specification.

An n input combinational network could be tested thoroughly by applying 2<sup>n</sup> input combinations and verifying that the correct output is obtained for each combination. The technique is sometimes called Exhaustive testing. It provides a thorough test but can require too much test time for networks with many inputs. Another testing known as pseudo exhaustive testing completely exercise combinational circuits without applying all possible circuit input combinations, [10]. For this testing first a circuit is broken into segments and then all possible input combinations are applied to each segment while the output of each segment is propagated to a primary output. Exhaustively testing the entire circuit requires over 2 million vectors but pseudo exhaustive testing requires fewer than 400 vectors. The goal of this approach is to detection all possible combinational faults. Diagnostic test is to locate the failure site on failed part and to find what might be wrong.

## **Production Testing**

Testing done during manufacturing is called manufacturing or production testing. These tests determine whether each product contains manufacturing defects. The purpose of this testing is to test the manufactured parts to sort out those that are faulty.

In order to achieve a high quality of components it is accepted that a good test strategy usually consists of a variety of test types. For any particular device the tests used would typically be of the following

- 1. Scan based stuck at fault test

- 2. Functional test

- 3. IDDQ test

- 4. Signature Analysis

## Scan Based Stuck-At Fault Test

Structural fault models assume that the components are fault-free and only their interconnections are affected. Usually faults affecting the interconnections are shorts and opens. A short is formed by connecting points not intended to be connected, while an open results from the breaking of a connection. A short between ground or power and a signal line can force the signal to a fixed voltage level. This logical fault consists of the signal being stuck at a fixed value and it is known as a stuck-at fault. By connecting all of the memory elements into scan chains, scan testing converts a sequential stuck-at test generation problem into a combinational stuck-at test generation problem.

## **Functional Test**

Functional Testing is a verification of the intended function of the circuit. Failures are modeled at the register transfer or functional level in terms of variation in expected function.

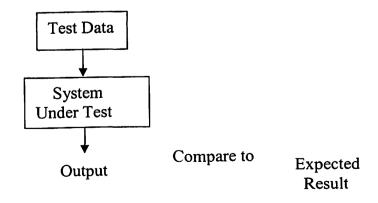

#### **Figure 1: Traditional Functional Testing**

The designer selects input vector sets based upon the intended functionality of the parts of the system. The expected output values are created by simulation. The Figure: 1 shows the flow of functional testing.

## **IDDQ** Test

$I_{DDQ}$  testing is an effective technique for improving the quality and reliability of CMOS ICs. Local defects (which affects a few transistor in a chip) result from contamination during circuit fabrication, results in either extra or missing material at a given site. These include gate oxide shorts, unintended bridges between nodes and missing connections. Such defects particularly shorts can result in unintended connections between power and ground. As a result the circuit draws current in its static state and the defects can be detected by monitoring the quiescent power supply current ( $I_{DDQ}$ ). Many defects which may be observed via  $I_{DDQ}$  are undetectable with conventional voltage testing, [6].

#### **Signature Analysis**

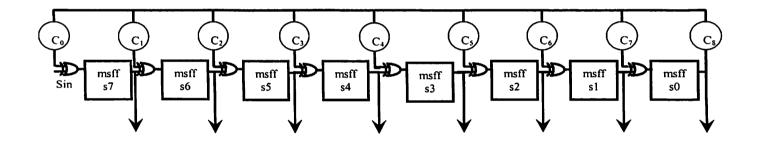

Polynomial division with a Linear Feedback Shift Register (LFSR) uses the remainder left in the register after completion of the test as the retained value for comparison with the good remainder. It is an extension of the well known CRC (Cyclic Redundancy Check) code and is the most popular data compression technique and it is easily modified for use with multiple output circuits. The remainder is usually called a signature and the technique is called signature analysis, [5].

An LFSR is a shift register that when clock advances the signal through the register from one bit to the next most significant bit, some of the outputs are combined in exclusive-OR configuration to form a feedback mechanism. A Linear Feedback Shift Register can be formed by performing exclusive-OR on the outputs of the flip-flops together and feeding those outputs back into one of the flip-flops. Any data such as the test response results from a circuit can be compressed into a code word by an LFSR. This code word, the remainder from the division process, is called the signature of the input data stream and the LFSR itself is called the signature analyzer.

Figure 2(b)

Figure 2: Built-In Self-Test with LFSR circuits

Figure 2(b) shows a generic LFSR that can be used as an input generator or a signature analyzer. One concern with the use of CRC check words as the signature of the circuit output sequence is the possibility that an erroneous sequence from a faulty circuit will be compressed into the same signature as the fault free circuit. This phenomenon is called masking since the effect of the fault is masked by the compression process. Masking is a loss of information caused by the compression of the output sequence. The masking probability of LFSR signature analysis can be reduced, independent of types of errors exhibit by the circuit, [3]. They are

- 1. Lengthen the LFSR

- 2. Repeating the test

- 3. Using variable-shift MISR (Multiple Input Signature Registers)

Signature testing on a newly built part requires knowing the correct or good machine signature for the part. The signature can be obtained in several ways. From a test engineering approach, the simplest is to take a part which has already passed functional testing in the system, run the part against the actual test patterns and save its signature as the reference for the new production. If testing is required before system installation, the simplest approach is to simulate both the circuit and the signature analyzer against the actual test patterns. An alternative to complete simulation is to simulate up to some break point say at the first 100 tests, and to obtain the expected signature at the point. Now the first 100 tests are applied to actual hardware and the hardware signature is checked against the simulated breakpoint signature. A mismatch between the two requires the hardware be reworked until it passes the checkpoint test. When the hardware passes the checkpoint test it is fault free. Now the remainder of the test patterns are applied to obtain the final hardware signature which is saved as the putative good machine signature,[3]. Signature analysis using selective feedback of various stages of a shift register fed by the data stream being created by a circuit is a powerful technique for coping with a large volume of test response data.

#### **Built - In Self - Test (BIST)**

Testing of digital circuits is a major portion of the effort in their design, production, and use. As the electronic industry evolved from discrete components through early integrated circuits to an increasingly high level of integration, the demands on testing methods and effectiveness have caused test technology to evolve to a high degree of sophistication. As the number of circuits that can be integrated onto one piece of silicon approaches twenty million it would seem that some small portion of those circuits could be devoted to testing. This concept is called Built-In Self-Test. The capability of a circuit (chip, board, or system) to test itself is known as Built-In Self-Test. There are two categories of BIST. In on-line BIST, testing is done during the normal operating conditions. On-line BIST is either concurrent or non-concurrent. Concurrent on-line BIST is a form of testing which occurs simultaneously with normal functional operation. This testing is usually done using coding techniques or duplication and comparison. In non-concurrent on-line BIST, testing is carried out while a system is in the idle state. Systems, boards, and chips can be tested in this mode. Off-line BIST is either Functional or Structural. Functional offline BIST deals with the execution of a test based on a functional description of the circuit under test and sometimes employs functional, or high level, fault model. Structural off-line BIST deals with the execution of a test based on the structure of the circuit under test. When Built-In Self-Test is incorporated into a digital network to meet a testability specification, the distinction between design and test becomes unclear. At that point test is a part of the design. The ultimate in testable design is to make the design test itself. Building test into the design, as might be expected, consumes added circuit and I/O overhead, but at the same time results in visible

reductions to the costs of testing when compared with an external test using automatic test equipment. Built-in testing achieves these savings by eliminating (or at least reducing) the costs of test pattern generation and fault simulation, decreasing the time required for tests, by running tests at circuit speed, simplifying the external test equipment, and easily adapting to engineering changes.

As there are many ways to build in the processing of test responses, so are there many ways to generate the tests. The various forms of testing are the following: Exhaustive Testing, Pseudorandom Testing, Pseudo-exhaustive Testing.

## **Exhaustive Testing**

Exhaustive testing deals with the testing of n-input combinational circuits where all 2<sup>n</sup> inputs are applied. Since all possible test patterns are applied, all detectable single and multiple stuck faults are detected. The tests are generated with any process that cycles exhaustively through the circuit input space, such as the binary counter, a Gray code generator or an n-stage linear feedback shift register. Exhaustive testing for high input pin count structures requires relatively long test times, but the circuit can be partitioned into sub-circuits, each of whose input pin count is low enough to permit exhaustive testing in a reasonable amount of time [10].

## **Pseudorandom Testing**

In Pseudorandom Testing, testing a circuit is done with test patterns that have many characteristics of random patterns but where the patterns are generated deterministically and are repeatable. Pseudorandom patterns can be generated with or without replacement.

Pattern generation with replacement means that a test pattern may be generated more than once, without replacement means that each pattern is unique. Not all 2<sup>n</sup> test patterns need to be generated. Pseudorandom Testing is applicable in both combinational and sequential circuits. Pseudorandom testing is a type of Built-In Self-Test that performs a structural test of the network involved.

## **Pseudo-Exhaustive Testing**

Pseudo-exhaustive testing usually requires fewer test patterns but achieves many of the benefits of exhaustive testing. It relies on various forms of circuit segmentation and attempts to test each segment exhaustively. This technique completely exercises combinational circuits without applying all possible circuit input combinations. For this technique, first a circuit is broken into segments and then all possible input combinations are applied to each segment while the output of each segment is propagated to a primary output.

Let us consider a 21 input combinational circuit. Exhaustively testing the entire circuit requires over 2 million vectors (exactly  $2^{21} = 2,097,152$ ). Now considering segmenting the circuit into three circuits with 7 inputs each. Using pseudo exhaustive testing on this segmented circuit requires fewer than 400 vectors (exactly 3 \*  $2^7 = 384$ ). The goal of this approach is to detection all possible combinational faults, [2].

## Linear Feedback Shift Register (LFSR)

An LFSR is a shift register that when clock advances the signal through the register from one bit to the next most significant bit. Some of the outputs are combined in exclusive-OR configuration to form a feedback mechanism. A Linear Feedback Shift Register can be formed by performing exclusive-OR on the outputs of two or more flip-flops together and feeding those outputs back into one of the flip-flops. LFSR make extremely good pseudorandom pattern generators. When the outputs of the flip-flops are loaded with the seed value (which is anything except all 0's, which would cause the LFSR to produce all 0 patterns) and when the LFSR is clocked it will generate a pseudorandom pattern of 0's and 1's.

A LFSR consisting of n flip-flops would go through the states 0, 1,  $...2^{n-1}$ , 0, 1. The maximum number of states for such a device is  $2^n$ . An n-bit shift register cycles through at most n states. The output sequence generated by such a device is also cyclic.

The theory behind the use of an LFSR for signature analysis is based on the concept of polynomial division where the remainder left in the register after completion of the test process corresponds to the final signature. The input sequence of a LFSR can be represented by the polynomial G(x) and the output sequence by Q(x). If the initial state of the LFSR is all 0's, let the final state of the LFSR be represented by the polynomial R(x). Then it can be shown that these polynomials are related by the equation

$$\frac{G(x)}{P(x)} = Q(x) + \frac{R(x)}{P(x)}$$

Where P (x) is the characteristic polynomial of the LFSR. Hence an LFSR carries out (polynomial) division on the input stream by the characteristic polynomial, producing an output stream corresponding to the quotient Q (x) and a remainder R (x), [1]. For a

primitive polynomial the LFSR will generate the maximum sequence no matter what the seed values are. There are two types of LFSR. They are 1) Type 1 LFSR and 2) Type 2 LFSR.

Type 1 LFSR is easier to understand and work with mathematics but Type 2 LFSR is easier to implement in hardware. Another name for type 1 LFSR is External XOR because the feedback is to XORed to one big XOR gate external to the serial registers. Type 2 is also called Internal XOR because the feedback is to XOR's between serial register stages.

Figure 3: An 8 bit LFSR Circuit (Type 2)

We will use an 8-bit type 2 LFSR as shown in Figure: 3, in our system. An 8-bit LFSR cycles through at most 8 states. An LFSR goes through a cyclic or periodic sequence of states and the output produced is also periodic. The maximum length of the period is  $2^n - 1$ , where n is the number of states. The characteristic polynomial associated with a maximum length sequence is called a primitive polynomial.

## **Biometrics for Identifications**

Biometrics are automated methods of recognizing a person based upon a physiological or behavioral characteristic. Some examples features measured in this method are face, fingerprints, hand geometry, handwriting, iris, retina, wrist vein, and voice. Biometric technologies are becoming the foundation of an extensive array of highly secure identification and personal verification solutions. In identification mode, the biometric system identifies a person from the entire enrolled population by searching a database for a match. In verification mode, the biometric system authenticates a person's claimed identity from his/her previously enrolled pattern. As the level of security breaches and transaction fraud increases, the need for highly secure identification and personal verification technologies is becoming apparent. Using biometrics for identifying and authenticating human beings offers some unique advantages.

Some terms that are used to describe the accuracy of biometric systems include falseacceptance rate (percentage of impostors accepted), false-rejection rate (percentage of authorized users rejected), and equal-error rate (when the decision threshold is adjusted so that the false- acceptance rate equals the false-rejection rate). When discussing the accuracy of a biometric system, it is often beneficial to talk about the equal-error rate or at least to consider the false-acceptance rate and false-rejection rate together, [8]. For many systems, the threshold can be adjusted to ensure that virtually no impostors will be accepted. This often means an unreasonably high number of authorized users will be rejected. Biometric-based authentication applications include workstation/ network/ domain access, single sign-on, application logon, data protection, remote access to resources, transaction security and web security. Utilizing biometrics for personal authentication is becoming convenient and considerably more accurate than current methods (such as the utilization of passwords or PINs). This is because biometrics links the event to a particular individual on the other hand someone other than the authorized user may use a password or token. It is convenient as nothing to carry or remember and is accurate which provides for positive authentication.

Biometric technologies are ideally suited to provide highly secure identification and personal verification solutions. Biometric-based personal authentication has multiple applications in commerce, the federal, state and local governments, in the military and in commercial applications. Biometrics has a high priority in the government sectors and also in the business world, especially in fast-growing sectors such as mobile appliances and e-commerce. Open system standards increase user's confidence by preventing sole source lock-in and are vital for the growth of the global economy. The biometrics industry's maturity is demonstrated by its commitment to the development of the required biometric standards. Evidence of the growing acceptance of biometrics is the availability in the marketplace of biometric-based authentication solutions that are becoming more accurate, less expensive, faster and easy to use.

#### Summary

This Background chapter has described how RSP improves product development cycle. Production testing was described, which improves final product quality. Extra explanation was provided for BIST. Identity verification improvement by adding biometrics has also been explained. The rest of this thesis will describe a new design methodology that combines all of these ideas.

21

## **CHAPTER III**

## SOFTWARE PROTOTYPE

#### Introduction/Objective

For the Rapid System Prototyping (RSP) Approach, the initial prototype is usually written in a general software language. This chapter describes the Fortran prototype of the access verification system. The program runs with three different sets of data. The calculation is done using three equations and the values are compared. The prototype is used to evaluate the equations and to select the equation that gives the best result as measured by match rates.

## **Design Description**

The following steps are planned for this prototype. First the measured data are compared with the database data, and absolute differences, ratios and root mean square values are calculated. Threshold values are applied and percentage of correct data, percentage of incorrect acceptance, percentage of incorrect rejection are calculated. Then the equation that performed best is picked from this calculation. That equation would be further used for designing the system for the next prototype version.

The Fortran prototype for my program is used to demonstrate how to get access to the system. To get access to the system each person will be asked to enter the account

number, PIN and height, weight, and hand geometry (i.e. each person's five fingerlengths from a particular point of the palm) will be measured. For hand geometry always the right hand will be used. These are the measured data. In the system, the database contains each person's account number, PIN (Personal Identification Number) height, weight, and hand geometry. The measured data is compared with the stored database data and the results are checked whether the data matched or not. To verify the accuracy of the measured data different equations are used. The three different equations: the absolute difference of the measured data from the stored data, the ratios of these two values, the root mean square value have determined the comparison value. From these equations the one that verified the system most accurately is chosen. The equation that fits best is chosen in designing the next system prototyping.

For the same person the height or weight or hand geometry can differ from the stored value, where the difference may be small. It is always possible that someone can gain weight or lose weight, the height may differ using different pairs of shoes and also the length of the fingers may vary for the nails. If we design our system where all the measured data's (inputs) have to match with the stored data exactly then sometimes it will not be possible for a person to get access to his/her own account. That is why an adjustable threshold is defined for each input. This will allow a person to access with small deviation in the measured data with the stored one. As the account number is a unique number for every single person it ensures that even a person with the same height or weight will not automatically get access to the other person's account.

In my access verification system I have used rapid system prototyping, which will evaluate whether the device meets the specification in short time. It also helps make

23

design decisions such as which equations and thresholds to implement. In prototyping I have incorporated the Built-in Self-Test (BIST) technique that will test the system in its early phase in less time.

## **Equations Used For Calculations**

The Prototype used the match rates to evaluate the equations. After evaluation, the equation that gives the best result as measured by the match rates will be selected. This section describes the equations used for the calculation. As mentioned in Chapter-I the equations are as follows. The data that is in the data base are the stored data which is denoted by S.D. and the data (Account number, PIN, height, weight and hand geometry) that are measured to get access to the system are the measured data M.D. The absolute value of the difference of these two values represents the absolute difference.

Absolute Difference =

$$|S.D. - M.D|$$

.....(1)

The second equation is the ratio of the stored data to the measured data, which is represented by

$$Ratio = \frac{S.D}{M.D} \qquad (2)$$

the third equation find the Root Mean Square value of the measured data and the stored data. The square of the stored data and the measured data will be added together and the average of the values will be taken. Then the square root of the value will yield the root mean square value of that particular data.

$$R.M.S = \sqrt{\frac{((S.D)^2 + (M.D)^2)}{2}} \qquad (3)$$

For the output data set the number of matched data is M, the number of data that are rejected is R. TT represents the number of test data. So we can write

$$TT = M + R \dots (4)$$

CM represents the number of data that matched correctly and CR is the number of data that are rejected correctly. So the number of correct data C can be written as

$$C = CM + CR \qquad (5)$$

In this system every persons account number is unique and only when it exactly match then the rest of the data will be checked to give access. But for height, weight and hand geometry any two persons can have the same height or weight or hand geometry. When two or more persons have the same value (i.e. height or weight or hand geometry) then in calculating the absolute difference or the ratio for height or weight or hand geometry we will get 0 or 1. These are incorrectly matched data.

Now if IM represents the number of data that match incorrectly and IR represents the number of data that are rejected incorrectly then the total number of test TT can be written as

$$TT = CM + CR + IM + IR....(6)$$

Where CM and CR are the number of data that matched correctly and the number of data that rejected correctly. Using these equations we can find the value of C, TT, IM, IR.

The percentage of the correct data can be calculated by the ratio of the number of correct data C to the total number of test data TT

*Percentage* of Correct Data =

$$\frac{C}{TT}$$

.....(7)

For example in our test dataset we have 225 data and for one data set, the number of correct data is 224 then the percentage of correct data is 224/225 = 99.56 %.

The false match rate and false non-match rate measure the accuracy of the matching process. The percentage of the false acceptance can be calculated by the ratio of the number of data that matched incorrectly IM to the total number of test data TT. So the False Match Rate (FMR) can be written as

False Match Rate (FMR) = *Percentage* of Incorrect Acceptance =

$$\frac{IM}{TT}$$

..... (8)

For example in our test dataset, we have 1 data that matched incorrectly in a total 225 test data then the percentage of incorrect acceptance is 1/225 = 0.44 %.

When the account number is matched but there is a slight difference in height or weight or in hand geometry then we will get the data for these (height or weight or hand geometry) fields which will not match with the stored data. These are the incorrectly rejected data. The percentage of incorrect rejection can be expressed by the ratio of the number of incorrectly rejected data IR to the total number of test data TT False Non Match Rate (FNMR) = Percentage of Incorrect Rejection =  $\frac{IR}{TT}$  ...... (9)

For the Account Number and PIN to verify access I have only used the absolute difference between the stored data and the measured data in Fortran programming. Because most access verification system already have a procedure to check Account number and PIN. For the other fields we will use the absolute difference, ratios and the root mean square values and then will select one for each field that gives the best result to that field.

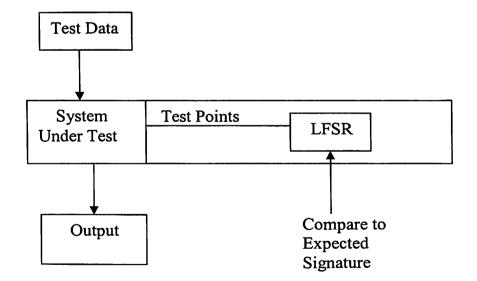

BIST was implemented in the Fortran prototype as shown in Figure: 4.

Figure 4: Signature Analysis with BIST

The flowchart for the Fortran programming and calculation is shown in Figure 5.

Figure 5: Flow Chart for the Fortran Programming and Calculations

As mentioned in the thesis proposal three equations have been used first in the program and from these three only one equation has been picked. Rapid system prototyping are of two types, one is throw-away approach and the other one is evolutionary approach. In this thesis I have used the throwaway approach, two equations are discarded and only one equation is picked based on the results. The percentage of correct values, the percentage of incorrect acceptance and the percentage of incorrect rejection (which are shown in Tables III, IV and V, Appendix B) have been calculated. For the equations different threshold values were applied in calculating these values, and then they are compared.

## **Analysis Of The Results**

The equations mentioned in the above sections are used to calculate the matching rates. The software prototype is used to evaluate these equations and to select the one that gives the best result as measured by the match rates. Three sets of input database are used and a brief description of the data base are given here. Input data set 1 uses the exact data for the database. The stored data and this data set are the same. With this data set the percentage of correct data and percentage of incorrect match are calculated. In data set 2 only the last entries are changed. The account number and the PIN are the same, only the height, weight and the Finger length L1 was changed. From this data set 3 each entry is changed by small amount in one or more data positions. For every field the percentage of correct data, false match rate, false non-match rate are calculated.

Using all three data sets the absolute difference (A.D), the ratios, and the root mean square (RMS) values are calculated for each input. The percentage of correctly matched

data, the percentage of incorrect acceptance and percentage of incorrect rejection are calculated. For all biometric inputs different threshold values are applied and all those are calculated again. The results with three sets of database will be discussed in this section and the calculations are shown in appendix B.

Using input dataset 1 to calculate the absolute difference for height the percentage of correct data is 98.23%, the incorrect acceptance is 1.77% and the incorrect rejection is 0%. Applying threshold value these values have been calculated again. Using the ratios for height the percentage of correct data is 98.23%, the percentage of incorrect acceptance 1.77% and percentage of incorrect rejection is 0%. Using the RMS values the percentage of correct data is 98.23%, the percentage of incorrect acceptance 1.77 and % of incorrect rejection is 0%. Again threshold is applied and values are calculated for both the ratios and RMS values. With all these values it has been found that applying threshold values the absolute difference gives the best result than the ratios or RMS values.

For weight calculation, absolute difference gives 100% correct data and the percentage of incorrect acceptance and the percentage of incorrect rejection is 0%. Applying threshold values in all three equations I have got 93.78% correct data, 6.22% incorrect acceptance and 0% incorrect rejection using absolute difference, 92% correct data, 8% incorrect acceptance and 0% incorrect rejection using ratios and 89.34% correct data 10.66% incorrect acceptance and 0% incorrect rejection using RMS values. The absolute difference gives better results than the other two equations used.

For finger length L1 to L5 using these three equations and applying thresholds the percentage of correct data, the percentage of incorrect acceptance, the percentage of incorrect rejection have been calculated. It has been found that for all finger lengths,

applying threshold the absolute difference gives the better results than the other two equations.

In input dataset 2, a slight change has been made in the some of the data. Height, weight and finger length 1 have been changed. Finger length2 to finger length5 are the same as in the dataset1. For height using absolute difference the percentage of correct data is 98.23%, percentage of incorrect acceptance 1.33% and percentage of incorrect rejection is 0.44%. Applying threshold the percentage of correct data is 89.33%, percentage of incorrect acceptance 10.67% and percentage of incorrect rejection is 0%. Using ratios the percentage of correct data is 98.23%, percentage of incorrect acceptance 1.33% and percentage of incorrect rejection is 0.44% and applying threshold the percentage of correct data is 73.33%, percentage of incorrect acceptance 26.67% and percentage of incorrect rejection is 0%. Using RMS values the percentage of correct data is 98.23%, percentage of incorrect acceptance 1.33% and percentage of incorrect rejection is 0.44% and applying threshold values percentage of correct data is 70.67%, percentage of incorrect acceptance 29.33% and percentage of incorrect rejection is 0%.

With all these values calculated it has been found that applying threshold values the absolute difference gives the better result than the ratios or RMS values for height with input dataset 2.

For weight using absolute difference the percentage of correct data is 99.12%, percentage of incorrect acceptance 0.44% and percentage of incorrect rejection is 0.44%. Applying threshold the percentage of correct data is 94.67%, percentage of incorrect acceptance 5.33% and percentage of incorrect rejection is 0%. Using ratios the percentage of correct data is 99.12%, percentage of incorrect acceptance 0.44% and percentage of incorrect acceptance the percentage of incorrect acceptance 0.44% and percentage of correct data is 99.12%, percentage of incorrect acceptance 0.44% and percentage of acceptance 0.44% and percentage of incorrect acceptance 0.44% and percentage 0.44% and percent

rejection is 0.44% and applying threshold the percentage of correct data is 91.11%, percentage of incorrect acceptance 8.89 and percentage of incorrect rejection is 0%. Using RMS values the percentage of correct data is 99.56%, percentage of incorrect acceptance 0% and percentage of incorrect rejection is 0.44% and applying threshold values percentage of correct data is 89.33%, percentage of incorrect acceptance 10.67% and percentage of incorrect rejection is 0%.

It has been found that applying threshold values the absolute difference gives the better result than the ratios or RMS values for weight with dataset2.

For finger length1 using absolute difference the percentage of correct data is 95.56%, percentage of incorrect acceptance 4% and percentage of incorrect rejection is 0.44%. Applying threshold the percentage of correct data is 96%, percentage of incorrect acceptance 4% and percentage of incorrect rejection is 0%. Using ratios the percentage of correct data is 98.23%, percentage of incorrect acceptance 1.33% and percentage of incorrect rejection is 0.44% and applying threshold the percentage of correct data is 96%, percentage of incorrect rejection is 0.44% and applying threshold the percentage of correct data is 96%, percentage of incorrect acceptance 4% and percentage of incorrect acceptance 1.33% and percentage of incorrect acceptance 4% and percentage of incorrect rejection is 0%. Using RMS values the percentage of correct data is 93.78%, percentage of incorrect acceptance 5.78% and percentage of incorrect rejection is 0.44% and applying threshold values percentage of correct data is 60.89, percentage of incorrect acceptance 39.11 and percentage of incorrect rejection is 0%.

It has been found that applying threshold values the absolute difference gives the better result than the ratios or RMS values for finger length1 with input dataset 2.

For input dataset 3 each entry has been changed by small amount in one or more data positions. Using three equations calculation has been done and the percentage of correct

data, percentage of incorrect acceptance and percentage of incorrect rejection have been calculated. These values are all given in Table V, appendix B. with input dataset 3 it has been found that applying threshold values the absolute difference gives the better results than the ratios or the root mean square values.

The following tables summarize this discussion. Specifically Table II shows false non matched or false rejection rate are about the same for all three equations. However the false match rate is the lowest for absolute difference.

|                        | Range of FMR (                                                                      | of FMR (False Match Rate) for the three sets |             |  |  |  |  |

|------------------------|-------------------------------------------------------------------------------------|----------------------------------------------|-------------|--|--|--|--|

| Types of Equations     | of data with three different equationsInput Dataset 1Input Dataset 2Input Dataset 3 |                                              |             |  |  |  |  |

|                        |                                                                                     |                                              |             |  |  |  |  |

| Absolute difference    | 0%-12.44%                                                                           | 0% - 12.44%                                  | 0% - 20.44% |  |  |  |  |

| Ratio                  | 0% 36.44%                                                                           | 0% - 36.44%                                  | 0% - 36.44% |  |  |  |  |

| Root Mean Square value | 0% – 39.55%                                                                         | 0% – 39.11%                                  | 0% - 35.56% |  |  |  |  |

Table I: Range of FMR (False Match Rate) For The Three Sets of Data

## Table II: Range of FNMR (False Non-Match Rate) For The Three Sets of Data

| Types of Equations     | Range of FNMR (False Non-Match Rate) for the<br>three sets of data with three different equations |            |            |  |  |  |  |

|------------------------|---------------------------------------------------------------------------------------------------|------------|------------|--|--|--|--|

|                        | Input Dataset 1 Input Dataset 2 Input Datase                                                      |            |            |  |  |  |  |

| Absolute difference    | 0%                                                                                                | 0% – 0.44% | 0% – 2.22% |  |  |  |  |

| Ratio                  | 0%                                                                                                | 0%-0.44%   | 0% – 2.22% |  |  |  |  |

| Root Mean Square value | 0%                                                                                                | 0%-0.44%   | 0% – 2.67% |  |  |  |  |

### Conclusions

For the next step to design and simulate the system the absolute difference will be used to compare the measured data with the stored data. To simulate the design the 6811 microprocessor will be used for the second prototype.

### **CHAPTER IV**

### **MICROCONTROLLER PROTOTYPE**

#### Introduction

The second step prototype for the access verification system uses the Motorola MC68HC11. This chapter describes briefly the 6811 microcomputer, then the design program and the results. The program has been written in assembly language. The TexaS (Test Execute and Simulate) simulator has been used to simulate the 6811 access verification system. A new idea for using BIST (Built-In Self-Test) as design verification has also been implemented in this second step prototyping.

# **Brief Description of 6811 Microprocessor**

The Motorola MC68HC11 (referred to simply as 6811) microcomputer is optimized for low power consumption and high performance operation. The 6811 have many versions and the MC68HC11A8 is used for research. The 6811 version used for this prototype has 8 Kbytes of internal ROM, 512 bytes of EPROM and 256 bytes of RAM, [11]. The RAM contains the variables and stack. The EPROM contains the constants that are unique to each application instance. The ROM contains the program and fixed constants. The 6811 has five external I/O ports. For 6811, as with many microcomputers, the I/O ports are memory mapped. Memory mapped means that the software accesses an I/O port by reading from or writing to the appropriate memory address rather than using specific I/O instructions.

The registers are high-speed storage devices that reside inside the processor. For the 6811, registers do not have specific memory address like RAM and ROM but have specific machine instructions that operate with the particular register. The 6811 uses either two separate 8 bit registers A and B or one combined 16bit accumulator RegD. RegA contains the most significant byte of register D. There are two index-registers X and Y. Register A and B contain data while register X and Y contain addresses. Assembly language instructions have four fields. The label field is optional and starts at the first column, and it is used to identify the position in the memory of the current instruction. The operation command (opcode) field specifies the microcomputer action to be performed. The operand field specifies where to find the data to be used by the instruction. The comment field is also optional, and it contains a description of the software, making the software easier to understand. The 6811 instructions set has five different addressing modes. The indexed addressing mode is useful when addressing data structures. The 16-bit register (RegX or RegY) is used as an index.

In this project I have used the TExaS simulator to run the Motorola 6811 microcomputer for the second prototype design of the access verification system. With the TExaS simulator, when the program is running, the microcomputer file shows the changes in different registers that help to figure out if there is any error. The I/O device file shows the port connections to the output LED's, output LCD, I/O CRT and input switches.

### **Design Description**

In the access verification system, rapid system prototyping (RSP) is included in order to get early feedback so that it can be modified rapidly and accurately in the development process. Based upon experiments with the Fortran program, I have decided that for the dataset (both measured data and the stored data) the absolute difference will be used because it has the best FMR (False Match Rate) results. Inputs (which are the measured data) are verified with the stored data and when the data matched the access is verified. For the account number and the PIN the data should match exactly. That is why the threshold value for these two tests is zero. But for the other inputs the threshold is defined so that one can get access with a very small variation in his/her measured data when compared with the stored data.

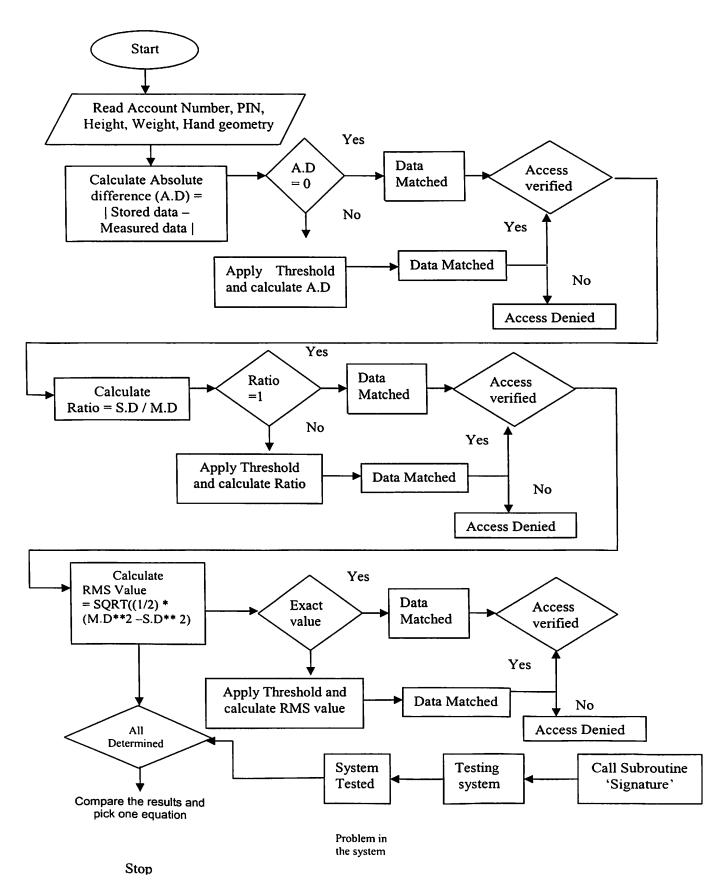

The flowchart for the design program in 6811 is shown in the Figure 6.

Stop

### Figure 6: The Flow Chart for the 6811 Program

Figure 7: Block Diagram for the simulation with Motorola MC6811

The ports are used to input the values and to output the results. The ports of 6811 have input, output and bi-directional pins. The block diagram shows the input/output connections. Some ports are bi-directional but specific pins are use for input and/or for output. Port E is used for input values. Height, weight and hand geometry are entered to this port. Port D is connected to the keyboard where the account number and pin are entered. Port A shows whether the data matched or not, if matched it gives access to the system and if not it denies access. The signature bits are calculated and are given as the output to the LCD's.

In the 6811microprocessor system with memory mapped I/O, although the I/O devices are connected to the processor the 6811 instructions access the I/O ports similar to memory. I/O devices are assigned addresses, and the software accesses I/O using read and writes to specific I/O address. The software gets data from an input device by using the same instructions as it would if it were reading from memory. Similarly the software drives data to an output device by using the same instructions as it would if he same instructions as it would he same instructions as it would if he same writing to memory. The memory map is shown in the Figure 8.

Figure 8: Memory Map For 6811

As shown in Figure 8 for a 6811 the address map for the devices are, for RAM address are from \$0000 to \$00FF, for I/O \$1000 to \$103F and for ROM \$E000 to \$EFFF.

The RAM (address from \$0000 to \$00FF), which contains the variables and stack, is shown in Figure 9. The variables specified are described in the assembly code. In general the input values are stored in accno, pinno, hg, wtB1, wtB2, fl1, fl2, fl3, fl4, fl5. The differences are stored in H, P, J, K, L, M, O. The one bit samples for signatures are stored in bit1, bit2, bit3, bit4, bit5, bit6, bit7, bit8. The internal test-points for the BIST are accbit, tp1, tp2, tp3, tp4, tp5, tp6, tp7. The stack pointer is started from \$F0.

| \$00 |   | accno (2 byte) |

|------|---|----------------|

| \$02 |   | pinno (2 byte) |

| \$04 |   | hg             |

| \$05 |   | wtB1           |

| \$06 |   | wtB2           |

| \$07 |   | fll            |

| \$08 |   | f12            |

| \$09 |   | fl3            |

| \$10 |   | fl4            |

| \$11 |   | f15            |

| \$12 |   | ac (2 byte)    |

| \$14 |   | H              |

| \$15 |   | P (2 byte)     |

| \$17 |   | J              |

| \$18 |   | K              |

| \$19 | 1 | L              |

| \$20 |   | M              |

| \$21 |   | 0              |

| \$22 |   | wt (2 byte)    |

| \$24 |   | pn (2 byte)    |

| \$26 |   | tmpb (2 byte)  |

| \$28 |   | bit1           |

| \$29 |   | bit2           |

| \$30 |   | bit3           |

| \$31 |   | bit4           |

| \$32 |   | bit5           |

| \$33 |   | bit6           |

| \$34 |   | bit7           |

| \$35 |   | bit8           |

| •    |   |                |

| \$45 |   | accbit         |

| \$46 |   | tp1            |

| \$47 |   | tp2            |

| \$48 |   | tp3            |

| \$49 |   | tp4            |

| \$50 |   | tp5            |

| \$51 |   | tp6            |

| \$52 |   | tp7            |

|      |   | · <b>T</b> · · |

| \$F0 |   | Stack          |

|      |   |                |

|      |   |                |

\$FF Figure 9: Memory Map for the Variables in RAM

The I/O ports, addresses from \$1000 to \$103F are shown in the Figure 10.

Figure 10: I/O Ports of 6811 (From \$1000 to \$103F)

#### Results

I have used the 6811 microprocessor to demonstrate my program accesses and verifies that it is working properly. As shown in the flowchart, in the program the variables are initialized and then the account number and PIN are entered from the keyboard, which is connected to Port D. The values of the height weight and the finger lengths are entered through port E. After entering the values they are compared with the database values and the differences are calculated. The threshold is checked for height, weight and the hand geometry and when these values are matched with the database values then the program permits access to the system otherwise it denies.

The program listing is in appendix C.

To carry test from the first step through this second step the Built-in Self-Test (BIST) technique is applied. In the 6811 the access verification program, the system can test itself and check whether it is fault free or faulty. Signature analysis technique is used in this program to test that. An 8bit LFSR is used to calculate the signature. The LFSR is implemented in an assembly language subroutine. One bit is taken from each input values (PIN, height, weight, and five finger lengths) and also from the database values to calculate the signature, when the signature matches it shows that the system is working properly and there is no fault in the system.

A surprising additional benefit of this LFSR approaches has been discovered in one of the test procedure where the signature of the entire database was calculated person by person. Error in the signature helped immediately identify error in the database. This demonstrates that the manufacturer functional test procedure of BIST with signature analysis is also useful for checking database integrity.

Values for both authorized and unauthorized cases are used as the input values in the program. It has been found that for the authorized individuals' values the system compares the values and gives access. And for the unauthorized individuals' values it shows that the values have not matched and it denies the access.

### Conclusions

The assembly language program has demonstrated that the access system works properly in TExaS simulator. The signature is also calculated to test the system whether it is fault free or not. The calculated signature has showed that the system is fault free. Our Main

goal here is to prototype the design to get feedback in short time and check that it is working properly. By using 6811 and demonstrating the program it has been found that the system is working well.

A notable benefit has been discovered that the system tests with signature is also good for checking data integrity. My next step is to design the system in verilog (the hardware description language) to show how the components of the system can be connected together. Then it will be simulated to test the design module before implementing the design to real hardware.

### **CHAPTER V**

#### FINAL IMPLEMENTATION

#### Introduction/Objective

Verilog, the hardware description language, is popular for designing digital circuitry. In this chapter, the implementation of the design for the access verification system from simple building blocks will be described. The implementation is the final product. Structural verilog is used here to describe how to put larger designs together out of smaller modules and building blocks all the way down to using the AMI standard cell library. Before implementing the design in hardware the simulator for verilog can test the functionality and timing of each design module. The simulator is also very useful for debugging designs without making the hardware prototypes.

#### **Design Description**

The access system combining the Rapid System Prototyping (RSP) with Built-In Self-Test (BIST) is the final product. It is the actual implementation of the design prototype. The access system consists of nine inputs and two outputs showing access or denial. The signatures are also shown as outputs of the final system. One of the signatures is based upon samples of the input values to test the overall system. The other signature is based upon internal tests points and the access output, to test the chip based upon the verilog, hardware description language. The Figure: 11 the block diagram shows the inputs and outputs of the final system.

Figure 11: Block Diagram of the Access System

Figure: 12, the detail block diagram, shows the connections of the different parts of the system. The 9 inputs (account number, pin, height, weight and 5 finger lengths) are stored in registers, which are then connected to two multiplexers. The three inputs, account number, pin and the weight are 16 bits and the other six inputs are 8 bits and they are padded with 0's to get a 16 bit values from the register.

One of the multiplexer has 8 inputs and 1 output with 3 bits of control, and the other multiplexer has two inputs and one output and one bit of control. One input is used at a time. The ALU (arithmetic and logic unit) does the arithmetic operation. ALU has 2 inputs, which are 16 bits and one output of 16 bits. The measured values and the database values are the two inputs of the ALU. The output is the difference of these two values.

\* 8 bit inputs are padded with "0" to get 16 bit value.

### Figure 12: Detail Block Diagram of Access System

Module control is in the testbench file. Another multiplexer is used to compare the limit. 8 threshold values (for PIN, height, weigh and hand geometry) are used for the differences that are obtained from the first ALU. The second ALU is used to apply the threshold values to get the result as output.

Two LFSR's are used to test the system. The system external to the access chip is tested with one LFSR that monitors the input. The other LFSR used to test the access chip is tested by monitoring outputs.

From 8 inputs (PIN, height, weigh and five finger lengths) stored in the register, one bit is taken from each input and are used as input for an 8bit LFSR to calculate the signature. This 8bit LFSR is used here as a part of Built- In Self-Test (BIST). In designing the access verification system the BIST is also a part of the system, which will test the system itself by calculating the signatures and showing that it is working fault free. Another 8bit LFSR uses 7 low order bits from the results of the second ALU and 1 bit from the access control output. This LFSR tests the access chip by monitoring the outputs.

#### Conclusions

The module has been tested with a testbench file. With this testbench file all the connections of the design module are tested and the signatures are calculated. It has been demonstrated that this system implementation successfully solves the problem of improved access verification.

### **CHAPTER VI**

#### **CONCLUSIONS**

#### Conclusions

In this thesis a new design methodology was proposed and demonstrated. Rapid System Prototyping (RSP) in the development process permitted early feedback for update requirements. Prototyping is fast and incorporating BIST in the design prototype ensures the quality of the final design without slowing down the design process. In this project nine inputs (account number, PIN, height, weight and five finger lengths) were used to provide secure identity verification of the system.

One of the advantages of using BIST is it reduces the cost of testing when compared with an external test using automatic test equipment. In this project BIST with signature analysis, helped check the database integrity. The surprise side benefit during prototyping was that an error in signature helped identify the error in the database.

For my access verification system, software prototyping the design (in Fortran) with the throw-away approach was used to evaluate and compare access design decisions. Based on those results, one equation was picked and used in second prototyping stage with 6811 microprocessor.

Then the system was designed in verilog and it was successfully simulated with a test bench file. In all these steps, the signatures (both whole system and chip) were calculated as a part of the BIST.

This thesis demonstrates a process to design a high quality new product by using BIST in prototyping phase. It links testing with security as well as testing with rapid system prototyping.

### Recommendations

Future research is recommended for comparing other biometric measures. Some physical measurements variation should be solved over a longer time period. For example the weight would vary more over some years. So an update of the biometric database would be required. Also the system could be submitted to the MSIS (Management Science and Information Systems) department of OSU, as a project to evaluate its security.

#### REFERENCES

Abramovici, Breuer and Friedman, "Digital Systems Testing and Testable Design", Computer Science Press, 1990.

[2]. Acken J. M, "Deriving Accurate Fault Models", September 1988.

[3]. Bardell P.H., McAnney W.H., Savir J, "Built-In Test for VLSI: Pseudorandom techniques", John Wiley& Sons, New York, 1987.

[4]. Booth C.J. and Kurpis G.P., The New IEEE Standard Dictionary of Electrical and Electronics Terms [Including Abstracts of All Current IEEE Standards]. Fifth Edition, New York: IEEE, 1993.

[5]. Frohwerk, "Signature Analysis: A New Digital Field Service Method", Hewlett-Packard J. May 1977.

[6]. Gulati R.K and Hawkins C.F, "IDDQ Testing of VLSI Circuits", Kluwer Academic Publishers, 1993.

7]. Kordon, F and Luqi, "An introduction to Rapid System Prototyping", IEEE Transaction on software Engineering, Vol 28, September 2002.

[8]. Masfield T, Kelly G, Chandler D, Kane J, "Biometric Product Testing Final Report", Issue 1.0, 19<sup>th</sup> March 2001.

[9]. McCluskey, E.J and Buelow, F " IC Quality and test transparency", International test conference, Proc. IEEE Sept 1988, pp. 295- 301

[10]. McCluskey, E.J and Bozorgui-Nesbat, S. " Design for Autonomous Test", Proceeding of International Test Conference, 1980

[11]. Valvano Jonathon W, "Embedded Microcomputer System", Brooks/Cole Thomson Learning, 2000.

Appendices

### Appendix A

Fortran Source Code

**PROGRAM** Access INTEGER accn(20) INTEGER PIN(15), pn(15) INTEGER ACCOUNTNUMBER, ac(15) REAL HEIGHT(15), WEIGHT(15), hg(15), wg(15), L1(15) REAL L2(15), L3(15), L4(15), L5(15) REAL fl1(15), fl2(15), fl3(15), fl4(15), fl5(15) INTEGER ADPIN, ADAC, VAC1, VAC2, VAC3 REAL VAC, RMSAC REAL ADHG, ADWG, ADL1, ADL2, ADL3, ADL4, ADL5 REAL RAC, RPIN, RHG, RWG, RFL1, RFL2, RFL3, RFL4, RFL5 INTEGER VP1, VP2, VP3 REAL RMSPN, VP REAL VHG, VHG1, VHG2, VHG3, RMSHG REAL VWG, VWG1, VWG2, VWG3, RMSWG REAL VL, VL1, VL2, VL3, RMSL1 REAL V2L1, V2L2, V2L3, V2L, RMSL2 REAL V3L1, V3L2, V3L3, V3L, RMSL3 REAL V4L1, V4L2, V4L3, V4L, RMSL4 REAL V5L1, V5L2, V5L3, V5L, RMSL5

- C OPEN DATA FILE OPEN(UNIT=10, FILE='DATA1.TXT', STATUS='OLD') OPEN(UNIT=20, FILE='SAMPLE1.TXT', STATUS='OLD')

- C WRITTING THE OUTPUT FILES OPEN(UNIT=30, FILE='OP.TXT', STATUS='UNKNOWN') OPEN(UNIT=31, FILE='OP1.TXT', STATUS='UNKNOWN') OPEN(UNIT=32, FILE='OP2.TXT', STATUS='UNKNOWN') OPEN(UNIT=33, FILE='OP3.TXT', STATUS='UNKNOWN') OPEN(UNIT=34, FILE='OP4.TXT', STATUS='UNKNOWN') OPEN(UNIT=35, FILE='OP5.TXT', STATUS='UNKNOWN') OPEN(UNIT=36, FILE='OP6.TXT', STATUS='UNKNOWN') OPEN(UNIT=37, FILE='OP7.TXT', STATUS='UNKNOWN') OPEN(UNIT=38, FILE='OP8.TXT', STATUS='UNKNOWN')