# UNIVERSITY OF OKLAHOMA GRADUATE COLLEGE

## FAST AND PRECISE POWER PREDICTION FOR COMBINATIONAL CIRCUITS CONSIDERING GLITCHING EFFECTS

#### A Dissertation

## SUMITTED TO THE GRADUATE FACULTY

in partial fulfillment of the requirements for the

degree of

Doctor of Philosophy

By

HONGPING LI Norman, Oklahoma 2003 UMI Number: 3109061

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

#### UMI Microform 3109061

Copyright 2004 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

## Fast and Precise Power Prediction for Combinational Circuits Considering Glitching Effects

## A Dissertation APPROVED FOR THE SCHOOL OF COMPUTER SCIENCE

BY

John K. Antonio, Committee Chair

Sudarshan Dhall

S. Lakshmivarahan

K. Thulasiraman

Victor DeBrunner

#### **ACKNOWLEDGEMENTS**

There are lots of people I would like to thank for a huge variety of reasons.

Firstly, I would like to thank my Supervisor, Dr. John K. Antonio. I could not have imagined having a better advisor and mentor for my Ph. D., and without his common-sense, knowledge, perceptiveness and cracking-of-the-whip I would never have finished. I would also like to thank Dr. Dhall and Dr. Varahan, who have helped immeasurably with contributions ranging from giving research lectures and suggestions to mentoring. Special thanks to Dr. K. Thulasiraman for giving me lots of suggestions. Thank you to all my examiners including Dr. DeBrunner (external), for managing to read the whole thing.

I would also like to thank all the rest of the academic and support staff of the School of Computer Science at The University of Oklahoma. Especially thanks to Barbara Bledsoe for finding lots of stuff for me to move around to keep my muscles strong. Thanks to Jim Summers for keeping my computer healthy and thanks to Sandy Johnson and Shanna Singleton for all they did for me.

Also thanks Dr. Su and Dr. Wei for putting up with me for almost three years. I really enjoyed the time we spent together especially fishing during the weekend. I would like to thank my family, my parents, have encouraged and supported me through years and years of school. I can't thank them enough for the loving environment they provided.

### TABLE OF CONTENTS

| ABSTRACT                                                 | XIII |

|----------------------------------------------------------|------|

| CHAPTER 1 INTRODUCTION                                   | 1    |

| CHAPTER 2 SOURCES OF POWER CONSUMPTIONS IN CMOS CIRCUITS | 8    |

| 2.1 Introduction                                         | 8    |

| 2.2 Three Sources of Power Consumption                   | 8    |

| 2.2.1 Brief Overview                                     | 8    |

| 2.2.2 Switching Current Power Dissipation                | 9    |

| 2.2.3 Short-Circuit Power Dissipation                    | 13   |

| 2.2.4 Leakage Current Power Dissipation                  | 15   |

| 2.3 Methodologies of Estimation of Power Consumption     | 16   |

| 2.3.1 Brief Overview                                     | 16   |

| 2.3.2 Statistical-Based Power Estimation                 | 18   |

| 2.3.3 Probabilistic-Based Power Estimation               | 21   |

| 2.4 Summary                                              | 22   |

| CHAPTER 3 PROBABILISTIC-BASED POWER ESTIMATION           | 25   |

| 3.1 Introduction                                         | 25   |

| 3.2 Modeling of Signals                                  | 25   |

| 3.3 Signal Probability Calculation                       | 28   |

|   | 3.3.1 Early Algorithm                                 | 29  |

|---|-------------------------------------------------------|-----|

|   | 3.3.2 General Algorithm                               | 31  |

|   | 3.3.3 CCM Algorithm                                   | 33  |

|   | 3.3.4 BDD Algorithm                                   | 35  |

|   | 3.4 Signal Activity Calculation                       | 38  |

|   | 3.4.1 Relative Boolean Difference Approach            | 38  |

|   | 3.4.2 Generalized Boolean Difference Approach         | 41  |

|   | 3.5 Summary                                           | 51  |

| C | CHAPTER 4 MARKOV-CHAIN SIGNAL MODEL AND MCP ALGORITHM | 53  |

|   | 4.1 Introduction                                      | 53  |

|   | 4.2 Markov Chain Signal Model                         | 55  |

|   | 4.2.1 Preliminaries                                   | 55  |

|   | 4.2.2 Definition of Correlation Cofactors             | 57  |

|   | 4.3 Markov Chain Model for Basic Logic Gates          | 59  |

|   | 4.4 Calculation of Correlation Factors                | 68  |

|   | 4.5 Markov Chain Propagation Algorithm                | 86  |

|   | 4.6 Summary                                           | 90  |

| C | CHAPTER 5 GLITCHING POWER CONSUMPTION ESTIMATION      | 92  |

|   | 5.1 Introduction                                      | 92  |

|   | 5.2 Probabilistic Glitching Model                     | 95  |

|   | 5.3 Markov Chain Propagation with Glitching Algorithm | 103 |

|   | 5.4 Summary                                           | 106 |

| CHAPTER 6 EXPERIMENTAL SETUP AND RESULTS | 108 |

|------------------------------------------|-----|

| 6.1 Introduction                         | 108 |

| 6.2 Experimental Setup                   | 108 |

| 6.2.1 Signal Generator                   | 109 |

| 6.2.2 Circuit Description Format         | 111 |

| 6.2.3 PSpice Simulator                   | 114 |

| 6.2.4 Filter                             | 114 |

| 6.2.5 MCP Algorithm Simulator            | 115 |

| 6.3 Experimental Results                 | 115 |

| 6.3.1 MCP Algorithm VS Other Algorithms  | 115 |

| 6.3.2 MCP Algorithm (Zero-Delay Model)   | 116 |

| 6.3.3 Glitching Power Prediction         | 120 |

| Chapter 7 Summary                        | 127 |

## LIST OF TABLES

| Table 3-1. The output probability expression of some basic logic gates                |

|---------------------------------------------------------------------------------------|

| Table 3-2. Comparison of actual signal probabilities and those calculated using       |

| General Algorithm for the circuit of Figure 3-2 with $P(x_1) = P(x_2) = 1/2$ 32       |

| Table 3-3. Set of basic rules used to calculate the probability of output signals and |

| correlation coefficients by given input signals' probability and correlation          |

| coefficients                                                                          |

| Table 4-1. Probability expressions of 16 transition edges associated with Figure 4-   |

| 361                                                                                   |

| Table 4-2. Formulas for computing Markov chain parameters for the output of           |

| basic gates66                                                                         |

| Table 4-3. Probability and activity values of output signals of basic gates 67        |

| Table 4-4. Set of basic rules used to calculate the output correlation factors 82     |

| Table 5-1. The cases that cause glitching in an AND gate $(Y=AB)$                     |

| Table 5-2. The cases that cause glitching for OR gate $(Y=A+B)$                       |

| Table 5-3. The cases that cause glitching for XOR gate ( $Y = A \oplus B$ )           |

| Table 5-4. The activity calculation results for three basic gates, AND, OR and        |

| XOR, by given the probabilities, activities, correlation factors and delay            |

| times in the assumption that signal $B$ has $d$ unit time delay than signal $A$ . 102 |

| Table 6-1. Results of output signal Y of a two-input multiplexer using different     |

|--------------------------------------------------------------------------------------|

| algorithms                                                                           |

| Table 6-2. Results obtained from C17 circuit                                         |

| Table 6-3. Results from MCP Algorithm and Simulation Studies for Circuit C432        |

| from the ISCAS-85 Benchmark Set                                                      |

| Table 6-4. The activity values for output signals for Figure 6-6 considering         |

| glitching and without considering glitching                                          |

| Table 6-5. Results of some most significant (i.e., largest) error signals in circuit |

| C432                                                                                 |

## LIST OF FIGURES

| Figure 2-1. Operation of a CMOS inverter driving a load capacitor $C_L$ : (a)                 |

|-----------------------------------------------------------------------------------------------|

| inverter circuit model, (b) discharging phase, (c) charging phase9                            |

| Figure 2-2. Short-circuit current in an inverter                                              |

| Figure 2-3. Two methodologies used to estimate the power consumption in                       |

| CMOS circuits                                                                                 |

| Figure 2-4. The block diagram of the Monte-Carlo method                                       |

| Figure 2-5. The typical diagram flow of probabilistic-based power estimation                  |

| approaches                                                                                    |

| Figure 2-6. Summary of most techniques used to estimate switching activities in               |

| CMOS circuits. 24                                                                             |

| Figure 3-1. The impact on the number of transitions with different input vectors              |

| with different correlations derived from [13]                                                 |

| Figure 3-2. An example combinational circuit used to illustrate signal probability            |

| calculations (derived from [7])                                                               |

| Figure 3-3. A BDD representation of Boolean function $f = x_1 \cdot x_2 + x_3 \cdot \dots 37$ |

| Figure 3-4. An example to illustrate the effect of simultaneous switching (derived            |

| from [4])41                                                                                   |

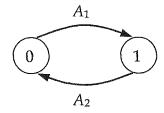

| Figure 4-1. Proposed Markov chain signal model 56                                             |

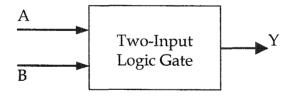

| Figure 4-2. Generic two-input logic gate                                                    |

|---------------------------------------------------------------------------------------------|

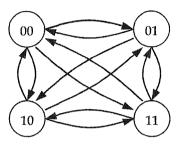

| Figure 4-3. State transition diagram for inputs <i>A</i> and <i>B</i> of Figure 4-2 60      |

| Figure 4-4. An Example to show the calculation of correlations among three                  |

| signals70                                                                                   |

| Figure 4-5. The circuit diagram associated with the fan-out rule                            |

| Figure 4-6. The circuit diagram associated with the AND rule                                |

| Figure 4-7. The circuit diagram associated with the OR rule77                               |

| Figure 4-8. The circuit diagram associated with the XOR rule                                |

| Figure 4-9. The circuit diagram associated with the NOT rule 82                             |

| Figure 4-10. Illustration of the basic steps of the MCP Algorithm                           |

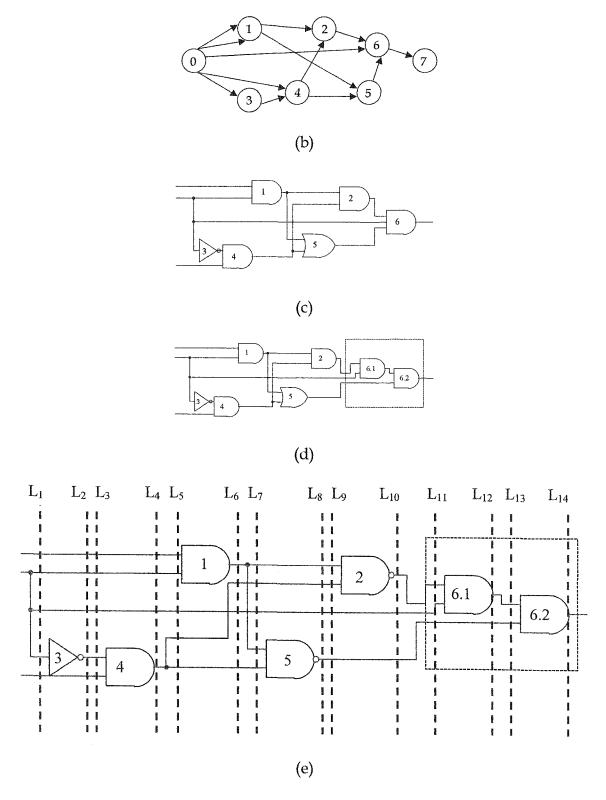

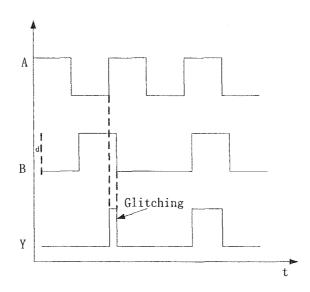

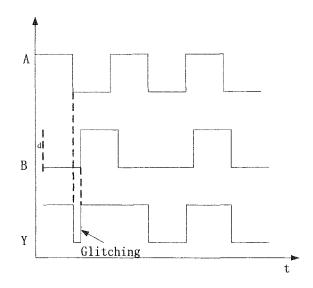

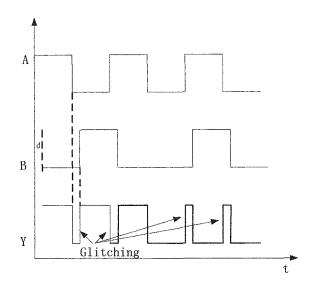

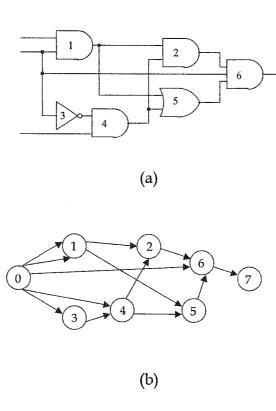

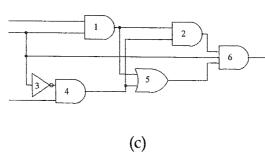

| Figure 5-1. An example used to show how non-zero delays cause glitches 94                   |

| Figure 5-2. The $d$ unit time delay causes glitching in an AND gate ( $Y=AB$ ) 96           |

| Figure 5-3. The $d$ unit time delay causes glitching in an OR gate ( $Y=A+B$ ) 98           |

| Figure 5-4. The $d$ unit time delay causes glitching in a XOR gate ( $Y = A \oplus B$ ) 100 |

| Figure 5-5. Illustration diagrams for basic steps of the MCPG Algorithm 106                 |

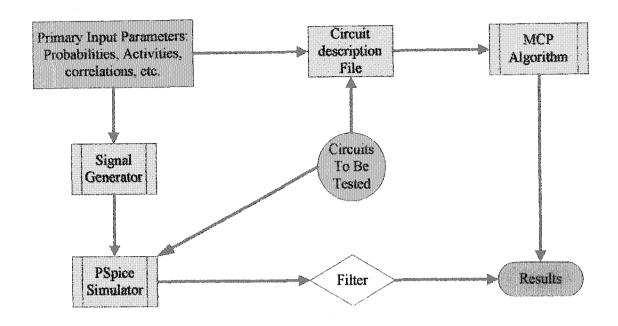

| Figure 6-1. Components of experimental setup to test the accuracy and efficiency            |

| of different approaches                                                                     |

| Figure 6-2. Signal A with two transition states 0 and 1, and two transition events          |

| $A_1$ and $A_2$                                                                             |

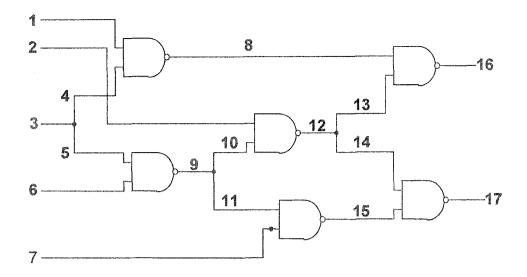

| Figure 6-3. An example circuit named C17 used to illustrate the netlist formation           |

| (ISCAS85 format)                                                                            |

| Figure 6-4. A two-input multiplexer for the first test case                                 |

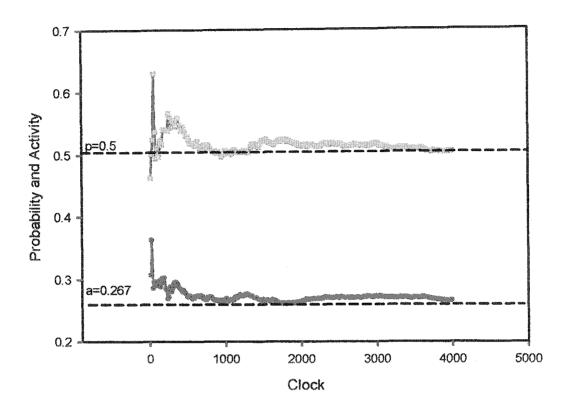

| Figure 6-5. Activity and probability convergence plot at output node $y$            |

|-------------------------------------------------------------------------------------|

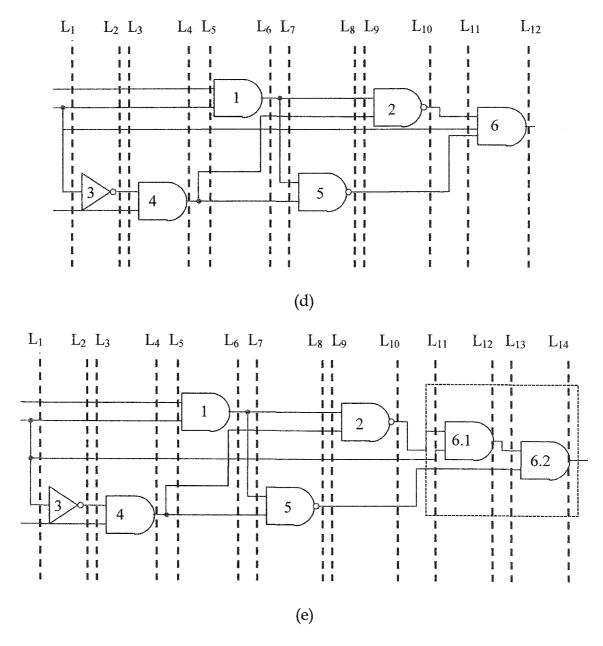

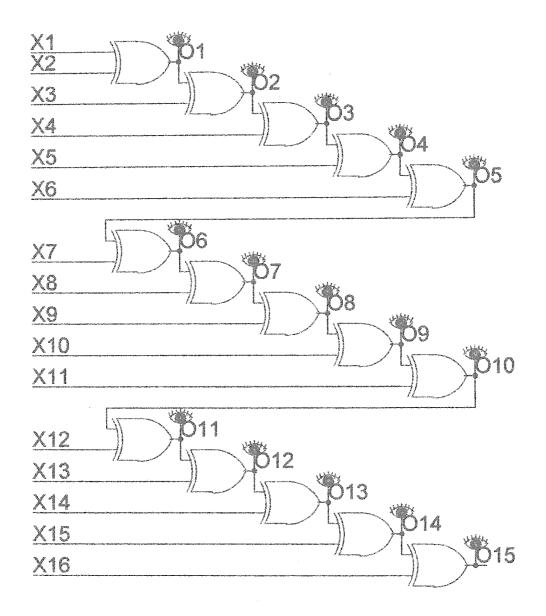

| Figure 6-6. A special example to show the large difference of the activity of the   |

| output signal O15 between considering glitching and without considering             |

| glitching121                                                                        |

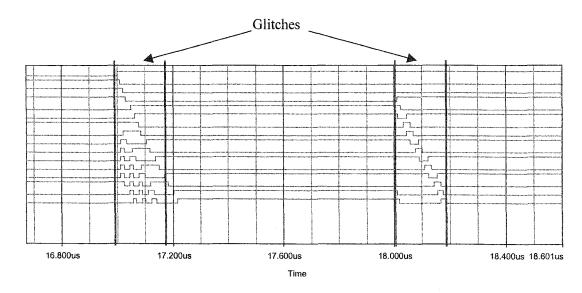

| Figure 6-7. A result from PSpice simulation run of the circuit in Figure 6-6, which |

| illustrates glitches effect the next stage                                          |

| Figure 6-8. Results produced by MMCP algorithm running under different l            |

| values                                                                              |

#### ABSTRACT

Hongping Li (Ph.D. Computer Science)

Fast and Precise Power Prediction for Combinational Circuits Considering Glitching Effects

Directed by Dr. John K. Antonio, Director and Professor, The School of Computer Science, University of Oklahoma

The power consumed by a combinational circuit is dictated by the switching activities of all signals associated with the circuit. Analytical approaches, named MCP and MCPG algorithms, are proposed for calculating signal activities for combinational circuits, and the later considers glitching effects. Both approaches are based on a Markov chain signal model, and directly account for correlations present among the signals. The accuracy of the approaches is verified by comparing signal activity values calculated using the proposed approaches with corresponding values produced through simulation studies. Another approach (called the MMCP algorithm) is also proposed to calculate the total transition activities including glitching, and can be more accurate than the proposed MCPG algorithm. It is also demonstrated that the proposed approaches are computationally efficient.

#### CHAPTER 1

#### INTRODUCTION

Power consumption of integrated circuits (ICs) is of growing concern as more electronic devices are being deployed in mobile and portable applications, e.g., PDAs, mobile telephones, and other battery-powered electronic devices. As the functionality of such devices increases, so does the complexity and sophistication of the underlying circuits. More complexity and faster clock rates generally translate into higher power consumption for a given hardware implementation technology. Because battery technology has not improved at the same rate as IC technology, there is strong motivation to design circuits that are as power efficient as possible to extend battery life for portable devices.

Improvements in IC technologies (e.g., reduction in feature size) can reduce power requirements of a given circuit design. However, functionality and complexity of commercial devices generally increase from one generation to the next. So, the next generation device implemented with the next generation IC technology will generally have more functionality and complexity than the previous generation. Thus, the issue of architectural design of the underlying circuits to be power efficient remains important. Predicting and optimizing the power consumption during the design phase is critical for low power designs.

Power consumption in a CMOS circuit is primarily due to three types of current flow: switching current, leakage current, and short circuit current [11]. The first type of current flow is switching current for charging and discharging load capacitance due to switching activities. The short-circuit current within CMOS gates is caused by a brief short circuit that can occur when the state of the complimentary gates changes from on-to-off and off-to-on. This short circuit occurs when the complimentary MOSFETs are concurrently "on" for a brief transient period of time. The leakage current is associated with the imperfection of field effect transistors (FETs) that are used in CMOS devices.

The total power dissipation of a CMOS circuit is the sum of the three types of power consumption, i.e., switching current power dissipation, short-circuit current power consumption and leakage current power consumption. Because the dynamic power dissipation is by far the dominant component, almost all methods used to calculate power consumption in CMOS circuits are focused on estimation of dynamic power consumption [14, 15].

Because the power estimation is calculated at the gate level, assuming both the supply voltage and the capacitance are known, the power consumption can be estimated by calculating the switching activity for each circuit node.

Power dissipation is strongly dependent on the applied input signals to the circuit. Each applied input propagates through the circuit causing the internal nodes to perform transitions according the functionality and the interconnection of the circuit gates. The same circuit under different input scenarios may have

totally different switching activities of the internal nodes, which will have different power dissipation. Thus the applied input must be taken into account.

The power estimation methodologies at the logic gate level can be divided into two general classes: the statistical-based and probabilistic-based methodologies. The statistical-based power estimation approaches use a large number of input vectors to simulate the circuit in order to achieve near real results and such simulations are highly dependent on the primary input vectors. This often makes statistical-based approaches impractical for large circuits and long input sequences. Several methods have been developed to overcome this drawback and the Monte-Carlo, the Advanced Sampling and the Vector Compaction methods are the most representative approaches [12, 14, 15].

Compared to the statistical-based approaches, probabilistic-based approaches compute switching activities in one run, which may result in much less computation time, but the accuracy may not be as good as statistical-based approaches. The goal of the research in this dissertation is to develop a signal model for a probabilistic-based approach that can achieve near statistical-based approaches' accuracy with much less time complexity.

Signals in a combinational logic circuit can be treated in a probabilistic sense, i.e., for signal x, the probability that x has logic value "1" is defined by P(x) = P(x = 1). Let x(t),  $t \in (-\infty, +\infty)$ , be a stochastic process that takes the values of logical "0" or logical "1", transitioning from one to the other at random times. Generally, a stochastic process is said to be strict-sense stationary (SSS) if its

statistical properties are invariable to a shift of time origin. Based on the assumption of a SSS 0-1 mean-ergodic process, the probability of a signal x(t) can be defined as the average fraction of time that the signal is high, and the activity can be defined as the average number of transitions in a time interval.

Several probabilistic-based approaches used to calculate signal probabilities, i.e. P(x), of all signals in a circuit are developed in [2, 6, 7]. Although this probability calculation is not directly used in calculating a circuit's power consumption, it is a necessary component for signal models common to the activity approaches, which utilize both signal probability and signal activity parameters [3, 4].

The approaches of [2], [3], and [4] can have high computational complexities because the number of terms in the underlying equations/transformations can grow exponentially with the number of primary inputs to the circuit. In [7], a trade-off between computational complexity and resulting accuracy is illustrated in the context of the underlying equations/transformations introduced in [2]. In particular, an approximate approach is defined in [7] in which the transformations of [2] are applied in a "gate-by-gate" fashion. Thus, instead of deriving the transformation for a signal's probability parameter in terms of the circuit's primary inputs, it is derived in terms of the immediate inputs to the logic gate associated with the signal. This approach greatly reduces the computational complexity, but introduces error in the calculated probability parameters for circuits with re-convergent fan-out.

Similar trade-offs between computational complexity and accuracy are possible relative to the evaluation of activities associated with [3] and [4], respectively. Instead of deriving a signal's logic function in terms of the circuit's primary inputs, the parameters to the immediate inputs of the signal's logic gate can be used. Again, this type of "gate-by-gate" technique will generally introduce error because it does not account for correlations present among the internal signals that drive the gates within the circuit. The approach of [6] is a fast and accurate "gate-by-gate" technique for calculating a signal's probability parameter. It introduces the concept of a correlation factor to account for and appropriately adjust the transformation for correlated inputs to a gate.

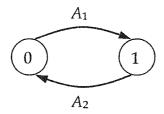

Signals can be modeled by a Markov-Chain, having two states: state 0 and state 1, associated with two transition events: the transition event from state 0 to state 1 and the transition event from state 1 to state 0. It is shown that the proposed Markov chain model is equivalent to the two-parameter probability/activity signal model of [3] and [4]. The advantage of modeling signals with Markov chains is that it makes it possible to compute correlations between signals related to both probability and activity. Based on this Markov-chain signal modeling, we can develop a more efficient and more accurate algorithm (named MCP algorithm) by propagating signal parameters and correlation cofactors from the primary inputs through a "gate-by-gate" fashion. This MCP algorithm can achieve a very good accuracy and an  $O(M^2)$  time complexity where M is the number of signals in the circuit.

Because the MCP algorithm assumes zero propagation delay through each gate, it will generate errors in real applications. In reality, gates have non-zero delays, which results in "signal glitching." In non-zero delay model, glitches will cause errors in general power consumption estimation algorithms and tools that assume a zero-delay model. So a MCPG algorithm is developed expanded from the MCP algorithm to take account of glitching effects. Compared to MCP algorithm, MCPG algorithm computes the glitching transitions caused by the associated input delays and propagates these glitching transitions to the next stage. Because it is assumed that the target circuit can be run ideally at infinite speed, every glitch may cause new glitches in the next stage, which gives us an upper bound of the activity of each node in the circuit.

Because circuits cannot run at an infinite frequency, MCPG algorithm will not generally give us an accurate result in real applications. To deal with this situation, another algorithm, named MMCP algorithm, is developed. It is shown that MCPG algorithm gives us a good prediction of the maximum activity of each node, which is an upper bound of the activity of each node, and the MMCP algorithm produces a closer prediction of activities of all signals in the circuit.

This thesis is organized as follows: In Chapter 2, three sources of power consumption will be discussed in detail and methodologies of estimation of power consumptions in CMOS circuits are also reviewed. Because we are focused on probabilistic approaches, we will briefly overview those past probabilistic-based approaches in Chapter 3. In Chapter 4, a Markov-Chain

signal model is developed and based on this signal model, the MCP algorithm is proposed and analyzed in detail. In Chapter 5, the MCPG algorithm expanded from the MCP algorithm is developed to deal with glitching power consumption. To investigate the accuracy and efficiency of algorithms we developed, experimental setup and results are listed in Chapter 6. A more accurate glitching power consumption prediction algorithm is also introduced in Chapter 6, which is named MMCP algorithm. The final summary and future work is in Chapter 7.

#### CHAPTER 2

#### Sources of Power Consumptions in CMOS Circuits

#### 2.1 Introduction

In this chapter, three sources of power consumption will be addressed first. Then the estimation of power consumption problem is stated, followed by an overview of past methodologies for estimation of CMOS power consumption.

#### 2.2 THREE SOURCES OF POWER CONSUMPTION

#### 2.2.1 Brief Overview

Power consumption in a CMOS circuit is primarily due to three types of current flow: switching current, short circuit current and leakage current [11], which are summarized in the following equation:

$$P_{avg} = P_{switching} + P_{short-circuit} + P_{leakage}. {2.1}$$

The first type of current flow, switching current, is due to charging and discharging of load capacitance associated with signal switching activities. The short-circuit current within CMOS gates is caused by a brief short circuit that can occur when the state of the complimentary gates changes from on-to-off and off-

to-on. This short circuit occurs when the complimentary MOSFETs are concurrently "on" for a brief transient period of time. The leakage current is associated with the imperfection of field effect transistors (FETs) that are used in CMOS devices. These three components of power consumption are described in detail below.

#### 2.2.2 Switching Current Power Dissipation

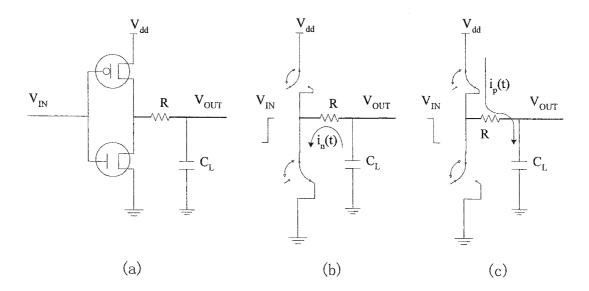

The switching current power consumption (also called dynamic power dissipation),  $P_{switching}$ , is caused by the charging and discharging of capacitances in the circuit. To illustrate the computation of dynamic power dissipation in a CMOS circuit, we use an example of a CMOS inverter driving a load capacitor  $C_L$ , as shown in Figure 2-1a.

Figure 2-1. Operation of a CMOS inverter driving a load capacitor  $C_L$ : (a) inverter circuit model, (b) discharging phase, (c) charging phase.

As shown in Figure 2-1, the dynamic power consumption of an inverter is associated with power dissipated in charging and discharging of the load capacitor. To simplify the analysis, assume the input signal,  $V_{in}$ , is a square wave having a period T and that the rising and fall time of  $V_{in}$  is much less than the period T. The rise time and fall time of a signal are depicted in Figure 2-2 as  $T_r$  and  $T_{fr}$  respectively. Assume the circuit is initially in a steady state with input having a logic value "0" and thus the output has a logic value "1". In this state the output capacitor is charged and the output voltage is  $V_{did}$ . When the input waveform undergoes a rising transition, the nMOS transistor conducts (ON) and the pMOS transistor turns OFF as shown in Figure 2-1b. Current is drawn from capacitor  $C_L$ , and the capacitor is discharged, resulting in an output voltage of zero. During this discharging process the average power dissipated can be expressed as

$$P_{\text{discharging}} = \frac{1}{T} \int_{0}^{\frac{T}{2}} i_n(t) V_{out}(t) dt, \qquad (2.2)$$

where  $i_n(t)$  is the current flowing from the capacitor through the nMOS to the ground as shown in Figure 2-1b.

As the input waveform goes from "1" to "0" (having a falling transition), the pMOS transistor will be ON and the nMOS will be OFF as shown in Figure 2-1c. In this charging phase, the current will flow from the power supply  $V_{dd}$  through the pMOS to the capacitor, and the average power consumed due to charging can be expressed as

$$P_{\text{charging}} = \frac{1}{T} \int_{\frac{T}{2}}^{T} i_p(t) (V_{dd} - V_{out}(t)) dt.$$

(2.3)

Using the assumptions that  $i_n(t) = -C_L \frac{dV_{out}(t)}{dt}$ ,  $i_p(t) = C_L \frac{dV_{out}(t)}{dt}$ ,  $V_{out}(0) = V_{dd}$ ,  $V_{out}(T/2) = 0$ , and  $V_{out}(T) = V_{dd}$ , the total power dissipation during charging and discharging can be expressed as 1

$$P_{\text{switching}} = P_{\text{charging}} + P_{\text{discharging}} = \frac{C_L V_{dd}^2}{T}. \tag{2.4}$$

Assume f represents the frequency (switching frequency) of the input signal, and f = 1/T, then the above equation can be rewritten as

$$P_{\text{switching}} = C_L V_{dd}^2 f . {2.5}$$

The dynamic power dissipation is the dominant factor compared with the other components of power dissipation in CMOS circuits. For current technologies, the dynamic power dissipation is about 80% of a circuit's total dissipation [14, 15]. Consequently, the majority of existing low power design and power estimation techniques focus on this dynamic component of dissipation.

Equation 2.5 shows that the dynamic power consumption in a CMOS circuit is proportional to the switching frequency, load capacitance and the square of the supply voltage. Based on this observation, the power reduction can be achieved by these methods:

<sup>&</sup>lt;sup>1</sup> The  $V_{out}$  (T/2) = 0 and  $V_{out}$  (T) =  $V_{dd}$  are based on the assumption that the RC time constant for the circuit satisfies RC << T.

- □ Reduction of output capacitance, C<sub>L</sub>

- $\Box$  Reduction of power supply voltage,  $V_{dd}$

- □ Reduction of the average switching frequency, *f*

Generally, power reduction can be achieved by the combination of one or more aforementioned methods. A very popular low power strategy aims at the reduction of the product of the load capacitance and the switching frequency, i.e.,  $C_L f$ , which sometimes is called *effective capacitance*. It is noted here that a signal waveform is generally not a periodic regular signal like the "clock" signal assumed in this analysis. In general, f represents the "average" frequency of a signal, and determines this value for all signals in a circuit is the focus of this dissertation.

Another main low power reduction strategy, which is one of the most aggressive techniques, is the reduction of supply voltage because the power savings are significant due to the quadratic dependence of  $V_{dd}$  (as shown in Equation 2.5). The disadvantage of this technique is that it might decrease the performance of the circuits, specifically, the reduction of the power supply voltage leads to an increase to the delay propagation. Thus, reducing supply voltage leads to a trade-off between the power consumption and the circuit's speed.

#### 2.2.3 SHORT-CIRCUIT POWER DISSIPATION

The short-circuit power consumption,  $P_{short-circuit}$ , is caused by the current flow directly from the power supply to the ground during the transition phase. Consider again the CMOS inverter shown in Figure 2-1. Assume initially that  $V_{in} = 0$  and then starts to increase from zero to  $V_{dd}$ . When  $V_{in} \ge V_{Tn}$  where  $V_{Tn}$  is the threshold of the nMOS, the nMOS starts to come out of cutoff and enters in conducting state. The load capacitor starts to discharge through nMOS and  $V_{ont}$  begins to decrease. At this time because pMOS is not totally cutoff, there exists a conducting path for current to flow directly from the  $V_{dd}$  to the ground. This current flow directly from the power supply to the ground is called the short-circuit current. When  $V_{in}$  increases to the point of  $V_{dd} - V_{in} < |V_{Tp}|$ , where  $V_{Tp}$  is the threshold of the pMOS, the pMOS is totally cutoff. This process for  $V_{in}$  changing from  $V_{dd}$  to zero follows a similar sequence of events.

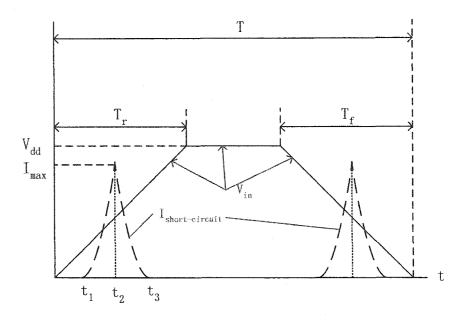

Figure 2-2 shows the short-circuit current behavior in an inverter. Exact analysis of the power dissipation due to short-circuit is complex. Here we give a simplified analysis which will give an upper bound of the power consumption due to short-circuit current in an inverter [12].

To simplify, consider a symmetric inverter (i.e.,  $V_{Tn} = V_{Tp}$ ) with a symmetric input signal  $V_{in}$  as shown in Figure 2-2. The rise and fall time of  $V_{in}$  are denoted by  $T_r$  and  $T_f$ . The time-averaged short-circuit current drawn from the power supply and the power dissipated due to this current of the symmetric inverter can be approximated by [12]

$$I_{short-circuit_{ovg}} = \frac{k}{V_{dd}} (V_{dd} - V_T)^3 T_r f$$

(2.6)

$$P_{short-circuit} = k(V_{dd} - V_T)^3 T_r f, \qquad (2.7)$$

Figure 2-2. Short-circuit current in an inverter.

respectively, where k is a constant that depends on transistor sizes as well as technology,  $V_T$  is threshold voltage of the nMOS and pMOS transistors,  $T_r$  is the rise (or fall time) of the symmetric input signal, and f is the switching frequency.

Reduction in the short-circuit power dissipation can be achieved in different ways. From Equation 2.7, the power is proportional to the rising (or falling time) of the input signal and the switching frequency and therefore, reducing these input transition times decrease the short-circuit current. In addition, new technology will help to reduce the constant k value and the power supply voltage

as a result to reduce the power dissipation due to short-circuit current in CMOS circuits.

#### 2.2.4 Leakage Current Power Dissipation

The power dissipation due to leakage current (also called static power dissipation) is caused by the imperfection of the MOSFET devices. Consider the same inverter as shown in Figure 2-1, when the input signal is  $V_{in} = 0$ , the pMOS is ON and nMOS is in cutoff, and vise visa, when  $V_{in} = V_{dd}$ , the pMOS will be cutoff and the nMOS is ON. Hence, ideally, whenever the input  $V_{in}$  stays in "0" or  $V_{dd}$ , no current flows from the power supply to the ground. A very small amount of power dissipation, though, does take place. This small amount of power dissipation is due to the leakage currents flow from the power supply to the ground, which is also called static power consumption.

The static power dissipation can be expressed by  $P_{static} = I_{leak}V_{dd}$  [13]. Compared to the other two types of power consumption in CMOS circuits, static power consumption is the smallest part and is often ignored in power consumption estimation. In our research, we mainly focus on power dissipation due to switching current to approximate the total power consumption by using

$$P_{avg} \approx P_{switching} = C_L V_{dd}^2 f . {(2.8)}$$

If the parameters are given, such as  $C_L$  and  $V_{dd}$  are known, then by estimation of the signal switching frequency f, we can use Equation 2.8 to approximately calculate the average power consumption of CMOS circuits.

#### 2.3 METHODOLOGIES OF ESTIMATION OF POWER CONSUMPTION

#### 2.3.1 Brief Overview

The total power dissipation of a CMOS circuit is the sum of the three types of power consumption, i.e., dynamic power dissipation, short-circuit current power consumption and static power consumption. Because the dynamic power dissipation is by far the dominant component, almost all methods used to calculation power consumption in CMOS circuits are focused on estimation of dynamic power consumption. Considering that the power estimation is calculated at the gate level (as shown in dynamic power calculation in the previous section), the power consumption can be estimated by calculating the switching activity for each circuit node assuming the supply voltage and capacitance are specified.

In addition, power dissipation is strongly dependent on the characteristics of the applied input signals to the circuit. Each applied input propagates through the circuit causing the internal nodes to perform transitions according the functionality and the interconnection of the circuit gates. The same circuit under different input scenarios may have totally different switching activities of the internal nodes, which may result in different power dissipation. Thus the applied input must be taken into account.

Power consumption estimation means calculation of the average and/or worst case power consumption. Furthermore we assume that the time between two

successive input vectors is enough to allow the circuit to reach in a steady state. Based on these assumptions, we state the problem of power estimation at the gate level as follows:

Power Estimation Problem: "Given a gate netlist of a synchronous static CMOS circuit and provided with an associated input vector sequence, estimate the average power dissipation of the circuit by calculating the average switching activity of each circuit node."

Therefore, the problem of estimation of the average power consumption of a given CMOS circuit is transferred into a problem of calculating the switching activity of each node in the circuit.

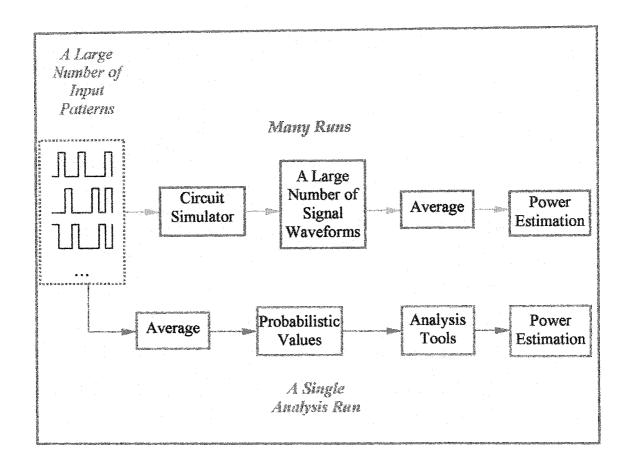

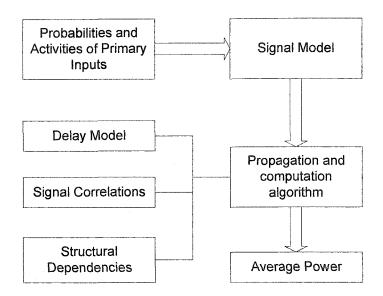

The power estimation methodologies at the logic gate level can be divided into two general classes: statistical-based and probability-based methodologies [5]. Figure 2-3 provides a general overview of these two methodologies [5]. The statistical-base methods (the upper flow) achieve power estimation by simulating the circuit with a large number of input vectors and averaging the large number of each internal signal waveform to get the average power consumption of the circuit. The probabilistic-based methods (the lower flow in Figure 2-3) first average the large number of input patterns to get probabilistic properties of input signals, then some analysis tools and/or techniques are used to predict the power consumption of the circuit.

Figure 2-3. Two methodologies used to estimate the power consumption in CMOS circuits.

#### 2.3.2 STATISTICAL-BASED POWER ESTIMATION

Because the simulation result is highly dependent on the primary input vectors, the statistical-based power estimation approach needs to use a large number of input vectors to simulate the circuit in order to achieve an accurate estimate of the circuit's behavior. This often makes this approach impractical for large circuits and long input sequences. Several methods have been developed to overcome this drawback; the Monte-Carlo, the Advanced Sampling and the Vector Compaction methods are the most representative methods [12]. Only the

Monte-Carlo approach will be described in this chapter, which is the most commonly used technique in statistical-based power estimation.

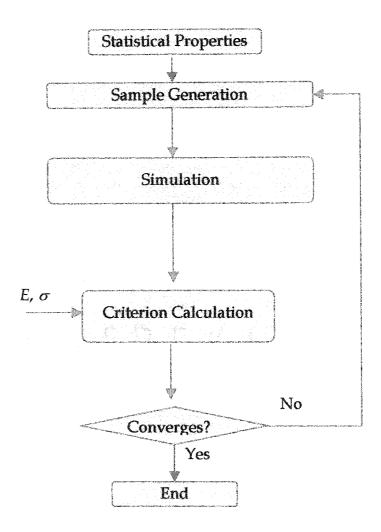

The block diagram in Figure 2-4 gives an overall view of this technique. The basic idea of Monte Carlo statistical technique is as follows [1]:

Figure 2-4. The block diagram of the Monte-Carlo method.

1. Input patterns are generated based on given input sequence statistical properties;

- 2. The number of transitions at each node is counted during a given period of duration, the power value (activity value) at the end of each simulation run is noted;

- 3. Decide whether to stop the process or to do another run. The decision is made based on the mean and standard deviation of the power values observed at the end of a number of successive iterations;

- 4. This process is repeated until it converges to the true result.

The main issue of this method is when to stop the simulation, which means a stopping criterion needs to be found. If the input patterns are independently generated as shown in step 1 in Monte-Carlo method, a large number of independent samples, represented as n independent samples, will be obtained by this measurement and the average will approach the desired average power for large n. In order to stop the simulation, the value of n needs to be found such that the average power is close enough to the true power, and this number of n is called the stopping criterion. This can be done by follows:

When we use a sample mean  $\overline{a}$  to estimate the mean a of a population, there always exists an error and for large n,  $\frac{\overline{a}-a}{\sigma/\sqrt{n}}$  is a value of a random variable having approximately the standard normal distribution, where  $\sigma$  is sample's standard deviation. We can assert with a probability of  $1-\alpha$  that

$$-z_{\alpha/2} < \frac{\overline{a} - a}{\sigma/\sqrt{n}} < z_{\alpha/2} \text{ or } \frac{|\overline{a} - a|}{\sigma/\sqrt{n}} < z_{\alpha/2}$$

(2.9)

where  $z_{\alpha/2}$  is such that the normal distribution curve area to its right equals  $\alpha/2$ . Using  $E=|\overline{a}-a|$ , we have

$$E < z_{\alpha/2} \frac{\sigma}{\sqrt{n}} . {(2.10)}$$

Equation 2.10 shows that if we estimate mean value by means of a random sample of size n, we can assert with a probability of  $1-\alpha$  that the error, E, is less than  $Z_{\alpha/2} \frac{\sigma}{\sqrt{n}}$ , at least for large n.

Solving for n in 2.10, we have

$$n > \frac{z_{\alpha/2}^2 \sigma^2}{E^2} \,. \tag{2.11}$$

So by given error E, standard deviation  $\sigma$ , and probability  $\alpha$ , we can use Equation 2.11 to decide how many samples need to be generated in Monte-Carlo statistic simulation<sup>2</sup>.

#### 2.3.3 PROBABILISTIC-BASED POWER ESTIMATION

Compared to the statistical-based approaches, probabilistic-based approaches estimate the switching activities in one run, which may result in much less computation time. Figure 2-5 is a block diagram that shows how probabilistic-based approaches compute the switching activities in CMOS circuits.

<sup>&</sup>lt;sup>2</sup> For detailed information of Monte-Carlo approaches, refer to [1].

Figure 2-5. The typical diagram flow of probabilistic-based power estimation approaches.

According to the type of a circuit, probabilistic-based approach can be categorized into methods for combinational and sequential circuits. For combinational circuits, it can be further classified into zero-delay and non-zero-delay model. The detailed analysis of probabilistic-based approaches and their associated algorithms are provided in Chapter 3.

#### 2.4 SUMMARY

There are three sources of power consumption in CMOS circuits: dynamic power dissipation, short-circuit power dissipation and static power dissipation. In these three power consumption components, dynamic power dissipation due to switching signal activities is dominant. Therefore, the problem of estimation of the average power consumption of a given CMOS circuit is transferred into a problem of calculating the switching activity of each node in the circuit.

Two general classes, the statistical-based and the probabilistic-based methodologies, exist in the power estimation methodologies at the logic gate level. The statistical-based approach, often represented by the Monte-Carlo approach, can provide accurate results, but generally, longer simulation time compared to probabilistic-based approaches.

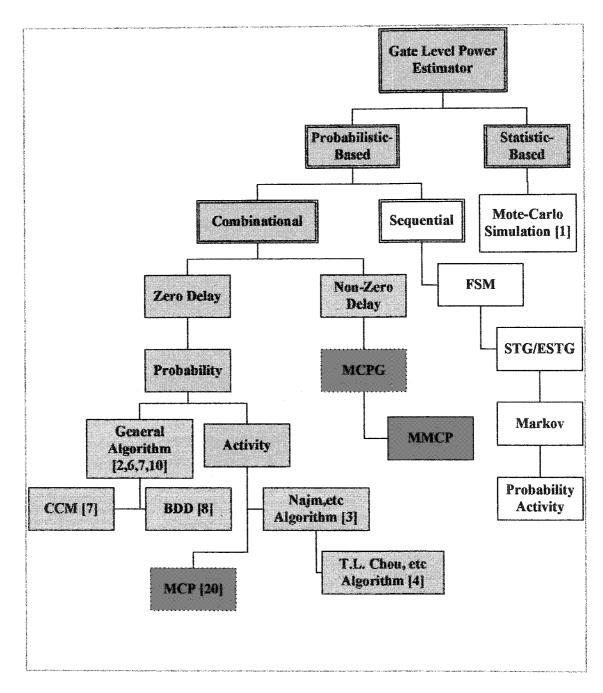

A taxonomy of techniques used to estimate switching activities in CMOS circuits is shown in Figure 2-6. All colored blocks will be analyzed in this dissertation. Approaches represented by pink colored blocks represent our research contributions, which provide a solution with comparable accuracy to statistic-based simulation, but having probabilistic-based time complexity, will be introduced in followed chapters.

Figure 2-6. Summary of most techniques used to estimate switching activities in CMOS circuits.

### CHAPTER 3

### PROBABILISTIC-BASED POWER ESTIMATION

### 3.1 Introduction

Probabilistic-based approaches have the potential advantage of performing the switching activity computation in less time than competing statistical-based approaches. Therefore, more efficient, accurate and more practical algorithms have become a major concern in power estimation research. In this chapter, we first introduce a general signal model. Then based on this signal model, several probabilistic-based algorithms used to calculate signal probabilities will be reviewed, followed by algorithms for calculating signal activities. Finally, the detailed analysis of these algorithms including complexity and accuracy will be discussed.

## 3.2 Modeling of Signals

Signals in a combinational logic circuit can be treated in a probabilistic sense [1], i.e., for signal x, the probability that x has logic value "1" is defined by P(x) = P(x = 1). Let x(t),  $t \in (-\infty, +\infty)$ , be a stochastic process that takes the values of logical "0" or logical "1", transitioning from one to the other at random times.

Generally, a stochastic process is said to be strict-sense stationary (SSS) if its statistical properties are invariable to a shift of time origin. Based on the assumptions of a SSS 0-1 mean-ergodic process x(t), the following definitions are derived from [3].

Definition 3.1 (Signal Probability) The probability of a logic signal x(t) is the average fraction of time that the signal is high and is given by

$$P(x) = \lim_{T \to \infty} \frac{1}{T} \int_{\frac{-T}{2}}^{\frac{+T}{2}} x(t)dt$$

Definition 3.2 (Signal Activity): The signal activity of a logic signal x(t) is the average number of transitions, i.e., n(T), in a time interval T and is given by

$$\alpha(x) = \lim_{T \to \infty} \frac{n(T)}{T}$$

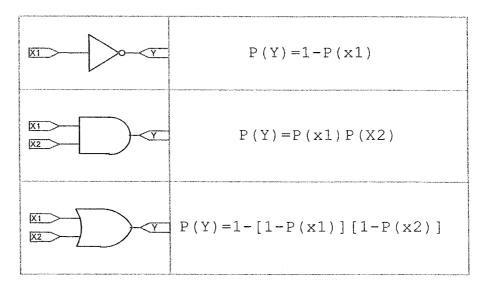

The analytical expressions of signal probability for some basic logic gates are defined in [2] and results are stated in Table 3-1.

Table 3-1. The output probability expression of some basic logic gates.

Clearly the input signals in Table 3-1 are assumed to be independent. But in general, signals might be correlated and can be separated into three types:

- Temporally correlated: a signal's value depends on the values that the signal has taken in the past

- Spatially correlated: a signal's value depends on the values of other signals

- Spatiotemporal correlated: a signal's value depends both on its own and other signal's value

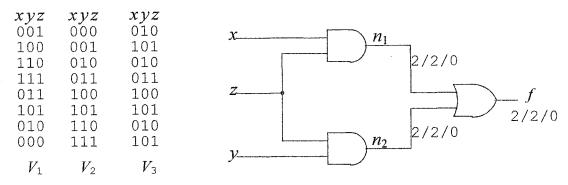

The impact of the above three kind of correlations is critical in the probabilities and switching activities calculation. Figure 3-1 shows the impact on the results with different input vectors.

As shown in Figure 3-1 with zero delay assumption, three different input vector sequences,  $V_1$ ,  $V_2$  and  $V_3$  are applied to the three primary inputs x, y and z. The input vector of sequence  $V_1$  is generated by a random number generator, which means that the three primary inputs x, y and z are mutually independent in  $V_1$ . The signals of sequence  $V_2$  is formed in such a way that the spatiotemporal correlations in input signals x, y and z are strong. In contrast to sequence  $V_2$ , the signals of sequence  $V_3$  has a weak spatiotemporal correlations in inputs x, y and z. The number of transitions of each node corresponding to different input vector sequences is also listed in Figure 3-1. It illustrates that the number of transitions is affected by the correlations of the primary input signals.

# of transitions for  $V_1/V_2/V_3$

Figure 3-1. The impact on the number of transitions with different input vectors with different correlations derived from [13].

Besides correlations among the primary inputs, the structure of the circuit may cause additional dependency between signals, which is introduced due to reconvergent fanouts. Even if the primary inputs x, y and z are mutually independent in Figure 3-1, signal z fans out into two signals, this kind of correlation will also impact the resulting calculation. The detailed effect of this correlation and methods dealing with this kind of correlation in switching activity calculation will be described later in this chapter.

# 3.3 SIGNAL PROBABILITY CALCULATION

Signal probability calculation is used for accurately estimating signal activity, which is necessary for power consumption estimation. Thus it is essential to estimate signal probability correctly for further use in signal activity calculation.

## 3.3.1 EARLY ALGORITHM

In [2], the concept of using probabilistic signal modeling for analysis of combinational circuits was first introduced. In this work, each signal is modeled with a single probabilistic parameter, P(x), defining the probability of a signal having a logical value of one. The purpose is to calculate the probability parameter for all signals, given the probability parameters of the circuit's primary inputs. The motivation for this work originated from the area of pseudorandom testing, in which fault coverage and identification is achieved without resorting to exhaustive testing. Instead, by subjecting a circuit to a large number of randomly generated input signal vectors, one can deduce faults in the circuit by measuring the fraction of time that any given signal has logic value one. If any of the measured signal probabilities do not match calculated signal probabilities, then the possibility of a fault is present.

As mentioned above, signals in a combinational logic circuit are treated in a probabilistic sense in [2]. For signal x, the probability that x has logic value "1" is defined by P(x) = P(x = 1). Two algorithms for calculating signal probabilities are introduced in [2] with an upper bound complexity of order  $2^n$  where n is the number of circuit inputs. The second with less complexity is given below:

**Early Algorithm:** Compute signal probability of each signal in a circuit.

*Input*: Signal probabilities of all primary inputs to the circuit.

Output: Signal probabilities of all signals in the circuit.

1. For each input and gate output in the circuit, assign a unique variable;

- 2. Starting at the inputs and proceeding to the outputs, write the expression for the output of each gate as a function of its input expressions (using expressions in Table 3-1);

- 3. Suppress all exponents in a given expression to obtain the probability expression for that signal.

In this algorithm, the primary inputs are assumed to be mutually independent, and a Boolean function expression associated with each signal can be derived in terms of the primary inputs. However, the internal nodes of a circuit may be correlated due to reconvergent fan-out which can produce expressions having exponents greater than 1. Hence, Step 3 is used to handle signal correlations by suppressing exponents of variables in the Boolean function expressions.

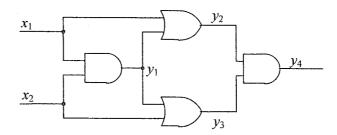

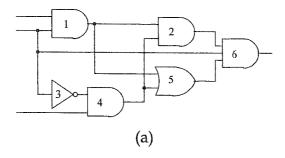

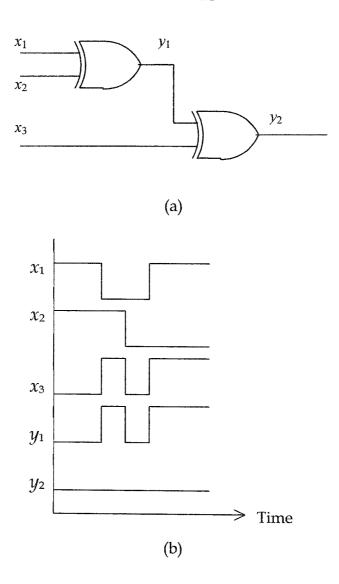

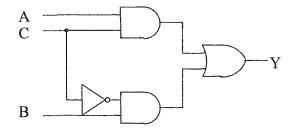

To illustrate how to use this algorithm to calculate signal probabilities of a circuit, consider a simple circuit as shown in Figure 3-2.

Figure 3-2. An example combinational circuit used to illustrate signal probability calculations (derived from [7]).

By using this Early Algorithm, the internal signal  $y_1$  and signal  $y_2$  can be expressed as

$$y_1 = x_1 x_2$$

$$y_2 = x_1 + y_1 - x_1 y_1 = x_1 + x_1 x_2 - x_1^2 x_2$$

Suppressing exponent of  $x_1$ , we have

$$y_2 = x_1 + x_1 x_2 - x_1 x_2 = x_1$$

.

Similarly,

$$y_3 = x_2 + y_1 - x_2 y_1 = x_2 + x_1 x_2 - x_1 x_2^2 = x_2 + x_1 x_2 - x_1 x_2 = x_2$$

$$y_4 = y_1 y_2 = x_1 x_2$$

## 3.3.2 GENERAL ALGORITHM

The Early Algorithm can solve the probabilities of all nodes in the circuit exactly when all primary inputs are assumed mutually independent. It results in exponential time complexity, though, due to simplification of Boolean functions associated with each node into Boolean functions expressed by primary inputs only. To reduce the time complexity, a computationally efficient algorithm for calculating signal probabilities is introduced in [6], named "General Algorithm," which operates by propagating probability values through the gates of circuit, thereby drastically reducing the size of the Boolean functions that must be evaluated. Specifically, the probability of the output of a gate is expressed in terms of the probability values for the inputs to that gate (instead of the primary inputs of the entire circuit, as required by the approach in [2]). This algorithm is an extension of the above Early Algorithm and is given below:

General Algorithm: Compute signal probability of each signal in a circuit.

*Input*: Signal probabilities of all primary inputs to the circuit.

Output: Signal probabilities of all nodes in the circuit.

- 1. For each input and gate output in the circuit, assign a unique variable;

- 2. Starting at the inputs and proceeding to the outputs, calculate the value of the output of each gate using expressions of Table 3-1.

This algorithm is simple and fast – it has a linear complexity in the number of gates – but is not accurate for all classes of circuits.

To illustrate the inaccuracies of General Algorithm, assume in Figure 3-2 that the probabilities of primary inputs  $x_1$  and  $x_2$  are both 0.5. By applying General Algorithm, the computed probabilities of the circuit's signals can be calculated and the results are provided in Table 3-2.

Table 3-2. Comparison of actual signal probabilities and those calculated using General Algorithm for the circuit of Figure 3-2 with  $P(x_1) = P(x_2) = 1/2$ .

|                   | $P(y_1)$ | $P(y_2)$ | $P(y_3)$ | $P(y_4)$ |

|-------------------|----------|----------|----------|----------|

| Actual            | 1/4      | 1/2      | 1/2      | 1/4      |

| General Algorithm | 1/4      | 5/8      | 5/8      | 25/64    |

The problem with the accuracy of the General Algorithm arises in circuits in which re-convergent fan-out signals are present. Re-convergent fan-out introduces functional dependencies and statistical correlations among the signals; however, the General Algorithm assumes statistical independence among the inputs to each gate. For example, signals  $y_2$  and  $y_3$  in Figure 3-2 both depend on signal  $x_1$  due to re-convergent fan-out. Thus, applying the algorithm

to calculate  $P(y_4)$  under the assumption that signals  $y_2$  and  $y_3$  are independent results in an error in the value calculated for  $P(y_4)$ , as shown in Table 3-2. Similarly, the values calculated for  $P(y_2)$  and  $P(y_3)$  are also in error.

# 3.3.3 CCM ALGORITHM

A method for accounting for signal probability correlations was developed in [6] named the correlation coefficient method (CCM). By defining the correlation coefficient of two events A and B as  $C_{A,B}$  where

$$C_{AB} = \frac{P(AB)}{P(A)P(B)} = \frac{P(A/B)}{P(A)} = \frac{P(B/A)}{P(B)}$$

,

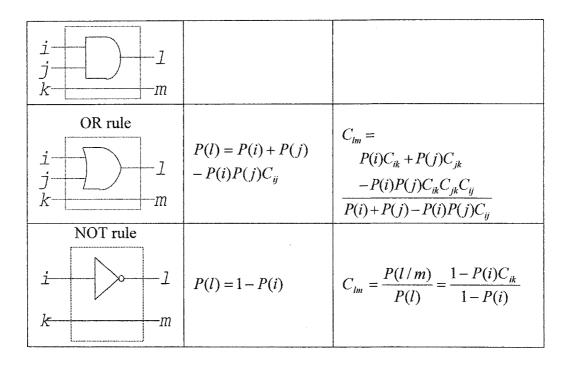

probabilities of output signals can be calculated by using these main rules as shown in Table 3-3 [6].

Table 3-3. Set of basic rules used to calculate the probability of output signals and correlation coefficients by given input signals' probability and correlation coefficients.

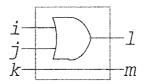

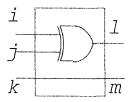

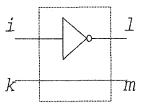

| Rules                                               | Probability             | Probability Correlation<br>Factors |  |

|-----------------------------------------------------|-------------------------|------------------------------------|--|

| Independent rule                                    |                         |                                    |  |

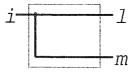

| $\begin{array}{c c} i & & 1 \\ j & & m \end{array}$ | Same as input           | $C_{lm} = C_{ij}$                  |  |

| Fan-out rule                                        |                         |                                    |  |

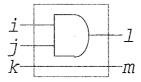

| i $m$                                               | Same as input           | $C_{lm} = \frac{1}{P(i)}$          |  |

| AND rule                                            | $P(l) = P(i)P(j)C_{ij}$ | $C_{lm} = C_{ik}C_{jk}$            |  |

By using this approach, the probability of the output of a two-input gate can be more accurately calculated, given the probabilities of the two inputs and an associated correlation factor associated with the two signals. In this algorithm, the correlation factor can also be calculated analytically by means of a set of basic propagation rules (as shown in Table 3-3). CCM algorithm is given as follows:

<u>CCM algorithm:</u> Compute signal probability of each signal in a circuit.<u>Input</u>: Probabilities and correlation coefficients of primary input signals.<u>Output</u>: Probabilities and correlation coefficients of all signals.

- 1. Compile the network transforming possible multiple inputs gates into a cascade of two input ones organizing the circuit into levels;

- 2. Initialize the correlation coefficients and the probabilities at primary inputs. Generally the probabilities of primary inputs are assumed to be

- 0.5 and are considered to be independent, thus the values for all correlation coefficients for the primary inputs are 1;

- 3. Calculate the node probabilities and signal correlation coefficients at each level by successively applying the rules, check that the calculated coefficients are within the bounds. If not, assign them the nearest bound values.

By applying this CCM algorithm to the circuit shown in Figure 3-2, the values of  $P(y_1)$ ,  $P(y_2)$ ,  $P(y_3)$ , and  $P(y_4)$  are properly calculated and correspond to the actual values shown in Table 3-2. The time complexity of the CCM algorithm is  $O(N^2)$  for a circuit with N gates.<sup>3</sup>

## 3.3.4 BDD ALGORITHM

Signal probabilities of any arbitrary Boolean expression can also be calculated using Binary Decision Diagrams (BDDs) [16, 17]. In general, each node of a circuit can be represented by a logic function and the functionality of a logic function can be graphically represented by Binary decision diagrams. Let us consider a Boolean function  $f(x_1, x_2,...,x_n)$ , where variables  $x_1, x_2,...,x_n$  correspond to primary inputs. Function f can be represented using Shannon's expression [17] as follows:

<sup>&</sup>lt;sup>3</sup> Sharper time complexity results can be obtained; for example, it can be shown that a circuit with  $\sqrt{N}$  levels has a complexity of  $O(N^{3/2})$

$$f = x_i \cdot f(x_1, ..., x_{i-1}, 1, x_{i+1}, ..., x_n) + \overline{x_i} \cdot f(x_1, ..., x_{i-1}, 0, x_{i+1}, ..., x_n).$$

(3.1)

The cofactors of Boolean function f with respect to  $x_i$  and  $\overline{x_i}$  respectively are defined as

$$f_{x_{i}} = f(x_{1},...,x_{i-1},1,x_{i+1},...,x_{n})$$

$$f_{\overline{x_{i}}} = f(x_{1},...,x_{i-1},0,x_{i+1},...,x_{n}).$$

(3.2)

Thus functions  $f_{x_i}$  and  $f_{\overline{x_i}}$  are obtained by replacing variable  $x_i$  with logic 1 and logic 0, respectively. Each node of the BDD represents an input  $x_i$  and the edges coming out of node  $x_i$  represent the value of input  $x_i$  either logic 1 or logic 0. By traversing the BDD from its root, one can determine the value of the function f by sequentially examining the values of the inputs.

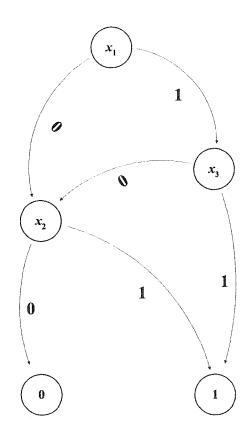

As an example to illustrate the BDD representation, consider the Boolean function  $f = x_1 \cdot x_2 + x_3$ , which can be represented by the BDD shown in Figure 3-3. The leaf nodes represent the value of function f. For example, if one traverses the path of the graph by edges  $x_1 = 1$ ,  $x_2 = 0$ , and  $x_3 = 1$ , then the function equals logic "1". The tree rooted to the left of  $x_1$  represents function  $f_{x_1}$ , while the tree rooted to the right of  $x_1$  represents function  $f_{x_1}$ . We can see that the ordering of the nodes of the BDD has direct implications on the complexity of BDD.

Figure 3-3. A BDD representation of Boolean function  $f = x_1 \cdot x_2 + x_3$ .

In general, let  $y = f(x_1, x_2, ..., x_n)$  be Boolean function. If the primary inputs  $x_1, x_2, ..., x_n$  are mutually independent, then the signal probability of y can be obtained in linear time (in the size of its BDD representation) as follows (using Equations 3.1 and 3.2):

$$p(y) = p(x_1 \cdot f_{x_1} + \overline{x_1} \cdot f_{\overline{x_1}})$$

$$= p(x_1 \cdot f_{x_1}) + p(\overline{x_1} \cdot f_{\overline{x_1}})$$

$$= p(x_1) \cdot p(f_{x_1}) + p(\overline{x_1}) \cdot p(f_{\overline{x_1}}).$$

(3.3)

The probability of y is stored in node  $x_1$  as shown in Figure 3-3, and the probability of the cofactors are stored in node  $x_2$  and  $x_3$ , respectively. The probability of the cofactors can now be represented in terms of its cofactors and

so on. A depth-first traversal of BDD, with a post order evaluation of p(.) at every node is required for evaluation of p(y). This can be implemented using the "scan" function of the BDD package [5].

Another algorithm is proposed in [7] called the Weighted Averaging Algorithm (WAA), which generally achieves better accuracy than does the General Algorithm and has a comparable time complexity. However, the WAA still does not always produce correct values.

# 3.4 SIGNAL ACTIVITY CALCULATION

The average number of transitions per unit of time of a signal is defined as signal activity. The above-described approaches of [2], [6], and [7] are concerned with determining the probabilities of signal values, not the probabilities of signal transitions, i.e., activities, which are necessary for estimating power consumption. In general, there are two approaches for activity analysis, which are called the relative Boolean difference approach and the generalized Boolean difference approach. In this subsection, we will focus on the analysis of these two approaches.

# 3.4.1 RELATIVE BOOLEAN DIFFERENCE APPROACH

An early approach for estimating signal activities was developed in [3], in which signals of a circuit are modeled to be mutually independent strict-sense-

stationary (SSS) mean-ergodic 0-1 processes. Under these assumptions, the activity of a signal y from a circuit with n-primary inputs can be expressed as

$$\alpha(y) = \sum_{i=1}^{n} P\left(\frac{\partial y}{\partial x_i}\right) \alpha(x_i)$$

(3.4)

where  $\frac{\partial y}{\partial x_i}$  is the Boolean difference of function y with respect to  $x_i$  and is defined by

$$\frac{\partial y}{\partial x_{i}} = y \mid_{x_{i}=1} \oplus y \mid_{x_{i}=0} = y(x_{1}, \dots, x_{i-1}, 1, x_{i+1}, \dots, x_{n})$$

$$\oplus y(x_{1}, \dots, x_{i-1}, 0, x_{i+1}, \dots, x_{n}).$$

(3.5)

Intuitively, the Boolean difference  $\frac{\partial y}{\partial x_i}$  defines whether a transition of signal  $x_i$  will cause a transition in output signal y. Specifically, if the Boolean difference function evaluates to one, then a transition of signal  $x_i$  causes a transition in y; if the Boolean difference function evaluates to zero, then a transition of signal  $x_i$  does not cause a transition in y. So, the probability of the Boolean difference function,  $P\left(\frac{\partial y}{\partial x_i}\right)$ , defines the probability that a change in y will occur given that there is a change in  $x_i$ . As an example of how to evaluate Equation 3.4, consider a simple case of a three-input AND function in which  $y = x_1x_2x_3$ .

$$\alpha(y) = \sum_{i=1}^{3} P\left(\frac{\partial y}{\partial x_i}\right) \alpha(x_i)$$

(3.6)

$$\frac{\partial y}{\partial x_1} = y |_{x_1=1} \oplus y |_{x_1=0} = (1 \cdot x_2 \cdot x_3) \oplus (0 \cdot x_2 \cdot x_3) = x_2 x_3$$

and similarly

$$\frac{\partial y}{\partial x_2} = x_1 x_3$$

$$\frac{\partial y}{\partial x_3} = x_1 x_2$$

Thus,

$$\alpha(y) = P(x_2x_3)\alpha(x_1) + P(x_1x_3)\alpha(x_2) + P(x_1x_2)\alpha(x_3).$$

Because  $x_1$ ,  $x_2$ , and  $x_3$  are mutually independent, we can further simplify the probability terms as follows:

$$\alpha(y) = P(x_2)P(x_3)\alpha(x_1) + P(x_1)P(x_3)\alpha(x_2) + P(x_1)P(x_2)\alpha(x_3)$$

(3.7)

The above expression is readily evaluated using the values of  $P(x_i)$  and  $\alpha(x_i)$ , which are the known probabilities and activities of the primary input signals.

Although the calculation of the probability of the Boolean difference terms, i.e.,  $P\left(\frac{\partial y}{\partial x_i}\right)$ , for the above example was relatively straightforward, this calculation can be complicated for large and complex circuits. In [3], the calculation of these terms is accomplished by first representing the nodes of the circuit with a binary decision diagram (BDD) [3, 5]. In practice, the BDD approach often achieves linear or near linear time complexity; however, in the worst case the complexity can grow exponentially with the number of gates.

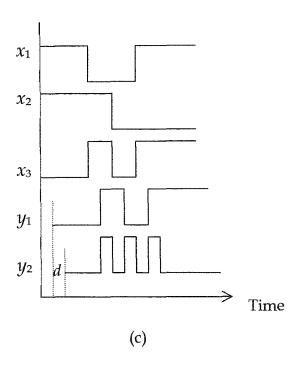

## 3.4.2 GENERALIZED BOOLEAN DIFFERENCE APPROACH

It is noted in [4] that Equation 3.4, i.e., the approach described in [3], fails to consider the effect of simultaneous switching of gate inputs. Figure 3-4 shows an example of how simultaneous switching of inputs to a logic gate affects the activity of the output node. As shown in the figure, if the two input signals always switch simultaneously, then the output signal of the XOR gate will have an activity of zero, even though the probability and activity terms in Equation 3.4 are nonzero [4]. This example is an extreme case, but is given to illustrate the importance of considering simultaneous switching.

Figure 3-4. An example to illustrate the effect of simultaneous switching (derived from [4]).

Each Boolean difference term associated with Equation 3.4 describes an inputswitching event in which exactly one of the inputs makes a transition. Thus, Equation 3.4 does not account for events involving simultaneous switching of two or more of the input signals. The concept of the generalized Boolean difference was introduced in [4] to account for simultaneous switching, and is denoted as follows:

$$\frac{\partial y^{k} \mid b_{i_{1}}, b_{i_{2}}, \dots, b_{i_{k}}}{\partial x_{i_{1}} \partial x_{i_{2}} \dots \partial x_{i_{k}}} = (y \mid x_{i_{1}} = b_{i_{1}}, x_{i_{2}} = b_{i_{2}}, \dots x_{i_{k}} = b_{i_{k}})$$

$$\oplus (y \mid x_{i_{1}} = \overline{b_{i_{1}}}, x_{i_{2}} = \overline{b_{i_{2}}}, \dots, x_{i_{k}} = \overline{b_{i_{k}}}),$$

(3.8)

where k is a positive integer,  $x_{i_j}$ , j=1,2,...,k, are distinct mutually independent primary inputs of y, and  $b_{i_j}$  are binary values of "0" or "1". Note that if the generalized Boolean difference evaluates to one, then the simultaneous transitions of signals  $(x_{i_1},x_{i_2},...,x_{i_k})$  from  $(b_{i_1},b_{i_2},...,b_{i_k})$  to  $(\overline{b_{i_1}},\overline{b_{i_2}},...,\overline{b_{i_k}})$  or from  $(\overline{b_{i_1}},\overline{b_{i_2}},...,\overline{b_{i_k}})$  to  $(b_{i_1},b_{i_2},...,b_{i_k})$  will cause a transition at y.

Theorem 3.1 [11]: Assume that the primary inputs are mutually independent, and the logical signals can be modeled as SSS mean ergodic 0-1 discrete-time stochastic processes with logic modules having zero-delays. Also assume that signals can only transition at the leading edge of the clock cycle. Then the activity of a Boolean expression y with three primary inputs  $x_1$ ,  $x_2$  and  $x_3$  (assumed mutually independent), i.e.,  $\alpha(y)$ , can be expressed as

$$a(y) = \sum_{i=1}^{3} Po(\frac{\partial y}{\partial x_{i}}) \left( a(x_{i}) \prod_{j \neq i, 1 \leq j \leq 3} [1 - a(x_{i})] \right)$$

$$+ \frac{1}{2} \left\{ \sum_{1 \leq i \leq j \leq 3} \left[ Po\left(\frac{\partial^{2} y|_{00}}{\partial x_{i} \partial x_{j}}\right) + Po\left(\frac{\partial^{2} y|_{01}}{\partial x_{i} \partial x_{j}}\right) \right] \times \left( a(x_{i}) a(x_{j}) \prod_{l \in \{1, 2, 3\} - \{i, j\}} [1 - a(x_{l})] \right\}$$

$$+ \frac{1}{4} \left\{ \left[ Po\left(\frac{\partial^{3} y|_{000}}{\partial x_{1} \partial x_{2} \partial x_{3}}\right) + Po\left(\frac{\partial^{3} y|_{001}}{\partial x_{1} \partial x_{2} \partial x_{3}}\right) + Po\left(\frac{\partial^{3} y|_{010}}{\partial x_{1} \partial x_{3}$$

where

$$Pc(\frac{\partial y}{\partial x_i}), Pc\left(\frac{\partial^2 y|_{00}}{\partial x_i \partial x_j}\right), ..., Pc\left(\frac{\partial^3 y|_{011}}{\partial x_1 \partial x_2 \partial x_3}\right)$$

are conditional probabilities under the condition that only the indicated primary inputs switch at the leading edge of the clock cycle and the rest do not.

Proof:

Because we assume that the module under consideration has zero delay and the primary inputs can switch only at the leading edge of the clock signal, the output signal will switch only at the leading edge of the clock signal. At any time t in which switching is possible, there will be only four kinds of events happening: none of the three inputs switching; one of the three inputs switching; two of the three inputs switching or all of the switching. The union of these four events is the sample space. To simplify the representation, assume  $x_i$  is the primary input, i = 1, 2, 3. Let event  $B_0$  be the event with none of the three inputs switch. Let  $B_i$  be the event that only  $x_i$  switches. Let  $B_{i,j}$ , i = 1, 2, 3, j = 1, 2, 3, and  $1 \le i < j \le 3$ , be the events that only signal i and signal j switch at time t but the other signal does not switch. Finally let  $B_{1,2,3}$  be the event that all three input signals switch at the same time. Based on the above definition, all the events are mutually exclusive; therefore, they form a partition of the sample space. Because signal  $x_1, x_2$  and  $x_3$  are mutually independent,

$$P(B_0) = [1 - \alpha(x_1)][1 - \alpha(x_2)][1 - \alpha(x_3)]$$

Similarly,

$$P(B_1) = \alpha(x_1)[1 - \alpha(x_2)][1 - \alpha(x_3)]$$

$$P(B_2) = \alpha(x_2)[1 - \alpha(x_1)][1 - \alpha(x_3)]$$

$$P(B_3) = \alpha(x_3)[1 - \alpha(x_1)][1 - \alpha(x_2)]$$

$$P(B_{i,j}) = \alpha(x_i)\alpha(x_j)[1 - \alpha(x_k)], i = 1,2,3; j = 1,2,3; k = 1,2,3; i \neq j \neq k$$

and

$$P(B_{1,2,3}) = \alpha(x_1)\alpha(x_2)\alpha(x_3)$$

Because the probability of the union of a set of disjoint events is the sum of the probabilities of the individual events, and assuming event A represents the event that y is switching at time t, this leads to

$$P(A) = P(A/B_0)P(B_0) + \sum_{i=1}^{3} P(A/B_i)P(B_i) + \sum_{1 \le i < i \le 3} P(A/B_{i,j})P(B_{i,j}) + P(A/B_{1,2,3})P(B_{1,2,3})$$

(3.10)

We know that if none of the primary inputs switches at time t, the output signal y will not switch at time t, then  $P(A/B_0) = 0$ . If there is only one signal switching at time t, i.e., signal  $x_i$  is switching, then the conditional probability can be expressed as

$$P(A/B_i) = P_c(\frac{\partial y}{\partial x_i}) \tag{3.11}$$

When there are two signals switching at time t, i.e., signals  $x_i$  and  $x_j$  switch simultaneously, there are four possible cases: signals  $x_i$  and  $x_j$  both transition from low to high; both switch from high to low;  $x_i$  switches from low to high and  $x_j$  switches from high to low; or signal  $x_i$  switch from high to low and  $x_j$  switches from low to high. Because a rising transition at any node is always followed by a

falling transition and vice versa, the conditional probability  $P(A/B_{i,j})$  can be expressed as [4]

$$P(A/B_{i,j}) = \frac{1}{2} \left[ Pc \left( \frac{\partial^2 y|_{00}}{\partial x_i \partial x_j} \right) + Pc \left( \frac{\partial^2 y|_{01}}{\partial x_i \partial x_j} \right) \right]$$

(3.12)

Similarly,

$$P(A/B_{1,2,3}) = \frac{1}{4} \begin{bmatrix} Pc\left(\frac{\partial^{3}y|_{000}}{\partial x_{1}\partial x_{2}\partial x_{3}}\right) + Pc\left(\frac{\partial^{3}y|_{011}}{\partial x_{1}\partial x_{2}\partial x_{3}}\right) \\ + Pc\left(\frac{\partial^{3}y|_{010}}{\partial x_{1}\partial x_{2}\partial x_{3}}\right) + Pc\left(\frac{\partial^{3}y|_{011}}{\partial x_{1}\partial x_{2}\partial x_{3}}\right) \end{bmatrix}.$$

(3.13)

Q.E.D.

The conditional probability Pc(x) can be calculated as follows: Assume signal x only switches at the leading edge of the clock signal, and t is some leading edge of the clock and T is the clock period. From the definition of generalized Boolean difference as shown in Equation 3.8, it is noted that x is actually an expression of primary input signals except those signals simultaneously switching at time t. To simplify the expression, we use x(t-T)x(t)=1 and  $\overline{x}(t-T)\overline{x}(t)=1$  to represent that signal x does not switch at time t, i.e., from "1" to "1" and from "0" to "0" respectively. Similarly  $x(t-T)\overline{x}(t)=1$  and  $\overline{x}(t-T)x(t)=1$  represent that signal x does switch from "1" to "0" and from "0" to "1" respectively. Also assume that the probability and activity of signal x are P(x) and  $\alpha(x)$  respectively. Then we have

$$P(x \text{ is not switching at time } t) = P(x(t-T)x(t) + \overline{x(t-T)x(t)}) = 1 - \alpha(x)$$

$$P(x \text{ is switching at time } t) = P(x(t-T)x(t) + x(t-T)x(t)) = \alpha(x)$$

Because we assume the signal is a SSS 0-1 process and mean-ergodic, the following equations hold:

$$P(x(t-T)x(t) + \overline{x}(t-T)\overline{x}(t)) = P(x(t-T)x(t)) + P(\overline{x}(t-T)\overline{x}(t))$$

$$P(x(t-T)\overline{x}(t) + \overline{x}(t-T)x(t)) = P(x(t-T)\overline{x}(t)) + P(\overline{x}(t-T)x(t))$$

$$P(x(t-T) = P(x(t)) = P(x)$$

$$P(\overline{x}(t-T)) = P(\overline{x}(t)) = 1 - P(x)$$

Since every transition from "1" to "0" will always be followed by a transition from "0" to "1" and verse visa, then we have

$$P(x(t-T)x(t)) = P(x(t-T)x(t)) = \frac{1}{2}\alpha(x)$$

(3.14)

In fact, x(t) = x(t)x(t-T) + x(t)x(t-T), then

$$P(x(t)) = P(x(t)x(t-T) + x(t)x(t-T))$$

$$= P(x(t)x(t-T)) + P(x(t)x(t-T)) = P(x)$$

(3.15)

Solving Equation 3.15 using Equation 3.14, results in

$$P(x(t-T)x(t)) = P(x) - \frac{1}{2}\alpha(x)$$

So the conditional probability of signal x being "1" while it does not switch at time t can be expressed as:

$$Pc(x) = P(x(t) = 1 | x \text{ does not switching at time } t)$$

Using the definition of conditional probability [8] that for two events A and B, the conditional probability P(A/B) is defined as

$$P(A/B) = \frac{P(AB)}{P(B)}$$

Then

$$Pc(x) = \frac{P(x(t) = 1 \& x \text{ does not switch at time } t)}{P(x \text{ does not switch at time } t)}$$

$$= \frac{P(x(t)[x(t-T)x(t) + \overline{x}(x-T)\overline{x}(t)] = 1)}{P([x(t-T)x(t) + \overline{x}(x-T)\overline{x}(t)] = 1)}$$

$$= \frac{P(x(t-T)x(t))}{1 - \alpha(x)} = \frac{P(x) - \frac{1}{2}\alpha(x)}{1 - \alpha(x)}$$

So the conditional probability of signal x being "1" under the condition that x does not switch at time t is given by

$$Pc(x) = \frac{P(x) - \frac{1}{2}\alpha(x)}{1 - \alpha(x)}$$

(3.16)

Equation 3-9 can be generalized to n-inputs and the proof is similar to that of the 3-input. Assume y is a Boolean expression and  $x_i$ , i = 1,2,...,n, are mutually independent primary inputs of y, the activity of y can be expressed as [11]

$$\alpha(y) = \sum_{i=1}^{n} Pc\left(\frac{\partial y}{\partial x_{i}}\right) \left(\alpha\left(x_{i}\right) \prod_{\substack{j \neq i \\ 1 \leq j \leq n}} \left[1 - \alpha\left(x_{i}\right)\right]\right) + \frac{1}{2} \left\{\sum \left[Pc\left(\frac{\partial^{2} y|_{00}}{\partial x_{i} \partial x_{j}}\right) + Pc\left(\frac{\partial^{2} y|_{01}}{\partial x_{i} \partial x_{j}}\right)\right] \left(\alpha\left(x_{i}\right) \alpha\left(x_{j}\right) \prod_{l \in \{1, 2, \dots, n\} - \{i, j\}} \left[1 - \alpha\left(x_{l}\right)\right]\right)\right\} + \dots$$

$$+ \frac{1}{2^{n-1}} \left[Pc\left(\frac{\partial^{n} y|_{00 \dots 0}}{\partial x_{1} \partial x_{2} \dots \partial x_{n}}\right) + Pc\left(\frac{\partial^{n} y|_{00 \dots 1}}{\partial x_{1} \partial x_{2} \dots \partial x_{n}}\right)\right] \left(\prod_{l=1}^{n} \alpha\left(x_{l}\right)\right).$$

$$+ \dots + Pc\left(\frac{\partial^{n} y|_{01 \dots 1}}{\partial x_{1} \partial x_{2} \dots \partial x_{n}}\right)$$

where  $Pc\left(\frac{\partial y}{\partial x_i}\right)$ ,  $Pc\left(\frac{\partial^2 y|_{00}}{\partial x_i \partial x_j}\right)$ , ...,  $Pc\left(\frac{\partial^n y|_{01...1}}{\partial x_1 \partial x_2 \cdots \partial x_n}\right)$  are conditional probabilities of

the generalized Boolean differences under the condition that only the indicated inputs simultaneously switch, and the rest do not.

We can see that the result obtained by considering the simultaneous switching activity is different with the result obtained by ignoring the simultaneous switching activity. Compare the results as shown in Equation 3.6, it is apparent that if the effect of simultaneous switching is neglected,  $Pc(\partial y/\partial x_i) = P(\partial y/\partial x_i)$ , and  $\{\alpha(x_i)\prod_{j\neq i,1\leq j\leq n}[1-\alpha(x_j)]\}$  is equal to  $\alpha(x_i)$  and the above expression becomes identical to Equation 3.6.

Let's use an example to show how to apply Equation 3.9. Consider a simple logic expression as  $y = x_1x_2\overline{x_3}$ , with  $x_i$ , i = 1,2,3 input signals with probability and activity  $p_i$  and  $\alpha_i$ , respectively. Then we have

$$\frac{\partial y}{\partial x_1} = (x_2 \overline{x_3}) \oplus 0 = x_2 \overline{x_3}$$

$$\frac{\partial y}{\partial x_2} = (x_1 \overline{x_3}) \oplus 0 = x_1 \overline{x_3}$$

$$\frac{\partial y}{\partial x_3} = 0 \oplus x_1 x_2 = x_1 x_2$$

$$P_c(\frac{\partial y}{\partial x_1}) = Pc(x_2\overline{x_3}) = \frac{P(x_2\overline{x_3}) - \frac{1}{2}\alpha(x_2\overline{x_3})}{1 - \alpha(x_2\overline{x_3})}$$

(3.18)

$$P_c(\frac{\partial y}{\partial x_2}) = Pc(x_1 \overline{x_3}) = \frac{P(x_1 \overline{x_3}) - \frac{1}{2}\alpha(x_1 \overline{x_3})}{1 - \alpha(x_1 \overline{x_3})}$$

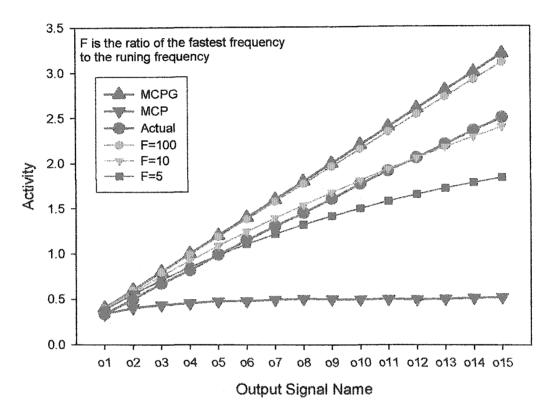

(3.19)