# DESIGN OF 3.3V DIGITAL STANDARD CELLS LIBRARIES FOR LEON3

#### By

#### **REHAN AHMED**

Bachelor of Science in Physics

Calcutta University

West Bengal, India

2002

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE December, 2009

# DESIGN OF 3.3V DIGITAL STANDARD CELLS LIBRARIES FOR LEON3

| Thesis Approved:             |

|------------------------------|

|                              |

| Dr. Chris Hutchens           |

| Thesis Adviser               |

| Dr. Sohum Sohoni             |

|                              |

| Dr. James E. Stine, Jr       |

|                              |

| Dr. A. Gordon Emslie         |

| Dean of the Graduate College |

#### **ACKNOWLEDGMENTS**

I would like to take this opportunity to thank my committee chair and advisor Dr. Chris Hutchens and express my sincere gratitude for his valuable advice, patience and understanding. I wish to express my sincere thanks to Dr. James E. Stine, Jr and Dr. Sohum Sohoni for serving on my graduate committee.

I feel proud to have served as a research assistant in the Mixed Signal VLSI Design Lab at Oklahoma State University. It has been a wonderful and exciting learning opportunity to work at MSVLSI Lab. I would also like to thank Dr. Chia-Ming Liu, Mr. Vijayraghavan Madhuravasal, Dr. Hooi Miin Soo, Mr. Srinivasan Venkataraman, Mr. Zhe Yuan, Ms Swati Shah and Mr. Yohannes Mitike for all their help and suggestions along the course of this work.

# TABLE OF CONTENTS

| Chapter          |                                               | Page          |

|------------------|-----------------------------------------------|---------------|

| 1.1 Standard Co  | NTRODUCTIONell Based ASIC Design Flownization | 1             |

| CHAPTER 2        | SILICON ON INSULATOR WAFFER T                 | TECHNOLOGY5   |

| 2.1 Introduction | 1                                             | 5             |

|                  | lk Device Structure                           |               |

|                  | n in Leakage                                  |               |

|                  | n in Parasitic                                |               |

| 2.2.3 Higher Do  | evice density                                 | 8             |

|                  | -up Problem                                   |               |

|                  | For Lower Threshold Voltage                   |               |

|                  | Body Effect                                   |               |

|                  | rce/Drain resistance                          |               |

|                  |                                               |               |

| CHAPTER 3 S      | TANDARD CELL LIBRARY CHARA                    | CTERIZATION13 |

| 3.1 Introduction | 1                                             | 13            |

|                  | y Design Flow                                 |               |

|                  | erview of Cell Library                        |               |

|                  | Description                                   |               |

|                  | Description                                   |               |

|                  | Description                                   |               |

|                  | cedure                                        |               |

| 3.5 Characteriz  | ation of Cell Library                         | 22            |

| 3.5.1 Cell Libra | ary Characterizer-Signalstorm                 | 22            |

|                  | le                                            |               |

|                  | Characterization                              |               |

|                  | s of Cell Library                             |               |

| Chapter     |                                       | Page |

|-------------|---------------------------------------|------|

| CHAPTER 4   | ABSTRACTION                           | 32   |

| 4.1 Introdu | ection                                | 32   |

|             | ning of Abstract Generator            |      |

|             | ement to Start Abstract Generation    |      |

| -           | Abstract                              |      |

| 4.5 Genera  | te Abstract                           | 38   |

| 4.5.1 Runn  | ing Form                              | 39   |

| 4.6 Inspect | ing The Result                        | 44   |

|             | Editor                                |      |

| CHAPTER 5   | ANTENNA ERROR PROBLEM                 | 47   |

| 5.1 Introdu | ection                                | 47   |

|             | c Requirement for Antenna Calculation |      |

| 5.3 Antenn  | a Ratio Definition                    | 49   |

|             | a Rule Checking                       |      |

|             | n for Antenna Problem                 |      |

| _           | otion of the antenna diode used       |      |

| 5.6 Proced  | ures For Fixing Antenna Problem       | 54   |

| CHAPTER 6   | CONCLUSION                            | 55   |

| REFERENCE   | S                                     | 57   |

| APPENDIX A  |                                       | 60   |

| APPENDIX B  |                                       | 65   |

| APPENDIX C  |                                       | 72   |

| APPENDIX D  | )                                     | 75   |

| APPENDIX E  |                                       | 78   |

| APPENDIX F. |                                       | 89   |

# LIST OF TABLES

| Table                                          | Page |

|------------------------------------------------|------|

| Table 3.1 Cell geometry definition and values  | 17   |

| Table 3.2 Parameter used for different corners | 26   |

| Table 5.1 Comparison of three Approaches       | 51   |

# LIST OF FIGURES

| Figure     | Page                                                                       |

|------------|----------------------------------------------------------------------------|

| Figure 1.1 | ASIC Design Flow4                                                          |

| Figure 2.1 | Comparison between Bulk CMOS and SOI CMOS structure7                       |

| Figure 2.2 | Layout of a CMOS inverter circuit using SOI and bulk technologies9         |

| Figure 2.3 | Cross-sectional view of an inverter showing parasitic bipolar transistors  |

|            | connected back to back ASIC Design Flow                                    |

| Figure 2.4 | Kink effect in PD SOI NMOS device                                          |

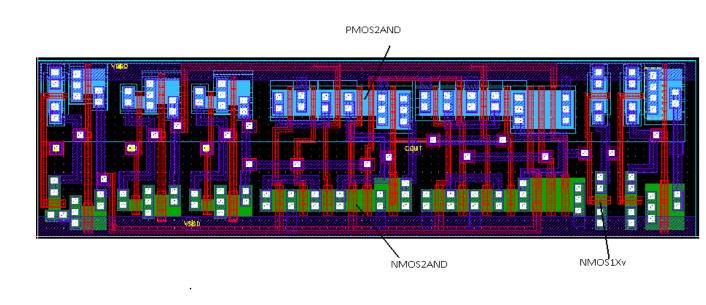

| Figure 3.1 | The Layout format of the Standard Cell Library17                           |

| Figure 3.2 | Definition of routing pitch                                                |

| Figure 3.3 | Snapshots of Cells a)PMOS2AND b)NMOS2AND c)NMOS1Xv                         |

|            | d)Fulladd_4                                                                |

| Figure 3.4 | Schematic view of Fulladd_4                                                |

| Figure 3.5 | Inputs and Outputs to SignalStorm Library Characterizer24                  |

| Figure 3.6 | Pin to pin Delays                                                          |

| Figure 3.7 | Setup and Hold time constraints for a positive edge triggered flip-flop 29 |

| Figure 4.1 | Stream out form                                                            |

| Figure 4.2 | Stream out user defined data form                                          |

| Figure 4.3 | Stream Out Option form                                                     |

| Figure 4.4 | Importing layout in abstract generator form36                              |

| Figure 4.5 | Types of Layout and Logical data that can be imported into the abstract    |

|            | generator and the format of data that can be exported38                    |

| Figure 4.6 | Running form for Pin step                                                  |

| Figure 4.7 | Running form for Extract step                                              |

| Figure 4.8 | Running form for Abstract step44                                           |

| Figure 4.9 | Pane showing various warning signs and progress in Abstraction Steps 45    |

| Figure 4.10 | Abstract view of Cell and 4_4                              | 46 |

|-------------|------------------------------------------------------------|----|

| Figure 5.1  | Analogy of antenna problem during manufacturing            | 48 |

| Figure 5.2  | Analogy of antenna problem during circuit normal operation | 48 |

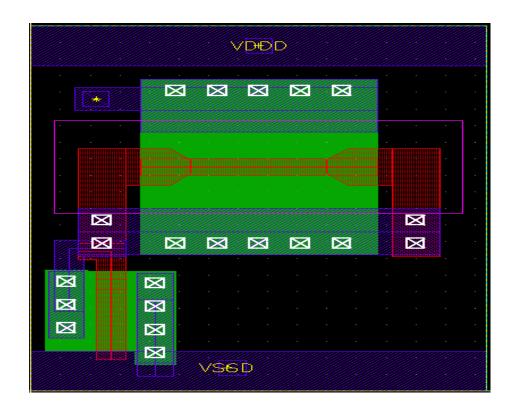

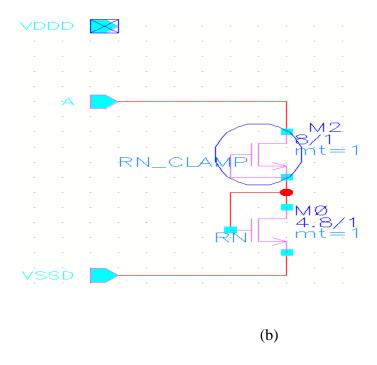

| Figure 5.3  | (a) Layout and (b) Schematic of Antenna diode cell         | 53 |

## CHAPTER 1

## INTODUCTION

Application specific integrated circuits are used to design entire system on chip. In Application specific integrated circuit also called ASIC cells from a standard cells library are interconnected to implement a desired system. With demand for more and more system on chip the complexity of the (IC) fabrication had also increased as complex layout issue had to be taken in to consideration. But automation tools such as library characterizer, Abstract view generators, Automatic Place and Route tools etc made, ASIC design flow highly automated and thus provide excellent performance and cost advantages over manual design process.

#### 1.1 Standard Cell Based ASIC Design Flow

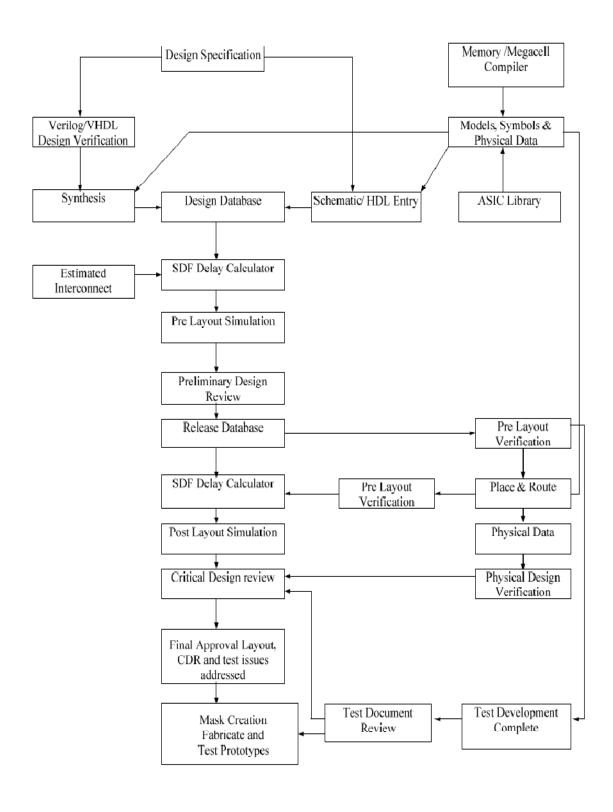

As ASIC (Application Specific Integrated Circuit) layout is highly automated, the reusability of basic cells for various design and also the optimal level of abstraction makes designing with cell library desirable. The cell based ASIC design flow diagram shown in Figure 1.1 categorizes the entire design procedure into tasks that fall under several design teams. The design procedure for ASICs given a fully characterized standard cell library is as follows [2]:

- 1. A synthesizable behavioral description of design in high-level description language (VHDL or Verilog) is written. This is called RTL (register transfer level) design.

- 2. The suitable functionality of the RTL code is verified by simulation.

- Design partitioning into fewer smaller blocks is performed. This provides easy handling of design, efficient synthesis results, with reduced time to market and reusability and fewer errors.

- 4. Logic synthesis on the RTL description is performed. This maps design on to standard cells and connectivity between them. This provides a gate-level net list depicting standard cells and electrical connections between them.

- 5. Functional simulation and static timing analysis are performed on the synthesized code.

- 6. A gate-level net list is imported into a place & route tool. Floor planning, power planning, placement, In Place Optimization (IPO) and trial route are performed on RTL level net list imported. Clock tree synthesis and timing analysis are performed. All the partitioned blocks are brought together at place & route level either with individual blocks placed and routed to give a block.

Figure 1.1 ASIC Design Flow [3].

- 7. Post layout simulation is performed and static timing is back annotated. Testing is performed demonstrating the functional correctness of the design over all extremes of process, voltage and temperature.

- 8. Physical verification (DRC and LVS) is performed at the end before the design is sent to semiconductor facility for fabrication. As designs grow in complexity day by day, it is becoming increasingly difficult to layout these circuits by hand. Hence a custom ASIC (Application Specific Integrated Circuit) cell library approach is desirable. This approach enables the designer to convert a design from its functional description in high level RTL (Register Transfer Level) code such as Verilog or VHDL to layout with minimum effort using automatic Placement & Routing (PNR) tools. The cell library would contain a set of combinatorial and sequential logic cells of different drive strengths with their corresponding layout, schematic and symbol views and their characterized timing and power models.

#### 1.2 Thesis Organization

This thesis consists of 6 chapters. Chapter 2 describes the details of Silicon on Insulator (SOI) implementation and its advantages over a typical bulk CMOS process. Chapter 3 describes the details of the cell library, its format, the library design guidelines, and characterization of cells for timing. Chapter 4 deals with Abstraction of the cell library. Chapter 5 discusses about the process Antenna error and the different ways we can solve the antenna error problems. Chapter 6 discusses conclusion and future work in the direction of improvement of the library Antenna error.

# **CHAPTER 2**

## SILICON ON INSULATOR WAFER TECHNOLOGY

#### 2.1 Introduction

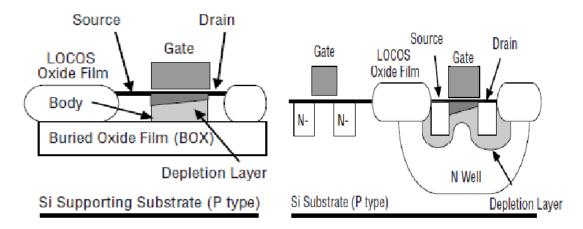

The term SOI stands for Silicon On Insulator. In SOI processes the devices are fabricated on a thin layer of crystalline silicon that exists on a thick layer of insulator such as sapphire or silicon dioxide which in turn is grown over a P substrate, it will be easy to understand when we observe Figure 2.1. Performance wise the SOI processes compared to the more normal Bulk process have the following advantages

- Latch up problem is eliminated

- Parasitic source and drain capacitance is reduced

- Improved subthreshold slope and transconductance

- Reduced leakage due to improved subthreshold and thinner parasitic diode

- Improved radiation hardness

- Higher device density

Due to the reduced parasitic and greater compactness, integrated circuits (IC) implemented on SOI are generation faster than bulk CMOS of same node geometry. Due to reduced leakage SOI ICs consume significant less power making them Ideal for low

power application. The soft error rate and data corruption caused by cosmic rays and are also significantly reduced in SOI processes.

#### 2.2 SOI and Bulk Device Structure

In bulk processes, individual devices are fabricated in the body of silicon. In an n-well process, N type MOSFETs are fabricated in P type silicon substrate while P type MOSFETs are fabricated in an n-well diffused in the P type silicon substrate on the other hand for the P-well process P type MOSFETs are fabricated in N type silicon substrate and N type MOSFET are fabricated in a P-well diffused in the N type substrate. The drain and source of NMOS and PMOS transistors are isolated from substrate by reverse bias p-n junction formed by drain or source itself with silicon substrate as can be seen in Figure 2.1. On the other hand devices in SOI process are fabricated in silicon thin film active layer over a buried oxide (BOX) layer. The (BOX) layer being an insulator provides isolation of transistors from silicon substrate underneath and other transistors. Local oxidation of silicon (LOCOS) or the removing of unused silicon between transistors isolating individual transistors provides the lateral isolation for transistor and resistor etc.

Figure 2.1 Comparison between Bulk CMOS and SOI CMOS structure [22].

#### 2.2.1 Reduction in leakage

The contributors to the leakage current in a MOSFET are the well diode current, the drain body current and the subthreshold current. As described in the device structure section Transistors in a bulk process are separated from the substrate by the reverse bias pn junction, the reverse bias current of these pn junctions contribute to the leakage currents. Finally leakage current is a function of the temperature and increases exponentially with increases in temperature. On the other hand in SOI process the devices are isolated from the substrate by the insulator so the leakage current is absent, thus reducing the total leakage current compared to the bulk process. The other contributor to the leakage current is the subthreshold leakage, which is lower in SOI processes compared to the bulk processes. As a result the standby and switching leakage current is significantly lower in SOI than in bulk process. Also surface leakage problems and field transistor action which may occur in bulk is absent in SOI resulting in SOI device operation with greater reliability at elevated temperature as high as 400°C with tolerable level of Ion/Ioff current ratios.

#### 2.2.2 Reduction in parasitic

In SOI the depletion region is well defined as denoted by the light grey region in the Figure 2.1. and do not extend in to the substrate as a result of the thin silicon film which greatly reduces the parasitic source and the drain junction capacitance compared to the bulk, as a result the RC delay due to the parasitic capacitance is lower, resulting the SOI processes having higher speed than an equivalent geometry bulk process at reduced power.

#### 2.2.3 Higher device density

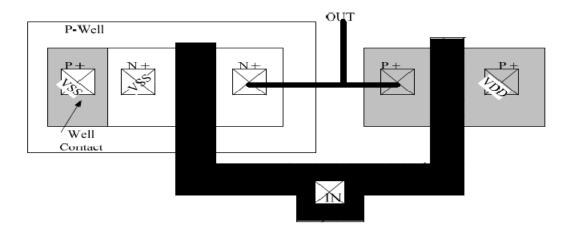

The devices In SOI process have higher device density as the source and drain of NMOS and PMOS can be placed in close proximity of each other which can be seen in Figure 2.2 without the possibility of a latch. Also in case of the SOI process the devices are fabricated on the insulator so we do not need well to separate the active area from the substrate as in case of the bulk process as a result we need smaller layout area, so the device density of SOI processes is much higher in comparison to Bulk process.

### (a) layout of bulk CMOS inverter

#### (b) layout of SOI CMOS inverter

Figure 2.2 Layout of a CMOS inverter circuit using SOI and bulk technologies [8].

#### 2.2.4 No Latch-up problem

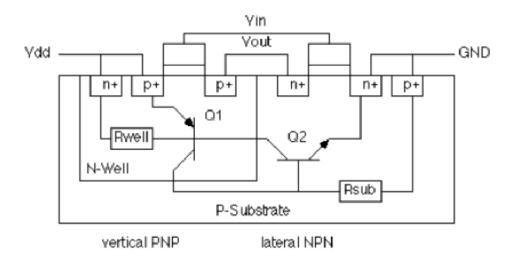

In bulk process due to the formation of the thyristor PNPN structure with parasitic PNP and NPN junctions connected back to back which can result in latch up. See Figure 2.3 during latch up a low impedance path is created between the power rail and the ground rail, so when latch up is triggered a high current passes through both the transistor until power is switched off. With CMOS the IC device gets permanently damaged due to passage of these high currents. On the other hand in a SOI processes the devices are electrically isolated from each other and the substrate by an insulator layer eliminating the parasitic transistor [10] and possibility of latch up.

Figure 2.3 Cross-sectional view of an inverter showing parasitic bipolar transistors connected back to back [11]

#### 2.2.5 Potential for lower threshold voltages $(V_T)$

The subthreshold slope of SOI is significantly lower than that of the bulk process resulting in lower subthreshold leakage currents in SOI processes for identical thresholds, In bulk process threshold voltage varies more with the channel length, any variation in poly silicon etching will show up as the variation of the threshold voltage. The threshold voltage must be high enough in the worst case to limit the subthreshold leakage; as a result nominal threshold voltages must be higher in the bulk process. In SOI processes the threshold voltage variation is smaller and the subthreshold slope is steeper hence the nominal threshold voltage can be reduced. The opportunity to reduce the threshold voltage results in greater ON currents. This results in SOI processes having lower threshold voltage than the bulk device [13]. As a result with SOI processes better delay power product performances can be obtained, especially at low supply voltages.

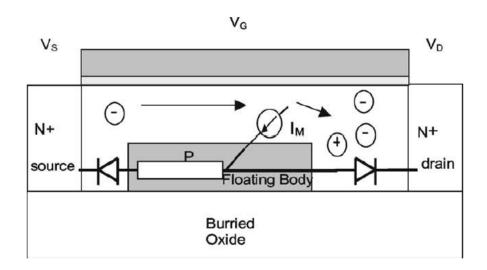

#### 2.5.6 Floating Body effect

Despite having the advantage of low power consumption and higher device density an SOI process has some structural disadvantages. First the MOS device is always accompanied by a parasitic transistor which functions in parallel. The transistor is formed by back to back diodes between the source/body and drain/body junction. In the bulk process the base of the npn(pnp) transistor in parallel with the NMOS(PMOS) channel is always connected to the VDD(ground), however in case of the SOI processes the base are floating. So when the MOS is in saturation and the drain voltage exceed a specific value so the source/body diode  $V_{\rm BE}$  is above saturation voltage, the parasitic transistor

turns on resulting in a increases in the drain current, this sudden increase in drain current shows a discontinuity of the drain current in I-V curves [8], this is referred to as the kink effect.

Figure 2.4 Kink effect in PD SOI NMOS device[22].

Kink effect is caused by the parasitic BJT effect in PD SOI. For a NMOS as shown in the Figure 2.4 for large drain voltage the mobile electron causes impact ionization due to the presence of high electric field near the drain end causing the formation of electron hole pair. The electron moves toward the positive drain and holes moves toward the more negative floating body and accumulate at the buried oxide boundary near the source which results in a increase in local body potential and decrease in local threshold potential this increases the drain current, while the holes injected in the parasitic BJT via it  $\beta$  trigger a sudden rise in the collector current which is observed as the increase in drain current.[23]

Kink effect is absent in fully depleted (FD) SOI devices making design easier for circuit designers but they do occur in partially depleted (PD) SOI devices. One way to reduce this effect is to provide body contact for the devices but the problem is that it

increases the layout area and thus lowering the device density. On the other hand, partially-depleted devices alleviate the constraint on the source/drain series resistance and threshold voltage, offering higher performance and easing the manufacturing problem by allowing the doping profiles to be tailored for any desired threshold [9]. The PD SOI process provides much better control over the sort channel effect than the fully depleted (FD) SOI devices.

#### 2.5.7 High source/drain resistance

In SOI process the devices are fabricated on a thin silicon film over a insulator as the thickness of the silicon film is reduced the source/drain resistance increases which in turn reduces the drive current and switching speed. This reduction is a direct result of source degeneration caused by the source resistor and source current IR drop.

#### 2.3 Summary

From the above discussion we can see that SOI process has the advantage of low power consumption, higher device density, lower parasitic capacitance and tolerable Ion/Ioff ratio at 400°C temperature over the bulk process. The disadvantages of SOI processes are higher source/drain resistance and the floating body effect.

So comparing the advantages and disadvantages we used the SOI process for our cell library for LEON3 which will operate at 200°C.

## **CHAPTER 3**

# STANDARD CELL LIBRARY

## **CHARACTERIZATION**

#### 3.1 Introduction

For efficient ASIC design we always need access to a properly characterized standard cell library. In a standard cell library we have both combinational and sequential logic cell of different drive strengths. In the cell library each cells have their own respective schematic, symbol, layout and abstract view. All cells in the library need to characterized electrically, logically and physically this includes their timing and power model. After the cell library is complete it can then used to translate a high level Verilog or VHDL description of the ASIC to layout using place and routing tools such as Encounter. The cells can be designed with varying drive strength so as to achieve maximum performance at minimum area. This results in the use of minimum size transistors for the logic and buffering to set the drive strength to charge a range of load capacitances. So we need to determine the size of the transistors to meet the design requirement such that we can have minimum area without sacrificing any speed and drive strength and make the cells as compact as possible.

#### 3.2 Cell Library Design Flow

The usual design flow for standard cell library development is as follows.

- Widths and lengths (typically selected at minimum except for high temperature efforts) for the NMOS and PMOS devices are set using analytical approach to meet the design requirements in terms of optimal delay, minimum geometry or optimal noise margins and drive current.

- 2. Initially a transistor level schematics are generated for each cell and the performance verified using spice/spectre circuit simulation tools

- 3. After schematic entry the layout for each of the cells is created with the effort taken to make each cell as compact as possible, while complying with all the design rules provided by process foundry.

- 4. After the layout verification is completed by running the DRC (Design rule check) and the LVS (layout versus schematic check) checks. These checks confirmed that there is no design rule error, sizing errors of the transistors or incorrect connections between the layout and schematic.

- 5. The cells are simulated to ensure proper functionality and to extract their timing and power model files. To obtain realistic manufacturing process characteristic, circuit simulation for model extraction is performed across temperature, voltage and process parameter corners over the range of values that are expected to occur in expected operation. The characterization is done using an automatic cell characterization tool, i.e. signal storm. After the simulation the power and timing data is transformed into the format that is required by the synthesis tool used for the ASIC design.

6. Along with the timing library, the place and route tool also requires a physical description library that includes definitions of blockages, information regarding routing layers, pin information and to avoid the generation of shorts among the cells when routing the cell interconnection. Cadence abstract generator is used for getting Layout Exchange Format (LEF) file and abstract views for all the cells.

### 3.3 General overview of the Cell library

#### 3.3.1 Physical description of Cell

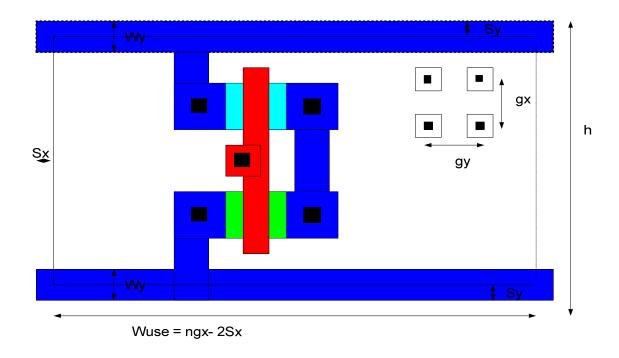

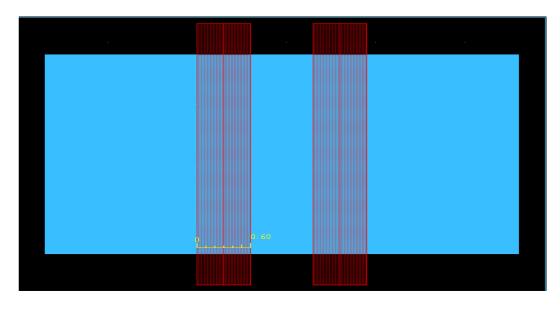

The peregrine process that is used for the library is a three layer metal process. We used metal1 and poly for the interconnection inside the cells while metal2 and metal3 are used for routing. In routing metal2 is used for vertical routing and metal3 is used for horizontal routing. The width of the power rail is 2.4µm and the height of each cell is 22µm. We need to have a safety zone of 0.9µm on the nlocos side and 0.4µm on the plocos side, the left and right sides also have safety zone of 0.4µm. The safety zones are required to avoid any DRC error when the cells are abutted to each other during the placing process. All the pins are placed on the routing grid (explained in section 3.4) to facilitate routing as shown in Figure 3.1

Figure 3.1 The Layout format of the Standard Cell Library.

Table 3.1 Cell geometry definition and values.

| Parameter | Value                                               | Comment                                                                                                                       |  |

|-----------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| gx        | 2.2um                                               | Horizontal grid spacing ( isolated metal width)                                                                               |  |

| gy        | 2.2um                                               | Vertical grid spacing                                                                                                         |  |

| Sy, Sx    | 0.9um(NMOS<br>rail)<br>0.4um(PMOS<br>rail)<br>0.4um | Safety zone required to avoid abutting DRC errors.  Safety Zone to avoid abutting errors from left and right side of the cell |  |

| Wp        | 2.4um                                               | Power rail width                                                                                                              |  |

| h         | 22um<br>(m*gy)                                      | m vertical grid equal to 10                                                                                                   |  |

| Wuse      | ngx-2Sx                                             | N horizontal grid point must be a integer                                                                                     |  |

#### 3.3.2 Logical description

In the library presented here we have both logical and sequential cells. The logical cells in our library are AND, OR, NOR, NOR, NAND, XOR, NXOR, ANDOR, ANDOR INV, ORAND, ORANDINV, INVERTER, BUFFER, FULLADDER, HALFADDER, HALFSUB AND TRISTATE BUFFER all the cells have combination of different number of inputs and are of four drive strengths. Similarly the sequential cells we have are different type of LATCHES, MASTERSLAVED FLIPFLOPS and SCANMASTERSLAVE D FLIPFLOPS. All the sequential cells also have four drive strengths. For details of the different type of cells see appendix A

#### 3.3.3 Electrical description

Before the cells can be used to layout an ASIC the cells need to be characterized, the characterization process is detailed in section 3.5. From the characterization of the cell we get the following information; pin to pin delay, power consumption and logic for each cell. In the case of the sequential cells in addition to the delay and power, information regarding setup, hold, recovery and removal time constraints are also extracted. All this information can be converted into a table format by converting the *alf* file in to *html* fie for example see appendix E

## 3.4 Layout Procedure

This section explains the procedure followed to create a cell layout. The layout of the cell is drawn using the cadence virtuoso layout editor. For Layout standard cell technique,

where the signals are routed perpendicular to the power rail with the polysilicon layer is used. With this approach dense layout for CMOS gates can be achieved. The Figure 3.1 will give a rough idea of cell layout. Table 3.1 provides values of the more important dimensions. In the layout process the first step is to determine the length and width of the transistor, once the length and the width of the transistor is finalized the following steps are followed.

- 1. Cell height is chosen to be the lowest possible integer multiple of metal1 routing grid that accommodate the most complex cell in the library such as a flipflop or a full adder. In this way it is ensured that any other cell in the entire library will fit in the selected fixed cell height. The finalized height was 22um.

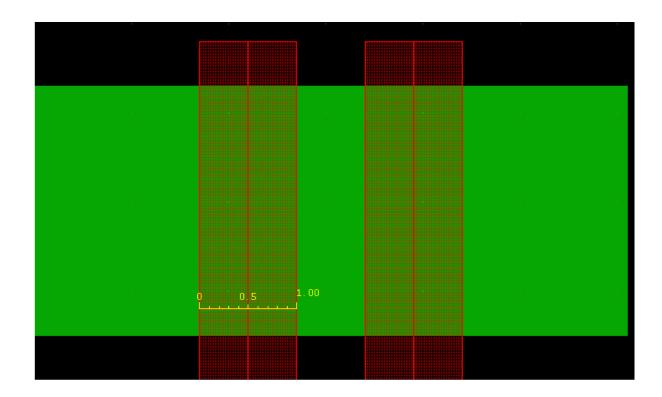

- 2. Small instances are created to be used throughout the cell library. These include instances like NMOS and PMOS with 1X, 2X, 3X, 4X drive strengths and also instances for 2, 3, 4, transistors in parallel see Figure 3.3 a, b, c. The P/N ratio is set so as to have the transistors beta matched. Creating small cell instances reduces manual design time to a great extent as we need to layout these instances many times while drawing the cells.

- 3. All the I/O pins should be placed on grid points (multiples of 2.2 um in our case), to produce optimum routing.

- 4. Put as many contact as possible to provide greater reliability and small resistance.

- Verification is performed so that each cell passes DRC and LVS checks so that

no design rule error exist in the cell and also no mismatch between layout and

schematic.

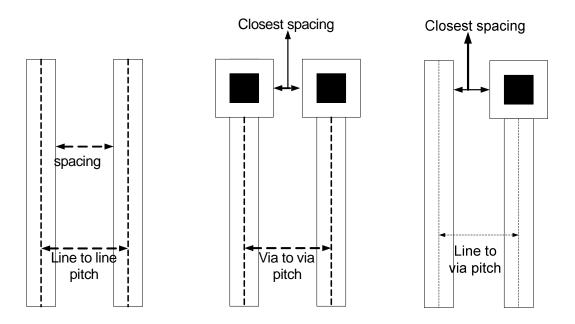

The width of all the cell are n times gx where 'n' is a integer and all the I/O pins are on horizontal grid gx and vertical grid gy to have greater efficiency while doing place and route. Here in Figure 3.2 we can see there are three ways we can determine the grid for routing, in our case the grid is determined by the via to via spacing, which is  $2.2\mu m$ . Since for this process the routing tools uses fixed-grid three-level routing the distance between the middle of two metal1 and metal2 is  $2.2\mu m$  and the distance for metal3 is  $2.4\mu m$ . As mentioned earlier only metal1 and poly are used for interconnect within the cells while metal2 and metal3 are used for vertical and horizontal routing respectively over the cell. (see Figure 3.3 d)

Figure 3.2 Definition of routing pitch.

(a)

(b)

Figure 3.3 Snapshots of Cells a)PMOS2AND b)NMOS2AND c)NMOS1Xv d)Fulladd\_4.

(d)

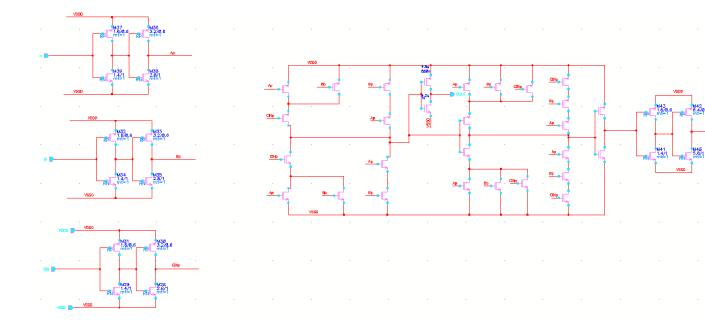

Figure 3.4 Schematic view of Fulladd\_4.

## 3.5 Characterization of Cell Library

The characterization system takes a standard cell after layout and performs simulation on it according to the requirement of the library. The simulator provides all the simulation stimuli and signal storm post processes the result to generate the logical functionality and document the timing and the power models for the simulated cell. This is tabled for use by the synthesizer to assemble the ASIC to meet the timing constraint and power constraint across corners. Cell characterization is the foundation on which the entire high-level RTL-to-GDSII flow has been built. Without accurately modeled ASIC cells IC design would not be possible, require many people hours and software licenses, while suffering multiple prototype failures.

#### 3.5.1 The Library Characterizer – SignalStorm

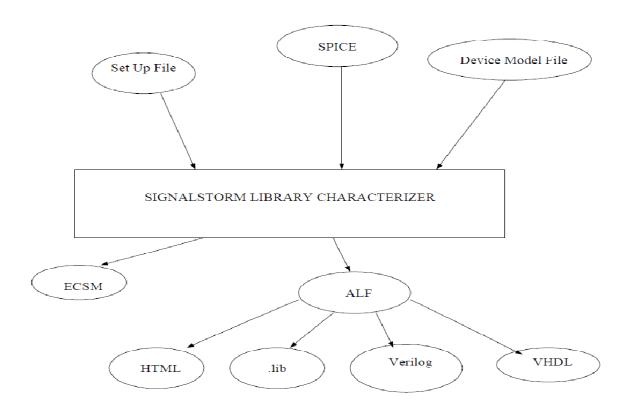

The main inputs in a library characterizer are a SPICE-format netlist that contains the detailed of transistors in the cell, the setup file which have the all the information about the condition of simulation and the transistor model files provided by foundry. The main output of library characterization is a library database that contains timing and power models for each of the cells. These models are then used in power and timing calculation. The simulator used for characterization is called signal storm (see Figure 3.5)

Figure 3.5 Inputs and Outputs to SignalStorm Library Characterizer

SignalStorm performs the following steps for automatic cell library characterization [14]:

Analysis of Spice models of transistor circuits and recognition of the logic structure and functionality.

- 2. Generation of the logic or function model for combinatorial, sequential and tristate circuits.

- 3. Generation of electrical, logical and timing specification definitions for the circuit such as pin directions and properties, pin to pin delays etc.

- 4. Generation of Delay Vectors.

- 5. Generation of Power Vectors.

- 6. Defining the cell library characterization environment by specifying parameters such as the supply voltage, temperature, input slew rate, output load and process corners (Fast ,Typical and Slow)

- 7. Execution of Spice netlist and summarizes the results see 8 below.

- 8. Generation of Abstract Library Format (ALF) file which can be further converted to .LIB, .VHDL, .V and HTML files.

All cells need to characterized logically and electrically. Electrically the cells are characterized for the propagation delays, input pin capacitances and current requirements. Propagation delays are the tabulation of the intrinsic and load-dependent delays and calculated for all pin-to-pin paths. Input pin capacitance consists of either the active capacitance, which occurs when the output node switches or the passive capacitance which occurs when the outputs remain in a stable state and wire parasitic. Current consumption requirements are needed for power analysis. For sequential logic cells along with the above data, the Signal Storm library characterizer characterizes the cell input signal constraints, like setup time, hold time, release time, removal time, recovery time, and minimum pulse width. Signal Storm characterizes sequential logic constraints by using a delay-tolerance-based binary search method. The results are saved as a table of

input slew rates. Thus for the sequential logics Signal Storm library characterizer generates the constraint definitions for the clock signal, data signal, preset signal and clear signal[14]. Html format of output of Signalstorm is shown in appendix E.

#### 3.5.2 Setup file

In the setup file all the condition required to accurately simulate our library are set, so one need to be careful and accurate when developing inputs for the setup file. The simulator will simulate with whatever input we give to it and the data may be of no use. The old adage of garage in garbage applies 10 or more fold with the possibility of garbage for every cell. One needs know about the functional detail of the parameters in the setup file see appendix B 2.

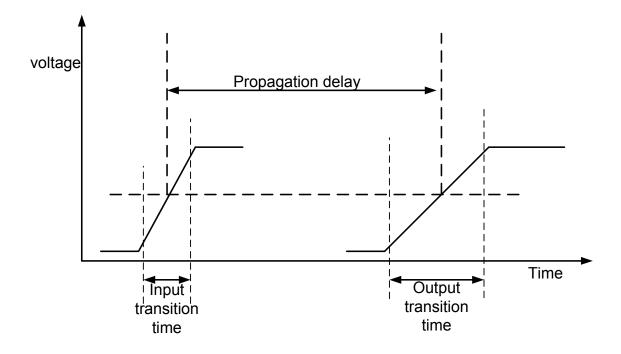

#### a) Corner

Propagation delay depends on both the input slew rate and the output load capacitance. Signal storm characterize the cells, in terms of different input slew rates and load capacitance. To get the correct information about the timing and power model at different conditions simulation is performed for three different corners that is "fast fast", "typical typical" and finally "slow slow" with the same input slew rate and load capacitance but for different supply voltages, temperatures and processes as we see in Table 3.2 .For example see section 1 of appendix C

Table 3.2 Parameter used for different corners.

| Corner             | Supply<br>Voltage | temperature | process |

|--------------------|-------------------|-------------|---------|

| Slow slow          | 3V                | 200°C       | slow    |

| Typical<br>typical | 3.3V              | 27°C        | typical |

| Fast fast          | 3.6V              | -25°C       | fast    |

#### b) Voltage Threshold

In the setup file all the voltages are defined relatively see section 2 in appendix C. where we can see the high level voltage "Vh" is 100% of the supply voltage and low level voltage "Vl" is 0, the threshold voltage "Vth" is 50% of the supply and the high slew voltage level "Vsh" is 90 % while low slew voltage level "Vsl" is 10% of the supply voltage. Also the voltage threshold levels are same both for input rising/falling and output rising/falling.

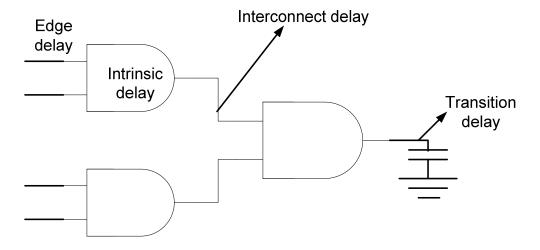

#### c) Intrinsic delay

This is a important parameter as it provides the frequency limit of the transistor. It is the built in delay of the logic gates caused due to the frequency limit of the transistor. For example in a NMOS as the electron move from the source to the drain it suffers collisions and finally reach a saturation velocity as a result it takes a finite time to cross the length of the transistor gate and cannot be any more faster. This finite time the electron takes is the intrinsic delay of the NMOS transistor. While setting the values of input slew in the set up file for characterization we have to take in to consideration the value of the

intrinsic delay to ensure selected slew times are NOT faster than intrinsic delay or  $1/\omega T$ . This is merely wasting the run time of the tool at best and at worst documents slew times faster than intrinsic delay than physically possible.

#### d) Input Slew

The input slew is the rate at which the input is rising / falling, the input slew with the output load capacitance that the gate is driving dominates the delay of the gate. As mentioned earlier the input slew cannot be lower than the intrinsic delay of the transistor as the transistor cannot respond so fast and the upper limit of the input slew in the setup file depends on maximum output slew that is acceptable.

#### *e)* Output Loading Capacitance $C_L$

The capacitance seen by output pin of the cell determines the output slew. The load capacitance should be selected as normalized load, for each gate drive strength from 1X to 8X, i.e. 1X, 2X, 3X, 4X, 8X. When determining intrinsic delay in which case the normalized load must be much smaller than the gate output capacitance i.e X/20 or lower. Since the amount of delay and rise/fall times depends on both the input slew rate and the capacitance seen by the output pin, the signal storm library characterizer executes simulations by using different input slew rates and output loading capacitance combinations and tabulating the results

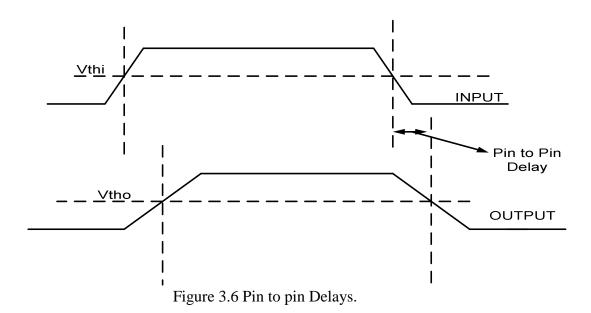

#### f) Pin to Pin delay

The Signal Storm library characterizer provides the delay for specific cells called pin to pin delay where pin-to-pin delay is the time that a change at an input pin takes to effect a change at the output pin. The time is measured from the point when an input signal

switches through an input threshold voltage (Vthi) to the point when an output signal switches through an output threshold voltage (Vtho), as shown in Figure 3.6. A detail explanation of the Pin to Pin delay is given in appendix C.

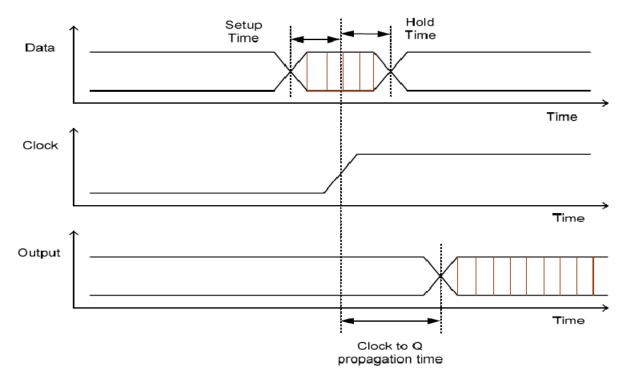

#### g) Setup time

The setup time is the time during which the input data to the input of the sequential logic must remain stable prior to the arrival of the clock so that the correct value is latched at the output.

#### h) Hold Time

It is defined as the minimum time that an input signal must remain stable after the active clock signal to ensure that input value is correctly latched at the output.

It is evident in the example shown in fig 3.7.

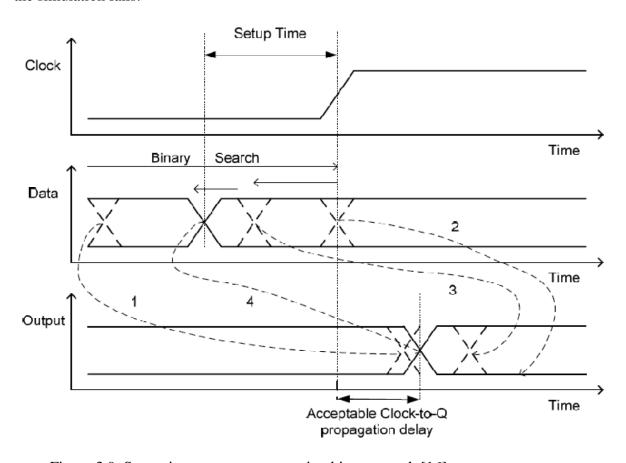

Figure 3.7 Setup and Hold time constraints for a positive edge triggered flip-flop.

In signal storm the constraint on setup time and hold time is determined by delay-tolerance-based binary search method that is the setup time should also be such that it does not degrade the Clock-Q propagation time beyond a pre-determined tolerance value. In Signal Storm library characterization, to ensure that set up time chosen is not so close to the switching point that the simulation fails, it performs a delay tolerance check by multiplying the delay from clock (CK) to the output Q by factor specified with SG\_BI\_DRATIO variable. As soon as the CK-Q delay is more than delay tolerance variable, the simulation is considered a failure and next iteration follows. The binary search is defined in detail in appendix E and the parameters for binary search in the setup file are in section 3 of appendix B 2

### 3.5.3 Output of the characterization

After characterizing the cells the input slew rate, output loading and calculated pin to pin delay are saved as a two dimensional delay table. The output slew rate which is also calculated by these Signal Storm SPICE simulations, is saved in a second table. There are several types of standard formats in the industry for describing Cell Library's characterized data. Different tools from different vendors read the same information from the technology libraries in their corresponding formats. Initially the output is in the *alf* format which can be converted in to *lib*, *html or verilog* format.

**Alf-** Advanced Library Format is more descriptive than .lib format file. SignalStorm generates this file as an output from its database. ALF can be further converted to .lib or .html format using 'alf2lib' and 'alf2html' commands.

**Lib** – Synopsis Liberty Library is used by Synopsys products for synthesis, timing and power information. This format supports most of the models; and is more or less the industrial a standard.

### 3.6 Components of a cell library

Irrespective of the Cell library it must have all the information listed below to be used for an ASIC design.

- Circuit Schematics, Symbols, Layouts, Parasitic Extraction and Abstracted views of each standard cell.

- 2. A model in Verilog /VHDL for all the cells.

- 3. File containing timing, power and logical functionality data for certain threshold voltage, temperature, Process and operating voltage in a format that is accurate and acceptable industry wide for synthesis and Place & Route (P&R).

- 4. Documentation of the cell library that contains the logical functionality of all cells along with the timing and power data of the cells

- 5. Physical description of the cell in terms of information about the routing layer to be used, the dimension of the cell and the information about the pins. This physical description is needed by the automatic place and route tool and can be obtained from the abstraction of the cell which is described in the next chapter.

## **CHAPTER 4**

## ABSTRACTION OF CELLS

#### 4.1 Introduction

An abstract is a high-level representation of a layout view it contains information about the type, size of the cell, position of pins or terminals, and the overall size of blockages. The abstracts generated are based on physical layout, logical data, process technology information, and specific cell-modeling requirements. Abstract views generated are used in place of full layouts to improve the performance of place-and-route tools, such as Cadence Encounter and Cadence Silicon Ensemble. After the place-and-route is complete, the abstracts are replaced back with the layouts.

### **4.2** Launching the Abstract Generator

- 1. First we have to stream out the layout of the cells in .gds format, while streaming out the cells we have to make sure that the pin information are not lost for which we have to label all the pins with text information layer while drawing the layout. Steps of streaming out are explained below.

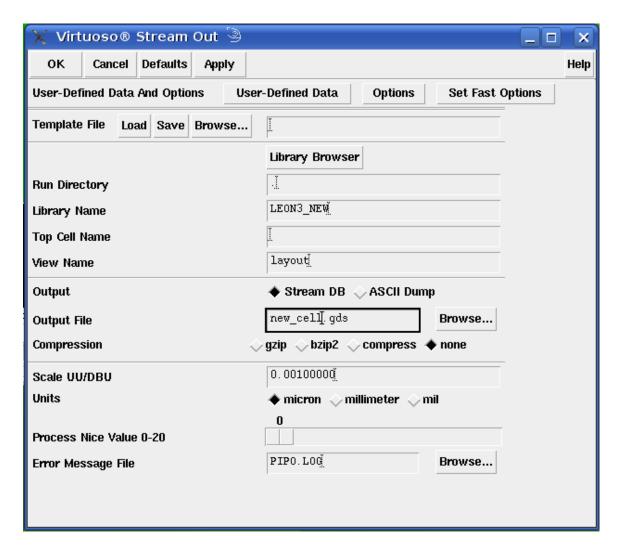

- a)On the icfb window select *File* ▶ *export* → *stream*. A window as shown in fig 4.1 pops up, where we have to type the name of the library such as *LEON3\_NEW* in our case and the name of gds file that will be generated which is *new\_cell.gds* here.

Figure 4.1 Stream out form.

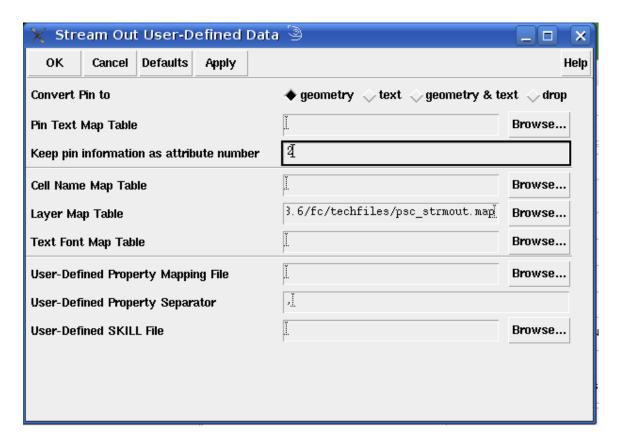

b) Next click the *User Defines Data* tab and the window as shown in fig 4.2 pops up in this window type **2** in the box of *Keep pin information and attribute number* and path of the *stream out map file* in the layer map table box and click OK

Figure 4.2 Stream out user defined data form.

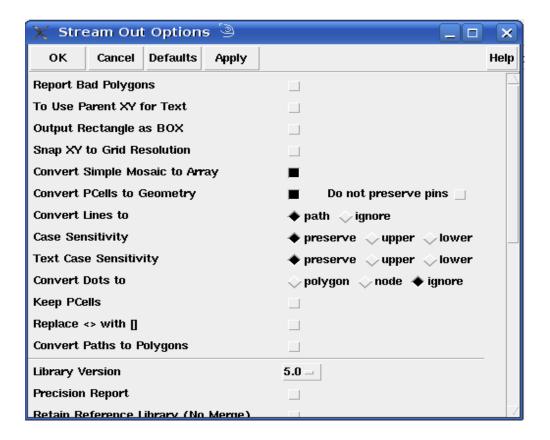

- c) In the next step click *Option* tab and the window as in Figure 4.3 pops up and the window is filled up as shown in the diagram and click OK.

- Then click OK on the window in Figure 4.1 and the streaming out starts and finally we have to make sure that a error free completion result pops up.

Figure 4.3 Stream Out Option form.

- 2. The next step in Abstraction is to create a new library and attach the new library to the proper technology file. We have to make sure that the technology file have all the information needed for Abstraction(see section 4.3)

- 3. We launch the abstract generator from the open terminal by typing the command *abstract*.

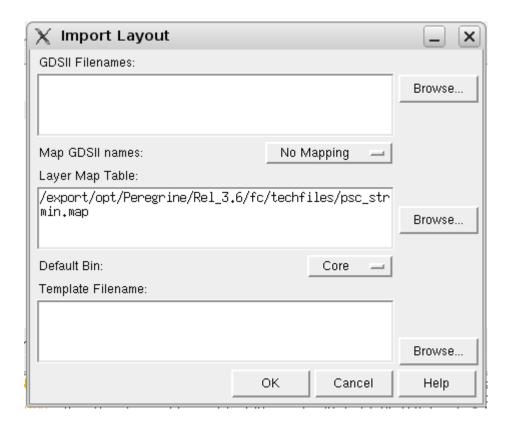

- 4. After the abstract terminal is opened we have to open the new library created and Click

File → Import and the window swown in Figure 4.4 pops up where we have to enter

the gds file and the path of the stream in map file.

Figure 4.4 Importing layout in abstract generator form.

Finnaly the cells are distributed in to appropriate bins to be abstracted accordingly.Now the cells are ready for abstraction.

## **4.3 Requirements to start the Abstract Generation**

This topic outlines the basic requirements to start generating cell abstraction:-

1. Ensure that you have all the necessary process technology information required by your cell library. Technology information provides details of the process technology used during IC fabrication, including names of layers, colors, and fill

- patterns, GDSII layer mapping data, and design rules for various layers and vias. In our case the technology library is psc\_PNR\_FA\_LEON3\_08.

- 2. At times we may have the technology file in form of LEF file, in which case we cannot directly attach the technology file to the library, first we have to convert it into ASCII format and generate the technology file.

- 3. Provide the abstract generator with information about the physical (layout) or logical construction of the cells in the library you want to process. You can do this by importing various types of data, such as LEF, DEF, and GDSII. You can also import logical information, typically represented in Verilog or Timing Library Format (TLF), Compiled Timing Library Format (CTLF) and also Encrypted Timing Library Format (ETLF).. In our case we have imported GDSII format file of cells.

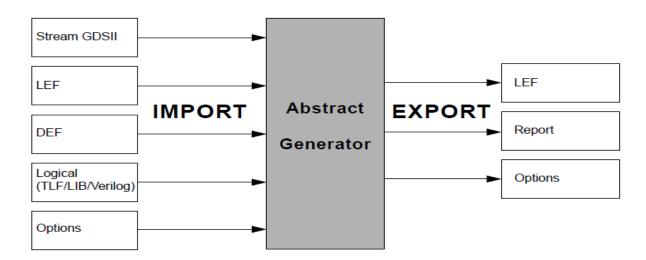

Figure 4.5 Types of Layout and Logical data that can be imported into the abstract generator and the format of data that can be exported [17].

#### **4.4 Create Abstracts**

Whether you are generating abstracts for an entire library or for a few hierarchical blocks, the approach is typically the same. You should initially focus on a small subset of cells or blocks, establish option settings for this subset, and then process the remaining cells or blocks in a single run.

- Identify the cells with which you want to experiment, and begin to Generate

Abstracts for these cells.

- 2. Inspect the Results in the generated abstracts.

- 3. You can then begin to Modify Option Settings as required, and then rerun the required steps.

- 4. If you are satisfied with the results, you can process the remaining cells in your library.

- 5. After the abstraction is complete the abstracted information is export out in the form of *LEF* file

#### **4.5 Generate Abstracts**

Each of the four main flow steps—*Pins, Extract, Abstract*, and *Verify*—have their own set of options that control the way in which any cell is processed. You can make your initial option settings either before you start generating abstracts or when you run any of the individual steps.

## **4.5.1 Running Forms**

Whenever you run any flow step, the abstract generator opens the *Running step* form. This form allows you to modify only the options that are relevant to the steps you are about to run. When you are satisfied with the options settings, generate the abstracts for the selected cells. You can run the steps either one at a time or all at once for any or all of the cells.

## Four main steps of abstraction

#### a) Pins

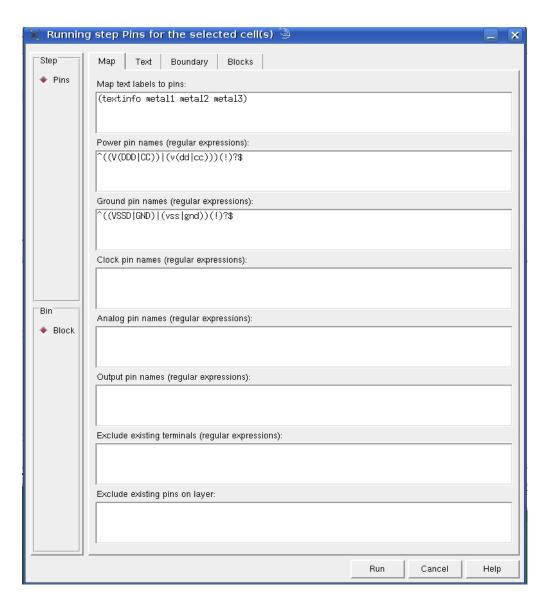

The Running form for the Pin step is shown in Figure 4.2 has four tabs which are *Map*, *Text*, *Boundary* and *Blocks* for the map tab we have to mention all the layer used for labeling the pins, the name of the power pins and finally the name of the output pins as all the pin are taken as input pin by default.

We leave the text tab form as it is, next for the boundary tab we have to choose *always* instead of *as needed* and keep the block tab form blank and finally click run. Thus in the Pins step, the abstract generator creates a place-and-route boundary for the cell and the starting pin shapes for each of the nets to be extracted. It then matches the pins created against those described in any logical view present and appends the appropriate pin direction.

Figure 4.6 Running form for Pin step.

Figure 4.7 Running form for Extract step.

### b) Extract

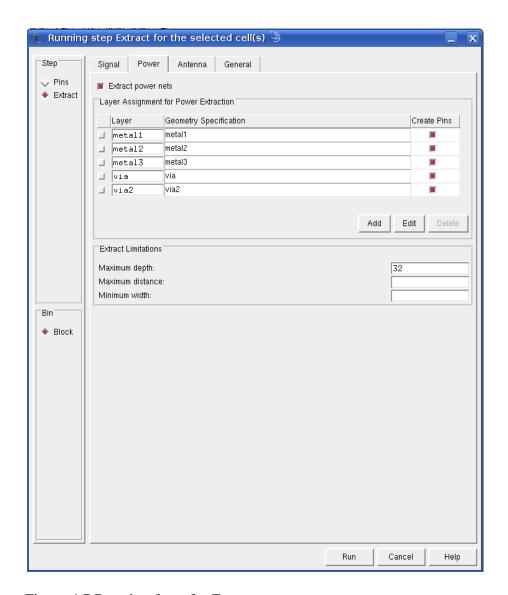

The Extract step running form is shown in Figure 4.7 also has four tabs which are *Signal*, *Power*, *Antenna*, and *General*. In the Signal tab form we deselect *extract signal nets* but for the power tab we have to select *extract power net* so that the whole power rails geometries get converted into a pin geometry. The form for the antenna tab will be filled automatically if the technology file contains all the required information for antenna calculation, we only have to select how we want to calculate the antenna area. An

antenna rule generally calculates the metal side plus surface area to gate area ratio or the metal surface area to gate area ratio by default. The last tab is the general in which we have to mention the detail of the layers for metal1 to meta2 contact, metal2 to metal3 contact, poly to metal1 contact and finally active to metal1 contact.

Thus in the Extract step, the abstract generator derives which shapes are connected to which nets by tracing the connectivity from the *pin* shapes created during the Pins step. The tool also creates shape with purpose *net* in the top level of the extract view, and for each such shape creates a pin on the appropriate net. The overlap boundary is also calculated if required(when overlap boundary layer is present). Finally, the abstract generator uses the antenna options to create library process antenna information for custom blocks and standard cells. The resulting antenna model helps mitigate the problem of gate damage caused during manufacturing.

### c) Abstract

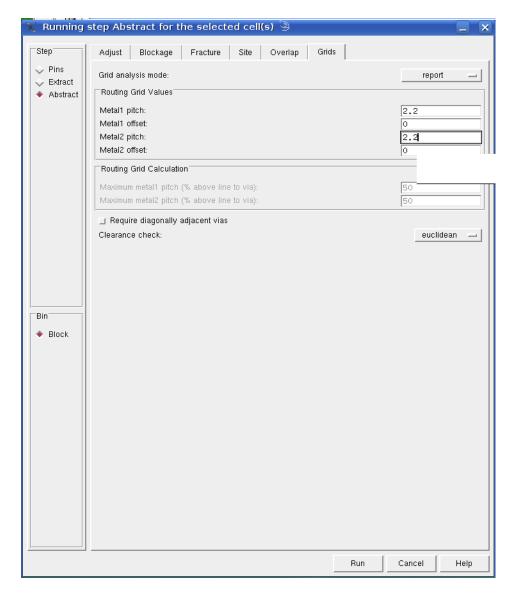

The abstract running form is shown in Figure 4.8 has six tabs in it *Adjust, Blockage, Fracture, Site, Overlap boundary* and *Grid.* In the *adjust* tab we have to mention all power pins and how they would be connected and oriented that is if they would be abutted or feedthrough and facing the core or not. In the case of the core cells the power rails are all abutted. In the *blockage* tab we have to choose "*detailed*" for all the metals, the *fracture* tab form is kept as it is, for the *Site* form we have to type "CORE" as all the cells in the library are of same height and are used for the core of leon3, the *overlap boundary* switch is kept off and finally the *grid* for both metal1 and metal2 is chosen to be 2.2 (Chapter 3) and offset is entered. For the LEON3 library offset is chosen to be 0. Thus in the Abstract step, the abstract generator adjusts the pin shapes created during the

Extract step to create the final shapes required by place and route tools. It then fractures these pin shapes into rectangles. Next, the abstract generator applies a layer blockage model selected by the user to create the final blockage geometry in the abstract. The blockage geometry is then optionally fractured into rectangles. It then removes from the abstract all layers other than those with purpose *pin*, *blockage* or *boundary*

Figure 4.8 Running form for Abstract step.

and deletes the instance hierarchy. At this stage, all the required geometry is at the top level of the abstract.

## d) Verify

The verify running tab have two tabs which are *terminal* and *Manufacturing* grid

The Verify step in the abstract generation process involves a series of functionality checks designed to detect any problems in the abstracts generated. During the Verify step, terminals are compared for any differences that might exist between logical and abstract views. Pin and geometry information on manufacturing grids is checked, and each abstract is tested within the target place-and-route system.

## 4.6 Inspecting the result

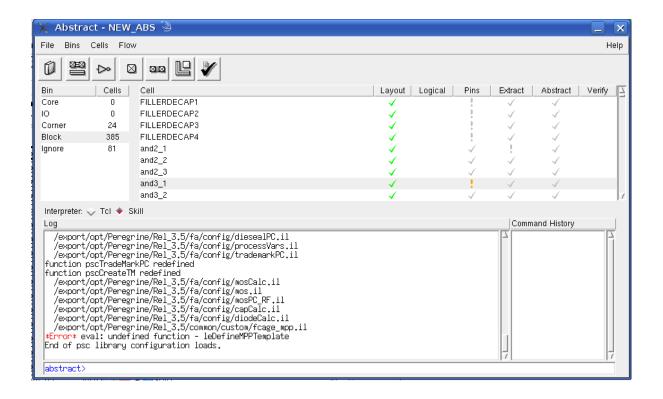

**Cell Pane:** The first source of result evaluation comes from the *Cell Pane* in the main window. The abstract generator uses color-coded symbols in the *Cell* pane to indicate the result of a particular abstract generation flow step. A green/red signifying pass/fail symbol attached to each cell in the cell matrix as observed in see Figure 4.9 corresponding to a particular step in the abstraction process steps.

Figure 4.9 Cell Pane showing various warning signs and progress in Abstraction Steps.

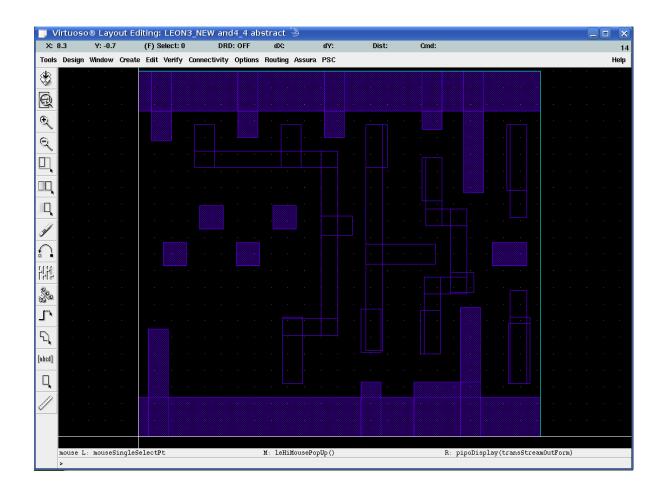

**4.7 Layout Editor:** - If you want to see a detailed graphical representation of any view, you can use the Layout Editor. You can use the Layout Editor functions to examine the pin and blockage geometry generated, the sizing and spacing applied, and to make minor edits. To launch the Layout Editor, select *Cells – Edit* and select a view. See Figure 4.10

Figure 4.10 Abstract view of Cell and 4\_4.

## **CHAPTER 5**

## ANTENNA ERROR PROBLEM

#### 5.1 Introduction

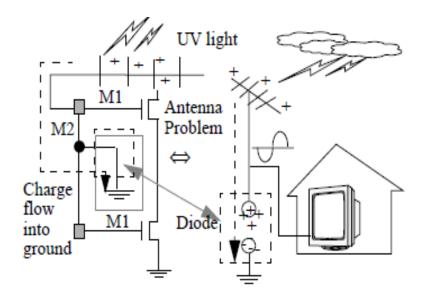

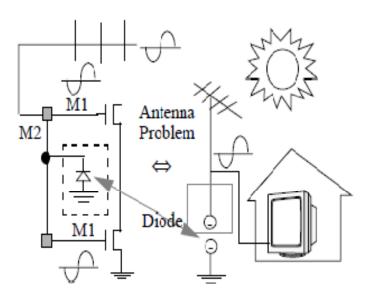

Antenna problems have existed in the chip manufacturing industry for more than one decade. During wafer manufacturing, charge caused by UV light, etching etc accumulates on the long floating wires. If the wire is connected to the input gate, the device may be damaged. This reduces the wafer manufacturing yield. To prevent the damage we have to find a way to bleed the accumulated charge. Analogies for antenna problems during wafer manufacturing and normal operation are shown as Figures 5.1 and 5.2. During manufacturing, the antenna diodes which are clamps connected to ground discharge the accumulated charges on the long wires. The antenna diodes used in manufacturing are such that do not load circuit function. They are reverse bias diodes and behave like an open circuit with very little parallel capacitance added to input ports during normal operation resulting in the transmitted signals maintaining their integrity. We get the data of Antenna calculation of a cell in Extract step during abstraction.

Figure 5.1 Analogy of antenna problem during manufacturing [21].

Figure 5.2 Analogy of antenna problem during circuit normal operation[21].

### 5.2 Specific Requirements for Antenna Calculation

This section describes the technology file requirements for using the abstract generator for antenna calculation. In Open Access 2.0, the metal layer thickness rule and also default Antenna Rule for that metal layer need to be specified in the characterization rules section which is a subclass of the electrical rules class in the technology file to perform antenna calculation in the abstract generator. In the technology file on Open Access 2.2, the antenna rules have been moved to the antenna Models section of the foundry constraint group. You can specify a separate antenna Models group for each oxide type and can specify antenna Models for up to four oxide types. The constraint specifies the antenna ratios for one oxide type corresponding to a specific thickness of the gate oxide. You can specify the thickness value in the tech Layer Properties subsection in the layer Definitions section if a antenna side area calculation is to be performed.[17]

#### 5.3 Antenna Ratio Definition

The total gate area that is electrically connected to a node (and therefore connected to the process antennas) determines the amount of charge the electrically connected gates can withstand, and because the size of the process antennas connected to the node determines how much charge the antennas collect, it is useful to calculate the ratio of the size of the process antennas on a node to the size of the gate area that is electrically connected to the node. This ratio is called the antenna ratio of the corresponding metal. Greater the antenna ratio, greater is the potential for damage to the gate oxide. If you check a chip and obtain an antenna ratio greater than the threshold specified by the foundry, gate damage is likely to occur.[17]

### **5.4 Antenna Rule Checking**

Use layout verification tools to check antenna errors. The error reports should contain the following information:[18]

- 1. The violated position of the wire: The (x,y) position of which the antenna ratio of the wire exceeds the specified antenna ratio, e.g, 400 in our case.

- 2. Error flattened: Since the wire is connected to every module, it should not be hierarchical. Therefore, the errors should be flattened. Set the error flattened option if the tool is a hierarchical verification tool. If the verification tool is not hierarchical, you do not need to set this option.

- 3. Chip level: At the chip level, since each block's antenna problem is fixed, we only need to consider the interconnection among the blocks. Since the whole chip may be very large. If the chip is too big, chip-level antenna violations can be avoided by putting a protection diode on every input pin. This can be done very quickly, in general within few seconds to one minute. If the chip is not too big and run time is acceptable, then antenna violation checking and dynamic diode dropping and jumper insertion approaches can be used.

#### **5.5 Solutions for Antenna Problem**

The three solutions proposed to solve the antenna problem are described as follows: [19, 20]

1. **Router options**: Break signal wires and routes to upper levels. This reduces the charge amount for each net during manufacturing. This is called the "jumper approach."

- 2. **Embedded protection diode**: Add protection diodes on every input port for every standard cell. However these protection diodes consume the cell area resources and increase manufacturing costs. Even though the diodes are not necessary, these diodes are always embedded.

- 3. **Dynamic dropping diode after placement and route**: Fixing only the wire with the antenna violation which will not waste routing resources. During wafer manufacturing, all the inserted diodes are grounded. Since the input ports are high impedance, the charge on the wire flows through the insert diode instead of flowing into the device gate. One diode can be used to protect all input ports that are connected to the same output

**Table 5.1 Comparison of three Approaches [21].**

| Impact                | Jumper | Embedded<br>diode | Dynamic diode dropping |

|-----------------------|--------|-------------------|------------------------|

| Cell area             | No     | Yes               | No                     |

| Routability/chip size |        |                   |                        |

|                       | Yes    | Yes               | No                     |

| Completeness          | No     | No                | Yes                    |

| Timing                | Most   | More              | Least                  |

| Integration           | Yes    | Yes               | No                     |

From table 5.1 it can be observed that dynamic diode dropping has the following advantages:

1. Least timing degradation (better than embedded) within the application

- 2. Least waste of chip area.

- 3. Least impact on routability. The jumper only approach is unusable on very dense ICs For the LEON3 Cell library dynamic diode dropping was used.

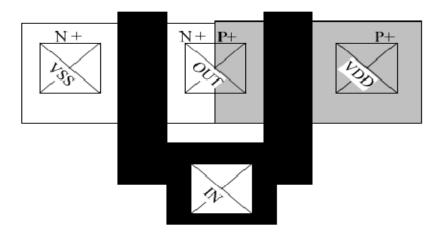

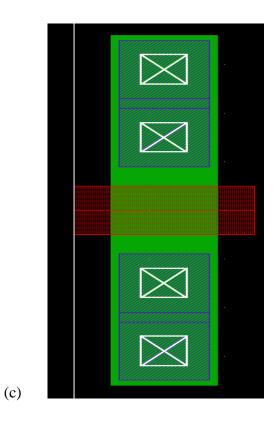

## 5.6 Description of the antenna diode used

Figure 5.3 shows the layout and the schematic of the antenna diode used. The RN Clamp is the diode which actually serve the main purpose of bleeding the charge the diode connected RN NMOS connected to it is there only to bypass the antenna error checking because if the gate of the clamp is directly connected to the ground rails which are long metal wires antenna error checking would generate antenna error for the antenna diode itself.

(a)

Figure 5.3 (a) Layout and (b) Schematic of Antenna diode cell.

## 5.7 Procedures for Fixing Antenna Violations.

The procedure for fixing antenna violations are illustrated below

- 1. We either drop the Antenna diode automatically as in encounter place and routing tool have a option where you can specify the antenna diode cell and then the router would automatically place and route the diode where ever its necessary.

- 2. Another way is as follow.[21]

- a. Bring up the tool for antenna fixing.

- b. Create the new library or open the existing library.

- c. Stream in GDSII file.

- d. Import the Diode from the GDSII format or create them from scratch.

- e. Open the top level cell.

- f. Drop the diodes without extension wires according to the rule files specified.

- g. Insert the jumper for the rest of the violation (if there is no space to drop a diode).

- h. Increase the extension wire to accommodate a bigger area.

- i. (Repeat Step .h until all the violations are cleaned.)

Save the design in a GDSII format.

## **CHAPTER 6**

## **CONCLUSION**

#### **6.1 Conclusion**

A 3.3V Digital standard Cell Library has been developed for LEON3 operable at 200°C temperature. For the library we used the SOI process as it has some advantage over the bulk. The dimension of IX NMOS is length 1µm and width 1.4µm and dimension of IX PMOS is length 0.6µm and width 1.6µm. Some other important dimensions of the cells like the height, the safety zone, the power rail width, the routing grid etc as given in table 3.1. In total we have 163 logical cells and 96 sequential cells. The cell have drive strength of 1X to 4X the inverter and buffer have drive strength of up to 15X and 24X respectively. The library has been characterized by using signal storm for timing and power. After characterizing the cells they were abstracted for use in place and route. The whole layout was validated by running DRC and LVS on the layout generated by the place and route tool. Finally we were able to place and route the LEON3 within a area of 6.5mm by 6.5mm

#### **6.2 Future Work**

In the library we can have some more cells as we do not have all the combination of AO (ANDOR) and AOI(ANDOR INVERTED). The antenna diode needs to be characterized

and also while doing place and route the antenna diode were not being dropped automatically in some places where it is needed so we need to go through the place and route tool to solve this problem.

## **REFERENCES**

- V.Madhuravasal, J.Wang, C.Hutchens, X.Zhu and Y.Zhang, "High Temperature Silicon-on-Insulator (SOI) Deep Submicron Device Performance," HITEC 2006 Conference, Santa Fe, New Mexico, May 2006.

- 2. Development of a 5V digital cell library For Use With The Peregrine Semiconductor Silicon on Sapphire (SOS) Process", by Usha Badam, Thesis, Oklahoma State University, 2007.

- 3. Michael John and Sebastian Smith, "Application-Specific Integrated Circuits", Addison-Wesley Publishing Company, VLSI Design Series, June 1997.

- 4. P. F. Lu et al., "Floating-Body Effects in Partially Depleted SOI CMOS Circuits," in IEEE Journal of Solid-State Circuits, Vol. 32, No. 8, August 1997, pp. 1241-1253.

- 5. P. McAdam and B.G. Goldberg, "CMOS SOS for Mixed Signal ICs," Peregrine Semiconductor Corporation, June 2001.

- 6. SOI VS CMOS for Analog Circuit Vivian Ma, 961347420, University of Toronto

- 7. J.M. Stern, P. A. Ivey, S. Davidson, and S. N. Walker, "Silicon-On-Insulator (SOI): A High Performance ASIC Technology," (1992).

- 8. R. Howes, W.Redman-White, "A Small-Signal Model for the Frequencydependent Drain Admittance in Floating Substrate MOSFETs", IEEE J. Sol. St. Ckts, 27(8), Aug 1992.

- 9. C. T. Chuang, "Design Challenges for High-Performance SOI Digital CMOS VLSI," in International Symposium on VLSI Technology, Systems, and Applications, 1999, pp. 270-273.

- J.-P. Colinge, "Silicon-On-Insulator Technology: Materials to VLSI," 2 ed.:

Kluwer Academic Publishers, 2000

- 11. "Proposal for a 3.3V/5V Low Leakage High Temperature Digital Cell Library Usign Stacked Transistors", by Singaravelan Vishwanathan, Oklahoma State University 2007.

- "Characterizing a Cell Library Using ICCS", Teri Hike McFaul Karl Perry, Intel Corporation, ASIC Seminar and Exhibit, Sep 1990 Proceedings Third Annual IEEE.

- CMOS VLSI Design, A Circuits and Sytems Perspective", by Neil .H.E.Weste and David Harris ,Third Edition

- 14. SignalStorm Characterization Manual

- 15. Design of 5V digital standard cells and I/O libraries for military standard temperature by Vibhore Jain, Thesis, Oklahoma State University, 2008.

- 16. "Automated Standard Cell Library Generation & study of Cell Library Functional Content", Yunbum Jung, University of Michigan

- 17. Abstract generator user guide

- Peter H. Chen et al, "VLSI Design Flow," National Semiconductor Corporation, Santa Clara, CA 95052, May, 1997.

- 19. Michael Santarini, "Tool Automatically Removes Antenna Violations," EE Times, Issue 1013, p. 88, June 22, 1998.

- 20. Changsheng Ying, "Techniques for Removing Antenna Rule Violations," Patent Pending, Stanza System, Inc., Cupertino, California, 95014.

- 21. "Fixing antenna problem by dynamic diode dropping and jumper insertion" PH

Chen, S Malkani, CM Peng, J Lin Proc. of ISQED, 2000

- 22. D. De Venutoa,\*, M.J. Ohletzb "Floating body effects model for fault simulation of fully depleted CMOS/SOI circuits", Microelectronics Journal 34 (2003) 889–895

- 23. Study of SOI Annular MOSFET by Swati Shah, Thesis, Oklahoma State University, 2009.

## APPENDIX A

# **Library Cells and Drive Strengths Specification**

## 1. Drive Strengths

• For inverters : 1X, 2X, 3X, 4X, 6X, 8X,9X,12X,15X

• For buffer: 1X, 2X, 3X, 4X, 6X, 8X,9X, 11X,12X,14X,15X,18X,20X,22X, 24X

• Three State Buffers: 1X, 2X, 3X, 4X.

2. For others: Four drive strengths: 1X, 2X, 3X and 4X.

3. Core Cell List

Table 1: List of core cells

| CELL<br>TYPE | CELL NAME | FUNCTION          |

|--------------|-----------|-------------------|

| Inverters    | Inv_X     | Y = not(A)        |

| Buffers      | buf_X     | Y = A             |

| NAND         | nand2_X   | Y = not(A.B)      |

| gates        | nand3_X   | Y = not (A.B.C)   |

|              | nand4_X   | Y = not (A.B.C.D) |

| NOR gates    | nor2_X    | Y = not(A+B)      |

|              | nor3_X    | Y = not (A+B+C)   |

|              | nor4_X    | Y = not (A+B+C+D) |

| CELL<br>TYPE | CELL NAME  | FUNCTION                                   |

|--------------|------------|--------------------------------------------|

| AND gates    | nor2_X     | Y = not (A+B)                              |

| _            | nor3_X     | Y = not (A+B+C)                            |

|              | nor4_X     | Y = not (A+B+C+D)                          |

| OR gates     | and2_X     | Y = A.B                                    |

| _            | and3_X     | Y = A.B.C                                  |

|              | and4_X     | Y = A.B.C.D                                |

| XOR gates    | xor_X      | $Y = A \oplus B$                           |

| XNOR gates   | xnor_X     | $Y = not(A \oplus B)$                      |

| AO gates     | ao21_X     | Y = (A0.A1) + B0                           |

| _            | ao22_X     | Y = (A0.A1) + (B0.B1)                      |

|              | ao32_X     | Y = (A0.A1.A2) + (B0.B1)                   |

|              | ao33_X     | Y=(A0.A1.A2)+(B0.B1.B2)                    |

|              | ao331_X    | Y=(A0.A1.A2)+(B0.B1.B2)+C0                 |

|              | ao322_X    | Y = A0.A1.A2)+(B0.B1)+(C0.C1)              |

|              | ao332_X    | Y = (A0.A1.A2)+(B0.B1.B2)+(C0.C1)          |

|              | ao333_X    | Y = (A0.A1.A2) + (B0.B1.B2) + (C0.C1.C2)   |

| OA gates     | oa21_X     | Y = (A0+A1).B0                             |

|              | oa22_X     | Y = (A0+A1).(B0+B1)                        |

|              | oa211_X    | Y = (A0+A1).B0.C0                          |

|              | oa221_X    | Y = (A0+A1).(B0+B1).C0                     |

|              | oa222_X    | Y = (A0+A1).(B0+B1).(C0+C1)                |

|              | oa31_X     | Y = (A0+A1+A2).B0                          |

|              | oa32_X     | Y = (A0+A1+A2).(B0+B1)                     |

|              | oa33_X     | Y = (A0+A1+A2).(B0+B1+B2)                  |

|              | oa311_X    | Y = (A0+A1+A2).B0.C0                       |

|              | oa321_X    | Y = (A0+A1+A2).(B0+B1).C0                  |

|              | oa331_X    | Y = (A0+A1+A2).(B0+B1+B2).C0               |

|              | oa322_X    | Y = (A0+A1+A2).(B0+B1).(C0+C1)             |

|              | oa332_X    | Y = (A0+A1+A2).(B0+B1+B2).(C0+C1)          |

|              | oa333_X    | Y = (A0+A1+A2).(B0+B1+B2).(C0+C1+C2)       |

| AOI gates    | aoi21_X    | Y = not((A0.A1) + B0)                      |

|              | aoi22_X    | Y = not((A0.A1) + (B0.B1))                 |

|              | ao31_X     | Y = (A0.A1.A2) + B0                        |

|              | ao32_X     | Y = (A0.A1.A2) + (B0.B1)                   |

|              | ao33_X Y = | Y=(A0.A1.A2)+(B0.B1.B2)                    |

|              | aoi331_X   | Y = not((A0.A1.A2)+(B0.B1.B2)+C0)          |

|              | aoi332_X   | Y = not((A0.A1.A2) + (B0.B1.B2) + (C0.C1)) |

|              | aoi333_X   | Y = not((A0.A1.A2)+(B0.B1.B2)+(C0.C1.C2))  |

| CELL<br>TYPE | CELL NAME  | FUNCTION                                   |

| OAI gates    | oai21_X    | Y = not((A0+A1).B0)                        |

|              | oai22_X      | Y = not((A0+A1).(B0+B1))                                                                                                  |  |

|--------------|--------------|---------------------------------------------------------------------------------------------------------------------------|--|

|              | oai211_X     | Y = not((A0+A1).(B0+B1))<br>Y = not((A0+A1).B0.C0)                                                                        |  |

|              | oai221_X     | Y = not((A0+A1).B0.C0)<br>Y = not((A0+A1).(B0+B1).C0)                                                                     |  |

|              | oai222_X     | Y = not((A0+A1).(B0+B1).(C0+C1))                                                                                          |  |

|              | oai31 X      | Y = not((A0+A1).(B0+B1).(C0+C1))<br>Y = not((A0+A1+A2).B0)                                                                |  |

|              |              | , ,                                                                                                                       |  |

|              | oai32_X      | Y = not((A0+A1+A2).(B0+B1)) $Y = not((A0+A1+A2).(B0+B1+B2))$ $Y = not((A0+A1+A2).B0.C0)$ $Y = not((A0+A1+A2).(B0+B1).C0)$ |  |

|              | oai33_X      |                                                                                                                           |  |

|              | oai311_X     |                                                                                                                           |  |

|              | oai321_X     |                                                                                                                           |  |

|              | oai331_X     | Y = not((A0+A1+A2).(B0+B1+B2).C0)                                                                                         |  |

|              | oai322_X     | Y = not((A0+A1+A2).(B0+B1).(C0+C1))                                                                                       |  |

|              | oai332_X     | Y = not(                                                                                                                  |  |

|              | :222 V       | (A0+A1+A2).(B0+B1+B2).(C0+C1))                                                                                            |  |

|              | oai333_X     | Y = not(                                                                                                                  |  |

| N/ 1/ 1      | 21 77        | (A0+A1+A2).(B0+B1+B2).(C0+C1+C2))                                                                                         |  |

| Multiplexers | mux21_X      | Multiplexer 2 to 1                                                                                                        |  |

|              | muxi21_X     | Multiplexer 2 to 1 with inverted output                                                                                   |  |

|              | muxi41_X     | Multiplexer 4 to 1Multiplexers                                                                                            |  |

|              | muxI41_X     | Multiplexer 4 to 1 with inverted output                                                                                   |  |

| Flip-Flops   | msdff_X      | D-type flip-flop with positive clock edge                                                                                 |  |

|              | msdffnr_X    | D-type flip-flop with positive clock edge and                                                                             |  |

|              |              | negative asynchronous reset                                                                                               |  |

|              | msdffns_X    | D-type flip-flop with positive clock edge and                                                                             |  |

|              | 122          | negative asynchronous set                                                                                                 |  |

|              | msdffnrns_X  | D-type flip-flop with positive clock edge and                                                                             |  |

|              |              | negative asynchronous reset and set                                                                                       |  |

|              | msdffn_X     | D-type flip-flop with negative clock edge                                                                                 |  |

|              | msdffnnr_X   | D-type flip-flop with negative clock edge and                                                                             |  |

|              |              | negative asynchronous reset                                                                                               |  |

|              | msdffnns_X   | D-type flip-flop with negative clock edge and                                                                             |  |

|              |              | negative asynchronous set                                                                                                 |  |

|              | msdffnnrns_X | D-type flip-flop with negative clock edge and                                                                             |  |

|              |              | negative asynchronous reset and set                                                                                       |  |

| Three State  | Tribuf_X     | Y = A.E; $Y = HiZ$ for not E                                                                                              |  |

| Buffers      |              |                                                                                                                           |  |

| Full adder   | Fulladd_X    | Full adder                                                                                                                |  |

| Half adder   | Halfadd_X    | Half adder                                                                                                                |  |