### MINICOMPUTER CONCEPTS

Вy

# BENEDICTO CACHO

#### Bachelor of Science

#### Southeastern Oklahoma State University

Durant, Oklahoma

1973

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE July, 1976

i i i

Thesis 1976 C119m Cop.2

2

•

# MINICOMPUTER CONCEPTS

Thesis Approved: ζ Thesis Adviser ama Maxwell mo Dean of Graduate College

#### PREFACE

This thesis presents a study of concepts used in the design of minicomputers currently on the market. The material is drawn from research on sixteen minicomputer systems.

I would like to thank my major adviser, Dr. Donald D. Fisher, for his advice, guidance, and encouragement, and other committee members, Dr. George E. Hedrick and Dr. James Van Doren, for their suggestions and assistance. Thanks are also due to my typist, Sherry Rodgers, for putting up with my illegible rough draft and the excessive number of figures, and to Dr. Bill Grimes and Dr. Doyle Bostic for prodding me on. Finally, I would like to thank members of my family for seeing me through it all.

# TABLE OF CONTENTS

| Chapte | er Page                                                                                                                        |

|--------|--------------------------------------------------------------------------------------------------------------------------------|

| Ι.     | INTRODUCTION                                                                                                                   |

|        | Objective                                                                                                                      |

| II.    | ELEMENTS OF MINICOMPUTER DESIGN                                                                                                |

|        | Introduction                                                                                                                   |

|        | Organization                                                                                                                   |

|        | The Memory                                                                                                                     |

|        | Device Controllers                                                                                                             |

| III.   | GENERAL SYSTEM DESIGNS                                                                                                         |

|        | Considerations                                                                                                                 |

|        | Fixed Purpose Register Design                                                                                                  |

|        | Microprogramming34Stack Structures37Bus Structures39Typical System Options41                                                   |

| IV.    | MINICOMPUTERS OF THE 70'S                                                                                                      |

|        | Introduction42Fixed Purpose Register Machines42                                                                                |

|        | Digital Equipment Corporation PDP 8/e42Cincinnati Milacron CIP/220045Computer Automation ALPHA LSI-250Texas Instruments 980B54 |

| Chap | ter                                                                      | Page           |

|------|--------------------------------------------------------------------------|----------------|

| IV.  | MINICOMPUTERS OF THE 70'S (Continued)                                    | 58             |

|      | Multi-accumulator Machines                                               | 58             |

|      | Digital Computer Controls D-116                                          | 58<br>58       |

|      | General Purpose Register Machines                                        | 68             |

|      | Digital Equipment Corporation PDP 11/40<br>Raytheon Data Systems RDS-500 | 68<br>72<br>78 |

|      | A Stack Machine The Microdata 32/S                                       | 85             |

|      | The 3200 Microprocessor                                                  | 86<br>86       |

| ۷.   | SUMMARY                                                                  | 100            |

| SELE | CTED BIBLIOGRAPHY                                                        | 104            |

| APPE | NDIX A - INSTRUCTION EXECUTION TIMES<br>(IN MICROSECONDS)                | 106            |

| APPE | NDIX B - APL DESCRIPTION OF EFFECTIVE<br>ADDRESS CALCULATING SCHEMES     | 109            |

| APPE | NDIX C - APL DESCRIPTION OF INTERRUPT<br>OPERATIONS                      | 117            |

|      |                                                                          |                |

# LIST OF TABLES

| Table |                                           | Page |

|-------|-------------------------------------------|------|

| Ι.    | 1974 Minicomputer Shipments               | 5    |

| II.   | PDP 8/e Functional Characteristics        | 43   |

| III.  | CIP/2200 Functional Characteristics       | 46   |

| IV.   | ALPHA LSI-2 Functional Characteristics    | 51   |

| ۷.    | TI 980B Functional Characteristics        | 57   |

| VI.   | D-116 Functional Characteristics          | 59   |

| VII.  | ECLIPSE S/200 Functional Characteristics  | 61   |

| VIII. | Memory Fault Codes                        | 64   |

| IX.   | PDP 11/40 Functional Characteristics      | 69   |

| Х.    | PDP 11/40 Addressing Modes                | 72   |

| XI.   | RDS-500 Functional Characteristics        | 74   |

| XII.  | Model 8/32 Functional Characteristics     | 80   |

| XIII. | Microdata 32/S Functional Characteristics | 88   |

| XIV.  | Addressing Modes and Effective Addresses  | 95   |

| XV.   | Summary of Minicomputer Characteristics   | 101  |

vi

## LIST OF FIGURES

| Figu | re                                                              | Page |

|------|-----------------------------------------------------------------|------|

| 1.   | Basic Computer Organization                                     | 7    |

| 2.   | Processor Organization                                          | 9    |

| 3.   | The Basic Processor Cycle                                       | 13   |

| 4.   | Machine Instructions                                            | 18   |

| 5.   | Processor Organization for Fixed Purpose<br>Register Machines   | 27   |

| 6.   | Program for a Fixed Purpose Register Type System                | 28   |

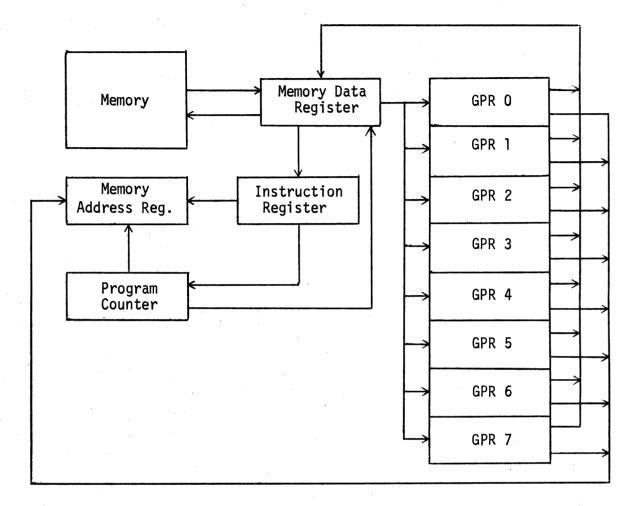

| 7.   | Processor Organization for General Purpose<br>Register Machines | 30   |

| 8.   | Programming a General Purpose Register Machine                  | 31   |

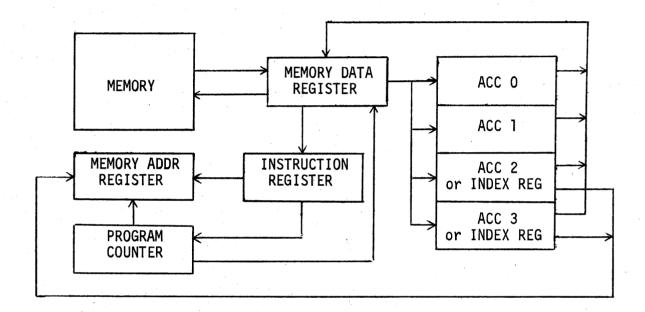

| 9.   | Processor Organization for Multi-accumulator Machines           | 32   |

| 10.  | Program For a Multi-accumulator System                          | 33   |

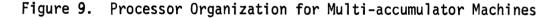

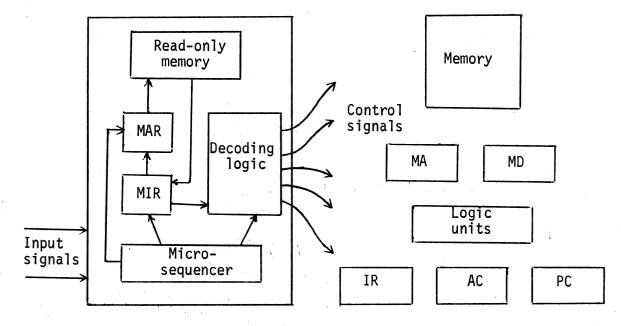

| 11.  | Two Types of Control Units                                      | 35   |

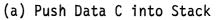

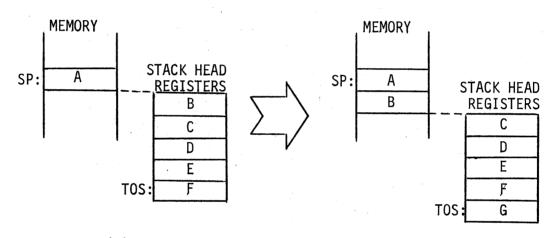

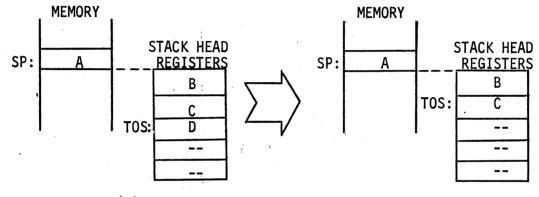

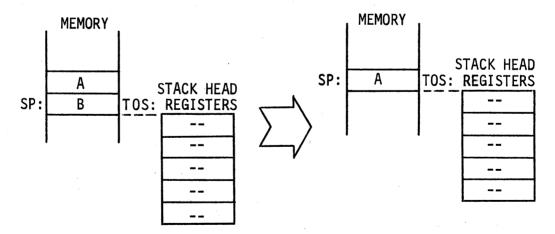

| 12.  | Stack Operations                                                | 38   |

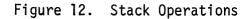

| 13.  | Stack Error Conditions                                          | 38   |

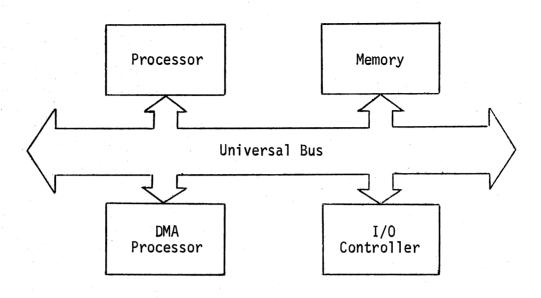

| 14.  | The Universal Bus                                               | 40   |

| 15.  | PDP 8/e Instruction Formats                                     | 44   |

| 16.  | CIP/2200 Simplified Instruction Formats                         | 47   |

| 17.  | Variable Length Data Formats                                    | 48   |

| 18.  | Decimal Data Representation                                     | 49   |

| 19.  | Memory Banking Example                                          | 55   |

| 20.  | D-116 Memory Reference Instruction Formats                      | 60   |

| Figure                                                          |           | Page |

|-----------------------------------------------------------------|-----------|------|

| 21. D-116 Arithmetic/Logic Instruction Format<br>(NL - No Load) | • • • • • | 60   |

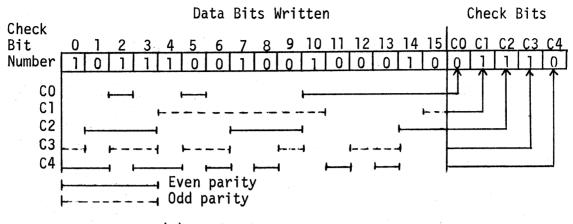

| 22. Error Checking and Correction Example                       | • • • • • | 63   |

| 23. Specify Address Accumulator Formats                         | • • • • • | 65   |

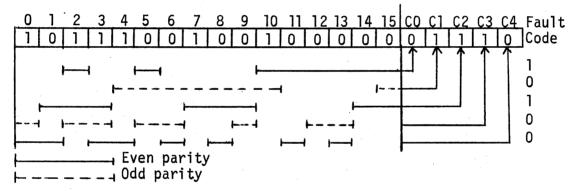

| 24. ECLIPSE S/200 Cache System                                  | • • • • • | 67   |

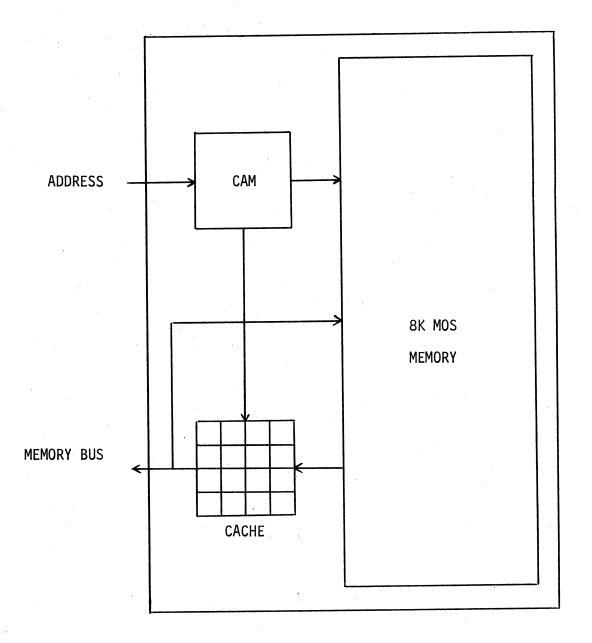

| 25. PDP 11/40 Instruction Formats                               |           | 71   |

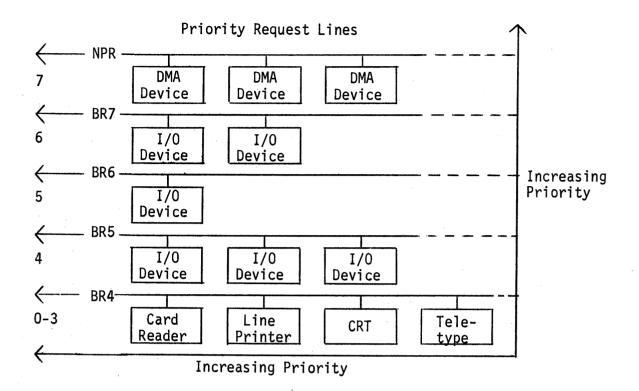

| 26. Automatic Priority Interrupt Structure                      |           | 73   |

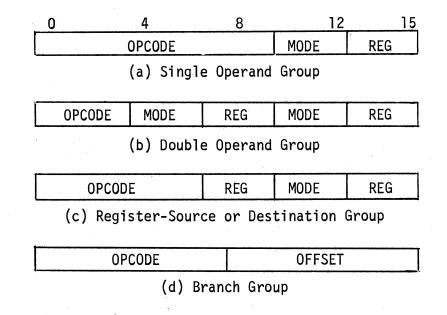

| 27. RDS-500 Instruction Formats                                 |           | 76   |

| 28. RDS-500 Dual Bus Architecture                               |           | 77   |

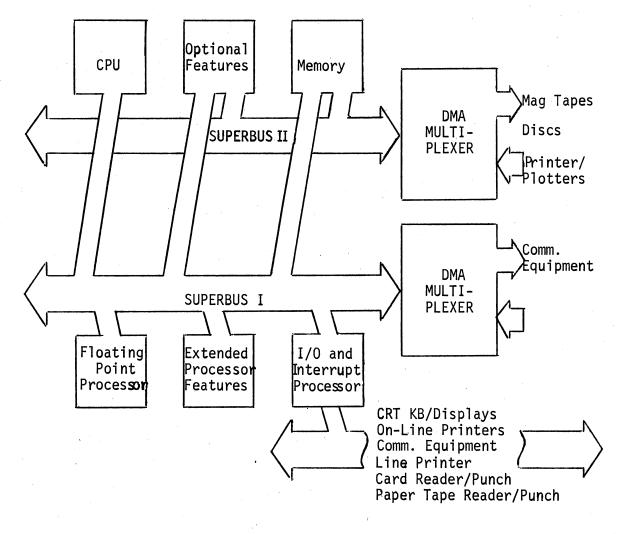

| 29. Model 8/32 Processor Block Diagram                          | •••••     | 79   |

| 30. Register Set Numbering                                      |           | 82   |

| 31. Model 8/32 Instruction Formats                              |           | 84   |

| 32. The 3200, 32/S, MPL Heirarchy                               |           | 85   |

| 33. 32/S System Configuration                                   | • • • • • | 87   |

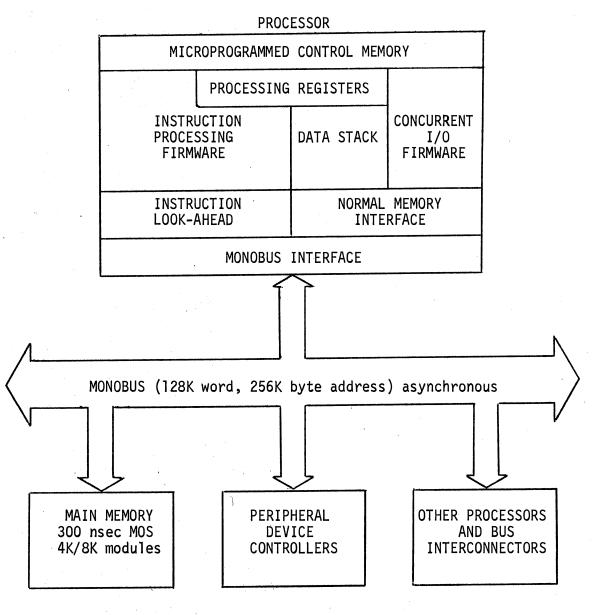

| 34. Monobus Organization                                        |           | 90   |

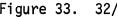

| 35. Push Stack Operation                                        | ••••      | 92   |

| 36. Pop Stack Operation                                         | • • • • • | 93   |

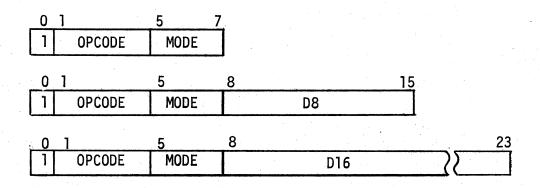

| 37. Memory Reference Instruction Formats                        | · · · · · | 95   |

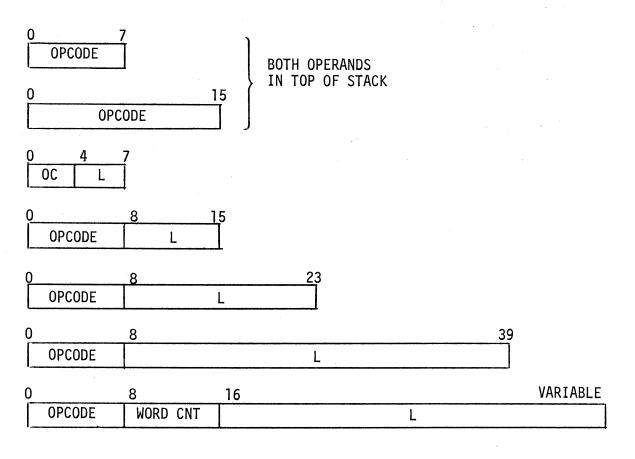

| 38. Stack Operate Instruction Formats                           |           | 97   |

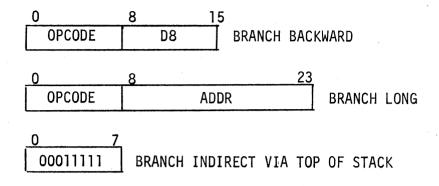

| 39. Branch Instruction Formats                                  | • • • • • | 98   |

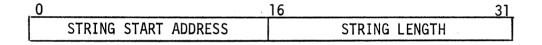

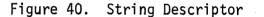

| 40. String Descriptor                                           |           | 99   |

ł

#### CHAPTER I

#### INTRODUCTION

#### **Objective**

In the past decade, the minicomputer industry was no doubt the fastest growing segment of the computer industry which to this day is the fastest growing industry in the world (30). Since the minicomputers first attracted the attention of end-users, much work has been done to optimize and expand the capabilities of these machines. Today they are powerful and versatile, and they cover a wide range of applications.

This paper presents a study of the concepts used in today's minicomputer designs. It is written from the viewpoint of a computer scientist with emphasis on logical organization. Details of circuit designs are not pursued. The basic elements of a minicomputer are described in Chapter II. Chapter III deals with the general system designs and some of the more important architecture found in today's minicomputers. Chapter IV focuses on what this author considers some of the more interesting systems being marketed. Chapter V contains a summary of the topics discussed, the future trends in the minicomputer industry, and the conclusions derived from this study. Appendix A contains a comparative chart of execution times of selected instructions for the minicomputers discussed in the text. Appendix B and Appendix C contain APL descriptions (8) of the effective address calculation

schemes and the interrupt systems for the same machines.

The basis for this paper comes from the 1974 survey of minicomputers by Hobbs and McLaughlin (7). Other surveys reviewed include the one by Butler (2) in 1970 and Theis and Hobbs (28) in 1969. Thompson's work (29) on developing a general minicomputer simulation system is very much related to the subject of this paper and is recommended for complementary reading.

#### History of Minicomputers

In 1963, at a time when the computer industry was just beginning to stabilize from its fast paced revolution, the first of a new breed of computers was delivered by Digital Equipment Corporation of Maynard, Massachusetts (9) (30). It was physically much smaller than the typical computer of the time and it had just the very basic processing capabilities. Its primary function was to control discrete and continuous processes. New as it was, the "minicomputer" was undoubtedly unimpressive, especially because the general trend then was to centralize and concentrate computing power in larger and larger machines. So the first delivery did not attract much attention, but it did, however, set into motion a movement which was to be termed "the minicomputer revolution" (15) (30).

The original equipment manufacturers (OEM's) were at the outset the almost exclusive market for the minicomputers. They did the job of installing the little machines into large application systems primarily for process control. Before long, however, keen end users began noticing the price/performance benefits that the minicomputers offered--benefits that were unavailable in the medium and large scale

computers. They began pointing to a wide variety of new applications suitable to the capabilities of the minicomputers. Such applications include:

- Instrumentation systems

- Automated test systems

- Data acquisition, monitor and control

- Communications control

- Transportation and distribution control

- Physical science monitoring, analysis, and control

- Medical science monitoring and analysis

By the end of 1965, an overwhelming interest in the new minicomputer industry was evident (28). In that year, over 1000 units were sold valued at approximately \$25 million. The growth rate became phenomenal. In 1968 sales including peripheral equipment neared the \$200 million mark. By 1972 over 35,000 units (54% of all computers installed in the country) had been sold and the industry had sustained a growth rate of over 30% per year (30). In 1975 alone world wide shipments were projected to reach \$1.24 billion which includes 55,400 units (14).

What accounted for such an explosion? What made the minicomputers so attractive? It certainly was not their processing capabilities, not alone, anyway. Well then, what was the characteristic that caught the eyes of the then medium and large scale computer users? It was none other than the "price/performance benefits", the relatively minimal cost of owning and operating a minicomputer system. That characteristic coupled with the fact that improvements in technology generally brought down prices was the primary catalyst in the dynamic nature of the mini-

computer industry. In March of 1969, a survey of minicomputers by Theis and Hobbs (28) included systems in the range of \$50,000 or less. In October of 1970, a survey by J. L. Butler (2) included systems costing \$25,000 or less. In July of 1974, a survey by Hobbs and McLaughlin (7) was limited to systems costing under \$10,000. So the cost of minicomputers were low to begin with, and as technology continued to improve, those low prices continued to decrease.

What is the current state of the minicomputer industry, that is, what now are the general characteristics of the minicomputers, what are their roles in today's society, and who are the manufacturers?

The minicomputers of today have very impressive processing capabilities. They are much more powerful and much more versatile than those of the strictly monitor and process control days. A key factor in the hardware improvements is the increased use of integrated circuits (10). In effect, because of the microscopic nature of integrated circuits, it is now possible to implement some of the sophisticated processes of large scale computers within the mainframe of a minicomputer. Inherent in today's minicomputers are three such sophistications:

• use of general registers

• microprogramming

interfacing through bus structures

As for the current roles of minicomputers, the applications mentioned earlier still make up close to 84% of the total number of applications. Of the remaining 16%, 9% consist of the more recent implementations in business functions, 4% in education, and 2% in the wide range of other applications (7) (10) (14). In the light of

today's advances, predictions state that there will be more new applications as well as continued size and cost reductions and performance improvements.

As mentioned earlier, the nature of the minicomputer industry is dynamic. This characteristic is evident when the history of minicomputer manufacturers is examined. Hobbs and McLaughlin (7) cite some of the recent trends in their 1974 survey. In light of that article, it is safe to say that today there are well over 20 manufacturers. Table I shows Modern Data's (14) 1975 rating of the top nine.

#### TABLE I

# 1974 MINICOMPUTER SHIPMENTS

| MANUFACTURERS             | UNITS SHIPPED | DOLLAR VALUE | CUSTOMER SITES |

|---------------------------|---------------|--------------|----------------|

| Digital Equipment Corp    | 28%           | 33%          | 35%            |

| Data General              | 20%           | 13%          | 16%            |

| Hewlett Packard           | 11%           | 10%          | 12%            |

| Texas Instruments         | 5%            | 5%           | 6%             |

| General Automation        | 6%            | 5%           | 3%             |

| Varian Data               | 2%            | 5%           | 4%             |

| Digital Computer Controls | 3%            | 5%           | 2%             |

| Interdata                 | 6%            | 3%           | 2%             |

| Modular Computer Systems  | 2%            | 3%           | 3%             |

|                           |               |              |                |

#### CHAPTER II

#### ELEMENTS OF MINICOMPUTER DESIGN

#### Introduction

Around 1830, an eccentric English mathematician named Charles Babbage, concerned with improving methods of computing mathematical tables, set forth the description of a machine which he called the Analytical Engine (6). In that description, the five most important features included the following:

- 1. It has an <u>input</u> medium, by means of which an unlimited number of operands and instructions may be entered.

- 2. It has a <u>memory</u>, where the operands and instructions may be stored and later retrieved.

- 3. It has a <u>calculating</u> unit capable of performing arithmetic and logical operations on the operands stored in the memory.

- 4. It has an <u>output</u> medium, by means of which the results of the calculations are returned to the user.

- 5. It has a <u>decision</u> capability, by means of which alternate courses of action may be taken depending on computed results.

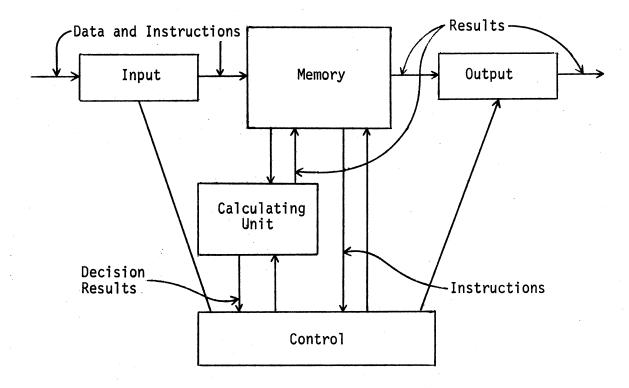

Today, a computer system is described in terms of the five features listed above. Its basic organization is illustrated in Figure 1. One other feature added in 1947 by John Von Neuman of Princeton is the stored program concept in which the calculating unit does not recognize the difference between operands and instructions since both are stored in the same form, in the same memory.

Figure 1. Basic Computer Organization

Minicomputers have the general features described above. When contrasted with medium and large scale computers, their distinguishing characteristics are:

- small physical size

- small word length

- small cost

Most minicomputers fit in a 19 x 11 x 21 inch mainframe. Their word lengths range from 8 to 24 bits with most systems using 16 bits. The cost of a basic system configuration including a processor, 4096 words of memory, and a teletype generally does not exceed \$10,000 (10) (26). Although they have evolved into versatile units and have acquired some large scale computer features, it is at present inconceivable that a

minicomputer system can actually replace a large scale computer system. There is still a big gap between the processing capabilities of the two classes of computers.

The description of the basic elements in a minicomputer system follow. The main topics correspond with the three major components:

the processor

• the memory

• the input/output controllers

#### The Processor

The processor of a system is concerned with the major operations of a computer. It may be likened to the foreman in a group of workers who tells everyone what to do and when to do it. Thus all computer operations are initiated by the processor and when each operation is completed, the processor is notified.

#### Organization

The processor contains four basic elements:

• a set of registers

• an arithmetic/logic unit

• bus connections

• a control unit

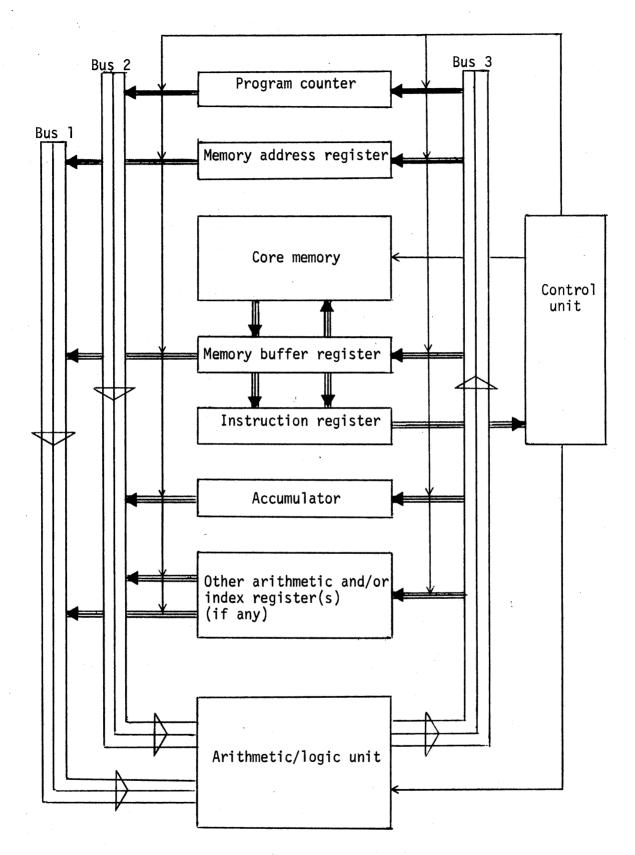

Figure 2 shows one way these elements may be organized.

Figure 2. Processor Organization

<u>The Register Set</u>. Processor registers are fast memory units used by the processor. Physically each register consist of a set of "flip flops", memory devices each capable of storing one bit (binary digit) of information. The number of bits that a register can store depends on the word length of the system.

The functions of each register vary. In general some are used strictly by the processor while others are accessible to the user. Those used in today's minicomputers are described below (6) (9):

- 1. The program counter contains the address of the next instruction to be processed.

- 2. The <u>instruction register</u> contains the instruction currently being processed.

- 3. The <u>memory address register</u> contains the address of the memory location accessed or to be accessed.

- 4. The <u>memory data register</u> contains the operand or instruction to be stored into or just retrieved from the memory.

- 5. The <u>status register</u> or individual status indicators contain current status information about the processor.

- 6. The <u>accumulator</u> stores operands and results of arithmetic/ logic operations.

- 7. The <u>accumulator extension</u> serves as an extended part of the accumulator for operations requiring more than the usual number of bits.

- 8. The index register is used in operand addressing.

- 9. The pointer register contains the address of an operand.

- 10. The <u>stack pointer</u> contains the address of "stacked" operands or results.

- 11. The <u>general purpose register</u> may serve any one of the above functions.

The Arithmetic/Logic Unit. The arithmetic/logic unit performs

all calculations required by user programs. The unit consists of logic circuits capable of performing operations such as the following:

• add the contents of two registers

logically "and" the contents of two registers

• complement the contents of a register

• shift or rotate the contents of a register

increment or decrement the contents of a register

<u>Bus Connections</u>. Data paths between the arithmetic/logic unit and the registers are simplified by the use of data buses. In Figure 2 note the use of three data buses. Buses 1 and 2 are input buses from the registers to the arithmetic/logic unit. Bus 3 is an output bus from the arithmetic/logic unit to the registers.

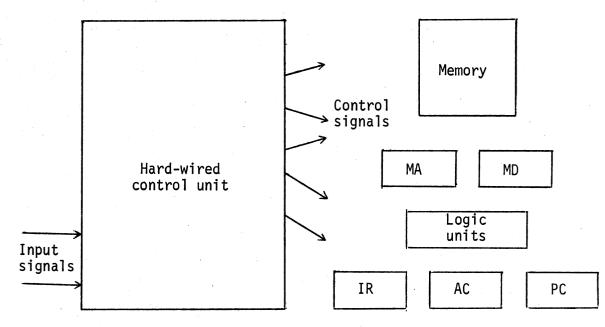

<u>Control Unit</u>. The control unit coordinates all the actions of a computer by generating pulses to effect logical sequences. Control units may be hardwired or microprogrammed. In the hardwired version, the logic sequences are built into the logic circuits of the control unit. Thus the sequences are fixed and unalterable. The microprogrammed version consists of a microsequencer and a control memory which is separate from the main memory. The microsequencer is a control unit in itself but its operations are much more basic. It operates on microprograms stored in the control memory. The control sequences are thus defined by microprograms. By changing the contents of the control memory or by replacing the control memory with another control memory containing different microprograms, the control sequence is changed. The ability to be altered makes microprogrammed processors more adaptable to specific user needs. See Chapter III for a more detailed discussion of microprogramming.

#### Operations

The Basic Cycle. Processor operations involve a basic cycle of:

1. fetching an instruction from main memory

2. decoding the instruction

3. executing the instruction

Each of these operations are initiated and controlled by timed pulses generated by the control unit.

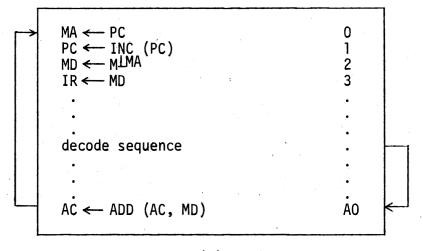

The first control pulse begins the instruction fetch by transferring the contents of the program counter (PC) into the memory address register (MA). Thus both registers contain the address of the next instruction to be processed. The next pulse gates the contents of PC through the arithmetic/logic unit (ALU) to be incremented and returned to the PC. The PC now contains the address of the next sequential instruction. The next control pulse is a read from memory. The contents of the location addressed by MA is transferred into the memory data register (MD). So MD contains the instruction which must be passed into the instruction register (IR) for the decoding operations. That transfer is effected by the next control pulse completing the instruction fetch cycle.

The decode stage of the cycle feeds the contents of IR into a set of decode logic circuits which performs a logic branch to the appropriate logic sequence. This logic sequence is associated with the machine instruction code in IR.

Suppose the machine instruction is an add operation. In the basic minicomputer one operand is assumed to be in the accumulator (AC). The second operand is taken from the memory location specified by the addressing portion of the instruction word. Once the second operand is

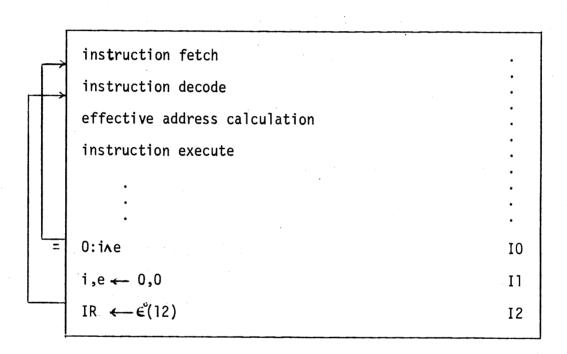

fetched and placed into MD, control pulses gate the contents of AC and MD into the adder unit of the ALU where the sum is generated and then returned into AC. Thus the execute phase of the basic cycle is completed. The control sequence returns to the beginning where the next instruction is fetched, decoded, and executed. An APL (8) description of the process described above is shown in Figure 3a. The symbols used in the description are defined in Figure 3b.

(a)

|     | Legend                  |

|-----|-------------------------|

| PC  | program counter         |

| MA  | memory address register |

| Μ   | memory                  |

| MD  | memory data register    |

| IR  | instruction register    |

| ADD | ALU add function        |

| INC | ALU increment function  |

(b)

Figure 3. The Basic Processor Cycle

<u>Interrupts</u>. During the basic cycle, conditions requiring the attention of the processor may arise. An overflow in the result of a calculation, machine failure, an input/output device (initiated earlier) ready for the processor to activate a data transfer are examples of such conditions. The processor must be "interrupted" from its normal sequence of operation to take appropriate actions in returning the system to its normal state.

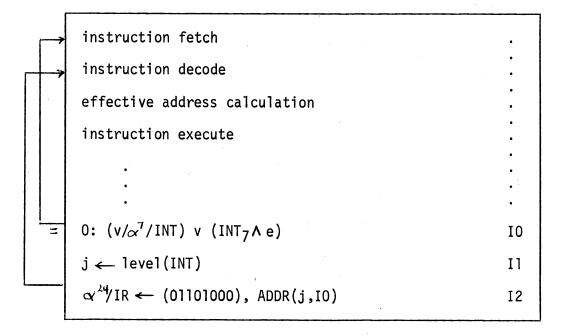

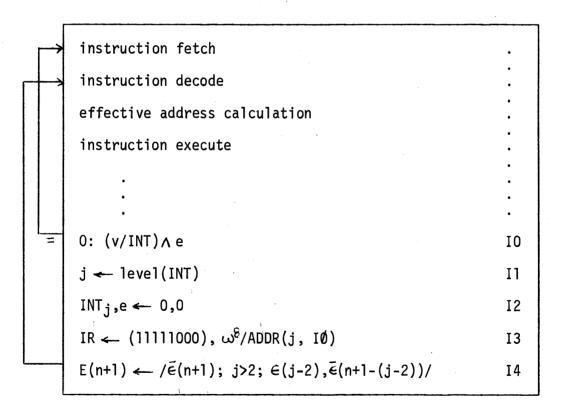

An interrupt is either internal or external. Internal interrupts are caused by various types of error conditions, such as arithmetic overflow, or invalid memory address. External interrupts are requests for attention from either the conventional I/O devices or external devices related to real time systems such as process control or lab experimentation.

Interrupts are monitored by the processor usually after the execute phase of the basic cycle. If an interrupt is required, the interrupting element must set an interrupt request indicator sometime during the current processing cycle. Upon recognition of the interrupt, the processor initiates an interrupt procedure by saving the "environment" of the program being interrupted. The environment of a program consists of the current contents of the registers and the status indicators. At the completion of the interrupt procedure, the environment of the interrupted program is restored and the processor continues with that program's execution.

Two general methods of processing interrupts are used in minicomputers. One of the methods uses one interrupt request line for all possible interrupts. When an interrupt is requested, the processor transfers to a general interrupt processing sequence where it must

determine which element caused the interrupt. Once that is resolved, the processor transfers to an interrupt sequence that services the element that caused the interrupt.

The second method allows each interrupting element an interrupt ("vectored") address. Whenever an interrupt is granted by the processor, the next instruction executed is taken from the address associated with the interrupt. The instruction is often a branch to the appropriate service routine. This method of processing interrupts is faster and more efficient than the first method.

What happens when more than one interrupt occurs within a cycle? Some type of a priority system must be established. Internal interrupts are usually given higher priority over external interrupts. Among the external interrupts, real time devices with fast response requirements are usually given top priority. Then depending on physical location and speed, each I/O device is given its unique priority.

Priority schemes may be programmed or hardwired (built-in). One implementation of the hardwired version requires two interrupt lines for I/O processing (21). One line is used by the devices to request interrupts. The other is used by the processor to grant interrupt requests. The priority is determined by the order in which the grant signal is propagated through all the devices. The device connected closest to the processor on the grant line thus has the highest priority. If two devices request an interrupt simultaneously, the device with the higher priority receives the grant signal first thereby not allowing the grant signal to reach the second device.

<u>Effective Address Calculations</u>. Instructions involving an operand fetch from memory must deal with the minicomputer's inherent problem

of the short word length (10). The problem lies in trying to code both the machine instruction and the operand address in one instruction word. In a system with 16 bit words, if 3 bits are used for the instruction code, then 13 bits are left for addressing the operand. With 13 bits, 8192 words (or bytes) is the maximum number of locations that are directly addressable. For some applications a minicomputer system with 8192 words of memory is sufficient. Yet, there are many more applications where 8K of memory is simply too small. And for some of those applications, 3 bits is often not enough to code all the necessary machine instructions.

To circumvent the problem, minicomputer designers devised a variety of addressing schemes. One scheme divides the memory into "pages". The size of a page depends on the number of bits used for the address part of an instruction word. For example, if the address is 8 bits long, then the page size is  $2^8$  or 256 words. If the memory size is say 16K words, then there are 64 pages of memory numbered from 0 to 63. With such a scheme, at least four modes of addressing are possible:

- 1. <u>Direct Page-0</u>. The effective address is taken to be the address specified in the instruction.

- <u>Direct Current Page</u>. Enough high order bits of the program counter are concatenated with the address in the instruction to form the effective address.

- 3. <u>Relative to the Program Counter</u>. The address in the instruction is treated as a signed value and added to the current value of the program counter.

- 4. <u>Direct with a Page Register</u>. A separate register provides the high order bits in the calculation of the effective address.

The key point in the schemes described is the forming of a 16 bit effective address which allows access to 64K of memory.

There are many other addressing schemes used in minicomputers. Some of the more common ones are described below:

- <u>Indirect Addressing</u>. The address specified in the instruction contains the effective address. Some systems have "multi-level" indirection where usually the most significant bit of an indirect address is tested. If it is set then the address points another indirect address, otherwise it points to the operand.

- 2. <u>Indexing</u>. The effective address is the sum of the address in the instruction and the contents of an index register.

- 3. <u>Extended Addressing</u>. The effective address is found in the location immediately following the instruction location.

- 4. <u>Immediate Addressing</u>. The operand is either in the instruction itself or in the word following the instruction.

In many systems, addressing schemes are combined. Terms such as <u>preindexing</u> or <u>postindexing</u> refer to the combination of index and indirect addressing. In preindexing, the indexing operation is performed, then the indirection is considered. It is vice versa for postindexing.

<u>Machine Instructions</u>. Machine instructions define the programmable operations of a computer. From one computer to another, the instruction sets usually differ according to their application. Generally, machine instructions are divided into three classes:

- 1. memory reference

- 2. register operate

- 3. input/output

These classes of instruction are discussed in the following paragraphs.

Memory reference instructions require some type of a memory access, either for fetching an operand or for transferring control. For minicomputers, instructions of this class usually include those listed in Figure 4a.

Register operate instructions deal mainly with the processor registers and the status indicators. There is no reference to the memory. The entire instruction word can thus be used to specify one or more register operations. Figure 4b lists the typical register operations.

Input/output (I/O) instructions deal with the transfer of data and device status information between the processor and the I/O devices. Three types of information, control, address, and data, may transferred. Control information are signals that initiates and/or terminates I/O operations. Address information refers to areas in the memory in which data is transferred in or out. The data, of course,

| INSTRUCTION   | ACTION                                                                                                                                      |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| ADD           | Add the contents of a register and a memory location, place the results in the register.                                                    |

| AND           | Logically AND the contents of a register and a memory location, place the results in the register.                                          |

| ISZ           | Increment the contents of a memory location and skip<br>the next instruction if the result is zero.                                         |

| JUMP          | Branch to a memory location and resume execution of the program.                                                                            |

| JSUB          | Store the address of the next instruction into a memory location and resume execution of the program at the location immediately following. |

| LOAD<br>STORE | Load a register with the contents of a memory location.<br>Store the contents of a register in a memory location.                           |

(a) Memory Reference Instructions

Figure 4. Machine Instructions

| INSTRUCTION | ACTION                                                                            |

|-------------|-----------------------------------------------------------------------------------|

| CLEAR       | Reset each bit in a register to zero.                                             |

| COMP        | Complement each bit in a register.                                                |

| EXCH        | Exchange the contents of two registers.                                           |

| INC         | Increment the contents of a register.                                             |

| ROTATE      | Rotate the contents of a register one bit left or right.                          |

| SET         | Set each bit in a register to one.                                                |

| SKIP        | Skip the next instruction (conditional - the contents of a register is examined). |

| SHIFT       | Shift the contents of a register one or more bits.                                |

(b) Register Operate Instructions

| INSTRUCTION | ACTION                                                         |

|-------------|----------------------------------------------------------------|

| DMAIN       | Initialize a DMA input block operation.                        |

| DMAOUT      | Initialize a DMA output block operation.                       |

| INBLK       | Initialize a concurrent input block operation.                 |

| INPUT       | Input a word from a device to a register or a memory location. |

| OUTBLK      | Initialize a concurrent output block operation.                |

| OUTPUT      | Output a word from the memory or a register to a device.       |

| SELECT      | Transmit a specified function code to a device.                |

| SENSE       | Test the status of a device.                                   |

(c) Input/Output Instructions

Figure 4. (Continued)

is the information being transferred between registers or memory locations and the I/O devices. Typical I/O instructions are listed in Figure 4c.

#### The Memory

The memory of a computer performs the vital function of storing data, instruction sequences, and intermediate results of computations. Minicomputer memories generally range from 1024 to 32,768 words. Their speeds are in terms of cycle time, which is the time required to select and write data into a memory location. The cycle times vary from 250 to 2000 nanosecond (billionth of a second). The common practice is to manufacture memories in modules of 1024, 2048, 4096, or 8192 words. Thus users can start with the bare minimum and as needed for system expansions separate modules are purchased and installed (7) (10).

Two types of memories are most common: magnetic core, and semiconductor. Core memories are the slower of the two types but they have the distinct advantage of being non-volatile, which means their contents are not lost when the power supply is shut off. This characteristic coupled with the fact that core memories have, until recently, been generally cheaper, has made them the primary type of memory used today. However, with vast improvements in large scale integrations (LSI) drastically reducing their cost, semiconductor memories are now considered to be serious competition for the core memories (6) (10).

Minicomputers continue to improve. In memory design, special features such as those listed below are becoming more common.

- 1. Parity logic is used for error detection and correction.

- 2. Memory protect logic is used for maintaining the integrity of a system.

- 3. Scratchpad or cache memories are being used as fast (50 to 100 nsec) intermediate storage (14).

- 4. Memory modules are interleaved allowing overlapped memory access (15).

- 5. Memory banking techniques allow the use of up to 256K of memory (15).

#### Input/Output Elements

Computers must have a way of communicating with their users. This is done through the input/output elements which include peripheral devices such as card readers, line printers, tape drives, and teletype Keyboard/printers. The devices, however, cannot communicate directly with the processor. Interfacing elements must be provided to bridge the gap between the processor and the peripheral devices. These elements are called device controllers.

#### Device Controllers

Device controllers vary according to the type of peripheral devices they control. One type is used for serving devices that transfer data serially such as a teletype keyboard/printer or a cathode ray tube (CRT) keyboard/display. These are slow devices with transfer rates not exceeding 30 characters per second. Another type may be used to service a card reader with transfer rates up to 200 (80 column) cards per minute. Another type might service a line printer with a transfer rate of over 1000 (132 column) lines per minute. Then there are those that service high speed devices such as magnetic tape and disc drives. Controllers for these high speed devices often bypass the processor using the direct memory access (DMA) technique. Generally a device controller is made up of two decoders. One decodes input from device selection lines. When an I/O operation is required the processor must send a device code through the device selection lines. All devices have access to these lines and each shall compare the signals with its unique device code. The device whose code matches those of the device selection lines then responds according to the function specified. The function is sent by the processor. It is decoded by a function decoder which activates the specified I/O operation - input/output of device status or input/ output of data.

#### I/O Operations

- I/O operations involve some or all of the following steps (6):

- 1. Check to see if device is available.

- 2. When device becomes available, activate.

- 3. Transfer data.

- 4. Deactivate.

The first step can be accomplished in two ways. The first method involves a program loop where the status information of an unavailable device is checked and rechecked until the device becomes available. This method is very inefficient primarily because of the processor hold up. The second method uses the interrupt facility. The processor can request an I/O device to enter an interrupt request as soon as it becomes available. While waiting for the interrupt request, the processor is free to do some other computations.

The second step (activation) may not be necessary for some devices. Teletypewriters and CRT's are usually ready to go as soon as

they become available. But for units such as a tape drive special activation processes must be performed.

The third step (transfer of data) can be accomplished using one of three methods:

• programmed

buffered or concurrent

direct memory access

Programmed data transfers make use of an interrupt procedure for each word transferred. This method is time consuming since every word transferred requires storage and restoration of the interrupted program. Buffered or concurrent data transfers usually involve a block of words and require extra hardware or microprogrammed logic. Once initiated by a special instruction, it interrupts the processes when it is ready for a transfer. It reads a buffer address and a word count from memory, determines the current address for the transfer, transfers the word in or out of memory, updates the word count, checks to see if the buffer is filled, and then returns to the interrupted program. In this method, the interrupted program need not be stored and restored, thus saving valuable processor time. The ultimate time saver, however, involves the use of the third method, direct memory access. In its implementation a separate processor is installed. The DMA processor consist of enough logic and registers to make data transfers in and out of the memory without having to go through the main processor. Like the buffered data transfer DMA transfers also usually involve a block of data words. Once initiated, the DMA processor "steals" a memory cycle from the processor each time it becomes ready to transfer a word. The main processor is not interrupted but "delayed" one memory cycle. When all I/O transfers are completed, the device is deactivated.

#### CHAPTER III

#### GENERAL SYSTEM DESIGNS

#### Considerations

The design of any computer system is influenced by the applications it is intended to cover. The systems of interest in this paper are the low cost general purpose minicomputers that are useable in the applications mentioned in Chapter I. Considerations involved in designing such systems include the following:

- 1. The system must be flexible. It must have the capability to assume a wide variety of configurations dictated specifically by the applications.

- The system must be expandable. Structures for expanding the memory and the I/O capabilities must be implemented in the system design.

- Designs involving the programmability of the system must be directed at achieving maximum effectiveness with minimum programming effort.

- 4. If possible, designs for a new system should also be directed at making the system compatible with earlier models. The software developed for the earlier models can thus be executable in the new system.

#### General Processor Designs

Processor operations generally involve information transfers to, from, and among the processor registers. The organization of the processor registers thus dictates the types of instructions that are to be included in a system's instruction set. In minicomputer systems, there are three general processor designs. The three designs are correlated to the type of programmable registers used. These three

types are fixed purpose registers, multi-accumulators, and general purpose registers. Systems with fixed purpose registers make use of single operand address instructions. Those with multi-accumulators use double register operands. Systems with general purpose registers also use double operands, but the operands do not have to represent contents of registers.

#### Fixed Purpose Register Design

Minicomputers employing fixed purpose registers represent the basic, less sophisticated systems found in dedicated applications such as industrial process control, communications, and peripheral processing for larger computers. Systems belonging to this class of minicomputers include:

- Cincinnati Milacron CIP/2200

- Computer Automation ALPHA LSI-2

- Digital Equipment Corporation PDP 8/e

- Texas Instruments 980B

- Varian Data Machines VARIAN 520/i

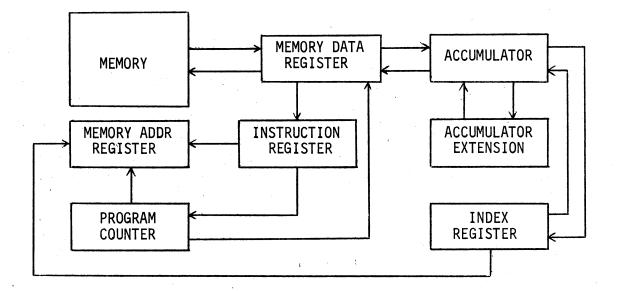

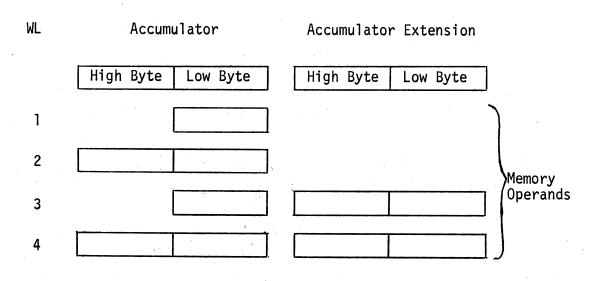

Figure 5 is a simplified block diagram of the processor organization for this class of minicomputers. As shown, the programmable register set includes an accumulator, an accumulator extension, and an index register. Some systems, however, may not have all three registers. The PDP 8/e, for example, does not have an index register. The ALPHA LSI-2 does not have an accumulator extension. Then there are systems that have all three of those registers plus some others. The TI 980B has, in addition, a base register and a subroutine linkage register.

Fixed purpose register systems are often referred to as single address machines. The implication comes from the use of one operand in each of the memory reference instructions. Figure 6 shows how such instructions are used in summing an array of values. The first instruction clears both the accumulator and the index register. The second instruction begins the summing loop. It instructs the system to add into the accumulator the contents of the memory location specified by the sum of the index register and the address value associated with ARRAY. The first time through the loop, the index register is zero, so the value added into the accumulator is 10. The next instruction increments the contents of the index register. Thus the next value to be added into the accumulator is taken from the address ARRAY + 1 which contains the value 25. The ISZ instruction increments the contents of COUNT from -4 to -3. Since COUNT is not zero the next instruction (JMP)

| M     | nemon | ic | Code     | Meaning                                                  |

|-------|-------|----|----------|----------------------------------------------------------|

|       | OPR   |    | CLA, DTX | Clear the accumulator and deposit to the index register. |

| LOOP  | ADD   | X  | ARRAY    | Add a memory value into the accumulator.                 |

|       | OPR   |    | INX      | Increment the contents of the index register.            |

|       | ISZ   |    | COUNT    | Increment memory value and skip if the result is zero.   |

|       | JMP   |    | LOOP     | Branch back to process the next value.                   |

|       | OPR   |    | HALT     | Terminate execution.                                     |

| COUNT | DC    |    | -4       | Define constants.                                        |

| ARRAY | DC    |    | 10       |                                                          |

|       | DC    |    | 25       |                                                          |

|       | DC    |    | 13       |                                                          |

|       | DC    |    | 75       |                                                          |

| SUM   | DS    |    |          | Define storage.                                          |

|       | END   |    |          |                                                          |

Figure 6. Program for a Fixed Purpose Register Type System

returns control to the instruction labeled LOOP. The value of 25 is taken from memory and added into the accumulator to form the new accumulator contents of 35. The process of incrementing the index register and the negative counter is repeated. Since the counter contains a -2, the third value 13 is added into the accumulator making the sum 48. The program loops back for the last time to add the fourth value 75. When the ISZ instruction is executed this time the counter becomes zero, thus the JMP instruction is skipped. The STO instruction stores the contents of the accumulator into the memory location associated with SUM. The OPR HALT instruction terminates the execution of the program.

#### General Purpose Register Design

If the systems with the fixed purpose register design represent one end of the spectrum of minicomputers, then the other end is represented by the systems with the general purpose register design. Minicomputers in this class are geared for applications involving complex operations such as multi-tasking. For example, one of these systems may be used to automate industrial processes, monitoring and controlling multiple operations in real-time while simultaneously preparing and printing production reports for management. The following are a few of the minicomputers belonging to this class of computers:

• Digital Equipment Corporation PDP 11/40

General Automation SPC-16

• Interdata Model 8/32

Lockheed SUE

Modular Computer Systems MØDCØMP II

Raytheon Data Systems RDS-500

Texas Instruments 960B

The processor organization of a system with a general purpose register design is shown in Figure 7. The programmable register set consists of eight general purpose registers numbered 0 to 7. Each of those registers can function as accumulators, accumulator extensions,

index registers, and operand pointers.

The programming example in Figure 8 illustrates how the general purpose registers are used. Like the program in Figure 6, it sums an array of values. Note the use of double operand instructions in which the operations are considered to be register-to-register or registerto-memory.

|      | Mnemo | nic Code    | Meaning                                                                                                         |

|------|-------|-------------|-----------------------------------------------------------------------------------------------------------------|

|      | SR    | 2,2         | clear register 2                                                                                                |

|      | LR    | 3, 2        | clear register 3                                                                                                |

| LOOP | ADD   | 2, ARRAY(3) | add into register 2 the value in the<br>location specified by the sum of<br>register 3 and the address of ARRAY |

|      | INC   | 3           | increment register 3                                                                                            |

|      | COM   | 3, COUNT    | compare the contents of register 3 and location COUNT                                                           |

| •    | BLT   | LOOP        | branch to loop if register is less than the memory value                                                        |

|      | ST0   | 2, SUM      | store the accumulated sum into the location SUM                                                                 |

|      | HALT  |             | terminate execution                                                                                             |

Figure 8. Programming a General Purpose Register Machine

# Multi-accumulator Design

The multi-accumulator design is a combination of the previous two designs. Operations in systems with this design are generally centered around four accumulators, two of which can be used as index registers. Systems implementing this design include:

- · Data General NOVA Computer

- Data General ECLIPSE Computer

- Digital Computer Controls D-116

The organization of a system with a multi-accumulator design is shown in Figure 9. Of the four programmable registers, the first two are used strictly as accumulators, the other two are used as accumulators or index registers.

The multi-accumulator design is an attempt at implementing a general purpose register design with the use of a minimum number of registers. In this design, there are only five memory reference instructions and these five do not include arithmetic/logic operations. The five instructions are:

• load

store

jump

# jump subroutine

٠

increment and skip if zero

All arithmetic/logic instructions are one cycle register-to-register instructions (they do not address memory). The extra instruction word bits can be used for other functions such as specifying a rotate of the resulting register and/or a conditional skip of the next instruction.

|      | Menmo | nic Code    | Meaning                                                                                                 |

|------|-------|-------------|---------------------------------------------------------------------------------------------------------|

|      | SUB   | 0,0         | Clear accumulator O.                                                                                    |

|      | MOV   | 2,0         | Clear accumulator 2.                                                                                    |

|      | LDA   | 3, COUNT    | Load the negative count into ACC 3.                                                                     |

| LOOP | LDA   | 1, ARRAY, 2 | Load the value at the address specified<br>by the sum of ACC 2 and address ARRAY<br>into accumulator 1. |

|      | ADD   | 0,1         | Add the contents of register O and register 1. Place the result in register 0.                          |

|      | INC   | 2,2         | Increment index register 2.                                                                             |

|      | INC   | 3, 3, SZR   | Increment negative counter in register<br>3. Skip next instruction if zero.                             |

|      | JMP   | LOOP        | Branch to instruction labeled LOOP.                                                                     |

|      | ST0   | O, SUM      | Store the contents of register O into memory location associated with SUM.                              |

|      | HALT  | 1           | Terminate execution.                                                                                    |

Figure 10. Program For a Multi-accumulator System

Figure 10 illustrates the use of some of those instructions. The algorithm for summing an array of values is used again for comparison. One might note that an extra load instruction had to be used since the ADD instruction does not reference memory.

#### Microprogramming

The concept of microprogramming as formulated by Professor M. V. Wilkes of Cambridge University (13) was incorporated into the design of minicomputers around 1970. The primary reasons were to give minicomputers added flexibility and to allow them to perform more sophisticated operations. The first large scale implementation of microprogramming was in the IBM 360 family of computers introduced in 1964 (6). One of the primary reasons for the implementation was to permit reasonably efficient emulation of earlier IBM computers for which the customer software had been developed. Needless to say, the microprogramming technique became a valuable marketing tool and it contributed greatly to the success of the new IBM computers.

The microprogramming concept is illustrated in Figure 11 along with the diagram for a non-microprogrammable machine. Note that the two architectures are identical except for the control unit. In effect, the same sequence of control pulses are generated by both versions. It is the means by which the control signals are generated that is different.

The microprogrammed control unit consists of a read only memory (ROM), a microaddress register (MAR), a microinstruction register (MIR), a microsequencer, and a network of decoding logic. The microsequencer acts as the controlling element in a microprogrammable control unit. The read only memory contains the microinstructions. The microprogram-

(a) Hard-Wired Control

(b) Microprogrammable Control

Figure 11. Two Types of Control Units

ming cycle begins by reading into MIR a microinstruction from a ROM word specified by the contents of MAR. From MIR the microinstruction is decoded to produce one of two actions--generate pulses for register transfers or modify the contents of MAR. The modification of MAR causes a microsequence branch. If a microsequence branch is not effected then the next microinstruction to be executed is read from the ROM word immediately following the ROM word of the current microinstruction (6).

An important feature in microprogramming is the ability to specify many different operations within a microinstruction word. As a matter fact, microinstruction word lengths are often longer than the word length of the main memory. This feature is useful in overlapping processor operations to save time.

One of the most important observations in microprogramming is the fact that the functions of the microprogrammable control unit are defined by the microprograms stored in the ROM. To meet different application requirements that dictates different control unit functions, one needs only to replace the microprograms. Thus microprogramming is advantageous in applications that require:

- 1. Implementation of large, sophisticated instruction set with a relatively simple processor.

- 2. Emulation of different computers with different designs for different applications.

- 3. Implementation of complex operations such as multiply/divide, floating point processing, and input/output.

Many of today's minicomputer systems employ a microprogrammed or microprogrammable control unit. In the Cincinnati Milacron CIP/2200, complex decimal number manipulation instructions including "edit and mark" and "translate and test" are implemented. Hewlett Packard 21MX and Data General ECLIPSE S/200 allows for customized instructions and subroutines through a writeable control store feature separate from the ROM of the control unit. One computer company, Microdata, manufactures only microprogrammable machines. The products include MICRO 800, MICRO 1600, and MICRO 3200. An interesting "firmware" (microprogram) development by Microdata is the MICRO 32/S. It is a MICRO 3200 processor microprogrammed to emulate a stack machine (11). The system is discussed in more detail in Chapter IV.

#### Stack Structures

A useful special-purpose feature incorporated in many of the current minicomputers is a push-down storage unit, sometimes called an LIFO (last-in-first-out) list, or a stack. A stack is considered to be a list storage structure in which data items are inserted and deleted from one end only. Its use ranges from evaluation of arithmetic expressions to implementation of high level languages (11). The primary advantage in using a stack structure is its ability to allocate and deallocate storage locations dynamically.

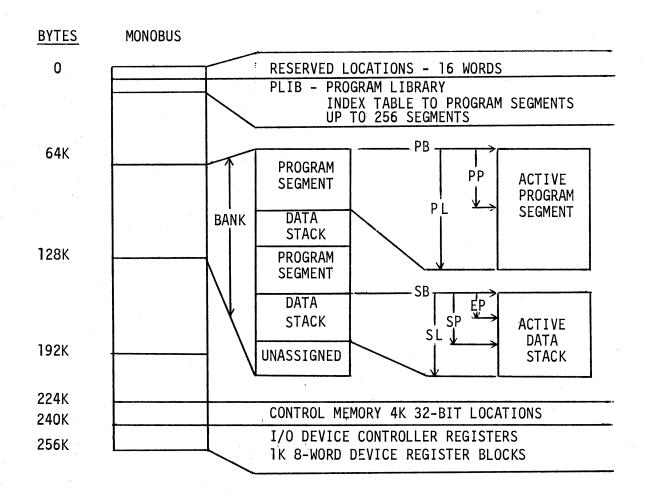

A stack structure is analogous to a stack of cafeteria trays where the last tray placed on top of the stack is the first to be removed. Thus there are two major operations involved in a stack structure, "push" a data item onto the top of the stack and "pop" a data item from the top of the stack. These operations are illustrated in Figure 12. Error conditions "stack overflow" and "stack underflow" are illustrated in Figure 13.

Generally there are three levels of stack structure implementations in minicomputers. The first level of implementation involves automatic saving and restoring of environments in subroutine and interrupt processing. In the Cincinnati Milacron CIP/2200 it is called the control

(b) Pop Data B. from Stack

stack facility (3). The user has no direct access to the facility. The second level of implementation is user oriented. The user can define and manipulate his own stacks through special stack manipulating instructions. The facility is considered to be an added feature. Such a facility is implemented in the ALPHA LSI-2 (19) and ECLIPSE S/200 (22) computers. The third level of implementation involves a completely stack oriented system. In such a system the machine instructions are specifically designed to manipulate stacks. The Microdata 32/S (11) is an example of such a system.

#### **Bus Structures**

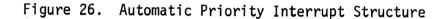

As microprogramming has contributed to the flexibility and usefulness of minicomputer systems, the use of bus structures has provided ease in the interfacing of a large number of peripherals, memory expansion and in some cases multiprocessor operations. Specifically the use of a universal bus has become very popular among minicomputer manufacturers. Just to name a few, the Computer Automation ALPHA LSI-2 has its MAXIBUS, the PDP 8/e has its OMNIBUS, the PDP 11/40 has its UNIBUS, Lockheed Electronics SUE system has its INFIBUS, and the Raytheon Data Systems RDS-500 has its SUPERBUS I and SUPERBUS II.

Figure 14 illustrates the relationship of a universal bus with its system components. In effect, the universal bus provides the communication link from one system component to another. Thus it is made up of communication lines with each line used for one of three types of signals -- address, data, or control.

Figure 14. The Universal Bus

The address lines are used by the processor and DMA controllers. The processor uses them to send device and function codes. DMA controllers use them to address memory locations for I/O data transfers.

The data lines are shared by the processor, memory, and all I/O controllers. The processor uses them to read data from or write data into the memory. It also uses them for transferring data to and from the I/O controllers. The DMA controller uses them to read data from or write data into memory. All other I/O controllers use them to convey their unique interrupt addresses during interrupt processing.

The control lines are used by the processor to effect specific actions involving the memory and/or the I/O controllers. These lines can be subdivided into four categories -- I/O commands, utility signals, interrupt signals, and DMA signals. I/O command signals define the type of I/O operation (input, output, etc.) to be processed. Utility signals are used by the processor in resetting system status during a power-up procedure. The interrupt signals are associated with interrupt requests by the I/O devices and the interrupt processing that follows. The DMA signals are used for DMA interrupt priority signal propagation, DMA bus acquisition, and processor grant of DMA bus control.

### Typical System Options

When an application requires more processing capabilities than what the standard equipment can offer, the user is usually made aware of the optional equipment. For the scientific applications where there is extensive use of mathematical computations, desirable options include the hardware multiply/divide and the floating point processor. These two greatly improve the speed of mathematical routines where the multiply/divide and floating point operations are normally done by slow software routines. Where power failure becomes a critical event, the power fail/restart option could be purchased to avoid disasters. This special option monitors the voltage levels in a system. When a voltage level drops below the normal operating level, an interrupt procedure saves the status of the current program in the non-volatile core memory. When the voltage level is restored, the restart procedure reloads the interrupted program. The normal processing operations are then reactivated at the point where the interruption occured. Where applications involve real world timing intervals, a real-time clock option is often necessary. Computer procedures may then monitor the clock and perform time-related operations. The options that have been discussed are the more typical options offered by today's minicomputers. Each system has its own set of options. Some may even offer some of the options described above as standard equipment.

## CHAPTER IV

## MINICOMPUTERS OF THE 70'S

#### Introduction

In this chapter, the system designs of ten of today's minicomputers are examined. Of the ten, four have fixed purpose registers, two have multi-accumulators, and three have general purpose registers. The last minicomputer has a specialized design implemented through microprogramming.

## Fixed Purpose Register Machines

#### Digital Equipment Corporation PDP 8/e

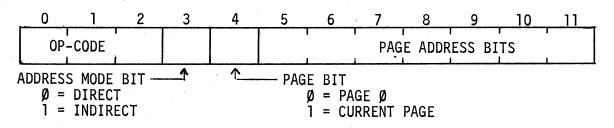

The first PDP 8 model was introduced in 1964, a year after its predecessor, the PDP 5, hit the market (20). Through the years, the PDP 8 series has proven itself to be one of the most successful line of minicomputers. The primary reason for its success is the preservation of the original instruction set (10). The succeeding models were thus compatible with the earlier models allowing users to develop a massive amount of general-purpose and application software. It is no wonder that today in 1976, the PDP 8/e, with its seemingly obsolete 12-bit design, is still a very serious competitor for the overwhelming 16-bit systems because of the large and valuable software inventory. The functional characteristics of the PDP 8/e are listed in Table II. The instruction formats are shown in Figure 15. There are five two-cycle memory-reference instructions with one level of indirect addressing possible, and eight memory locations on page-0 serving as

## TABLE II

PDP 8/e FUNCTIONAL CHARACTERISTICS

### Features

Processor Programmable Registers

Control Unit Instructions Memory Reference Register Operate Interrupt Addressing Direct Current page Indirect Interrupt System

Memory

Word length Cycle time Capacity Minimum Maximum Increment Parity

Input/Output Maximum number of devices Programmed Direct memory access

Universal Bus

1 accumulator 1 accumulator extension hardwired 34 6 20 8 128 words 128 words 4096 words polling (1 interrupt line)

Characteristics

12 bits 1200 nsecs (core)

4096 words 32,768 words 2096 or 4096 words option

60 10 characters/sec 833 K words/sec

96 lines (bidirectional)

autoindex (automatic incrementing) registers. The processor has one accumulator and a temporary storage register whose contents can be transferred to and from, or exchanged with the accumulator by one-cycle instructions. Up to 512 I/O instructions are possible with the use of a single-level interrupt system. A DMA processor allows data transfer within one memory cycle or three memory cycles if the transfer is just one of a block transfer (10) (20).

(a) Memory Reference Instruction Format

| <br>0 1                                               | 2                                                                  | 3                                              | 4         | 5                            | 6                                                   | 7                         | 8      | 9                       | 10                           | 11 |

|-------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------|-----------|------------------------------|-----------------------------------------------------|---------------------------|--------|-------------------------|------------------------------|----|

| GROUP                                                 | SPECIFIC                                                           | ATION                                          |           | I<br>I                       | MI                                                  | CRO IN                    | STRUCT | IONS                    |                              | GS |

| Bits<br>0-3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11 | 1110<br>Clear<br>Clear<br>Compl<br>Compl<br>Rotat<br>Rotat<br>Byte | Link<br>ement /<br>ement  <br>e Righ<br>e Left | Link<br>t | Skip<br>Skip<br>Skip<br>Reve | r AC<br>on AC<br>on AC<br>on Li<br>rse Sk<br>cal OR | 0<br>=0<br>nk 0<br>ip Log |        | 1111<br>Clear<br>AC ext | AC<br>into<br>o AC e<br><br> |    |

(b) Register Operate Instruction Format

Figure 15. PDP 8/e Instruction Formats

### Cincinnati Milacron CIP/2200

The Cincinnati Milacron CIP/2200 is a general purpose, byte oriented minicomputer employing a microprogrammed control unit (3). It has an extensive instruction set including binary arithmetic, decimal arithmetic and character manipulation. The functional characteristics are listed in Table III. The instruction formats are shown in Figure 16.

The CIP/2200 has an 8-bit hardware data path and memory. The CPU registers, however, are 16 bits in length. The instruction set includes a complete set of 16 bit register-to-memory and register-to-register binary arithmetic instructions. In addition, variable length binary arithmetic on 8, 16, 24, or 32 bit operands are possible. Another group of instructions provides memory-to-memory decimal arithmetic and character string move and compare, code conversions, and decimal editing.

The CIP/2200 I/O structure consists of a microprogrammed serial I/O interface, a byte I/O facility, a microprogrammed facility for concurrent transfers, and up to two independent DMA processors. The serial I/O interface controls a teletype or other similar terminal devices. The byte I/O facility transmits 8-bit data between one of 32 peripheral devices and either a register or a memory location. The microprogrammed Direct Memory Channel (DMC) for concurrent transfers allows a maximum transfer rate of 86,000 bytes per second concurrently operating with program execution. The independent DMA processors compete with the CPU for access to main memory and have a maximum transfer rate of 909,000 bytes per second.

# TABLE III

# CIP/2200 FUNCTIONAL CHARACTERISTICS

| Features                                 | Characteristics                              |

|------------------------------------------|----------------------------------------------|

| Processor                                |                                              |

| Programmable Registers                   | l accumulator                                |

|                                          | 1 accumulator extension                      |

|                                          | 1 index register                             |

| Control Unit                             | microprogrammed                              |

| Instructions                             | 119                                          |

| Arithmetic                               | 14 (binary and decimal)                      |

| Memory moves                             | 3                                            |

| Register change                          |                                              |

| Shifts                                   | 41<br>12                                     |

|                                          |                                              |

| String manipulation<br>Control transfers | 6                                            |

|                                          | 19                                           |

| Interrupt                                | 13                                           |

| I/O                                      | 8                                            |

| Immediate                                | 7                                            |

| Addressing                               |                                              |

| Direct                                   | 256 words                                    |

| Indirect                                 | 32,768                                       |

| Indexed                                  | 32,768                                       |

| Extended                                 | 32,768                                       |

| Immediate                                | 1 - 4 bytes in instruction                   |

| Relative                                 | 128 behind - 127 ahead of<br>program counter |

| Interrupt System                         | <b>1 1 1 1 1 1 1 1 1 1</b>                   |

| Туре                                     | vectored with priority                       |

| Internal                                 | 6 lines                                      |

| External                                 | l line (64 signals)                          |

| emory                                    |                                              |

| Word length                              | l6 bits                                      |

| Cycle time                               | 1.1 nsecs (core)                             |

| Capacity                                 | (                                            |

| Minimum                                  | 8192 words                                   |

| Maximum                                  | 32,768 words                                 |

| Increment                                | 8192                                         |

| Parity                                   | optional with 9 bit/byte                     |

|                                          | memory                                       |

| Protect                                  | optional                                     |

| Read Only Memory                         | 1536 words used for teletyp                  |

|                                          | controls, bootstrap load                     |

|                                          | concurrent block I/O,                        |

|                                          | instruction set extensio                     |

TABLE III (Continued)

| Features                                                                                                                                  | Characteristics                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Input/Output<br>Maximum number of devices<br>Maximum transfer rates<br>Serial I/O<br>Byte I/O<br>Concurrent block<br>Direct memory access | 32<br>110 bits/sec<br>10,000 bytes/sec<br>86,000 bytes/sec<br>910,000 bytes/sec |

| Control and Reg. oper. | OPCODE |        |     |      |                   |      | ·     |

|------------------------|--------|--------|-----|------|-------------------|------|-------|

| Conditional skip       | OPCODE | DISPL  |     |      |                   |      |       |

| Shift                  | OPCODE | COUNT  |     |      |                   |      |       |

| I/O (register)         | OPCODE | FUNC D | EV  |      |                   |      |       |

| I/O (memory)           | OPCODE | FUNC D | EVX | ADE  | DR                |      |       |

| Memory immediate       | OPCODE | DATA   | X A | DDR  |                   |      |       |

| Memory to Memory       | OPCODE | LENGTH | XA  | DDRD | X                 | ADDR | 3     |

| Memory to Memory ext.  | OPCODE | DATA   | LEN | X    | ADDR <sub>D</sub> | X    | ADDRS |

| Memory reference       | OPCODE | ADDR   |     |      |                   |      |       |

| Memory reference ext.  | OPCODE | X ADDR |     |      |                   |      |       |

| Literal                | OPCODE |        | 1-4 | data | bytes             |      |       |

Figure 16. CIP/2200 Simplified Instruction Formats

The use of microprogramming in CIP/2200 has allowed instructions of considerable power and flexibility to be implemented. "Edit and mark" and "translate and test" are two such instructions. If more specialized instructions are needed, the writeable control store (WCS) feature of CIP/2200 may be used. The user may use special instructions provided by CIP/2200 to transfer to user written application microprograms residing in the WCS.

<u>Variable Length Binary Arithmetic</u>. Special variable word length instructions perform binary arithmetic on one, two, three, or four bytes of data. This is useful for character operations, single byte arithmetic, and extended precision arithmetic on 24 or 32-bit quantities.