## UNIVERSITY OF OKLAHOMA

## GRADUATE COLLEGE

## A HIGH-PERFORMANCE INNER-PRODUCT PROCESSOR FOR REAL AND COMPLEX NUMBERS

A Dissertation

#### SUBMITTED TO THE GRADUATE FACULTY

in partial fulfillment of the requirements for the

degree of

Doctor of Philosophy

By GUOPING WANG Norman, Oklahoma 2003 UMI Number: 3260769

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

#### UMI Microform 3260769

Copyright 2007 by ProQuest Information and Learning Company. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

© Copyright by Guoping Wang 2003

All Rights Reserved.

# A HIGH-PERFORMANCE INNER-PRODUCT PROCESSOR FOR REAL AND COMPLEX NUMBERS

## A Dissertation APPROVED FOR THE SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING

BY

Monte P. Jull Dr. Monte P. Tull

Dr. Gerald Crain Jurner

Linda DeBrunner

oe Havlicek

Dr. Murad Ozaydin

To my family who have lovingly supported my years of study.

#### ACKNOWLEDGMENTS

In the years leading to this dissertation, I have had the great pleasure of working for and with an advisor who provided an environment conducive to learning. I would like to take this opportunity to thank my advisor, Dr. Monte P. Tull for his consistent guidance.

I would also like to thank Dr. Gerald Crain, Dr. Linda DeBrunner, Dr. Joe Havlicek and Dr. Murad Ozaydin for serving on my supervisory committee.

I appreciate many others who have been helpful at the University of Oklahoma. They make my years at the university a unique and memorable experience.

I am especially indebted to my family for their support. Guanglan Zhang, my wife, has been invaluable for her patience and love during my research. My daughter, Ying, and my son, Christopher always give me great joy and peace.

"This is what the Lord says ... 'Call to me and I will answer you and tell you great and unsearchable things you do not know.'"

Jeremiah 33:2-3

### TABLE OF CONTENTS

| CHAP  | TER 1 INTRODUCTION1                                                                        |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------|--|--|--|--|

| 1.1   | Inner-Product Implementation by the General Purpose Processors                             |  |  |  |  |

| 1.2   | Inner-Product Implementation by Digital Signal Processing Processors 6                     |  |  |  |  |

| 1.3   | Other Inner-Product Processor Implementation Methods7                                      |  |  |  |  |

| 1.4   | Multiplier Implementation Review10                                                         |  |  |  |  |

| 1.5   | The Redundant Binary Number System13                                                       |  |  |  |  |

| 1.6   | The Conversion of 2's-Complement to Redundant Binary 15                                    |  |  |  |  |

| CHAP  | PTER 2 INNER-PRODUCT PROCESSOR OF REAL, COMPLEX AND<br>REDUNDANT BINARY NUMBERS            |  |  |  |  |

| 2.1   | Real Number Inner-Product Computation                                                      |  |  |  |  |

| 2.1.  | 1 Inline Partial Product Redundant Binary Inner-Product                                    |  |  |  |  |

| 2.1.2 | 2 Cross Partial Product Redundant Binary Inner-Product                                     |  |  |  |  |

| 2.1.  | 3 Booth Encoding Methods                                                                   |  |  |  |  |

| 2.1.4 | 4 Implementation Comparison of Inline and Cross Inner-Product Methods 34                   |  |  |  |  |

| 2.2   | Complex Number Inner-Product Computation                                                   |  |  |  |  |

| 2.2.  |                                                                                            |  |  |  |  |

| 2.2.2 | 2 Comparison of Different Complex Radices                                                  |  |  |  |  |

| 2.2.  | Complex Number Multiplier and Inner-Product Computation                                    |  |  |  |  |

| 2.3   | Inner-Product Computation Comparison58                                                     |  |  |  |  |

| 2.4   | Implementation of Unified Signed/Unsigned Multiplier                                       |  |  |  |  |

| 2.4.  | 1 Unified Signed/Unsigned Multiplier Without Booth Coding                                  |  |  |  |  |

| 2.4.2 | 2 Unified Signed/Unsigned Multiplier With Booth Coding                                     |  |  |  |  |

| 2.5   | The Implementation of a Unified Signed/Unsigned Inner-Product Processor<br>for $AB \pm CD$ |  |  |  |  |

|       | $101  AB = CD  \dots  09$                                                                  |  |  |  |  |

| 2.6   | The Implementation of a Redundant Binary Multiplier                                        |  |  |  |  |

| 2.6.  | 1 Direct Implementation of Redundant Binary Multiplier                                     |  |  |  |  |

| 2.6.2 | 2 Redundant Binary Multiplier Implementation                                               |  |  |  |  |

|       | Using Inner-Product Processor                                                              |  |  |  |  |

| 2.7   | Redundant Binary Inner-Product Computation75                                               |  |  |  |  |

| CHAPTER 3 IMPLEMENTATIONS OF DIVISION METHOD |                                                                   |       |  |  |

|----------------------------------------------|-------------------------------------------------------------------|-------|--|--|

| 3.1 E                                        | Division Algorithm Review                                         | 76    |  |  |

| 3.2 F                                        | urther Studies of the Goldschmidt and Newton-Raphson Methods      | 80    |  |  |

| 3.2.1                                        | Comparison of the Goldschmidt and Newton-Raphson Methods          |       |  |  |

| 3.2.2                                        | Further Discussion of the Goldschmidt Method                      |       |  |  |

| 3.2.3                                        | Implementation of the Goldschmidt Division                        |       |  |  |

| 3.3 F                                        | Real Number Division Implementation                               | 85    |  |  |

| 3.4 0                                        | Comparison of the Implementations of Division                     | 87    |  |  |

| 3.5 0                                        | Complex Number Division Implementation                            | 88    |  |  |

| СНАРТ                                        | ER 4 COMPUTATIONAL EXTENSIONS                                     | 90    |  |  |

| 4.1 F                                        | eal-Number Computational Extensions                               | 92    |  |  |

| 4.1.1                                        | 8-Element Real Number Inner-Product Computation                   |       |  |  |

| 4.1.2                                        | Dual 4-Element Real Number Inner-Product                          | 92    |  |  |

| 4.1.3                                        | Quad 2-Element Real Inner-Product                                 |       |  |  |

|                                              | Using Four Redundant Binary Accumulators                          |       |  |  |

| 4.1.4                                        | Eight Parallel Multipliers Using 8 Redundant Binary Accumulators  | 93    |  |  |

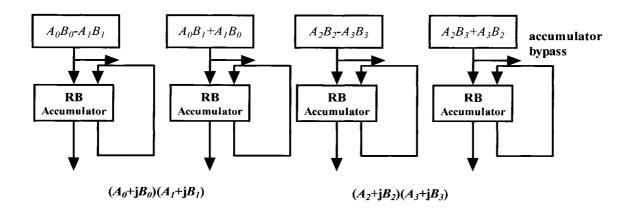

|                                              | Complex-Number Computational Extensions                           | 94    |  |  |

| 4.2.1                                        | Single 2-Element Complex Number Inner-Product Computation Using   |       |  |  |

| 4.0.0                                        | Real/Imaginary Redundant Binary Accumulator                       |       |  |  |

| 4.2.2                                        | Dual Single-element Complex Number Inner-Product Computation Usin |       |  |  |

| 4.2.3                                        | Four Redundant Binary Accumulators                                |       |  |  |

|                                              | Two Parallel Complex Number Multipliers                           |       |  |  |

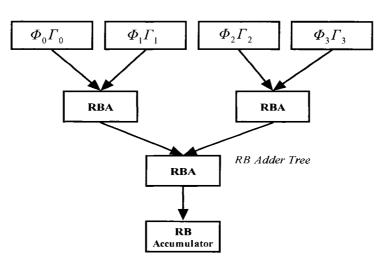

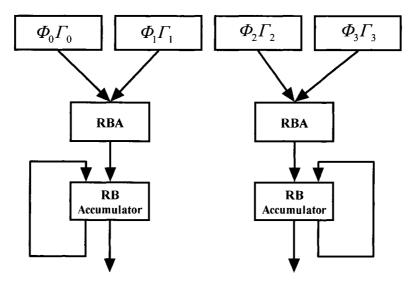

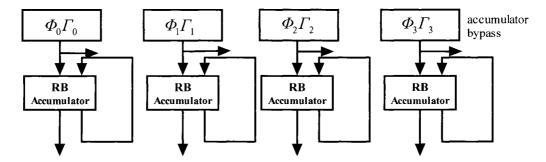

| 4.3 R                                        | edundant Binary Number Computational Extensions                   | 95    |  |  |

| 4.3.1                                        | Single Element Redundant Binary Number Inner-Product Computation. | 95    |  |  |

| 4.3.2                                        | Dual 2-Element RB Inner-Product plus                              |       |  |  |

|                                              | Two Redundant Binary Accumulators                                 | 96    |  |  |

| 4.3.3                                        | Four Parallel Redundant Binary Multipliers Using                  | ~ -   |  |  |

|                                              | Four Redundant Binary Accumulators                                | 97    |  |  |

| 4.4 P                                        | ipeline Extensions                                                | 97    |  |  |

| СНАРТ                                        | ER 5 REDUNDANT BINARY TO 2'S-COMPLEMENT NUMBER                    |       |  |  |

|                                              | CONVERSION                                                        | . 102 |  |  |

| 5.1 A                                        | n Improved Redundant Binary to 2's-Complement Converter           | 102   |  |  |

| 5.2 C                                        | omparison Result                                                  | 108   |  |  |

~

| CHAPTER 6    | SUMMARY AND C  | CONCLUSIONS   |     |

|--------------|----------------|---------------|-----|

| APPENDIX: VI | IDL HARDWARE I | MPLEMENTATION | 113 |

| REFERENCES   |                |               | 114 |

#### LIST OF FIGURES

| Figure 1-1. Flowchart of Inner-Product Computation by the General Purpose                                 |      |

|-----------------------------------------------------------------------------------------------------------|------|

| Processors                                                                                                |      |

| Figure 1-2. Inner-Product Implementation in Pentium MMX Processor                                         |      |

| Figure 1-3. Sample Code for an Inner-Product by Pentium MMX                                               | 5    |

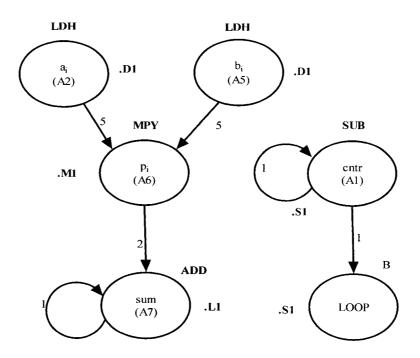

| Figure 1-4. Sample Code of the Fixed-Point Inner-Product by TMS 320C60                                    | 6    |

| Figure 1-5. Kazakova's Inner-Product Processor Architecture                                               | 8    |

| Figure 1-6. Lin's Reconfigurable Inner-Product Processor                                                  | 9    |

| Figure 1-7. A RB MAC (Multiply and Accumulate) by Huang                                                   | 9    |

| Figure 1-8. Baik's Redundant Binary Filter Implementation                                                 | . 10 |

| Figure 1-9. Design of a 5×5 Array Multiplier                                                              | . 11 |

| Figure 1-10. 4:2 Counter Using 3:2 Counter                                                                | . 11 |

| Figure 1-11. 3:2 Counter Based 4×4 Multiplier                                                             |      |

| Figure 1-12. 4:2 Counter Based 4×4 Multiplier                                                             | . 12 |

| Figure 1-13. Mapping from the Sum of Two 2's-Complement Numbers to a RB                                   |      |

| Number                                                                                                    | . 17 |

| Figure 1-14. Mapping from the Subtraction of Two 2's-Complement Numbers to                                | a    |

| RB Number                                                                                                 | . 18 |

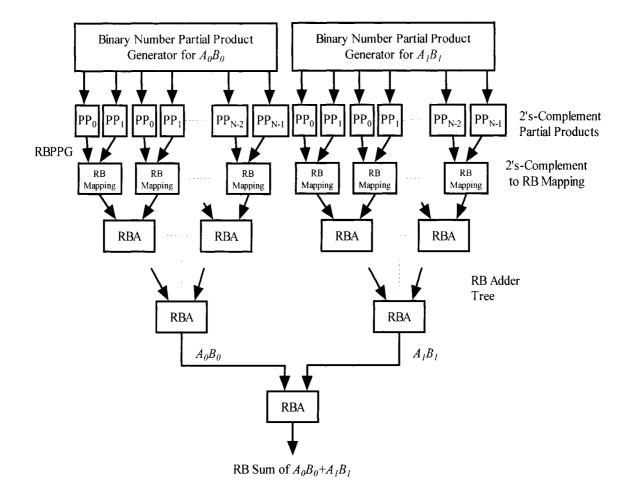

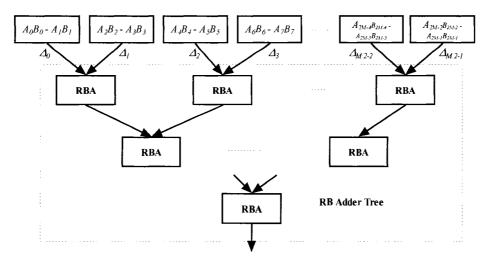

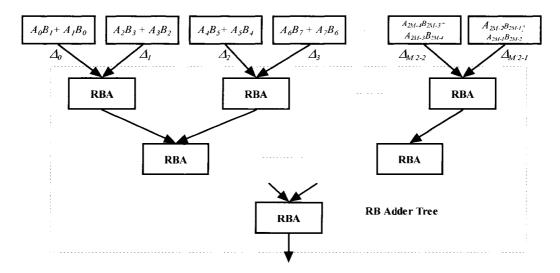

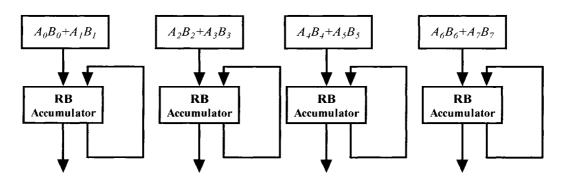

| Figure 2-1. Inline Partial Product RB Implementation of $A_0B_0 + A_1B_1$                                 | . 24 |

| Figure 2-2. Inline Partial Product Structure of $A_0 B_0 + A_1 B_1$                                       | . 25 |

| Figure 2-3. Overall Structure of the Redundant Binary Inner-Product                                       |      |

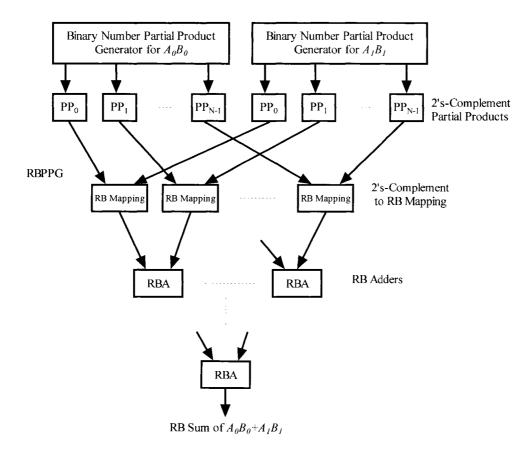

| Figure 2-4. Cross Partial Product Structure of $A_0B_0 + A_1B_1$                                          |      |

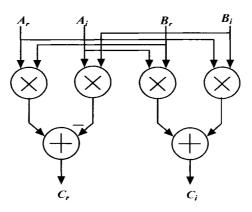

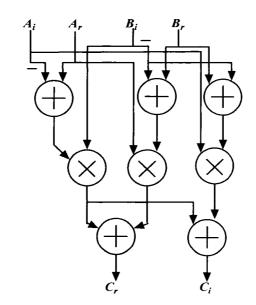

| Figure 2-5. Basic Diagram of Complex Number Multiplication                                                | . 38 |

| Figure 2-6. Blahut's Complex Number Multiplier                                                            |      |

| Figure 2-7. An Example of Addition in Radix-(2j)                                                          | . 43 |

| Figure 2-8. An Example of Subtraction in Radix-(2j)                                                       | . 44 |

| Figure 2-9. An Example of Multiplication in Radix-(2j)                                                    |      |

| Figure 2-10. An Example for Radix-(j-1) Carry Propagation                                                 |      |

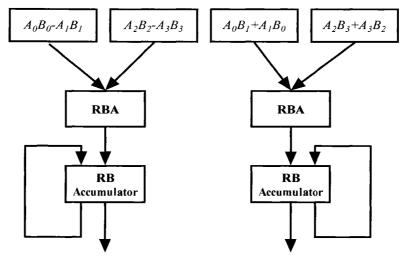

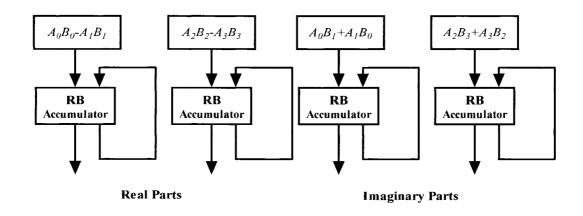

| Figure 2-11. Inline Implementation of $A_0 B_0 - A_1 B_1$                                                 | . 52 |

| Figure 2-12. The Real Part of the Complex Number Inner-Product                                            |      |

| Figure 2-13. The Imaginary Part of Complex-Number Inner-Product                                           |      |

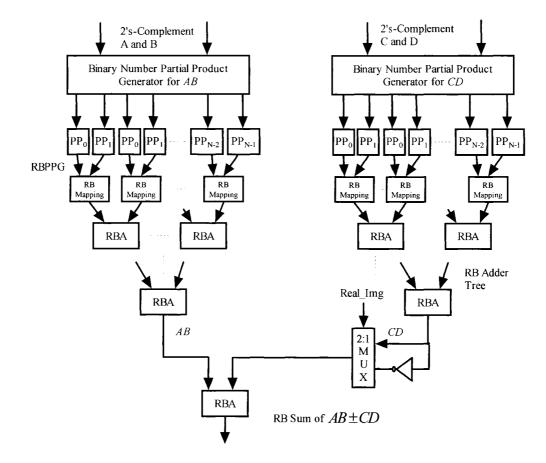

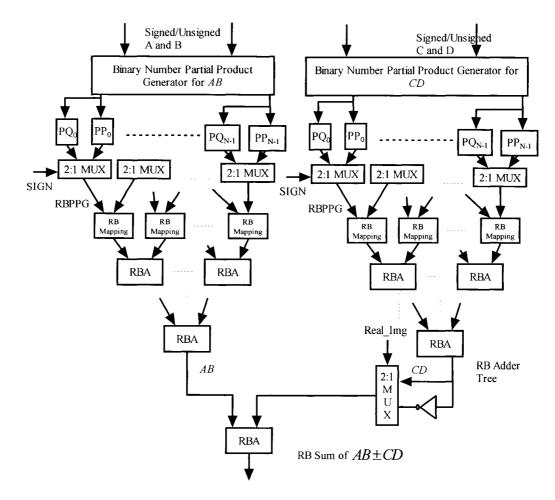

| Figure 2-14. Unified $\overrightarrow{RB}$ IP Processor for $\overrightarrow{AB} \pm \overrightarrow{CD}$ |      |

| Figure 2-15. An Example Code of Fixed-Point Inner-Product                                                 |      |

| Figure 2-16. Dependency Graph of Fixed-Point Inner-Product                                                |      |

| Figure 2-17. RB Inner-Product Implementation                                                              |      |

| Figure 2-18. Unsigned Multiplier with Partial Product Generation                                          |      |

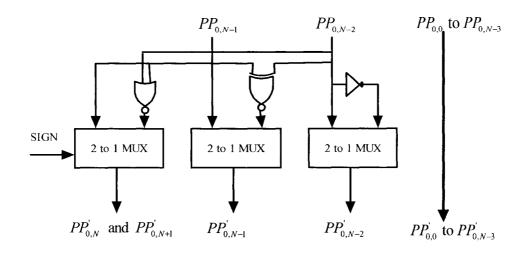

| Figure 2-19. Mapping of $PP_{N-2}$ and $PP_{N-1}$ for Signed Multiplier into a RB Digit                   |      |

| Figure 2-20. Mapping of $PQ_{N-2}$ and $PQ_{N-1}$ for Signed Multiplier into a RB Digit                   | 64   |

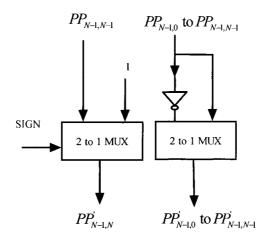

| Figure 2-21. Circuit Realization of the Last Partial Product $PP'_{N-1}$ for                              |      |

| Signed/Unsigned Multiplier                                                                                | 64   |

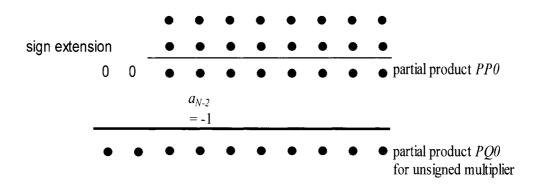

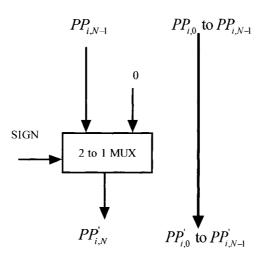

| Figure 2-22. First Partial Product <i>PQ0</i> for Unsigned Multiplier                                     |      |

-

| Figure 2-23. Circuit of the First Partial Product $PP_{\theta}$                              |

|----------------------------------------------------------------------------------------------|

| for Signed/Unsigned Multiplier67                                                             |

| Figure 2-24. Circuit of the Partial Products from $PP_1'$ to $PP_{N-2}'$ for Signed/Unsigned |

| Multiplier                                                                                   |

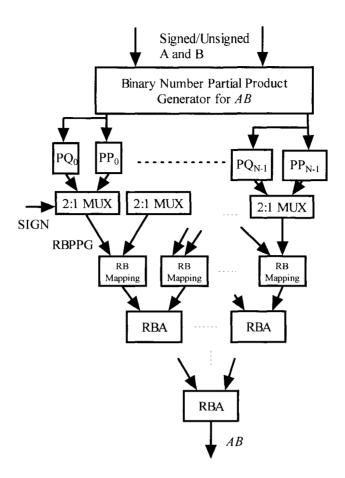

| Figure 2-25. A Unified Sign/Unsigned Multiplier                                              |

| Figure 2-26. Unified Signed/Unsigned IP Processor for $AB \pm CD$                            |

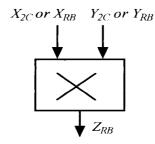

| Figure 2-27. A RB Multiplier Diagram                                                         |

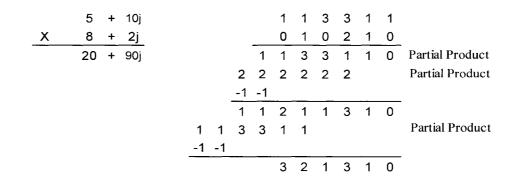

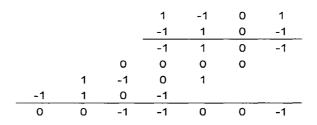

| Figure 2-28. An Example of RB Multiplication                                                 |

| Figure 2-29. Implementation of RB Multiplier $A_{RB}B_{RB}$                                  |

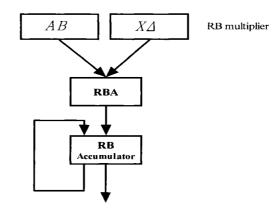

| Figure 2-30. IP Implementation for RB Number $AB + XA$                                       |

| Figure 2-30. If Implementation for KB (umber AB + AB           |

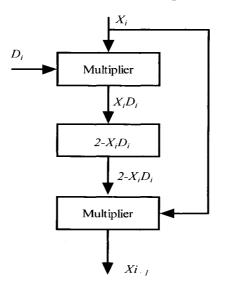

| Figure 3-2. Newton-Raphson Divider Implementation                                            |

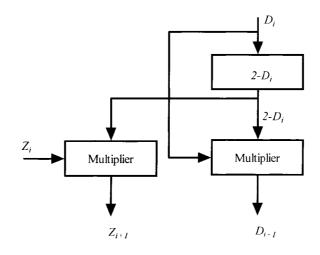

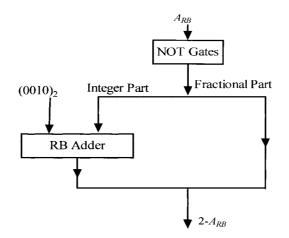

| Figure 3-3. Implementation of $2-A_{RB}$                                                     |

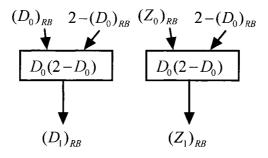

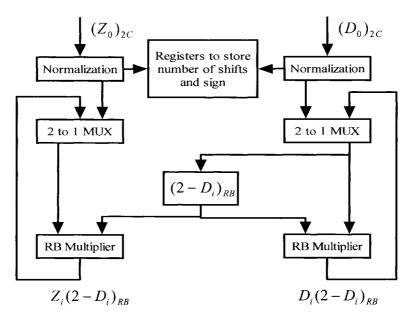

| Figure 3-4. First Iteration Implementation of the Goldschmidt Division                       |

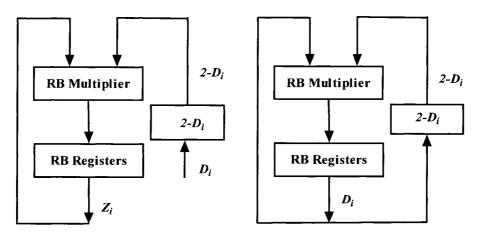

| Figure 3-5. Implementation of Successive Iteration Computation for Z and D                   |

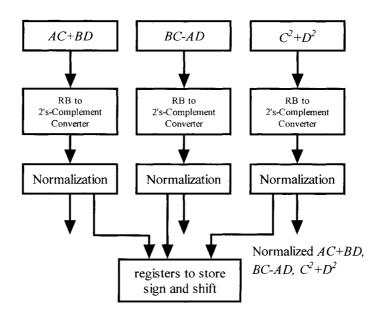

| Figure 3-6. Overall Structure of Divider Using RB IP Processor                               |

| Figure 3-7. Complex-Number Division Implementation Initial Process                           |

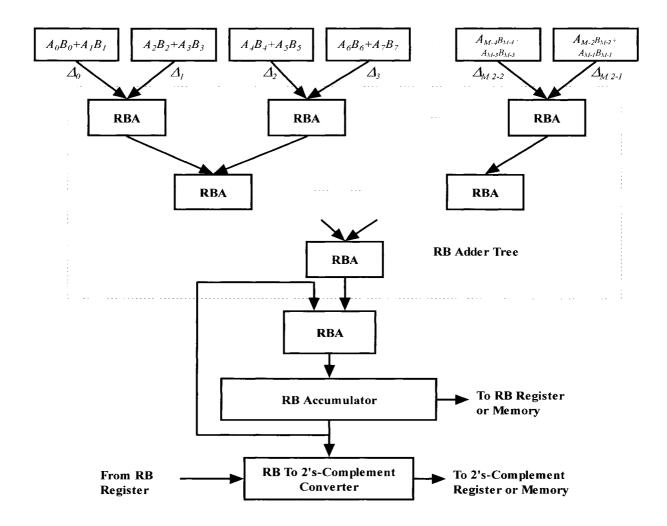

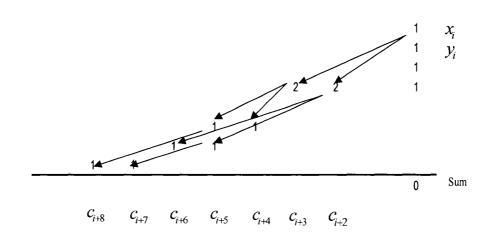

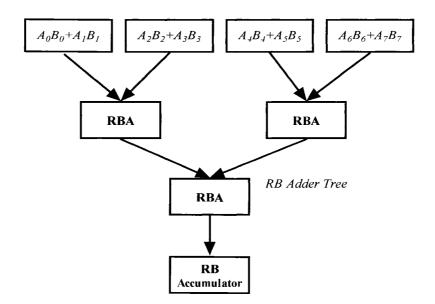

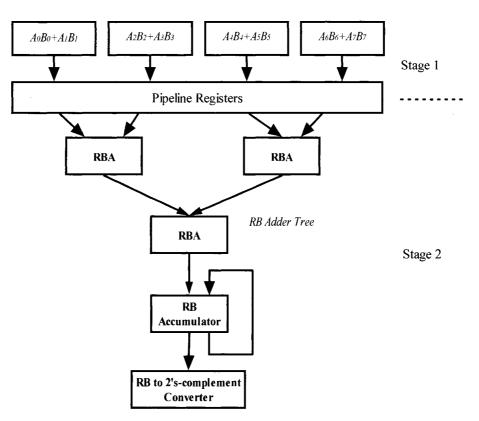

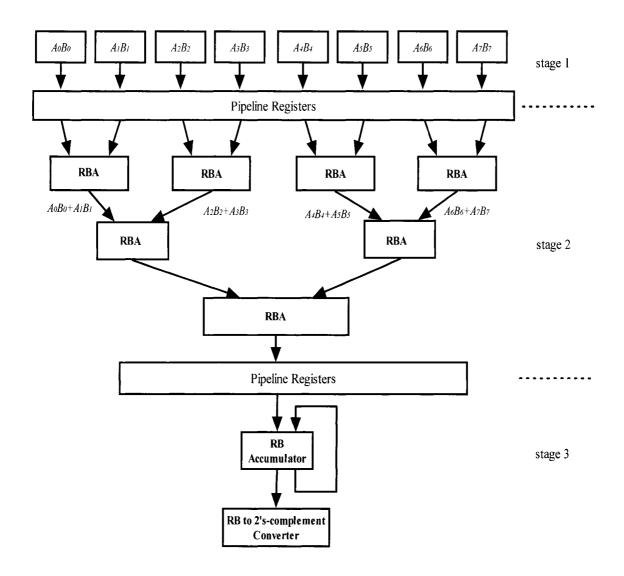

| Figure 4-1. An Example of a Redundant Number Adder Tree                                      |

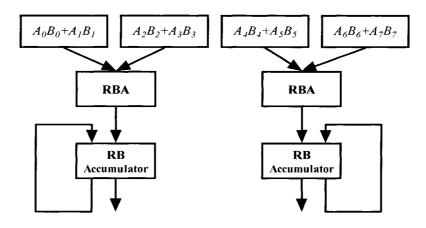

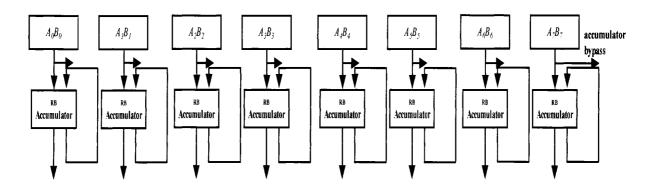

| Figure 4-2. Dual 4-Element Real Number Inner-Product                                         |

| Figure 4-3. Quad 2-Element Real Number Inner-Product                                         |

| Figure 4-4. Eight Parallel Multipliers Using 8 RB Accumulators                               |

| Figure 4-5. Single 2-Element Complex Number IP Using One Real/Imaginary RB                   |

| Accumulator                                                                                  |

| Figure 4-6. Dual 2-Element Complex Number Inner-Products Using Four RB                       |

| Accumulators                                                                                 |

| Figure 4-7. Two Parallel Complex Number Multipliers                                          |

| Figure 4-8. 4-Element Redundant Binary Inner-Product                                         |

| Figure 4-9. Dual 2-Element RB Inner-Product                                                  |

| Figure 4-10. Four Parallel RB Multipliers Using 4 RB Accumulators                            |

| Figure 4-11. 6- word 6-Bit KB IF Frocessor                                                   |

| Figure 4-12. Two-Stage Fipelined RB IP Processor                                             |

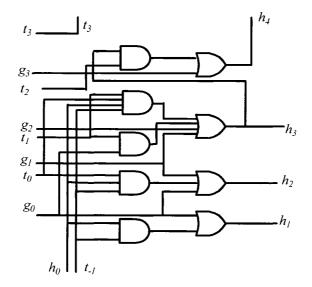

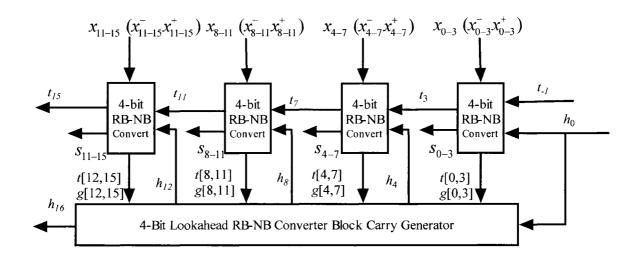

| Figure 5-1. Four-Bit Carry-Lookahead RB-NB Converter                                         |

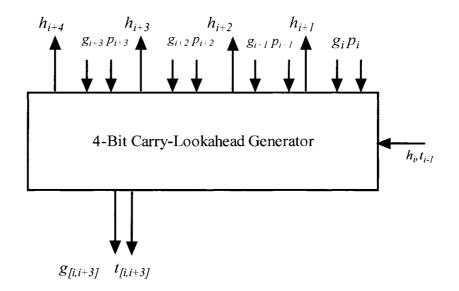

| Figure 5-2. Diagram of a 4-Bit Carry-Lookahead RB-NB Carry Generator 107                     |

| Figure 5-3. Two-Level 16-bit RB-NB Converter                                                 |

#### LIST OF TABLES

| Table 1-A. Computation Rules for the First Step in Carry-Propagation-Free                  |      |

|--------------------------------------------------------------------------------------------|------|

| Addition for RB Numbers                                                                    | . 15 |

| Table 1-B. Coding Table for Binary Signed Digits                                           |      |

| Table 1-C. Logic Functions for RBFA and RBHA                                               | . 19 |

| Table 2-A. Modified Booth Encoding Table                                                   | . 30 |

| Table 2-B. Booth Correction Factors for the Inline Multiplication Method                   | . 32 |

| Table 2-C. Booth Correction Factors for the Cross Partial Product Method                   | . 33 |

| Table 2-D. 16-Bit FPGA Implementations of $A_0 B_0 + A_1 B_1$                              |      |

| Without Booth Encoding                                                                     | . 35 |

| Table 2-E. 16-Bit FPGA Implementations of $A_0 B_0 + A_1 B_1$ With Booth Encoding          |      |

| Table 2-F. Truth Table for Radix- $(-1 + j)$ One-Bit Addition                              | . 50 |

| Table 2-G. Booth Correction Factors for Redundant Binary Partial Product                   |      |

| Generation of $A_{\theta}B_{\theta}$ - $A_{I}B_{I}$                                        | . 55 |

| Table 2-H. Comparison of IP Computation between TMS320C62X and RB Inner-                   | -    |

| Product Processor                                                                          |      |

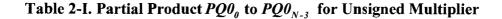

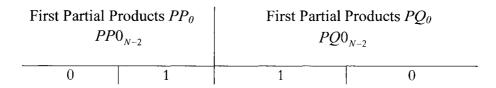

| Table 2-I. Partial Product $PQ\theta_{\theta}$ to $PQ\theta_{N-3}$ for Unsigned Multiplier | . 65 |

| Table 2-J. Partial Product $PQ\theta_{N-2}$ for Unsigned Multiplier                        | . 65 |

| Table 2-K. Partial Product $PQ\theta_{N-I}$ for Unsigned Multiplier                        | . 66 |

| Table 2-L. Partial Product $PQ\theta_N$ and $PQ\theta_{N+I}$ for Unsigned Multiplier       | . 66 |

| Table 2-M. RB Partial Product Generation                                                   | . 72 |

| Table 2-N. Encoded RB Partial Product Generation                                           | . 73 |

| Table 4-A. Time Delay Model of RB Multiplier                                               | . 97 |

| Table 5-A. Conversion Rules in Stage I                                                     | 103  |

| Table 5-B. Conversion Truth Table for RB-NB                                                | 104  |

#### ABSTRACT OF THE DISSERTATION

## A High-Performance Inner-Product Processor for Real and Complex Numbers

by

**Guoping Wang** Doctor of Philosophy in Electrical and Computer Engineering University of Oklahoma, Norman, OK, 2003 Dr. Monte P. Tull, Chair

A novel, high-performance fixed-point inner-product processor based on a redundant binary number system is investigated in this dissertation. This scheme decreases the number of partial products to 50%, while achieving better speed and area performance, as well as providing pipeline extension opportunities. When modified Booth coding is used, partial products are reduced by almost 75%, thereby significantly reducing the multiplier addition depth. The design is applicable for digital signal and image processing applications that require real and/or complex numbers inner-product arithmetic, such as digital filters, correlation and convolution. This design is well suited for VLSI implementation and can also be embedded as an inner-product core inside a general purpose or DSP FPGA-based processor. Dynamic control of the computing structure permits different computations, such as a variety of inner-product real and complex number computations, parallel multiplication for real and complex numbers, and real and complex number division. The same structure can also be controlled to accept redundant binary number inputs for multiplication and inner-product computations. An improved 2's-complement to redundant binary converter is also presented.

## Chapter 1 Introduction

Consider the definition of the inner-product. For two vectors  $\boldsymbol{A} = (A_0, A_1, A_2, \dots, A_{M-1})$ , and  $\boldsymbol{B} = (B_0, B_1, B_2, \dots, B_{M-1})$ , the inner-product of  $\boldsymbol{A}$  and  $\boldsymbol{B}$  is defined as:

$$\langle \boldsymbol{A}, \boldsymbol{B} \rangle = \boldsymbol{A} \left( \boldsymbol{B}^{*} \right)^{T} = \sum_{i=0}^{M-1} A_{i} B_{i}^{*}$$

(1.1)

In general,  $A_i$  and  $B_i$  may be real or complex numbers.  $AB^*$  denotes matrix multiplication with the row vectors A and B considered as  $1 \times M$  matrices, and  $(B^*)^T$  denotes the conjugate transpose of B. In the traditional method, all of the multiplications are processed independently of one another, thereby requiring M multiplications and M-1 additions. To obtain high-performance circuit implementations of the inner-product, several salient features of Equation (1.1) can be utilized; namely, carry-free addition, high-speed multiplication, and parallel or pipelined multiplication and addition.

The application of redundant binary (RB) numbers was previously investigated for carry-free addition and fast multiplication. These techniques have proven to be easily laid out in VLSI and result in high-speed circuit implementations [1]-[4]. In this dissertation, high-performance and easily pipelined implementations of an inner-product processor are presented. The designs utilize RB numbers for achieving the carry-free addition of partial products. Redundant binary schemes are less viable in applications that require persistent conversion back to 2's-complement [5]-[7], since this process is relatively slow due to an unavoidable carry propagation requirement. The overall motivation for this work is the design of a high-performance Complex Arithmetic Signal Processor (CASP) capable of offering novel extended inner-product operations. The CASP design relies on the high-speed multiplication afforded by redundant binary techniques, while avoiding the relatively slow conversion back to 2's-complement numbers until a final 2's-complement result is necessary. Inherently, the CASP device provides intermediate register storage for redundant binary, as well as 2's-complement numbers. The methods for implementing the core inner-product structure and general extensions are presented in this dissertation.

Inner-product computations play a central role in digital signal processing, most often in digital filters, signal correlation, convolution, FFT, etc. Current implementations of inner-product computations include the following methods: 1) general purpose processors, 2) digital signal processor devices, such as Texas Instruments TMS320C60, 3) VLSI devices, such as FPGAs or ASICs. Various researchers have investigated the implementation of inner-product processors. Implementations include array multipliers [8],[9], VLSI Residue Number System architecture [10], serial implementations [11],[12], distributed arithmetic [13],[14], carry-save addition [15]-[19], specific DSP processor and FPGA [20]-[27], redundant binary implementations [28]-[30].

Complex number arithmetic computation is a key arithmetic feature required in modern digital communication and optical systems [31]-[38]. Many algorithms based on convolution, correlation, and complex number filters require complex number multiplication and high-speed inner-product computation. These applications require efficient representation and manipulation of complex numbers together with real numbers. Considerable research exists for hardware implementations of complex number systems [39]-[54] and representations of complex numbers in different radices [55]-[68].

The redundant binary (RB) representation is one of the signed-digit number representations originally introduced by Avizienis [69] for achieving the carry-propagation-free addition. RB numbers differ from the conventional 2's-complement representation in that the individual digits comprising a number may have negative values as well as positive values. High-speed VLSI multiplication algorithms, which are based on redundant binary numbers, are proposed in [1],[3],[4]. Since integer numbers in most digital systems are represented in 2's-complement form, a converter is needed to convert a redundant binary number to a 2's-complement number in the last step. Different implementations of this converter have been proposed in [5], [7], [12], [70]-[74].

Although division is an infrequent operation, it has been shown [75] that ignoring its hardware implementation can result in significant system performance degradation for many applications. Extensive literature describes the theory of division [75]-[90]. Division algorithms can be generally divided into the following classes: digit recurrence, functional iteration, table look-up and variable latency [84]. Choosing an optimal design of a divider depends heavily upon its requirements for area and speed.

In the following sections, these hardware implementations and research issues will be reviewed and investigated.

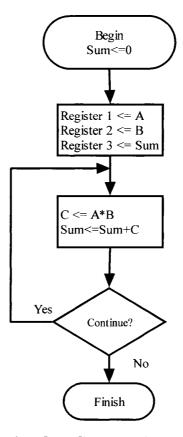

## 1.1 Inner-Product Implementation by the General Purpose Processors

General purpose processors, such as Intel Pentium and 80x86, Motorola 68000, AMD K6 and K7, *etc.*, can perform different algorithms using combinations of various machine instructions. The systems built with these programmable processors are adaptable to different applications and easily upgradeable to changing requirements. Even with such potential advantages, traditional programmable processors have not been widely used for high-speed inner-product computation because of their limited performance. For example, in order to find the inner-product of two vectors A and B, the flowchart in Figure 1-1 is usually employed.

Figure 1-1. Flowchart of Inner-Product Computation by the General Purpose Processors

In a general purpose (GP) processor, all these computations are sequential and each load, multiplication or summation requires one or more clock cycles. Traditional multiplication and accumulation methods are generally used. Some GP processors provide additional hardware features for inner-product calculations. Among these processors, the Pentium MMX processor contains a super scalar architecture, which includes: 1) enhanced pipelines 2) two pipelined integer units capable of two instructions per clock, as well as other features. With the new architecture, the Pentium MMX can compute inner-products more efficiently than other general purpose processors. The diagram of inner-product implementation by the Pentium MMX processor is shown as Figure 1-2 [91]:

|            | Vector Dot P      | 17777777777777777777777777777777777 |

|------------|-------------------|-------------------------------------|

| <b>e</b> 5 | e4 e3 e2 e1 e0    | ←_ a_vector                         |

| Step 1     |                   | → MMX ™ register                    |

| <b>b</b> 5 | b4 b3 b2 b1 b0    | ⊷ b_vector                          |

| Step 2     |                   | MMX * register                      |

|            | adri en Darbert i |                                     |

|            | e3 e2 e1 e0 *     | b3 b2 b1 b0                         |

| Step 3     | e3*b3+e2*b2       | e1*b1+e0*b0                         |

|            | ale a statut      |                                     |

|            | e3*b3+e2*b2       | a1*b1+a0*b0                         |

|            | +                 |                                     |

| Step 4     | Σ prev. loops     | E prev. loops                       |

#### Figure 1-2. Inner-Product Implementation in Pentium MMX Processor [91]

Sample code [91] for an inner-product implementation using Pentium assembly

language is shown Figure 1-3:

loop: 1 movq MMO, [a\_vector] 2 movq MM1, [b\_vector] 3 pmaddwd MMO, MM1 4 paddd MM7, MMO 5 add [a\_vector], 8 6 add [b\_vector], 8 7 sub [count], 4 8 jnz loop 9 movq MMO, MM7 10 psrlq MM7, 32 ll paddd MM7, MM0 12 movd mem\_vdp, MM7

Figure 1-3. Sample Code for an Inner-Product by Pentium MMX [91]

# 1.2 Inner-Product Implementation by Digital Signal Processing Processors

DSP processors are specifically designed for DSP applications. One typical DSP processor is the Texas Instruments TMS320C60. It is a highly integrated, multiprocessor, single chip device specifically designed for DSP applications. The TMS320C60 integrates the following components onto a single device [92]:

- 1. a single 32-bit RISC master processor (MP) with an integral IEEE-754 floating point unit

- 2. four 32-bit integer DSP parallel processors (PP)

- 3. a sophisticated direct memory access (DMA) transfer controller (TC)

- 4. a video controller (VC)

[A1]

5. 50K bytes of on-chip SRAM memory

The five processors on the TMS320C60, i.e. the MP and four PPs, can be configured for a variety of multiple-instruction, multiple-data, multiple-instruction, single-data, or single-instruction, multiple-data modes. The PPs, similar to most DSPs, perform all operations, except division, in a single cycle. For example, it can perform the parallel operations, A\*B =>C and A+1 => A in one clock cycle, while in a general purpose processor, at least two cycles are required. Sample code of the fixed-point innerproduct computation is shown Figure 1-4 [92].

| ZERC | ) .L1 | A7             |                                             |

|------|-------|----------------|---------------------------------------------|

| LDH  | .D1   | *A4++,A2       | ;load ai from memory                        |

| LDH  | .D1   | *A3++,A5       | ;load b <sub>i</sub> from memory            |

| MPY  | .M1   | A2,A5,A6       | ; a <sub>i</sub> * b <sub>i</sub>           |

| ADD  | .L1   | A6,A7,A7       | ; sum += (a <sub>i</sub> * b <sub>i</sub> ) |

| SUB  | .S1   | A1,1,A1; decre | ment loop counter                           |

| В    | .S2   | LOOP           | ; branch to loop                            |

While DSP processors allow flexibility, for some applications that require high speed inner-product computation, FPGAs or ASICs can provide higher performance options.

## 1.3 Other Inner-Product Processor Implementation Methods

Besides the inner-product implementations on general purpose processors and DSP processors, other arithmetic and implementations of inner-product processors have been investigated. Ahmad and Poornalah [8] proposed an inner-product implementation using array multipliers. Although the array multipliers provide convenient layout for VLSI, this method may not be a good option in high-performance requirements for inner-product computation because of its high latency. Fahmi, *et al.*, [11] and Haynal and Parhami [12] investigated serial implementations of an inner-product processor. The designs result in a small area but has a high latency. Inner-product implementations based on distributed arithmetic are proposed by Burleson *et al.*, [13] and Vega, *et al.*, [14]. Various inner-product implementations using carry-save adders are investigated by many researchers [15]-[19]. Application specific inner-product processors are studied in [21]-[25] and redundant binary implementations are proposed in [28],[29]. In this research, which is focused upon the high-performance implementation of an inner-product processors will be reviewed and compared.

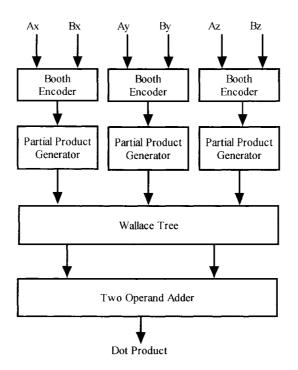

With a carry-save adder structure, Kazakova [15] investigated a fast and lowpower three-dimensional inner-product processor. This processor consists of Booth encoders, a Wallace reduction tree, and a final two-operand adder. Its structure is shown in Figure 1-5.

Figure 1-5. Kazakova's Inner-Product Processor Architecture [15]

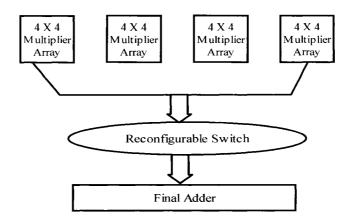

A novel approach for high-performance inner-product processor, which is dynamically reconfigurable, was proposed by Lin [24],[25]. This processor mainly consists of an  $8 \times 8$  or  $4 \times 4$  array of small multipliers plus two or three arrays of adders. It requires very simple reconfigurable components. The entire summation network can be reconfigured by using a few control bits for the desired computations, where the reconfiguration can be done dynamically. The design is regular, modular, and, it can easily be pipelined. The diagram is shown in Figure 1-6.

Since the implementation of an array multiplier has a high latency, compared to the design of carry-save addition and redundant binary representation, this proposed inner-product processor has a high latency.

Figure 1-6. Lin's Reconfigurable Inner-Product Processor [24],[25]

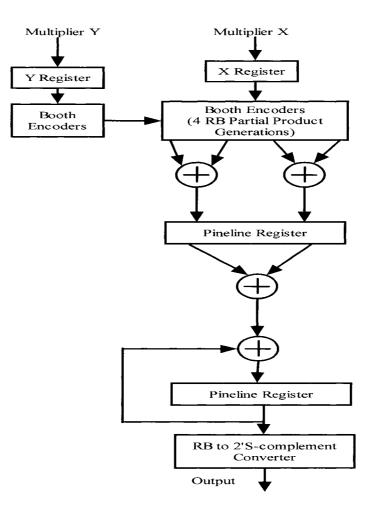

Figure 1-7. A RB MAC (Multiply and Accumulate) by Huang [2] Based upon redundant binary numbers and the Booth encoding, Huang [2] proposed a high-performance, two-stage pipelined MAC (Multiply and Accumulate) unit,

which is shown in Figure 1-7. Later, Sacristan [29] further developed this structure as a reusable inner-product unit for multipliers with different sizes of word length.

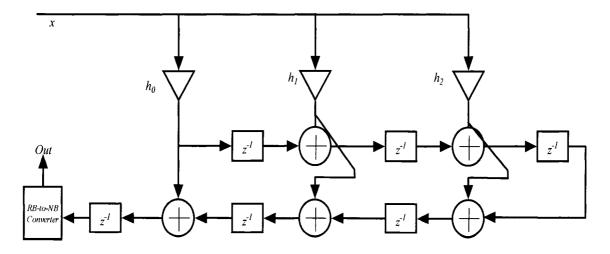

Baik *et al.* [28] proposed a redundant binary implementation of an FIR filter. The diagram is shown in Figure 1-8 (See Section 2.1.4. for further discussion):

Figure 1-8. Baik's Redundant Binary Filter Implementation [28]

## 1.4 Multiplier Implementation Review

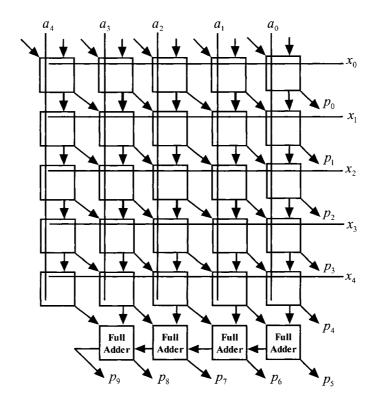

Multiplication is the key operation in the implementation of inner-product computation. Three popular implementations for multipliers are an array multiplier [85],[93], a multiplier using a Wallace tree [94] and a multiplier using redundant binary number representation [1],[4]. An array multiplier has good repeatability of unit cells and is very regular in its structure. It uses only short wires that connect one full adder to horizontally, vertically, or diagonally adjacent full adders. Thus, it results in a very simple and efficient layout in VLSI implementation. However, the *N*-bit multiplication time is linearly proportional to *N*. This method requires a long computation time for larger *N*'s. Figure 1-9 [85] is a design of  $5 \times 5$  unsigned multiplier:

Figure 1-9. Design of a 5×5 Array Multiplier [85],[93]

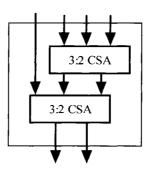

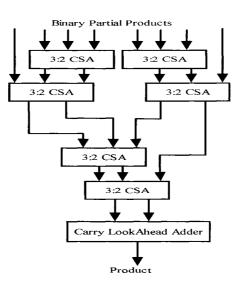

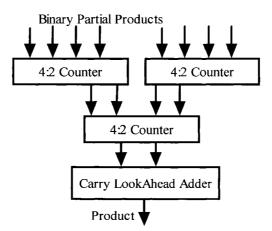

The Wallace-tree method is commonly used to realize high-speed multiplication. The basic cell in Wallace-tree multiplication is 3-to-2 or 4-to-2 CSA (Carry Save Adder), also called 3:2 or 4:2 counter. A 3:2 counter can be realized by a full adder, which reduces three numbers to two numbers while a 4:2 counter can be realized by two 3:2 counters, as shown in Figure 1-10 [85]. Figure 1-11 and Figure 1-12 are  $4 \times 4$  multipliers, using 3:2 counters and 4:2 counters.

Figure 1-10. 4:2 Counter Using 3:2 Counter [94]

Figure 1-11. 3:2 Counter Based 4×4 Multiplier [85]

Figure 1-12. 4:2 Counter Based 4×4 Multiplier [85]

The traditional Wallace-tree method uses a 3:2 counter. This scheme results in a complicated interconnection between three-input/two-output counters. This makes the VLSI layout difficult and inefficient. The extended layout process increases the design complexity. As the multipliers increase in bit length, the interconnection becomes exponentially complicated. To solve this problem with conventional Wallace-trees, the following two methods have been proposed. One method is to use 4:2 counters [94] instead of 3:2 counters [94]. The use of 4:2 counters simplifies the interconnection

drastically because the partial products are added using a binary tree. Another method is to use redundant binary representation for the partial products [1], [3], [4]. The use of the RB simplifies the interconnection because the RB partial products can be summed using an RB adder tree. The *N*-bit multiplication time of RB multipliers and Wallace-tree multipliers is proportional to  $log_2N$ . The physical layout of a RB multiplier has good repeatability. The RB multiplier does not require any optional sign bits for adding partial products. Makino's research [3] indicates that a 54×54-bit multiplier using redundant binary number representation is faster than the conventional 4:2 counter-based multiplier and has lower power dissipation. The power dissipation of 540 mW is estimated for the 54×54 RB multiplier operating at 100 MHz. These figures are more than 12% faster speed and 38% lower power than the conventional CSA multipliers.

Using redundant binary representation in our research results in an easily controlled/reconfigurable high-performance computing structure capable of handling various computations for both real and complex numbers.

## 1.5 The Redundant Binary Number System

Redundant binary (RB) representation is one of the signed-digit (SD) number systems originally introduced by Avizienis [69], which provides carry-propagation-free (CPF) addition. In a signed-digit system, the individual digits have negative as well as positive values. Given a radix-(r) signed-digit number, each digit of the signed-digit number can take one of the following  $2\alpha + 1$  values:

$$\{-\alpha, ..., -1, 0, 1, ..., \alpha\}$$

(1.2)

where the magnitude of a positive integer  $\alpha$  must be within the following interval:

$$\left\lfloor \frac{r}{2} \right\rfloor \le \alpha \le r - 1 \tag{1.3}$$

The radix-(2) signed-digit system (Redundant Binary (RB) representation) uses the digit set {-1, 0, 1} to represent numbers. The SD number system is also called redundant because a given integer number may have more than one representation. For example, the radix-(2) integer, (7)<sub>10</sub>, can be represented in several ways, e.g.,  $[0\ 1\ 1\ 1]_{RB}$ ,  $[1\ 0\ 0\ -1]_{RB}$ , or  $[1\ -1\ 1\ 1]_{RB}$ . Based on the SD redundancy property, addition rules can be devised so that carry propagation is limited to only one digit position, thereby eliminating the possibility of a carry from the LSD (Least-Significant-Digit) to the MSD (Most-Significant-Digit). In a RB adder circuit implementation, the addition time is fixed and does not depend on the word length. Also, no explicit mechanism to handle the overall sign of a signed-digit number is required since it is determined by the most significant non-zero digit. Since the multiplication of two numbers is generally performed by the addition of partial products, the carry-propagation-free (CPF) feature of the RB arithmetic can be used to design high-speed multipliers [1], [3], [4] and multiply-andaccumulate (MAC) units [2].

The algorithmic rules for the RB addition are defined by Takagi, et al., [4]. Basically, two steps are required. In the first step, the intermediate carry-out,  $\chi_i \in \{-1, 0, 1\}$ , and the intermediate sum digit,  $\sigma_i \in \{-1, 0, 1\}$ , is generated at each position and satisfy the equation:

$$\alpha_i + \beta_i = 2\chi_i + \sigma_i \tag{1.4}$$

where  $\alpha_i$  and  $\beta_i$  are the RB augend and addend digits, respectively. Note that for increased speed, the circuit implementation may utilize the next lower order digits,

$\alpha_{i-1}$  and  $\beta_{i-1}$ , to determine the carry-out from that digit position. Table 1-A describes these rules of step 1 in detail. In the second step, the final sum digit  $\zeta_i$  is obtained at each position by adding the intermediate sum digit,  $\sigma_i$ , and the intermediate carry,  $\chi_{i-1}$ , from the next-lower-order position, without generating a carry. That is,

$$\zeta_i = \sigma_i + \chi_{i-1} \tag{1.5}$$

| Table 1-A. Computation Rules for the First Step in Carry-Propagation-Free |  |  |  |  |

|---------------------------------------------------------------------------|--|--|--|--|

| Addition for RB Numbers [1]                                               |  |  |  |  |

|                                                                           |  |  |  |  |

| Туре | Augend<br>digit | Addend<br>digit | Digits at the next-<br>lower-order | Intermediate<br>carry | Intermediate<br>sum digit |

|------|-----------------|-----------------|------------------------------------|-----------------------|---------------------------|

|      | $\alpha_{i}$    | $\beta_i$       | position                           | $(\chi_i)$            | $(\sigma_i)$              |

|      |                 |                 | $(\alpha_{i-1},\beta_{i-1})$       |                       |                           |

| <1>  | 1               | 1               |                                    | 1                     | 0                         |

| <2>  | 1               | 0               | Both are negative                  | 0                     | 1                         |

| ~2~  | 0               | 1               | All other cases                    | 1                     | -1                        |

| <3>  | 0               | 0               |                                    | 0                     | 0                         |

| <4>  | 1<br>-1         | -1<br>1         |                                    | 0                     | 0                         |

| <5>  | 0               | -1              | Both are negative                  | -1                    | 1                         |

| <32  | -1              | 0               | All other cases                    | 0                     | -1                        |

| <6>  | -1              | -1              |                                    | -1                    | 0                         |

In general, throughout this dissertation, RB numbers are expressed using Greek symbols.

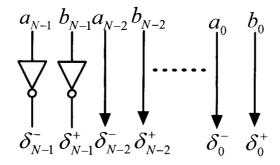

# 1.6 The Conversion of 2's-Complement to Redundant Binary

A limited precision RB number,  $\Delta$ , can be derived from the addition of a pair of *N*-bit 2's-complement numbers *A* and *B* [2].

$$(A+B)_{2c} = A - (-B)_{2c}$$

=  $A - (\overline{B}+1)$

=  $A - \overline{B} - 1$

=  $\left(-a_{N-1}2^{N-1} + \sum_{i=0}^{N-2}a_i2^i\right) + \left(\overline{b_{N-1}}2^{N-1} - \sum_{i=0}^{N-2}\overline{b_i}2^i\right) - 1$  (1.6)

=  $\left(-a_{N-1} + \overline{b_{N-1}}\right)2^{N-1} + \left(\sum_{i=0}^{N-2}(a_i - \overline{b_i})2^i\right) - 1$

=  $\left(\delta_{N-1}2^{N-1} + \sum_{i=0}^{N-2}\delta_i2^i\right) - 1$

=  $\Delta - 1$

where  $\delta_{N-1} = -a_{N-1} + \overline{b_{N-1}}$ ,  $\delta_i = a_i - \overline{b}_i$  for  $0 \le i \le N-2$ , 2c is the 2's-complement operations,  $\overline{B}$  is the 1's-complement operations,  $\overline{b}_i$  is the bit-complement, and -1 can be considered as a -1 carry-in to a subsequent RB addition. For inner-product calculations, the -1 correction is applied in the RB partial product adder tree.

The binary-signed digits can be encoded into binary in several ways. In this work, the binary signed digits  $\{-1, 0, 0, 1\}$  are coded as  $\{00, 01, 10, 11\}$ , respectively, as given in Table 1-B. Another encoding method is to encode redundant binary number in signed-magnitude [28], that is, to encode  $\{-1, 0, 0, 1\}$  as  $\{11,00,10,01\}$ . It is less efficient to map 2C to RB for signed-magnitude encoding. See Section 2.1.4 for further discussions.

| <i>a</i> value | Encoded $a^-a^+$ |

|----------------|------------------|

| -1             | 0 0              |

| 0              | 0 1              |

| 0              | 1 0              |

| 1              | 1 1              |

Examining Equation (1.6), beginning with the  $\delta_i$  term, the signed digits are encoded using the relationship,  $\delta_i = a_i - \overline{b_i}$ , where  $\delta_i$  is a binary signed digit,  $\delta_i \in \{-1, 0, 1\}$ . The mapping equations for  $\delta_i^-$  and  $\delta_i^+$  are [2],[49],[50]

$$\delta_i^- = a_i$$

$$\delta_i^+ = b_i \quad \text{for } 0 \le i \le N - 2$$

(1.7)

Similarly, in the Most Significant Digit (MSD) term of Equation (1.6),  $\delta_{N-1}$  is encoded with the mapping equations

$$\delta_{N-1}^{-} = \overline{a_{N-1}}$$

$$\delta_{N-1}^{+} = \overline{b_{N-1}}$$

(1.8)

The structure of mapping the sum of two 2's-complement binary numbers to a RB number is shown in Figure 1-13:

#### Figure 1-13. Mapping from the Sum of Two 2's-Complement Numbers to a RB Number

Note that a single 2's-complement number, A, is converted directly into a RB

number  $\Delta$  in Equation (1.9):

$$\delta_{N-1}^{+} = \overline{a_{i}}, \ \delta_{N-1}^{-} = 0$$

$$\delta_{i-1}^{+} = a_{i}, \ \delta_{i}^{-} = 1 \quad (0 \le i \le N - 2)$$

(1.9)

For example, a 2's-complement number  $(00000101)_{2C}$  is converted directly into a RB number  $(01\ 01\ 01\ 01\ 01\ 11\ 01\ 11)_{RB}$ .

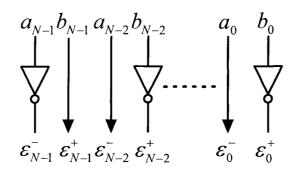

The subtraction of two *N*-bit 2's-complement numbers can also be represented by a redundant binary number:

$$E = (A - B)_{2c} = \left( -a_{N-1} 2^{N-1} + \sum_{i=0}^{N-2} a_i 2^i \right) + \left( b_{N-1} 2^{N-1} - \sum_{i=0}^{N-2} b_i 2^i \right)$$

=  $(-a_{N-1} + b_{N-1}) 2^{N-1} + \sum_{i=0}^{N-2} (a_i - b_i) 2^i$  (1.10)

=  $\varepsilon_{N-1} 2^{N-1} + \sum_{i=0}^{N-2} \varepsilon_i 2^i$

where  $\varepsilon_{N-1} = -a_{N-1} + b_{N-1}$  and  $\varepsilon_i = a_i - b_i$  for  $0 \le i \le N - 2$ .

The mapping equations for the encoded  $\varepsilon_i$ ,  $(0 \le i \le N-1)$  in Equation (1.10) are:

$$\varepsilon_i^- = a_i$$

$$\varepsilon_i^+ = \overline{b_i} \text{ for } 0 \le i \le N - 2$$

(1.11)

and

The structure of mapping the subtraction of two 2's-complement binary numbers to a RB number is shown in Figure 1-14.

Figure 1-14. Mapping from the Subtraction of Two 2's-Complement Numbers to a RB Number

Based on this coding for RB numbers, the logic functions of a RBFA (RB full adder) and RBHA (RB half adder) are obtained [49] and shown in Table 1-C for the sum,  $z_i$ , with inputs x and y. Boolean variables, g and h, are used as intermediate variables to simplify the equations for the carry, c, and sum, z. Note, in Table 1-C, the notation used is the same as [49] but corrects the RBHA equations found in [49].

| RBFA                                                     | RBHA                                                                            |

|----------------------------------------------------------|---------------------------------------------------------------------------------|

| $g_i = (x_i^- \oplus x_i^+) \oplus (y_i^- \oplus y_i^+)$ | $\overline{z_i^-} = (\overline{x_i^- \oplus x_i^+}) \oplus \overline{y_i^-}$    |

| $h_i = x_i^- x_i^+ + y_i^- y_i^+$                        | $z_i^+ = y_i^+$                                                                 |

| $z_i^- = g_i \oplus c_{i-1}^-$                           | $c_i^- = x_i^- + x_i^+$                                                         |

| $z_i^+ = c_{i-1}^+$                                      | $c_i^+ = (\overline{x_i^- \oplus x_i^+})y_i^- + (x_i^- \oplus x_i^+)x_i^-x_i^+$ |

| $c_i^- = (x_i^- + x_i^+)(y_i^- + y_i^+)$                 |                                                                                 |

| $c_i^+ = g_i c_{i-1}^- + \overline{g_i} h_i$             |                                                                                 |

Table 1-C. Logic Functions for RBFA and RBHA

In this work, a novel, high-performance, fixed-point, inner-product processor based upon a redundant binary number system will be investigated. Similar to Baik's [28] methods, this scheme decreases the number of partial products by 50%, while achieving better speed and area performance and providing pipeline extension opportunities. When modified Booth encoding is used, partial products are reduced by almost 75%, thereby significantly reducing the multiplier addition depth. This design is well suited for VLSI implementation, and it can also be embedded as an inner-product core inside a general purpose DSP FPGA-based processor. This inner-product processor can be easily reconfigured for different computations, such as real number inner-product computations, parallel real number multipliers, complex number multipliers, complex number innerproduct processors, redundant binary multipliers, redundant binary inner-product processors, etc. Chapter 2 proposes a fixed-point number inner-product processor. Computational structures for both real and complex number inner-products for both 2's-complement and unsigned integers is presented. A new division method using the IP structure is investigated in Chapter 3. Two convergence division methods — Goldschimdt and Newton-Raphson are compared. Chapter 4 discusses extended computations, such as parallel multiplications, inner-product processors using the inner-product processor for real, complex and redundant binary numbers. In Chapter 5, an improved redundant binary number to 2's-complement number converter is discussed. Chapter 6 provides a summary of contributions and future research directions for this work. The implementation of the redundant binary IP processor for real and complex number and the Goldschmidt division unit using the IP processor have been implemented using VHDL on Xilinx FPGA. The original contributions of this research are:

- IP processor reduces the number of partial products.

- A unified signed/unsigned 2's-complement/RB multiplier is developed using this IP structure.

- With the same IP structure, a novel Goldschmidt high-performance division circuit is developed.

- This IP structure can be used to build a multi-purpose dynamical processor for real, complex and redundant binary number computations.

- An improved 2's-complement to RB converter is proposed.

# Chapter 2 Inner-Product Processor of Real, Complex and Redundant Binary Numbers

#### 2.1 Real Number Inner-Product Computation

Consider an inner-product for an M dimensional (M=even), N-bit real vectors (N

even), A and B, where  $A = (A_0, A_1, A_2, ..., A_{M-1})$  and  $B = (B_0, B_1, B_2, ..., B_{M-1})$  with

$$A_{i} = (a_{N-1,i} \ a_{N-2,i} \ a_{N-3,i} \ \dots a_{1,i} \ a_{0,i}) \text{ and } B_{i} = (b_{N-1,i} \ b_{N-2,i} \ b_{N-3,i} \ \dots b_{1,i} \ b_{0,i})$$

(2.1)

where  $A_i$  and  $B_i$  are real numbers.

The real inner-product is defined as:

$$< A, B > = (A_0 \ A_1 \ \cdots \ A_{M-2} \ A_{M-1}) \bullet (B_0 \ B_1 \ \cdots \ B_{M-2} \ B_{M-1}) = \sum_{i=0}^{M-1} A_i B_i$$

(2.2)

Two basic approaches exist for performing the necessary inner-product multiplications using redundant binary arithmetic. The first method uses *inline* conversion or mapping of 2's-complement partial products into a redundant binary number for each multiplication of  $A_iB_i$ . The second method combines or maps equivalent 2's-complement partial products into a redundant binary number *across* the  $A_iB_i$  pairs [49]. Both approaches are considered in the following sections.

#### 2.1.1 Inline Partial Product Redundant Binary Inner-Product

Considering the simple case of M = 2,  $A_0B_0 + A_1B_1$ , we first compute the redundant binary products for  $A_0B_0$  and  $A_1B_1$ , and then add the RB products together to produce the inner-product. Redundant binary partial products are generated by mapping even/odd pairs of 2's-complement partial product sums. For *N*-bit numbers, the product of *AB* is expanded in the following equations:

$$AB = (-a_{N-1}2^{N-1} + \sum_{i=0}^{N-2} a_i 2^i)(-b_{N-1}2^{N-1} + \sum_{i=0}^{N-2} b_i 2^i)$$

=  $(-a_{N-1}b_02^{N-1} + \sum_{i=0}^{N-2} a_i b_0 2^i)2^0 + (-a_{N-1}b_12^{N-1} + \sum_{i=0}^{N-2} a_i b_1 2^i)2^1 + (-a_{N-1}b_22^{N-1} + \sum_{i=0}^{N-2} a_i b_2 2^i)2^2 + (-a_{N-1}b_32^{N-1} + \sum_{i=0}^{N-2} a_i b_3 2^i)2^3 + \dots$

......

$(-a_{N-1}b_{N-2}2^{N-1} + \sum_{i=0}^{N-2} a_i b_{N-2} 2^i)2^{N-2} + (a_{N-1}b_{N-1}2^{N-1} - \sum_{i=0}^{N-2} a_i b_{N-1} 2^i)2^{N-1}$

Denote the 2's-complement partial products as:

$$PP_{0} = (-a_{N-1}b_{0}2^{N-1} + \sum_{i=0}^{N-2}a_{i}b_{0}2^{i})2^{0}, PP_{1} = (-a_{N-1}b_{1}2^{N-1} + \sum_{i=0}^{N-2}a_{i}b_{1}2^{i})2^{1}$$

$$PP_{2} = (-a_{N-1}b_{2}2^{N-1} + \sum_{i=0}^{N-2}a_{i}b_{2}2^{i})2^{2}, PP_{3} = (-a_{N-1}b_{3}2^{N-1} + \sum_{i=0}^{N-2}a_{i}b_{3}2^{i})2^{3}$$

.....

(2.3)

$$PP_{N-2} = (-a_{N-1}b_{N-2}2^{N-1} + \sum_{i=0}^{N-2} a_i b_{N-2}2^i)2^{N-2}, PP_{N-1} = (a_{N-1}b_{N-1}2^{N-1} - \sum_{i=0}^{N-2} a_i b_{N-1}2^i)2^{N-1}$$

Consider the first N-2 even/odd partial products,  $PP_{2j}$  and  $PP_{2j+1}$ , where  $j=0,1,2,...,\frac{N-4}{2}$ . To align the 2's-complement partial products, the sign of the even partial products is extended, and a low order zero is appended to the odd partial products:

$$PP_{2j} = (-a_{N-1}b_{2j}2^{N-1} + \sum_{i=0}^{N-2}a_ib_{2j}2^i)2^{2j}$$

= $(-a_{N-1}b_{2j}2^N + a_{N-1}b_{2j}2^{N-1} + \sum_{i=0}^{N-2}a_ib_{2j}2^i)2^{2j}$

$$PP_{2j+1} = (-a_{N-1}b_{2j+1}2^{N-1} + \sum_{i=0}^{N-2}a_ib_{2j+1}2^i)2^{2j+1}$$

= $(-a_{N-1}b_{2j+1}2^N + a_{N-2}b_{2j+1}2^{N-1} + \sum_{i=1}^{N-2}a_{i-1}b_{2j+1}2^i + 0)2^{2j}$

(2.4)

Combining even/odd 2's-complement partial product pairs according to Equation (1.6), we have:

-

$$PP_{2j} + PP_{2j+1} = \{(-a_{N-1}b_{2j} + \overline{a_{N-1}b_{2j+1}})2^{N} + \sum_{i=1}^{N-1}(a_{i}b_{2j} - \overline{a_{i-1}b_{2j+1}})2^{i} + a_{0}b_{2j} - 1 - 1\}2^{2j}$$

$$= (\alpha_{N,2j}2^{N} + \sum_{i=1}^{N-1}\alpha_{i,2j}2^{i} + \alpha_{0,2j} - 1)2^{2j}$$

(2.5)

where,

$$\alpha_{N,2j} = -a_{N-1}b_{2j} + \overline{a_{N-1}b_{2j+1}}$$

$$\alpha_{i,2j} = a_i b_{2j} - \overline{a_{i-1}b_{2j+1}}, \qquad 1 \le i \le N-1 \qquad (2.6)$$

$$\alpha_{0,2j} = a_0 b_{2j} - 1$$

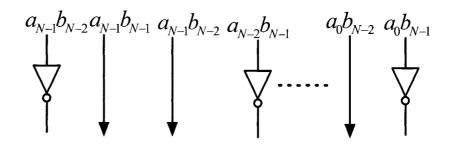

Encoding the redundant binary coefficients,  $\alpha_i$ , using two binary bits, all but the final RB partial product is encoded as:

For

$$j = 0, 1, ..., \frac{N-4}{2}$$

,

$\alpha_{N,2j}^{+} = \overline{a_{N-1}b_{2j}}, \quad \alpha_{N,2j}^{-} = \overline{a_{N-1}b_{2j+1}},$

$\alpha_{i,2j}^{+} = a_{i}b_{2j}, \quad \alpha_{i,2j}^{-} = a_{i-1}b_{2j+1}, \quad 1 \le i \le N-1$

$\alpha_{0,2j}^{+} = a_{0}b_{2j}, \quad \alpha_{0,2j}^{-} = 0$

$$(2.7)$$

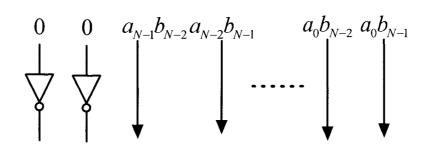

Now, consider the last two 2's-complement partial products,  $PP_{N-2}$  and  $PP_{N-1}$ :

$$PP_{N-2} + PP_{N-1} = (-a_{N-1}b_{N-2}2^{N} + a_{N-1}b_{N-2}2^{N-1} + \sum_{i=0}^{N-2} a_{i}b_{N-2}2^{i})2^{N-2} + (a_{N-1}b_{N-1}2^{N} - a_{N-2}b_{N-1}2^{N-1} - \sum_{i=1}^{N-2} a_{i-1}b_{N-1}2^{i})2^{N-2} = \{(-a_{N-1}b_{N-2} + a_{N-1}b_{N-1})2^{N} + \sum_{i=1}^{N-1} (a_{i}b_{N-2} - a_{i-1}b_{N-1})2^{i} + a_{0}b_{N-2} - 0\}2^{N-2} = \beta_{N} + \sum_{i=1}^{N-1} \beta_{i}2^{i} + \beta_{0}$$

$$(2.8)$$

where,

$$\beta_{N} = -a_{N-1}b_{N-2} + a_{N-1}b_{N-1}, \ \beta_{i} = a_{i}b_{N-2} - a_{i-1}b_{N-1}, \ (1 \le i \le N-1), \beta_{0} = a_{0}b_{N-2} - 0 \quad (2.9)$$

Encoding the redundant binary coefficients,  $\beta_i$ , using two binary bits, the final RB partial product is:

$$\beta_{N}^{+} = a_{N-1}b_{N-2}, \quad \beta_{N}^{-} = a_{N-1}b_{N-1},$$

$$\beta_{i}^{+} = a_{i}b_{N-2}, \quad \beta_{i}^{-} = \overline{a_{i-1}b_{N-1}}, \qquad 1 \le i \le N-1$$

$$\beta_{0}^{+} = a_{0}b_{N-2}, \quad \beta_{0}^{-} = 1$$

(2.10)

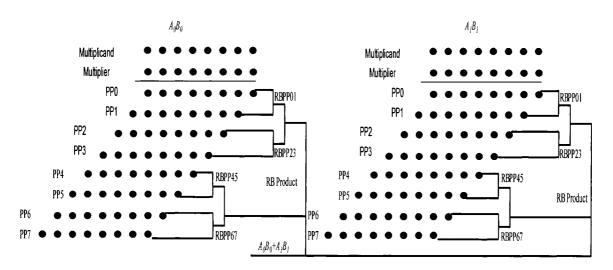

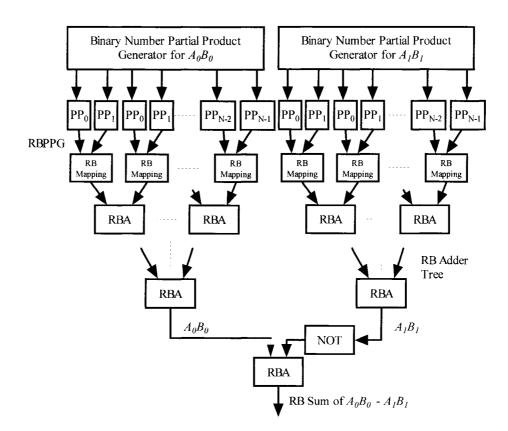

Figure 2-1 shows the RB implementation diagram of  $A_0B_0 + A_1B_1$  for 8-bit numbers and Figure 2-2 shows the hardware implementation of  $A_0B_0 + A_1B_1$  with the inline redundant binary partial product generation (RBPPG) using 2's-complement even/odd partial products. If the final redundant binary adder (RBA) is bypassed, the circuit in Figure 2-2 can also perform the separate multiplications,  $A_0B_0$  and  $A_1B_1$ .

Figure 2-1. Inline Partial Product RB Implementation of  $A_{\theta}B_{\theta} + A_{I}B_{I}$

Defining the redundant binary number  $\Delta_j = A_{2j}B_{2j} + A_{2j+1}B_{2j+1}$ , the general form of the inline multiplication inner-product is given by:

$$\langle \boldsymbol{A}, \boldsymbol{B} \rangle = \sum_{j=0}^{M-1} A_i B_i = \sum_{j=0}^{\frac{M}{2}-1} (A_{2j} B_{2j} + A_{2j+1} B_{2j+1}) = \sum_{j=0}^{\frac{M}{2}-1} \Delta_j$$

(2.11)

Figure 2-2. Inline Partial Product Structure of  $A_{\theta}B_{\theta} + A_{I}B_{I}$

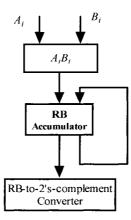

To realize the inner-product, all of the redundant binary numbers,  $\Delta_j$ , are added using a redundant binary adder tree, and the final sum of the redundant binary numbers can be converted into a 2's-complement number using a RB-NB converter [5],[7],[12]. Figure 2-3 depicts the overall architecture of the RB inner-product circuit showing the RB adder tree, a RB accumulator, a RB-to-2's-complement converter, and additional data paths that might exist when the circuit is implemented in a DSP core.

Figure 2-3. Overall Structure of the Redundant Binary Inner-Product

# 2.1.2 Cross Partial Product Redundant Binary Inner-Product

An alternative method for mapping 2's-complement partial products to redundant binary partial products is to combine like partial products across the  $A_jB_j$  and  $A_{j+1}B_{j+1}$ pairs. The method derived here is similar to that provided by Shin and Jeon [50] for complex number multiplication. Consider the simple case of M=2,  $A_0B_0 + A_1B_1$ , and expand it as:

$$\begin{aligned} A_{0}B_{0} + A_{1}B_{1} \\ &= (-a_{N-1,0}2^{N-1} + \sum_{i=0}^{N-2} a_{i,0}2^{i})(-b_{N-1,0}2^{N-1} + \sum_{i=0}^{N-2} b_{i,0}2^{i}) + \\ &\quad (-a_{N-1,1}2^{N-1} + \sum_{i=0}^{N-2} a_{i,1}2^{i})(-b_{N-1,1}2^{N-1} + \sum_{i=0}^{N-2} b_{i,1}2^{i}) \\ &= 2^{N-1}\{a_{N-1,0}b_{N-1,0}2^{N-1} + \sum_{i=0}^{N-2} (-a_{i,0}b_{N-1,0})2^{i} + a_{N-1,1}b_{N-1,1}2^{N-1} + \sum_{i=0}^{N-2} (-a_{i,1}b_{N-1,1})2^{i}\} + \\ &\sum_{i=0}^{N-2} 2^{i}\{b_{i,0}(-a_{N-1,0}2^{N-1} + \sum_{j=0}^{N-2} a_{j,0}2^{j}) + b_{i,1}(-a_{N-1,1}2^{N-1} + \sum_{j=0}^{N-2} a_{j,1}2^{i})\} \\ &= 2^{N-1}\{(a_{N-1,0}b_{N-1,0} + a_{N-1,1}b_{N-1,1})2^{N-1} + \sum_{i=0}^{N-2} (-a_{i,0}b_{N-1,0} - a_{i,1}b_{N-1,1})2^{i}\} + \\ &\sum_{i=0}^{N-2} 2^{i}\{(-a_{N-1,0}b_{i,0} - a_{N-1,1}b_{i,1})2^{N-1} + \sum_{j=0}^{N-2} (a_{j,0}b_{i,0} + a_{j,1}b_{i,1})2^{j}\} \end{aligned}$$

Consider the first term of Equation (2.12),

$$2^{N-1} \{ (a_{N-1,0}b_{N-1,0} + a_{N-1,1}b_{N-1,1}) 2^{N-1} + \sum_{i=0}^{N-2} (-a_{i,0}b_{N-1,0} - a_{i,1}b_{N-1,1}) 2^i \}$$

$$= -2^{N-1} \{ (-a_{N-1,0}b_{N-1,0}) 2^{N-1} + \sum_{i=0}^{N-2} (a_{i,0}b_{N-1,0}) 2^i + (-a_{N-1,1}b_{N-1,1}) 2^{N-1} + \sum_{i=0}^{N-2} (a_{i,1}b_{N-1,1}) 2^i \}$$

$$= 2^{N-1} \{ (a_{N-1,0}b_{N-1,0} - \overline{a_{N-1,1}b_{N-1,1}}) 2^{N-1} + \sum_{i=0}^{N-2} (-a_{i,0}b_{N-1,0} + \overline{a_{i,1}b_{N-1,1}}) 2^i + 1 \}$$

$$= 2^{N-1} \{ \kappa_{N-1,0} 2^{N-1} + \sum_{i=0}^{N-2} \kappa_{i,0} 2^i + 1 \}$$

(2.13)

where  $\kappa_{i,0}$  is a redundant binary number and ,

$$\kappa_{N-1,0} = a_{N-1,0}b_{N-1,0} - \overline{a_{N-1,1}b_{N-1,1}}$$

, and  $\kappa_{i,0} = -a_{i,0}b_{N-1,0} + \overline{a_{i,1}b_{N-1,1}}$  for  $0 \le i \le N-2$  (2.14)

Encoding the redundant binary numbers,  $\kappa_{\scriptscriptstyle N-1,0}$  and  $\kappa_{\scriptscriptstyle i,0}$  , the Boolean equations are

$$\kappa_{n,0}^{-} = a_{N-1,0} b_{N-1,0}, \quad \kappa_{N-1,0}^{+} = a_{N-1,1} b_{N-1,1},$$

$$\kappa_{i,0}^{-} = \overline{a_{i,0}} b_{N-1,0}, \quad \text{and} \quad \kappa_{i,0}^{+} = \overline{a_{i,1}} b_{N-1,1}$$

(2.15)

Considering the second term of Equation (2.12), and using Equation (1.6),

$$\sum_{i=0}^{N-2} 2^{i} \{ (-a_{N-1,0}b_{i,0} - a_{N-1,1}b_{i,1})2^{N-1} + \sum_{j=0}^{N-2} (a_{j,0}b_{i,0} + a_{j,1}b_{i,1})2^{j} \}$$

$$= \sum_{i=0}^{N-2} 2^{i} \{ -a_{N-1,0}b_{i,0} + \sum_{j=0}^{N-2} (a_{j,0}b_{i,0})2^{j} - (a_{N-1,1}b_{i,1})2^{N-1} + \sum_{j=0}^{N-2} (a_{j,1}b_{i,1})2^{j} \}$$

$$= \sum_{i=0}^{N-2} 2^{i} \{ (-a_{N-1,0}b_{i,0} + \overline{a_{N-1,1}b_{i,1}})2^{N-1} + \sum_{j=0}^{N-2} (a_{j,0}b_{i,0} - \overline{a_{j,1}b_{i,1}})2^{j} - 1 \}$$

$$= \sum_{i=0}^{N-2} 2^{i} \{ \lambda_{i,N-1}2^{N-1} + \sum_{j=0}^{N-2} \lambda_{i,j}2^{j} - 1 \}$$

$$(2.16)$$

where  $\lambda_{i,j}$  ( $0 \le i \le N-2, 0 \le j \le N-1$ ) is a redundant binary number with

$$\lambda_{i,j} = a_{j,0}b_{i,0} - \overline{a_{j,1}b_{i,1}}$$

for  $0 \le j \le N-2$ , and  $\lambda_{i,N-1} = -a_{N-1,0}b_{i,0} + \overline{a_{N-1,1}b_{i,1}}$  for  $j = N-1$ .(2.17)

Encoding  $\lambda_{i,j}$  as two binary bits,  $\lambda_{i,j}^-$  and  $\lambda_{i,j}^+$ ,  $(0 \le i \le N-2, 0 \le j \le N-1)$ ,

$$\lambda_{i,N-1}^{-} = \overline{a_{N-1,0}b_{i,0}}, \quad \lambda_{i,N-1}^{+} = \overline{a_{N-1,1}b_{i,1}},$$

$$\lambda_{i,j}^{-} = a_{j,0}b_{i,0}, \text{ and } \lambda_{i,j}^{+} = a_{j,1}b_{i,1}.$$

(2.18)

The overall inner-product is expressed as:

$$\begin{aligned} A_{0}B_{0} + A_{1}B_{1} \\ &= 2^{N-1}\{(a_{N-1,0}b_{N-1,0} + a_{N-1,1}b_{N-1,1})2^{N-1} + \sum_{i=0}^{N-2}(-a_{i,0}b_{N-1,0} - a_{i,1}b_{N-1,1})2^{i}\} + \\ &\sum_{i=0}^{N-2}2^{i}\{(-a_{N-1,0}b_{i,0} - a_{N-1,1}b_{i,1})2^{N-1} + \sum_{j=0}^{N-2}(a_{j,0}b_{i,0} + a_{j,1}b_{i,1})2^{j}\} \\ &= 2^{N-1}\{\kappa_{N-1,0}2^{N-1} + \sum_{i=0}^{N-2}\kappa_{i,0}2^{i} + 1\} + \sum_{i=0}^{N-2}2^{i}\{\lambda_{i,N-1}2^{N-1} + \sum_{j=0}^{N-2}\lambda_{i,j}2^{j} - 1\} \end{aligned}$$

(2.19)

$$&= 2^{N-1}\{\kappa_{N-1,0}2^{N-1} + \sum_{i=0}^{N-2}\kappa_{i,0}2^{i}\} + \sum_{i=0}^{N-2}2^{i}\{\lambda_{i,N-1}2^{N-1} + \sum_{j=0}^{N-2}\lambda_{i,j}2^{j}\} \\ &+ 2^{N-1} - \sum_{i=0}^{N-2}2^{i} \end{aligned}$$

Since  $2^{N-1} - \sum_{i=0}^{N-2} 2^i = 1$ , Equation (2.19) becomes:

$$A_0B_0 + A_1B_1 = 2^{N-1} \{\kappa_{N-1,0} 2^{N-1} + \sum_{i=0}^{N-2} \kappa_{i,0} 2^i\} + \sum_{i=0}^{N-2} 2^i \{\lambda_{i,N-1} 2^{N-1} + \sum_{j=0}^{N-2} \lambda_{i,j} 2^j\} + 1$$

(2.20)

The adjusting term, +1, can be applied as a carry-in to the LSD of the redundant binary full adder. Figure 2-4 shows the schematic structure of the  $A_0B_0 + A_1B_1$  hardware implementation.

Figure 2-4. Cross Partial Product Structure of  $A_{\theta}B_{\theta} + A_{I}B_{I}$  [50]

Defining the redundant binary number  $\Phi_j = A_{2j}B_{2j} + A_{2j+1}B_{2j+1}$ , the general form of the cross partial product method inner-product is given by:

$$\langle \boldsymbol{A}, \boldsymbol{B} \rangle = \sum_{j=0}^{M-1} A_i B_i = \sum_{j=0}^{\frac{M}{2}-1} (A_{2j} B_{2j} + A_{2j+1} B_{2j+1}) = \sum_{j=0}^{\frac{M}{2}-1} \boldsymbol{\Phi}_j$$

(2.21)

Again, all of the redundant binary numbers,  $\Phi_j$ , are added using a redundant binary adder tree, and the final sum of the redundant numbers can be converted into a 2's-complement number using a RB-NB converter [5],[7],[12]. The same redundant binary adder tree used for the inline inner-product, shown in Figure 2-4, can be applied to the cross partial product method.

## 2.1.3 Booth Encoding Methods

To further reduce the number of partial products, the modified Booth encoding technique is used [96]. The modified Booth algorithm recodes an N-bit 2's-complement number, B, by the following equation:

$$B = -b_{N-1}2^{N-1} + \sum_{i=0}^{N-2} b_i 2^i = \sum_{i=0}^{\frac{N}{2}-1} (-2b_{2i+1} + b_{2i} + b_{2i-1})2^{2i}$$

$$= \sum_{i=0}^{\frac{N}{2}-1} Q_i 2^{2i}$$

(2.22)

where  $b_{-1} = 0$  and  $Q_i \in \{-2, -1, 0, +1, +2\}$  is determined according to the bit pattern of the 3-bit string of B as given in Table 2-A.

| $b_{i+1}$ | $b_i$ | $b_{i-1}$ | $Q_i$ |

|-----------|-------|-----------|-------|

| 0         | 0     | 0         | 0     |

| 0         | 0     | 1         | 1     |

| 0         | 1     | 0         | 1     |

| 0         | 1     | 1         | 2     |

| 1         | 0     | 0         | -2    |

| 1         | 0     | 1         | -1    |

| 1         | 1     | 0         | -1    |

| 1         | 1     | 1         | 00    |

Table 2-A.

Modified Booth Encoding Table [96]

For the inline partial product method, we apply Booth coding to find the product of A and B (assuming N is even), using Equation (2.22),

$$AB = (-a_{N-1}2^{N-1} + \sum_{k=0}^{N-2} a_k 2^k) \sum_{i=0}^{N-1} Q_i 2^{2i}$$

$$= \sum_{i=0}^{N-1} Q_i (-a_{N-1}2^{N-1} + \sum_{k=0}^{N-2} a_k 2^k) 2^{2i}$$

$$= \sum_{i=0}^{N-1} (C_i + g_i) 2^{2i}$$

(2.23)

If

$$Q_i = 1$$

,  $C_i = -a_{N-1}2^{N-1} + \sum_{k=0}^{N-2} a_k 2^k$  and  $g_i = 0$

If

$$Q_i = 2$$

,  $C_i = -a_{N-1}2^N + \sum_{k=0}^{N-2} a_k 2^{k+1}$  and  $g_i = 0$

If

$$Q_i = -1$$

,  $C_i = -\overline{a_{N-1}} 2^{N-1} + \sum_{k=0}^{N-2} \overline{a_k} 2^k$  and  $g_i = 1$  (2.24)

If

$$Q_i = -2$$

,  $C_i = -\overline{a_{N-1}}2^N + \sum_{k=0}^{N-2} \overline{a_k}2^{k+1}$  and  $g_i = 1$

Notice that  $C_i$  is a 2's-complement number. Mapping the product to redundant binary,

$$AB = \sum_{i=0}^{\frac{N}{2}-1} (C_i + g_i) 2^{2i}$$

$$= \sum_{i=0,2,4,\dots,\frac{N}{2}-2} \{ (C_i + g_i) 2^{2i} + (C_{i+1} + g_{i+1}) 2^{2i+2} \}$$

$$= \sum_{i=0,2,4,\dots,\frac{N}{2}-2} \{ (C_i + 4C_{i+1}) 2^{2i} + (g_i + 4g_{i+1}) 2^{2i} \}$$

$$= \sum_{i=0,2,4,\dots,\frac{N}{2}-2} \{ E_i 2^{2i} + (g_i + 4g_{i+1} - 1) 2^{2i} \}$$

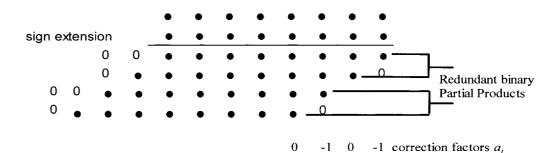

$$= \sum_{i=0,2,4,\dots,\frac{N}{2}-2} (E_{i,i+1} + \gamma_i + \gamma_{i+1}) 2^{2i}$$

(2.25)

where  $E_i$  is a redundant binary number and  $E_i - 1 = C_i + 4C_{i+1}$ . The correction factors,  $\gamma_i$  and  $\gamma_{i+1}$ , depend on the values of  $g_i$  and  $g_{i+1}$ , as shown in Table 2-B. Here, the two redundant binary Booth correction factors,  $\gamma_i$  and  $\gamma_{i+1}$ , are used since  $g_i$  and  $g_{i+1}$  can not be combined. The -1 is encoded into the  $\gamma_i$  correction factor.

| $g_i$ | $g_{i+1}$ | $\gamma_i (\gamma_i^+ \gamma_i^-)$ | $\gamma_{i+1} (\gamma_{i+1}^+ \gamma_{i+1}^-)$ |

|-------|-----------|------------------------------------|------------------------------------------------|

| 0     | 0         | -1 (0 0)                           | 0 (0 1)                                        |

| 0     | 1         | -1 (0 0)                           | 1 (1 1)                                        |

| 1     | 0         | 0 (0 1)                            | 0 (0 1)                                        |

| 1     | 1         | 0 (0 1)                            | 1 (1 1)                                        |

Table 2-B. Booth Correction Factors for the Inline Multiplication Method

Referring to Booth coding Table 2-A, the Boolean equations for the correction factors are,

$$\gamma_{i}^{+} = 0$$

$$\gamma_{i}^{-} = b_{i+1}\overline{b_{i}} \ \overline{b_{i-1}} + b_{i+1}\overline{b_{i}} \ b_{i-1} + b_{i+1}b_{i} \ \overline{b_{i-1}}$$

$$= b_{i+1} \ \overline{b_{i}b_{i-1}}$$

$$\gamma_{i+1}^{+} = b_{i+3} \ \overline{b_{i+2}b_{i+1}}$$

$$\gamma_{i+1}^{-} = 1$$

(2.26)

where  $i = 0, 2, 4, \dots, \frac{N}{2} - 2$ . After the redundant binary products of  $A_0 B_0$  and  $A_1 B_1$  are

computed, a redundant binary adder is used to compute  $A_0B_0 + A_1B_1$ .

The general form of the inline Booth encoded inner-product is,

$$\langle \boldsymbol{A}, \boldsymbol{B} \rangle = \sum_{j=0}^{M-1} A_j B_j = \sum_{j=0}^{M-1} \sum_{i=0,2,4,\dots,\frac{N}{2}-2} (E_{j,(i,i+1)} + \gamma_{j,i} + \gamma_{j,i+1}) 2^{2i}$$

(2.27)

where the number of partial products is decreased to slightly above 25%, with consideration being given to the correction factors.

consider  $A_0B_0 + A_1B_1$ . Using Equation (2.22),

$$A_{0}B_{0} + A_{1}B_{1} = \sum_{i=0}^{\frac{N}{2}-1} Q_{i,0} \left(-a_{N-1,0} 2^{N-1} + \sum_{k=0}^{N-2} a_{k,0} 2^{k}\right) 2^{2i} + \sum_{i=0}^{\frac{N}{2}-1} Q_{i,1} \left(-a_{N-1,1} 2^{N-1} + \sum_{k=0}^{N-2} a_{k,1} 2^{k}\right) 2^{2i} = \sum_{i=0}^{\frac{N}{2}-1} (C_{i,0} + g_{i,0}) 2^{2i} + \sum_{i=0}^{\frac{N}{2}-1} (C_{i,1} + g_{i,1}) 2^{2i} = \sum_{i=0}^{\frac{N}{2}-1} (C_{i,0} + C_{i,1} + g_{i,1} + g_{i,0}) 2^{2i}$$

$$(2.28)$$

From Equation (1.6), the sum of two 2's-complement numbers can be considered as a redundant binary number minus 1. Equation (2.28) can be converted to:

$$A_{0}B_{0} + A_{1}B_{1} = \sum_{i=0}^{\frac{N}{2}-1} (C_{i,0} + C_{i,1} + g_{i,1} + g_{i,0})2^{2i}$$

$$= \sum_{i=0}^{\frac{N}{2}-1} (\Gamma_{i,01} + g_{i,1} + g_{i,0} - 1)2^{2i}$$

$$= \sum_{i=0}^{\frac{N}{2}-1} (\Gamma_{i,01} + \gamma_{i,01})2^{2i}$$

(2.29)

where  $\Gamma_{i,01}$  is a redundant binary number from the addition of  $C_{i,0}$  and  $C_{i,1}$ , and the redundant binary number  $\gamma_{i,01} = g_{i,0} + g_{i,1} - 1$ . The correction factor,  $\gamma_{j,01}$ , depends on the values of  $g_{i,0}$  and  $g_{i,1}$ , as shown in Table 2-C.

| $g_{i,0}$ | $g_{i,1}$ | $\gamma_{i,01} = g_{i,0} + g_{i,1} - 1$ | $\gamma_{i,01}^- \gamma_{i,01}^+$ |

|-----------|-----------|-----------------------------------------|-----------------------------------|

| 0         | 0         | -1                                      | 0 0                               |

| 0         | 1         | 0                                       | 0 1                               |

| 1         | 0         | 0                                       | 1 0                               |

| 1         | 1         | 1                                       | 1 1                               |

Table 2-C. Booth Correction Factors for the Cross Partial Product Method

From the Booth coding Table 2-A, the bit encoding Boolean equations are:

$$\gamma_{i,01}^{-} = g_{i,0} = b_{i+1,0}\overline{b_{i,0}} \overline{b_{i-1,0}} + b_{i+1,0}\overline{b_{i,0}} b_{i-1,0} + b_{i+1,0}b_{i,0} \overline{b_{i-1,0}}$$

$$= b_{i+1,0} \overline{b_{i,0}b_{i-1,0}}$$

$$\gamma_{i,01}^{+} = g_{i,1} = b_{i+1,1}\overline{b_{i,1}} \overline{b_{i-1,1}} + b_{i+1,1}\overline{b_{i,1}} b_{i-1,1} + b_{i+1,1}b_{i,1} \overline{b_{i-1,1}}$$

$$= b_{i+1,1} \overline{b_{i,1}b_{i-1,1}}$$

(2.30)

Using Booth coding, the cross partial product inner-product method is given by

$$\langle \boldsymbol{A}, \boldsymbol{B} \rangle = \sum_{j=0}^{M-1} A_j B_j = \sum_{j=0}^{\frac{M}{2}-1} (A_{2j} B_{2j} + A_{2j+1} B_{2j+1}) = \sum_{j=0}^{\frac{M}{2}-1} \sum_{i=0}^{\frac{N}{2}-1} (\Gamma_{i,(2j,2j+1)} + \gamma_{i,(2j,2j+1)}) 2^{2i} \quad (2.31)$$

Again, the number of partial products is decreased to slightly above 25%, with consideration being given to the correction factors.

## 2.1.4 Implementation Comparison of Inline and Cross Inner-Product Methods

An 8-tap digital filter implementation in [28] uses a signed-amplitude system to encode a redundant binary number. The signed-amplitude method requires two gate delays for the conversion from 2's-complement to redundant binary. Examining Equations (1.7) and (1.8), only inverters are necessary for the inline partial product redundant binary mapping.

In [49], the cross partial product implementations of  $A_0B_0 + A_1B_1$  and  $A_0B_0 - A_1B_1$ are discussed for complex number multiplication. An equivalent derivation was provided in Section 2.1.2. The inline method, presented in Section 2.1.1, combines partial products *within* the partial products of  $A_0B_0$  and  $A_1B_1$ , respectively. Figure 2-2 and Figure 2-4 depict these methods. For a qualitative comparison of these two designs, note that as feature sizes shrink in deep submicron VLSI technology, interconnection wires contribute a large portion of the total delay [49],[50]. The inline implementation provides more direct routing for vertical (horizontal) wires, while the cross partial product method [49],[50] will need crossing horizontal (vertical) wiring paths for partial product mapping, with the routing distance proportional to the word width. Therefore, the inline partial product method will result in improved performance, compared to the cross partial product method. In addition, the inline method offers more extended operational capability than the cross partial product scheme (see Chapter 4). The inline method requires more horizontal gates, primarily due to the overhead of the partial product alignment. Table 2-D and Table 2-E show comparisons for Xilinx FPGA implementations for  $A_0B_0 + A_1B_1$ , with and without Booth encoding. The Xilinx Virtex2 2V6000FF1517 device was targeted for the implementations using VHDL and Xilinx Foundation software. For this word length, the higher performance and area savings of the Booth encoded designs are evident (See Appendix for VHDL code availability).

Table 2-D. 16-Bit FPGA Implementations of  $A_{\theta}B_{\theta} + A_{I}B_{I}$  Without Booth Encoding

|                       | Cross PP Method | Inline PP Method |

|-----------------------|-----------------|------------------|

| Number of Slices      | 1094            | 1094             |

| Number of LUTs        | 1992            | 2002             |

| Equivalent Gate Count | 11952           | 12012            |

| Maximum Delay         | 30.014ns        | 28.084ns         |

Table 2-E. 16-Bit FPGA Implementations of  $A_{\theta}B_{\theta} + A_{I}B_{I}$  With Booth Encoding

|                       | Cross PP Method | Inline PP Method |

|-----------------------|-----------------|------------------|

| Number of Slices      | 846             | 905              |

| Number of LUTs        | 1603            | 1717             |

| Equivalent Gate Count | 9618            | 10302            |

| Maximum Delay         | 29.460ns        | 27.970ns         |

## 2.2 Complex Number Inner-Product Computation

## 2.2.1 Review of Complex Number Arithmetic

Complex number arithmetic computation is a key arithmetic feature in modern digital communication, radar systems and optical systems. Many algorithms based on convolutions, correlations, and complex filters require complex number multiplication, complex number division, and high-speed inner-products. These applications require efficient representation and manipulation of complex numbers together with real numbers. Among these computations, high-performance complex number multipliers and complex number inner-products are desirable in modern digital communication, optical systems, and radar systems. Recent research in hardware implementation of complex number arithmetic circuits is focused on utilization of radix-(2), as well as alternative radices, for the representation of complex numbers.

In this chapter, different complex radices are investigated and compared. It is found that the complex radices have no advantage in hardware implementations. Traditional radix-(2) redundant binary numbers are used to implement complex-number multiplication and inner-product processing. The investigated inline inner-product processor can be reconfigured/controlled to perform complex-number computations. The computational structures of  $A_0B_0 + A_1B_1$  and  $A_0B_0 - A_1B_1$  are developed for performing complex number inner-products. The implementation of  $A_0B_0 + A_1B_1$  can be easily controlled to perform the computation of  $A_0B_0 - A_1B_1$ . A complex number inner-product processor is realized, based upon a unified structure for  $A_0B_0 \pm A_1B_1$ .