## HARDWARE IMPLEMENTATION OF TUNABLE HETERODYNE BAND-PASS FILTERS

By

ASAD AZAM Bachelor of Science Oklahoma State University Stillwater, Oklahoma 1999

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE August, 2001

## HARDWARE IMPLEMENTATION OF TUNABLE HETERODYNE BAND-PASS FILTERS

Thesis Approved:

Mail M

Thesis Adviser 72  $\square$ G n

Dean of the Graduate College

### PREFACE

Modern wireless and satellite communication systems make use of spreadspectrum modulation concepts such as Frequency-hopping spread-spectrum (FHSS) and Direct sequence spread-spectrum (DSSS). The spread-spectrum modulation method inherently possesses anti-jamming and anti-interception properties due to the fact that the narrowband information signal is spread over a wide range of frequencies, masking the information-bearing signal as noise. Despite these properties, these communication channels can be severely corrupted by high-powered narrowband interference signals generated by local FM or AM transmitters which may cause complications when detecting the information signal at the receiver. Therefore, the communication system is made more efficient with the use of signal processing techniques for narrowband interference attenuation. Control systems is another area where the presence of narrowband interference signal due to mechanical resonance can be responsible for causing distortion in information signal.

Any Band-pass, High-pass or a Low-pass filter may be converted into a tunable filter through the use of new Tunable Heterodyne Band-pass Filter concept in which the frequency of the heterodyne signal is adjusted thereby creating the effect of translating the entire transfer function of the fixed filter in frequency. In this thesis, hardware implementation techniques and results of the new Digital Tunable Heterodyne Band-pass filter is proposed that allows a prototype IIR or FIR filter to be shifted through the entire range of digital frequencies with a single parameter, the heterodyning frequency. The unique property of this new tunable filter is the range of tunability it possesses. With this technique, the fixed filter is tuned continuously using the concept of frequency translation. The images created by the heterodyne process are cancelled without the use of image canceling filters, which significantly contribute towards a hardware efficient design. In this thesis, simulation results are observed to illustrate the effects of having the fixed prototype filter as a band-pass, high-pass, low-pass or notch filter.

This thesis concentrates on the hardware implementation of the tunable heterodyne filter structure with a band-pass filter as the fixed prototype filter. Thus, simulation and experimental results show that if the fixed filter is a narrowband Bandpass filter, a much hardware efficient implementation can be achieved by using the new Tunable Heterodyne Band-pass filter to extract the narrowband interference from broadband communication or control systems as compared to the standard techniques used.

The proposed heterodyne filter is suitable both as a tunable filter or to be implemented with standard algorithms to design adaptive digital filters. The new structure proposed is composed of three main components which can be implemented using Field Programmable Gate Arrays (FPGA) or easily be retargeted for an Application Specific Integrated Circuits (ASIC) standard cell technology or custom designed for Very Large Scale Integration (VLSI) processes. A prototype system is implemented using a single chip Xilinx Virtex Series Field Programmable Gate Arrays (FPGA) and the simulation results are compared with the hardware data.

Dedication

## To AMI AND ABU

### ACKNOWLEDGMENTS

I wish to express my sincere appreciation to my research advisor, Dr. Michael A. Soderstrand for his intelligent supervision, constructive guidance, inspiration and friendship. His inspiring insight and incomparable patience guided me through my study and provided me with a valuable experience and knowledge. My sincere appreciation also extends to my committee member Dr. Louis G. Johnson whose guidance, assistance, encouragement, and friendship are also invaluable. I would also like to thank committee member Dr. Keith Teague for carefully reviewing my thesis and giving me his precious advice.

I am thankful to all my colleague researchers in the Digital Signal Processing and Communication (DSP&C) Lab for assisting and helping me on numerous occasions. I like to thank Ms. Regina Henry at the International Students and Scholars office for being a great friend and advisor. I would like to thank all my close friends for providing me with love, encouragement and support during the period of my studies.

To complete this acknowledgement, I would like to give my special thanks to my family for their patience and support. I like to thank my parents who have provided me with support and encouragement through their prayers and love. I like to thank my sisters, Nayyar and Nargis for their love and encouragement. I would like to thank my brother Asim for his support and guidance through my studies.

# **TABLE OF CONTENTS**

| Chapte | r ]                                                             | Page |

|--------|-----------------------------------------------------------------|------|

| 1. In  | troduction and Thesis Organization                              | 1    |

| 1.1    | The Problem Statement                                           | 1    |

| 1.2    | Introduction                                                    |      |

| 1.3    | Thesis Organization                                             | 5    |

| 2. Ba  | ckground                                                        | 7    |

| 2.1    | Introduction                                                    |      |

| 2.2    | Spread-Spectrum Communication                                   | 7    |

| 2.2.   |                                                                 | 10   |

| 2.2.   | 2 Structural Issues                                             | 12   |

| 2.3    | Tunable Heterodyne Band-pass Filter                             | 12   |

| 2.4    | Complex Mathematical Analysis                                   | 13   |

| 2.5    | Field Programmable Gate Arrays (FPGA)                           | 16   |

| 2.6    | Hardware Implementation of the Tunable Heterodyne Filter        | 16   |

| 2.7    | Simulation and Experimental Results                             | 17   |

| 3. Tu  | nable Heterodyning Filter Concept                               | 18   |

| 3.1    | Introduction                                                    |      |

| 3.2    | Basic Tunable Heterodyne Filter Structure.                      |      |

| 3.2.   | -                                                               |      |

| 3.2.   |                                                                 |      |

| 3.2.   |                                                                 |      |

| 3.3    | System Transfer Function Analysis for various Prototype Filters |      |

| 3.3.   |                                                                 |      |

| 3.3.   |                                                                 |      |

| 3.3.   |                                                                 |      |

| 3.3.   |                                                                 |      |

| 4. Signa | l Analysis for Tunable Heterodyning                                 |    |

|----------|---------------------------------------------------------------------|----|

| Filter   | ***************************************                             |    |

|          |                                                                     |    |

| 4.1 Int  | roduction                                                           |    |

| 4.2 Si   | gnal Analysis of Tunable Heterodyne Band-pass Filter                |    |

| 4.2.1    | Signal Response of In-phase and Quadrature Signals                  |    |

| 4.2.2    | Signal Response after Combiner Circuit                              |    |

| 5. Field | Programmable Gate Array (FPGA)                                      |    |

| 5.1 Int  | roduction                                                           |    |

|          | linx FPGA Architecture                                              |    |

| 5.2.1    | Configurable Logic Block (CLB) or Slices                            |    |

| 5.2.2    | Programmable Interconnect                                           |    |

| 5.2.3    | I/O Blocks                                                          |    |

|          | GA Design Flow                                                      |    |

| 5.3.1    | Synthesis                                                           |    |

| 5.3.2    | Synthesis Flow                                                      |    |

| 5.3.3    | What is Synthesized?                                                |    |

| 5.3.4    | Implementation                                                      |    |

| 6. Hard  | ware Implementation of the Basic Block                              | 60 |

| u. Itatu | ware implementation of the basic block                              |    |

| 6.1 Ha   | rdware Implementation of the Splitter Circuit                       |    |

| 6.1.1    | Sine/Cosine Function Generator Circuit Design                       |    |

| 6.1.2    | Signal to Noise Ratio For Sine / Cosine Generation                  |    |

| 6.1.3    | Synthesized Circuit of Sine/Cosine Generator                        |    |

| 6.1.4    | Quadrature Mixers Circuit Design                                    |    |

| 6.1.5    | Synthesized Circuit of the Quadrature Mixer                         |    |

| 6.1.6    | Complete Splitter Circuit                                           |    |

| 6.1.7    | Synthesized Circuit of Splitter                                     |    |

| 6.1.8    | FPGA Resource Utilization in Splitter Circuit                       |    |

| 6.2 Ha   | rdware Implementation of Prototype 2 <sup>nd</sup> Order IIR Filter |    |

| 6.2.1    | Synthesized Circuit of 2 <sup>nd</sup> Order Band-pass IIR Filter   |    |

| 6.2.2    | FPGA Resource Utilization in Filter Circuit                         |    |

| 6.3 Ha   | rdware Implementation of Combiner Circuit                           |    |

| 6.3.1    | Synthesized Circuit of Combiner                                     |    |

| 6.3.2    | FPGA Resource Utilization in Combiner Circuit                       |    |

| 6.4 Ha   | rdware Implementation of Prototype 6 <sup>th</sup> Order IIR Filter |    |

| 6.4.1    | Synthesized Circuit of 6 <sup>th</sup> Order Band-pass IIR Filter   |    |

| 6.4.2    | FPGA Resource Utilization in 6 <sup>th</sup> Order Filter Circuit   |    |

| 0.4.2    | FPGA Resource Offization in 6 Order Filter Circuit                  |    |

| Pag | ge |

|-----|----|

|-----|----|

| 7. Simulation and Experimental Results                                          |

|---------------------------------------------------------------------------------|

| 7.1 Simulation, 101                                                             |

| 7.2 Experimental Results                                                        |

| 7.2.1 Experiment Setup                                                          |

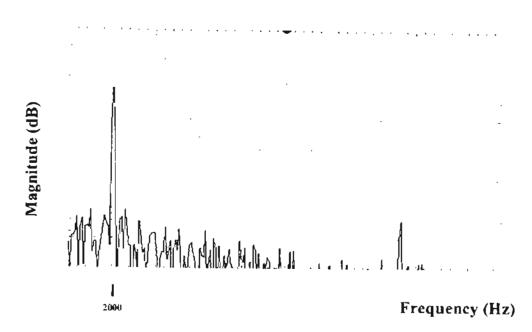

| 7.2.2 Hardware Results for Heterodyne Filter using 2 <sup>nd</sup> Order Filter |

| 7.2.2.1 Splitter Experimental Results 111                                       |

| 7.2.2.2 2 <sup>nd</sup> Order Band-pass Filter Experimental Results             |

| 7.2.2.3 Combiner Experimental Results                                           |

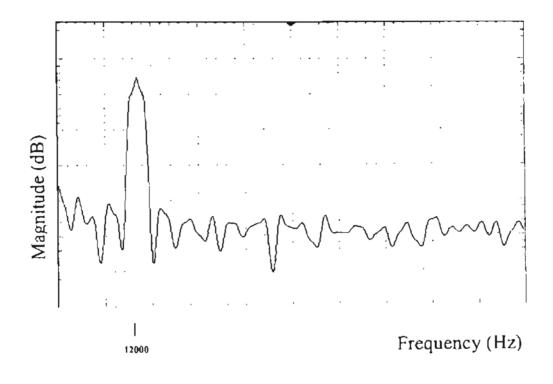

| 7.2.3 Hardware Results for Heterodyne Filter using 6 <sup>th</sup> Order Filter |

| 7.2.3.1 6th Order Band-pass Filter Experimental Results                         |

| 7.2.3.2 Combiner Experimental Results 117                                       |

| 7.3 Hardware Resource Comparison between Standard and Heterodyne Techniques 118 |

| 8. Future Work                                                                  |

| 8.1 Alternative Structures                                                      |

| BIBILOGRAPGY124                                                                 |

| Appendix A 128                                                                  |

# LIST OF TABLES

### Table

| 3.1  | Tuning range and heterodyne frequency relationships.                              | 49 |

|------|-----------------------------------------------------------------------------------|----|

| 6.1  | Signal to Noise Ratio for various length outputs                                  | 77 |

| 6.2  | FPGA Resource Utilization in the Splitter Circuit.                                | 86 |

| 6.3  | FPGA Resource Utilization for the Filter Circuit.                                 | 93 |

| 6.4  | FPGA Resource Utilization in the Combiner Circuit.                                | 96 |

| 6.5  | FPGA Resource Utilization for the 6 <sup>th</sup> order Filter Circuit.           | 99 |

| 6.6a | Hardware utilization for heterodyne structure with 2 <sup>nd</sup> order filter   | 00 |

| 6.6b | Hardware utilization for heterodyne structure with 6 <sup>th</sup> order filter 1 | 00 |

| 7.1  | Comparison of Heterodyne Tunable Filter to Standard Tunable Filter                | 20 |

# **LIST OF FIGURES**

## Figure

| 2.1  | Spread-Spectrum generated at transmitter end.                               | 8  |

|------|-----------------------------------------------------------------------------|----|

| 2.2  | Information retrieved at receiver end.                                      | 9  |

| 2.3  | Information and narrowband noise at receiver end                            | 9  |

| 2.4  | The Basic Block of Heterodyne Unit                                          | 11 |

| 2.5  | Complex number representation.                                              | 13 |

| 2.6  | Complex Phasor representation.                                              |    |

| 2.7  | Helix formed by rotating Phasor in time                                     | 15 |

| 2.8  | Conjugate pair rotating Phasor                                              |    |

| 3.1  | Heterodyne Structure with " $\omega_0$ " as heterodyning frequency.         | 19 |

| 3.2  | The Heterodyned Signal.                                                     |    |

| 3.3  | The Splitter Structure                                                      |    |

| 3.4  | Splitter and Band-pass filter configuration.                                |    |

| 3.5  | The Combiner Structure.                                                     |    |

| 3.6  | Magnitude response of original high-pass filter                             |    |

| 3.7  | Zero/pole diagram for the 6 <sup>th</sup> order high-pass filter            |    |

| 3.8  | Magnitude response of the filter transfer function shifted by $+\omega_0$   | 29 |

| 3.9  | Zero/pole plot for the transfer function shifted by $+\omega_0$             | 30 |

| 3.10 | Magnitude response of the filter transfer function shifted by $-\omega_0$ . | 30 |

| 3.11 | Zero/pole plot for the transfer function shifted by $-\omega_0$             | 31 |

| 3.12 | Magnitude response of the tunable heterodyne filter                         | 32 |

| 3.13 | Zero/pole plot for the tunable heterodyne filter transfer function.         | 32 |

| 3.14 | Magnitude response of original Low-pass filter                              | 33 |

| 3.15 | Zero/pole diagram for the 6 <sup>th</sup> order Low-pass filter             | 34 |

| 3.16 | Magnitude response of the filter transfer function shifted by $+\omega_0$   | 34 |

| 3.17 | Zero/pole plot for the transfer function shifted by $+\omega_0$ .           | 35 |

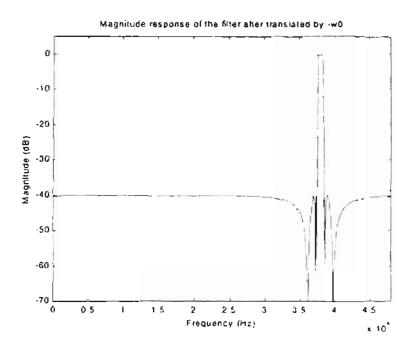

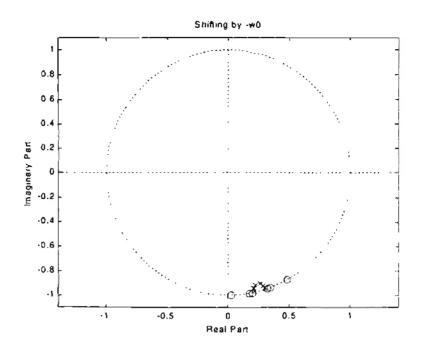

| 3.18 | Magnitude response of the filter transfer function shifted by $-\omega_0$ . | 35 |

| 3.19 | Zero/pole plot for the transfer function shifted by $-\omega_0$ .           |    |

| 3.20 | Magnitude response of the tunable heterodyne filter                         |    |

| 3.21 | Zero/pole plot for the tunable heterodyne filter transfer function.         |    |

| 3.22 | Magnitude response of original Band-pass filter                             |    |

| 3.23 | Zero/pole diagram for the 6 <sup>th</sup> order Band-pass filter            |    |

| 3.24 | Magnitude response of the filter transfer function shifted by $+\omega_0$   |    |

| 3.25 | Zero/pole plot for the transfer function shifted by $+\omega_0$ .           |    |

| 3.26 | Magnitude response of the filter transfer function shifted by $-\omega_0$ . |    |

| 3.27 | Zero/pole plot for the transfer function shifted by $-\omega_0$ .           |    |

| 5,61 |                                                                             |    |

## Figure

L.

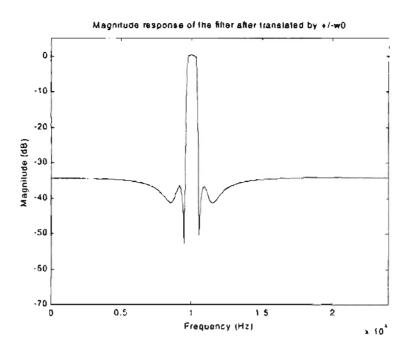

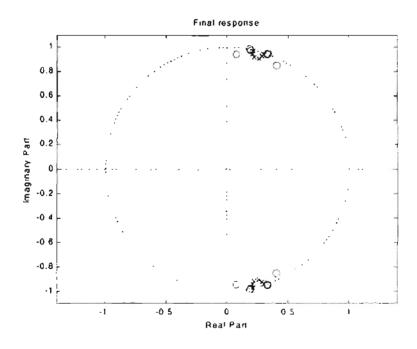

| 3.28 | Magnitude response of the tunable heterodyne filter                 | 42 |

|------|---------------------------------------------------------------------|----|

| 3.29 | Zero/pole plot for the tunable heterodyne filter transfer function. | 42 |

| 3.30 | Magnitude response of original Stop-band filter                     |    |

| 3.31 | Magnitude response of the tunable heterodyne filter                 |    |

| 3.32 | Magnitude response of 2 <sup>od</sup> order Band-pass filter        |    |

| 3.33 | Magnitude response of the tunable heterodyne filter                 | 46 |

| 3.34 | Magnitude response of the modified tunable heterodyne filter.       |    |

| 3.35 | Magnitude response of distorted notch filters                       |    |

| 3.36 | Zeros/poles plot of notch filter converted from band-pass filter    | 47 |

| 4.1  | Block Diagram of Tunable Heterodyne Band-pass Filter                | 50 |

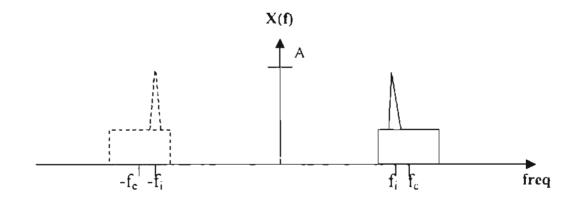

| 4.2  | 3D Representation of Real Signal Spectrum                           | 51 |

| 4.3  | Wide-band signal with narrowband interference                       | 52 |

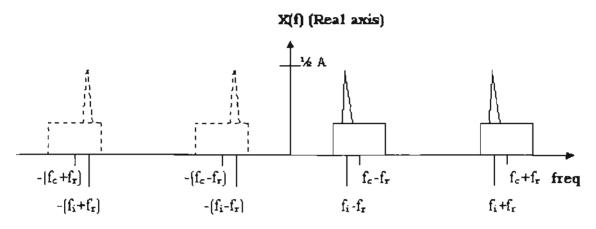

| 4.4  | Translation of input signal using Cosine Function.                  | 54 |

| 4.5  | Band-pass Signal (I) in In-Phase Channel.                           | 54 |

| 4.6  | Translation of input signal using Sine Function.                    | 55 |

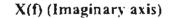

| 4.7  | Band-pass Signal (Q) in Quadrature Channel.                         | 55 |

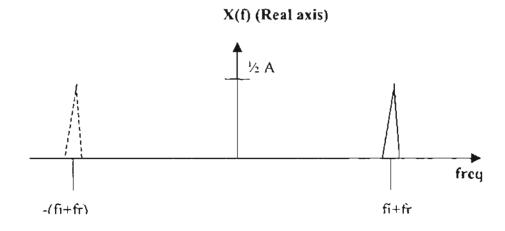

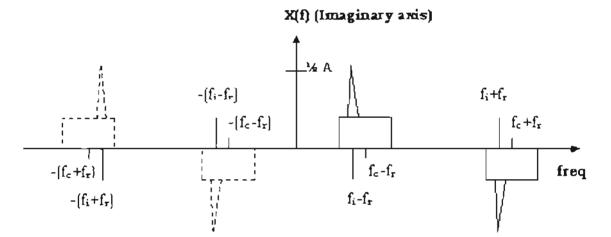

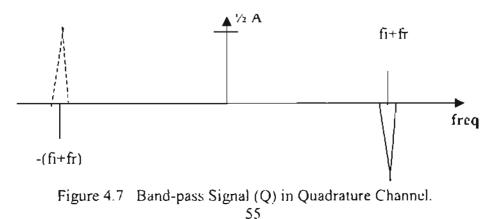

| 4.8  | In-phase Signal (I) to the Combiner Circuit.                        | 56 |

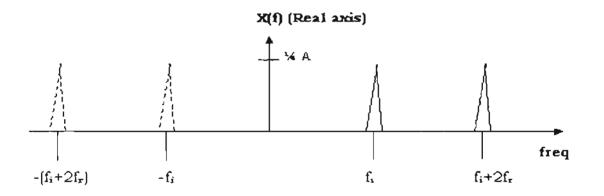

| 4.9  | Multiplying Q signal by j                                           |    |

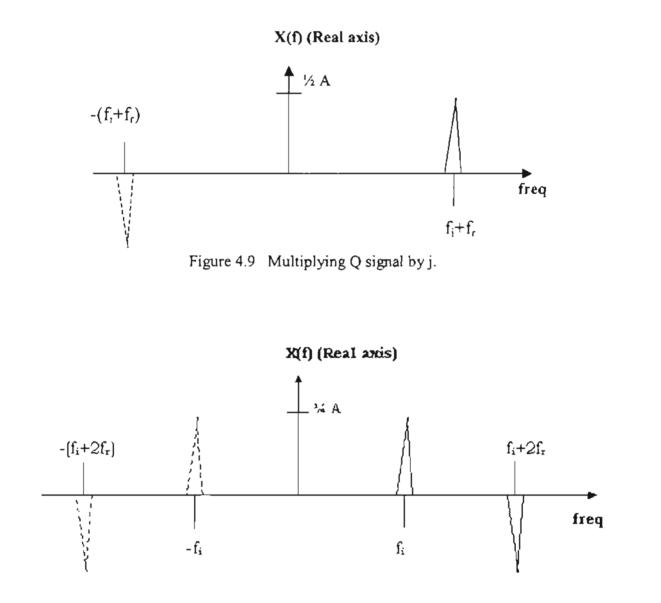

| 4.10 | Quadrature Signal (Q) to the Combiner Circuit                       | 57 |

| 4.11 | Final output from Tunable Heterodyne Band-pass filter               | 58 |

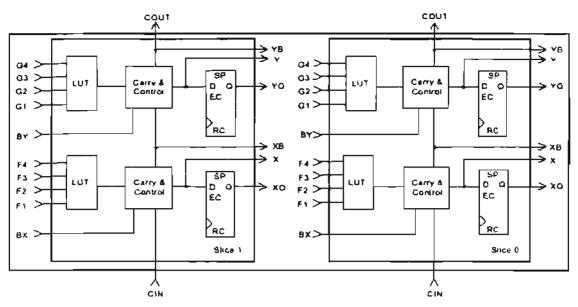

| 5.1  | Virtex Family Configurable Logic Block (CLB)                        |    |

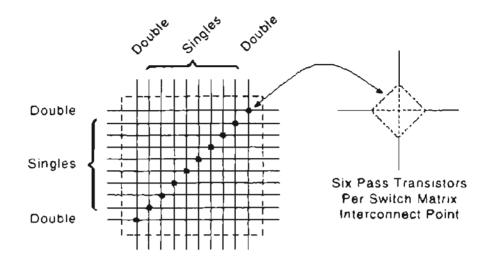

| 5.2  | Programmable switch matrix.                                         | 64 |

| 5.3  | Simplified Block diagram of a Virtex Series IOB                     |    |

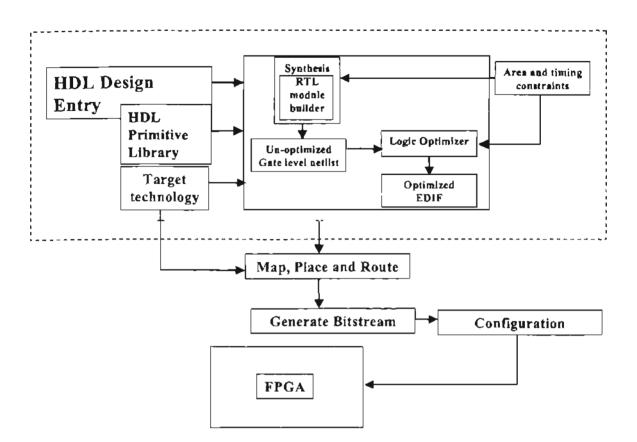

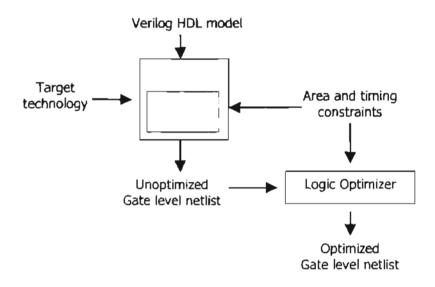

| 5.4  | FPGA Design Flow Block Diagram                                      | 66 |

| 5.5  | Synthesizer optimizing flow diagram.                                |    |

| 6.1  | Tunable Heterodyne Filter Basic Block                               | 69 |

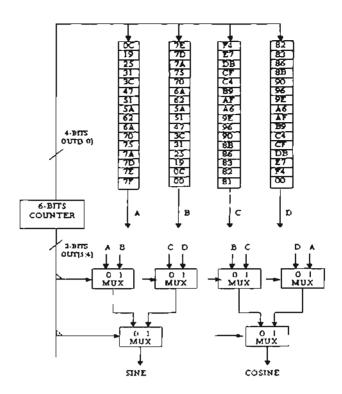

| 6.2  | Sine/Cosine Generator Hardware Structure                            |    |

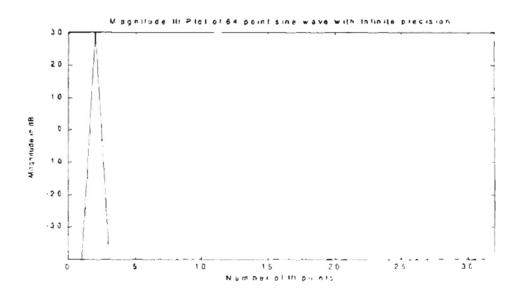

| 6.3  | Magnitude response of 64-point waveform.                            |    |

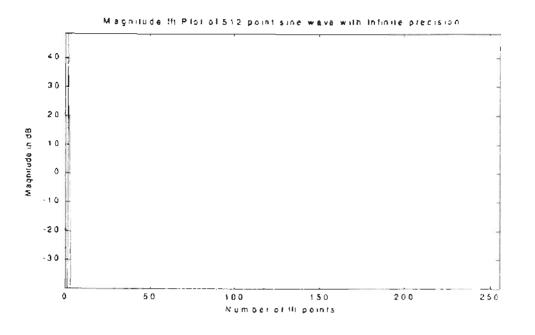

| 6.4  | Magnitude response of 512-point waveform.                           |    |

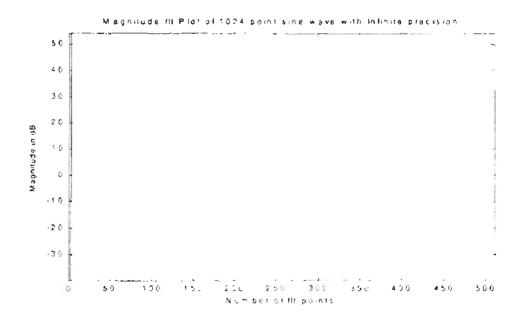

| 6.5  | Magnitude response of 1024-point waveform.                          |    |

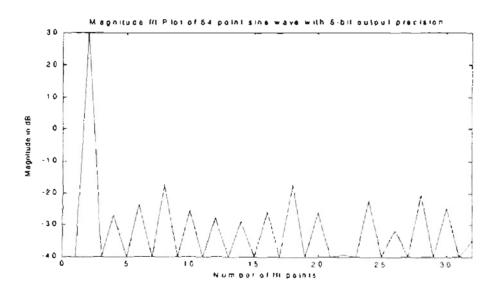

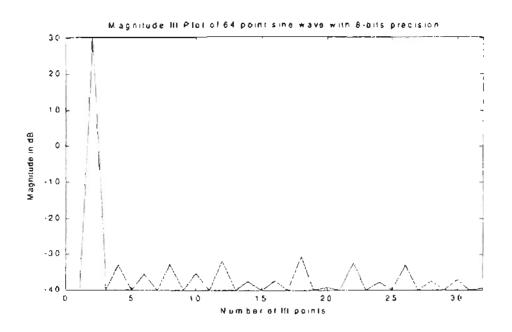

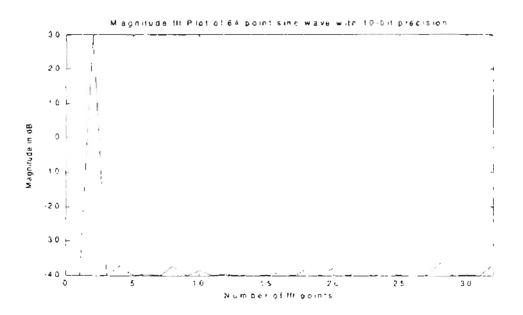

| 6.6  | Magnitude response of 64 point, 6-bits output sinusoid.             |    |

| 6.7  | Magnitude response of 64 point, 8-bits output sinusoid.             |    |

| 6.8  | Magnitude response of 64 point, 10-bits output sinusoid             |    |

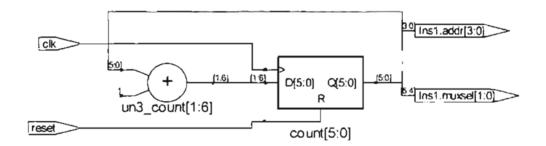

| 6.9  | Synthesized circuit for 6-bit counter.                              |    |

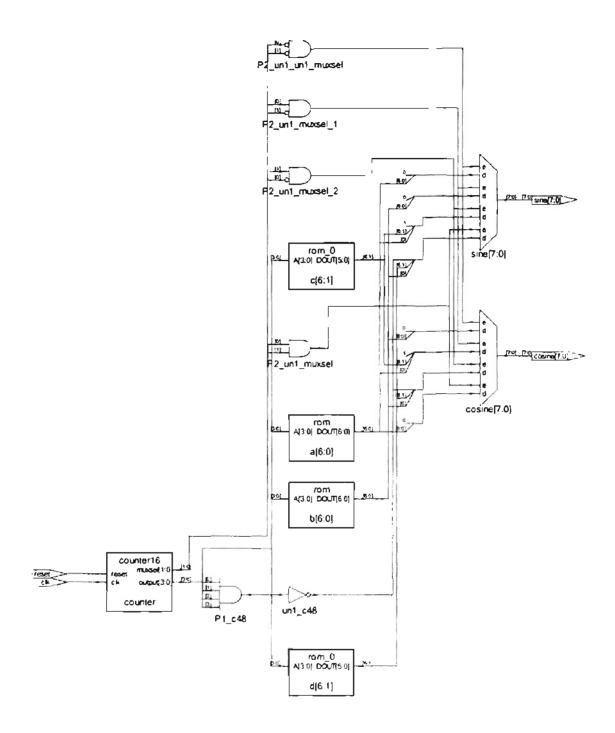

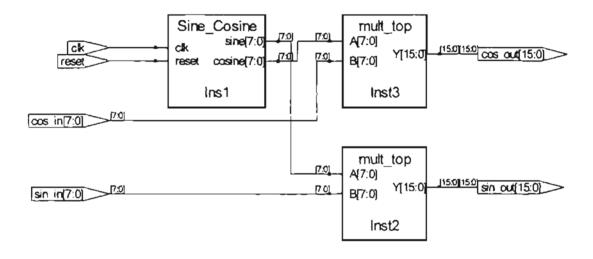

| 6.10 | Synthesized circuit for Sine/Cosine Generator.                      |    |

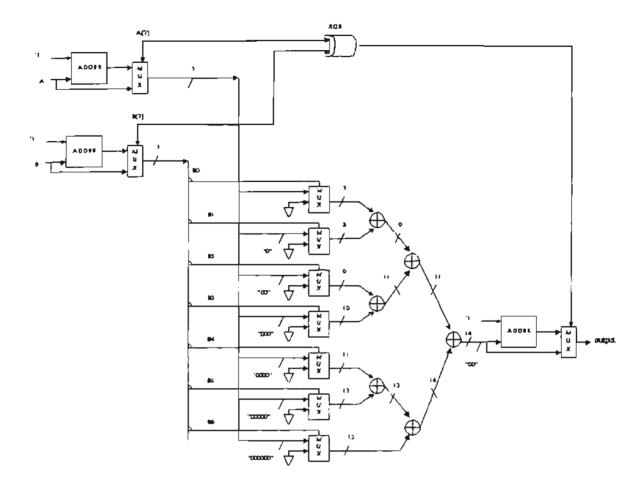

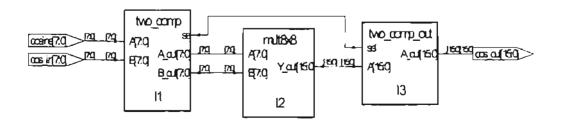

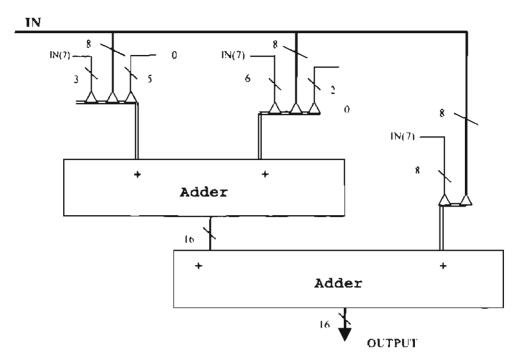

| 6.11 | Two's Complement 8x8 Multiplier Circuit.                            |    |

| 6.12 | Synthesized Circuit to adjust the inputs                            |    |

| 6.13 | Synthesized Circuit to adjust the output.                           |    |

| 6.14 | Synthesized Circuit Partial Product Summation.                      |    |

| 6.15 | Synthesized Circuit for the 8x8 Multiplier.                         |    |

| 6.16 | Block Diagram of the Splitter Circuit.                              |    |

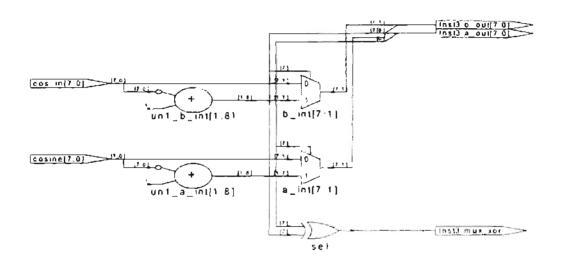

| 6.17 | Synthesized Circuit for Splitter.                                   |    |

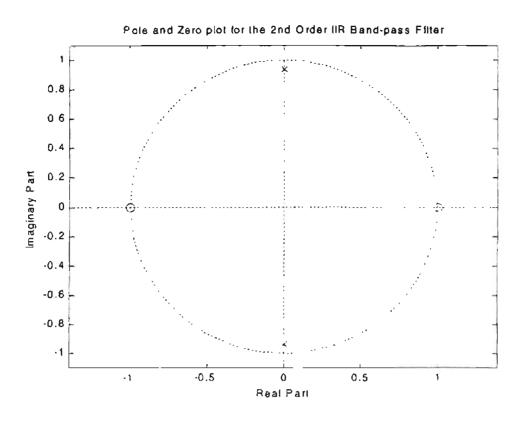

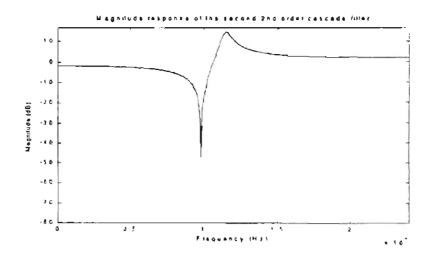

| 6.18 | Magnitude response of 2 <sup>nd</sup> Order IIR Band-pass Filter    | 87 |

## Figure

-

2

| 6.19 | Poles and Zero Plot for 2 <sup>nd</sup> Order IIR Band-pass Filter                  | . 88 |

|------|-------------------------------------------------------------------------------------|------|

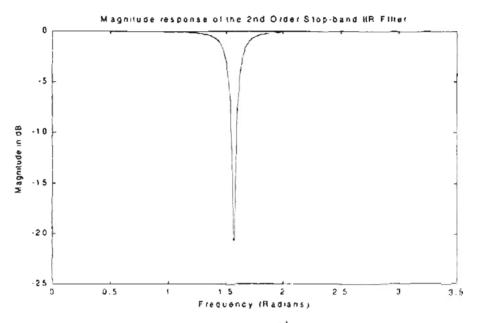

| 6.20 | Magnitude Response of 2 <sup>nd</sup> Order IIR Stop-band Filter.                   | . 89 |

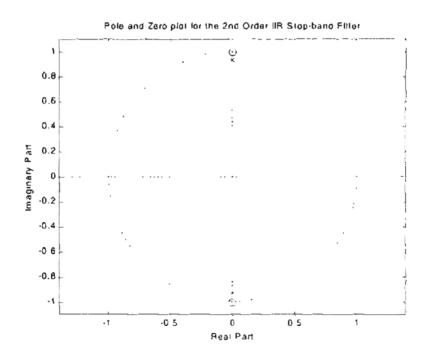

| 6.21 | Pole and Zero plot for 2 <sup>nd</sup> Order IIR Stop-band Filter                   |      |

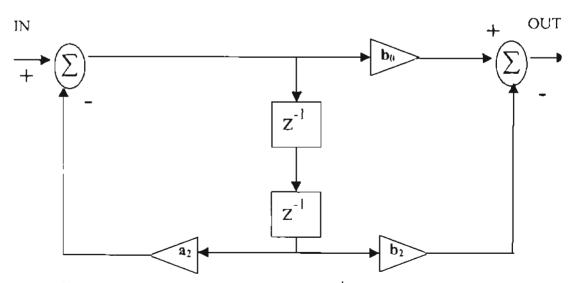

| 6.22 | Direct Form II structure of 2 <sup>nd</sup> order Band-pass IIR Filter.             | . 90 |

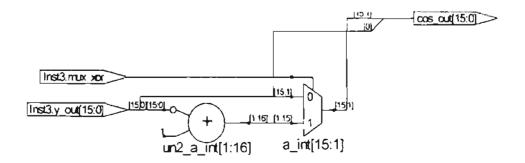

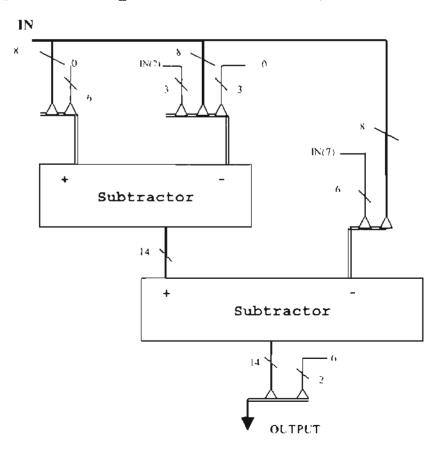

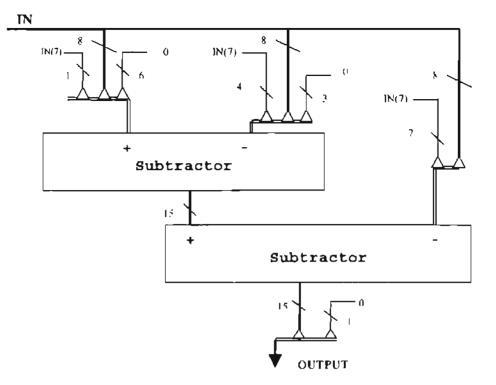

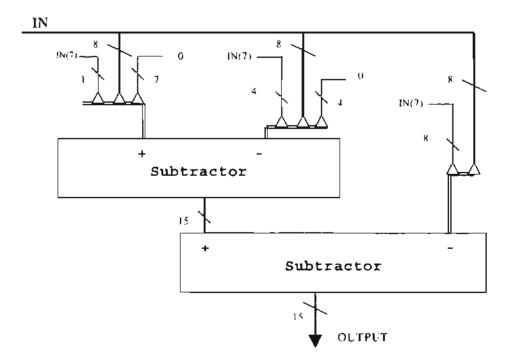

| 6.23 | 'a' Coefficient Implementation Structure.                                           | . 92 |

| 6.24 | Synthesized Circuit of IIR Filter                                                   |      |

| 6.25 | Block Diagram for Combiner Circuit.                                                 | . 94 |

| 6.26 | Synthesized Combiner Circuit.                                                       | . 95 |

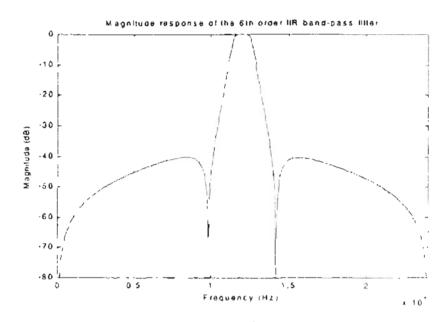

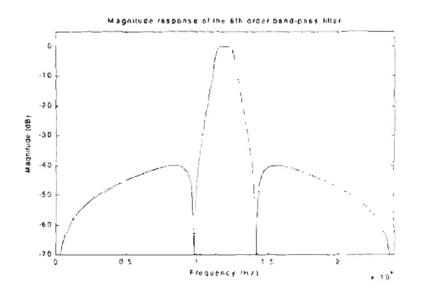

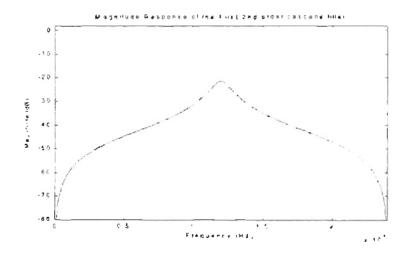

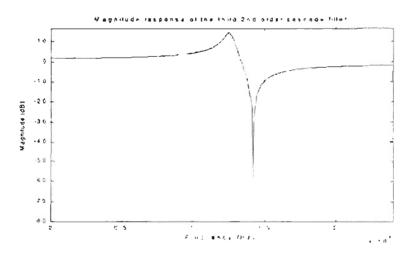

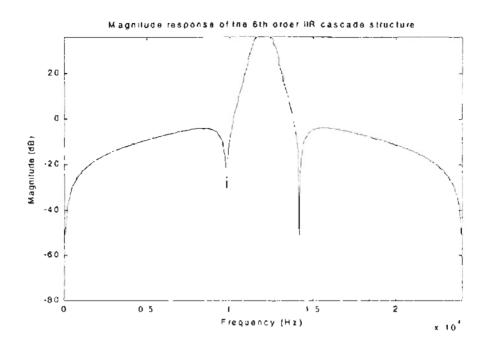

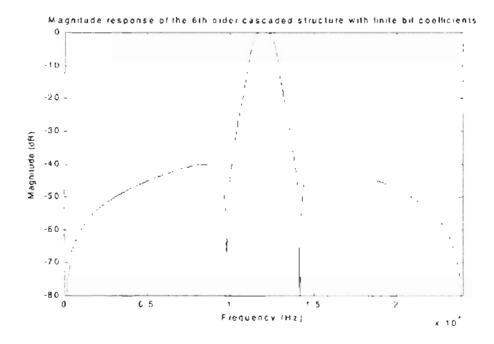

| 6.27 | Magnitude response of the 6 <sup>th</sup> order Chebyshev band-pass filter          | . 97 |

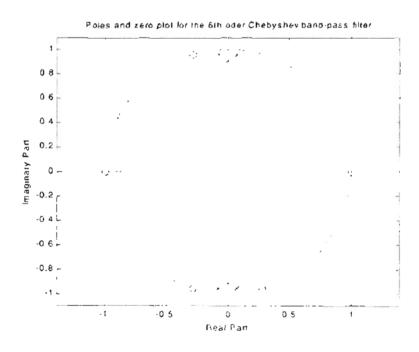

| 6.28 | Poles and zeros of the 6 <sup>th</sup> order Chebyshev band-pass filter.            | . 97 |

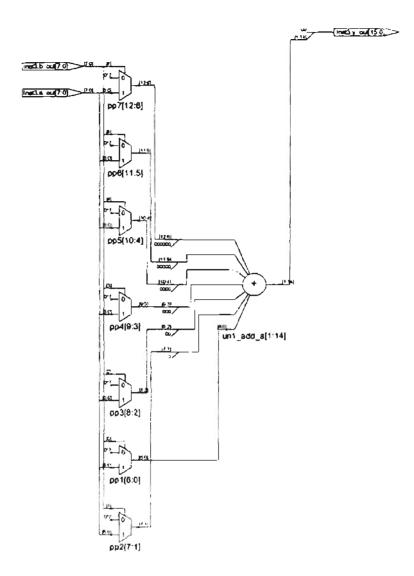

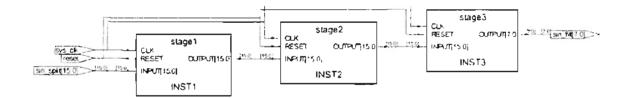

| 6.29 | Synthesized cascaded IIR band-pass filter                                           | . 98 |

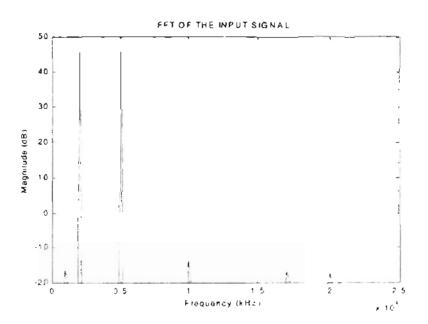

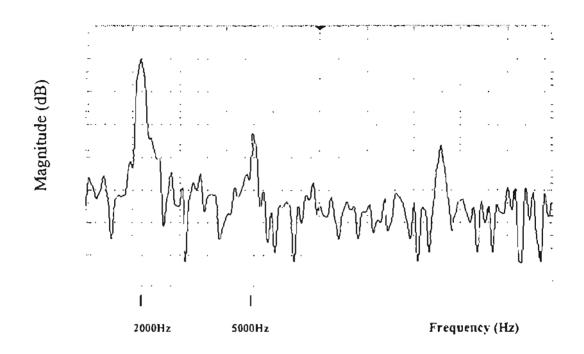

| 7.1  | Input Spectrum for the Heterodyne Filter                                            | 102  |

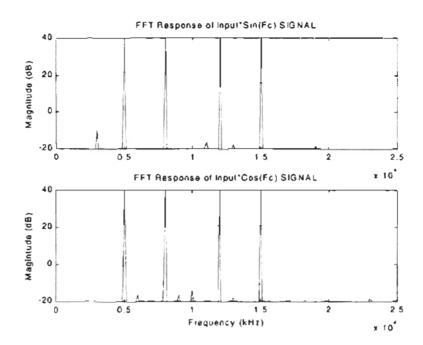

| 7.2  | FFT magnitude response at the outputs of Splitter two branches.                     | 104  |

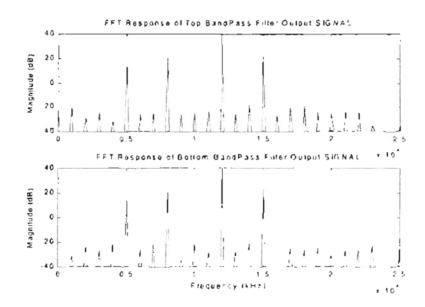

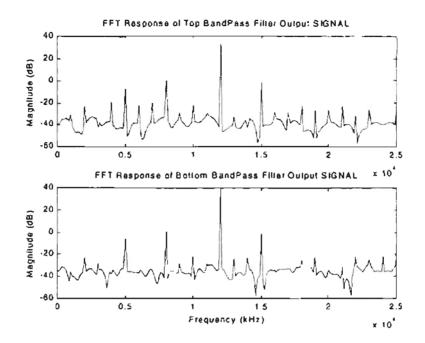

| 7.3  | FFT magnitude response at the outputs of Filters                                    | 104  |

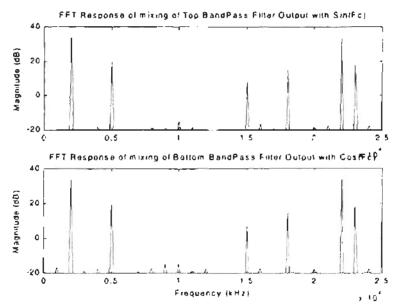

| 7.4  | FFT magnitude response at the final mixers                                          | 105  |

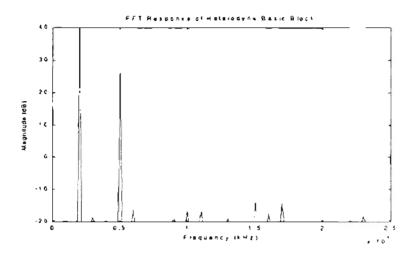

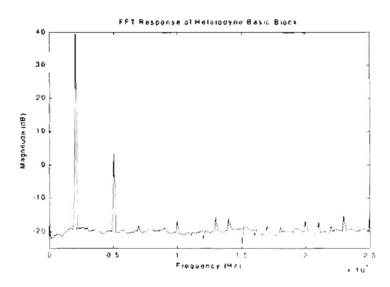

| 7.5  | FFT magnitude response of Tunable Heterodyne Band-pass Filter.                      | 106  |

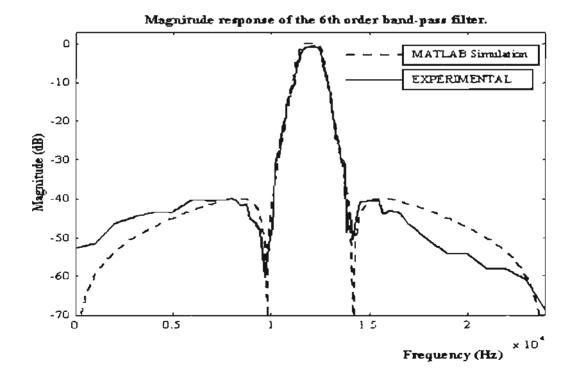

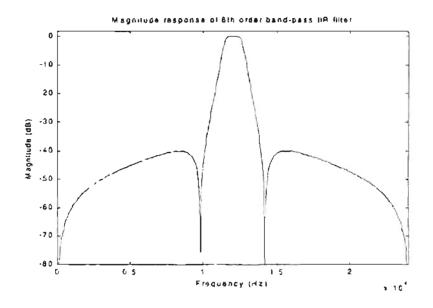

| 7.6  | Magnitude response of 6 <sup>th</sup> Order Band-pass IIR Filter                    |      |

| 7.7  | FFT magnitude response at the outputs of 6 <sup>th</sup> order Filters              | 108  |

| 7.8  | FFT magnitude response Heterodyne Filter, 6 <sup>th</sup> order Band-pass Filter    | 108  |

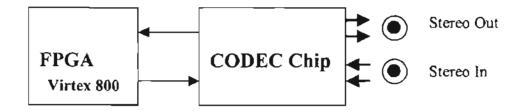

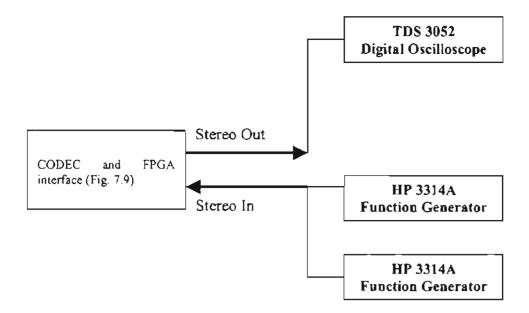

| 7.9  | CODEC and FPGA interface with external signals                                      | 110  |

| 7.10 | Data Acquisition setup, stereo in/out jack ports.                                   | 111  |

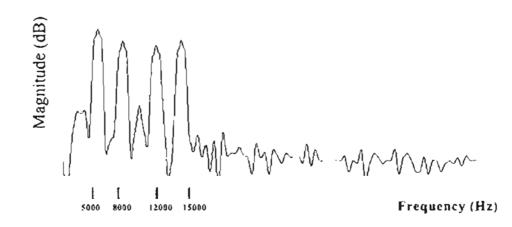

| 7.11 | Hardware results of the Splitter circuit.                                           |      |

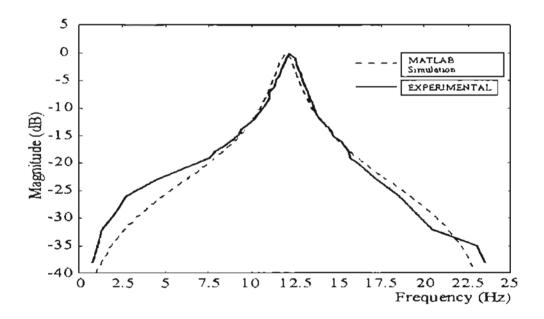

| 7.12 | Superimposed results of IIR filter from hardware and Matlabs.                       |      |

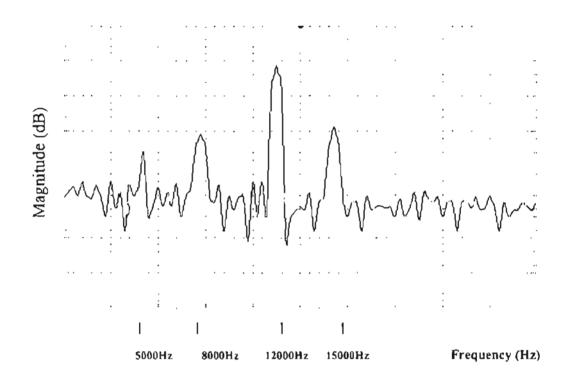

| 7.13 | Hardware response after the Band-pass filter in Heterodyne Structure                |      |

| 7.14 | Hardware results of the output of the Tunable Heterodyne Filter.                    |      |

| 7.15 | Superimposed results of 6 <sup>th</sup> order IIR filter from hardware and Matlabs  |      |

| 7.16 | Hardware response after the 6 <sup>th</sup> order Band-pass filter                  |      |

| 7.17 | Hardware results of the Tunable Heterodyne Filter with 6 <sup>th</sup> order filter | 118  |

| 7.18 | Direct Form II IIR filter structure                                                 |      |

| 7.19 | Number of tuning position against the order of the filter.                          | 121  |

# Chapter 1 Introduction and Thesis Organization

#### 1.1 The Problem Statement

Tunable filters are widely used in applications where the frequency of interest varies over a period of time. Some of the applications lie in the field of communications and controls, where occurrence of narrowband interference is unpredictable and thus needs to be eliminated from the desired signal for an efficient system. In order to tune a filter over a range of frequencies, the coefficients of the filter have to be changed for every tunable frequency. This would require a much larger hardware structure to implement even for a moderate order filter with decent range of discrete tuning frequencies. A novel technique of heterodyne filtering allows us to tune a high-pass or a low-pass filter continuously over the range from DC to Nyquist and to tune a band-pass filter continuously over the range from DC to Nyquist/2 to Nyquist. In this concept, the incoming signal is translated to the fixed filter frequency rather then moving the filter over the incoming signal.

Through the mirroring effect of poles and zeros and their conjugates, a high-pass or a low-pass filter can be converted into a tunable band-pass filter with the method of frequency translation. To analyze the effects on the tunability of the heterodyne filter based on the category of prototype filter used in this structure, detailed simulations are required for all forms of common filters; high-pass, low-pass, band-pass and band-stop. However, this thesis only deals with the hardware implementation of Tunable Heterodyne filter structure [1], where the prototype filters chosen for this implementation were bandpass filters. For rapid prototyping, the hardware was implemented using a Xilinx Virtex family of Field Programmable Gate Arrays (FPGA). One of the key goals of the work reported in this thesis was to implement the theoretical core of the tunable heterodyne filtering concept in hardware and to show that the heterodyne technique is more efficient for continuous tuning of frequencies compared to the standard techniques.

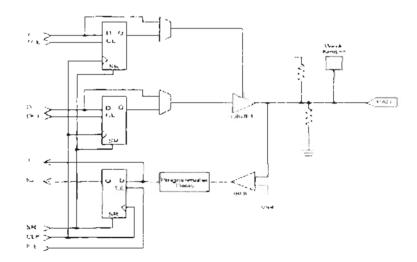

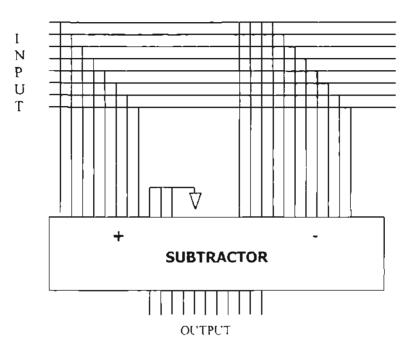

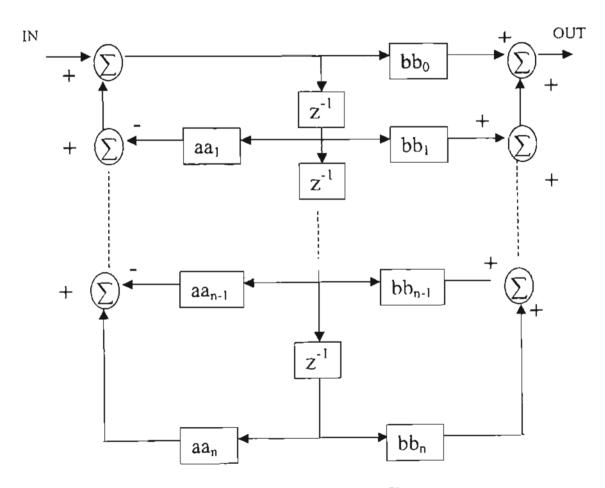

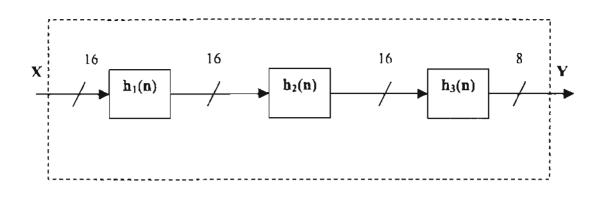

The particular Tunable Heterodyne filter structure discussed in this thesis has three distinct parts, Splitter, Fixed Prototype Filter and Combiner. The Splitter and Combiner structures are basically the heterodyne units, where the Splitter circuit is responsible for translating the incoming signal to the fixed filter frequency and the Combiner circuit translates the filtered response from the fixed filter structure to its base band.

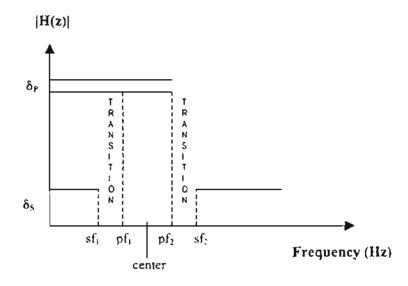

The fixed prototype band-pass filter can be chosen as either an FIR or IIR filter. Applications for this type of tunable or adaptive filter can be found in many areas including embedded control and communications systems. For example, in broadband communication and control systems, where it is extremely important not to filter out the important information data, this type of filter can be used to attenuate narrow-band interference with minimum degradation of the broadband signal. Thus the need for high performance filters with sharp transition bands is essential in these applications in order to prevent degradation of the broadband signal due to large transition bands associated with typical digital filters. Therefore, in this thesis, we focus on using IIR filters, which yield sharp transition bands, but are also extremely hard and tricky to tune.

In order to be able to target this design to various FPGA or ASIC technologies, the behavioral code for the circuit needed to be written in Hardware Description Languages (VHDL & Verilog). While this VHDL or Verilog code must be written with some target-specific technology (in our case, targeted specifically for the Xilinx Virtex FPGAs), as much as possible we have tried to develop a target-free code that can be easily be retargeted to other FPGAs or to ASIC designs.

The theory of Tunable Heterodyne Filters is based on complex mathematics and has been used in many communication systems; one such application is Single Side Band (SSB) Modulation. Most of these communication structures are built using analog devices [13]. This project deals with the implementation of Tunable Heterodyne Bandpass Filter for Digital Signal Processing applications.

#### 1.2 Introduction

The importance of Digital Signal Processing (DSP) has been significantly exhibited over the years with advances in broadband communications. Several issues plague the modern communication systems, namely narrowband interferences in broadband Binary Phase Shift Keying (BPSK) and Quadrature Phase Shift Keying (QPSK) signals.

Narrowband interferences are usually generated from oscillators that are local to the area where the receiver is located. These signals have strong energy confined in a narrow-band at a specific frequency and are effective enough to make it extremely hard for the receivers to detect the wide-band signal. With this effect on signals around it, narrowband interference causes problems especially in the mobile communication industry whereby the received signal will be corrupted due to the system failure and low performance. Thus, to improve the system performance, signal processing techniques are applied to eliminate these interferences [2].

The basic idea behind the digital heterodyne filter structure is to develop a tunable band-pass filter in the digital domain. Utilizing the heterodyne property of signal translation, the signal is modulated with a carrier frequency in the digital domain to shift the interference frequency to the center frequency of the fixed filter. The signal is then filtered and retranslated through the process of heterodyning back to its base-band. The filter frequency can be situated at any place in the frequency spectrum, thus a relationship between the heterodyning frequency and the incoming interference frequency with respect to the center frequency of the band-pass filter needs to be established. The tunable heterodyne filter can be made adaptive by using an adaptive algorithm such as LMS, in which the heterodyning frequency.

The newly proposed filter implementation was discovered based upon the heterodyne process in which the prototype filter could be adjusted or "tuned" to the appropriate frequency in order to attenuate narrowband interferences. The heterodyne process itself can be defined as the generation of new frequencies by mixing two or more signals in a nonlinear device. The proposed heterodyne filter implementation cancels the

effect of all the undesired images created during the heterodyne processes without using image-canceling filters.

Although theoretically the proposed digital filter has been proven to perform as intended, the emphasis presented here is towards the hardware implementation of the "Tunable" Heterodyne Filter which was carried out on the Xilinx Virtex Series FPGA. The Xilinx FPGA was chosen as a suitable test environment, which will eventually lead to the design being hardwired into an ASIC or VLSI process.

#### 1.3 Thesis Organization

In chapter 2, previous work and research in the area of narrowband interference suppression from wide-band communication has been presented. A brief overview of Spread-Spectrum communication system is provided and the problems related to narrowband interference are pointed out. It is analyzed and researched, as to which technique our Tunable Filter is comparable to. This project has emerged from the heart of the communication systems, therefore the point of applications for the other similar structures are addressed. Then this chapter goes into a brief description of complex numbers and signals. This chapter forms a basis for the understanding of the underlying mathematics in this application.

In chapter 3, introduction to the Tunable Heterodyne Filter structure is elaborated. Each component of this filter is separately analyzed through mathematical expressions, which are derived at each node of the filter [8]. A detailed analysis in simulation is performed to show the tuning characteristics of different categories of the prototype filters, when implemented as fixed filters in the tunable heterodyne filter structure. In chapter 4, a similar analysis of Tunable Heterodyne Band-pass Filter is used, but this time instead of explaining with mathematical equations, a graphical signal analysis is done to explain the workings of this structure.

In chapter 5, an introduction of FPGA systems and their architecture, along with a brief description of the synthesis process and method is presented. Terminologies built in this chapter will be extensively used in the successive chapters.

In chapter 6, hardware for the Tunable Heterodyne Band-pass filter is constructed using Xilinx FPGAs. This chapter elaborates the design process and synthesized circuitry. Implementation topics and issues included in this chapter are, Sine/Cosine wave generator, Signal to Noise Ratios, Multipliers and Prototype filter designs.

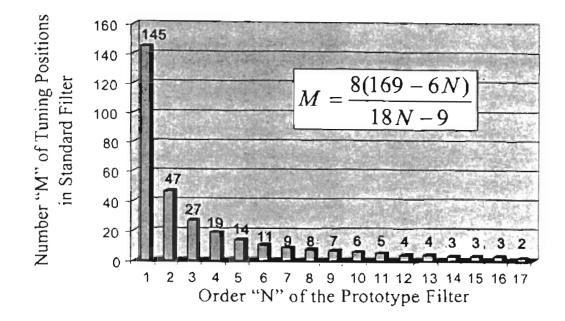

In chapter 7, the results that were obtained from Matlab simulation and FPGA hardware implementation, are presented. This chapter also shows the effect of having a higher order IIR filter to improve the system response. This chapter goes into a brief detail of our testing techniques and experimental setup. We also compare and estimate hardware requirements between the standard technique and the tunable heterodyne filtering technique.

Finally in chapter 8, we conclude the discussion of tunable heterodyne band-pass filters and set forth the goals and ideas for more future work.

# Chapter 2 Background

#### 2.1 Introduction

Digital Signal Processing has its applications embedded in a vast number of disciplines. Introduction of Signal processing in the field of communication has enhanced the quality of information transferred from one place to another. One of the fields of communication where signal processing has made a dominant effect is wide-band communication. In this chapter a brief overview of the broadband communication techniques and their associated problems are analyzed. Some of the material presented in this chapter deals with the research work done in the field of narrowband interference suppression from broadband signals and related techniques that are comparable to the one presented in this thesis. Signal Processing applied in this thesis is not only applied in narrowband interference in the field of communications but also in control systems.

#### 2.2 Spread-Spectrum Communication

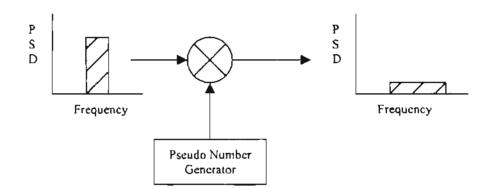

In this section, a brief description of Spread-Spectrum Communication is given along with some of the problems associated with this technique. The concept of SpreadSpectrum is to encode a relatively narrowband information signal in such a way that the information is spread over a broad band of the frequency spectrum. This can be accomplished by several well-known techniques. For example, Direct-Sequence Spread-Spectrum (DSSS) is accomplished by mixing the input signal with a sequence of numbers. The signal to be transmitted is first multiplied by a pseudo noise to spread the information signal over a bandwidth of B. In this manner the power spectral density of the information signal is spread to about 100-1000 times the bandwidth of the original signal, thus making the information appear as noise. This process is shown in figure 2.1, where the PSD is the Power Spectral Density.

Figure 2.1 Spread-Spectrum generated at transmitter end.

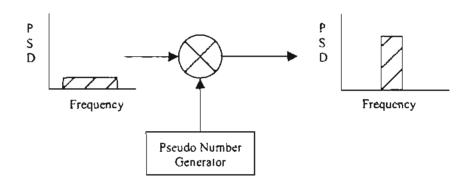

To retrieve the information data from the noise-like spread-spectrum signal, the receiver has to use the same sequence of pseudo numbers. Through this process the data is recovered since there is very little correlation between the pseudo sequence generated by other users and the sequence used to retrieve the data. At the receiver end, the noise like data is multiplied by the same sequence. This process is shown in figure 2.2.

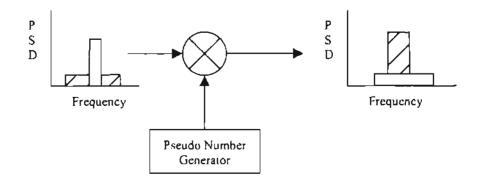

The advantage of spreading the information signal over a wide range of frequencies is that it is hard to detect the information data, which appear as noise in the communication channel and thus making it extremely difficult for deliberate jammers to distort or intercept the information. One of the advantages to this scheme is when the noise-like spread-spectrum information signal corrupted with a narrowband interference signal over the channel is multiplied by the pseudo sequence at the receiver end, the power of the narrowband is spread over a wide band of frequencies. Thus, this spread of narrowband would appear as noise to the retrieved information signal. This process is shown in figure 2.3, where the shaded area is the narrowband interference.

Figure 2.2 Information retrieved at receiver end.

Figure 2.3 Information and narrowband noise at receiver end.

Although theoretically it seems that the narrowband interference can be suppressed and spread down into the noise level at the receiver end, in practice these narrowband interferences have high power associated with them, which would saturate the receiver amplifier, and thus would cause system failure. These strong narrowband signals generated by AM and FM radio transmissions within the communication systems make it impossible to detect the spread-spectrum signals [9][10][11][12]. Introduction of signal processing techniques for interference suppression is applied prior to detecting the signal, where narrowband interference suppression techniques are applied to eliminate them and consequently to enhance the performance of spread-spectrum communications [1][2].

#### 2.2.1 Narrowband Interference Suppression Techniques

There are a number of research groups that are working to find novel techniques to eliminate narrowband interference from broadband communication systems without corrupting the information data. One of the techniques is to implement an adaptive algorithm to filter out the narrowband frequencies. These algorithmic techniques use transversal or tapped delayed filters to adjust the filter response to the frequencies of the narrowband interference. Since the thermal noise and the spread-spectrum signals are wideband processes, their future values cannot be predicted, whereas in the case of a narrowband signal, they can be predicted from their past behavior [2]. Therefore, the narrowband interference can be subtracted from the original signal. To eliminate the interference from the system, the tap weights of the filter are adapted until the mean squared error is minimized [1][4][5][6][7]. Another technique used for the suppression of

narrowband interference is the transform method. This technique consists of a Fourier Transform, a multiplier and an Inverse Fourier Transform [2].

The method implemented in this thesis closely resembles the adaptive algorithm technique described above, as the digital filter described here can be made adaptive by placing it in an adaptive algorithm. Since the coefficients of the transversal filter are not fixed, therefore variable multipliers are utilized, which consume a lot of silicon area. Also in the technique using the Fourier Transform method for narrowband interference elimination, considerable hardware is required to implement the Fast Fourier Transform and inverse Fourier transform. The tunable heterodyne band-pass filter proposed in this thesis can replace the traversal filter in the adaptive algorithm such as Least Mean Squared (LMS) [8] and can be tuned to any frequency from DC to  $\pi/2$  or  $\pi/2$  to  $\pi$  with a single parameter, the heterodyne frequency.

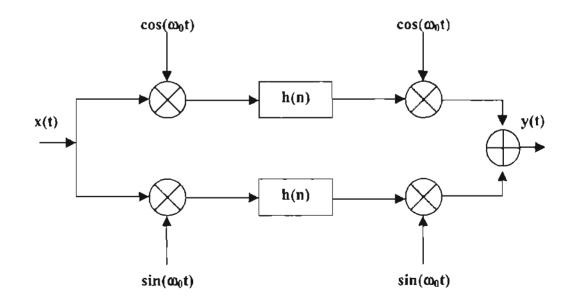

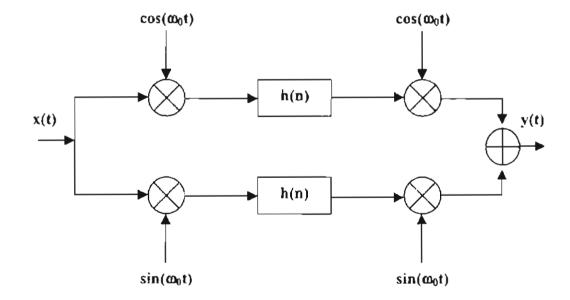

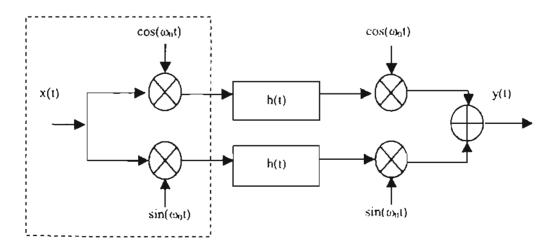

Figure 2.4 The Basic Block of Heterodyne Unit.

#### 2.2.2 Structural Issues

The concept of the heterodyne filter is drawn from classical communications theory. The structural configuration shown in figure 2.4, which we will use to implement the tunable band-pass filter, is employed in many communication systems for various different applications. Most of these applications are designed as analog circuits in transmitters and receivers for the communication channels. The most common application found for this technique is Single Side Band (SSB) modulation Radio Transceivers [13][14]. In these implementations, low-pass filters are used where the heterodyning frequency translates the incoming signal down to the low pass filter, on the other hand, uses this communication concept to implement a unique filtering scheme. which can be tuned with a single parameter and can be adapted when used in an adaptive algorithm [8]. Using a digital scheme allows us to construct identical filters, which are essential in eliminating all the images generated due to the heterodyne process.

#### 2.3 Tunable Heterodyne Band-pass Filter

The tunable heterodyne band-pass filter is a novel idea, which uses the concept of the heterodyne process to translate the incoming signal from base-band up to the fixed filter frequency [8][15]. The concept of tunable filtering by frequency translation has its roots embedded in communication theory. The basic idea behind the Tunable Heterodyne Filter is very similar to the concept of super-heterodyne used for radio transmission, where the signal coming into the system is heterodyned or mixed with a tunable heterodyne frequency which translates the signal to a fixed intermediate frequency (IF), thus translating the signal to a new, but fixed, frequency spectrum. In the case of the super heterodyne receiver, the IF is filtered and then demodulated to produce the audio or video output. In our new heterodyne filter, the signal is translated by modulation with the heterodyne frequency to a fixed intermediate frequency (IF) of the filter and then a second heterodyne process brings the signal back to the original frequency, but it is now filtered by the action of the fixed IF filter. While the IF filter is fixed, the frequencies of the signals being filtered vary depending upon the heterodyne frequency. The result is a hardware efficient tunable filter with a single tuning parameter. In the tunable heterodyne filter structure, a fixed filter is implemented with constant coefficients, which is mathematically proven to give the same results as those obtained from a much more complicated tunable filter implemented with variable coefficients.

#### 2.4 Complex Mathematical Analysis

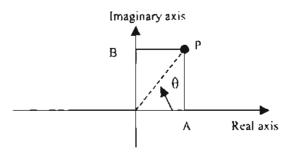

A real signal is composed of imaginary and real components, that is if we view a real signal as a vector, then one of its constituent lies on the real axis and the other on the imaginary axis. We can represent a complex number as shown in figure 2.5

Figure 2.5 Complex number representation.

where 'P' is a complex number, represented in rectangular form by P = a + jb. The magnitude of this complex number is given by,  $M = (a^2 + b^2)^{1/2}$  and the angle is given by,  $\theta = \tan^{-1}(b/a)$ . If we see this form as a vector instead of a point, we get a phasor representation or rotating vector. Figure 2.6 shows this effect.

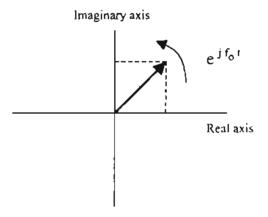

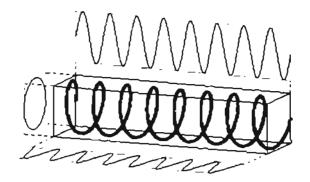

The phasor shown in figure 2.6 has both real and imaginary parts and can be expressed as  $e^{jfot} = cos(2\pi fot) + j sin(2\pi fot)$ . Thus if the phasor is rotating as time progresses, we get a spiral shape helix coming out of the page. The projection of the helix on the real/time plane is a cosine wave and its projection on to the imaginary/time plane is the sine wave, as shown in figure 2.7.

Figure 2.6 Complex Phasor representation.

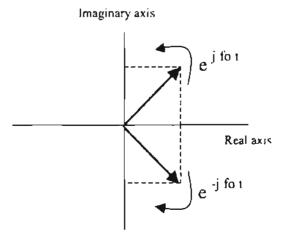

Therefore, to represent a phasor in rectangular form we require two sinusoids, a cosine for the real part and a sine for the imaginary part. If we have two phasors, which are complex-conjugate pairs, rotating in a counter direction with respect to each other, the real components of the two complex-conjugate phasors would add constructively and the imaginary parts of the two complex-conjugate phasors would cancel each other out, thus producing a real sinusoid [16][17].

Figure 2.7 Helix formed by rotating Phasor in time.

In communication systems, real signals are represented as band-limited signals that have an equal amount of positive and negative frequencies. These signals behave in a similar way to the phasor representation above. Thus to make use of the property of rotating conjugate pair cancellation to obtain a purely real signal, the incoming signal to the Tunable Heterodyne filter is distributed in two branches, real (cosine) and imaginary (sine). Thus the results of the second heterodyne units are added to cancel all the images without the use of image canceling filters.

Figure 2.8 Conjugate pair rotating Phasor.

#### 2.5 Field Programmable Gate Arrays (FPGA)

To implement the structure shown in figure 2.4 we used Xilinx FPGA. FPGAs are programmable devices that can be configured and reconfigured to provide circuit designers the flexibility of designing a system on a chip within the comfort of their lab. We used Xilinx Virtex 800 family FPGAs, which have some added features that allow having a better and more efficient system design. To synthesize the design behaviorally, we described the hardware using hardware description language (VHDL), which is then used in the Synplicity Synthesis tools to generate a Netlist file. The Netlist file created by the synthesis tools is then mapped to a Virtex library using the Alliance place and route tools. After mapping, the components are then placed and routed to create a configuration bit file, which can be downloaded into the Xilinx FPGA through the parallel port.

#### 2.6 Hardware Implementation of the Tunable Heterodyne Filter

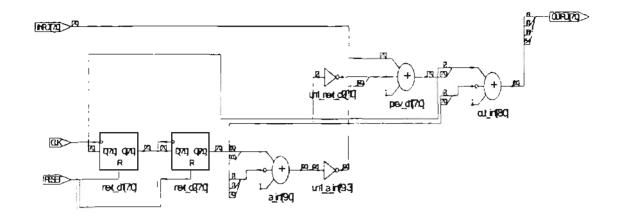

The implementation of the Tunahle Heterodyne Band-pass filter was done using the VHDL (VHSIC Hardware Description Language) behavioral code. There are three parts to this structure (1) the Splitter, which translates the signal up to fixed filter frequency, (2) the Prototype IIR Filter, which is the fixed frequency filter used to extract the narrowband interference from the incoming signal, and (3) the Combiner which translates the signal back to the base-band and adds the output of the two branches, thus yielding a image free narrowband interference frequency. The transfer function of Tunable Heterodyne Band-pass Filter can be shown to be [8]:

$$H(z,\omega_h) = H(ze^{j\omega_h}) + H(ze^{-j\omega_h})$$

(2-1)

where,  $\Box_{*}$  is the beterodyne frequency. Since the final transfer function of the tunable heterodyne filter is the sum of translated transfer functions of the fixed filter, some limitation is imposed on the types of filters that can be tuned using this structure. High-pass, low-pass and band-pass filters are the best candidates for implementation with this technique. There are a few unique band-pass filters, which can be converted into a notch filter and thus made tunable with this heterodyne technique. An example of such a filter is a simple  $2^{nd}$  order band-pass filter, with the following transfer function:

$$H(z,\omega_{h}) = \frac{(1-\alpha)}{2} \frac{(1-z^{-2})}{(1+\alpha z^{-2})}$$

(2.2)

#### 2.7 Simulation and Experimental Results

To simulate the behaviour of the tunable heterodyne band-pass filter, we made use of Matlab tools. The results obtained from both the simulation and hardware show the feasibility of tunable heterodyne filtering technique. It is apparent from the results that for the extraction of narrowband interference signals. we would require an extremely narrowband band-pass filter. As a consequence of this statement, we require a high order band-pass filter with sharp transition bands to avoid elimination and distortion of the information signal contained in the spread-spectrum signal. Thus an estimate comparison can be devised to show that it would be more hardware efficient to implement a tunable heterodyne filter for narrowband interference suppression.

# Chapter 3 Tunable Heterodyning Filter Concept

#### 3.1 Introduction

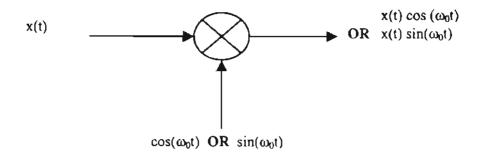

The notion of heterodyne filtering stems from communications theory and is embedded in many analog wireless applications. Heterodyning (figure 3.1) is another term for frequency translation, which is the process of mixing (multiplying) an incoming signal with a heterodyning frequency to shift the entire signal to a new frequency spectrum. The following equations give the Fourier transform of the cosine and sine functions:

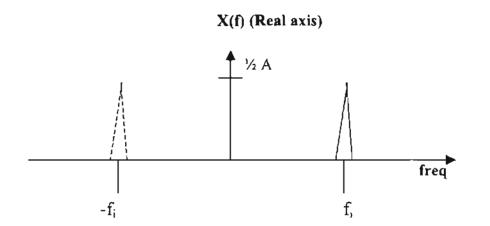

$$\cos(\omega_0 t) \leftrightarrow 1/2 \quad [d(\omega - \omega_0) + d(\omega + \omega_0)]$$

$$\sin(\omega_0 t) \leftrightarrow 1/2j [d(\omega - \omega_0) - d(\omega + \omega_0)]$$

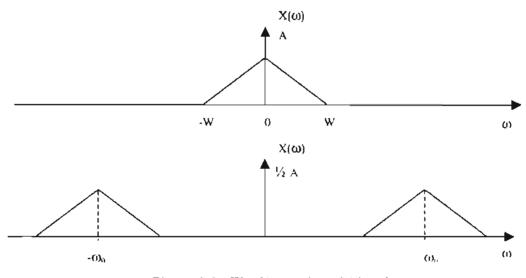

Therefore, multiplying by an input signal x(t) where  $x(t) \leftrightarrow X(\omega)$ :

$$\begin{aligned} \mathbf{x}(t) * \cos(\omega_0 t) &\leftrightarrow 1/2 \quad [\mathbf{X}(\omega - \omega_0) + \mathbf{X}(\omega + \omega_0)] \\ \mathbf{x}(t) * \sin(\omega_0 t) &\leftrightarrow 1/2 \mathbf{j} \quad [\mathbf{X}(\omega - \omega_0) - \mathbf{X}(\omega + \omega_0)] \end{aligned}$$

The incoming signal which is considered as a real band-pass signal centered at a certain frequency ( $\omega$ ) when multiplied with the local oscillator (LO) operating at a fixed

intermediate frequency ( $\omega_0$ ), translates the input signal to the new spectral locations of  $(\omega - \omega_0)$  and  $(\omega + \omega_0)$ , as shown in figure 3.2.

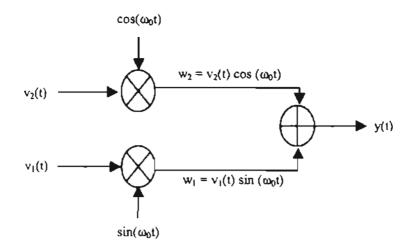

Figure 3.1 Heterodyne Structure with " $\omega_0$ " as heterodyning frequency.

Figure 3.2 The Heterodyned Signal.

The incoming signal for the tunable heterodyne band-pass filter is assumed to be a broadband signal that is corrupted with narrowband interference during its path from the transmitter to the receiver. The heterodyning frequency is selected to shift the input signal to a new frequency spectrum, thus assuring that the narrowband interference falls within the pass-band frequencies of the fixed filter. This technique works perfectly in getting the signal to the fixed filter frequency where the filtering occurs. The problem with the technique of heterodyning is the generation of images whenever two frequencies are multiplied. Although the images formed in the first stage of heterodyning are eliminated because of the selection of a narrowband of frequencies by the band-pass filter, when the signal is translated back to it's base-band with a second stage of heterodyne, images are generated again. In order to cancel these images, we have two branches which are  $90^{0}$  out of phase from each other and are discussed in detail later.

#### 3.2 Basic Tunable Heterodyne Filter Structure

The Basic Heterodyne Tunable Filter Block is divided into three parts, performing distinct operations: 1) Splitter 2) Band-Pass Filter 3) Combiner

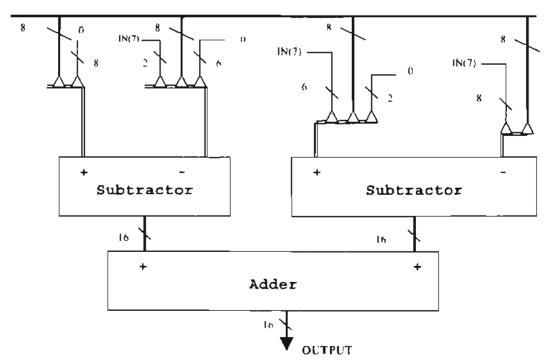

#### 3.2.1 Splitter

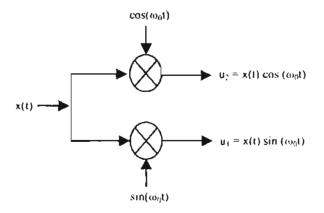

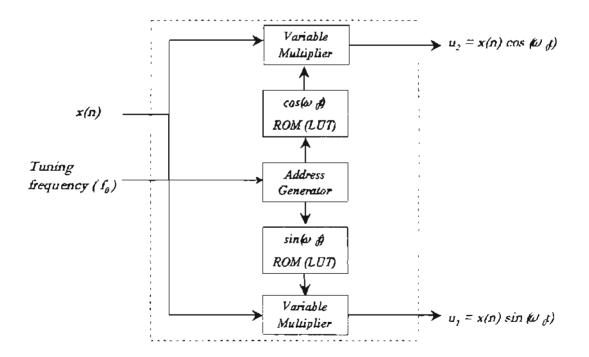

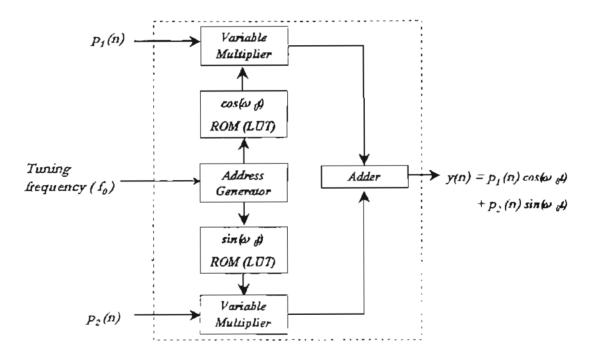

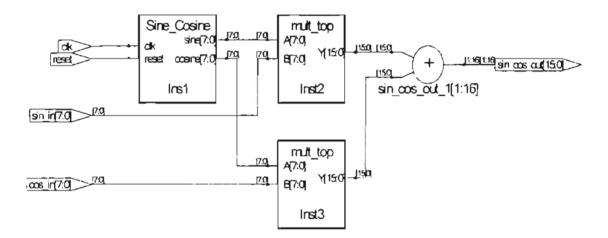

The Splitter is a direct digital up-converter that multiplies the input signal by sine and cosine at the heterodyne frequency to create the intermediate frequency quadrature signals. The input for this application will be an 8-bit 2's complement fixed-point audio signal sampled at 48kHz.

Figure 3.3 The Splitter Structure.

The Splitter is the first part of the Tunable Heterodyne Band-pass filter. It splits the incoming signal  $x(t) \leftrightarrow X(f)$  into real and imaginary parts thus producing two outputs, input signal x(t) multiplied with cosine and with sine, respectively. Both the sine and the cosine frequency is the heterodyning frequency and is the same for all the heterodyning units.

If we assume X(f) as the incoming signal in frequency domain, equations 3.1 and 3.2 show the Fourier Transform of the results when the incoming signal is convolved with the Fourier transform of the sine and the cosine signals, respectively. As we can see from equations 3.1 and 3.2, the input signal is split into two images and each image is translated to a new spectral position, located at  $+/-\omega_0$ , where  $\omega_0$  is the heterodyning frequency. The power of the incoming signal is equally split between each of the images.

$$U_{i}(z) = X(z) * \Im[\sin(\omega_{0}n)] = \frac{1}{2j} \Big[ X(ze^{-j\omega_{0}}) - X(ze^{+j\omega_{0}}) \Big] \qquad (3.1)$$

$$U_{2}(z) = X(z) * \Im[\cos(\omega_{0}n)] = \frac{I}{2} \Big[ X(ze^{-j\omega_{0}}) + X(ze^{+j\omega_{0}}) \Big]$$

(3.2)

Both the branches produce the images in the same spectral locations but are  $90^{\circ}$  out of phase due to the imaginary term 'j' in equation 3.1. This defines the cosine branch as the real (In-phase) branch and sine branch as the imaginary (Quadrature) branch.

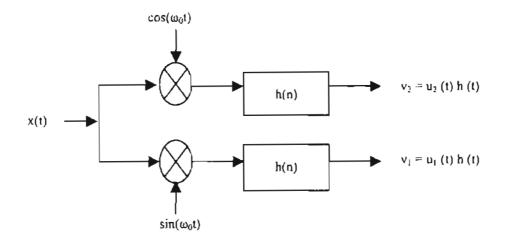

#### 3.2.2 Prototype Filter

The next part of the Tunable Heterodyne Band-pass Filter is the Fixed Filter, which is required to isolate the narrowband interference. Both the branches have identical filters with the same transfer function. These filters are required to extract the narrowband interference signal in both the channels. It is essential to have identical filters to cancel the images. This can be done easily with digital filters, whereas it is extremely difficult to produce identical analog filters. Since analog filters are implemented with discrete components which are greatly dependent on many factors which effect their values, this technique is perfectly suitable for implementation in the digital domain.

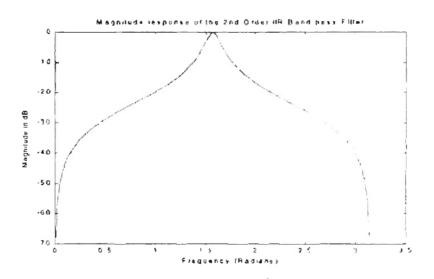

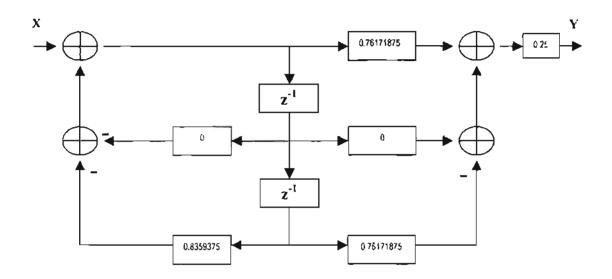

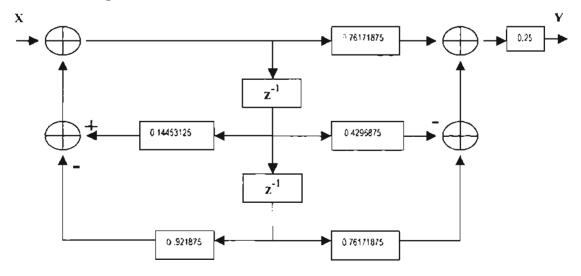

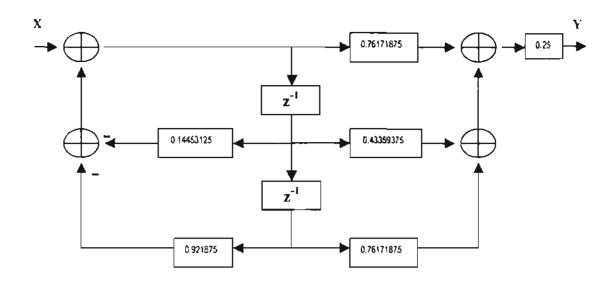

In this thesis, the fixed digital filter is implemented as a band-pass filter but can be replaced by a narrow low-pass or a high-pass filter that generates the tunable bandpass filter. Tunable heterodyne filters are suitable for tuning IIR filters, which are extremely difficult to tune but bear with them many advantages that would require a very high order FIR filter. Therefore, in this technique, it is suitable to have a narrowband band-pass IIR filter with sharp transition bands. Also due to the targeted applications, the requirement for having a linear phase is non-critical and thus makes IIR filters a more desired choice. Since the filter is fixed, it gives an advantage to the technique of heterodyning to have very high order filters, which can be designed with a constant coefficient multiplier using techniques such as Canonic Sign Digits (CSD) or Dempster-McLeod (DM) [19][20]. Implementing the heterodyne structure with higher order filters does not have as significant an effect on the hardware complexity when compared to the standard technique of constructing a tuning band-pass filter. To validate the theoretical aspects of the tunable heterodyning filter technique, a prototype second-order band-pass filter was designed and implemented using FPGAs. The filter was chosen to be centered at quarter of the sampling frequency  $(f_s / 4)$ , where  $f_s$  is the sampling frequency. The filter equation is given by

$$H(z) = \frac{(1-\alpha)(1-z^{-2})}{2(1+\alpha z^{-2})}$$

where  $\alpha = \frac{7}{8} = 0.875$

Then  $H(z) = \frac{(0.125)[1-z^{-2}]}{2[1+(0.875)z^{-2}]}$

$$\frac{Y(z)}{X(z)} = \frac{0.0625 - 0.625 z^{-2}}{1+0.875 z^{-2}}$$

$[1+0.875 z^{-2}]Y(z) = [0.0625 - 0.0625 z^{-2}]X(z)$

$Y(z) + 0.875 z^{-2}Y(z) = 0.0625 X(z) - 0.0625 z^{-2}X(z)$

$Y(z) = 0.0625 X(z) - 0.0625 X(z)z^{-2} - 0.875 Y(z)z^{-2}$  (3.3)

Let  $k = 0.0625$  and  $r = 0.875$ , Then

$Y(z) = kX(z) - kX(z)z^{-2} - rY(z)z^{-2}$  (3.4)

The heterodyne frequency is chosen to translate the interference signal to the band-pass filter frequency. Figure 3.4 shows the insertion of Band-Pass Filters in both the channels.

Figure 3.4 Splitter and Band-pass filter configuration.

The transfer function of the filter is:

$$H(z) = \frac{B(z)}{A(z)}$$

Equations 3.5 and 3.6 show in the form of Fourier Transform, the effect after the output of the Splitter is multiplied by the transfer function of the prototype filter.  $U_1(z)$  and  $U_2(z)$  are taken from equations 3.1 and 3.2, respectively.

$$V_{1}(z) = U_{1}(z)H(z) = \frac{1}{2j} \Big[ X(ze^{-j\omega_{0}}) - X(ze^{+j\omega_{0}}) \Big] H(z)$$

(3.5)

$$V_{2}(z) = U_{2}(z)H(z) = \frac{1}{2} \Big[ X(ze^{-j\omega_{0}}) + X(ze^{+j\omega_{0}}) \Big] H(z)$$

(3.6)

The Splitter circuit translates the input signal to the fixed frequency of the bandpass filter, which allows the band-pass filter to select out the interference from the input signal.

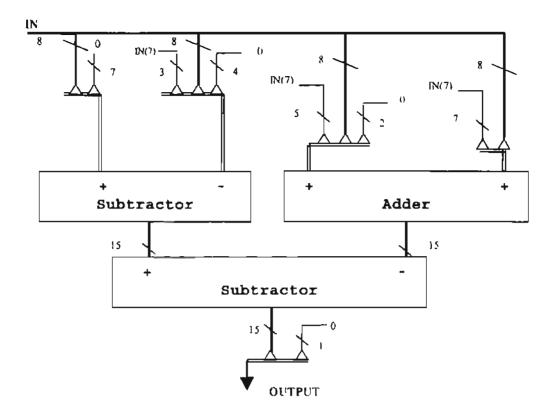

### 3.2.3 Combiner

The final part of the tunable heterodyne filter is the Combiner structure. The Combiner is a direct digital down-converter that multiplies the intermediate frequency quadrature signals (one signal by sine and the second signal by cosine) thus bringing back the signal to its base-band. Since both the branches in the tunable heterodyne filter structure are out of phase, the summation of both the channels cancels the effect of all the images created by the heterodyning process. Figure 3.5 shows the structure for the combiner circuit.

Figure 3.5 The Combiner Structure.

Equations 3.7 and 3.8 show the effect of convolving the output of the prototype filters in both channels with the Fourier transform of the sine and the cosine functions.

$$W_{l}(z) = V_{l}(z) * \Im[sin(\omega_{0}n)] = \frac{1}{2j} \left[ V_{l}(ze^{-j\omega_{0}}) - V_{l}(ze^{+j\omega_{0}}) \right]$$

(3.7)

$$W_{2}(z) = V_{2}(z) * \Im[\cos(\omega_{0}n)] = \frac{1}{2} \Big[ V_{2}(ze^{-j\omega_{0}}) + V_{2}(ze^{+j\omega_{0}}) \Big]$$

(3.8)

Substituting the  $V_1(z)$  and  $V_2(z)$  terms from equation 3.5 and 3.6 respectively, we get the results shown in equations 3.9 and 3.10. Since  $V_1(z)$  contains imaginary terms when convolved with another imaginary term, the imaginary terms cancel out and the equation becomes real. As we can see, there are no imaginary terms present in either of the equations. Since both the channels are real and have images produced in the same spectral locations but with different signs, when these terms are added, the images cancel each other out. This is the reason the transfer function of both of the prototype filters is required to be identical, otherwise the images would not cancel out completely and an image canceling filter needs to be implemented to extract the desired response.

$$W_{1}(z) = \frac{1}{4} \Big[ X(z) - X \Big( z e^{+2j\omega_{0}} \Big) \Big] H \Big( z e^{+j\omega_{0}} \Big) + \frac{1}{4} \Big[ X(z) - X \Big( z e^{-2j\omega_{0}} \Big) \Big] H \Big( z e^{-j\omega_{0}} \Big)$$

(3.9)

$$W_{2}(z) = \frac{1}{4} \Big[ X(z) + X \Big( z e^{+2/\omega_{0}} \Big) \Big] H \Big( z e^{+j\omega_{0}} \Big) + \frac{1}{4} \Big[ X(z) + X \Big( z e^{-2j\omega_{0}} \Big) \Big] H \Big( z e^{-j\omega_{0}} \Big)$$

(3.10)

Equations 3.11 and 3.12 show the response of the complete structure.

$$Y(z) = W_{1}(z) + W_{2}(z)$$

$$Y(z) = \frac{1}{2} \Big[ H(ze^{+j\omega_{0}}) + H(ze^{-j\omega_{0}}) \Big] X(z)$$

(3.11)

$$H(z,\omega_0) = \frac{Y(z)}{X(z)} = \frac{1}{2} \Big[ H(ze^{j\omega_0}) + H(ze^{-j\omega_0}) \Big]$$

(3.12)

The transfer function equation 3.12 for the tunable heterodyne filter is given in terms of  $\omega_0$ , thus reflecting that poles and zeros are located at a new position as a function of  $\omega_0$ . The transfer function of the tunable heterodyne filter gives the effect of the filter being moved or translated, but in reality the incoming signal was translated to the fixed filter. Thus if we express the "z" terms in form of  $z = e^{j\omega}$ , then  $ze^{+i/j\omega_0}$  is translated in the frequency domain and is given by  $e^{j(\omega+i/\omega_0)}$ .

## 3.3 System Transfer Function Analysis for various Prototype Filters

In this section we will develop and analyze the characteristics of tunable heterodyne filter's transfer function with different types of prototype filters. To vigorously analyze the output response, we chose three different types of filters; Highpass, Low-pass and Band-pass. Since the final transfer function of the tunable heterodyne filter is the sum of the translated transfer function of prototype filter (equation 3.12), notch filters cannot be used in this structure of a tunable heterodyne filter. It can be shown by this analysis that the range of tunability of the heterodyne filter is relative to the type of prototype filter used as the fixed filter. In this chapter, all the simulation from this point onwards will be considered to have a sampling frequency of 48000Hz and heterodyning frequency ( $\omega_0$ ) of 10000Hz.

### 3.3.1 High-pass Prototype Fixed Filter

Through the use of frequency translation, we can show that a high-pass filter can be converted into a tunable band-pass filter. Elaborating equation 3.12 in the following form can show the effect of frequency translation:

$$H(z) = \frac{1}{2} \Big[ H(e^{+j\omega}e^{+j\omega_0}) + H(e^{+j\omega}e^{-j\omega_0}) \Big]$$

$$H(z) = \frac{1}{2} \Big[ H(e^{j(\omega+\omega_0)}) + H(e^{j(\omega-\omega_0)}) \Big]$$

(3.13)

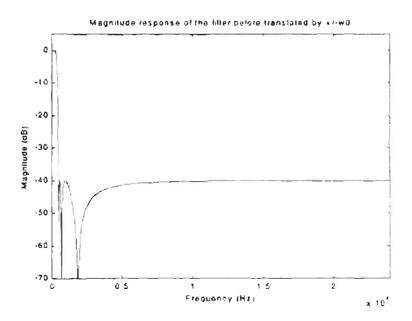

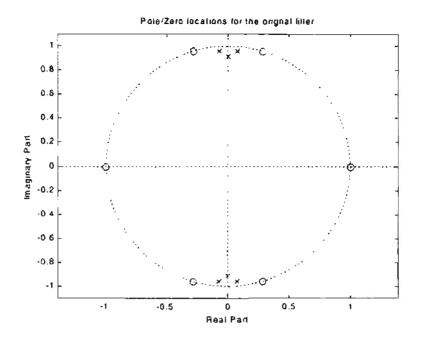

A  $6^{1h}$  order high-pass filter is taken as an example to show the consequence of each component in equation 3.13. Figure 3.6 shows the magnitude response of the  $6^{1h}$  order high-pass filter and figure 3.7 shows the corresponding zero/pole plot.

Figure 3.6 Magnitude response of original high-pass filter

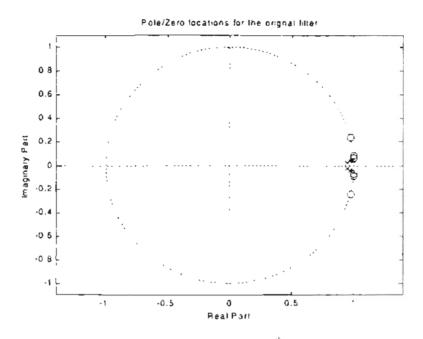

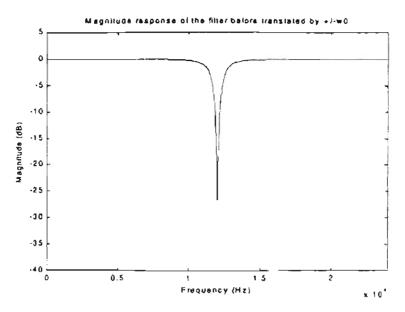

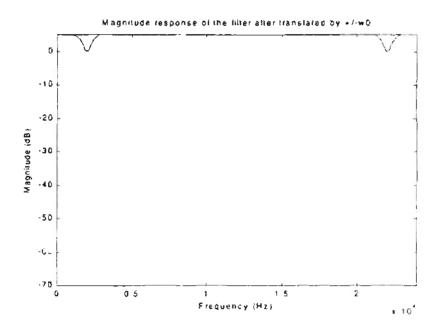

The response of the transfer function  $H(e^{j(\omega + \omega_0)})$  is obtained when the zero and pole locations of the fixed filter have been shifted by  $+\omega_0$ . This result shows that although the incoming signal is translated to the fixed filter, in the final response of the tunable heterodyne filter, it appears as if the filter has been translated to the signal. Figures 3.8 and 3.9 show the plot of the magnitude response of the translated transfer function and the relocated zeros/poles, respectively. From figure 3.7 we can see that the zeros and poles to the right of Nyquist frequency on the unit circle have their conjugates on the left side of the Nyquist frequency, thus giving a band-pass filter centered at Nyquist frequency. When we rotate these poles and zeros by  $+\omega_0$  as shown in figure 3.9, we see that the center frequency of the band-pass filter is shifted to the left of the Nyquist frequency to (Nyquist  $+\omega_0$ ). Similarly, figures 3.10 and 3.11 show the magnitude response and the zeros/poles plot for the transfer function when shifted by  $-\omega_0$ . respectively. Since the Nyquist is at 24kHz, translation by  $+\omega_0$  centers the band-pass at 34kHz and translation by  $-\omega_0$  centers the band-pass at 14kHz.

Figure 3.7 Zero/pole diagram for the 6<sup>th</sup> order high-pass filter

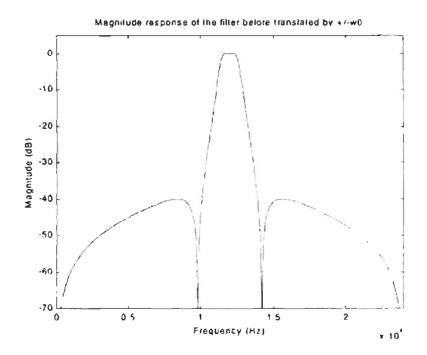

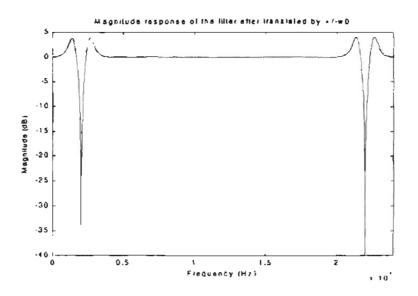

Figure 3.8 Magnitude response of the filter transfer function shifted by  $+\omega_0$ . 29

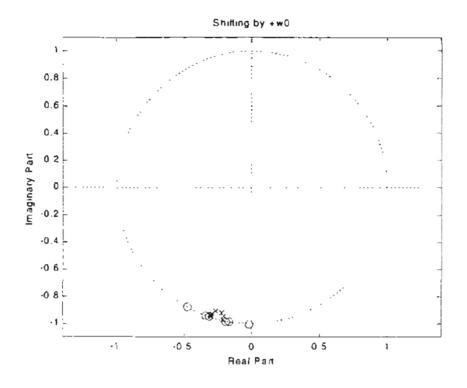

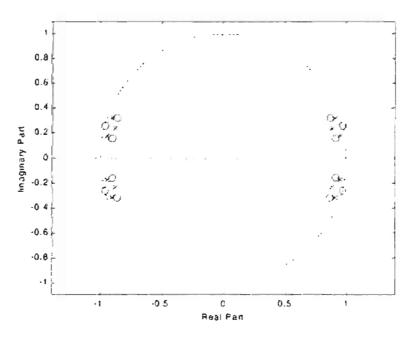

Figure 3.9 Zero/pole plot for the transfer function shifted by  $+\omega_0$ .

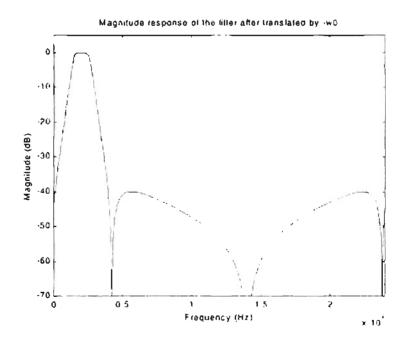

Figure 3.10 Magnitude response of the filter transfer function shifted by  $-\omega_{00}$ .

Figure 3.11 Zero/pole plot for the transfer function shifted by  $-\omega_0$ .

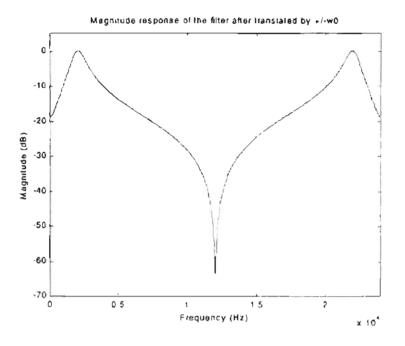

Now finally we add the two transfer functions, as is done in equation 3.13. We get the magnitude response and zeros/poles locations as shown in figure 3.12 and 3.13, respectively.

Figure 3.12 Magnitude response of the tunable heterodyne filter.

Figure 3.13 Zero/pole plot for the tunable heterodyne filter transfer function.

The final transfer function gives a  $12^{th}$  order band-pass filter centered at frequency (F<sub>S</sub>/2 - f<sub>0</sub>), where F<sub>S</sub> is the sampling frequency and f<sub>0</sub> is the heterodyning frequency. Thus this band-pass filter, which is generated from a high-pass filter through the process of frequency translation, can be tuned continuously from DC to the Nyquist frequency.

### 3.3.2 Low-pass Prototype Fixed Filter

The characteristics of the output response of the tunable heterodyne filter with a low-pass filter used as a fixed prototype filter are similar to the results obtained when a high-pass filter is used as a fixed prototype filter. Therefore we go through the similar excrecise as we did with the high-pass filter and observe the results obtained when a 6<sup>th</sup> order low-pass filter is used. The magnitude response and the zero/pole plot for the low-pass filter is given in figures 3.14 and 3.15, respectively.

Figure 3.14 Magnitude response of original Low-pass filter

Figure 3.15 Zero/pole diagram for the 6<sup>th</sup> order Low-pass filter

Figures 3.16 and 3.17 show the responses when the transfer function of the fixed low-pass filter is shifted by  $+\omega_0$ . Similarly, figures 3.18 and 3.19 shows the responses when the transfer function of the fixed low-pass filter is shifted by  $-\omega_0$ .

Figure 3.16 Magnitude response of the filter transfer function shifted by  $\pm \omega_0$ .

Figure 3.17 Zero/pole plot for the transfer function shifted by  $+\omega_0$ .

Figure 3.18 Magnitude response of the filter transfer function shifted by  $-\omega_0$ .

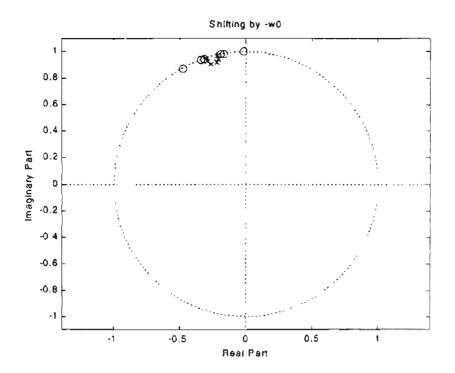

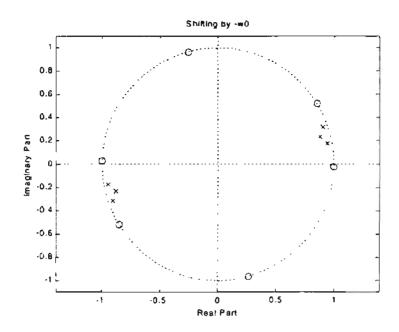

Figure 3.19 Zero/pole plot for the transfer function shifted by  $-\omega_0$ .

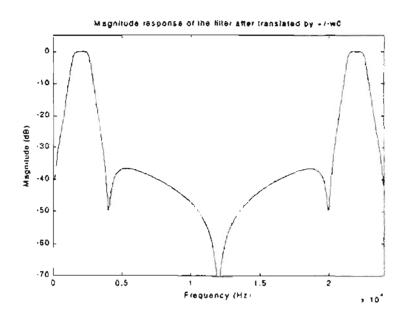

Due to the zeros and poles conjugate mirroring effect, the low-pass filter response produces an effect of having a band-pass filter centered at DC and therefore translation by  $+\omega_0$  centers the band-pass at 10kHz and translation by  $-\omega_0$  centers the band-pass at 38kHz. Comparing these results with the response of high-pass filter, we see that the only difference between the responses of the high-pass filter and the low-pass filter is where the resulting band-pass filter is centered. When we add these two translated transfer functions, we get the responses given in figure 3.20 and 3.21.

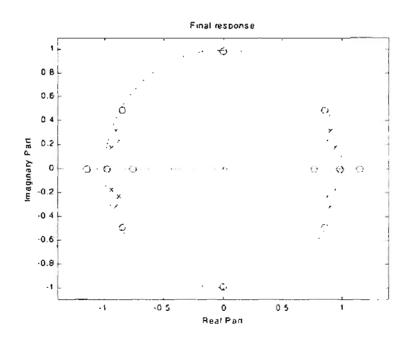

Again a  $12^{th}$  order band-pass filter is obtained which is centered at frequency  $(\omega_0)$ , where  $\omega_0$  is the heterodyning frequency. Thus this band-pass filter, which is generated from a low-pass filter through the process of frequency translation, can be tuned continuously from DC to the Nyquist frequency as well.

Figure 3.20 Magnitude response of the tunable heterodyne filter.

Figure 3.21 Zero/pole plot for the tunable heterodyne filter transfer function.

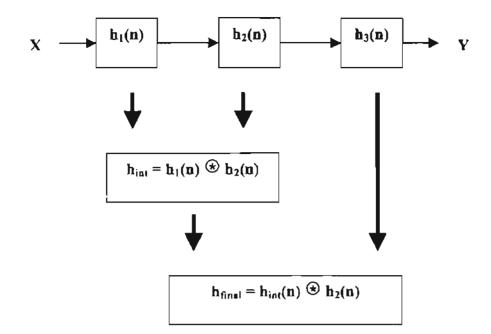

## 3.3.3 Band-pass Prototype Fixed Filter

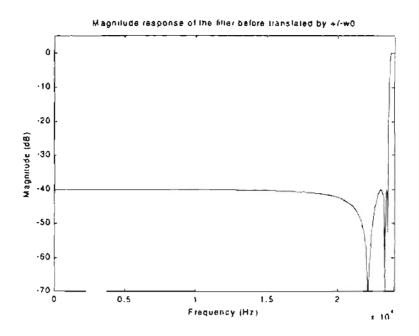

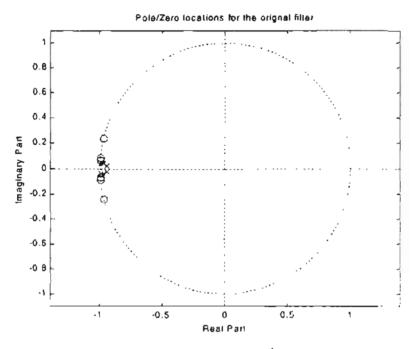

In the discussion above we have converted a  $6^{th}$  order high-pass and a  $6^{th}$  order low-pass filter to a  $12^{th}$  order tunable band-pass filter. In this sub-section we will develop and analyze the results when a  $6^{th}$  order band-pass filter is used as a fixed prototype filter in the tunable heterodyne structure. The type of filters used as prototype filter in the tunable heterodyne filters depends on the application where the structure is employed. The magnitude response of the band-pass filter is given in figure 3.22 and its corresponding zeros/poles plot is given in figure 3.23.

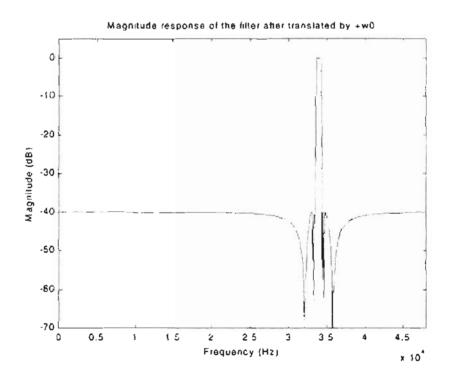

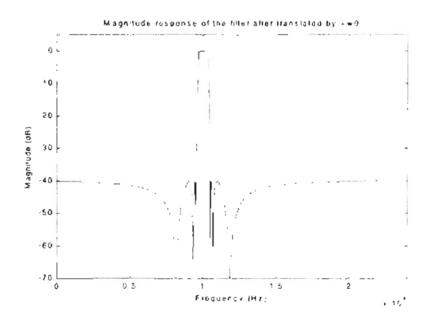

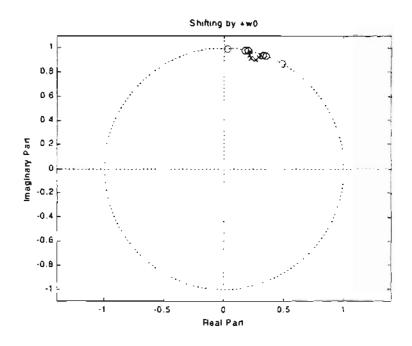

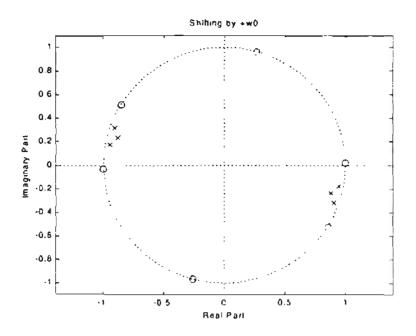

We go through the same procedure to rotate the poles and zeros of this band-pass filter by  $+\omega_0$  which gives us the corresponding magnitude response shown in figure 3.24 and the zeros/poles plot shown in 3.25. Similar to high-pass and low-pass filters, we rotate the zeros/poles location by  $-\omega_0$  to get the magnitude response and zero/pole plot as shown in figures 3.26 and 3.27, respectively.

Figure 3.22 Magnitude response of original Band-pass filter

Figure 3.23 Zero/pole diagram for the 6<sup>th</sup> order Band-pass filter

Figure 3.24 Magnitude response of the filter transfer function shifted by  $+\omega_{x_0}$ .

Figure 3.25 Zero/pole plot for the transfer function shifted by  $+\omega_0$ .

Figure 3.26 Magnitude response of the filter transfer function shifted by  $-\omega_0$ .

Figure 3.27 Zero/pole plot for the transfer function shifted by  $-\omega_0$ .

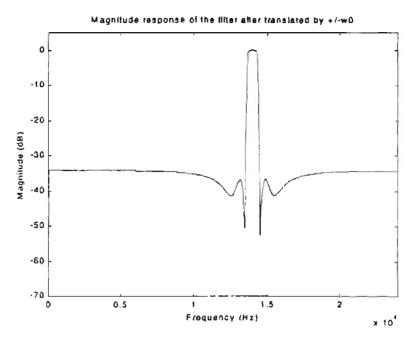

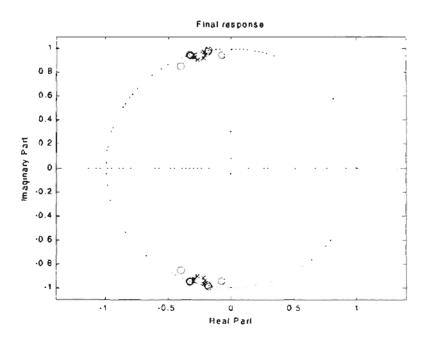

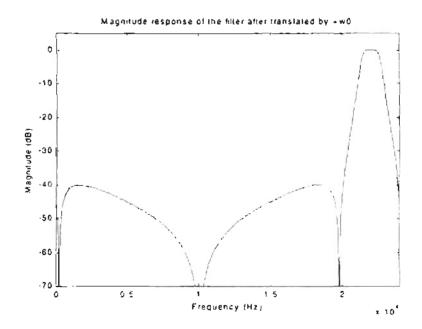

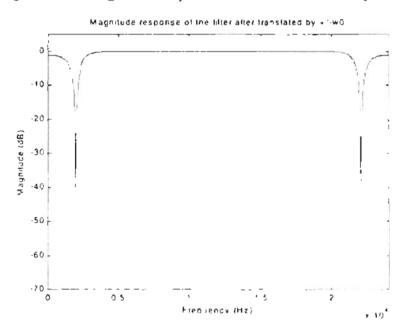

The fixed prototype band-pass filter is centered at a quarter of the sampling frequency ( $F_S/4$ ). Therefore, when we translate the zeros and poles of the band-pass filter to +/- $\omega_0$  (where the heterodyning frequency  $f_0$  is set at 10000Hz) and add these translated transfer functions as in equation 3.13, we get two band-pass filters; one centered at 2000Hz and the other one at 22000Hz. The final magnitude response and corresponding zero/pole plot for the tunable heterodyne filter is shown in figure 3.28 and 3.29, respectively.

As a consequence of having two band-pass filter responses at the output of the tunable heterodyne filter, the tuning range for this tunable heterodyne structure with the band-pass filter as prototype filter is split into two regions. Therefore we have to apply a constraint to the incoming interference frequency, thus limiting the tuning range from either DC to Nyquist/2 or Nyquist/2 to Nyquist frequency.

Figure 3.28 Magnitude response of the tunable heterodyne filter.

Figure 3.29 Zero/pole plot for the tunable heterodyne filter transfer function.

### 3.3.1 Band-stop (Notch) Prototype Fixed Filter

Since the transfer function of the tunable heterodyne filter (given in equation 3.13) is a sum of the two translated filter transfer functions, a notch filter cannot be made tunable with this structure. Figure 3.30 shows the magnitude response of a notch filter and figure 3.31 shows the magnitude response of the tunable heterodyne final output when a notch filter is utilized as the prototype filter. The output response of the tunable heterodyne filter structure in figure 3.31 shows that the notches are only 3dB deep, thus rendering the output response to appear as almost an all-pass filter.

One way to get around this problem is to have a band-pass filter that has a unique property where it can be converted into a perfect notch filter. But this characteristic for particular band-pass filters is extremely rare and limited. A special second order filter with the following transfer function can be converted into a stop-band filter

$$H(z) = \frac{(1-\alpha)}{2} \frac{(1-z^{-2})}{(1+\alpha z^{-2})}$$

(3.14)

Figure 3.30 Magnitude response of original Stop-band filter

Figure 3.31 Magnitude response of the tunable heterodyne filter.

The magnitude response of the band-pass filter and the tunable heterodyne filter is shown in figures 3.32 and 3.33, respectively. Now if we subtract ')' from the tunable heterodyne filter transfer function we get:

$$H'(z, \omega_0) = H(z, \omega_0) - 1$$

$$= \frac{B(z, \omega_0)}{A(z, \omega_0)} - 1$$

$$= \frac{B(z, \omega_0) - A(z, \omega_0)}{A(z, \omega_0)}$$

$$= \frac{B'(z, \omega_0)}{A'(z, \omega_0)}$$

(3.15)

Where H'(z,  $\omega_0$ ) is the new transfer function with zeros defined as B'(z,  $\omega_0$ ) and poles defined as A'(z,  $\omega_0$ ). Figure 3.34 shows the magnitude response of new transfer function. As can be seen from this figure we have similar results for the band-pass filter but this time we have two notches placed at 2000Hz and 22000Hz.

Figure 3.32 Magnitude response of 2<sup>nd</sup> order Band-pass filter

Figure 3.33 Magnitude response of the tunable heterodyne filter.

Figure 3.34 Magnitude response of the modified tunable heterodyne filter.

To show the effect when a band-pass filter that does not have the characteristic to be converted into a notch filter, we take the example of  $6^{th}$  order band-pass filter

described in sub-section 3.3.3. Figure 3.35 shows the magnitude response of the filter if we insert a  $6^{th}$  order filter transfer functions in equation 3.14.

Figure 3.35 Magnitude response of distorted notch filters

The poles and zeros plot corresponding to the magnitude response shown in figure 3.35 is shown in figure 3.36.

Figure 3.36 Zeros/poles plot of notch filter converted from band-pass filter

Thus the results show that if the specifications do not allow 4dB ripples at either edge of the notch, then this type of notch filter cannot be used. This matter can be further probed to find some unique way to produce distorted band-pass filter response, which yields a perfect tunable notch filter.

### 3.3.4 Tuning Ranges and Heterodyne Frequency Relationships

#### Summary

From the preceding analysis and results we can conclude that a band-pass, highpass or a low-pass filter can be tuned easily with a single parameter, the heterodyning frequency. Notice that the range of tunability depends on the type of fixed prototype filter used in the tunable heterodyne filter structure; high-pass, low-pass or band-pass. Another factor that depends on the category of the prototype fixed filter used in the heterodyne structure is the heterodyne frequency. The interference signal coming in the tunable heterodyne filter is translated to the fixed filter frequency by the process of heterodyning. Thus there exists a relationship between the interference frequency and the fixed filter frequency. This relationship is used to calculate the heterodyning frequency required to bring the interference signal to the fixed filter. The following table summarizes the range of tuning frequencies for the different types of prototype filter. This table also illustrates the relationship between the interference and the tuning heterodyne frequency.

|                                          | Low-pass<br>Filter                                  | High-pass<br>Filter                                                             | Band-pass<br>Filter                                                                                          |

|------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Tuning<br>Range                          | From DC to<br>Nyquist<br>Frequency                  | From DC to<br>Nyquist<br>Frequency                                              | 1) From DC to Nyquist/2 Frequency<br>OR<br>2) From Nyquist/2 to Nyquist Frequency                            |

| Heterodyne<br>Frequency<br>Relationships | $\mathbf{F}_{\mathrm{H}} = \mathbf{F}_{\mathrm{I}}$ | $\mathbf{F}_{\mathrm{H}} = \mathbf{F}_{\mathrm{S}}/2 - \mathbf{F}_{\mathrm{I}}$ | 1) $F_{H} = F_{F} - F_{I}$ If, $F_{I} \le F_{S}/4$<br>OR<br>2) $F_{H} = F_{I} - F_{F}$ If, $F_{I} > F_{S}/4$ |

Note It is assumed for the band-pass filter that the center of the pass-band is located at quarter of the sampling frequency

FH = Heterodyne Tuning Frequency

FS = Sampling Frequency

FI = Interference Frequency

FF = Fixed Filter Center Frequency

Table 3.1 Tuning range and heterodyne frequency relationships.

## Chapter 4

# Signal Analysis for Tunable Heterodyning Filter

## 4.1 Introduction

Figure 4.1 shows the block diagram of the Tunable Heterodyne Band-pass filter.

Figure 4.1 Block Diagram of Tunable Heterodyne Band-pass Filter.

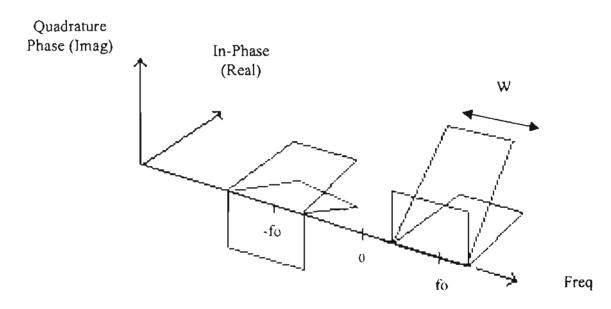

Real signals are composed of an infinite number of frequencies limited to a bandwidth of 'W'. All the real signals have equal amounts of positive and negative frequencies. Therefore, for signal x(t) we would have spectrum |X(f)| = |X(-f)|. This is shown in figure 4.2, where the three dimensional real signal spectrum is shown at (+/- fo) frequency. The real (in-phase) component of the spectrum is shown on the real plane and the imaginary (Quadrature) component of the real signal spectrum is shown on the imaginary plane [17]. Terms, ln-phase and Quadrature signal are used to signify the fact that the imaginary and real components of the real signals are 90<sup>o</sup> out of phase with respect to each other.

Figure 4.2 3D Representation of Real Signal Spectrum.

### 4.2 Signal Analysis of Tunable Heterodyne Band-pass Filter

### 4.2.1 Signal Response of In-phase and Quadrature Signals

The concept of tunable heterodyne band-pass filter utilizes the tricks of complex mathematics to eliminate the images generated through the process of heterodyning. This process yields a hardware efficient tunable band-pass filter with the ability to tune continuously across the range from DC to Nyquist frequencies in the case of high-pass and low-pass prototype filters and from DC to Nyquist/2 or Nyquist/2 to Nyquist in the case of band-pass prototype filters. To illustrate the concept used to develop the foundation of this theory, the following case can be used. We assume an input to our tunable heterodyne band-pass filter structure (figure 4.1) is a band limited signal of 'W' width centered at frequency  $f_C$  with narrowband interference at frequency  $f_1$  shown in figure 4.3. Figure 4.3 shows the real signal spectrum X(f) with both positive and negative frequencies centered at +/-  $f_c$  respectively.

Figure 4.3 Wide-band signal with narrowband interference.

In the Splitter circuit, the input signal is distributed in two separate channels, where one of the branches multiplies the input signal with cosine and in the other channel the input signal is multiplied by sine. The frequency for both the sine and cosine signals' generation is set as the heterodyne frequency. For future reference we would identify the channel with cosine mixers as the 'In-phase' channel and channel with sine mixers as the 'Quadrature' channel, since both are  $90^{\circ}$  out of phase from each other [17].