# STUDY OF RECURSIVE DIVIDE ARCHITECTURES IMPLEMENTATION FOR DIVISION AND

MULTIPLICATION

By

## AMEY P PHADKE

Bachelor of Engineering in Electronics

University of Pune

Pune, India

2007

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE December, 2011

# STUDY OF RECURSIVE DIVIDE ARCHITECTURES IMPLEMENTATION FOR DIVISION AND

MULTIPLICATION

Thesis Approved:

Dr. James E. Stine

Thesis Adviser

Dr. Chris Hutchens

Dr. Louis G. Johnson

Dr. Sheryl A. Tucker

Dean of the Graduate College

# TABLE OF CONTENTS

|                                                     |                                                                                                                                                                                                                      | Page        |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1                                                   |                                                                                                                                                                                                                      |             |

| NTRC                                                | DUCTION                                                                                                                                                                                                              |             |

| 2                                                   |                                                                                                                                                                                                                      |             |

| EVIEV                                               | W OF LITERATURE                                                                                                                                                                                                      |             |

| 2.1.                                                | DIGIT RECURRENCE ALGORITHM                                                                                                                                                                                           |             |

| 2.2.                                                | QUOTIENT SELECTION TABLE                                                                                                                                                                                             |             |

| 2.3.                                                | CONTAINMENT CONDITION                                                                                                                                                                                                |             |

| 2.4.                                                | CONTINUITY CONDITION                                                                                                                                                                                                 |             |

| 2.5.                                                | ON THE FLY CONVERSION                                                                                                                                                                                                | 1           |

|                                                     |                                                                                                                                                                                                                      |             |

| 3                                                   |                                                                                                                                                                                                                      |             |

|                                                     | DOLOGY                                                                                                                                                                                                               |             |

|                                                     |                                                                                                                                                                                                                      | 1           |

| ETHO                                                | DOLOGY                                                                                                                                                                                                               | 1           |

| ЕТНО<br>3.1                                         | DOLOGY                                                                                                                                                                                                               | 1<br>1<br>1 |

| ETHO<br>3.1<br>3.2                                  | DOLOGY<br>Division<br>Radix2 Division                                                                                                                                                                                |             |

| ETHO<br>3.1<br>3.2<br>3.3                           | DOLOGY<br>Division<br>Radix2 Division<br>Radix4 Division                                                                                                                                                             |             |

| ETHO<br>3.1<br>3.2<br>3.3<br>3.4                    | DOLOGY<br>DIVISION<br>RADIX2 DIVISION<br>RADIX4 DIVISION<br>RADIX16 DIVISION USING OPERAND SCALING                                                                                                                   |             |

| ETHO<br>3.1<br>3.2<br>3.3<br>3.4                    | DOLOGY<br>Division<br>Radix2 Division<br>Radix4 Division<br>Radix16 division using operand scaling<br>Radix 512 division                                                                                             |             |

| ETHO<br>3.1<br>3.2<br>3.3<br>3.4                    | DOLOGY<br>DIVISION<br>RADIX2 DIVISION<br>RADIX4 DIVISION USING OPERAND SCALING<br>RADIX16 DIVISION USING OPERAND SCALING<br>RADIX 512 DIVISION<br>3.5.1 Recoding                                                     |             |

| ETHO<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6      | DOLOGY<br>DIVISION<br>RADIX2 DIVISION<br>RADIX4 DIVISION USING OPERAND SCALING<br>RADIX16 DIVISION USING OPERAND SCALING<br>RADIX 512 DIVISION<br>3.5.1 Recoding<br>3.5.2 Adder                                      |             |

| ETHO<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>4 | DOLOGY<br>DIVISION<br>RADIX2 DIVISION<br>RADIX4 DIVISION<br>RADIX16 DIVISION USING OPERAND SCALING<br>RADIX 512 DIVISION<br>3.5.1 Recoding<br>3.5.2 Adder<br>RECURSIVE DIVIDE/MULTIPLIER UNIT                        |             |

| ETHO<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>4 | DOLOGY<br>DIVISION<br>RADIX2 DIVISION<br>RADIX4 DIVISION USING OPERAND SCALING<br>RADIX16 DIVISION USING OPERAND SCALING<br>RADIX 512 DIVISION<br>3.5.1 Recoding<br>3.5.2 Adder<br>RECURSIVE DIVIDE/MULTIPLIER UNIT. |             |

| 4.1.2 | HDL Coding            | 48 |

|-------|-----------------------|----|

| 4.1.3 | Logic synthesis       | 50 |

| 4.1.4 | Place and Route       | 52 |

| 4.1.5 | Post-Layout Analysis: | 52 |

| 4.2    | 2 COMPARISON | 53 |

|--------|--------------|----|

| 5      |              | C  |

| ONC    | CLUSION      | 57 |

| REFERE | ENCES        | 59 |

| APPPEN | NDICES       | 60 |

# LIST OF TABLES

| Table                                                                        | Page |

|------------------------------------------------------------------------------|------|

| Table 1 - Truth table for OTF logic                                          | 15   |

| Table 2 - Signed Digit Conversion to Normal Representation                   |      |

| Table 3 - Truth table for Radix2 QST                                         |      |

| Table 4 - Quotient bit encoding for Radix2                                   |      |

| Table 5 - Selection Intervals and mk constants [4]                           | 22   |

| Table 6 – Quotient bit encoding for Radix4                                   | 24   |

| Table 7 - Selection multiples for scaling                                    |      |

| Table 8 - Quotient selection table for Radix16                               |      |

| Table 9 - Quotient recoding in Carry-Save format                             |      |

| Table 10 - Division cycle timing chart                                       |      |

| Table 11 - Multiplication cycle timing chart                                 |      |

| Table 12 - Radix2 Divide Results                                             | 53   |

| Table 13 - Radix4 Divide Results                                             | 54   |

| Table 14 - Radix16 Divide Results                                            | 54   |

| Table 15 - Radix512 Divide Results                                           | 54   |

| Table 16 - Radix512 Mult-Div Results                                         |      |

| Table 17 - Relative area increase                                            | 56   |

| Table 18 - Single Precision Comparisons for various multiplier architectures | 56   |

# LIST OF FIGURES

| Figure P                                                                 | Page |

|--------------------------------------------------------------------------|------|

| Figure 1 - Distribution of FP instructions                               | 2    |

| Figure 2 - Distribution of unit stall time                               | 3    |

| Figure 3 - Robertson's PD Diagram                                        | 9    |

| Figure 4 - On the fly conversion                                         | 13   |

| Figure 5 - Radix2 hardware block diagram                                 | 20   |

| Figure 6 - Hardware block diagram for QST                                | 23   |

| Figure 7 - Radix4 hardware block diagram                                 | 24   |

| Figure 8 - Radix16 hardware block diagram                                | 30   |

| Figure 9 - SBTM implementation                                           | 32   |

| Figure 10 - Block diagram for recoder                                    | 36   |

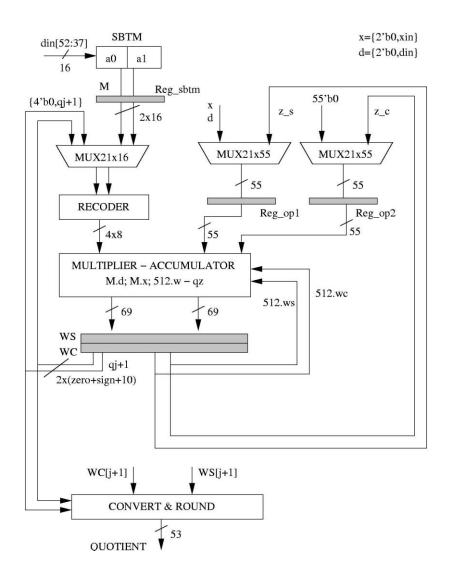

| Figure 11 - Radix512 hardware block diagram                              | 38   |

| Figure 12 - Radix512 hardware block diagram using Carry-Save format      | 39   |

| Figure 13 - Radix512 hardware block diagram for integrated Mult-Div Unit | 43   |

| Figure 14 - Design Flow                                                  | 46   |

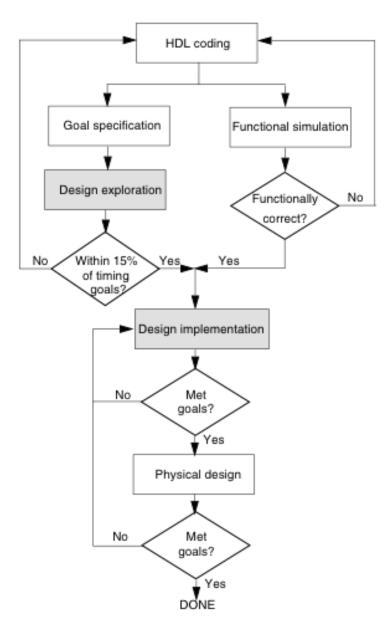

| Figure 15 - ModelSim simulation snapshot                                 | 49   |

| Figure 16 - Place and Route Design Flow                                  | 51   |

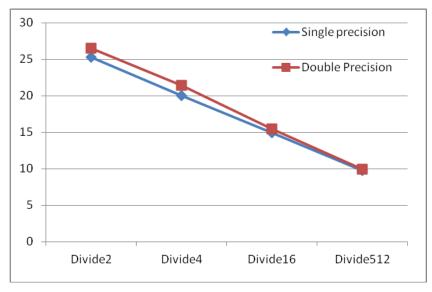

| Figure 17 - Delay Comparisons                                            | 55   |

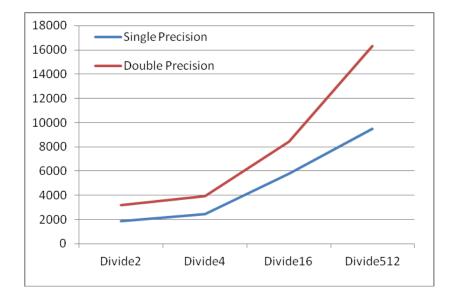

| Figure 18 - Area Comparisons                                             | 55   |

## CHAPTER I

#### INTRODUCTION

Due to advancement in VLSI technology many industrial and business related applications makes use of floating point operations as a result of which floating point unit has become critical component of modern processor design as well as dedicated embedded systems. Special purpose applications such as graphics rendering has further demanded need of high speed & efficient floating point units as performance of the processor is often limited by high latency of floating point unit.

Modern applications consist of several floating-point operations, which mainly include addition, subtraction, multiplication, division and square root [1]. These days focus is more on the implementation of high speed floating point adders and multipliers as a result of which latency of these operations has come down to 2 to 4 cycles, but at the same time latency associated with division and square root is large, in some cases latency for such operations is around 50-60 cycles. This ignorance towards implementation of high-speed divider is due to instruction mix of the benchmarks, which are used to validate performance of processors.

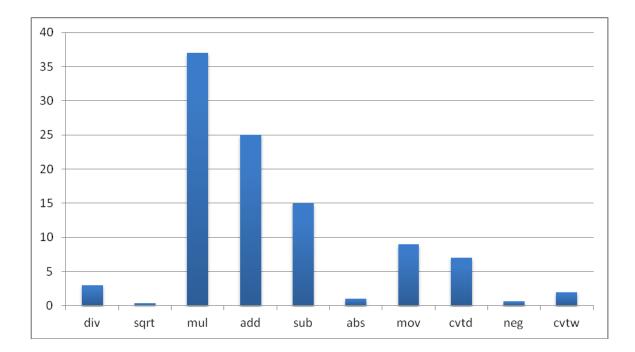

Figure 1 - Distribution of FP instructions

Figure1 shows average frequency of division and square root operations in benchmark suite as compared to other floating-point operations. All benchmark applications are compiled using O3 optimization. From figure1 we can observe that division and square root are very uncommon operations comprising only 3% of total floating point operations [2].

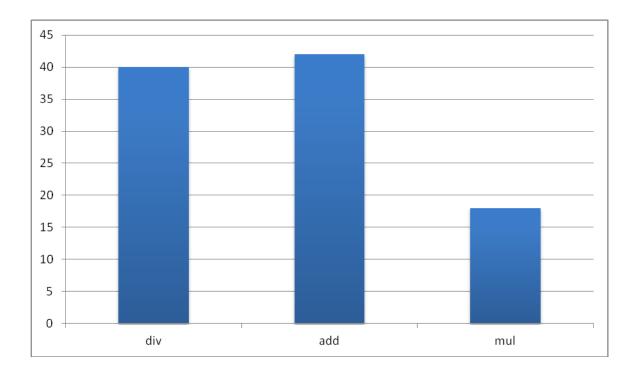

On the other hand floating point multiplication holds for 37% of the instructions & floating point addition accounts for 55% of the instructions. Due to this common view of division operation is that it is an infrequent operation which does not required high priority, but if we look into Figure2 which shows latency associated with floating point operations, it indicates that latency of divide operation is 20 cycle as compared to multiply and addition operations which has 3 cycle of latency each. Distribution of stall time due to FP hardware shows that FP division is responsible for 40% of the latency, FP addition accounts for 42% and FP multiply results in remaining 18%. This shows that slow division operation results in overall degradation of system performance.

Figure 2 - Distribution of unit stall time

There is an extensive mathematical literature available for implementation of division algorithm but still implementation of these algorithms is considers as black box due to many parameters involved in it. Division algorithms can be divided into five classes such as digit recurrence, functional iteration, very high radix, table look up and variable latency.

Some division algorithms don't belong to any specific class; they make the use of more than one technique mentioned above to perform the operation. Out of algorithms mentioned above digit recurrence is the oldest class of high-speed division as a result of which lot of literature is published related to it. The most common and popular implementation of digit recurrence algorithm is SRT division algorithm, which has been named SRT division by Freiman taking its name from the initials of Sweeney, Robertson and Tocher, who developed the algorithm independently at the same time.

Implementation work related to SRT division algorithms have been done previously without an actual implementation, Ercegovac and Lang provide comparison between different division algorithms in terms of delay and area using full adder units and NAND gate units. Objective of this work is to provide accurate comparison between different SRT algorithms by actual RTL implementation of all of them, followed by synthesis and PNR of the design in order to get area, delay and power numbers associated with it. This work includes implementation of SRT Radix2, Radix4, Radix16 and Radix512 algorithms. More emphasis is given on the implementation of high Radix512 division algorithms and how the same hardware can be utilized to perform high radix multiplication to save area and maximize performance.

### CHAPTER II

#### **REVIEW OF LITERATURE**

Digit recurrence algorithm consists of n iterations, where each iteration produces one digit of the quotient. However, digit recurrence algorithms do have preprocessing as well as post processing steps, which are vital in order to, make sure that the dividend, divisor, quotient and remainder are presented correctly [3].

#### 2.1. Digit Recurrence Algorithm

Division operation starts by taking divisor d, dividend x and computes quotient q, and its remainder, r. the basic equation for division is recursive as follows:

$$x = q \cdot d + r \quad \text{where } r < d \tag{2.1.1}$$

The quotient digit is one of the most interesting elements in the division process. In particular, quotients are most often implemented as redundant digit set. The reason behind doing so is that it simplifies the quotient digit selection. Unfortunately as radix increases, complexity of the quotient digit selection also increases. Therefore as designers one of the challenges for division is to make right decision on which algorithm to chose for implementation and its circuit implications [4]. This tradeoff is noticeable in division due to variation in which division can be implemented.

Digit recurrence algorithm of division works iteratively using following equation where  $w_i$  is the partial remainder for iteration *i*, *d* is the divisor, *r* is the radix and *qi* is the quotient digit for iteration *i*

$$w_{i+1} = r \cdot w_i = q_{i+1} \cdot d$$

(2.1.2)

Algorithm starts by assigning first partial remainder denoted by  $w_{[0]}$  as dividend x. The quotient selection function is chosen based on comparison between the divisor and shifted partial reminder

$$q_{i+1} = QST(r, w_i, d)$$

(2.1.3)

Where QST is the Quotient Selection Table. The QST can be implemented in various ways such as using ROM, PLA or combinational logic. All RTL implementation in this work use combinational logic to construct QST due to an obvious advantage of speed over other techniques as well as in order to avoid use of Macro block in the design.

The most challenging step in the division procedure is the comparison between the divisor and remainder to determine the quotient bit. If this is done by subtracting d from  $w_i$ , one has to be careful if the result is negative. If so, a correction operation occurs restoring the remainder to the previous interaction, this method is called restoring division. Non-restoring division is an alternative for sequential division by having specific logic for not correcting the quotient; this is achieved by allowing a correlation factor within the algorithm. Unfortunately, because non-restoring division requires a correction factor, there may be some post processing

that is required if the final remainder is negative. Accordingly, it is necessary to have a correction step that adjusts the quotient as flows where m is the final iteration of the recurrence relation and  $r^{-n}$  is an ulp

$$q = q_{\rm m} \text{ if } w_{\rm i} >= 0$$

(2.1.4)

$$q_{\rm m} - {\rm r}^{-{\rm n}}$$

if  $w_{\rm i} < 0$  (2.1.5)

Therefore, the process of division by recurrence can improve upon general division algorithms by taking advantage of flowing elements

- 1. As Radix increases, it decreases the number of iterations assuming  $r = 2^{k}$

- 2. Redundancy within the quotient digit set reduces and simplifies the QST

- 3. Partial remainder can be implemented using redundant notation, which simplifies the computation of the partial reminder using carry-free adder.

All the designs implemented in this work make the use of these choices and showing tradeoffs for these choices.

#### 2.2. Quotient Selection Table

This section presents basic theoretical background required to design quotient digit selection function. Algorithm for division is challenging because the implementations for quotient digit selection vary from design to design. The basic idea of the QST is to choose the value of quotient digit  $q_{i+1}$ , based on comparison between shifted partial remainder and the divisor. A symmetric SD digit set is utilized where the range of quotient is

$$q_{i+1}$$

belongs to {-a, -a+1, ..., -1, 0, 1, ..., a-1, a}

Redundancy factor  $\rho$  is defined as

$$\rho = \frac{a}{r-1}, \frac{1}{2} < \rho < 1 \tag{2.2.1}$$

Even though choosing the right function for a QST is complex, it can be easily formulated into two conditions called containment and continuity. The containment condition identifies selection interval for each quotient digit qi+1. On the other hand continuity condition details the range, which the quotient digit is selected.

#### 2.3. Containment condition

Since the equation for recurrence involves subtraction and shifts from equation 2.1.2, it is important to note that the quotient digit selection becomes difficult. For example, if user decided to divide 300 / 5 in radix 10 and chooses  $q_i$  to be 2, this will violate the bound available for next quotient digit making the computation cumbersome. In other words a quotient digit will need to be calculated for partial reminder of 200.

The containment condition sets up the selection intervals necessary for computing the subsequent quotient digit. For given quotient digit  $q_{i+1}$  to be chosen as k, there should be bounds on an interval of allowable partial reminders, these regions are defined by the interval  $[L_k, U_k]$  such that  $L_k$  is the smallest value of partial remainder  $r.w_j$  for which it is possible to choose  $q_{i+1} = k$ , whereas  $U_k$  is largest value of partial reminder  $r.w_j$  for which it is possible to choose  $q_{i+1} = k$ .

In other words selection intervals are for quotient digit  $q_{i+1} = k$  is given by

$$U_k = (k + \rho). d$$

(2.3.1)

$$L_k = (k - \rho). d$$

(2.3.2)

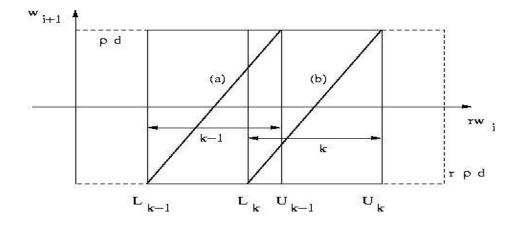

Figure 3 - Robertson's PD Diagram

Sometimes, this can be visualized by examining a graph of subsequent partial remainder,  $w_{i+1}$  versus the shifted partial remainder, *r*.  $w_i$ . This visualization is represented in Robertson's diagram as shown in figure3. Robertson's plot the recurrence relationship for a given quotient digit  $q_{i+1}$ , assuming the user is varying the shifted partial reminder and plotting or computing the subsequent partial remainder. The axis of Robertson's diagram is bounded by axis ([ -rp.d ; rp.d;=p.d;p.d]) where the axis function defines the range of function such that the argument is defined as {[ $x_{min}$ ;  $x_{max}$ ; $y_{min}$ ;  $y_{max}$ ]}. Interestingly, the redundancy introduced by using SD digit set imposes an overlap between quotient digits. For example, in figure3 there is an overlap between  $q_{i+1} = k-1$  and  $q_{i+1} = k$ . This overlap will be useful in defining the continuity equation.

#### 2.4. Continuity Condition

Since the containment condition defines range of subsequent partial reminder, choosing the correct quotient digit from this region is job of continuity condition. To satisfy the containment condition, the minimum value of x-axis of the Robertson's diagram is chosen such that  $q_{i+1}$ =k is our quotient digit. This can be defined as the following inequality where  $s_k$  is the minimum value that user chooses before an implementation is devised.

$$L_k \ll S_k \ll U_k \tag{2.4.1}$$

Unfortunately, because the overlap that occurred in the containment condition, the quotient digit may be chosen as either k or k-1. For example, in figure3 an overlap exists between  $L_k$ , which is Lower bound for quotient digit k, and  $U_{k-1}$ , which is the largest bound on partial reminder for a quotient digit to be k-1 such that sk can either be k-1 or k. Since the containment equations are defined, it is easy to measure this overlap as

$$U_{k-1} - L_k = (k - 1 + \rho. d) - (k - \rho. d) = (2. \rho - 1).d$$

(2.4.2)

The simplest selection function is to make  $s_k$  constant and do a comparison on the constant. Thus many implementations for QST's resort to ROM or PLA elements. The constants should satisfy the following equation

$$\max(\mathbf{L}_{k}) \leq \mathbf{m}_{k} \leq \min(\mathbf{U}_{k-1}) + ulp$$

A second requirement of the selection in the continuity condition states that every value of r.w[i] must belong to at least one selection interval. This can be expressed as

$$U_{k-1} \ge L_k - r^{-n} \tag{2.4.3}$$

As shown in Robertson's diagram the term  $r^{-n}$  reflects granularity of representable values, since r.w[*i*] is represented with *n* fractional digits. To simplify the derivations and to be independent of iteration *i*, the more conservative bound is

$$U_{k-1} \ge L_k$$

By substituting the values of bound in above equation we get

$$k + 2k - 4 \qquad (2.4.4)$$

which results in  $\rho \ge 2^{-1}$

This proves that minimum bound on the redundancy factor  $\rho$  is 1/2

2.5. On the fly conversion

The use of the redundant representation complicates the use of SRT division. In most radix system that most digital devices employ, the digit set is restricted to 0, ...., r-1. One of the benefits of using SD number system is that it simplifies the QST. Although SD numbering is useful, it unfortunately is cumbersome to convert from SD notation back to a conventional representation.

Fortunately division algorithm implemented in this work calculates quotient bit with Most Significant Digit First. Arithmetic performed in this fashion is sometimes referred as online arithmetic. Since quotient is calculated as a fraction

$$q_i = \sum q_m r^{-m} \tag{2.5.1}$$

Therefore, using the correction factor and plugging it into the equation above results in the following form

$$q_{i+1} = q_i + q_{i-1} r^{-i(i+1)} \qquad q_{i+1} \ge 0 \qquad (2.5.2)$$

$$q_{+1} = q_{-1} r^{-j} + (r_{-1} q_{+1}) r^{-(i+1)} q_{i+1} < 0 \qquad (2.5.3)$$

The later equation is formed since the quotient for that iteration is negative; hence subtraction is required for the conversion. If we substitute a variable for the correction factor,  $qm_i$  the equation shown above is presented more efficiently as

$$q_{i+1} = q_i + q_{i-1} r^{-i(i+1)}$$

$q_{i+1} \ge 0$  (2.5.4)

$$q_{i+1} = q_{i+1} (r - q_{i+1}) r^{-(i+1)} \qquad q_{i+1} < 0$$

(2.5.5)

With simple manipulation we can also convert the equation above into an equation for  $qm_i$  such that  $qm_i = q_i - r^{-n}$ . In other words, if the final remainder is negative, subtraction of an *ulp* from the quotient is performed to adjust the correction factor. Then  $qm_i$  is calculated as follows

$$q_{i+1} > 0 \qquad (2.5.6)$$

$$q_{n_1} = q_{n_1} (f_{-1}) q_{-1} ) f^{(i+1)} \qquad q_{i+1} \le 0 \qquad (2.5.7)$$

Fortunately there is an easy algorithm to convert back redundant quotient into conventional representation for online algorithms. It is called as on-the-fly conversion. The basic idea behind on the fly conversion is to produce the conversion as the digits of the quotient are produced by performing a concatenation instead of any carries or borrows within a carry propagate adder. One element keeps tracks of the quotient, whereas other element keeps track of normal quotient-*ulp*.

Since on-the-fly conversion involves concatenations, the MSDF enables the appropriate quotient digit to be converted by simple combinational logic and shifting as opposed to utilizing CPA. The algorithm can be summarized as follows

$$q_{i+1} = \{q_i, q_{i+1}\}$$

if  $q_{i+1} \ge 0$  (2.5.8)

$$q_{i+1} = \{qm_{i}(r - q_{i+1})\}$$

if  $q_{i+1} < 0$  (2.5.9)

&

$$q_{1} = q_{1} = 1$$

if  $q_{i+1} > 0$  (2.5.10)

$$q_{n} = \{q_{n} \in \{ f_{-1} \mid f_{q_{+1}} \} \text{ if } q_{i+1} \le 0$$

(2.5.11)

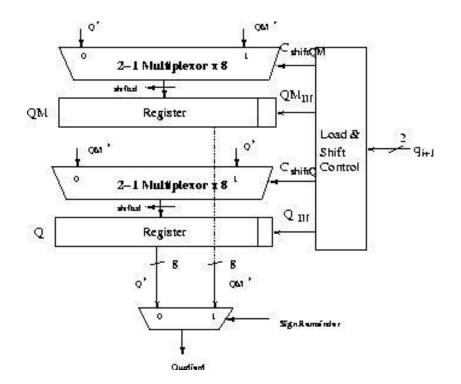

Figure 4 - On the fly conversion

In order to implement on-the-fly conversion, it requires 2 registers to hold  $q_i$  and  $qm_i$ . These registers are shifted one digit left with insertion into the least-significant digit, depending on the value of  $q_{i+1}$ . In other words, depending on what the subsequent quotient digit, the register either chooses q or qm and concatenates the current converted quotient digit into the least significant digits. The figure4 shows on the fly conversion technique implemented for Radix2 division. In all the implementations, structure of on-the-fly technique remains the same except number of bits of quotient shifted in every iteration changes; number of bits shifted into 2 registers depends on the radix of the divider.

Two multiplexers are utilized to select either q or qm and combinational logic is used to select  $q_{in}$  or  $qm_{in}$ . In order to handle shifting after every cycle, the outputs of the multiplexor are shifted by one (multiplied by 2, which changes for other radix dividers) and either  $q_{in}$  or  $qm_{in}$  are inserted into the least significant bit during each load.

The final multiplexer choose the correct quotient once the final reminder is known. If the sign of final reminder is 1, it will choose qm since this register contains the proper corrected quotient. Finally  $q_{star}$  and  $q_{mstar}$  are designated to  $q_{i+1}$  and  $qm_{i+1}$  respectively.

For Radix2 on the fly conversion, the registers are updated according to the table1. The values in this table are computed utilizing the equations above for  $qm_i$  and  $q_i$ . The quotient digit set used for this example is {-1, 0, 1}. The values of  $C_{shiftq}$  and  $C_{shiftqm}$  are used to control the multiplexers. The values of  $q_{in}$  and  $qm_{in}$  is the concatenation element input into the register. The quotient is utilized as input to compare  $C_{shiftq}$ ,  $C_{shiftqm}$ ,  $q_{in}$  and  $q_{min}$ . In order to simplify the logic, the quotient utilizes one hot logic encoding.

(One hot logic is chosen to simplify the digital logic design; this doesn't mean it is mandatory to use the same technique)

Boolean two-level simplified expressions for control signal are as follows

$$C_{s \ h \ i} = q_{i \neq 1}[Q]$$

$$C_{s \ h \ i} = q_{i \neq 0}[M]$$

$$q_{i} = q_{i+1}[0] + q_{i+1}[1]$$

$$q \ m = \sim (q_{i+1}[0] + q_{i+1}[1])$$

For example suppose conversion is required for the following Signed Digit number 11010 to a conventional representation using on-the-fly conversion. Table2 shows the same example. At step i=0, the values of both registers are reset which is accomplished by using a flip-flop with reset capabilities. In addition since division is online algorithm, on-the-fly conversion works from most significant bit to last significant bit. The last value in the register is the final converted value assuming a fractional number for  $q_i$  and  $qm_i$ , which is 0.78125 and 0.77334375 respectively

It should be obvious that both these numbers are one ulp from each other (i.e. an ulp is  $2^{-7}$

or 0.0078125) and 0.78125 is the conventional representation.

| qi <sub>+1</sub> | $q_{in}$ | $C_{shiftq}$ | $\boldsymbol{q}_{i+1}$ | qm <sub>in</sub> | $C_{shiftqm}$ | $qm_{i+1}$           |

|------------------|----------|--------------|------------------------|------------------|---------------|----------------------|

| 1                | 1        | 1            | $\{q_{i},1\}$          | 0                | 0             | ${q_{i},0}$          |

| 0                | 0        | 1            | {q <sub>i</sub> ,0}    | 1                | 1             | {qm <sub>i</sub> ,1} |

| -1               | 1        | 0            | $\{qm_i, 1\}$          | 0                | 1             | {qm <sub>i</sub> ,0} |

| i | qi | q         | qm        |

|---|----|-----------|-----------|

| 0 | -  | 0         | 0         |

| 1 | 1  | 0.1       | 0.0       |

| 2 | 1  | 0.11      | 0.10      |

| 3 | 0  | 0.110     | 0.101     |

| 4 | 1  | 0.1101    | 0.1100    |

| 5 | -1 | 0.11001   | 0.11000   |

| 6 | 0  | 0.110010  | 0.110001  |

| 7 | 0  | 0.1100100 | 0.1100011 |

Table 1 - Truth table for OTF logic

Table 2 - Signed Digit Conversion to Normal Representation

## CHAPTER III

#### METHODOLOGY

In this section initially we describe how lower radix divider were built and problems associated with the techniques involved in it. It is followed by an explanation of operand scaling technique, and its implementation in higher radix division

### 3.1 Division

The division algorithm performs division between two double precision floating point numbers x and d, that produces quotient q

$$q = \frac{x}{d} \tag{3.1.1}$$

In the algorithm described in this work only the mantissa is calculated since sign and exponent calculation is pretty straightforward. The ranges of the operands are

$$\frac{1}{2} \le d \le 1 \tag{3.1.2}$$

$$\frac{1}{2} \le x \le 1 \tag{3.1.3}$$

So for the quotient we have -

$$\frac{1}{2} \le q \le 1 \tag{3.1.4}$$

The IEEE double precision standard defines a format of 64 bits for this representation. These 64 bits are divided into 3 fields sign, exponent and mantissa consists of 1, 11 and 52 bits respectively. Because number in this format are normalized with the mantissa in the range 1 < x < 2 with most significant bit is always 1 and can be omitted. Thus real mantissa consists of 52 bit with 1 in most significant position, giving total of 53 bits, as our algorithms requires both the operands to be in the range of [1/2, 1] we divide the IEEE mantissa by 2 and increase their exponent respectively. This is similar to shifting the mantissa right by one bit, algorithm also requires d > x so when this condition is not satisfied mantissa is further divide by 2 due to which x looks like:  $x = 0.0 x_{[-1]}x_{[-2]} x_{[-3]}....x_{[-53]}$  number of bits of both operands are extended by 1 bit from 53 to 54 bits to make sure it don't lose the precision due to right shift [4].

#### 3.2 Radix2 Division

The Radix2 division SRT algorithm is most easy to implement. It produces one bit of quotient every iteration, requiring 25 or 54 clock cycles for single and double precision floating point respectively. This algorithm is an extension of non-restoring division with a quotient digit set of  $\{-1, 0, 1\}$ . The equation used for this division is as follows

$$w_{i+1} = 2. w_i = q_{i+1} d$$

(3.2.1)

SRT division was named after Sweeney, Robertson and Touher. Main objective of this algorithm is to speed up the division by allowing 0 as a quotient digit. This eliminates need of subtraction or addition when the value of quotient selected is 0

Now we will derive the containment and continuity conditions for Quotient Selection table. Using the equation of containment and  $\rho = 1$ , the following condition exists

$$L1 = 0$$

$U1 = 2.d$  (3.2.2)

$$L0 = -d$$

$U0 = d$  (3.2.3)

$$L-1 = -2d$$

$U-1 = 0$  (3.2.4)

To maximize the selection of quotient digit with value 0, most straight forward quotient selection table

$$q_{i+1} = 1$$

if  $d = 1$  (3.2.5)

$$q_{i+1} = 0 \quad \text{if } -d \leq 1$$

$$q_{i+1} = -1 \text{ if } -24 \times 10^{-1} \text{ (3.2.7)}$$

From the equation expressing number of bits of divisor required for QST we get

$$2^{-\delta} \le \frac{2\rho - 1}{2(a - \rho)} = \frac{1}{2(1 - 1)} = \infty$$

Consequently, a single set of selection constants can be used for whole range of divisor (it means quotient selection is independent of value of the divisor. So the equation becomes

$$q_{i+1} = 1$$

if  $\frac{1}{2} < 2w[i]$  (3.2.8)

$$q_{i+1} = 0$$

if  $-\frac{1}{2} < 2w[i] \le \frac{1}{2}$  (3.2.9)

$$q_{i+1} = -1$$

if  $2w[i] < \frac{-1}{2}$  (3.2.10)

So we require 3 bits of partial remainder to find the quotient as sign bit, integer bit and first fraction bit. Truth table for implementation is shown in Table3

| Sign | Int           | f0           | Result       | Quotient |

|------|---------------|--------------|--------------|----------|

| 0    | 0             | 0            | <1/2         | 0        |

| 0    | 0             | 1            | >=1/2        | 1        |

| 0    | 0             | 0            | >=1/2        | 1        |

| 0    | 0             | 1            | >=1/2        | 1        |

| 0    | 1             | 0            | <-1/2        | -1       |

| 0    | 1             | 1            | <-1/2        | -1       |

| 0    | 1             | 0            | <-1/2        | -1       |

| 0    | 1             | 1            | >=1/2        | 0        |

|      | Table 3 - Tri | ith table fo | r Radix2 OST |          |

**Table 3 -** Truth table for Radix2 QST

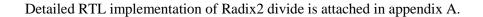

Each quotient bit is recoded into 2 bits as q+ and q- to simplify logical implementation. Hardware implementation of Radix2 divide is shown below in figure5

Steps involved in Radix2 SRT divide are as follows

- On reset operand x is loaded in. 2 bits are added to it at the start which serves as sign and a. integer bit. It acts as first partial remainder w [0]

- b. Partial reminder is shifted by 2 every iteration

- c. First 3 bits of partial reminder identifies correct quotient which is recoded into 2 bits as q+ and q-

- d. Selected quotient chooses appropriate value of d from  $\{d, 0, -d\}$

- e. When -d is selected multiplexor chooses inverted version of d & additional 1 required to produce its 2's compliment is added as carry input to the CPA adder.

- f. Redundant quotient bit is sent to OTF (On The Fly) converter.

- When algorithm requires input operands to be of size greater than double precision, delay due g. to carry propagate adder becomes the critical path, CPA can be replaced by carry save format adder.

| Quotient | q+ | q- |

|----------|----|----|

| 0        | 0  | 0  |

| 1        | 0  | 1  |

| -1       | 1  | 0  |

Table 4 - Quotient bit encoding for Radix2

Figure 5 - Radix2 hardware block diagram

#### 3.3 Radix4 Division

In Radix4 divider algorithm two possibilities exist for redundant quotient digit set with digit set can be {-2, 1,0, 1, 2} or {-3, -2, -, 1, 0, 1, 2, 3}. The case with a=2 has an advantage that

multiple of d required are easy to generated whereas with a=3 multiple of 3d is required which can not be generated using shifting of operand d and it needs to be split into (d and 2d) which requires an extra adder in the critical path.

But for case a = 3 from equation providing condition on number of bits of divisor

$$2^{-\delta} \le \frac{2\rho - 1}{2(a - \rho)} = \frac{2(1 - 1)}{2(3 - 1)} = \frac{1}{4}$$

(3.3.1)

Number of bits of the divisor required are 2 as compared to the case with a= 2 where bits of divisor required are 3.

$$2^{-\delta} \le \frac{2\rho - 1}{2(a - \rho)} = \frac{2(2/3) - 1}{2(2 - 1)} = \frac{1}{8}$$

(3.3.2)

Again similar to containment and continuity conditions derived for radix2, bounds on partial reminder in order to select correct quotient digit set are as follows

$$U_{2} = \frac{8}{3.d} \qquad L_{2} = \frac{4}{3.d}$$

$$U_{1} = \frac{5}{3.d} \qquad L_{1} = \frac{1}{3.d}$$

$$U_{0} = \frac{2}{3.d} \qquad L_{0} = \frac{-2}{3.d}$$

$$U_{-1} = \frac{-1}{3.d} \qquad L_{-1} = \frac{-5}{3.d}$$

$$U_{-2} = \frac{-4}{3.d} \qquad L_{-2} = \frac{-8}{3.d}$$

As shifted partial remainder can reach maximum value of 8/3, it requires 2 bits of integer, 1 bit of sign and 4 bits of fractions, In addition to this 3 bits divisor are required to identify correct quotient digit. Table5 shows how value of quotient chosen based on partial reminder and bits of divisor. Table is derived from Roberson's diagram for the continuity relationship [5]

| $[d_i, d_{i+1})^a$               | [8,9)    | [9, 10)  | [10,11)  | [11,12)  |

|----------------------------------|----------|----------|----------|----------|

| $L_2(d_{i+1}), U_1(d_i)^b$       | 36, 40   | 40,45    | 44,50    | 48,55    |

| $m_2(i)$                         | 3/4      | 7/8      | 1        | 1        |

| $L_1(d_{i+1}), U_0(d_i)^b$       | 9, 16    | 10, 18   | 11,20    | 12, 22   |

| $m_1(i)$                         | 1/4      | 1/4      | 1/4      | 1/4      |

| $L_0(d_{i+1}), U_{-1}(d_i)^b$    | -16, -9  | -18, -10 | -20, -11 | -22, -12 |

| $m_0(i)$                         | -1/4     | -1/4     | -1/2     | -1/2     |

| $L_{-1}(d_{i+1}), U_{-2}(d_i)^b$ | -40, -36 | -45, -40 | -50, -44 | -55, -48 |

| $m_{-1}(i)$                      | -3/4     | -7/8     | -1       | -1       |

| $[d_i, d_{i+1})^a$               | [12,13)  | [13, 14) | [14,15)  | [15,16)  |

| $L_2(d_{i+1}), U_1(d_i)^b$       | 52, 60   | 56, 65   | 60, 70   | 48,55    |

| $m_2(i)$                         | 5/4      | 5/4      | 1        | 1        |

| $L_1(d_{i+1}), U_0(d_i)^b$       | 13, 24   | 14, 26   | 15, 28   | 16, 30   |

| $m_1(i)$                         | 1/2      | 1/2      | 1/2      | 1/2      |

| $L_0(d_{i+1}), U_{-1}(d_i)^b$    | -24, -13 | -26, -14 | -28, -15 | -30, -16 |

| $m_0(i)$                         | -1/2     | -1/2     | -1/2     | -1/2     |

| $L_{-1}(d_{i+1}), U_{-2}(d_i)^b$ | -60, -52 | -65, -56 | -70, -60 | -75, -64 |

| $m_{-1}(i)$                      | -5/4     | -5/4     | -5/4     | -3/2     |

Table 5 - Selection Intervals and mk constants [4]

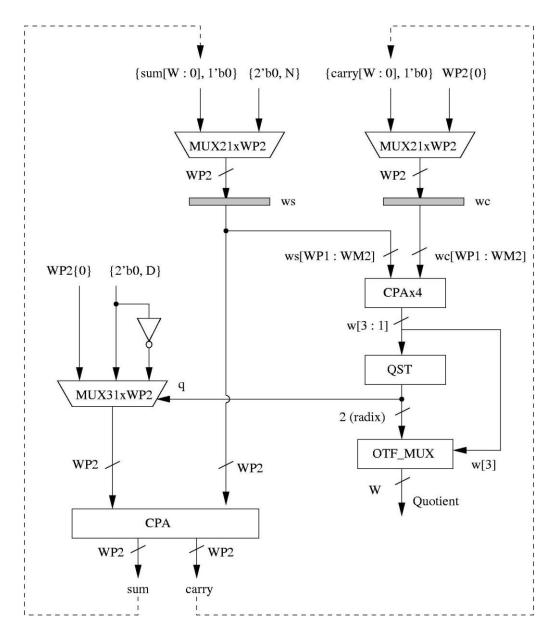

Figure 6 - Hardware block diagram for QST

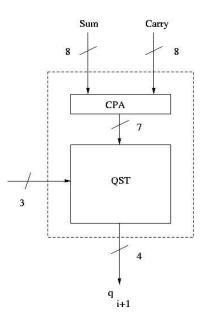

Steps involved in Radix4 SRT divide are as follows

- a. On reset operand x is loaded. 3 bits are added to it at the start which serves as sign and two integer bits. It acts as first partial remainder w[0]

- b. Partial reminder is shifted by 4 (left shift by 2) every iteration & producing 2 bits of the quotient according to recurrence formula.

- c. First 7 bits of partial reminder and 3 bits of divisor identifies correct quotient which is recoded into 4 bits as q2+, q+, q2- and q- as shown in table6.

- d. Selected quotient chooses appropriate value of d from {2d, d, 0, -d, -2d}

- e. When -d or -2d is selected multiplexer chooses inverted version of d & additional 1 required to produce its 2's compliment is added as carry input to the CPA adder.

- f. Redundant quotient bit is sent to OTF (On-The-Fly) converter.

- g. When algorithm requires input operands to be of size greater than double precision, delay due to carry propagate adder becomes the critical path, CPA can be replaced by carry save format adder

| Quotient | $q^{2+}$ | $q^+$ | q | q <sup>2-</sup> |

|----------|----------|-------|---|-----------------|

| -2       | 0        | 0     | 0 | 1               |

| -1       | 0        | 0     | 1 | 0               |

| 0        | 0        | 0     | 0 | 0               |

| 1        | 0        | 1     | 0 | 0               |

| 2        | 1        | 0     | 0 | 0               |

| Table 6 – Quotient | bit encoding | g for Radix4 |

|--------------------|--------------|--------------|

|--------------------|--------------|--------------|

Detailed RTL implementation of Radix4 divide is attached in appendix A. We observed that as we jump from Radix2 to Radix4 complexity of the Quotient Selection Table increase as no of inputs bits to increases from 3 to 10. As calculation of quotient from QST is in critical path of the circuit, which in turn decides the frequency at which divider unit can work. Hardware implementation of Radix4 divide is shown in Figure 7.

Figure 7 - Radix4 hardware block diagram

#### 3.4 Radix16 division using operand scaling

From the analysis of Radix2 & Radix4 division algorithm it is apparent that the quotient digit selection is more costly to implement as we make jump from Radix2 to Radix4. We have seen that even Radix4 decreases number of clock cycles by half as compared to Radix2, this advantage gets nullified by the fact that quotient selection table becomes more complex resulting in increase in cycle time, this trend continues as we move to higher radix division, which can be proved from substituting the value of redundancy factor and quotient digit set in the equation from section 3.2 & 3.3, for e.g. Raix8 number of bits of partial reminder and divisor required are 9 and 5 bits respectively.

We need way of speeding up the algorithm; one of the ways of speeding up the algorithm is to use prediction of quotient digit. This allows simultaneous calculation of quotient as well as residual, but problem associated with this technique is that this prediction requires even more complex quotient selection table, making this approach impractical to use unless the method is simplified.

One way of simplifying this approach is to reduce the complexity of quotient selection table is by restricting the range of divisor. Since the overlap is largest close to d = 1, it is convenient to restrict the range of divisor close to 1. Moreover in order to preserve the precision of quotient both operands need to prescale [6].

It is possible to apply the scaling techniques to Radix2 as well as Radix4 division. However, reduction in execution time is more noticeable if the radix is increased to a value where using conventional method of quotient selection table incurs heavy penalty. This work shows the Radix16 division algorithm using scaling techniques. The basic requirements of the algorithm are a simple scaling technique to make quotient digit selection function independent of divisor and using small number of bits from partial reminder. Since there are many conflicting parameters involved in the scaling, quotient digit selection functions are discrete some trial and error is necessary to achieve trade-offs.

Steps involved in the scaling algorithms for radix 16 are as follows

a. Quotient digit set taken into consideration is from {-10, -9, ...., 9,10} it is decomposed into two components as qh = { -8, -4, -, 4, 8} and ql= {-2, -1, 0, 1, 2} respectively. Redundancy factor *P* for this algorithm is calculated as

$$\rho = \frac{a}{r-1} = \frac{10}{15} = \frac{2}{3} \tag{3.4.1}$$

Thus, the value of  $\rho$  is within bounds of [1/2, 1]. Number of bits of divisor required could be calculated from the 3.2.1 as  $\delta = 6$  so for scaling all divisors are shifted to a range, which is above value of 1 from [6/6, 7/6].

b. The scaling should be obtained by two pass through adder as recursive algorithm requires 2 redundant adders to add ql and qh components. The scaling factor can consists of up to four multiples of unscaled divisor d of the form 2<sup>-i</sup>.d. More specifically we want to transform the unscaled divisor into scaled divisor such that

$$Z = M.d$$

and  $1 - \alpha \le |Z| \le 1 - \beta$

$M = 1 + b.2^{-6}$  with b integer,  $0 \le b \le 64$

c. Since the range of divider is now small, selection function is independent of divisor.

$$q_{j+1} = SEL(\hat{y})$$

for  $1 - \alpha \le Z \le 1 - \beta$

where,  $\hat{y}$  is the redundant partial remainder

Consequently,

$$m_{k} \geq \mathbf{m} \quad \mathbf{a} L_{k}(\mathbf{1}(-\alpha) \ L_{k}(\mathbf{1}-\beta))$$

$$(3.4.2)^{m_{k}+2^{-t}} \leq \mathbf{m} \quad U_{k}\mathbf{n}_{l}(\mathbf{1}-\alpha) \ U_{k-1}(\mathbf{1}-\beta)$$

$$(3.4.3)$$

Table7 is used to find out the value of M by which operand needs to be multiplied to get scaled operand. Maximum value that M can have is 127/64 where as 64/64 is the least value M can have in order to scale the divisor.

| Bits of divisor<br>.1(d-2d-3d-4d-5d-6d-7) | Value of M | Lookup table | Multiplication by MUX     |  |

|-------------------------------------------|------------|--------------|---------------------------|--|

| As divider is in range 0.5                |            |              |                           |  |

| to 1                                      |            |              |                           |  |

| 000000                                    | 127/64     | 1.98438      | (64/64+32/64+16/64+8/64)D |  |

| 000001                                    | 125/64     |              | (64/64+32/64+16/64+8/64)D |  |

| 000010                                    | 123/64     |              | (64/64+32/64+16/64+8/64)D |  |

| 000011                                    | 121/64     |              | (64/64+32/64+16/64+8/64)D |  |

| 000100                                    | 120/64     |              | (64/64+32/64+16/64+8/64)D |  |

| 000101                                    | 118/64     |              | (64/64+32/64+16/64+8/64)D |  |

| 000110                                    | 116/64     |              | (64/64+32/64+16/64+4/64)D |  |

| 000111                                    | 115/64     |              | (64/64+32/64+16/64+2/64)D |  |

| 001000                                    | 113/64     |              | (64/64+32/64+16/64+1/64)D |  |

| 001001                                    | 112/64     |              | (64/64+32/64+16/64+0/64)D |  |

| 001010                                    | 110/64     |              | (64/64+32/64+16/64+0/64)D |  |

| 001011                                    | 109/64     |              | (64/64+32/64+8/64+4/64)D  |  |

| 001100                                    | 107/64     |              | (64/64+32/64+8/64+4/64)D  |  |

| 001101                                    | 106/64     |              | (64/64+32/64+8/64+2/64)D  |  |

| 001110                                    | 104/64     |              | (64/64+32/64+8/64+0/64)D  |  |

| 001111                                    | 103/64     |              | (64/64+32/64+8/64+0/64)D  |  |

| 010000                                    | 102/64     |              | (64/64+32/64+4/64+2/64)D  |  |

| 010001                                    | 101/64     |              | (64/64+32/64+4/64+1/64)D  |  |

| 010010                                    | 99/64      |              | (64/64+32/64+2/64+1/64)D  |  |

| 010011                                    | 98/64      |              | (64/64+32/64+2/64+0/64)D  |  |

| 010100                                    | 97/64      |              | (64/64+32/64+0/64+1/64)D  |  |

| 010101                                    | 96/64      |              | (64/64+32/64+0/64+0/64)D  |  |

| 010110                                    | 95/64      |              | (64/64+32/64+0/64+0/64)D  |  |

| 010111                                    | 94/64      |              | (64/64+32/64+0/64+0/64)D  |  |

| 011000                                    | 93/64      |              | (64/64+16/64+8/64+4/64)D  |  |

| 011001                                    | 92/64      |              | (64/64+16/64+8/64+4/64)D  |  |

| 011010                                    | 91/64      |              | (64/64+16/64+8/64+4/64)D  |  |

| 011011                                    | 90/64      |              | (64/64+16/64+8/64+2/64)D  |  |

| 011100                                    | 90/64 | (CA)(CA + 1C)(CA + 0)(CA + 1)(CA) |  |  |  |  |

|-------------------------------------------|-------|-----------------------------------|--|--|--|--|

| 011100                                    | 89/64 | (64/64+16/64+8/64+1/64)D          |  |  |  |  |

| 011101                                    | 88/64 | (64/64+16/64+8/64+0/64)D          |  |  |  |  |

| 011110                                    | 87/64 | (64/64+16/64+8/64+0/64)D          |  |  |  |  |

| 011111                                    | 86/64 | (64/64+16/64+4/64+2/64)D          |  |  |  |  |

| 100000                                    | 85/64 | (64/64+16/64+4/64+1/64)D          |  |  |  |  |

| 100001                                    | 84/64 | (64/64+16/64+4/64+0/64)D          |  |  |  |  |

| 100010                                    | 83/64 | (64/64+16/64+2/64+1/64)D          |  |  |  |  |

| 100011                                    | 82/64 | (64/64+16/64+2/64+0/64)D          |  |  |  |  |

| 100100                                    | 82/64 | (64/64+16/64+2/64+0/64)D          |  |  |  |  |

| 100101                                    | 81/64 | (64/64+16/64+1/64+0/64)D          |  |  |  |  |

| 100110                                    | 80/64 | (64/64+16/64+0/64+0/64)D          |  |  |  |  |

| 100111                                    | 79/64 | (64/64+16/64+0/64+0/64)D          |  |  |  |  |

| 101000                                    | 78/64 | (64/64+32/64+4/64+2/64)D          |  |  |  |  |

| 101001                                    | 78/64 | (64/64+8/64+4/64+2/64)D           |  |  |  |  |

| 101010                                    | 77/64 | (64/64+8/64+4/64+1/64)D           |  |  |  |  |

| 101011                                    | 76/64 | (64/64+8/64+4/64+0/64)D           |  |  |  |  |

| 101100                                    | 76/64 | (64/64+8/64+4/64+0/64)D           |  |  |  |  |

| 101101                                    | 75/64 | (64/64+8/64+2/64+1/64)D           |  |  |  |  |

| 101110                                    | 74/64 | (64/64+8/64+2/64+0/64)D           |  |  |  |  |

| 101111                                    | 74/64 | (64/64+8/64+2/64+0/64)D           |  |  |  |  |

| 110000                                    | 73/64 | (64/64+8/64+1/64+0/64)D           |  |  |  |  |

| 110001                                    | 72/64 | (64/64+8/64+0/64+0/64)D           |  |  |  |  |

| 110010                                    | 72/64 | (64/64+4/64+0/64+0/64)D           |  |  |  |  |

| 110011                                    | 71/64 | (64/64+4/64+2/64+1/64)D           |  |  |  |  |

| 110100                                    | 70/64 | (64/64+4/64+2/64+0/64)D           |  |  |  |  |

| 110101                                    | 70/64 | (64/64+4/64+2/64+0/64)D           |  |  |  |  |

| 110110                                    | 69/64 | (64/64+4/64+1/64+0/64)D           |  |  |  |  |

| 110111                                    | 69/64 | (64/64+4/64+1/64+0/64)D           |  |  |  |  |

| 111000                                    | 68/64 | (64/64+4/64+0/64+0/64)D           |  |  |  |  |

| 111001                                    | 67/64 | (64/64+2/64+1/64+0/64)D           |  |  |  |  |

| 111010                                    | 67/64 | (64/64+2/64+1/64+0/64)D           |  |  |  |  |

| 111011                                    | 66/64 | (64/64+2/64+0/64+0/64)D           |  |  |  |  |

| 111100                                    | 66/64 | (64/64+2/64+0/64+0/64)D           |  |  |  |  |

| 111101                                    | 65/64 | (64/64+1/64+0/64+0/64)D           |  |  |  |  |

| 111110                                    | 65/64 | (64/64+1/64+0/64+0/64)D           |  |  |  |  |

| 111111                                    | 64/64 | (64/64+0/64+0/64+0/64)D           |  |  |  |  |

| Table 7 - Selection multiples for scaling |       |                                   |  |  |  |  |

| <b>Fable 7 -</b> Selee | ction mu | ltiples : | for | scaling |

|------------------------|----------|-----------|-----|---------|

|------------------------|----------|-----------|-----|---------|

Steps involved in radix 16 SRT divide are as follows

- a. On reset operand x is loaded in. 5 bits are added to it at the start which serves as sign and four integer bit.

- b. Multiple of d and x are created which are shifted versions of operands

| $q_{total}$ | $q_{\rm h}$ | $q_1$ | U <sub>k-</sub><br>1(8288/8192) | L <sub>k</sub> (8288/8192) | m <sub>k</sub> |

|-------------|-------------|-------|---------------------------------|----------------------------|----------------|

| 10          | 8           | 2     | 9.566                           | 9.44                       | 9.5            |

| 9           | 8           | 1     | 8.57                            | 8.43                       | 8.5            |

| 8           | 8           | 0     | 7.58                            | 7.42                       | 7.5            |

| 7           | 8           | -1    | 6.59                            | 6.40                       | 6.5            |

| 6           | 4           | 2     | 5.60                            | 5.39                       | 5.5            |

| 5           | 4           | 1     | 4.61                            | 4.38                       | 4.5            |

| 4           | 4           | 0     | 3.62                            | 3.37                       | 3.5            |

| 3           | 4           | -1    | 2.63                            | 2.36                       | 2.5            |

| 2           | 4           | -2    | 1.64                            | 1.34                       | 1.5            |

| 1           | 0           | 1     | 0.66                            | 0.33                       | 0.5            |

| 0           | 0           | 0     | -0.33                           | -0.66                      | -0.5           |

| -1          | 0           | -1    | -1.34                           | -1.64                      | -1.5           |

| -2          | 0           | -2    | -2.36                           | -2.63                      | -2.5           |

| -3          | -4          | 1     | -3.37                           | -3.62                      | -3.5           |

| -4          | -4          | 0     | -4.38                           | -4.61                      | -4.5           |

| -5          | -4          | -1    | -5.39                           | -5.60                      | -5.5           |

| -6          | -4          | -2    | -6.40                           | -6.59                      | -6.5           |

| -7          | -8          | 1     | -7.41                           | -7.58                      | -7.5           |

| -8          | -8          | 0     | -8.43                           | -8.57                      | -8.5           |

| -9          | -8          | -1    | -9.44                           | -9.56                      | -9.5           |

Table 8 - Quotient selection table for Radix16

- c. First 6 bits of divisor are used to probe selection table to find appropriate multiples of d which are used to generate scaled divisor Z=M.d

- d. Then multiples of x are chosen to generate scaled dividend M.x which serves as the initial partial reminder  $w_{[0]}$ , at the same time Z is assimilated into standard form using carry propagate adder.

- e. According to the quotient selection table (Table8) shown above maximum bounds on partial remainder to get correct quotients are  $9.5 < y^2 < -9.5$  so sign bit, 4 integer bits and 1 fractional bit are sent to qst to chose correct values of  $q_1$  and  $q_h$

- f. Selected ql and qh chooses appropriate value of scaled divisor Z = M.d from pre-computed multiple of Z { -8, -4, 0, 4, 8} and {-2, -1, 0, 1, 2}

- g. When negative multiple of scaled divisor is selected multiplexer chooses inverted version of d & additional 1 required to produce its 2's compliment is added in *ulp* position of carry save adder.

- h. Redundant quotient bit is sent to OTF (On The Fly) converter.

- i. When algorithm requires input operands to be of size greater than double precision, delay due to carry propagate adder, which assimilates scaled, divisor becomes the critical path, CPA can be replaced by carry save adder which results in increase in number of inputs to the carry save path in recursive path.

Figure 8 - Radix16 hardware block diagram

#### 3.5 Radix 512 division

Previous algorithm showed that operand scaling is useful technique to reduce the complexity of quotient selection table by making selection function independent of bits of the divisor by scaling the operands. Operand scaling techniques multiplies both dividend and divisor by prescaling factor. When we go to radix, which are higher than radix 16 (for e.g.: radix 512) maintaining condition of minimum number of quotient digits in the set to satisfy bounds on redundancy factor requires quotient digit set to be {-255, 256}.

And if we use similar technique to radix 16 we require 8 different multiples of *d*, x and quotient needs to be split into 8 components as compared 2 components in radix 16. Moreover 8 pre-computed multiples of d and x not only increases the redundant hardware, it also makes Carry Save Adder tree in the recursive path to grow big. As a result of which using same technique in radix 512 nullifies the advantage gained by computing 9 bits of quotient every iteration.

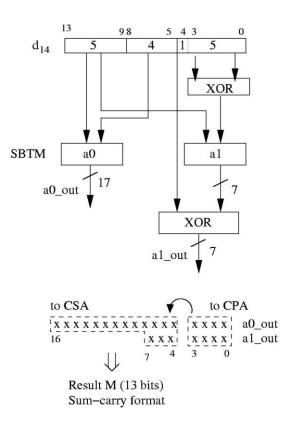

There are several methods to accomplish the pre-scaling function. Some designs actually incorporate linear approximations to the function, so that for all values inside a given interval same scaling factor is used [7]. Although this method is useful, it requires extra iterations to acquire the approximation. Instead of using linear approximations this work uses table lookup that gets the best approximation to the function for given interval. This approximation called the Symmetric Bipartite Table Method (SBTM). Number of bits of divisor for which we need approximation are 14. There are various ways in which number for which approximation is required can be split up. In this setup 16 bits of divisor is split into 3 components as {5,4,5}. First two components form number which acts as in input to table a0 and first 5 and last 5 bits acts as an input to table 2 as shown in fig below.

Figure 9 - SBTM implementation

Generally values generated by SBTM lookup table a0 and a1 needs to be added together however initial pre-scaling value can be stored in carry-save mode, so there is no need to incorporate the carry propagate adder saving clock cycle time.

According to recursive algorithm for SRT 512 division

$$w_{[i+1]} = 512. \ w_{[i]} + q_{[i+1]} * d$$

(3.5.1)

With quotient digit selection:

$$q_{i+1} = \begin{bmatrix} \hat{y} + 1/2 \end{bmatrix}$$

(3.5.2)

Where, w[i] is the residual after iteration i

$$w_{[0]} = M.x$$

$q_{j+1}$  is the quotient digit generated in the iteration  $q_i = \{-511, ..., 0, ..., 511\}$

$y = {rw[j]}_2$  is partial remainder restricted till 2 fractional bits

At the end, q must be rounded according to the sign of the residual of the last iteration. If last residual is positive we have to add 1 in the least significant position after rounding. We do not add anything if it is negative.

To execute the recurrence two multiplications and one addition is required. The partial remainder w[i] and the quotient digit qi+1 both are in carry save presentation to avoid carry propagation adder in critical path. Multiplying a number by  $r = 512 = 2^9$  is equivalent to the shifting of it's binary representation by 9 positions to the left. Shifting the scaled divisor by quotient value can't perform the other multiplication as its not strictly in multiples of 2; so recoding one of the operands is used to perform other multiplication. Recoding the multiplier into radix 4 representation reduce the number of partial products and make the operation faster. The recoded operand is in Signed Digit representation and each digit can assume values {-2, -1, 0, 1, 2}.

In carry save representation of M both MSB's are going to be 0 as we know the value of M is positive, but qs and qc can be positive or negative, since the sign is not known, the only solution is to extend partial reminder y by one bit the carry save representation of  $q_i$ . This also requires appending 3 integer bits at the start.

3.5.1 Recoding

In recursive algorithm concept of recoding is used. This is a standard radix 4 multiplication. Every partial product is 2 positions left shifted with the respect to previous one, because of the radix 4 representations of the digits. Sign extension is required to get correct result.

When a negative digit is encountered, we bit compliment the partial product (before the shift) and we put a 1 in the next product in correspondence of least significant bit of the actual product. If digit is -1 we have

ssssscccccccccccc00

sssxxxxxxxxxxxxxx0100

And if the digit is -2 we have

Putting 1 for negative multiples of operand doesn't change the complexity of the circuits. As shown in the following diagram these bits in the first and second shift extension are simple through M2 and M1.

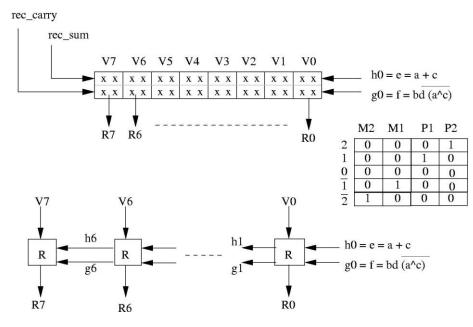

But this method cannot be used if the last partial product is negative; this problem will never occur during scaling as value of M is positive, but during calculation of quotient as well as during high radix multiplier last partial product can be positive or negative. In such case we bit compliment shifted partial product and add 1 in the least significant position As shown in the figure 10 input to the each recoder pair is  $v_i$  is in carry save format, so maximum value of  $v_i$  can be 6, when both sum and carry bit of the input are 11. Input to the each recoder is  $v_i$  is in the range of {0,6}. Recoding of the carry save operands is shown below.

| $v_{i}$ | h <sub>i</sub> =0 |           |                | h <sub>i</sub> =1 |           |                |

|---------|-------------------|-----------|----------------|-------------------|-----------|----------------|

|         | $h_{i+1}$         | $g_{i+1}$ | t <sub>i</sub> | $h_{i+1}$         | $g_{i+1}$ | t <sub>i</sub> |

| 0       | 0                 | 0         | 0              | 0                 | 0         | 0              |

| 1       | 0                 | 0         | 1              | 0                 | 1         | -3             |

| 2       | 1                 | 0         | -2             | 1                 | 0         | -2             |

| 3       | 1                 | 0         | -1             | 1                 | 0         | -1             |

| 4       | 1                 | 0         | 0              | 1                 | 0         | 0              |

| 5       | 1                 | 0         | 1              | 1                 | 1         | -3             |

| 6       | 1                 | 1         | -2             | 1                 | 1         | -2             |

Table 9 - Quotient recoding in Carry-Save format

Final recoded output is  $R_i = t_i + h_i + g_i$

Figure 10 - Block diagram for recoder

## 3.5.2 Adder

Adder employed in Radix512 design can be split into components, first one calculates partial product depending on the output of recoder, and second component adds them. During calculations of scaled divisor and dividend 8 partial products are generated as pp0, pp1, pp2, pp3, pp4, pp5, pp6, pp7. During recursive algorithms as only 6 partial products are generated by quotient qi+1. Upper 2 partial products pp6, pp7 are replaced by shifted partial residual 512.ws[i] and 512.wc[i].

| Cycle         | 1          | 2          | 3          | 4          | 5          |

|---------------|------------|------------|------------|------------|------------|

| Operation     | Prescaling | Prescaling | Recurrence | Recurrence | Recurrence |

| SBTM Register | М          | М          | М          | М          | М          |

| W (Carry/Sum) | M.d = Z    | M.x=W[0]   | W[1]       | W[2]       | W[3]       |

| Ζ             | -          | M.d        | M.d        | M.d        | M.d        |

Table 10 - Division cycle timing chart

Steps involved in divide512 algorithm are as follows

a. In cycle 1 that is termed as Prescaling, SBTM Register sends pre-scaling factor M in carry save format to one of the multiplexors, which in turn sends those value to the recoder.

Operand selector multiplexor chooses operand d, recoder outputs chooses correct multiple of operand (d in this cycle), which are added in CSA tree to form M.d n carry save format.

- b. In cycle 2 that is also termed as Prescaling, SBTM Register sends prescaling factor M in carry save format to one of the multiplexers, which in turn sends those values to the recoder. Operand selector multiplexer chooses operand *x*, recoder outputs chooses correct multiple of operand (*x* in this cycle) which are added in CSA tree to form M.*x* in carry save format which is the initial partial reminder w[0], and in same cycle M.*d* is assimilated using carry propagate adder.

- c. From cycle 3 onwards which is termed as Recurrence operation quotient qi+1 is sent to the recoder and operand selected is Z scaled divisor

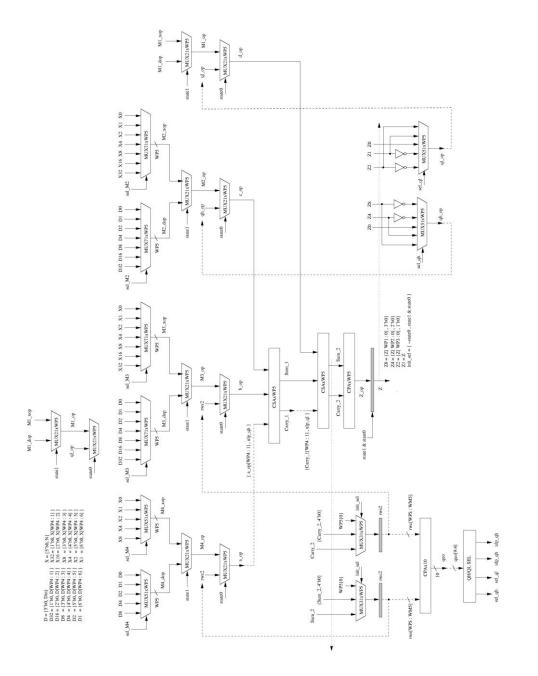

Figure 11 - Radix512 hardware block diagram

Quotient produced by recurrence algorithm is in Signed Digit representation, which is converted into standard representation using on the fly converter block.

d. While implementing radix 512 division for quad precision or some other industry floating point formats with large range if carry propagate adder involved in cycle 2 which assimilates scaled divisor M.d becomes critical path of the circuit, scaled operand can be stored in carry save format. (Modification are shown in figure 12)

Figure 12 - Radix512 hardware block diagram using Carry-Save format

e. In such case where prescaled divisor is stored in carry save format, number of partial products getting added in Carry Save Adder tree gets doubled as each partial product will be have its sum and carry version.

#### 3.6 Recursive divide/multiplier unit

This section describes modifications in the radix 512-division algorithm to accommodate high radix multiplier. This unit reduces its overall area and power footprint by utilizing a low area sequential architecture, but still maintains high amounts of computation power by employing high radix and redundant digit encoding for each digit.

Multipliers have been key and critical components for most application specific and general-purpose computer architectures. However, these architectures have been transitioning towards multiple cores that process large amount of data through parallel approaches to computation. Unfortunately, traditional arithmetic functional units that worked well for dingle core architectures have the side effect of incurring large amounts of area and power. Consequently, multi-core architecture needs new ways of thinking about increased throughput to handle large amounts of data. This section presents modification in the recursive high radix divide unit that is modified to handle both multiplication and division targeted at multi-core architectures.

Multiplication involves the use of addition in some way to produce product p=x.y from a multiplicand x and multiplier y. Multipliers and even division have been workhorse of scientific computing [8]. High-speed multipliers are typically classified into two categories. The first known as parallel multiplication, involves the use of hardware to multiply an m bit number by an n bit number to completely produce an n+m product. On the other hand, serial or sequential multipliers compute the product sequentially usually utilizing storage elements so that hardware of the multiplier is reused during an iterative process.

Although multipliers are important for processing scientific data; they tend to consume a significant amount of area and delay within computer architectures. Today's architectures require significant amount of area to integrate multiple cores on a chip to satisfy Moore's Law.

For example, the Niagara 2 architecture has significant resources allocated for supporting multiple threading [9]. Subsequently Sun Microsystems utilized architecture to reduce area in order to allow the integrating of floating point and graphics unit. Decisions such as these will continue to dominate as the number of threads and cores increase and multi-core architecture becomes more prevalent. Consequently, designers must design new computational blocks that still maintain the same level of algorithmic complexity, but also have smaller area and power footprints.

Multipliers are an integral part in scientific computing, however they consume a large amount of resources. To reduce the size of the computation, it is common to have architectures that are designed to serially instead of parallel. Serial multipliers are typically computed by repetitively adding partial products to form the final product as follows:

$$p[j+1] = (p[j] + x[j].y).r^{-1}$$

(3.6.1)

where p is the product, y is the multiplicand x is the multiplier r is the radix.

Although serial multiplication units are fairly simple to build in digital hardware, they tend to be significantly slower than the larger parallel multiplier architectures. More complex architectures, such as Goldschmidt and Newton Raphson algorithms, allow faster and more efficient multiplication and division algorithms to occupy the same functional unit. Although these quadratically converging algorithms are efficient, they have the disadvantage of using a significant amount of area, mainly for the parallel multiplier. In addition, traditional parallel multipliers also consumes large amount of power with their spurious switching activity [9].

Although serial multiplication units are fairly simple to build in digital hardware, they tend to be significantly slower than larger parallel multiplier architectures. More complex architectures, such as Goldschmidt and Newton Raphson algorithms, allow faster and more efficient multiplication and division algorithms to occupy the same functional unit. Although these quadratically converging algorithms are efficient, they have the disadvantage of using a significant amount of area, mainly for the parallel multiplier. In addition, traditional parallel multipliers also consumes large amount of power with their spurious switching activity [9].

Long standing argument that diminishing feature sizes justify larger area for more functionality is starting to lack any substance in today's multicore environment. This is because many multi-core architecture needs additional blocks for other on chip and off chip communications. Therefore, multi-core architectures require substantial area for the use of local and off-chip routers and reducing the size of key and critical functional units such as multipliers and dividers, is paramount to promoting multi-core paradigms. On the other hand, the reduction in size of these arithmetic circuits should be tempered with not decreasing the efficiency of the unit too dramatically.

One potential improvement for serial architectures is to compensate for the low algorithmic complexity of serial recursive multipliers by using higher radix and Signed Digit encoding. The advantage to this approach is that a designer can obtain lower power functional units while still maintaining high throughput. Recursive division algorithms have long had success in promoting high amounts of computing power by using a higher radix as shown by the following equation

$$w_{[i+1]} = r. \ w_{[i]} - d. \ q_{i+1} \tag{3.6.2}$$

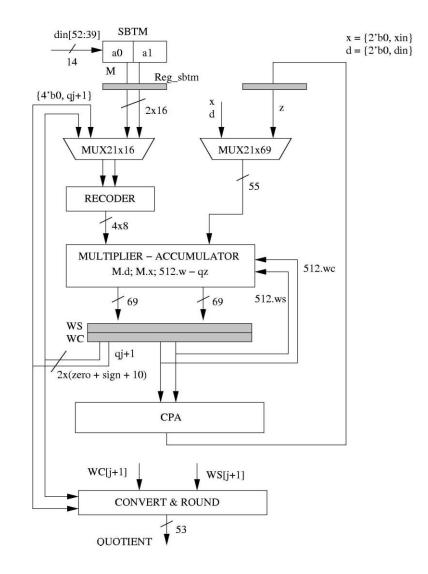

Figure 13 - Radix512 hardware block diagram for integrated Mult-Div Unit

The division architecture can easily be expanded into one that computes both division and multiplication by adding an extra data flow such that the prescaling operation is concatenated for a selection of multiplier. This is, since only a limited number of bits are utilized with lookup table for the scaled divisor, it can easily be modified to handle the lower elements of product, given the dividend is changed to the multiplicand [10]. For the r=512 unit paper, 16 bit is assumed for the approximation within the SBTM unit, half of the product or 32 bits is produced after 1 cycle, That is the following operation is computed:

$M_{plier}$  16 bits .  $M_{cand}$  32 bits = Partial Product 48 bits

A subsequent iteration can then incorporate into the datapath so that upper 16 bits of the product or the complete 64 bits of the product is produced. Since the multiplication algorithm is based closely on the radix 512-division algorithm, it is conceivable to easily modify the architecture to handle both multiplication as well as division within one unit. The major difference is for 32 bit multiplication requires 3 cycles, whereas, division requires 5 cycles. Moreover since multiplication has to shift multiplier by 16 bits, whereas, division shifts each partial reminder by 9 bits. Figure13 displays the combined architecture for 32-bit division and multiplication.

| Cycle         | 1             | 2             | 3             |

|---------------|---------------|---------------|---------------|

| Operation     | Iteration     | Iteration     | Iteration     |

| SBTM Register | М             | М             | М             |

| W (Carry/Sum) | Mcand.MplierL | Mcand.MplierH | -             |

| Ζ             | -             | -             | Mcand.MplierH |

| Prod_mult_L   |               | Mcand.MplierL | Mcand.MplierL |

| Carry         | -             | С             | С             |

Table 11 - Multiplication cycle timing chart

## CHAPTER IV

#### RESULTS

In order to quantify the architectures within the paper, the implementations were analyzed using the IBM cmos10lpe 65nm CMOS technology[11]. The standard cell library from Virage is utilized for the synthesis and place and route of the all architecture discuss in this work. All designs are coded in RTL Verilog and synthesized and place and routed using Synopsys tool chain. The power dissipation is calculated by running 1,000 different test vectors for each design.

All radix dividers are compared against each other to get accurate estimate of power as well as area and speedup comparison. To compare the recursive divide/multiplication structure versus traditional multipliers, a 32-bit carry-save array and Dadda multiplier are designed and analyzed. Parallel multipliers are chosen for this comparison, because they are typically employed within multiplicative-dive architectures and consequently can give a good comparison to the proposed architecture within the paper.

# 4.1 Design Flow:

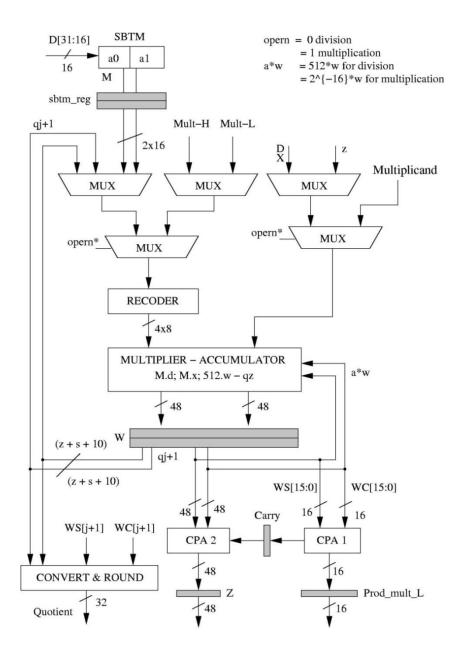

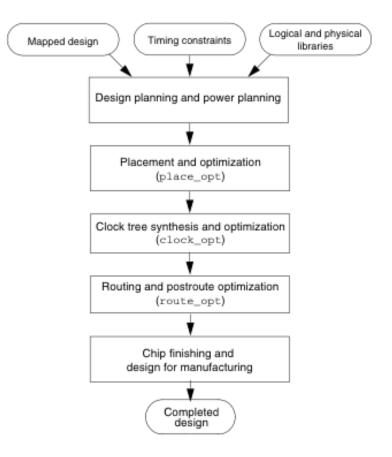

Flowchart in figure14 shows steps involved in the design and implementation of architecture mentioned in this work [12]

Figure 14 - Design Flow

## 4.1.1 Design Specifications