# ARCHITECTURAL VERIFICATION OF FOUR-INSTRUCTION SUPERSCALAR PROCESSOR FOR MIPS I INSTRUCTION SET

By

### ANSHUMAN ANAND

Bachelor of Engineering

Nagpur University

INDIA

1999

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE December 2003

# ARCHITECTURAL VERIFICATION OF FOUR-INSTRUCTION SUPERSCALAR PROCESSOR FOR MIPS I INSTRUCTION SET

Thesis Approved:

Thesis Advisor

Dean of the Graduate College

#### ACKNOWLEDGEMENTS

Although it has just been just two and a half years studying in Oklahoma State University, it is an experience that will stay with me forever. My stay in Stillwater has given me a lot to cherish, good friendships, an excellent studying environment to name a few.

First of all I would like to thank my parents, Sushma Anand and Arun Kumar Anand. They have inspired me throughout my life and have taught me never to give up. I would also like to thank my aunt and uncle, Malika Chaudhary and Ravi Chaudhary, for helping me realize my long-standing dream of studying in an esteemed university. I would also like to thank my brother, Ayush Anand for his help and support.

I consider myself fortunate enough to have made a lot of good friends. I would like to thank all of then for the help and support they extended towards me. I would especially like to thank Ritesh, Srinivasan and Nitin for making my stay in Stillwater an experience of home away from home.

I was fortunate enough to work under Fritz Writ at the Daily O'Collegian. I would like to thank him for believing in me and providing me with financial support.

I wish to extend my sincere appreciation to my adviser Dr. Louis G. Johnson for his able guidance, intelligent supervision and inspiration that helped me finish this thesis. My sincere appreciation also extends to my committee members Dr. Yumin Zhang and Dr. Weili Zhang whose assistance and encouragement are also invaluable.

Finally, I would like to thank the Department of Electrical and Computer Engineering for supporting me during these two and a half years of study.

### TABLE OF CONTENTS

| Chapter                                     | Page                                        |

|---------------------------------------------|---------------------------------------------|

| 1. Introduction                             | n and Thesis organization1                  |

| 1.1 Bac<br>1.1.0<br>1.1.1<br>1.1.2<br>1.1.3 | sis Introduction                            |

| 2. Architectur                              | ral Overview                                |

|                                             | oduction                                    |

| 2.1 Ove                                     | rall design & dataflow13                    |

| 2.1.0                                       | Architectural Features                      |

| 2.1.1                                       | Handling Branch and Jump Instructions       |

| 2.1.2                                       | Handling Speculated Data 19                 |

| 2.1.3                                       | Handling out of order execution             |

| 2.1.4                                       | Handling dynamic scheduling of instructions |

| 2.1.5                                       | Handling Multiply and Divide Instruction    |

| 2.1.6                                       | Handling Memory Stores                      |

| 2.1.7                                       | Handling Data Consistency                   |

| 2.2 Pip                                     | eline Stages                                |

| 2.2.0                                       | Introduction                                |

| 2.2.1                                       | Instruction Fetch Stage                     |

| 2.2.2                                       | Instruction Decode/Issue Stage              |

| 2.2.3                                       | Instruction Dispatch                        |

| 2.2.4                                       | Instruction Execution                       |

| 2.2.5                                       | Instruction Write Back                      |

| 2.2.6                                       | Instruction Commit I                        |

| 2.2.7                                       | Instruction Commit II                       |

| 3. Design of I                              | Branch Prediction Mechanism                 |

|                                             | oduction                                    |

|                                             | nch Target Buffer                           |

| 3.2 Bra                                     | nch Prediction Buffer                       |

### Chapter

| 4. Instruction Set Architecture Decoder & Prioritizer |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 40 |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.0                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 40 |

| 4.1                                                   | Instruction set architecture decoder design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 43 |

| 4.2                                                   | Prioritizer design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 46 |

| 5. Regist                                             | er file design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 50 |

| 5.0                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 50 |

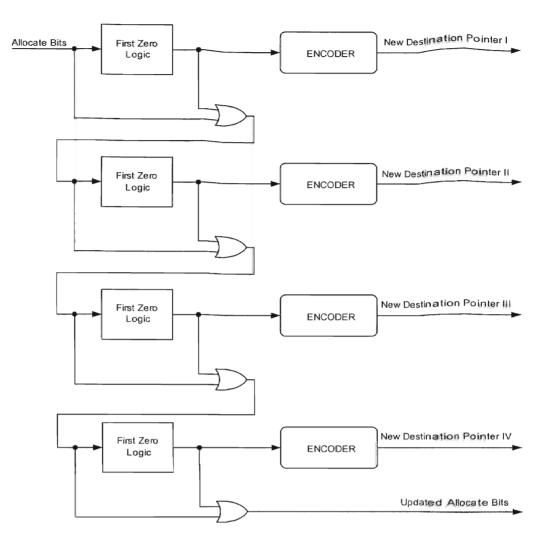

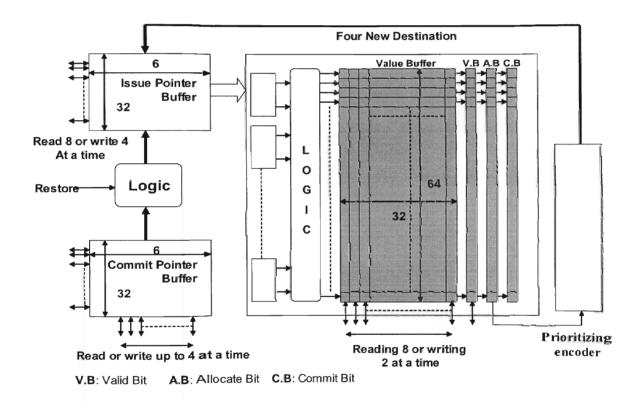

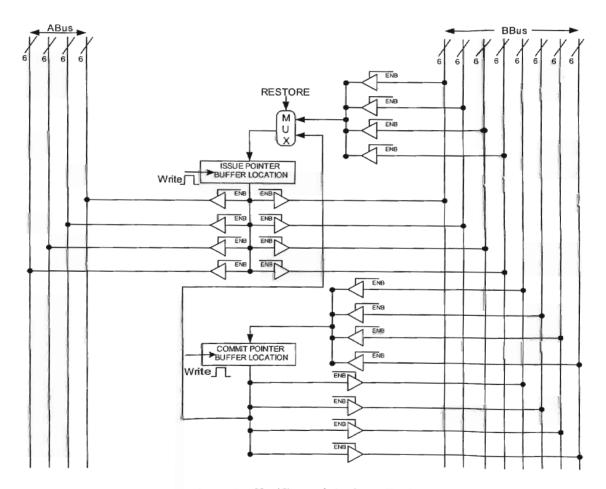

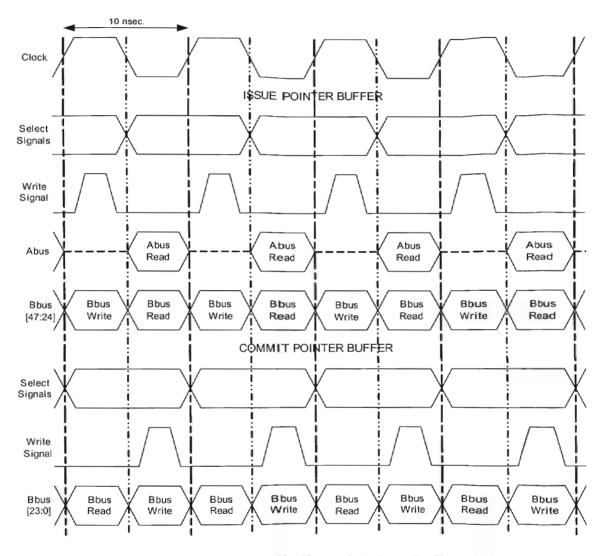

| 5.1                                                   | Issue pointer buffer/Commit pointer buffer design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 52 |

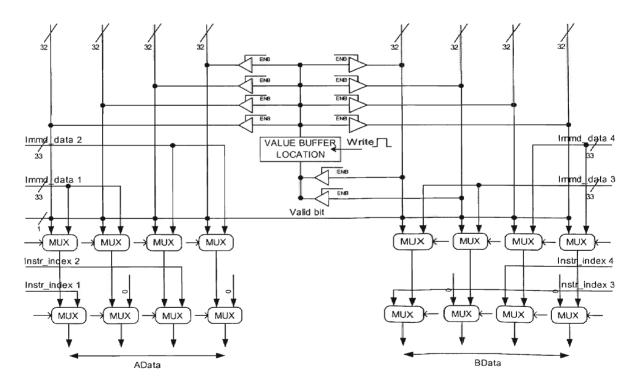

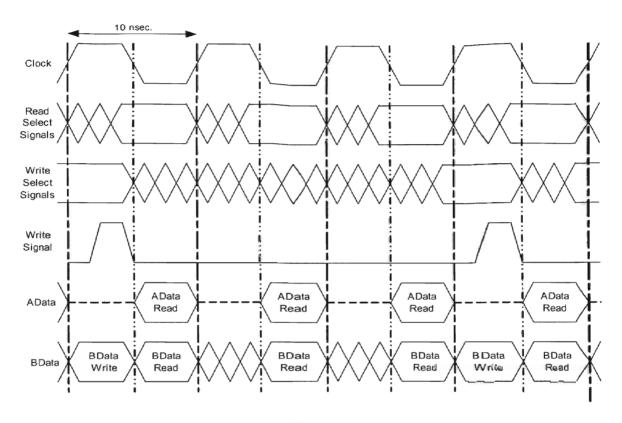

| 5.2                                                   | Value Buffer Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 56 |

| 6. Maint                                              | aining Data Consistency & Instruction Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 59 |

| 6.0                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 59 |

| 6.1                                                   | Source Overwrite Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

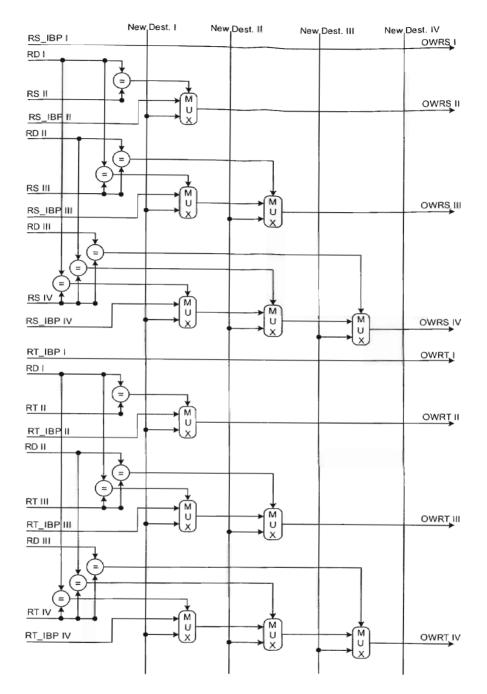

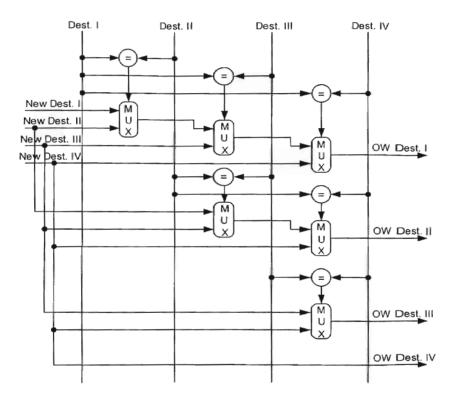

| 6.2                                                   | Destination Overwrite Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 63 |

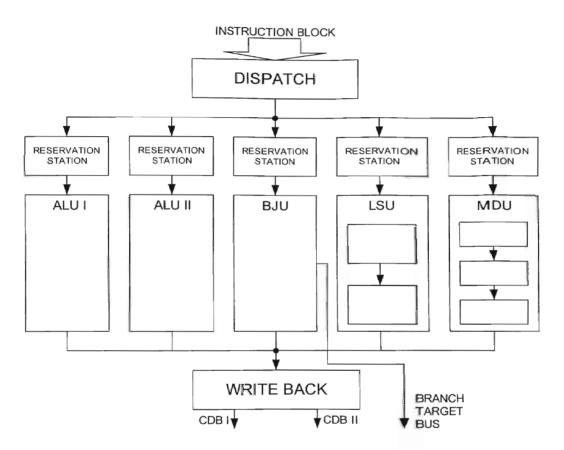

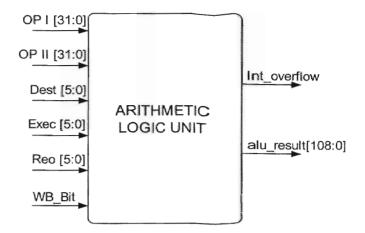

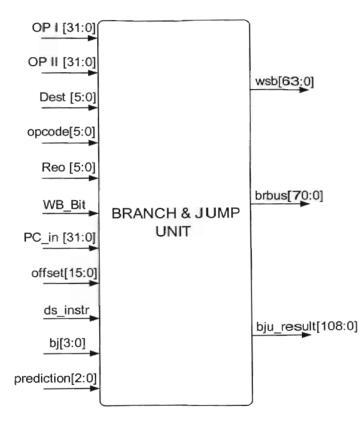

| 6.3                                                   | Instruction Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 65 |

| 7. Desig                                              | n Verification Methodology & Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 71 |

| 7.0                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 71   |

| 7.1                                                   | Memory Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72   |

| 7.3                                                   | Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| 7.4                                                   | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 77   |

| 7.4                                                   | 0 Instruction per cycle (IPC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 77   |

| 7.4                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| 7.4                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| 7.4                                                   | 1 Determinant of the second s |      |

| 8. Concl                                              | usion & Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 81   |

| 8.0                                                   | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 81   |

| 8.1                                                   | Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 83   |

| Referen                                               | ces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 85   |

### LIST OF TABLES

| Table                                        | Page |

|----------------------------------------------|------|

| 4.1: Functional Unit Codes for the Processor |      |

| 7.1: Simulation Results                      |      |

### LIST OF FIGURES

| Figure                                                         | Page |

|----------------------------------------------------------------|------|

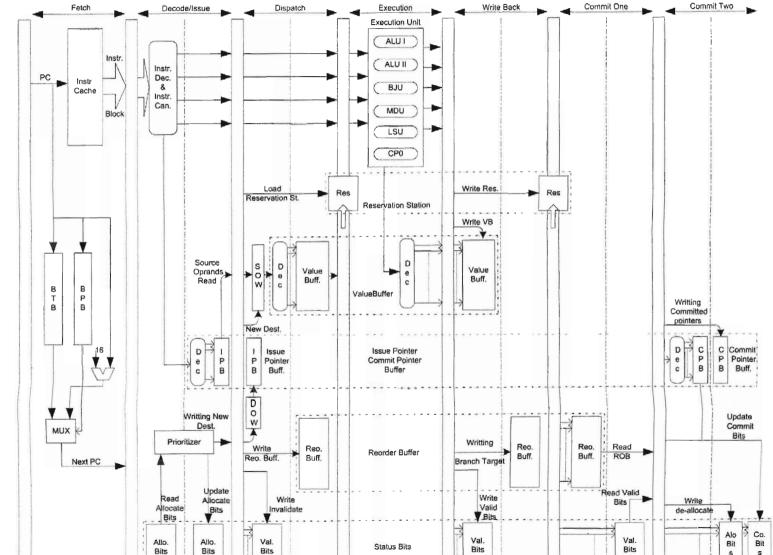

| 2.1: Overall Architecture.                                     |      |

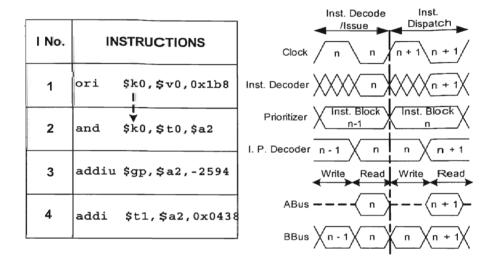

| 2.2: Sample code                                               |      |

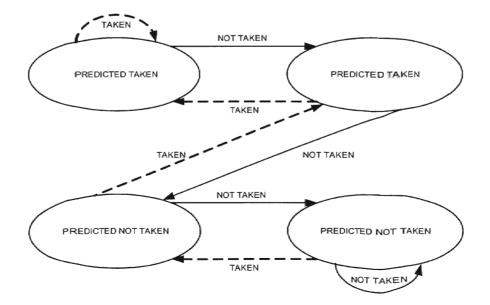

| 3.1: States in a two-bit prediction scheme.                    |      |

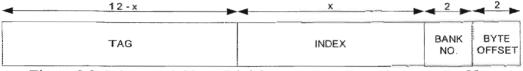

| 3.2: Memory Address Division to access Branch Target Buffer    |      |

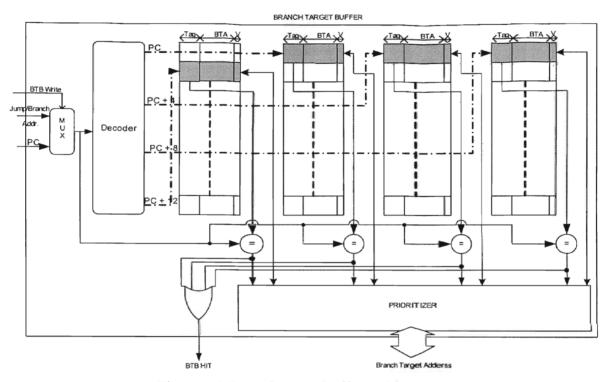

| 3.3 Branch target buffer architecture                          |      |

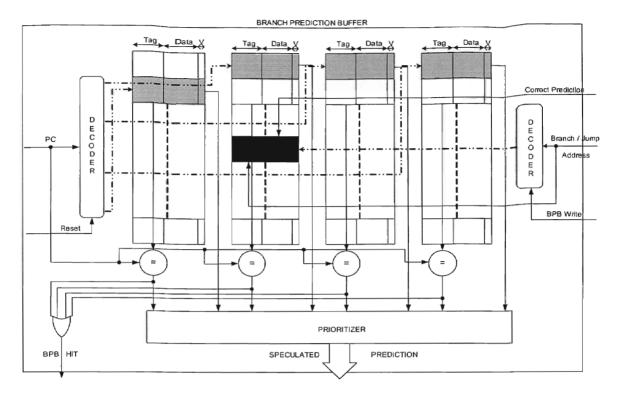

| 3.4: Branch prediction buffer architecture                     |      |

| 4.1: I-Type instruction format                                 |      |

| 4.2: J-Type instruction format                                 |      |

| 4.3: R-Type instruction format.                                |      |

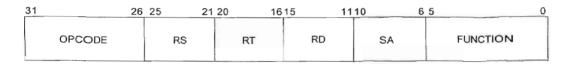

| 4.4: Instruction Set Architecture Decoder.                     |      |

| 4.5: Decoder output format for instructions                    | 43   |

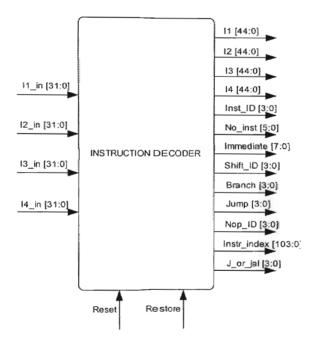

| 4.6: Prioritizer.                                              |      |

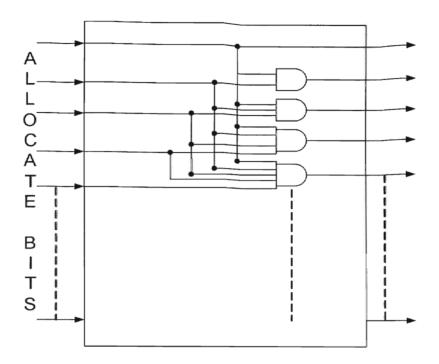

| 4.7: First zero logic                                          |      |

| 5.1: Block Diagram of the Register-file                        |      |

| 5.2: Issue Pointer Buffer/Commit Pointer Buffer Implementation |      |

| 5.3: Issue Pointer Buffer/Commit Pointer Buffer Timing         |      |

| 5.4: Value Buffer Implementation                               |      |

| 5.5: Value Buffer timing                                       |      |

| 6.1: Sample Source code and Issue Pointer Buffer timing.       | 60   |

| 6.2: Source overwrite logic Implementation.                    |      |

| 6.3: Sample Source code and Issue Pointer Buffer timing.       | 63   |

| 6.4: Destination overwrite logic Implementation.               | 64   |

| 6.5: Functional units block diagram                            |      |

| 6.6: Block diagram of Arithmetic and logic unit.               | 67   |

| 6.7: ALU result encoding                                       | 67   |

| 6.8: Block diagram of Branch and jump unit                     | 68   |

| 6.9: Branch bus encoding                                       |      |

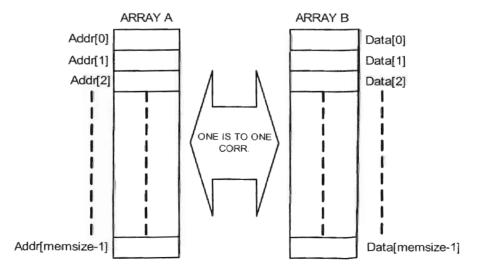

| 7.1: Address-Data memory array pair                            |      |

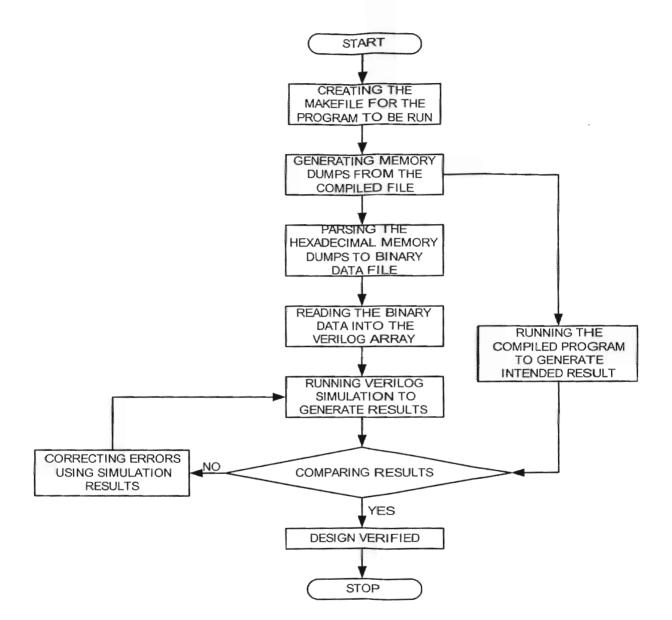

| 7.2: Flowchart of design verification methodology              |      |

| 7.3: Stack Memory dump before simulation                       |      |

| 7.4: Stack Memory dump after simulation                        | 76   |

## **Chapter 1**

# Introduction and Thesis organization

### 1.0 Thesis Introduction

Computer applications continue to require higher and higher processing speed. This has led researchers and designers to come up with new ideas to enhance the speed of the processors. A common approach is to exploit Instruction Level Parallelism inherent in the codes. Instruction level parallelism can be defined as the potential overlap of the instructions, so that they can be executed in parallel. Identifying instruction level parallelism contributes to increasing the number of execution units in the processor that operate concurrently to enhance the performance of the processor. Multi-linear processors have more than one execution or functional unit to evaluate parallel instructions. Two common RISC (Reduced instruction set computer)-type multi-linear processor alternatives are the Super-scalar architecture and Very Large Instruction Word (VLIW) architecture. The difference between these two architectures stems from the way they utilize instruction level parallelism. VLIW processors require static scheduling of parallel instructions that can be fetched as one instruction word. Alternatively, superscalar processors do dynamic scheduling of instruction as they are fetched from a linear instruction sequence. Static scheduling of the instructions is done at compile time. On the other hand, dynamic scheduling is done at run time when a particular sequence of instructions is being executed. The compiler plays a critical roll in optimizing the

1

performance of a multi-linear processor since the compiler has to identify instructions that could be evaluated in parallel.

A typical multi-linear processor fetches and decodes several instructions at a time. To ensure a steady stream of instructions, control instructions are predicted at fetch time. Decoded instructions are evaluated for data dependencies, dynamically scheduled and issued to the execution units for evaluation. Each execution unit can have a different latency causing the instructions to finish execution out of program order. Latency can be defined as the number of clock cycles between issuing an instruction to a particular pipeline and completion of execution of that instruction. At the end of execution, the results are reordered to update the machine state in program order.

Since on an average there is a branch or a jump instruction every five instructions [1], accurate branch prediction plays a critical roll in improving the efficiency of the processor, since the control flow of the program after a branch instruction is predicted, the instruction fetched after a predicted branch is referred to as a *speculated instruction* until the branch is evaluated in the pipeline. These instructions should not be allowed to alter the machine state until the branch conditions are evaluated. Hence for this intermediate period, results produced by the speculated instruction must be stored in registers other than the architectural registers to avoid alteration of the machine state. Once the branch is evaluated and the branch action matches the predicted action i.e. *taken* or *not taken*, these results should be allowed to write into the architectural registers to alter the machine state in accordance with the program. It is seen from the above

2

discussion that for a speculated instruction, two 32-bit data transfers are required to complete it. This is highly inefficient and takes up a lot of silicon area.

The study undertaken in this thesis tries to tackle this inefficiency by having extra register locations other than the architectural registers called pseudo-registers, and a pointer scheme is followed to reference both architectural and pseudo registers. This scheme renames each logical destination register of an incoming instruction, to a pseudo register referenced by pointers called pseudo-pointers. Two separate lists of these pointers are maintained, one for all types of instructions and the other for only unspeculated instructions. When a branch instruction preceding the speculated instruction is evaluated and it is established that the prediction was correct, the machine state is altered by updating the pointer lists instead of moving the data. As the pointes are only 6-bits, the inefficiency is considerably reduced.

This processor scheme is implemented using the Verilog hardware description language (HDL). The following study provides architectural details of each component used in the processor, stressing issues involved in the implementation and methods used to overcome these issues. This study also discusses verification methodology, documenting steps involved in compiling a 'C' program and loading it onto the simulated instructions cache and data cache for simulation. Finally, simulation results are presented for a sample 'C' program verifying the design.

### 1.1 Background Study

### 1.1.0 Preliminary Studies

Two important implementation alternatives for multi-linear processors are the VLIW approach and the Superscalar approach. A discussion on the performance comparison of both approaches is presented at length in [9]. It is shown in the paper that both the approaches have comparable performance for selected benchmarks. It is further shown that a relatively small instruction window is required for a superscalar processor as compared to a VLIW processor to exploit the same amount of parallelism. The overall micro-architecture of a superscalar processor is well elaborated in [10]. This paper discusses the concept of instruction level parallelism. It also discusses the technique involved in the implementation of the basic phases of a superscalar processor including instruction fetch and conditional branch processing, identifying data dependencies, issuing instructions for execution, memory interaction and committing the processor state in the correct order. A prototype implementation of a superscalar processor with a fetch size of two following the million instructions per second (MIPS) instruction set is presented in [11]. This paper brings out different design issues involved in a superscalar processor including a detailed study of the data-path, multi-ported register file, data and control hazards. These papers give an overall understanding of the micro-architecture and the issues involved in the design of a superscalar architecture without going into details.

### 1.1.1 Understanding branches & branch prediction alternatives

An efficient branch prediction mechanism is gaining more and more importance because processors are getting wider and wider and the functional units are getting deeper and deeper [2]. Reference [2] talks about different types of branches and their behavior patterns, which is important to understand. According to [2], branches can be conditional or unconditional. Conditional branches are further divided into immediate branch, indirect branch and return [2]. The branch target address is encoded in the instruction for an immediate branch, whereas indirect branch reads the branch target address from a register and return gets its target address from the stack memory. It further points out that for the SPECint95 benchmark, 72% of branches are conditional, 17% are unconditional. 10% are return and 1% are indirect. Reference [2] further shows the distribution of execution frequencies of static conditional branches. On an average 53% of all the branches were executed 99 times or fewer and 11% of all the branches were executed 10,000 times or more. It also points out that 53% of the branches that were executed 99 times or fewer make up 0.2% of the branches in the dynamic instruction stream while 11% of the branches that were executed 10,000 times or more make up 87% of the branches in the dynamic instruction stream. This proves that 10% of the code is responsible for 90% of the execution [2]. This proves that a good branch prediction scheme is an imperative for a highly efficient processor. Different schemes employed for predicting branches are as follows:

- 1. Two-bit branch predictor [7].

- 2. GAg branch predictor [1].

- 3. gshare branch predictor [1].

- 4. LGshare branch predictor [1].

- 5. Block-level prediction scheme [8] [3].

- 6. Hybrid prediction scheme.

The two-bit branch predictor is the most simple prediction scheme. This scheme employs a two-bit saturating counter for each predicted branch and the most significant bit is the prediction of branches. The counter is updated at the time of commit. If the prediction was correct, the counter is incremented or else decremented. This prediction scheme is capable of ignoring a single divergent branch.

The *GAg*, *gshare* and *LGshare* branch predictor is a two-level adaptive branch prediction scheme [2]. GAg branch prediction maintains two levels of branch history. The first level is maintained in a buffer called the global history register (GHR) which stores the history of all most recently executed branches. The second level of history, called the pattern history, stores the information about the most likely branch outcome if a particular pattern matches in the GHR. *Gshare* branch prediction indexes the pattern history by doing a logical XOR of the global history and branch address. This scheme is more accurate than the GA share scheme as the branch interference is reduced due to the XORed branch address [1]. The LGshare scheme instead of using a global history of the branches uses the hybrid history by concatenating global history to the local history of a particular branch. This local history is stored in the branch target buffer. This hybrid history is XORed with the branch address to index the pattern history table. For a wider superscalar processor with an instruction block size of eight or more, the probability of having more than one branch in the fetch group is high [8]. Hence multiple branch prediction is required to ensure a continuous flow of instructions. Instead of predicting individual instructions the block prediction scheme predicts the outcome of the entire block. In this scheme two pattern tables are maintained, the first is the block history table (BHT) which stores the outcome of the recently executed branches and is indexed using the block address. The second level is the pattern history which consists of counters for each possible target of the block and is incremented and decremented depending on the prediction. Reference [3] claims 15% increase in the fetch size for an 8-wide superscalar processor and improvement of 25% for a 12-wide superscalar processor.

According to [5], a higher hardware budget for the branch history tables tends to yield a more accurate branch predictor. Recent studies have shown that feature size reduction and a shorter clock cycle will lead to multi-cycle accesses to large on-chip structures. Hence, the access delay of large branch history tables will reduce the instruction per cycle (IPC) count. For a gshare prediction scheme with a pattern history size of 2 KB implemented for a clock rate of 2 GHz, memory accesses time is doubled causing the IPC to drop by 40% [5]. A Hybrid prediction scheme is proposed by [5] to counter this effect. A Hybrid predictor is similar to the two-level adaptive predictor but has smaller branch history tables.

The implementation in this thesis uses the most simple prediction scheme of twobit prediction. This scheme was preferred over others because it is less complex than the two-level prediction scheme. The block prediction scheme and hybrid prediction scheme was not considered as the fetch size of the processor implemented is four; hence the probability of having more that one branch in a fetch group is small.

#### 1.1.2 Branch target buffer indexing

To avoid a pipeline stall the branch prediction mechanism has to predict the branch target address no later than the first pipeline stage, since the branch address is not known prior to instruction decode. Hence some indirect technique is required to index the branch target buffer. Reference [13] highlights this problem and identifies the scheme used in the Intel Pentium processor for a fetch size of two. The Intel Pentium processor indexes the branch target buffer with the address of the instruction in the first decode stage. If there is a hit in the branch target buffer, the branch instruction is predicted without incurring any penalties. Hence, in this case a branch instruction is identified by the address of the instruction fetched one cycle before the branch instruction. This paper argues that the fetch width of a future generation superscalar processor will be much greater that two. To identify a branch instruction, instruction in the decode stage (whose address is used to index the branch prediction information) should always be the same. This is difficult to achieve for a larger fetch size. Reference [13] proposes two indexing schemes for indexing branch target buffers:

- 1. Basic block based indexing

- 2. Fetch address based indexing.

According to this paper, the time at which a branch instruction is predicted depends on which address is used to identify it. In order to predict a branch sufficiently early a branch instruction should be identified by the address of an instruction that

8

dominates the branch [13]. The dominant instruction is the one that is executed prior to a branch whenever the branch is executed. The basic block indexing scheme identifies the branch with the basic block address, whereas the fetch address based scheme identifies the branch with the instruction cache line address. There may be more than one branch instruction in a cache line. In this case, to avoid all the branch instructions in the same cache line mapping to the same branch target buffer entry, all the other branches are identified by their corresponding basic block starting address. These schemes assume delayed branches are not used.

The branch target buffer indexing scheme used in our processor is similar to the basic block indexing scheme. The branch target buffer in our cases fetches four consecutive locations starting from the basic block address. If there is a hit, branch target address corresponding to the first hit is used.

### 1.1.3 Register file issues

Superscalar processors exploit instruction level parallelism by dynamically scheduling instructions for out-of-order execution. These processors evaluate a large window of in flight instructions to find multiple ready and independent instructions for parallel execution every clock cycle. Supporting a larger instruction window requires larger components within the processor like the register file, reorder buffer etc. Typically, a register file of a superscalar processor is required to be multi-ported to handle more than one instruction every cycle. These large multi-ported register files can potentially compromise clock cycle time. Reference [12] identifies these problems and proposes two schemes to handle them.

The first scheme handles the problem of increased register file size by a twolevel register file, where the number of registers in the critical data path is reduced. The other scheme handles the multi-porting problems by using a minimally ported banked register file.

The two-level register file uses an allocation policy that leaves values that have potential readers in the level one register file and transfer other values to the level two register file. A special hardware component, named *Usage table* [12], keeps track of the potential readers of each register in the level one register file. *Usage table* [12] consists of a counter, called *Pending Consumers* [2], which is incremented during rename if an instruction sources that particular register value. The same instruction decrements the counter when it is dispatched. If a counter for a particular register reads zero, it is copied to the level two register file. Information of this transfer is maintained in a buffer called the *Copy List* [2] to restore the machine state after misprediction.

Even though the port requirement on a register file for a processor of fetch size of eight is at least 24 ports, the average port requirement is fewer for several reasons:

- 1. Many operands are read from the forwarding network and not from the register file.

- 2. Many instructions have single register operands.

3. Many instructions are not register write instructions.

An IPC degradation of 2% was observed if the ports on the register file above were restricted to four read and four write ports [12]. This three fold reduction in the ports complicates the issue logic and the restricted write bandwidth must be handled with an added complexity in the commit logic. Hence, [12] suggests a minimally-ported banked register file. The register file bank with a single read port incurs an IPC degradation of 1% because of read conflicts [12]. If the write ports are also restricted to one per bank, IPC degradation increases to 5% [12].

The register file designed for our processor is designed based on s pointer scheme, where pointers to the data are transferred from the reorder buffer to the commit pointer buffer which keeps data at one location during commit.

Background studies put forward in the above discussion helped us make design decisions for a lot of components of the processor design under test.

### **1.2 Thesis Organization**

This documentation is divided into eight chapters. Chapter 2 talks about the overall design of the processor, identifying different components used to realize the design. Chapter 3 talks about the design of the branch prediction mechanism. Chapter 4 describes the design of the MIPS I Instruction set architecture decoder and priorotizer logic for renaming. Chapter 5 presents the design of the register file explaining the

concept of pseudo-registers. Chapter 6 identifies the data inconsistency problem and presents a solution employed in this design. Chapter 7 presents design verification methodology and simulation results. Chapter 8 concludes the discussion by proposing future work beyond this study.

## **Chapter 2**

# **Architectural Overview**

### 2.0 Introduction

The design under verification here is a four-instruction speculative super-scalar processor, which can fetch four instructions from a liner instruction sequence every clock cycle and dynamically schedule them. Speculative prediction of the outcome of branch or jump instruction is done to reduce control stalls in the processor. This chapter talks about the overall design of the processor, how different components interact with each other, overall data flow and different pipeline stages of the processor.

### 2.1 Overall design & dataflow

#### 2.1.0 Architectural Features

The processor design is based on the MIPS Instruction Set Architecture; this instruction set architecture is one of the industry standard architectures. The MIPS instruction set comes in four different versions MIPS I, II, III & IV. This processor is an implementation of the MIPS I Instruction Set Architecture. Basic instruction types in the MIPS I instruction set are:

Arithmetic & logic instructions for basic arithmetic operation such as addition, subtraction and logical operations like AND, OR etc.,

- 2. Branch & Jump instructions, they can be conditional or unconditional. These instructions decide the control flow of the program.

- Multiply & Divide instructions are special instruction for multiplication and division operations, as these instructions take longer than the other instructions they are grouped into one type.

- 4. Load & Store instructions, these instructions perform data transfers from and to the data memory.

- 5. Floating-point instructions, these instructions operate on floating-point numbers.

- Co-Processor 0 Instruction, co-processor is the control functional unit described by the MIPS Instruction Set. The co-processor 0 handles interrupt's, configuration options and controls on-chip functions like the cache and timer. A set of instructions described in the MIPS instruction set interacts with the co-processor 0.

- BREAK and SYSCALL instructions fall in a special category called miscellaneous instructions.

The SDE-MIPS compiler is used to generate memory dumps of the 'C' programs. This compiler does not handle interrupts on its own; hence interrupt handling capabilities are not build in this processor design. As the processor does not handle interrupts the coprocessor 0 is designed as a static element that always has logical '0' at the output. It is further assumed that the compiler does not produce floating-point instructions. This assumption is true as a flag in the compiler make file restricts the compiler from generating these instructions. Hence, the processor does not need capability to execute floating-point instructions. As the main focus of the study is on the processor architecture and not on the design of the peripherals it is also assumed that the instruction and data cache is infinite.

There are six functional units in the processor to execute up to six instructions in parallel. They are:

- 1. Two Arithmetic Logic Units (ALU).

- 2. One Branch and Jump Unit (BJU).

- 3. One Multiply and Divide Unit (MDU).

- 4. One Load and Store Unit (LSU).

- 5. Co-processor 0 (CP0).

The probability of two out of four instructions in a block to be arithmetic is high as the number of arithmetic instructions is nearly twice that of any other types. Hence having two arithmetic logic units will reduce a lot of structural stalls.

The processor is clocked at 10 nsec. and is divided into seven pipeline stages which are.

- 1. Instruction Fetch.

- 2. Instruction Decode/Issue.

- 3. Instruction Dispatch.

- 4. Instruction Execution.

- 5. Instruction Write Back.

- 6. Instruction Commit I.

#### 7. Instruction Commit II.

Each pipeline stage is of the duration of one clock cycle. The diagram on the next page shows the different pipeline stages divided by pipeline registers. The first pipeline register is the program counter. Each component in the processor is divided in time to show how it interacts with other components in each pipeline stage.