## PARALLEL-PREFIX STRUCTURES FOR BINARY AND MODULO

$\{2^n - 1, 2^n, 2^n + 1\}$  ADDERS

By

## JUN CHEN

Bachelor of Science in Information and Control Engineering Shanghai Jiao Tong University Shanghai, China 2000

Master of Science in Electrical Engineering Illinois Institute of Technology Chicago, IL, U.S.A. 2004

> Submitted to the Faculty of the Graduate College of Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY December, 2008

## PARALLEL-PREFIX STRUCTURES FOR BINARY AND MODULO

$\{2^n - 1, 2^n, 2^n + 1\}$  ADDERS

Dissertation Approved:

Dr. James E. Stine

Dissertation Advisor

Dr. Louis G. Johnson

Dr. Sohum Sohoni

Dr. Hermann G. W. Burchard

Dr. A. Gordon Emslie

Dean of the Graduate College

### ACKNOWLEDGMENTS

First, I would like to thank my advisor, Dr. James E. Stine, for his continuous efforts on helping me with the work through a Ph.D. degree. His enthusiasm in teaching, positive thinking, along with his strong professional strengths, guided me towards the completion of this degree.

My family's support is also greatly appreciated. This work cannot be done without the support from my parents Guangzhao Chen and Shengyuan Chen and sister Yu Chen.

I am very proud of being able to work with Ivan, my fellow at VLSI Computer Architecture Group (VCAG). Thanks also go to Johannes Grad, an alumni of Illinois Institute of Technology, who helped me much on EDA tools.

Finally, I would like to thank all the committee members, Dr. Johnson, Dr. Sohoni, Dr. Burchard and Dr. Stine. Thank you all for everything you have done to help through.

# TABLE OF CONTENTS

| Cł | napter |                                                                             | Pa | age |

|----|--------|-----------------------------------------------------------------------------|----|-----|

| 1  | Intro  | oduction                                                                    |    | 1   |

|    | 1.1    | Motivations                                                                 |    | 1   |

|    | 1.2    | Carry-Propagate Adders                                                      |    | 2   |

|    | 1.3    | Algorithmic Architectures for Parallel-Prefix Binary and Modulo $2^n \pm 1$ |    |     |

|    |        | Adders                                                                      |    | 3   |

|    | 1.4    | Research Contributions                                                      |    | 4   |

|    | 1.5    | Dissertation Organized                                                      |    | 5   |

| 2  | Bina   | ry Adder Schemes                                                            |    | 6   |

|    | 2.1    | Binary Adder Notations and Operations                                       |    | 6   |

|    | 2.2    | Ripple-Carry Adders (RCA)                                                   |    | 9   |

|    | 2.3    | Carry-Select Adders (CSEA)                                                  |    | 10  |

|    | 2.4    | Carry-Increment Adders (CINA)                                               |    | 13  |

|    | 2.5    | Carry-Skip Adders (CSKA)                                                    |    | 15  |

|    | 2.6    | Carry-Lookahead Adders (CLA)                                                |    | 17  |

|    |        | 2.6.1 Algorithmic Analysis                                                  |    | 19  |

|    | 2.7    | Ling Adders                                                                 |    | 20  |

|    | 2.8    | NAND/NOR Adders                                                             |    | 23  |

|    | 2.9    | Parallel-Prefix Structures                                                  |    | 27  |

|    | 2.10   | Carry Save Adders (CSA)                                                     |    | 28  |

|    | 2.11   | Summary                                                                     | •  | 30  |

| 3 | Buil | ding Pr     | efix Structures                                                  | 31 |

|---|------|-------------|------------------------------------------------------------------|----|

|   | 3.1  | Prefix      | Tree Family                                                      | 32 |

|   | 3.2  | Prefix      | Structure Synthesis                                              | 33 |

|   |      | 3.2.1       | Taxonomy                                                         | 33 |

|   |      | 3.2.2       | Synthesis Rules                                                  | 35 |

|   |      | 3.2.3       | Preparing Prefix Tree                                            | 36 |

|   |      | 3.2.4       | Kogge-Stone Prefix Tree                                          | 40 |

|   |      | 3.2.5       | Knowles Prefix Tree                                              | 43 |

|   |      | 3.2.6       | Brent-Kung Prefix Tree                                           | 48 |

|   | 3.3  | Other ]     | Prefix Trees                                                     | 51 |

|   |      | 3.3.1       | Sklansky Prefix Tree                                             | 51 |

|   |      | 3.3.2       | Ladner-Fischer Prefix Tree                                       | 52 |

|   |      | 3.3.3       | Han-Carlson Prefix Tree                                          | 53 |

|   |      | 3.3.4       | Harris Prefix Tree                                               | 54 |

|   |      | 3.3.5       | Algorithmic Analysis for Prefix Trees                            | 55 |

|   | 3.4  | Paralle     | el-Prefix Ling Structures                                        | 56 |

|   | 3.5  | Prefix      | Tree with Carry-Save Notation                                    | 58 |

|   |      | 3.5.1       | Carry-Save Notation                                              | 58 |

|   |      | 3.5.2       | Carry-Save Notation and Application to Prefix Tree               | 60 |

|   |      | 3.5.3       | Adding Binary Carry-Save Numbers                                 | 63 |

|   |      | 3.5.4       | Incorporating Parallel-Prefix Structure with Carry-save Notation | 64 |

|   | 3.6  | Summ        | ary                                                              | 67 |

| 4 | Mod  | ulo $2^n$ - | $\pm 1$ Adders                                                   | 68 |

| • | 4.1  |             | o $2^n - 1$ Adders                                               | 68 |

|   |      | 4.1.1       | Background                                                       |    |

|   |      | 4.1.2       | Full Parallel-Prefix Structure                                   |    |

|   |      | 4.1.3       | Reduced Parallel-Prefix Structure                                |    |

|   |      | 1.1.5       |                                                                  | 15 |

|    |      | 4.1.4     | Parallel-Prefix Ling Structures for Modulo $2^n - 1$ Adders $\ldots$                                | 75  |

|----|------|-----------|-----------------------------------------------------------------------------------------------------|-----|

|    |      | 4.1.5     | Carry-Select Incrementer                                                                            | 78  |

|    |      | 4.1.6     | Summary                                                                                             | 81  |

|    | 4.2  | Modul     | o $2^n + 1$ Adders $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 82  |

|    |      | 4.2.1     | Background                                                                                          | 82  |

|    |      | 4.2.2     | Reduced Parallel-Prefix Structure                                                                   | 83  |

|    |      | 4.2.3     | Parallel-Prefix Ling Structures for Modulo $2^n + 1$ Adders $\ldots$                                | 85  |

|    |      | 4.2.4     | Full Parallel-Prefix Structure                                                                      | 85  |

|    |      | 4.2.5     | Carry-Select Incrementer                                                                            | 91  |

|    | 4.3  | Combi     | nation of Binary and Modulo $2^n \pm 1$ Adder                                                       | 91  |

|    | 4.4  | Summ      | ary                                                                                                 | 94  |

| 5  | Resu | ılts of P | arallel-Prefix Structures and Comparisons                                                           | 95  |

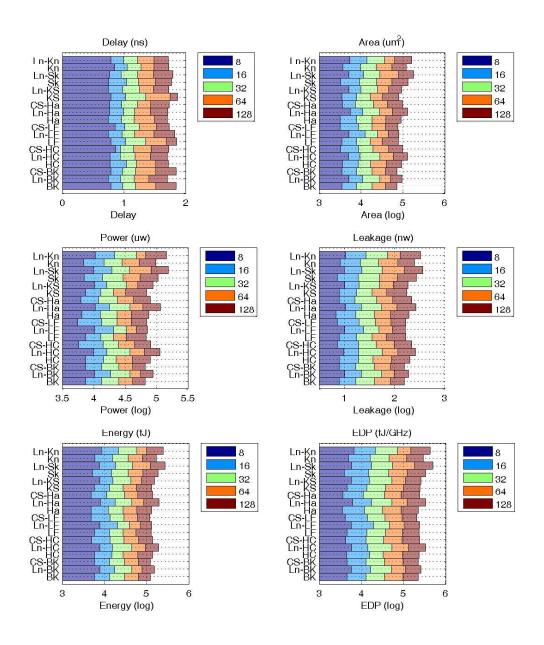

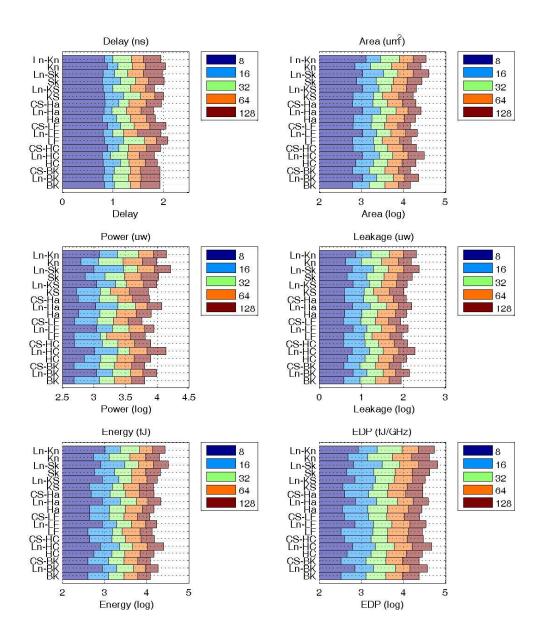

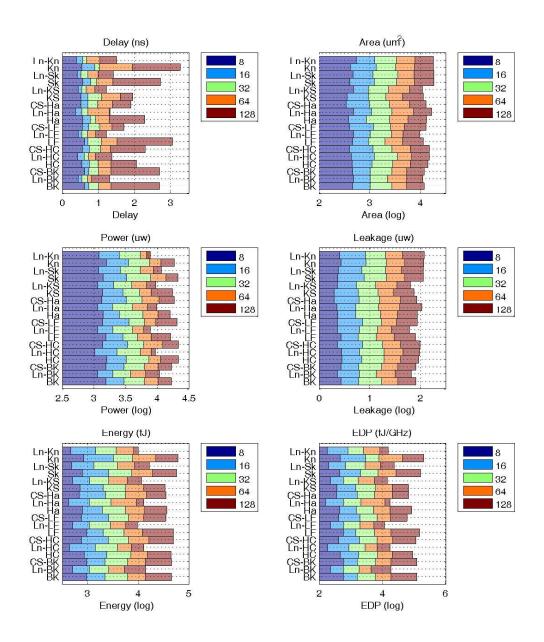

|    | 5.1  | Binary    | Parallel-Prefix Adders                                                                              | 96  |

|    | 5.2  | Modul     | o $2^n - 1$ Adders with Prefix Implementation                                                       | 98  |

|    | 5.3  | Modul     | o $2^n + 1$ Adders with Prefix Implementation                                                       | 102 |

|    | 5.4  | A Con     | nbination of Modulo $2^n \pm 1$ and Binary Adders with Prefix Imple-                                |     |

|    |      | mentat    | ion                                                                                                 | 106 |

|    | 5.5  | Summ      | ary                                                                                                 | 113 |

| 6  | Con  | clusion   |                                                                                                     | 114 |

|    | 6.1  | Disser    | tation Summary                                                                                      | 114 |

|    | 6.2  | Future    | Directions                                                                                          | 116 |

|    | 6.3  | In Sun    | nmary                                                                                               | 118 |

| BI | BLIC | OGRAP     | НҮ                                                                                                  | 119 |

# LIST OF FIGURES

| Figure |                                           | Page |

|--------|-------------------------------------------|------|

| 1.1    | Binary Adder Example.                     | . 2  |

| 2.1    | 1-bit Half Adder.                         | . 7  |

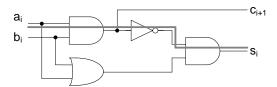

| 2.2    | 1-bit Full Adder.                         | . 8  |

| 2.3    | Ripple-Carry Adder.                       | . 9  |

| 2.4    | Carry-Select Adder.                       | . 11 |

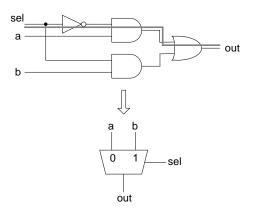

| 2.5    | 2-1 Multiplexor.                          | . 12 |

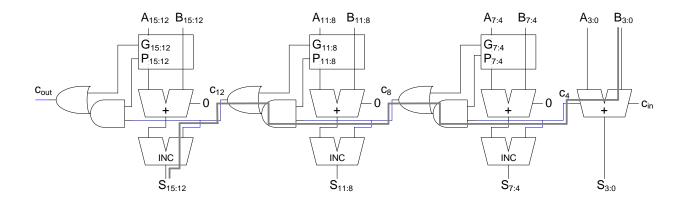

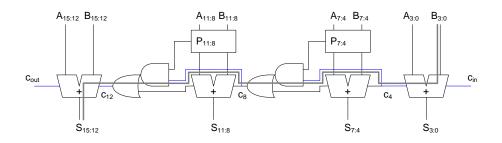

| 2.6    | Carry-Increment Adder.                    | . 15 |

| 2.7    | Carry-Skip Adder.                         | . 16 |

| 2.8    | Reduced Full Adder.                       | . 17 |

| 2.9    | Carry-Lookahead Adder.                    | . 19 |

| 2.10   | NAND Adder Carry Chain.                   | . 23 |

| 2.11   | NOR Adder Carry Chain.                    | . 25 |

| 2.12   | 8-bit Parallel-Prefix Structure           | . 28 |

| 2.13   | Sklansky Parallel-Prefix Examples.        | . 29 |

| 2.14   | 4-bit Carry-Save Adder                    | . 30 |

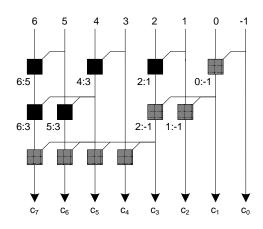

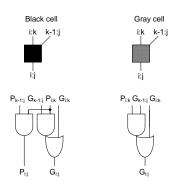

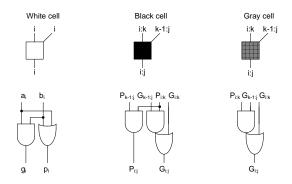

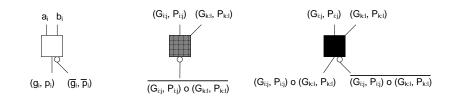

| 3.1    | Cell Definitions.                         | . 32 |

| 3.2    | Valid Prefix Structure Synthesis.         |      |

| 3.3    | Invalid Prefix Structure Synthesis.       |      |

| 3.4    | 8-bit Empty Prefix Tree                   |      |

| 3.5    | Build 8-bit Sklansky Prefix Tree: Step 1. |      |

| 3.6    | Build 8-bit Sklansky Prefix Tree: Step 2. |      |

| 5.0    | Dure of the shunday from from oup 2       |      |

| 3.7  | Build 8-bit Sklansky Prefix Tree: Step 3                                               | 40 |

|------|----------------------------------------------------------------------------------------|----|

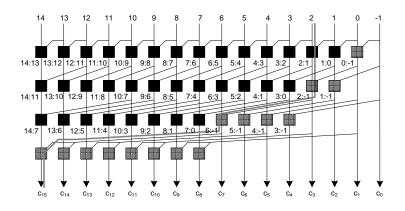

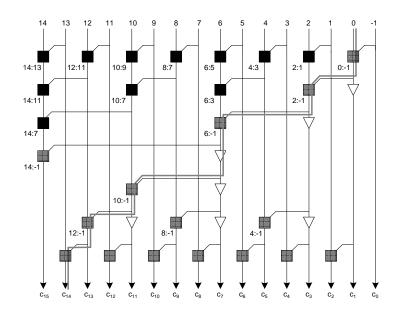

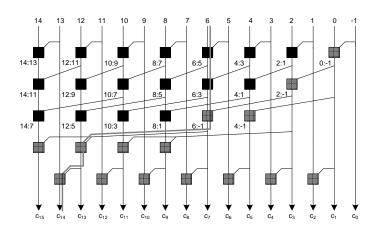

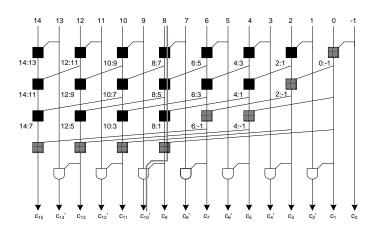

| 3.8  | 16-bit Kogge-Stone Prefix Tree                                                         | 41 |

| 3.9  | 16-bit Kogge-Stone Prefix Tree with Buffers.                                           | 43 |

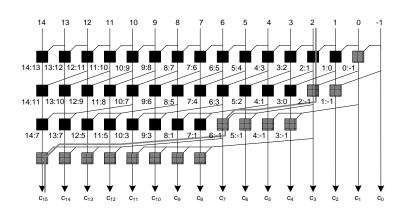

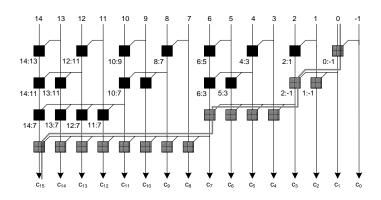

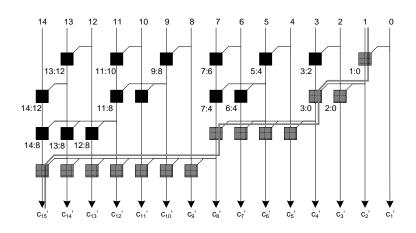

| 3.10 | 16-bit Knowles [2,1,1,1] Prefix Tree                                                   | 44 |

| 3.11 | 16-bit Knowles [4,2,1,1] Prefix Tree                                                   | 44 |

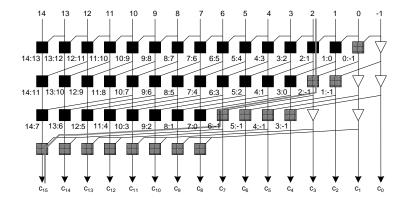

| 3.12 | 16-bit Knowles [2,1,1,1] Prefix Tree with Buffers                                      | 47 |

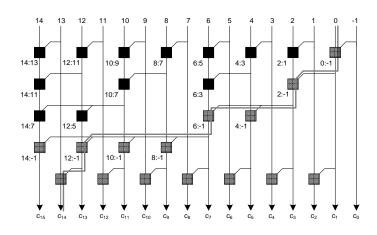

| 3.13 | 16-bit Brent-Kung Prefix Tree                                                          | 49 |

| 3.14 | 16-bit Brent Kung Prefix Tree with Buffers                                             | 50 |

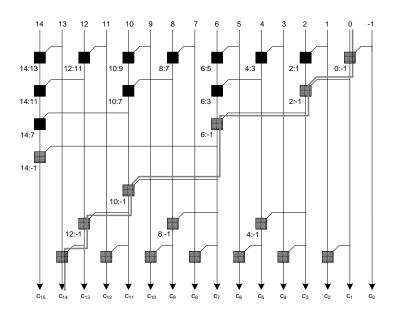

| 3.15 | 16-bit Sklansky Prefix Tree                                                            | 51 |

| 3.16 | 11-bit Ladner-Fischer Prefix Tree Synthesis.                                           | 52 |

| 3.17 | 16-bit Han-Carlson Prefix Tree                                                         | 53 |

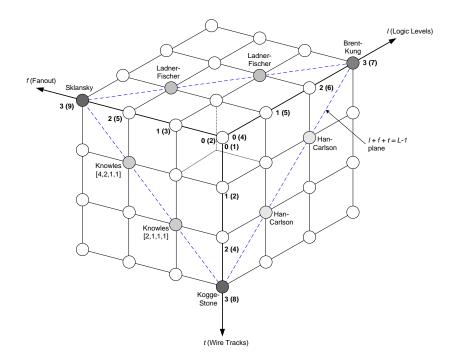

| 3.18 | Taxonomy of 16-bit Prefix Tree (Adapted from [1]).                                     | 54 |

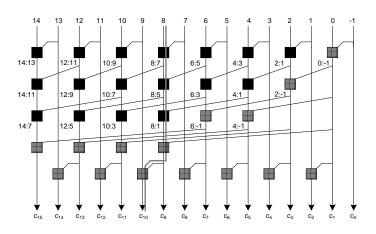

| 3.19 | 16-bit Harris Prefix Tree                                                              | 55 |

| 3.20 | Cell Definition for Ling's Parallel-Prefix Tree                                        | 56 |

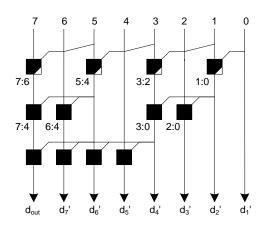

| 3.21 | 8-bit Sklansky Prefix Tree with Ling's Scheme.                                         | 57 |

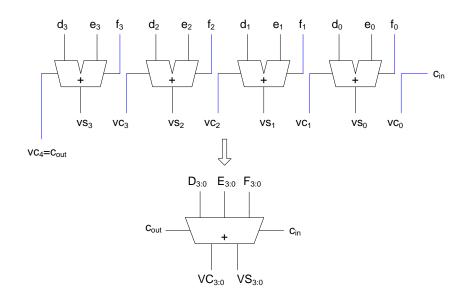

| 3.22 | n-bit Binary Adder with Carry-Save Notation.                                           | 59 |

| 3.23 | 16-bit Sklanksy Prefix Tree with Carry-Save Notation.                                  | 61 |

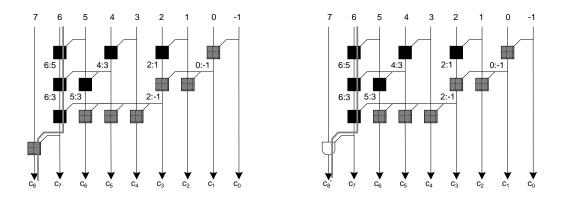

| 3.24 | 8-bit Example of Carry-Save Add                                                        | 63 |

| 3.25 | 9-bit Sklansky Parallel-Prefix Adder Comparison.                                       | 64 |

| 3.26 | 16-bit Han-Carlson Parallel-Prefix Structure with Carry-Save Notation                  | 65 |

| 3.27 | 8-bit Parallel-Prefix Adder with Carry-Save Notation.                                  | 66 |

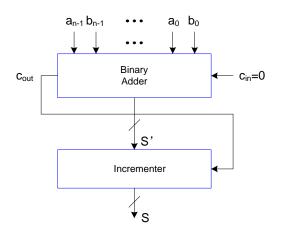

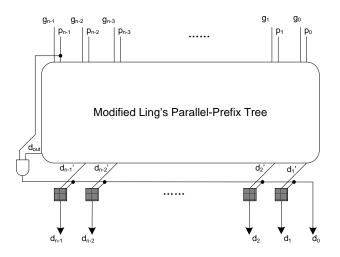

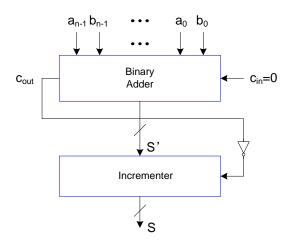

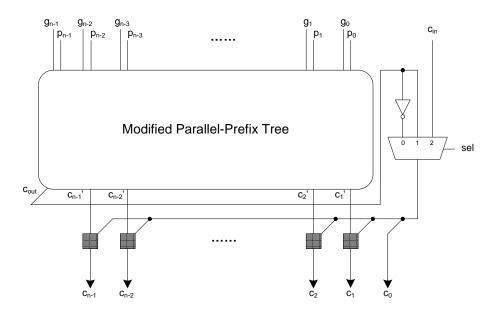

| 4.1  | General Block Diagram Modulo $2^n - 1$ Adder.                                          | 70 |

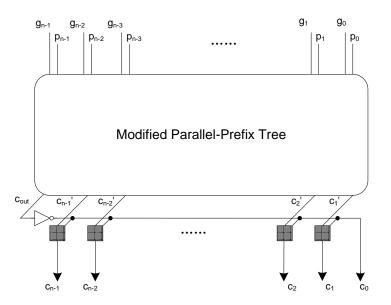

| 4.2  | Cell Definitions.                                                                      | 71 |

| 4.3  | Modulo $2^n - 1$ Adder with the Full Parallel-Prefix Structure                         | 72 |

| 4.4  | Another Way to Look at Modulo $2^n - 1$ Adder with the Full Parallel-Prefix Structure. | 72 |

| 4.5  | Modulo $2^n - 1$ Adder with the Reduced Parallel-Prefix Structure                      | 76 |

| 4.6  | The Reduced Sklansky Parallel-Prefix Tree                                              | 76 |

| 4.7  | 8-bit Sklansky with Ling's Scheme for Modulo $2^n - 1$ Adders                     |

|------|-----------------------------------------------------------------------------------|

| 4.8  | Modulo $2^n - 1$ Adder with the Reduced Parallel-Prefix Ling Structure            |

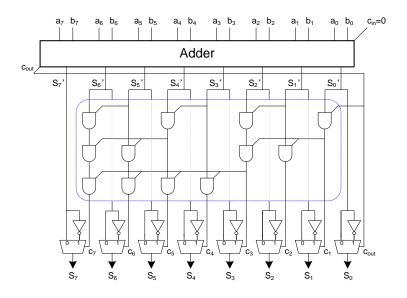

| 4.9  | 8-bit Carry-Select Modulo $2^n - 1$ Adder                                         |

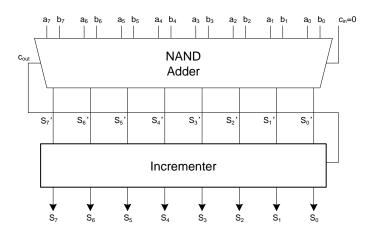

| 4.10 | CSEI with NAND Adder                                                              |

| 4.11 | General Block Diagram Modulo $2^n + 1$ Adder                                      |

| 4.12 | Modulo $2^n + 1$ Adder with the Reduced Parallel-Prefix Structure                 |

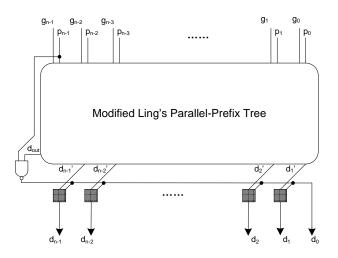

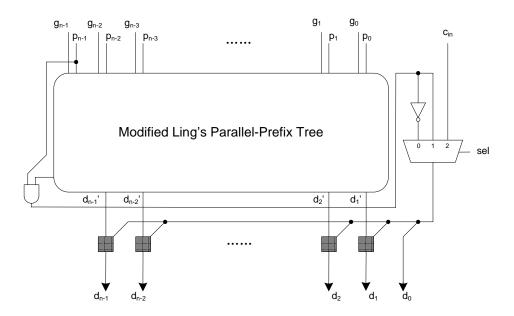

| 4.13 | Modulo $2^n + 1$ Adder with the Reduced Parallel-Prefix Ling Structure 86         |

| 4.14 | Additional Cell Definitions                                                       |

| 4.15 | Modulo $2^n + 1$ Adder with the Full Parallel-Prefix Structure                    |

| 4.16 | 8-bit Carry-Select Modulo $2^n + 1$ Adder                                         |

| 4.17 | Combined Binary and Modulo $2^n \pm 1$ Adders                                     |

| 4.18 | Combined Binary and Modulo $2^n \pm 1$ Adders using Ling's Scheme                 |

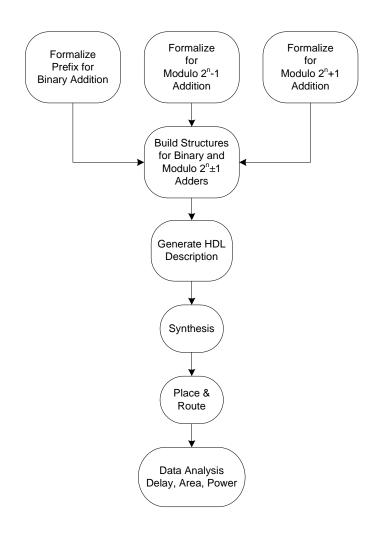

| 5.1  | Methodology of This Work                                                          |

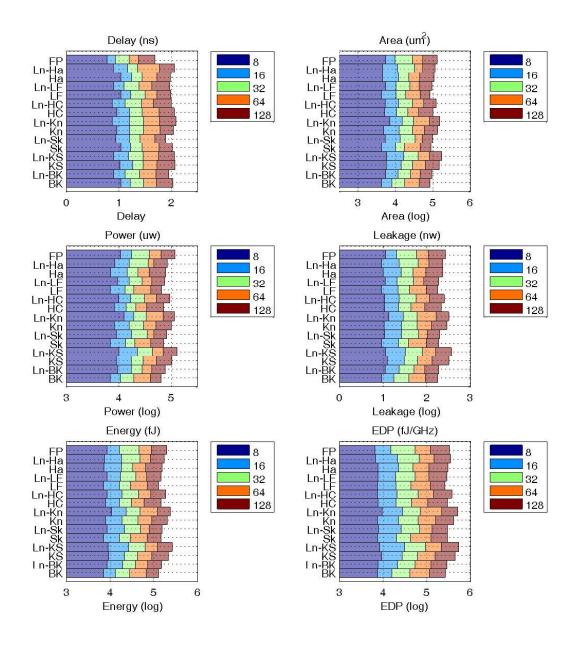

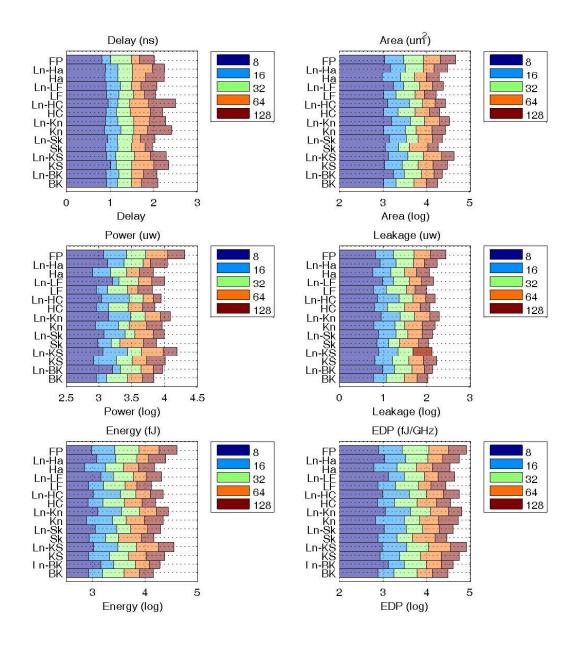

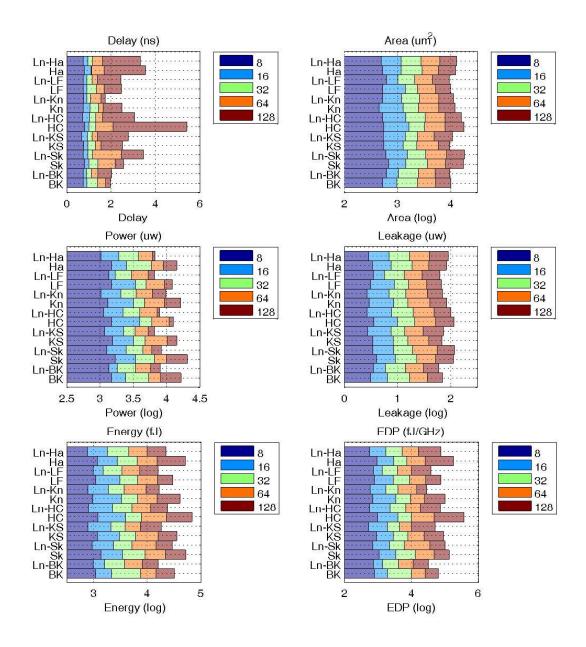

| 5.2  | TSMC 180nm Technology for Parallel Prefix Adders                                  |

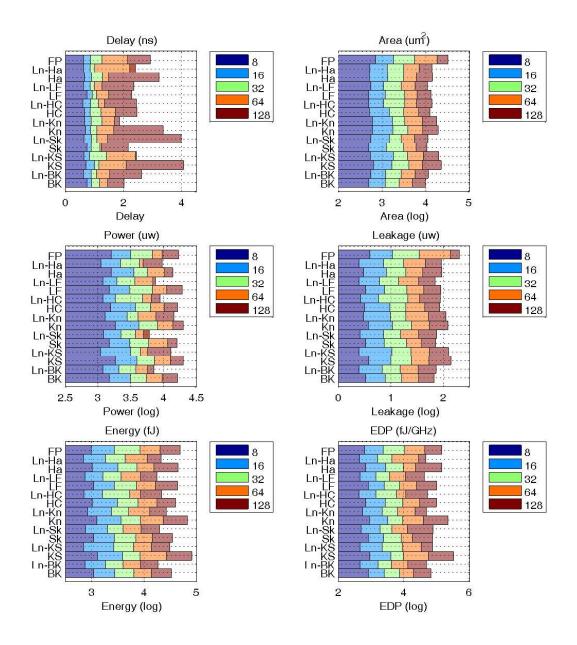

| 5.3  | Cadence GSCL 90nm Technology for Parallel Prefix Adders                           |

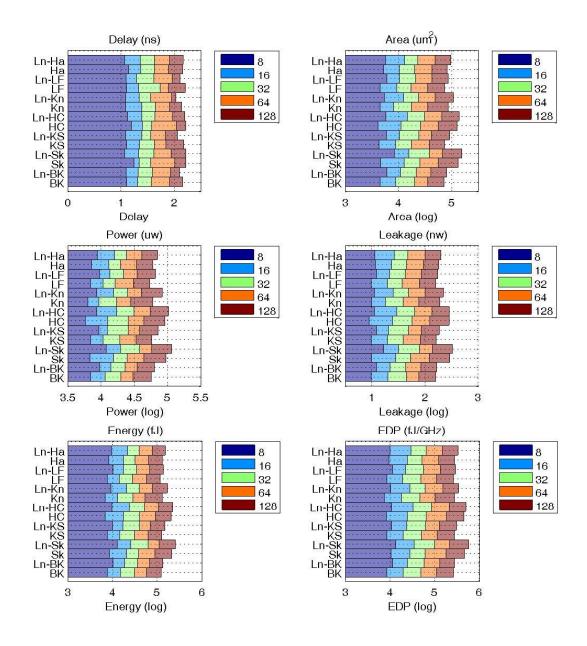

| 5.4  | FreePDK 45nm Technology for Parallel Prefix Adders                                |

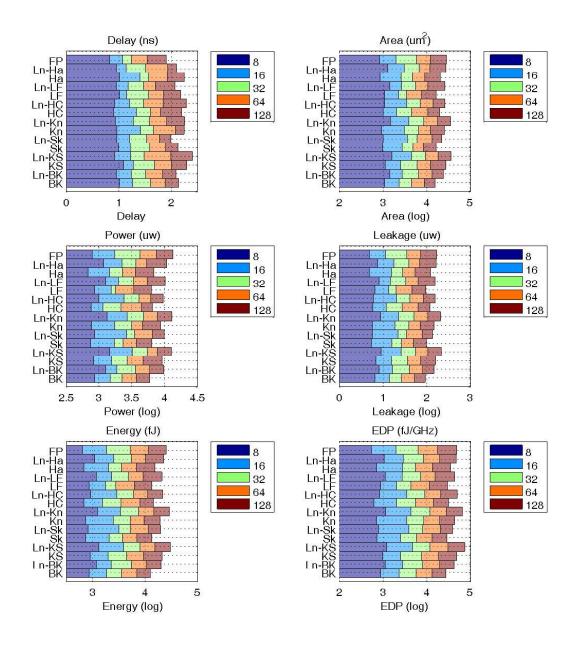

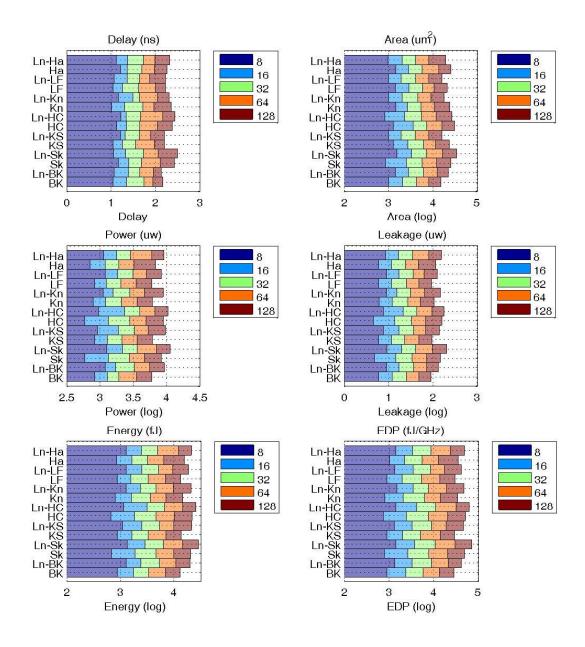

| 5.5  | TSMC 180nm Technology for Modulo $2^n - 1$ Adders                                 |

| 5.6  | Cadence GSCL 90nm Technology for Modulo $2^n - 1$ Adders                          |

| 5.7  | FreePDK 45nm Technology for Modulo $2^n - 1$ Adders                               |

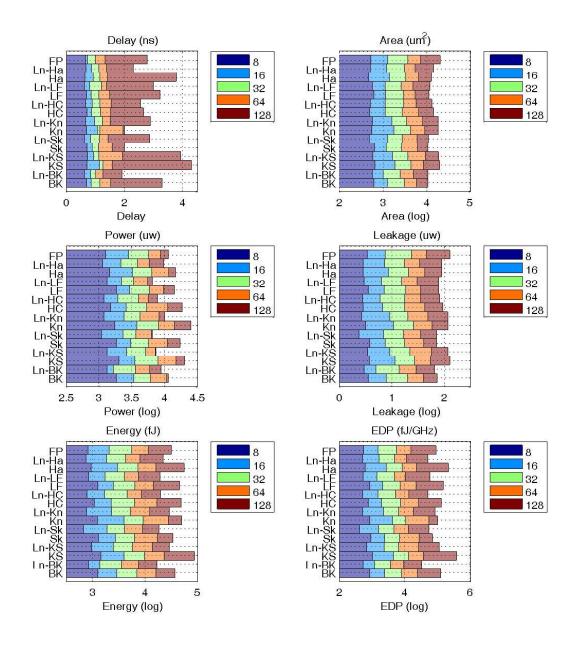

| 5.8  | TSMC 180nm Technology for Modulo $2^n + 1$ Adders                                 |

| 5.9  | Cadence GSCL 90nm Technology for Modulo $2^n + 1$ Adders                          |

| 5.10 | FreePDK 45nm Technology for Modulo $2^n + 1$ Adders                               |

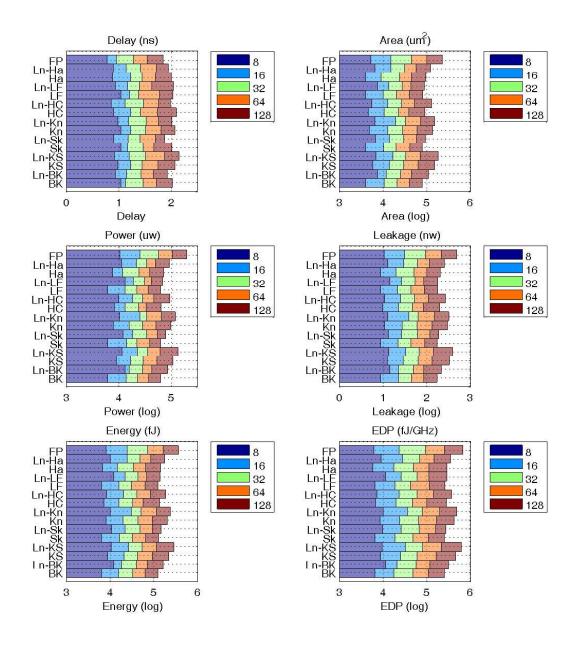

| 5.11 | TSMC 180nm Technology for Modulo $2^n \pm 1$ and Binary Prefix Adders 110         |

| 5.12 | Cadence GSCL 90nm Technology for Modulo $2^n \pm 1$ and Binary Prefix Adders. 111 |

| 5.13 | FreePDK 45nm Technology for Modulo $2^n \pm 1$ and Binary Prefix Adders 112       |

# LIST OF TABLES

Table

| ble |                                                                           | Page  |

|-----|---------------------------------------------------------------------------|-------|

| 2.1 | Algorithmic Analysis                                                      | . 20  |

| 3.1 | Verifying the Pseudo-Code of Building a Kogge-Stone Prefix Tree           | . 42  |

| 3.2 | Verifying the Pseudo-Code of Building a Knowles [2,1,1,1] Prefix Tree .   | . 47  |

| 3.3 | Verifying the Pseudo-Code of Building a Brent-Kung Prefix tree            | . 50  |

| 3.4 | Algorithmic Analysis                                                      | . 55  |

| 3.5 | Comparison of selected parallel-prefix structures                         | . 65  |

| 6.1 | Results for 64-bit Parallel-Prefix Adders within FreePDK 45nm Technolog   | y 116 |

| 6.2 | Results for 64-bit Modulo $2^n - 1$ Parallel-Prefix Adders within FreePDK |       |

|     | 45nm Technology                                                           | . 117 |

| 6.3 | Results for 64-bit Modulo $2^n + 1$ Parallel-Prefix Adders within FreePDK |       |

|     | 45nm Technology                                                           | . 117 |

#### **CHAPTER 1**

#### Introduction

## 1.1 Motivations

To humans, decimal numbers are easy to comprehend and implement for performing arithmetic. However, in digital systems, such as a microprocessor, DSP (Digital Signal Processor) or ASIC (Application-Specific Integrated Circuit), binary numbers are more pragmatic for a given computation. This occurs because binary values are optimally efficient at representing many values [2].

Binary adders are one of the most essential logic elements within a digital system. In addition, binary adders are also helpful in units other than Arithmetic Logic Units (ALU), such as multipliers, dividers and memory addressing [3]. Therefore, binary addition is essential that any improvement in binary addition can result in a performance boost for any computing system and, hence, help improve the performance of the entire system.

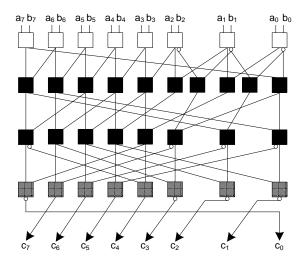

The major problem for binary addition is the carry chain [4]. As the width of the input operand increases, the length of the carry chain increases. Figure 1.1 demonstrates an example of an 8-bit binary add operation and how the carry chain is affected. This example shows that the worst case occurs when the carry travels the longest possible path, from the least significant bit (LSB) to the most significant bit (MSB) [4]. In order to improve the performance of carry-propagate adders, it is possible to accelerate the carry chain, but not eliminate it. Consequently, most digital designers often resort to building faster adders when optimizing a computer architecture, because they tend to set the critical path for most computations.

Figure 1.1: Binary Adder Example.

#### **1.2 Carry-Propagate Adders**

Binary carry-propagate adders have been extensively published, heavily attacking problems related to carry chain problem. Binary adders evolve from linear adders, which have a delay approximately proportional to the width of the adder, e.g. ripple-carry adder (RCA) [5], to logarithmic-delay adder, such as the carry-lookahead adder (CLA) [6]. There are some additional performance enhancing schemes, including the carry-increment adder [7] and the Ling adder [8] that can further enhance the carry chain, however, in Very Large Scale Integration (VLSI) digital systems, the most efficient way of offering binary addition involves utilizing parallel-prefix trees [9] [10] [11] [12] [13] [14], this occurs because they have the regular structures that exhibit logarithmic delay.

Parallel-prefix adders compute addition in two steps: one to obtain the carry at each bit, with the next to compute the sum bit based on the carry bit. Unfortunately, prefix trees are algorithmically slower than fast logarithmic adders, such as the carry propagate adders, however, their regular structures promote excellent results when compared to traditional CLA adders. This happens within VLSI architectures because a carry-lookahead adder, such as the one implemented in one of Motorola's processors [15], tends to implement the carry chain in the vertical direction instead of a horizontal one, which has a tendency to increase both wire density and fan-in/out dependence. Therefore, although logarithmic adder structures are one of the fastest adders algorithmically, the speed efficiency of the carry-lookahead adder has been hampered by diminishing returns given the fan-in and fan-out dependencies as well as the heavy wire load distribution in the vertical path. In fact, a traditional carry-lookahead adder implemented in VLSI can actually be slower than traditional linear-based adders, such as the Manchester carry adder [16].

## **1.3** Algorithmic Architectures for Parallel-Prefix Binary and Modulo $2^n \pm 1$ Adders

Although parallel-prefix structures are discussed in many articles, the process utilized to create them is briefly mentioned or described in most texts. More importantly, there is still a lack of insight how the architecture impacts circuit technology. As technology advances and minimum feature sizes within integrated circuit technology get smaller, there is limited quantitative data for binary adders using nanometer range technologies. Also good circuit design depends on a balance between architecture, circuit and technology choices. If a VLSI designer ignores any one of these design aspects, it can lead to design failures. This work addresses the problem of forming and algorithmically assembling parallel-prefix architectures as well as comparing their performance under nanometer technologies.

This work also extends binary adders to perform modulo addition. Modular arithmetics find applications in a wide range of areas since the operations are the basis for Residue Number Systems (RNS) [17]. Modulo addition/subtraction and multiplication are applied to digital filters [18] in digital signal processing, cryptography [19], error detection and correction [20], as well as checksum computation in high-speed networks [21]. There-fore, utilizing efficient architectures for modulo operations can impact many fields within science and engineering.

Modulo addition, an operation with a small variation to binary addition, can also be applied with prefix architectures [22] [23] [24] [25]. Common modulo addition can even be found in memory addressing. Modulo  $2^n - 1$  addition is one of the most common operations that has been put to hardware implementations because of its circuit efficiency [26]. Furthermore, modulo  $2^n + 1$  addition is critical to improving advanced cryptography techniques. As the variations of binary adders, modulo  $2^n - 1$ ,  $2^n$  and  $2^n + 1$  adders face the same problem as binary adders do: the carry chain dominates any performance seen at the output. There are multiple ways to algorithmically implement modulo adders. The most straightforward way to perform modulo addition is using an end-around addition [27], which is usually inefficient in terms of delay. The more aggressive architectures for modulo addition utilize modified parallel-prefix structures with minimum logic levels [23] [24]. There are also schemes that have a trade-off between logic levels and structural complexity [28].

Ling [8]'s scheme is not only effective on carry-propagating adders, but also can be utilized with parallel-prefix adders. Previously, Ling's scheme has be combined with parallelprefix adder structures, however, there is limited work done on applying Ling's scheme, especially for modulo prefix adders [29].

According to Moore's law, the number of transistors that can be put on a integrated circuit doubles every two years [30]. More functional parts can be present on a single die, leading engineers with the resource to add new and improved logic to an architecture, such as modulo addition, with dramatic performance improvements. Based on the work presented in this dissertation, it is feasible to incorporate both binary and modulo  $2^n \pm 1$  adders in a single architecture. More importantly, this work also describes how to efficiently build modulo adders and combine them with traditional binary carry propagate adders.

#### **1.4 Research Contributions**

The implementation that have been developed in this dissertation help to improve the design of parallel-prefix adders and their associated computing architectures. This has the potential of impacting many application specific and general purpose computer architectures. Consequently, this work can impact the designs of many computing systems, as well as impacting many areas of engineers and science. The following list are contributions of this work.

1. Simple algorithms that describe how to build parallel-prefix trees for various operand

sizes;

- 2. Parallel-prefix structures embedded with carry-save notation;

- 3. Modulo  $2^{n} \pm 1$  adder architectures that employ traditional prefix and Ling algorithms;

- 4. A better understanding of the relationship between addition and its algorithmic implementation in nanometer VLSI technology.

## 1.5 Dissertation Organized

This work is organized as follows. Chapter 2 reviews the basic arithmetic and background information on the implementation of binary adders. Chapter 3 illustrates the methods of building binary adders with prefix structures. This chapter also compares different types of prefix structures algorithmically. Chapter 4 offers the background of doing modulo  $2^n \pm 1$  adders and discusses various implementation methods, including parallel-prefix Ling structures. A combined binary and modulo  $2^n \pm 1$  adder architecture is proposed in this chapter. Chapter 5 presents results under 3 different technologies and compares the adder performance. Chapter 6 summarizes and concludes the work.

#### **CHAPTER 2**

#### **Binary Adder Schemes**

Adders are one of the most essential components in digital building blocks, however, the performance of adders become more critical as the technology advances. The problem of addition involves algorithms in Boolean algebra and their respective circuit implementation. Algorithmically, there are linear-delay adders like ripple-carry adders (RCA) [5], which are the most straightforward but slowest. Adders like carry-skip adders (CSKA) [31], carry-select adders (CSEA) [32] and carry-increment adders (CINA) [7] are linear-based adders with optimized carry-chain and improve upon the linear chain within a ripple-carry adder. Carry-lookahead adders (CLA) [6] have logarithmic delay and currently have evolved to parallel-prefix structures. Other schemes, like Ling adders, NAND/NOR adders and carry-save adders can help improve performance as well.

This chapter gives background information on architectures of adder algorithms. In the following sections, the adders are characterized with linear gate model, which is a rough estimation of the complexity of real implementation. Although this evaluation method can be misleading for VLSI implementers, such type of estimation can provide sufficient insight to understand the design trade-offs for adder algorithms.

#### 2.1 Binary Adder Notations and Operations

As mentioned previously, adders in VLSI digital systems use binary notation. In that case, add is done bit by bit using Boolean equations. Consider a simple binary add with two n-bit inputs A, B and a one-bit carry-in  $c_{in}$  along with n-bit output S.

Figure 2.1: 1-bit Half Adder.

$$S = A + B + c_{in}.\tag{2.1}$$

where  $A = a_{n-1}, a_{n-2}...a_0, B = b_{n-1}, b_{n-2}...b_0$ .

The + in the above equation is the regular add operation. However, in the binary world, only Boolean algebra works. For add related operations, AND, OR and Exclusive-OR (XOR) are required. In the following documentation, a dot between two variables (each with single bit), e.g.  $a \cdot b$  denotes 'a AND b'. Similarly, a + b denotes 'a OR b' and  $a \oplus b$  denotes 'a XOR b'.

Considering the situation of adding two bits, the sum s and carry c can be expressed using Boolean operations mentioned above.

$$s_i = a_i \oplus b_i$$

$$c_{i+1} = a_i \cdot b_i$$

(2.2)

The Equation (2.2) can be implemented as shown in Figure 2.1. In the figure, there is a half adder, which takes only 2 input bits. The solid line highlights the critical path, which indicates the longest path from the input to the output.

Equation (2.2) can be extended to perform full add operation, where there is a carry input.

$$s_i = a_i \oplus b_i \oplus c_i$$

$$c_{i+1} = a_i \cdot b_i + a_i \cdot c_i + b_i \cdot c_i$$

(2.3)

A full adder can be built based on Equation (2.3). The block diagram of a 1-bit full adder is shown in Figure 2.2. The full adder is composed of 2 half adders and an OR gate for

Figure 2.2: 1-bit Full Adder.

computing carry-out. The gates in Figure 2.2 do not implement directly Equation 2.3. Using Boolean algebra, the equivalence can be easily proven.

To help the computation of the carry for each bit, two binary literals are introduced. They are called carry generate and carry propagate, denoted by  $g_i$  and  $p_i$ . Another literal called temporary sum  $t_i$  is employed as well. There is relation between the inputs and these literals.

$$g_i = a_i \cdot b_i$$

$$p_i = a_i + b_i$$

$$t_i = a_i \oplus b_i$$

(2.4)

where i is an integer and  $0 \le i < n$ .

With the help of the literals above, output carry and sum at each bit can be written as

$$c_{i+1} = g_i + p_i \cdot c_i$$

$$s_i = t_i \oplus c_i$$

(2.5)

In some literatures, carry-propagate  $p_i$  can be replaced with temporary sum  $t_i$  in order to save the number of logic gates. Here these two terms are separated in order to clarify the concepts. For example, for Ling adders, only  $p_i$  is used as carry-propagate.

The single bit carry generate/propagate can be extended to group version G and P. The

Figure 2.3: Ripple-Carry Adder.

following equations show the inherent relations.

$$G_{i:k} = G_{i:j} + P_{i:j} \cdot G_{j-1:k}$$

$$P_{i:k} = P_{i:j} \cdot P_{j-1:k}$$

(2.6)

where i: k denotes the group term from i through k. Using group carry generate/propagate, carry can be expressed as expressed in the following equation.

$$c_{i+1} = G_{i:j} + P_{i:j} \cdot c_j \tag{2.7}$$

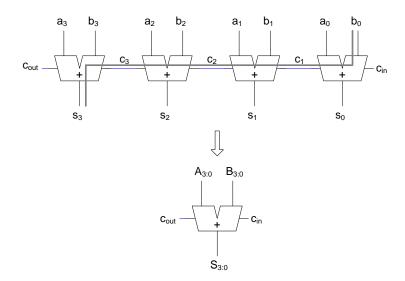

## 2.2 Ripple-Carry Adders (RCA)

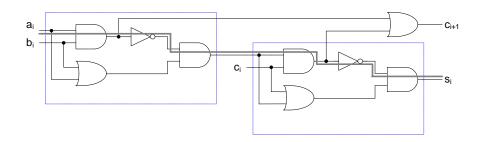

The simplest way of doing binary addition is to connect the carry-out from the previous bit to the next bit's carry-in. Each bit takes carry-in as one of the inputs and outputs sum and carry-out bit and hence the name ripple-carry adder. This type of adders is built by cascading 1-bit full adders. A 4-bit ripple-carry adder is shown in Figure 2.3. Each trapezoidal symbol represents a single-bit full adder. At the top of the figure, the carry is rippled through the adder from  $c_{in}$  to  $c_{out}$ . It can be observed in Figure 2.3 that the critical path, highlighted with a solid line, is from the least significant bit (LSB) of the input  $(a_0 \text{ or } b_0)$  to the most significant bit (MSB) of sum  $(s_{n-1})$ . Assuming each simple gate, including AND, OR and XOR gate has a delay of  $2\Delta$  and NOT gate has a delay of  $1\Delta$ . All the gates have an area of 1 unit. Using this analysis and assuming that each add block is built with a 9-gate full adder, the critical path is calculated as follows.

$$a_{i}, b_{i} \rightarrow s_{i} = 10\Delta$$

$$a_{i}, b_{i} \rightarrow c_{i+1} = 9\Delta$$

$$c_{i} \rightarrow s_{i} = 5\Delta$$

$$c_{i} \rightarrow c_{i+1} = 4\Delta$$

(2.8)

The critical path, or the worst delay is

$$t_{rca} = \{9 + (n-2) \times 4 + 5\}\Delta$$

=  $\{4n+6\}\Delta$  (2.9)

As each bit takes 9 gates, the area is simply 9n for a *n*-bit RCA.

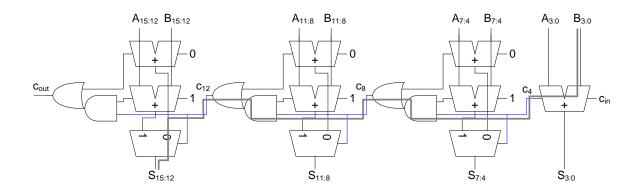

#### 2.3 Carry-Select Adders (CSEA)

Simple adders, like ripple-carry adders, are slow since the carry has to to travel through every full adder block. There is a way to improve the speed by duplicating the hardware due to the fact that the carry can only be either 0 or 1. The method is based on the conditional sum adder [33] and extended to a carry-select adder [32]. With two RCA, each computing the case of the one polarity of the carry-in, the sum can be obtained with a 2–1 multiplexer with the carry-in as the select signal. An example of 16-bit carry-select adder is shown in Figure 2.4. In the figure, the adder is grouped into four 4-bit blocks. The 1-bit multiplexors for sum selection can be implemented as Figure 2.5 shows. Assuming the two carry terms

Figure 2.4: Carry-Select Adder.

are utilized such that the carry input is given as a constant 1 or 0:

$$c_k^0 \triangleq c_k|_{c_j=0}$$

$$c_k^1 \triangleq c_k|_{c_j=1}$$

(2.10)

In Figure 2.4, each two adjacent 4-bit blocks utilizes a carry relationship

$$c_{i+4} = c_{i+4}^0 + c_{i+4}^1 \cdot c_i.$$

(2.11)

The relationship can be verified with properties of the group carry generate/propagate in Equation (2.7) and  $c_{i+4}^0$  can be written as

$$c_{i+4}^{0} = G_{i+4:i} + P_{i+4:i} \cdot 0$$

=  $G_{i+4:i}$ . (2.12)

Similarly,  $c_{i+4}^1 \, {\rm can}$  be written as

$$c_{i+4}^{1} = G_{i+4:i} + P_{i+4:i} \cdot 1$$

=  $G_{i+4:i} + P_{i+4:i}$ . (2.13)

Figure 2.5: 2-1 Multiplexor.

Then

$$c_{i+4}^{0} + c_{i+4}^{1} \cdot c_{i} = G_{i+4:i} + (G_{i+4:i} + P_{i+4:i}) \cdot c_{i}$$

$$= G_{i+4:i} + G_{i+4:i} \cdot c_{i} + P_{i+4:i} \cdot c_{i}$$

$$= C_{i+4} \qquad (2.14)$$

Varying the number of bits in each group can work as well for carry-select adders. Similar to (2.10), temporary sums can be defined as follows.

$$s_{i+1}^{0} = t_{i+1} \cdot c_{i}^{0}$$

$$s_{i+1}^{1} = t_{i+1} \cdot c_{i}^{1}.$$

(2.15)

The final sum is selected by carry-in between the temporary sums already calculated.

$$s_{i+1} = \overline{c_j} \cdot s_{i+1}^0 + c_j \cdot s_{i+1}^1 \tag{2.16}$$

Assuming the block size is fixed at r-bit, the n-bit adder is composed of k groups of r-bit blocks, i.e.  $n = r \times k$ . The critical path with the first RCA has a delay of  $(4r + 5)\Delta$ from the input to the carry-out, and there are k - 2 blocks that follow, each with a delay of  $4\Delta$  for carry to go through. The final delay comes from the multiplexor, which has a delay of  $5\Delta$ , as indicated in Figure 2.5. The total delay for this CSEA is calculated as

$$t_{csea} = 4r + 5 + 4(k - 2) + 5\Delta$$

=  $\{4r + 4k + 2\}\Delta.$  (2.17)

The area can be estimated with (2n - r) FAs, (n - r) multiplexors and (k - 1) AND/OR logic. As mentioned above, each FA has an area of 9 and a multiplexor takes 5 units of area. The total area can be estimated

$$9(2n-r) + 2(k-1) + 4(n-r) = 22n - 13r + 2k - 2$$

(2.18)

The delay of the critical path in CSEA is reduced at the cost of increased area. For example, in Figure 2.4, k = 4, r = 4 and n = 16. The delay for the CSEA is  $34\Delta$  compared to  $70\Delta$  for 16-bit RCA. The area for the CSEA is 310 units while the RCA has an area of 144 units. The delay of the CSEA is about the half of the RCA. But the CSEA has an area more than twice that of the RCA. Each adder can also be modified to have a variable block sizes, which gives better delay and slightly less area [34].

## 2.4 Carry-Increment Adders (CINA)

The delay of carry-select adders is reduced by duplicating the carry and sum part and hence, the area increase is significant. Tyagi [7] proposed a scheme that can have similar delay of carry-select adders without much increase in area. This type of adder is called a carry-increment adder. Zimmermann [35] expanded the idea to have multi-level structures.

The area can be reduced in that the carries defined in Equation (2.10) has the following relationship.

$$c_{i}^{1} = G_{i-1:j} + P_{i-1:j} \cdot c_{j}|_{c_{j}=1}$$

=  $G_{i-1:j} + P_{i-1:j}$  (2.19)

These requires that  $c_i^1$  is the carry when carry-in  $c_j = 1$  and  $c_i^0$  is the carry when  $c_j = 0$ . The superscript of "1" and "0" can be switched in the definition, however, the implementation

is not affected. Conversely, the carry-out equation assuming a carry-in of 0 can be written as

$$c_i^0 = G_{i-1:j} + P_{i-1:j} \cdot c_j|_{c_j=0}$$

=  $G_{i-1:j}$ . (2.20)

Inserting Equation (2.20) into Equation (2.19), the following relationship is established, which is the central equation for carry-increment adders.

$$c_i^1 = c_i^0 + P_{i-1:j} \tag{2.21}$$

The carry-out  $c_i$  can be also expressed with  $c_i^0$  and  $c_i^1$ .

$$c_i = \overline{c_j} \cdot c_i^0 + c_j \cdot c_i^1 \tag{2.22}$$

Inserting Equation (2.21) into Equation (2.22),  $c_i$  can finally be rewritten as

$$c_{i} = \overline{c_{j}} \cdot c_{i}^{0} + c_{j} \cdot (c_{i}^{0} + P_{i-1:j})$$

=  $c_{i}^{0} + P_{i-1:j} \cdot c_{j}.$  (2.23)

As Equation (2.20) indicates,  $c_i^0 = G_{i-1:j}$ , the above equation agrees with Equation (2.7). A 16-bit carry-increment adder example is shown in Figure 2.6. This is a 1-level structure with fixed 4-bit block size. Incrementers, instead of full adders are used to compute the sum (i.e. the temporary sum will be incremented either by 0 or by 1). Variable block size and multi-leveling can help improve the performance of CINA [36].

The critical path is similar to that of CSEA. The difference is that the incrementers replace the multiplexors in CSEA. The incrementor can be implemented using HAs as shown in Figure 2.1. An *r*-bit RCA using HAs has a delay of  $\{2(r-1)+3\}\Delta = \{2r+1\}\Delta$ . From Equation (2.23), the carry computation is through an OR after AND, which has a delay of  $4\Delta$ . The first RCA has a delay of  $(4r+5)\Delta$  from the input to the carry-out. There are k-2 carry generation blocks that follow, each has a delay of  $4\Delta$ .

Figure 2.6: Carry-Increment Adder.

$$t_{cina} = \{4r + 5 + 4(k - 2) + 2r + 1\}\Delta$$

=  $\{6r + 4k - 2\}\Delta$  (2.24)

The group propagate/generate is not in the critical path and does not contribute to the delay estimation. For an r-bit group propagate/generate, it takes 2r gates for generating single bit propagate/generate. For group propagate, one AND gate will suffice and r gates will be required for group generate. An r-bit group propagate/generate requires a total of 3r + 1 gates. The area is estimated with n-bit RCAs, k - 1 groups of propagate/generate logic and carry generation blocks along with incrementers. Hence, the total area is estimated as

$$9n + (3r+1)(k-1) + 2(k-1) + 4r(k-1) = 16n + 3k - 7r - 3$$

(2.25)

The delay of a CINA is slightly larger than a CSEA but the area is obviously reduced. The block size and the number of blocks can be varied to implement CINAs. Multi-leveling carry architectures can further improve the performance of this adder [35].

## 2.5 Carry-Skip Adders (CSKA)

There is an alternative way of reducing the delay in the carry-chain of a RCA by checking if a carry will propagate through to the next block. This is called carry-skip adders [31].

Figure 2.7: Carry-Skip Adder.

The idea of this adder is to modify the Equation (2.7), as shown in Equation (2.26).

$$c_{i+1} = \overline{P_{i:j}} \cdot G_{i:j} + P_{i:j} \cdot c_j \tag{2.26}$$

Figure 2.7 shows an example of 16-bit carry-skip adder.

The carry-out of each block is determined by selecting the carry-in and  $G_{i:j}$  using  $P_{i:j}$ . When  $P_{i:j} = 1$ , the carry-in  $c_j$  is allowed to get through the block immediately. Otherwise, the carry-out is determined by  $G_{i:j}$ . The CSKA has less delay in the carry-chain with only a little additional extra logic. Further improvement can be achieved generally by making the central block sizes larger and the two-end block sizes smaller [37].

Assuming the *n*-bit adder is divided evenly to k *r*-bit blocks, part of the critical path is from the LSB input through the MSB output of the final RCA. The first delay is from the LSB input to carry-out, which is 4r + 5. Then, there are k - 2 skip logic blocks with a delay of  $3\Delta$ . Each skip logic block includes one 4-input AND gate for getting  $P_{i+3:i}$  and one AND/OR logic. The final RCA has a delay from input to sum at MSB, which is 4r + 6. The total delay is calculated as follows.

$$t_{cska} = \{4r + 5 + 3(k - 2) + 4r + 6\}\Delta$$

=  $\{8r + 3k + 5\}\Delta$  (2.27)

The CSKA has *n*-bit FA and k - 2 skip logic blocks. Each skip logic block has an area of 3 units. Therefore, the total area is estimated as

$$9n + 3(k - 2) = 9n + 3k - 6 \tag{2.28}$$

Figure 2.8: Reduced Full Adder.

#### 2.6 Carry-Lookahead Adders (CLA)

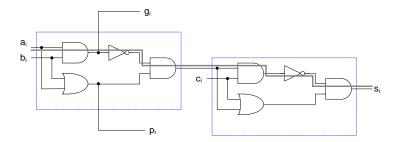

The carry-chain can also be accelerated with carry generate/propagate logic, as in Equation (2.7). Carry-lookahead adders employ the carry generate/propagate in groups to generate carry for the next block [6]. In other words, digital logic is used to calculate all the carries at once. When building a CLA, a reduced version of full adder, which is called a reduced full adder (RFA) is utilized. Figure 2.8 shows the block diagram for an RFA. The carry generate/propagate signals  $g_i/p_i$  feed to carry-lookahead generator (CLG) for carry inputs to RFA.

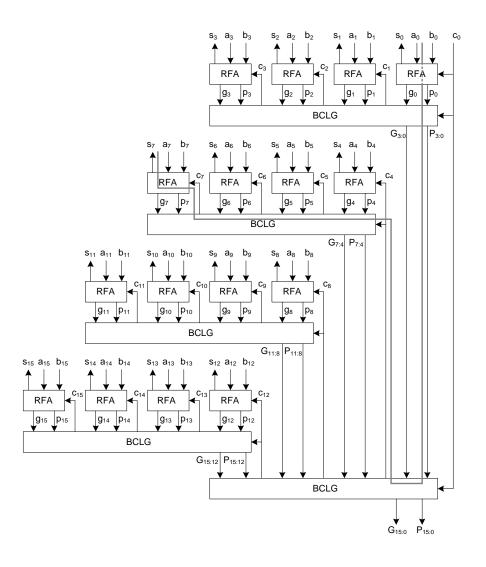

The theory of the CLA is based on Equation (2.6) and (2.7). Figure 2.9 shows an example of 16-bit carry-lookahead adder. In the figure, each block is fixed at 4-bit. BCLG stands for Block Carry Lookahead Carry Generator, which generates generate/propagate signals in group form [6]. For the 4-bit BCLG, the following equations are created.

$$G_{i+3:i} = g_{i+3} + p_{i+3} \cdot g_{i+2} + p_{i+3} \cdot p_{i+2} \cdot g_{i+1} + p_{i+3} \cdot p_{i+2} \cdot p_{i+1} \cdot g_i$$

$$P_{i+3:i} = p_{i+3} \cdot p_{i+2} \cdot p_{i+1} \cdot p_i$$

(2.29)

The group generate takes a delay of  $4\Delta$ , which is an OR after an AND, therefore, the carry-out can be computed, as follows.

$$c_{i+3} = G_{i+3:i} + P_{i+3:i} \cdot c_i \tag{2.30}$$

The carry computation also has a delay of  $4\Delta$ , which is an OR after an AND. The 4-bit BCLG has an area of 14 units [38].

The critical path of the 16-bit CLA can be observed from the input operand through 1 RFA, then 3 BCLG and through the final RFA. That is, the critical path shown in Figure 2.9 is from  $a_0/b_0$  to  $s_7$ . The delay will be the same for  $a_0/b_0$  to  $s_{11}$  or  $s_{15}$ , however, the critical path traverses logarithmically, based on the group size. The delays are listed below.

$$a_{0}, b_{0} \rightarrow p_{0}, g_{0} = 2\Delta$$

$$p_{0}, g_{0} \rightarrow G_{3:0} = 4\Delta$$

$$G_{3:0} \rightarrow c_{4} = 4\Delta$$

$$c_{4} \rightarrow c_{7} = 4\Delta$$

$$c_{7} \rightarrow s_{7} = 5\Delta$$

$$a_{0}, b_{0} \rightarrow s_{7} = 19\Delta$$

(2.31)

The 16-bit CLA is composed of 16 RFAs and 5 BCLGs, which amounts to an area of  $16 \times 8 + 5 \times 14 = 198$  units.

Extending the calculation above, the general estimation for delay and area can be derived. Assume the CLA has *n*-bits, which is divided into k groups of r-bit blocks. It requires  $\lceil log_rn \rceil$  logic levels. The critical path starts from the input to  $p_0/g_0$  generation, BLCG logic and the carry-in to sum at MSB. The generation of (p, g) takes a delay of  $2\Delta$ . The group version of (p, g) generated by the BCLG has a delay of  $4\Delta$ . From next BCLG, there is a  $4\Delta$  delay from the CLG generation and  $4\Delta$  from the BCLG generation to the next level, which totals to  $8\Delta$ . Finally, from  $c_{k+r}$  to  $s_{k+r}$ , there is a delay of  $5\Delta$ . Thus, the total delay is calculated as follows.

$$t_{cla} = \{2 + 8(\lceil log_r n \rceil - 1) + 4 + 5\}\Delta$$

$$= \{3 + 8\lceil log_r n \rceil\}\Delta$$

(2.32)

An *n*-bit CLA requires *n* RFAs and a logarithmical number of BCLGs assuming each BCLG has the same block size  $\log_{n} n$

$$\sum_{l=1}^{\log_r n} \frac{n}{r^l} \tag{2.33}$$

Figure 2.9: Carry-Lookahead Adder.

Each BCLG requires  $\frac{(3+r)r}{2}$  gates and each RFA requires 8 gates, therefore, the total area of a CLA can be estimated as follows.

$$8n + \frac{(3+r)r}{2} \sum_{l=1}^{\log_r n} \frac{n}{r^l}$$

(2.34)

#### 2.6.1 Algorithmic Analysis

As seen in previous chapters, the basic adder algorithms have several algorithmic enhancements based on the length of their carry-chain. The algorithmic analysis is summarized in Table 2.1, and assumes all the adders have a width of n. Some of the adders divide these n

| Adder Type      | $Delay(\Delta)$               | Area (gates)                                                |

|-----------------|-------------------------------|-------------------------------------------------------------|

| Ripple-Carry    | 4n + 6                        | 9n                                                          |

| Carry-Select    | 4r + 4k + 2                   | 22n - 13r + 2k - 2                                          |

| Carry-Increment | 6r + 4k - 2                   | 16n - 7r + 3k - 3                                           |

| Carry-Skip      | 8r + 3k + 5                   | 9n + 3k - 6                                                 |

| Carry-Lookahead | $3 + 8 \lceil log_r n \rceil$ | $8n + \frac{(3+r)r}{2} \sum_{l=1}^{\log_r n} \frac{n}{r^l}$ |

Table 2.1: Algorithmic Analysis

bits into k groups, with a constant r-bits in each group.

## 2.7 Ling Adders

Although CLA structures are optimal for speeding up addition, they still can be improved. Ling adder [8] optimizes the performance by reducing fan-in of the logic gates. The idea is to utilize the property of carry generate and propagate.

$$g_i = a_i \cdot b_i \quad p_i = a_i + b_i, \tag{2.35}$$

The inherent relation can be observed as shown in the following equation.

$$g_i = g_i \cdot p_i \tag{2.36}$$

since

$$a_i \cdot b_i = a_i \cdot b_i \cdot (a_i + b_i) \tag{2.37}$$

The group carry generate can then be re-written as

$$G_{i:k} = p_i \cdot (g_i + g_{i-1} + p_{i-1} \cdot g_{i-2} + \dots + p_{i-1} \cdot \dots \cdot p_{k+1} \cdot g_k)$$

=  $p_i \cdot H_{i:k}$  (2.38)

where

$$H_{i:k} = g_i + g_{i-1} + p_{i-1} \cdot g_{i-2} + \dots + p_{i-1} \cdot \dots \cdot p_{k+1} \cdot g_k$$

(2.39)

Since the carry depends on a new term, it can be re-written as

$$c_{i+1} = G_{i:k} + P_{i:k} \cdot c_k$$

=  $p_i \cdot (H_{i:k} + P_{i-1:k})$

=  $p_i \cdot d_{i+1}$  (2.40)

where the pseudo carry is introduced as

$$d_{i+1} = H_{i:k} + P_{i-1:k} \tag{2.41}$$

In the case of k = -1,

$$c_{i+1} = G_{i:-1} \tag{2.42}$$

and

$$d_{i+1} = H_{i:-1}. (2.43)$$

Ling adders extract  $p_i$ , such that the fan-in of logic gates in the carry-chain is reduced. This is useful for dynamic logic since the serial stack of NMOS can be reduced by one and subsequently reduces sizing constraints. For example, consider a 4-bit group generate, such that

$$G_{i+3:i} = g_{i+3} + p_{i+3} \cdot g_{i+2} + p_{i+3} \cdot p_{i+2} \cdot g_{i+1} + p_{i+3} \cdot p_{i+2} \cdot p_{i+1} \cdot g_i$$

(2.44)

while

$$H_{i+3:i} = g_{i+3} + g_{i+2} + p_{i+2} \cdot g_{i+1} + p_{i+2} \cdot p_{i+1} \cdot g_i.$$

(2.45)

$H_{i+3:i}$  takes 7 inputs to 3 gates with a maximum fan-out of 3 whereas  $G_{i+3:i}$  takes 10 inputs to 4 gates with a maximum fan-out of 4. It is obvious that the *H* term is much easier to obtain than the *G* term.

The H term shares the property of G, such that H can be derived as a group version as expressed in the following equation.

$$H_{i:k} = H_{i:j+1} + P_{i-1:j} \cdot H_{j:k}$$

(2.46)

Thus, the carry chain can be calculated with H instead of G. Due to the simpler circuit to computing H, the carry chain can be significantly reduced compared to a carry chain computing from G. If a long carry chain is divided with several blocks using H, the speed gain can significantly enhance the critical path, as opposed to using G in the blocks.

The sum for Ling adder can, therefore, be expressed in the following form.

$$s_i = p_i \oplus H_{i:-1} + g_i \cdot p_{i-1} \cdot H_{i-1:-1} \tag{2.47}$$

To prove Equation (2.47), there is another important relation that can be derived from Equation (2.45).

$$H_{i+3:i} = g_{i+3} + p_{i+2} \cdot (g_{i+2} + g_{i+1} + p_{i+1} \cdot g_i)$$

=  $g_{i+3} + p_{i+2} \cdot H_{i+2:i}$  (2.48)

since  $H_{i+2:i} = g_{i+2} + g_{i+1} + p_{i+1} \cdot g_i$ . Rewriting Equation (2.48), a more general and simpler expression can be derived.

$$H_{i:k} = g_i + p_{i-1} \cdot H_{i-1:k} \tag{2.49}$$

As  $s_i = t_i \oplus c_i$  and  $c_i = G_{i-1:-1} = p_{i-1} \cdot H_{i-1:-1}$ ,

$$s_{i} = t_{i} \oplus p_{i-1} \cdot H_{i-1:-1}$$

=  $\overline{t_{i}} \cdot p_{i-1} \cdot H_{i-1:-1} + t_{i} \cdot \overline{p_{i-1}} \cdot H_{i-1:-1}$

=  $(g_{i} + \overline{p_{i}}) \cdot p_{i-1} \cdot H_{i-1:-1} + p_{i} \cdot \overline{g_{i}} \cdot \overline{p_{i-1}} \cdot H_{i-1:-1}$  (2.50)

where  $\overline{t_i} = g_i + \overline{p_i}$  and  $t_i = p_i \cdot \overline{g_i}$ . These two inserted equations can be easily proven by reducing the terms with  $a_i/b_i$ . Continue with Equation (2.50),

$$s_{i} = \overline{p_{i}} \cdot p_{i-1} \cdot H_{i-1:-1} + p_{i} \cdot \overline{g_{i}} \cdot \overline{p_{i-1}} \cdot \overline{H_{i-1:-1}} + g_{i} \cdot p_{i-1} \cdot H_{i-1:-1}$$

(2.51)

Figure 2.10: NAND Adder Carry Chain.

Adding another term  $\overline{p_i} \cdot g_i$  to the Equation (2.51) also reduces the logic significantly. The added term has no effect on altering the logic since  $\overline{p_i} \cdot g_i = 0$ . Rewrite Equation (2.51) and applying Equation (2.49), the following equation can be derived, which is the same as Equation (2.47).

$$s_{i} = \overline{p_{i}} \cdot (g_{i} + p_{i-1} \cdot H_{i-1:-1}) + p_{i} \cdot \overline{g_{i} + p_{i-1} \cdot H_{i-1:-1}} + g_{i} \cdot p_{i-1} \cdot H_{i-1:-1}$$

$$= \overline{p_{i}} \cdot H_{i:-1} + p_{i} \cdot \overline{H_{i:-1}} + g_{i} \cdot p_{i-1} \cdot H_{i-1:-1}$$

(2.52)

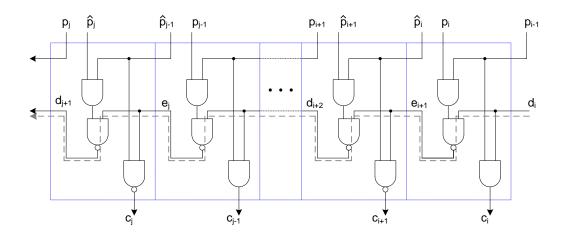

#### 2.8 NAND/NOR Adders

Ling's equations can be further modified to enhance ripple-carry adders. This type of adders are also called NAND or NOR adders [39] [40]. In CMOS logic, NAND gates are usually faster than NOR gates while NOR adders are more suitable for domino logic. Be-cause CMOS NOR gates have stacked PMOS transistors, they are usually slower than the NMOS transistors stacked in NAND gates. In domino logic, NOR gates has NMOS transistors are stacked in serial.

NAND/NOR adders utilize a similar idea as Ling's, but use a complemented version of

the propagate and generate from the following equations.

$$\hat{g}_{i} = \overline{a_{i}} \cdot \overline{b_{i}}$$

$$\hat{p}_{i} = \overline{a_{i}} + \overline{b_{i}}$$

(2.53)

These equations can be formed into a new equation using the complemented values of the propagate/generate.

$$\hat{c}_{i+1} = \hat{g}_i + \hat{p}_i \cdot \overline{c_i} \tag{2.54}$$

An important property between the carry terms is

$$\hat{c}_{i+1} = \overline{c_{i+1}}.\tag{2.55}$$

This can be proven as the following procedure.

$$\overline{c_{i+1}} = \overline{g_i + p_i \cdot c_i}$$

$$= \overline{g_i} \cdot (\overline{p_i} + \overline{c_i})$$

$$= \overline{p_i} + \overline{g_i} \cdot \overline{c_i}$$

$$= \hat{g}_i + \hat{p}_i \cdot \overline{c_i} = \hat{c}_i \qquad (2.56)$$

Besides Ling's pseudo-carry d, a second pseudo-carry e is introduced as following definition.

$$e_i \triangleq \hat{d}_i \tag{2.57}$$

For NAND adders, the pseudo-carries can be written as

$$d_{i+1} = g_i + c_i$$

$$e_{i+1} = \hat{g}_i + \overline{c_i}$$

(2.58)

Applying DeMorgan's law and the relation  $\hat{g}_i = \overline{p_i}$  and  $\hat{p}_i = \overline{g_i}$ , the complemented pseudocarries can be expressed as

$$\overline{d_{i+1}} = \hat{p_i} \cdot \overline{c_i}$$

$$\overline{e_{i+1}} = p_i \cdot c_i$$

(2.59)

Figure 2.11: NOR Adder Carry Chain.

Insert the following relation between carry and pseudo-carries into the equations above.

$$c_{i} = p_{i-1} \cdot d_{i}$$

$$\overline{c_{i}} = \hat{p}_{i-1} \cdot e_{i}$$

(2.60)

The NAND equations can now be rewritten as

$$\overline{d_{i+1}} = \hat{p}_i \cdot \hat{p}_{i-1} \cdot e_i$$

$$\overline{e_{i+1}} = p_i \cdot p_{i-1} \cdot d_i$$

(2.61)

or

$$d_{i+1} = \overline{\hat{p}_{i:i-1} \cdot e_i}$$

$$e_{i+1} = \overline{p_{i:i-1} \cdot d_i}$$

(2.62)

The carry chain in NAND adders with two pseudo-carries is shown in Figure 2.10. Thus, sum can be obtained using the following equation.

$$s_i = t_i \oplus c_i \tag{2.63}$$

or, in a different expression,

$$s_i = t_i \oplus (p_{i-1} \cdot d_i)$$

=  $\overline{t_i}(p_{i-1} \cdot d_i) + t_i(\hat{p}_{i-1} \cdot e_i)$  (2.64)

by referencing Equation (2.60). This can be implemented with a multiplexor with  $t_i$  as the select signal.

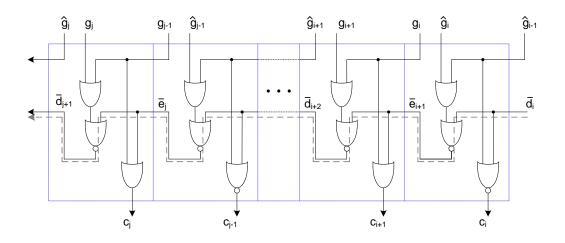

Similarly, the NOR adder can be derived from rewriting Equation (2.61).

$$\overline{d_{i+1}} = \overline{\hat{p}_i \cdot \hat{p}_{i-1} \cdot e_i}$$

$$\overline{e_{i+1}} = \overline{p_i \cdot p_{i-1} \cdot d_i}$$

(2.65)

Further simplification can be achieved using DeMorgan's law.

$$\overline{d_{i+1}} = \overline{g_i + g_{i-1} + \overline{e_i}}$$

$$\overline{e_{i+1}} = \overline{\hat{g}_i + \hat{g}_{i-1} + \overline{d_i}}$$

(2.66)

or

$$d_{i+1} = g_i + g_{i-1} + \overline{e_i}$$

$$e_{i+1} = \hat{g}_i + \hat{g}_{i-1} + \overline{d_i}$$

(2.67)

Similar to the NAND adder, when computing the sum, the following equation can be utilized.

$$\overline{s_i} = t_i \oplus \overline{c_i} \tag{2.68}$$

In other words, the carry-chain has to be complemented and applied through Boolean logic to form the sm.

$$s_{i} = t_{i} \odot \overline{c_{i}}$$

$$= \overline{t_{i}}(g_{i-1} + \overline{e_{i}}) + t_{i}(\hat{g}_{i-1} + \overline{d_{i}})$$

(2.69)

These simplifications assume two carries produced after the carry tree.

$$c_{i} = g_{i-1} + \overline{e_{i}}$$

$$\overline{c_{i}} = \hat{g}_{i-1} + \overline{d_{i}}$$

(2.70)

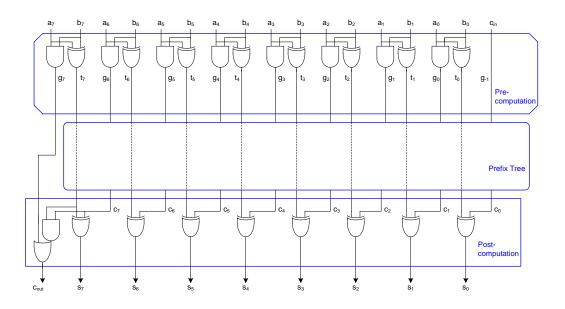

### 2.9 Parallel-Prefix Structures

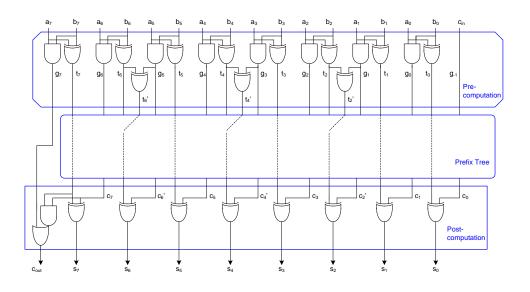

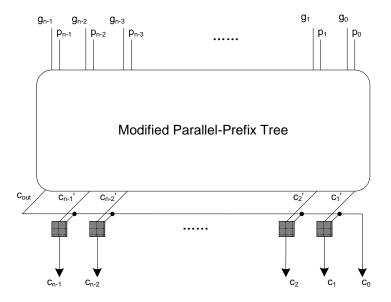

To resolve the delay of carry-lookahead adders, the scheme of multilevel-lookahead adders or parallel-prefix adders can be employed [41]. The idea is to compute small group of intermediate prefixes and then find large group prefixes, until all the carry bits are computed. These adders have tree structures within a carry-computing stage similar to the carry propagate adder. However, the other two stages for these adders are called pre-computation and post-computation stages.

In pre-computation stage, each bit computes its carry generate/propagate and a temporary sum as in Equation (2.4). In the prefix stage, the group carry generate/propagate signals are computed to form the carry chain and provide the carry-in for the adder below. Equation (2.6) is repeated here as a reminder

$$G_{i:j} = G_{i:k} + P_{i:k} \cdot G_{k-1:j}$$

$$P_{i:j} = P_{i:k} \cdot P_{k-1:j}$$

(2.71)

In the post-computation stage, the sum and carry-out are finally produced. The carry-out can be omitted if only a sum needs to be produced.

$$s_i = t_i \oplus G_{i:-1}$$

$c_{out} = g_{n-1} + p_{n-1} \cdot G_{n-2:-1}$

(2.72)

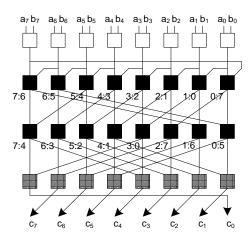

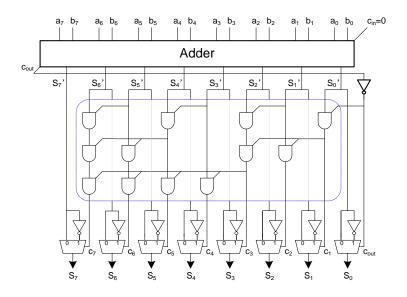

where  $G_{i:-1} = c_i$  with the assumption  $g_{-1} = c_{in}$ . The general diagram of parallel-prefix structures is shown in Figure 2.12, where an 8-bit case is illustrated.

All parallel-prefix structures can be implemented with the equations above, however, Equation (2.71) can be interpreted in various ways, which leads to different types of parallelprefix trees. For example, Brent-Kung [9] is known for its sparse topology at the cost of more logic levels. There are several design factors that can impact the performance of prefix structures [42]

• Radix/Valency

Figure 2.12: 8-bit Parallel-Prefix Structure.

- Logic Levels

- Fan-out

- Wire tracks

To illustrate a sample prefix structure, an 8-bit Sklansky [12] prefix tree is shown in Figure 2.13. Although Sklansky created this prefix structure with relationship to adders, it is typically referred to as a member of the Ladner-Fischer [13] prefix family. More details about prefix structures, including how to build the prefix structures and the performance comparison, will be described the next chapter of this dissertation.

# 2.10 Carry Save Adders (CSA)

Instead of performing binary addition by carry-propagating, it is possible to use redundant notation, to represent a number by using a carry-save adder [43] [44] [45]. Carry-save notation utilizes two vectors to store the carry bits and sum bits. In this way, carry-propagation is avoided but generally still required to form a final sum. Carry-save notation is usually

Figure 2.13: Sklansky Parallel-Prefix Examples.

used in multi-operand addition/subtraction, where multiple inputs are joined into two outputs. A 4-bit three-input carry-save adder example is shown in In Figure 2.14. The top of the figure shows the 4-bit adder bit by bit and bottom shows the vector form of the adder. Each bit is a full adder that takes three inputs and has two outputs. This can also be called as 3-2 counter. The computation at each bit for bit 0 through bit *n* is as follows.

$$vs_i = d_i \oplus e_i \oplus f_i,$$

$$vc_i = d_i \cdot e_i \cdot f_i$$

(2.73)

The only exception is that

$$vc_0 = c_{in} \tag{2.74}$$

Since every bit is independent of each other and thus, there is no carry-chain. To compute the final binary sum, one more carry-propagate addition is required. The final process is,

$$S = VC + VS$$

$$c_{out} = vc_n \tag{2.75}$$

Although not straight-forward, carry-save notation can also be applied to parallel-prefix structures to obtain a more balanced architecture, which will be discussed later on in this dissertation.

Figure 2.14: 4-bit Carry-Save Adder.

# 2.11 Summary

This chapter gives the background of binary carry propagate adders. Basic adder algorithms, from linear-based adders to logarithmic adders, are discussed in this chapter. Based on the defined terms and knowledge about the adders, next chapter will illustrate how to build prefix trees for use in logarithmic adders.

# **CHAPTER 3**

### **Building Prefix Structures**

Parallel-prefix structures are found to be common in high performance adders because of the delay is logarithmically proportional to the adder width. Such structures can usually be divided into three stages, pre-computation, prefix tree and post-computation. An example of an 8-bit parallel-prefix structure is shown in Figure 2.12

In the prefix tree, group generate/propagate are the only signals used. The group generate/propagate equations are based on single bit generate/propagate, which are computed in the pre-computation stage.

$$g_i = a_i \cdot b_i$$

$$p_i = a_i \oplus b_i$$

(3.1)

where  $0 \le i \le n$ .  $g_{-1} = c_{in}$  and  $p_{-1} = 0$ . Sometimes,  $p_i$  can be computed with OR logic instead of an XOR gate. The OR logic is mandatory especially when Ling's [8] scheme is applied. Here, the XOR logic is utilized to save a gate for temporary sum  $t_i$ .

In the prefix tree, group generate/propagate signals are computed at each bit.

$$G_{i:k} = G_{i:j} + P_{i:j} \cdot G_{j-1:k}$$

$$P_{i:k} = P_{i:j} \cdot P_{j-1:k}$$

$$(3.2)$$

More practically, Equation (3.2) can be expressed using a symbol " $\circ$ " denoted by Brent and Kung [9]. Its function is exactly the same as that of a black cell. That is

$$(G_{i:k}, P_{i:k}) = (G_{i:j}, P_{i:j}) \circ (G_{j-1:k}, P_{j-1:k}),$$

(3.3)

Figure 3.1: Cell Definitions.

or

$$G_{i:k} = (g_i, p_i) \circ (g_{i-1}, p_{i-1}) \circ \dots \circ (g_k, p_k)$$

$$P_{i:k} = p_i \cdot p_{i-1} \cdot \dots \cdot p_k.$$

(3.4)

The " $\circ$ " operation will help make the rules of building prefix structures.

In the post-computation, the sum and carry-out are the final output.

$$s_i = p_i \cdot G_{i-1:-1}$$

$$c_{out} = G_{n:-1}$$

$$(3.5)$$

where "-1" is the position of carry-input. The generate/propagate signals can be grouped in different fashion to get the same correct carries. Based on different ways of grouping the generate/propagate signals, different prefix architectures can be created.

Figure 3.1 shows the definitions of cells that are used in prefix structures, including black cell and gray cell. Black/gray cells implement Equation (3.2) or (3.3), which will be heavily used in the following discussion on prefix trees.

# 3.1 Prefix Tree Family

Parallel-prefix trees have various architectures. These prefix trees can be distinguished by four major factors. 1) Radix/Valency 2) Logic Levels 3) Fan-out 4) Wire Tracks In the following discussion about prefix trees, the radix is assumed to be 2 (i.e. the number of

inputs to the logic gates is always 2). The more aggressive prefix schemes have logic levels  $\lceil log_2(n) \rceil$ , where *n* is the width of the inputs. However, these schemes require higher fanout, or many wire-tracks or dense logic gates, which will compromise the performance e.g. speed or power. Some other schemes have relieved fan-out and wire tracks at the cost of more logic levels. When radix is fixed, The design trade-off is made among the logic levels, fan-out and wire tracks.

In the following sections, discussion on how to build a prefix tree will be presented. First, the basic elements to build a prefix tree are defined with a small example given as an introduction. After that, three representatives of the prefix family are described in detail, starting with Kogge-Stone [10], Knowles [11], followed by Brent-Kung [9]. Subsequently, Sklansky [12], Ladner-Fischer [13], Han-Carlson [14], and Harris [1] prefix trees are generally described. Finally, a new prefix scheme embedded with carry-save notation is introduced along with the explanation on how to form its structure.

# 3.2 Prefix Structure Synthesis

### 3.2.1 Taxonomy

The prefix trees can be classified using the factors mentioned above. Since the radix is fixed, the taxonomy uses the (l, f, t) [1], with each variable representing Logic Levels, Fan-out and Wire Tracks, respectively.

- Logic Levels: L + l

- Fan-out:  $2^f + 1$

- Wire Tracks:  $2^t$

For Logic Levels,  $L = log_2(n)$  for any n-bit prefix tree. l, f and t are integers between 0 and L - 1. Brent-Kung (L - 1, 0, 0) prefix tree has the least fan-out and wiring tracks. This type of prefix tree always has a maximum fan-out of  $2^0 + 1 = 2$  and maximum wire

$(G_{i:j}, P_{i:j}) \ o \ \{(G_{j-1:k}, P_{j-1:k})] \ o \ [(G_{k-1:l}, P_{k-1:l}) \ o \ (G_{l-1:m}, P_{l-1:m})]\}$

$(G_{i:j}, \ P_{i:j}) \ o \ \{[(G_{j-1:k}, \ P_{j-1:k}) \ o \ (G_{k-1:l}, \ P_{k-1:l})] \ o \ (G_{l-1:m}, \ P_{l-1:m})\}$

$\{(G_{i:j}, P_{i:j}) \ o \ [(G_{j-1:k}, P_{j-1:k}) \ o \ (G_{k-1:l}, P_{k-1:l})]\} \ o \ (G_{l-1:m}, P_{l-1:m})$

$\{[(G_{i:j}, P_{i:j}) \ o \ (G_{j-1:k}, P_{j-1:k})] \ o \ (G_{k-1:l}, P_{k-1:l})\} \ o \ (G_{l-1:m}, P_{l-1:m})$

$[(G_{i:j},\,P_{i:j})\;o\;(G_{j\text{-}1:k},\,P_{j\text{-}1:k})]\;o\;[(G_{k\text{-}1:l},\,P_{k\text{-}1:l})\;o\;(G_{l\text{-}1:m},\,P_{l\text{-}1:m})]$

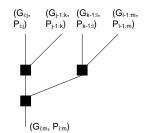

Figure 3.2: Valid Prefix Structure Synthesis.

track of  $2^0 = 1$ . But it requires the most logic levels among the prefix trees. For logic levels, a 16-bit Brent-Kung prefix tree has L = 4 and l = L - 1 = 3, which indicates a total of 7 logic levels is required. Kogge-Stone (0, 0, L - 1) prefix tree has the least logic levels and fan-out. However, the wire tracks is  $2^{L-1}$ , which is based on input width as L is logarithmically proportional to n. A 16-bit Kogge-Stone prefix tree has a maximum wire track of  $2^{4-1} = 8$  with a dense gate structure. Sklansky (0, L - 1, 0) prefix tree has the smallest number of logic levels and wiring tracks while the fan-out increases with wider inputs in the form of  $2^{L-1} + 1$ . A 16-bit Sklansky prefix tree has a maximum fan-out of  $2^{4-1} + 1 = 9$ . Knowles family (0, f, t) has the least logic levels whereas the fan-out and wire tracks depend on the specific structure. Like Kogge-stone, Knowles prefix tree family use a high density gate structure. Ladner-Fischer (L - 2, 1, 0) prefix tree targets at a fixed maximum fan-out which is  $2^1 + 1 = 3$ , compared to Sklansky prefix tree without too much compromise on logic levels. Han-Carlson (1, 0, L - 2) prefix tree reduces the gate density compared to Kogge-Stone prefix tree with one more extra logic level than minimum. Its wire tracks is logarithmically proportional to input width.

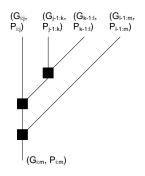

### 3.2.2 Synthesis Rules

The key operation in a prefix structure is described in Equation (3.4). To build a prefix structure, the key operation is that the " $\circ$ " in (3.4), which is associative but not commutative. That is, which two of the neighboring term comes to the " $\circ$ " operation does not matter but the sequence of the neighboring terms can not be altered. For example, consider the following operation.

$$(G_{i:m}, P_{i:m}) = (G_{i:j}, P_{i:j}) \circ (G_{j-1:k}, P_{j-1:k}) \circ (G_{k-1:l}, P_{k-1:l}) \circ (G_{l-1:m}, P_{l-1:m}), \quad (3.6)$$

Only the neighboring two terms can go through a " $\circ$ " operation. The sequence of the 4 terms on the right side of the equation can not be changed. The associativity, or the valid combination of the operations are shown in Figure 3.2.

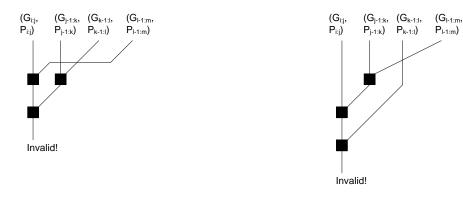

$[(G_{i:j},\,P_{i:j})\;o\;(G_{i\text{-}1:m},\,P_{i\text{-}1:m})]\;o\;[(G_{j\text{-}1:k},\,P_{j\text{-}1:k})\;o\;(G_{k\text{-}1:l},\,P_{k\text{-}1:l})]$

Figure 3.3: Invalid Prefix Structure Synthesis.

All the topologies in Figure 3.2 can be applied to building prefix structures. It can be observed that the last combination is the most efficient since it only take 2 logic levels while the other takes 3. This will be further discussed in the following sections.

Altering the order of the terms is not allowed because it will introduce invalid result. Two examples of invalid operations are shown in Figure 3.3.

# 3.2.3 Preparing Prefix Tree

The synthesis rules apply to any type of prefix tree. In this section, the methodology utilized to build fixed prefix structures is discussed. Moreover, procedure to build fixed prefix tree can be adapted to building non-fixed prefix tree with a slight modification.

In general, building prefix trees can be reduced to solving the following problems.

- How to align the bit lines.

- Where to place cells that compute group generate G and propagate P, i.e. black cells in this case (gray cells are ignored here to simplify the discussion.).

- How to connect input/output of the cells.

The solutions are based on the numbers which are power of 2 as both of the locations of the cells and wires can be related to those numbers.

To solve the problems, 3 terms are defined.

- *llevel*: logic level;

- *u*: maximum output bit span;

- *v*: maximum input bit span;

The *llevel* refers to the logic row where group generate G and propagate P are computed. u/v are the maximum output bit span and input bit span of the logic cells. If the logic level is not the last of the prefix tree, the output of the current logic level will be the input to the next logic level. The maximum bit span sets the limit of the bit span at a certain logic level. The relations between these terms are described by the following equations

$$u = 2^{llevel}$$

$$v = 2^{llevel-1}$$

(3.7)

The value of v is 1/2 of the value of u. To further ease the illustration, the term  $(G_{i:m}, P_{i:m})$  is briefed as  $GP_{i:m}$ . For example,

$$GP_{6:3} = GP_{6:5} \circ GP_{4:3} \tag{3.8}$$

which is equal to

$$G_{6:3} = G_{6:5} + P_{6:5} \cdot G_{4:3}$$

$$P_{6:3} = P_{6:5} \cdot P_{4:3}$$

(3.9)

For this case, llevel = 2, u = 4, v = 2. The inputs are  $GP_{6:3}$  and  $GP_{4:3}$  that have a bit span of 2, as the subscripts of GP indicate. The output is  $GP_{6:3}$ , which has a bit span of 4.

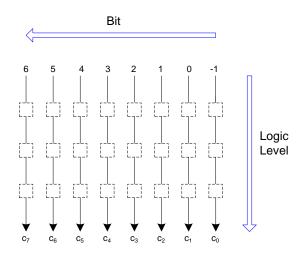

Figure 3.4 shows an 8-bit example of an empty matrix with only bit lines and dashed boxes filled in. The inputs  $g_i/p_i$  go from the top and the outputs  $c_i$  are at the bottom. The LSB is labeled as -1 where the carry-input  $(c_{in})$  locates. The objective is to obtain all  $c_i$ 's in the form of  $G_{i-1:-1}$ 's, where  $c_0 = G_{-1:-1}, c_1 = G_{0:-1}, c_2 = G_{1:-1}, ..., c_{n-1} = G_{n-2:-1}$

Figure 3.4: 8-bit Empty Prefix Tree.

Figure 3.5: Build 8-bit Sklansky Prefix Tree: Step 1.

Figure 3.6: Build 8-bit Sklansky Prefix Tree: Step 2.

The way of building a prefix tree can be processed as the arrows indicate (i.e. from LSB to MSB horizontally and then from top logic level down to bottom logic level vertically).

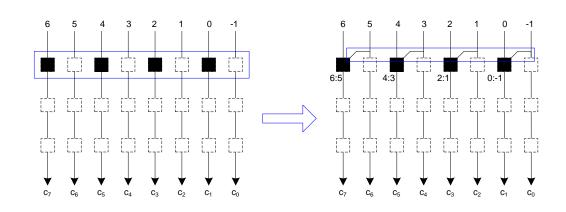

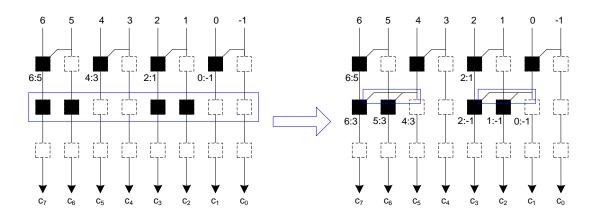

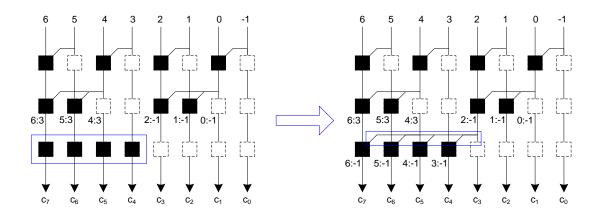

Next, the empty matrix will be filled to compose a Sklansky prefix tree. In the first logic level, black cells are filled every other bit, which means the neighboring 2 bits will be the input to only one black cell. (For example, Kogge-Stone prefix trees, the  $g_i/p_i$  will be the input to 2 black cells.) This complies with the term mentioned above (i.e. maximum input span is 1 bit and maximum output span is  $2^1 = 2$  bits). The inter-connect can be wired according the the location of the black cell and the maximum output span. The process is shown in Figure 3.5 as step 1.

The 2nd logic level can be continued, such that the black cells are placed as step 2 shown in Figure 3.6. Two black cells are grouped together and the distance between the neighboring group is 2 bits (i.e. 2 empty bit slots). The maximum input span is 2 bits and the maximum output span is  $2^2 = 4$  bits, e.g.  $GP_{6:3}$ . In this level, the maximum fan-out is 3.

The similar fashion applies to logic level 3, where black cells are placed in a group of 4. The distance between the neighboring group is supposed to be 4 bits. As this is a 8-bit example, there exists only one such group. The maximum input span is 4 bits and the maximum output span is  $2^3 = 8$  bits, e.g.  $G_{6:-1}$ . In this logic level, the maximum fan-out increases to 5. Finally, the prefix tree is complete when the tree computes all the carry-out

Figure 3.7: Build 8-bit Sklansky Prefix Tree: Step 3.

bits.

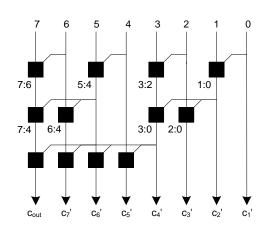

The example shown in Figure 3.7 is an 8-bit Sklansky prefix tree. Other types of prefix trees can be built following the similar procedure by utilizing the bit span and black cell placement according to the specific structure requirement. In the following sections, building several fixed prefix trees will be discussed with pseudo-code and examples given.

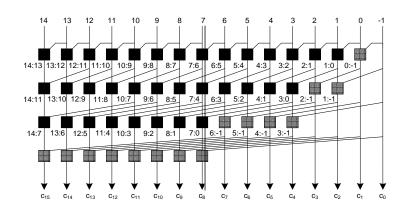

# 3.2.4 Kogge-Stone Prefix Tree

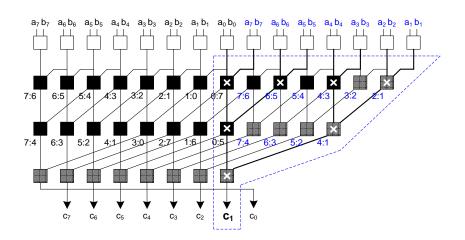

Kogge-Stone prefix tree is among the type of prefix trees that use the fewest logic levels. A 16-bit example is shown in Figure 3.8. In fact, Kogge-Stone is a member of Knowles prefix tree 3.10. The 16-bit prefix tree can be viewed as Knowels [1,1,1,1]. The numbers in the brackets represent the maximum branch fan-out at each logic level. The maximum fan-out is 2 in all logic levels for all width Kogge-Stone prefix trees.

The key of building a prefix tree is how to implement Equation (3.2) according to the specific features of that type of prefix tree and apply the rules described in the previous section. Gray cells are inserted similar to black cells except that the gray cells final output carry outs instead of intermediate G/P group. The reason of starting with Kogge-Stone prefix tree is that it is the easiest to build in terms of using a program concept. The example in Figure 3.8 is 16-bit (a power of 2) prefix tree. It is not difficult to extend the structure to any width if the basics are strictly followed.

Figure 3.8: 16-bit Kogge-Stone Prefix Tree.

For the Kogge-Stone prefix tree, at the logic level 1, the inputs span is 1 bit (e.g. group (4:3) take the inputs at bit 4 and bit 3). Group (4:3) will be taken as inputs and combined with group (6:5) to generate group (6:3) at logic level 2. Group (6:3) will be taken as inputs and combined with group (10:7) to generate group (10:3) at logic level 3, and so on so forth. With this inspection, the structure can be described with the Algorithm 3.1 listed below.

| Algorithm 3.1 Building Kogge-Stone Prefix Tree               |  |  |  |  |  |

|--------------------------------------------------------------|--|--|--|--|--|

| $L = log_2(n);$                                              |  |  |  |  |  |

| for $llevel = 1$ ; $llevel \le L$ ; $llevel + + \mathbf{do}$ |  |  |  |  |  |

| $u = 2^{llevel};$ {output bit span}                          |  |  |  |  |  |

| $v = 2^{llevel-1};$ {input bit span}                         |  |  |  |  |  |

| for $i = v - 1; i < n - 1; i + + do$                         |  |  |  |  |  |

| $GP_{i:i-u+1} = (GP_{i:i-v+1}) \circ (GP_{i-v:i-u+1});$      |  |  |  |  |  |

| end for                                                      |  |  |  |  |  |

| end for                                                      |  |  |  |  |  |

In Algorithm 3.1, the number of logic levels is calculated first. At each logic level, the maximum input bit span and maximum output bit span are computed. Equation (3.2) is applied in the inner loop, where bit goes from bit v - 1 though bit n - 1. If any of the subscript goes less than -1, the value stays at -1. This means there is no crossing over bit

| Logic  | u  | v | Output    | Input1                  |                     | Equation                                 |

|--------|----|---|-----------|-------------------------|---------------------|------------------------------------------|

| Levels |    |   | (i:i-u+1) | $(i\!:\!i\!-\!v\!+\!1)$ | (i - v : i - u + 1) | Mapping                                  |

| 1      | 2  | 1 | 7:6       | 7:7                     | 6:6                 | $GP_{7:6} = GP_7 \circ GP_6$             |

| 2      | 4  | 2 | 11:8      | 11:10                   | 9:8                 | $GP_{11:8} = GP_{11:10} \circ GP_{9:8}$  |

| 3      | 8  | 4 | 14:7      | 14:11                   | 10:7                | $GP_{14:7} = GP_{14:11} \circ GP_{10:7}$ |

| 4      | 16 | 8 | 7:-1      | 7:0                     | -1:-1               | $GP_{7:-1} = GP_{7:0} \circ GP_{-1}$     |

Table 3.1: Verifying the Pseudo-Code of Building a Kogge-Stone Prefix Tree

-1, or the LSB boundary.

The statement in the inner *for* loop is applying Equation (3.2). The validity of this implementation can be verified by looking at Table 3.1. In the table, one group operation is randomly selected at each logic level. Other operations can be verified by inserting the numbers as listed in Table 3.1. The term  $GP_{i:i} = GP_i$  and LSB boundary of the inputs/outputs is bit -1. Table 3.1 can also be matched against Figure 3.8 to see the correspondence.

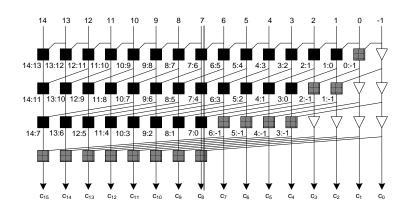

The pseudo-code is a simplified version of the exact program. In the real program, the code should tell where are the black cells and gray cells. The program also needs control so that the LSB never goes beyond -1 and utilizes optional buffers. In Figure 3.8, there are fan-outs more than 2 because the structure is not buffered. Figure 3.9 shows a buffered 16-bit prefix tree, however, the exact number of buffers is based on the capacitance and resistance of the interconnect network [46]. Both figures indicate a wire track of 8.

The algorithmic delay is simply the number of logic levels. The area can be estimated as the number of cells in the prefix tree. To simply the calculation, all cells are counted as black cells. To understand this structure, remember that the number of gray cells always equals to n - 1 since the prefix tree only outputs n - 1 carries. A black cell has one more AND gate than a gray cell, and therefore, a more accurate area estimation will just subtract that n - 1 AND gates.

Figure 3.9: 16-bit Kogge-Stone Prefix Tree with Buffers.

The number cells for a Kogge-Stone prefix tree can be counted as follows. Each logic level has n - m cells, where  $m = 2^{llevel-1}$ . That is, each logic level is missing m cells. That number is the sum of a geometric series starting from 1 to n/2 which totals to n - 1. The total number of cells will be  $nlog_2n$  subtracting the total number of cells missing at each logic level, which winds up with  $nlog_2n - n + 1$ . When n = 16, the area is estimated as 49.

#### 3.2.5 Knowles Prefix Tree