# A 700mV LOW POWER LOW NOISE IMPLANTABLE NEURAL RECORDING

### SYSTEM DESIGN

By

GUANGLEI AN

Bachelor of Engineering JiLin University Changchun, JiLin 2004

Master of Science ChongQing University of Post and Telecommunication ChongQing, ChongQing 2007

> Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY December, 2014

# A 700mV LOW POWER LOW NOISE IMPLANTABLE NEURAL RECORDING SYSTEM DESIGN

Dissertation Approved:

Dr. Chris Hutchens

Dissertation Adviser

Dr. Louis G. Johnson

Dr. James Stine

Dr. Ning Wang

Outside Committee Member

#### ACKNOWLEDGEMENTS

First of all, I would like to thank my thesis advisor, Professor Chris Hutchens, for his support and encouragement throughout my graduate school years. I am grateful to him for all his efforts in teaching me, challenging me to achieve the highest standards and guiding me in my professional career. He gave me the freedom to explore new ideas, tolerated my mistakes and supported my efforts. I also highly value the overall professional experience he provided by involving me in activities that go beyond the thesis, such as presenting at meetings, attending workshops and conferences, leading collaborations and contributing to grant proposals. I sincerely thank him for working so hard to provide this environment for my graduate studies.

I am greatly indebted to Dr. Xunyun Zhu for being my mentor and manager during my intern work at Intergreen. He is the one who guided me to the design and measurements of ADC and DAC. His support and guidance are vital to my PhD research. I also want to extend my gratitude to Shuxin Cao for discussions about circuit design.

I would like to thank Dr. Louis G. Johnson, Dr. James Stine and Dr. Ning Wang for serving on my committee. I am heartily thankful to them for reviewing my work, sharing their thoughts and giving me helpful suggestions.

The members of the MSVLSI Group have been providing me countless help which is benefit for me very much. Many thanks go to Zhe Yuan, Vijay Madhuravasal, Srinivas Venkataraman, Yohannes Worku, Rehan Ahmed, Naresh Anne, Ran Liao, Cheng Hao, De Kanishka and those who graduated before me but left valuable documentations.

At last, I want to thank my wife Qinyue Pan for her unconditional love and support.

Acknowledgements reflect the views of the author and are not endorsed by committee members or Oklahoma State University.

### Name: Guanglei An

### Date of Degree: DECEMBER, 2014

### Title of Study: A 700mV LOW POWER LOW NOISE IMPLANTABLE NEURAL

### **RECORDING SYSTEM DESIGN**

### Major Field: Electrical and Computer Engineering

Abstract: This dissertation presents the work for design and implementation of a low power, low noise neural recording system consisting of Bandpass Amplifier and Pipelined Analog to Digital Converter (ADC) for recording neural signal activities. A low power, low noise two stage neural amplifier for use in an intelligent Radio-Frequency Identification (RFID) based on Operational Transconductance Amplifier (OTA) is utilized to amplify the neural signals. The optimization of the number of amplifier stages is discussed to achieve the minimum power and area consumption. The amplifier power supply is 0.7V. The midband gain of amplifier is 58.4dB with a 3dB bandwidth from 0.71 to 8.26 kHz. Measured input-referred noise and total power consumption are 20.7µVrms and 1.90 µW respectively. The measured result shows that the optimizing the number of stages can achieve lower power consumption and demonstrates the neural amplifier's suitability for instu neutral activity recording. The advantage of power consumption of Pipelined ADC over Successive Approximation Register (SAR) ADC and Delta-Sigma ADC is discussed. An 8 bit fully differential (FD) Pipeline ADC for use in a smart RFID is presented in this dissertation. The Multiplying Digital to Analog Converter (MDAC) utilizes a novel cancellation technique robust to device leakage to reduce the input drift voltage. Simulation results of static and dynamic performance show this low power Pipeline ADC is suitable for multi-channel neural recording applications. The performance of all proposed building blocks is verified through test chips fabricated in IBM 180nm CMOS process. Both bench-top and real animal test results demonstrate the system's capability of recording neural signals for neural spike detection.

### TABLE OF CONTENTS

| Chapter                                             | Page |

|-----------------------------------------------------|------|

| 1. INTRODUCTION                                     | 1    |

| 1.1 Background and Motivation                       | 1    |

| 1.2 Literature Review.                              |      |

| 1.3 Research Objective1.4 Thesis Organization       | 13   |

|                                                     |      |

| 2. REVIEW OF OTA/OPAMP TOPOLOGOIES, THEIR DESIGN IN |      |

| SUBTHRESHOLD AND APPLICATION TO BP AMPLIFIER DESIGN | 18   |

| 2.1 Telescopic OTA                                  | 20   |

| 2.1 Telescopic UTA                                             | 20 |

|----------------------------------------------------------------|----|

| 2.2 Folded Cascode OTA                                         | 21 |

| 2.3 Two stage opamp with Miller compensation                   | 23 |

| 2.4 Two stage opamp with indirect compensation                 |    |

| 2.5 Two stage opamp with split length transistors compensation | 26 |

| 2.6 Two stage opamp with Miller p-z cancellation               |    |

| 2.7 Sarpeshkar's modified OTA                                  | 29 |

| 2.8 Neural amplifier design                                    | 34 |

| 2.8.10ptimal stages for Power consumption, Area and Gain       | 34 |

| 2.8.2 Noise Analysis and Sizing                                | 37 |

| 2.9 Performance Summary of Neural Amplifier                    | 42 |

| 2.10 Conclusion                                                | 43 |

| 3. REVIEW OF ADC POWER CONSUMPTION AND PIPELINED ADC DESIGN    | 11 |

| DESIGN                                                         |    |

| 3.1 ADC power consumption comparison                           | 45 |

| 3.1.1 Pipelined ADC power consumption                          | 45 |

| 3.1.2 Sigma-Delta ADC power consumption                        | 47 |

| 3.1.3 SAR ADC power consumption                                |    |

| 3.2 Pipelined ADC design                                       |    |

| 3.2.1 1.5 bit MDAC with low input drift voltage                | 52 |

| 3.2.2Self-timing static comparator                             |    |

| 3.2.3 Bootstrapped Switch                                      |    |

| 3.3 MDAC Errors                                                | 57 |

| 3.3.1 Finite OTA gain error          | 57 |

|--------------------------------------|----|

| 3.3.2 Finite OTA bandwidth           |    |

| 3.3.3 Capacitor mismatch             | 62 |

| 3.3.4 Noise in MDAC                  | 63 |

| 3.4 Pipelined ADC simulation results | 65 |

| 3.5 Conclusion                       | 68 |

| 4. MEASUREMENT RESULTS            | 69 |

|-----------------------------------|----|

| 4.1 Neural amplifier test results | 69 |

| 4.1.1 BP1 test results            |    |

| 4.1.2 BP2 test results            | 72 |

| 4.1.3 BP1&2 test results          | 74 |

| 4.2 Pipelined ADC test results    |    |

| 4.2.1 2.5 bit MDAC test results   |    |

| 4.2.2 1.5 bit MDAC test results   |    |

| 4.3 Conclusion                    |    |

| 5. CONCLUSION   |  |

|-----------------|--|

| 5.1 Summary     |  |

| 5.2 Future work |  |

|                 |  |

| REFERENCE | ) | ] | L |

|-----------|---|---|---|

|-----------|---|---|---|

### LIST OF TABLES

### Table

# Page

| 1.1 Survey of existing work in neural interface SoC                     | 14 |

|-------------------------------------------------------------------------|----|

| 1.2 Performances of Neural Amplifiers                                   | 15 |

| 2.1 Comparison of Performance of OTA/Opamps                             |    |

| 2.2 Comparisons of two stage opamps with telescopic, folded cascode and |    |

| Sarpeshkar's modified OTA input stage                                   | 33 |

| 2.3 Noise contribution of transistors in first OTA                      |    |

| 2.4 Geometries of transistors in first and second OTA/opamp             | 41 |

| 2.5 Simulated Performance of Neural Amplifier                           | 42 |

| 3.1 Power Consumption Comparison of three ADCs                          | 51 |

| 3.2 Settling error and Differential error of MDAC                       | 54 |

| 3.3 ADC Performance                                                     | 68 |

| 4.1 Performance summary of BP amplifiers                                | 76 |

| 4.2 Output signal amplitudes of BP amplifiers                           | 78 |

| 4.3 2.5 bit MDAC transfer function                                      | 83 |

| 4.4 2.5 bit MDAC errors                                                 | 84 |

| 4.5 1.5 bit MDAC transfer function                                      | 86 |

| 4.6 1.5 bit MDAC errors                                                 | 87 |

| 4.7 Performance comparisons with existing neural interface              | 87 |

|                                                                         |    |

### LIST OF FIGURES

# Figure

# Page

| 1.1 Microphotograph of a low power low voltage neural recording Chip        |    |

|-----------------------------------------------------------------------------|----|

| 1.2 Schematic of Harrison's neural amplifier                                | 5  |

| 1.3 Schematic of Sarpeshkar's BP amplifier                                  | 6  |

| 1.4 Schematic of Sarpeshkar's low-noise OTA                                 | 8  |

| 1.5 Schematic of Ming Yin's BP amplifier                                    | 9  |

| 1.6 Schematic of Sitong's BP amplifier                                      | 10 |

| 1.7 The penny-size microsystem implemented on the platform                  | 11 |

| 1.8 Mixed-signal feedback architecture                                      | 12 |

| 1.9 Proposed architecture of proof-of-concept system for activity-dependent |    |

| ICMS.                                                                       | 13 |

| 1.10 Block diagram of system                                                | 14 |

| 1.11 Block diagram of the neural recording system                           | 16 |

| 2.1 Schematic of Telescopic OTA                                             | 20 |

| 2.2 Schematic of folded cascode OTA                                         | 22 |

| 2.3 Schematic of two stage opamp with Miller compensation                   | 23 |

| 2.4 Schematic of two stage opamp with indirect compensation                 |    |

| 2.5 Schematic of two stage opamp with split length transistors compensation | 26 |

| 2.6 Schematic of two stage opamp with Miller p-z compensation               | 28 |

| 2.7 Simulated and measured subthreshold current                             | 32 |

| 2.8 System block diagram, first stage with current programmable band pass   |    |

| function and stage two gain function                                        | 34 |

| 2.9 Plot of normalized power area product for different number of stages    | 37 |

| 2.10 Schematic diagram of stage one OTA with its common mode feedback       |    |

| circuit                                                                     | 37 |

| 2.10 Schematic diagram of stage two opamp with its common mode feedback     |    |

| circuit                                                                     | 39 |

| 2.11 Schematic diagram of stage second opamp with its common mode feedback  |    |

| circuit                                                                     | 40 |

| 2.12 Simulated frequency response of two stage neural amplifier             | 42 |

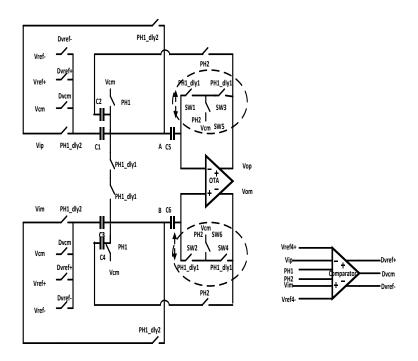

| 3.1 Schematic of 1.5 bit MDAC                                               | 45 |

| 3.2 Schematic of two stage opamp with split length transistors compensation | 45 |

| 3.3 Switched-capacitor implementation of an integrator                      | 48 |

| 3.4 Schematic of SAR ADC                                                    |    |

| 3.5 Block Diagram of Pipelined ADC                                          | 52 |

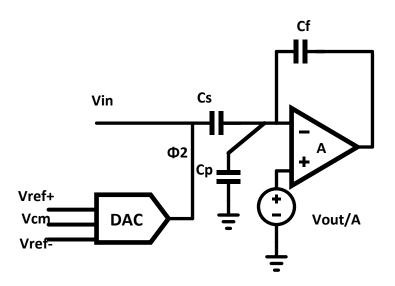

| 3.6 Proposed 1.5 bit MDAC architecture                                      |    |

# Figure

# Page

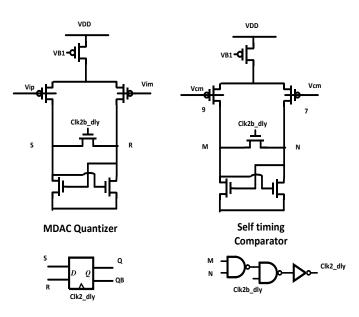

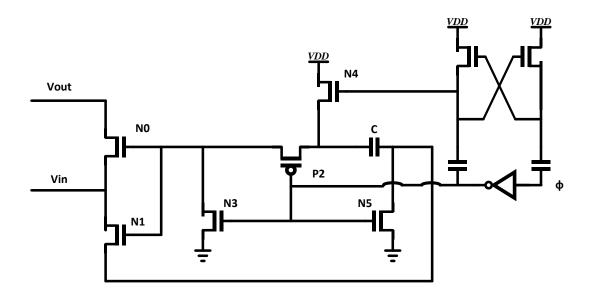

| 3.7 Schematic of self-timing static latched comparator                       | 54  |

|------------------------------------------------------------------------------|-----|

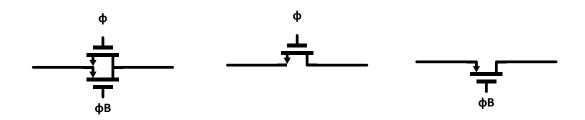

| 3.8 MOS switches                                                             |     |

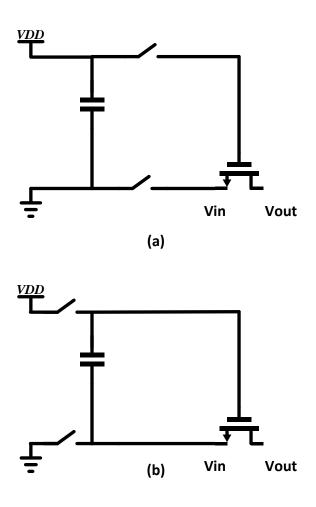

| 3.9 Operation of bootstrapped switch                                         | 56  |

| 3.10 Schematic of bootstrapped switch                                        | 57  |

| 3.11 1.5 bit MDAC in amplifying phase                                        | 58  |

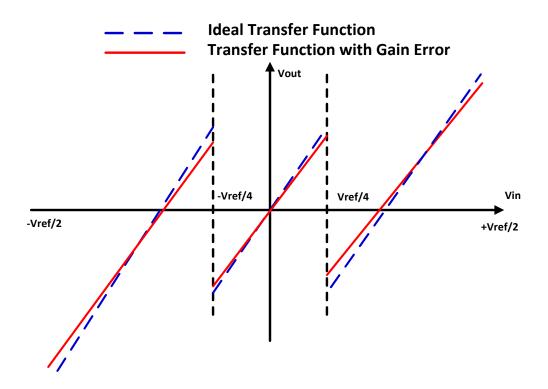

| 3.12 Finite gain effect on 1.5 bit MDAC transfer function                    |     |

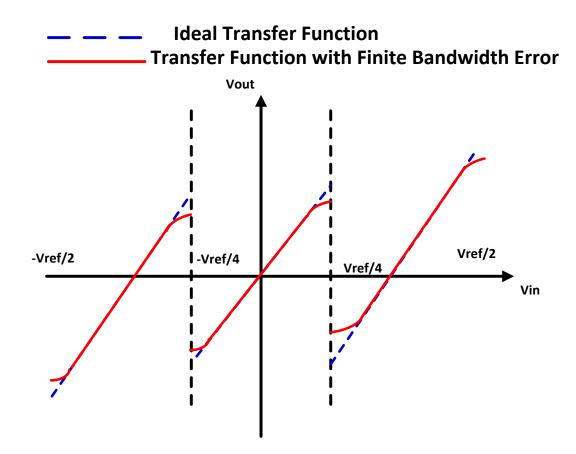

| 3.13 Finite OTA bandwidth effect on 1.5 bit MDAC transfer function           | 61  |

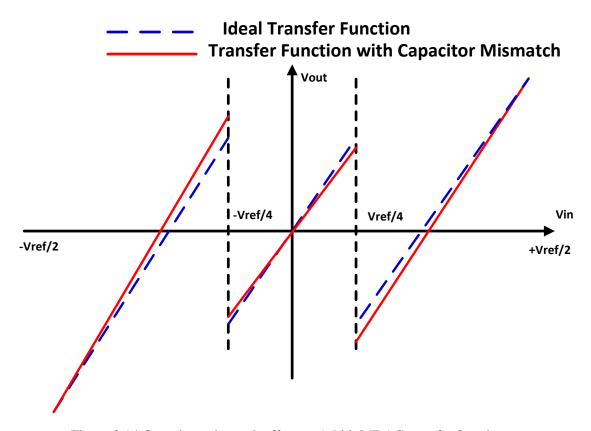

| 3.14 Capacitor mismatch effect on 1.5 bit MDAC transfer function             | 63  |

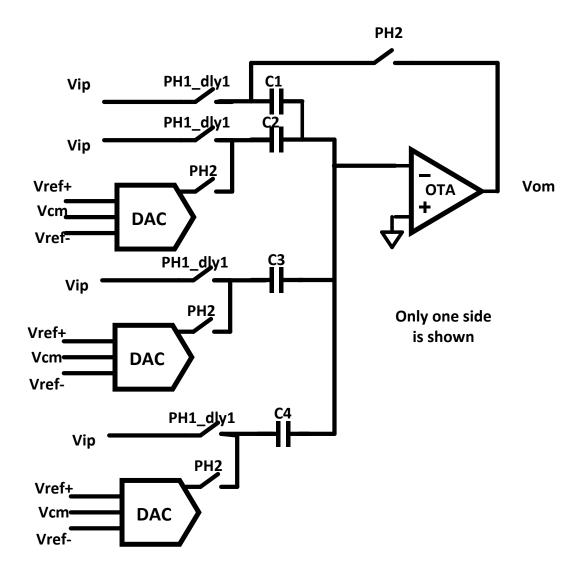

| 3.15 2.5 bit MDAC                                                            |     |

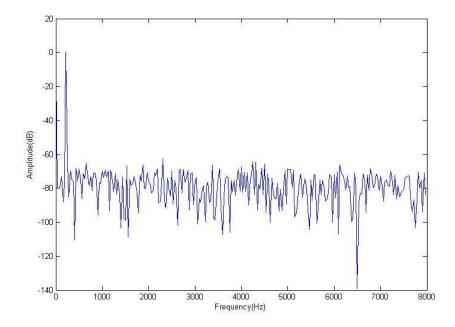

| 3.16 Simulated ADC Output FFT Spectrum Input@218Hz                           | 65  |

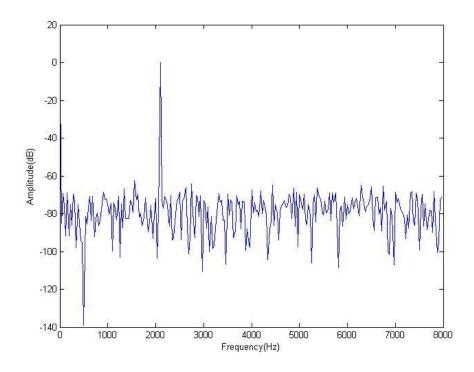

| 3.17 Simulated ADC Output FFT Spectrum Input@2.1kHz                          | 66  |

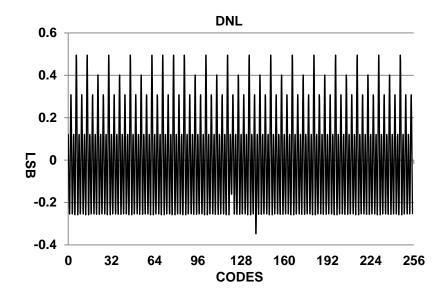

| 3.18 Simulated DNL                                                           | 67  |

| 3.19 Simulated INL                                                           | 67  |

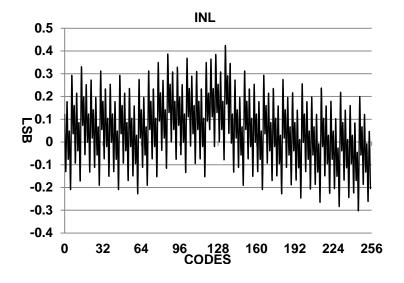

| 4.1 Die picture of bandpass amplifiers                                       | 70  |

| 4.2 Test set up for bandpass amplifiers                                      |     |

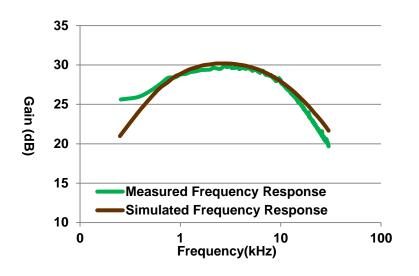

| 4.3 Simulated and measured frequency response of BP1                         | 71  |

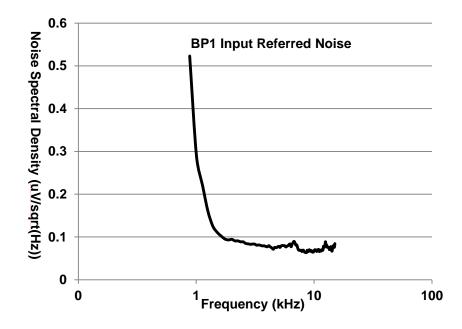

| 4.4 Measured input referred noise of BP1                                     | 71  |

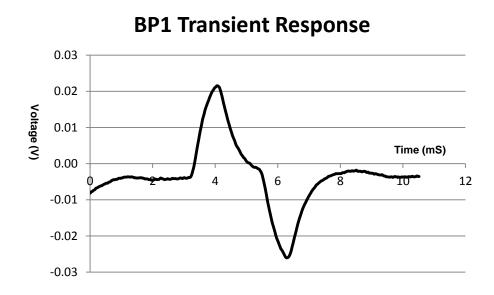

| 4.5 BP1 transient response                                                   |     |

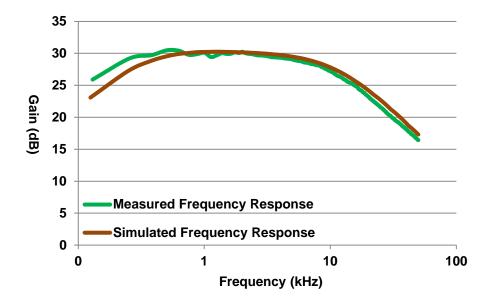

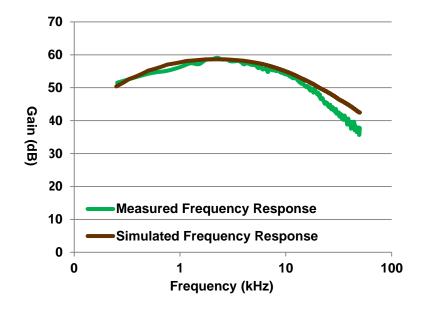

| 4.6 Simulated and Measured Frequency Response of BP2                         |     |

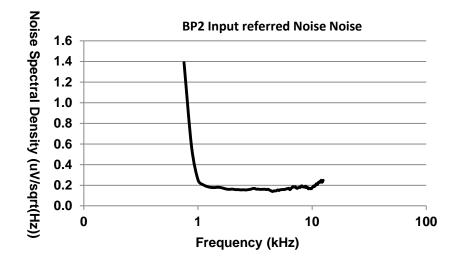

| 4.7 Measured Input Referred Noise of BP2                                     | 73  |

| 4.8 Simulated and Measured Frequency Response of BP1&2                       | 74  |

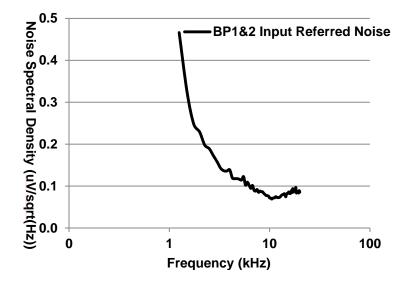

| 4.9 Measured Input Referred Noise of BP1&2                                   | 74  |

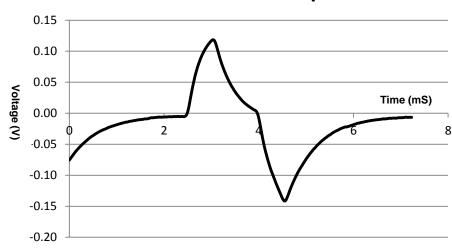

| 4.10 BP1&2 transient response                                                |     |

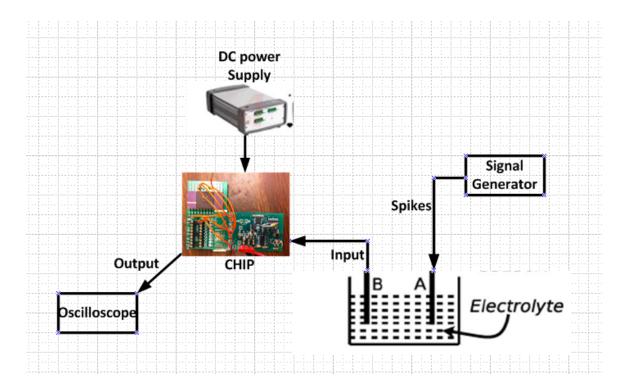

| 4.11 Experimental setup for saline test of BP amplifier                      | 77  |

| 4.12 Saline solution test setup for BP amplifier                             | 77  |

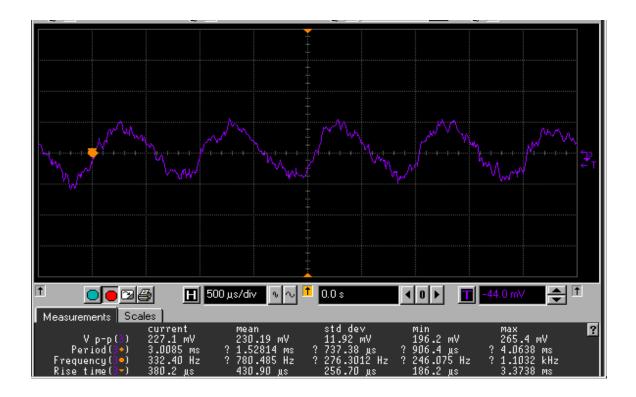

| 4.13 Output sinusoid signal when sensed input equals 240uV@1kHz in saline    |     |

| solution                                                                     |     |

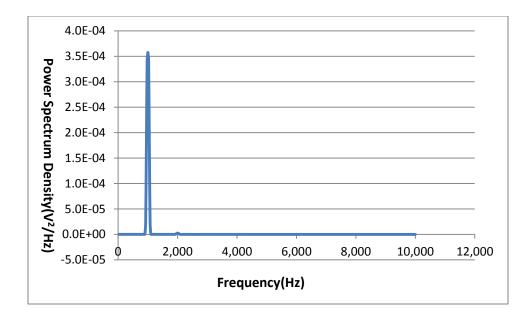

| 4.14 Output signal spectrum when sinusoid signal input is sensed             |     |

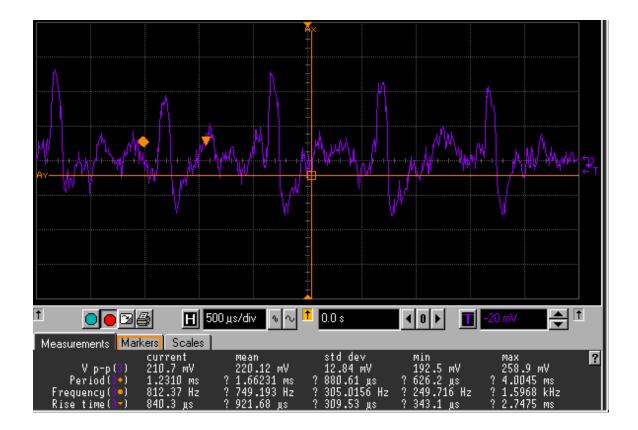

| 4.15 Sensed output pulse signal when sensed pulsed input equals 200uV@1kHz i | in  |

| saline solution                                                              |     |

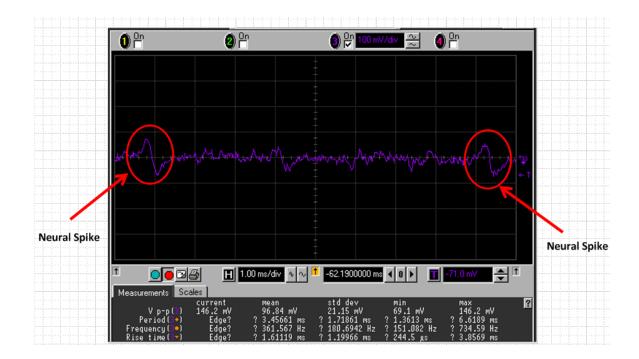

| 4.16 Recorded data from rats                                                 |     |

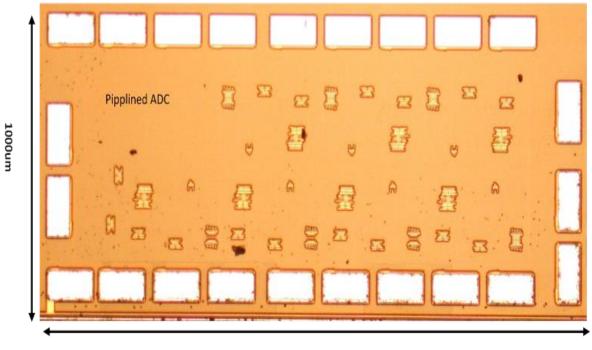

| 4.17 Die for 8 bit Pipelined ADC                                             | 81  |

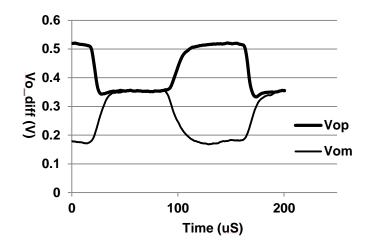

| 4.18 2.5 bit MDAC transient response                                         | 81  |

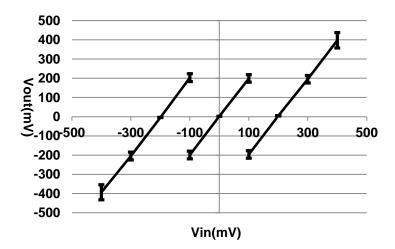

| 4.19 2.5 bit MDAC transfer function                                          | 82  |

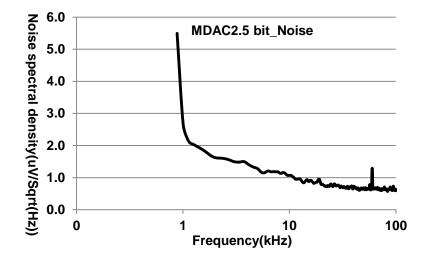

| 4.20 Measured noise of 2.5 bit MDAC                                          | 83  |

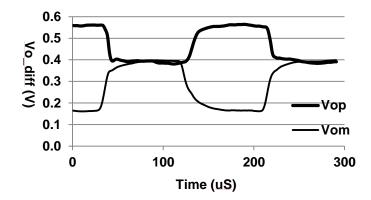

| 4.21 1.5 bit MDAC transient response                                         | 85  |

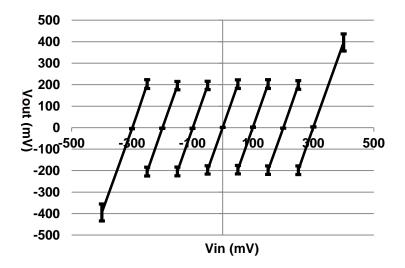

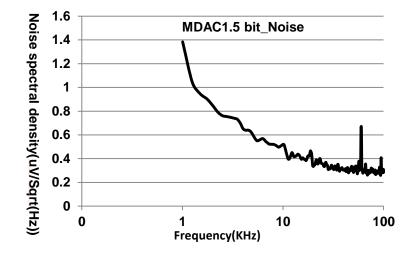

| 4.22 1.5 bit MDAC transfer function                                          |     |

| 4.23 Measured noise of 1.5 bit MDAC                                          | .86 |

### GLOSSARY

### Abbreviations:

| RF   | - | Radio Frequency                              |

|------|---|----------------------------------------------|

| INI3 | - | Integrated Neural Interface 3                |

| FSK  | - | Frequency-shift keying                       |

| ADC  | - | Analog to Digital Converter                  |

| PMOS | - | P- type Metal Oxide Semiconductor            |

| ΟΤΑ  | - | Operational Transconductance Amplifier       |

| NEF  | - | Noise Efficiency Factor                      |

| MOS  | - | Metal Oxide Semiconductor                    |

| NMOS | - | N- type Metal Oxide Semiconductor            |

| BP   | - | Bandpass Amplifier                           |

| ASIC | - | Application Specific Integrated Circuit      |

| ICMS | - | Intracortical Microstimulation               |

| SoC  | - | System-on-chip                               |

| SAR  | - | Successive Approximation Register            |

| RFID | - | Radio Frequency Identification               |

| IC   | - | Integrated Circuit                           |

| EPC  | - | Electronic Product Code                      |

| WISP | - | Wireless Identification and Sensing Platform |

| RAM  | - | Random-access Memory                         |

| CMOS | - | Complementary Metal Oxide Semiconductor      |

| PWM  | - | Pulse-width Modulation                       |

| PSK  | - | Phase-shift Keying                           |

| PLL     | - | Phase Lock Loop                         |

|---------|---|-----------------------------------------|

| LDO     | - | Low-dropout regulator                   |

| RF-DC   | - | Radio Frequency to Direct Current       |

| EEG     | - | Electroencephalography                  |

| EMG     | - | Electromyography                        |

| ECG     | - | Electrocardiography                     |

| ID      | - | Identification                          |

| FOM     | - | Figure of Merit                         |

| MDAC    | - | Multiplying Digital-to-Analog Converter |

| GBP     | - | Gain Bandwidth Product                  |

| CMFB    | - | Common Mode Feedback                    |

| DAC     | - | Digital to Analog converter             |

| OSR     | - | Oversampling Times                      |

| СМ      | - | Common Mode                             |

| FD      | - | Fully Differential                      |

| CDS     | - | Correlated Double Sampling              |

| FFT     | - | Fast Fourier Transform                  |

| DNL     | - | Differential Nonlinearity               |

| INL     | - | Integral Nonlinearity                   |

| OCP     | - | Open-circuit Potential                  |

| PCB     | - | Printed Circuit Board                   |

| $V_{T}$ | - | Threshold Voltage                       |

| VLSI    | - | Very large scale integration            |

| DR      | - | Dynamic Range                           |

| ENOB    | - | Effective number of bits                |

| MIM     | - | Metal-Insulator-Metal                   |

### CHAPTER I

#### INTRODUCTION

This chapter consists of four main sections: motivation, literature review, system design and dissertation organization. Section 1.1 provides an introduction to implantable medical electronics. Section 1.2 reviews the various existing neural recording systems. Section 1.3 states the complete system design and section 1.4 discusses the dissertation organization.

#### 1.1 Motivation

Due to the rapid advancement of microelectronics and integrated circuits, compelling applications in both the scientific and medical monitoring of biosignals have created a demand for wireless, unobtrusive sensors to collect this data [1-3]. Commercial medical implants like artificial pacemakers, cochlear implants and vagus nerve stimulators are providing the common functions like measuring of physiological information or stimulating nerves as medical implant devices [4, 5]. Example biosignals include; temperature, blood pressure, Electrocardiogram, heart rate, blood glucose level, neural signals and neural activity. In scientific applications, measurements of biosignals assist researchers to observe and study complex biological systems and their interactions, the effect of various diseases, and associated research treatments. In clinical settings, these signals are used by the physician or patient to either detect disease at onset or assist in the administration of treatment [6-8].

Measurement of biosignals presents several challenges. 1) Most importantly, the sensor must be unobtrusive or transparent as practical to the user. This involves minimizing the size and weight of the sensor and batteries. 2) The mobile nature of applications requires the entire system to operate on a limited power budget. The sensors should consume minimal power to maximize the sensor lifespan [9-13]. A number of solutions have been proposed to power smart sensors for data collection and communication including; a small batteries, an inductive power link, energy harvesting (light, RF etc.) as well as in combination [14-20]. Unfortunately, battery-powered sensors suffer from short lifespan due to the size and weight constraints of the battery [21, 22]. Inductively-coupled devices suffer from short wireless range (on the order of cm) [23-25]. 3) A means of wireless data collection is necessary for scientific research, where data should be available in real-time, and for medical biosensors where data is otherwise inaccessible. Wired connections suffer from infection and seriously restrain freedom of movement. As a result wireless telemetries are essential to the design of system of mobile biological subjects [26, 27]. 4) Compatibility of the system with bandwidth or noise floor of neural amplifier programmable is also essential because of a wide range of monitoring objects.

In this dissertation, we focus on neural recording system design. Neural activities can be observed simultaneously in more details down to a single cell [10] and Neuromotor prostheses is used to assist those paralyzed individuals to restore the lost motor functions [11]. Many experiments in human subjects showed that control signals derived from clusters of neurons' spike activities can be applied to the control and use of a computer mouse, a keyboard and robotic arms [11-31].

These neural signals range from 50-500 uV. Their successful use requires that the input-referred noise to be less than 5-10 $\mu$ V [31], as a result there are major design challenges in developing very small low-power circuits while simultaneous achieving acceptable input-referred noise levels. Given allowed neural power constraints of less than 100uW [10-14], signal fidelity is limited by either capacitor matching or input referred noise. Capacitor mismatching error can be alleviated

by capacitor trimming and/or calibration techniques. Lower input referred noise is in direct conflict with low power performance. For chronic clinical applications where these devices may remain implanted for the life of the patient, another challenge is powering and communicating with these devices without the presence of wires or batteries.

#### 1.2 Literature Review

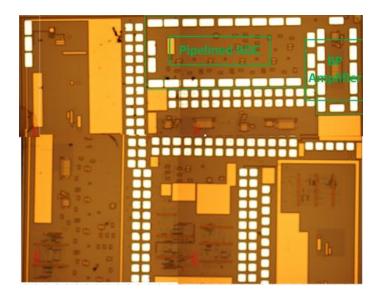

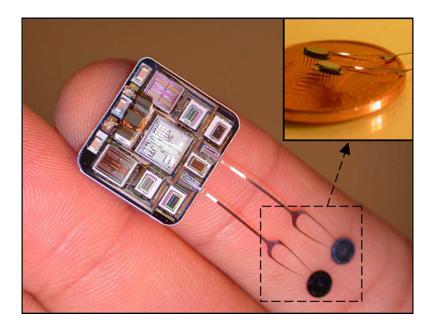

Many neural recording systems have been developed in the past years [14-31]. Harrison [14, 15] proposed a neural amplifier using a pseudoresistor as a high-resistance element and on-chip capacitors to amplify low frequency signals down to millihertz range. Most neural amplifiers [16-31] use Harrison's structure or a modification there of, differential to single ended or differential to differential modes. There is also a tradeoff between distortion and power in neural amplifier design. Sarpeshkar [16] presented an amplifier based on modified folded-cascode OTA structure replacing the degenerated MOS transistor current with a degenerated resistor. Ming [17] developed a programmable gain and bandwidth amplifier. Sitong [18] designed an alternative programmable bandwidth amplifier using current biased pseudo-resistor. A microphotograph of a low power low voltage neural recording chip is shown in Figure 1.1.

Fig.1.1 Microphotograph of a low power low voltage neural recording

Chip

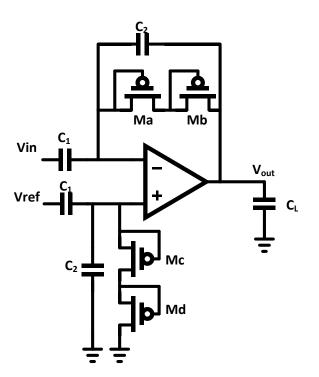

Harrison's group [14] integrated all the functionalities including neural signal amplification, data reduction, neural signal digitization, and wireless communication into a single chip. The system contains 100 neural recording channels and includes a wireless data transmission feature by a fully-integrated FSK (Frequency-shift keying) transmitter. The power and commands are transferred from an external unit to the implanted system via an inductive power link. The system utilizes a simple thresholding scheme with analog spike detection circuitry to reduce the amount of data needed to be transmitted and allow one raw analog channel to be selected for full digitization by a 10 bit resolution ADC (Analog to Digital Converter). The total power consumption of the system is 13.5mW. In Figure 1.2, a novel bioamplifier was designed and tested that uses a pseudoresistor element to amplify low-frequency signals down to the millihertz range while rejecting large dc offsets [15]. Transistors Ma-Md are acting as pseudo resistors. When Vgs is negative, each device functions as a diode connected PMOS transistor; when Vgs is positive, the parasitic source-well-drain p-n-p bipolar junction transistor is utilized to achieve extremely high resistor  $r_{inc}$ . For  $\Delta V < 0.2V$ ,  $r_{inc}$  is measured higher than  $10^{11}\Omega$ . The low frequency of amplifier is given by  $1/(2\pi r_{inc}C_2)$ . The amplifier uses a standard wide-output swing operational transconductance amplifier (OTA) with capacitive feedback to realize a gain of approximately 40 dB. The resulting amplifier passes signals from 0.025 Hz to 7.2 kHz with an input-referred noise of 2.2  $\text{uV}_{rms}$  and a power dissipation of 80 uW while consuming 0.16 mm<sup>2</sup> of chip area.

Figure 1.2 Schematic of Harrison's neural amplifier [15]

The tradeoff between power and noise is quantified with a NEF (noise efficiency factor). Where the NEF is given as:

$$NEF = V_{ni,rms} \sqrt{\frac{2I_{tot}}{\pi U_T * 4kT * BW}}$$

(1.1)

Where  $V_{ni,rms}$  is the input referred rms noise voltage,  $I_{tot}$  is the total amplifier supply current, and BW is the amplifier bandwidth. In weak inversion, the expression for NEF reduces to

$$NEF = \sqrt{\frac{4}{n^2}} \cong 2.9 \tag{1.2}$$

Assuming n=1.4, where n is the subthreshold slope factor. This is the theoretical NEF limit for amplifier with that circuit topology constructed, the current mirror ratios of unity are assumed. In

practice, the NEF will be limited by the ratios of other currents to differential pair current and 1/f noise.

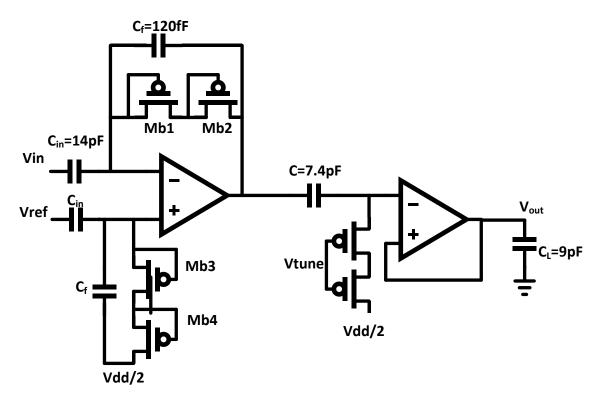

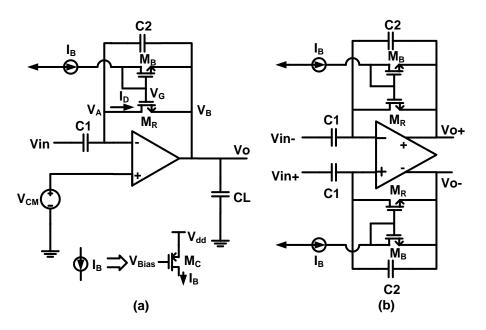

Sarpeshkar [16] shows that the minimum NEF for any existing amplifier topology using a differential pair as the input stage is equal to 2.02 for a typical value of n=1.4 by setting differential pair current dominates current of amplifier. Moreover, an NEF 2.67 is measured by using the modified folded-cascode OTA structure, which is in very close agreement with the theory. The Sarpeshkar's amplifier shown in Figure 1.3 yielded a midband gain of 40.8 dB and a 3-dB bandwidth from 45 Hz to 5.32 kHz; the amplifier's input-referred noise was measured to be  $3.06 \text{ uV}_{rms}$  while consuming 7.56 uW of power from a 2.8-V supply.

Figure 1.3 Schematic of Sarpeshkar's BP amplifier [16]

A modified version of a standard folded-cascode OTA topology with source-degenerated current mirrors achieves a very efficient power–noise tradeoff because it uses a new low-power low-noise OTA topology that makes efficient use of the supply current. The schematic of a modified

version of a folded cascaded topology low-noise OTA is shown in Figure 1.4. The current source is implemented by M5, M6 and source degeneration resistors R1 and R2. With an appropriate choice of degeneration resistors, the noise contributions of new current source are mainly from the resistors and can be made much smaller than the contributions from MOS transistors. The tradeoff of using resistors as current sources is the greater current (possible excessive) consumed by the differential pair, the area consumed by the resistors over the MOS transistors current sinks, reduced gain and power inefficiency.

Subthreshold noise current is  $\overline{i_n^2} = 2nkTg_m$ [32], n is slope factor, k is Boltzmann's constant, T is temperature, gm is transconductance.

M1 and M2 operate in weak inversion and M11 and M12 operate in strong inversion. The input referred noise spectral density of the OTA is

$$v_{n,1}^{2} = \frac{1}{g_{m1}^{2}} (2 * 2nkTg_{m1} + \frac{8kT}{R_{1}} + \frac{16}{3}kTg_{m11})$$

$$= \frac{1}{g_{m1}} 4nkT (1 + \frac{2U_{T}}{I_{1}R_{1}} + \frac{4}{3}k\alpha \frac{I_{11}}{I_{1}})$$

(1.3)

Where k=0.7 and  $\alpha = \frac{2}{(1 + \sqrt{1 + 4 * IC_{11}})} \approx 1$ , IC is the inversion coefficient of the transistor

which is defined as the ratio of its channel current to the moderate inversion characteristic current. Equation (1.3) suggests that  $I_1R_1$  should be large compared to  $2U_T$  and current ratio  $I_1/I_{11}$  should also be large. In the implementation, the second and third terms in (1.3) are 0.18 and 0.054. Then equation (1.3) reduces to

$$v_{n,1}^2 = \frac{4.94 * nkT}{g_{m1}} \tag{1.4}$$

Assuming the classical folded cascade amplifier is using P diff pair while P diff pair and P rail side devices have 1:1 current ratio. For folded cascode amplifiers the current noise spectral density is

$$i_{n,2}^{2} = 2 * 2nkTg_{m1} + 2 * 2nkTg_{mn} + 2 * 2nkTg_{mp}$$

(1.5)

Where  $gm_1$  is the transconductance of differential pair,  $gm_n$  is the transconductance of N rail side transistor and  $gm_p$  is the transconductance of P rail side transistor. Input referred noise spectral density is

$$v_{n,2}^{2} = \frac{i_{n}^{2}}{g_{m1}^{2}} = \frac{2*2nkT}{g_{m1}} + \frac{2*2nkTg_{mn}}{g_{m1}^{2}} + \frac{2*2nkTg_{mp}}{g_{m1}^{2}}$$

$$= \frac{4nkT}{g_{m1}}(1+2+1) = \frac{16nkT}{g_{m1}}$$

(1.6)

From (1.4) and (1.6) the input referred noise spectral density of Sarpeshkar's OTA is around 1/4 time as classical folded cascade amplifier which is more energy efficient topology.

Figure 1.4 Schematic of Sarpeshkar's low-noise OTA [16]

The schematic of Ming Yin's BP amplifier is shown is Figure 1.5. The amplifier current consumption is 8  $\mu$ A with a ±1.7 V supply, with two measured AC gains of 39.3 dB and 45.6 dB [17]. The measured input referred noise is 3.6  $\mu$ V over 20 Hz ~ 10 kHz. The low cutoff frequency is from 0.015 Hz to 700 Hz by varying the gate bias voltage of pseudo resistor. The high cutoff frequency is 4-bit programmable and can be adjusted from 120 Hz to 12 kHz at negligible load and 40 Hz to 4 kHz with a 2 pF active probe loading. The tunable high cutoff frequency is realized by two sets of PMOS and NMOS tail current transistors with gate enable bits B1-B4.

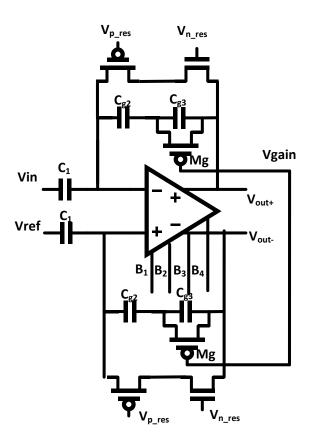

Figure 1.5 Schematic of Ming Yin's BP amplifier [17]

Figure 1.6 Schematic of Sitong's BP amplifier [18]

The schematic of Sitong's BP amplifier is shown in Figure 1.6 [18]. The bandwidth of this filter is from 500 Hz to 5 KHz. The power consumption is 0.6  $\mu$ W for a gain of 19.5 dB. The input referred noise is 67.7  $\mu$ Vrms with a power supply of 5 V. A current biased programmable pseudoresistor for implantable extracellular neural signal recording applications is introduced to reduce this feedback resistor variation. The pseudo-resistor, biased in the subthreshold operation, is able to realize a very large resistance while keeping the silicon area small. The lower cutoff frequency is tunable from tens of Hz to hundreds of Hz by offering a wide range of resistances implemented by log nature of the bias current. The effective resistance is given as:

$$R_{eq} = \frac{S_B U_T}{S_R I_B} \tag{1.7}$$

where  $S_B$  and  $S_R$  are the aspect ratios (W/L) of  $M_B$  and  $M_R$   $I_B$  is the bias current of  $M_B$ . Equation (1.7) shows that the effective resistance accuracy is limited by the matching between MR and MB and the accuracy of  $I_B$ .

Another system with 64 channels was reported by Sodagar in [19]. The penny-size microsystem implemented on the platform is shown in Figure 1.7. To record from 64 channels, the system utilizes four 16-channel neural preconditioning ASICs in parallel. The preconditioning ASICs are interfaced with a neural processing unit which consists of two 32-channel neural processing chips. The system also contains a bi-directional telemetry chip for transmitting neural data to the external world, and for receiving power, commands, and a clock to operate the implant. The recording front-end was characterized as having a mid-band gain of 59.5dB, an input referred noise of  $8\mu$ V, a tunable low frequency range from 0.1Hz to 100Hz and high cutoff frequency 9.1 kHz. The scan rate of the channel is 62.5kS/sec using 2MHz clock with the power dissipation of  $225\mu$ W/Ch.

Fig.1.7 The penny-size microsystem implemented on the platform in [19]

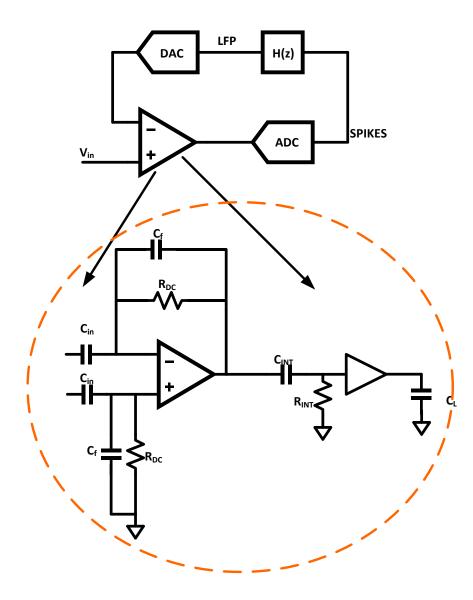

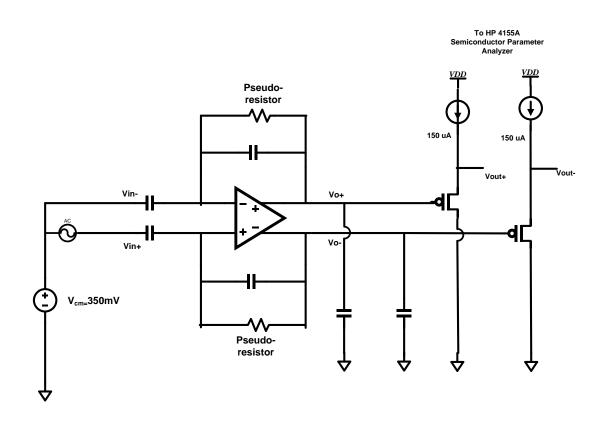

Rabaey [20] presents an area-efficient neural signal acquisition system in Figure 1.8 that uses digital blocks to reduce system area while operating on a power supply 0.5V. Replacing ac coupling capacitors and analog filters with a dual servo loop, the system is enables simultaneous digitization of the action and local field potentials. A noise efficient DAC and a compact sampling ADC are used to cancel input offset and prevent noise folding. The system consumes

5uW with input-referred noise of 4.9uV for a 10 kHz bandwidth. In order to reduce the dynamic range requirement of the instrumentation amplifier and ADC, the feedback of digital low-pass filter and DAC regenerate the sum of low-frequency components. The ADC is 8bit resolution and DAC performs 7 bit coarse offset cancellation.

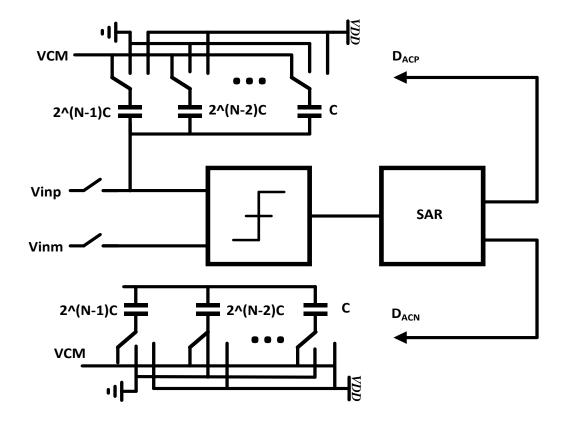

Figure 1.8 Mixed-signal feedback architecture in [20]

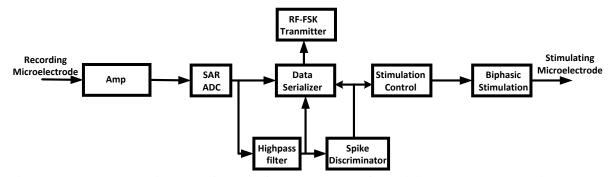

Mohseni [21] designed an activity-dependent intracortical microstimulation (ICMS) system-onchip (SoC) that converts the extracellular neural spikes to an electrical stimuli delivered to another region of the brain in real time in *vivo*. The proposed ICMS architecture is shown in Figure 1.9. The ICMS architecture incorporates two identical 4-channel modules and each consisting of; An analog recording front-end with a total input noise voltage of 3.12 uV and an NEF of 2.68 (Folded Cascode), consuming 5.9uW, an 10-bit successive approximation register analog-to-digital converters (SAR ADC) at 35.7 kS/Ch consuming 12.4uW with a digital spike discrimination processor, and a programmable constant-current microstimulating back-end that delivers up to 94.5 uA with 6-bit biphically stimulus to cortical tissue when triggered by neural activity.

Figure 1.9 Proposed architecture of proof-of-concept system for activity-dependent ICMS in [21]

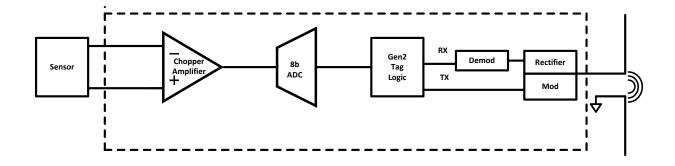

A number of full tag RFID (Radio Frequency Identification) implementations have been presented in the literature [9, 22-24]. Otis presented a fully-passive 900 MHz RFID tag IC (Integrated Circuit) with addressability, full EPC (Electronic Product Code) Class 1 Generation 2 (Gen2) protocol compatibility, a 1.25  $\mu$ V<sub>rms</sub> integrated noise chopper-stabilized micropower sensor interface amplifier from 0.05Hz to 100Hz, and an 8b ADC in [9]. The block of system is shown in Figure 1.10. An off-the-shelf RFID reader is enabling previously impossible recording scenarios like temperature and motor patterns of small insects with communication range 3 m.

Figure 1.10 Block diagram of system in [9]

| Work             | Application                          | Supply<br>Voltage<br>(V) | Midband<br>Gain<br>(dB) | Band<br>Width<br>(kHz) | Input<br>Referred<br>Noise<br>(µVrms) | NEF  | Total<br>Power<br>(µW) |

|------------------|--------------------------------------|--------------------------|-------------------------|------------------------|---------------------------------------|------|------------------------|

| Harrison [14]    | Neural recording                     | 3.3                      | 60                      | 5                      | 4.8                                   | 4.8  | 80                     |

| Azin [21]        | Neural<br>recording&<br>Stimulation  | 1.5                      | 51.9-65.6               | 12                     | 3.12                                  | 3.9  | 26.9                   |

| Zhiming [25]     | Neural recording                     | 0.8                      | 49                      | 6.2                    | 14                                    | 6.5  | 20                     |

| Walker [26]      | Neural<br>recording&<br>Stimulation  | 1.2                      | 40                      | 10                     | 2.2                                   | 4.5  | 43                     |

| M.Chae [27]      | Neural recording                     | ±1.65                    | 40                      | 20                     | 4.9                                   | 5.0  | 46.9                   |

| F.Shahrokhi [28] | Neural<br>recording &<br>Stimulation | 3                        | 73                      | 5                      | 6.08                                  | 5.55 | 15.52                  |

Table 1.1 Survey of existing work in neural interface SoC

Table 1.1 reviews the performance of existing research work in neural interface SoC. Extracellular action potentials signal amplitude range from  $50-500\mu$ V with most of neural activity between 0.1 Hz and 5 kHz [31]. Most neural amplifiers and ADC consume about  $100\mu$ W of power while attaining low input referred noise 5-10  $\mu$ V with a bandwidth of 5-10 kHz and the

background neural noise of recording site is 5-10  $\mu$ V [14-21]. The extracellular action potential is sensed by the electrode and amplified by the neural amplifier. The actual input voltage of the amplifier is determined by the impedance ratio of the electrode and amplifier's input impedance. The input impedance of neural amplifier should be high enough to keep the gain error low. The impedance of electrode used for neural recording could be as high as 1M $\Omega$  at 1K Hz [27], as a result the input impedance of neural amplifier needs to be at least a few M $\Omega$  at 1K Hz. Fully differential architectures are utilized to provide high common-mode rejection ratio (CMRR) and reduce the even harmonic distortion.

| Author         | Supply         | Midband      | Bandwidth  | Input             | Noise               | Total         |

|----------------|----------------|--------------|------------|-------------------|---------------------|---------------|

|                | Voltage<br>(V) | Gain<br>(dB) | (Hz)       | Referred<br>Noise | Effective<br>Factor | Power<br>(µW) |

|                |                | ()           |            | $(\mu V_{rms})$   |                     |               |

| [15]Harrison   | ±2.5           | 40           | 0.025-7.5k | 2.1               | 4.8                 | 80            |

| [16]Sarpeshkar | 2.8            | 40.85        | 45-5.32k   | 3.06              | 3.21                | 7.56          |

| [17]Yin        | 1.7            | 39.3-45.6    | 0.015-4k   | 3.6               | 4.9                 | 27.2          |

| [18]Sitong     | ±2.5           | 19.5         | 500-5k     | 67.7              | 9.5                 | 0.6           |

Table 1.2 Performances of Neural Amplifiers

Table 1.2 reviews the performance of existing neural amplifiers. Most amplifiers consumes less than 100  $\mu$ W power to achieve low input referred noise ( $<5\mu$ V<sub>rms</sub>) in the bandwidth 5-10k Hz [15-18].

#### 1.3 Research Objective

The many challenges associated with the design of a low power low noise implantable neural recording system include: 1) Efficient RF, thermal, or light power harvesting scheme are used to support signal conditioning bandpass amplifiers, ADC, system control and communications circuits [10-14]; 2) The implanted devices must not consume too much power due to the harmful effects to the surrounding tissue. Neural recording systems must consume less than 100uW [15-21]; 3) To achieve a large dynamic range, the total input referred noise from the recording circuit

less than 5-10 $\mu$ V [14-21]; 4) The input impedance of neural amplifier needs to be at least a few M $\Omega$  to minimize gain error [27].

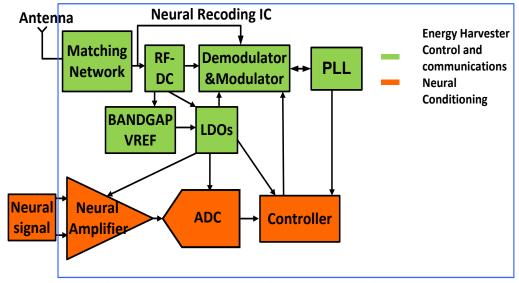

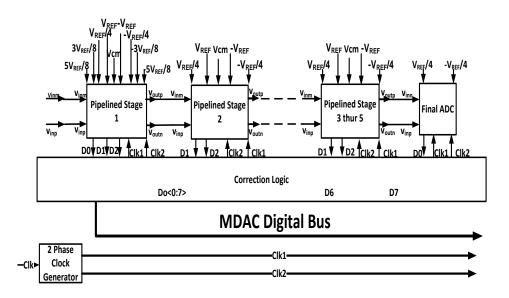

Figure 1.11 Block diagram of the neural recording system

A typical neural recording system architecture is shown in Fig. 1.11. The neural recording system consists of a neural amplifier, an 8-bit ADC, a controller, a power harvesting front end, a voltage reference and a PLL. The whole system is capable of harvesting power and amplifying, recording, digitizing and transmitting data in real time. The objective of this dissertation is to design and develop a signal conditioning circuit including a neural amplifier and an ADC. The neural amplifier will be designed to provide a 900 mid-band gain, a 500 to 8 kHz bandwidth, and a 10- $\mu V_{rms}$  input referred noise. An 8-bit, 16ksps Pipelined ADC will then be designed to digitize the amplified sensor data. The neural amplifier and ADC both will use a 700mV power supply.

#### 1.4 Thesis organization

Chapter I introduced the background, motivation and objective of this work. Chapter II reviews the FOM (Figure of Merit) of different OTA/Opamps for subthreshold application and two stage neural amplifier bandwidth, power and noise performance/efficiency. Chapter III reviews the power consumption advantage of Pipelined ADC over Sigma-Delta and Successive Approximation ADC. The design methodology and building blocks of 8 bit Pipelined ADC including MDAC (Multiplying Digital to Analog Converter), comparators and non overlapping clocks are also discussed. Chapter IV presents test results for the neural amplifier and pipelined ADC. Chapter V summarizes the results of this work.

#### CHAPTER II

# REVIEW OF OTA/OPAMP TOPOLOGOIES, THEIR DESIGN IN SUBTHRESHOLD AND APPLICATION TO BP AMPLIFIER DESIGN

There are ten sections in this chapter: sections 2.1-7 review seven more prominent OTA and Opamp topologies and developing a FOM (Figure of Merit) for each in subthreshold. Section 2.8 reviews and addresses neural amplifier design and section 2.9 present the performance summary of neural amplifier. Section 2.10 summarizes the chapter. The OTA/Opamp is the most significant block in bandpass amplifier design, providing low noise, low distortion, high gain, and sufficient output swing for input neural signal. The OTA or Opamps with best FOM is to be selected for the bandpass amplifier.

The GBP-Dynamic range/watt FOM [15, 16] for OTA/Opamps is defined as follows;

$$FOM = \frac{GBP_{OL} * DR}{Power}$$

Where GBP<sub>OL</sub> is open loop Gain Bandwidth Product and DR is Dynamic Range of OTA/Opamp. It is necessary to make several assumptions to facilitate ease of analysis before proceeding with the topology comparison.

• Only thermal noise is considered for simplicity where in subthreshold the thermal noise model is given by [32]:

$$\overline{i_n^2} = 2nkTg_m$$

,  $g_m = \frac{I}{nU_T}$  and  $n = \frac{C_j + C_{ox}}{C_j} \overline{i_n^2}$  is noise current spectral density, n is

slope factor, k is Boltzmann's constant, T is temperature, gm is transconductance,  $U_T$  is thermal voltage,  $C_j$  is depletion layer capacitance and  $C_{ox}$  is gate-oxide capacitance.

- The OTA/Opamps used in the bandpass amplifiers are required to achieve the same performance specification; equal gain bandwidth and noise requirement. Additionally it is assumed all OTA/Opamps will support similar or equal load capacitance requirements.

- All devices are assumed to be operating in subthreshold saturation,  $V_{ds}$  greater than  $5U_T$  or approximately 125mV.

- For two stage OTA/Opamps, there are three different cases for the relationship between the load and compensation capacitance:  $C_L \approx Cc$ ,  $C_L >> Cc$  and  $C_L << Cc$ .

- 1. For  $C_L \approx Cc$ , to shift the non-dominant pole requires the second stage leg of current  $I_2$  be greater than the stage 1 differential pair current  $I_0$ ;

- 2. For  $C_L >> Cc$ , the current of second stage leg of current  $I_2$  is required to be much greater than the stage 1 differential pair current  $I_0$ ;

- 3. For  $C_L \ll Cc$ , the current  $I_0$  of first stage of two stage OTA/Opamps will dominate the total power consumption.

- The V<sub>ds</sub> of each transistor is greater than or equal 5U<sub>T</sub>, to ensure all OTA/Opamps transistors are saturated, VDD is selected greater than 30U<sub>T</sub>≈750mV. With greater VDD comes greater signal swing and greater SNR or DR efficiency.

The initial evaluation uses open loop analysis. However, in fully differential applications the closed loop  $GBP_{CL}$  equals half the open loop  $GBP_{OL}$ . To achieve critical settling phase margin (PM) in closed loop is selected to be 76 degrees [40]. For two stage OTA/Opamps comparisons where the feedback factor  $\beta$  is less than 0.1 (See neural amplifier design specification in section 2.8) PM can be written as;

$$PM = 360 - 180 - \tan^{-1} \frac{GBP_{CL}}{\beta GBP_{CL}} - \tan^{-1} \frac{GBP_{CL}}{1.2 * GBP_{CL}} + \tan^{-1} \frac{GBP_{CL}}{x GBP_{OL}}$$

$$= 180 - 88 - 40 + \tan^{-1} \frac{GBP_{CL}}{x GBP_{OL}} = 76$$

$$1/2x = \tan(76 + 88 + 40 - 180) = \tan(24) = 0.44$$

$$x = 1.1$$

(2.2)

From (2.1) the non-dominant pole is set  $1.2*GBP_{CL}$  for 20% process variation with  $GBP_{CL}$  and left plane zero is found as  $1.1*GBP_{OL}$  equals  $2.2*GBP_{CL}$ .

After assumptions are introduced, we will start the FOM comparison of OTA/Opamps topologies.

2.1 Telescopic OTA where  $C_C = C_L$

Figure 2.1 Schematic of Telescopic OTA [40]

Input referred noise spectral density is given:  $\overline{v_n^2} = \frac{4nkT}{g_{m1}} \left(1 + \frac{g_{m6}}{g_{m1}}\right) \approx \frac{8nkT}{g_{m1}}$  (2.3)

Output referred noise is:

$$\overline{v_{no}} = \frac{1}{\beta} \sqrt{\frac{8nkT}{g_{m1}}} \sqrt{\frac{\pi}{2}} \beta^* GBP_{CL} = \sqrt{\frac{1}{\beta^2} \frac{8nkT}{g_{m1}} \frac{\pi}{2}} \beta \frac{g_{m1}}{2^* 2\pi C_L} = \sqrt{\frac{nkT}{\beta C_L}}$$

(2.4)

$$GBP_{OL} = \frac{g_{m1}}{C_L} = \frac{I_1}{nU_T C_L} = 2*GBP_{CL}$$

(2.5)

Fully differential dynamic range is:

$$DR \propto \frac{\left(\frac{V_o}{\sqrt{2}}\right)^2}{v_{no}^2} = \frac{\left(2*\frac{(V_{DD}-5*5U_T)}{\sqrt{2}}\right)^2}{\frac{nkT}{\beta C_L}} = \frac{\left(2*\frac{(30U_T-5*5U_T)}{\sqrt{2}}\right)^2}{\frac{nkT}{\beta C_L}} = \frac{2*25U_T^2}{\frac{nkT}{\beta C_L}} \quad (2.6)$$

$$Power=VDD*2I_1=60U_TI_1$$

(2.7)

$$FOM = \frac{GBP_{OL} * DR}{Power} = \frac{\frac{I_1}{nU_T C_L} * \frac{2 * 25U_T^2}{\frac{nkT}{\beta C_L}}}{60U_T I_1} = 0.83 * \frac{\beta}{n^2 kT}$$

(2.8)

2.2 Folded Cascode OTA where  $C_C = C_L$

Figure 2.2 Schematic of folded cascode OTA [40]

Input referred noise spectral density is given:

$$\overline{v_n^2} = \frac{4nkT}{g_{m1}} \left( 1 + \frac{g_{m3} + g_{m6}}{g_{m1}} \right) \approx \frac{16nkT}{g_{m1}} \qquad \text{Assume gm}_1 = \text{gm}_3 \approx 1/2 \text{gm}_6 \tag{2.9}$$

$$GBP_{OL} = \frac{g_{m1}}{C_L} = \frac{I_1}{nU_T C_L} = 2*GBP_{CL}$$

(2.10)

Output referred noise is:

$$\overline{v_{no}} = \frac{1}{\beta} \sqrt{\frac{16nkT}{g_{m1}}} \sqrt{\frac{\pi}{2}} \beta^* GBP_{CL} = \sqrt{\frac{1}{\beta^2}} \frac{16nkT}{g_{m1}} \frac{\pi}{2} \beta \frac{g_{m1}}{2^* 2\pi C_L} = \sqrt{\frac{2nkT}{\beta C_L}}$$

(2.11)

$$DR \propto \frac{\left(\frac{V_o}{\sqrt{2}}\right)^2}{v_{no}^2} = \frac{\left(2 * \frac{(V_{DD} - 4 * 5U_T)}{\sqrt{2}}\right)^2}{\frac{2nkT}{\beta C_L}} = \frac{\left(2 * \frac{(30U_T - 4 * 5U_T)}{\sqrt{2}}\right)^2}{\frac{2nkT}{\beta C_L}} = \frac{2 * 100U_T^2}{\frac{2nkT}{\beta C_L}}$$

(2.12)

$$FOM = \frac{GBP_{OL} * DR}{Power} = \frac{\frac{I_1}{nU_T C_L} * \frac{2*100U_T^2}{2nkT}}{120U_T I_1} = 0.83 * \frac{\beta}{n^2 kT}$$

(2.14)

### 2.3 Two stage opamp with Miller compensation

Figure 2.3 Schematic of two stage opamp with Miller compensation [33]

Input referred noise spectral density is given:

$$\overline{v_n^2} = \frac{4nkT}{g_{m1}} \left( 1 + \frac{g_{m3} + g_{m6}}{g_{m1}} \right) \approx \frac{16nkT}{g_{m1}} \qquad \text{Assume gm}_1 = \text{gm}_3 \approx 1/2 \text{gm}_6 \tag{2.15}$$

$$GBP_{OL} = \frac{g_{m1}}{C_c} = \frac{I_1}{nU_T C_c} = 2 * GBP_{CL}$$

(2.16)

Output referred noise is:

$$\overline{v_{no}} = \frac{1}{\beta} \sqrt{\frac{16nkT}{g_{m1}} \frac{\pi}{2} \beta^* GBP_{CL}} = \sqrt{\frac{1}{\beta^2} \frac{16nkT}{g_{m1}} \frac{\pi}{2} \beta \frac{g_{m1}}{2^* 2\pi C_c}} = \sqrt{\frac{2nkT}{\beta C_c}}$$

(2.17)

Because right plane zero equals non-dominant pole [40],

$$\omega_{non} \approx \frac{g_{m9}}{C_L} \approx \omega_z \approx \frac{g_{m9}}{C_C}$$

(2.18)

The non-dominant pole and right plane zero are set to  $3.6*GBP_{OL}$ ,

$$PM = 360 - 180 - \tan^{-1} \frac{GBP_{CL}}{\beta GBP_{CL}} - \tan^{-1} \frac{GBP_{CL}}{xGBP_{OL}} - \tan^{-1} \frac{GBP_{CL}}{xGBP_{OL}} = 180 - 88 - 2\tan^{-1} \frac{GBP_{CL}}{xGBP_{OL}} = 76$$

(2.19)

$$\frac{1}{2}x = \tan\left[\frac{(180 - 88 - 76)}{2}\right] = \tan(8) = 0.14$$

(2.20)

$$x = 3.6$$

$$\omega_{non} \approx \frac{g_{m9}}{C_L} = 3.6 \frac{g_{m1}}{C_c}$$

(2.21)

$$g_{m9} = 3.6g_{m1} \tag{2.22}$$

$$DR \propto \frac{\left(\frac{V_o}{\sqrt{2}}\right)^2}{\overline{v_{no}^2}} = \frac{\left(2 * \frac{(V_{DD} - 2 * 5U_T)}{\sqrt{2}}\right)^2}{\frac{2nkT}{\beta C_c}} = \frac{\left(2 * \frac{(30U_T - 2 * 5U_T)}{\sqrt{2}}\right)^2}{\frac{2nkT}{\beta C_c}} = \frac{2 * 400U_T^2}{\frac{2nkT}{\beta C_c}} \quad (2.23)$$

Power=VDD\*

$$(2I_1*2+2*3.6I_1)=336U_TI_1$$

(2.24)

$$FOM = \frac{GBP_{OL} * DR}{Power} = \frac{\frac{I_1}{nU_T C_c} * \frac{2 * 400U_T^2}{\frac{2nkT}{\beta C_c}}}{336U_T I_1} = 1.19 * \frac{\beta}{n^2 kT}$$

(2.25)

2.4 Two stage opamp with indirect compensation

Figure 2.4 Schematic of two stage opamp with indirect compensation [40]

Input referred noise spectral density is given:

$$\overline{v_n^2} = \frac{4nkT}{g_{m1}} \left( 1 + \frac{g_{m3} + g_{m6}}{g_{m1}} \right) \approx \frac{16.8nkT}{g_{m1}} \quad \text{Assume gm}_3 = 1.1 \text{gm}_1 \text{ and gm}_6 = 2.1 \text{gm}_1 \tag{2.26}$$

$$GBP_{OL} = \frac{g_{m1}}{C_c} = \frac{I_1}{nU_T C_c} = 2*GBP_{CL}$$

(2.27)

Output referred noise is:

$$\overline{v_{no}} = \frac{1}{\beta} \sqrt{\frac{16.8nkT}{g_{m1}} \frac{\pi}{2} \beta^* GBP_{CL}} = \sqrt{\frac{1}{\beta^2} \frac{16.8nkT}{g_{m1}} \frac{\pi}{2} \beta \frac{g_{m1}}{2^* 2\pi C_c}} = \sqrt{\frac{2.1nkT}{\beta C_c}}$$

(2.28)

The non-dominant pole [40] equals 0.6\*GBP  $_{\rm OL}$  ,

$$\omega_{non} \approx \frac{g_{m9}C_c}{C_1(C_L + C_c)} = 0.6 \frac{g_{m1}}{C_c}$$

(2.29)

Where  $C_1$  is the capacitance of the node Vo1, assume  $C_1$  equals  $0.1C_c$ ,

$$g_{m9} = 0.12g_{m1} \tag{2.30}$$

$$DR \propto \frac{\left(\frac{V_o}{\sqrt{2}}\right)^2}{v_{no}^2} = \frac{\left(2 * \frac{(V_{DD} - 2 * 5U_T)}{\sqrt{2}}\right)^2}{\frac{2.1nkT}{\beta C_c}} = \frac{\left(2 * \frac{(30U_T - 2 * 5U_T)}{\sqrt{2}}\right)^2}{\frac{2.1nkT}{\beta C_c}} = \frac{2 * 400U_T^2}{\frac{2.1nkT}{\beta C_c}} \quad (2.31)$$

Power=VDD\*

$$(2*I_1+2*1.1I_1+2*0.12I_1) = 133.2U_TI_1$$

(2.32)

$$FOM = \frac{GBP_{OL} * DR}{Power} = \frac{\frac{I_1}{nU_T C_c} * \frac{2 * 400U_T^2}{2.1nkT}}{133.2U_T I_1} = 2.86 * \frac{\beta}{n^2 kT}$$

(2.33)

# 2.5 Two stage opamp with split length transistors compensation

Figure 2.5 Schematic of two stage opamp with split length transistors compensation [40] Input referred noise spectral density is given:

$$\overline{v_n^2} = \frac{4nkT}{g_{m1}} \left( 1 + \frac{g_{m3} + g_{m6}}{g_{m1}} \right) \approx \frac{12.4nkT}{g_{m1}} \text{ Assume gm}_3 = 0.55 \text{gm}_1 \text{ and gm}_6 = 1.55 \text{gm}_1 \tag{2.34}$$

$$GBP_{OL} = \frac{g_{m1}}{C_c} = \frac{I_1}{nU_T C_c} = 2*GBP_{CL}$$

(2.35)

Output referred noise is:

$$\overline{v_{no}} = \frac{1}{\beta} \sqrt{\frac{12.4nkT}{g_{m1}} \frac{\pi}{2} \beta^* GBP_{CL}} = \sqrt{\frac{1}{\beta^2} \frac{12.4nkT}{g_{m1}} \frac{\pi}{2} \beta \frac{g_{m1}}{2^* 2\pi C_c}} = \sqrt{\frac{1.55nkT}{\beta C_c}}$$

(2.36)

The non-dominant pole [40] equals 0.6\*GBP<sub>OL</sub>,

$$\omega_{non} \approx \frac{g_{m9}C_c}{2C_1C_L} = 0.6 * \frac{g_{m1}}{C_c}$$

(2.37)

Where  $C_1$  is the capacitance of the node Vo1, assume  $C_1$  equals  $0.1C_c$

$$g_{m9} = 0.12g_{m1} \tag{2.38}$$

$$DR = \frac{\left(\frac{V_o}{\sqrt{2}}\right)^2}{\overline{v_{no}^2}} = \frac{\left(2*\frac{(V_{DD} - 2*5U_T)}{\sqrt{2}}\right)^2}{\frac{1.55nkT}{\beta C_c}} = \frac{\left(2*\frac{(30U_T - 2*5U_T)}{\sqrt{2}}\right)^2}{\frac{1.55nkT}{\beta C_c}} = \frac{2*400U_T^2}{\frac{1.55nkT}{\beta C_c}} \quad (2.39)$$

$$Power=VDD^{*}(2^{*}I_{1}+2^{*}0.55^{*}I_{1}+2^{*}0.12I_{1})=100.2U_{T}I_{1}$$

(2.40)

$$FOM = \frac{GBP_{OL} * DR}{Power} = \frac{\frac{I_1}{nU_T C_c} * \frac{2 * 400U_T^2}{1.55nkT}}{100.2U_T I_1} = 5.15 * \frac{\beta}{n^2 kT}$$

(2.41)

2.6 Two stage opamp with Miller p-z compensation

Figure 2.6 Schematic of two stage opamp with Miller p-z compensation [40]

Input referred noise spectral density is given:

$$\overline{v_n^2} = \frac{4nkT}{g_{m1}} \left( 1 + \frac{g_{m3} + g_{m6}}{g_{m1}} \right) \approx \frac{12nkT}{g_{m1}} \text{ Assume gm}_3 = 1/2 \text{gm}_1 \text{ and gm}_3 = 1/3 \text{gm}_6$$

(2.42)

\_

$$GBP_{OL} = \frac{g_{m1}}{C_c} = \frac{I_1}{nU_T C_c} = 2*GBP_{CL}$$

(2.43)

Output referred noise is:

$$\overline{v_{no}} = \frac{1}{\beta} \sqrt{\frac{12nkT}{g_{m1}}} \frac{\pi}{2} \beta^* GBP_{CL} = \sqrt{\frac{1}{\beta^2}} \frac{12nkT}{g_{m1}} \frac{\pi}{2} \beta \frac{g_{m1}}{2^* 2\pi C_c} = \sqrt{\frac{1.5nkT}{\beta C_c}}$$

(2.44)

The non-dominant pole equals 0.6\*GBP<sub>OL</sub>,

$$\omega_{non} \approx \frac{g_{m9}}{C_L} = 0.6 \frac{g_{m1}}{C_c}$$

(2.45)

$$g_{m9} = 0.6g_{m1} \tag{2.46}$$

$$DR = \frac{\left(\frac{V_o}{\sqrt{2}}\right)^2}{\overline{v_{no}^2}} = \frac{\left(2*\frac{(V_{DD} - 2*5U_T)}{\sqrt{2}}\right)^2}{\frac{1.5nkT}{\beta C_c}} = \frac{\left(2*\frac{(30U_T - 2*5U_T)}{\sqrt{2}}\right)^2}{\frac{1.5nkT}{\beta C_c}} = \frac{2*400U_T^2}{\frac{1.5nkT}{\beta C_c}}$$

(2.47)

Power=VDD\*(

$$I_1$$

\*2+2\*0.5 $I_1$ +2\*0.6 $I_1$ )=126 $U_TI_1$  (2.48)

$$FOM = \frac{GBP_{OL} * DR}{Power} = \frac{\frac{I_1}{nU_T C_c} * \frac{2 * 400U_T^2}{1.5nkT}}{126U_T I_1} = 4.23 * \frac{\beta}{n^2 kT}$$

(2.49)

Section 2.7 Sarpeshkar's modified OTA

Sarpeshkar's modified OTA is shown in Figure 1.4.

Input referred noise spectral density is given [16]:

$$\overline{v_n^2} = \frac{1}{g_{m0}^2} \left( 4nkTg_{m0} + 4nkTg_{m11} + \frac{8kT}{R_1} \right)$$

$$= \frac{4nkT}{g_{m0}} \left( 1 + \frac{g_{m11}}{g_{m0}} + \frac{2U_T}{I_0R_1} \right) \approx \frac{4nkT}{g_{m0}}$$

(2.50)

$$GBP_{OL} = \frac{g_{m0}}{C_L} = \frac{I_0}{nU_T C_L}$$

(2.51)

Output referred noise is:

$$\overline{v_{no}} = \frac{1}{\beta} \sqrt{\frac{4nkT}{g_{m0}}} \sqrt{\frac{\pi}{2}} \beta^* GBP_{CL} = \sqrt{\frac{1}{\beta^2}} \frac{4nkT}{g_{m0}} \frac{\pi}{2} \beta \frac{g_{m0}}{2^* 2\pi C_L} = \sqrt{\frac{nkT}{\beta^2 C_L}}$$

(2.52)

The current of transistor M11 is negligible compared with  $I_0$  and  $I_0R_1$  should be higher than  $20U_T$  to ensure the resistor noise contribution negligible.

Total current is:

$$2^{*}(I_{0}+I_{11})\approx 2I_{0} \tag{2.53}$$

Since the input neural signal range is 50-500 $\mu$ V, the minimum gain of first stage amplifier is 20; the maximum output signal amplitude is 10mV as a result U<sub>T</sub> is included for output swing and the common mode variation is also U<sub>T</sub>, the power supply VDD is given,

$$VDD=5*5U_{T}+U_{T}+U_{T}+(I_{0}+I_{11})R_{1}\approx 27U_{T}+I_{0}R_{1}\approx 47U_{T}$$

(2.54)

$$DR \propto \frac{\left(\frac{V_o}{\sqrt{2}}\right)^2}{\overline{v_{no}^2}} = \frac{\frac{V_o^2}{2}}{\frac{nkT}{\beta 2C_L}} = \frac{U_T^2}{\frac{nkT}{\beta C_L}}$$

(2.56)

FOM of Sarpeshkar's modified OTA is

$$FOM_{Sarp} = \frac{GBP_{OL} * DR}{Power} = \frac{\frac{I_0}{nU_T C_L} * \frac{U_T^2}{nkT}}{94U_T I_0} = 0.01 * \frac{\beta}{n^2 kT}$$

(2.57)

|                           | -                                         |                    |                                | _                                  |                            |

|---------------------------|-------------------------------------------|--------------------|--------------------------------|------------------------------------|----------------------------|

| OTA<br>architecture       | Output<br>Referred                        | Output swing       | Dynamic<br>Range               | Power                              | FOM                        |

| arenneeture               | Noise                                     |                    | Range                          |                                    |                            |

| Telescopic                | nkT                                       | 2*5U <sub>T</sub>  | $2 * 25 U_T^2$                 | 60U <sub>T</sub> I <sub>1</sub>    | $0.83*\frac{\beta}{n^2kT}$ |

| OTA                       | $\sqrt{\frac{nkT}{\beta C_L}}$            |                    | nkT                            |                                    | $\frac{0.83}{n^2 kT}$      |

|                           | <b>₩</b> <i>Y</i> = <i>L</i>              |                    | $\overline{\beta C_{_L}}$      |                                    |                            |

| Folded                    | $\sqrt{\frac{2nkT}{\beta C_L}}$           | 2*10U <sub>T</sub> | $2*100U_T^2$                   | $120U_TI_1$                        | $0.83*\frac{\beta}{n^2kT}$ |

| cascade OTA               | $\sqrt{\beta C_L}$                        |                    | 2nkT                           |                                    | $n^2 kT$                   |

|                           |                                           |                    | $\beta C_L$                    |                                    |                            |

| Two stage                 | 2nkT                                      | 2*20U <sub>T</sub> | $2*400U_T^2$                   | $336U_TI_1$                        | $1.19*\frac{\beta}{n^2kT}$ |

| opamp with                | $\sqrt{\frac{2nkT}{eta C_c}}$             |                    | 2nkT                           |                                    | $n^2kT$                    |

| Miller compensation       |                                           |                    | $\beta C_c$                    |                                    |                            |

|                           | $\sqrt{2 \ln kT}$                         | 2*20U <sub>T</sub> | $2*400U_T^2$                   | 133.2U <sub>T</sub> I <sub>1</sub> | β                          |

| Two stage opamp with      | $\sqrt{\frac{2.1nkT}{\beta C_c}}$         | -                  | $\frac{2 + 400C_T}{2.1 n k T}$ |                                    | $2.86*\frac{\beta}{n^2kT}$ |

| indirect                  | $\int \rho c_c$                           |                    | $\frac{2.1661}{\beta C_c}$     |                                    |                            |

| compensation              |                                           |                    | , ,                            |                                    |                            |

| Two stage                 | 1.55nkT                                   | 2*20U <sub>T</sub> | $2*400U_T^2$                   | $100.2U_TI_1$                      | $5.15*\frac{\beta}{n^2kT}$ |

| opamp with                | $\sqrt{\beta C_c}$                        |                    | 1.55 <i>nkT</i>                |                                    | $n^2 kT$                   |

| split length compensation |                                           |                    | $\beta C_{c}$                  |                                    |                            |

| Two stage                 | 1.5nkT                                    | 2*20U <sub>T</sub> | $2*400U_{T}^{2}$               | $126U_TI_1$                        | $_{4.22*}\beta$            |

| opamp with                | $\sqrt{\frac{1.5\pi c_{r}}{\beta C_{c}}}$ |                    | $\frac{1.5nkT}{1.5nkT}$        |                                    | $4.23*\frac{\beta}{n^2kT}$ |

| Miller p-z                | $V \mathcal{P}^{\sim}_{c}$                |                    | $\beta C_c$                    |                                    |                            |

| compensation              |                                           | TT                 | -                              |                                    |                            |

| Sarpeshkar's              | $\sqrt{\frac{nkT}{2\beta C_L}}$           | U <sub>T</sub>     | $\frac{U_T^2}{nkT}$            | $94U_TI_1$                         | $0.01*\frac{\beta}{n^2kT}$ |

| modified<br>OTA           | $\sqrt{2\beta C_L}$                       |                    | $\frac{nkT}{nkT}$              |                                    | n²kT                       |

| UIA                       |                                           |                    | $\overline{\beta C_{_L}}$      |                                    |                            |

Table 2.1 Comparison of Performance of OTA/Opamps

Table 2.1 summarizes the FOM comparisons of OTA/Opamps. From the Table 2.1, two stage Opamp with split length compensation has the best FOM and Sarpeshkar's modified OTA has the lowest FOM due to its limited output swing. From equation (2.52), Sarpeshkar's modified OTA can achieve the lowest output referred noise, however, the drawbacks of Sarpeshkar's modified OTA are: 1) for the input power@-6dBm, power harvester can achieve raw VDD 1.1V with output load current 70µA [28], after Low Dropout Regulator (LDO) we can only get power supply less than 0.9V. Power supply VDD of Sarpeshkar's modified OTA needs to be higher than  $45U_T \approx 1.1V$ , which frequently requires to increase the number of stages rectifier resulting in

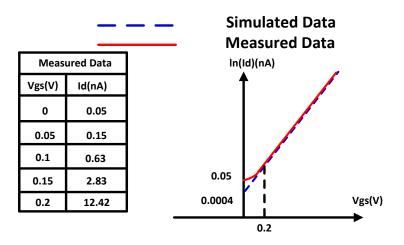

reducing harvester efficiency; 2) the ratio of  $I_{11}/I_0$  should be less than 1/10 to ensure the noise contribution of M11 is negligible, for  $I_0$  equals 100nA,  $I_{11}$  needs to be less than 10nA, this is not practical from measurement data. Figure 2.7 shows the simulated and measured subthreshold current of NMOS transistor with width/length 9.92um/2.2um, we can see the measured leakage current is higher than simulated current when Vgs is less than 200mV, which proves the bias current less than 10nA is not practical. For the 1st stage neural amplifier's requirement of low noise, low power and no strict constraint of output swing, Telescopic OTA is the best choice.

Figure 2.7 Simulated and measured subthreshold current

Table 2.2 summarizes three different two stage opamp topologies with first stage telescopic, folded cascoded and Sarpeshkar's modified OTA, two stage opamp with Miller compensation is not discussed in Table 2.2 due to its right plane zero degrading PM and high power consumption. With Sarpeshkar's modified OTA input stage, two stage opamp topologies may achieve the lower noise but higher power consumption than telescopic and folded cascode stage; however, due to non-availability of realization of closed loop PM of 76 degree, these telescopic and Sarpeshkar's modified OTA stage topologies are very difficult to be implemented in closed loop applications. Additionally, Sarpeshkar's modified OTA needs higher VDD for operation, which is not feasible for our low voltage design.

Table 2.2 Comparisons of two stage opamps with telescopic, folded cascode and Sarpeshkar's

| modified OTA input stage |  |

|--------------------------|--|

|                          |  |

|                                                                                   | Noise                              | Closed loop<br>PM@76<br>Feasibility | Power                              |

|-----------------------------------------------------------------------------------|------------------------------------|-------------------------------------|------------------------------------|

| 2 stage opamp with indirect<br>compensation with<br>telescopic stage              | $\sqrt{\frac{nkT}{eta C_c}}$       | No                                  | 67.2U <sub>T</sub> I <sub>1</sub>  |

| 2 stage opamp with indirect<br>compensation with folded<br>cascode stage          | $\sqrt{\frac{2.1nkT}{\beta C_c}}$  | Yes                                 | 133.2U <sub>T</sub> I <sub>1</sub> |

| 2 stage opamp with indirect<br>compensation with<br>Sarpeshkar's modified OTA     | $\sqrt{\frac{nkT}{2\beta C_c}}$    | No                                  | 282U <sub>T</sub> I <sub>1</sub>   |

| 2 stage opamp with split<br>length compensation with<br>telescopic stage          | $\sqrt{\frac{nkT}{eta C_c}}$       | No                                  | 918U <sub>T</sub> I <sub>1</sub>   |

| 2 stage opamp with split<br>length compensation with<br>folded cascode stage      | $\sqrt{\frac{1.55nkT}{\beta C_c}}$ | Yes                                 | 100.2U <sub>T</sub> I <sub>1</sub> |

| 2 stage opamp with split<br>length compensation with<br>Sarpeshkar's modified OTA | $\sqrt{\frac{nkT}{2\beta C_c}}$    | No                                  | 282U <sub>T</sub> I <sub>1</sub>   |

| 2 stage opamp with Miller<br>p-z compensation with<br>telescopic stage            | $\sqrt{\frac{nkT}{\beta C_c}}$     | No                                  | 96U <sub>T</sub> I <sub>1</sub>    |

| 2 stage opamp with Miller<br>p-z compensation with<br>folded cascode stage        | $\sqrt{\frac{1.5nkT}{\beta C_c}}$  | Yes                                 | 126U <sub>T</sub> I <sub>1</sub>   |

| 2 stage opamp with Miller<br>p-z compensation with<br>Sarpeshkar's modified OTA   | $\sqrt{\frac{nkT}{2\beta C_c}}$    | No                                  | 150.4U <sub>T</sub> I <sub>1</sub> |

2.8 Neural amplifier design

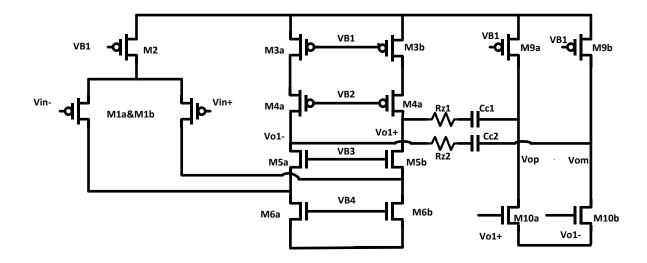

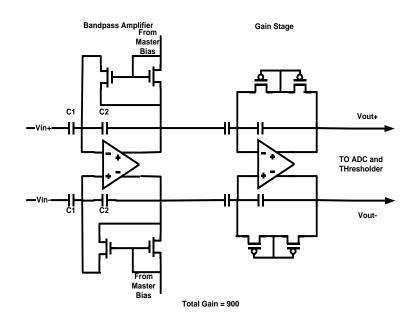

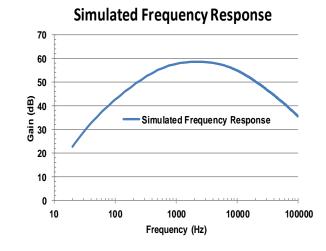

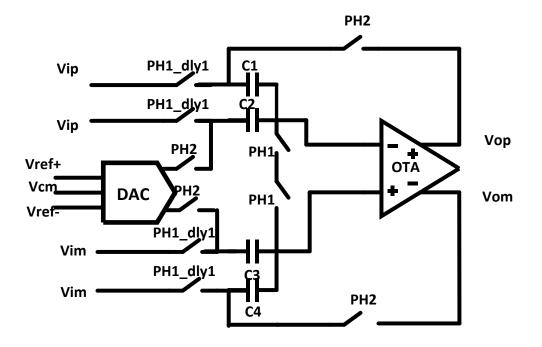

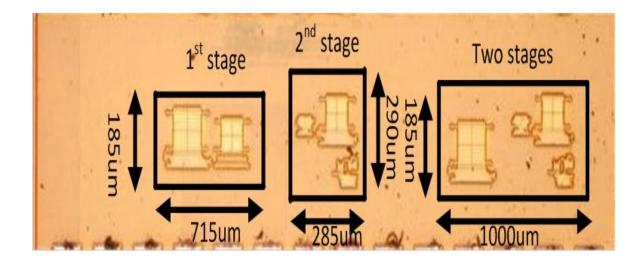

The neural amplifier system block diagram is shown in Figure 2.8. The neural amplifier includes two stages: a bandpass stage and a gain stage. The bandpass amplifier which utilizes a fully differential structure is based on Harrison's capacitive and resistive feedback method [15]. The lower 3dB frequency is determined by the feedback capacitor and current biased Pseudo resistor [18, 37]. A fully differential approach is selected to improve common mode rejection and reduce distortion. Because the input neural signal (50-500 $\mu$ V) is much less than a few thermal voltages (26mV) there is no slew rate limitation for either amplifier design. The midband gain of neural amplifier is 58.6dB with a 3dB bandwidth from 500 to 8 kHz. The input referred noise is  $10\mu$ V<sub>rms</sub> with power supply of 0.7V.

Figure 2.8 Neural Amplifier system block diagram, first stage with current programmable band pass function and stage two gain function.

2.8.1 Stages for Power consumption, Area and Gain

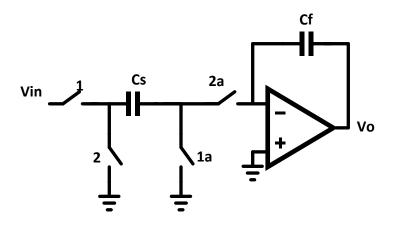

Amplifier gain, K is set by the ratio of the input capacitance and feedback capacitance  $(C_1/C_2)$  with the lower 3dB frequency given by:

$$f_{low} = \frac{1}{2\pi \cdot R_2 \cdot C_2} \tag{2.59}$$

Because  $R_2$  is inversely proportional to the current through the Pseudo resistor mirror, then the lower 3dB frequency is made tunable by trimming the scaled down current from the master bias circuit. The higher 3dB frequency is set by OTA loading and given by:

$$f_{high} = \frac{g_m}{2\pi \cdot \left[K(C_2 + C_L) + C_L + C_{gs} + C_L C_{gs} / C_2\right]}$$

(2.60)

where gm is the transconductance of the differential amplifier, gain per stage K equal  $C_1/C_2$ ,  $R_2$  is the resistance of the pseudo resistor,  $C_{gs}$  is the gate capacitance of input pair and  $C_L$  is the amplifier load capacitance, i e. stage 2 OTA or ADC.

In this application, low power and low area consumption are both important. This makes optimizing the number of amplifier stages very important. Assuming the OTA of each stage is a folded cascode structure with equal gains K, and gain bandwidth products:

$$BW = \frac{g_m}{2\pi C_{leff}} = \frac{g_m}{2\pi K(K+2)C_2} = \frac{GBP}{(K+1)}$$

(2.61)

$$C_{leff} = K(C_L + C_2) + C_L = K(K + 2)C_2, C_L = C_1 = KC_2$$

(2.62)

The bandwidth shrinkage of n stages is [38]:

$$|A(1+j\omega\tau)| = \frac{1}{|(1+j\omega\tau)|^n} = \frac{1}{\sqrt{2}}$$

(2.63)

Solving for  $\omega$  and n>2

$$\omega_{amplifier} = \frac{1}{\tau} \sqrt{2^{\frac{1}{n}} - 1noting \, 2^{\frac{1}{n}}} \approx 1 + \frac{1}{n} \ln(2) \tag{2.64}$$

$$\omega_{amplifier} = \frac{1}{\tau} \sqrt{\frac{1}{n} Ln(2)} = \frac{0.833}{\tau} \frac{1}{\sqrt{n}} = \omega_{3dB} \frac{0.833}{\sqrt{n}}$$

(2.65)

Substitute  $\omega$  into total power consumption [37] :

$$P \propto \frac{2\pi n * \sqrt[n]{G_T} (\sqrt[n]{G_T} + 2)}{(\sqrt[n]{G_T} + 1)} * \frac{0.833}{\sqrt{n}}$$

(2.66)

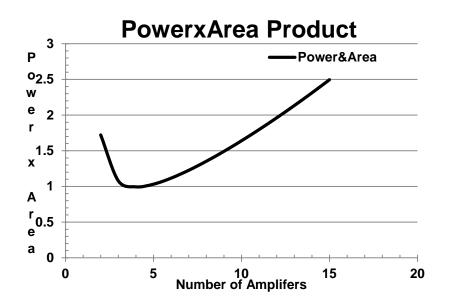

where n is the number of amplifier stages,  $C_{leff}$  is the effective load capacitance, GBP is the open loop gain bandwidth product,  $G_T$  is total required gain of neural amplifier,  $\omega_{amplifier}$  is the bandwidth of neural amplifier,  $\omega_{3dB}$  is the bandwidth of each stage amplifier. Taking  $G_T$  equal 900, and identical  $\omega_{3dB}$  and gain K for all stages, n=2, 3, 4, the total power consumption can be found. Continuing this approach, we can derive the optimal number of stages for the power area product:

$$P \& Area \propto \frac{2\pi n^2 * \sqrt[n]{G_T} (\sqrt[n]{G_T} + 2)}{(\sqrt[n]{G_T} + 1)} * \frac{0.833}{\sqrt{n}}$$

(2.67)

Normalizing and plotting of (2.67), Figure 2.9 shows the optimal number of stages is 3 to 4. Considering that each stage should have a gain greater than 10 to ensure noise contributions for following stages is negligible, and the  $G_T$  requirement is 900, a 2 stage amplifier with a gain of 30 per stage was selected. The 1st stage OTA sets amplifier bandwidth and noise and the second stage OTA maintains gain and noise performance while ensuring high output swing. From post layout of two stage neural amplifier, the area of 1<sup>st</sup> stage is only 10% larger than that of 2<sup>nd</sup> stage, which is ensuring our previous assumption.

Figure 2.9 Plot of normalized power area product for different number of stages.

## 2.8.2 Noise Analysis and Sizing

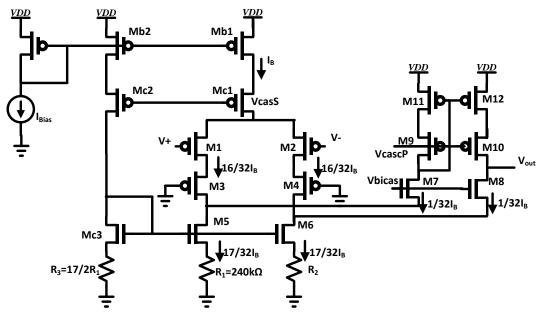

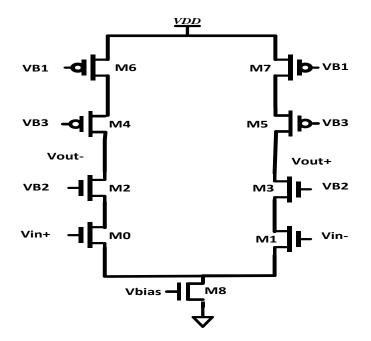

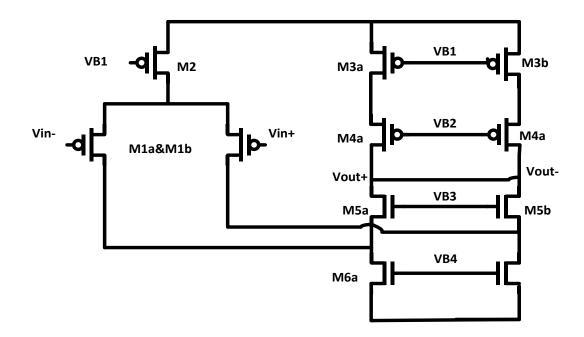

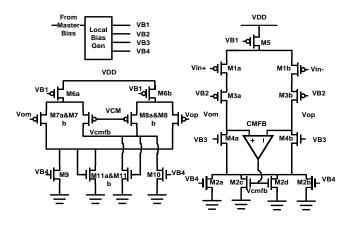

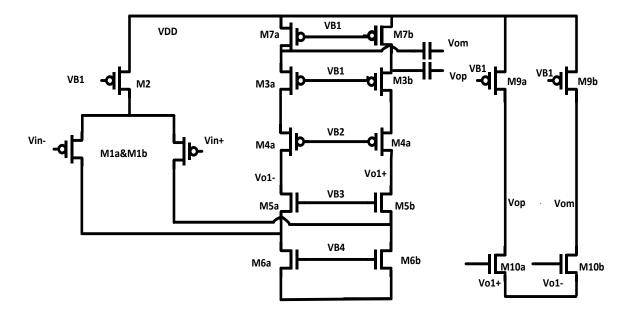

The schematic of the 1st stage OTA including the common mode feedback (CMFB) circuit is shown in Figure 2.10. The main contributors to input referred OTA noise are the input pairs and NMOS current sources. PMOS differential pairs are selected due to their lower 1/f noise properties [40]. The geometries of the transistors for the first and second OTA are shown in Table 2.3.

Figure 2.10 Schematic diagram of stage one OTA with its common mode feedback circuit [40].

As a result of source degeneration, cascode transistors make no significant noise contributions to OTA. The rail side NMOS transistors and differential pair should be made as large to as practical to minimize flicker noise. The spectral density of input thermal noise voltage is written as [40]:

$$\overline{v_{ni,thermal}^{2}} = \frac{4nkT}{g_{m1}} \left(1 + \frac{g_{m2}}{g_{m1}}\right) \approx \frac{8nkT}{g_{m1}}$$

(2.68)

where  $gm_1$  is the transconductance of input pair,  $gm_2$  is the transconductance of NMOS current sources, n is slope factor in subthreshold operation, k is Boltzmann's constant and T is the absolute temperature, the input thermal noise voltage is shown:

$$\overline{v_{ni,thermal}} \approx \sqrt{\frac{8nkT}{g_{m1}} * \frac{\pi}{2} \frac{g_{m1}}{2 * 2\pi K(C_L + C_2)}} = \sqrt{\frac{nkT}{K(C_L + C_2)}}$$

(2.69)

The input flicker noise of the OTA is:

$$\overline{v_{ni,flicker}} = \sqrt{2Ln(B)} \left( \frac{K_{flicker,p}}{W_1 L_1 C_{oxp}} + \frac{K_{flicker,n}}{W_{2a,2b} L_{2a,2b} C_{oxn}} + \frac{K_{flicker,n}}{W_{2c,2d} L_{2c,2d} C_{oxn}} \right)$$

(2.70)

where W, L,  $C_{ox}$  take on their usually meaning for M1 and M2;  $K_{flicker,n}$  and  $K_{flicker,p}$  are processdependent constants and B is the 3dB bandwidth.

The total input-referred noise is:

$$\overline{v_{ni,total}} \approx \sqrt{\frac{nkT}{K(C_{L}+C_{2})} + 2Ln(B) \left(\frac{K_{flicker,p}}{W_{1}L_{1}C_{oxp}} + \frac{K_{flicker,n}}{W_{2a,2b}L_{2a,2b}C_{oxn}} + \frac{K_{flicker,n}}{W_{2c,2d}L_{2c,2d}C_{oxn}}\right)} \approx \sqrt{2Ln(B) \left(\frac{K_{flicker,n}}{W_{2a,2b}L_{2a,2b}C_{oxn}} + \frac{K_{flicker,n}}{W_{2c,2d}L_{2c,2d}C_{oxn}}\right)}$$

(2.71)

The noise contributions of transistors in the first OTA are summarized in Table 2.3. From the noise simulation, the flicker noise of NMOS current source dominates the total input-referred noise.

| Transistors | Contributions (Flicker/Thermal noise) |  |  |

|-------------|---------------------------------------|--|--|

| M2c&M2d     | 40.02%/8.36%                          |  |  |

| M2a&M2b     | 19.26%/9.3%                           |  |  |

| M1a&M1b     | 1.08%/13.74%                          |  |  |

Table 2.3 Noise contribution of transistors in first OTA

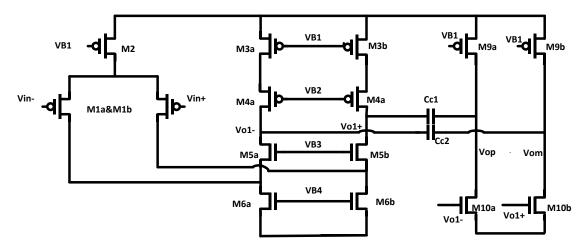

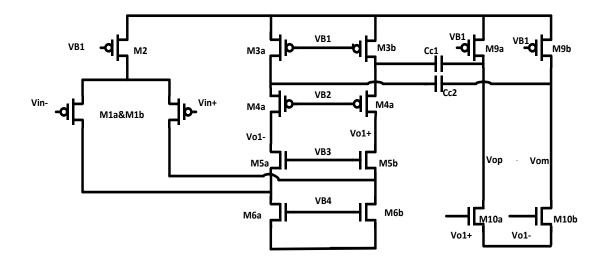

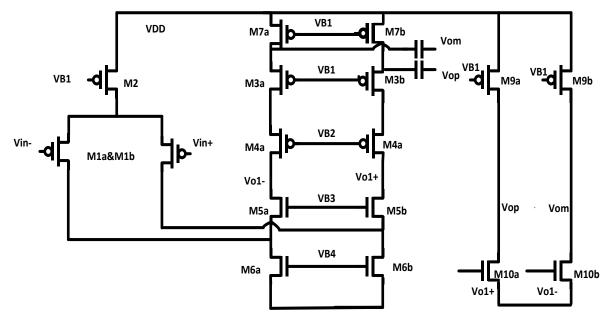

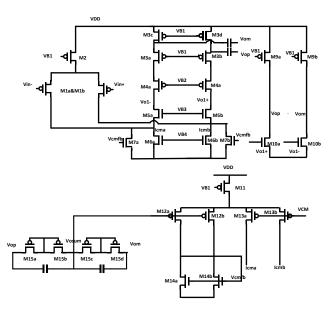

The schematic of the 2nd stage opamp including the CMFB circuit as well as their geometries are shown in Figure 2.11 and Table 2.4 respectively. Due to high output swing requirements of the second stage is a 2 stage folded cascode structure employing split length compensation for its highest FOM, as its main contribution is signal swing and not signal fidelity. BP2 requires Cc equals 2.5pF the maintain 10 bit accuracy and I<sub>diff</sub> equals 276.9nA for sufficient bandwidth.

The voltage divider of Vop and Vom, the resistance of RC network in the CMFB circuit needs to be large enough to ensure the gain of OTA is not degraded and does not introduce distortion in the OTA. When Vop > Vom, M15b and M15d are off, M15a and M15c are diode connected, according to linear pseudo-Ohm's law [38]:

$$I_{DS} = G^* (V_D^* - V_S^*)$$

(2.72)

$$G^* = \frac{1}{R^*} = \frac{I_s}{V_0} \exp(\frac{V_G - V_{T0}}{nU_T})$$

(2.73)

where R\* and G\* are the pseudo resistance and pseudo conductance between Vop, Vom and  $V_{osum}$ , and are the pseudo voltages,  $I_S$  is the specific current,  $V_{T0}$  is the threshold voltage of transistors M15,  $V_G$  is the gate voltage and  $V_0$  is the arbitrary scaling voltage. For  $I_S$  equal 100nA,

$U_T$  at room temperature and n equal 2, R\* is estimated using  $I_{OFF}$  in the configuration providing common mode summing for the CMFB circuit, while requiring sufficient area to control mismatch error.

Figure 2.11 Schematic diagram of stage two opamp with its common mode feedback circuit.

| 1st OTA         |            | 2nd OTA                |         |

|-----------------|------------|------------------------|---------|

| Devices         | W/L(µm)    | Devices                | W/L(µm) |

| M1a&M1b         | 40/1.6     | M1a&M1b                | 13.3/2  |

| M2a&M2b         | 24/4.4     | M2                     | 60/4    |

| M2c&M2d         | 26.4/2.4   | M3a&M3b                | 24/4    |

| M3a&M3b         | 40/1.6     | M4a&M4b                | 8/0.6   |

| M4a&M4b         | 96/2.2     | M5a&M5b                | 6.4/2.5 |

| M5              | 238.08/1.6 | M6a&M6b                | 18/12   |

| M6a&M6b         | 39.68/1.6  | M7a&M7b                | 6.4/3   |

| M7a&M7b M8a&M8b | 9.92/1.6   | M8a&M8b                | 8/3     |

| M9&M10          | 8/4.4      | M9a&M9b                | 264/4   |

| M11a&M11b       | 8.8/2.4    | M10a&M10b              | 2/3     |

|                 |            | M11                    | 96/4    |

|                 |            | M12a&M12b              | 10/1    |

|                 |            | M13a&M13b              | 6.4/3   |

|                 |            | M14a&M14b              | 3.6/2   |

|                 |            | M15a&M15b<br>M15c&M15d | 2/8     |

Table 2.4 Geometries of transistors in first and second OTA/opamp

## 2.9 Performance Summary of Neural Amplifier

|               | Midband<br>Gain | f_low<br>_3dB | f_high_<br>3dB | Input<br>referred<br>noise | Total<br>Harmonic<br>Distortion | Power<br>Consumption | Power<br>Supply |

|---------------|-----------------|---------------|----------------|----------------------------|---------------------------------|----------------------|-----------------|

| Stage 1       | 30.2dB          | 625Hz         | 12kHz          | 9.4uV                      | 0.1%                            | 0.76uW               | 0.7V            |

| Stage 2       | 30.2dB          | 250Hz         | 11.6kHz        | 47.7uV                     | 0.28%                           | 0.67uW               | 0.7V            |