# A LOW POWER DIGITAL BASEBAND CORE FOR WIRELESS MICRO-NEURAL-INTERFACE USING CMOS SUB/NEAR-THRESHOLD CIRCUIT

# By

# **RAN LIAO**

Bachelor of Engineering Southwest Jiaotong University Chengdu, China 2008

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY December, 2013

# A LOW POWER DIGITAL BASEBAND CORE FOR WIRELESS MICRO-NEURAL-INTERFACE USING CMOS SUB/NEAR-THRESHOLD CIRCUIT

Dissertation Approved:

| Dr. Chriswell G. Hutchens   |  |  |  |  |

|-----------------------------|--|--|--|--|

| Dissertation Adviser        |  |  |  |  |

| Dr. George Scheets          |  |  |  |  |

| Dr. James E. Stine, Jr      |  |  |  |  |

| Dr. Satish T.S. Bukkapatnam |  |  |  |  |

#### **ACKNOWLEDGEMENTS**

I am extremely grateful to my thesis advisor, Professor Chris Hutchens, for including me in his lab and putting me at the seat just behind him in the same room. It has been a truly privilege and rewarding experience to do research under his guidance. His sharing of wisdom, experience, work ethic and love of circuits has reshaped me in the past five years and it will be a role model for me in the future. One day CMOS may become obsolete, Moore's law may become past, but his instructions will always guide me and motivate me to become better.

I am equally grateful for my committee members. Professor George Scheets has given insightful suggestions on the protocol design in the early stage and been supportive throughout this work. Professor James Stine very patiently answered my questions on digital flow and has given critical suggestions which helped my tapeouts. Professor Satish Bukkapatnam has asked key questions and shared his expertise on Gen-2 Standard, which influenced this work to utilize some of the useful features of the mature Standard.

The members of the Hutchens MSVLSI Group have been lending countless help which is critical to my work. Many thanks go to Zhe Yuan, Vijay Madhuravasal, Srinivas Venkataraman, Yohannes Worku, Rehan Ahmed, Naresh Anne, Guanglei An, Giridhar Sharma, Rajashekargouda Patil and those who graduated before me but left valuable documentations. I also want to thank Jun Chen, Amey Phadke, Surpriya Tike, Verada Ogale, Rashmi Wadhwa, Manju Kiran Subbarayappa, Siddharth Shah and Robert Elliott for all valuable technical discussions and Yihong Yang for helping me taking the die photo in his lab.

Friends at OSU and across the world have been a constant source of fun and encouragement, and some of them have given critical help without which this work would not be possible. I want to thank Ming Yu, Guan Xu, Yue Han, Yujie Guo, Cunliang Zhu, Xiaoguo Huang, Sukesh Kannan, Xing Zhong, Xiaoying Liu, and EUMLab members YiXiang Xiao & Ming Zhong.

At last and most, I want to thank my parents Hua Guo and Fa'an Liao for their unconditional love and support. To you this work is dedicated to.

iii

Acknowledgements reflect the views of the author and are not endorsed by committee members or Oklahoma State University.

Name: Ran Liao

Date of Degree: DECEMBER, 2013

Title of Study: A LOW POWER DIGITAL BASEBAND CORE FOR WIRELESS

MICRO-NEURAL-INTERFACE USING CMOS SUB/NEAR-

THRESHOLD CIRCUIT

Major Field: ELECTRICAL AND COMPUTER ENGINEERING

Abstract: This thesis presents the work on designing and implementing a low power digital baseband core with custom-tailored protocol for wirelessly powered Micro-Neural-Interface (MNI) System-on-Chip (SoC) to be implanted within the skull to record cortical neural activities. The core, on the tag end of distributed sensors, is designed to control the operation of individual MNI and communicate and control MNI devices implanted across the brain using received downlink commands from external base station and store/dump targeted neural data uplink in an energy efficient manner. The application specific protocol defines three modes (Time Stamp Mode, Streaming Mode and Snippet Mode) to extract neural signals with on-chip signal conditioning and discrimination. In Time Stamp Mode, Streaming Mode and Snippet Mode, the core executes basic on-chip spike discrimination and compression, real-time monitoring and segment capturing of neural signals so single spike timing as well as inter-spike timing can be retrieved with high temporal and spatial resolution. To implement the core control logic using sub/nearthreshold logic, a novel digital design methodology is proposed which considers INWE (Inverse-Narrow-Width-Effect), RSCE (Reverse-Short-Channel-Effect) and variation comprehensively to size the transistor width and length accordingly to achieve close-tooptimum digital circuits. Ultra-low-power cell library containing 67 cells including physical cells and decoupling capacitor cells using the optimum fingers is designed, laidout, characterized, and abstracted. A robust on-chip sense-amp-less SRAM memory (8X32 size) for storing neural data is implemented using 8T topology and LVT fingers. The design is validated with silicon tapeout and measurement shows the digital baseband core works at 400mV and 1.28 MHz system clock with an average power consumption of 2.2 µW, resulting in highest reported communication power efficiency of 290Kbps/µW to date.

# TABLE OF CONTENTS

| Chapter                                                      | Page |

|--------------------------------------------------------------|------|

| I. INTRODUCTION                                              | 1    |

| 1.1. Neural Interface Overview                               | 1    |

| 1.2. Existing Work in Neural Interface                       |      |

| 1.3. Challenges                                              |      |

| 1.4. Thesis Contributions                                    |      |

| 1.5. Thesis Organization                                     |      |

| II. MNI PROTOCOL DESIGN                                      | 12   |

| 2.1. MNI System Overview                                     |      |

| 2.2. MNI System Architecture                                 |      |

| 2.3. MNI System Operation                                    |      |

| 2.4. System Constraints and Impact on Digital Core Design    |      |

| 2.5. Survey of Relevant Work in Protocol and Digital Control |      |

| 2.6 MNI Protocol                                             |      |

| 2.6.1 Downlink Communication                                 |      |

| 2.6.2 Uplink Communication                                   |      |

| 2.7 Digital Core High Level Design                           |      |

| 2.7.1 Digital Core Architecture                              |      |

| 2.7.2 Downlink Packet Decomposition                          |      |

| 2.7.3 Uplink Packet Composition                              |      |

| 2.7.4 Mode Controller                                        |      |

| 2.2 Conclusion                                               | 40   |

| III. SUB/NEAR-THRESHOLD DIGITAL DESIGN                       | 41   |

| 3.1 Introduction                                             |      |

| 3.2 Power Model                                              |      |

| 3.3 Survey of Low Power Digital Design Techniques            |      |

| 3.4 Sub/Near-Threshold Digital Design                        |      |

| 3.4.1 Parameter Variation                                    |      |

| 3.4.2 NWE and INWE                                           |      |

| 3.4.3 SCE and RSCE                                           |      |

| 3.5 Design Considering INWE, RSCE and Threshold Variation    | 48   |

| Chapter                                                                                                                                                                                                                                                                                                               | Pa                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 3.5.1 Threshold Voltage W.R.T Geometry                                                                                                                                                                                                                                                                                | 4                    |

| 3.5.2 Current and Current Efficiency W.R.T Geometry                                                                                                                                                                                                                                                                   |                      |

| 3.5.3 Proposed Cell Library Sizing and Design                                                                                                                                                                                                                                                                         |                      |

| 3.6 Standard Cell Library Development                                                                                                                                                                                                                                                                                 |                      |

| 3.6.1 Cell Library Layout                                                                                                                                                                                                                                                                                             |                      |

| 3.6.2 Cell Library Characterization                                                                                                                                                                                                                                                                                   |                      |

| 3.6.3 Cell Library Abstraction                                                                                                                                                                                                                                                                                        |                      |

| 3.6.4 Cell Library Summary                                                                                                                                                                                                                                                                                            | 6                    |

| 3.7 Design Flow                                                                                                                                                                                                                                                                                                       |                      |

| 3.8 Design Verification                                                                                                                                                                                                                                                                                               |                      |

| 3.9 Low Power Sense-Amp-Less 8T Memory with Read Boost                                                                                                                                                                                                                                                                |                      |

| 3.10 Conclusion                                                                                                                                                                                                                                                                                                       |                      |

| IV. SILICON IMPLEMENTATION AND MEASUREMENTS                                                                                                                                                                                                                                                                           | 7                    |

| 4.1 Introduction                                                                                                                                                                                                                                                                                                      | 7                    |

| 4.2 SRAM Memory                                                                                                                                                                                                                                                                                                       | 7                    |

| 4.3 Digital Core LVT Implementation                                                                                                                                                                                                                                                                                   |                      |

| 4.4 Digital Core Implementation with Optimum Finger Library                                                                                                                                                                                                                                                           | 8                    |

| V. CONCLUSION                                                                                                                                                                                                                                                                                                         | 8                    |

| 6.1. Summary of Work                                                                                                                                                                                                                                                                                                  | 8                    |

| 6.2. Future Work                                                                                                                                                                                                                                                                                                      | 8                    |

|                                                                                                                                                                                                                                                                                                                       |                      |

| REFERENCES                                                                                                                                                                                                                                                                                                            | 9                    |

| APPENDICES                                                                                                                                                                                                                                                                                                            | 10                   |

| APPENDICES                                                                                                                                                                                                                                                                                                            | 10                   |

| APPENDICES                                                                                                                                                                                                                                                                                                            | 10                   |

| APPENDICES                                                                                                                                                                                                                                                                                                            | 10<br>10             |

| APPENDICES                                                                                                                                                                                                                                                                                                            | 10<br>10<br>10<br>10 |

| APPENDICES  APPENDIX A. Cell Library  A.1 elccfg file  A.2 Footprint.def  A.3 setup.ss  A.4 NAND2X1 Characterization Result                                                                                                                                                                                           | 10<br>10<br>10<br>10 |

| APPENDICES                                                                                                                                                                                                                                                                                                            | 10<br>10<br>10<br>10 |

| APPENDICES                                                                                                                                                                                                                                                                                                            |                      |

| APPENDICES  APPENDIX A. Cell Library  A.1 elccfg file  A.2 Footprint.def  A.3 setup.ss  A.4 NAND2X1 Characterization Result  A.5 NOR2X1 Characterization Result                                                                                                                                                       |                      |

| APPENDICES  APPENDIX A. Cell Library  A.1 elccfg file  A.2 Footprint.def  A.3 setup.ss  A.4 NAND2X1 Characterization Result  A.5 NOR2X1 Characterization Result  A.6 INVXX1 Characterization Result                                                                                                                   |                      |

| APPENDICES  APPENDIX A. Cell Library  A.1 elccfg file  A.2 Footprint.def  A.3 setup.ss  A.4 NAND2X1 Characterization Result  A.5 NOR2X1 Characterization Result  A.6 INVXX1 Characterization Result  A.7 DFFPOSSRX1 Characterization Result  A.7 DFFPOSSRX1 Characterization Result  APPENDIX B. Digital Flow Scirpts |                      |

| APPENDICES  APPENDIX A. Cell Library  A.1 elccfg file  A.2 Footprint.def  A.3 setup.ss  A.4 NAND2X1 Characterization Result  A.5 NOR2X1 Characterization Result  A.6 INVXX1 Characterization Result  A.7 DFFPOSSRX1 Characterization Result                                                                           |                      |

# LIST OF TABLES

| Гable                                                                      | Page |

|----------------------------------------------------------------------------|------|

| 1.1 Survey of existing work in neural interface SoC                        | 10   |

| 2.1 Power budget for MNI building blocks                                   | 21   |

| 2.2 Survey of communication protocol for biomedical sensors                | 22   |

| 2.3 Survey of relevant work in digital control within biomedical platforms |      |

| 2.4 Comparison of encoding schemes                                         |      |

| 2.5 Downlink packet format                                                 |      |

| 2.6 Downlink command function                                              | 29   |

| 2.7 Uplink packet format for Respond Stamp Mode                            | 30   |

| 2.8 Uplink packet format for Respond Calibration/Streaming/Snippet Mod     |      |

| 3.1 Survey of relevant low power digital design techniques                 | 30   |

| 3.2 OF cell library performance comparison with conventional design        | 58   |

| 3.3 Cell library grid and pitch                                            | 61   |

| 3.4 Standard cell library cell list                                        | 63   |

| 3.5 Timing constraints summary                                             |      |

| 4.1 SRAM result summary                                                    | 76   |

| 4.2 Digital core LVT implementation result summary                         | 80   |

| 4.3 Digital core OF implementation result summary                          | 85   |

| 4.4 Performance comparisons with existing neural interface's digital block | ks86 |

# LIST OF FIGURES

| 1.1 Neural interface category                                             | 5  |

|---------------------------------------------------------------------------|----|

| 1.2 Common form of wireless neural interface                              | 5  |

|                                                                           | 6  |

| 1.3 Examples of state-of-the-art Neural Interfaces                        |    |

| 2.1 Concept of MNI                                                        | 13 |

| 2.2 Block Diagram of Micro-Neural-Interface                               | 14 |

| 2.3 State Diagram of MNI System Operation                                 | 15 |

| 2.4 Work flow of Do Calibration Mode                                      | 17 |

| 2.5 Demonstration of Do Stamp Mode                                        |    |

| 2.6 Demonstration of Do Snippet Mode                                      |    |

| 2.7 MNI communication signal flow                                         |    |

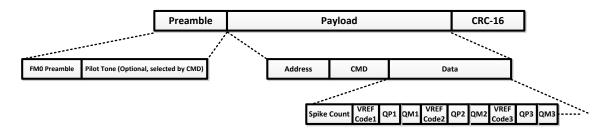

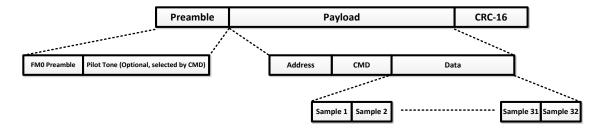

| 2.8 Downlink packet format                                                |    |

| 2.9 PIE Encoding for data-0 and data-1                                    |    |

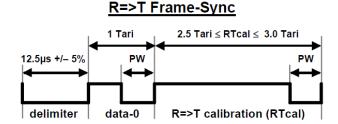

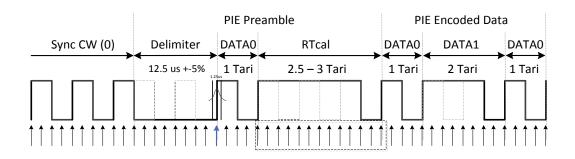

| 2.10 Frame Sync for downlink communication                                |    |

| 2.11 Uplink packet format for Respond Stamp Mode                          |    |

| 2.12 Uplink packet format for Respond Calibration/Streaming/Snippet Mode. |    |

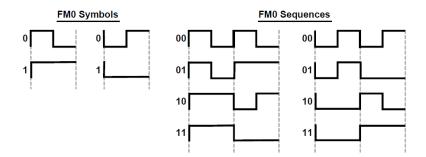

| 2.13 FM0 symbols and sequences                                            |    |

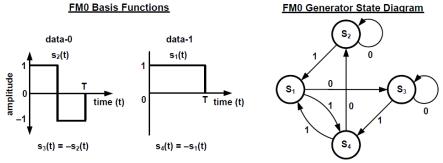

| 2.14 FM0 basis function and generator state diagram                       |    |

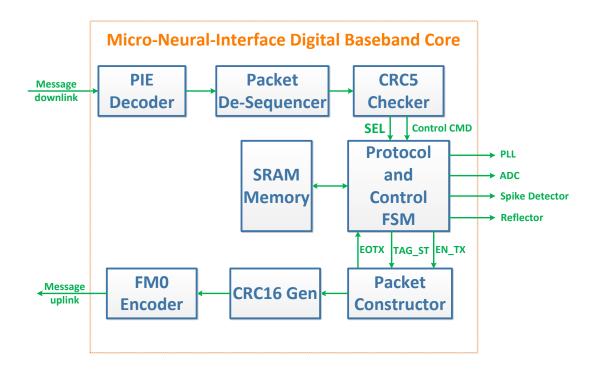

| 2.15 High level block diagram of MNI digital core                         |    |

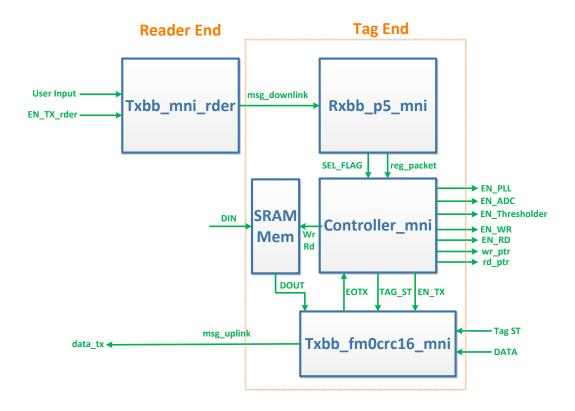

| 2.16 Design partitioning of of MNI digital core                           |    |

| 2.17 Downlink packet decomposition                                        |    |

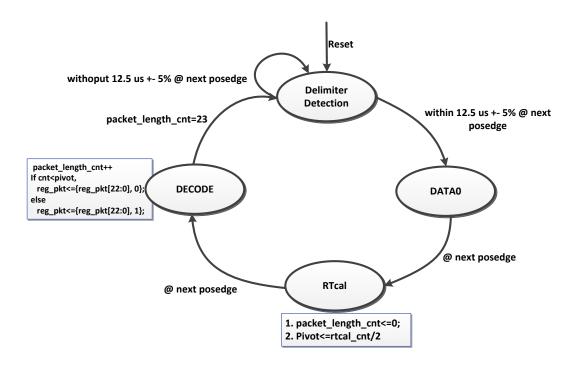

| 2.18 PIE decoding state diagram                                           |    |

| 2.19 Packet decomposition state diagram                                   |    |

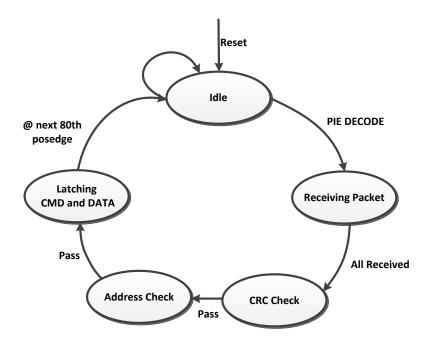

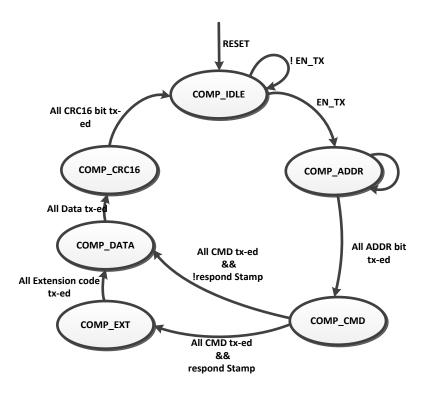

| 2.20 State diagram of uplink packet formation                             |    |

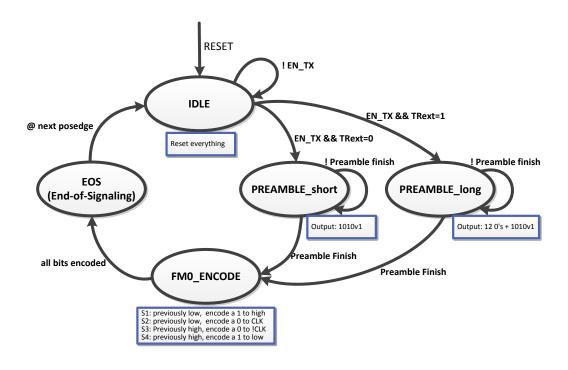

| 2.21 State diagram of uplink packet FM0 encoding                          |    |

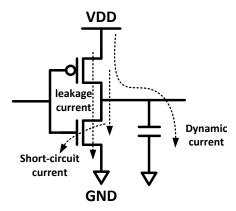

| 3.1 Power model of CMOS digital logic circuit                             |    |

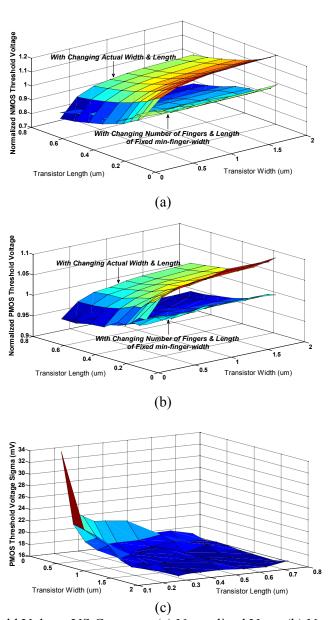

| 3.2 Threshold Voltage VS Geometry                                         |    |

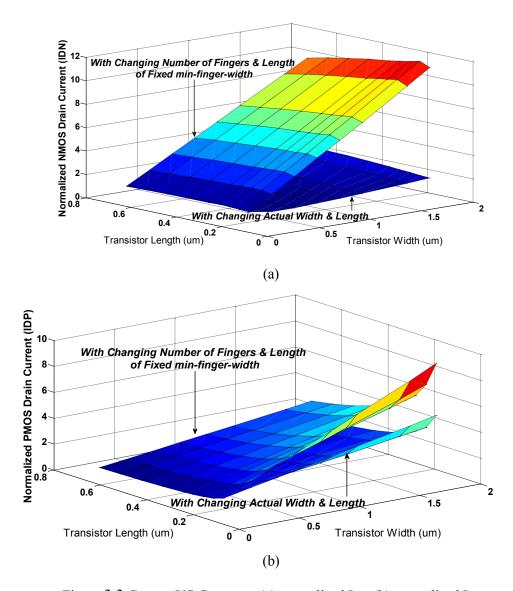

| 3.3 Current VS Geometry                                                   |    |

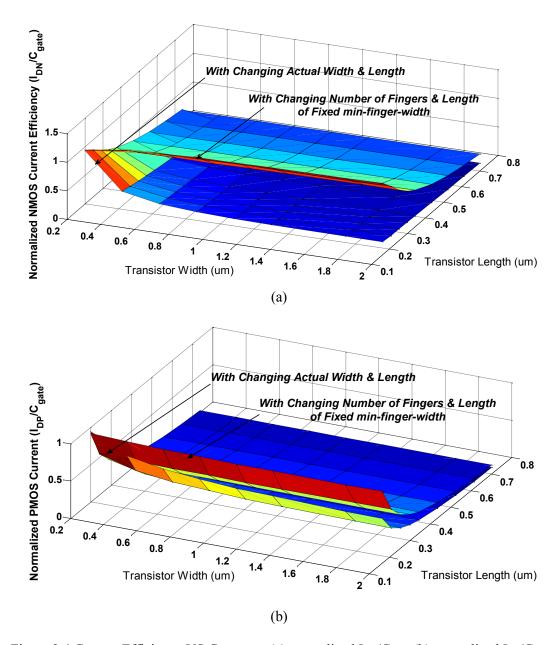

| 3.4 Current Efficiency VS Geometry                                        |    |

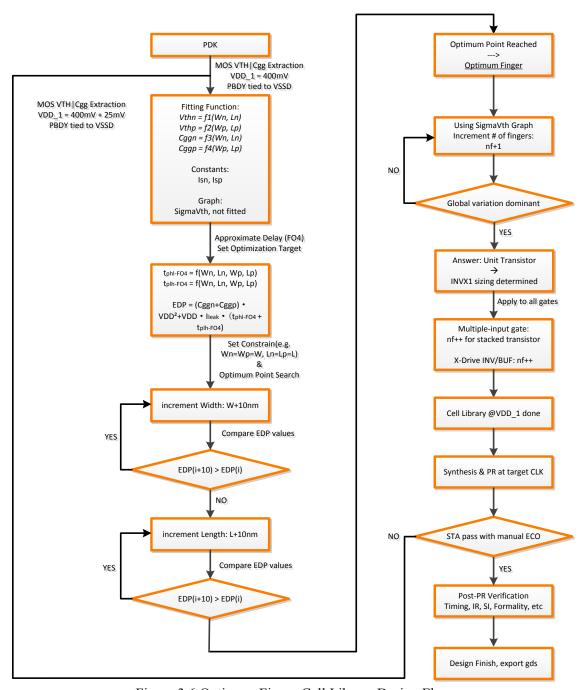

| 3.5 Optimum finger size searching algorithm                               |    |

| 3.6 Optimum finger cell library design flow                               |    |

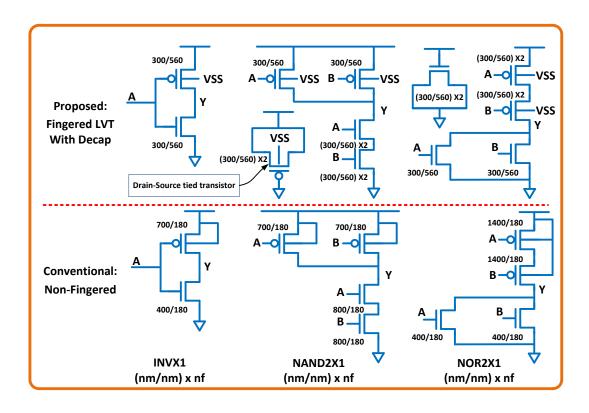

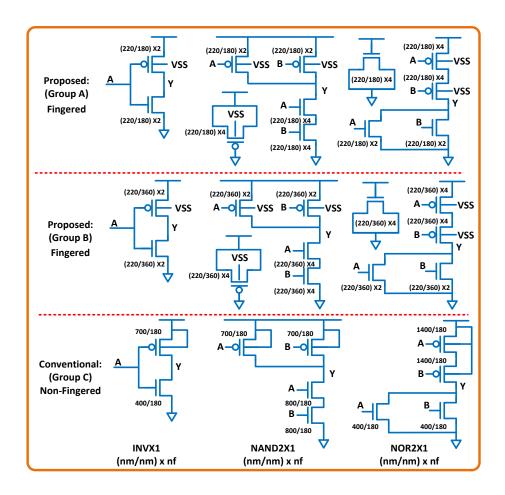

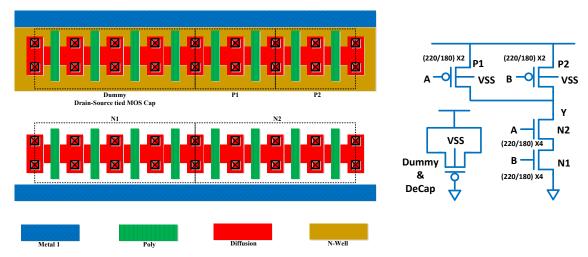

| 3.7 LVT cell schematic                                                    |    |

| 3.8 OF cell schematic                                                     |    |

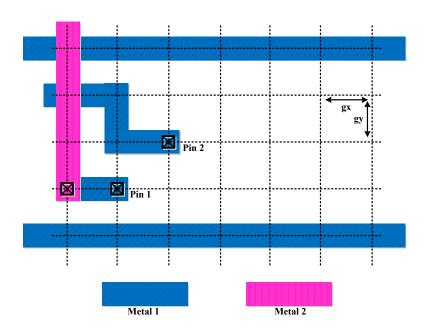

| 3.9 Cell library abstraction                                              |    |

| 3.10 Cell library layout pitch and grid                                   |    |

| 3.11 NAND2X1 layout style                                                 |    |

| Figure                                                                      | Page |

|-----------------------------------------------------------------------------|------|

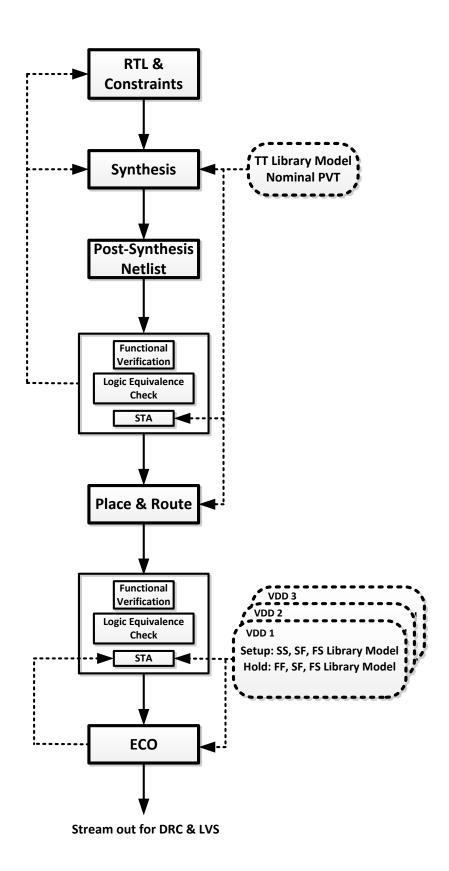

| 3.12 Design Flow                                                            | .66  |

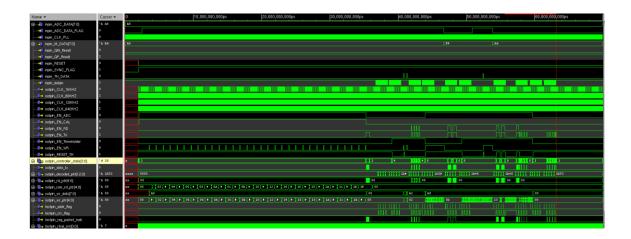

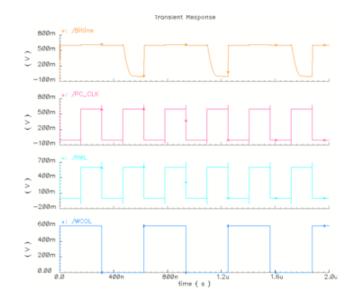

| 3.13 Top level functional simulation of the digital core                    | .68  |

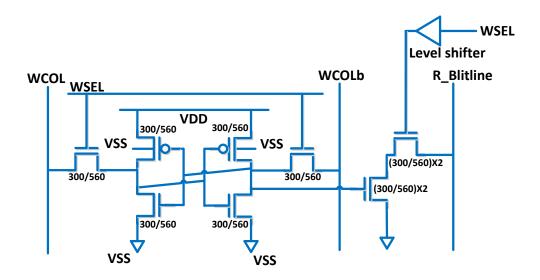

| 3.14 8T SRAM memory cell schematic                                          | .71  |

| 3.15 8T SRAM memory simulation waveform                                     | .71  |

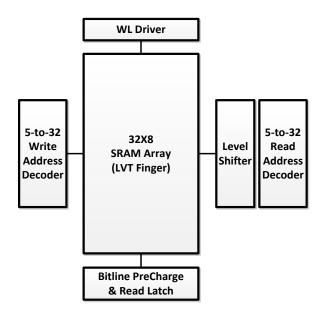

| 4.1 Block diagram of 32X8 SRAM Memory                                       |      |

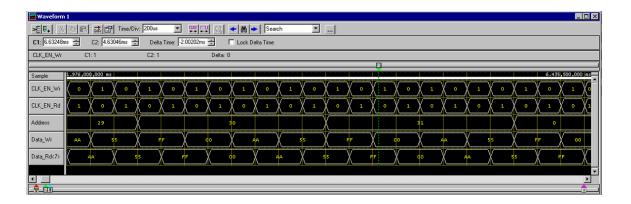

| 4.2 SRAM memory functional testing waveform                                 | .75  |

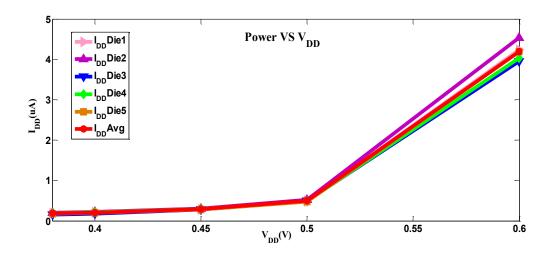

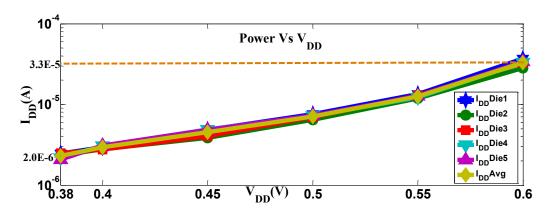

| 4.3 SRAM memory power sweeping measurement result                           | .76  |

| 4.4 SRAM memory frequency sweeping measurement result                       | .76  |

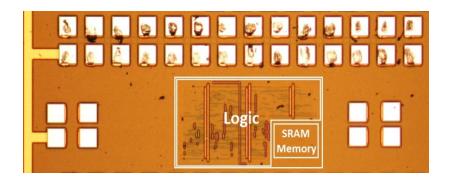

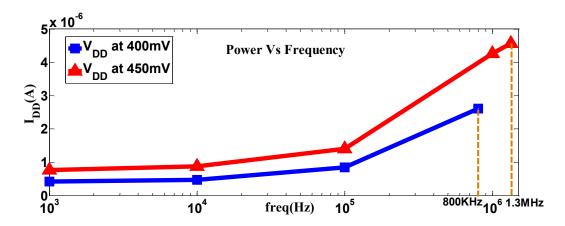

| 4.5 die microphotograph of Digital core LVT implementation                  | .77  |

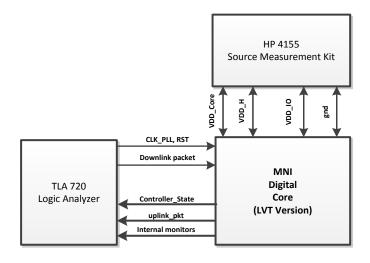

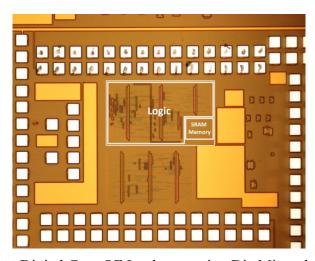

| 4.6 Digital core testbench (LVT implementation)                             | .77  |

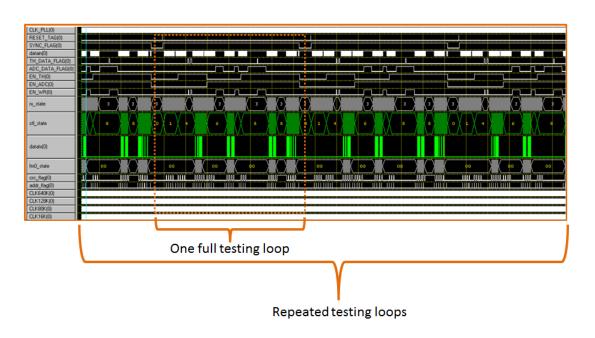

| 4.7 Digital core functional testing waveform (LVT implementation)           | .78  |

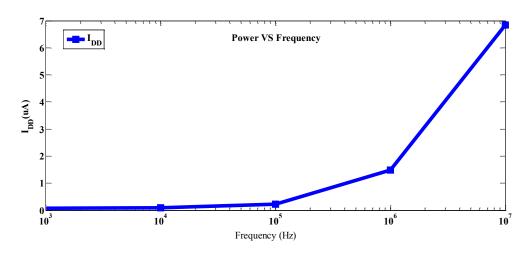

| 4.8 Digital core power sweeping measurement result (LVT implementation)     | .79  |

| 4.9 Digital core frequency sweeping measurement result (LVT implementation) | .80  |

| 4.10 Digital core shmoo plot (LVT implementation)                           | .80  |

| 4.11 Digital core die microphotograph (OF implementation)                   | .81  |

| 4.12 Digital core testbench (OF implementation)                             | .81  |

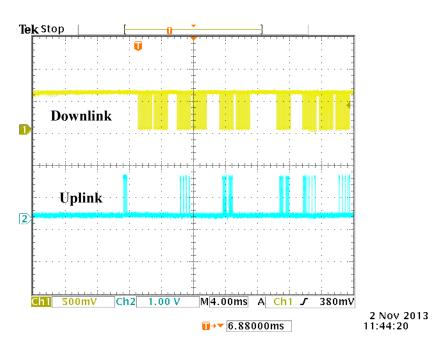

| 4.13 Digital core communication waveform (OF implementation)                | .82  |

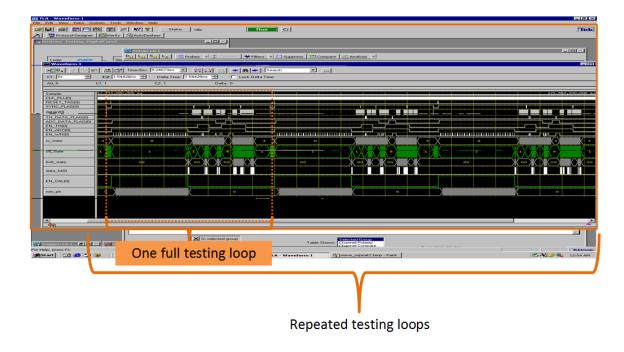

| 4.14 Digital core functional testing waveform (OF implementation)           | .83  |

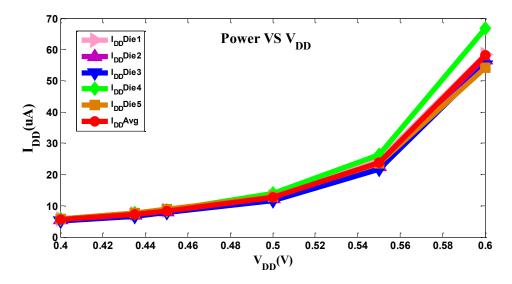

| 4.15 Digital core power sweeping measurement result (OF implementation)     | .84  |

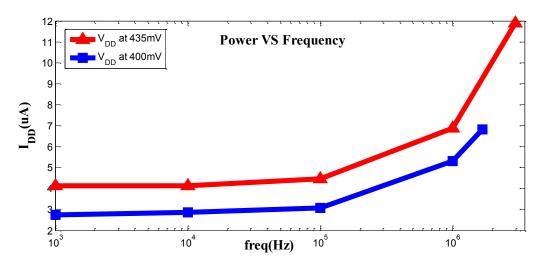

| 4.16 Digital core frequency sweeping measurement result (OF implementation) | .84  |

| 4.17 Digital core shmoo plot (OF implementation)                            | .85  |

## **GLOSSARY**

## **Abbreviations:**

ADC - Analog to Digital Converter

AFE - Analog Front End

AMS-FE - Analog and Mixed Signal Front End

ASIC - Application Specific Integrated Circuit

ASIP - Application Specific Instruction-set Processor

BIST - Built-In Self Test

BW - Bandwidth

CMOS - Complementary Metal Oxide Semiconductor

CMP - Chemical-Mechanical Polishing

CNS - Central Nervous System

CRC - Cyclic Redundancy Check

DAC - Digital to Analog Converter

DRC - Design Rule Check

DFS - Dynamic Frequency Scaling

DIBL - Drain-Induced Barrier Lowering

DSM - Deep Sub-Micron

DUT - Design Under Test

DVS - Dynamic Voltage Scaling

DVFS - Dynamic Voltage and Frequency Scaling

ECG - Electrocardiography

ECO - Engineering Change Order

EDA - Electronic Design Automation

EDP - Energy Delay Product

ELC - Encounter Library Characterizer

EEG - Electroencephalography

EMG - Electromyography

EPC - Electronic Product Code

ETS - Encounter Timing System

FSM - Finite State Machine

GDS - Graphic Database System

GIDL - Gate-induced Drain Leakage

GUT - Gate Under Test

HDL - Hardware Description Language

HF - High Frequency

HVT - High Threshold Voltage

IBM - International Business Machine, Inc.

IC - Integrated Circuit

IEEE - Institute of Electrical and Electronics Engineers

INWE - Inverse Narrow Width Effect

ISO - International Standard Organization

IVEC - In Vivo Electrochemistry

I<sub>DN</sub> - NMOS Drain Current

I<sub>DP</sub> - PMOS Drain Current

LEACH - Low Energy Adaptive Clustering Hierarchy

LEF - Layout Exchange Format

LOCOS - Local Oxidation of Silicon

\*.lib - Liberty

LVS - Layout Versus Schematic

LVT - Low Threshold Voltage

MAC - Media Access Control

MCU - Micro-Controller Unit

MEG - Magnetoencephalography

MNI - Micro-Neural-Interface

MPW - Multi-Project Wafer

MSVLSI - Mixed Signal VLSI lab

MTCMOS - Multi-Threshold CMOS

NI - Neural Interface

NLOPALV - Non-Linear, Operating Point Analysis of Local Variations

NMOS - N- type Metal Oxide Semiconductor

NRZ - Non-Return Zero

NTC - Near-Threshold Computing

NWE - Narrow Width Effect

OF - Optimum Finger

OS - Operating System

OSU - Oklahoma State University

OTS - On-The-Shelf

PGS - Power Gating Switch

PLL - Phase Lock Loop

PMOS - P- type Metal Oxide Semiconductor

PNS - Peripheral Nervous System

RF - Radio Frequency

RF-DC - Radio Frequency to Direct Current

RFID - Radio Frequency Identification

RSCE - Reverse Short Channel Effect

RVT - Normal Threshold Voltage

RZ - Return Zero

SDF - Standard Delay Format

SNM - Static Noise Margin

SNR - Signal to Noise Ratio

SOI - Silicon on Insulator

SPEF - Standard Parasitic Exchange Format

STA - Static Timing Analysis

STI - Shallow Trench Isolation

TX - Transmitter

PCB - Printed Circuit Board

PDK - Process Design Kit

PIE - Pulse Interval Encoding

P&R - Place and Route

RAM - Random Access Memory

ROM - Read Only Memory

RTL - Register Transfer Level

RX - Receiver

SBD - Schottky Barrier Diode

SCE - Short Channel Effect

SMP - Shape Memory Polymer

SOC - System On Chip

SRAM - Static Random Access Memory

VCO - Voltage Controlled Oscillator

VCSEL - Vertical-Cavity Surface-Emitting Laser

UEA - Utah Electrodes Array

UMA - Utah Microelectrode Array

U<sub>T</sub> - Thermal Voltage

USA - Utah Slant Array

UTBB - Ultra Thin Body BOX

VLSI - Very large scale integration

VCD - Value Change Dump

$V_T$  - Threshold Voltage

$V_{TH}$  - Threshold Voltage

$V_{\text{THN}} \qquad \quad \text{-} \qquad \quad \text{NMOS Threshold Voltage}$

$V_{\text{THP}}$  - PMOS Threshold Voltage

WSN - Wireless Sensor Network

#### CHAPTER I

### INTRODUCTION

### 1.1 Neural Interface Overview

Understanding the human brain and body is one of the most generation-spanning and challenging effort of human society to explore the meaning of our self-existence, life and universe. "Who are we, why we are here, and where we are going" are the three most fundamental questions have been asked since our quest for truth. Plato, Descartes and other ancient sages contributed metaphysics and idealism to the body of human knowledge and significantly influenced several generations of society. However, it is not until the availability of sufficiently mature medical, surgical and measurement technology it was made possible for people to explore ourselves through physiological means to give both qualitative and quantitive analysis of health and to some extent, cognition. Telemetry, a technology that allows measurement and transmission of information at an inaccessible location to an accessible location where measured data can be stored, displayed and processed by external and peripheral equipment, has evolved and been utilized from its origin in battlefield to many places including biomedical field[1-4].

Biomedical telemetry first came up with a radio cardiograph in a French journal in 1956, since then this technology has been adopted in manned space flight. From simulated flight in the training session, to real flight in a mission, a pilot's physiological characteristics such as heart beat, pulse, and temperature could be supervised to provide biomedical information. This data could then be used for astronauts selection or to ensure their safety. In 1968, Evarts first recorded the

electrical activity of individual neurons from living animals, starting the field of research on neurophysiology with biomedical telemetry being used as an essential technique in the experiments[5]. In 1978, Dr. Mirowsk was the first one who used transistors as a "circuit for monitoring a heart and for effecting cardioversion of a needy heart"[6]. Micro wires, cone electrodes and arrays were developed as the transmission media, and integrated signal processing circuits were also designed to provide better SNR (signal to noise ratio), clinical compatibility, reliability and flexibility with minimum impacts on the subject under test[7, 8]. The first report on an implantable RFID into human body is by Dr. Kevin Warwick, who used this device to open doors, switch on lights, etc in 1998[9]. In the same year, wireless ECG monitoring was proven to be a clinical success[10]. These are just a few examples how the advances of technologies such as electronics, micro-fabrication and communication have boosted instrumentation for human body from outside to inside, and from with to without wires. The biomedical telemetry and engineering with the above stated technological advancement thereby have opened the door for neural interfacing, which helps people to understand ourselves to a deeper extent. As early as in the 1930's, it was demonstrated that electrical stimulation of a cat's brain would produce motor and emotional responses, and people could then explore the functional organization of the cat diencephalon[11]. In the late 1960's, the concept of both recording and stimulation of the brain was demonstrated by showing that the behavior of primates and adult bulls can be modified by proper stimulations[12, 13]. Around the same year, an artificial vision prosthesis was created to be implanted on the surface of the brain to restore vision sensation by direct electrical stimulation to the brain [14]. Also, substantial research efforts have been devoted to advance this work to include microchip and high density electrode arrays to even restore rudimentary vision to totally blind individuals[15-18].

A Neural-Interface (NI) creates a link between the nervous system and machines and devices outside the body by two-way communication. This enables exchange of information with the nervous system and could ultimately help analyze neurological function, as well as treat people with neurological limitation or dysfunction[19, 20], even seamless human augmentation in the future[21]. While the latter may be possible someday, the more significant and immediate application is to record and/or stimulate neurons to treat patients with a damaged nervous system. There are millions of people in America and around the world suffering from the loss of physical and mental functions due to traumatic injuries and diseases such as Parkinson's, Huntington's, Alzheimer's, and various degrees of blindness and deafness, etc [22-27]. Severe limb losses and traumatic brain injuries have placed major crisis among wounded solders and accident survivors. All these disabilities are caused by severed connection in the nervous system [28, 29], where future neural interfaces, can come to the rescue by filling this gap with artificial prostheses [30, 31]. Monitoring neural activities in behaving subjects enables a deeper understanding of the nervous system and offers the potential to diagnose neurological diseases or injuries, and treat/reverse neurological conditions. It is of great interest to understand neural sensory/motor encoding from the locations distributed across the brain to more fully understand complex processes such as intentional motor control, unintentional reflex, learning, memory and cognition [32].

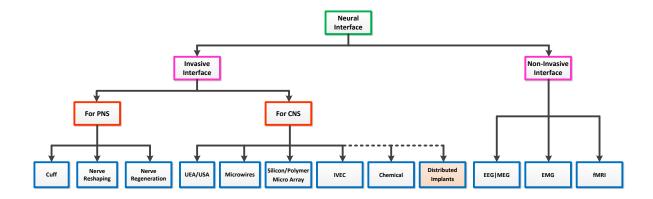

Figure 1.1 Neural interface category

As shown in Figure 1.1, neural Interfaces can be categorized into two groups: Invasive and Non-Invasive, depending on whether or not the technology requires surgical procedures that break into the skin to accomplish implantation[33]. Non-Invasive neural interface does not require surgery,

injection, or any other types of procedure to invade the body so it can be used without unwanted surgery. For example, EEG (Electroencephalography) and MEG (Magnetoencephalography) use scalp electrodes to record voltage fluctuations which are caused by brain neural activities. Although this method can provide real-time sensing through multiple channels, it has limited precision due to the long distance from the neural transmitter and spatial resolution by the limitation of the number of probes that can be placed on the scalp. It also requires sophisticated computation to extract meaningful information from the sensed composite signals [34-37]. EMG (Electromyography) shares the same concept as EEG but the signals measured are electrical activities produced by muscle cells, which are mostly used to detect medical abnormalities, measure activation levels and predict gesture movement[38, 39], fMRI (functional Magnetic Resonance Imaging) measures the brain activity by detecting changes in blood flow, which is based on the fact that brain neural activity can be monitored by observing cerebral blood flow. fMRI often provides very high spatial resolution but has low temporal resolution [40-42]. Invasive Neural Interface, on the other hand, can access to the immediate site of human or animal neural acitivity to provide incomparable accuracy on targeting neural tracts and even single neurons due to size and proximity to the signal source, but with the risk of infection and tissue damage. Invasive Neural Interfaces are often used for both PNS (Peripheral Nervous System) and CNS (Central Nervous System). PNS includes nerves that link skin, muscles and internal organs to CNS, where CNS consists of the brain and spinal cord[33]. For PNS, probing is usually achieved with Cuff Electrodes[43], Nerve Re-Shaping Electrodes[44], or Nerve Regeneration Arrays[45]. In CNS, brain is responsible for high level functions such as cognition and voluntary motions, while the spinal cord is responsible for low level autonomic functions and reflexive response. CNS is typically interfaced using arrays of penetrating micro-fabricated electrodes inserted into the tissues. Examples includes UEA (Utah Electrodes Array) and USA (Utah Slant Array), which were invented by researchers at the University of Utah[46, 47]. Later the UEA is paired with wireless power and communication with the aid of low power circuit designs [48]. Microwires use fine wires to record and stimulate the brain with one special feature which is the flexibility to shift position with

neuron movement, avoiding the loss of signal strength[49]. Silicon/Polymer Microelectrode Arrays provide a flexible and biocompatible means for the adaptive implantation, reducing brain micromotion rejection [50-53]. IVEC (In Vivo Electrochemistry) is used for real time detection and quantization of neurochemicals in living tissue[54]. Chemical Stimulation is a concept that allows stimulation of neuron tissues with chemical stimulus but to date there are no mature fabrication technologies to fine control the scale of such system. Distributed Implant combines state-of-the-art neural probing with existing technologies such as WSN (Wireless Sensor Network) and RFID (Radio Frequency Identification) to develop large scale, high resolution and bio-compatible neural interfaces for continuous and chronical neural monitoring. A Neural interface formed by distributed neural probes can provide incomparable site coverage and bandwidth which made possible to develop advanced prosthetic limbs with dexterous control functions for amputees [55-58].

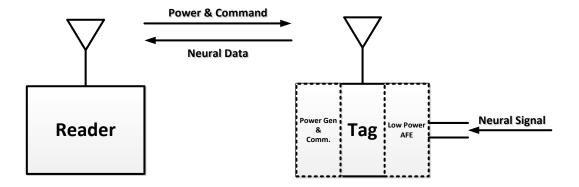

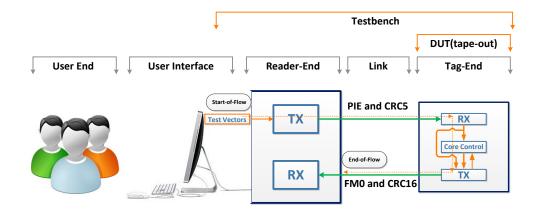

The general form of the popular RF-powered wireless neural recording system is shown in Figure 1.2 which often works as Reader (base station) -Tags (transponders with sensory circuits) pairs similar to passive RFIDs. The reader transmits RF waves to power and communicate with the passive sensor tags. Downlink data is recovered by the tag demodulating the incident wave. Uplink data is encoded and backscattered by the tag modulating its impedance to reflect the incident wave and then decoded by the base station. This enables neural interfaces to have low cost, small form factor, implantable, addressable and distributed sensing capability with a theoretically unlimited lifespan.

Figure 1.2 Common form of wireless neural interface

# 1.2 Existing Work in Neural Interface

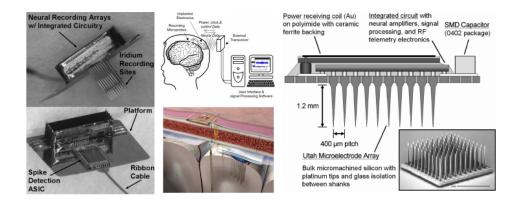

In recent years there have been tremendous advances in collaborative research on wired and wireless neural recording systems to develop low power circuit designs to improve signal-to-noise ratio, wireless powering and communication with low power consumption [59-61]. Numerous neural interfaces have been developed for clinical research experiments with the assistant of integrated circuit chips. This section reviews existing work of state-of-the-art neural interface within the past decade that use a fully functioning SoC to process sensed neural signals and of suitable form for implantation. These surveyed designs all have electrodes or arrays for neural signal acquisition and the most commonly deployed form is a derivation of UMA (Utah Microelectrode Array [48]) for multi-channel recording. A few examples of such systems are shown in Figure 1.3.

Figure 1.3 Examples of state-of-the-art Neural Interfaces [48, 62, 63]

As a result to support multi-channel recording, low power low noise band pass amplifiers with multiplexers are used extensively in these systems to address the needs of signal conditioning. Some systems like [48, 62, 64-70] added low power ADCs and/or comparators to digitize neural samples and/or record neural spike events so the data can be transmitted from the recording site to external devices and then be recovered for study. The way that neural data is handled and transmitted varies widely ranging from using simple shift registers to application specific processor unit. The most popular method is to use shift registers to directly stream the serial data out for its simplicity, such as

in [62, 66, 68-70]. To maintain proper scheduling of data communication with a large scale deployment of sensors, low power processors with support of general purpose instruction set and light weight OS (operating system) were used for high level system management [65, 67, 71]. What lies between is custom logic and controllers that can maintain application specific control/scheduling of data transmission at a secure level while keeping operation overhead minimum to optimize power and communication efficiency. Custom logic offers the best performance power trade-off, however at high design time cost and multiple engineering iterations due to the complex nature of the nervous system and stringent constraints. The surveyed systems operate at power supply voltages ranging from 1V to 5V and have power consumption ranging from tens of  $\mu$ W to over a hundred mW to support anywhere from a few Kbps to a few Mbps of communication data rate respectively. Table 1.1 summarizes the survey.

Table 1.1 Survey of existing work in neural interface SoC

| work                | Year | AFE                  | Neural Data Handling       | Uplink     | VDD     | Power/Ch | Probe Form        |

|---------------------|------|----------------------|----------------------------|------------|---------|----------|-------------------|

| Michigan Probe [64] | 2005 | Amp + Mux            | Binary Counter             | N/A        | 3 V     | 2.2 mW   | microelectrodes   |

| 3D probe [62]       | 2005 | Amp+Comparator + ADC | Mux+Shift Register         | 100 Kbps   | 3V      | 170 μW   | Array + Chip      |

| MICA2 NI [65]       | 2006 | OTS Amp              | TinyOS                     | 9.6 Kbps   | 3 V     | 66 mW    | РСВ               |

| Utah Array [48]     | 2007 | Amp+Comparator+ADC   | Mux+Custom frame           | 100 Kbps   | 3.55V   | 13.5 mW  | Array + Chip      |

| Neural WISP [67]    | 2009 | Amp + Comparator     | MSP430 + Gen2              | 360 bps    | 1.8 V   | 36 μW    | РСВ               |

| Michigan Probe [63] | 2009 | Amp + ADC            | Custom Controller          | 2 Mbps     | 1.5~3V  | 225 μW   | Array + Chip      |

| HermesC-INI3[66]    | 2009 | Amp + ADC            | Shift Register             | 345.6 Kbps | 4 V     | 63.2 mW  | Array + Chip      |

| HermesD [68]        | 2010 | Amp+ ADC             | Shift Register             | 24 Mbps    | 5 V     | 142 mW   | Array + Chip      |

| Brown [69]          | 2011 | Amp + ADC            | Laser for transmission     | 40KSps     | N/A     | 12.5mW   | Chip+VCSEL        |

| 3IC-NI [70]         | 2012 | Amp + ADC            | Direct TX                  | 54.24 Mbps | 1/1.8 V | 21 mW    | Electrode + Chip  |

| Brown [72]          | 2012 | Amp                  | Controller + VCSEL         | N/A        | 3V      | 30.2mW   | Array +PCB + Chip |

| [71]                | 2012 | Amp + ADC            | Event Based Processor Unit | 4 MHz      | 1.2 V   | 377 μW   | Chip              |

| NUS [73]            | 2013 | Amp + ADC            | Custom Logic               | N/A        | 1/1.8 V | 1.16 mW  | Array + Chip      |

The emphasis on improving these systems has been on the development of fine microelectrodes and micro-arrays fabrication technologies, low power low noise band pass amplifiers, low power comparators and ADCs, and efficient energy harvesters. Little attention has been focused on custom low power digital design to suit the application specific needs. Most systems consume power from hundreds of  $\mu$ W to tens of mW and have data rates of a few hundred bps to a few hundreds Kbps [48, 62-73]. These design constraints place fundamental limitations on wireless power and communication with neural interfaces embedded within the brain [74, 75].

# 1.3 Challenges

Current Neural Interface technologies provide monitoring and stimulation to a limited extent and have not yet reached a point where it can be said to be fully human body compatible and chronically functional with sufficient interfacing resolution and site coverage. The physical limitations of the nervous system, fine granularity and distributed nature place even more stringent constraints on the development of neural interface for advanced sensing and recording.

First, local neural tissue temperature increase resulting from implanted electronics and RF power dissipation must be kept below ~1°C. This limitation requires that the entire electronics powered by far-filed RF energies must have power budgets of a few hundred μW while maintaining all functionalities [76, 77]. Second, neural spikes (action potentials) usually last for 1~2 ms with a wide range of firing rates ranging from 0.5 Hz to 500 Hz, depending on the recording location and behavioral state of the subject. It is essential to capture trains of action potentials at different regions simultaneously to understand the spatial and temporal relationships of the spikes to subject behavior [78]. Third, inter/intra-spike timing is relevant for understanding network functions due to possibilities of timing codes, so it is critical to obtain millisecond precision to describe the temporal phasing between spikes. Therefore it is desirable to develop a neural interface capable of recording the frequency of spike generations, inter/intra-spike timing and spike strains, and the geographical

feature of spikes across the brain simultaneously and continuously to extract the neural spikes rate code, temporal code and spatial code. Traditional array based neural interfaces are no longer an adequate means to monitor neural activities on a larger scale, such as across the cortex. Having several tens, or hundreds, of distributive probes implanted under the skull can elegantly address this issue. However, this requires technologies that allow safe probe insertion and efficient communication for all probes to update neural data without interfering with one another while maintaining temporal accuracy.

Neural Interface (NI) development is highly inter-disciplinary in nature and also demand advances in bio-compatibility, fine micro-electrode/array fabrication, low power analog front-end (AFE) for neural signal conditioning and power harvesting techniques. The focus of this work is in custom low power digital design to bring a radical solution addressing the above stated challenges.

### 1.4 Thesis Contributions

The goal of the funding project is to design and implement a SoC (System on Chip) for distributive and implantable neural interface sensors, which can be used for chronical cortex neural monitoring and serve as a tool for developing the next generation neural prosthetic devices. This work focuses on the digital baseband circuit and system design aspect for such system. The major contributions of this work include:

• Custom tailored protocol with EPC Gen-2 feature for efficient control and communication An innovative custom protocol is developed to control the proposed MNI system operation. The protocol, with which the sensor tags are controlled by reader commands, allows state transition and data query of the MNI sensors with little communication overhead, and enables three different modes (Stamp Mode, Streaming Mode and Snippet Mode) to record different aspect of neural spikes. This gives possibility of extracting neural spikes temporal, spatial and rate coding with the aid of such system. With aggressive voltage scaling, power can be significantly reduced with the penalty of performance and robustness. Non-ideal effects from fabrication process exacerbate circuit energy efficiency and reliability in Sub/Near-Threshold region under this reduced supply. We carefully examined INWE (Inverse Narrow Width Effect), RSCE (Reverse Short Channel Effect) and Threshold Variation and consider these effect comprehensively for energy efficient gate sizing for low power cell library. We proposed optimum finger methodology to obtain optimum finger geometry which yields the optimum energy efficiency as a unit device for our cell library. The resulted cell library gate design shows 76% ~ 90% reduction in EDP (Energy-Delay Product) compared with conventional sizing method and significantly reduced ECO (Engineering Change Order) time during physical implementation for timing closure and energy optimization.

Low Power Cell Library using Optimum Finger Design Methodology

- Low Power Sense-Amp-Less 8T SRAM With Read Boost

- A 32X8 SRAM memory which has 8T bitcell, with isolated read path for non-destructive read and level shifter on read pass transistor is designed to serve as on chip neural data storage.

- Silicon Implementation of low power digital baseband core for wirelessly power Micro-Neural-Interface for cortex neural signal extraction

A digital baseband core is designed to implement the proposed custom MNI protocol and demonstrate our optimum finger methodology. The design is taped-out using IBM 180nm standard CMOS technology via MOSIS MPW service. Measurement results show the digital core consumes 2.2 μW average power with 1.28MHz system clock and 400mV power supply for 640Kbps data rate, resulting in a communication power efficiency of 290 Kbps/μW.

# 1.5 Thesis Organization

This thesis is organized into six chapters. Chapter 1 presents the background of the funding project, which covers overview of neural interfaces and brings up the challenges and motivation of the work. Chapter 2 describes the concept of proposed MNI and presents the custom MNI protocol for control and communication. Chapter 3 discusses the digital core design which implements the MNI protocol. It discusses in detail of the design issues of low power digital design including INWE, RSCE and variation, and presents our proposed optimum finger methodology for energy efficient operation and design flow that uses the developed optimum finger cell library. Chapter 4 presents the silicon implementation and measurement results. Finally, the conclusions, future work and discussion are given in Chapter 5.

#### CHAPTER II

### MNI PROTOCOL DESIGN

# 2.1 MNI System Overview

As noted in Section 1.2, the emphasis of previous work has been focused on the development of fine microelectrodes and micro-array fabrication technologies, low power low noise band pass amplifiers, low power comparators & ADCs, and efficient energy harvesters. Little attention has been focused on custom low power digital design to suit the application specific needs. The computation speed and communication bandwidth of previous work does not satisfy the needs of advanced neural experiment to record with acceptable temporal and spatial resolution to meet research and medical diagnostic requirements while extracting inter/intra-spike timing. General purpose design methodologies introduce unwanted power dissipation and unacceptable latency in neural interfaces to meet the application specific constraints.

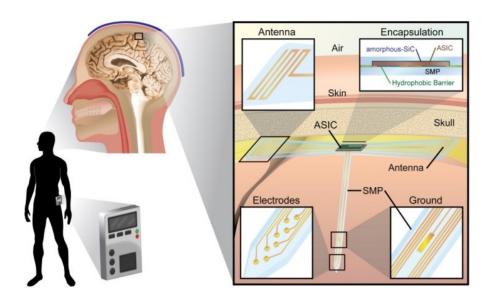

The MNI (Micro-Neural-Interface) proposed in this effort is a distributed neural interface using a custom ASIC approach to satisfy the requirements of extreme in low power, small form factor and medium/high fidelity data logging for complex neural recording applications. Shown in Figure 2.1, the wireless, battery-free MNI ASIC chip sits on top of a SMP (Shape Memory Polymer) substrate with off-chip antennas at the edge, neural electrodes vertically bonded and penetrating down to the deep brain for sensing neurological signals. The MNI is encapsulated inside of stable inorganic coating such as amorphous SiC material for physical isolation from the in-vivo tissue fluid, biomedical compatibility and minimum RF power delivery loss[79].

Figure 2.1: Concept of Micro-Neural-Interface for extracellular neural recording with wirelessly powered ASIC implanted under the skull (Figure Courtesy of Robert Rennaker)

The MNI sensor tags are aimed to be inserted and placed under the skull of the behaving subject at desired physical locations through surgery. During normal operation, the MNI ASIC receives modulated RF waves from external base station as the energy harvesting source to power functional circuits. Demodulated signals are used as control commands to maintain/change system states and upload neural data.

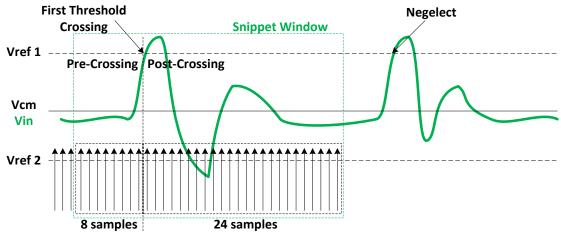

Three data collection modes are designed for neural recording. They are *Time Stamp Mode*, *Streaming Mode* and *Snippet Mode*. In Stamp mode, the MNI records neural spike occurrence as well as the time interval between consecutive spikes, using simple threshold crossing events with a remotely programmable reference voltage. In Streaming Mode, the MNI continuously digitizes the sensed neural signal with 8 bit resolution at 16 KS/s sampling rate and stores the data into the on-chip memory. In Snippet Mode, the system awaits for a neural spike to cross a pre-defined reference voltage which is programmed on-the-fly using predefined downlink command. In the Snippet Mode, when a threshold crossing event is observed by the spike detector, only the

preceding 8 samples and 24 samples after the threshold crossing are to be stored in the memory, making more efficient use of the communication bandwidth.

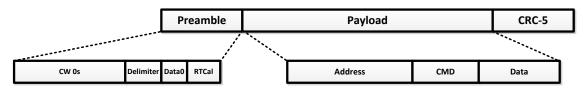

## 2.2 MNI System Architecture

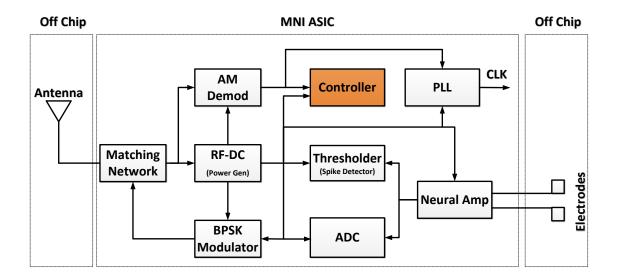

The MNI ASIC system level block diagram is shown in Figure 2.2. The MNI system works as a fully passive RFID with sensing capability. One of the challenges when designing this system is to integrate three analog front end circuits: a low power low noise band pass amplifier, a low power 8-bit ADC at sampling rate of 16 KS/s and a spike detector (Thresholder) consisting of dual comparators with programmable references with stringent power budget. These analog blocks have power supply regulated at 700mV for low power operation. Another challenge is to minimize the power consumption of the digital logic which manages control and communication without sacrificing functionality and performance. The digital control logic has its power supply voltage regulated at 400 mV and has been carefully designed to be fully functional under such down-scaled power supply.

Figure 2.2: Block diagram of Micro-Neural-Interface

Differential neural signal input from the sensing electrodes is first amplified with the low noise band pass amplifier. The amplified signal is then either digitized by an 8-bit pipeline ADC at 16KS/s or compared with reference voltages by the Thresholder at 16 KHz for spike detection. The captured neural data can be stored with on-chip memory and be used to form outbound packet as sensor tag responses. The controller also decodes/encodes data and transmits them by modulating the impedance of the matching network for backscattering, which establishes uplink data communication.

# 2.3 MNI System Operation

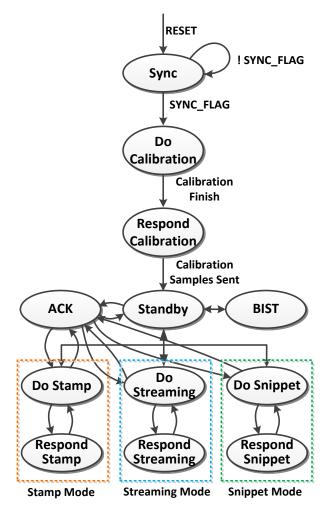

The MNI operation is summarized in the simplified state diagram shown in Figure 2.3. The digital controller core maintains a total number of 12 states for system operation, among which 6 states are used for the three data collecting mode. This section describes each of the states.

Figure 2.3: State diagram of MNI system operation

# 2.3.1 Power up & Sync

The MNI requires a stable power supply and a synchronized clock before executing any task. Upon powering up when receiving RF power and the supply voltages reaching steady state, the RF-DC circuit sends out a power on reset signal to asynchronously reset all registers in the controller core. The state of the controller enters Sync Mode. During this startup period, the PLL is powered up and synchronizes its VCO (Voltage Controlled Oscillator) oscillation with the embedded clock from the demodulator, which demodulates the incident wave from the base station. After lock is achieved by the PLL, the system clock is synchronized with the base station reference clock and a SYNC FLAG triggers the controller core to enter Do Calibration Mode.

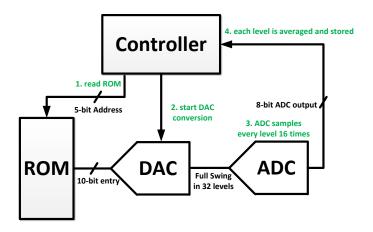

# 2.3.2 Do Calibration (ADC Calibration)

The stringent power requirement of being limited to a few hundred µW maximum puts a severe constraint on the analog signal path, particularly on achieving ADC accuracy. There are many sources of analog errors to manage under such limited power budget. These errors result from manufacturing variation, particularly transistor and capacitor mismatch, linear finite op-amp gain, charge injection, offsets, non-ideality in reference voltage, and etc. Digital calibration is needed as a way to mitigate the above errors, which otherwise can only be solved by paying an excessive power penalty [80-82].

When the MNI enters Do Calibration Mode, the controller core enables the read operation of a calibration ROM and loops through its 32 entries. Each entry, which is a 10 bit word, will be used as the input to a calibration DAC to produce a full swing ramp with 32 levels. The ADC will initiate operations that convert the ramp signal and each of the 32 levels will be sampled 16 times to produce an averaged result to be stored. When the sampled results of all 32 levels are stored in the on chip memory, the system automatically goes into Respond Calibration Mode. Figure 2.4 shows how Do Calibration works.

Figure 2.4 Work flow of Do Calibration Mode

## 2.3.3 Respond Calibration

In Respond Calibration Mode, the 32 stored samples alongside with address of the tag are sent to the base station so the samples could be used as a correcting factor for calibrating future neural samples. The system then goes to Standby Mode after all samples are sent out.

# 2.3.3 Standby

In Standby Mode, the system power off non-necessary blocks to minimize power consumption and waits for further commands.

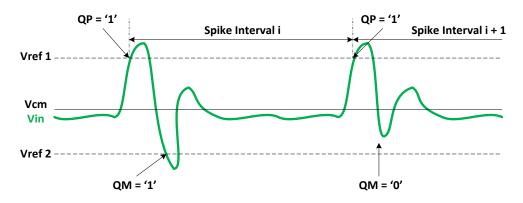

# 2.3.4 Do Stamp

In Stamp mode, the digital core controls the MNI system to record neural spike occurrences as well as the time interval between consecutive spikes, using threshold crossing events. In this mode, the analog signal path is through the fully differential band pass amplifier to Thresholder while the ADC is disabled. Upon receiving commands to enter this mode, a code in the command is used to select the two desired differential reference voltages, and the dual comparator in the Thresholder then uses these two references and samples the input with 16 KHz rate. A demonstration of this mode is shown in Figure 2.5. Upon detection of a threshold crossing event,

the comparator produces a latched QP value for positive reference crossing and QM value for negative reference crossing. A 5-bit counter clocked at 128 KHz is used to time the inter-spike duration. When the next threshold event occurs, QP, QM with the reference selection code and the spike interval value represented by counter values are consecutively written into on-chip memory. If there is only one threshold crossing event (positive or negative) triggered which caused the counter to be saturated, the saturated value is to be written to denote that the spike interval is equal or larger than the maximum countable duration. The system will remain in this state with memory being overwritten with the latest recordings until a new command is received and triggers the state transition.

Figure 2.5: Demonstration of Do Stamp Mode

## 2.3.5 Respond Stamp

The Respond Stamp Mode is triggered when MNI is queried with a command for updating time stamp recordings. In this mode, neural data in memory will be read with a clock frequency of 80 KHz, and used to construct a variable length packet for outbound transmission at a data rate of 640 Kbps. Meanwhile, the Thresholder keeps functioning for neural spike detection and writes to memory if a new spike is detected. After sending out a packet, the system will return to Do Stamp Mode. It is assumed that the base station is capable of polling the data from MNI with proper timing to avoid missing spikes.

# 2.3.6 Do Streaming

In Streaming Mode, the digital core controls the MNI to continuously sample and record the sensed neural signals. In this mode, the analog signal path is through Band Pass Amplifier to ADC while Thresholder is disabled. Upon receiving commands to enter this mode, the ADC samples the amplified neural signal with 8 bit resolution at a sampling rate of 16 Kbps, and writes the digitized samples into the on-chip memory. The system will remain in this state unless further command triggers the state transition and memory will be overwritten with the latest recordings.

## 2.3.7 Respond Streaming

The Respond Streaming Mode is triggered when MNI is queried with a command for updating the streaming recordings. In this mode, digitized samples will be read with a clock frequency of 80 KHz and used to construct a fixed length packet for outbound transmission at data rate of 640 Kbps. Meanwhile, the ADC keeps functioning to continuously digitize neural samples and writes memory. After streaming out a packet containing all data from the memory, the system will go back to Do Streaming Mode. Again, it is assumed that the base station is capable of polling the data from MNI with an adequate timing to avoid loss of data.

# 2.3.8 Do Snippet

In Do Snippet Mode, the system waits for a neural spike to cross a pre-defined reference voltage. When a threshold crossing event is detected, only the preceding 8 samples and 24 samples after the threshold crossing are stored in the memory. In this mode, Band Pass Amplifier, Thresholder and ADC are all enabled and functioning. Upon receiving commands to enter this mode, a code in the command is used to select the two desired differential reference voltages. The dual comparator in the Thresholder uses these two references and samples the input with 16 KHz rate, as in Time Stamp Mode. The ADC, in the meantime, samples the neural signal and continuously writes the digitized data into the on chip memory. When any of the positive or negative thresholds are crossed by the input signal, a spike occurrence is said to have been detected. At

this moment, the ADC will write the next 24 samples into the memory and then stops. After this process, the data stored in the memory contains the 8 samples before the threshold crossing and 24 samples after the threshold crossing, which is defined as a useful segment and is of great interest for neural science research. The sensing is suspended after the memory is filled with this spike segment of interest. Figure 2.6 shows a demonstration of Do Snippet Mode.

Figure 2.6 Demonstration of Do Snippet Mode

# 2.3.9 Respond Snippet

The Respond Snippet Mode is triggered when the MNI is queried for updating the snippet data. In this mode, the snippet samples are read with a clock frequency of 80 KHz and used to construct a fixed length packet for outbound transmission at 640 Kbps. After sending out a packet, the system returns to Do Snippet Mode. Again, it is assumed that the base station is capable of polling MNI data with proper timing to avoid loss of data.

## 2.3.10 ACK & Chatterbox BIST

If the MNI is in any of the following modes: Standby, Do Stamp, Do Stream and Do Snippet Mode, the system can be triggered to enter ACK (Acknowledgement) or Chatterbox BIST Mode for quick debugging purposes with minimal impact on neural recording. In ACK Mode, the system keeps doing neural recordings as in the previous mode but reply a short uplink packet

containing only the bits representing tag address, operation mode and Thresholder reference selection codes. After the packet is sent, the system will go back to the previous mode. In Chatterbox BIST Mode, the system will stop the neural recording and continuously send out the short packet containing address, operation mode and reference selection code repeatedly until a new command triggers it to transit to another state.

# 2.4 System Constraints and Impact on Digital Core Design

The MNI has to consume minimum power despite its complex operations in order to reduce the possibility of tissue over-heating and neuron cell damage. Table 2.1 summarizes the power budget for each critical building block in MNI system. As is shown, digital control and memory place a heavy load on the power and must be optimized for energy efficiency. The digital controller core manages the system through proper control and efficient communication. Proper system operation includes controlling state transition, managing block-to-block interfacing, data processing (such as spike discrimination and data manipulation), establishing protocol processing for downlink packet decomposition and uplink composition. It is highly desired that the digital core to address the need for Kbps data rate protocol processing with just a few  $\mu$ W power budget. With these design specifications and constraints in mind, the next section will survey relevant work for suitable solutions.

Table 2.1 Power budget for MNI building blocks

| Block                            | Power Budget (μW)    |

|----------------------------------|----------------------|

| Power Management and Voltage Gen | 20.0 [83]            |

| PLL                              | 3.0 [84]             |

| Modulator and Demodulator        | 0.2 [84]             |

| Band pass Amplifier              | 2.0 (target)         |

| Thresholder                      | 0.5 (target)         |

| ADC                              | 5.1 [85]             |

| Digital Control + Memory         | <b>10.0</b> (target) |

| Total                            | 40.8                 |

# 2.5 Survey of Relevant Work in Protocols and Digital Control

Biomedical sensing systems usually work with a base station-targets or in other words, master-slaves architecture[3]. The sensor nodes respond to the base station with transmission of predetermined messages upon specific requests. Biomedical telemetry communication links will generally have low power and short duty cycle requirements for two main reasons[4]. First, low power and short duty cycle consumes less battery power or on-chip storage capacitor charge, leading to longer usage duration for active systems (with battery) and reliable transmission for both active and passive systems (with battery or battery-less); Second, low duty cycle can prevent excessive heat generation, especially when the sensors are implanted to avoid destroying the tissue or upsetting the biochemical chemistry. Frequency or phase modulation schemes are preferred, as opposed to amplitude modulation in order to feed the sensors with more RF power through RF-DC power harvesting as well as offering greater data security at cost of increased circuit complexcity and power. A summary of existing protocols is shown in Table 2.2.

Table 2.2 Survey of communication protocol for biomedical sensors

|           | Pros                                         | Cons                                                  |

|-----------|----------------------------------------------|-------------------------------------------------------|

| Bluetooth | Mature                                       | Power hungry, limited channel #                       |

| ZigBee    | Mature                                       | Low data rate and power hungry, limited channel count |

| Gen-2     | Medium data rate and mature for passive RFID | Latency penalty                                       |

| LEACH     | Evenly distribute energy load                | Not for passive sensors, inefficient communication    |

| MAC       | scalability                                  | Low temporal resolution                               |

| ANT       | Mature                                       | Low data rate                                         |

The most frequently investigated solutions to establish data transmission in biomedical telemetry systems are Bluetooth (IEEE 802.15.1 standard), Zigbee (IEEE 802.15.4 standard), EPC Global Gen2 Standard and custom designed protocols targeted to specific applications[86-91]. Bluetooth

is defined as "an open wireless protocol for exchanging data over short distances from fixed and mobile devices" [88]. As defined in Bluetooth, a master Bluetooth device will establish an ad-hoc connection with up to 7 other devices, forming a group called piconet. Two or more piconets can be connected together to form a scatternet with no interference among each other by using different hop sequences and transmitting on different 1MHz hop channels. Bluetooth operates in the 2.4GHz band and has a maximum data rate of 720Kbps. Frequency hopping spread spectrum is used to divide the bandwidth into a number of channels.

Zigbee was designed "for a cost-efficient network that supports low data rates, low power consumption, security and reliability" based on IEEE 802.15.4 low rate wireless personal area network standard. Zigbee working in star topology and is well suited for biomedical telemetry application, in which a full function device works as a coordinator while reduced function devices work as passive sensors which can be implemented with a pre-assigned address and minimal hardware [86, 89].

RFIDs, which use radio frequency electromagnetic energy to transfer data, can be categorized into Active, Semi-Active or Passive RFIDs based on the power supply technology. Active RFID tags use battery to power and normally support active transmitter for long range operation. Semi-Active RFID tags use both battery and RF power as a supplemental energy source. Passive RFID tags use only the RF power as energy source by harvesting power using an RF-DC circuit[92] and reflecting RF energy for communication [93, 94]. The EPC Global Gen-2 standard is designed for passive RFIDs in field applications such as object identification, inventory and tracking[91]. In this standard, active reader and passive tags use a random-accessed, packet-based protocol in an interrogator-responders fashion to establish communication.

MAC (B-MAC, D-MAC, S-MAC, T-MAC, Z-MAC and etc) protocols are low duty cycle prtocols utilizing various CSMA techniques and are primary for cooperative data transmission of

wireless sensors. They are suitable for scalable sensor networks, but have trade-off between energy efficiency and latency. The synchronization and re-synchronization of the network can lead to significant energy penalty and communication inefficiency, resulting in low temporal resolution in neural recording application [95]. ANT protocol is developed for wireless sensors to measure parameters that don't change rapidly (such as temperature) and update data every a few seconds [96]. It is maturely developed and used for applications with sports and smart hand held devices but has very low data rate, which made is unsuitable for neural recording.

There are other protocols which can be used for biomedical telemetry, such as IEEE 802.11[97]. But the high power consumption makes these options unrealistic with the ultra low energy constraint. For our purpose, Bluetooth suffers from limited communication channel count for the MNI is intended to deploy tens to hundreds of probes, ZigBee has a low data rate which prohibits its adoption for the required temporal resolution, 16 KS/s data rate. EPC Gen-2 addresses the above two shortcomings but has a long turn-around time because it requires several command-and-acknowledgement communications to setup the tag. None of these protocols can be directly utilized for efficient communication and control of our MNI system, and thereby a custom protocol is needed. This requires careful consideration of all constrains for cortex neural monitoring scenario.

As discussed in Section 1.2, little attention has been placed on the digital aspect of neural interfaces, so the neural data have been primarily transmitted using simple shift registers, lacking support for advanced sensing tasks and future scaling. As the basis for an innovative way to efficiently handle neural data, a survey was carried out to investigate possible solutions from existing relevant work in biomedical applications. Table 2.3 summarizes the survey of relevant work in digital control within low power and fully functional biomedical platforms. It can be seen that most work have been developed to target at general KHz biomedical sensing applications, with general-purpose processor to control and process data communication with data rate ranging

from 25 Kbps to 640Kbps. In [67, 98], the actual effective data rate is 360 bps due to the latency penalty induced by CSMA's random access overhead. It is desirable to develop a custom controller with custom protocol to support efficient control and communication to the neural recording specific application.

Table 2.3 Survey of relevant work in digital control within biomedical platforms

|                   | Tech. (μ) | Control & Comm.     | Uplink Clock Digital |          | Digital V <sub>DD</sub> | Digital Power   | Applications               |  |

|-------------------|-----------|---------------------|----------------------|----------|-------------------------|-----------------|----------------------------|--|

| Kwong [99]        | 0.13      | MSP430+Accelerators | N/A                  | 1MHz     | 0.6                     | 9.68 μW         | General KHz Biomedical     |  |

| Yeager [67]       | 0.13      | EPC Gen-2           | 640 Kbps             | 3MHz     | 0.7                     | 4.2 μW          | Body Temperature           |  |

| Chen [100]        | 0.18      | MCU + ANT           | 25 Kbps              | 20~24MHz | 0.95                    | 1.3 mW          | Capsule Endoscope          |  |

| Ricci [101]       | 0.18      | ISO 18000-6B        | 40 Kbps              | 800 KHz  | 0.6                     | 440 nW          | General RFID Sensor        |  |

| Reinisch [98]     | 0.13      | EPC HF and Gen2     | 640Kbps              | 1.92 MHz | 1                       | 3.5 μW          | Temperature Sensing        |  |

| Lee [102]         | 0.18      | EPC Gen-2           | 64 Kbps              | 100 KHz  | 0.87                    | 29.3 μW         | Healthcare                 |  |

| Constantin [103]  | 65        | ASIP                | N/A                  | 100KHz   | 0.37                    | 288 nW          | Compressed Sensing         |  |

| Zhai [104]        | 0.13      | Processor           | N/A                  | 833 KHz  | 0.36                    | 2.6pJ/Inst      | General Sensor Processor   |  |

| Hanson [105]      | 0.18      | Processor           | N/A                  | 106KHz   | 0.5                     | 226nW           | General Sensor Processor   |  |

| Yoo [106]         | 0.18      | N/A                 | N/A                  | 512KHz   | 1                       | 2.03 μJ/clasifc | EEG Seizure Classification |  |

| Wattanapani [107] | 0.18      | Custom              | 10 Mbps              | N/A      | 1.8                     | 42 μW           | Neural Recording           |  |

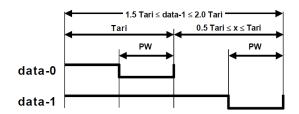

## 2.6 MNI Protocol

There are many existing encoding schemes regarding the physical layer to enhance the reliability and security when data is transmitted via RF. For passive RFIDs and low power wireless sensors both bandwidth and power limit the algorithm complexity. This most always results in a tradeoff between performance and feasibility when choosing an implementation scheme. Six mature encoding schemes [108-111] were surveyed and compared by their pros and cons, and are summarized in Table 2.4.

Table 2.4 Comparison of encoding schemes

| Encode Scheme | Pros                                                                                                   | Cons                                       | R->T downlink | T->R uplink |

|---------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------|-------------|