#### UNIVERSITY OF OKLAHOMA

#### GRADUATE COLLEGE

# THEORY, DESIGN, AND SIMULATION OF LINA: A PATH FORWARD FOR QCA-TYPE NANOELECTRONICS

A DISSERTATION

#### SUBMITTED TO THE GRADUATE FACULTY

in partial fulfillment of the requirements for the

Degree of

DOCTOR OF PHILOSOPHY

By

LOYD REED HOOK IV Norman, Oklahoma 2012

# THEORY, DESIGN, AND SIMULATION OF LINA: A PATH FORWARD FOR QCA-TYPE NANOELECTRONICS

#### A DISSERTATION APPROVED FOR THE SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING

$\mathbf{B}\mathbf{Y}$

Dr. Samuel C. Lee, Chair

Dr. Michael Santos

Dr. Monte Tull

Dr. Ronald Barnes

Dr. Qi Cheng

© Copyright by LOYD REED HOOK IV 2012 All Rights Reserved. To Tammy, Luke, Jacob, Angel, and Sunshine – my beautiful storm, solid rock, warm light, free river, and green valley

#### Acknowledgements

I would like to thank Dr. Samuel C. Lee, for his support and guidance while I pursued this research. In particular, thank you for providing me confidence when I was unsure and putting on the brakes when I was too sure. But mostly, thank you for cultivating the dreams that drive me and also daring to occasionally join me in them.

Additional thanks are due to Dr. Monte Tull, Dr. Ronald Barnes, Dr. Qi Cheng, and Dr. Michael Santos for serving on my committee. The insights and suggestions that you have provided me have greatly strengthened the content of this work.

I also must acknowledge my family and friends (especially my parents) who have strengthened and supported me through a quarter century of schooling and made sure that the paths I traveled were not traveled alone.

And lastly, I must give thanks to my Father, my Brother, and my Friend who are the source of all creativity, vision, and purpose in my life.

| Ackno   | owledgements                                | iv |

|---------|---------------------------------------------|----|

| Table   | of Contents                                 | v  |

| List of | Tables                                      | ix |

| List of | Figures                                     | x  |

| Abstra  | act                                         | XV |

| Chapt   | er 1 Introduction                           | 1  |

| 1.1     | Advancement and impact of this work         | 5  |

| 1.2     | Organization                                | 7  |

| Chapt   | er 2 Background Material                    | 9  |

| 2.1     | Quantum-dot cellular automata (QCA) Basics  | 9  |

| 2.1.1   | Cellular Automata (CA)                      | 9  |

| 2.1.2   | QCA as CA                                   | 11 |

| 2.2     | QCA Basics                                  | 13 |

| 2.2.1   | QCA Cell Structure                          | 13 |

| 2.2.2   | Theoretical Development of a model QCA cell | 14 |

| 2.2.3   | Other cell configurations                   | 18 |

| 2.2.4   | Cell to Cell Interaction                    | 19 |

| 2.3     | Logical and Communication Structures in QCA | 22 |

| 2.3.1   | The binary wire                             | 22 |

| 2.3.2   | The QCA inverter                            | 23 |

| 2.3.3   | The majority voter                          | 24 |

| 2.3.4   | Co-planer wire crossing                     | 25 |

| 2.4     | QCA Implementation Technologies             | 26 |

| 2.4.1   | Electrostatic Metal-Dot QCA                 | 27 |

## **Table of Contents**

| 2.4.2 | Electrostatic Semiconductor QCA                        | . 28 |

|-------|--------------------------------------------------------|------|

| 2.4.3 | Molecular QCA                                          | . 30 |

| 2.4.4 | Magnetic QCA                                           | . 32 |

| 2.5   | QCA Adiabatic Switching and Clocking                   | . 34 |

| 2.5.1 | Adiabatic Switching of QCA                             | . 37 |

| 2.5.2 | QCA clocking                                           | . 38 |

| 2.5.3 | Implementation of QCA Clocking                         | . 41 |

| 2.6   | QCA Logic Advances                                     | . 43 |

| 2.6.1 | QCA Fault Tolerance                                    | . 44 |

| 2.6.2 | Reversible Logic Designs and Bennett Clocking          | . 45 |

| 2.7   | Power, Speed, and Reliability in QCA                   | . 48 |

| 2.7.1 | Non-clocked QCA evaluation                             | . 49 |

| 2.7.2 | Clocked QCA circuits                                   | . 52 |

| 2.8   | Chapter Summary                                        | . 55 |

| Chapt | ter 3 Design of 2D 2-Dot Quantum Dot Cellular Automata | . 57 |

| 3.1   | Introduction                                           | . 58 |

| 3.2   | 2-D 2-Dot QCA Architecture                             | . 59 |

| 3.2.1 | Advantages of a 2-dot QCA architecture                 | . 60 |

| 3.2.2 | 2-D lattice structure of the 2-dot QCA                 | . 61 |

| 3.3   | Logic design using 2-D 2-Dot QCA                       | . 64 |

| 3.3.1 | The binary wire                                        | . 65 |

| 3.3.2 | Inverter                                               | . 65 |

| 3.3.3 | The fan out gate                                       | . 66 |

| 3.3.4 | The 2-D 2-dot planer wire crossing                     | . 66 |

| 3.3.5 | The majority gate                                      | . 68 |

| 3.3.6 | The delay flip flop (D-FF)                                         | 72 |

|-------|--------------------------------------------------------------------|----|

| 3.3.7 | The XOR gate                                                       | 73 |

| 3.3.8 | The Toggle Flip-Flop                                               | 76 |

| 3.4   | Chapter Summary                                                    | 77 |

| Chapt | ter 4 Simulation Methods and 2D 2-Dot QCA Results                  | 78 |

| 4.1   | Chapter Introduction                                               | 78 |

| 4.2   | Simulation Engines                                                 | 78 |

| 4.3   | Statistical mechanical simulation                                  | 79 |

| 4.4   | Coherence vector simulation                                        | 84 |

| 4.5   | Comparison of 2-dot and traditional QCA wire                       | 86 |

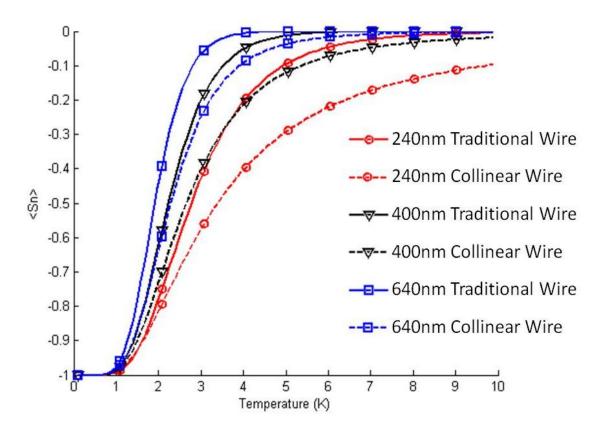

| 4.5.1 | Wire comparison simulation results                                 | 88 |

| 4.5.2 | Thermodynamic analysis of 2-D 2-dot majority gates                 | 91 |

| 4.6   | Chapter Summary                                                    | 93 |

| Chapt | ter 5 Lattice-based Integrated-Signal Nanocellular Automata (LINA) | 94 |

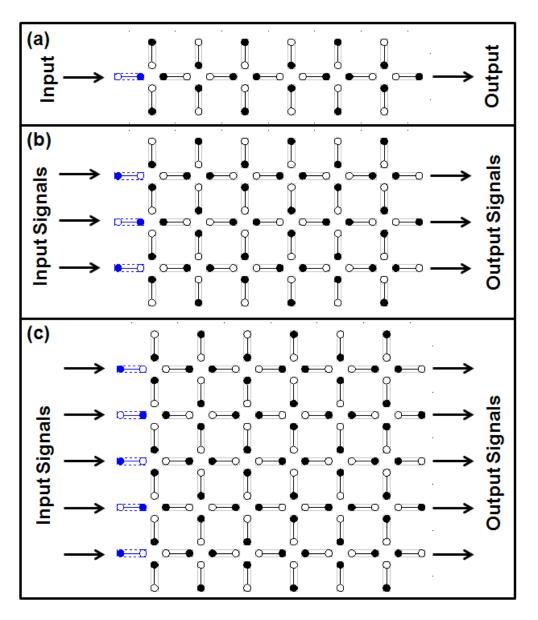

| 5.1   | Theory and Advantages of LINA                                      | 95 |

| 5.1.1 | LINA design convention                                             | 98 |

| 5.1.2 | LINA Thermal reliability improvements1                             | 01 |

| 5.1.3 | LINA robustness to fabrication defect1                             | 03 |

| 5.2   | LINA Logic Structures and Circuitry1                               | 05 |

| 5.2.1 | LINA majority gates and blocks 1                                   | 05 |

| 5.2.2 | LINA planer wire crossing1                                         | 09 |

| 5.2.3 | LINA Inverter 1                                                    | 10 |

| 5.3   | Chapter Summary1                                                   | 11 |

| Chapt | ter 6 LINA Analysis and Design Study 1                             | 13 |

| 6.1   | LINA design trade space: power, speed, geometry, and reliability 1 | 13 |

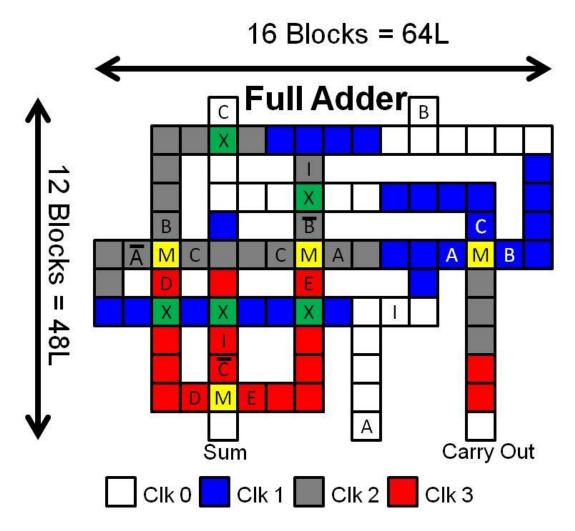

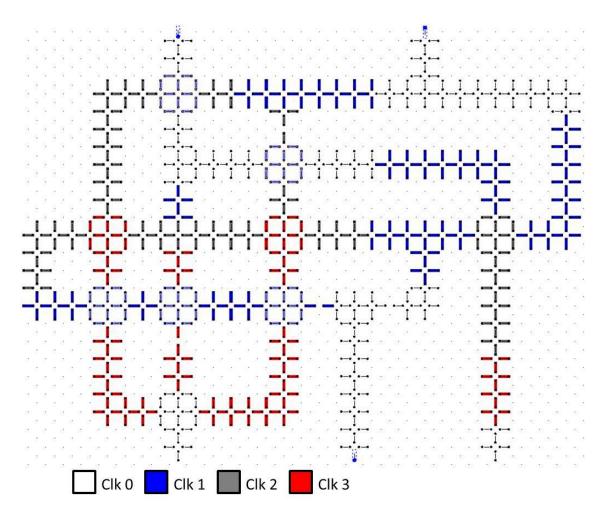

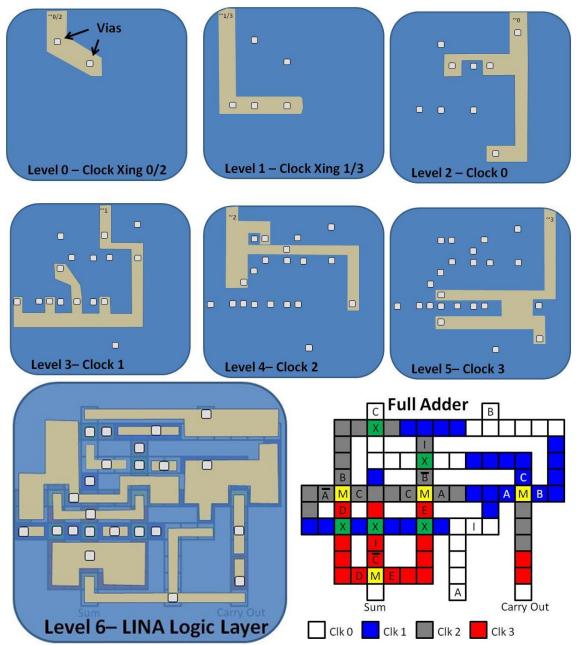

| 6.2    | LINA design examples (full adder circuit)               | 121 |

|--------|---------------------------------------------------------|-----|

| 6.2.1  | Greatest space/power efficiency approach                | 122 |

| 6.2.2  | Full adder design using practical implementation issues | 127 |

| 6.3    | Chapter Summary                                         | 132 |

| Chapt  | er 7 Summary and Future Directions                      | 133 |

| 7.1    | Dissertation Summary                                    | 133 |

| 7.2    | Future Directions                                       | 136 |

| Refere | ences                                                   | 138 |

### List of Tables

| Table 1 - Minimum full pitch and wire design parameters for various clock |       |

|---------------------------------------------------------------------------|-------|

| speeds, and reliabilities                                                 | . 121 |

## List of Figures

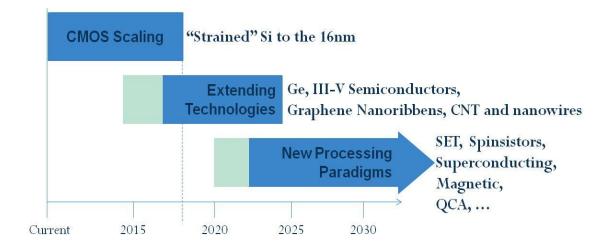

| Figure 1-1. Outlook of Computing Technologies                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

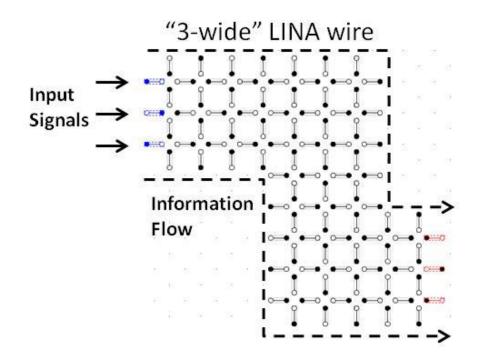

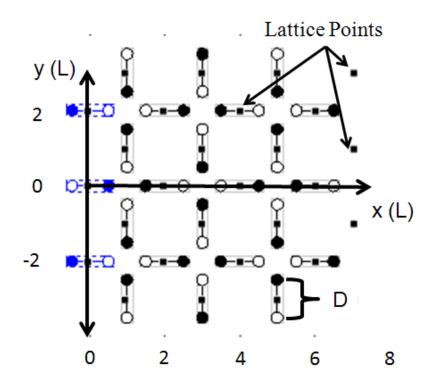

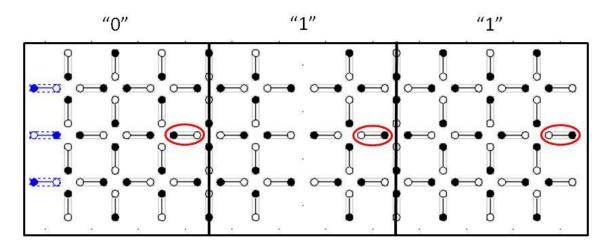

| Figure 1-2. Lattice-based Integrated-signal Nanocellular Automata (LINA) wire design structure                                                                                                                                                                                                                                                                                                               |

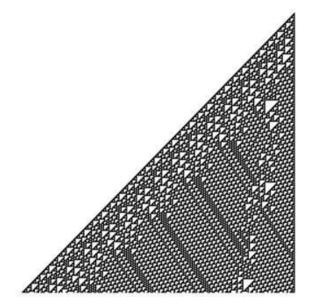

| Figure 2-1. Rule 110 CA - The figure is a graphical representation of the evolution of a 1-D array of two-state cells (white depicting a "0" state and black depicting a "1" state). The CA begins with a single "1" surrounded by all "0"s which is the top of the triangle. Each row of the figure is a discrete time step of the evolution of the cells beginning at the top and progressing down [36] 10 |

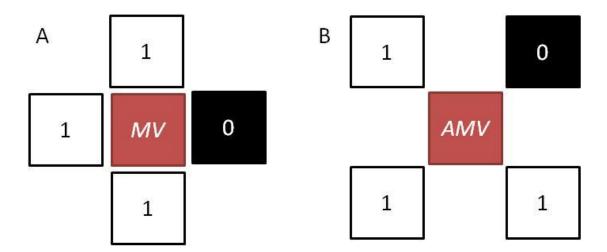

| Figure 2-2. A. Configuration of cells which produce a majority voter (MV) logical function. B. Configuration of QCA cells which produces a minority (anti-majority) voter (AMV) function                                                                                                                                                                                                                     |

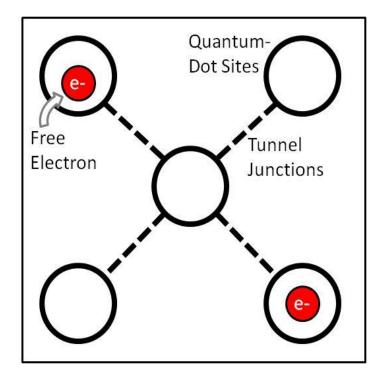

| Figure 2-3. Original QCA Cell - Here shown with two free electrons completely localized on quantum dot sites                                                                                                                                                                                                                                                                                                 |

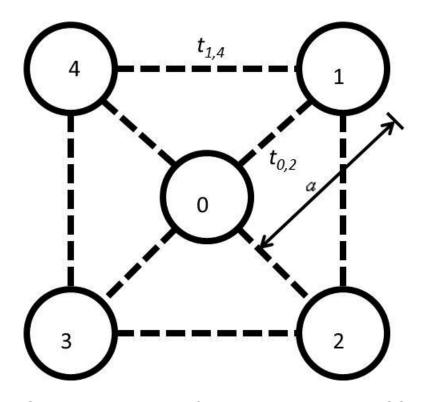

| Figure 2-4. Graphical schematic of the original "standard" QCA cells with numbered quantum dot sites, tunnel junctions, and the distance measure "a". 15                                                                                                                                                                                                                                                     |

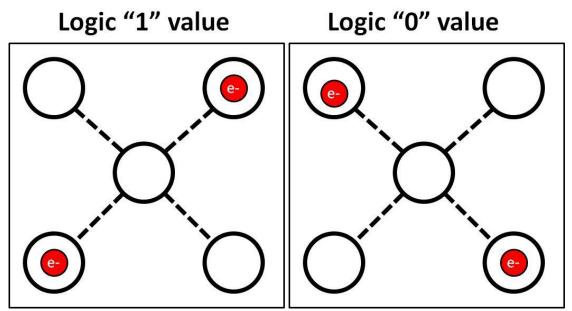

| Figure 2-5. Two ground state electron configurations of the model QCA cells and the logical values associated with them                                                                                                                                                                                                                                                                                      |

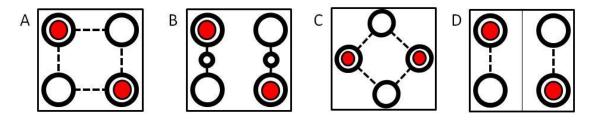

| Figure 2-6. Other QCA cell configurations - A. Four-dot QCA cell configuration – B. Six-dot QCA cell configuration – C. Rotated four-dot QCA cell configuration – D. Two-half-cell QCA cell configuration                                                                                                                                                                                                    |

| Figure 2-7. Four cell configurations and the resultant cell-to-cell response function. Here the Cell B geometry produces the best polarization gain and is thus the optimal choice based on this parameter. Taken from [37]                                                                                                                                                                                  |

| Figure 2-8. Polarization response of cell 1 to the polarization of cell 2.<br>Tunneling energy t is modified from .2meV (solid line), .3meV (dot line),<br>.5meV(dash line), and .7meV (dot-dash line). Taken from [37]                                                                                                                                                                                      |

| Figure 2-9. Binary wires with polarization gain less than 1, equal to 1, and greater than 1. Expectation of the number operator for each of the 4 logically interactive sites are shown as black dots. A expectation number of 1 is shown                                                                                                                                                                    |

| as a full black dot and of 0 as a full white dot. Expectation values between 0 and 1 are shown as dots filled to various degrees                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-10. QCA inverter and associated symbol                                                                                                                                                                          |

| Figure 2-11. QCA majority gate with associated symbol and truth table25                                                                                                                                                  |

| Figure 2-12. Planer wire crossing structure in QCA. Taken from [40]                                                                                                                                                      |

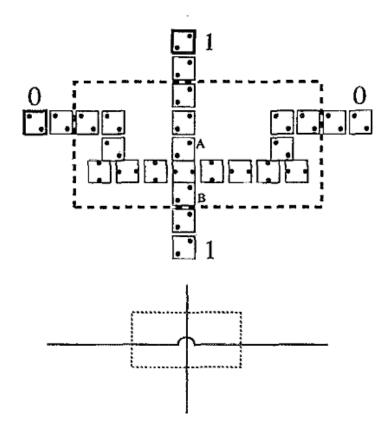

| Figure 2-13. SEM image of Metal-dot QCA cell and associated schematic. From [52]                                                                                                                                         |

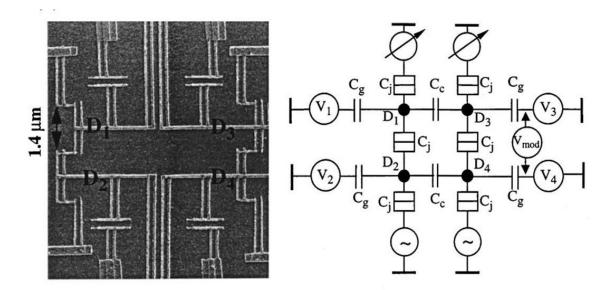

| Figure 2-14. Silicon based QCA schematic and SEM images from [26]                                                                                                                                                        |

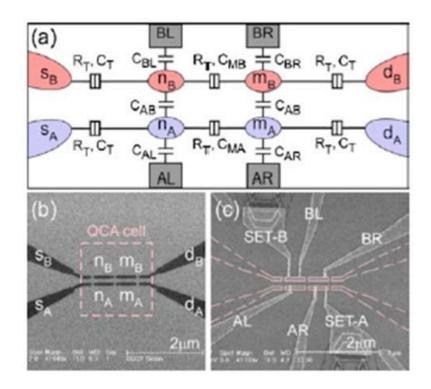

| Figure 2-15. QCA full adder templates formed by electron beam lithographical patterning from [63]                                                                                                                        |

| Figure 2-16. Mixed valence candidate molecular cell for QCA, along with the constant charge radiuses for the two logical QCA states, taken from [27] 32                                                                  |

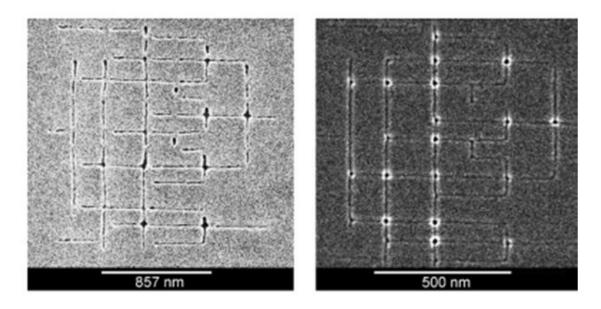

| Figure 2-17. Implementations of a majority gate for magnetic quantum-dot cellular automata. From [28]                                                                                                                    |

| Figure 2-18. Binary wire switching event may lead to a correct output or metastable states                                                                                                                               |

| Figure 2-19. Adiabatic Switching of QCA binary wire                                                                                                                                                                      |

| Figure 2-20. Four phases of the QCA clock                                                                                                                                                                                |

| Figure 2-21.Four clocks used for QCA 40                                                                                                                                                                                  |

| Figure 2-22. QCA memory cell. The cells are colored with different shades of grey corresponding to the usage of one of the four clock zones. Taken from [79]                                                             |

| Figure 2-23. Candidate QCA molecules when clocked – Buried clocking wires induce a perpendicular electric field into the QCA molecular cells – red dot shows free electron in each of the two molecule parts – from [80] |

| Figure 2-24. Block of QCA composing two cascading majority gates a) regular arrays b) irregular defective arrays. From [89]                                                                                              |

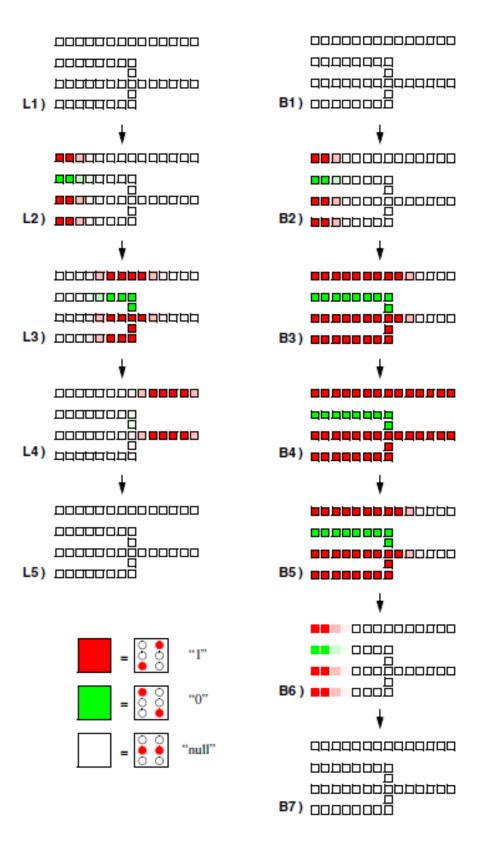

| Figure 2-25. Example of the information propagation for Landauer clocking (right) and Bennett Clocking (left). From [78]                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

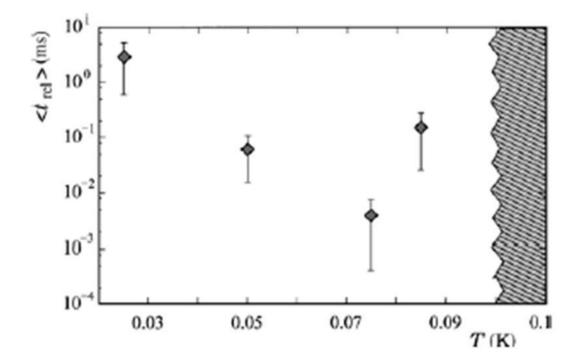

| Figure 2-26. Average and range of relaxation times < <i>trel</i> > for metal dot implementations as a function of temperature. From [98]                                                                                                                      |

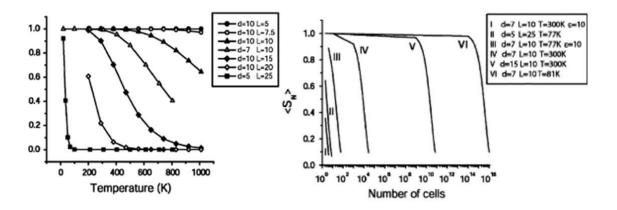

| Figure 2-27. Reliability dependence of non-clocked QCA wires on cellular geometry, temperature, and number of cells. From [61]                                                                                                                                |

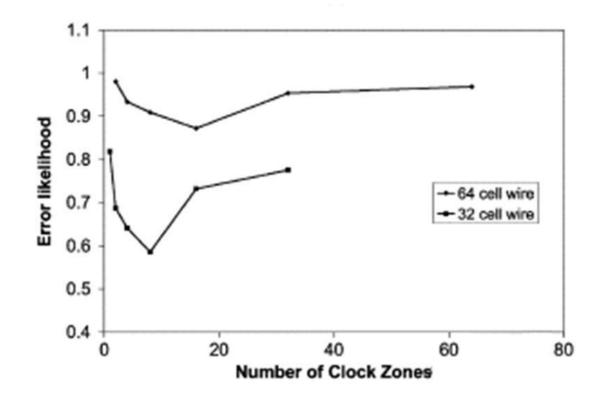

| Figure 2-28. Relationship between reliability and clocking zone size in wire of different sizes. From [99]53                                                                                                                                                  |

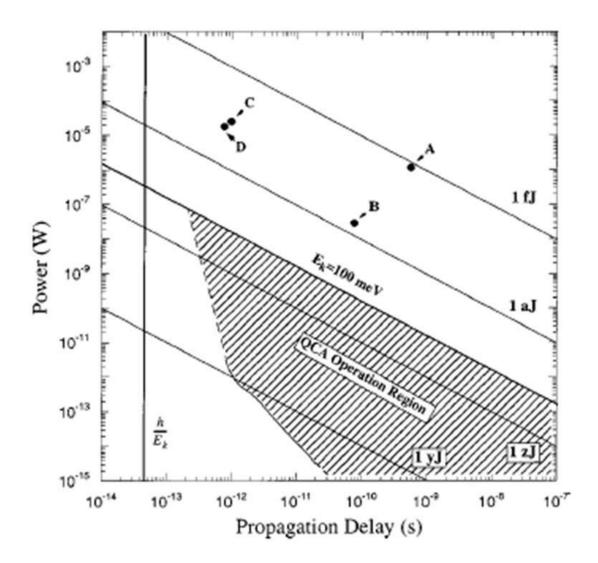

| Figure 2-29. Projected circuit speeds and power dissipation for QCA circuits as well as previous CMOS technology (A-D). (30nm and 20nm gate length CMOS circuits are shown as C and D, A and B are somewhat older CMOS versions). From [60]                   |

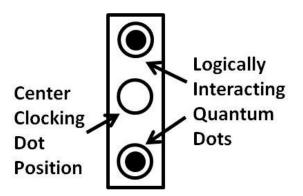

| Figure 3-1. Electrostatic 2-dot QCA cell consisting of 2 logically interacting quantum dots (quantum dot) and a single quantum dot used for clocking 59                                                                                                       |

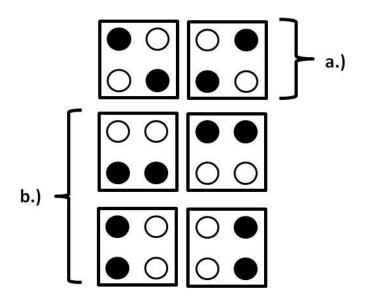

| Figure 3-2. Six possible configurations of 4-dot QCA cells a) Nominal unambiguous configurations b) Possible additional ambiguous configurations 61                                                                                                           |

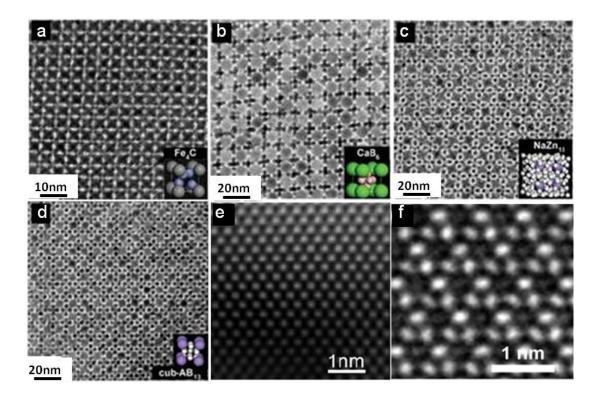

| Figure 3-3. a-d) TEM images of self-assembled binary superlattices from [101] e) HRTEM image of centered rectangular 2-D molecular lattice of cross section of MnGe [102] f) HRTEM image from molecular $\beta$ -Si <sub>3</sub> N <sub>4</sub> lattice [103] |

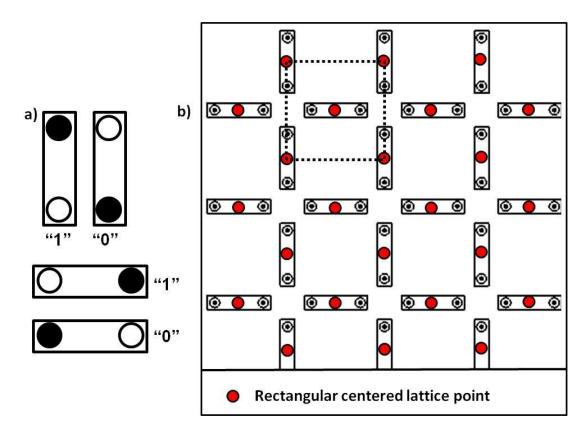

| Figure 3-4. a) 2-D 2-dot QCA logic convention b) Completely populated 2-dot QCA "map" with lattice points placed on the cells for illustration purposes only64                                                                                                |

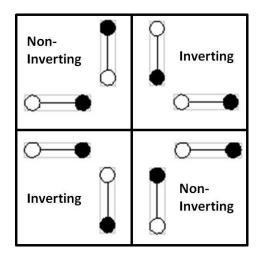

| Figure 3-5. Direction of inverting corners                                                                                                                                                                                                                    |

| Figure 3-6. Fundamental logic constructs: a) Binary wire b) Inverter c) Fan-out gate d) Planer wire crossing68                                                                                                                                                |

| Figure 3-7. a) Schematic for the simplest of 2-dot QCA majority gates b) implementation of this majority gate70                                                                                                                                               |

| Figure 3-8. Majority gate with global inputs which are removed from the local input sites a) Schematic b) 2-dot QCA implementation                                                                                                                            |

| Figure 3-9. Delay flip-flop implementation in the 2-dot QCA73                                                                                                                                                                                                 |

| Figure 3-10. Majority gate based XOR gate using 2-dot QCA cells along with its schematic                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

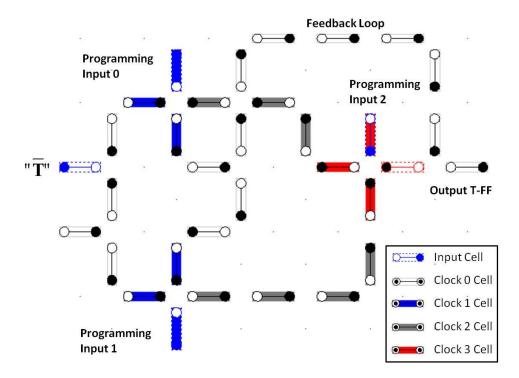

| Figure 3-11. 2-dot QCA implementation of Toggle Flip-Flop                                                                                                                                                                                                                                                                                                            |

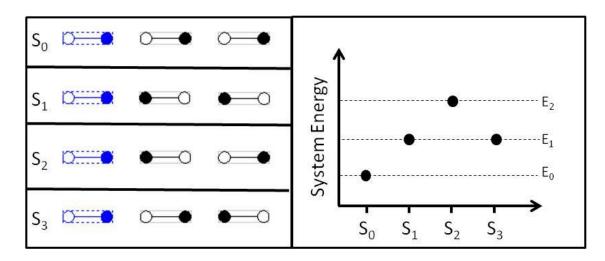

| Figure 4-1. Possible circuit states of small binary wire example                                                                                                                                                                                                                                                                                                     |

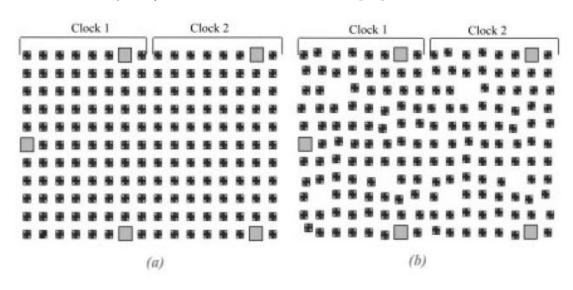

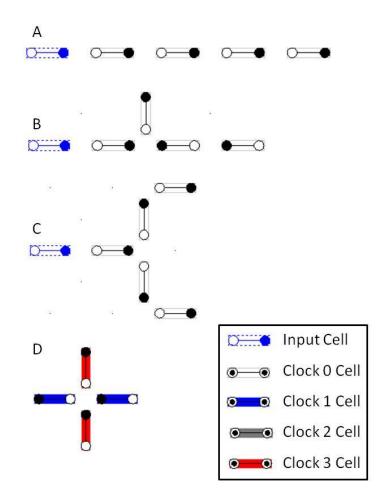

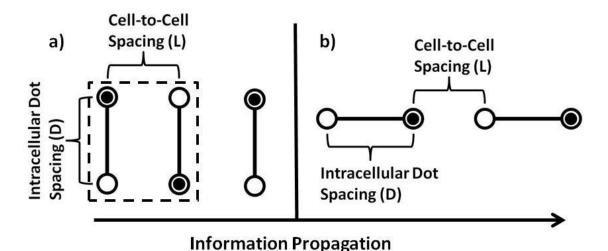

| Figure 4-2. a) Traditional QCA layout used by four dot designs b) Parallel 2-D 2-dot QCA wire design                                                                                                                                                                                                                                                                 |

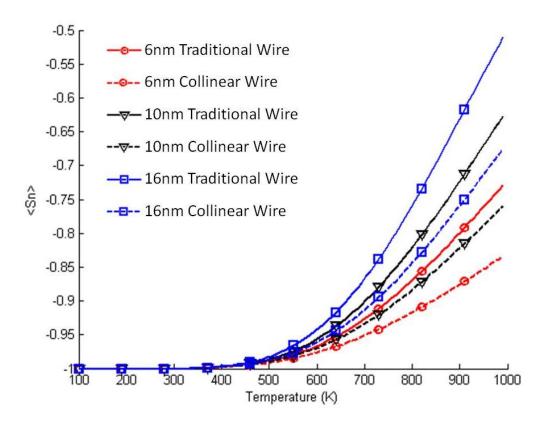

| Figure 4-3. D=L=1nm QCA cell wire expectation vs. temperature                                                                                                                                                                                                                                                                                                        |

| Figure 4-4. D=L=40nm QCA cell wire expectation vs. temperature                                                                                                                                                                                                                                                                                                       |

| Figure 4-5. D=L=5nm QCA cell wire expectation vs. temperature                                                                                                                                                                                                                                                                                                        |

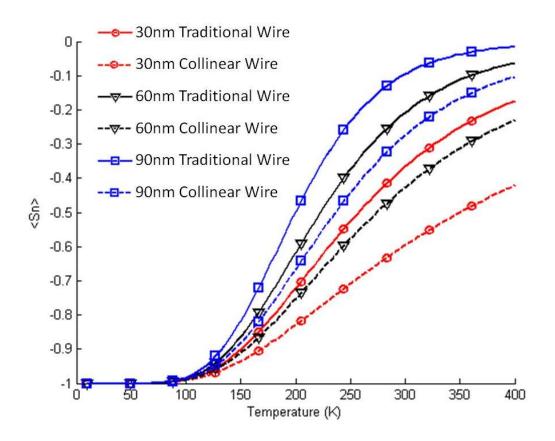

| Figure 4-6. Thermodynamic analysis of universal logic gate of Figure 3-8 for devices with D=L=1nm (solid lines) and D=L=5nm (dotted lines) with different inputs given to the gate (circles indicate all inputs favorable to the output, triangles indicate perpendicular (to output QCA) input rejection and squares indicate collinear (to output) input rejection |

| Figure 5-1. (a) 1-wide LINA wire (b) 3-wide LINA wire (c) 5-wide LINA wire 98                                                                                                                                                                                                                                                                                        |

| Figure 5-2. Geometrical layout convention used for LINA designs 101                                                                                                                                                                                                                                                                                                  |

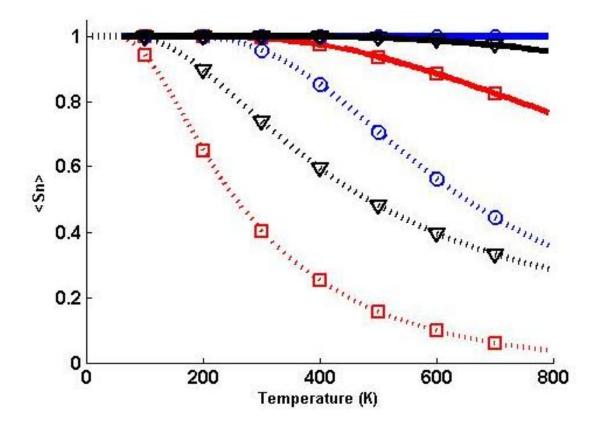

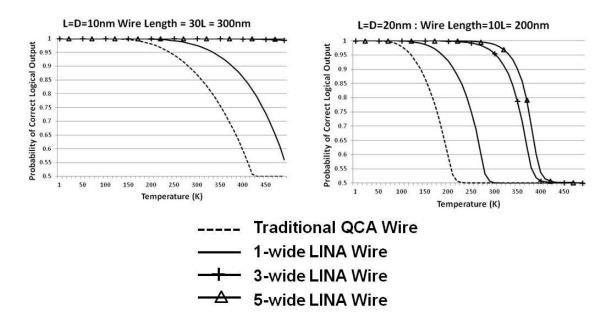

| Figure 5-3. Probability of Correct Logical Output (PCLO) for traditional and LINA wires utilizing different cell sizes and spacings (The simulations were performed with relative permittivity of 1, high clock level of 9.8e-20 J, and low clock level of 3.8e-23J.)                                                                                                |

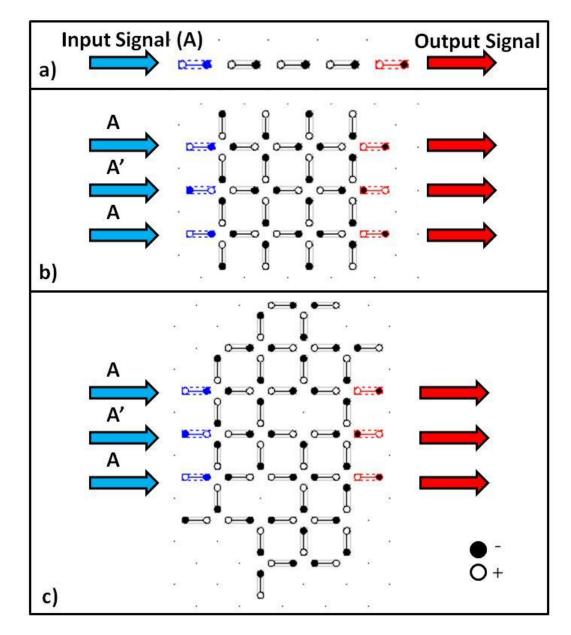

| Figure 5-4. Figure 1a) 2-D 2-dot QCA wire which, like traditional QCA, are not robust in the presence of fabrication errors b) ideal 3-signal LINA wire c) Fully functional LINA wire with random cell additions and deletions                                                                                                                                       |

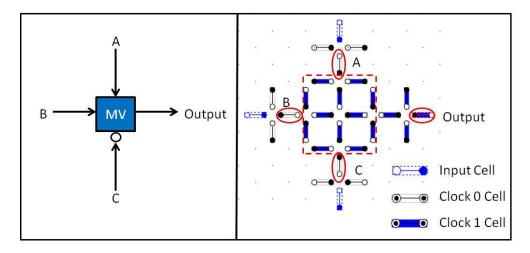

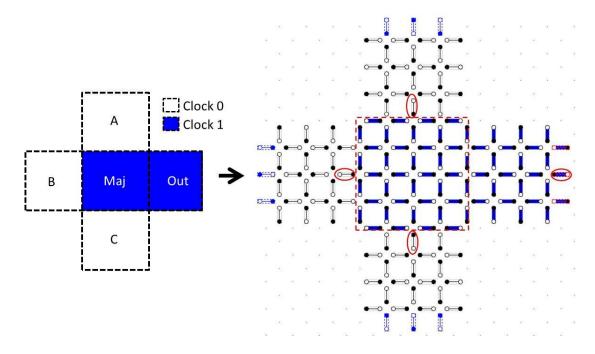

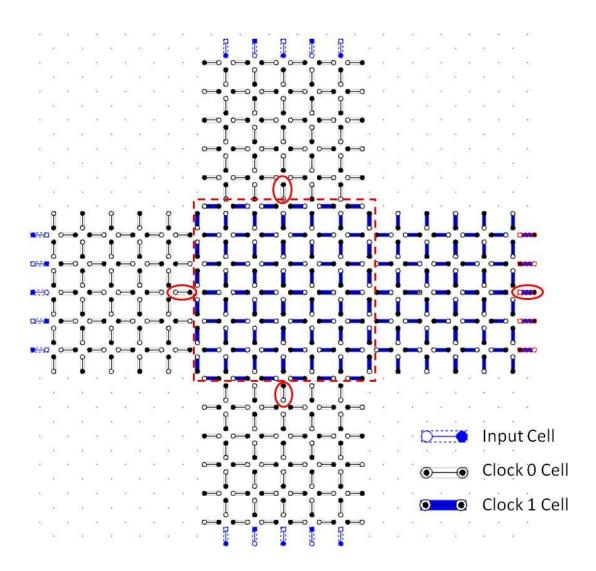

| Figure 5-5. Majority Voter gate in 1-wide LINA106                                                                                                                                                                                                                                                                                                                    |

| Figure 5-6. 3-wide LINA majority gate with associated LINA block representation                                                                                                                                                                                                                                                                                      |

| Figure 5-7. 5-wide LINA majority gate 108                                                                                                                                                                                                                                                                                                                            |

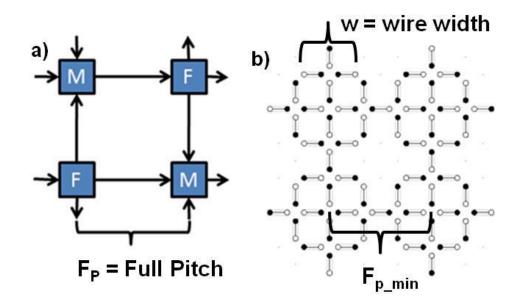

| Figure 6-1. a) Small array of blocks (in this case Majority (M) and Fan-out (F) |

|---------------------------------------------------------------------------------|

| gates) with associated full pitch (Fp) b) Example of smallest possible 1-wide   |

| LINA full pitch                                                                 |

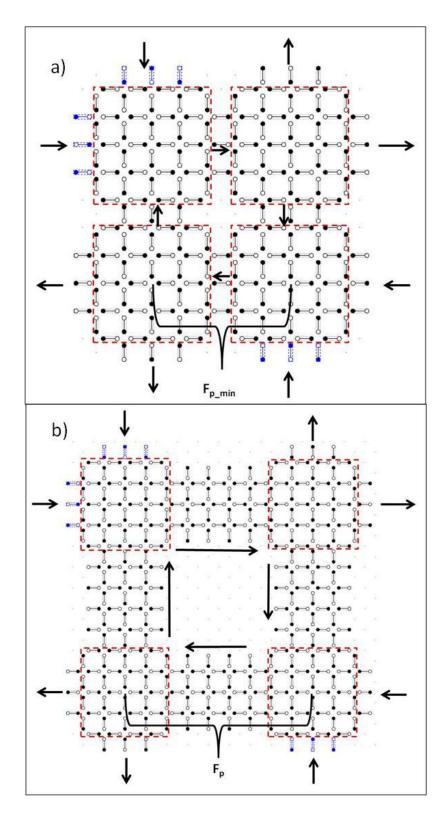

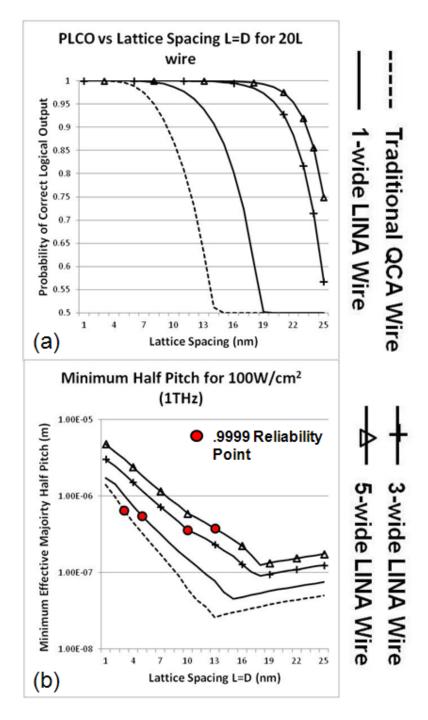

Figure 6-3. (a) Probability of correct logical output (PCLO) for room temperature operation with increasing lattice spacing from 1nm to 25nm for traditional and 1,3,5-wide LINA wire designs. Wire length is 20L. (b) Minimum "effective majority" half pitch for 4 traditional and LINA wire circuit design along with the 4 9's reliability point at 1THz. Note the minimum half pitch is seen with the 3-wide LINA design at this reliability. The simulations feeding this data was ran with relative permittivity of 1, high clock level of 9.8e-20 J, and low clock level of 3.8e-23J.

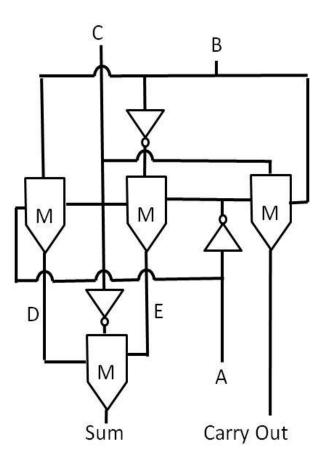

| Figure 6-4. Logical Schematic of the full adder used in the design examples | of    |

|-----------------------------------------------------------------------------|-------|

| Section 6.2                                                                 | . 122 |

Figure 6-5. Blocks design for the first LINA full adder example (1-wide 4nm) 125

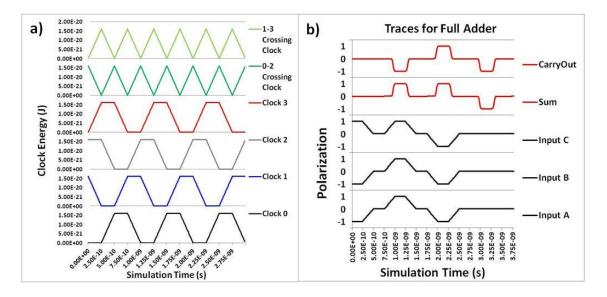

| Figure 6-7. a) Clock traces used for the full adder b)Traces for the inputs and |    |

|---------------------------------------------------------------------------------|----|

| outputs of full adder circuit12                                                 | 27 |

| Figure 6-8. 3-wide LINA | layout for Section 6.2.2 | . 130 |

|-------------------------|--------------------------|-------|

|-------------------------|--------------------------|-------|

Figure 6-9. Proposal layout of clocking wires for full adder implementation ... 131

#### Abstract

The past 50 years have seen exponential advances in digital integrated circuit technologies which has facilitated an explosion of uses and functionality. Although this rate (generally referred to as "Moore's Law") cannot be sustained indefinitely, significant advances will remain possible even after current technologies reach fundamental limits. However if these further advances are to be realized, nanoelectronics designs must be developed that provide significant currently-utilized, complementary metal-oxide improvements over, the semiconductor (CMOS) transistor based integrated circuits. One promising nanoelectronics paradigm to fulfill this function is Quantum-dot Cellular Automata (QCA). QCA provides the possibility of THz switching, molecular scaling, and provides particular applicability for advanced logical constructs such as reversible logic and systolic arrays within the paradigm. These attributes make QCA an exciting prospect; however, current fabrication technology does not exist which allows for the fabrication of reliable electronic QCA circuits which operate at room-temperature. Furthermore, a plausible path to fabrication of circuitry on the very large scale integration (VLSI) level with QCA does not currently exist. This has caused doubts to the viability of the paradigm and questions to its future as a suitable nanoelectronic replacement to CMOS. In order to resolve these issues, research was conducted into a new design which could utilize key attributes of QCA while also providing a means

ΧV

for near-term fabrication of reliable room-temperature circuits and a path forward for VLSI circuits.

The result of this research, presented in this dissertation, is the Lattice-based Integrated-signal Nanocellular Automata (LINA) nanoelectronics paradigm. LINA designs are based on QCA and provide the same basic functionality as traditional QCA. LINA also retains the key attributes of THz switching, scalability to the molecular level, and ability to utilize advanced logical constructs which are crucial to the QCA proposals. However, LINA designs also provide significant improvements over traditional QCA. For example, the continuous correction of faults, due to LINA's integrated-signal approach, provides reliability improvements to enable room-temperature operation with cells which are potentially up to 20nm and fault tolerance to layout, patterning, stray-charge, and stuck-at-faults. In terms of fabrication, LINA's lattice-based structure allows precise relative placement through the use of self-assembly techniques seen in current nanoparticle research. LINA also allows for large enough wire and logic structures to enable use of widely available photolithographical patterning technologies. These aspects of the LINA designs, along with power, timing, and clocking results, have been verified through the use of new and/or modified simulation tools specifically developed for this purpose. To summarize, the LINA designs and results, presented in this dissertation, provide a path to realization of QCA-type VLSI nanoelectronic circuitry. Furthermore, they offer a renewed viability of the paradigm to replace CMOS and advance computing technologies beyond the next decade.

xvi

#### Chapter 1

#### Introduction

Few would doubt the importance of the integrated circuit (IC) to the societies of the modern world. They have permeated nearly every aspect of our everyday lives and enabled unquestioned creativity, unparalleled togetherness, and the instantaneous spread of information throughout the globe. The man given most of the credit for the invention of the IC is Jack Kilby, who won the Nobel Prize for physics in 2000 for his work developing the first IC at Texas Instruments in 1958 [1]. Kilby's original ICs consisted of a single phase-shift oscillator and a digital flip flop circuit whose functionality was well known and not at all revolutionary. What was revolutionary, however, was that the logical components, passive elements, and interconnection wiring were constructed and integrated together using only a single piece of germanium. This change removed the expensive, time-consuming, and unreliable process of hand wiring and soldiering of several individual components to achieve the desired circuit function [2]. It also allowed the IC to be rapidly and effectively scaled, both up in the number of components integrated in a device (termed integration level scaling), and down in the size of the components and interconnections (termed size scaling).

These scaling advances allowed for not only the addition of functionality and efficiencies into ICs but also for decreased power per circuit element and increased circuit speed due to the underlying nature of the physics of the host semiconductors.

1

It could be argued, very effectively, that the ability to be scaled has been the driving force in the success of the integrated circuit, giving rise to an exponential increase in computing performance over the past 50 years. This success can clearly be seen in microprocessor ICs which have grown in complexity from around 2,300 transistors in the early 1970s to currently being distributed with billions of transistors integrated on a piece of silicon only a few square centimeters in area while running at clock speeds which allow several billion calculations to be performed per second.

However, size scaling of the current processor IC technology, complementary metal-oxide semiconductor (CMOS), is rapidly approaching practical, if not fundamental, limits [3]. This is due to the size of today's CMOS transistors which have gate widths in the lower tens of nanometers. At this size scale, quantum mechanical effects, such as tunneling, begin to affect device behavior. In fact, circuit designers are already being plagued by these small scale effects as limited per element power consumption gains are no longer able to support large increases in circuit clock speeds. In order to offset these challenges, designers are turning to more parallel multi-core designs to continue the increase in IC performance, but they are most assuredly a harbinger of other, more fundamental, difficulties to come. Therefore, if the pace of progress seen in computing over the past 50 years is to be maintained, new technologies must be developed to supplement and eventually replace CMOS transistor-based designs and provide a paradigm which can continue the scaling of electronic circuit elements into the quantum and molecular regimes.

2

Nanoelectronics, named after the nanometer dimensions of the field's electronic elements, contain the emerging IC implementation paradigms from which will come the next generation of computing technologies. While CMOS is itself delving into the nanometer realm for size dimensions, CMOS is not a nanoelectronics paradigm. Instead, current nanoelectronics paradigms include single electron transistors (SET) [4, 5, 6, 7], Superconducting electronics [8, 9, 10], carbon nanotube (CNT) [11, 12, 13, 14], nanowire and nano-ribbon transistors [15, 16, 17, 18], resonant tunneling devices [19, 20], spintronics [21, 22, 23, 24], and Quantum-Dot Cellular Automata (QCA) [25, 26, 27, 28]. Many of these technologies simply offer the potential to extend the life of CMOS and expand more traditional circuit design techniques to smaller scales. However, this extension will only delay the inevitable necessity of a completely new processing paradigm. In Figure 1-1, a projection of roles and timeline for several of these nanoelectronics proposals based on current industry projections [3] is shown.

Figure 1-1. Outlook of Computing Technologies

There are certain attributes which make nanoelectronics proposals suitable candidates to replace CMOS electronics. Specifically, the particular proposal must offer a technology which exceeds current and projected CMOS abilities in areas such as: clock speed, power requirements, parallel structure, circuit area, and/or circuit robustness. Many proposals are able to exceed the abilities of current technologies in some areas, but fall short in others. For example, single electron transistors can be made much smaller than current CMOS transistors (potentially down to a single nanometer sized molecular component). Additionally, their power requirements are very low compared to CMOS. However, robust operation at room temperature has been very difficult to achieve especially at the very large scale integration (VLSI) level.

Other paradigms have similar advantages and disadvantages. For instance, QCA offers molecular scalability and low power, similar to the SET, along with the potential of THz switching speeds and an inherently parallel circuit structure. Further exploration of the potential of the QCA paradigm reveals the hope for revolutionary advancements in logic design and computing circuitry through constructs such as reversible computing [29] and/or reconfigurable systolic architectures [30]. These attributes along with the advancements in size, speed, and power have attracted many researchers to QCA, making it one of the most theoretically well-developed nanoelectronics paradigms. However, QCA have also been hampered by the inability to provide robust large scale circuits in a room temperature environment; a challenge that if left unsolved will undermine

4

the promising potential of QCA and the confidence of the nanoelectronics community in the paradigm.

#### **1.1** Advancement and impact of this work

Major advancements in two areas of research must be achieved if the QCA paradigm is able to fulfill its promise as a nanoelectronic replacement to CMOS. First, an architecture which allows for robust room-temperature operation of QCA must be developed; and second, that architecture must be amenable to currently available or near term fabrication technologies. Too often, researchers in the QCA field have overlooked these two challenges and resorted to the traditional QCA cellular structure and architecture paradigm. The effect of this lack of attention has been the steady decline in confidence of the electronics community as to the theoretical predictions made for QCA [31, 32, 33]<sup>1</sup>, and thus the paradigm itself. In this work, we tackle these two pressing challenges and produce a new design which retains the promising potential in logic design methods and performance, and also provides viable implementation strategies which fit with current and near term technologies. The new design is called the Lattice-based Integrated-signal Nanocellular Automata (LINA) (example shown in Figure 1-2). LINA is a design strategy and circuit architecture that is a variant of the QCA paradigm. However, it is built around a lattice-based structure which allows for common self-assembly methods to be utilized in the deposition and

<sup>&</sup>lt;sup>1</sup> These references highlight theoretical disagreements between physicists and system designers. Lack of fabrication methods has served to facilitate these disagreements and doubts.

placement phase of circuit construction. Additionally, LINA provides a dramatic increase in reliability (for a constant cell size) over traditional QCA designs by integrating several "signals" of information together in a process that continually corrects faults. The increase in reliability allows for larger cells and spacings to be used to fabricate circuitry for room-temperature operation and additional opportunities for currently available materials to be used as circuit elements. Additionally, the larger footprint of the logical and communicative elements should allow for traditional lithographic patterning methods to be used for the fabrication of LINA circuitry allowing utilization of current VLSI technologies and fabrication facilities. The LINA designs also allow for continued scaling of circuitry to the molecular level as technologies improve.

Figure 1-2. Lattice-based Integrated-signal Nanocellular Automata (LINA) wire design structure

The theories and structures which will be presented in this work have been verified using physics based simulation methods which were originally produced for traditional QCA and have been modified to also be applicable to LINA. The software provides data on timing, logical function, power, reliability, and other physical parameters whose results were checked against other commonly available simulation tools. It also provides a design tool for creating logical elements and circuitry in the LINA design framework.

In summary, QCA is one of the most theoretically well-developed nanoelectronics design paradigms. Its challenges have been with the inability to fabricate reliable room-temperature large scale circuitry. The results of the LINA research have the potential to overcome these challenges and alter the course of QCA nanoelectronics by making QCA designs more applicable to existing materials and technologies. This could then position QCA as one of the favorite candidates to replace CMOS based integrated circuitry in the coming decades and usher in a new era of electronics and computing.

#### 1.2 Organization

This dissertation is organized as follows. Background material for the QCA paradigm is presented in Chapter 2. 2D 2-Dot QCA designs, which are the basic building block of LINA, are presented in Chapter 3. The details of the simulation engines used in the development of the 2D 2-dot QCA and LINA are given in Chapter 4. Chapter 5 details the new LINA designs and methods and presents simulation results which provide critical evidence to support its suitability. Chapter 6 provides further analysis for LINA and two LINA design

examples. The dissertation is then concluded with Chapter 7, which provides summaries and an outlook to future research on LINA.

#### Chapter 2

#### **Background Material**

Before a thorough discussion of LINA theory and designs can be presented, it is important that traditional QCA principles of structure, design, and fabrication must be understood. This is because LINA are based on many of these QCA principles. Additionally, a great deal of the published theoretical research is applicable to both paradigms. Therefore, this chapter provides the material necessary to this understanding, beginning with an introduction to cellular automata concepts and QCA basics. This is followed by current QCA implementation technologies and theory which provide the starting point to further advances provided in this dissertation. More complex QCA topics such as clocking and advanced logical concepts will also be discussed due to their criticality to the LINA architecture. Finally, the chapter ends with a discussion on analysis of important QCA properties which provide the motivation for further exploration of QCA as a nanoelectronics replacement for CMOS ICs.

#### 2.1 Quantum-dot cellular automata (QCA) Basics

#### 2.1.1 Cellular Automata (CA)

Cellular Automata (CA), first proposed by von Neumann [34], are generally ndimensional fully populated arrays of identical cells, which may be in any one of a set of finite states. Each of these cells updates their states at discrete time intervals based on a global evolution function that is typically dependent on the states of a set of neighboring cells. Because the CA computation model obeys physical principles of locality and invariance to shifts in time and space, many scientists have suggested a link between CA and the physics of the quantum world [35]. Additionally, the fact that many molecular structures have natural attributes demonstrating CA interaction suggests that CA may be ideal computational elements for nanoelectronics.

This suggestion is further substantiated by the fact that CA can achieve complexity and even logical completeness with very simple structure and evolution functions. This fact is exemplified in research by Wolfram, who classified and proved that elementary CA, (which are bi-state, 1-D, fully populated arrays) achieve complexity by means of a specific set of rules (here another name for the evolution function), such as rule 110 [36], which can be seen in Figure 2-1.

Figure 2-1. Rule 110 CA - The figure is a graphical representation of the evolution of a 1-D array of two-state cells (white depicting a "0" state and black depicting a "1" state). The CA begins with a single "1" surrounded by all "0"s which is the top of the triangle. Each row of the figure is a discrete time step of the evolution of the cells beginning at the top and progressing down [36].

#### 2.1.2 QCA as CA

The QCA paradigm deviates from conventional CA in that QCA achieve logical completeness and complexity by selectively patterning (meaning adding or deleting) cells based in a 2-D grid and actively driving certain input cells<sup>2</sup>. Because of this, QCA cell patterns more closely resemble the form and function of traditional logical circuits compared to other CA types. This provides benefits in circuit design techniques but also limits inherent advantages of the QCA paradigm, such as parallelism.

QCA also deviate in that the cells' evolution functions are not based on the state of the neighboring cells at the previous time step as in conventional CA, but instead on the least energy configuration of the entire system at that time step. This means that QCA are not inherently sequential, instead the input cells are used to explicitly set the cell states of the remaining cells. In order to make QCA sequential, clocking schemes are applied to effectively lock cell states of certain neighboring cells in a cyclic fashion. This provides a more conventional CA evolution function to the QCA circuit states.

The evolution functions for both clocked and unclocked QCA are based on the summation of the electromagnetic interaction of neighboring cells. The strength and polarization of this interaction has factors of relative placement, cellular geometry, and distance; and, due to the structure of QCA cells, essentially limits the cell interaction neighborhood to a radius of two or three cell spacings.

<sup>&</sup>lt;sup>2</sup> Input cells thus have evolution functions that are not dependent on neighboring cells.

Additionally, the bipolar nature of the electromagnetic interaction produces QCA cells which are two-state, allowing for simplicity, robustness, and even logical gain.

The evolution function produces a ferromagnetic<sup>3</sup> type of interaction for cells directly horizontal or vertically positioned to each other. Cells which are positioned diagonally relative to each other tend to produce an anti-ferromagnetic type of interaction. This produces a logical majority voter function for cells at the ferromagnetic position with similar distances, and a logical minority function for cells at the anti-ferromagnetic positions with similar distances (shown graphically in Figure 2-2). This inherent property of QCA will become a critical piece to allow logic and communication in the QCA computing architecture.

Figure 2-2. A. Configuration of cells which produce a majority voter (MV) logical function. B. Configuration of QCA cells which produces a minority (anti-majority) voter (AMV) function.

<sup>&</sup>lt;sup>3</sup> Ferromagnetic is in the sense of an Ising model and does not necessarily mean magnetism

#### 2.2 QCA Basics

#### 2.2.1 QCA Cell Structure

Standard QCA cells are, at their most basic, a configuration of charge containers which enable the localization of a fixed number of free electrons in a way which produces a two state CA. The first "model" QCA cells were theoretical structures, proposed by Lent et al. [25], containing five quantum dots arranged in the manner shown in Figure 2-3. These quantum dots act as the charge containers for the localization of two free electrons, which because of Coulombic repulsion prefer to occupy diagonal corner quantum dot sites. Each quantum dot is electrically separated from the other dots by a potential barrier generated by the electrical properties of the surrounding material. Classically, after an electron falls into one of these dots and relaxes sufficiently, it cannot escape until it is given suitable energy to overcome the dot's barriers. However, quantum mechanical principles allow, at some non-zero probability, electrons to travel, or "tunnel", from one dot to another without the application of extra energy. This occurs with a frequency and likelihood dependent on properties such as the electron's energy, applied force to the electron, and the potential energy barrier height the quantum dot provides. These properties must be precisely controlled in QCA cells allowing the design of specifically placed paths, or tunnel junctions, between specific dots internal to a single cell but not between dots of two separate cells.

13

Figure 2-3. Original QCA Cell - Here shown with two free electrons completely localized on quantum dot sites.

#### 2.2.2 Theoretical Development of a model QCA cell

The theoretical development of a physical model of a QCA cell begins with a graphical schematic of what was originally called the "standard" QCA cell [25, 37] (shown in Figure 2-4). The standard cell contains quantum dot sites which are labeled from 0 to 4, and are connected with tunnel junctions which are labeled based on the sites which they connect. It is assumed that the barriers to tunneling for any path not shown in the model are so large to effectively eliminate tunneling in them. A standard distance of a is used to denote the base measurement of this cell as given a one could determine any distance in the cell based on standard geometry.

Figure 2-4. Graphical schematic of the original "standard" QCA cells with numbered quantum dot sites, tunnel junctions, and the distance measure "a"

This graphical model allows construction of a model Hamiltonian for the cell. A Hubbard-type Hamiltonian was chosen and any internal degrees of freedom to the dots of the cell were ignored. The Hamiltonian for the cell is:

$$H_0^{Cell} = \sum_{i,\sigma} E_o \,\hat{n}_{i,\sigma} + \sum_{i>j,\sigma} t_{i,j} (\hat{a}_{i,\sigma}^{\dagger} \hat{a}_{j,\sigma} + \hat{a}_{j,\sigma}^{\dagger} \hat{a}_{i,\sigma}) + \sum_i E_Q \hat{n}_{i,\downarrow} \hat{n}_{i,\uparrow} + \sum_{i>j,\sigma,\sigma'} V_Q \frac{\hat{n}_{i,\sigma} \hat{n}_{j,\sigma'}}{(R_i - R_i)}$$

$$(2.1)$$

In (2.1) the second quantization notation is used where  $\hat{a}_{i,\sigma}^{\dagger}(\hat{a}_{i,\sigma})$  creates (annihilates) an electron at site *i* with spin  $\sigma$ . The number operator for site *i* with spin  $\sigma$  is  $\hat{n}_{i,\sigma} = \hat{a}_{i,\sigma}^{\dagger} \hat{a}_{i,\sigma}$ . The first term of (2.1) is the energy,  $E_0$ , associated with an electron confined on the *i*<sup>th</sup> site. The second term is the tunneling energy

between sites *i* and *j* where  $t_{i,j} = t$  for neighboring sites and  $t_{i,j} = 0$  for antipodal sites. The third term is the energy cost associated with confining two electrons on the same dot and the fourth term is the Coulombic interaction between electrons at different sites. To find the stationary states of the model cell, the time-independent Schrödinger equation ((2.2) must be solved.

$$\widehat{H}^{Cell}|\psi_i\rangle = E_i|\psi_i\rangle \tag{2.2}$$

$\langle \alpha \rangle$

In (2.2),  $|\psi_i\rangle$  is the *i*<sup>th</sup> eigenstate of the Hamiltonian and  $E_i$  is the associated eigenvalue. These eigenstates are found using the many-particle site-ket basis for the five sites and two electrons of opposite spins such as seen in (2.3):

$$\begin{aligned} |\psi_{0}\rangle &= \begin{vmatrix} 0 & 0 & 0 & 0 & 1 \\ 0 & 0 & 0 & 0 & 1 \end{vmatrix}, \\ |\psi_{1}\rangle &= \begin{vmatrix} 0 & 0 & 0 & 0 & 1 \\ 0 & 0 & 0 & 1 & 0 \end{vmatrix}, \\ &, \dots, \\ |\psi_{25}\rangle &= \begin{vmatrix} 1 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 0 \end{vmatrix}, \end{aligned}$$

(2.3)

where the columns correspond to the sites and the rows to the spins (with the upper row being spin up and the lower row spin down).

Using this basis, the Hamiltonian matrix is calculated numerically as in (2.4)

$$H_{i,j} = \langle \phi_i | \widehat{H} \phi_j \rangle$$

(2.4)

and diagonalization of this 25x25 matrix leads to the calculation of the ground states of this model system.

The ground states of the model are the two preferred configurations shown in Figure 2-5 for the case of high tunneling barriers and essentially localized electrons. Tunneling barriers of this type create difficulty in fast switching which is essential in digital systems. However, as tunneling barriers are lowered the localization on the sites is reduced and the electron wavefunctions become spread out amongst the sites making the polarization of the cell weak. This is also an unsuitable situation for digital electronics due to the resultant indeterminate nature of the logic state in this situation. Therefore, a balance must be found to optimize among these two considerations.

In order to quantify the polarization of the cell in regards to the two logic states, (2.5) defines a value P (polarization) which equals -1 for the completely localized logic "0" case and +1 for the completely localized logic "1" case.

$$P \equiv \frac{(\rho_1 + \rho_3) - (\rho_2 + \rho_4)}{\rho_0 + \rho_1 + \rho_2 + \rho_3 + \rho_4}$$

(2.5)

In (2.5),  $\rho_i$  is the expectation value for the number operator for site *i*.

Figure 2-5. Two ground state electron configurations of the model QCA cells and the logical values associated with them.

#### 2.2.3 Other cell configurations

Other types of QCA cells have been proposed in literature and are utilized in QCA designs including cells with four quantum dots, six quantum dots, four quantum dots rotated by 45 degrees with respect to corners of the cell, and cells composed of two dot half-cells. These different cellular configurations, which are shown in Figure 2-6, have slightly different advantages or functions than the model cell. Of particular importance, is the 6-dot configuration, shown in Figure 2-6b, due to its ability to allow for clocking in molecular or macromolecular implementations (which will be discussed later in this chapter). A common trait of all of these configurations is that they all have two free electrons and two preferred electron configurations corresponding to the binary logic values. Therefore, all cell configurations benefit from the basic research into QCA logical design and circuit layouts of the other configurations. Also,

development of the physical model and calculations of these cells utilize the same methodology and similar equations which are used for the model cell.

Figure 2-6. Other QCA cell configurations - A. Four-dot QCA cell configuration – B. Six-dot QCA cell configuration – C. Rotated four-dot QCA cell configuration – D. Two-half-cell QCA cell configuration

#### 2.2.4 Cell to Cell Interaction

In order to be useful as digital communication and logic devices, the state (and subsequent binary value) of QCA cells must be highly influenced by its neighbors. A cell should also saturate at the strongest polarization value possible even in response to weak polarization of a neighboring driver cell. A measure of these properties takes the form of polarization gain in QCA, where  $P_{gain} = P_{resultant}/P_{driver}$ . High polarization gain provides good noise immunity to QCA circuitry and thus allows for reliable communication and computation.

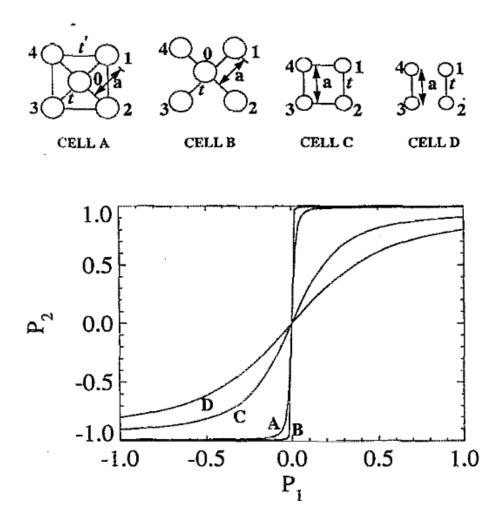

In the early QCA studies [37, 38, 39], several cellular configurations were examined to determine which one produced the highest polarization gain. These studies resulted in the choice of the standard cell configuration due to its high  $P_{gain}$  around the logical transition point. This can be seen In Figure 2-7, where the cell-to-cell response function is shown for various cells and dot configurations. High  $P_{gain}$  at this point causes a large swing in polarization in

the resultant  $P_2$  to the saturation level of +/- 1 as the polarization of the driver cell transitions from negative to positive. In cases where  $P_{gain} < 1$ , (polarization loss), the signal is degrading as it is communicated down the line and thus as is will not be acceptable for circuit construction. An example of this, occurs in the cell D configuration at the higher input polarization values. For this case, another mechanism (which will be discussed later in this chapter) must be used to provide signal gain.

Figure 2-7. Four cell configurations and the resultant cell-to-cell response function. Here the Cell B geometry produces the best polarization gain and is thus the optimal choice based on this parameter. Taken from [37]

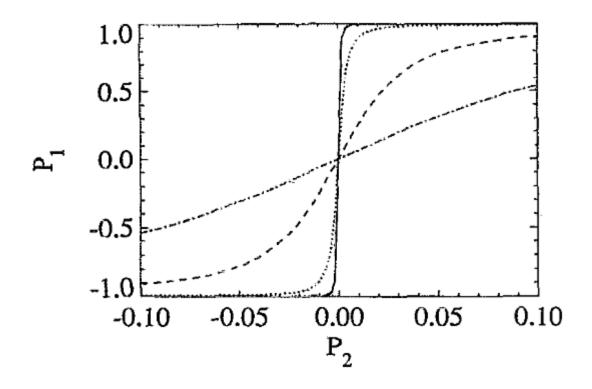

As has been discussed, the mechanism for producing the bistable cell-to-cell response for standard electrostatic QCA cells is the electron localization in the quantum dots and the Coulombic interaction with electrons in neighboring cells. Therefore, the configuration of the dots, intracellular tunneling barriers, and inter-cellular geometry play an important role in this interaction. The ratio of tunneling energy to the Coulombic energy is also important in determining the abruptness of the bistable response function and  $P_{gain}$  value as are factors such as temperature, dot size, and relative placement of the cells. For example, Figure 2-8 shows the change in response function are the cases when the tunneling energy. The extremes of this function are the cases when the tunneling energies are very high or zero. In both of these cases the polarization gain would be zero and would not allow for communication or logic.

Figure 2-8. Polarization response of cell 1 to the polarization of cell 2. Tunneling energy t is modified from .2meV (solid line), .3meV (dot line), .5meV(dash line), and .7meV (dot-dash line). Taken from [37]

## 2.3 Logical and Communication Structures in QCA

## 2.3.1 The binary wire

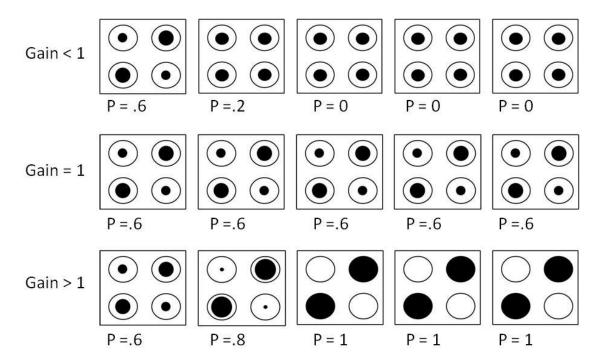

The QCA properties that have been mentioned thus far provide a favorable base to build digital logic and communication structures with the paradigm. However, until a set of logically complete circuit elements can be constructed with QCA cells, its full use cannot be determined. A basic component of this set is a digital communication element, which for QCA, takes the form of a binary wire. The binary wire (or just wire) was designed based on the principle that the polarization of each cell tends to be equal with its neighbor when the cells are linearly aligned [40, 41]. Therefore, the wires travel in either a horizontal or vertical line and are able to turn only 90° corners. The wires are robust and are able to effectively transmit signals if the polarization gain for its cells is greater than one. In contrast, if the polarization gain value is less than 1 then the wire will eventually fail after a certain length is exceeded. Binary wires with this property are shown in Figure 2-9. The figure demonstrates indeterminate cell states resulting from a finite length wire with a low  $P_{gain}$  value.

Figure 2-9. Binary wires with polarization gain less than 1, equal to 1, and greater than 1. Expectation of the number operator for each of the 4 logically interactive sites are shown as black dots. A expectation number of 1 is shown as a full black dot and of 0 as a full white dot. Expectation values between 0 and 1 are shown as dots filled to various degrees.

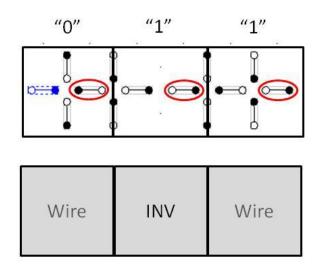

#### 2.3.2 The QCA inverter

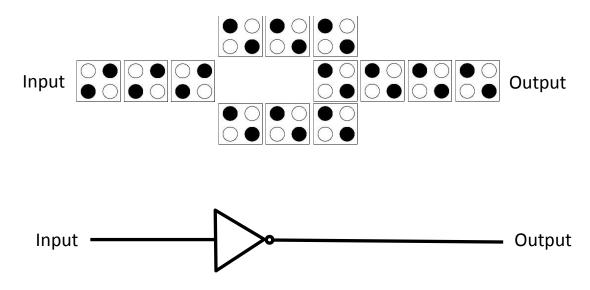

As has been discussed, if two cells are oriented in a diagonal manner with respect to each other, the resultant polarization of the driven cell is the inverse of the driver cell. This is used to create a logical gate that functions as an inverter. In the typical QCA inverter design, shown in Figure 2-10, a single binary wire is inverted with two diagonally positioned wire segments. These segments are then condensed back down to the single wire for output of the gate. Using two segments (instead of one) makes up for the loss of polarization gain due to the increased distance between centers of diagonally oriented cells.

Figure 2-10. QCA inverter and associated symbol

#### 2.3.3 The majority voter

The most fundamental logic element in the QCA architecture is a direct result of the majority-type interaction of horizontally and vertically aligned cells. This element is the three-input majority gate, which has a Boolean logic equation equal to (2.6).

$$Out = AB + BC + AC$$

(2.6)

Its structure, shown in Figure 2-11, requires only a single QCA cell to perform the function. The gate can be used to directly perform three-input majority operations or it can be used implement more traditional two-input AND or OR gates by adding a fixed input (0 or 1 respectively) to the gate's third input. However, while using AND-OR logic is a more traditional design method, it does not provide optimal logic minimization or circuit reduction. Therefore, research into design techniques and tools which utilize majority gate logic is an active area of interest [42, 43, 44, 45].

|                                          | А | В | С | Output |

|------------------------------------------|---|---|---|--------|

| Input A<br>Input B<br>Input B<br>Input C | 0 | 0 | 0 | 0      |

|                                          | 0 | 0 | 1 | 0      |

|                                          | 0 | 1 | 0 | 0      |

|                                          | 0 | 1 | 1 | 1      |

|                                          | 1 | 0 | 0 | 0      |

|                                          | 1 | 0 | 1 | 1      |

| Input A                                  | 1 | 1 | 0 | 1      |

| Input B Maj Output                       | 1 | 1 | 1 | 1      |

| Input C                                  |   |   | 2 |        |

Figure 2-11. QCA majority gate with associated symbol and truth table

#### 2.3.4 Co-planer wire crossing

Another fundamental communication element in the QCA architecture is the coplanar wire crossing. In traditional CMOS digital logic, in plane wire crossings are not possible. Instead chips must be made with several layers so that wires can pass above or below each other. In QCA, it will be difficult to create structures which could transition to different layers and so a planer wire crossing structure is preferred. Luckily the original designs were able to create a planer wire crossing structure by using QCA cells whose quantum dot sites

were rotated 45° internal to the cell. In this way two wires could intersect at a 90° angle and pass through without affecting each other. The cellular structure of a planer wire crossing and its associated symbol is shown in Figure 2-12.

Figure 2-12. Planer wire crossing structure in QCA. Taken from [40]

With these fundamental and logically complete circuit primitives, the QCA architecture is able to produce any desired logical function. Examples of the use of QCA to produce more advanced logic can be seen in [40, 46, 47, 48].

## 2.4 QCA Implementation Technologies

In the early stages, the theoretical development of QCA was restricted to the original coupled quantum-dot systems which took the form of electrostatic metal-dot implementations. However, these systems represent only a part of the experimental implementations which have been attempted or theorized for QCA to date. This is due to fact that other implementations have been found to provide the same fundamental characteristics of a local bistable cell to cell response, majority voter evolution function, and ground state computing as the original metal-dot systems. Furthermore, these new implementations are able to utilize other materials and other state variables to provide advantages in size, robustness, or fabrication concerns over traditional designs.

The new QCA implementations, along with the metal-dot realizations, can be grouped into two categories relating to the physical state variable used for computation. The first of these groups is the electrostatic QCA which contains the original designs and is the most prevalent. The second group contains magnetic QCA implementations. The electrostatic implementations can be subdivided into three additional groups: the original metal-dot QCA, semiconductor QCA, and molecular QCA. This section contains a brief description of these implementations along with their advantages and disadvantages.

#### 2.4.1 Electrostatic Metal-Dot QCA

Early experimental fabrication of QCA cells and logical devices was accomplished through the use of cells constructed of metal quantum dots. In particular, several metal-dot QCA cells were fabricated utilizing AI dots with AI/AIO<sub>x</sub>/AI tunnel junctions [49, 50, 51, 52, 53], one example of which is shown

in Figure 2-7. These cells were shown to produce the required bi-stability of QCA devices and effectively demonstrated communication [54], majority gate logic [55], clocking of QCA cells [56], and fan out structure [57].

However, they were fabricated as more of proof of concept demonstrations and not feasible paths to large scale nanoelectronic circuitry. Thus, they were composed of relatively large cells which were difficult to fabricate except for very simple circuits. Additionally, due to the very small energies associated with their operation, they had to be operated at liquid He temperatures (<100mK) and with magnetic fields to suppress resultant superconductivity.

Figure 2-13. SEM image of Metal-dot QCA cell and associated schematic. From [52]

#### 2.4.2 Electrostatic Semiconductor QCA

Due to the prevalence of semiconductor devices and technologies, QCA fabricated with semiconductor quantum-dots would potentially enable direct

integration with current CMOS and allow for an easier transition to the new paradigm. Because of this, research into a semiconductor realization of QCA has been strong, yielding QCA fabricated with GaAs/AlGaAs quantum dots [58, 59] and recently published implementation based on Silicon [26] (shown in Figure 2-14). Unfortunately, current semiconductor patterning technologies do not allow for a small enough size scale to make room temperature operation possible<sup>4</sup>. Therefore, semiconductor QCA suffer from the same temperature and speed limitations found with metal-dot QCA.

Figure 2-14. Silicon based QCA schematic and SEM images from [26]

<sup>&</sup>lt;sup>4</sup> Size scale is inversely proportional to energy separation of ground and excited states, thus smaller size QCA allow for greater noise immunity, a fact which will be shown later in the dissertation.

#### 2.4.3 Molecular QCA

In order to compete with conventional CMOS electronics circuitry in terms of speed [60], reliability, and room-temperature operation [61], projections indicate that traditional QCA will require cells on the size scale of individual molecules [27, 62]. As such, a large amount of research into potential molecular QCA implementations has been accomplished. This research can be broken down into two major fields, the placement and construction of QCA circuits and the choice of a suitable molecule which can provide the required QCA cellular attributes.

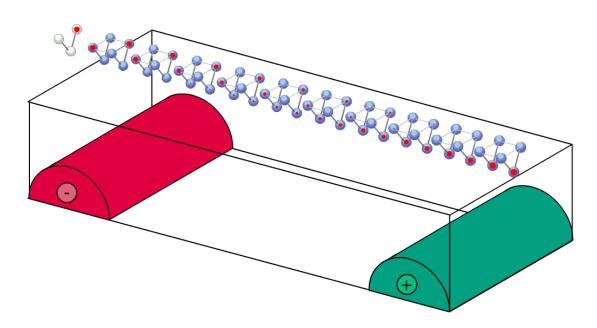

One of the more promising potential technologies for molecular QCA circuit construction involves the use of DNA rafts which are able to form templates for the self-assembly of candidate QCA molecules. The DNA rafts are positioned into lithographically defined trenches in a Si base structure [63] (shown in Figure 2-15). This technique utilizes electron beam lithography which does not scale well into VLSI level circuitry and also produces QCA cells which are slightly above the size scale required for room-temperature operation. However, the direct utilization of both self-assembly for correct relative placement of cells and lithography methods for circuit construction is sound and directly applicable to work proposed in this dissertation.

Figure 2-15. QCA full adder templates formed by electron beam lithographical patterning from [63]

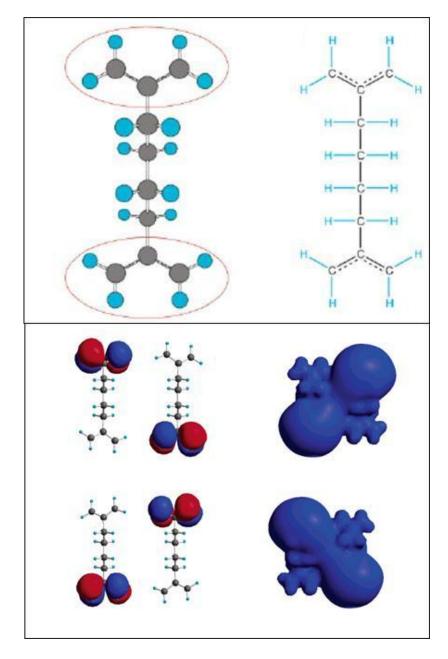

Other work in molecular QCA has focused on the identification of suitable molecules for which QCA cells can be constructed. These molecules are generally mixed valence complexes with either two or four redox centers acting as the quantum dots [64, 65, 66, 67]. In these cells, electron transport between and localization in the redox centers define which molecules will be suitable for QCA. A typical molecular candidate is shown in Figure 2-16 along with *Ab Initio* simulation results for the surfaces of constant potential for each of the QCA states.

Figure 2-16. Mixed valence candidate molecular cell for QCA, along with the constant charge radiuses for the two logical QCA states, taken from [27]

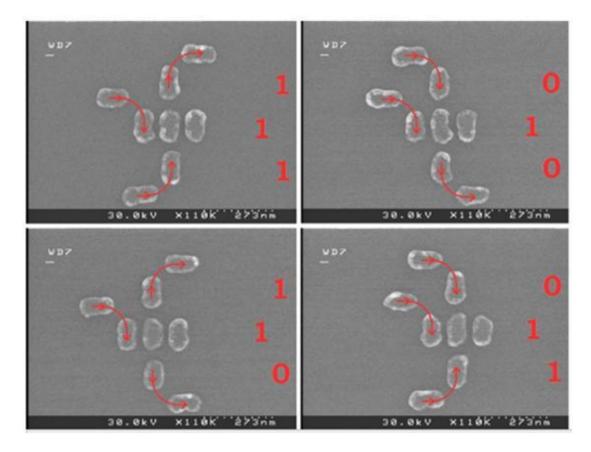

# 2.4.4 Magnetic QCA

Implementations which utilize magnetic dipole interaction between cells have recently gained much attention due to their ability to allow for near roomtemperature operation and very low power requirements [68, 69, 70, 71]. Magnetic QCA are constructed of oblong nano-magnetic particles which form QCA half cells. Due to shape anisotropy, the magnetic dipole aligns along the longer part of the cell. Therefore, these cells can be laid out in the way shown in Figure 2-17 to produce QCA computing and communication. In several instances these cells have been laid out in a way which deviates from the square QCA cell in order to more effectively utilize their half-cell geometry especially for logic structures [28]. One instance of this can be seen in Figure 2-17 for a majority gate.

Magnetic implementations have relatively slow switching speeds, which are in the MHz range, making them unsuitable for competition with even current CMOS electronics. However, because of their robust nature and natural radiation immunity, certain specific applications may find benefit by using this implementation.

Figure 2-17. Implementations of a majority gate for magnetic quantum-dot cellular automata. From [28]

# 2.5 QCA Adiabatic Switching and Clocking

As has been discussed, the QCA paradigm is dependent on the state of the system being in the preferable least energy configuration based on the Hamiltonian in (2.1). However, utilizing this property for digital electronics has several difficulties which must be addressed. Most importantly, the QCA system is not isolated and thus other factors play into the system energy state other than the QCA cells themselves. Temperature for instance, may play a large role in determining system state of QCA devices. Thermal excitations may promote the QCA cells to a higher energy configuration and thus cause

errors in the digital logic. To be robust and protect against these types of excitations the lowest energy configuration must be separated from the 1<sup>st</sup> excited state by several times  $k_BT$  (the Boltzmann constant multiplied by the temperature). This separation in the first energy levels of the system is dependent on several factors including the spacing between quantum dot and QCA cells and the configuration of the dots. Therefore, these properties must be determined before robust application can occur.

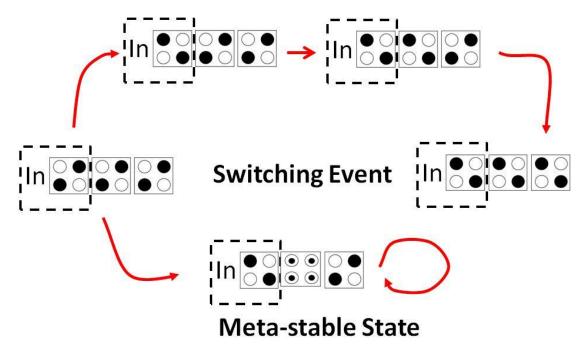

Another source of error in QCA is states that provide local energy minimums which may be attractive as the system switches. These states are called metastable states and can produce circuit errors if they are not overcome within the normal settling timescales. Unfortunately, the process of overcoming the barriers associated with these states is probabilistic and dependent on several factors including the barrier height and energy of the system. However, adjusting these parameters to create favorable conditions for successfully transitioning through meta-stable states will cause other problems that may lead to circuit errors.

A simple example of metastable states and their potential to cause circuit errors is seen in Figure 2-18. In this figure, a switching event occurs in a simple binary wire as the input cell is set from a logic 1 to a logic 0 state. Ideally, this switching event would move down the wire sequentially until all of the cells in the wire had the same logic value (this is the global minimum wire state). However, the process of switching is not instantaneous and therefore as the wire transitions, it is possible for a cell to be caught in a unpolarized state with

the cells to the left and right inducing equal and opposite polarizations on it. Because of this the cell would not transition out of the unpolarized state and thus the switched signal would not propagate to the end of the wire.

Figure 2-18. Binary wire switching event may lead to a correct output or metastable states.

The process and dynamics by which this switching happens is dependent on the coupling of the QCA to the environment and the ability of the QCA to gain and then dissipate the energy gained through the change of input. These processes also affect circuit properties such as speed and temperature in which robust operation is possible and provide a very challenging environment for optimization.

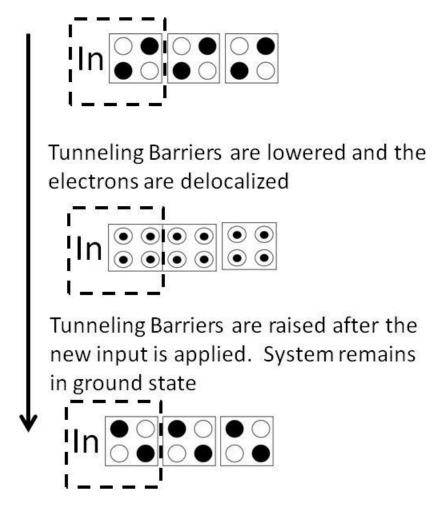

#### 2.5.1 Adiabatic Switching of QCA

To overcome the problems of metastable states and their effects on the correctness of QCA computation and the speed at which switching may occur, an alternate mode of switching was proposed in [72] and verified in metal-dot implementations in [73]. In this method, the system is switched slowly enough to allow it to continuously remain in the lowest energy state. This adiabatic switching is accomplished through direct control of tunneling barrier heights which allow or inhibit interdot electron tunneling. The process works by lowering the tunneling energy barriers internal to the cells prior to switching inputs of the system. Then, as the cells are in a state in which the electrons are delocalized, the inputs are changed. The tunneling energy barriers are then slowly increased and the system converges to the instantaneous global ground state which corresponds to the correct logical configuration. Figure 2-19 shows an example of this process.

While adjustment of each individual cell's tunneling barriers is crucial to enable adiabatic switching, it is necessary to limit the complexity of the wiring which allows for it. If this is not accomplished, the wiring required to distribute the switching signals would easily dominate the device design and therefore improvements over modern digital circuits would not be achieved. Therefore, switching groups of QCA cells with the same wire and signal is the preferred method of laying out clocking circuitry and making implementation tractable [74, 75]. This process would resemble the functional pipelining found in modern processor circuitry and the adjusting of tunnel barriers would resemble a clock.

In fact, the process for raising and lowering tunnel barriers should be thought of this way in order to organize the circuitry to perform logical operations [76].

Figure 2-19. Adiabatic Switching of QCA binary wire

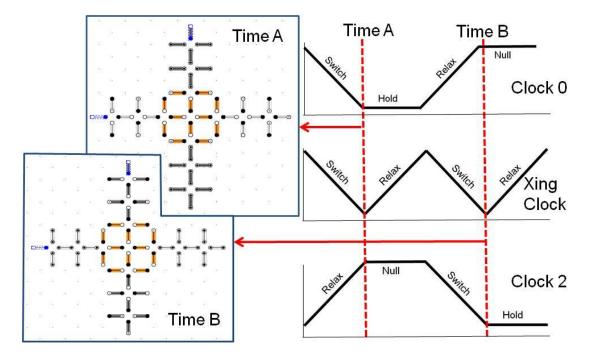

# 2.5.2 QCA clocking

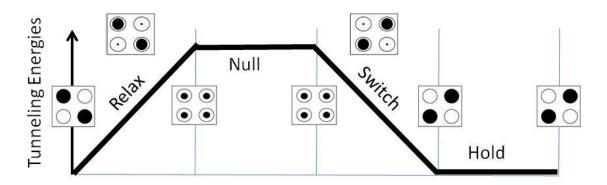

The adiabatic clocking process is divided into four phases which correspond to the raising and lowering of tunnel barriers. These four phases, shown in Figure 2-20 are:

Relax - in which the tunnel barriers are lowered and the electrons are delocalized,

- Null in which the electrons are delocalized and the cells have no logical effect on other QCA cells,

- Switch in which the cells tunneling barriers are raised, the cell's electrons become localized and are switched to their new ground state, and

- Hold in which the interdot barriers are made high enough to where no switching is allowed; thus allowing for these cells to be used as inputs to other parts of the circuit without the other cells affecting their state.

The QCA clock not only allows for pipelining of QCA circuitry which allows for fast operation, but it also allows for more robust operation, higher complexity potential in circuit layouts, and important logical constructs such as feedback of signals [75, 77]. In fact, clocking has become crucial to the theoretical development of QCA electronics.

Figure 2-20. Four phases of the QCA clock

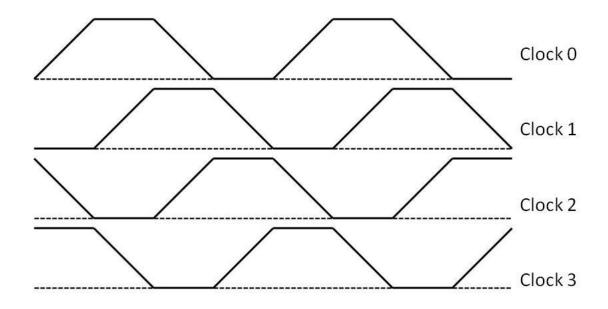

Figure 2-21.Four clocks used for QCA

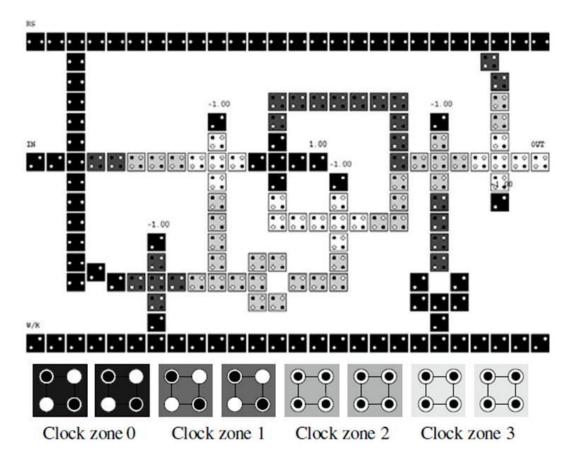

In large scale QCA circuitry, it is required to have four different clocks (shown in Figure 2-21) distributed throughout the circuit. These four clocks all contain the exact same waveform and each clock is out of phase with the others on ¼ cycle intervals. This produces a single clock in each of the four QCA phases at any given instant. With this design, clocking is applied to the QCA cells so that cells in the Hold phase drive cells which are in the Switch phase. An example of a circuit with each of these four clocks being utilized is shown in Figure 2-22. In this figure, a sequential circuit element is shown (in this case a QCA memory cell) to demonstrate feedback with QCA. This clocking scheme is usually referred to as Laudaner clocking and is the basic way of pipelining throughout a circuit. Other clocking schemes such as Bennett Clocking are suitable for reversible clocking of QCA circuitry [78] and will be discussed further, later in this chapter.

Figure 2-22. QCA memory cell. The cells are colored with different shades of grey corresponding to the usage of one of the four clock zones. Taken from [79]

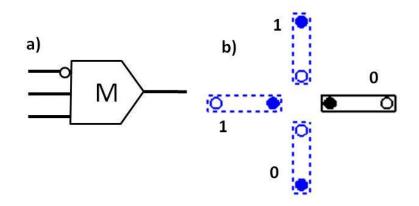

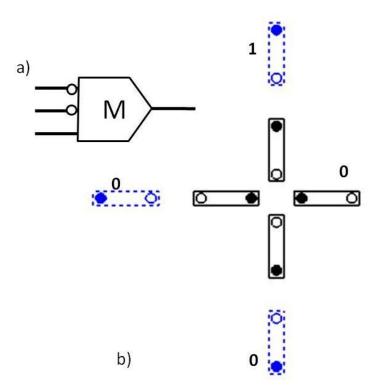

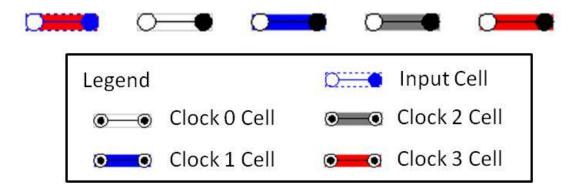

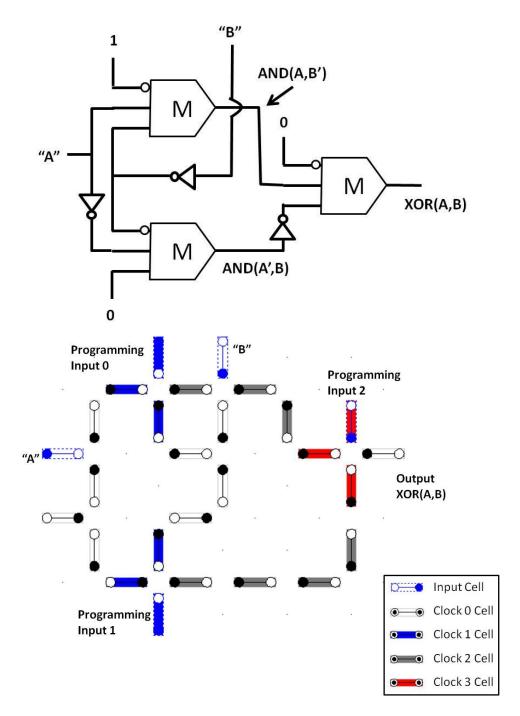

## 2.5.3 Implementation of QCA Clocking