# UNIVERSITÉ DE MONTRÉAL

# IMPLEMENTATION OF ULTRA-LOW LATENCY AND HIGH-SPEED COMMUNICATION CHANNELS FOR AN FPGA-BASED HPC CLUSTER

ROBERTO SANCHEZ CORREA DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES (GÉNIE ÉLECTRIQUE) MAI 2017

# UNIVERSITÉ DE MONTRÉAL

# ÉCOLE POLYTECHNIQUE DE MONTRÉAL

## Ce mémoire intitulé :

# IMPLEMENTATION OF ULTRA-LOW LATENCY AND HIGH-SPEED COMMUNICATION CHANNELS FOR AN FPGA-BASED HPC CLUSTER

présenté par : <u>SANCHEZ CORREA Roberto</u> en vue de l'obtention du diplôme de : <u>Maîtrise ès sciences appliquées</u> a été dûment accepté par le jury d'examen constitué de :

- M. SAVARIA Yvon, Ph. D., président

- M. <u>DAVID Jean Pierre</u>, Ph. D., membre et directeur de recherche

- M. BOIS Guy, Ph. D., membre

# **DEDICATION**

To my wife Ely and my parents, Thank you for all.

#### ACKNOWLEDGEMENTS

First, I would like to thank my supervisor, professor Jean Pierre David, for giving me the possibility to be part of his research lab and seeing in me the potential to complete this work. I am very thankful for all of his advice and support in both professional and personal areas. His professionalism and research skills are worthy of inspiration. Professor Jean Pierre is the kind of professor that tells you:  $\ll$  "if you have problems or you are stuck, don't hesitate to knock on the door of my office" $\gg$ , and he means it; and I am very thankful for that.

I also would like to thank the "Groupe de Recherche en Microélectronique et Systèmes" (GR2M) and the Electrical Engineering Department for funding this research. It has been an amazing journey at Poly.

To my family and my friends, thank you guys for your support and concerns. To my beautiful wife, thank you for being a constant source of support and encouragement, for waking always by my side and for helping me during the challenges of life. To my parents, thank you for all you have done for me. To all of you, this work is as mine as yours.

Finally, I would like to thank Federico Montano, Ph.D. student and friend from the lab. Thank you for your help and your advice, and for the great times we had at the lab.

## RÉSUMÉ

Les clusters basés sur les FPGA bénéficient de leur flexibilité et de leurs performances en termes de puissance de calcul et de faible consommation. Et puisque la consommation de puissance devient un élément de plus en plus importants sur le marché des superordinateurs, le domaine d'exploration multi-FPGA devient chaque année plus populaire.

Les performances des ordinateurs n'ont jamais cessé d'augmenter mais la latence des réseaux d'interconnexion n'a pas suivi leur taux d'amélioration. Dans le but d'augmenter le niveau d'abstraction et les fonctionnalités des interconnexions, la complexité des piles de communication atteinte à nos jours engendre des coûts et affecte la latence des communications, ce qui rend ces piles de communication très souvent inefficaces, voire inutiles. Les protocoles de communication commerciaux existants et les contrôleurs d'interfaces réseau FPGA-FPGA n'ont la performance pour supporter ni les applications à temps critique ni un partitionnement étroitement couplé des systèmes sur puce. Au lieu de cela, les approches de communication personnalisées sont souvent préférées.

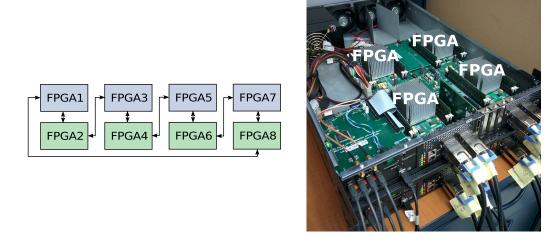

Dans ce travail, nous proposons une implémentation de canaux de communication à haut débit et à faible latence pour une grappe de FPGA. Le système est constitué de deux BEE3, chacun contenant 4 FPGA de la famille Virtex-5 interconnectés par une topologie en anneau. Notre approche exploite la technologie à transducteur à plusieurs gigabits par seconde pour l'obtention d'une bande passante fiable de 8Gbps. Le module de propriété intellectuelle (IP) de communication proposé permet le transfert de données entre des milliers de coprocesseurs sur le réseau, grâce à l'implémentation d'un réseau direct avec capacité de routage de paquets. Les résultats expérimentaux ont montré une latence de seulement 34 cycles d'horloge entre deux nœuds voisins, ce qui est un des plus bas parmi ceux rapportés dans la littérature.

En outre, nous proposons une architecture adaptée au calcul à haute performance qui comporte un traitement extensible, parallèle et distribué. Pour une plateforme à 8 FPGA, l'architecture fournit 35.6Go/s de bande passante effective pour la mémoire externe, une bande passante globale de réseau de 128Gbps et une puissance de calcul de 8.9GFLOPS. Un solveur matrice-vecteur de grande taille est partitionné et mis en œuvre à travers le cluster. Nous avons obtenu une performance et une efficacité de calcul concurrentielles grâce à la faible empreinte du protocole de communication entre les éléments de traitement distribués.

Ce travail contribue à soutenir de nouvelles recherches dans le domaine du calcul parallèle intensif et permet le partitionnement de système sur puce à grande taille sur des clusters à base de FPGA.

#### **ABSTRACT**

An FPGA-based cluster profits from the flexibility and the performance potential FPGA technology provides. Since price and power consumption are becoming increasingly important elements in the High-Performance Computing market, the multi-FPGA exploration field is getting more popular each year.

Network latency has failed to keep up with other improvements in computer performance. Complex communication stacks have sacrificed latency and increased overhead to achieve other goals, being in most of the time inefficient and unnecessary. The existing commercial off-the-shelf communication protocols and Network Interfaces Controllers for FPGA-to-FPGA interconnection lack of performance to support time-critical applications and tightly coupled System-on-Chip partitioning. Instead, custom communication approaches are preferred.

In this work, ultra-low latency and high-speed communication channels for an FPGA-based cluster are presented. Two BEE3s grouping 8 FPGAs Virtex-5 interconnected in a ring topology, compose the targeting platform. Our approach exploits Multi-Gigabit Transceiver technology to achieve reliable 8Gbps channel bandwidth. The proposed communication IP supports data transfer from coprocessors over the network, by means of a direct network implementation with hop-by-hop packet routing capability. Experimental results showed a latency of only 34 clock cycles between two neighboring nodes, being one of the lowest in the literature.

In addition, it is proposed an architecture suitable for High-Performance Computing which includes performing scalable, parallel, and distributed processing. For an 8 FPGAs platform, the architecture provides 35.6GB/s off-chip memory throughput, 128Gbps network aggregate bandwidth, and 8.9GFLOPS computing power. A large and dense matrix-vector solver is partitioned and implemented across the cluster. We achieved competitive performance and computational efficiency as a result of the low communication overhead among the distributed processing elements.

This work contributes to support new researches on the intense parallel computing fields, and enables large System-on-Chip partitioning and scaling on FPGA-based clusters.

# TABLE OF CONTENTS

| DEDICATION                                                       | • |  |  | • | . iii  |

|------------------------------------------------------------------|---|--|--|---|--------|

| ACKNOWLEDGEMENTS                                                 |   |  |  |   | . iv   |

| RÉSUMÉ                                                           |   |  |  |   | . v    |

| ABSTRACT                                                         |   |  |  |   | . vi   |

| TABLE OF CONTENTS                                                |   |  |  |   | . vii  |

| LIST OF TABLES                                                   |   |  |  |   | . ix   |

| LIST OF FIGURES                                                  |   |  |  |   | . x    |

| LIST OF SYMBOLS AND ABBREVIATIONS                                |   |  |  |   | . xii  |

| LIST OF APPENDIXES                                               |   |  |  |   | . xiii |

| CHAPTER 1 INTRODUCTION                                           |   |  |  |   | . 1    |

| CHAPTER 2 BACKGROUND                                             | • |  |  |   | . 6    |

| 2.1 Project background: The Goliath supercomputer                |   |  |  |   | . 6    |

| 2.2 Basic interconnection network concepts                       | • |  |  |   | . 8    |

| CHAPTER 3 LITERATURE REVIEW                                      |   |  |  |   | . 11   |

| 3.1 Pure multi-FPGA machines                                     |   |  |  |   | . 11   |

| 3.2 FPGA-based network accelerators and heterogeneous machines . |   |  |  |   | . 15   |

| 3.3 Recent trends in FPGA interconnect technology                |   |  |  |   | . 19   |

| 3.4 Matrix-vector multiplication for scientific applications     |   |  |  |   | . 20   |

| 3.5 Conclusions                                                  | • |  |  |   | . 23   |

| CHAPTER 4 THE COMMUNICATION IP                                   |   |  |  |   | . 26   |

| 4.1 Communication requirements                                   |   |  |  |   | . 26   |

| 4.2 Architecture                                                 |   |  |  |   | . 27   |

| 4.2.1 Physical layer                                             |   |  |  |   | . 27   |

| 4.2.2 Link and network layers                                    |   |  |  |   | . 30   |

| 4.3 Software interface                                           |   |  |  |   | . 39   |

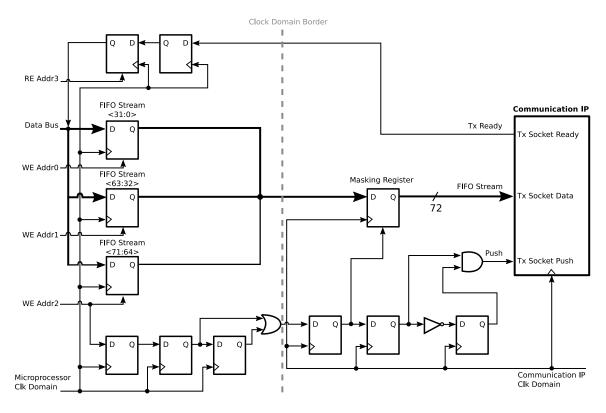

|        | 4.3.1   | Transmission software interface module                | 40 |

|--------|---------|-------------------------------------------------------|----|

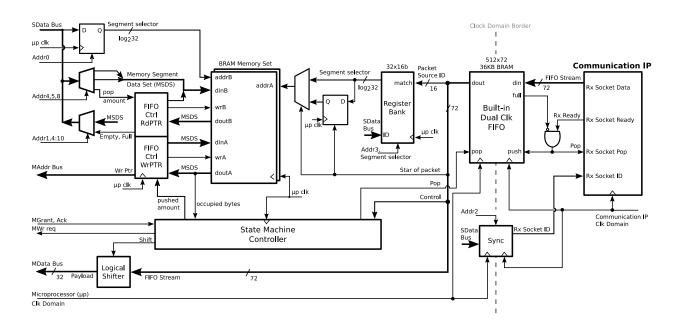

|        | 4.3.2   | Reception software interface module                   | 40 |

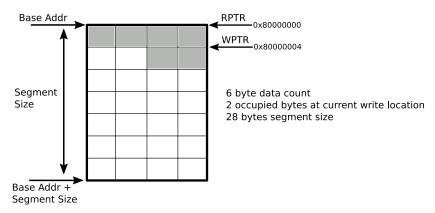

|        | 4.3.3   | IP configuration and utilization by software examples | 43 |

| 4.4    | Implei  | mentation and results                                 | 48 |

|        | 4.4.1   | Platform description                                  | 49 |

|        | 4.4.2   | Implementation                                        | 49 |

| 4.5    | Verific |                                                       | 58 |

| 4.6    | Conclu  | usion                                                 | 60 |

| СНАРТ  | TER 5   | HIGH-PERFORMANCE COMPUTING TEST ON A MULTI-FPGA       |    |

|        | TFOR    |                                                       | 63 |

| 5.1    | HPC t   | test: Dense matrix-vector multiplication              | 63 |

| 5.2    |         | rm architecture                                       | 65 |

|        | 5.2.1   | Memory system                                         | 66 |

|        | 5.2.2   | Processing units                                      | 71 |

|        | 5.2.3   | Microprocessor system                                 | 75 |

|        | 5.2.4   | Communication IP                                      | 78 |

| 5.3    | Tightl  | y coupled FPGA cluster                                | 79 |

|        | 5.3.1   | Programming and diagnostic                            | 79 |

|        | 5.3.2   | Performance evaluation and results                    | 81 |

| 5.4    | Conclu  | usion                                                 | 85 |

| СНАРТ  | TER 6   | CONCLUSION                                            | 86 |

| 6.1    | Advan   | acement of knowledge                                  | 88 |

| 6.2    |         | and constraints                                       | 88 |

| 6.3    |         | nmendations                                           | 88 |

| REFER  | ENCE    | S                                                     | 89 |

| ∆ PPEN | DICES   | <u>.</u>                                              | 03 |

# LIST OF TABLES

| Popular Interconnection Networks Diameters [1]                           | 9                                                                                                                          |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| UltraScale and ultraScale+ architecture transceiver portfolio [2]        | 19                                                                                                                         |

| Xilinx's latest trends in high-speed serial solution [3]                 | 20                                                                                                                         |

| Summary on high-performance communication implementations using          |                                                                                                                            |

| FPGAs                                                                    | 24                                                                                                                         |

| Summary on computational performance on different MVM implemen-          |                                                                                                                            |

| tations with dense matrices results                                      | 25                                                                                                                         |

| Register address space for the transmission and reception software in-   |                                                                                                                            |

| terface modules                                                          | 44                                                                                                                         |

| Resource utilization for communication IP in a Virtex-5 xl155t FPGA.     | 55                                                                                                                         |

| Latency report in clock cycles for the communication IP                  | 55                                                                                                                         |

| Communication IP test plan summary for the transmission section          | 59                                                                                                                         |

| NPI latency and throughput for the implemented memory system [4].        | 67                                                                                                                         |

| Maximum matrix-vector data set size for matrix-vector multiplication     |                                                                                                                            |

| on the BEE3 platform. Architecture constraints                           | 69                                                                                                                         |

| Resource utilization for the floating point double-precision dot-product |                                                                                                                            |

| operators on a Virtex-5 xl155t FPGA                                      | 74                                                                                                                         |

| Resource utilization for the HPC test on a Virtex-5 xl155t FPGA          | 84                                                                                                                         |

| The communication IP features and a state-of-the-art comparison          | 87                                                                                                                         |

| Computational performance on different MVM implementations with          |                                                                                                                            |

| dense matrices results                                                   | 87                                                                                                                         |

|                                                                          | UltraScale and ultraScale+ architecture transceiver portfolio [2] Xilinx's latest trends in high-speed serial solution [3] |

# LIST OF FIGURES

| Figure 1.1                                                                | High-Performance Computer architectures over time [5] (Nov2016)          | 2  |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------|----|

| Figure 1.2                                                                | HPC Interconnect families [5] (Nov2016)                                  | 3  |

| Figure 2.1 VESI architecture proposed by Professor Jean Pierre David et Y |                                                                          |    |

|                                                                           | Savaria at Polytechnique Montréal                                        | 6  |

| Figure 2.2                                                                | Goliath's 1Gbps Ethernet communication solution                          | 7  |

| Figure 3.1                                                                | AIREN block diagram for a single communication channel on the $Spirit$   |    |

|                                                                           | FPGA-based cluster                                                       | 12 |

| Figure 3.2                                                                | Internet protocols stack implementation example over 10 Gigabit Eth-     |    |

|                                                                           | ernet                                                                    | 13 |

| Figure 3.3                                                                | Switch module architecture                                               | 14 |

| Figure 3.4                                                                | BlueLink communication approach                                          | 15 |

| Figure 3.5                                                                | Interconnection framework block diagram for multi-FPGA cluster [6].      | 17 |

| Figure 3.6                                                                | Row-major BLAS gaxpy architecture [7]                                    | 22 |

| Figure 3.7                                                                | Parallel matrix-vector multiplication with $R3$ processing elements [8]. | 23 |

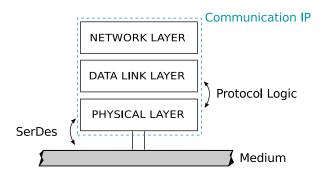

| Figure 4.1                                                                | The communication IP layers based on the OSI model                       | 27 |

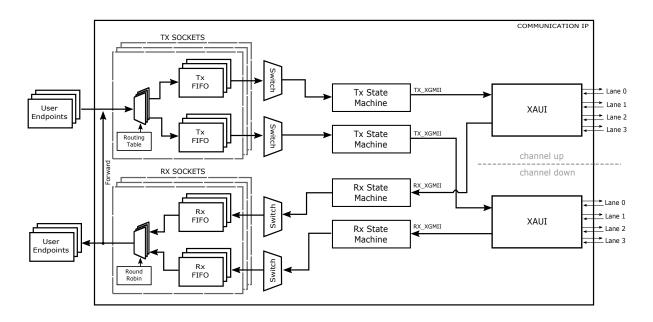

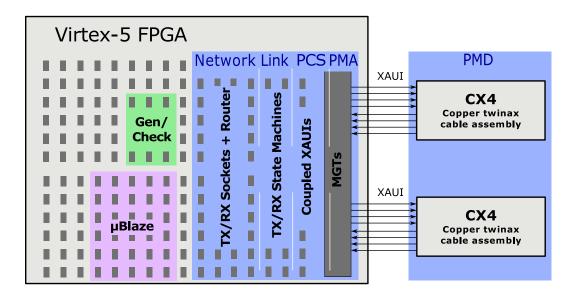

| Figure 4.2                                                                | The communication IP block diagram                                       | 28 |

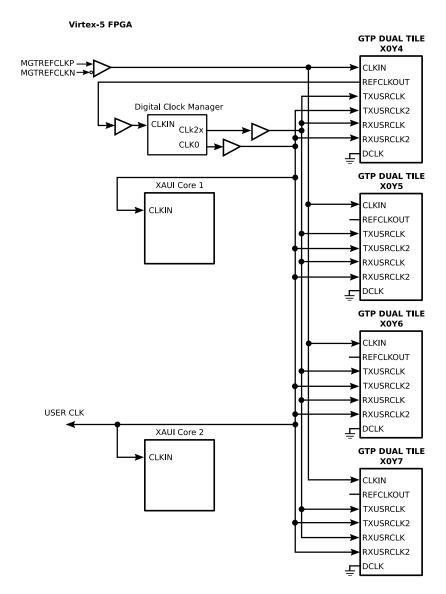

| Figure 4.3                                                                | Two coupled XAUIs clocking scheme                                        | 29 |

| Figure 4.4                                                                | A custom protocol example at the communication IP user side (FIFO        |    |

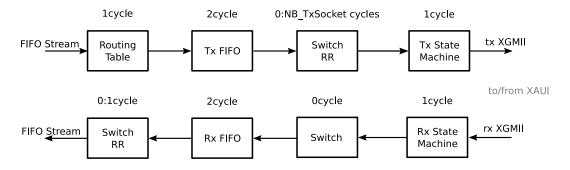

|                                                                           | stream) and at the XAUIs user side (XGMII stream)                        | 31 |

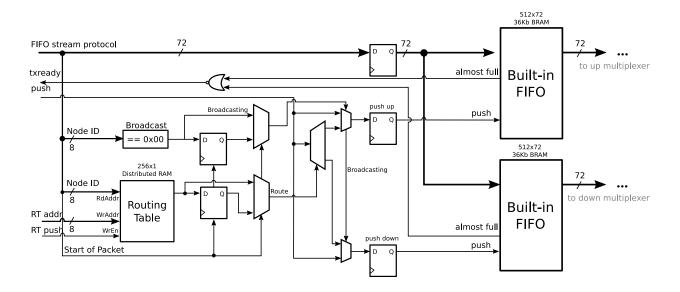

| Figure 4.5                                                                | Transmission socket architecture                                         | 33 |

| Figure 4.6                                                                | Default Tx and Rx sockets architecture interconnected for packet for-    |    |

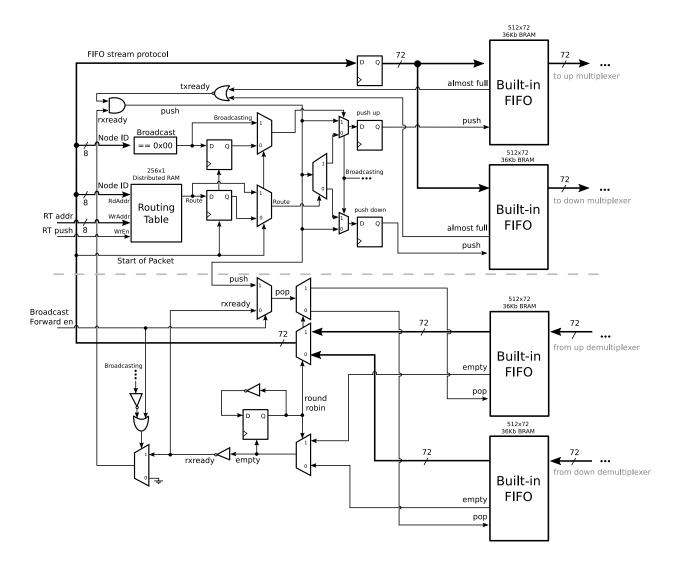

|                                                                           | warding                                                                  | 35 |

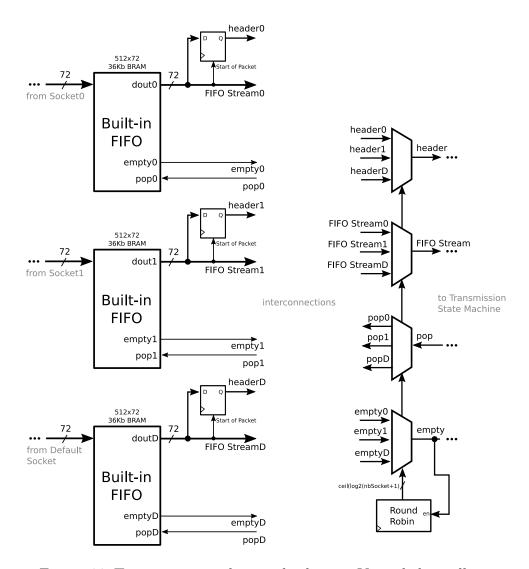

| Figure 4.7                                                                | Transmission sockets multiplexing. Virtual channelling                   | 36 |

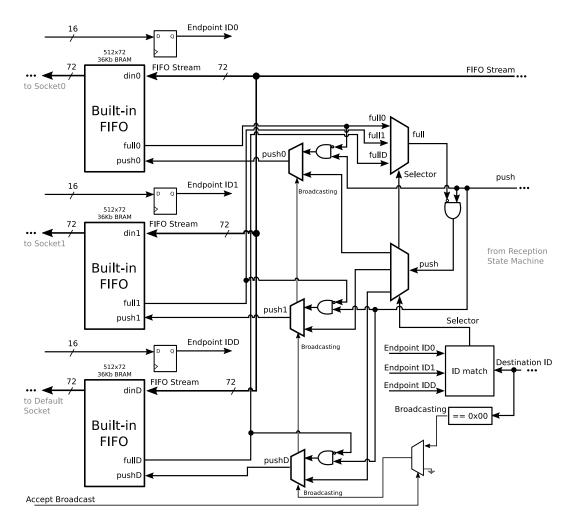

| Figure 4.8                                                                | Reception sockets demultiplexing. Virtual channelling                    | 37 |

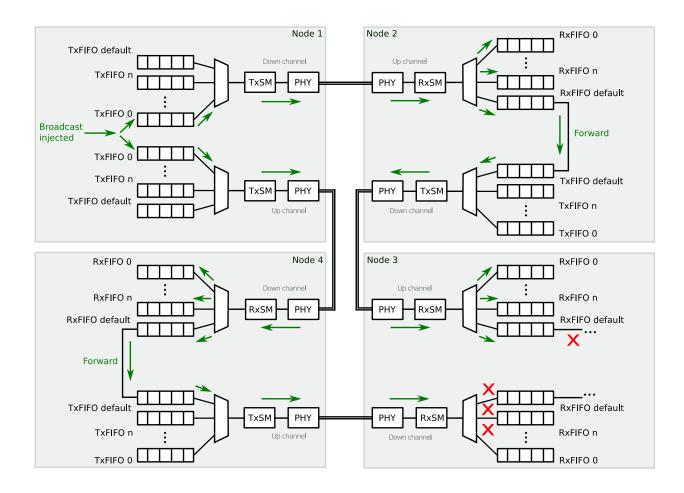

| Figure 4.9                                                                | Broadcast packet propagating across the network                          | 38 |

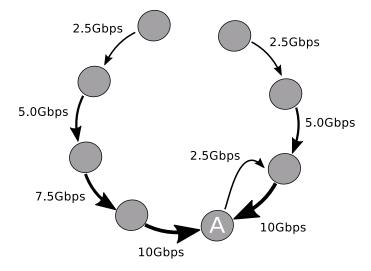

| Figure 4.10                                                               | Effective data rate estimation example to avoid flow control             | 39 |

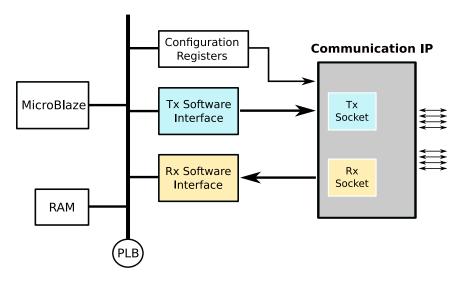

| Figure 4.11                                                               | Software interface for the communication IP                              | 39 |

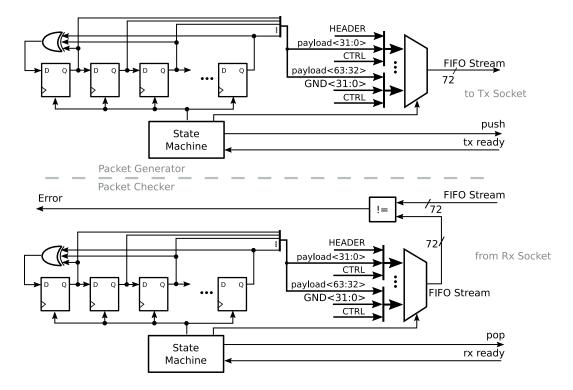

| Figure 4.12                                                               | Transmission software interface module                                   | 41 |

| Figure 4.13                                                               | Reception software interface module                                      | 42 |

| Figure 4.14                                                               | An example of a memory segment state controlled by the Rx software       |    |

|                                                                           | interface module                                                         | 43 |

| Figure 4.15                                                               | Multi-FPGA platform for testing the communication IP. Eight-FPGA         |    |

|                                                                           | machine based on two BEE3 systems                                        | 49 |

| Figure 4.16 | The implementation system. A technology view                        | 50 |

|-------------|---------------------------------------------------------------------|----|

| Figure 4.17 | Packet generator and checker architecture                           | 51 |

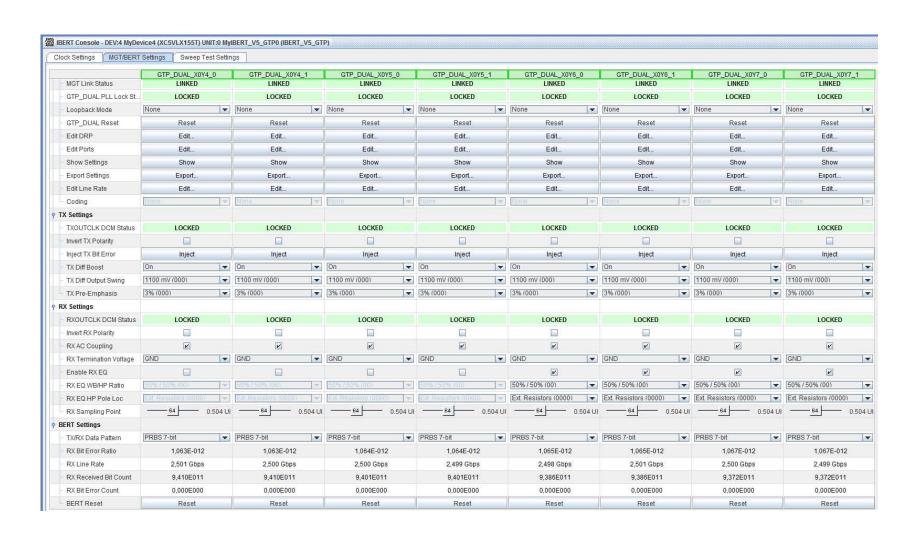

| Figure 4.18 | Xilinx IBERT screenshot for link tune up                            | 53 |

| Figure 4.19 | Latency estimation per block on the communication stack             | 54 |

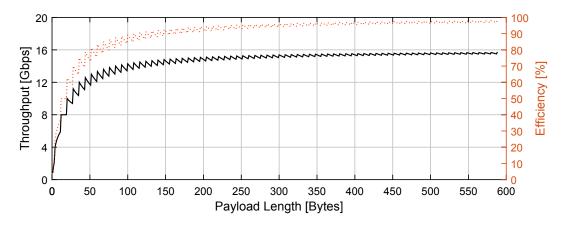

| Figure 4.20 | Custom protocol throughput                                          | 56 |

| Figure 4.21 | Minimum latency for 32-bit payload packets. Communication IP wave-  |    |

|             | form simulation                                                     | 57 |

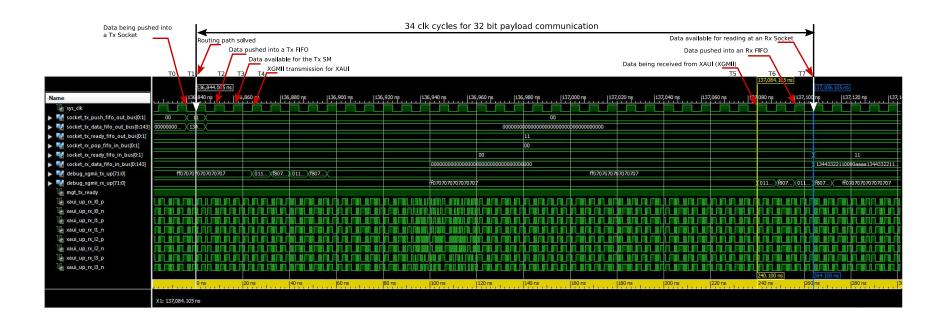

| Figure 4.22 | Features verification example with software stimulus and Chipscope  |    |

|             | monitoring                                                          | 61 |

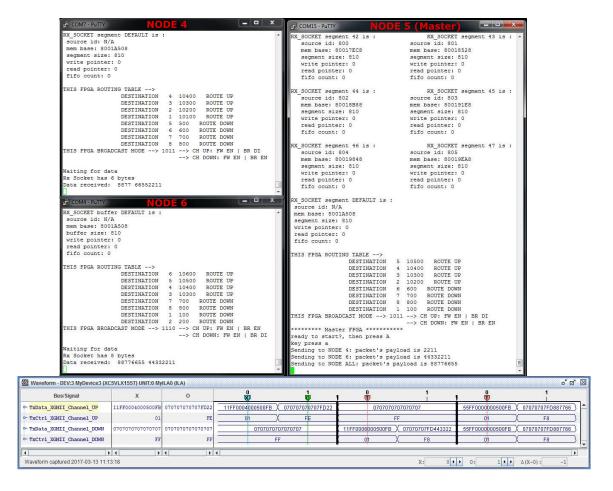

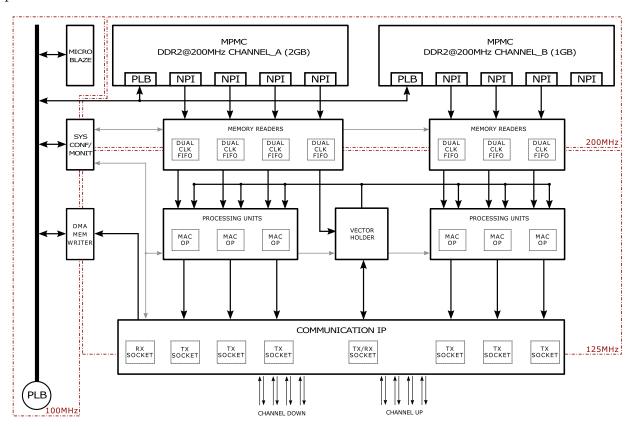

| Figure 5.1  | Architecture for the High-Performance Computing test                | 65 |

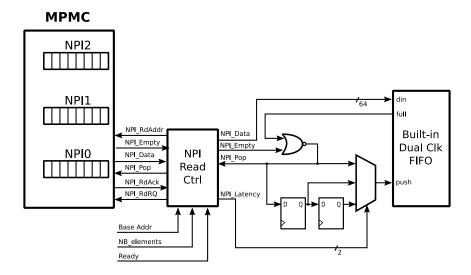

| Figure 5.2  | Architecture of the native port interface memory reader             | 68 |

| Figure 5.3  | Vector holder architecture                                          | 70 |

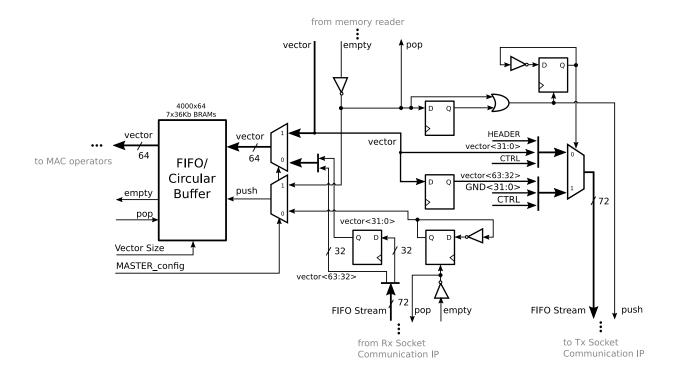

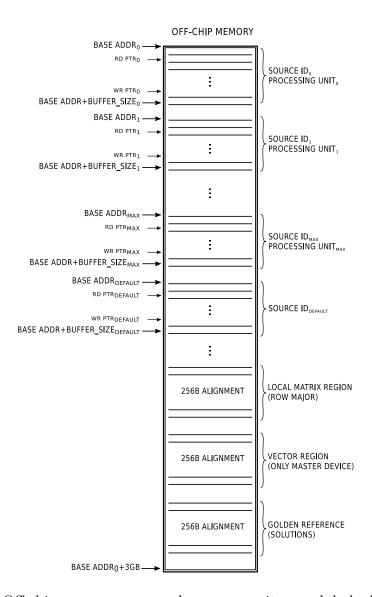

| Figure 5.4  | Off-chip memory map and memory writer module look-up table          | 72 |

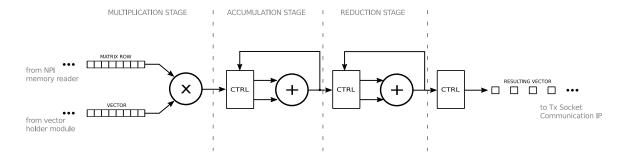

| Figure 5.5  | Dot-product operator architecture                                   | 73 |

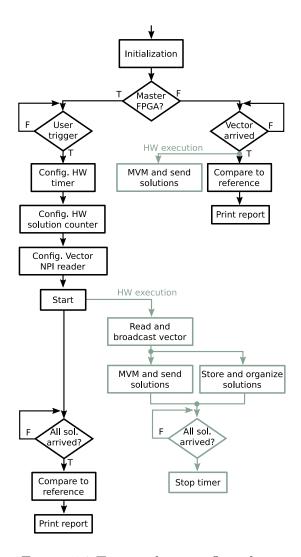

| Figure 5.6  | Test application flow chart                                         | 77 |

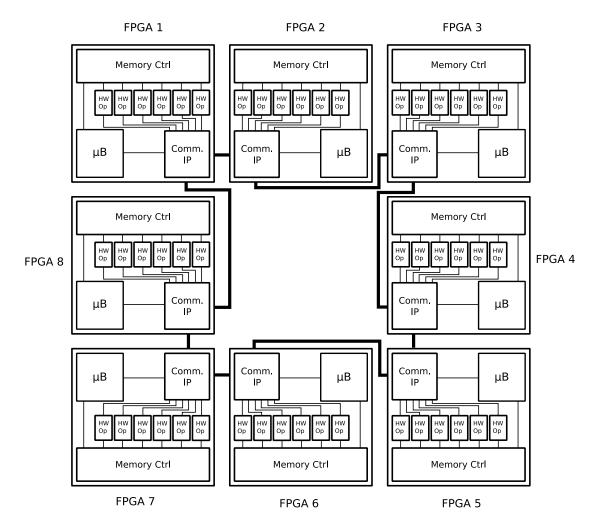

| Figure 5.7  | Global view of the high-performance computing system                | 80 |

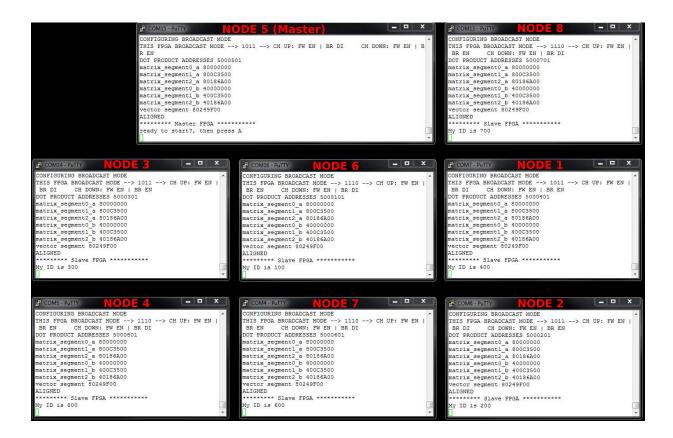

| Figure 5.8  | Eight window shells, one per FPGA. Screenshot on platform ready.  . | 82 |

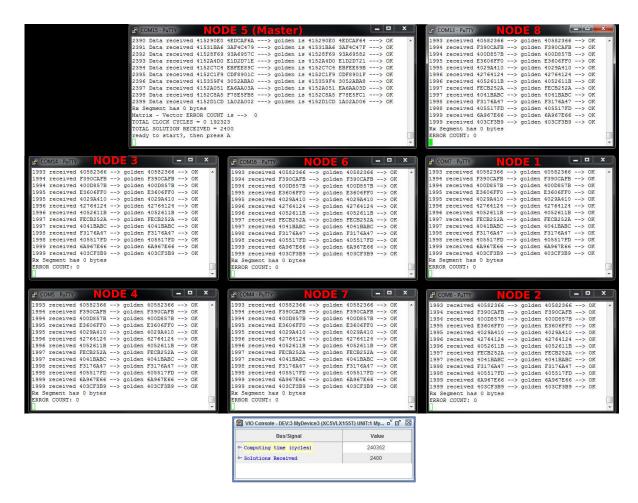

| Figure 5.9  | Computing completion screenshot                                     | 84 |

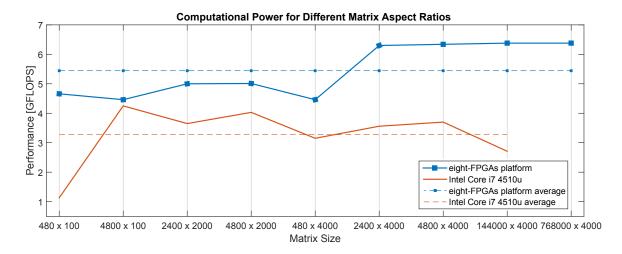

| Figure 5.10 | Experimental results for performance estimation using dense matrix- |    |

|             | vector multiplication on the eight-FPGA Virtex-5 platform and the   |    |

|             | Intel Core i7-4510u microprocessor                                  | 85 |

#### LIST OF SYMBOLS AND ABBREVIATIONS

10GbE 10-Gigabit Ethernet

BEE Berkeley Emulation Engine

BER Bit Error Ratio

CDR Clock Data Recovery

CRC Cyclic Redundancy Check

FMC FPGA Mezzanine Card

HPC High Performance Computing

IBERT Integrated Bit Error Ratio Tester

IP Intellectual Property

MAC Media Access ControllerMGT Multi-Gigabit Transceiver

MPSoC MultiProcessor System-on-Chip

NIC Network Interface Controller

OSI Open Systems Interconnection

PCB Printed Circuit Board

PCS Physical Coding Sublayer

PE Processing Element

PHY Physical Layer Device

PMA Physical Medium Attachment

PRBS Pseudo-Random Bit Sequences

SATA Serial Advanced Technology Attachment

SerDes Serializer/Deserializer

TCP Transmission Control Protocol

XAUI Ten Gigabit Attachment Unit Interface

XGMII Ten Gigabit Media Independent Interface

# LIST OF APPENDIXES

| Annexe A | Modifications to the transceivers' wrapper source file | 93 |

|----------|--------------------------------------------------------|----|

| Annexe B | Native Port Interface source code                      | 95 |

#### CHAPTER 1 INTRODUCTION

Numerous applications like mining exploration, weather forecasting, molecular dynamics modeling, financial computing, among others, demand increasing amounts of processing capability. In many cases, the computation cores and data types are suited to field-programmable gate arrays (FPGA). A solution is thus hardware acceleration which increases processing with application-specific coprocessors.

FPGAs offer tremendous performance potential and on-chip facility for diverse applications. Modern high-end FPGAs have not only millions of configurable "gates" and interconnections, but also large numbers of hard-wired components. In addition, they have hundreds of general-purpose I/O pins and tens of transceivers for high-speed serial interconnect. FPGAs offer speed-up by hardware and software co-design environments and parallelization, with reduced energy power consumption over other platforms like GPUs or CPUs. Endless design alternatives are possible and may go from pipelines structures with hundreds of stages to soft/hard configurable processors, systolic arrays, etc. Their flexibility enables the designers to realize almost any computer configuration that can be imagined and use any form of concurrent execution to suit the applications. FPGAs work well when applications contain enough parallelism to compensate for their relatively low clock speeds.

Parallel computing is a computational technique where many calculations or the execution of processes are carried out simultaneously. Parallelism has been employed for many years, especially in the High-Performance Computing (HPC) field. Recently, such paradigm has aroused a renewed interest due to the physical constraints preventing frequency scaling.

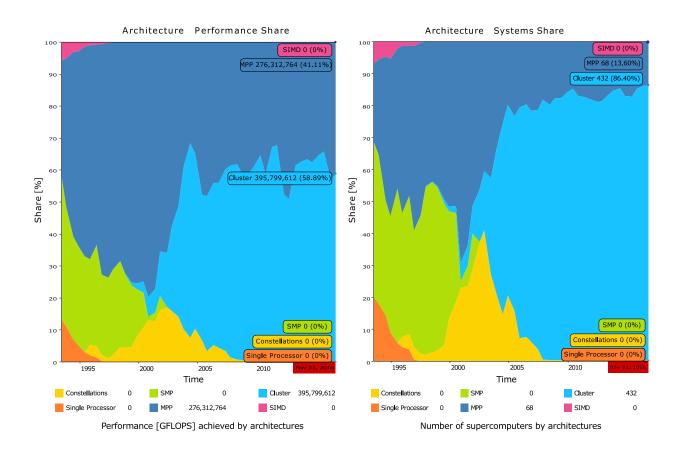

Advanced research in HPC has moved beyond the processing capacity of single computers to supercomputers with different architectures. Figure 1.1 shows the top 500 supercomputers' architecture tendency from the performance and the system points of view. The last trend points out to clustering of commodity devices as the predominant architecture over others like Massively Parallel Processing (MPP) and Symmetric Multiprocessing (SMP). Clustering has been gaining more and more popularity each year since about 2000. Nowadays, 86% of the top 500 supercomputers around the world utilize clustering architecture while the rest focus on Massively Parallel Processing. Moreover, it can be seen that clustering has proven higher performance compared to others. For instance, from the total amount of floating point operations per second (expressed in GFLOPS in Figure 1.1 left) achievable by all 500 supercomputers together, 58.89% corresponds to cluster architectures.

In this context, it is natural that FPGA-based clusters have been focused by the HPC

Figure 1.1 High-Performance Computer architectures over time [5] (Nov2016).

community. In addition, since price and power consumption are becoming increasingly important elements in the HPC market, the multi-FPGA exploration field is growing rapidly. An FPGA-based cluster profits from the flexibility and the performance potential this technology accommodates. It also enables large System-on-Chip partitioning which provides a great deal to create ideal machines for specific applications.

In an HPC cluster, there are three main ways of increasing computational performance: incrementing the number of processing units, improving application algorithm and reducing nodes' interconnections overhead. Loosely coupled computing nodes generally don't communicate too much, so they are not affected by the interconnection metrics. In opposition, tightly coupled nodes do require low latency and high-bandwidth message passing, otherwise, the network becomes the bottleneck of the entire system and the overall performance of the machine may be compromised. Hence, cluster computing scalability and the degree of parallelism is limited by the performance of the interconnect network.

The network's latency property is very important for round-trip communication patterns.

Despite that, network latency has failed to keep up with other improvements in computer performance [9]. Complex communication protocol stacks have affected the latency and increased the overhead, being most of the time inefficient and unnecessary. That is the case of commercial off-the-shelf communication protocols and Network Interfaces Controllers (NIC) when they are used for FPGA-to-FPGA interconnection. It has been demonstrated their lack of performance to support time-critical applications and tightly coupled SoC partitioning [10]. Therefore, custom communication approaches are preferred when targeting high-performance interconnections. This statement is broadened beyond the multi-FPGA field to the supercomputers field where custom interconnection deployments are being widely used.

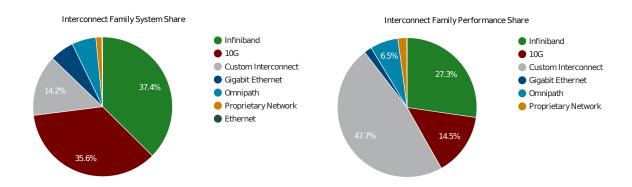

Figure 1.2 presents the interconnection families of the top 500 supercomputers all around the world. As can be seen, the custom interconnects represents the third most utilized interconnect family behind Infiniband and 10Gbps Ethernet. 14.2% of the supercomputers has adopted customizable approaches for communicating their nodes. In terms of performance (Figure 1.2 right), the custom interconnect family takes credits for 47.7% of the global combined performance in the top 500 list. In other words, most of the achievable computing power presently relies on custom approaches.

Figure 1.2 HPC Interconnect families [5] (Nov2016).

Standard and Proprietary interconnects, i.e. 10Gbps Ethernet and Infiniband, are rapidly deployed compared to custom. However, there is a performance penalty to pay and to be considered when building supercomputers. Custom interconnects benefit from a personalized solution for a specific application and/or machine but at the expenses of an increased effort and time delay in the building process. There are different levels on which a custom solution may stand depending on the degree of customization. A fully custom interconnect system personalizes all the layers in the communication stack including the physical device and

the transmission medium. On the other hand, a partially custom interconnect selects the components, functionalities, and layers to be personalized while using commodity when it satisfies the project's needs.

Many challenges have to be faced when designing high-performance custom interconnect network. Each of them is associated with a level of abstraction (layer) in the communication stack. For instance, at the physical level, the link's power consumption, bandwidth, latency, reliability and fault tolerance should be considered. Similarly, at higher communication levels, the network topology and its scalability, the routing algorithm, the congestion control and the programming models have to be addressed as well. Handling these aspects while maintaining high-performance features (i.e. low end-to-end latency, high channel bandwidth and small network diameter) issues a tremendous challenge for the designers.

Once a High-Performance Computing cluster is built, the next step is testing and benchmarking. Running a standard benchmark or a standard parallel application in an FPGA cluster is not straightforward. Since they are written based on a parallel programming model, they need hardware and software support implemented in the FPGAs. This means an operating system should run on a microprocessor and a parallel programming library should be adapted to work properly with the custom interconnect's drivers. Rather than this complicated solution for testing and benchmarking, a simpler approach could be implementing a low-level version of the benchmark or the application instead of its standard counterpart.

A closer look at most common scientific and engineering applications, entailing huge amount and intensity of computing power, shows that they generally have the same basic algebraic operations. This is extended to standard benchmarks in which the computing time elapsed when solving systems of linear equations is measured for estimating the machine performance. Therefore, the implementation of an algebraic kernel partitioned and distributed all across an FPGA cluster allows correctness testing of the cluster's computational units and the interconnect network while still giving an approximate idea of its performance potential. In this context, the matrix-vector multiplication raises as one of the preferred low-level applications to be run on a multi-FPGA machine.

This research is framed as the acceleration of the communication system for the *Goliath* supercomputer located at Polytechnique Montréal. Since *Goliath* is an heterogeneous machine with different types of computational units and interconnect networks, we focus on the 10Gbps FPGA-to-FPGA communication. This research stands on the aforementioned facts that the commercial off-the-shelf communication solutions lack performance to support time-critical applications and tightly coupled System-on-Chip (SoC) partitioning for multi-FPGA machines. In addition, custom communication approaches are being preferred

over standard deployments when high-performance interconnects are required. In *Goliath*'s FPGA-to-FPGA interconnect network, the utilization of a custom communication Intellectual Property (IP) module with low latency and high-bandwidth properties will reduce the overhead associated with data movement and will increase the processing efficiency of the machine. Moreover, it will adapt the communication to satisfy *Goliath*'s needs.

Our main objective is the implementation of communication channels for an FPGA-based High-Performance Computing (HPC) cluster targeting ultra-low latency and high-speed interconnections. We aim at tight integrating of the FPGAs as a result of this research, allowing large SoC partitioning. At the end of this work, a communication IP will be delivered as well as a hardware and software system for HPC support.

## The specific objectives are:

- 1. Design and implement a communication IP that serves as a 10Gbps Network Interface Controller with low overhead features and direct network support.

- 2. Integrate the IP into a hardware and software codesign environment providing network accesses from both systems.

- 3. Build and test a tightly coupled FPGA-based cluster supported by the communication IP.

- 4. Accelerate an application by parallelizing and distributing workloads on the cluster.

This thesis is organized as follows.

- Chapter 2 provides a brief background on this work as part of the *Goliath* supercomputer research program.

- Chapter 3 presents a literature review of the existing implementations on high-speed serial communication between FPGAs.

- Chapter 4 refers to the proposed Intellectual Property module for FPGA-to-FPGA communication, its architecture, implementation and experimental results.

- Chapter 5 explores the inter-FPGA communication channels under a High-Performance Computing environment. A large matrix-vector SoC is partitioned across an FPGA-based cluster for accelerating by parallelization.

- Chapter 6 presents the conclusions of this work and a state-of-the-art comparison.

- Appendix A provides the transceivers' wrapper source file modification after the serial links tune up process.

- Appendix B shares a VHDL description of the Native Port Interface controller for 32 double word burst read transfers from a Multi-Port Memory Controller.

#### CHAPTER 2 BACKGROUND

This chapter describes the environment on which this research stands. It also provides the basic knowledge for the comprehension of the rest of the document and the work carried out.

## 2.1 Project background: The Goliath supercomputer

VESI (Figure 2.1) is an architecture born at Politechnique Montréal. Its creators, Professor Jean Pierre David and Professor Yvon Savaria, aim at the integration of different high-performance computing platforms for scientific and engineering researches. In this context, the Goliath supercomputer emerges as the materialization of VESI.

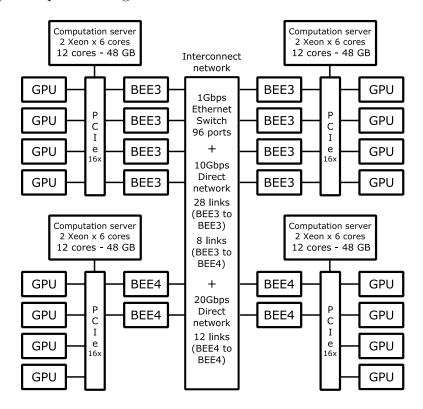

Figure 2.1 VESI architecture proposed by Professor Jean Pierre David et Yvon Savaria at Polytechnique Montréal.

The Goliath supercomputer is an heterogeneous machine that integrates several computational servers equipped with two Intel® Xeon six-core CPUs each. The servers are connected, throughout a PCI-Express 16x bus, to four NVidia® Tesla C2050 GPUs. There are also two types of multi-FPGA machine, each of them hosting four FPGAs: the Berkeley Emulation

Engine 3 (BEE3) and its next generation the BEE4. All of the computational units in the architecture communicate by means of a combination of interconnect networks, i.e. the Ethernet 1Gbps, the 10Gbps and 20Gbps direct links, and the PCIe bus. The tremendous computing potential and the flexibility of Goliath supercomputer make it an ideal machine for High-Performance Computing applications. However, having a highly effective interconnect system supporting the communication between the computational units remains imperative to avoid limiting the overall architecture performance.

This research is framed as the acceleration of the communication system in Goliath. It is the continuity of the Ethernet 1Gbps interconnect project developed for the Goliath's FPGAs at Professor David's research lab.

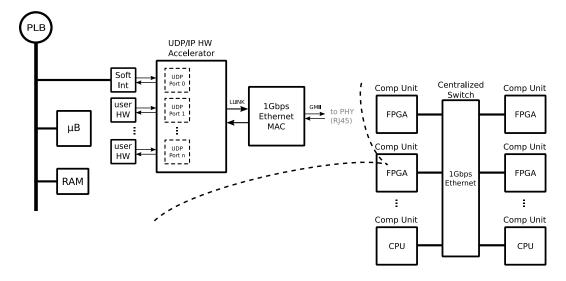

The 1Gbps Ethernet project relies on an indirect network supported by a centralized switch. As shown in Figure 2.2, the switch provides full connectivity to all of the computational units having an RJ-45 interface. From the FPGAs point of view, the communication stack is accelerated with a UDP/IP hardware module and a 1Gbps Ethernet MAC.

Figure 2.2 Goliath's 1Gbps Ethernet communication solution.

The UDP/IP module provides several UDP ports for transmitting, receiving and queueing UDP packets across the 1Gbps network. Each port has an independent interface. They are used to indicate the UDP/IP protocol fields and to give access to the internal transmission and reception buffers (FIFOs). The ports' buffers are multiplexed and demultiplexed, dividing the physical channel into several logical channels. Therefore, any number of user modules along Goliath's FPGAs can be assigned to a UDP port for enabling accessing time to the network. A software interface module and its associated driver facilitate the communication from a microprocessor environment. Within the software interface module, there is a Direct

Memory Access controller which bridges the UDP/IP port to the main memory system.

Closer to the network side, the Ethernet MAC module interfaces the PHY and implements the standard Ethernet MAC function. With this interconnection system, a user can have both hardware and software facilities to communicates across Goliath. However, the overall performance of the supercomputer is compromised because of the well-known limitations of Ethernet solutions. More specifically, the reduced channel bandwidth along with the high-overhead of the Ethernet protocol and its latency penalty, affect directly the system performance by becoming the bottleneck. This drawback may not be important if loosely coupled computational units are intended in Goliath. But, since high-communicating parallel and distributed computational units are in fact intended, then there is clearly a limitation on this interconnection system.

To overcome the presently communication bottleneck in Goliath supercomputer, the next step is the 10Gbps FPGA-based direct network development, on which this research finds its foundation. The Ethernet 1Gbps environment sets the basis and the starting point for pushing further Goliath's interconnection and for solving its aforementioned limitation.

## 2.2 Basic interconnection network concepts

Some of the basic concepts mentioned all along this document are following clarified [11].

- Channel Bandwidth

- Maximum capacity of a network channel (in bit/s). The bandwidth of a link is the theoretical amount of data that could be sent over a channel without regard to practical consideration (latency, protocols) during a specified time period.

- Aggregate Bandwidth

The aggregate bandwidth is defined as the channel bandwidth multiplied by the number of ports.

- Throughput

- It refers to the rate of information arriving or being transmitted at a particular point in a network system. It is the rate of successful payload data delivered over a communication channel (payload transmitted per second). In other words, the throughput is how much payload data actually does travel through the channel. The overhead reduces throughput and increases latency. It can be measured at any layer in the OSI model.

- Overhead

Sending a payload of data (reliably) over a communication network requires sending

more than just the desired payload data. It also involves sending various control data required to achieve the reliable transmission of the desired data. The control information is the overhead.

## — Latency

The time required to deliver a unit of data through the network, measured as the elapsed time between the injection of the first bit at the source to the ejection of the same bit at the destination.

#### — Radix

Refers to the number of ports of a switch.

## — Hop count

The number of links traversed between source and destination.

## — Network Diameter

It is the longest of the shortest path (distance) between any two nodes in a network. In other words, the network diameter is the largest number of nodes which must be traversed in order to travel from one node to another when only direct paths are considered (no detour or loops). It also indicates how long it will take at most to reach any node in the network [12]. Sparser networks will generally have greater diameters. Therefore, the network diameter should be relatively small if the latency is to be minimized.

Table 2.1 Popular Interconnection Networks Diameters [1].

| Network      | Number of Nodes | Network Diameter |

|--------------|-----------------|------------------|

| Linear Array | k               | k-1              |

| Ring         | k               | k/2              |

| 2D mesh      | $k^2$           | 2k-2             |

| 2D torus     | $k^2$           | k                |

| 3D mesh      | $k^3$           | 3k - 3           |

| 3D torus     | $k^3$           | 3k/2             |

| Binary tree  | $2^{l} - 1$     | 2l-2             |

| Hypercube    | $2^l$           | l                |

#### — Indirect Network

The Endpoints connect through a central switch unit. It has intermediate routing-only nodes. There is no direct connection between the Endpoints. Most modern networks are indirect network, i.e. Ethernet, Infiniband.

#### — Direct Network

The Endpoints provide multiple links towards the network side and integrate the switching unit. No centralized switching resource is required. Instead, distributed

switches as part of the network interface are used. Most common topologies are mesh, torus, and hypercube. The main drawback of direct networks is that it increases the number of hops to reach the destination. Latency increases linearly with the number of hops. Hop-based routing is used so that a fully connected network is not required.

— Bit Error Ratio (BER)

Bit Error Ratio of a physical link is given in errors/bit. It refers to the number of bit errors divided by the total number of transferred bits during the studied time interval. The Bit Error Ratio can be converted to Bit Error Rate by multiplying by the link bandwidth in bit/s.

— Bit Error Rate (also BER)

The Bit Error Rate is the number of bit errors of a physical link per unit of time.

#### CHAPTER 3 LITERATURE REVIEW

The multi-FPGA exploration field is getting more popular each year. The High-Performance Computing (HPC) community, for example, has been focusing on FPGA technology for acceleration at small scale i.e. task or algorithms with FPGA development boards, and at big scale i.e. complex system simulation with powerful FPGA-based clusters. Network deployment solutions have been applying FPGA technologies as well. The high-speed serial protocol support from FPGA vendors has offered to the Network Interface Controller (NIC) manufacturer a new exploration field in the growing market of communications. In this chapter, we review the state-of-the-art of high-speed interconnect networks technology on FPGAs. For that purpose, we have categorized the reviewed articles into two main groups based on similar approaches: pure multi-FPGA machines and FPGA-based network accelerators on heterogeneous machines. Later in this chapter, the recent trends in high-speed serial technology supported by FPGAs vendors are discussed. Finally, for our high-performance computing test, we review some implementations of FPGA-based matrix-vector multiplication kernels.

#### 3.1 Pure multi-FPGA machines

In this section, we review some pure multi-FPGA machine implementations, their interconnect technologies, protocols and topologies; putting under the scope metrics as point-to-point latency, communication bandwidth, network diameter, network efficiency and the scalability of the solution.

Cube [13] is a 512-FPGA machine built of eight boards carrying 64 Xilinx's Spartan 3 FPGAs each. The machine is assembled as an 8x8x8 cluster, where each FPGA is considered a Processing Element (PE) of a systolic array interconnection. The communication between PEs is done through parallel lines on the Printed Circuit Board (PCB), which were designed to achieve a theoretical bandwidth of 6.4Gbps. The high cost and complexity due to the parallel routes in such a PCB assembly make this solution unpopular. Systolic arrays offer low latency communication between neighboring PEs but they lack flexibility.

The Reconfigurable Computing Cluster Project at the University of North Carolina at Charlotte [14] has as the main goal to investigate the feasibility of using FPGA platforms in building cost-effective HPC systems that will scale to a PetaFLOP. As part of the project, the *Spirit* cluster was built of 64 Xilinx ML-410 development boards hosting Virtex-4 FPGAs. An Architecture Independent REconfigurable Network (AIREN) addresses the question of

how to efficiently communicate among compute nodes, putting under the scope a high-speed, low latency and low overhead communication channels [15,16]. Figure 3.1 presents AIREN's block diagram for a Data Link hardware core and its switching module implementations. The Link layer core wraps around a Xilinx's Aurora protocol module. It uses two buffers for supporting back pressure flow control and for handling short interruptions in the data flow. Finite state machines monitor the buffers and the Aurora core prior proceeding to data transfers.

Figure 3.1 AIREN block diagram for a single communication channel on the *Spirit* FPGA-based cluster.

The authors also implements a configurable (software addressable configuration registers) full crossbar switch with broadcast capabilities. Here again, the state machines at each input port control data flow by applying back pressure to pause transfers. Xilinx's LocalLink (LL) interface is used as the standard communication interface.

The *Spirit* cluster uses Aurora to interface eight independent Multi-Gigabit Transceiver (MGT) along with a custom Serial Advanced Technology Attachment (SATA) breakout board, providing up to eight connectivity channels per node at a bit rate of 3.2Gbps. Such a high radix (8 connectivity channels) has the advantage of better network topology exploration, hence, smaller network diameter but at the expenses of higher FPGA resources usage due to the on-chip packet switching. A drawback on this approach is the I/O bounds related to the switch implementation, which limits the bandwidth to 3.2Gbps per channel even with channel bonding.

This approach implements a custom packet-based protocol over Aurora for data transfers between nodes. This allowed them to reduce overhead and utilize 95% of available channel bandwidth with 16KB payload packet size. The inter-nodes latency reported for the AIREN network was  $0.8\mu$ s.

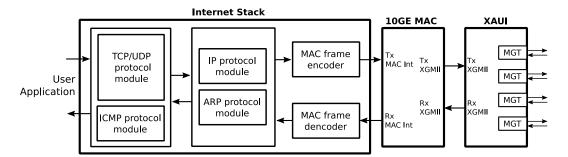

A quad-FPGA cluster implementation on a Berkeley Emulation Engine (BEE) 3 multi-FPGA prototyping platform is presented in [17]. The author's intention is the study of applicationlevel network processing, for what they implement and accelerate all required protocols in high-speed internet connexion. At the Physical and Link level of the Open Systems Interconnection (OSI) reference model, they used Xilinx's Ten Gigabit Attachment Unit Interface (XAUI) and 10 Gigabit Ethernet (10GbE) Media Access Controller (MAC) modules pair. The system only leverages one high-speed serial port used as the system entry of eight available, bounding the platform aggregate bandwidth to only 10Gbps. Internal PCB parallel lines interconnect the four FPGAs in a ring topology. As expected, the high overhead and complexity of internet protocol implementation resulted in around 45% FPGA resources utilization. Even if network interface latency was not reported, it can be is easily deduced from the Physical and Link layer implementations, that it is above  $1\mu$ s. Similar internet protocol acceleration approach have been presented in [18] where a full TCP/IP stack was implemented, reporting  $5.5\mu s$  as the lowest stack latency. Figure 3.2 shows a block diagram example of an internet protocols implementation over 10GbE. The complexity associated with each functional block inevitably leads to latency penalties. In addition, internet protocols implementation does not support direct network, hence, an external switching device is mandatory.

Figure 3.2 Internet protocols stack implementation example over 10 Gigabit Ethernet.

In [19], eight BEE3 platforms are arranged to form a 32-FPGA cluster. This approach proposes a latency optimized hybrid interconnection network composed of high-speed serial inter-BEE3 and parallel PCB intra-BEE3 links. Two protocols are implemented for the serial links: 10 Gigabit Ethernet and Aurora. To extend platform connectivity beyond the eight

CX4 ports, the authors use, for Aurora implementation, CX4-to-SATA breakout cables for breaking apart intrinsic CX4 channel bonding. This allows them to explore different topologies in the cluster. Similar to [17] the 10 Gigabit Ethernet approach instanciates Xilinx's XAUI and 10GbE MAC modules pair. All of the FPGAs in the cluster were connected to an external 10 Gigabit Ethernet switch to achieve full connectivity. The reported channel latency was 840ns and  $1.56\mu s$  for the network diameter.

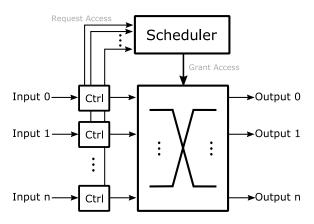

The Aurora communication approach is similar to [16] (depicted in Figure 3.1). In this case, the switching module architecture is based on multiplexers which are controlled by a mix of round robin and priority schedulers. They also used port controllers at each individual switch port for determining the packet's destination path (routing capability), requesting access to the switch and controlling data flow. Figure 3.3 depicts the switch block diagram from [19]. The latency reported associated with the switch implementation was 16 clock cycles running at 250Mhz.

Figure 3.3 Switch module architecture.

Aurora interconnection showed more resources utilization employing many thin channels than fewer, wider channels because of the routing costs. The switch implementation on a high connectivity configuration, adds a significant delay to the packet routing. As a consequence, the system shows almost no improvement in the network diameter (845ns) compared to low connectivity. In terms of Bit Error Ratio (BER), this approach does not implement any error detection/correction mechanism. However, to reduce channel faults, the transceivers are forced to operate at a line rate of 1.95Gbps from the initially set 3.75Gbps. The overall network efficiency peak, the lowest FPGA resources utilization and the channel latency reported are 86%, around 10%, and 541ns respectively.

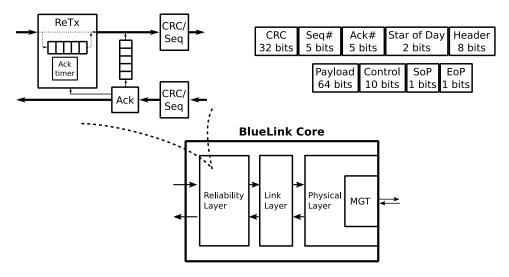

Bluehive is a custom 64-FPGAs machine assembled at the University of Cambridge [10,20,21]. It is composed of 64 DE4 boards from Terasic, hosting Altera's Stratix IV FPGAs. Each

board has twelve SATA3 channels connected to twelve multi-gigabit transceivers in the FPGA. A PCIe-to-SATA breakout board is used to provide independent access to eight transceivers in the PCIe connector. At the FPGA-level, a custom interconnection Intellectual Property (IP) module (BlueLink) wraps up the transceivers to implement a custom communication protocol. Figure 3.4 shows the BlueLink core layers and its protocol fields. Cyclic Redundancy Check (CRC)32 is used for error detection, which is appended to the packet structure. The authors proposed a reliability layer to ensure reliable communications over the link. When an error is detected, the packet is retransmitted by means of a windowbased retransmission buffer and a packet sequence number. The packets are removed from the buffer and the retransmission window is shifted, only after a delivery acknowledgment has been received. A Start of Day field is used for link reinitialization. The Ack field contains an extra bit for back pressure data flow control which tells the sender to stop or start transmission. Reliable links are achieved but at the expenses of less bandwidth efficiency. A major drawback of this approach is that the custom protocol can only send a maximum of 64 bits data payload packed in 128 bits. This represents 50% overhead which combined with the 8b/10b transceiver encoding, reduces available bandwidth to around 40%. The reported effective data rate and latency, for a single FPGA-to-FPGA link at a transceiver operating rate of 3.125Gbps, are 1.2Gbps and 400ns.

Figure 3.4 BlueLink communication approach.

#### 3.2 FPGA-based network accelerators and heterogeneous machines

Other research works have pointed to heterogeneous computing cluster rather than pure FPGA cluster. Many of these solutions integrate FPGA-based expansion boards to CPU

systems for accelerating communication of nodes. The PCIe connector is generally used to achieve tight integration between the NIC on the boards and the hosting CPUs. This involves complex protocol transformation resulting in a higher NIC footprint and latency than pure cluster solutions. Since the use of the entire FPGA for a NIC implementation is out of scope, we have focused only on the FPGA-to-FPGA communication part for the reviewed literature.

CusComNet in [22] is an FPGA-based interconnection network implementation for heterogeneous computing clusters. Sixteen nodes composed of a CPU system hosting a Virtex 5 LX330T FPGA board each, are interconnected in a 4x4 2D torus topology. Similar to [23], each node has four Infiniband 1x cables connected to four multi-gigabit transceivers, allowing a maximum theoretical bandwidth of 1.6Gbps per link after 8b/10b encoding. At the low communication level, CusComNet wraps the four transceivers individually, creating four independent full duplex channels. However, there are no signs of any channel bonding support for increasing channels aggregate bandwidth. A customizable communication protocol developed by the authors permits them to set, in design time, a variety of parameters for the protocol, such as the number of bits of the source and destination IDs and the payload size to be used. This results in a better utilization of the available bandwidth and the FPGA resources. An up to 97% efficiency per link of 1.6Gbps is reported for 64 bytes payload. Despite that, we estimate up to 91\% effective data rate approximately, for the same payload size due to the CRC32 error detection mechanism appended to the protocol which it seems like it wasn't considered. Packets routing is achieved by means of a simple round robin scheduler module, a route module that contains routing information base on the network topology and a cross-bar switch. CusComNet implementation latency (FPGA-to-FPGA) reported was 830ns for 0 bytes data payload packets.

Some research projects like EXTOLL [24–26], APEnet+ [27] and NetFPGA [28] have addressed and commercialized high-speed and low latency FPGA-based communication solutions, as high-performance boards for clusters. While these solutions have good network performance, they intended to use almost the entire FPGA fabric letting little room left for user applications. EXTOLL project, for instance, introduces an IP core for low latency message exchange in an interconnection network. The architecture is divided into three main layers: at the top layer is the host interface implementing protocol for the hosting machine (PCIe or HyperTransport); the middle layer implements translations and interfaces between the top and the bottom layers; and at the bottom layer a cross-bar switch with a round robin arbiter connects the network interface to six FPGA transceivers running at 6.24Gbps. The authors implement a credit-based flow control mechanism for avoiding reception buffer overflow, a CRC error detection, and a packet retransmission mechanism. A prototype on a Xilinx's Virtex 4 FX100 FPGA achieved a half-round-trip latency of  $1.16\mu s$  for 8 bytes

payload messages. Reported device utilization shows the high complexity of this approach where 85% of the FPGA resources were utilized even after floorplanning.

Similar to EXTOLL, APEnet+ ([27]) proposed a three-layer custom architecture for an FPGA-based NIC card. A central switch at the middle layer interconnects and controls flow between a PCIe interface for the hosting PC and the Multi-Gigabit Transceivers (MGT) at the Physical layer. Virtual channel technique is used to improve accesses to the physical links and buffering. Twenty-four transceivers on an Altera Stratix IV FPGA are used in a four-lane configuration to provide six QSFP+ links with a maximum theoretical bandwidth of 34Gbps per link. Once again, maintaining the maximum transceivers bit rate is difficult because of the errors on the links, so the authors reduced the rate to 28Gbps. The reported device utilization was 42% but no details about protocol or latency were presented.

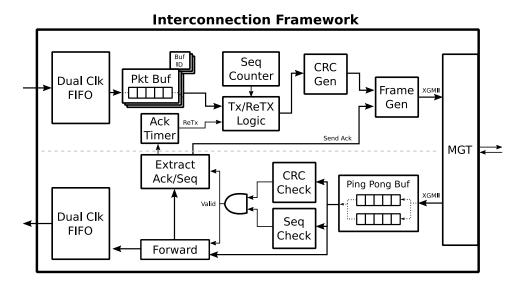

In an effort to abstract and simplify FPGA cluster designs, [6] presents a framework for multi-FPGA interconnection using multi-gigabit transceivers. The authors proposed a FIFO-like interface to the NIC that receives a continuous stream of data and subdivide it into packets for transmission. The framework uses CRC for error detection and an acknowledgment mechanism to signal each received packet integrity to the sender. The Acknowledgment mechanism is well-known for limiting exploitation of the available bandwidth even with piggybacking technique. A better solution for a framework would be the negative acknowledgment for signaling thus the occurrence of an error. Packet sequence identifier is also proposed to detect missing and not in order packets. A retransmission buffer at the sender side provides error correction features. Figure 3.4 depicts the interconnection framework block diagram usign Multi-Gigabit Transceivers (MGTs).

Figure 3.5 Interconnection framework block diagram for multi-FPGA cluster [6].

The packet structure defined for the interconnection framework has 256 bits protocol overhead and fixed (defined in design time) payload length. Packets are assembled in 64-bits chunks to match XGMII interface at the transceivers user side. The framework evaluation was done on two Xilinx ML605 development boards carrying two Virtex-6 LX240T FPGAs. The device utilization reported was around 6%. No other details of implementation can be presented for this approach because of the lack of clarity in the report. The framework refers to neither packet routing nor transceivers grouping for channel bonding support.

NetFPGA [28] is an open source FPGA-based platform designed for research and teaching of high-speed interconnection networks. NetFPGA SUME is PCI Express board with I/O capabilities for 10 and 100 Gbps operation. At its core, a Xilinx's Virtex-7 FPGA empowers the platform and provides one of the last generation transceivers in the market: the 7 Series GTH (13.1 Gbps). To achieve 100Gbps aggregate bandwidth and increase the board connectivity to the network, the platform supports expansion through an FPGA Mezzanine Card (FMC). A total of 14 high-speed serial links among SPF+ and FMC interfaces are available per board. As part of the open source project, various reference projects can be accessible for implementation on the board. All of the reviewed network reference projects use Xilinx's XAUI - 10GE MAC IPs at the physical and link layers. As we have seen before Ethernet's full stack performance is not too attractive for FPGA-to-FPGA communication.

Aurora is a link-layer protocol of the OSI model [29]. In [30] the authors present a custom network and transport layer implementation over Aurora, aiming high-layer functionalities for FPGA interconnection networks with low latency and lightweight characteristics. The network layer proposed implements a router with fixed packet routing path to achieve loss-less and in order features. Endpoint modules (virtual channel) are connected to the router to allow information exchange with them-self throughout the network. The transport layer is implemented at each individual endpoint, to support individual credit-based end-to-end flow control. For prototyping, the authors used twenty Xilinx Virtex-7 VC707 FPGA development boards on an Intel Xeon-based heterogeneous machine. An FMC pinned out eight GTX transceivers configured as two-per-lane to provide four 20Gbps serial links per node. The reported Aurora per-hop latency was  $0.48\mu$ s deduced from 75 clock cycles at 156.25MHz. Packet and flow control overhead yielded 85% channel efficiency, which means 17Gbps effective throughput. The device utilization for entire network stack using two Endpoint modules was less than 4%.

## 3.3 Recent trends in FPGA interconnect technology

In the race for high-performance serial I/O, FPGA vendors are reaching impressive achievement in the transceivers technology field. In 2010 Xilinx announced its 7 Series FPGAs family introducing a new high-k metal gate (HKMG) variant of 28nm process technology [31]. The scaling process from the previous 45nm family resulted in an increase in cell density and system performance whilst reducing power consumption. High-speed serial connectivity also benefited great improvement. The 7 series introduced up to 96 built-in multi-gigabit transceivers blocks capable of operating at 13.1Gbps maximum rate, and 16 others transceivers blocks operating at up to 28.05Gbps. Devices I/O bandwidth raised to 2.8Tbps.

In 2013 Xilinx introduced the UltraScale series manufactured in a 20nm planar process and the UltraScale+ families based on 16nm FinFET+ 3D transistors technology. Once again transceivers were boosted, now to support 100G Ethernet, 150G Interlaken, and the next to come PCIe Gen4 protocols [32]. Transceivers density went up to 128 per FPGA at a maximum operating speed of 32.75Gbps for 8384Gbs total I/O bandwidth. Table 3.1 summarizes the latest trends in transceivers technology from Xilinx's FPGAs.

| Family     | Type           | Max                  | Max          | I/O Peak             |

|------------|----------------|----------------------|--------------|----------------------|

|            |                | Performance          | Transceivers | Bandwidth            |

| Virtex US+ | GTY            | 32.75 Gbps           | 128          | 8384 Gbps            |

| Kintex US+ | GTH/GTY        | 16.3/32.75 Gbps      | 44/32        | $3530 \mathrm{Gbps}$ |

| Zynq US+   | PS-GTR/GTH/GTY | 6.0/16.3/32.75Gbps   | 4/44/28      | 3316 Gbps            |

| Virtex US  | GTH/GTY        | 16.3/30.5 Gbps       | 60/60        | 5616 Gbps            |

| Kintex US  | GTH            | $16.3 \mathrm{Gbps}$ | 64           | 2,086 Gbps           |

Table 3.1 UltraScale and ultraScale+ architecture transceiver portfolio [2]

Protocols scalability has been related to transceivers performance and flexibilities. Nowadays FPGA vendors offer massive bandwidth standard IP solutions for a high range of networking applications. Table 3.2 summarizes some of the serial IP protocols supported by Xilinx's latest FPGAs.

Xilinx's 7 series architecture introduced integrated hard IP for PCIe solutions. The UltraScale family has extended this hardened approach to 100G Ethernet and 150G Interlaken protocols. The number of hard IPs available in each FPGA varies from one family to the other, but it does not exceed one tenth. This still represents a great improvement on the FPGAs interconnection technology especially in terms of the latency because now the high complexity and overhead of these standard protocols profit from specialized fabric.

| Protocol      | LogiCORE IP solution              | Lane Rate(Gbps) | Configuration    |

|---------------|-----------------------------------|-----------------|------------------|

| 10G Ethernet  | XAUI/RXAUI/                       | 3.125/6.25/     | 4 Lanes/2 Lanes/ |

|               | 10G Ethernet PCS-PMA              | 10.3125         | 1 Lane           |

| 40G Ethernet  | $\mathrm{XLAUI}^a/$               | 10.3125         | 4 Lanes          |

|               | 40G Ethernet PCS-PMA <sup>a</sup> |                 |                  |

| 100G Ethernet | CAUI-10 $^a/100$ G Ethernet       | 10.3125/        | 10 Lanes/        |

|               | $PCS-PMA^a/CAUI-4^b$              | 25.78125        | 4 Lanes          |

| Interlaken    | Interlaken 150G                   | 3.125 - 12.5 /  | 1-12  Lanes/     |

|               |                                   | 12.5 - 25.78125 | 1-6 Lanes        |

| Aurora        | Aurora 8b/10b                     | up to $6.6/$    | 1-16  Lanes/     |

|               | Aurora $64B/66B$                  | up to $25.7813$ | 1-16 Lane        |

| PCI Express   | Gen2/Gen3                         | 5/8             | x1/x2/x4/x8      |

Table 3.2 Xilinx's latest trends in high-speed serial solution [3].

In the first trimester of 2016, Xilinx announced the first 56Gbps transceiver using the 4-level Pulse Amplitude Modulation (PAM4) transmission scheme, setting thus the foundations for the 400GE standardization to come. Intel (Altera) FPGA materialized 56Gbps PAM4 transceivers with the release of the Stratix 10 family [33]. Stratix 10 FPGAs have been built on the Intel 14nm Tri-Gate process offering a powerful platform for networking applications. Hard IP solutions for PCIe and 100G Ethernet are supported too in the Stratix 10, as well as a broad range of soft standards IP solutions for high-speed serial protocols.

Both main FPGA vendors offer high integration and flexibility in their latest devices. FPGA designers have now a broad range of possibilities for FPGA interconnection to choose from, i.e. soft or integrated hard IPs and custom or standard protocols. The hard IP solution for some standard protocols available in the newest FPGA architectures offers high potentialities in the communication field, by managing protocol complexity with specialized fabric, and reducing communication footprint. The high cost of this technology and the no yet free access to products information makes performance studies still difficult for the research community.

#### 3.4 Matrix-vector multiplication for scientific applications

The Basic Linear Algebra Subprograms (BLAS) [34] describes low-level routines that provide standard building blocks for solving algebra problems and equations. It is widely used as the benchmarks' core in supercomputers. BLAS has three different categories according to the complexity of the algorithm. BLAS level 1 comprises vector-level math, i.e. dot prod-

a. 40G/100G Ethernet LogiCORE IP.

b. UltraScale Devices Integrated Block for 100G Ethernet LogiCORE IP.

uct. Level 2 and level 3 increases complexity to matrix-vector and matrix-matrix operations respectively. The BLAS libraries serve as basic blocks for many numerical linear algebra applications. Any BLAS level implementation benefits from the wide variety of published implementations to compare with, giving a close idea of the computing power performance of any targeted machine. Moreover, a BLAS implementation performance may be extrapolated to higher level scientific and engineering application performance estimations.

Matrix-vector multiplication (BLAS level 2) is an ideal low-level application for FPGA-based computing platforms. Because of its highly parallel nature, the computations may be done in parallel by distributing multipliers and adders all across the FPGA machine. Many authors have addressed matrix-vector multiplication seeking acceleration of scientific applications. Sparse matrices are more popular for architecture researches than dense matrices since the matrix traversal, the indirect memory accesses and the matrix compression methods are more challenging. However, most of the sparse matrix-vector multiplication implementations on FPGAs include a dense matrix test that generally up bounds the performance estimation. Thus, our literature review focuses on matrix-vector multiplication implementations on FPGAs with dense matrices performance results.

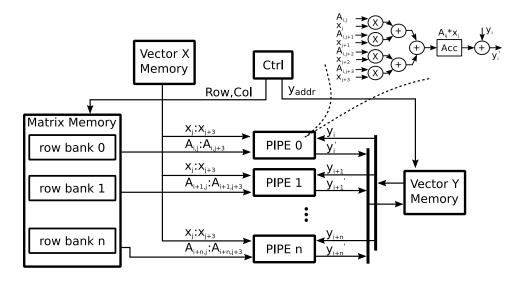

In [7,35], a Basic Linear Algebra Subroutines (BLAS) FPGA implementation using double-precision floating point is presented. This approach is a row-major Gaxpy design that uses various PIPE operators for parallel computing dot-product of a row of the matrix A with the vector X. PIPE operator performs several multiplications in parallel and accumulates them throughout an adder tree structure and a dual stage accumulator. The operator is stall-free, being capable of accepting new data sets every clock cycle. Figure 3.6 shows the authors approach for matrix-vector multiplication. It includes multiple PIPEs in parallel, each operating on a different row of the matrix. The vector X output data is broadcasted to all the operators. The partial sums has been reduced in the accumulator module, the corresponding Y vector element is updated. The arithmetic operators are double-precision floating point Xilinx IP cores. The arrangement in parallel of PIPE operators allows interrow and intra-row parallelism. The design is implemented on a Virtex-5 lx155t and a Virtex-6 lx240t FPGAs with 16 and 32 processing element respectively. The authors reported 3.1GFLOPS peak and 0.92GFLOPS sustained for the Virtex-5, as well as 6.4GFLOPS peak and 1.14GFLOPS sustained for the Virtex-6 platforms.

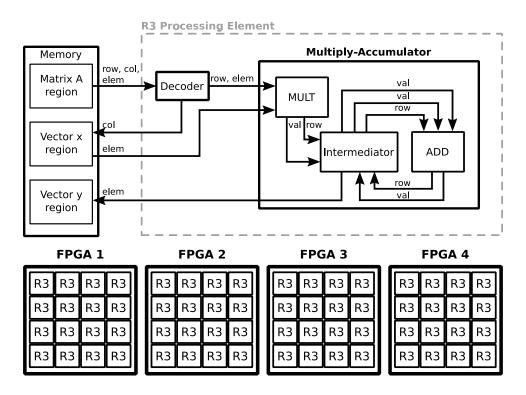

Similar to the above no-stall multiply-accumulator implementation, in [8,36] the authors propose the R3 processing element architecture with an intermediator module between a multiplier and an adder core to compose a single processing element. To address a stall-free operator despite the incoming data flow rate, their approach works on multiple intermediate

Figure 3.6 Row-major BLAS gaxpy architecture [7].

Y vector values and does the additions out of order. The Intermediator module allows the matrix to be traversed in a loosely row-major traversal in a matrix block set of 16 rows, by storing 32 intermediate Y vector values. It takes in two values, one from the multiplier's result and one from the adder's result and outputs a pair of values to be added. Internally is has a dual-port Block RAM module that stores intermediate values until an element in the same row appears. Figure 3.7 depicts the a single matrix-vector processing element and its distribution on a multi-FPGA platform.

The authors managed to fit 64 processing elements in a Convey HC-1 platform with four Virtex-5 lx330 FPGAs and 40GB/s of sustainable global memory bandwidth. They achieved 13.6GFLOPS peak and 7.6GFLOPS average for a dense 2000 × 2000 matrix. The more recent work of the same authors shows an implementation on a Convey HC-2ex platform hosting 64 processing elements on four Virtex-6 lx760 FPGAs with 19GB/s memory bandwidth per device. This new improved system reach up to 16.3GFLOPS peak processing power and 11.9GFLOPS average. Both distributed solutions don't address node communication.

Authors from [37] present a single-precision floating point processing elements architecture for matrix-vector multiplication based on a dual-port RAM, a multiplier and an adder. The targeting device is a Virtex-5 sx95t FPGA with 35.74GB/s of memory bandwidth hosted by a Reconfigurable Open Architecture Computing Hardware (ROACH) platform. For a  $2000 \times 2000$  dense matrix and 64 processing elements, this approach reaches a computational performance of 19.16GFLOPS peak and 17.64GFLOPS average.

Figure 3.7 Parallel matrix-vector multiplication with R3 processing elements [8].

#### 3.5 Conclusions

Computational units and interconnect network are the two typical main components in today's High-Performance Computing (HPC) systems. In order to increase performance by parallelization, large parallel systems with many nodes are built. Nonetheless, HPC is compromised, among others, by the interconnect network. The interconnect network should meet requirements like low latency, high-bandwidth, fault tolerance, and scalability to allow high-performance communication between the computational units.

From the reviewed articles, it is possible to observe that the utilization of complex features on high-speed serial protocols yields reliable communication channels. However, there is latency penalty and resource over-utilization cost to pay. We have seen that often the authors relied on protocols, originally designed for different applications, which results in an unnecessary overhead and a reduced effective throughput.

Ethernet is the most popular solution since its broad utilization on internet networks. The full Ethernet stack implementation has demonstrated this solution is not effective for time-critical applications. [10] has shown for FPGA-to-FPGA communication, custom solutions are preferable over standards off-the-shelf approaches. Nevertheless, a custom approach does not preclude standard IP cores wherever they are useful, i.e they may be components in a

#### communication stack.

In terms of FPGA connectivity for a fixed physical bandwidth, we have seen that a high fan-out leads to better direct-network topologies (2D mesh, torus, etc.) and reduced network diameter. But as a consequence, a high-radix router implementation is generally necessary thus causing high resource consumption and latency. A trade-off between the fan-out and the channel bonding must be evaluated in order to achieve the best performance.

Most popular error detection mechanisms found in the literature are Checksum, CRC, and parity. Most popular error correction mechanism is the Automatic Repeat Request (ARQ) with its different variants like stop-and-wait ARQ, Go-Back-N, and Selective Repeat ARQ [6, 20–22, 25]. Data acknowledgment (Ack) or negative acknowledgment (NaK) is very used too. It is generally combined with a sliding window technique for the retransmission buffer implementation and/or an acknowledgment timer for timeout signaling when packet loss occurs. Flow control mechanism is used to allocate the different resources in the network such as the buffers and the channels as the data progresses from the source to its destination. Most popular implementations of flow control regarding FPGA interconnection networks utilizes the credit-based or the back pressure (ON/OFF) techniques [10, 14, 26].

For concluding this chapter, the consulted researches are summarized hereafter. Table 3.3 summarizes the main results and features of the reviewed implementations for high-performance interconnections on FPGAs. We should highlight that all of the custom protocols showed better end-to-end latency results than standard implementations.

Table 3.3 Summary on high-performance communication implementations using FPGAs.

| Implementation | Fanout       | Bandwidth   | Protocol           | Latency           | Efficiency       | Resources | Platform   |

|----------------|--------------|-------------|--------------------|-------------------|------------------|-----------|------------|

|                | (Channels)   | per Channel |                    |                   | peak             |           |            |

| [15]           | 8 one-lane   | 3.2 Gbps    | Custom over Aurora | 800ns             | 95% <sup>a</sup> |           | Virtex-4   |

| [17]           | 1 four-lanes | 10 Gbps     | Internet stack     | $>1\mu s$         |                  | 45%       | Virtex-5   |

|                |              |             | 10GE (XAUI+MAC)    |                   |                  |           |            |

| [19]           | 2 four-lanes | 10 Gbps     | 10GE               | $840 \mathrm{ns}$ |                  | 18%       | Virtex-5   |

| [19]           | 2 four-lanes | 6.24 Gbps   | Aurora             | $541 \mathrm{ns}$ | 86%              | 10%       | Virtex-5   |