# UNIVERSITÉ DE MONTRÉAL

# LOW-IMPACT SYSTEM PERFORMANCE ANALYSIS USING HARDWARE ASSISTED TRACING TECHNIQUES

# SUCHAKRAPANI DATT SHARMA DÉPARTEMENT DE GÉNIE INFORMATIQUE ET GÉNIE LOGICIEL ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION DU DIPLÔME DE PHILOSOPHIÆ DOCTOR (GÉNIE INFORMATIQUE) FÉVRIER 2017

# UNIVERSITÉ DE MONTRÉAL

# ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Cette thèse intitulée :

# LOW-IMPACT SYSTEM PERFORMANCE ANALYSIS USING HARDWARE ASSISTED TRACING TECHNIQUES

présentée par :  $\underline{{\sf SHARMA}}$  Suchakrapani Datt

en vue de l'obtention du diplôme de : <u>Philosophiæ Doctor</u> a été dûment acceptée par le jury d'examen constitué de :

- M. QUINTERO Alejandro, Doctorat, président

- M. DAGENAIS Michel, Ph. D., membre et directeur de recherche

- M. BOYER François-Raymond, Ph. D., membre

- M. GAGNON Étienne M., Ph. D., membre externe

## **DEDICATION**

"Somewhere, something incredible is waiting to be known"

- Carl Sagan

Dedicated to the unknown cosmos.

#### ACKNOWLEDGEMENTS

I would first like to express my sincere gratitude to my research adviser and supervisor, Prof. Michel Dagenais, for giving me this opportunity to work under his guidance and helping me grow intellectually and personally. His interest in my work and passion in the field of research helped me steer through the largest of hurdles.

I would also like to thank Francis Giraldeau who has been a professional companion and a dear friend for guiding me through the ups and downs of the PhD life. He welcomed me to this beautiful land of Québec and advised me from time to time with his vast experience and knowledge of computers. He has been a personal inspiration to me. I am also grateful to Genevieve Bastien for her support during my research. Her advice has been a key factor in development of technologies resulting from this work. A thanks is also due to Tanushri Chakravorty for being around for yet another graduation journey. Her moral support has been invaluable.

I would like to thank Mathieu Desnoyers and Julien Desfossez for their work on tracers in Linux and giving me an opportunity to discuss Linux internals with them. I am also thankful to EfficiOS, Ericsson, the Natural Sciences and Engineering Research Council of Canada (NSERC) and prompt Québec for providing funds to carry out this research.

I express my gratitude to all past and present *inhabitants* of the DORSAL Lab with whom I periodically engaged in intellectual exchanges – in particular, Simon Marchi, François Rajotte, Raphaël Beamonte, Hani Nemati, Mohamad Gebai, Houssem Daoud, Naser-Ezzati Jivan, Matthew Khouzam and Thomas Bertauld who have helped diversify my knowledge. Many thanks to *Dream Theater*, *Indian Ocean* and *Indus Creed* as well, for their inspiring music throughout these years.

I would also like to thank my uncle Ganesh Dutt Sharma, for sharing with me his love for physics and my father for allowing excursions to his research lab. They have been instrumental in imbibing a scientific conscience and the culture of *reason* in me.

Finally and most importantly, I would like to thank my mother for making me who I am as a human being. There are no words in any language that can express her importance in my research.

## RÉSUMÉ

Les applications modernes sont difficiles à diagnostiquer avec les outils de débogage et de profilage traditionnels. Dans les système de production, la première priorité est de minimiser la perturbation sur l'application cible. Les outils de traçage sont très appropriés pour l'étude des performances de tels systèmes car les événements sont enregistrés et l'analyse se fait a posteriori. Une des principales exigences des systèmes de traçage est le faible surcoût. L'activation d'un nombre réduit d'événements aide à respecter cette exigence, mais au prix de la diminution de la granularité de la trace.

Dans cette thèse, nous présentons notre travail de recherche qui traite du problème de la granularité limitée des traces en maintenant un faible surcoût sur les applications cibles. Nous présentons de nouvelles techniques et algorithmes qui abordent le problème en se basant d'abord sur une approche de filtrage logiciel et de traçage coopératif, puis en explorant des mécanismes plus avancés de traçage matériel. Nous avons proposé une approche efficace de traçage conditionnel dans l'espace noyau et utilisateur qui se base sur des mécanismes de filtrages compilés en code natif. Afin d'atteindre l'objectif d'avoir une trace détaillée du système, nous expliquons que les processeurs modernes contiennent des blocs de traçage matériel qui n'ont pas encore été entièrement exploités dans le domaine du traçage. Nous caractérisons leur performance et nous analysons les paquets de traces, leur relation avec l'exécution du logiciel, et les possibilités de les utiliser pour une trace détaillée. Nous proposons des techniques à faible surcoût, assistées par le matériel, rendant possible une analyse détaillée permettant la détection des latences d'interruption et des appels systèmes. Nous présentons aussi une nouvelle technique qui se base sur les paquets de trace à bas niveau du processeur pour analyser efficacement les processus et les ressources utilisées dans une machine virtuelle. De plus, nous avons identifié et solutionné des problèmes reliés au traçage matériel en utilisant l'assistance logicielle du système d'exploitation, ouvrant ainsi la voie à des recherches plus approfondies sur les approches coopératives de traçage matériel-logiciel. Comme nos techniques sont axées sur les exigences du traçage à haute vitesse dans les systèmes embarqués et de production traitant des transactions à haute fréquence, nous avons constaté que nos progrès dans le domaine du traçage matériel-logiciel se sont avérés très utiles pour détecter la contention des ressources et la latence dans les systèmes.

#### **ABSTRACT**

Modern applications are becoming hard to diagnose using traditional debugging and profiling tools. For production systems the first priority is to have minimal disturbance on the target application. To analyze performance of such systems, tracing tools are imperative where events can be logged and analyzed post-execution. One of the key requirements for tracing solutions however, is low overhead. A generic solution can be to select only a few events to trace, but at the cost of trace granularity. In this thesis, we present our research work that deals with the problem of lack of high granularity in traces while maintaining a low-overhead on target applications. We present our new techniques and algorithms that approach the problem initially from a software filtering and co-operative tracing approach, and then explore more advanced hardware tracing mechanisms that can be used. We have proposed an efficient kernel and userspace conditional tracing approach, with an enhanced native compiled filtering mechanism. Continuing towards our goal to have a detailed trace of a system, we further discuss how modern processors contain new hardware tracing blocks that have not yet been fully explored and exploited in the tracing domain. We characterize their performance and analyze the trace packets, their relation with software executions and opportunities to utilize them for a detailed trace. We therefore propose low-overhead hardware assisted techniques that allow a fine grained instruction based interrupt and system call latency detection mechanism. We also present a new algorithm that shows how such lowlevel trace packets coming directly from the processor, can be effectively utilized to analyze even the processes or resources consumed inside a VM. We have also identified and improved upon issues related to hardware tracing itself using software assistance from operating systems thus laying out ground for further research in hardware-software co-operative tracing approaches. As our techniques are focused towards requirements of high speed tracing in embedded or production systems, catering high frequency transactions, we have found that our advancements in the hardware-software domain have proved to be invaluable in detecting resource contention and latency in systems.

# TABLE OF CONTENTS

| DEDIC        | ATION          | ·                                | iii    |

|--------------|----------------|----------------------------------|--------|

| ACKNO        | )WLEI          | DGEMENTS                         | iv     |

| RÉSUM        | ΙÉ             |                                  | V      |

| ABSTR        | ACT            |                                  | vi     |

| TABLE        | OF C           | ONTENTS                          | vii    |

| LIST O       | F TAE          | BLES                             | xi     |

| LIST O       | F FIG          | URES                             | xii    |

| LIST O       | F ABE          | BREVIATIONS                      | XV     |

| CHAPT<br>1.1 |                | INTRODUCTION                     | 1<br>1 |

| 1.1          | 1.1.1          | Instrumentation                  | 1      |

|              | 1.1.2<br>1.1.3 | Tracing                          | 3<br>4 |

| 1.2          |                | em and Scope                     | 5      |

| 1.3          | Resea          | rch Objectives                   | 6      |

| 1.4          | Contr          | ibutions                         | 7      |

| 1.5          | Outlin         | ne                               | 7      |

| СНАРТ        | -              | LITERATURE REVIEW                | 9      |

| 2.1          | Tracin         | ng and Instrumentation           | 9      |

|              | 2.1.1          | CASE STUDY : DyTrace             | 9      |

|              | 2.1.2          | Kprobes                          | 13     |

|              | 2.1.3          | TRACE_EVENT                      | 14     |

|              | 2.1.4          | Tracing Infrastructure Hierarchy | 14     |

|              | 2.1.5          | SystemTap                        | 16     |

|              | 2.1.6          | LTTng                            | 18     |

| 2.2          | Proce          | ss Virtual Machines              | 20     |

|              | 2.2.1          | Design Strategies                | 20     |

|       | 2.2.2   | Interpreter Dispatch Mechanisms                    |

|-------|---------|----------------------------------------------------|

|       | 2.2.3   | DTrace                                             |

|       | 2.2.4   | Runtime Code Compilation                           |

|       | 2.2.5   | Optimizing Filters                                 |

| 2.3   | Progra  | am Flow Tracing                                    |

|       | 2.3.1   | Software PFT Techniques                            |

|       | 2.3.2   | Hardware PFT Techniques                            |

| 2.4   | Hardw   | vare Trace Reconstruction                          |

| 2.5   | Summ    | ary of Literature Review                           |

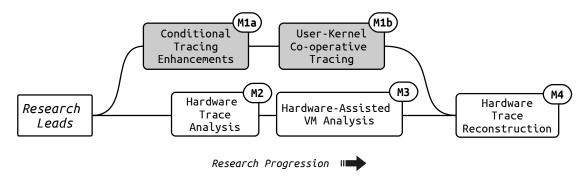

| СНАРТ | TER 3   | RESEARCH METHODOLOGY                               |

| 3.1   | Resear  | rch Progression                                    |

|       | 3.1.1   | Research Leads                                     |

|       | 3.1.2   | Problem Definition                                 |

|       | 3.1.3   | Defining Scope                                     |

|       | 3.1.4   | Research Body                                      |

|       | 3.1.5   | Experimentation                                    |

| СНАРТ | TER 4   | ARTICLE 1 : ENHANCED USERSPACE AND IN-KERNEL TRACE |

| FIL   | ΓERIN   | G FOR PRODUCTION SYSTEMS                           |

| 4.1   | Abstra  | act                                                |

| 4.2   |         | uction                                             |

| 4.3   |         |                                                    |

| 4.4   | Backg   | round                                              |

|       | 4.4.1   | Tracing                                            |

|       | 4.4.2   | Filters                                            |

|       | 4.4.3   | Trace Filtering                                    |

| 4.5   | Filtere | ed Tracing Architecture                            |

|       | 4.5.1   | Base Framework                                     |

| 4.6   | Impro   | ved Tracing Infrastructure                         |

|       | 4.6.1   | Dynamic Tracing                                    |

|       | 4.6.2   | Data Sharing                                       |

|       | 4.6.3   | KeBPF and UeBPF Interactions                       |

| 4.7   | Exper   | imentation and Results                             |

|       | 4.7.1   | Test Environment                                   |

|       | 4.7.2   | Filter Experiment Set                              |

|       | 4.7.3   | Shared Memory Experiment Set                       |

| СНАРТ | ΓER 5 ARTICLE 2 : HARDWARE-ASSISTED INSTRUCTION PROFILING |    |

|-------|-----------------------------------------------------------|----|

| ANI   | D LATENCY DETECTION                                       | 71 |

| 5.1   | Abstract                                                  | 71 |

| 5.2   | Introduction                                              | 72 |

| 5.3   | Background                                                | 75 |

|       | 5.3.1 Program Flow Tracing                                | 75 |

|       | 5.3.2 Hardware Tracing                                    | 77 |

| 5.4   | Trace Methodology                                         | 79 |

|       | 5.4.1 Intel PT                                            | 80 |

|       | 5.4.2 Architecture                                        | 81 |

|       | 5.4.3 Delta Profiling                                     | 82 |

|       | 5.4.4 Syscall Latency Profiling                           | 84 |

|       | 5.4.5 Software Tracer Impact                              | 86 |

| 5.5   | Experimentation and Results                               | 87 |

|       | 5.5.1 Test Setup                                          | 87 |

|       |                                                           | 87 |

|       | 5.5.3 Delta Profiling Instructions                        | 93 |

| 5.6   | Conclusion and Future Work                                | 93 |

| 5.7   | Acknowledgement                                           | 95 |

| CHAPT | ΓER 6 ARTICLE 3 : LOW OVERHEAD HARDWARE-ASSISTED VIRTUAL  |    |

| MA    | CHINE ANALYSIS AND PROFILING                              | 96 |

| 6.1   | Introduction                                              | 97 |

| 6.2   | Related Work                                              | 98 |

| 6.3   | Hardware Tracing VMs                                      | 99 |

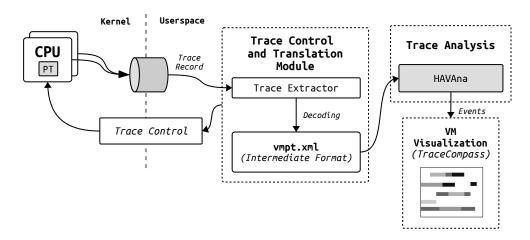

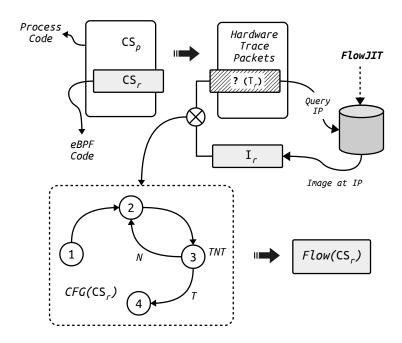

|       | 6.3.1 System Architecture                                 | 01 |

|       | 6.3.2 HAVAna Algorithm                                    | 01 |

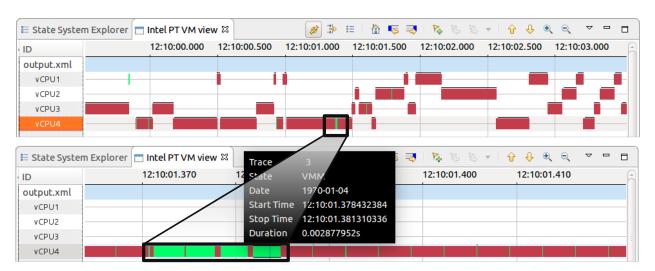

|       | 6.3.3 Trace Visualization                                 | 02 |

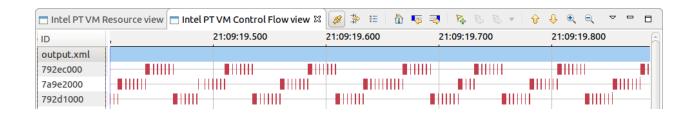

| 6.4   | Usecases - Resource Contention                            | 04 |

| 6.5   | Overhead Analysis Experiments                             | 05 |

| 6.6   | Conclusion                                                | 06 |

| СНАРТ | ΓER 7 ARTICLE 4 : HARDWARE TRACE RECONSTRUCTION OF RUN-   |    |

| TIM   | ME COMPILED CODE                                          | 07 |

| 7.1   | Introduction                                              | 07 |

| 7.2   | Literature Review                    | 109 |

|-------|--------------------------------------|-----|

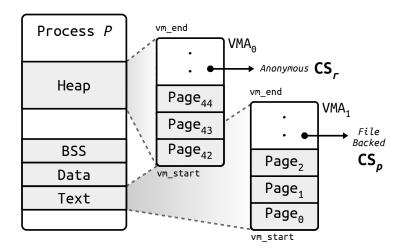

| 7.3   | Background and Motivation            | 111 |

| 7.4   | Methodology                          | 114 |

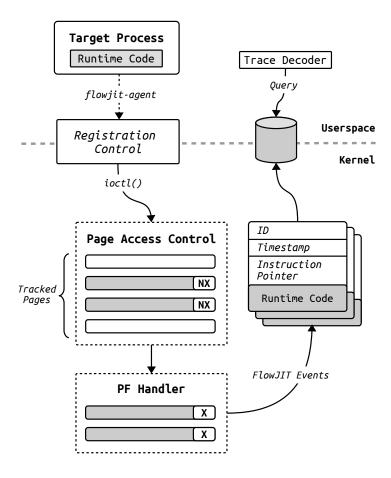

|       | 7.4.1 FlowJIT Architecure            | 114 |

| 7.5   | Illustrative Use-Cases               | 118 |

|       | 7.5.1 JIT Compiled Code              | 118 |

|       | 7.5.2 Static Key Instrumentation     | 120 |

| 7.6   | Experimentation and Results          | 122 |

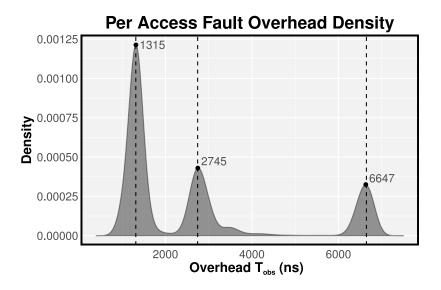

|       | 7.6.1 Access Fault Overhead          | 124 |

| 7.7   | Conclusion                           | 126 |

| CHAPT | TER 8 GENERAL DISCUSSION             | 127 |

| 8.1   | Revisiting Milestones                | 127 |

| 8.2   | Research Impact                      | 128 |

| 8.3   | Limitations                          | 129 |

| СНАРТ | TER 9 CONCLUSION AND RECOMMENDATIONS | 130 |

| 9.1   | Concluding Remarks                   | 130 |

| 9.2   | Recommendations for Future Research  | 130 |

| REFER | RENCES                               | 132 |

# LIST OF TABLES

| Table 4.1 | Register mapping for eBPF-x86                                       | 55  |

|-----------|---------------------------------------------------------------------|-----|

| Table 4.2 | Time taken for 1000 reads of an integer array-map                   | 68  |

| Table 5.1 | Execution overhead and trace bandwidth of Intel PT under various    |     |

|           | workloads. The TailFact and Omega tests define the two upper limits | 88  |

| Table 5.2 | Comparison of Intel PT and Ftrace overheads for synthetic loads     | 93  |

| Table 6.1 | PT based VM trace and LTTng trace overhead                          | 105 |

# LIST OF FIGURES

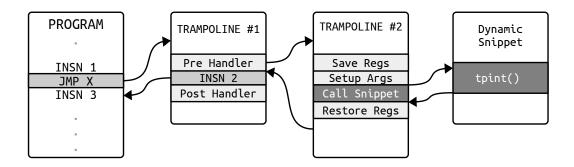

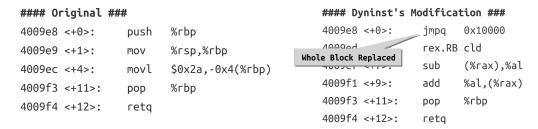

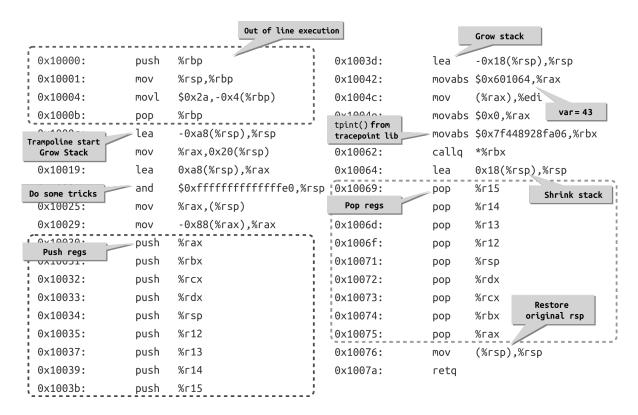

| Figure 2.1  | Trampoline approach used by Dyninst                                           | 11 |

|-------------|-------------------------------------------------------------------------------|----|

| Figure 2.2  | Original code and jumps inserted for trampolines                              | 12 |

| Figure 2.3  | Inside a Dyninst trampoline                                                   | 13 |

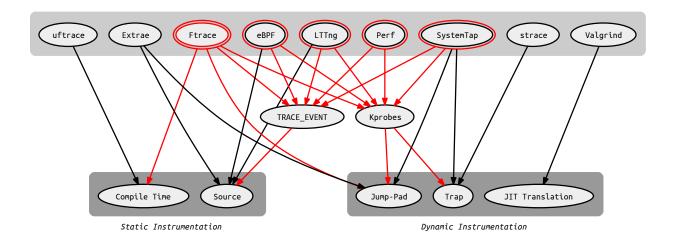

| Figure 2.4  | Dependency graph of tracing tools and frameworks showing kernel (red)         |    |

|             | & userspace (black) tracers                                                   | 15 |

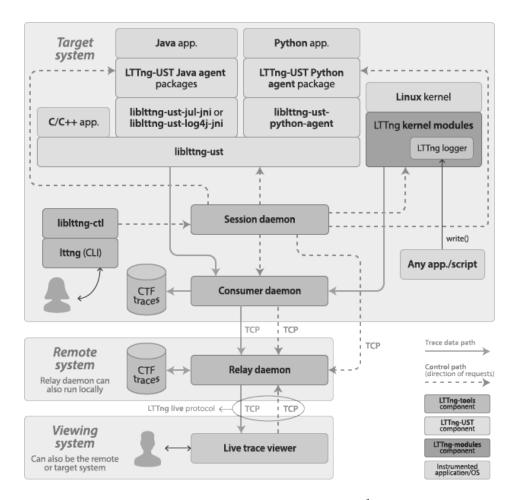

| Figure 2.5  | LTTng Architecture                                                            | 19 |

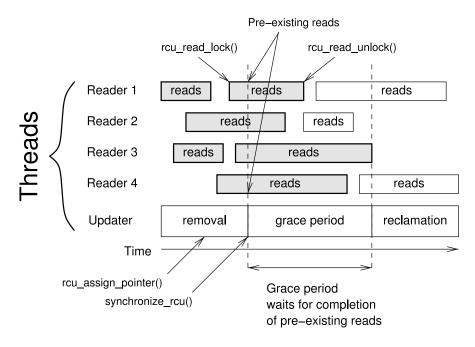

| Figure 2.6  | Flow of RCU handling resource critical sections                               | 20 |

| Figure 3.1  | research milestones and progression                                           | 35 |

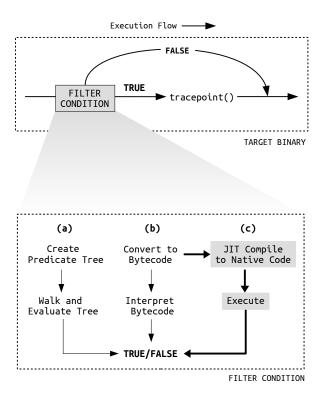

| Figure 4.1  | Overview of filtering in trace and debug context. The bold path (c) is        |    |

|             | the approach which yields minimum overhead                                    | 42 |

| Figure 4.2  | The <i>client</i> is responsible for conversion of a filter expression to the |    |

|             | bytecode, which is sent through lttng-sessiond to the instrumented            |    |

|             | userspace application for validation, linking and an eventual interpre-       |    |

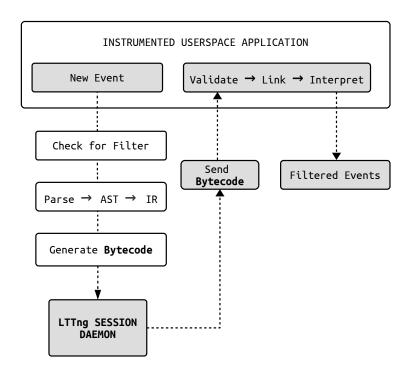

|             | tation per event                                                              | 50 |

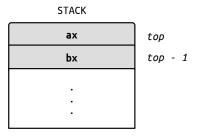

| Figure 4.3  | The LTTng interpreter is stack based with two registers (ax and bx)           |    |

|             | aliased to top of stack                                                       | 51 |

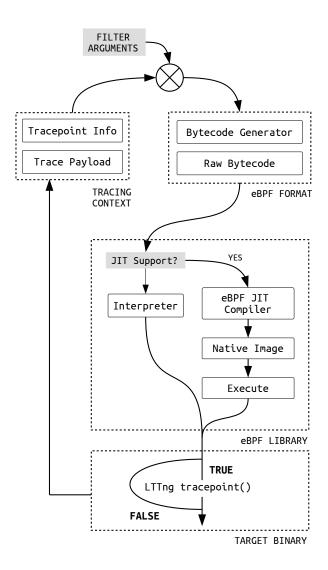

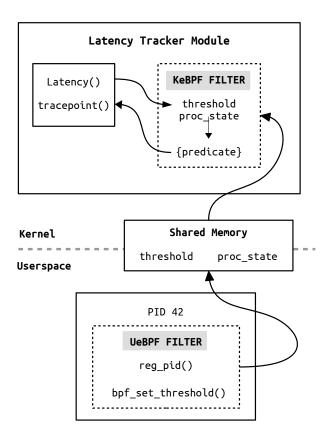

| Figure 4.4  | The architecture of our proposed eBPF based trace filtering system $$ .       | 54 |

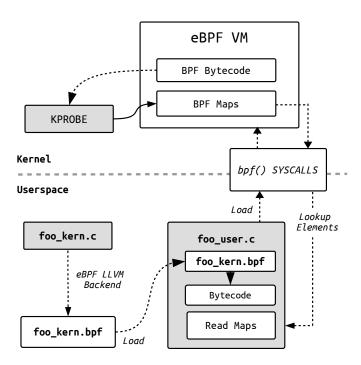

| Figure 4.5  | An eBPF program in its current form, with the kernel part (foo_kern.c)        |    |

|             | and a userspace part (foo_user.c). The userspace part uses the bpf()          |    |

|             | syscall to load bytecode in the eBPF kernel VM, as well as reading and        |    |

|             | updating data in $BPF\ maps$                                                  | 59 |

| Figure 4.6  | The KeBPF-UeBPF shared memory implementation showing syscall                  |    |

|             | latency thresholds being set dynamically from within a UeBPF filter           |    |

|             | program                                                                       | 62 |

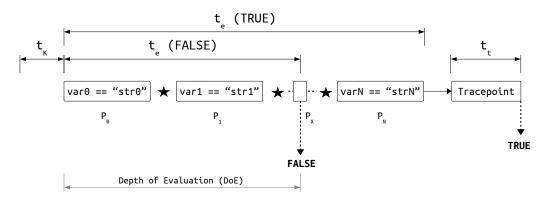

| Figure 4.7  | Design of the trace filter benchmark. Evaluation time $t_e$ depends on        |    |

|             | DoE                                                                           | 65 |

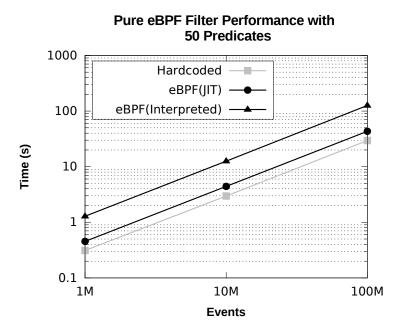

| Figure 4.8  | Pure eBPF filter performance with a 50 predicate TRUE biased AND              |    |

|             | chain                                                                         | 66 |

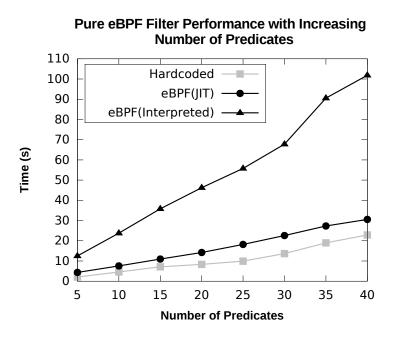

| Figure 4.9  | Pure eBPF filter performance with 100M events and a TRUE biased               |    |

| T           | AND chain                                                                     | 66 |

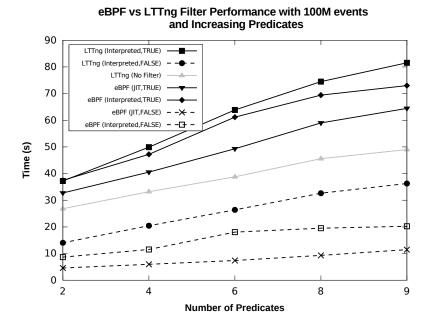

| Figure 4.10 | eBPF vs LTTng's filter performance with increasing number of TRUE/-           | c= |

| D: *4       | FALSE biased AND chain predicates                                             | 67 |

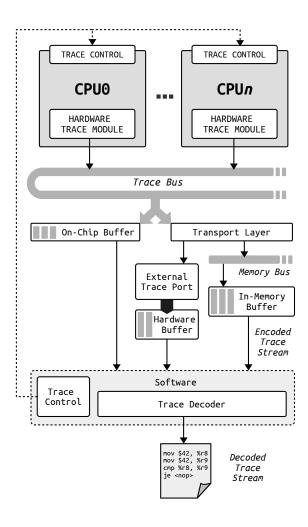

| Figure 5.1  | Hardware tracing overview                                                     | 74 |

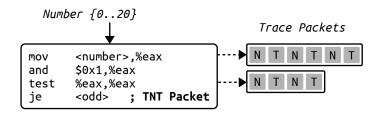

| Figure 5.2  | An odd-even test generates corresponding Taken-Not-Taken Packets .         | 78    |

|-------------|----------------------------------------------------------------------------|-------|

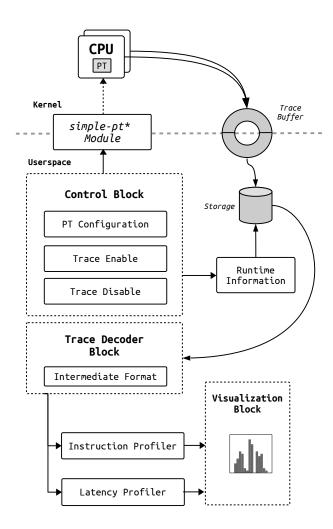

| Figure 5.3  | The architecture of our proposed hardware-assisted trace-profile fra-      |       |

|             | mework. Simple PT is used for trace hardware control                       | 81    |

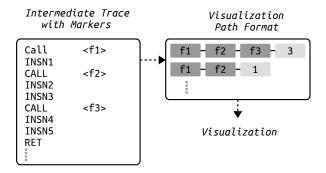

| Figure 5.4  | A sample trace sequence converted to a section of visualization path       |       |

|             | format                                                                     | 85    |

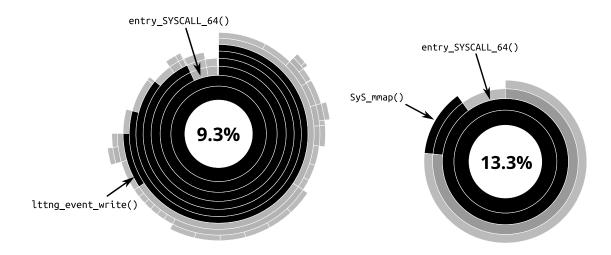

| Figure 5.5  | The effect of an external software tracer on the mmap() syscall, obtained  |       |

|             | from a near zero overhead hardware trace, is visible in (a) as extra       |       |

|             | layers as compared to (b), which took a shorter path and a shallower       |       |

|             | callstack. The rings represent the callstack and are drawn based on        |       |

|             | instruction count per call                                                 | 85    |

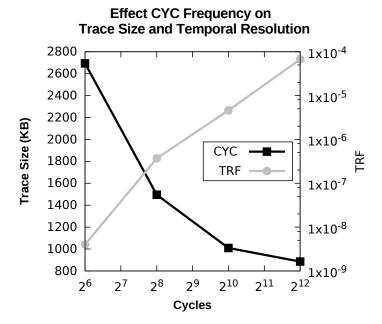

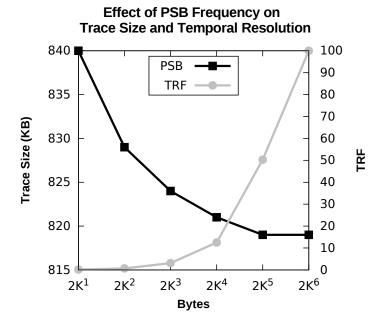

| Figure 5.6  | Trace size and resolution while varying valid CPU cycles between two       |       |

|             | subsequent CYC packets. Lower TRF value is better                          | 90    |

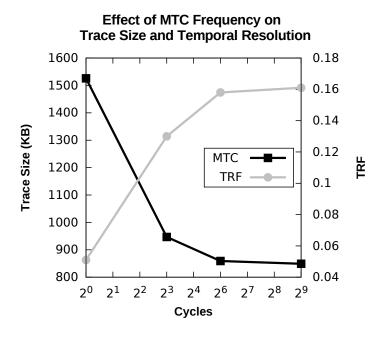

| Figure 5.7  | Trace size and resolution while varying valid CPU cycles between two       |       |

|             | subsequent MTC packets. Lower TRF value is better                          | 90    |

| Figure 5.8  | Trace size and resolution while varying valid bytes of data between two    |       |

|             | subsequent PSB packets                                                     | 91    |

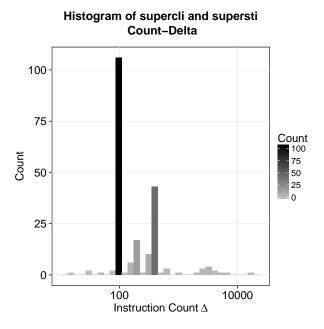

| Figure 5.9  | Histogram of instruction count delta for superSTI and superCLI ins-        |       |

|             | tructions generated using Delta Profiling algorithm                        | 94    |

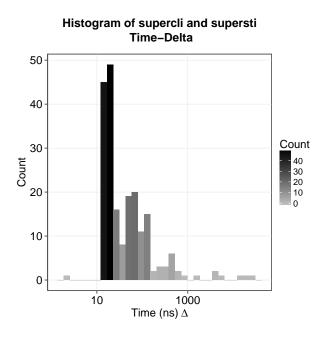

| Figure 5.10 | Histogram of time delta for superSTI and SuperCLI instructions ge-         |       |

|             | nerated using Delta Profiling algorithm                                    | 94    |

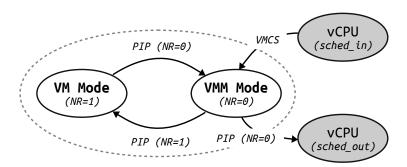

| Figure 6.1  | System Architecture                                                        | 101   |

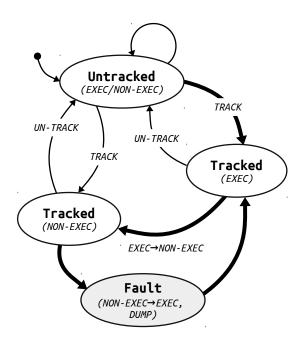

| Figure 6.2  | HAVAna State Machine                                                       | 102   |

| Figure 6.3  | Resource View showing 4 vCPUs and their execution distribution on          |       |

|             | single pCPU along with a zoomed view of the VMM mode                       | 104   |

| Figure 6.4  | Control Flow View showing 3 RabbitMQ worker processes contending           |       |

|             | for existing pCPU                                                          | 105   |

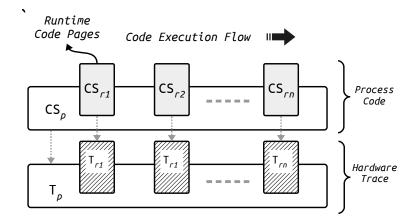

| Figure 7.1  | Runtime and file-backed code section for a process $P$ as observed by      |       |

|             | the OS                                                                     | 112   |

| Figure 7.2  | Corresponding hardware pages                                               | 113   |

| Figure 7.3  | FlowJIT Architecture                                                       | 115   |

| Figure 7.4  | Access Tracking State Machine                                              | 116   |

| Figure 7.5  | FlowJIT retrieved runtime code image of eBPF $(I_r)$ merged with failed    |       |

|             | decoding in hardware trace $(T_r)$ to reconstruct flow of JIT compiled cod | .e120 |

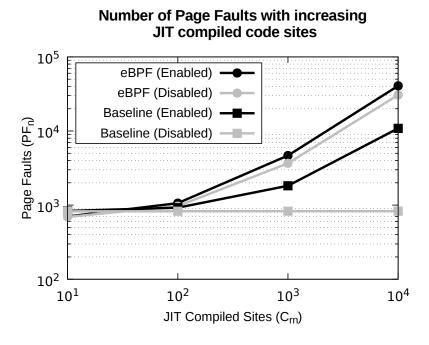

| Figure 7.6  | Effect of JIT compile sites on Page Faults with FlowJIT                    | 123   |

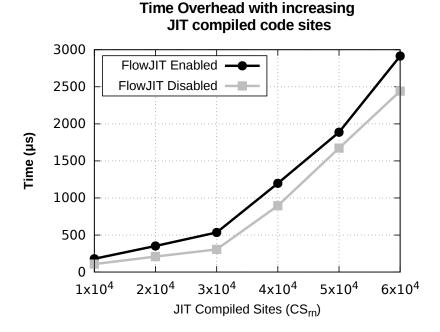

| Figure 7.7  | Overhead of FlowJIT enabled executions with increasing JIT compiled        |       |

|             | sites                                                                      | 124   |

| •   |  |

|-----|--|

| XIV |  |

#### LIST OF ABBREVIATIONS

API Application Programming Interface

ARM Advanced RISC Machines

ART Always Running Timer

AVX Advanced Vector Extensions

BLAS Basic Linear Algebra Subprograms

BPF Berkeley Packet Filter

BSD Berkeley Software Distribution

BTS Branch Trace Store

CFG Control Flow Graph

CISC Complex Instruction Set Computer

CPU Central Processing Unit

CSPF CMU/Stanford Packet Filter

CYC Cycle Count

DBI Dynamic Binary Instrumentation

DBT Dynamic Binary Translation

DCPI Digital Continuous Profiling Infrastructure DGEMM Double-Precision General Matrix Multiply

ETB Embedded Trace Buffer

ETM Embedded Trace Macrocell

FPU Floating Point Unit

GCC GNU Compiler Collection

HAVAna Hardware Assisted VM Analysis

I/O Input/Output

ICE In-Circuit Emulation IRQ Interrupt Request

ISA Instruction Set Architecture

JIT Just-In-Time

JTAG Joint Test Action Group

JVMDI Java Virtual Machine Debugger Interface

LBR Last Branch Record

LLVM Low Level Virtual Machine

LTTng Linux Trace Toolkit Next Generation

MIPS Microprocessor without Interlocked Pipeline Stages

MTC Mini-Timestamp Counter NMI Non-Maskable Interrupt

NR Non-Root

PIP Paging Information Packet PSB Packet Stream Boundary

PT Processor Trace

PTM Program Trace Macrocell

SIMD Single Instruction Multiple Data SIMD Single Instruction Multiple Data SSE Streaming SIMD Extensions

SoC System-on-Chip

TIP Target Instruction Pointer

TMA Timing Alignment

TNT Taken-Not-Taken

TRF Temporal Resolution Factor

TSC Timestamp Counter

VM Virtual Machine

VM(s) Virtual Machine(s)

VMA Virtual Memory Area

VMCS Virtual Machine Control Structure

VMM Virtual Machine Monitor

pCPU Physical CPU vCPU Virtual CPU

#### CHAPTER 1 INTRODUCTION

System analysis tools are indispensable to developers. The advent of newer many-core systems have made it hard for current debuggers and tracers to keep up in terms of features and performance. To get a detailed view of system internals, a more in-depth analysis is required which usually involves probing millions of locations in application code. In software with large code-bases, such as the Linux kernel, thousands of statically instrumented tracepoints exist. Analyzing such software requires thousands of such tracepoints to be enabled at runtime, which eventually generates a huge amount of trace data that needs to be analyzed. For resource constrained systems, it would be inefficient to store such a huge amount of trace data and retrieve it for offline analysis. In our work, we first investigated a software-only approach where we focused on efficient filtering of trace data at runtime to weed out unnecessary tracepoints and select only the interesting ones. We also proposed a kernel-userspace cooperative tracing approach where the trace filters would co-operatively work on conditions that can be changed dynamically.

Furthermore, we observed that modern debugging and tracing tools are not utilizing the full support of hardware provided by the current generation processors which have in-built tracing blocks. These hardware tracing techniques could allow a more detailed way of analyzing data by further reducing the runtime overhead. We investigated this line of thought and came up with innovative hardware-assisted tracing techniques that can be combined with software tracing tools to provide low-overhead and more granular analysis of modern systems.

#### 1.1 Definitions and Basic Concepts

#### 1.1.1 Instrumentation

In the domain of computer program analysis, we define the term *instrumentation* as the addition of extra code in the analysis program either before or after compilation that enables the observer to gather metrics about the program as it eventually executes. These metrics can be as simple as a histogram of the number of times a function got called or complex memory and thread sanitation routines. Most of the advanced tools used for profiling, tracing or debugging that we eventually discuss are built upon such instrumentation primitives. In this thesis, we classify instrumentation as either static, dynamic or hybrid in nature.

#### Static Instrumentation

In many cases, before compilation begins, the analysis code can be added as part of the target program source. For example, in the case of a simple function profiler, a function that increments a small counter can be added at every entry of all functions in the target program. This is usually the case for large software such as the Linux kernel which use statically inserted tracepoints in all major functions. Various tools hook onto their tracepoints in the kernel to gather data for further analysis. We will elaborate on this in subsequent sections. Such instrumentation is inexpensive but has a drawback of always being in the critical execution path during execution. Another approach to static instrumentation is when the compiler itself instruments paths in the code to execute analysis code [1]. In any case, static instrumentation requires the source code knowledge or compiler assistance, to introduce analysis code in the target application.

Modern compilers such as GCC and LLVM Clang allow special symbols or callback-function hooks to be inserted at entries and exits of all functions in the source code at compile time. At runtime, an instrumentation agent can latch onto those functions and execute its own analysis code. As an example, the Linux kernel can be compiled with the gcc -pg switch which inserts a mcount symbol at each function entry and exit. This can be latched onto by the Ftrace tracer at runtime to provide dynamic tracing capabilities. Similarly, for any userspace program, GCC offers the -finstrument-functions switch, which provides compile time instrumentation of calls to \_\_cyg\_profile\_func\_enter() and \_\_cyg\_profile\_func\_exit() functions. These can then be interposed at runtime and be used to run analysis code. The analysis infrastructure and tools such as LTTng, Ftrace, SystemTap and eBPF heavily utilize static instrumentation which is part of the Linux kernel infrastructure.

#### **Dynamic Instrumentation**

Analysis code can also be inserted in binaries post compilation – either on application binaries residing on the disk or more importantly while the target application is executing. This is known as Dynamic Binary Instrumentation (DBI) and is of special interest to us as it allows the insertion of code while the process is executing. DBI eliminates the need of having a prior knowledge of program source code while providing the benefit of enabling and disabling the analysis code We classify most of the dynamic instrumentation techniques used in building frameworks and tools as follows:

**TRAP Based**: This technique is used in tools such as older Kprobes [2, 3] and GDB's normal tracepoints [4, 5]. During execution, when the TRAP is encountered, the OS halts

the program and its state is saved. It sends a SIGTRAP signal to the process which can handle the exception. Usually in the handler, the original instructions are executed, out of line and then the intended instrumentation code is executed. Upon return from the handler, the original instruction is restored and the execution continues. On x86, 0xCC is reserved for such an interrupt. The target instruction in the target function is replaced with an exception causing instruction (such as int 3 on i386 architecture), and the exception handler then executes the instrumentation code. Traditional debuggers use this approach to implement breakpoints, with the help of debugging calls (such as ptrace() on Linux) to insert the TRAP and read the status and content of the debugged process.

Jump-pad Based: Most of the good instrumentation frameworks such as Dyninst, PIN and tools like GDB (for fast tracepoints) [6], however, employ the much faster trampoline approach. Dyninst usually replaces the complete target function with a patched version in which a jump is placed at the specified instrumentation point in the target. This jump transfers the execution to a trampoline which executes the displaced instructions from the target function. Then, the stack is adjusted and the CPU registers are saved on stack. Finally, a call to the snippet (instrumentation code) is made. Upon return, the stack is rearranged, the original register state is restored, and the execution continues. As the execution stream is not disturbed, and the snippet execution only incurs some jumps and a few more instructions instead of a costly trap, this process is one of the fastest instrumentation approaches.

JIT Translation: Other tools like Valgrind [7] use Just-in-Time (JIT) code translation based techniques. The binary is first disassembled and converted into an intermediate representation (IR). The IR is then instrumented with analysis code (such as the memory analysis code of memcheck). It is then recompiled back to the machine code and this instrumented code is stored in a code-cache. This can then be executed on Valgrind's synthetic CPU. It is much like interpreting native instrumented instructions in a process virtual machine [8]. With this scheme, the tool (Valgrind) has a very good control over the target executable. However, being very costly, this is not appropriate for the tracing domain.

#### 1.1.2 Tracing

Tracing can be defined as a very fast system-wide fined grained logging mechanism. With the traditional debugging approach, it becomes quite difficult to gather very low level, as well as time accurate details about the system's behavior in quasi real-time. Sampling based profiling tools are also only moderately useful in such cases. Therefore, the fast logging mechanism called tracing is employed. Tracing tools and frameworks are built upon the base instrumentation techniques discussed previously. Tracing can be divided according to the functional

aspect (static or dynamic) or by its intended use (kernel or userspace tracing – also known as tracing domains). Static tracing requires source code modification and recompilation of the target binary/kernel, whereas in dynamic tracing one can insert a tracepoint directly into a running process/kernel, or in a binary residing on the disk.

#### **Tracepoint**

Tracing usually involves adding a special *tracepoint* in the code. This tracepoint can look like a simple function call, which can be inserted anywhere in the code (in case of userspace applications) or be provided as part of the standard kernel tracing infrastructure.

#### **Event**

Each tracepoint hit is usually associated with an event. When a tracepoint is hit, a callback function is called which allows trace data to be collected, aggregated or stored in a buffer. The events are very low level and occur more frequently. Some examples are syscall entry/exit, scheduling calls, etc. For userspace applications, these can be some important functions in the target application such as a request processing thread of a server or an insert operation in a database.

#### Trace Buffer

In general, tracing involves storing associated data in a special buffer, whenever an event occurs. For a detailed execution trace of a very fast system, this data is obviously huge and contains precise time-stamps of the tracepoints hit, along with any optional event-specific information (value of variables, registers, etc). All this information can be stored in a specific format for later retrieval and analysis.

#### 1.1.3 Program Flow

Another important way to debug and profile programs is by analyzing the paths a program took while executing. This can help in understanding if the call stack for a given function was the one that we expected, or be used to profile function executions and observe latency between any two points in the program. Information about possible program paths can be obtained by static or dynamic analysis of source code, or more advanced hardware-assisted techniques. While static analysis of a program through its source code can yield a detailed Control Flow Graph (CFG), and eventually a way to visualize the program flow, it is only at runtime that the information about reachable CFG paths can be known. As an example, the

Ftrace tracer in the Linux kernel uses the software based hybrid instrumentation techniques discussed above to obtain the program flow at function granularity. The program flow can be obtained at a very high granularity through either analyzing every instruction executed by the processor or through offline reconstruction of instruction flow by recording only branches and change-of-flow instructions in the program.

#### Hardware Tracing

A major part of the work presented in this thesis revolves around special hardware tracing blocks that are part of modern processor chips. These on-chip tracing blocks generate high frequency trace packets at instruction or branch granularity in a program which allows the analysis tool to reconstruct program and/or data flow by looking at the instruction flow and timings. This allows a more fine-grained analysis of applications. As an example, Intel provides the Branch Trace Store (BTS), Last branch Record (LBR) and Processor Trace (PT) hardware blocks which allow recording each branch status and its target. Such trace hardware is implemented on silicon with enable/disable control from control registers of the processor. This is the lowest level of tracing, which allows analysis of instructions as they execute. The same hardware can also be configured to generate timestamp packets to analyze latency issues very closely in real-time systems. As there is no tracepoint being called in the software and trace recording happens in parallel, the overhead of this hardware-assisted approach on the target application is minimal. We elaborate more on this in the next chapter.

#### 1.2 Problem and Scope

Up until recently, code analysis tools have always been simpler in terms of design and functionality owing to the fact that test applications were monolithic and processing hardware was simple. For the more complex modern, multi-core and distributed systems of today, even though debuggers can give a detailed view of the target process at any given time, they require pausing the process and running a manual or conditional automated analysis. This alters the time-correctness of applications. Tracing, as discussed before, has proven to be an important technique in such cases. It is robust and useful for long-running systems in production for which halting the process for analysis is not an option. For a detailed view of such systems however, as expected, enabling millions of trace events generates a lot of data and hence causes unwanted overhead in the system. This forces the analyst to disable multiple tracepoints, which then impedes the understanding of proper application context post-execution. Even though modern tracers allow preliminary filtering of events, the conditions on which they check are restricted to only the kernel context. Moreover, tracing tools

and frameworks do not leverage advancements in processor hardware over the years, due to their complexity and lack of empirical data on their performance, even when these hardware tracing frameworks could address the problem of detailed trace data obtained with low overhead.

**Research Questions** The state-of-the art analysis techniques have not considered such limitations and lack any advancement that allow the reduction of overhead and maintaining reproducible and useful traces. In view of the issues discussed above, we go a bit further and define three important research questions that have not yet been addressed in-depth in this domain:

- Is it possible to develop a new, modern tracing technique that allows a more detailed view of the system but at a lower overhead and with a larger trace context?

- Can we further enhance the information gathered from the control flow traces and reduce the overhead on production systems using modern hardware techniques coupled with software assistance?

- Will the newly proposed algorithms and techniques, be robust, have low overhead and cause minimum perturbations to the target system?

# 1.3 Research Objectives

For obtaining a highly detailed view of the system but at a low cost to the system itself, the conditional aspect of tracing has not been investigated in-depth before – especially considering the cost of filtering high-frequency events with a software approach. Conditional tracing can be used where filters can be applied over tracepoints, which allow the tracepoint to fire and actually record data only when a particular condition is verified. The conditions need to have a context of the operating system as well as the target process and would require some sort of expression language that could be evaluated at runtime at a high speed. Apart from that, modern processor chips now contain hardware tracing blocks that have not been sufficiently utilized to obtain detailed traces. Therefore, the lack of very accurate trace information is still a major issue for production systems. For this research, the general objective has been to solve the problem of low-overhead yet detailed traces by exploring pure software as well as hardware-assisted techniques recently becoming available.

Going further, we identified specific objectives of our research as follows:

— To propose a new tracing technique that introduces the concept of software based conditional tracing which can yield a holistic yet detailed view of the target applications.

- To propose algorithms that utilize hardware tracing support in modern processors for a detailed analysis of target applications and virtual machines with a low-impact on the observed system.

- To develop new algorithms and techniques that optimize the state-of-the-art hardware trace analysis approach for improving accuracy of trace data gathered for an overall improved tracing framework.

#### 1.4 Contributions

In-line with the research objectives stated above, this thesis presents the following original contributions in the field of systems and program analysis:

- A fast conditional tracing architecture which incorporates JIT compiled filters and an improved kernel VM - user VM direct data sharing mechanism for low overhead co-operative tracing.

- An instruction and time delta profiling algorithm which utilizes on-chip hardware tracing blocks for a low-overhead program flow and latency analysis. This technique also allows us to profile software tracing overhead with cycle-accurate resolution.

- A hardware-assisted virtual machine analysis algorithm which utilizes trace packets from on-chip hardware to detect resource contention in virtual CPUs, and processes running inside the VM with near-zero overhead and in a non-intrusive manner.

- A robust, low-overhead, kernel-assisted hardware trace reconstruction algorithm which allows hardware traces to be reconstructed in partial or incorrect decoding scenarios when runtime compiled code is executed on the hardware.

#### 1.5 Outline

This thesis is organized as follows. Chapter 2 is dedicated to the review of state-of-the-art literature and associated software frameworks, the techniques they use and our inference from them. Chapter 3 outlines our research methodology and explains the process of generating research leads, identifying problems, actionable items, specific milestones and eventual outcomes in terms of research papers and a succinct description of their content. It presents an overall view of the body of this research. We then move towards the core body of the research which has been presented as four articles.

We first present a new and improved trace filtering and conditional tracing architecture as the article titled "Enhanced Userspace and In-Kernel Trace Filtering for Production Systems". We propose our new kernel and userspace co-operative tracing approach as well as a fast

tracing architecture based on eBPF and LTTng. This article appears in the November 2016 issue of *Journal of Computer Science and Technology* (Springer) and constitutes Chapter 4 of this thesis.

The second article discusses new hardware trace based high resolution and low overhead filtering techniques and a new algorithm to generate instruction and time delta profiles for accurate profiling of interrupt and syscall latency. This article is titled "Hardware-Assisted Instruction Profiling and Latency Detection" and appears in the August 2016 issue of *Journal of Engineering* (IET) and is presented in Chapter 5 of the thesis.

Our third article presents a novel non-intrusive algorithm to trace VMs, with very low overhead hardware-assisted tracing, through analysis of raw hardware trace packets. This work has been presented in the International Workshop on Cloud Computing Systems, Networks, and Applications at IEEE Globecom conference and appears in *Proceedings of Globecom Workshops* (IEEE). This is reproduced as Chapter 6 in this thesis.

The fourth article in Chapter 7 presents a new algorithm and an in-kernel implementation which tackles the issue of faulty hardware trace reconstruction when runtime code such as JIT compiled sections are being executed in a target process. This work has been submitted to ACM Transactions on Computer Systems

Finally, in Chapter 9, we present a summary and discussion of our research contributions, their impact on the tracing ecosystem and provide recommendations for future work that may be carried out in this field.

#### CHAPTER 2 LITERATURE REVIEW

In this chapter we attempt to classify and review techniques used within popular trace, profile and debugging tools - both software and hardware based. This has helped us gain an understanding of the benefits and deficiencies in state-of-the-art methods and algorithms.

#### 2.1 Tracing and Instrumentation

As discussed in Chapter 1, static and dynamic instrumentation techniques form the core of the tracing, debugging and profiling tools and frameworks available. We first begin with a case-study of a small experimental dynamic tracing tool called **DyTrace**, which we developed while analyzing tracers in-depth. This gives the reader a deeper understanding of what goes on behind most popular trace frameworks from a very low-level perspective while discussing the state-of-the-art techniques used in developing them. We shall then move towards the description of other dynamic and static instrumentation techniques and details of other modern trace frameworks and related recent advancements.

# 2.1.1 CASE STUDY : DyTrace

The goal of this initial effort was to build a minimal tracing tool that allows insertion of static tracing code in a binary dynamically. For this, we used a binary instrumentation framework called Dyninst and a special POSIX syscall called ptrace().

#### ptrace()

Linux has a special system call called ptrace() which "provides a means by which one process (the "tracer") may observe and control the execution of another process (the "tracee"), and examine and change the tracee's memory and registers. It is primarily used to implement breakpoint debugging and system call tracing" [9]. A target child process on which ptrace has to be used goes through the following states:

- 1. Child process is stopped upon receiving a signal (like SIGSTOP)

- 2. Parent receives child status from wait() (it is safe to start ptrace)

- 3. Ptrace operations are performed on the child

- 4. Parent signals child again to continue execution

A typical ptrace() call may be written as,

```

long ret = ptrace(PTRACE_ATTACH, pid, NULL, NULL);

```

where the first argument is a special ptrace code, the second is the PID of the target child process to control, and the third and fourth arguments are the memory addresses for modification and data structures to be written to the process respectively. As an example in the above code line, the PTRACE\_ATTACH code is used when a task (T) wishes to control the child (C) with PID as pid. It makes C a child of the tracing task T. Similarly, in the following listing,

```

long ret = ptrace(PTRACE_POKEDATA, pid, addr, new_val);

```

The call writes new\_val to address addr in the address space of the child task. Such actions are useful for debuggers where variables can be changed upon pausing the process to observe its behavior. There are other ptrace codes such as PTRACE\_SETREGS, PTRACE\_GETREGS, PTRACE\_PEEKTEXT etc. which perform similar related tasks. The modifications done by ptrace itself are at the binary level and hence have a direct effect on the execution. Consider an execl call,

```

execl("/bin/ls", "ls", NULL);

```

According to the calling conventions for the calls on a x86 machine, first the syscall number is loaded in %eax and then the subsequent arguments are loaded in %ebx, %ecx, %edx, %esi and %edi. After setting these registers, the soft interrupt 0x80 is called as int \$0x80 which signals the kernel to go ahead with the system call [10]. However, before executing the syscall, the kernel checks if the process is being traced or not. So, in the traditional fork-exec model, if the child has a ptrace() call before an execve() call, the kernel will hand over the control to the parent before execve(). At the syscall, the kernel saves the value of the eax register which has the syscall number. The parent then continues to call ptrace with actions such as modifying/reading the memory or registers. This is usually followed by a PTRACE\_CONT code which continues the child execution and the syscall but now with modified register/memory values. Thus, it can be seen that ptrace can act as a building block for any dynamic instrumentation technique and an instrumentation primitive. The subsequent sections discuss some tools built using such primitives and their performance.

#### **Dyninst**

Dyninst presents a very simple and powerful API for dynamic instrumentation [6]. There are two main essential terminologies involved in performing instrumentation, *snippets* and *points*. Points are simply the locations in a program where instrumentation can be inserted. They can be function entry, function exit etc. Snippets are the abstraction for the code that can be inserted at the points. Snippets are not directly written in assembly, but instead Dyninst uses an intermediate representation via an abstract syntax tree. If the complexity of the snippet increases, it can be built separately using a C-like syntax based scripting support in DynC.

Dyninst introduces the concept of mutator which is the program that is supposed to modify the target (mutatee). This mutatee can either be a running application or a binary residing on disk. The process attaching or creating a new target process allows the mutator to control the execution of the mutatee. This can be achieved by either processCreate() or processAttach() which returns a BPatch object. This functionality is achieved internally using the ptrace() call discussed before. The mutator then gets the program image using the object, which is a static representation of the mutatee. Using the program image, the mutator can identify all possible instrumentation points in the mutatee. The next step is creating a snippet for insertion at the identified point. The mutator can then create a snippet, to be inserted into the mutatee. Building small snippets can be trivial. For example, small snippets can be defined using the BPatch\_arithExpr and BPatch\_varExp types. The snippet is compiled into machine language and copied into the application's address space.

**Jump-Pad** For executing the built snippets, the concept of jump-pad or trampolines is used. The normal execution flow is modified by *jumping* to another memory location, executing the snippet code there and then returning, as illustrated in figure 2.1.

Figure 2.1 Trampoline approach used by Dyninst

The instruction at the instrumentation point is replaced by a jump to a base trampoline.

The base trampoline then jumps to a mini-trampoline that starts by saving any registers that will be modified. Next, the instrumentation is executed. The mini-trampoline then restores the necessary registers, and jumps back to the base trampoline. Finally, the base trampoline executes the replaced instruction and jumps back to the instruction after the instrumentation point.

Instruction Instrumentation While building the experimental DyTrace tool, particularly at the instrumentation phase, the changes made at the assembly level to the executing process's executable memory were observed. Figure 2.2 shows how Dyninst uses the trampoline approach at instruction level to insert our own static tracing functions dynamically.

We see a test function where our tool intends to insert our static tracing function tpint() just before its exit. This tpint() function simply saves the integer value provided to it as an argument to a trace file - thereby tracing the value dynamically as the program executes and demonstrating a small trace tool.

Figure 2.2 Original code and jumps inserted for trampolines

When instrumentation at function exit was done for Dyninst, it replaced the whole function block and patched a jump on entry with address to its trampoline. Dyninst executes the instructions out-of-line and then returns from the function. Figure 2.3 shows what goes inside the trampoline. First, the remaining function is executed out-of-line. The basic idea for instrumentation is to prepare the stack first, and save the current state by pushing all the registers. Then, it continues to execute the snippet (containing the pre-built tracepoints from the library), restores the stack state, pops all the registers and finally restores the original stack pointer and returns. In our small experiment with DynTrace, as shown in the figure, a variable with the value 43 (trace payload) was recorded dynamically, using a static tracing function tpint() by instrumenting it at end of the target function.

Irrespective of whether the available tracing frameworks are in userspace or in the kernel, the same basic static and dynamic tracing techniques are used. As an example, the jump-pad technique is used by GDB in its fast userspace tracepoints as well as by Kprobes to provide

Figure 2.3 Inside a Dyninst trampoline

an efficient dynamic tracing framework in the kernel. Before moving further, we discuss some common intermediate techniques used in kernels on which high level trace frameworks can hook onto.

#### 2.1.2 Kprobes

With the basic mechanism in place to modify instructions, developers have provided a support infrastructure in the Linux kernel in the form of Kprobes, to instrument almost any kernel function on-the-fly and gather debugging and performance information without any disruption [3]. Tracing tools can build upon the Kprobe interface by providing kernel modules. The module's init function registers one or more probes, and the exit function un-registers them. A registration function such as register\_kprobe() specifies where the probe is to be inserted and what handler is to be called when the probe is hit. Upon a probe registration, Kprobes makes a copy of the probed instruction and replaces the first byte(s) of the probed instruction with a breakpoint instruction (e.g., int 3 on i386 and x86\_64). When a CPU hits the breakpoint instruction, a trap occurs, the CPU's registers are saved, and control passes to Kprobes. Kprobes executes the pre\_handler associated with the Kprobe, passing the addresses of the Kprobe struct and the saved registers to the handler. A newer fast

kprobes implementation which removed the slower TRAP based dependency on int 3 was proposed and implemented recently, which aims to improve the performance further [2]. This is based on the jump-pad instrumentation approach discussed before. Most tracers such as LTTng, SystemTap or Perf, that wish to provide dynamic tracing capabilities in the Linux kernel, use Kprobes and get the trace payload data through their own mechanisms.

#### 2.1.3 TRACE\_EVENT

The majority of static tracepoints in the Linux kernel are provided using the TRACE\_EVENT() macro [11, 12]. It is one of the most common ways to connect a tracer to the tracepoints in the kernel, mainly due to the fact that it allows the developers to just use the macro to add tracepoints and acts as an abstraction for the trace or profile tools. The same tracepoint can then be used by all the popular Linux tracers - Perf, LTTng, SystemTap or Ftrace. This macro allows the kernel developers to basically define a callback function hook that would be called upon a tracepoint hit. It also allows arguments that should match the function prototype and a structure that can contain the tracepoint data. Tools such as LTTng or SystemTap can then define their own tracepoint wrappers as part of statically or dynamically generated kernel modules that match those defined in the TRACE\_EVENT macro statically in the kernel code. This allows a standard location of tracepoints strategically placed in the Linux kernel source code but a facility for other tracers to hook onto them and use their own mechanisms of data transfer or computation.

#### 2.1.4 Tracing Infrastructure Hierarchy

Static and dynamic tracing functionality in the userspace and Linux Kernel is provided by standard static and dynamic instrumentation techniques discussed earlier. There are a huge number of tracers that have been developed over the years, with varying capabilities and support. They can either support the kernel domain or userspace domain, or both. Tracers can sometimes hook to the standard interfaces described above or use their own low level static and dynamic tracing mechanisms. While tracers have been described elsewhere in detail, there has been no attempt to classify them based on the underlying infrastructure. Therefore, before going further to describe some state-of-the-art tracing tools, we classify them. This should help the reader to better understand as we describe some common trace frameworks. Figure 2.4 shows some common trace frameworks and the underlying mechanisms they use. The red color signifies kernel support and the black color signifies userspace support. The same figure also indicates the dynamic or static capabilities by direction of the arrows - either towards static instrumentation or dynamic instrumentation. As an example, we can

Figure 2.4 Dependency graph of tracing tools and frameworks showing kernel ( $\blacksquare$ ) & userspace ( $\blacksquare$ ) tracers

see that Ftrace, the kernel tracer allows tracing with the help of kprobes based events that in turn use either an optimized jump-pad based approach or a trap based technique. The same tracer also allows dynamically activated static tracepoints, which use compile-time static instrumentation approach. We now discuss some of these tools in detail.

#### Ftrace

The Linux kernel's native trace support is provided by its function tracer called ftrace [13]. It is a kernel-exclusive tracer which allows recording a trace of all eligible kernel functions along with accurate timestamps. It can then provide a function call graph representation or other analysis outputs such as interrupt-off or scheduling latency [14]. Ftrace simultaneously allows two mechanisms for tracing with trace control and data recording provided using the kernel's Debugfs pseudo-filesystem [15]. There are multiple trace targets available that can be used, but most of them either use the event tracer or a custom hooking mechanism.

Event Tracing Event tracing in ftrace is provided using the kernel's static tracing hooks exposed as TRACE\_EVENT() macro. This is similar to how Perf or LTTng use them. The tracepoint handler function of Ftrace allows the data to be collected in its own buffer, thus providing uniform information, as obtained from other tracers. An important feature of the event tracing mechanism of Ftrace is the ability to use filters. These filters allow a basic degree of limited conditional tracing. However, the filtering is done after the trace data has been recorded in the buffer. Another important limitation of filters in Ftrace is the inability of

Ftrace to access register values and variables at tracepoint locations. However, each tracepoint contains high resolution timing information which is valuable in diagnosing latency issues.

Dynamic Tracing Even though the name suggests the dynamic nature of tracing, this mechanism is essentially a dynamically activated static instrumentation technique. At kernel compile time, when the CONFIG\_DYNAMIC\_FTRACE option is used, the buildsystem uses GCC's compile time instrumentation option which inserts the mcount symbol at function entry. This allows Ftrace to directly hook onto most of the functions in the kernel directly and execute tracing or filtering code. Tim Bird has discussed this earlier in relation to function latency calculation in the Linux kernel [16] where these capabilities of Ftrace have been utilized. Apart from that, Ftrace also allows true Kprobe based dynamic tracing, which is itself based on jump-pad or trap based dynamic instrumentation. This allows Ftrace to dynamically probe not just entries of functions but also offsets within the function and functions-exits using the Kretprobes. This, however, carries all the limitations of Kprobes, such as restrictions on certain kernel functions. Overall, Ftrace is one of the most stable kernel tracing tools in use and is actively maintained by the kernel community.

#### 2.1.5 SystemTap

SystemTap [17] allows the dynamic insertion of tracepoints as well as collecting traces for tracepoints defined using TRACE\_EVENT. The trace collected can be displayed on the console while it is generated, or can be saved to a file. The flight recorder mode can dump the trace in memory to a file for it to be analyzed later. Instrumentation and trace code for SystemTap is written as scripts. The language is similar to C in terms of syntax and supports all ANSI C operations. The supported data types are only integers and strings but the same SystemTap script can be used to declare multiple instrumentation points. The declaration of an instrumentation point is composed of two parts. The first part is used to identify the event that you want to associate with the instrumentation point. The second part is the code to execute when the tracepoint is encountered. SystemTap also supports conditional tracing. To set a condition, the *if* style syntax is used:

```

probe kernel.function("vfs_read")

{

dev_nr = $file->f_path->dentry->d_inode->i_sb->s_dev

if (dev_nr >= 3)

printf ("%x\n", dev_nr)

}

```

In the above script, the instrumentation point is inserted at the entry of the function vfs\_read. The information is extracted from the parameter file and is copied into a temporary variable. This condition is then evaluated and the script outputs the value if true.

SystemTap scripts are converted into C code, which is then compiled as a module. This module is then inserted in the kernel and communicates with SystemTap for tracing. There is also a special mode where it is possible to insert C code in scripts mainly to overcome some limitations of the scripting language. Dynamic kernel tracepoints in SystemTap are implemented using Kprobes. SystemTap also takes input from the DWARF debugging information generated during the kernel compilation to determine the addresses of instrumentation points, as well as to resolve references to kernel variables used in scripts. SystemTap then registers the handler passed to Kprobe to retrieve the values of these variables. The dynamic tracepoints can use all the available variables from the instrumentation point addresses.

SystemTap provides a multitude of events that can be associated with instrumentation points. A few examples are listed below :

```

/* Function entry */

probe kernel.function("vfs_read").call

/* Function exit */

probe kernel.function("vfs_write").return

/* specific location in kernel code */

probe kernel.statement("*@fs/read_write.c:42")

/* Specific address in binary */

probe kernel.statement(0xc00424242)

```

SystemTap also allows static tracepoint connections using the TRACE\_EVENT macro. A static tracepoint can be activated by a script as follows:

```

probe kernel.trace("event name")

```

The event name is the name given to the static tracepoint during the call to the TRACE\_EVENT macro. Just as other trace probe types, static tracepoints defined in this way can be conditional too. However, they can only use the variables passed as parameters at the point of instrumentation. This is because the static tracepoint handlers do not receive copies of the

calling stack frame when the event is launched. In addition, SystemTap cannot use the display format specified in the TRACE\_EVENT using the macro TP\_printk. To represent the data as defined in the TRACE\_EVENT macro, the user must redefine how to do it in the script.

Though a very elaborate, feature-rich, and easy to use tool, SystemTap suffers from serious performance issues in terms of data gathering speed and scalability. Some benchmarks which compared SystemTap and LTTng-UST were performed by Julien Desfossez and showed results where in some instances UST was 289 times faster than SystemTap (in flight recorder mode) with the LTTng kernel [18]. This huge difference in performance is due to the use of buffering while collecting trace data for UST, instead of the SystemTap approach to have a system-call transition for each event. Also, a major chunk of work is handled in kernel rather than in user-space by SystemTap [19]. This is an architectural difference which leads to a deteriorated performance. The idea of dynamic compilation, also comes with an interrupt-driven approach and frequent context switches. Apart from that, mechanisms like preparing the code for compilation, the actual compilation to a module and the insertion process into the kernel as a module carries extra overhead, which overshadows the efforts of having an overall better tracing system.

### 2.1.6 LTTng

The Linux Trace Toolkit next generation is a very fast and extremely low-overhead kernel and userspace tracer. Low overhead, in simple terms, means that even with a *non-activated* tracepoint inserted in the code, it gives near-zero impact on the overall execution of the target application. This makes LTTng a bit different from the other tools and a default choice for real time applications. Its tracing technique implements a fast wait-free read-copy-update (RCU) buffer for storing data from tracepoint execution.

In figure 2.5, it can be seen that the LTTng session daemon acts as a focal point for trace control. Static instrumentation can be defined as tracepoints in the source code of the kernel, as well as in user-space applications with UST. The TRACE\_EVENT macro can also be used for kernel events. Dynamic instrumentation in kernel is provided by Kprobe, in the same way as for other tools. An instrumented application, which contains the user's desired tracepoints, automatically registers itself to the session daemon, just as its execution starts. This is also the case with the kernel. This is useful for handling simultaneous trace control for multiple trace sessions. Thereafter, the session daemon manages all the tracing activity. The LTTng consumer daemon is responsible for handling the trace data coming from the applications. It exports raw trace data and builds a CTF stream to be written on the disk. The Common Trace Format (CTF) is a compact binary format, which stores all the trace data in a very well

Figure 2.5 LTTng Architecture <sup>1</sup>

structured manner for further analysis by trace viewers and converters, such as Babeltrace (command line), or Trace Compass (graphical). For example, one can view the exact time of each event and the control flow through the various calls in the kernel, graphically in a time-line using Trace Compass.

Performance LTTng is currently the fastest tracer available for userspace tracing. Various performance comparisons with other tracers have revealed this before as well [18] [21]. The major factor for such improvements in performance is mainly due to the use of userspace RCU techniques for having a lock-less ring buffer in LTTng-UST. In figure 2.6, it can be seen how multiple readers trying to access a resource are managed by the RCU technique. The major reasons for such performance benefits are that rcu\_read\_lock() and rcu\_read\_unlock() are very fast [20]. However, LTTng still lacks some good features which some other tools already have such as trace support through scripting, dynamic tracepoint generation and

<sup>1.</sup> http://lttng.org/docs/v2.8/

Figure 2.6 Flow of RCU handling resource critical sections [20]

insertion in userspace, and a more elaborate trace filtering framework which supports both userspace and kernel trace filtering. Its current filtering approach is slow and restricts is support for conditional filtering with a kernel-userspace support scheme. We discuss these later in Chapter 4, where we improve upon this and propose a novel scheme.

#### 2.2 Process Virtual Machines

Process Virtual Machines (VMs) are created within a process context and are frequently used in scenarios where code may be dynamically injected in applications such as an OS kernel. Linux as well as Solaris have supported Process VMs such as DTrace and Berkeley Packer Filter (BPF) for tracing and network filtering usecases. This section explores process VMs in depth - focusing on precursors to full fledged process virtual machines, such as the techniques used in their design and bytecode interpreters. Keeping in mind the lightweight implementations required in the context of this research, lightweight and minimal VM implementations are discussed.

#### 2.2.1 Design Strategies

From a low-level design perspective, a virtual machine can be either stack based or register based. After all, a virtual machine is actually just like a real hardware machine implemented

in software, which allows it to execute code for an architecture, other than or the same as the one on which it is being run. To execute some code for that software defined machine, it has to follow the standard procedure to emulate an actual hardware machine:

- Conversion of high level language program to the virtual machine's bytecode (akin to  $C \rightarrow$  machine language conversion)

- Setup a Program Counter to keep track of each instruction in the stream

- Fetch the next instruction

- Decode operands based on the ISA

- Execute the instruction and write back data

To execute the instructions, the operands can either be stored on a stack or be considered to be registers for operations to be performed. Therefore, from this perspective, the machine can either be a stack-based or a register-based virtual machine.

Stack based VM Traditionally, a virtual stack has been used for evaluating expressions in VMs. For stack-based architectures locations of operands are implicit, following the stack pointer. In register-based machines, they would have to be specified explicitly in registers and then the operations would have to be performed on them. As an example, in an imaginary language, a code to add two numbers at the top of stack and store the result back on the stack may look something like this:

add ; A+B in accumulator (ACC) now

push ACC ; ACC pushed back to stack

This is of course assuming that the stack pointer is pointing to A and B which are the first two values at the top of stack. Owing to the fact that operands are implicitly defined, it would thus seem that stack-based machined would produce more compact machine code and would be more efficient than its counterpart. Most of the current VMs such as Java VM and .NET CLR are stack-based.

**Register based VM** Another approach is to store the operands and provide direct addresses from which to get data. These "addresses" are simply the virtual registers. A similar addition operation in a register based VM may look like:

```

add R1, R2, R3 ; A+B stored in R3

```

This assumes that values A and B are stored in registers R1 and R2 already. However, it means that these registers are not implicitly defined and they have to be specified for each

operation. This drastically reduces the number of instructions to be executed but the code size increases somewhat because of the register arguments. This means a trade-off between instruction length and instruction count. Apart from that, register based VMs have been found to be more efficient and quicker than their counterparts. For example, there may be expressions which need to be recalculated each time they appear in the code. This means that a register based VM can optimize this by storing the value in a register for repeated use. Fewer instructions also mean that the number of instruction dispatch needed will be smaller. Usually the instruction dispatch (fetching the instruction from memory) is implemented using a "switch case" and is a hard to predict indirect branch - thus it is expensive [22]. For such reasons, some newer VMs such as Dalvik and Lua VMs are register-based.

A formal study of the performance of stack and register-based VMs was done by Davis, Yunhe et al. [23]. They translated stack-based Java VM code to register-based code and independently studied how it performed. It has been observed that doing so eliminated around 47% of executed VM instructions and the corresponding machine code size gets increased by only 25%. They also observed smaller execution times (32.3% less) for the register-based machines using standard benchmarks. This points to an inclination towards usage of register-based VMs on modern processors. However, real life use cases vary a lot and it is not easy to draw any a priori conclusion favoring any specific approach.

#### 2.2.2 Interpreter Dispatch Mechanisms

The maximum time consumed in VM execution is actually the cost of instruction dispatch [23, 22]. The actual computation can be equivalent to a few machine instructions but the dispatch mechanism usually takes a maximum of 10 to 12 machine instructions and involves a time consuming indirect branch. The dispatch mechanisms are typically either of switch or threaded type:

Switch Dispatch - The main loop of the interpreter contains a large switch-case statement. For each opcode in the virtual machine, there is one case statement. An example in listing 2.1 shows a typical function which evaluates the bytecode instruction (instr) and then fetches the next instruction from the instruction buffer, after incrementing the virtual program counter (pc).

Listing 2.1 Example of a switch dispatch

This type of dispatch is simple but is somewhat inefficient in some instances. The break in the end translates to an unconditional jump to the start of the loop, there is only a single indirect branch for dispatching instructions, and the branch is very unpredictable on branch predictor enabled machines. There is also a range check on opcode to be performed. However, for the JVM, there is already a separate bytecode verifier. Overall, this is an acceptable method for the generic use-cases.

**Threaded Dispatch -** Another method is to use *threaded code*. This is a technique where the generated code consists only of calls to subroutines. In this dispatching technique, instructions are represented by the address of the routine that implements them and the dispatch consists in fetching that address and branching to the subroutine. A threaded dispatch can be of multiple types - direct, indirect, token dispatch etc. Refer to listing 2.2.

Such an implementation is possible in non ANSI C compilers only. For instance, GNU C provides a facility for goto statements to jump to multiple different locations by usage of labels as first-class values.

Listing 2.2 Example of a switch dispatch

```

void evaluate() {

Inst dispatch_table = { &&nop, &&add, ... }

goto dispatch_table[*pc];

add:

regs[r1] = regs[r2] + regs[r3];

pc++;

goto dispatch_table[*pc];

sub:

regs[r1] = regs[r2] - regs[r3];

pc++;

goto dispatch_table[*pc];

...

}

```

Translation to machine code generally involves 3-4 machine code instructions for each VM instruction in a direct dispatch, while it takes 9-10 machine code instructions for each VM instruction [24]. Davis et al. have discussed the implementation and efficiency of token threaded dispatch in [22]. The dispatch code is appended to the end of the code for each VM instruction. This allows the dispatch to be scheduled more efficiently and increases the prediction accuracy of indirect branches (45% versus 2%, 20%).

## **2.2.3** DTrace