# UNIVERSITÉ DE MONTRÉAL

## VERIFYING TIMED LTL PROPERTIES USING SIMULINK DESIGN VERIFIER

# MOHAMMAD-REZA GHOLAMI DÉPARTEMENT DE GÉNIE INFORMATIQUE ET GÉNIE LOGICIEL ÉCOLE POLYTECHNIQUE DE MONTRÉAL

# THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION DU DIPLÔME DE PHILOSOPHIÆ DOCTOR (GÉNIE INFORMATIQUE) AVRIL 2016

© Mohammad-Reza Gholami, 2016.

## UNIVERSITÉ DE MONTRÉAL

## ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Cette thèse intitulée :

### VERIFYING TIMED LTL PROPERTIES USING SIMULINK DESIGN VERIFIER

présentée par : <u>GHOLAMI Mohammad-Reza</u> en vue de l'obtention du diplôme de : <u>Philosophiæ Doctor</u> a été dûment acceptée par le jury d'examen constitué de :

Mme <u>BELLAÏCHE Martine</u>, Ph.D., présidente

Mme <u>BOUCHENEB Hanifa</u>, Doctorat, membre et directrice de recherche

Mme <u>NICOLESCU Gabriela</u>, Doctorat, membre

M. BENTAHAR Jamal, Ph.D., membre

### DEDICATION

This thesis is dedicated with love to my wife, Baharafarin, and two beautiful children, Daniel and Diana.

#### ACKNOWLEDGEMENTS

There are so many important people to whom I owe my sincere gratitude, and I will try to highlight some of them in these acknowledgements. First off, I would like to thank my supervisor, Professor Hanifa Boucheneb, for encouraging me and supporting me without hesitation throughout my studies. Her dedication to my research and unwavering guidance has been incredibly helpful and inspiring – words cannot express my appreciation for Dr. Boucheneb's efforts.

While the destination is grand, I would be nowhere without the journey to get here. This journey with my colleagues at Ecole Polytechnique de Montreal has provided me with lifetime experiences, and has set me up for a prosperous future. I would like to thank the Department of Computer and Software Engineering for affording me the opportunity to learn and grow with the best.

I would like to thank the committee members, Professor Martine Bellaiche, Professor Gabriela Nicolescu, and Professor Jamal Bentahar, for their attention and dedication of their time to evaluate my research work. I would like to thank my colleagues at VeriForm Laboratory, especially Parisa Heidari and Aurel Randolph. I would also like to thank Daniel Wolfe, my manager at IsaiX Technologies Inc. for his support throughout this process.

Lastly, but certainly not least, I would like to thank my "inner circle" support system : my family. My amazing wife, Baharafarin, for her incredible patience and huge sacrifice – this has been a tiresome journey for her as much as it has been for me. My mother-in-law and father-in-law, Maryam RezaiTabar and Hossein Esbati, who have experienced this journey with my wife and I, and have been so helpful in raising our children and taking care of our household. My parents, for always encouraging me to be the best I can be, and pursue the highest level of education. And of course, my children, Daniel and Diana, for being understanding when their "Baba" didn't have time to play, and had to work on his thesis.

#### RÉSUMÉ

Les logiciels jouent un rôle de plus en plus important dans les systèmes embarqués notamment dans les domaines de la santé, de l'automobile et de l'avionique. Un objectif important du génie logiciel est d'offrir, aux développeurs, un support ainsi que les outils d'aide à la conception de systèmes fiables nonobstant leur complexité.

Dans le but d'atteindre cet objectif, des environnements de développement comme Simulink et SCADE proposent un processus de développement, basé sur des modèles, qui intègre, d'une manière réfléchie, différentes approches et outils de vérification (test, simulation, vérification formelle, évaluation, génération de code, etc). Ils permettent ainsi de concevoir, tester, simuler, vérifier, corriger des modèles puis de générer automatiquement du code à partir de ces modèles.

Cette thèse s'intéresse aux méthodes formelles et à l'intégration de celles-ci dans l'environnement de développement Simulink. Les méthodes formelles s'appuient sur des outils mathématiques pour spécifier, par des modèles, le comportement et les propriétés d'un système et prouver qu'il satisfait ses requis. Simulink-Design-Verifier (SLDV) est un outil de vérification formelle, intégré à l'environnement de développement Simulink, qui permet de vérifier des propriétés de sûreté (assertions) sur des modèles Simulink. Cette thèse vise à étendre cette classe de propriétés à des propriétés linéaires LTL (Linear Temporal Logic), LTL temporisé et LTL à base d'événements. Les contributions de cette thèse sont présentées sous forme de trois articles.

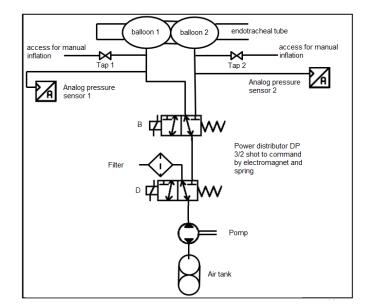

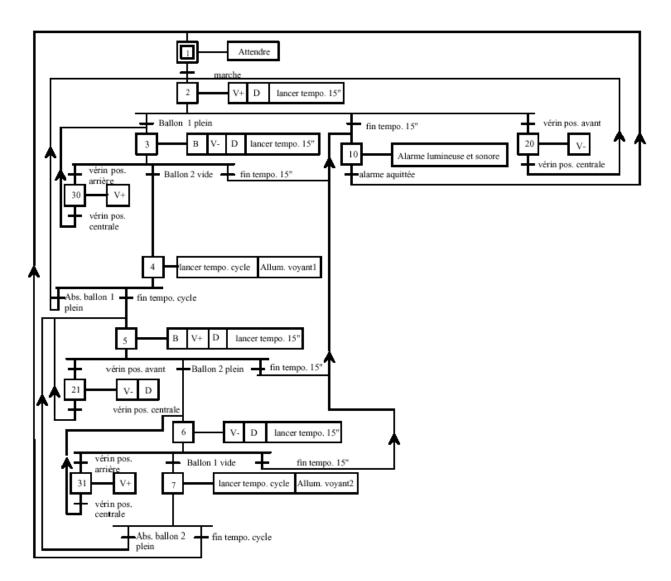

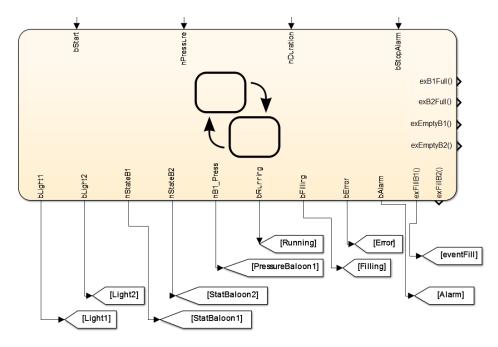

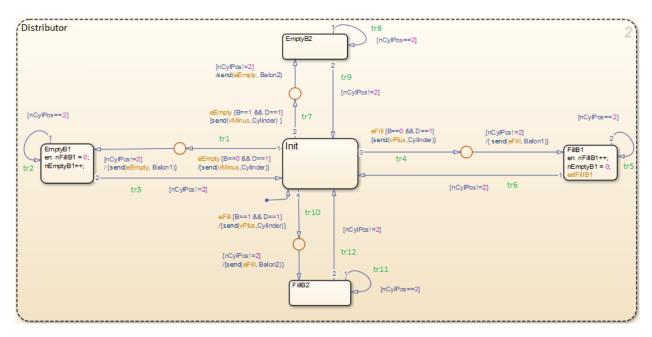

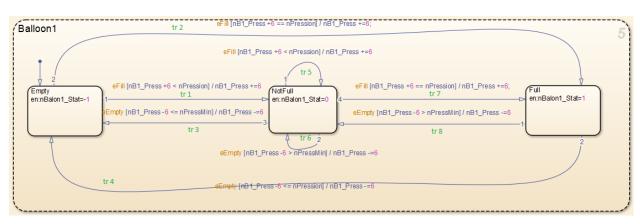

Le premier article présente une étude de cas qui a permis d'expérimenter l'environnement de développement Simulink, d'identifier ses caractéristiques et ses limitations. Il s'agit de modéliser et vérifier un dispositif médical appelé sonde d'intubation. Une sonde d'intubation est une tubulure mise en place sur un sujet inconscient qui permet notamment d'assurer en permanence le passage de l'air vers les poumons. Ce système est composé de deux ballonnets, deux robinets d'accès pour gonflage manuel, deux capteurs de pression, un distributeur de puissance, une pompe et un réservoir d'air. Tous ces composants sont concurrents et contrôlés par contrôleur programmable décrit par un grafcet. Cet article montre comment utiliser l'environnement Simulink pour, d'une part, modéliser ces différents composants ainsi que leurs interactions, et d'autre part, vérifier formellement des propriétés, afin de s'assurer du bon fonctionnement du système. Cependant, la spécification de certaines propriétés temporelles n'est pas évidente car elles doivent être exprimées sous forme d'assertions. Les articles suivants proposent des blocks canevas pour des propriétés temporelles linéaires. Le deuxième article est une version améliorée et étendue du premier article. Il s'est intéressé à réduire la complexité de vérification en modifiant significative le modèle et en proposant des blocks de spécification de propriétés linéaires basées sur les événements émis par le contrôleur.

Le troisième article est dédié à la spécification de propriétés LTL en utilisant SLDV. Il propose des blocs Simulink configurables qui spécifient ces propriétés. Le but de ces blocs est de transformer les propriétés en assertions qui sont vérifiables par SLDV.

La solution proposée dans le seconde et troisième article, est donc une extension de la bibliothèque de blocs de Simulink qui permet aux utilisateurs moins experts de spécifier et vérifier certaines propriétés LTL.

Ce travail est donc limité aux propriétés LTL à temps discret, et restreint à certaines propriétés LTL. Nos travaux futurs consisteraient à l'extension de la bibliothèque de blocs de Simulink pour supporter des propriétés LTL plus complexes et à plus grande échelle.

#### ABSTRACT

Software plays increasingly a significant role in embedded systems particularly used in healthcare, automotive and avionics. An important goal of software engineering is to offer developers support tools to design reliable systems despite the system complexity.

In order to achieve this, development environments like Simulink and SCADE propose a model-based development process, which integrates in a thoughtful way, different approaches and verification tools (test, simulation, formal verification, evaluation, code generation, etc.). They allow to design, test, simulate, verify, correct the models and then automatically generate code from these models.

This thesis is interested in formal methods and integrating them in the Simulink development environment. Formal methods are based on mathematical tools to specify the behavior and properties of a system by models, and prove, if it meets its requirements. Simulink Design Verifier (SLDV) is a formal verification tool, integrated in Simulink development environment, to verify safety properties (assertions) on Simulink models. This thesis aims to extend this class of properties to linear properties LTL (Linear Temporal Logic), timed LTL and event based LTL. The contributions of this thesis are presented in three articles.

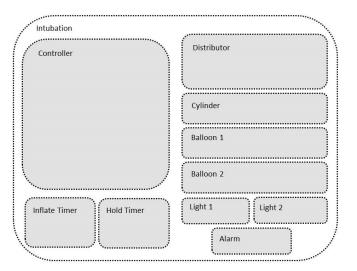

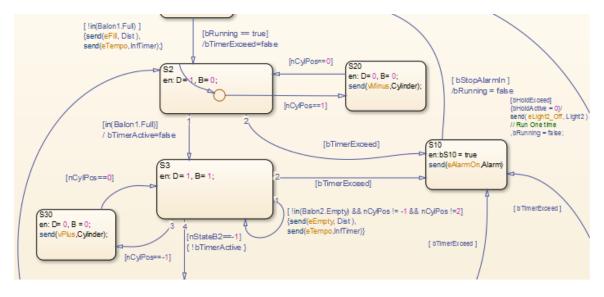

The first article presents a case study that experiment the Simulink development environment, to identify its characteristics and limitations. It consists of modeling and verifying a medical device called intubation tube. An intubation tube is a tube that assures permanent air flow to the lungs of unconscious person. This system consists of two balloons, two access valves for manual inflation, two pressure sensors, a power distributor, a pump and an air reservoir. All these components work in parallel and are controlled by a programmable controller described by grafcet. This article shows how to use the Simulink environment, to model these components and also how to verify formally the properties to ensure the system is well functioning. However, the specification of certain temporal properties is not obvious because they must be expressed as assertions. The following articles propose canvas blocks for linear temporal properties.

The second article is an improved and extended version of the first article. It is interested in reducing verification complexity by changing significantly the model, and proposing specification blocks of linear properties, based on events issued by the controller.

The third article is dedicated to the specification of LTL properties using SLDV. It proposes configurable Simulink blocks that specify these properties. The purpose of these blocks is to transform the properties into assertions that are verifiable by SLDV.

The solution proposed in the second and third articles, is to extend the block library of Similink, which allows less-expert users to specify and verify some Linear Temporal Logic (LTL) properties.

This work is limited to discrete time LTL properties, and restricted to specify some LTL properties. Our future work is devoted to extend the block library of Simulink to have support for a large scale and more complex LTL properties.

## TABLE OF CONTENTS

| DEDIC  | ATION          | 'i                              | iii |

|--------|----------------|---------------------------------|-----|

| ACKNO  | OWLED          | DGEMENTS                        | iv  |

| RÉSUM  | ſÉ             |                                 | v   |

| ABSTR  | ACT            |                                 | vii |

| TABLE  | OF CO          | ONTENTS i                       | ix  |

| LIST O | F TAB          | LES                             | iii |

| LIST O | F FIGU         | JRES xi                         | iv  |

| LIST O | F SIGN         | IS AND ABREVIATIONS             | vi  |

| LIST O | F APP          | ENDIX                           | iii |

| СНАРЛ  | TER 1          | INTRODUCTION                    | 1   |

| 1.1    | Definit        | tions and Basic Concepts        | 1   |

|        | 1.1.1          | Software Development Process    | 2   |

| 1.2    | Proble         |                                 | 3   |

| 1.3    |                |                                 | 4   |

| 1.4    |                |                                 | 5   |

| СНАРЛ  | TER 2          | LITERATURE REVIEW               | 6   |

| 2.1    | Model          | ing Concepts                    | 6   |

|        | 2.1.1          |                                 | 6   |

|        | 2.1.2          |                                 | 7   |

| 2.2    |                | ation and Validation Techniques | 7   |

|        | 2.2.1          | -                               | 8   |

|        | 2.2.2          |                                 | 9   |

|        | 2.2.3          |                                 | 10  |

| 2.3    |                |                                 | 11  |

| 2.0    | 2.3.1          |                                 | 12  |

|        | 2.3.1<br>2.3.2 |                                 | 12  |

|        |                |                                 |     |

|       | 2.3.3    | Simulink Library                                                                                                                                                   |

|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 2.3.4    | Constant, Inport and Outport blocks                                                                                                                                |

|       | 2.3.5    | Sum block                                                                                                                                                          |

|       | 2.3.6    | Unit Delay block                                                                                                                                                   |

|       | 2.3.7    | Relational Operator block                                                                                                                                          |

|       | 2.3.8    | Logical Operator block                                                                                                                                             |

|       | 2.3.9    | Embedded MATLAB Function block                                                                                                                                     |

|       | 2.3.10   | Subsystem block                                                                                                                                                    |

|       | 2.3.11   | Function-Call Subsystem block                                                                                                                                      |

|       | 2.3.12   | Simulink Block Methods                                                                                                                                             |

|       | 2.3.13   | Simulink Semantics                                                                                                                                                 |

|       | 2.3.14   | Simulink Block Priorities                                                                                                                                          |

|       | 2.3.15   | Stateflow                                                                                                                                                          |

| 2.4   | Verific  | ation Tools $\ldots$ $\ldots$ $\ldots$ $18$                                                                                                                        |

|       | 2.4.1    | SCADE Design Verifier                                                                                                                                              |

|       | 2.4.2    | Simulink Design Verifier                                                                                                                                           |

| 2.5   | Forma    | l Verification of Simulink Models                                                                                                                                  |

|       | 2.5.1    | Approach based on other Model Checking Tools                                                                                                                       |

|       | 2.5.2    | Approach based on Simulink Design Verifier                                                                                                                         |

| 2.6   | Conclu   | 1sion                                                                                                                                                              |

|       | פ חחר    |                                                                                                                                                                    |

| СНАРЛ |          | ARTICLE 1                                                                                                                                                          |

|       |          | ormal Methods into Safety-Critical Health Applications                                                                                                             |

| 3.1   |          | uction $\dots \dots \dots$                                         |

| 3.2   | 0        | $\begin{array}{c} \text{cound and Related Work} \dots \dots$ |

| 3.3   |          | nk and Stateflow                                                                                                                                                   |

| 3.4   |          | 29                                                                                                                                                                 |

| 25    | 3.4.1    | The model                                                                                                                                                          |

| 3.5   |          | s and Analysis                                                                                                                                                     |

| 0.0   | 3.5.1    | Properties                                                                                                                                                         |

| 3.6   | Conclu   | usion                                                                                                                                                              |

| СНАРТ | TER 4    | ARTICLE 2                                                                                                                                                          |

| Form  | nal Veri | fication of Event-driven Health Applications                                                                                                                       |

| 4.1   |          | uction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $40$                                                                                                           |

| 4.2   | Backgr   | cound and Related Work                                                                                                                                             |

| 4.3   |          | nk and Stateflow                                                                                                                                                   |

|       | 4.3.1   | Simulink Library                                                                                                                                    | 15         |

|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|       | 4.3.2   | Simulink Design Verifier                                                                                                                            | 16         |

| 4.4   | Case S  | Study                                                                                                                                               | 17         |

|       | 4.4.1   | The model                                                                                                                                           | 18         |

| 4.5   | Metho   | ods and Analysis                                                                                                                                    | 57         |

|       | 4.5.1   | Properties                                                                                                                                          | 68         |

|       | 4.5.2   | Verification                                                                                                                                        | 37         |

| 4.6   | Conclu  | usion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                              | 67         |

| СНАРТ | TER 5   | ARTICLE 3                                                                                                                                           |            |

| Usin  | g Desig | gn Verifier for Proving some LTL Properties 6                                                                                                       | <b>5</b> 9 |

| 5.1   | Introd  | uction                                                                                                                                              | <b>5</b> 9 |

| 5.2   | Backg   | round And Related Work                                                                                                                              | 70         |

|       | 5.2.1   | Model-Based Design                                                                                                                                  | 70         |

|       | 5.2.2   | Formal Methods                                                                                                                                      | 71         |

|       | 5.2.3   | Formal Verification                                                                                                                                 | 71         |

|       | 5.2.4   | Related Work                                                                                                                                        | 72         |

| 5.3   | Tempo   | pral Logic                                                                                                                                          | 73         |

|       | 5.3.1   | Linear Temporal Logic                                                                                                                               | 73         |

| 5.4   | Simuli  | ink and Stateflow                                                                                                                                   | 75         |

|       | 5.4.1   | Simulink                                                                                                                                            | 75         |

|       | 5.4.2   | Stateflow                                                                                                                                           | 78         |

|       | 5.4.3   | Simulink Design Verifier                                                                                                                            | 80         |

| 5.5   | Impler  | mentation $\ldots$                                                 | 31         |

|       | 5.5.1   | Understanding Simulink Model                                                                                                                        | 82         |

|       | 5.5.2   | Property Specifying Process                                                                                                                         | 33         |

|       | 5.5.3   | Definition of Properties                                                                                                                            | 35         |

| 5.6   | Evalua  | $ation \ldots \ldots$        | 96         |

|       | 5.6.1   | Case Study                                                                                                                                          | 97         |

|       | 5.6.2   | Verification $\ldots \ldots \ldots$ | )()        |

| 5.7   | Conclu  | usion                                                                                                                                               | )()        |

| СНАРТ |         | GENERAL DISCUSSION                                                                                                                                  | )2         |

| 6.1   |         | esis of work $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $10$                                                           | 12         |

| 6.2   | Analys  | sis of the achievements                                                                                                                             | )4         |

| СНАРТ | TER 7   | CONCLUSION AND RECOMMENDATIONS                                                                                                                      | )6         |

| 7.1   | Summary of work                      | 106 |

|-------|--------------------------------------|-----|

| 7.2   | Limitations of the proposed solution | 107 |

| 7.3   | Future Work                          | 107 |

| REFER | ENCES                                | 109 |

| APPEN | IDIX                                 | 114 |

## LIST OF TABLES

| Table 2.1 | The supported operations                                               | 15  |

|-----------|------------------------------------------------------------------------|-----|

| Table 3.1 | Variables in Intubation Stateflow                                      | 32  |

| Table 3.2 | Events                                                                 | 32  |

| Table 3.3 | Actions                                                                | 34  |

| Table 4.1 | Variables in Intubation Stateflow                                      | 51  |

| Table 4.2 | Events                                                                 | 51  |

| Table 4.3 | Actions                                                                | 53  |

| Table 4.4 | Distributor - Evolution of states and status of events over the time . | 56  |

| Table 4.5 | Evolution of variables over the time - Cylinder at rear                | 62  |

| Table 4.6 | Evolution of variables over the time - Cylinder at center $\ldots$ .   | 62  |

| Table 4.7 | Verification results                                                   | 68  |

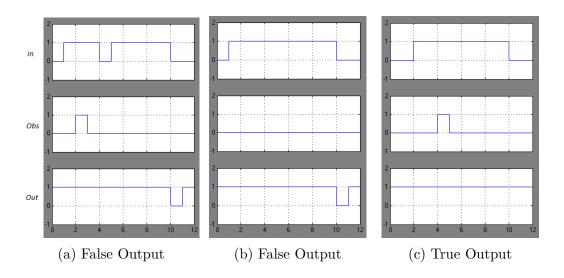

| Table 5.1 | Evolution of signal values over the time - $\diamond_{[0,5]}p$         | 91  |

| Table 5.2 | Evolution of block outputs over the time - $\diamond_{[0,5]}p$         | 91  |

| Table 5.3 | Evolution of variables over the time - $p \ U \ q$                     | 94  |

| Table 5.4 | $p \ U_{[0,5]} \ q$ - Evolution of variables over the time             | 97  |

| Table 5.5 | Verification results                                                   | 101 |

|           |                                                                        |     |

## LIST OF FIGURES

| Figure 1.1  | V-Shaped Life Cycle Model [69]                                                   | 3  |

|-------------|----------------------------------------------------------------------------------|----|

| Figure 2.1  | Model-based Design used in development of real applications                      | 8  |

| Figure 2.2  | High-level overview of BMC                                                       | 11 |

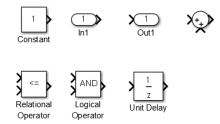

| Figure 2.3  | Sample Simulink Model                                                            | 12 |

| Figure 2.4  | Source and Sinks blocks                                                          | 13 |

| Figure 2.5  | Sum block                                                                        | 14 |

| Figure 2.6  | Unit Delay                                                                       | 14 |

| Figure 2.7  | Relational Operators                                                             | 14 |

| Figure 2.8  | Logical Operators                                                                | 15 |

| Figure 2.9  | MATLAB Function                                                                  | 15 |

| Figure 2.10 | Sum block with ports and functions at time $t$                                   | 17 |

| Figure 3.1  | Endotracheal intubation                                                          | 26 |

| Figure 3.2  | Stateflow Semantics                                                              | 29 |

| Figure 3.3  | Components of the Endotracheal Intubation $\ldots \ldots \ldots \ldots \ldots$   | 31 |

| Figure 3.4  | Part of Controller State                                                         | 33 |

| Figure 3.5  | Pressure distributor                                                             | 35 |

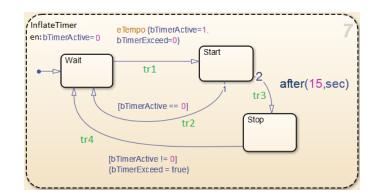

| Figure 3.6  | Timer State                                                                      | 35 |

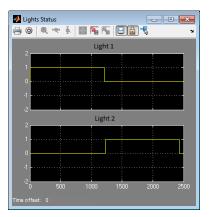

| Figure 3.7  | Lights status                                                                    | 36 |

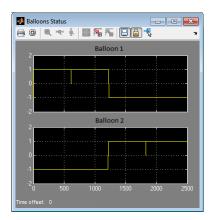

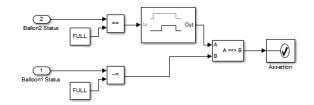

| Figure 3.8  | Balloons status                                                                  | 36 |

| Figure 3.9  | Formalization of property I                                                      | 37 |

| Figure 4.1  | Endotracheal intubation $[8]$                                                    | 41 |

| Figure 4.2  | Stateflow Semantics                                                              | 44 |

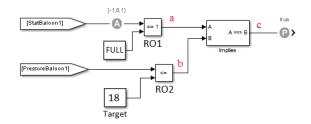

| Figure 4.3  | Within Implies Simulink Block                                                    | 47 |

| Figure 4.4  | Physical Features of the control system                                          | 48 |

| Figure 4.5  | Grafcet describing the operation of the controller $\ldots \ldots \ldots \ldots$ | 49 |

| Figure 4.6  | Components of the Endotracheal Intubation                                        | 50 |

| Figure 4.7  | Intubation Stateflow with its I/O                                                | 52 |

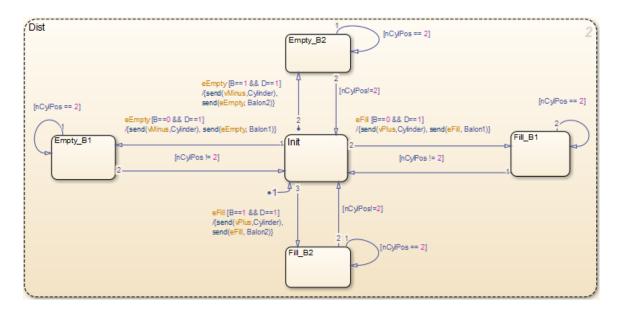

| Figure 4.8  | Pressure distributor                                                             | 54 |

| Figure 4.9  | Stateflow of Balloon1                                                            | 55 |

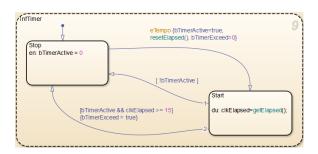

| Figure 4.10 | Inflate/Deflate Timer State                                                      | 57 |

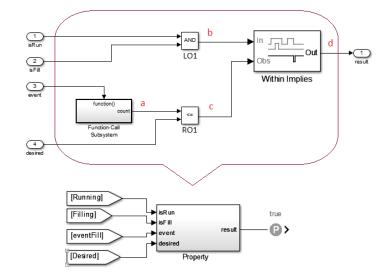

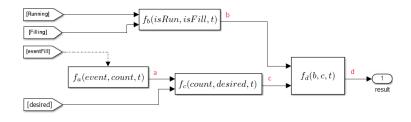

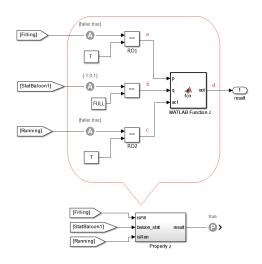

| Figure 4.11 | Formalization of property 1                                                      | 59 |

| Figure 4.12 | Internal functions in property 1                                                 | 59 |

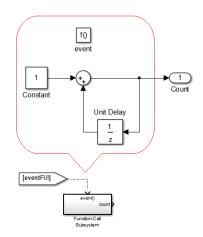

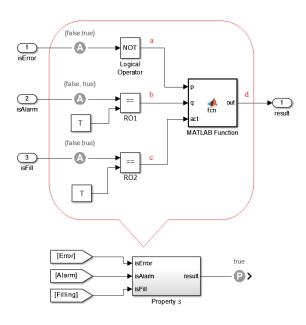

| Figure 4.13 | Using Standard Simulink Block                                                    | 62 |

| Figure 4.14 | Function-call Subsystem Block                                                                                                                          | 63  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.15 | Property 2                                                                                                                                             | 63  |

| Figure 4.16 | Internal functions in property $2 \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                      | 64  |

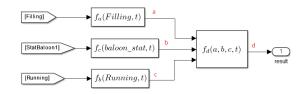

| Figure 4.17 | Property 3                                                                                                                                             | 65  |

| Figure 4.18 | Property 4                                                                                                                                             | 66  |

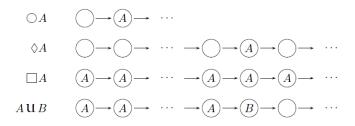

| Figure 5.1  | Semantics of Temporal Operators                                                                                                                        | 75  |

| Figure 5.2  | Simulink sample blocks                                                                                                                                 | 76  |

| Figure 5.3  | Simulink blocks with ports and functions at time $t$                                                                                                   | 77  |

| Figure 5.4  | Stateflow Semantics                                                                                                                                    | 79  |

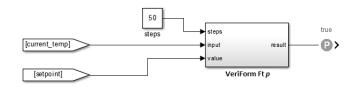

| Figure 5.5  | Within Implies Simulink Block                                                                                                                          | 81  |

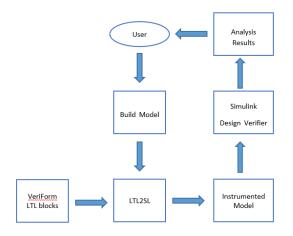

| Figure 5.6  | Life cycle of the entire process                                                                                                                       | 82  |

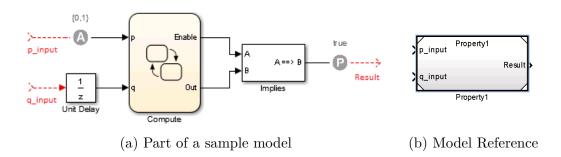

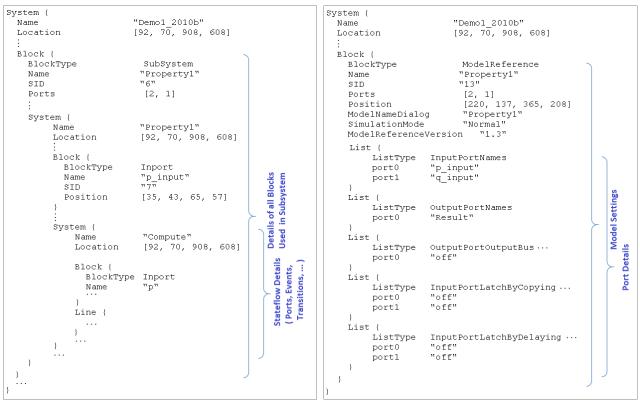

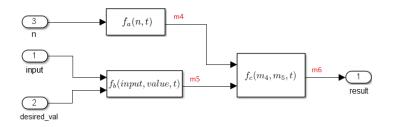

| Figure 5.7  | Sample Simulink Model                                                                                                                                  | 83  |

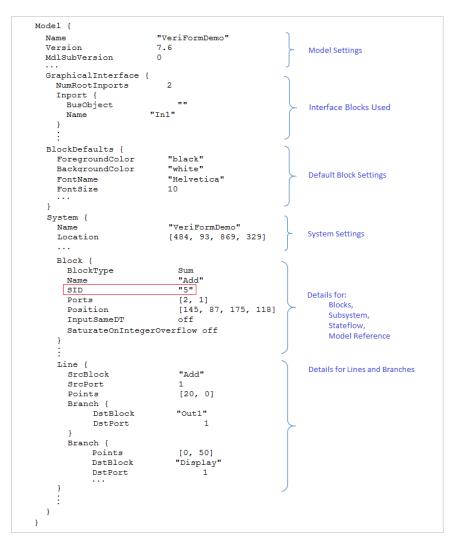

| Figure 5.8  | Simulink Model File Format                                                                                                                             | 84  |

| Figure 5.9  | Converting group of blocks to a Model Reference                                                                                                        | 85  |

| Figure 5.10 | The difference between Subsystem and Model Reference                                                                                                   | 86  |

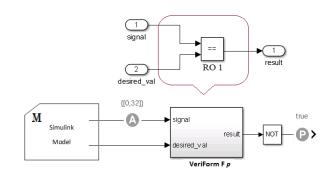

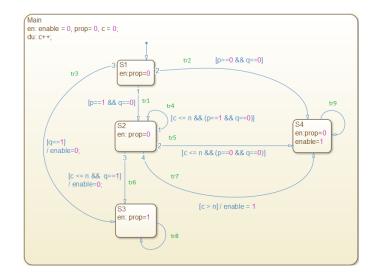

| Figure 5.11 | LTL $F p$                                                                                                                                              | 87  |

| Figure 5.12 | LTL $F_{[0,n]} p$                                                                                                                                      | 89  |

| Figure 5.13 | Internal functions in $F_{[0,n]} p$                                                                                                                    | 89  |

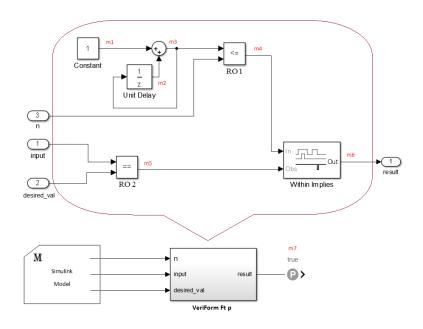

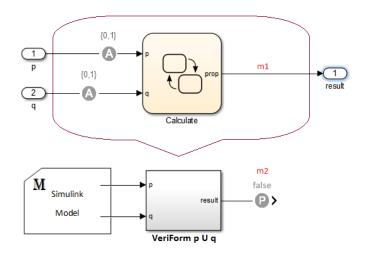

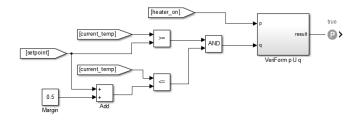

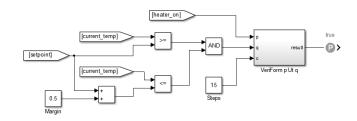

| Figure 5.14 | LTL $p \ U \ q$                                                                                                                                        | 92  |

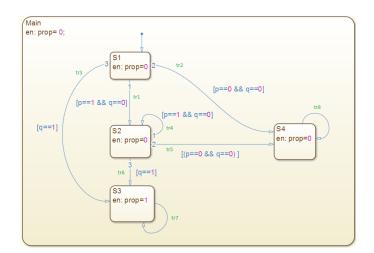

| Figure 5.15 | Stateflow in $p \ U \ q \ldots \ldots$ | 92  |

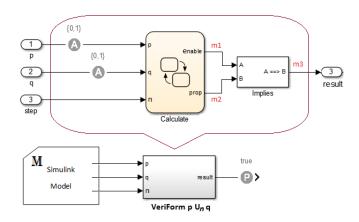

| Figure 5.16 | LTL $p U_{[0,n]} q$ Property                                                                                                                           | 94  |

| Figure 5.17 | Stateflow in $p U_{[0,n]} q \ldots \ldots$                         | 95  |

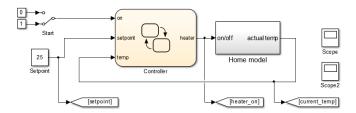

| Figure 5.18 | Home Heating System                                                                                                                                    | 97  |

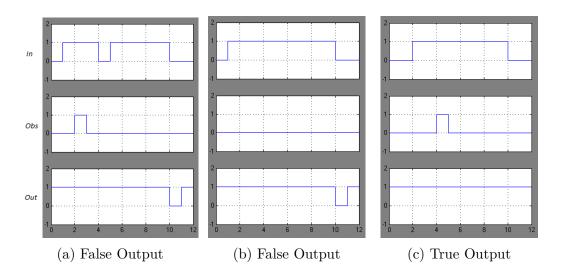

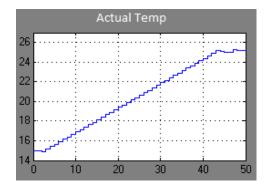

| Figure 5.19 | Simulation: Home Heating System                                                                                                                        | 98  |

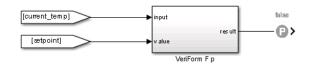

| Figure 5.20 | Requirement 1                                                                                                                                          | 99  |

| Figure 5.21 | Requirement 2                                                                                                                                          | 99  |

| Figure 5.22 | Requirement 3                                                                                                                                          | 100 |

| Figure 5.23 | Requirement 4                                                                                                                                          | 100 |

## LIST OF SIGNS AND ABREVIATIONS

| ABS            | Antilock Break System                               |

|----------------|-----------------------------------------------------|

| BDD            | Binary Decision Diagram                             |

| BMC            | Bounded Model Checking                              |

| CTL            | Computation Tree Logic                              |

| DAL            | Design Assurance Level                              |

| FCA            | Formal Concept Analysis                             |

| $\mathbf{FM}$  | Formal Methods                                      |

| FMTS           | Formal Methods Technical Supplement                 |

| FSM            | Finite-State Machine                                |

| $\mathrm{FV}$  | Formal Verification                                 |

| HLR            | High Level Requirements                             |

| IEEE           | Institute of Electrical and Electronics Engineers   |

| LLR            | Low Level Requirements                              |

| LTL            | Linear Temporal Logic                               |

| MAAB           | MathWorks Automotive Advisory Board                 |

| MC/DC          | Modified Condition/Decision Coverage                |

| MBD            | Model-based Design                                  |

| MDD            | Model Driven Development                            |

| NASA           | National Aeronautics and Space Administration       |

| OBDD           | Ordered Binary Decision Diagrams                    |

| PIL            | processor-in-the-loop                               |

| PVS            | Prototype Verification System                       |

| ROBDD          | Reduced Ordered Binary Decision Diagrams            |

| SAT            | Satisfiability                                      |

| $\mathbf{SC}$  | Software Consideration                              |

| SCADE          | Safety-Critical Application Development Environment |

| SDLC           | Software Development Life Cycle                     |

| SDP            | Software Development Process                        |

| SG             | Sub Group                                           |

| SIL            | software-in-the-loop                                |

| SLDV           | Simulink Design Verifier                            |

| SMT            | Satisfiability Modulo Theories                      |

| $\mathrm{SMV}$ | Symbolic Model Verifier                             |

|                |                                                     |

| SSM   | Safe State Machine         |

|-------|----------------------------|

| SysML | System Modelling Language  |

| TAF   | Test Automation Framework  |

| TCG   | Test Case Generation       |

| TDD   | Task Design Document       |

| UML   | Unified Modelling Language |

## LIST OF APPENDIX

| Appendix A | Within Implies Code      | 114 |

|------------|--------------------------|-----|

| Appendix B | Embedded Matlab Function | 115 |

#### CHAPTER 1 INTRODUCTION

Software plays an important role in almost every part of our everyday life from working in the office and driving the car to navigation systems in the aircraft. Over the last decades, reliability of complex software and hardware systems became increasingly crucial. Consequently, software verification of such systems, has been a significant problem in computer science for several years. Software failure could possibly cause catastrophic consequences regarding human life. In addition, a system is identified as *safety-critical*, when its failure causes catastrophic consequences, such as compromising the human life or even destruction to the system itself. Moreover, in the safety-related real-time system, verification and validation activities are becoming larger and more costly whenever its size and complexity grows.

A key objectives of software engineering is to support developers building a system that functions reliably even if it is complex. In order to attain this goal, formal methods are advised to be employed. To clarify, these methods are mathematically based techniques, and each tool has it own supported language. The use of formal methods has been addressed in DO-178B<sup>1</sup> and can significantly increase the knowledge of developers about the system [43]. In addition, formal methods disclose inconsistencies as well as ambiguities in the early phase of system design phase. As a result, they can be eliminated in order to make sure that the system has a suitable behavior.

Applying Model-Based Design [33] in safety-related applications and using formal verification, illustrates that the system fulfils its correctness criteria. For performing formal verification, the first need is to specify a formal model of the system. In addition, availability of executable models to perform verification, validation and test is one of the most effective factors of model-based design that helps one to apply formal verification techniques.

#### 1.1 Definitions and Basic Concepts

In this section, we introduce some concepts related to the software development process and its enhancements. These concepts are the base and will be used in the process of applying formal method techniques into development life-cycle of software for the safetycritical embedded systems.

<sup>1.</sup> DO-178B is a standard for certification of software used in airborne systems

#### **1.1.1** Software Development Process

The Software Development Process (SDP) sometimes is mentioned as Software Development Life Cycle (SDLC). In fact, it is a structure which is required for the development of software product. Moreover, it is a step-by-step process involved in the development of a software product as well as altering software systems, methodologies and models which people employ for developing these systems. Over the past years, efforts to enhance SDLC practices have been presented for improving the quality of software, reliability, and fault-tolerance. In addition, various software life cycle models exist which they describe different phases of the software development cycle as well as the order in which those phases are implemented. Furthermore, some companies have their own, but all models have very similar patterns which are just customized in purpose. Each model has its advantages and disadvantages, and it is up to the company's development team to use the most suitable one for the project.

In the following, we briefly describe some process models that are used for developing the safety-critical systems.

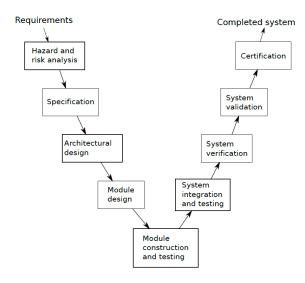

#### V-Shaped Model

The typical process of developing a safety-critical system is based on the V-Shaped lifecycle model [14]. This model is highly disciplined and it is also an extended version of the waterfall model which processes are executed in a sequential path. In addition, it is based on association of a testing phase for each matching development phase. Moreover, a system test plan is produced before the development phase is started. In this model, each phase in the cycle has a particular deliverables and should be verified in the same phase. In other words, the next phase of the development cycle starts only if the previous phase is successfully completed. Figure 1.1, illustrated the V-Shaped model.

#### Formal Methods Model

The formal methods model includes a set of activities that advances to the formal mathematical specification of software system [62]. If formal methods are employed during the software development, many of problems that are hard to find can be identified and eliminated by its provided mechanism. In particular, mathematical analysis helps easily to discover Ambiguity, inconsistency and incompleteness in the software system, so that they can be corrected early in the development. In other words, by using formal methods during the design phase, they assist as a basis for software verification, and consequently allows developers to identify and fix errors that might be otherwise go undetected. Several notations are available for

Figure 1.1 V-Shaped Life Cycle Model [69]

formalizing the software specifications. In general, the automata theory is the one that can be employed to design a system in finite state machines, in order to build and validate its behavior. When the software is used in the safety-critical system like avionics systems, it is recommended that formal methods be applied. Standards for safety assurance of software, like DO178B [43] request formal methods at the highest level of classification (Level A).

#### 1.2 Problem Statement

The growth in sophistication in embedded systems used in safety-critical applications such as automotive, healthcare and avionics, necessitates to use more efficient processes for design and development. Ordinary design processes are not responsive enough in identifying the flaws in requirements; thus, the whole process would be more costly and take longer.

Even a sole error in the source code may cause the failure of the system. In a safety critical system, this failure can impose high costs and might even have the risk for the health of people. Imagine the Antilock Break System (ABS) in the car, navigation systems in an air plane or medical devices in the hospital operation room. For such safety-critical systems, availability of robust guidelines for software, have remarkable value for developers of these systems. In fact, guidelines should outline processes, artifacts and goals for the development of software that focuses on the quality.

In particular, support to build a system which functions reliably irrespective of its complexity, is a key objective of software engineering. Moreover, run-time errors that are not identified during the development phase of the software, might be serious. In addition, all commercial software which are designed and developed for avionics in the U.S., are requested to comply with the DO-178 standard. The guidelines defined in DO-178 are projected to determine that developers of avionics systems employ a particular degree of process rigor. In fact, development and verification must follow a rigorous process to ensure that the software will perform its anticipated function with a suitable level of confidence in safety.

One of the ways to succeed this goal, is applying formal methods techniques, and tools to the software development life-cycle for specifying and verifying properties in such systems. Moreover, different levels of rigor or formality can be adopted, and different formal methods techniques can be used as well, to address the tasks in software development.

Although there are several cases proving the applicability of formal methods in the high complexity domains as well as industrial applications, they use more complex notations than other lightweight and intuitive graphical notations (e.g., Unified Modeling Language (UML)). So, creating a mathematical model of a system as well as specifying the functional requirements are not easy and could be mentioned as one of the important concerns to software producers. In addition, model checking technique might cause the state space explosion for large or complex systems. Moreover, the absence of easy to use tools that can assist the developers during the life cycle activities, could be another case. In addition to this, formal verification requires specific environment. Matlab/Simulink is an often used industrial tool in designing embedded systems. One of the primary uses of Matlab/Simulink is modeling the embedded software and its physical environment in a common formalism. This feature of the tool renders it highly valuable in the validation of embedded software design, leveraging numerical simulation. Having claimed this, formal verification of such models still proves problematic, as Simulink is a programming language without enough documented formal semantics. Furthermore, currently verification tools which have supports for DO-178C standard (e.g., SCADE Design Verifier and Simulink Design Verifier), does not support formal verification of continuous time systems.

#### 1.3 Research Objectives

According to previously mentioned problems and obstacles, tremendous amount of effort is needed in order to have complete system verification acquiring the highest level of safety. In this chapter, we explain our objectives as well as the methodology to achieve those objectives. One of the main goals of this thesis is to address the essential problems for early detection of errors, in complex and safety critical applications, whereby facilitate the research in this area for developing and maintain a high-integrity application which comply with DO-178 [43] objectives for certification. We summarize the detailed objectives of our research as the following items:

- To improve verification of critical systems we use Simulink and we add some customizable blocks into the Simulink library and make the formalization of the requirement specifications easier.

- Introducing a tool that facilitates instrumenting Simulink models by automatically adding some predefined and customizable properties to the model.

- Specifying some critical properties that are not easy to become formalized in Simulink.

- Investigation of applying verification for some LTL properties in Simulink Design Verifier.

### 1.4 Thesis Structure

The rest of this document is organized as follows: Chapter 2 presents a critical review on methods and environments for verification of safety critical systems. In particular, in this chapter, we review verification techniques and some available tools, and introduce Simulink Design Verifier which is qualified for development of safety-critical systems.

The next three chapters are articles that deal with formalization and verification of some safety and (timed) linear properties that are modeled in the Matlab/Simulink environment.

The first article, whose title is Applying Formal Methods into Safety-Critical Health Applications, is dedicated to the result of our studies for modeling and formalizing the requirements of an embedded system in the Simulink and Stateflow environment. We bring an introduction about the tool, its library of blocks and Stateflow as well. This article is the subject of the chapter 3, and is published in Model-Based Safety and Assessment, Lecture Notes in Computer Science (LNCS).

Chapter 4 entitled *Formal Verification of Event-driven Health Applications*, is an article which is published in the *Journal of Software Engineering: Theories and Practices*. It focuses on applying formal verification for an event-driven safety-critical system. This extends the previous work by proposing a technique for verification of temporal properties in a system which is modeled with Stateflow and issues some of external events.

In chapter 5, we propose a technique to facilitate formalizing some LTL properties which can be added to the Simulink block library. This chapter also presents the LTL2SL tool that helps the instrumentation of Simulink models with predefined properties.

Finally, chapters 6 and 7 discuss the techniques proposed in previous chapters, the general results, and possible avenues for future work.

#### CHAPTER 2 LITERATURE REVIEW

The following chapter puts forth a review of different development environments for safetycritical systems and corresponding development process such as advanced formal verification techniques and tools. We first explain the basic concepts and verification techniques in a categorized format, including modeling concepts and different model checking approaches. The remainder of the chapter will consist of the following: Introducing Simulink tool suit and its block library that the thesis is based on it, followed by describing two different formal verification tools and approaches.

#### 2.1 Modeling Concepts

In order to apply formal methods into development process of safety critical applications, there is a need to construct a formal model of such systems. In addition, development tools in safety critical domain offer a design environment for modeling the system. Following this section modeling concepts are briefly described.

#### 2.1.1 Software Modeling

A model is generally identified as the abstract demonstration of a system. Software modeling is one of the ways to express the software design. To address this, some sort of abstract languages or images are typically used. In addition, the whole software design comprising all software methods, its interactions with other software and interfaces needs to be dealt in software modeling [34]. As such, the system can be modeled by developers with the help of a modeling language which can be textual or graphical [39]. As an illustration, UML which is an object modeling language and can be used to express the software design for an object-oriented language [35].

In addition, System Modeling Language (SysML) [7] is another multi-use modeling language for engineering applications. It is actually a domain specific language which is firstly developed by an open-source specification project for defining the specifications, applying the analysis, design and verification of wide collection of systems.

Since simulation is the execution of a model, by using models at the core of the development process and performing simulation, developers have an intuition into the dynamics and algorithmic characteristics of the system [56].

#### 2.1.2 Model-based Design

Model-based design can be used to facilitate the addressing of difficulties as well as complexities in a control system design. It actually provides an executable specification that indicates the model acts as a functional part of the design process rather than being just a document [54]. It empowers developers to use a single model of their entire system by providing a design environment. In addition, the constructed model can be visualized, analyzed, tested, validated and eventually deployed through the design environment [46]. Additionally, model-based design produces a structure for the software reuse. In particular, it enables that designs being efficiently and dependably upgraded in a more simplistic and cost effective way.

Model-based design as well as automated code generation, are being used gradually at National Aeronautics and Space Administration (NASA) [28]. That is because this kind of design offers several benefits such as higher productivity, increased portability, and elimination of errors that might be caused by manual coding. In addition, MathWorks Simulink<sup>(R)</sup> [6] and Simulink Coder<sup>TM</sup>[4] which formerly known as Real-Time Workshop are currently being used by NASA for some part of their modeling and code development [29].

To put it differently, this type of design emphases on using executable system models as the basis for all phases such as specification, design, implementation, test, as well as the verification behboodian2006model. Some parts or all the system specification and requirements in the paper format can be replaced by the executable specification in Model-based design as the main deliverables among design stages. It also contains of an executable model of the application logic that can be simulated. The model elaboration is the next step in the Model-Based Design. In fact, it comprises of some actions to transform the executable specification into a more design based form [60].

The executable model can be built by Simulink<sup>®</sup> which is a tool that provides an environment for Model-based Design as well as the simulation for dynamic and embedded systems. Moreover, an interactive graphical environment as well as a customizable set of block libraries are provided by Simulink that let the developer to design, simulate, implement, and test a wide range of systems. The Figure 2.1 illustrates some application that Model-based design is used for their development [46].

#### 2.2 Verification and Validation Techniques

Due to advancements in embedded computing technologies, people are incredibly dependent on that technology in home electronic appliances, phones, cars, and more. As a result, those complex software and hardware systems are relied on more than ever in everyday life, and

| Aerospace             | Automotive               | Industrial Automation                  | Goods and Equipment |

|-----------------------|--------------------------|----------------------------------------|---------------------|

| DO 178B Certification | Engine emission control  | Robotics and automation                | Printers            |

| Satellites            | Anti-lock brakes         | Motor and machine control              | Copying machines    |

| Missiles              | Climate control, windows | Theme park rides                       | Mass storage        |

| Autopilots            | Automatic transmissions  | Upgrades to unsupported legacy systems | Home appliances     |

|                       | Wire-to-wheel controls   |                                        | Refrigerators       |

|                       |                          |                                        | Washing machines    |

Figure 2.1 Model-based Design used in development of real applications

their reliability became gradually essential. Therefore, as demand rises there is a rise in the complexity of the technologies as well as size, and a decrease in development time it has become more difficult to produce said applications with current standards of production. This creates concern over the embedded software's quality. In order to resolve this problem, various verification techniques which can be used for the verification of software, have been introduced. Following this section, verification and validation concepts as well as different verification techniques are briefly described.

### 2.2.1 Software Verification and Validation

Software producers typically spend large amounts of their total development time and resources for testing the software. In addition, the severity of the flaws also increases the required time for detect the bug. As a result, the cost of the entire development budget for software product increases correspondingly. For this reason, a sophisticated discipline of software engineering is required in order to make sure that all requirements are satisfied by the developed software. In accordance with the IEEE Standard Glossary of Software Engineering Terminology [41]:

- *Verification*: When a system or the component under development is evaluated, to figure out whether the artifacts of the given phase fulfils the requirements imposed at the beginning of that phase, it is called verification process.

- *Validation*: When a system or the component under development is evaluated during or at the end of the development phase, to figure out whether it fulfils specified requirements, it is called validation process.

In other words, software verification is about to guaranty that the software has been developed according to the provided design specifications and requirements. Moreover, as defined by DO-178B standard, verification is performed by applying the reviews, analyses or test [43].

Two fundamental approaches to software verification are: 1) Dynamic verification, 2) Static verification. Dynamic verification is commonly known as the Software testing, and Static verification applies to a process that formally analyses for proving the correctness of a program to meet the requirements.

#### 2.2.2 Model Checking

Model checking has been developed in early 80's by Clarke and Emerson [25] and also individually has been introduced by Queille and Sifakis [63]. The elementary idea is an automated method to determine if a given specification holds, by exhaustively exploring the reachable states of a program. In other words, it is an automated verification technique that checks whether the given model of a system meets specified properties of the system. If the specified property does not hold in each state, a counterexample as well as an execution trace are produced by the model checker, which leads to a state where the property is violated.

In order to overcome the challenge of directly examining the large state space of software programs, model checking is often combined with abstraction techniques. The *Kripke* structure is the formalism, which is used to represent the system models as a state-transition graph in model checking. A Kripke structure M is a four tuple  $M = (S, S_0, T, L)$ :

- S is a set of states.

- $S_0 \subseteq S$  is an initial state set.

- $T \subseteq S \times S$  is a transition relation over S, such that for every  $s \in S$  there is  $s' \in S$  such that  $(s, s') \in T$ .

- $L: S \to 2^{AP}$  is a labeling function that maps each state to a set of atomic propositions that hold in this state.

The property P is often specified as a temporal logic formula and LTL and Computation Tree Logic (CTL) are two temporal logics which are mostly used. LTL formulas are employed to express the properties pertaining to all paths in the model, while CTL formulas can be used to discriminate among paths.

#### Symbolic Model Checking

Symbolic model checking is a variation of the traditional format in that it includes the new representation for transition relations [26], and with it the user is able to verify extremely large reactive systems. In symbolic model checking, boolean functions implicitly

represent sets of states. In addition, manipulating Boolean formulas can be done efficiently with Reduced Ordered Binary Decision Diagrams (ROBDD) [20] (or shortly Binary Decision Diagram (BDD)), which is a compact, canonical graph representation of Boolean functions.

This is able to be accomplished due to the number of nodes in the Ordered Binary Decision Diagrams (OBDD) that have to be built, and no longer having to rely on the number of states or size of the transition relation. This has allowed for the possibility to verify reactive systems with realistic complexity.

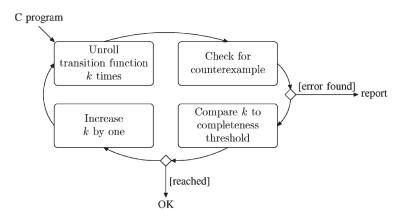

#### **Bounded Model Checking**

Bounded Model Checking (BMC) was first proposed in 1999 by Biere *et al.* [16], and got its name because it involves states that can only be reached during a bounded number of steps. At its core, the BMC is about looking for a counterexample in executions that has a length bounded through the integer k. In the event that a bug is not found then the steps are repeated, but k is increased by one, until the bug is discovered, the issue becomes intractable, or a pre-known upper bound is reached (known as *Completeness Threshold*). By reducing the BMC problem to a propositional satisfiability problem, it can be solved by Satisfiability (SAT) methods instead of Binary Decision Diagram BDDs. Unlike BDD based methods, SAT do not hampered by the space explosion problem. Moreover, they are able to support propositional satisfiability problems that have hundreds of thousands of variables or more. Through experiments, the SAT has shown that it is able to solve many issues that BDD-based techniques cannot. However, BMC has the disadvantage that it cannot prove the absence of errors in many realistic cases [17]. When applying design verification in BMC, the design first unwound for k times, and then conjoined with a property to make a propositional formula, and finally is passed to a SAT solver (Figure 2.2 [30]).

#### 2.2.3 Theorem Proving

Theorem proving is considered as a formal verification technique in which the system and desired properties are represented as formulas in some mathematical logics. Provided by a formal system, this logic defines a set of axioms and inference rules. It is actually the process of discovering a proof for a property, from the axioms of the system. Theorem provers are being used more and more in the mechanical verification of safety-critical properties of hardware and software designs.

According to Clarke et al. in [27], theorem provers for the most part can be divided in a spectrum from *highly automated* to *interactive systems*. The former referring to general-

Figure 2.2 High-level overview of BMC

purpose programs and the later referring to special purpose capabilities. The automated systems are beneficial when used for general search procedures and have had a substantial amount of success in solving the different combinational problems. Moreover, the interactive systems are more useful with regards to the systematic formal development of mathematics and mechanizing formal methods.

Since theorem proving does not have the state space explosion problem, it can be used for systems with *infinite* state spaces. This feature makes it different from model checking that suffers from state space explosion problem. There is also a reliance on *structural induction* techniques to prove over infinite domains. However, this technique is flawed in the sense that a human is required for the interactive theorem provers, making the process time consuming and sometimes vulnerable to errors.

#### 2.3 Simulink and Stateflow

By definition, Simulink is a platform for model-based Design and multi-domain simulation of dynamic systems. Stateflow, on the other hand, is a model-based development environment that is widespread and is used in several industries, such as medical, aerospace and automotive. Particularly, Stateflow diagram facilitates the graphical representation of parallel and hierarchical states together with transitions between them and inherits all code and simulation generation capabilities from Matlab toolset. Following this section, Simulink and Stateflow semantics are briefly described.

#### 2.3.1 Simulink

Simulink helps in the design and simulation of wide range of systems by providing an interactive environment along with collections of customizable blocks. It includes extensive library and toolboxes of functions commonly employed in modeling a system.

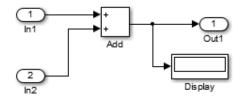

#### 2.3.2 Simulink model

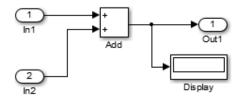

A physical model can be represented graphically as block diagrams in Simulink environment. This is possible through the use of different blocks hosted in the standard library which is provided by Simulink tool suite. In other words, a Simulink model contains different blocks that are connected through lines as well as some special blocks for communicating to external environment. In addision, Simulink models are stored as '.mdl' files, which contains textual description of the model (properties of blocks and their interconnections along with information required for simulation and graphical display of model) [51],[64]. Sample Simulink model is denoted in Figure 2.3.

Figure 2.3 Sample Simulink Model

#### 2.3.3 Simulink Library

Simulink comes with a standard block library whose blocks are placed in different categories. To build models in Simulink, blocks are the main elements that are used, and they are hosted in the library. A Simulink block has sets of *input* and *output* ports. A block with N input and M output ports defines a function which describes each of the signals at the output ports as a (possibly time-dependent) expression of the signals at the input ports. Formally, a block is a tuple  $(P_i, P_o, f)$ , where  $P_i$  is the set of input ports,  $P_o$  is the set of output ports and  $f : \mathbb{R}^{\mathbb{N}} \to \mathbb{R}^{\mathbb{M}}$  is a function which defines the behavior of the block [52]. In the following, some blocks from the standard Simulink library [6] are briefly described. These blocks are also used in our contribution while specifying properties.

### 2.3.4 Constant, Inport and Outport blocks

The *Constant* block produces a constant value with the type real or complex, and it can be found in *Sources* category of Simulink library. The constant value as well as the output data type for this block can be defined when designing the model.

*Inport* block connects a subsystem into an external input by creating an input port. Likewise to *Constant* block, this block can also be found in *Sources* category of Simulink library.

*Outport* block represents output from a subsystem. In other words, it connects a subsystem to a destination outside of the subsystem by creating an output port. This block and can be found in *Sinks* category of Simulink library.

Simulink<sup>(R)</sup> [6] software assigns port numbers for both *Inport* and *Outport* blocks automatically within a top-level system or subsystem sequentially, starting with 1. Figure 2.4, illustrates how above mentioned blocks are represented in Simulink.

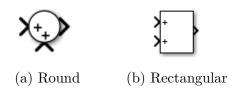

### 2.3.5 Sum block

The *Sum* block applies addition or subtraction on its given inputs, and it is hosted in the *Math Operations* category of Simulink library. It has no state and the sample time for this block is also inherited from driving blocks. This block has two different icon shapes: 1) Round, 2) Rectangular. The Sum block in illustrated in Figure 2.5b has two inputs and one output ports. In this case, the output of the block at the time step t, equals to the addition of both input values at the same time.

#### 2.3.6 Unit Delay block

The Unit Delay block holds and delays its given discrete sample time input by the sample period specified as parameter. In other words, *unit-delay* block gives the opportunity to change the sample time of the signal. In addition, he output of this block for the first sampling period is specified using the *initial conditions* parameter.

Figure 2.4 Source and Sinks blocks

Figure 2.5 Sum block

Figure 2.6 Unit Delay

### 2.3.7 Relational Operator block

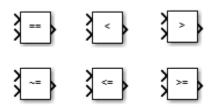

The *Relational Operator* block performs a relational operation on its two inputs and produces output. Given operators can be equal, not-equal, smaller than, smaller or equal, greater than, and greater than or equal. Different icon shapes for this block are illustrated in Figure 2.7.

Figure 2.7 Relational Operators

### 2.3.8 Logical Operator block

The *Logical Operator* block is being used to perform the specified logical operation on its given inputs. The supported operations consist of AND, OR, NAND, NOR, XOR, NXOR and NOT. Table 2.1, represents the supported operations along with their descriptions.

In this block, the number of input ports is specified with the number of input ports parameter. The output type is specified with the Output data type parameter. An output value is 1 if *True* and 0 if *False*.

Figure 2.8, denotes the different icon shapes for this block.

| Operation Item | Description                               |

|----------------|-------------------------------------------|

| AND            | TRUE if all inputs are TRUE               |

| OR             | TRUE if at least one input is TRUE        |

| NAND           | TRUE if at least one input is FALSE       |

| NOR            | TRUE when no inputs are TRUE              |

| XOR            | TRUE if an odd number of inputs are TRUE  |

| NXOR           | TRUE if an even number of inputs are TRUE |

| NOT            | TRUE if the input is FALSE                |

Table 2.1 The supported operations

Figure 2.8 Logical Operators

#### 2.3.9 Embedded MATLAB Function block

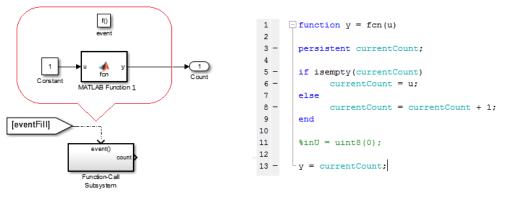

The Embedded MATLAB Function Block facilitates writing the MATLAB m-code which can be incorporated into a Simulink model. this block is placed in the User Defined Functions Library and can be inserted into a model in the same way as any other Simulink blocks. We use this block whenever there is a need to implement part of the logic of the property by code.

Figure 2.9 MATLAB Function

#### 2.3.10 Subsystem block

A subsystem is a set of blocks that we replace with a single block called a Subsystem block. As the model increases in size and complexity, it can be simplified by grouping blocks into subsystems. In other words, using *Subsystem* blocks can make the system look simpler and more easier to debug, because these blocks can include other blocks within themselves. Using subsystems has these advantages:

- Assists in decreasing the number of blocks demonstrated in the model window.

- Retains functionally related blocks together.

- Forms a hierarchical block diagram, where a Subsystem block is on one layer and lower layer contains the blocks which made the subsystem.

#### 2.3.11 Function-Call Subsystem block

This block represents a subsystem that can be invoked as a function by another block. In other words, a function-call subsystem is a subsystem that another block can invoke it directly during a simulation. It is similar to a function in a procedural programming language. Invoking a function-call subsystem is equivalent to invoking the output methods of the blocks that the subsystem contains in sorted order. The block that invokes a function-call subsystem is called the function-call initiator. Moreover, the Stateflow, Function-Call Generator, and S-function blocks can all serve as function-call initiators.

#### 2.3.12 Simulink Block Methods

Blocks represent multiple equations which are represented through *Output* and *Update* types known as block methods. Moreover, by running a block diagram these methods are also evaluated.

A simulation loop is used to evaluate block methods in which each cycle through the simulation illustrates a block diagram evaluation at a specific point in time. As such, at the current time step, outputs of each block as well as its states at the previous time step, are calculated by the output method depending on the block inputs. Likewise, discrete state of each block at current and the previous time step are calculated by update method.

A Simulink block has sets of *input* and *output* ports. A block with N input and M output ports defines a function which describes each of the signals at the output ports as a (possibly time-dependent) expression of the signals at the input ports. Formally, a block is a tuple  $(P_i, P_o, f)$ , where  $P_i$  is the set of input ports,  $P_o$  is the set of output ports and  $f : \mathbb{R}^{\mathbb{N}} \to \mathbb{R}^{\mathbb{M}}$ is a function which defines the behavior of the block [52, 22].

As an illustration, the *Sum* block in Figure 2.10 has two inputs and one output ports. In particular, the output of this block at time step t, equals to the addition of values of both input ports at time t, and the block function is shown as  $m_1(t) = n_1(t) + n_2(t)$ .

| Block | Ports                                | Function                   |

|-------|--------------------------------------|----------------------------|

| >     | $P_i = \{n_1, n_2\}$ $P_o = \{m_1\}$ | $m_1(t) = n_1(t) + n_2(t)$ |

Figure 2.10 Sum block with ports and functions at time  $_t$

#### 2.3.13 Simulink Semantics

Simulink has a plethora of semantics (depending on options that are configured by the user), which are informally and partially documented.

Regarding Simulink timing, it is a known fact that the discrete-time Simulink signals are piecewise-constant, continuous-time signals [72]. Associated timing information can be linked to these signals, referred to as *sample time*. Furthermore, the sample time of a signal shows exactly when the signal is updated in the model. When the sample time equals zero, the block is identified as having continuous sample time. This means that, it executes at every point in time. When sample time has a value greater than zero, the block is identified to have discrete sample time.

In Simulink, a discrete block executes at sample time points, and remains constant in the intervals between these sample time points. In like manner, Simulink block methods such as *Output* and *Update* methods are executed at each sample time.

#### 2.3.14 Simulink Block Priorities

Update priorities to blocks can be assigned explicitly. The output methods of each block in the model are executed depending on the their priorities from higher to lower priority. If there is consistency with block sorting rules the priorities can be honoured. Moreover, if the execution order of the block is set explicitly by setting block priorities within a subsystem, Simulink removes those block priority settings when the subsystem is expanded. Simulink checks the block properties in the following order:

- Sample time (faster rate first)

- Priority (lower priority number first)

- Port number (lower input port number first)

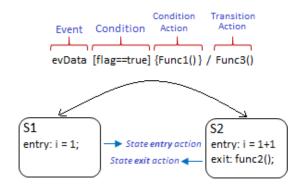

#### 2.3.15 Stateflow

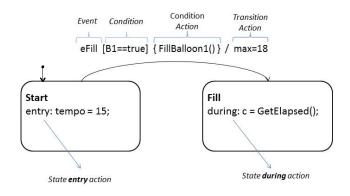

Simulink is used to model the continuous dynamics and Stateflow is used to specify the discrete control logic and the modal behavior of the system [71]. The Stateflow modeling language is based on hierarchical state machines with discrete transitions between states. It employs a variant of the finite state notation of machine as established by Harel [38] and offers the elements of language needed to describe complex logic in a readable, natural and understandable form. Given that it is strongly integrated with Simulink and MATLAB, it can offer an environment efficient enough for designing embedded systems that contain supervisory and control.

A state is referred to as *superstate* if there are other states in it and a *substate* when it is held in another state. When a state comprises of two or more substates, it has *decomposition* that can be either parallel (AND) or exclusive (OR) decomposition. All substates at a given level in the hierarchy of the Stateflow must have the same decomposition. In parallel (AND) decomposition, states can be active simultaneously and the activity of each parallel state is independent of all other states.

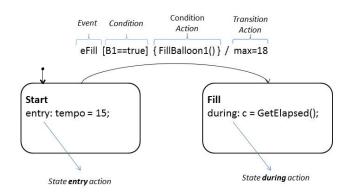

Defined *Events* can be used to trigger actions in parallel states of a Stateflow chart. One way of triggering an action and/or transition is through broadcasting of an event. The execution of *Actions* can be either as part of a transition from one state to another or based on the activity status of a state which can be *during exit*, *entry* and *on event* actions.

#### **Temporal Operators in Stateflow**

These operators are used in the Stateflow and control the execution of a chart in terms of time. In state actions and transitions, you can use two types of temporal logic: eventbased and absolute-time. Event-based temporal logic keeps track of recurring events, and absolute-time temporal logic defines time periods based on the simulation time of your chart.