# Electrically Robust Single-Crystalline WTe<sub>2</sub> Nanobelts for Nanoscale Electrical Interconnects

Seunguk Song, Se-Yang Kim, Jinsung Kwak, Yongsu Jo, Jung Hwa Kim, Jong Hwa Lee, Jae-Ung Lee, Jong Uk Kim, Hyung Duk Yun, Yeoseon Sim, Jaewon Wang, Do Hee Lee, Shi-Hyun Seok, Tae-il Kim, Hyeonsik Cheong, Zonghoon Lee, and Soon-Yong Kwon\*

As the elements of integrated circuits are downsized to the nanoscale, the current Cu-based interconnects are facing limitations due to increased resistivity and decreased current-carrying capacity because of scaling. Here, the bottom-up synthesis of single-crystalline WTe2 nanobelts and low- and high-field electrical characterization of nanoscale interconnect test structures in various ambient conditions are reported. Unlike exfoliated flakes obtained by the top-down approach, the bottom-up growth mode of WTe<sub>2</sub> nanobelts allows systemic characterization of the electrical properties of WTe2 single crystals as a function of channel dimensions. Using a 1D heat transport model and a power law, it is determined that the breakdown of WTe<sub>2</sub> devices under vacuum and with AlO<sub>2</sub> capping layer follows an ideal pattern for Joule heating, far from edge scattering. High-field electrical measurements and self-heating modeling demonstrate that the WTe2 nanobelts have a breakdown current density approaching ≈100 MA cm<sup>-2</sup>, remarkably higher than those of conventional metals and other transitionmetal chalcogenides, and sustain the highest electrical power per channel length (≈16.4 W cm<sup>-1</sup>) among the interconnect candidates. The results suggest superior robustness of WTe2 against high-bias sweep and its possible applicability in future nanoelectronics.

S. Song, S.-Y. Kim, Prof. J. Kwak, Y. Jo, J. H. Kim, J. H. Lee, Dr. H. D. Yun, Y. Sim, J. Wang, D. H. Lee, S.-H. Seok, Prof. Z. Lee, Prof. S.-Y. Kwon School of Materials Science and Engineering & Low-Dimensional Carbon Materials Center Ulsan National Institute of Science and Technology (UNIST) Ulsan 44919, Republic of Korea E-mail: sykwon@unist.ac.kr Dr. J. U. Lee, Prof. H. Cheong Department of Physics Sogang University Seoul 04107, Republic of Korea J. U. Kim, Prof. T.-i. Kim School of Chemical Engineering Sungkyunkwan University (SKKU) Suwon 16419, Republic of Korea The ORCID identification number(s) for the author(s) of this article

can be found under https://doi.org/10.1002/advs.201801370.

© 2018 The Authors. Published by WILEY-VCH Verlag GmbH & Co. KGaA, Weinheim This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

DOI: 10.1002/advs.201801370

#### 1. Introduction

Scaling of integrated circuits (ICs) has led to improved performance and reduced cost of electronic nanodevices, though revolutionary process and materials changes are required to enable technological advances.[1] Nowadays, circuit performance is no longer limited by the transistors, and the problem of interconnect performance degradation is expected to become more significant. As feature sizes continue to shrink toward the nanoscale, surface and grain boundary (GB) scatterings severely hinder electronic conductivity (a major roadblock to Moore's law at the most fundamental level) owing to the strongly nonlinear increase in their resistivity with scaling.[1-3] The microstructure in nanodevices is no longer stable over practical lifetimes, [2,4] although the current density should be increased to outperform bulk devices. According to the International Technology Roadmap for Semiconductors,[5] typical interconnect metals (e.g., Cu and Al) are required in

complementary metal oxide semiconductor (CMOS) technology to increase the maximum current density up to  $\approx\!5.35$  MA cm $^{-2}$  within the cross-sectional area of 10.8 nm $^2$  by 2028. However, it is very difficult for these polycrystalline metals to support such a high current density at the nanoscale because electrical stress-induced Joule heating and defect-mediated electromigration cause device degradation  $^{[2-6]}$  in addition to the abovementioned size effects. With a long-term vision, the most promising prospects for establishing new electrical interconnect technologies that ensure continued validity of Moore's law may be realized by developing fundamentally new interconnect fabrication strategies that gradually replace the prevailing top-down approach to multilevel metallization via lithography with bottom-up protocols based on the nanoscale self-assembly of new interconnect nanomaterials.  $^{[1]}$

Recently, transition-metal (TM) ditellurides with a distorted 1T-structure (1T'-phase), such as WTe<sub>2</sub><sup>[7-10]</sup> and MoTe<sub>2</sub>,<sup>[10,11]</sup> have attracted tremendous interest because of their exotic electronic band structure<sup>[7,12]</sup> activating extraordinary electromagnetic characters. For example, they can exhibit nonsaturating, extremely large, and positive magnetoresistance (MR),<sup>[8,13]</sup> and

can possess type-II Weyl fermions that evolve topologically protected states.[8,13] Out-of-plane van der Waals (vdW) bonds allow the TM ditellurides to be thinned down to the nanoscale, which triggers new physical phenomena like chiral anomaly induced negative MR<sup>[8]</sup> and the quantum spin Hall effect with bandgap opening. [9,11] Moreover, it is compatible for TM ditellurides to fabricate low-dimensional metal-semiconductor heterostructures or local interconnects using their high current-carrying capacity<sup>[14]</sup> and low Schottky barrier to 2D semiconductors,<sup>[15]</sup> which promises future nanosized spintronics, electronics, and photonics applications. However, most of the observed novel physical phenomena in TM ditellurides have been demonstrated in mechanically exfoliated samples, [7,8,11,12,14,15] which are irregular and not scalable. Furthermore, owing to the lack of reliable production methods for the materials, high-field transport studies of type-II Weyl semimetal systems under different ambient conditions are rare compared to the studies of Dirac semimetals (e.g., graphene) at the present stage, even though large current-carrying capacities are expected based on their fast carrier mobility.[16] On top of that, a systematic investigation of the influence of dimensions on the electrical breakdown through TM ditellurides or even other metallic TM chalcogenides (e.g., TiS2, TaS3, NbSe3, and ZrTe3) has not yet been carried out, though this would enable us to understand the fundamental physics of how the interface area impacts carrier transport and scattering mechanisms. Therefore, for practical device applications, it is important to achieve the bottom-up synthesis of the single-crystalline TM ditellurides with high electrical performance and reliability under current-carrying conditions by understanding the electrical breakdown mechanism.

Here, we report low- and high-field electrical properties of quasi-1D-like WTe2 single crystals, mainly focusing on their electrical breakdown and current-carrying capacities under various ambient conditions. The bottom-up growth mode of WTe<sub>2</sub> nanobelts allowed us to systemically characterize the electrical properties of single-crystalline WTe2 crystals as a function of channel dimensions (i.e., cross-sectional area) by preventing random crystalline orientation and degraded edges (by harsh etching) of the crystals (which is unavoidable for the exfoliated flakes). The breakdown of single-crystalline WTe2 devices under vacuum and with AlO<sub>x</sub> capping layer was found to follow the ideal behavior for Joule heating and especially the AlOxcapped WTe2 nanobelts (a practical interconnect design, where interconnects are encapsulated by dielectrics<sup>[1]</sup>) endured large input power in spite of their high resistivity. The grown WTe<sub>2</sub> nanobelts exhibited a remarkably high breakdown current densities ( $I_B$ ) of up to  $\approx 100$  MA cm<sup>-2</sup> (almost twice greater than the previously reported value for exfoliated flakes<sup>[14]</sup>), which are remarkably higher than conventional metals and other vdW atomic crystals. Furthermore, WTe2 nanobelts could sustain the highest electrical power per channel length of ≈16.4 W cm<sup>-1</sup> among the interconnect candidates, even higher than reported graphene films prepared by top-down and bottom-up processes.

#### 2. Results and Discussion

Chemical vapor deposition (CVD) has so far adopted for the growth of layered vdW atomic crystals on various

substrates;[10,17] however, the production of high-quality, stoichiometric WTe2 layers using CVD process remains an unsolved challenge due to the low stability and activity of Te, and difficulties in Te incorporation during growth.[10,17b] Inherently, the synthetic films produced are polycrystalline and therefore the GBs are expected to degrade the intrinsic properties of the resulting films.<sup>[10,17]</sup> These problems prevent studying the intrinsic electrical properties and carrier-carrying capacity of WTe2 especially on a nanoscale, owing to electron scattering and disorder effects.<sup>[18,19]</sup> Very recently, we established a strategy to introduce CuxTev (or AuxTev) eutectic alloy to overcome these problems, providing a liquid-like Te-rich ambient condition adequate to make stoichiometric binary and ternary single crystals composed of TM ditellurides.<sup>[20]</sup> We note that any salt promoters (e.g., NaCl or KCl),[21] which have recently been used for 2D growth of TM chalcogenides, have not been considered in this work to prevent the inclusion of any unintentional impurities and to avoid the need for additional processes to define the device channel.

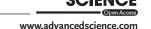

Figure 1 illustrates a schematic for WTe2 growth on SiO2/Si that relies on a eutectic alloy-assisted synthesis approach. [20] Before the growth, a W-Cu-SiO<sub>2</sub>/Si sample was located ≈1 cm above the Te-powder inside a furnace system (Figure S1a,b, Supporting Information). Note that, to investigate the degree of degradation of the as-synthesized WTe<sub>2</sub>, the reverse sequence of a W-Cu-SiO<sub>2</sub>/Si sample (this study) is formed by reversing the deposition steps of W and Cu on SiO2/Si (i.e., Cu-W-SiO2/Si) (ref. [20]). In this study, vaporized Te reacts with Cu at growth temperature T, yielding a eutectic matrix of CuxTe<sub>v</sub> located above/below the W layer (Figure S1c, Supporting Information) and the liquid-like Cu<sub>x</sub>Te<sub>v</sub> formed just below the W layer (i.e., above the SiO<sub>2</sub>/Si substrate) accelerates the formation of WTe2 (details of the growth mechanism are presented in Note S1 and Figure S2 of the Supporting Information). After cooling to room temperature, high-density WTe2 crystals were prepared directly on SiO<sub>2</sub>/Si by "tape-treatment" (Figure S3, Supporting Information), a method to remove the as-reacted by-products without any chemical etching followed by a H2 bubbling transfer process based on water electrolysis. [20] In this way, the degradation of WTe2 single crystals after growth could be minimized (Figure S4, Supporting Information), achieving a significant increase in electrical properties.

The as-synthesized WTe2 crystals show a belt-like anisotropic 1D morphology with flat surface and uniform thickness (Figure 1c; Figure S5 (Supporting Information)) by combining scanning electron microscopy (SEM) and atomic force microscopy (AFM). Raman spectra and X-ray diffraction (XRD) of the nanobelts (Figure 1c; Figure S6a (Supporting Information), respectively) exhibit all expected peak positions for WTe<sub>2</sub><sup>[10,22]</sup> (without any observable change in Raman signals in Figure S7 (Supporting Information)). We can easily recognize the longest direction of the nanobelts using optical microscopy (OM) from polarized Raman analysis<sup>[20]</sup> (Figure S8, Supporting Information). High-resolution transmission electron microscopy (HR-TEM) images reveal that the WTe2 nanobelts have the 1T'phase with an elongated shape along the a-axis (Figure S9a, Supporting Information). The measured unit cell size is significantly close to the computationally obtained one (Figure S9b,c, Supporting Information). Uniform atomic distributions of

Figure 1. WTe<sub>2</sub> nanobelts directly prepared on a SiO<sub>2</sub>/Si substrate. a–c) Experimental scheme used to prepare WTe<sub>2</sub> nanobelts on SiO<sub>2</sub>/Si. Generally, synthesis is conducted at T = 500 °C by tellurization of predeposited W/Cu layers on the substrate as schemed in (a). As-reacted eutectic matrix of Cu<sub>x</sub>Te<sub>y</sub> illustrated in (b) enables growth of WTe<sub>2</sub> within itself. Inset of (b) shows (left) cross-sectional SEM image of as-reacted sample displaying the composed material (Cu<sub>x</sub>Te<sub>y</sub>/W/Cu<sub>x</sub>Te<sub>y</sub>), and (right) corresponding EDS mapping image. (c) A schematic showing as-prepared WTe<sub>2</sub> exposed on the substrate after "tape-treatment," which denotes removal of the by-products of Cu<sub>x</sub>Te<sub>y</sub> and unreacted W layers by peeling off using adhesive tape. Inset of (c) shows (left) OM and (middle) SEM images of tape-treated WTe<sub>2</sub> nanobelts on SiO<sub>2</sub>/Si, grown for t = 2 min, and (right) Raman spectra of WTe<sub>2</sub> nanobelts characterized by using 514.5 nm laser as a light source. Raman spectra from each point marked in a left OM image show five distinct vibrational modes of WTe<sub>2</sub>, indicating uniform distributions of WTe<sub>2</sub> in the tape-treated sample.

W and Te without noticeable defects are observed across the nanobelts in the scanning TEM (STEM) image as well as in the TEM-EDS mapping (Figure S9d–e, Supporting Information), further confirming the high quality of the crystal. The high stoichiometry of the WTe<sub>2</sub> and complete removal of by-products after tape-treatment were verified by XRD and SEM-EDS (Figure S6, Supporting Information).

From growth-parameters-dependent study, we observed the significantly different growth rate of WTe<sub>2</sub> crystals in the  $\text{Cu}_x\text{Te}_y(l)$  droplets depending on the crystallographic directions (Figure S5e, Supporting Information). We note that a significant dimensional control of WTe<sub>2</sub> crystals was possible by decreasing T and t for potential application in future nanoelectronics; e.g., the cross-sectional area of WTe<sub>2</sub> nanobelts could be reduced to  $W = 59.8 \pm 29.4$  nm and  $H = 3.7 \pm 1.7$  nm

for the samples grown at T = 450 °C and t = 0 min (Figure S5f, Supporting Information). In principle, there is more room to narrow down the average size and standard error of crystals grown while decreasing T once it is higher than 340 °C, as discussed in Note S1 (Supporting Information).

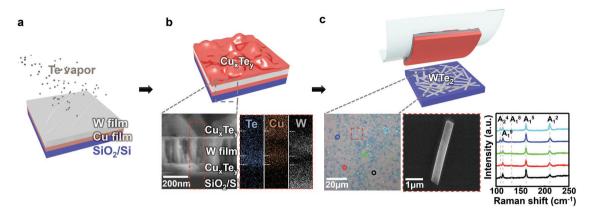

Figure 2a presents typical current density (J) versus electrical field (F) characteristics of the two-probe WTe<sub>2</sub> devices (along the a-axis) with different channel thicknesses (H) under vacuum. One can easily find that the channel has a uniform width and thickness from an AFM image (inset in Figure 2a). The perfectly linear J–Fs at low electric fields indicate a well-defined Ohmic contact after the ultrahigh vacuum (UHV) annealing process (Figure S10a, Supporting Information), regardless of the investigated channel thickness (2 < H < 50 nm). We note that the WTe<sub>2</sub> devices sustained high J of  $4.07 \pm 0.84$  MA cm<sup>-2</sup>

Figure 2. Low-bias electrical properties of WTe₂ nanobelts under various ambient conditions. a) Representative current density depending on electric field (J–F) curve indicating the well-defined Ohmic contact shown as linear behavior. Inset shows a representative AFM image of an electrical device made from the thinnest WTe₂ channel we tested (along the a-axis) with two-terminal Au/Ti contacts, showing the channel thickness of a device ≈2.5 nm. The scale bar in the AFM image is 400 nm. b,c) Resistant behavior change of WTe₂ interconnects with ambient differences at  $V_{ds} = 0.3$  V. b) Plot showing resistivity ( $\rho$ ) of WTe₂ nanobelts with different channel thickness (H). The positive slop of the H– $\rho$  graph ( $d\rho/dH \approx 4.2$  μΩ cm nm<sup>-1</sup> for samples under vacuum, and 21.5 μΩ cm nm<sup>-1</sup> for air-exposed ones) might be attributable to the existence of interlayer resistances ( $R_{int}$ ). Inset of (b) represents resistor network model that explains increase in  $\rho$  as a function of the number of layers. c) In situ resistance change ( $\Delta R/R_0$ ) of samples under varied ambient, depending on sampling time. Insets show current ( $I_{ds}$ ) decreases in the air-exposed WTe₂ device as a function of measurement time, plotted by fitted parameters of linear (above) and exponential (below) contributions.

www.advancedscience.com

those under vacuum and with  $AlO_x$  capping layer (Figure 2c; Figure S14 (Supporting Information)). From the electrical data fitting (see Note S2 of the Supporting Information for more details), we found that the permanent degradation of current was quite fast for tested WTe<sub>2</sub> nanobelts ( $\approx 34 \text{ A cm}^{-2} \text{ s}^{-1}$ ) (higher than  $Cu^{[24]}$  ( $\approx 0.62 \text{ nA cm}^{-2} \text{ s}^{-1}$ ) and phosphorene<sup>[25]</sup> ( $\approx 0.55 \text{ mA cm}^{-2} \text{ s}^{-1}$ ), but lower than MXene<sup>[26]</sup> ( $\approx 1.8 \text{ kA cm}^{-2} \text{ s}^{-1}$ )),

implying the importance of air-passivation for WTe<sub>2</sub>.

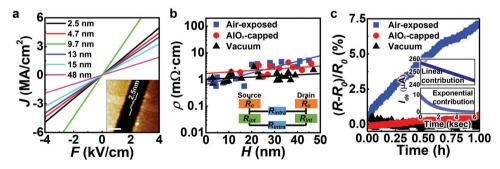

We now shift our focus to the high-field electrical properties. We conducted electrical field sweep up to failure of the WTe<sub>2</sub> devices and the representative J versus F plot is presented in **Figure 3a**. The current-carrying capacity of the WTe<sub>2</sub> devices increases to a breakdown current density ( $J_B$ ) and then decreases abruptly. We found that the  $\rho$  (reciprocal slope of J–F graph) slightly lowers as the current increases. This tendency is analogous to a trend of reducing  $\rho$  at an increased ambient temperature (Figure S11a, Supporting Information), which is the first evidence of Joule heating until the electrical breakdown. As current flows significantly, electrically induced Joule heating typically stresses devices, resulting in increases in temperature and finally failure by atomic displacements.

The formation of nanosized voids along the channel after high-field sweep shows that the failure happened along the WTe<sub>2</sub> nanobelts, not within the electrical contacts, as marked with a blue circle to stand out against the pristine one (red circle) in the inset of Figure 3b. By comparing the SEM images with the secondary electron (SE) and back-scattered electron (BSE)<sup>[17a]</sup> modes and the EDS spectra, we could precisely distinguish the atomic distribution of W and Te after the electrical failure, as shown in Figure 3b. Because the heavier metal, W, is

WTe2 nanobelts. Figure 2b shows the changes in the resistivity ( $\rho$ ) of the WTe<sub>2</sub> devices at a low bias ( $V_{ds} = 0.3 \text{ V}$ ) depending on the ambients and H, without any subtraction of contact resistance  $(R_c)$  effect. The devices under vacuum had a low resistivity of 1.62  $\pm$  0.85 m $\Omega$  cm, slightly lower than that of exfoliated flakes.[14,23] The temperature-dependent electrical characteristic of  $\rho$  further indicates the crystals' high quality as well as their intrinsic metallic behavior (Figure S11, Supporting Information). In contrast to the WTe2 under vacuum, the air-exposed samples had a higher resistivity of  $3.09 \pm 1.5 \text{ m}\Omega$  cm that might be caused by channel degradation, because WTe2 is vulnerable to air- and moisture-induced oxidation[18,19] (Figure S10b, Supporting Information). We employed the 3 nm thick AlO<sub>x</sub>capping layer for the WTe2 devices to avoid air degradation; however, the measured resistivity of AlO<sub>x</sub>-capped samples was  $3.54 \pm 2.35 \text{ m}\Omega$  cm. We believe that an avoidable air-exposure (<15 min) during sample preparation for the atomic layer deposition (ALD) process or high  $R_C$  might lead their higher resistivity (Here, we estimated  $R_c$  using both the two-probe model (Figure S12, Supporting Information) and transfer-length method (Figure S13, Supporting Information) and compared them in Figure S10c (Supporting Information). The  $R_c$ -excluded  $\rho$  as a function of H was plotted in Figure S10d (Supporting Information)). Nevertheless, we find that air-passivation is critical for WTe<sub>2</sub> to sustain its intrinsic electrical properties. We observed upsurges in the resistance of an air-exposed device with time because of channel degradation process, contrary to

at low F of 4 kV cm<sup>-1</sup>, which are comparable to those for exfo-

liated flakes,[14] showing the high quality of bottom-up grown

**Figure 3.** Electrical breakdown of WTe<sub>2</sub> devices during high electrical stress. a) Representative current density (*J*) versus electrical field (*F*) features of WTe<sub>2</sub> interconnects showing abrupt decreases in *J*. b) SEM-EDS analysis of a device broken by electrical failure. (left) Representative SEM image with the BSE mode of the WTe<sub>2</sub> interconnect, noted with the atomic distributions after the failure. Inset of (b) is the corresponding SEM image in the SE mode wherein the formed void (blue circle) is significantly different from the pristine one (red circle). (Right) EDS spectra of marked red and blue points at the SEM image, showing the Te deficiency at the void. c) Breakdown current density ( $J_B$ ) of the measured WTe<sub>2</sub> devices versus channel thickness (H) in various ambient conditions. A solid line indicates a curve fitted to the 1D heat dissipation model (i.e.,  $J_B \simeq H^{-1/2}$ ). d) Input power ( $P_B$ ) into WTe<sub>2</sub> channel shortly before electrical failure, as a function of each channel's contacted area ((WL)<sup>1/2</sup>) to substrate. e) Averaged maximum temperature ( $T_B$ ) extracted in accordance with pure Joule heating mechanism (black) and by finite-element simulation performed using a COMSOL modeling software (red).

ADVANCED SCIENCE

displayed brighter in the BSE mode, the darkest region (marked by a yellow arrow) is where both W and Te do not exist; thus. we assume that the first atomic displacement occurred in this region. The area that consists of only W and not Te (marked by a blue arrow) demonstrates that the electrical breakdown severely affects the atomic movement of the Te atoms. Considering easy evaporation of Te (evaporation of Te power begins at ≈400 °C under vacuum), the unstable and displaced Te atoms possibly disappeared due to the elevated temperature of the self-heated WTe2 channel (the weakness of Te under electrical stress is further discussed in the note for Figure S15, Supporting Information).

High  $J_{\rm B}$  over 40 MA cm<sup>-2</sup> could be observed in the few-layered devices (H < 10 nm), and remarkably, even higher  $J_{\rm B}$  of  $\approx 100$  MA cm<sup>-2</sup> was shown for a 2.5 nm thick (three-layered) device, as summarized in Figure 3c. We found that the devices exhibited thickness-dependent current-carrying capacities, similar to the studies on nanowires'  $J_{\rm B}$ , which are reliant on their diameter.<sup>[27,28]</sup> We plotted the  $J_{\rm B}$  as a function of H, obeying the following 1D thermal dissipating relation [6,14,29]

$$P_{\rm B} = g \left( T_{\rm B} - T_{\rm 0} \right) L \tag{1}$$

01

$$J_{\rm B} = \left[\frac{g(T_{\rm B} - T_{\rm 0})}{\rho_{\rm B}HW}\right]^{\frac{1}{2}} \propto H^{-\frac{1}{2}} \tag{2}$$

where  $P_{\rm B}$  is the power flowing into channel by Joule heating, g is the thermal conductance of the channel per unit length to the substrate,  $T_{\rm B}$  is the Joule heating-induced

maximum temperature at breakdown,  $T_0$  is the ambient temperature, and  $\rho_B$  is a resistivity shortly before failure. The value of  $J_B$  versus W also agrees well with the model (Figure S16, Supporting Information); however, the value of  $J_B$  seems to rely on H rather than W in the nanobelts.

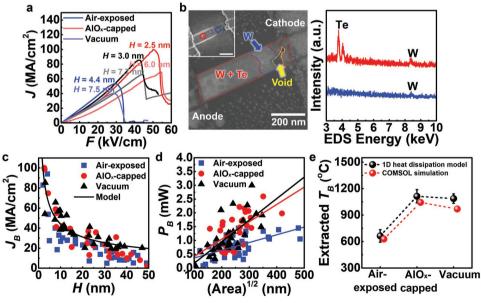

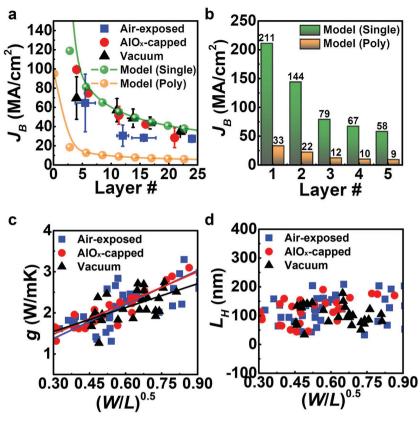

The ideal  $J_B$  for WTe<sub>2</sub> is calculated and demonstrated, using Equation (2) and the parameters. The obtained  $J_B$  is consistent with this calculated trend, as shown in **Figure** 4a (and also see Figure 3c). We also found that the  $J_B$  of monolayer WTe<sub>2</sub> may reach  $\approx$ 211 MA cm<sup>-2</sup> in theory if it sustains metallic behavior at that thickness (Figure 4b). (As for the monolayer device, we could not obtain any reliable data because degradation of a monolayer of WTe<sub>2</sub> is quite fast; less than 13 min is required for complete oxidation under air.<sup>[19]</sup>) However, it has been recognized that bandgap opening due to the quantum spin Hall effect happens in such a thin layer (<three layers),<sup>[9,11]</sup> indicating the obtained  $J_B$  ( $\approx$ 100 MA cm<sup>-2</sup>, Figure 3a) for the 2.5 nm thick WTe<sub>2</sub> in this study is very close to the highest value that one can realize. Note that the intrinsic metallic behavior lasted

**Figure 4.** Electrical characteristics of WTe<sub>2</sub> interconnects during high current injection. a) Comparisons of experimental data and calculated breakdown current density  $(J_B)$  as a function of the number of layers. The 1D heat dissipation model and average of the parameters for the thinner WTe<sub>2</sub> is used to calculate  $J_B$ . For the polycrystalline structure (orange circle), thermal conductivity<sup>[17b]</sup> of k = 0.8 W (mK)<sup>-1</sup> and the Wiedemann–Franz law<sup>[30]</sup>  $k/\sigma \propto T$  is used to extract electrical conductivity  $\sigma$ . Thickness of WTe<sub>2</sub> was converted to layer number by considering interlayer distance. b) Ideal  $J_B$  for the single- and polycrystalline WTe<sub>2</sub> dependent on layer number.  $J_B$  up to 221 MA cm<sup>-2</sup>, can be achieved if a negative bandgap is sustained in a few layers. c) Calculated thermal conductance to substrate (g) with varied geometry factor ( $(W/L)^{1/2}$ ). It demonstrates a linear relation between g and  $(W/L)^{1/2}$ , as shown in the solid lines. d) The calculated characteristic healing length ( $L_H$  = 100 nm on average) for all tested devices. The details on the extract method are included in the Note S3 of the Supporting Information.

at our few-layer WTe<sub>2</sub> with a negligible disorder effect<sup>[31]</sup> (Figure S11c, Supporting Information). Moreover, higher g causes higher input power ( $P_B = I^2_B(R_B - R_C)$ ) and higher J until the breakdown, which is significantly affected by the channel area ( $W \times L$ ) contacted to the substrate. This is because the fast heat transport through the contacted area into SiO<sub>2</sub>/Si substrate contributed to the overall g of the channel, as implied in Figure 4c. Note that Equations (1) and (2) do not have any contributions from lateral transport into metal electrodes because our samples' shorter characteristic healing length  $L_H$  ( $\approx$ 100 nm on average (Figure 4d) than the channel length ( $L \gg L_H$ ) allows almost all the heat to transport mainly through substrate vertically, as discussed in Note S3 (Supporting Information).

We found that  $P_{\rm B}$  of devices is dependent on their ambient conditions. The vacuum- and  ${\rm AlO}_x$ -capped samples showed the higher averaged  $P_{\rm B}$  than those under air ambient, indicated as greater slope in Figure 3d. This indicates that power sustaining ability could be degraded by air, particularly for the larger area channel. To unveil this effect, we extracted  $T_{\rm B}$  using

ADVANCED SCIENCE

Equation (2) and the trend of  $T_{\rm B}$  follows the variation in  $P_{\rm B}$  expectedly (Figure 3e). Notably, the  $T_{\rm B}$  of devices under vacuum and with AlOx capping layer could approach the melting point of the WTe<sub>2</sub> ( $T_{\rm m} \approx 1020$  °C).<sup>[32]</sup> Thus, we can say that the vacuum- and AlO<sub>x</sub>capped samples failed almost purely by the Joule heating mechanism. However, the air-exposed samples' lower  $T_B$  represents that the other failure mode was activated in tandem with self-heating. To validate the thermal transfer model, we calculated  $T_{\rm R}$  for the samples in various ambient conditions by finite-element simulation, and the results fit well into the model as shown in Figure 3e, and Figure S17 (Supporting Information).

Next, we tried to analyze electrical breakdown mechanism systematically by means of a power law that is a modified version of Equation (2)

$$J_{\rm B} \propto \rho_{\rm B}^{-m} \tag{3}$$

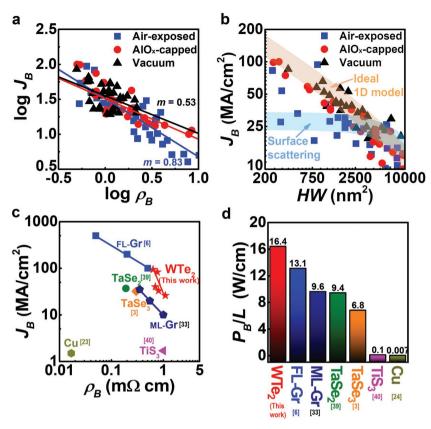

where m is 0.5 for ideal Joule heating, and exceeds 0.5 for the defect-induced electromigration generally, which is a good indicator of the rate of breakdown by self-heating.<sup>[6,33]</sup> **Figure 5**a shows the  $I_B$  versus  $\rho_B$  on a logarithmic scale to fit to Equation (3). The lowest m of 0.52 for AlO<sub>x</sub>-capped samples indicates the robustness of channel under high-bias, probably due to further suppression of electromigration (i.e., surface diffusion) by passivation (Figures S15 and S18, Supporting Information). By contrast, the air-exposed samples possessed the highest extracted m value of 0.83, implying that due to the defect-induced electromigration, the failure occurs faster than the intrinsic stability (the failure occurs even before the temperature reaches  $T_{\rm m}$ ).

To further understand the electromigration-related breakdown mechanism, we investigated the failure locations within the channels depending on the ambients (Figure S15, Supporting Information). In our WTe<sub>2</sub> devices, we found that the change in the failure point location depends on the isolation of air and prevention of atomic migration on the surface, which vary strongly with ambient conditions and to a lesser extent with sample thickness (H) and contact resistance ( $R_c$ ). For the air-exposed samples, the damage was observed to be caused by the electrical stress near the cathode, and not at the center or near the anode. Since the electrons bombard the atoms as they move from the cathode to anode under the effect of the electron wind force  $(F_{wd})^{[1,4]}$  along the selfheated WTe2 nanobelt, this electromigration could also transport the W or Te atoms especially those at the surface of the WTe2 nanobelt, along the same direction. This increases the possibility of defect formation near the cathode, which is observed as voids after all (Figure S15a, Supporting Information). Regarding the electromigration process in atomic scale,

**Figure 5.** Analysis of electrical breakdown mechanism and comparison of current-carrying capacity of interconnect candidate materials under air ambient. a) Logarithm  $J_B - \rho_B$  plot of WTe<sub>2</sub> interconnects with varied ambient conditions. The extracted m using a power law of  $J_B = k\rho_B^{-m}$  for each condition is noted, which is a useful signal to infer the rate of Joule heating until failure. b)  $J_B$  versus cross-sectional area (WH) of the channel shows the size effect by edge scattering on air-exposed WTe<sub>2</sub> transport. The calculations using ideal 1D heat dissipation model (orange) and scattering model (light blue) are plotted as solid lines. The parameters used for calculation were W = 150-450 nm, L = 500 nm, p = 0.85, and  $I_0 = W/4$ . c) Maximum current density until breakdown ( $J_B$ ) of each material regarding its resistivity. d) Averaged maximum input power per channel length ( $P_B/L$  ( $=J_B^2\rho_BHW$ )) for different channel materials that can endure under air.

we believe that the atomic displacement (including the process of breaking the W-Te bonds) took place first, under the influence of both electron bombardment and self-heating; and then the unstable Te atoms (rather than the W atoms) possibly evaporated. Compared to air-exposed samples, the damaged locations of the AlOx-capped devices were observed to be closer to the center (Figure S15b, Supporting Information), because the Joule heating induced failure occurs as a result of the increase in temperature: as temperature of the  $WTe_2$  devices reaches  $T_m$ ,  $WTe_2$  cannot continue to exist in its solid form. Hence, a failure could occur at a location regardless of the location of the application of  $F_{\rm wd}$  with respect to the cathode. This indicates that the AlOx capping layer has retarded the electromigration, possibly by blocking the absorption of the ambient molecules on the lattice (which give rise to structural vulnerability and vacancy formation) and by physically restraining the atomic migration on the surface (for more details, please see the note for Figure S15, Supporting Information).

www.advancedscience.com

The effect of air exposure on current-carrying capacity was further investigated by surface scattering model as a function of cross-sectional area of channel ( $W \times H$ ). Taking thicknessdependent resistant behavior into account, we recalculated 1D heat transport model with Fuchs-Sondheimer model<sup>[34,35]</sup> for the electron-nanobelt edge scattering (see Note S4 of the Supporting Information for more details) and this is shown as blue line in Figure 5b. Here, some air-exposed devices deviated randomly from ideal 1D model (gray line), but they followed the size effect by edge scattering (blue line). Since the oxidation usually starts from edge of nanomaterial, carrier transport along the quasi-1D metallic bonds could be more diffusive especially at the edge under air ambient. This implies that air-passivation is required to maintain its high  $I_{\rm R}$ without deterioration from edge scattering at along narrow channels.

However, we found that none the vacuum-devices'  $J_B$ showed any evidence of severe surface scattering as  $(W \times H)$ decreases down to ≈200 nm<sup>2</sup>, consistent with calculations using the ideal 1D model (gray line). This is very interesting because nanoribbons prepared by the top-down process usually show degraded electrical properties for such narrow channels.<sup>[2,23]</sup> Contrary to the WTe<sub>2</sub> flakes prepared by the top-down processes, [14,23,36,37] our WTe2 nanobelts may show rather scattering-free carrier motion along the contained metallic dimers. This is possible owing to the absence of any degraded edges by harsh etching<sup>[23,36]</sup> and random crystalline orientation<sup>[14,37]</sup> in our WTe2 nanobelts, that prevent deterioration of current flow by backscattering. The dangling-bond-free, smooth vdW surface also contributes to elastic reflection of carriers on the surface. [2,3,34] Furthermore, the single-crystalline nature of WTe2 helps to avoid GB scattering, which is also an important mechanism to lower conducting capacity. These negligible scattering effects indicate that we can control an increase in resistivity, permitting high current-carrying capacity. We suppose that carrier transport along low noisy metallic bonds in WTe2 also help to provide such a high durability against electrical stress, as recently reported in a quasi-1D vdW material, TaSe<sub>3</sub>.[38]

Compared to other candidate materials, our WTe<sub>2</sub> promises great advantages as a local interconnect with respect to  $J_B$  (Figure 5c). The  $J_B$  of WTe<sub>2</sub> (up to  $\approx$ 94 MA cm<sup>-2</sup>, under air) in our work is higher than Cu<sup>[24]</sup> (several MA cm<sup>-2</sup>), and even more than other vdW nanomaterials, such as TaSe<sub>2</sub><sup>[39]</sup> ( $\approx$ 37 MA cm<sup>-2</sup>), TaSe<sub>3</sub><sup>[3]</sup> ( $\approx$ 32 MA cm<sup>-2</sup>), and TiS<sub>3</sub><sup>[40]</sup> ( $\approx$ 1.7 MA cm<sup>-2</sup>). The obtained value is close to that of graphene ( $J_B$  of several hundred MA cm<sup>-2</sup> for mechanically exfoliated few-layered graphene (FL-Gr)<sup>[6]</sup> and  $\approx$ 40 MA cm<sup>-2</sup> for CVD-grown multilayer graphene (ML-Gr)<sup>[33]</sup>), which is a well-known material that can carry larger  $J_B$  than any other vdW materials. The high  $J_B$  in WTe<sub>2</sub> crystals is peculiar with respect to their higher resistivity ( $\approx$ 1 m $\Omega$  cm) compared to other vdW materials, indicating their high stiffness against electrical stress.

To further compare the materials' reliability under high-voltage sweep, we estimate that the maximum electrical power per channel length that a material can tolerate on the brink of breakdown is  $P_{\rm B}/L$  (Figure 5d). Importantly, WTe<sub>2</sub> nanobelts could sustain the highest  $P_{\rm B}/L$  of  $\approx 16.4~{\rm W~cm^{-1}}$  among the interconnect candidates, even higher than those of mechanically

exfoliated FL-Gr<sup>[6]</sup> ( $\approx$ 13.1 W cm<sup>-1</sup>) and CVD-grown ML-Gr<sup>[33]</sup> ( $\approx$ 9.6 W cm<sup>-1</sup>). This shows the superior robustness of WTe<sub>2</sub> against electrical breakdown, which might be attributed to the high  $T_{\rm B}$  ( $\approx$ 1001 °C under vacuum,  $\approx$ 664 °C under air), particularly compared with those of graphene<sup>[33]</sup> ( $\approx$ 600 °C) or TiS<sub>3</sub><sup>[40]</sup> ( $\approx$ 450 °C) under oxygen-rich condition (Figure S19a, Supporting Information). The dimension difference of the channel could induce a change in a capacity for heat transfer as  $g \propto (W/L)^{1/2}$ , although the effect was not sufficient to make a significant difference (Figure S19b, Supporting Information). It is worthwhile to note that polycrystalline Cu obviously had a low value of  $P_{\rm B}/L$ , despite its high  $T_{\rm m}$ , because the electrical failure happens mainly due to GB migration, not self-heating. Therefore, the GB-free nature of WTe<sub>2</sub> nanobelts also significantly helped to enhance their electrical reliability.

### 3. Conclusion

We have performed low- and high-field electrical characterization of single-crystalline WTe2 nanobelts obtained via a bottom-up process under various ambients. We found that the breakdown of WTe2 devices under vacuum and with AlOx capping layer follows the ideal behavior for Joule heating, far from edge scattering. As opposed to the WTe<sub>2</sub> flakes prepared by the top-down process, our WTe2 nanobelts show rather scatteringfree transport behavior along their quasi-1D atomic intermetallic chains, owing to the absence of any degraded edges by harsh etching and random crystalline orientation, as well as the single-crystalline nature of WTe<sub>2</sub> with a dangling-bond-free, smooth vdW surface. Accordingly, the WTe2 nanobelts could exhibit a higher  $J_{\rm B}$  of up to  $\approx 100~{\rm MA~cm^{-2}}$  as compared to conventional interconnect metals and other TM chalcogenides, and sustain the highest  $P_B/L$  of  $\approx 16.4 \text{ W cm}^{-1}$  among the interconnect candidates.

Although direct integration with the CMOS process seems difficult at this stage, we believe that our strategy sufficiently shows the potential for applications in future downscaled nanoelectronics technology in terms of the interesting fundamental electrical properties of quasi-1D-like WTe2 single crystals compared to other vdW materials. Moreover, our work provides the first direct insights into the role of channel size on the Joule heating-induced electrical breakdown of layered TM chalcogenides and type-II Weyl semimetals. We believe that further size reduction of our nanobelts to orders of less than 10 nm by spontaneous growth would facilitate their application for "post-CMOS interconnect", which is a requirement because of the limited signaling and reliability caused by interconnect technology with downscaled IC features (we calculated how the performance of WTe2 interconnect could be improved in percentage in Note S5 of the Supporting Information). We also suggest that the introduction of doping procedures using intercalation<sup>[2]</sup> or substitutional<sup>[20]</sup> dopants will provide a practical pathway to increase carrier density and to modulate the work function for WTe2 interconnects with lower resistivity and contact resistance. With steady improvements in growth/fabrication techniques and 1D nanomaterial springboards, we expect that our nanobelts will develop into a large field of their own.

www.advancedscience.com

## 4. Experimental Section

Growth of WTe2 Nanobelts: WTe2 was grown using a similar setup as that for conventional powder vaporization; the schematic of the setup used in this work is shown in Figure S1, Supporting Information. To prepare metal precursors (predeposited sample of W-Cu-SiO<sub>2</sub>/Si) before growth, the Cu film (50 nm) was deposited onto Si/SiO<sub>2</sub> by using an UHV e-beam evaporator with a high-purity Cu solid source (99.99% Cu pellet). A W layer (20–200 nm) was fabricated on this Cu–SiO<sub>2</sub>/Si sample using a direct current magnetron sputtering system under the optimized deposition conditions (less than ±5% uniformity within the wafer). Next, the prepared W-Cu-SiO<sub>2</sub>/Si was suspended above a quartz boat containing 0.1 g Te powder (Sigma-Aldrich, 99.5%), which was located at the center of the furnace. By simply heating the reactants at T = 450-500 °C and atmospheric pressure using Ar (500 sccm) as the carrier gas in an 8 in. quartz tube during the designated growth time (usually t = 0-120 min, depending on the experimental conditions), WTe2 crystals inside the CuxTex matrix located above/below the W layer (Cu<sub>y</sub>Te<sub>y</sub>/W/Cu<sub>y</sub>Te<sub>y</sub>/SiO<sub>2</sub>/Si) could be prepared. After the growth, the system was cooled to room temperature by opening the furnace cover. The tellurization for t = 0 min (i.e., shoot) implies that the growth furnace was turned off when reaching to the growth temperature T.

The WTe2 crystals were analyzed after removing CuxTe, by "chemical etching" or "tape-treatment." For the "tape-treatment" method, the tape was first placed on the as-grown sample. A compressive force was applied manually to ensure good adhesion between the tape and the sample. By simply peeling off the tape from the sample, the Cu<sub>2</sub>Te<sub>4</sub>/W/ Cu<sub>x</sub>Te<sub>y</sub> structure could be removed from the Si/SiO<sub>2</sub> substrate, leaving behind WTe2. Using this method, most of the other materials except WTe2 were removed from the substrate. It is noted that removal of those by-products like W and Cu compounds can be effectively accomplished using an ammonium persulfate (APS) etchant as well, [20] but an APS water-containing solution degrades their performance by oxidation and/ or defect formations of WTe2 crystals if they are exposed for long time (Note S1 and Figure S4, Supporting Information). Chemical etching of the Cu compounds was performed by dipping the as-synthesized sample in 1 and 30 M APS solutions for ≈1 h (slow etching) and 2 min (fast etching), respectively. The etched-sample was rinsed with isopropyl alcohol (IPA) and then with deionized water to remove any APS residue.

Structural Characterization: The sample morphology was investigated based on SEM (Hitachi S-4800) images recorded at an accelerating voltage of 7 kV. EDS analysis was conducted using the SEM setup at 15 kV. For compositional analysis by EDS, the crystals were attempted to transfer onto another substrate in order to avoid overlapping of the W M-shell and Si K-shell peaks at ≈1.7 keV. For the transfer, the crystals were dispersed in IPA by sonication and then dropped onto the other desired substrate using a pipette at an elevated temperature (≈90 °C), on a hotplate.

Micro-Raman measurements were carried out with the 514.5 nm (2.41 eV) line of an Ar ion laser. The laser beam was focused onto a single  $WTe_2$  nanobelt by using a  $50\times$  objective lens (0.8 N.A.). The scattered light was collected by the same objective lens and dispersed with a Jobin-Yvon Horiba iHR550 spectrometer (2400 grooves mm<sup>-1</sup>) and detected with a liquid-nitrogen-cooled back-illuminated charge-coupled-device array detector. Volume holographic filters (Ondax and Optigrate) were used to reject the Rayleigh-scattered light. The laser power was kept at  $100 \mu W$  to avoid local heating of the samples. The spectral resolution was below 1 cm<sup>-1</sup>. For polarized Raman measurements, the 632.8 nm (1.96 eV) line of a He-Ne laser was used. An achromatic half-wave plate was used to rotate the polarization direction of the linearly polarized incident laser beam to the desired direction. The analyzer angle was set such that photons with polarization parallel to the incident polarization pass through (parallel configuration). Another achromatic half-wave plate was placed in front of the spectrometer to keep the polarization direction of the signal entering the spectrometer constant with respect to the groove direction of the grating.

XRD patterns were recorded using a Bruker AXS D8 system with a  $\text{Cu-K}\alpha$  source. AFM images were recorded on a Bruker Dimension

AFM apparatus operating in tapping mode. For TEM observation, WTe $_2$  was transferred onto TEM grids by using the method adopted for EDS analysis. HR-TEM images and SAED patterns were recorded at several points of the nanobelts by using a JEM-2100F system equipped with a probe-aberration corrector at an acceleration voltage of 200 kV; the corresponding results were consistent with each other.

Electrical Device Fabrication and Measurements: For electric characterization of WTe2, two-probe Ti/Au (10/80 nm) electrodes were contacted using e-beam lithography (NBL-NB3) and an e-beam evaporator (Temescal FC-2000). During device preparation, PMMA encapsulation was carried out whenever the sample was exposed to air, in order to minimize degradation; however, minimum exposure within t < 15 min was unavoidable. After the fabrication, the electrodes under UHV conditions at 300 °C for 1 h to improve the contact were annealed. For some devices, a 3 nm thick  ${\rm AlO}_x$  layer was deposited by ALD to protect the channel from oxidation.

Electrical characterization was performed in a cryogenic probe station (Lakeshore CRX-4K) equipped with a Keithley 4200-SCS detector, at  $T\approx 6.5$ –300 K and either high vacuum to  $10^{-6}$  Torr or atmospheric pressure, depending on the experimental conditions. For the resistance sampling mode, the electrical current density (typically,  $J_{\rm ds}\approx 4$  MA cm<sup>-2</sup>) was injected every 10 s. For the electrical field sweep up to failure of the devices, the voltage sweep rate was 10 mV s<sup>-1</sup>. All the electrical exchange along the a-axis, to avoid any variations resulting from random crystalline orientation.

### **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

#### Acknowledgements

This work was supported by Nano-Material Technology Development Program (Grant No. 2017M3A7B8065377) and by the Basic Science Research Program (Grants Nos. 2016R1A2B3008363 and 2017R1E1A1A01075283) through the National Research Foundation (NRF) of Korea funded by the Ministry of Science, ICT, and Future Planning. This work was benefited from the use of the facilities at UNIST Central Research Facilities.

#### **Conflict of Interest**

The authors declare no conflict of interest.

## Keywords

bottom-up process, electrical performance and reliability, future nanoelectronics, nanoscale interconnect, tungsten ditelluride (WTe<sub>2</sub>)

Received: August 17, 2018 Revised: December 3, 2018 Published online:

A. Kolodny, in Advanced Nanoscale ULSI Interconnects: Fundamentals and Applications (Eds: Y. Shacham-Diamand, T. Osaka, M. Datt, T. Ohba), Springer, New York, USA 2009, pp. 39–62.

<sup>[2]</sup> J. Jiang, J. Kang, W. Cao, X. Xie, H. Zhang, J. H. Chu, W. Liu, K. Banerjee, *Nano Lett.* 2017, 17, 1482.

- [3] M. A. Stolyarov, G. Liu, M. A. Bloodgood, E. Aytan, C. Jiang, R. Samnakay, T. T. Salguero, D. L. Nika, S. L. Rumyantsev, M. S. Shur, K. N. Bozhilov, A. A. Balandin, *Nanoscale* 2016, 8, 15774.

- [4] K.-N. Tu, Microelectron. Reliabil. 2011, 51, 517.

- [5] L. Wilson, International Technology Roadmap for Semiconductors (ITRS), Semiconductor Industry Association, Washington DC, USA 2013.

- [6] R. Murali, Y. Yang, K. Brenner, T. Beck, J. D. Mindl, Appl. Phys. Lett. 2009, 94, 243114.

- [7] M. N. Ali, J. Xiong, S. Flynn, J. Tao, Q. D. Gibson, L. M. Schoop, T. Liang, N. Haldolaarachchige, M. Hirschberger, N. P. Ong, R. J. Cava, *Nature* 2014, 514, 205.

- [8] Y. Wang, E. Liu, H. Liu, Y. Pan, L. Zhang, J. Zeng, Y. Fu, M. Wang, K. Xu, Z. Huang, Z. Wang, H.-Z. Lu, D. Xing, B. Wang, X. Wan, F. Miao, Nat. Commun. 2016, 7, 13142.

- [9] X. Qian, J. Liu, L. Fu, J. Li, Science 2014, 346, 1344.

- [10] J. Zhou, F. Liu, J. Lin, X. Huang, J. Xia, B. Zhang, Q. Zeng, H. Wang, C. Zhu, L. Niu, X. Wang, W. Fu, P. Yu, T.-R. Chang, C.-H. Hsu, D. Wu, H.-T. Jeng, Y. Huang, H. Lin, Z. Shen, C. Yang, L. Lu, K. Suenaga, W. Zhou, S. T. Pantelides, G. Liu, Z. Liu, Adv. Mater. 2017, 29, 1603471.

- [11] D. H. Keum, S. Cho, J. H. Kim, D.-H. Choe, H.-J. Sung, M. Kan, H. Kang, J.-Y. Hwang, S. W. Kim, H. Yang, K. J. Chang, Y. H. Lee, *Nat. Phys.* 2015, 11, 482.

- [12] P. K. Das, D. D. Sante, I. Vobornik, J. Fujii, T. Okuda, E. Bruyer, A. Gyenis, B. E. Feldman, J. Tao, R. Ciancio, G. Rossi, M. N. Ali, S. Picozzi, A. Yadzani, G. Panaccione, R. J. Cava, *Nat. Commun.* 2016, 7, 10847.

- [13] A. A. Soluyanov, D. Gresch, Z. Wang, Q Wu, M. Troyer, X. Dai, B. A. Bernevig, *Nature* 2015, 527, 495.

- [14] M. J. Mleczko, R. L. Xu, K. Okabe, H.-H. Kuo, I. R. Fisher, H.-S. P. Wong, Y. Nishi, E. Pop, ACS Nano 2016, 10, 7507.

- [15] S. Cho, S. Kim, J. H. Kim, J. Zhao, J. Seok, D. H. Keum, J. Baik, D.-H. Choe, K. J. Chang, K. Suenaga, S. W. Kim, Y. H. Lee, H. Yang, *Science* 2015, 349, 625.

- [16] Z. Zhu, X. Lin, J. Liu, B. Fauqué, Q. Tao, C. Yang, Y. Shi, K. Begnia, Phys. Rev. Lett. 2015, 114, 176601.

- [17] a) S.-Y. Kim, J. Kwak, J. H. Kim, J.-U. Lee, Y. Jo, S. Y. Kim, H. Cheong, Z. Lee, S.-Y. Kwon, 2D Mater. 2017, 4, 011007; b) Y. Zhou, H. Jang, J. M. Woods, Y. Xie, P. Kumaravadivel, G. A. Pan, J. Liu, Y. Liu, D. G. Cahill, J. J. Cha, Adv. Funct. Mater. 2017, 27, 1605928; c) J. Kwak, Y. Jo, S.-D. Park, N. Y. Kim, S.-Y. Kim, H.-J. Shin, Z. Lee, S. Y. Kim, S.-Y. Kwon, Nat. Commun. 2017, 8, 1549.

- [18] W. L. Liu, M. L. Chen, X. X. Li, S. Dubey, T. Xiong, Z. M. Dai, J. Yin, W. L. Guo, J. L. Ma, Y. N. Chen, J. Tan, D. Li, Z. H. Wang, W. Li, V. Bouchiat, D. M. Sun, Z. Han, Z. D. Zhang, 2D Mater. 2017, 4, 011011.

- [19] F. Ye, J. Lee, J. Hu, Z. Mao, J. Wei, P. X.-L. Feng, Small 2016, 12, 5802.

- [20] J. Kwak, Y. Jo, S. Song, J. H. Kim, S.-Y. Kim, J.-U. Lee, S. Lee, J. Park, K. Kim, G.-D. Lee, J.-W. Yoo, S. Y. Kim, Y.-M. Kong, G.-H. Lee,

- W.-G. Lee, J. Park, X. Xu, H. Cheong, E. Yoon, Z. Lee, S.-Y. Kwon, Adv. Mater. 2018, 30, 1707260.

- [21] a) S. Li, S. Wang, D.-M. Tang, W. Zhao, H. Xu, L. Chu, Y. Bando, D. Golberg, G. Eda, Appl. Mater. Today 2015, 1, 60; b) K. Chen, Z. Chen, X. Wan, Z. Zheng, F. Xie, W. Chen, X. Gui, H. Chen, W. Xie, J. Xu, Adv. Mater. 2017, 29, 1700704; c) J. Zhou, J. Lin, X. Huang, Y. Zhou, Y. Chen, J. Xia, H. Wang, Y. Xie, H. Yu, J. Lei, D. Wu, F. Liu, Q. Fu, Q. Zeng, C.-H. Hsu, C. Yang, L. Lu, T. Yu, Z. Shen, H. Lin, B. I. Yakobson, Q. Liu, K. Suenaga, G. Liu, Z. Liu, Nature 2018, 556, 355; d) S.-Y. Kim, J. Kwak, C. V. Ciobanu, S.-Y. Kwon, Adv. Mater. 2019, 1804939, https://doi.org/10.1002/adma.20.

- [22] M. Kim, S. Han, J. H. Kim, J.-U. Lee, Z. Lee, H. Cheong, 2D Mater. 2016, 3, 034004.

- [23] F. Zhang, C.-H. Lee, J. A. Robinson, J. Appenzeller, Nano Res. 2018, 11, 1768.

- [24] A. R. Rathmell, B. J. Wiley, Adv. Mater. 2011, 23, 4798.

- [25] J. O. Island, G. A. Steele, H. S. J. van der Zant, A. Castellanos-Gomez, 2D Mater. 2015, 2, 011002.

- [26] A. Lipatov, M. Alhabeb, M. R. Lukatskaya, A. Boson, Y. Gogotsi, Adv. Electron. Mater. 2016, 2, 1600255.

- [27] S. Karim, K. Maaz, G. Ali, W. Ensinger, J. Phys. D: Appl. Phys. 2009, 42, 185403.

- [28] T. W. Cornelius, O. Picht, S. Muller, R. Neumann, F. Volklein, S. Karim, J. L. Duan, J. Appl. Phys. 2008, 103, 103713.

- [29] A. Behnam, A. S. Lyons, M.-H. Bae, E. K. Chow, S. Islam, C. M. Neumann, E. Pop, *Nano Lett.* **2012**, *12*, 4424.

- [30] G. V. Chester, A. Thellung, Proce. Phys. Soc. 1961, 77, 1005.

- [31] R. Menon, C. O. Yoon, D. Moses, A. J. Heeger, Y. Cao, Phys. Rev. B 1993, 48, 17685.

- [32] Y.-Y. Lv, L. Cao, X. Li, B.-B. Zhang, K. Wang, B. Pang, L. Ma, D. Lin, S.-H. Yao, J. Zhou, Y. B. Chen, S.-T. Dong, W. Liu, M.-H. Lu, Y. Chen, Y.-F. Chen, Sci. Rep. 2017, 7, 44587.

- [33] K.-J. Lee, A. P. Chandrakasan, J. Kong, IEEE Electron Device Lett. 2011, 32, 557.

- [34] W. Steinhogl, G. Schindler, G. Steinlesberger, M. Engelhardt, Phys. Rev. B 2002, 66, 075414.

- [35] W. Steinhoegl, G. Schindler, G. Steinlesberger, M. Traving, M. Engelhardt. Scaling Laws for the Resistivity Increase of Sub-100 nm Interconnects in Simulation of Semiconductor Processes and Devices, SISPAD, IEEE, Boston, USA 2003, pp. 27–30.

- [36] Y. Sui, T. Low, M. Lundstrom, J. Appenzeller, Nano Lett. 2011, 11, 1319.

- [37] H. Liu, A. T. Neal, Z. Zhu, Z. Luo, X. Xu, D. Tomanek, P. D. Ye, ACS Nano 2014, 8, 4033.

- [38] G. X. Liu, S. Rumyantsev, M. A. Bloodgood, T. T. Salguero, M. Shur, A. A. Balandin, Nano Lett. 2017, 17, 377.

- [39] A. T. Neal, Y. Du, H. Liu, P. D. Ye, ACS Nano 2014, 8, 9137.

- [40] A. J. Molina-Mendoza, J. O. Island, W. S. Paz, J. M. Clamagirand, J. R. Ares, E. Flores, F. Leardini, C. Sanchez, N. Agrait, G. Rubio-Bollinger, H. S. J. van der Zant, I. J. Ferrer, J. J. Palacios, A. Castellanos-Gomez, Adv. Funct. Mater. 2017, 27, 1605647.