# Southern Illinois University Carbondale **OpenSIUC**

Articles

Department of Electrical and Computer Engineering

Spring 2-2-2018

# A fully integrated RSSI and an ultra-low power SAR ADC for 5.8 GHz DSRC ETC transceiver

Meijuan Zhang

Tianjin University of Technology, meijuan@hotmail.com

Ruifeng Liu

RF Microelectronics Corp, Ruifeng@hotmail.com

Yuanzhi Zhang

Southern Illinois University Carbondale, yzzhang@siu.edu

Wenshen Wang

RF Microelectronics Corp, wenshen@hotmail.com

Huimin Liu

Southern Illinois University Carbondale, Huimin.liu1@siu.edu

See next page for additional authors

Follow this and additional works at: http://opensiuc.lib.siu.edu/ece\_articles

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivs 3.0 Unported License.

#### Recommended Citation

Zhang, Meijuan, Liu, Ruifeng, Zhang, Yuanzhi, Wang, Wenshen, Liu, Huimin and Lu, Chao. "A fully integrated RSSI and an ultra-low power SAR ADC for 5.8 GHz DSRC ETC transceiver." *International Journal of Electronics and Communications* 86 (Spring 2018): 154-163. doi:10.1016/j.aeue.2018.01.020.

This Article is brought to you for free and open access by the Department of Electrical and Computer Engineering at OpenSIUC. It has been accepted for inclusion in Articles by an authorized administrator of OpenSIUC. For more information, please contact opensiuc@lib.siu.edu.

| Authors<br>Meijuan Zhang, Ruifeng Liu, Yuanzhi Zhang, Wenshen Wang, Huimin Liu, and Chao Lu |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                                                             |  |  |  |  |  |  |

|                                                                                             |  |  |  |  |  |  |

|                                                                                             |  |  |  |  |  |  |

|                                                                                             |  |  |  |  |  |  |

|                                                                                             |  |  |  |  |  |  |

|                                                                                             |  |  |  |  |  |  |

|                                                                                             |  |  |  |  |  |  |

|                                                                                             |  |  |  |  |  |  |

|                                                                                             |  |  |  |  |  |  |

|                                                                                             |  |  |  |  |  |  |

|                                                                                             |  |  |  |  |  |  |

|                                                                                             |  |  |  |  |  |  |

|                                                                                             |  |  |  |  |  |  |

|                                                                                             |  |  |  |  |  |  |

|                                                                                             |  |  |  |  |  |  |

# A Fully Integrated RSSI and an Ultra-Low Power SAR ADC for 5.8GHz DSRC ETC Transceiver

Meijuan Zhang<sup>1</sup>, Ruifeng Liu<sup>2</sup>, Yuanzhi Zhang<sup>3</sup>, Wenshen Wang<sup>12</sup>, Huimin Liu<sup>1\*</sup>, Chao Lu<sup>3\*</sup>

<sup>1</sup> Tianjin Key Lab of Film Electronics and Communication Devices, School of Electrical and Electronic Engineering, Tianjin University of Technology, China, email: lhmdxx@tjut.edu.cn

<sup>2</sup>RF Microelectronics Corp., Tianjin, China

<sup>3</sup>Department of Electrical and Computer Engineering, Southern Illinois University,

Carbondale, IL, USA, 62901, email: chaolu@siu.edu

\*Corresponding authors

Abstract: This study presents a monolithic received signal strength indicator (RSSI) and an ultra-low power SAR ADC for 5.8GHz DSRC transceiver in China electronic toll collection systems. In order to meet the stringent requirement of wide input range for the transceiver, two RSSIs collaborate with auxiliary ADC circuits to provide the digitalized received signal strength to the digital baseband of a transceiver. The RSSI design achieves fast transient response, low power consumption, and a small die area with internal active low-pass filters instead of external passive ones. The proposed design has been fabricated using a 0.13 $\mu$ m 2P6M CMOS technology. Measurement results show that the overall input dynamic range is 86dB with an accuracy of  $\pm 1.72$ dB and a transient response of less than  $2\mu$ s. Compared with the state-of-the-art designs in the literature, the overall input range and transient settling time are improved by at least 14.6%, and 300%, respectively.

Keywords—RSSI, ADC, electronic toll collection, fully integrated, ultra-low power

#### I. Introduction

Electronic toll collection (ETC) systems are widely deployed in intelligent transportation systems around the world. In 2015, Chinese Ministry of Communications issued the latest Chinese ETC standard, which adopts Amplitude Shift Keying (ASK) modulation and Dedicated Short Range Communication (DSRC) at 5.8 GHz. A complete ETC system consists of road side units (RSU) and an on-board unit (OBU). An OBU system requires low cost, small form factor, low power, good reliability, large dynamic range, and long battery life [1-2]. An on-chip fully integrated design, which is composed of RF, analog, and digital baseband circuits, is well suited to meet these requirements in OBU systems.

The amplitude of input signal received at an OBU typically varies significantly. A received signal strength indicator (RSSI) circuit can be used to detect and inform the input signal level to the baseband of an OBU system, which runs an automatic gain control (AGC) algorithm to adjust the receiver gain and ensure continuous coverage (*i.e.*, no dead zone) for a wide range of input power levels (*e.g.*, 80dBm). AGC demands a wide dynamic range, good linearity, and fast settling time of RSSI circuits [3]. Moreover, since the OBU system is battery powered and attached to a vehicle window, it is desired to minimize power

consumption and limit off-chip components to improve user convenience and system size. However, up to date, traditional RSSI circuits [3-7] [10] and [12] have difficulties to realize wide input ranges (e.g., 80dBm). These RSSIs also exhibit slow transient response, high power consumption, and low level of system integration due to the use of large off-chip capacitors. Therefore, it is attractive to develop novel RSSI circuits or system architectures that enable higher levels of system integration, a wider input range, lower power consumption, and faster settling time. This is the focus of this paper.

This work makes the following contributions: (a) a new DSRC transceiver architecture is proposed, where two identical RSSI circuits work together to achieve a wide dynamic range. Each RSSI circuit consists of only on-chip devices, resulting in a much smaller die size while achieving fast settling time and low power consumption. To the best of our knowledge, this is the first work in the literature to present design details of monolithic RSSI circuits. (b) We have implemented and fabricated the proposed RSSI design with an ultra-low power SAR ADC in a standard 0.13µm CMOS technology. Measurement results demonstrate the benefits of this proposed design in terms of chip area, detection accuracy, power consumption, input dynamic range, and transient response. Compared with the state-of-the-art designs in the literature, the overall input dynamic range and transient settling time are improved by at least 14.6%, and 300%, respectively.

This rest of this paper is organized as follows. In Section II, the proposed RSSI architecture in a 5.8GHz DSRC transceiver is presented and analyzed. The details of RSSI circuit analysis and implementation are described in Section III. Chip measurement results are introduced and discussed in Section IV. Section V concludes the paper.

# II. Proposed RSSI Architecture

#### A. DSRC Transceiver Architecture

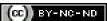

Fig. 1. Overall architecture of the developed 5.8 GHz DSRC RF-SoC transceiver

Fig. 1 illustrates the overall hardware architecture of a 5.8GHz DSRC transceiver, which includes a wake-up block (WuRx), a receiver (Rx), a transmitter (Tx), a phase-locked loop (PLL), a power management block, and a baseband. The entire system operates in three

modes: Tx, Rx, and sleep. The signal from/to antenna is controlled by baseband to switch among Tx, Rx, and WuRx blocks. A wake-up receiver (WuRx) is required to achieve long battery life. The WuRx block is only active in standby mode. The PLL, which includes LC-VCO block, offers local oscillator (LO) signal for Rx and Tx. To reduce power consumption, a duty controller is also realized in the baseband to enable/disable the Rx.

Rx is composed of a low-noise amplifier (LNA), a down-conversion mixer (MIXER), a band-pass filter (BPF), RSSI circuits (RSSI<sub>1</sub> and RSSI<sub>2</sub>), programmable gain amplifiers (PGA<sub>1</sub> and PGA<sub>2</sub>), auxiliary ADCs (Aux ADC<sub>1</sub> and Aux ADC<sub>2</sub>), a main ADC buffer, and an attenuator for AuxADC<sub>2</sub>. The BPF is inserted between the MIXER and PGA<sub>1</sub>. Thus the out-of-band noise and spur, such as flicker noise and DC offset at low frequency, adjacent-channel signals at high frequency, can be removed before the in-band signal is passed into PGA<sub>1</sub>. The in-band noise can be avoided by using an active BPF with a 10dB gain. The received signal strength has a large variation when a vehicle approaches an ETC system. In order to keep an appropriate signal level into the main ADC in Fig. 1, it is necessary to adjust the gain of each block in the Rx according to the detected signal strength. In the proposed architecture, two RSSI blocks (RSSI<sub>1</sub> and RSSI<sub>2</sub>) and two auxiliary ADC blocks are embedded in Rx. The received input signal strength from the antenna is assessed by two RSSIs and then digitized by the subsequent auxiliary ADCs. The digitized RSSI signals are provided to the baseband. Our system relies on an AGC algorithm to control the gain of each block in Rx.

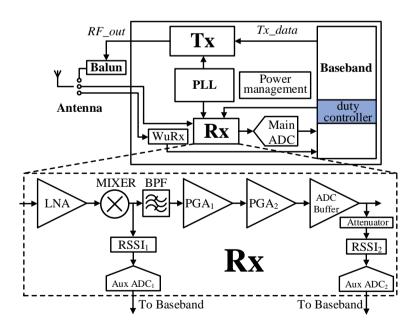

Fig. 2 depicts the flowchart of proposed AGC algorithm. Once the Rx is enabled, gains of Rx circuits enter to gain mode 1. Then, the RSSI $_1$  circuit begins to detect the signal power. After the digitized RSSI $_1$  signal is provided to the baseband, based on the signal range of RSSI $_1$ , the gains of LNA, MIXER, and PGA $_1$  will be adjusted. For example, if the received input signal is within the range 4, gain mode 3 is first applied. Then, the RSSI $_1$  value is assessed again, the gain mode of LNA, MIXER, and PGA $_1$  is updated accordingly. Finally, RSSI $_2$  begins to detect the signal magnitude. Based on the value of RSSI $_2$ , the AGC algorithm will regulate the gains of PGA $_2$  and ADC buffer. Both RSSIs are always detecting the signal strength, the baseband decides which one to read at any given time.

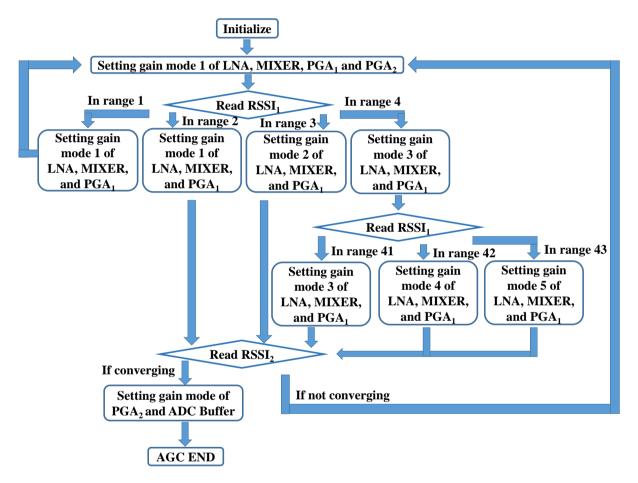

Fig. 3 plots the gain settings of RSSI<sub>1</sub> and RSSI<sub>2</sub> circuits for different input signal strength according to the proposed AGC algorithm. LNA has three gain options: maximum (Max), middle (Mid), and minimum (Min). MIXER and PGA1 have two gain options: maximum (Max) and minimum (Min). As the gains of BPF and attenuator circuits are fixed, both circuits are not varying with the signals of RSSI<sub>1</sub> and RSSI<sub>2</sub>. The gains of LNA, MIXER, and PGA<sub>1</sub> are adjusted according to the RSSI<sub>1</sub> reading. The gains of PGA<sub>2</sub> and ADC buffer are adjusted after reading the RSSI<sub>2</sub> value. In this design, LNA, MIXER, and PGA<sub>1</sub> support coarse gain adjustment, while PGA2 and ADC buffer support fine gain adjustment. After reading RSSI<sub>1</sub>, the gain modes of LNA, MIXER and PGA<sub>1</sub> are determined as listed in Table I. After reading RSSI<sub>2</sub>, the gain modes of PGA<sub>2</sub> and ADC buffer are finalized by the complete AGC algorithm in digital baseband. If there is no convergence when reading RSSI<sub>2</sub>, the AGC algorithm will return to start over. According to entire system requirements, the targeted input power levels is from -86dBm to 0dBm. As the input signal passes through the LNA, MIXER, PGA<sub>1</sub> and PGA<sub>2</sub> in Fig. 1, each RSSI only needs to handle a portion of the whole input signal range. For design simplicity, two RSSIs are designed to be identical, and used at different locations of signal path where signal strength to be detected is distinct. An attenuator added to RSSI2 to accommodate the higher power level and ensure proper detection range for RSSI<sub>2</sub>. Observed from Fig. 3, an operation range of 40dB is sufficient for each RSSI circuit.

TABLE I. Summary of gain settings of various blocks in targeted receiver input power range

| Gain<br>mode | Receiver input power (dBm) | LNA gain (dB) | MIXER<br>gain (dB) | PGA <sub>1</sub> gain (dB) | PGA <sub>2</sub><br>gain (dB)                                     | ADC buffer gain (dB) |  |

|--------------|----------------------------|---------------|--------------------|----------------------------|-------------------------------------------------------------------|----------------------|--|

| 1            | -86 ~ -65                  | Max           | Max                | Max                        | Setup by complete AGC algorithm in digital baseband for fine gain |                      |  |

| 2            | -65 ~-53                   | Max           | Max                | Min                        |                                                                   |                      |  |

| 3            | -53 ~ -38.5                | Mid           | Min                | Max                        |                                                                   |                      |  |

| 4            | -38.5 ~ 28                 | Mid           | Min                | Min                        |                                                                   | ontrol               |  |

| 5            | -28 ~ 0                    | Min           | Min                | Min                        |                                                                   |                      |  |

Fig. 2. AGC flow and RSSIs setting flow

Fig. 3. Proposed range settings and gain modes of our RSSI circuit

#### B. Conventional RSSI Architecture

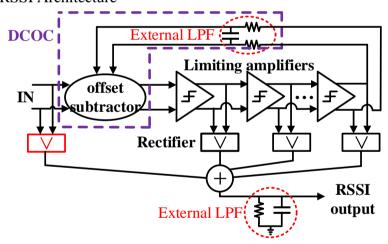

Fig. 4. Conventional RSSI circuit architecture

Fig. 4 depicts the conventional RSSI architecture, which consists of a dc offset subtractor, a summer circuit, two external passive low-pass filters (LPFs), several limiting amplifiers and rectifiers for successive detection [5, 8-9]. The traditional RSSI circuit is based on passive low-pass filters with discrete RC components. In order to achieve low bandwidth, large capacitance and resistance are required in passive low-pass filters. Due to big area overhead, capacitance usually does not integrate on chip. Therefore, extra pads and wiring metal are used for off-chip capacitor connection. In contrast, fully integrated active LPFs have the advantages of being smaller, lighter, more reliable and less expensive. The dc offset cancellation (DCOC) loop includes external LPFs, which increases chip area. The input signal is processed through this amplifier chain. In each stage, the voltage signal is converted into current domain with a logarithmic transfer function. The summer circuit superimposes

output currents of all stages. Then, another external LPF filters out AC components and converts the total current into a voltage as the RSSI output. The use of two external passive LPFs excludes monolithic integration, increases chip area and signal settling time.

#### C. Proposed RSSI architecture

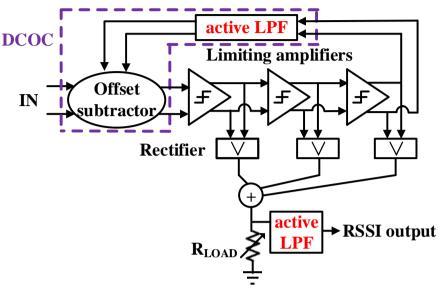

Fig. 5. Proposed RSSI circuit architecture

A new RSSI architecture is proposed in Fig. 5, where the most left rectifier is removed and two external LPFs are replaced. The input signal is amplified by three cascade limiting amplifiers. Three rectifiers convert the output signals of these limiting amplifiers into a current. If the input signal is very small, the RSSI output voltage is also small. Thus, it leads to a bad signal to noise ratio (SNR) of subsequent auxiliary ADC and hence degrades the performance of AGC algorithm. To address this challenge, a novel summer circuit is proposed, which superimposes the output currents of rectifiers and the bias currents. Note the bias currents do not vary with the RSSI input, so the bias currents can be treated as constants. To mitigate the impact of process variation, two calibration schemes are developed to change bias currents and adjust the load resistor (R<sub>LOAD</sub>) through digital baseband.

### III. RSSI Circuit Implementation

#### A. Limiting amplifier and rectifier

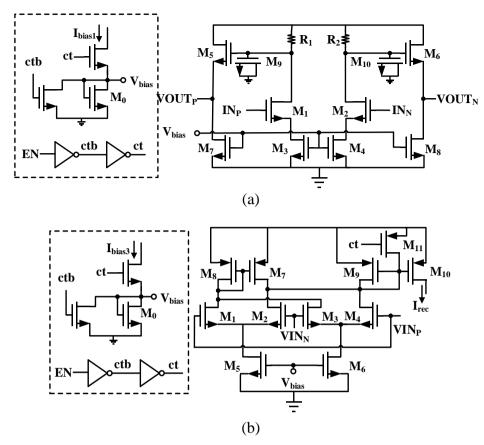

In [12], a limiting amplifier is a differential one with a gain of 10dB and 250 $\mu$ A at a 1.8 V supply. Yet, this design is not efficient because of a complex circuit structure. As shown in Fig. 6(a), the proposed design adopts a two-stage amplifier as the fixed gain stage. The circuit outlined by dotted lines provides the bias voltage ( $V_{bias}$ ), which is generated by  $I_{bias1}$  through a diode connected transistor  $M_0$ . The source and drain terminals of  $M_9$  and  $M_{10}$  are connected together to act as bypass capacitors. The proposed rectifier circuit [3, 5, 11] is drawn in Fig. 6(b), where the unbalanced source-coupled differential pairs rectify the input signals. The transistor sizes of  $M_2$  and  $M_4$  are k (k>1) times of  $M_1$  and  $M_3$ . When there is no input signal, the output current  $I_{rec}$  reaches its peak value. The output current  $I_{rec}$  is expressed as

$$I_{\text{rec}} = (I_{\text{D2}} + I_{\text{D4}}) - (I_{\text{D1}} + I_{\text{D3}})$$

(1)

Here I<sub>D1</sub>, I<sub>D2</sub>, I<sub>D3</sub>, I<sub>D4</sub> are drain current of M<sub>1</sub>, M<sub>2</sub>, M<sub>3</sub>, M<sub>4</sub>. This proposed rectifier circuit exhibits good linearity, full-wave rectification, and insensitivity to process variation.

Fig. 6. (a) Proposed limiting amplifier circuit, and (b) Proposed rectifier circuit

#### B. DC offset cancellation

In a limiting amplifier, offset cancellation is essential to eliminate any offset due to device mismatch. An offset cancellation usually consists of an LPF and an offset subtractor. An external passive LPF is used in [4-6]. In [10-11], the use of AC-coupling prevents DC offset from propagating along the amplifier chain. A common drawback of these prior works is the use of large resistor or capacitor, which increases settling time of an RSSI circuit and requires extra chip area. The closed loop gain  $H_{closed}$  and low cut-off frequency,  $\omega_L$  is expressed as [21]

$$H_{\text{closed}}(s) = \frac{A}{1 + AF} = \frac{A_f A_0^N(\omega_0 + s)}{(A_f A_0^N + 1)\omega_0 + s}$$

(2)  $\omega_L \approx A_f A_0^N \omega_0$  (3)  $\omega_0 = \frac{1}{C_f R_f}$  (4)

Here,  $A_f$  and  $A_\theta$  are the gains of offset subtractor and limiting amplifier, respectively, N is the stages of limiting amplifiers covered in the DCOC,  $\omega_\theta$  is the -3dB frequency of external passive LPF. In Rx, the input signal frequency to the RSSI circuit is 5MHz. From the equation (4), the required resistance  $R_f$  and capacitance  $C_f$  are large. In the proposed RSSI design, we utilize an active LPF to decrease the size of capacitance and resistance. Based on the fundamental circuit analysis, the input-referred offset voltage is approximated as

$$VO_{OS} = \frac{A}{1 + A\beta} VI_{OS} \cong \frac{VI_{OS}}{\beta}$$

(5)

Here  $VO_{OS}$  and  $VI_{OS}$  are the output-referred and input-referred offsets of the RSSI circuit,  $\beta$  is the gain of the LPF, and A is the total gain of the limiting amplifier [9]. As the gain of an active LPF is much higher, the output-referred offset is much less.

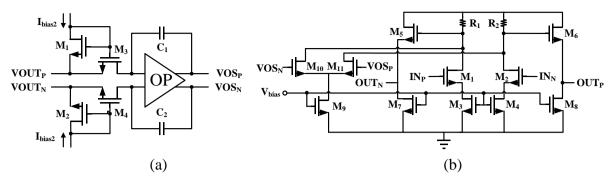

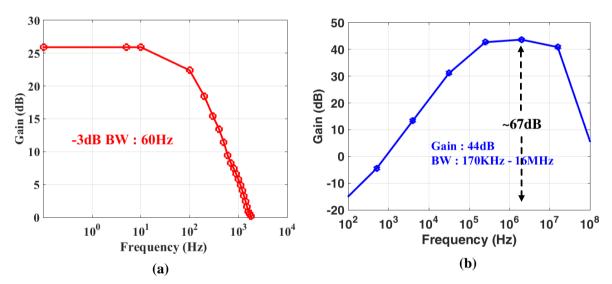

Fig. 7. (a) proposed LPF circuit (b) offset subtractor

Fig. 7(a) depicts the proposed LPF circuit. M<sub>3</sub> and M<sub>4</sub> work in the deep linear region as resistors. Fig. 7(b) shows an offset subtractor, whose inputs are the outputs of the LPF circuit. Fig. 8(a) shows the frequency response, where a -3dB bandwidth of 60Hz is observed. Fig. 8(b) shows the frequency response of the limiting amplifier, whose gain is 46dB and bandwidth is from 170 kHz to 16MHz. The achieved 67dB dc offset suppression effectively rejects low-frequency signals.

Fig. 8. Frequency response of (a) the active LPF, and (b) the limiting amplifier

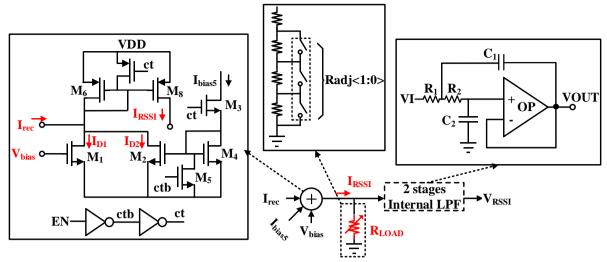

### C. I-V conversion circuit

In [3-5], the total output current of rectifiers is filtered by a first-order passive LPF, which results in long settling time and large die area. In Fig. 9, the proposed I-V conversion circuit of current to voltage is shown. To solve the above issues, we design an on-chip active LPF to replace the external passive LPF. The required resistance and capacitance are decreased, as well as transient response time. The output current I<sub>RSSI</sub> is shown as

$$I_{RSSI} = I_{D1} + I_{D2} - I_{rec}$$

(10)

$I_{rec}$  is the total current from the three stages full-wave rectifiers.  $I_{DI}$  and  $I_{D2}$  are drain currents of  $M_1$  and  $M_2$ .  $I_{bias5}$  is provided by the common bias generator. The output voltage (V<sub>RSSI</sub>) is proportional to the input power.

Fig. 9. Proposed I-V conversion circuit

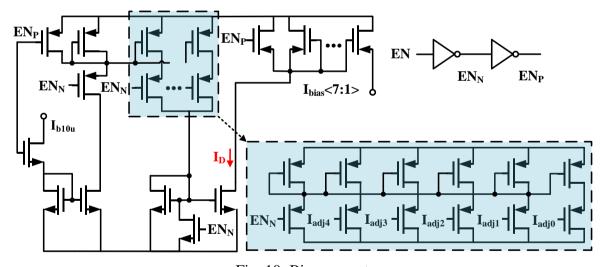

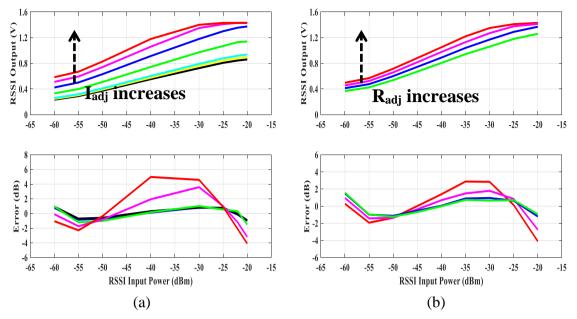

#### D. Calibration

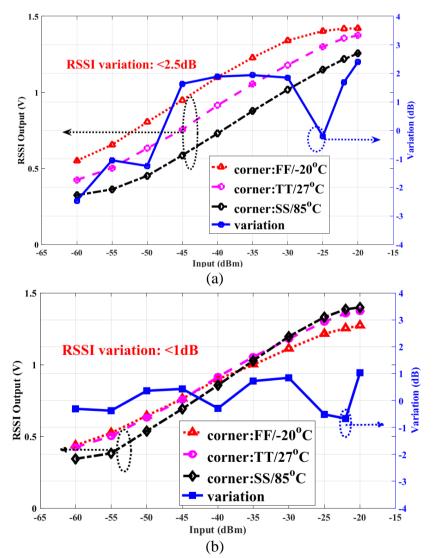

Process variation affects the circuit performance, such as dynamic range and output voltage range. We integrated two calibration schemes. First, Fig. 10 is the bias generator, where the bias current is controlled by  $I_{adj}$ <4:0> to turn on/off current mirrors. Fig. 11(a) plots the simulation results of RSSI output voltage and error versus  $I_{adj}$ . Second, the load resistor ( $R_{LOAD}$ ) is controlled by the digital signal  $R_{adj}$ <1:0>. Fig. 11(b) plots the simulation results of RSSI output voltage and error versus  $R_{adj}$ . Fig. 12 shows the corner simulation results of RSSI output voltage before and after calibration. We can see that the RSSI variation for three cases of process corners and temperatures are reduced from 2.5dB to 1dB with calibration.

Fig. 10. Bias generator

Fig. 11. RSSI output and error versus (a) I<sub>adj</sub> and (b) R<sub>adj</sub>

Fig. 12. (a) Corner simulation results of RSSI output (a) before and (b) after calibration

#### E. SAR ADC

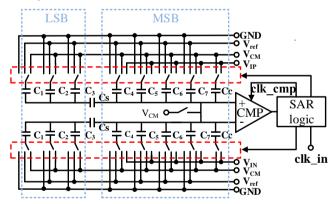

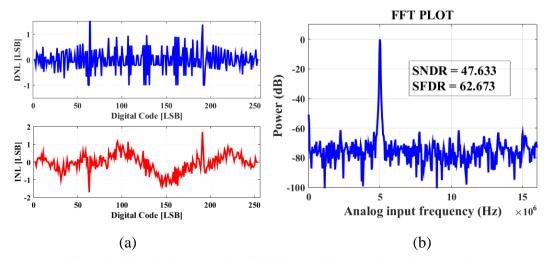

We propose an 8-bit successive approximation register (SAR) analog-to-digital converter (ADC), in which the logic control circuit, comparators, and capacitive reference network are main sources of power consumption. In the literature, several energy-efficient methods [13-16] have been presented to reduce the switching energy of SAR ADCs. The number of conversion bits can be adjusted to balance between the area, power, conversion rate, and accuracy [18-19]. In [18], a 10-bit SAR ADC is implemented with a 5-bit DAC, and consumes 4.4 µW at a 0.5V supply voltage. In contrast to conventional 10-bit SAR ADCs, the total capacitance can be reduced by more than 96%. In [19], a 5-bit DAC helps to realize an 8-bit SAR ADC with 212nW at a 1V supply voltage. For SAR ADCs, the conversion rate is inversely proportional to the resolution. It is reported [17] that synchronous logic control for the ADCs is not power efficient. The design in [20] achieves a sampling rate of 40MS/s with doubled power consumption. Therefore, asynchronous operation of comparators gets rid of a high-frequency clock and greatly improves the power efficiency [17]. Fig. 13 shows the proposed SAR ADC circuit, where the segmented and V<sub>CM</sub>-based [16] methods are used to reduce power consumption. Compared to the traditional binary weighting method, the total capacitance is reduced by 50%. In order to reject common-mode noise, a differential architecture is adopted [15]. The simulation results of DNL and INL are shown in Fig. 14(a). The conversion rate is 32.768MHz with a 1.5V supply voltage. The peak values of DNL and INL are -1/1.5 LSB and -1.8/1.8 LSB, respectively. The simulated FFT spectrum shows an input frequency is close to 5MHz as shown in Fig. 14(b). The simulation results of signal-tonoise and distortion ratio (SNDR) and spurious-free dynamic range (SFDR) are 47.633 dB and 62.673dB, respectively. The effective number of bits (ENOB) is found to be 7.62.

Fig. 13. Proposed SAR ADC Circuit

Fig. 14. Simulation results of DNL and INL, and FFT power plot

# IV. Chip Measurement Results and Discussions

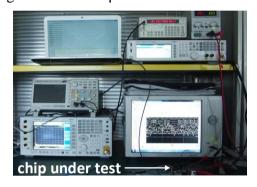

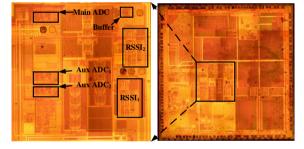

The proposed 5.8GHz RF-SoC transceiver is fabricated using a 0.13µm CMOS process. Since there are no specific pads in the chip layout to enable measuring the RSSI circuit alone, we measure the overall circuit performance of the RSSI and SAR ADC. The chip measurement environment and the die micrograph are shown in Fig. 15. The active area of a RSSI is 0.07 mm². A QFN package encapsulated the die. Chip measurements were carried out using a dc power supply (*i.e.*, Instek SPS-1230), a signal source generator (*i.e.*, Agilent N5182B), a synthesized clock generator (*i.e.*, Stanford Research System CG635) and a test signal controller. The table in Fig.15 summarizes the performance results of a RSSI and an SAR ADC. In this table, the performance results for RSSI and SAR ARC were measured and simulated, respectively. A RSSI only consumes 0.5mW in active mode, while in sleep mode it consumes 36nW. Due to the use of on-chip active LPFs, the on-off settling time of this design is less than 2µs.

| SAR A               | .DC        | RSSI                  |              |  |  |

|---------------------|------------|-----------------------|--------------|--|--|

| Area (mm²)          | 0.026      | Area (mm²)            | 0.07         |  |  |

| Power (mW)          | 0.516      | Power (on duty) (mW)  | 0.5          |  |  |

| Peak DNL            | -1.2 ~ 1.5 | Power (off duty) (nW) | 36           |  |  |

| INL (LSB)           | -1.8 ~ 1.8 | Accuracy (dB)         | $< \pm 1.72$ |  |  |

| Sampling rate (MHz) | 32.77      | Dynamic range (dBm)   | -60 ~ -20    |  |  |

| SNDR (dB)           | 47.63      | On-off settling       | < 2          |  |  |

| SFDR (dB)           | 62.67      | time (µs)             | < 2          |  |  |

| ENOB (dB)           | 7.62       | Accuracy (dB)         | $<\pm1.72$   |  |  |

Fig. 15. Chip measurement environment, micrograph, and performance summary

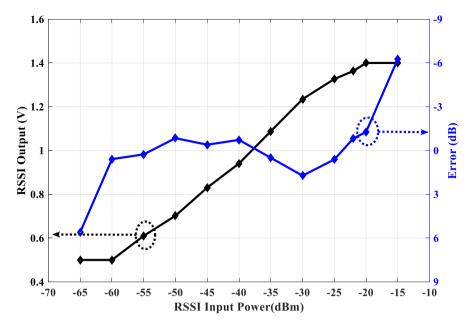

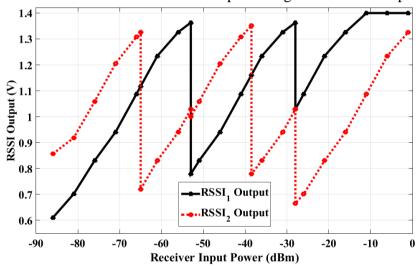

Fig. 16 plots the measurement results of a RSSI circuit varying with the RSSI input power. We can observe that its linear operation range is from -60dBm to -20dBm. The absolute value of the measurement error is less than 1.72dB. Fig. 17 shows the measurement results of RSSI<sub>1</sub> and RSSI<sub>2</sub> during the entire chip testing, in which the input power of Rx varies from -90dBm to 0dBm. Under the control of proposed AGC algorithm, appropriate gain settings were adjusted based on the input signal strength. Compared with Fig. 3, the chip measurement curves in Fig. 17 validates the correct operation of the proposed AGC algorithm.

Table III provides a comprehensive comparison of this work with other state-of-the-art designs in the literature. The proposed design demonstrates significant advantages in the overall chip area, power consumption, accuracy, and off-on settling time. The overall input dynamic range achieved is from -86dBm to 0dBm using our AGC algorithm, with an accuracy of  $\pm 1.72$ dB. The transient response is less than  $2\mu s$ . Compared with these existing designs [3-7] [10] [12], the overall input dynamic range and transient settling time are improved by at least 14.6%, and 300%, respectively. Power consumption and accuracy are also better than most of these existing designs in the literature. All of these design enhancements are due to the proposed new RSSI circuits and system architecture.

Fig. 16. Measurement results of RSSI output voltage versus RSSI input power

Fig. 17. Measurement results of RSSI<sub>1</sub> and RSSI<sub>2</sub> during the entire system testing TABLE II. Comparison of the proposed RSSI with state-of-the-art designs in the literature

| Performance Metric                   | IEEE<br>2007 | IEEE<br>2008 | CMCE<br>2010 | IEEE<br>2011 | TCSC<br>2013 | IEEE<br>2014 | IEEE<br>2016 | This  |

|--------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|-------|

|                                      | [4]          | [3]          | [5]          | [10]         | [6]          | [12]         | [7]          | work  |

| Overall chip area (mm <sup>2</sup> ) | 0.052        | 0.2          | 0.11         | 0.16         | 0.21         | 0.6          | 0.85         | 0.14  |

| Supply voltage (V)                   | 2.5          | 1.8          | 1.8          | 1.2          | 1.8          | 1.8          | 1.5          | 1.5   |

| Process (µm)                         | 0.13         | 0.18         | 0.18         | 0.13         | 0.18         | 0.18         | 0.18         | 0.13  |

| Total power (mW)                     | 9            | 4.5          | 3.7          | 1.8          | 2.34         | 4.68         | 0.54         | 1     |

| Accuracy (dB)                        | ±1           | ±2           | ±1.5         | ±0.5         | ±2           | ±1           | ±2           | ±1.72 |

| Overall input dynamic range (dB)     | 56           | 75           | 55           | 56           | 70           | 51           | 75           | 86*   |

| Off-on settling time (µs)            | N/A          | 20           | N/A          | N/A          | N/A          | N/A          | 8            | 2     |

<sup>\*</sup>this overall dynamic range is achieved by using the proposed algorithm with two RSSIs, each of which has a dynamic range of 40dB.

#### V. Conclusion

In this paper, a novel RSSI circuit and architecture are proposed and implemented using a  $0.13\mu m$  CMOS process for a 5.8GHz DSRC ETC system. The removal of one rectifier and external RC components decreases die size and power consumption. Internal active LPFs in the DCOC loop enables full on-chip integration of RSSI circuit, which effectively leads to fast transient response. In order to meet the requirement of the wide input range, two RSSIs with a smaller dynamic range and a proposed algorithm are used instead of one RSSI with a larger dynamic range. Thus, the design complexity of the RSSI circuit is alleviated. Chip measurement results show the overall input dynamic range is 86dB with an accuracy of  $\pm 1.72dB$ , and the transient response is less than  $2\mu s$ . Compared with the state-of-the-art designs in the literature, the overall input range and transient settling time are improved by at least 14.6%, and 300%, respectively.

#### VI. ACKNOWLEDGE

This work was supported by Tianjin Science and Technology Committee project No. 15JCTPJC63200, No.15JCZDJC30900, and No.17YFZCGX01110.

#### References

- [1] Kwon K, Choi J. A 5.8 GHz integrated CMOS dedicated short range communication transceiver for the Korea/Japan electronic toll collection system. IEEE Trans Microw. Theory Techn. November 2010; 58(11): 2751-63.

- [2] He X, Zhu X, Duan L, Sun Y, Ma C. A 14-mW PLL-less receiver in 0.18-μm CMOS for Chinese electronic toll collection standard. IEEE Trans. Circuits Syst. II Aug 2014; 61(10): 763-7.

- [3] Lee S, Song Y, Nam S. Fast RSSI circuit using novel power detector for wireless communication. IEEE International SoC Design Conference 2008, p. I-9–12.

- [4] Yang C, Mason A. Precise RSSI with high process variation tolerance. In: IEEE international symposium on circuits and systems. p. 2870-73.

- [5] Sun Y, Zhang X, Xia W. The design of a RSSI for the GPS receiver. In: International conference on computer, mechatronics, control and electronic engineering. p. 219-22.

- [6] Wang K, Lei X, Ma K, Yeo K, Cao X, Wang Z. A CMOS low-power temperature-robust RSSI using weak-inversion limiting amplifiers. Journal of Circuits, Systems, and Computers December 2013; 22(10): 1340034.

- [7] Jang J, Lee Y, Cho H, Yoo H. A 540-μW duty controlled RSSI with current reusing technique for human body communication. IEEE Trans Biomedical Circuits Syst 2016; 10(4): 893-901.

- [8] Huang P, Chen Y, Wang C. A 2-V 10.7-MHz CMOS limiting amplifier/RSSI. IEEE J Solid-State Circuits 2000; 35(10):1474–1480.

- [9] The Y, Choi Y, Yeoh W. A 40-MHz CMOS RSSI with data slicer. In: IEEE international symposium on integrated circuits. p. 26-2

- [10] Lei Q, Lin M, Peng M, Chen Z, Shi Y. A CMOS low power, wide dynamic range RSSI with integrated AGC loop. In: IEEE international conference on anti-counterfeiting, security, and identification. p. 24-6.

- [11] Chen Z, Zheng Y. A CMOS low-power variable-gain amplifier with RSSI for a noncoherent low data rate IR-UWB receiver. In: International symposium on integrated circuits. p. 425-8.

- [12] Byun S. Analysis and design of CMOS received signal strength indicator. IEEE Trans Circuits and Syst. I October 2014; 61(10): 2970-77.

- [13] Ginsburg B, Chandrakasan A. A 500MS/s 5b ADC in 65nm CMOS. In: IEEE symposium on VLSI circuits. p. 174–5.

- [14] Yoshioka M, Ishikawa K, Takayama T, Tsukamoto S. A 10-b 50-MS/s 820µW SAR ADC with on-chip digital calibration. In: IEEE international solid-state circuits conference. p. 384-5.

- [15] Pang W, Wang C, Chang Y, Chou N, Wang C. A 10-bit 500-KS/s low power SAR ADC with splitting capacitor for bio-medical applications. In: IEEE Asian solid-state circuits conference. p. 149-52.

- [16] Liu C, Chang S, Huang G, Lin Y. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J Solid-State Circuits April 2010; 45(4): 731-40.

- [17] Chen S, Brodersen R. A 6-bit 600-MS/s 5.3-mW asynchronous ADC in 0.13µm CMOS. In: IEEE international solid-state circuits conference.

- [18] Inanlou R, Yavari M. A simple structure for noise-shaping SAR ADC in 90nm CMOS technology. Int J Electron Commun August 2015; 69(8): 1085-93.

- [19] Yang Y, Goh W, Zhou J, Cheong J, Liu X. Ultra-low power delta sampling SAR ADC for sensing applications. In: IEEE international conference on electron devices and solid-state circuits. p. 213-6.

- [20] Sadeghipour K, Hadidi K, Khoei A. A new successive approximation architecture for high-speed low-power ADCs. Int J Electron Commun March 2006; 60(3): 217-23.

- [21] Mak P, U S, Martins R. On the design of a programmable-gain amplifier with built-in compact DC-offset cancellers for very low-voltage WLAN systems. IEEE Trans Circuits and Syst. I. March 2008; 55(2):496-509.

## **Authors Biography**

Meijuan Zhang received the B.S. degree in electrical engineering from Tianjin University of Technology, Tianjin, China in 2015. She is currently a postgraduate student in Tianjin University of Technology. Her research interests include CMOS RF and successive-approximation-register analog-to-digital converter (SAR ADC).

Ruifeng Liu received the B.S. degree in Microelectronics and Ph.D. degree in Electronic Science and Technology from Tsinghua University, Beijing, China, in 2001 and 2006, respectively. He is currently a senior design engineer in RF Microelectronics Corp., Tianjin, China. His research interests include CMOS RF and mixed signal system-on-chip design.

Yuanzhi Zhang received the B.S. and M.S. degrees in Electronic Engineering from Shandong University, China in 2011 and 2014, respectively. He is working towards his Ph.D. degree at Southern Illinois University Carbondale, IL, United States since 2015 August. His research interests include HEVC/H.265 video/image processing circuit and system optimization, low power SRAM VLSI design and methodology, and 3D-IC system design.

Wenshen Wang received the B.S. and M.S. degree in Electronic Physics and Laser from Tsinghua University, Beijing, China in 1983 and 1986, the M.S. degree in Physics from UCI,

and his Ph.D. degree in Quantum Electronics and Electromagnetic from UCLA, USA, in 1995. He is currently a manger in RF Microelectronics Corp., Tianjin, China. He has been serving as a joint professor of Tianjin University of Technology since 2014. His current research interests are CMOS RF and mixed signal system-on-chip design.

Huimin Liu received the B.S. degree from Tianjin University of Technology and Education and the M.S. degree from Tianjin Normal University, and her Ph.D. degree in Microelectronics and Solid State Electronics from Nankai University. As an associate professor, she works in Tianjin key laboratory of film electronic and communication devices, school of electronic information engineering, Tianjin University of Technology. She was a visiting scholar in ECE Department of Southern Illinois University Carbondale. Her research

interests include CMOS RF, analog, and mixed-signal IC design for radio systems.

Chao Lu received the B.S. degree in electrical engineering from the Nankai University, and the M.S. degree from HKUST. He obtained his Ph.D. degree at Purdue University, West Lafayette, Indiana, in 2012. From 2013 to 2015, He worked as an analog system/circuit design engineer at Arctic Sand Technologies Inc. and Tezzaron Semiconductors. Since August 2015, Dr. Lu is an assistant professor in ECE Department of Southern Illinois University Carbondale. His research interests include micro-scale energy harvesting systems,

RF/analog transceiver systems, H.265 video encoder, and 3D-IC system optimization.