# Southern Illinois University Carbondale OpenSIUC

### Articles

Department of Electrical and Computer Engineering

1-2018

# Design of Scalable Hardware-Efficient Compressive Sensing Image Sensors

Stefan Leitner ls3130@siu.edu

Haibo Wang zhwang@siu.edu

Spyros Tragoudsa spyros@siu.edu

Follow this and additional works at: http://opensiuc.lib.siu.edu/ece\_articles

© 2018 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

### **Recommended** Citation

Leitner, Stefan, Wang, Haibo and Tragoudsa, Spyros. "Design of Scalable Hardware-Efficient Compressive Sensing Image Sensors." *IEEE Sensors Journal* 18, No. 2 (Jan 2018): 641-651. doi:10.1109/JSEN.2017.2766040.

This Article is brought to you for free and open access by the Department of Electrical and Computer Engineering at OpenSIUC. It has been accepted for inclusion in Articles by an authorized administrator of OpenSIUC. For more information, please contact opensiuc@lib.siu.edu.

# Design of Scalable Hardware-Efficient Compressive Sensing Image Sensors

Stefan Leitner, Haibo Wang, Member, IEEE and Spyros Tragoudas, Senior Member, IEEE

Abstract—This work presents a new compressive sensing (CS) measurement method for image sensors, which limits pixel summation within neighbor pixels and follows regular summation patterns. Simulations with a large set of benchmark images show that the proposed method leads to improved image quality. Circuit implementation for the proposed CS measurement method is presented with the use of current mode pixel cells; and the resultant CS image sensor circuit is significantly simpler than existing designs. With compression rates of 4 and 8, the developed CS image sensors can achieve 34.2 dB and 29.6 dB PSNR values with energy consumption of 1.4  $\mu$ J and 0.73  $\mu$ J per frame, respectively.

Index Terms— Active Pixel Sensors, Compressive Sensing, CMOS Image Sensors

#### I. INTRODUCTION

**I**MAGE sensors have been used in a wide range of applications, including consumer electronics, medical diagnosis instruments, robotics, defense and reconnaissance equipment, etc. Recently, there are increasing demands for lowpower and high-resolution image sensors. For example, such sensors are extremely desirable for Internet of Things (IoT), hand-held or wearable gadgets, and might be mandatory for swallowable medical devices due to power and heat dissipation constraints. However, with the continuous improvement on image sensor resolutions, the number of pixels that needs to be read out, digitized, and transmitted is growing rapidly, which makes it increasingly challenging to further reduce image sensor power consumption.

Recently, compressive sensing (CS) techniques emerged as a promising paradigm to address this challenge [3, 6]. Unlike conventional CMOS image sensors that read and digitize each pixel output individually, a CS image sensor only digitizes a small set of random pixel summations [5, 11, 12, 14, 18], which not only reduces analog to digital conversion (ADC) operations and hence the sensor power consumption, but also cuts down the size of raw data produced by the sensor. The small set of data, which is also referred to as CS measurements, can be directly used for information analysis with less data storage and transmitting burden [2, 17, 26]. Also, the original image can be recovered from the CS measurements with high fidelity via CS

techniques.

For purposes of explanation, assume that vector x denotes the pixel data. The aforementioned random pixel summation can be expressed by matrix operation  $\phi \cdot x$ , where  $\phi$  is called CS measurement matrix. At present, existing CS image sensor designs use random measurement matrices to guide how pixel outputs are summed [5, 11, 12, 14, 18]. The randomness is for satisfying the incoherence requirement or restricted isometry property (RIP) suggested by CS theories [3, 6]. However, both generating large sets of random bits on-chip and conducting CS measurements following the random patterns lead to complicated CS image sensor circuits, degrading sensor fill factors and power efficiencies. It is also not easy to apply these techniques to large pixel arrays.

This work proposes a new CS measurement method that avoids the use of random measurement matrices, which simplifies CS image sensor circuits, and makes them more scalable to large pixel arrays. The proposed method targets image sensors capturing natural images. Statistical data show that the vast majority of the signal power of natural images is described by low frequency (or low index) coefficients in their sparse representations [25]. Taking advantage of this property, the proposed method performs signal summations only for a small number of neighboring pixels following regular patterns. A preliminary version of this proposed CS measurement method is presented in [13]. In this work, the validity of the proposed method is more thoroughly justified and examined with a large set of benchmark images. In addition, new circuit techniques, when compared to [13], are presented for implementing the proposed CS measurement method on image sensors. The developed CS image sensors have dramatically simplified structures, attain better image quality compared to existing designs, and exhibit significant reduction on power dissipation compared to a conventional image sensor that is based on the same CMOS technology.

The rest of the paper is organized as follows. Section 2 first briefly explains the CS theory and then reviews existing CS image sensor designs. The proposed CS measurement method is discussed in Section 3. CS image sensor circuits to implement the proposed method are presented in Section 4. Circuit simulation results are provided in Section 5 and the paper is concluded in Section 6.

Stefan Leitner, Haibo Wang and Spyros Tragoudas are with the Department of Electrical and Computer Engineering, Southern Illinois University Carbondale. Emails: <u>{ls3130@siu.edu</u>, <u>zhwang@siu.edu</u>, <u>spyros@siu.edu</u>}

#### II. RELATED WORK

#### A. Compressive Sensing Theory and Operation

The CS theory is sparked from an interesting mathematical question. If an N-element vector c is sparse, is it possible to recover vector c from M (M < N) linear observations? A vector is k-sparse if it has k non-zero (or significant) elements and the remaining N - k elements are zero (or insignificant). The linear observation, also called measurement, can be expressed by matrix operation  $y = A \cdot c$ , where A has a size of  $M \times N$ . In general, solving for N unknown variables from M (M < N)equations is not well-posed and there is no unique solution. However, if c is sparse and A satisfies certain properties, the CS theory shows that c can be recovered from measurement y with high confidence [3, 6]. Properties that guarantee the recovery of c include spark, null-space, restricted isometry property (RIP), etc. In CS applications, the incoherence requirement and RIP are often used as the criteria for selecting matrix A. RIP was originally introduced in [3] and later generalized in [1]. Matrix A obeys RIP with constant  $\delta_k$  if

$$(1 - \delta_k) ||c||_p^2 \le ||A \cdot c||_p^2 \le (1 + \delta_k) ||c||_p^2$$

(1)

for all k-sparse vectors c,  $|| ||_p$  denoting the standard  $l_p$ -norm.  $\delta_k$  must be small in order to guarantee the recovery of c. In general, it must hold that  $0 < \delta_k < 1$ . Intuitively,  $\delta_k$  indicates how well measurement y preserves the energy (norm) of vector c.

Signals in many applications may not be sparse in their original forms, but their transformations may be sparse. For example, a sinusoidal signal is not sparse in time domain but its Fourier coefficient vector is very sparse, containing only one non-zero element. The transformation that projects signal x to its sparse representation can be described by  $x = \psi \cdot c$ , where  $\psi$  is the sparse basis and c is the transformation coefficient vector. For these types of signals, CS techniques recover vector c from measurement y and, subsequently, signal x can be easily constructed by the transformation relation. The linear observation or CS measurement of x can be expressed as y = $\phi \cdot x$ . This leads to  $y = \phi \cdot x = \phi \cdot \psi \cdot c$ . Note that the product of  $\phi \cdot \psi$  is the aforementioned matrix A. Often, a random matrix is used as measurement matrix  $\phi$ , since it leads to high probability for  $\phi \cdot \psi$  to satisfy the RIP requirement. Also, from the incoherence perspective, random measurement matrices are largely incoherent to many sparse bases used in CS operations [4]. Thus, they likely satisfy the incoherence requirement, which demands the coherence measure  $\mu$  to be small. It is defined as:

$$\mu(\phi, \Psi) = \sqrt{N} \cdot \max_{1 \le i \le m; 1 \le j \le n} |\langle \phi_i, \psi_j \rangle| \tag{2}$$

where  $\phi_i$  and  $\psi_j$  represent the i<sup>th</sup> row of measurement matrix  $\phi$ and the j<sup>th</sup> column of sparse matrix  $\psi$ , respectively. Finally, a number of methods, including adaptive binary search,  $l_i$ minimization (or basis pursuit), greedy pursuits, etc., can be used to recover vector *c* from CS measurement *y*. Among them, the  $l_1$  minimization method, which is formulated below, is often used to recover c in CS applications.

$$min||c||_{1}, subj. to y = \phi \cdot \psi \cdot c \tag{3}$$

Although the mathematical theory of CS is developed purely based on signal sparsity, many practical CS applications also consider additional constraints or take advantage of other signal properties to achieve improved performance. The approaches in [15, 16] take into consideration that the energy of many real signals mainly concentrates in localized regions, e.g. in the low frequency region. The method introduces an additional criterion in the design of CS measurement matrices in order for the CS measurement operation to rake the most signal energy. Based on this premise, an alternative optimization problem is proposed to find a tradeoff between projections satisfying the RIP property and taking advantage of localized signal spectrum to boost signal quality.

For CS image applications, sophisticated reconstruction models are developed in [9, 22], among many others. These techniques exploit the tree structures and associated specific properties of the transform coefficients of natural images in CS image reconstruction processes to improve accuracy. These approaches still use conventional random based measurement matrices in CS measurement operations. In [21], relations among the sparse transform coefficients are exploited in the design of measurement matrices and CS image recovery systems. The resulting matrices have a high probability to capture the significant transform coefficients of the image and hence lead to better image quality.

#### B. Previously Proposed Compressive Sensing Image Sensors

A number of CS image sensors have been reported in literature. Some of them perform CS measurement operations in the optical domain with the aim of using reduced number of pixels to capture high resolution images [23]. These approaches are appealing in applications that require expensive pixel cells, e.g. infrared cameras. Other CS image sensors perform CS measurements during pixel readout operation in order to reduce image sensor power consumption. They commonly require summing the outputs of randomly selected pixels; but differ by the mechanisms on how to use random bit streams to guide the pixel summation as well as how the pixel summation circuits are implemented.

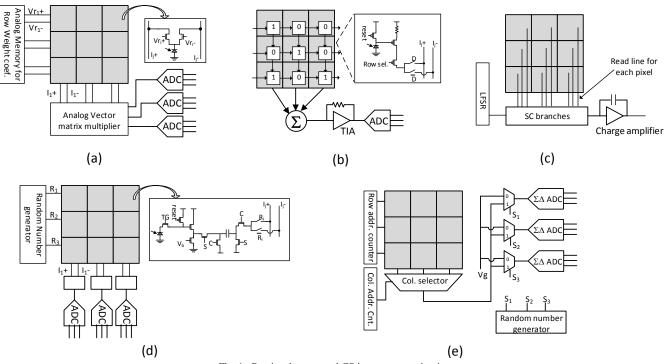

The CS measurement circuit in [20] produces weighted sums of pixel outputs and the weight is controlled by the differential row drive voltage  $V_r^+$ ,  $V_r^-$ , as well as the parameters stored in the analog vector matrix multiplier as shown in Fig. 1 (a). This circuit is also capable to perform other types of transformations but at the price of quite complicated implementation. Unlike the design in [20] that supports fractional weighting values, most CS image sensors use binary weighting values, 1 and -1, or 1 and 0. The designs in [11, 14] limit the weighting values to 1 and -1, and use a dual bit-line structure as illustrated in Fig. 1 (b). It relies on linear feedback shift registers (LFSR) to generate pseudo random bit streams, which are then shifted to the pixel cells via embedded shift registers. If the register bit in

Fig. 1. Previously proposed CS image sensor circuits

a pixel cell is 1, the current output of the pixel is directed to the positive bit-line  $I_{j+}$ ; otherwise, it is connected to the negative bit-line  $I_{j-}$ . At the end of the column, currents from the two bit-lines are subtracted to generate CS measurements. The drawbacks of this circuit include complicated pixel cell design and signal swing challenges due to summing a large number of pixels.

The design in [12] also uses a dual bit-line structure to accommodate weighting values of 1 and -1. Its pixel outputs are in the form of charge and hence pixel summations are carried out by charge amplifiers. To support random summation, a large and complex pixel cell design, shown in Fig. 1 (d), is used. A charge amplifier is also used to conduct pixel summation in [5], which supports weighting values 1 and 0. A conventional compact 3-transistor (3T) pixel cell is used. However, to accommodate random pixel summations, each pixel has its own read line as shown in Fig. 1 (c). This negatively affects the scalability of the design and CS measurements have to be implemented within small blocks partitioned from the pixel array. The design in [18] uses conventional pinned 4T active pixel cells and integrates the pixel summation function into  $\Delta\Sigma$ ADC circuits as shown in Fig. 1 (e). Depending on the pseudo random bits generated by LFSRs, either a pixel cell output or a reference voltage is fed to the ADC input in each  $\Delta\Sigma$ modulation cycle. This approach also has to be implemented in a block by block manner. The number of pixels within a block is equal to the over sampling rate of the ADC. To support multiple ADCs simultaneously generating CS measurements for the same block as well as to share the ADCs among different blocks, fairly complicated multiplexer trees have to be implemented.

In summary, existing CS image sensor designs performing

compressive acquisition in the analog domain use either large complicated pixel cells or complex pixel access schemes, such as large number of read lines or massive multiplexer trees, to support random pixel summation. Some of them also require to partition the pixel array into small blocks. These factors adversely affect CS image sensor fill factor and power efficiency. Thus, more scalable and hardware efficient CS measurement methods are highly desirable for the development of future CS image sensors.

#### III. PROPOSED CS MEASUREMENT METHOD

This section first explains the proposed CS measurement method. A generalized formula for the measurement matrix associated with the proposed method is derived. Then, the validity of the proposed method is justified in subsection B.

#### A. Proposed CS Measurement Operation

Unlike existing CS image sensor circuits that perform random summations for variable sets of pixels, the proposed method follows regular patterns to sum neighboring pixels within the same column or row. Thus, it eliminates the need of several complex circuit blocks that are commonly used in existing CS image sensors, leading to more scalable and hardware-efficient CS image sensor circuits.

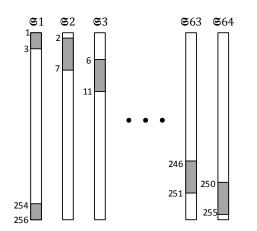

The operation of the proposed method is explained with the following example. Without losing generality, assume that the CS measurement is conducted for a pixel column containing 256 pixels and the compression rate R is 4. R is defined as the ratio of the number of pixels over the number of CS measurements. Thus, 64 CS measurements are to be generated,

Fig. 2. Pixel access pattern in CS measurement operation

which are denoted by  $\mathfrak{S}_1$ ,  $\mathfrak{S}_2$ ,  $\cdots \mathfrak{S}_{64}$ . To generate a single CS measurement, six neighboring pixels are added together and there is an overlap of two pixels between two neighboring summation groups. The CS measurement operations are illustrated in Fig. 2. Note that the vertical bars in the figure represent the same pixel column and the groups of six pixels in the shaded regions are summed together to produce the 64 CS measurements. The starting and ending pixel positions of each summation group are listed on the left side of the shaded regions. For example, in the first CS measurement, the outputs of pixels  $1 \sim 3$  and  $254 \sim 256$  are added together; in the second CS measurement, the outputs of pixels  $2 \sim 7$  are added. Thereafter, the position of the measurement group is moved by 4 pixels to start the next CS measurement. The first measurement group  $\mathfrak{S}_1$ contains pixels from both ends of the column, which is to cope with the fact that the number of pixels in a column is not evenly divided by the number of pixels in a measurement group. Grouping pixels from both ends of the column in  $\mathfrak{S}_1$  enables that every summation group has the same number of pixels.

For the convenience of discussion, let x be an  $N \times 1$  vector formed by stringing together the pixel signals from an  $L \times L$ pixel array in a column after column manner and  $N = L \times L$ . Then, the pixel summations can be described by the following equations:

$$\mathfrak{S}_{1}^{m} = \sum_{i=m\cdot L+1}^{m\cdot L+3} \mathbf{x}(i) + \sum_{i=(m+1)\cdot L-2}^{(m+1)\cdot L} \mathbf{x}(i)$$

(4)

$$\mathfrak{S}_{k}^{m} = \sum_{i=m\cdot L+4\cdot k-6}^{m\cdot L+4\cdot k-1} \mathbf{x}(i), \quad for \ k > 1$$

where, letter *m* indicates for which pixel column the CS measurement is performed and  $0 \le m \le L - 1$ .

In general, to generate M CS measurements for a pixel array containing N pixels, the size of summation groups should be  $\frac{N}{M}$  + *OL*, where *OL* represents the number of overlapping pixels between two neighboring summation groups. As a guideline, *OL* is preferred to be  $\frac{R}{2}$ , if possible. For given N, M, and *OL* values, the entries of measurement matrix  $\phi$  can be determined using:

$$\phi(i,j) = \begin{cases} 1 & if \ 1 + \frac{(i-1) \cdot N}{M} \le j \le \frac{i \cdot N}{M} + OL \\ 0 & otherwise \end{cases}$$

(5)

for 1 < i < M. For i = 1, M (the first and last row respectively), the pattern needs to be slightly adjusted to meet the image size constraint, since the dimension of the frame may not be a multiple of  $\frac{N}{M}$ .

#### B. Justification of Proposed CS Measurement Method

As discussed earlier, signals must be sparse with respect to a sparse basis to be able to take advantage of CS techniques. Image signals are generally sparse with respect to inverse discrete cosine transform (IDCT) basis. The vectors in IDCT correspond to samples of the cosine function with variable frequency starting from DC, which are given as:

$$\psi(k,j) = \sum_{i=1}^{N} \alpha(i) \left[ I(i,j) \cdot \cos\left(\frac{\pi(2k+1)(i-1)}{2N}\right) \right] \quad (6)$$

where *I* is the  $N \times N$  dimensional identity matrix,  $\alpha(i) = \sqrt{1/N}$  when i = 1, and  $\alpha(i) = \sqrt{2/N}$  when i > 1. This sparse basis is used in the following discussion as well as later image reconstruction.

The coherence measure  $\mu(\Phi, \Psi)$  defined in Equation 2 is evaluated for the pair of the proposed measurement matrix  $\phi$  and the IDCT sparse basis  $\psi$ . Matrix  $\phi$  is normalized before the evaluation in accordance to Equation 2. The obtained coherence value is 3.46. For comparison purposes, a random matrix generated by Matlab *rand* function is also examined in the study. The coherence between the random matrix and the IDCT sparse bases is 5.2. The proposed measurement matrix achieves about the same level of incoherence as random measurement matrices, confirming the suitability of the proposed measurement method in CS image applications.

The proposed measurement matrix does not satisfy RIP requirements. Note that RIP requirements are sufficient but not necessary conditions for recovering the original signal from CS measurements. For example, both RIP-2 and RIP-1, defined in Equation 1 with p = 2 and p = 1 respectively, guarantee signal recovery. A matrix that satisfies RIP-1 may not satisfy RIP-2, and vice versa. Further, RIP is a very strong condition guaranteeing the recovery of any signal, providing it is sufficiently sparse with respect to a properly chosen basis.

It has been shown that natural images generally have dominating low frequency components, and insignificant high frequency components. According to [25], the frequency spectrum of natural images along the frequency axis decays following the relation:

$$A(f) = \frac{A_{DC}}{f^{\alpha}} \tag{7}$$

where  $A_{DC}$  and  $\alpha$  represent the magnitude of the image DC component (average pixel power) and decay rate along the frequency *f* axis, respectively. Statistical data from a large number of images show that, on average,  $\alpha$  is about 2.08, with

an average standard deviation of 0.53 [25]. Thus, if a natural image is projected to the IDCT domain, the significant coefficients will be mainly distributed in the low frequency or low index region. Our study indicates that this is the key factor resulting in the improved performance of the proposed CS measurement method.

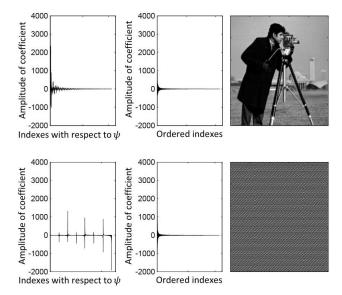

To exemplify our finding, we used the proposed measurement matrix and a random measurement matrix, which satisfies RIP conditions, to conduct CS operations for two images. One is a common benchmark image Cameraman and the other is an artificially created image by alternately assigning one pixel to black, the next pixel to gray and the third pixel to white. Clearly, the artificial image does not exist in the real world since no natural images can exhibit such dramatic changes from one pixel to another. Both images are sparse with respect to the IDCT basis and their IDCT coefficients are plotted in the left panel of Fig. 3. For image Cameraman, its significant coefficients concentrate in the low frequency region. However, the significant coefficients of the artificial image are scattered in a wide range. Despite this difference, the two images approximately have the same level of sparsity. This becomes evident after the coefficients are sorted in a descending order and plotted in the middle panel of the figure. For image Cameraman, both the proposed and random measurement matrices lead to successful image reconstruction. For the artificial image, it can be satisfyingly recovered from the CS measurements using the random matrix; but the proposed CS measurement method does not lead to successful image recovery. These observations support the earlier statements about the proposed and random measurement matrices. Nevertheless, the failure of recovering the artificial image from the proposed CS measurements should not be alarmed, since such an image is unlikely to be seen in the real world.

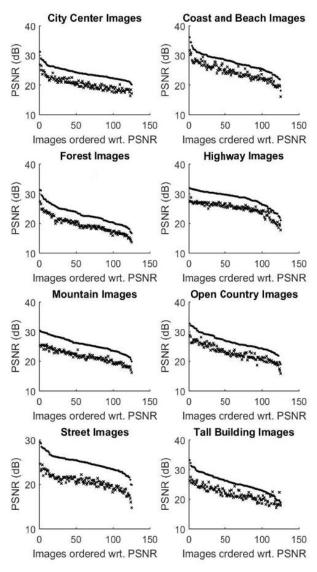

An extensive performance comparison with a set of 1000 images from database [28] has been conducted. The database contains eight image categories, covering different types of scenery. The study examined the first 125 images from each of the eight scenery categories. The PSNR values of the reconstructed images with the proposed measurement techniques are plotted in descending order in Fig. 4. The corresponding data obtained using the random measurement method is plotted directly below the reordered data using  $\times$ markers. The advantage of using the proposed measurement technique is evident, as it outperforms the conventional approach on all but three images. For the 1000 images, the proposed approach outperforms the conventional approach on average by about 3.7dB, with a standard deviation of about 0.9dB. The improvement is due to the fact that the proposed method can more accurately capture the low-frequency energy and the signal energy of natural images concentrates in the low frequency region.

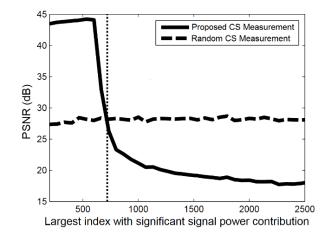

Additional studies were also conducted via Matlab simulations. Without losing generality, sparse signals with a length of 2560 samples were used in the study. The sparsity of the signals is selected as 200. Thus, among the 2560 IDCT

Fig. 3. IDCT coefficients of Cameraman (top) and black-gray-white pattern (bottom)

coefficients, 200 are significant and the remaining 2360 coefficients are negligible, which are at least 75 times smaller than the largest magnitude of the significant coefficients. A large set of such sparse signals was generated by randomly varying the magnitudes and positions of the 200 significant coefficient terms. Then, the proposed and random measurement matrices were used to generate CS measurements of these signals and later  $l_1$  minimization techniques were used to recover the signals from their CS measurements. The PSNRs of the recovered signals with using the proposed and random matrices are compared in Fig. 5. The horizontal axis indicates the highest index or frequency of the significant coefficients for a given signal. For example, if a data point in the figure has horizontal axis value of 500, then the significant coefficients of the corresponding signal are distributed in the region with indexes ranging from 1 to 500. The plot shows that if the significant coefficients are distributed in the region with indexes smaller than 720, the position marked by the dotted line in the figure, the proposed method outperforms the conventional random matrix based CS measurement method. Equation 7 indicates that signal energy drops to about 1/75 of its DC value at the frequency corresponding to index 720, when  $\alpha$  is chosen approximately 0.67. This value is off from the average value of  $\alpha$  by 2.66 times the standard deviation. This leads to the conclusion that the proposed method results in better image quality for about 99.6% of all natural images. If the significant coefficients are distributed in the region with index smaller 600, which corresponds to 99.4% of natural images according to Equation 7, the proposed CS measurement method results in significantly better image quality.

Simulations were also conducted to compare the image reconstruction time from CS measurement results obtained with the proposed and random measurement matrices. Benchmark images Lenna and Cameraman were used in the study with compression rates of 4 and 8. Simulations were performed on a

Fig. 4. Performance comparison of proposed vs. random CS techniques on a large set of natural images

desktop computer with Core i7 CPU, 3.4GHz clock, and 8GB memory. Matlab  $l_1$  magic package was used to solve the  $l_1$ minimization problem during image reconstruction. The image reconstruction time and the number of iterations are compared in Table 1. In the study, the 256×256 sized benchmark images are partitioned into 16 256×16 blocks for CS measurement and image reconstruction. Thus, the reported image reconstruction time and number of iterations are accumulated numbers for the 16 blocks. It shows the proposed measurement matrices also lead to slightly reduced image reconstruction time.

#### IV. CS IMAGE SENSOR IMPLEMENTATION

CS image sensors using the proposed measurement method can be implemented with conventional compact pixel cells and simple pixel summation circuits. This is a significant advantage compared to existing designs, which require either complicated pixel cells or complex pixel summation circuits. This section

Fig. 5. PSNR of recovered signals with variable signal spectrum bandwidth from the proposed and random CS measurements

| COMPARISON OF IMAGE RECONSTRUCTION TIME |   |          |      |              |            |  |

|-----------------------------------------|---|----------|------|--------------|------------|--|

| Images                                  | R | Meas.    | PSNR | Image recon. | Number of  |  |

|                                         |   | Matrices | (dB) | time (s)     | iterations |  |

| Lenna                                   | 4 | Proposed | 37.8 | 134.5        | 322        |  |

|                                         |   | Random   | 30.4 | 142.6        | 347        |  |

|                                         | 8 | Proposed | 32.5 | 78.0         | 314        |  |

|                                         |   | Random   | 25.6 | 87.0         | 375        |  |

| Camera<br>man                           | 4 | Proposed | 28.0 | 133.5        | 316        |  |

|                                         |   | Random   | 21.8 | 145.1        | 353        |  |

|                                         | 8 | Proposed | 24.1 | 77.1         | 309        |  |

|                                         |   | Random   | 18.6 | 87.5         | 383        |  |

TABLE I

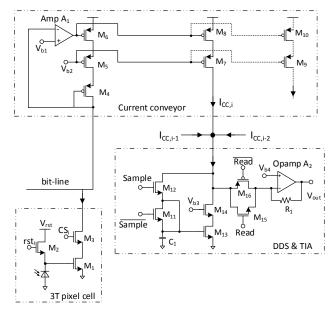

discusses circuit implementation techniques for such CS image sensors with using current-mode active pixel cells [8, 19, 27]. The decision of using current-mode pixel cells is mainly due to the convenience of performing current summation at the inputs of current conveyors as well as sampling circuits. Note that the proposed CS measurement method can also be easily implemented with voltage-mode pixel cells, in which the pixel summations are carried out in terms of voltage or charge summations.

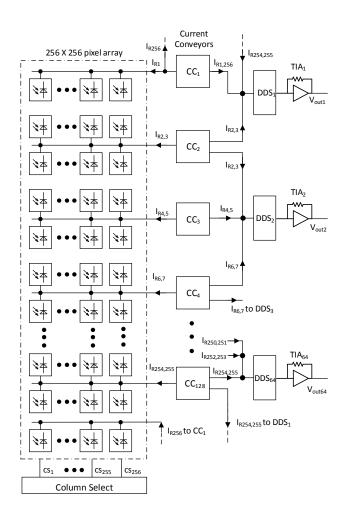

Fig. 6 shows the block diagram of a CS image sensor that implements the CS measurement operation illustrated in Fig. 2. It assumes the pixel array is  $256 \times 256$  and the compression rate is 4. The proposed method can conduct CS measurements in a row-by-row or column-by-column manner. To be consistent with the example in Fig. 2, the sensor circuit in Fig. 6 also conducts CS measurements in a column-by-column manner. As a result, the pixel read lines or bit-lines are routed horizontally (the horizontal lines within the pixel array) and the column select lines are routed vertically (labeled by  $CS_1, \cdots CS_{255}, CS_{256}$  outside the pixel array). The sensor performs row read operations in parallel and hence there is no row selection circuit. The horizontal bit-line structure is not a significant deviation from the conventional or existing CS image sensors which route bit-lines vertically, since the pixel array in Fig. 6 can be simply rotated by 90° to achieve vertical bit-lines. The above block diagram indicates that the outputs of

Fig. 6. CS image sensor block diagram

pixel cells in rows 2 & 3, 4 & 5, ..., 254 & 255, in the same column are connected. These pixel pairs are not combined into single pixel cells, because the area of the photo diode of a merged pixel cell should be twice of the original photo diode size. Since the area of a pixel cell is dominated by its photo diode size, merging pixels does not yield any significant area advantage. Furthermore, not all pixels can be merged, thus merging pixels will result in non-uniform pixel sizes.

During pixel read operation, the *i*<sup>th</sup> column is selected by asserting  $CS_i$  to 1, all the pixels within this column are accessed. The output currents of the pixel cells that share the same bitline are added together at the bit-line and then are fed to the inputs of current conveyors which are labeled by  $CC_1, CC_2, \dots CC_{128}$  in the figure. There are two types of current conveyors: One has single current output and the other has dual output ports. The latter is to accommodate the overlaps between adjacent CS measurement patterns as illustrated in Fig. 2. The current conveyor outputs are further summed according to the measurement patterns before being fed to the inputs of delta double sampling (DDS) circuits, which are denoted by  $DDS_1, DDS_2, \dots DDS_{64}$  in the figure. The current outputs of the DDS circuits are then amplified and converted to voltage signals by trans-impedance amplifiers (TIAs).

Fig. 7. CS image sensor schematic

A conventional image sensor with column-parallel read operation reads the pixels of a single row at the same time. Hence, the number of amplifiers as well as ADCs at the end of the bit-lines equals the number of columns. In the proposed design, the outputs of multiple pixels at different rows are combined together while being read out. As a result, the number of amplifiers and ADCs that are needed to support row-parallel read operation in the proposed design is R times smaller than that required in the conventional image sensor with the same array size. This improves sensor fill factor and reduces power consumption.

Thanks to its regularity, the CS measurement pattern is hardwired in the proposed design. Thus, it neither requires LFSR for random bit generation nor uses complex pixel cells or complicated pixel signal routing circuits that support pixel random summation. As shown in Fig. 7, a 3T current-mode active pixel cell is selected for the design. Other current-mode pixel cells [8, 27] can be used as well. The schematic of the current conveyor is given in the top portion of Fig. 7. It includes cascode current mirrors consisting of M5-M10 and amplifier A1, which forms a negative feedback with  $M_6$  to keep the bit-line voltage at V<sub>b1</sub>. The second output branch of the current mirror, implemented by M<sub>9</sub> and M<sub>10</sub>, is only needed for the current conveyors that have two outputs and hence are drawn in dotted lines. To keep transistor M<sub>1</sub> of the pixel cells in linear region, the bit-line voltage should be low. Meanwhile, the voltage at the current mirror output is preferred to be relatively high due to the consideration of signal swing headroom at TIA outputs. If pixel output ports are directly connected to the drain of M5 in the current mirror input branch, it potentially results in a relatively large voltage difference between its input and output ports, which negatively affects current mirror accuracy. To mitigate this problem, diode connected transistor M<sub>4</sub> is inserted between pixel bit-line and the drain of M<sub>5</sub> for level shifting purposes.

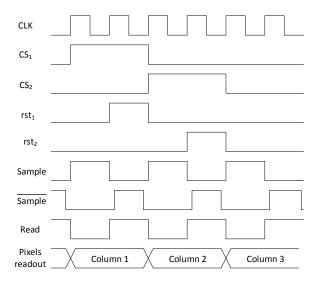

To cope with transistor threshold variations across the pixel array, delta double sampling [7] is implemented in the design. Unlike conventional image sensors that conduct DDS for each pixel individually, the proposed design collectively performs DDS for the group of pixels to be summed in a single CS measurement. This does not diminish the benefit of DDS, since the current errors caused by threshold variations are linear terms added to the actual pixel signals. As illustrated inside the DDS & TIA block of Fig. 7, transistors  $M_{11}$ - $M_{14}$  and capacitor  $C_1$ form a current memory circuit that samples the summed pixel cell outputs after the pixel integration period. Transistor M<sub>12</sub> is the sampling switch and  $M_{11}$ , half the size of  $M_{12}$ , is to compensate for the channel charge injection of M<sub>12</sub>. The cascode structure of M<sub>13</sub> and M<sub>14</sub> keeps V<sub>DS13</sub> at a constant level, helping improve the accuracy of the sampling circuit. Immediately after finishing the above read operation, the pixel cells are reset and remain accessed. Then, the input of the DDS circuit is the sum of the pixel output currents in reset phase, which is the second sampled value of the DDS operation. The two sampled values are naturally subtracted before being fed to the TIA via the transmission gate consisting of  $M_{15}$  and  $M_{16}$ . The control signals for reading out the first two pixel columns are depicted in Fig. 8. It shows that the design takes two clock cycles to read a column and hence 512 cycles for the entire array.

In addition to its simple structure, the proposed design also possesses several advantages in its pixel read operation compared to existing CS image sensors. The designs in [11, 14] use current-mode pixels and perform pixel summation in current format as well. However, these designs sum a large number of pixel outputs to generate CS measurements, which significantly increases signal dynamic range and requires high resolution ADCs. In the proposed design, the number of pixels being summed in a single CS measurement is small and thus it has relaxed dynamic range and ADC resolution requirements. Excluding the pixel integration time, a CS measurement can be generated within two pixel read cycles in the proposed design.

Fig. 8. Control signals during CS image sensor readout operation

This is much faster than the scheme used in [18], whose  $\Delta\Sigma$  ADC speed is limited by the pixel read cycle. For an 8-bit ADC resolution, it takes 512 pixel read cycles to generate a CS measurement. Finally, the circuit block diagram and schematic provided in this section are based on the compression rate of 4. For other compression rates, the bit-line sharing scheme as well as the connections between current conveyors and DDS circuits can be easily modified according to the measurement matrix described by Equation 5.

#### V. CIRCUIT SIMULATION RESULTS

To demonstrate the proposed CS image sensor techniques, two CS image sensors with compression rates of 4 and 8 are designed along with a conventional image sensor. The pixel arrays of the three sensors have the same size of  $256 \times 256$  and use the same 3T pixel cell design shown in Fig. 7. The circuit implementation of the CS image sensor with compression rate 4 is discussed in the previous section. The sensor with compression rate 8 is implemented similarly with the following modifications. It sums 12 pixels in a single CS measurement and there are overlaps of 4 pixels between neighboring summation groups. Thus, four pixel rows share a bit-line. There are 64 current conveyors to copy current signals from bit-lines and 32 DDS & TIA blocks to generate CS measurements. In the conventional image sensor, every pixel row has its own bit-line; it uses 256 current conveyors, all with single output port, and 256 DDS & TIA blocks. The conventional image sensor design is mainly used for the comparison of power consumption in this study.

The three image sensors are designed using a 0.13 µm CMOS technology and 1.5V power supply voltage. The gate leakage as well as the drain to source leakage in transistor off state of the thin silicon dioxide transistors are too large for such devices to be used in pixel cells [24]. Thick silicon dioxide devices with large feature sizes and higher threshold voltage are used for transistors  $M_1$  and  $M_2$ . This leads to a slightly larger pixel size and does not affect the evaluation of the proposed CS image sensor techniques. The remaining transistors are thin silicon transistors to fully take advantage of technology scaling. Low power devices, which have reduced I<sub>DS</sub> leakage in off state, are used for transistors that function as switches, including M<sub>3</sub>, M<sub>11</sub>,  $M_{12}$ ,  $M_{15}$  and  $M_{16}$  of Fig. 7. The transistor sizes and other component values are listed in Table II. Amplifier A1 in the current conveyor circuit is implemented using a single stage folded-cascode amplifier, which provides a gain of 100. As a result, the input resistance, estimated by  $1/(A_1 \cdot g_{m6})$ , of the current conveyor is about 170  $\Omega$ , which is much smaller than the on-resistance of the pixel access device M<sub>3</sub>. Operational amplifier (Opamp) A<sub>2</sub> in the TIA is a two-stage amplifier with a cascode first stage. Miller compensation is used to achieve a phase margin of about 65 degree. The gains, bandwidths, and current dissipations of the two amplifiers are summarized in Table III.

The clock frequency of the image sensors is 1MHz and the three sensors share the same design for their digital control, which is based on a "token-pass" shift register consisting of 512 D Flip-Flops (DFF). During pixel read operation, a token, logic 1, is passed along the DFF chain and a group of two consecutive

| TABLE II<br>Component Values used in the Design |              |  |  |  |

|-------------------------------------------------|--------------|--|--|--|

| Component                                       | Values       |  |  |  |

| $M_1, M_2^*$                                    | 360nm/240nm  |  |  |  |

| $M_3^{**}$                                      | 160nm/120nm  |  |  |  |

| M4, M5, M6, M7, M8, M9, M10                     | 6400nm/360nm |  |  |  |

| $M_{11}^{**}$                                   | 320nm/120nm  |  |  |  |

| $M_{12}^{**}$                                   | 640nm/120nm  |  |  |  |

| M <sub>13</sub>                                 | 160nm/1um    |  |  |  |

| $M_{14}$                                        | 160nm/360nm  |  |  |  |

| $M_{15}, M_{16}^{**}$                           | 1.6um/120nm  |  |  |  |

| $C_1$                                           | 100 fF       |  |  |  |

| R1                                              | 100 kΩ       |  |  |  |

\* Thick silicon oxide transistors

\* Low power transistors

|  | TABLE III |   |

|--|-----------|---|

|  | -         | _ |

| AMPLIFIER PERFORMANCE PARAMETERS           Amplifier         Gain $f_T$ (MHz)         Current dissipation ( $\mu$ A) |      |     |     |  |  |

|----------------------------------------------------------------------------------------------------------------------|------|-----|-----|--|--|

| Amp. A <sub>1</sub>                                                                                                  | 100  | 1   | 0.5 |  |  |

| Opamp A <sub>2</sub>                                                                                                 | 7000 | 100 | 23  |  |  |

DFFs correspond to a pixel column. Column select signal  $CS_i$  is the logic OR of the outputs of the two DFFs corresponding to column *i*; reset signal *rst<sub>i</sub>* is the output of the second DFF in the pair. Signals *Sample* and *Read* have opposite phases and their frequency is half of the clock frequency. Necessary buffers and delay elements are inserted into the signal paths to achieve adequate driving strength, avoid overlaps between control signals, and attain desirable signal phase arrangement. For example, Signal *Sample* should switch to 0 slightly ahead of the rising edge of reset signals as well as its complementary signal *sample* as shown in Fig. 8.

Circuit simulations have been conducted to obtain CS image sensor outputs for benchmark images Lena and Cameraman. The photocurrents in pixel cells are emulated by current sources in circuit simulation. The Lenna and Cameraman images were first read into Matlab, which converts the gray tone of every pixel into an integer value between 0 and 255. These values were then downscaled proportionally into the pico range (range of photocurrents in Amperes), and individually assigned to 256x256 current sources. The netlist of the current sources with assigned current values was generated in Matlab, and copied into the netlist of the CS circuit. After circuit simulation, Matlab  $l_1$  magic package was used to reconstruct the images from the sensor outputs. Fig. 9 shows the originals and the reconstructed images. The original images are placed on the left side of the figure. For comparison purposes, Matlab programs were also used to emulate the CS measurement operations implemented on the CS image sensors. The reconstructed images from Matlab emulations are given in the middle panel of the figure. The images reconstructed from CS image sensor outputs are on the right side of the figure. The PSNRs of the reconstructed images are listed underneath the pictures. Images Lena and Cameraman were used in the simulation. It shows that the PSNR values of the reconstructed images from circuit simulation are reasonably close to those obtained from Matlab simulation, validating the functionality of the proposed CS image sensor circuits.

Fig. 9. Reconstructed images from CS measurements

The power consumptions of the proposed CS image sensors are also compared with the conventional image sensor via circuit simulation. The power consumption and energy per frame of the three sensors are listed in Table IV, along with the numbers of key functional blocks in the sensors. Compared to the conventional design, CS image sensors approximately reduce energy dissipation by R times, which is mainly attributed to the reduced number of pixel readout circuits.

The double sampling method used in the above sensor design only removes additive errors and cannot eliminate multiplicative errors caused by variations and mismatches [19]. Simulations were conducted to study the impact of such multiplicative errors on CS image sensor performance. Monte Carlo simulations were first conducted to find out the statistic distribution of the multiplicative errors and then variations following the same distribution were introduced to pixel cell output values in Matlab simulations to examine the PSNRs of the obtained images. For the conventional image sensor, the PSNR values for both Lenna and Cameraman images are degraded to 26.2 dB. Without a calibration, the PSNRs of the images reconstructed from CS measurements are listed in the fourth column of Table V. For comparison purposes, the third column of the Table lists the image PSNR values when variations and mismatches are not considered in simulation, hence labeled as Ideal PSNR. It shows that the multiplicative

|                                                  | [18]                                          | [14]                                                | [12]             | [5]                             | Our work                   |

|--------------------------------------------------|-----------------------------------------------|-----------------------------------------------------|------------------|---------------------------------|----------------------------|

| Pixel cell design                                | 4T conventional                               | 3T cell & local<br>memory (DFF) &<br>logic (3 NAND) | 10T custom       | 3T conventional                 | 3T conventional            |

| Bit lines per column                             | 1                                             | 2                                                   | 2                | One line per pixel              | 1/2                        |

| Meas. vector generation                          | LFSR                                          | LFSR                                                | LFSR             | LFSR                            | N/A                        |

| Additional circuits for<br>supporting rand. Sum. | Multiplexer tree                              | None                                                | None             | Multiplexer tree                | None                       |

| Pixel summation circuit                          | Voltage summation by $\Sigma\Delta$ modulator | Current summation                                   | Charge summation | Charge summation                | Current summation          |

| Comp. ratios                                     | 4, 8, 16<br>(Programmable)                    | 3.3                                                 | 4                | 1.33, 2, 4, 8<br>(Programmable) | 4, 8<br>(Not programmable) |

| Simulated PSNR (dB)                              | 35 (R=4)<br>31.5 (R=8)<br>28.5 (R=16)         | NA                                                  | NA               | NA                              | 37.8 (R=4)<br>32.5(R=8)    |

| Energy/frame (uJ)                                | 195 (R=4)<br>98.4 (R=8)                       | 1278                                                | 3.27-5.8         | NA                              | 1.4 (R=4)<br>0.73 (R=8)    |

TABLE VI

COMPARISON BETWEEN PROPOSED WORK AND EXISTING DESIGNS

TABLE IV

COMPARISON OF IMAGE SENSOR COMPLEXITY & ENERGY DISSIPATION

| Compression rate       | Conv.  | CS Sensor | CS Sensor |

|------------------------|--------|-----------|-----------|

|                        | Sensor | (R=4)     | (R=8)     |

| Power consump. (mW)    | 9.63   | 2.74      | 1.42      |

| Energy/Frame (µJ)      | 4.93   | 1.4       | 0.73      |

| # of bit-lines/row     | 1      | 1/2       | 1/4       |

| # of current conveyors | 256    | 128       | 64        |

| # of DDS & TIA blocks  | 256    | 64        | 32        |

TABLE V IMAGE PSNR VALUES WITH AND WITHOUT CALIBRATIONS

| images | R | Ideal<br>PSNR | PSNR w/o calibr. | PSNR with calibr. 1 | PSNR with calibr. 2 |

|--------|---|---------------|------------------|---------------------|---------------------|

| т      | 4 | 37.8          | 30.4             | 34.6                | 37.8                |

| Lenna  | 8 | 32.5          | 30.3             | 31.8                | 32.5                |

| Camera | 4 | 28.0          | 26.4             | 27.5                | 28.0                |

| man    | 8 | 24.1          | 23.8             | 24.0                | 24.1                |

errors can cause significant image quality degradation for CS image sensors, especially when the compression rate is not very high. For Lenna image, the CS measurement and image reconstruction process also exhibits a de-noise function, noting that the PSNRs of the reconstructed image are higher than that obtained from the conventional image sensor. This is because the image reconstruction process only recovers the significant coefficients of the images and the noise may be represented by less significant coefficients in this case. For Cameraman image, the de-noise effect is not manifested

In the conventional image sensor, every pixel cell can be individually read out and hence the multiplicative errors can be calibrated using 2-point correction or uniform illumination methods [19]. In the proposed CS image sensors, pixels are grouped together to be read out, which prohibits calibrating each pixel cell individually. Two possible calibration schemes were examined in simulation. One is to perform calibration based on CS measurement groups. It requires no hardware modification and can be done in a similar way as that for the conventional image sensors. The drawback is that the same correction parameter will be applied to all the cells in the same CS measurement group. The image PSNR values with this calibration method are listed in the fifth column of Table V. For compression rate of 8, this method achieves satisfactory results. The second calibration method involves adding programmable switches at the input branches of the DDS circuits such that every current conveyor output can be individually read out during the calibration process. This reduces the number of pixels sharing the same correction parameters to one third of that in the first calibration method. The simulation results, listed in the sixth column of Table V, indicate that this calibration adequately mitigates image quality degradations caused by the multiplicative errors.

Finally, Table VI compares the proposed image sensors with existing designs from various aspects. It can be seen that the proposed CS image sensors are the only designs that use conventional compact pixels and meanwhile don't require complex CS measurement circuits. The simplicity of the proposed CS image sensor structure helps it reduce power consumption and achieve high scalability for large pixel arrays. Also, the proposed CS image sensors outperform other designs in terms of reconstructed image quality.

#### VI. CONCLUSIONS

This paper presented a simple and effective CS measurement method for image sensors as well as circuit implementation techniques with using current-mode pixel cells. The developed CS image sensors have dramatically simplified structures and achieved better image quality compared to existing designs. Circuit simulation showed significant power reduction by the developed CS image sensor techniques. The developed CS image sensor techniques are highly suitable for a wide range of applications, including IoT, wearable devices, medical devices, etc.

#### ACKNOWLEDGEMENT

This research has been supported in part by grant NSF IIP 1535658 and the NSF I/UCRC for Embedded Systems at SIUC under grant NSF IIP 1361847. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the authors and do not necessarily reflect the views of the National Science Foundation.

#### REFERENCES

[1] R. Berinde, A. C. Gilbert, P. Indyk, H. Karloff, and M. J. Strauss, "Combining geometry and combinatorics: A unified approach to sparse signal recovery," 46th Annual Allerton Conference on Communication, Control, and Computing, Urbana-Champaign, IL, pp. 798-805, 2008.

- [2] R. F. Bridge and L. McMackin, "High-speed Event Detection Using a Compressive-sensing Hyperspectral-imaging Architecture," US Patent, 0128042, May 23, 2013.

- [3] E. J. Candes, J. Romberg, and T. Tao, "Stable signal recovery from incomplete and inaccurate measurements," Comm. Pure Appl. Math., pp. 1208–1223, vol. 59, no. 8, 2006.

- [4] E. J. Candes and M. B. Wakin, "An Introduction To Compressive Sampling," IEEE Signal Processing Magazine, pp.21-30, vol. 25, no.2, 2008.

- [5] M. Dadkhah, M. D. Jamal, and S. Shirani, "Block-Based CS in a CMOS Image Sensor," IEEE in Sensors Journal, pp.2897-2909, vol.14, no.8, 2014.

- [6] D. L. Donoho, "Compressed sensing," IEEE Transactions on Information Theory, pp.1289–1306, vol. 52, no. 4, 2006.

- [7] A. El Gamal and H. Eltoukhy, "CMOS image sensors," IEEE Circuits and Devices Magazine, pp. 6-20, vol. 21, no. 3, 2005.

- [8] V. Gruev, Z. Yang, J. Van der Spiegel and R. Etienne-Cummings, "Current Mode Image Sensor With Two Transistors per Pixel," IEEE Transactions on Circuits and Systems I: Regular Papers, pp. 1154-1165, vol. 57, no. 6, 2010.

- [9] L. He, H. Chen and L. Carin, "Tree-Structured Compressive Sensing With Variational Bayesian Analysis," in *IEEE Signal Processing Letters*, pp. 233-236, vol. 17, no. 3, March 2010.

- [10] Q. Huynh-Thu and M. Ghanbari, "Scope of validity of PSNR in image/video quality assessment," in Electronics Letters, pp. 800-801, vol. 44, no. 13, 2008.

- [11] L. Jacques, P. Vandergheynst, A. Bibet, V. Majidzadeh, A. Schmid, and Y. Leblebici, "CMOS compressed imaging by random convolution," Proc. IEEE Int. Conf. Acoustics, Speech and Signal Processing, pp. 1113– 1116, 2009.

- [12] N. M. Katic, H. Kamal, M. Kilic, A. Schmid, P. Vandergheynst, and Y. Leblebici, "Power-efficient CMOS image acquisition system based on compressive sampling," Proc. IEEE Intl. Midwest Symp. on Circuits and Systems, pp.1367-1370, 2013.

- [13] S. Leitner, H. Wang and S. Tragoudas, "Compressive Image Sensor Technique with Sparse Measurement Matrix," Proc. 29th IEEE International System on Chip Conference, Seattle, WA, pp. 223-228, September, 2016.

- [14] V. Majidzadeh, L. Jacques, A. Schmid, P. Vandergheynst, and Y. Leblebici, "A 256x256 pixel 76.7 mW CMOS imager/compressor based on real-time in-pixel compressive sensing," Proc. IEEE Int. Symp. Circuits and Systems (ISCAS), pp. 2956–2959, 2010.

- [15] M. Mangia; F. Pareschi; V. Cambareri; R. Rovatti; G. Setti, "Rakeness-Based Design of Low-Complexity Compressed Sensing," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 64, no. 5, pp. 1201-1213, May 2017.

- [16] M. Mangia, R. Rovatti and G. Setti, "Rakeness in the Design of Analogto-Information Conversion of Sparse and Localized Signals," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, pp. 1001-1014, vol. 59, no. 5, May 2012.

- [17] M. L. Mekhalfi, F. Melgani, Y. Bazi and N. Alajlan, "A Compressive Sensing Approach to Describe Indoor Scenes for Blind People," in IEEE Transactions on Circuits and Systems for Video Technology, pp. 1246-1257, vol. 25, no. 7, 2015.

- [18] Y. Oike, and E. A. Gamal, "CMOS Image Sensor With Per-Column ΣΔ ADC and Programmable Compressed Sensing," IEEE Journal of Solid-State Circuits, pp.318-328, vol.48, no.1, 2013.

- [19] R. M. Philipp, D. Orr, V. Gruev, J. Van der Spiegel and R. Etienne-Cummings, "Linear Current-Mode Active Pixel Sensor," IEEE Journal of Solid-State Circuits, pp. 2482-2491, vol. 42, no. 11, 2007.

- [20] R. Robucci, J. D. Gray, L. K. Chiu, J. Romberg, and P. Hasler, "Compressive sensing on a CMOS separable-transform image sensor," Proc. IEEE, pp. 1089–1101, vol. 98, no. 6, 2010.

- [21] B. Shahrasbi and N. Rahnavard, "Model-Based Nonuniform Compressive Sampling and Recovery of Natural Images Utilizing a Wavelet-Domain Universal Hidden Markov Model," in *IEEE Transactions on Signal Processing*, pp. 95-104, vol. 65, no. 1, Jan.1, 1 2017.

- [22] S. Som and P. Schniter, "Compressive Imaging Using Approximate Message Passing and a Markov-Tree Prior," in *IEEE Transactions on Signal Processing*, pp. 3439-3448, vol. 60, no. 7, July 2012.

- [23] D. Takhar, J. Laska, et. al. "A new compressive imaging camera architecture using optical-domain compression," Proc. IS&T/SPIE Symposium on Electronic Imaging, 2006.

- [24] H. Tian, X. Liu, S. Lim, S. Kleinfelder, and A. El. Gamal, "Active pixel sensors fabricated in a standard 0.18-µm CMOS technology," Proc. SPIE, 4306, Sensors and Camera Systems for Scientific, Industrial, and Digital Photography Applications II, pp. 441-450, 2001.

- [25] A. Torralba and A. Oliva, "Statistics of Natural Image Categories," Network: Computation in Neural Systems, pp. 391–412, vol. 14, no. 3, 2003.

- [26] M. Trevisi, R. Carmona-Galán and Á. Rodríguez-Vázquez, "Nonrecursive method for motion detection from a compressive-sampled video stream," 2016 12th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Lisbon, pp. 1-4, 2016.

- [27] X. Wu, X. Liu, M. Zhang and J. Van der Spiegel, "Current Mode Image Sensor With Improved Linearity and Fixed-Pattern Noise," IEEE Transactions on Circuits and Systems I: Regular Papers, pp. 1666-1674, vol. 61, no. 6, 2014.

- [28] http://cvcl.mit.edu/database.htm

Stefan Leitner received the B.S. degree in Mechatronics and Machinery Construction from Management Center Innsbruck in Austria in 2013. He then continued to study at Southern Illinois University Carbondale, where he graduated in December 2016 with a Master degree in Electrical and Computer Engineering, and in May 2017 with a

Master degree in Mathematics. He is currently employed by the Voith Group in Germany, as a Control Engineer in Research and Development. His interests are electric drives, electric vehicles and applied control of Mechatronic systems.

Haibo Wang received the B.Eng. degree from Tsinghua University, Beijing, China, in 1992, the M.Eng. degree from Nanyang Technological University, Singapore, in 1997, and the Ph.D. degree from the University of Arizona, Tucson, in 2002. Currently, he is a professor with the Department of Electrical and Computer Engineering at Southern Illinois University, Carbondale. His current

research interests are mainly in design and test of analog and mixed-signal integrated circuits. He is a recipient of NSF Career award and best paper awards at the SOCC 2014, ISQED 2007, and MIXDES 2001.

**Spyros Tragoudas** received his Diploma degree in Computer Engineering from the University of Patras, Greece (July 1986). He received his M.S. and Ph.D. degrees in Computer Science from the University of Texas at Dallas, USA (August 1988 and August 1991, respectively). He is the Chairman and Professor at the Electrical and Computer Engineering Department, Southern Illinois University at

Carbondale (SIUC), and the Director of the National Science Foundation (NSF) Industry University Cooperative Research Center (IUCRC) on Embedded Systems at the SIUC site. He has held prior appointments with the faculty of the Electrical and Computer Engineering Department, the University of Arizona, and with the faculty of the Computer Science Department, Southern Illinois University at Carbondale.

His current research interests are in the areas of VLSI Design and Test Automation and embedded systems. He has published over 70 journal papers and over 130 articles in peer-reviewed conference proceedings in these areas. He has been funded from industry and federal agencies, including the NSF and the US Navy. He has served on the editorial board of several journals, including the IEEE Transactions on Computers, the VLSI Design journal, and the Journal of Electrical and Computer Engineering. He is a program committee member for many conferences. He has been the program and general chair of the DFTS'09 and DFTS'10, respectively. He received the ICCD'94, ICCD'97 and the ISQED'01 Outstanding Paper Awards for research in VLSI Testing. Dr. Tragoudas is a senior member of the IEEE.