# High-Power T/R circuits for a Multichannel VHF/UHF/HF Ice Imaging Radar

By

# Syed Faiz Ahmed

Submitted to the graduate degree program in Electrical Engineering and Computer Science and the Graduate Faculty of the University of Kansas in partial fulfillment of the requirements for the degree of Master of Science.

| Chairperson Dr. Carlton Leuschen |

|----------------------------------|

|                                  |

| Dr. Fernando Rodriguez - Morales |

| Dr. Christopher Allen            |

Date Defended: 01 October 2015

| The Thesis Committee for Syed Faiz Ahmed                            |   |

|---------------------------------------------------------------------|---|

| certifies that this is the approved version of the following thesis | : |

High-Power T/R circuits for a Multichannel VHF/UHF/HF Ice Imaging Radar

Chairperson Dr. Carlton Leuschen

Date approved: 01 October 2015

#### **Abstract**

This thesis presents the design and implementation of high-power wide-bandwidth transmit/receive (T/R) switches and modules for use in multi-channel ice-penetrating imaging radars. The switches were designed to address the lack of standard off-the shelf (COTS) devices that meet our technical requirements.

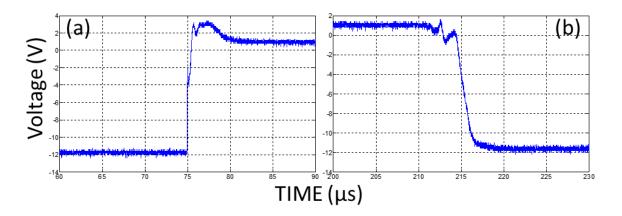

The design of these switches was accomplished using electronic design automation (EDA) tools and implemented with quadrature hybrids and actively-biased PIN diodes. Three different circuits were developed for three different frequency bands: 160-230 MHz (VHF band), 150-600 MHz (VHF/UHF), and 10-45 MHz (HF band). The circuits are capable of transmitting at least 1000 W of peak power and exhibit an insertion loss lower than 1.3 dB for 160-230 MHz, 1.6 dB for 150-600 MHz, and 2.39 dB for 10-45 MHz ranges. A fourth, miniaturized prototype for the 160-230 MHz range was implemented for use in future multi-channel systems. The circuits developed exhibit turn-on times better than 1.3 μs for the VHF/UHF circuits; and 1.5 μs for the HF circuits. The turn-off times were better than 200 ns for the first two bands and 1.36 μs for the HF band. Both the VHF and VHF/UHF have been demonstrated in field operations with two different radar systems.

# **Table of Contents**

| Chapter 1: Introduction                                   | 1-   |

|-----------------------------------------------------------|------|

| 1.1 Motivation                                            | 1 -  |

| 1.2 This Work                                             | 3 -  |

| 1.3 Thesis Outline                                        | 5 -  |

| Chapter 2: Background                                     | 5 -  |

| 2.1.1 T/R Switch Design Overview                          | 5 -  |

| 2.2 Previous Work                                         | 7 -  |

| 2.3 Design Requirements                                   | 8 -  |

| Chapter 3: 150-600 MHz T/R switch                         | 8 -  |

| 3.1 Design Requirements                                   | 8 -  |

| 3.2 Design Overview                                       | 9 -  |

| 3.2.1 Design description                                  | 9 -  |

| 3.2.2 Computer Simulations                                | 18 - |

| 3.3 Small signal measurements                             | 27 - |

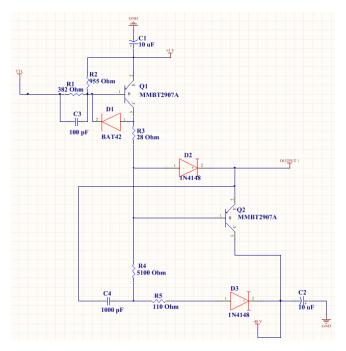

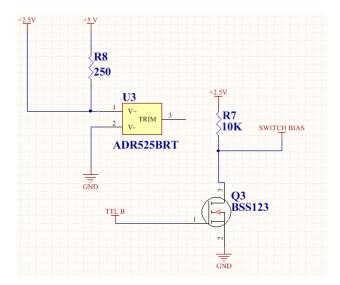

| 3.4 PIN diode Driver Circuit                              | 29 - |

| 3.4.1 Description of the driver                           | 29 - |

| 3.4.2 Computer Simulations                                | 32 - |

| 3.4.3 Driver Components                                   | 35 - |

| 3.4.4 Board design                                        | 37 - |

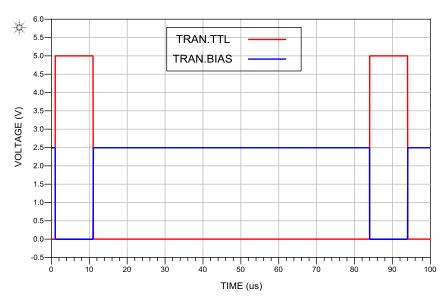

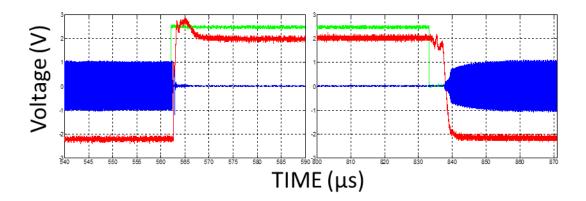

| 3.4.5 PIN Diode Switching Time Measurements               | 38 - |

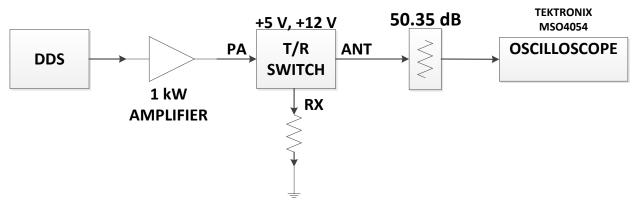

| 3.5 System integration, Laboratory tests, and field tests | 40 - |

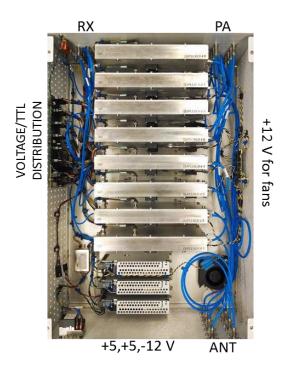

| 3.5.1 Board and Chassis design                            | 40 - |

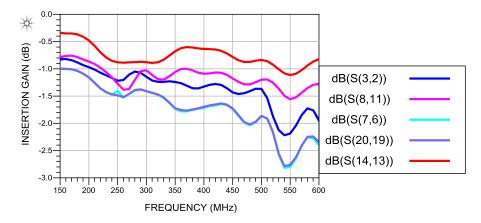

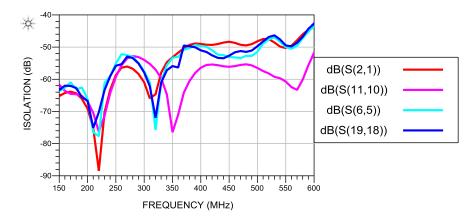

| 3.5.2 Characterization of the Complete Modules            | 42 - |

| 3.5.3 Sample Field results                                | 49 - |

| 4 160-230 MHz T/R switch                                  | 50 - |

| 4.1 Design overview                                       | 50 - |

| 4.1.1 Quadrature Hybrids                                  | 51 - |

| 4.1.2 High Power Amplifier and Driver                     | 51 - |

| 4.1.3 Computer Simulations of the T/R switch              | 52 - |

| 4.2 Small signal measurements                             | 61 - |

| 4.3 System integration, Laboratory tests, and field tests | 63 - |

|     | 4.3.1 Board and Chassis design                            | - 63 - |

|-----|-----------------------------------------------------------|--------|

|     | 4.3.2 Characterization of the Complete Modules            | - 64 - |

|     | 4.3.3 Sample Field Results                                | - 69 - |

| 5 1 | 0-40 MHz T/R switch                                       | - 72 - |

| į   | 5.1 Design Requirements                                   | - 72 - |

| į   | 5.2 Design Overview                                       | - 73 - |

|     | 5.2.1 High Power Side Quadrature Hybrid                   | - 73 - |

|     | 5.2.2 Low Power Side Quadrature Hybrid                    | - 74 - |

|     | 5.2.3 High Pass Filter                                    | - 75 - |

|     | 5.2.4 Bias Tee                                            | - 76 - |

|     | 5.2.5 High Power Amplifier                                | - 77 - |

| į   | 5.3 Computer Simulations                                  | - 77 - |

|     | 5.3.1 Low level simulation                                | - 77 - |

|     | 5.3.2 High Level Simulations                              | - 79 - |

|     | 5.3.3 EM simulations                                      | - 81 - |

| į   | 5.4 Small signal measurements                             | - 86 - |

| į   | 5.5 System integration, Laboratory tests, and field tests | - 88 - |

|     | 5.5.1 Board and Chassis design                            | - 88 - |

|     | 5.5.2 Characterization of the Complete Modules            | - 89 - |

| 6 1 | 60-230 MHz Miniaturized T/R switch                        | - 96 - |

| (   | 5.1 Design Overview                                       | - 96 - |

|     | 6.1.1 Quadrature Hybrids                                  | - 97 - |

|     | 6.1.2 Receiver switch                                     | - 97 - |

| (   | 5.2 Computer Simulations                                  | - 98 - |

|     | 6.2.1 Low level simulation                                | - 98 - |

|     | 6.2.2 High Level Simulations                              | 100 -  |

|     | 6.2.3 EM simulations                                      | 102 -  |

| (   | 5.3 Small signal measurements                             | 108 -  |

| (   | 5.4 PIN Diode Driver Circuit                              | 110 -  |

| (   | 5.5 System integration, Laboratory tests, and field tests | 111 -  |

|     | 6.5.1 Board and Chassis design                            | 111 -  |

|     | 6.5.2 Characterization of the Complete Modules            | 112 -  |

| 7 C | onclusion and Future work                                 | 115 -  |

| References 116 |

|----------------|

|----------------|

# **Table of Figures**

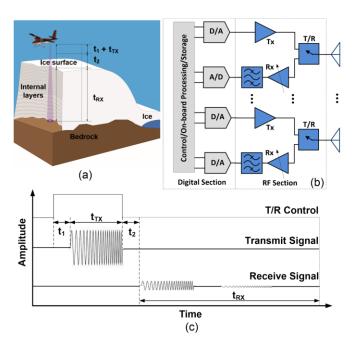

| Figure 1.1: : (a) Illustration of airborne ice sounding radar; (b) Simplified system block diagram (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Transmit/receive timing diagram [14]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1 -      |

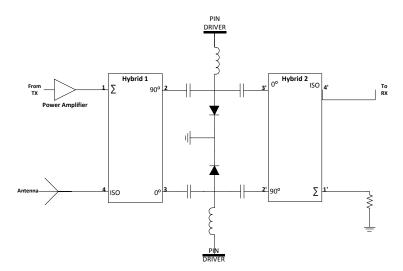

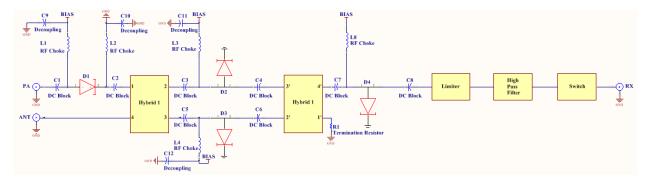

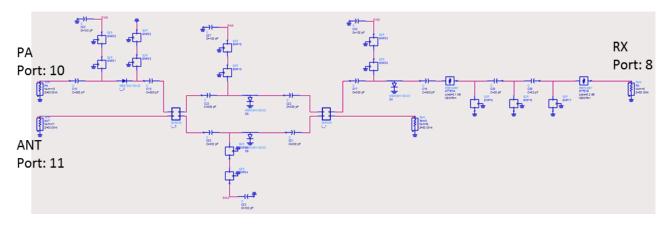

| Figure 3.1: Schematic diagram of the 150-600 MHz T/R switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10 -     |

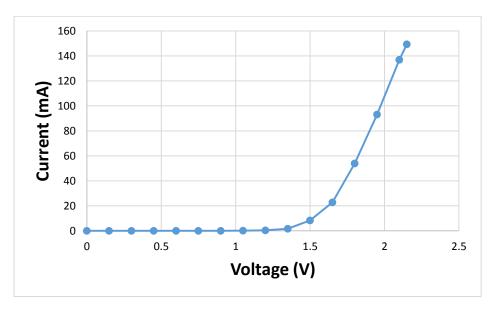

| Figure 3.2: Measured I-V curve for the MEST2G-150-020-CM26 series PIN diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13 -     |

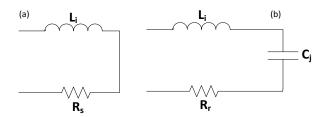

| Figure 3.3: PIN diode equivalent circuits: (a) forward bias; (b) reverse bias [18]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14 -     |

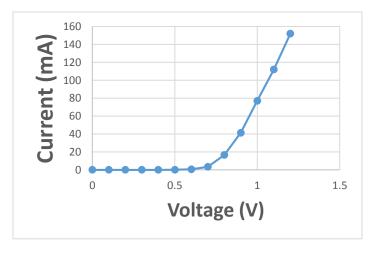

| Figure 3.4: Measured I-V curve for THE MSWSH-100-30 PIN diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15 -     |

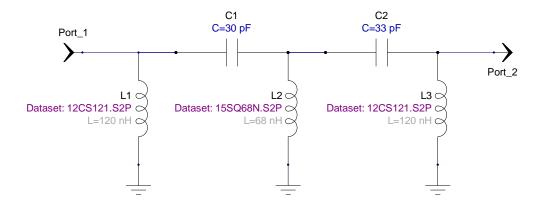

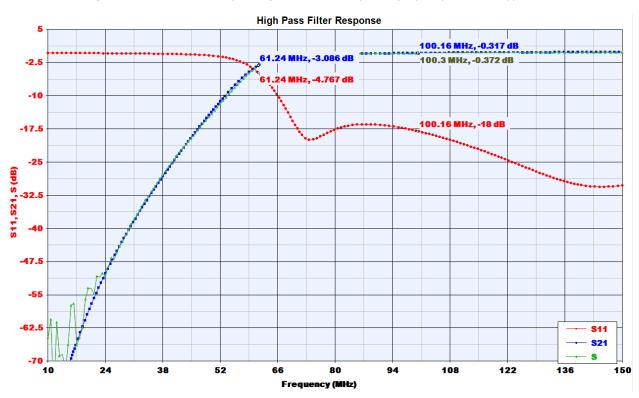

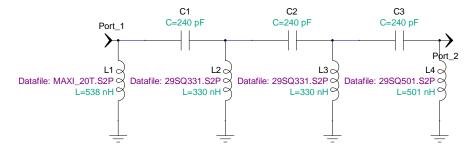

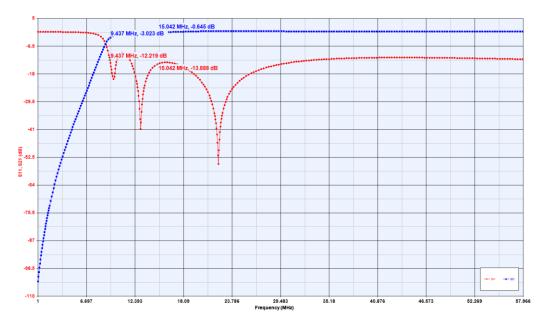

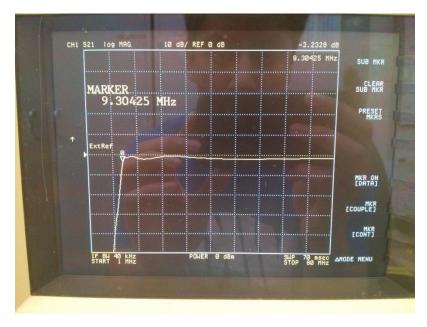

| Figure 3.5: Simulated (Blue) vs measured (Green) high pass filter response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17 -     |

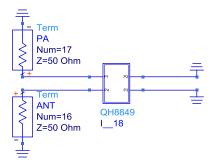

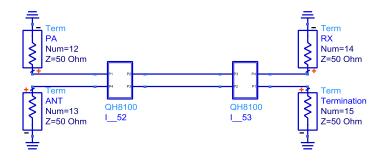

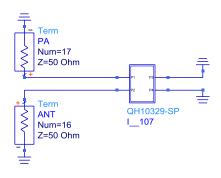

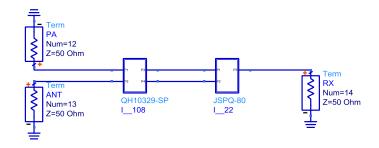

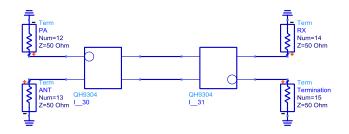

| Figure 3.6: Simulation setup representing semi-ideal behavior in transmit state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19 -     |

| Figure 3.7: Simulation setup representing semi-ideal behavior of the circuit in receive state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19 -     |

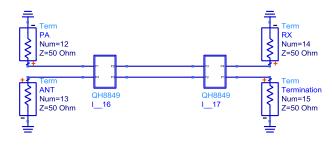

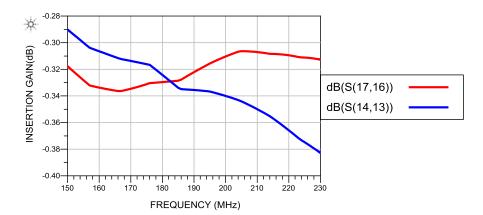

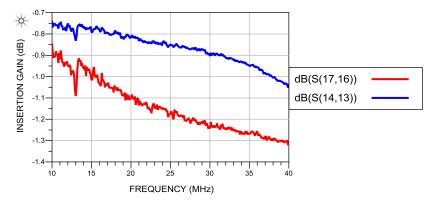

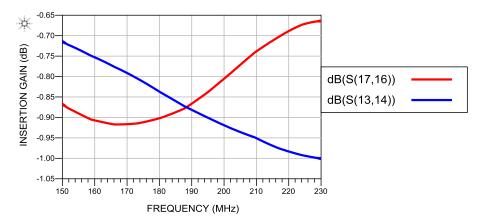

| Figure 3.8: Simulated response for the insertion gain during (a) Transmit between PA and ANT poi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | rts .    |

| (S(17,16)); (b) Receive between ANT and RX ports (S(13,14))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20 -     |

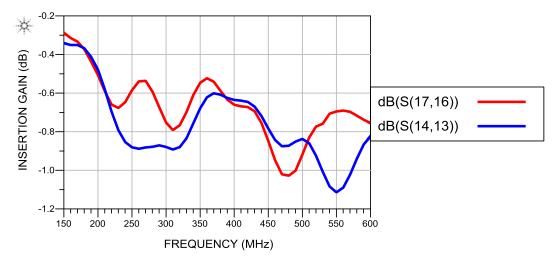

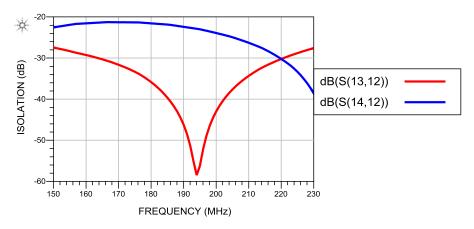

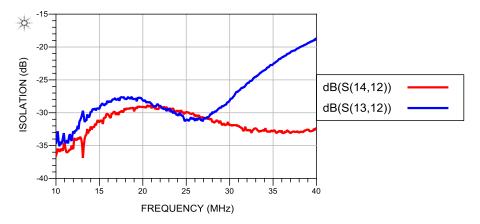

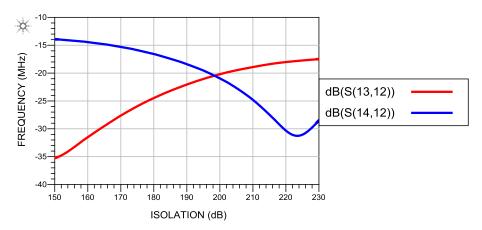

| Figure 3.9: Simulated isolation in receive mode between: (a) PA and ANT ports (S(13,12)); (b) PA a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nd RX    |

| ports (S(14,12))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20 -     |

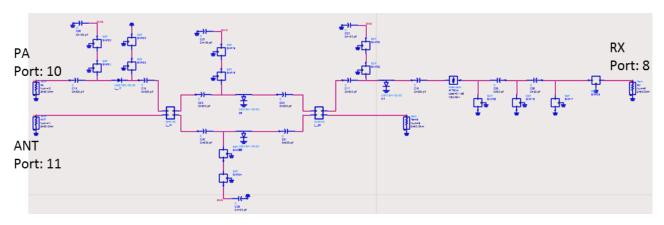

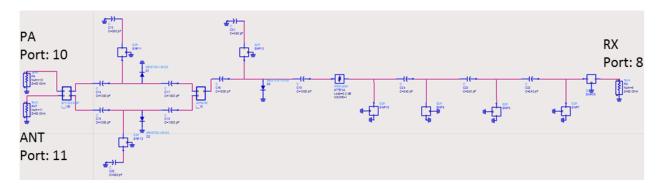

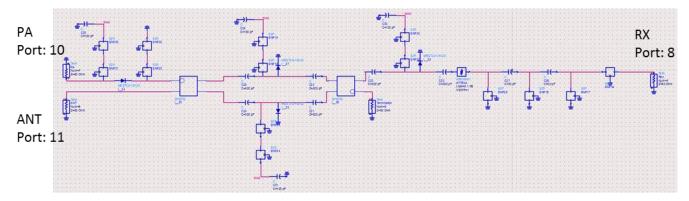

| Figure 3.10: ADS simulation setup including first order effects in all the components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21 -     |

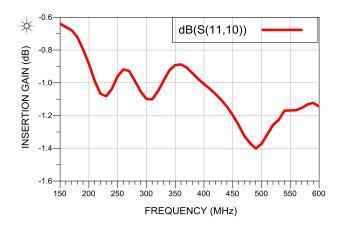

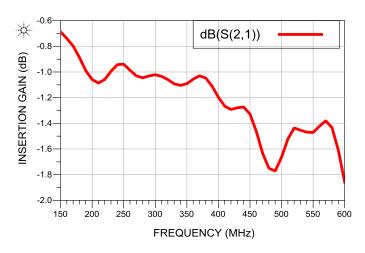

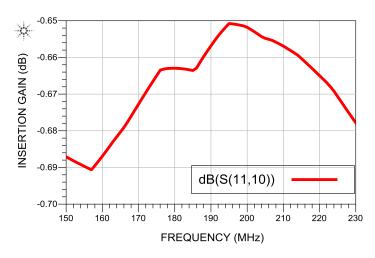

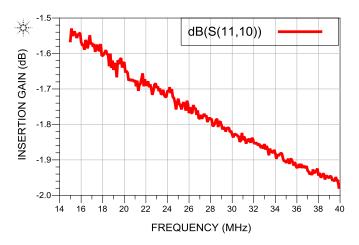

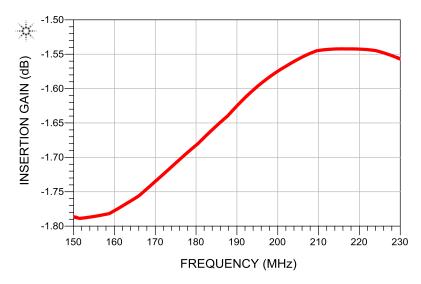

| Figure 3.11: Simulated insertion gain between PA and ANT ports (S(11,10) during transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21 -     |

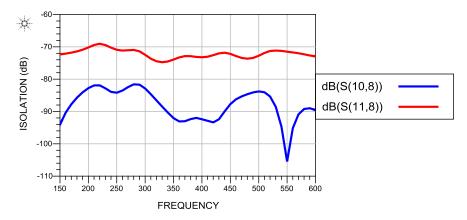

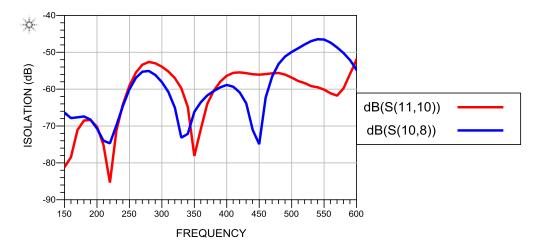

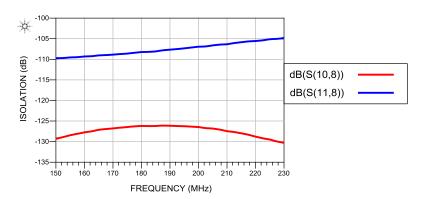

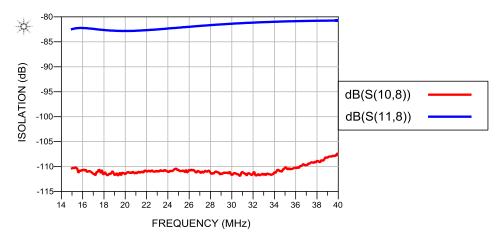

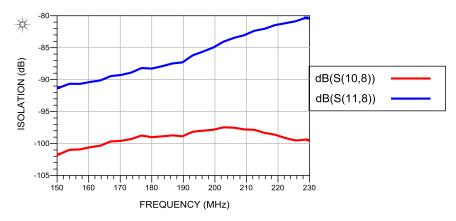

| Figure 3.12: Simulated coupling between (a) PA and RX ports (S(10,8)); (b) ANT and RX ports (S(11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ,8))     |

| during transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22 -     |

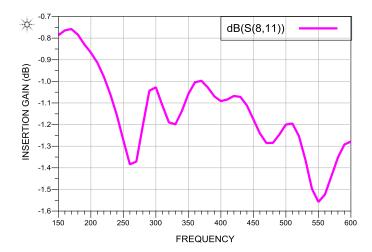

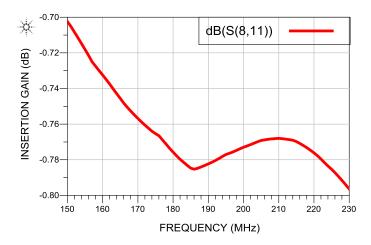

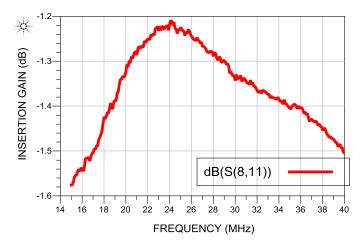

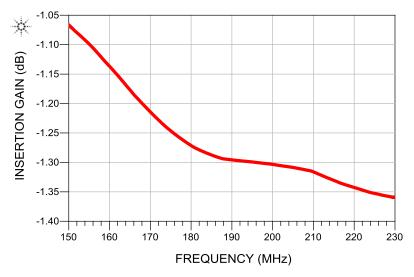

| Figure 3.13: Simulated insertion gain between ANT and RX ports (S(8,11)) during receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22 -     |

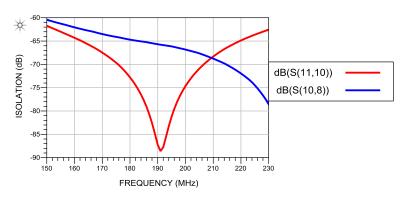

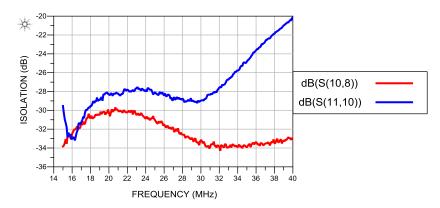

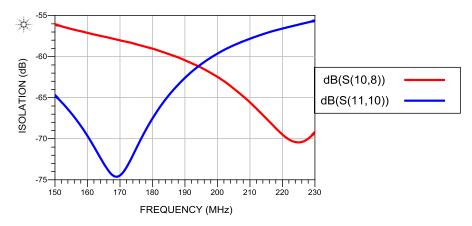

| Figure 3.14: Simulated coupling between (a) PA and ANT ports (S(11,10); (b) PA and RX ports (S(10,10)) | ),8))    |

| during receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23 -     |

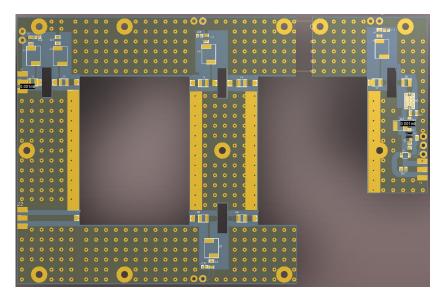

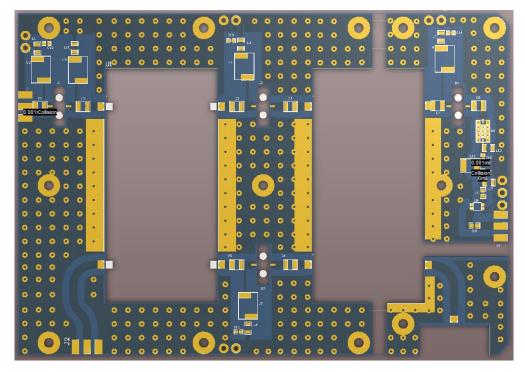

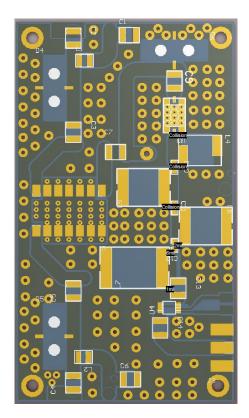

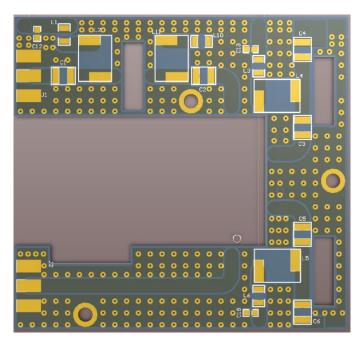

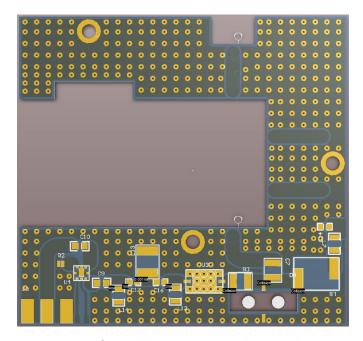

| Figure 3.15: T/R switch PCB layout in Altium Designer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24 -     |

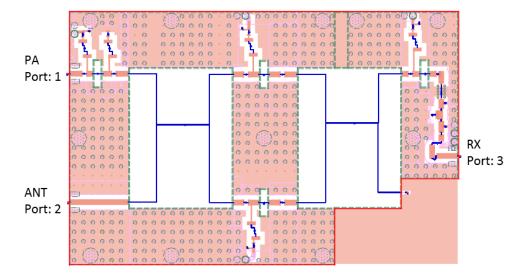

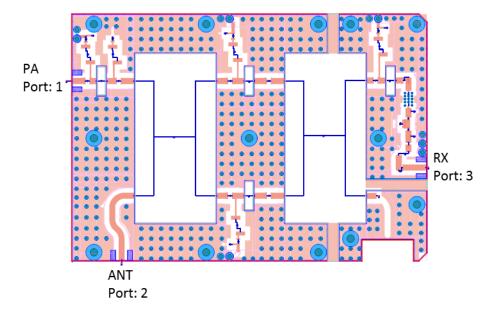

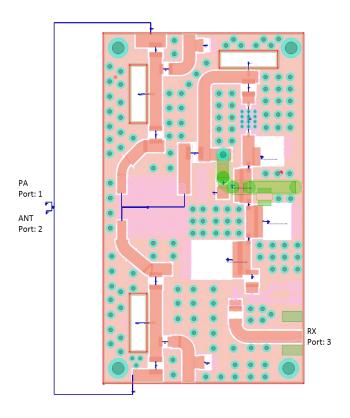

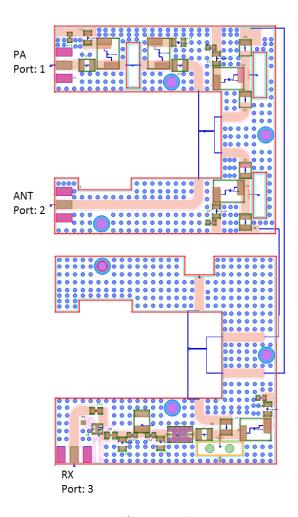

| Figure 3.16: Circuit/EM co-simulation setup in ADS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24 -     |

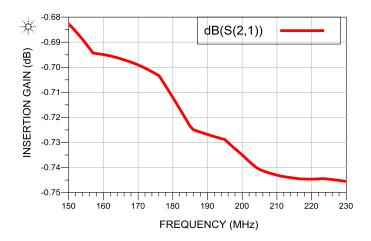

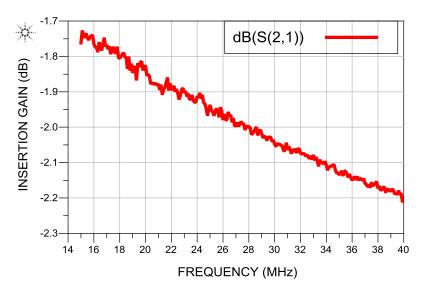

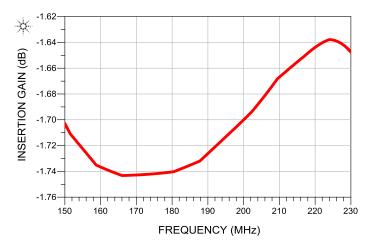

| Figure 3.17: Simulated insertion gain between PA and ANT ports during transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25 -     |

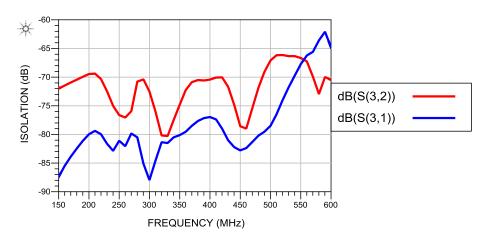

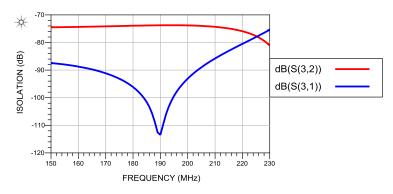

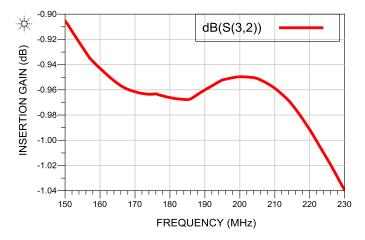

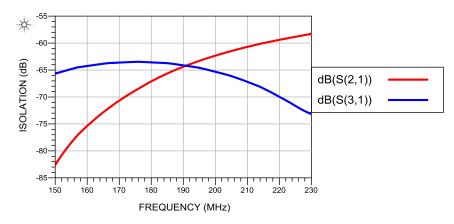

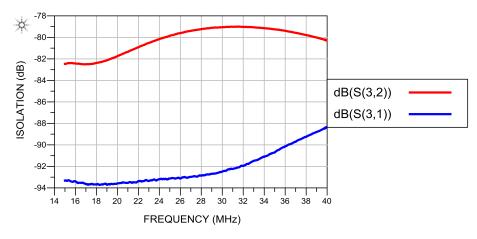

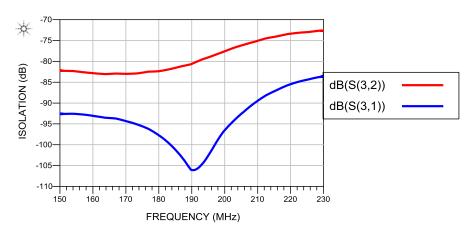

| Figure 3.18: Simulated coupling between (a) ANT and RX (S(3,2)); (b) PA and RX (S(3,1)) during tra 25 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | nsmit    |

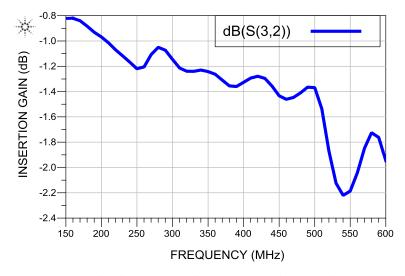

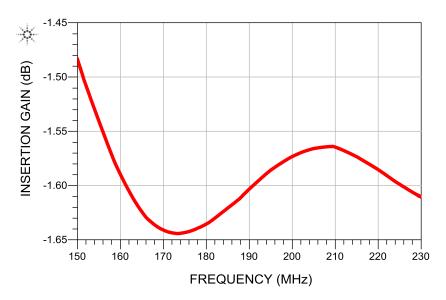

| Figure 3.19: Simulated insertion gain between ANT and RX ports during receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26 -     |

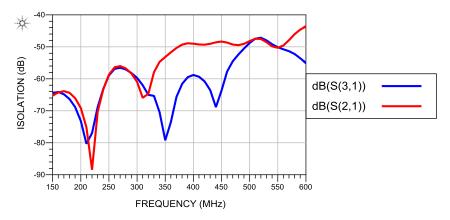

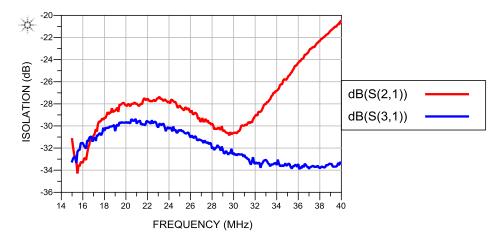

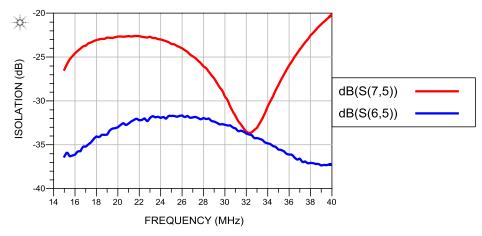

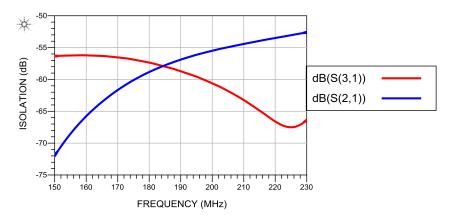

| Figure 3.20: Simulated coupling between (a) PA and ANT (S(2,1); (b) PA and RX (S(3,1)) during rece                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

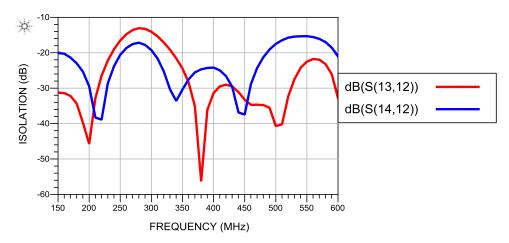

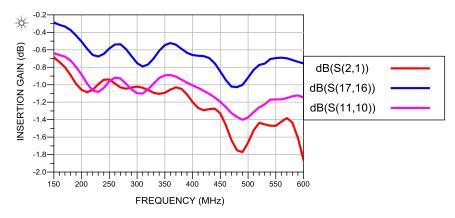

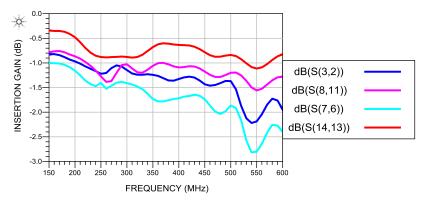

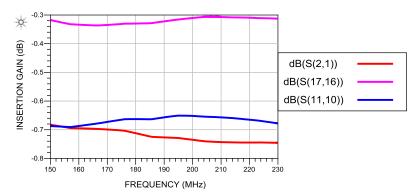

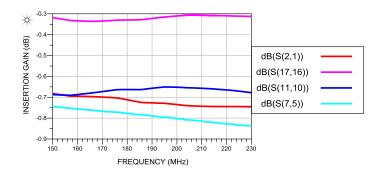

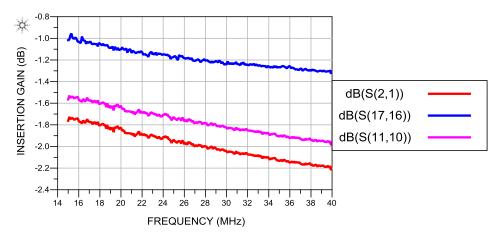

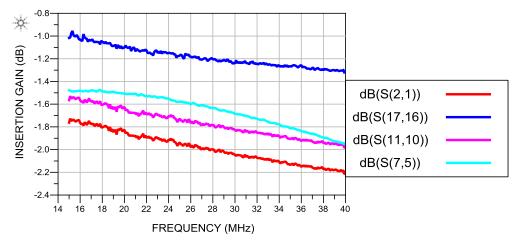

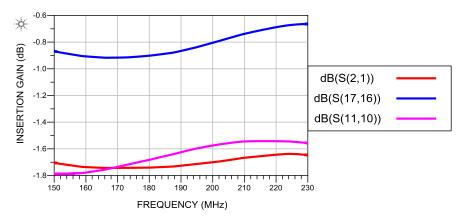

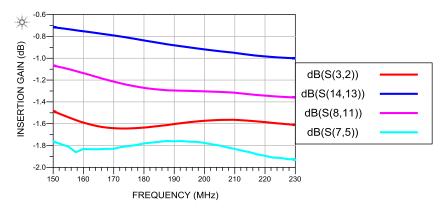

| Figure 3.21: Simulated insertion gain between PA and ANT during transmit (a) Ideal (S(17,16)); (b) level (S(11,10)); (c) EM/Circuit Co-simulation (S(2,1))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -        |

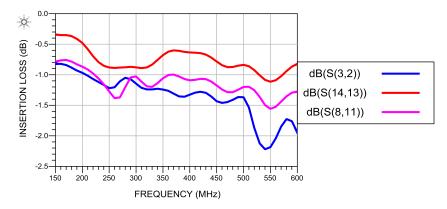

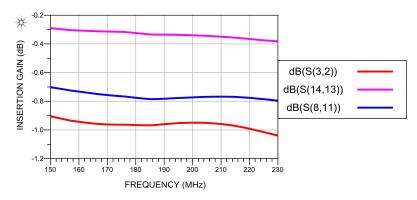

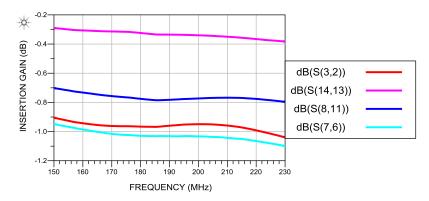

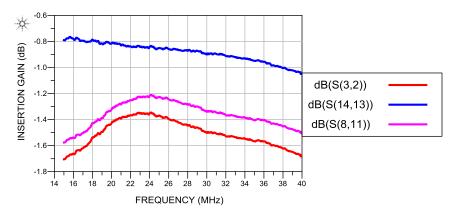

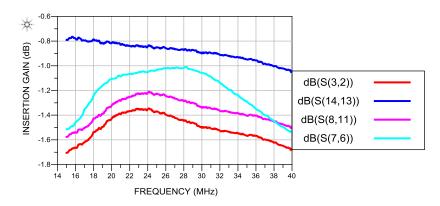

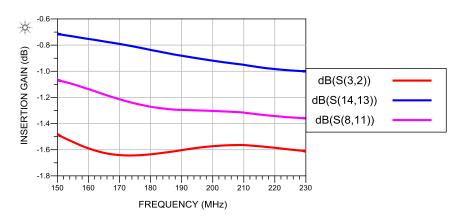

| Figure 3.22: Simulated insertion gain between ANT and RX during receive (a) Ideal (S(14,13)); (b) H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

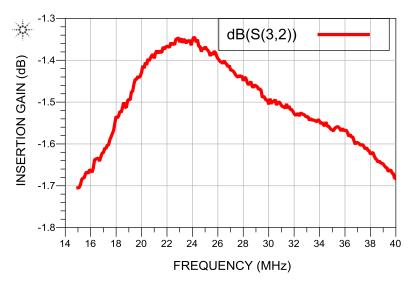

| level (S(8,11)); (c) EM/Circuit Co-simulation (S(3,2))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _        |

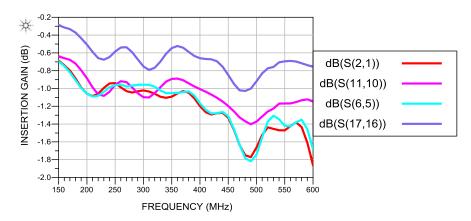

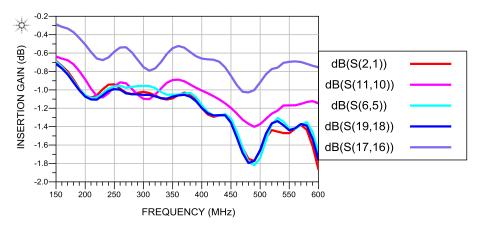

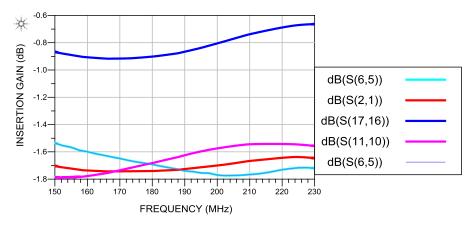

| Figure 3.23: Simulated vs measured insertion gain between PA and ANT during transmit (a) Ideal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| (S(17,16)); (b) High level (S(11,10)); (c) EM/Circuit Co-simulation (S(2,1)); (d) measured (S(6,5))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28 -     |

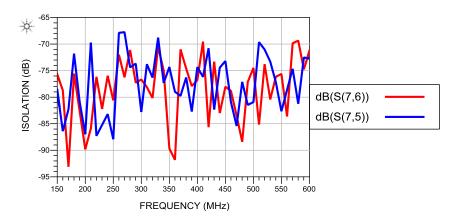

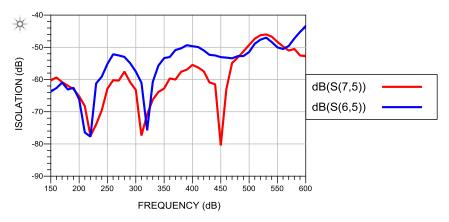

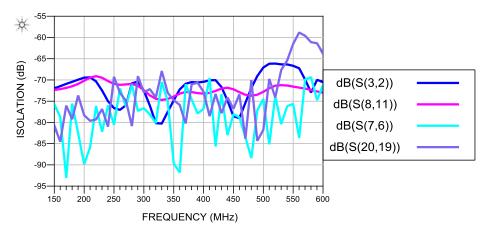

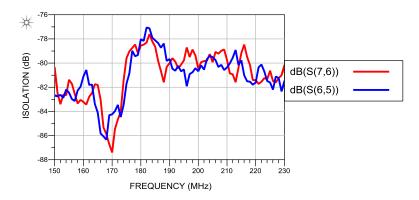

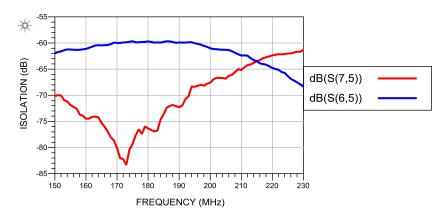

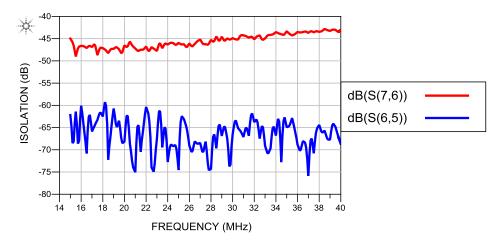

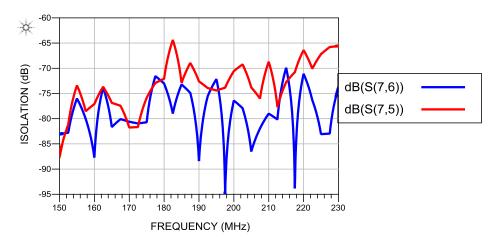

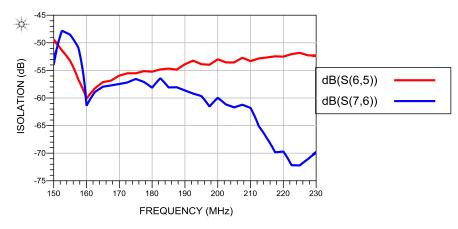

| Figure 3.24: Measured coupling during transmit between (a) PA and RX (S(7,6)); (b) ANT and RX (S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

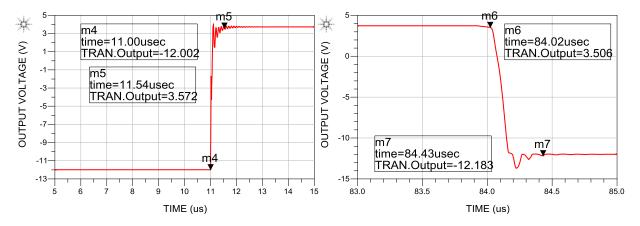

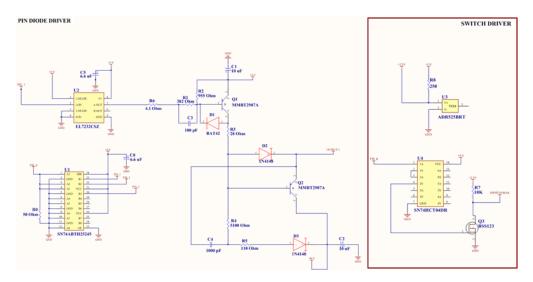

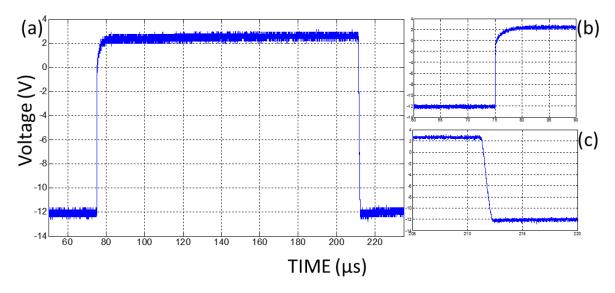

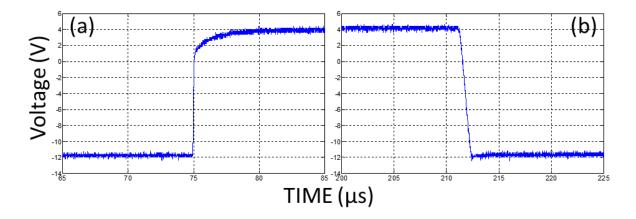

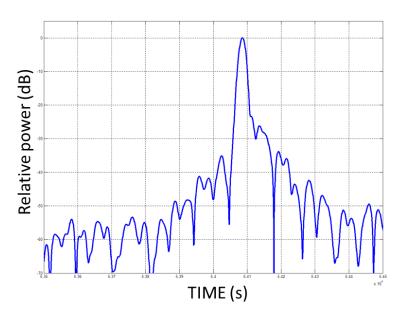

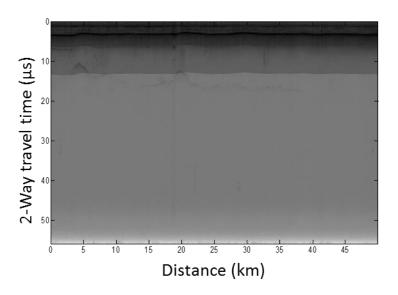

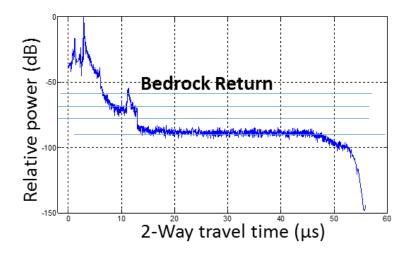

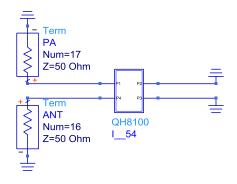

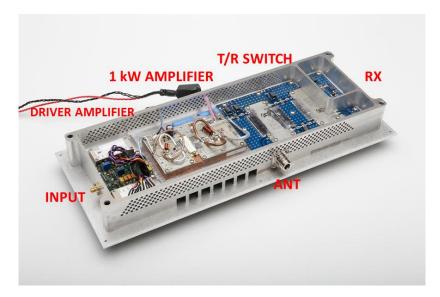

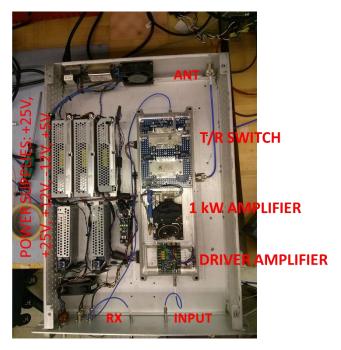

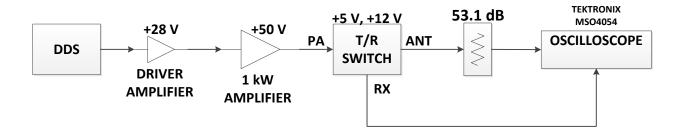

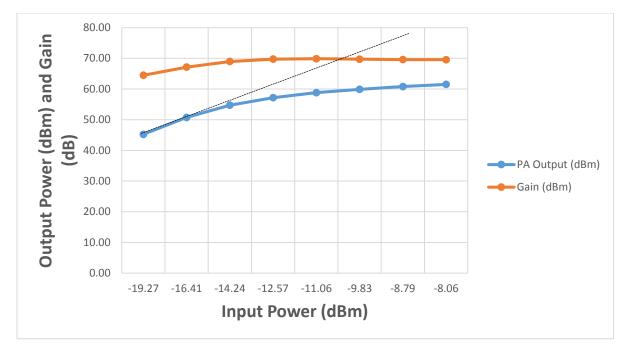

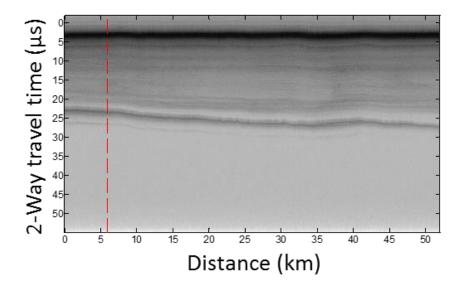

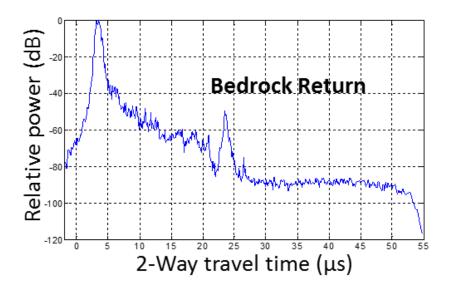

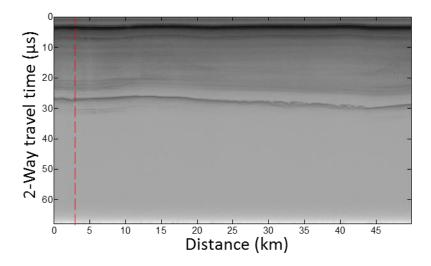

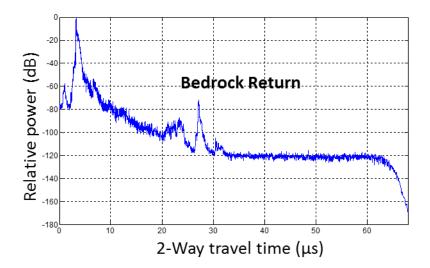

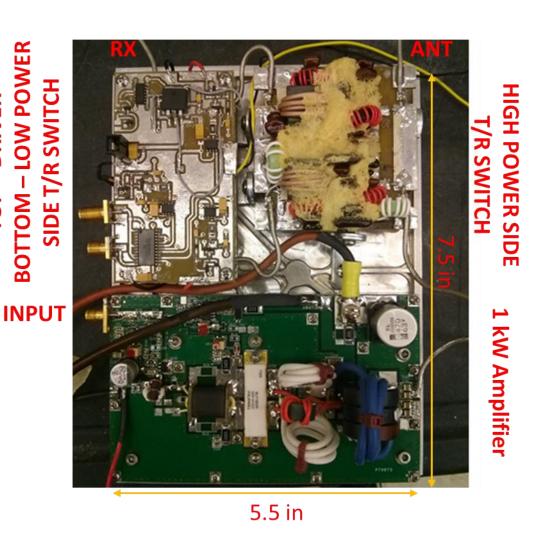

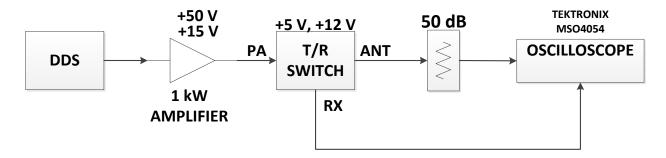

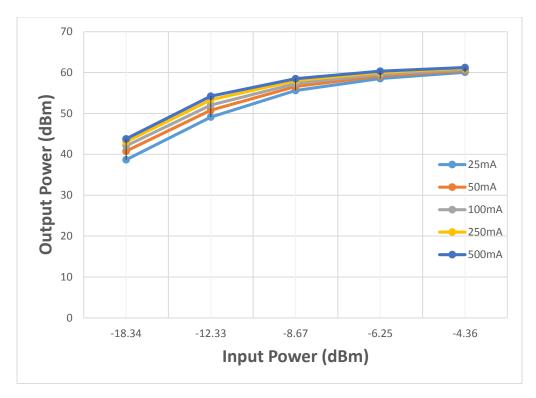

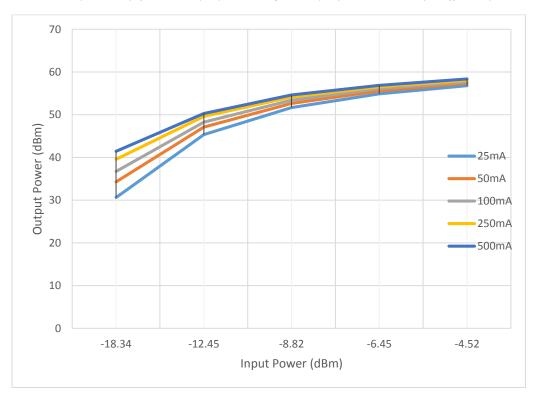

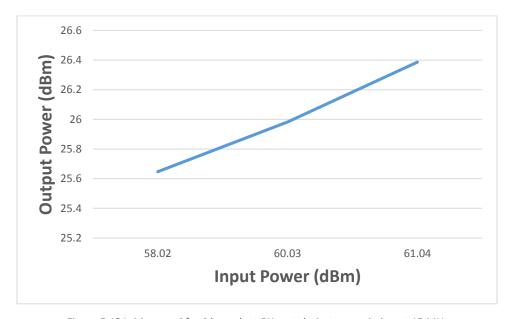

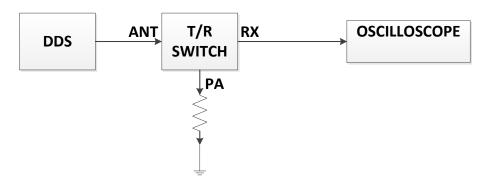

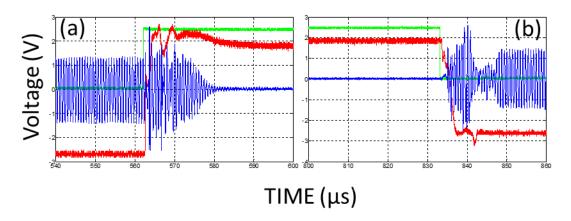

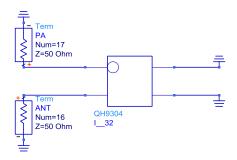

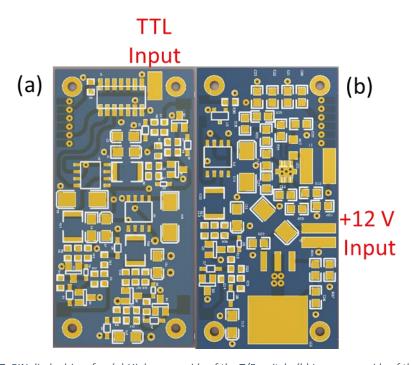

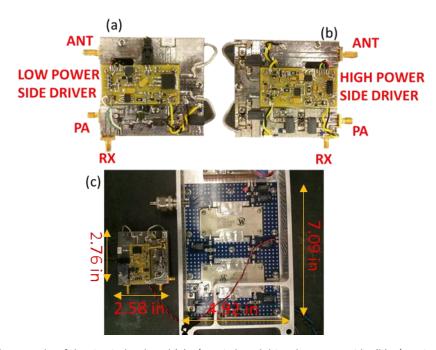

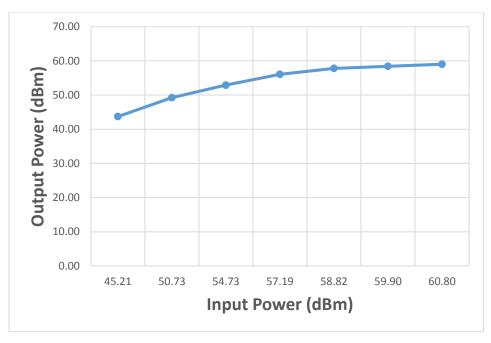

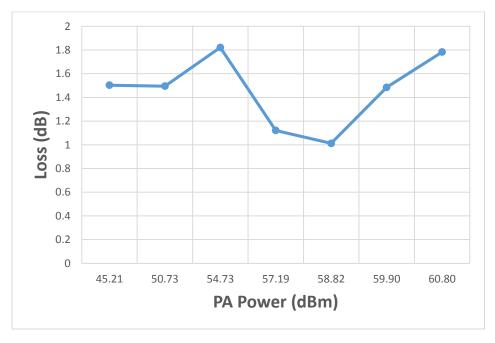

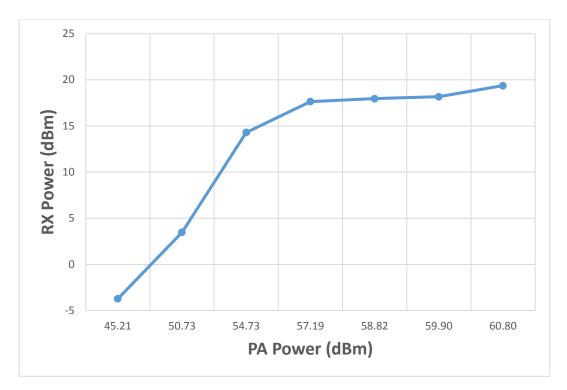

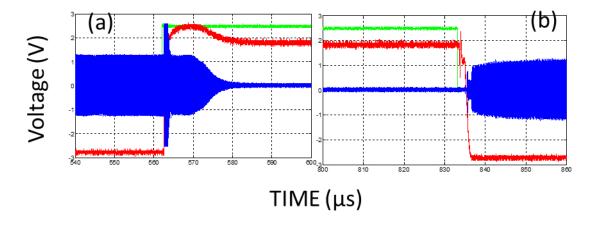

| 28 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ( )- //  |