# **Electrochemical Double Layered Capacitor Development and Implementation System**

| п | г. |    |

|---|----|----|

|   | к  | T. |

|   |    |    |

# Gavin P. Strunk

Submitted to the graduate degree program in Department of Mechanical Engineering and the Graduate Faculty to the University of Kansas in parital fulfillment of the requirements for the degree of Doctor of Philosophy.

| Dr. Terry N. Faddis, Chair         |

|------------------------------------|

|                                    |

| Dr. Carl Luchies, Committee Member |

|                                    |

| Dr. James Miller, Committee Member |

|                                    |

| Dr. Sara Wilson, Committee Member  |

|                                    |

| Dr. Xinmai Yang, Committee Member  |

Date Defended:

| The Dissertation Committee for Gavin P. Strunk certifies that this is the approved version of the following dissertation: |

|---------------------------------------------------------------------------------------------------------------------------|

| Electrochemical Double Layered Capacitor Development and Implementation System                                            |

|                                                                                                                           |

|                                                                                                                           |

| Dr. Terry N. Faddis, Chair                                                                                                |

### **ABSTRACT**

Electrochemical Double Layered Capacitors (EDLC's) are becoming a more popular topic of research for hybrid power systems, especially vehicles. They are known for their high power density, high cycle life, low internal resistance, and wider operating temperature compared to batteries. They are rarely used as a standalone power source; however, because of their lack of energy density compared to batteries and fuel cells. Researchers are now discovering the benefits of using them in hybrid systems. The increased complexity of a hybrid power source presents many challenges. A major drawback of this complexity is the lack of design tools to assist a designer in translating a simulation all the way to a full scale implementation.

A full spectrum of tools was designed to assist designers at all stages of implementation including: single cell testing, a multi-cell management system, and a full scale vehicle data acquisition system to monitor performance. First, the full scale vehicle data acquisition is described. The system is isolated from the electric shuttle bus it was tested on to allow the system to be ported to other vehicles and applications. This was done to modularize the system to characterize a wide variety of full scale applications. Next, a single cell test system was designed that allows the designer to characterize cell specifications, as well as, test control and safety systems in a controlled environment. The goal is to ensure safety systems can be thoroughly tested to ensure robustness as the bank is scaled up. This system also includes simulation models that provide examples of using the simulation to predict the behavior of a cell and the test system to validate the results of the simulation. This information is then used by the designer to more effectively design sensor ranges for the bank.

Finally, a multi-cell EDLC management system was designed to implement a bank. It incorporates 12 series EDLC cells per control module, and the modular design allows expandability in parallel and series to fit any application and number of cells required. Lastly, test procedures were run to validate the proper operation of the systems.

### **ACKOWLEDGEMENTS**

I would like to extend a special thanks to my graduate advisor, Dr. Terry N. Faddis, for his guidance and support during this research. He has truly given me an unmeasurable amount of valuable experience and knowledge. I would also like to thank my committee members, Dr. Carl Luchies, Dr. James Miller, Dr. Sara Wilson, and Dr. Xinmai Yang. They have all given excellent advice and support throughout my time at the University of Kansas.

Next, I would like to thank the University of Kansas Transportation Research Institute and the University of Kansas Medical Center for providing me with funding for my research.

Finally, I would like to thank my family and friends whose support has been vital to my success. I would like to give special thanks to my parents, Richard and Benita, for their advice, support, and encouragement. To my sister Sara, your support was also very much appreciated. Thanks.

# TABLE OF CONTENTS

| LI | ST OF FIGURES                                  | viii |

|----|------------------------------------------------|------|

| NO | OMENCLATURE                                    | X    |

| 1  | INTRODUCTION                                   | 1    |

| 1. | 1.1. Hybrid Electric Vehicles and Control      |      |

|    | 1.2. Current Power Sources                     |      |

|    | 1.3. Problem Identification                    |      |

|    | 1.4. Research Objective                        |      |

|    | 1.5. Future Impact                             |      |

|    | 1.6. References                                |      |

| 2. | ELECTRIC SHUTTLE BUS DATA ACQUISITION RETROFIT | 11   |

|    | 2.1. Introduction                              |      |

|    | 2.2. Design Requirements                       |      |

|    | 2.3. Data Acquisition System.                  |      |

|    | 2.4. Sensor Selection                          | 19   |

|    | 2.5. Software                                  | 21   |

|    | 2.6. Test Procedures                           | 24   |

|    | 2.7. Results                                   |      |

|    | 2.8. Conclusion                                |      |

|    | 2.9. Recommendations                           |      |

|    | 2.10. References                               | 37   |

| 3. | EDLC TEST SYSTEM                               |      |

|    | 3.1. Introduction                              |      |

|    | 3.2. EDLC Properties                           |      |

|    | 3.2.1. EDLC Voltage                            |      |

|    | 3.2.2. EDLC Current                            |      |

|    | 3.2.3. EDLC Temperature                        |      |

|    | 3.3. Simulation                                |      |

|    | 3.3.1. Constant Voltage Model                  |      |

|    | 3.3.2. Constant Current Model                  | 47   |

|    | 3.4. Physical Test System                      |      |

|    | 3.4.1. Hardware Configuration                  |      |

|    | 3.4.2. Software Configuration                  |      |

|    | 3.4.3. Measurements                            |      |

|    | 3.4.4. Programmable Load                       |      |

|    | 3.5. Results                                   |      |

|    | 3.6. Conclusion                                |      |

|    | 3.7. References                                | 65   |

| 4. | EDLC MANAGEMENT SYSTEM                         |      |

|    | 4.1. Introduction                              | 66   |

| 4.2. Hardware System                      | 68  |

|-------------------------------------------|-----|

| 4.3. Software System                      | 73  |

| 4.4. Results                              |     |

| 4.5. Conclusion                           |     |

| 4.6. References                           |     |

| 5. CONCLUSIONS AND RECOMMENDATIONS        | 95  |

| APPENDIX A: EDLC CHARGE DERIVATION        | 98  |

| A.1 Constant Voltage Source               | 98  |

| A.2 Constant Current Source               |     |

| APPENDIX B: EDLC TEST SYSTEM DESIGN       | 100 |

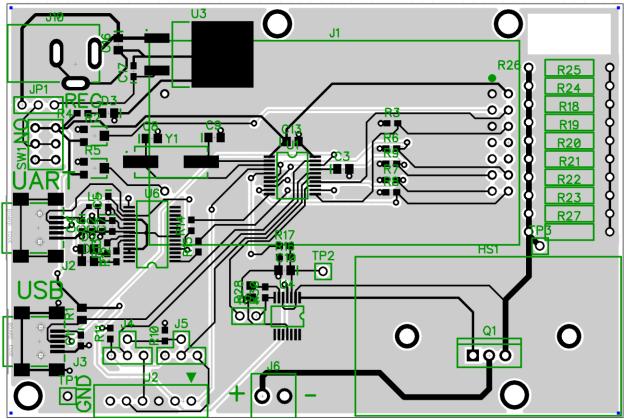

| B.1 Schematics                            |     |

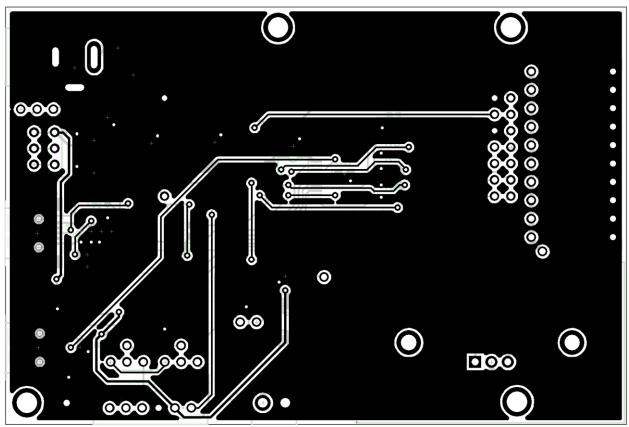

| B.2 PCB Layout Diagrams                   |     |

| B.3 Code                                  |     |

| APPENDIX C: PROGRAMMABLE LOAD DESIGN      | 133 |

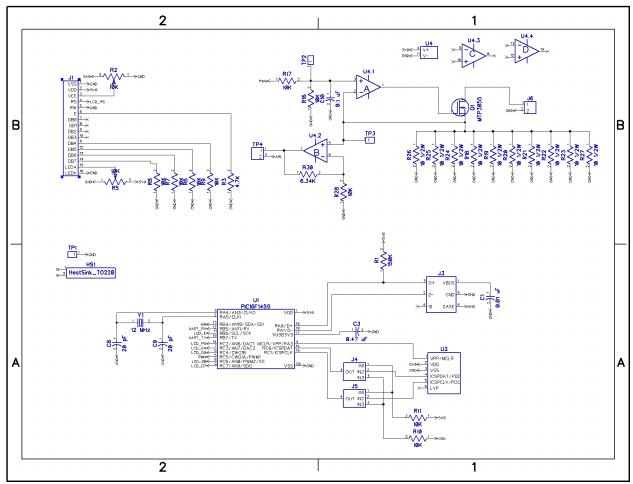

| C.1 Schematics                            | 133 |

| C.2 PCB Layout Diagrams                   |     |

| C.3 Bill of Materials                     |     |

| C.4 Code                                  | 140 |

| APPENDIX D: EDLC MANAGEMENT SYSTEM DESIGN | 154 |

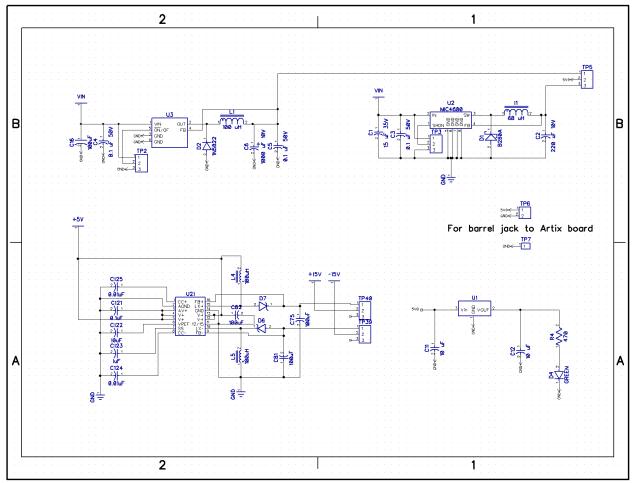

| D.1 Schematics                            |     |

| D.2 PCB Layout Diagrams                   |     |

| D.3 Bill of Materials                     |     |

| D.3 Code                                  |     |

# LIST OF FIGURES

| Figure 2.1.1   | : University of Kansas Electric Shuttle Bus                | 11 |

|----------------|------------------------------------------------------------|----|

| Figure 2.3.1   | : Custom Designed Electric Bus Data Acquisition System     | 16 |

| Figure 2.3.2   | : NI cRIO-9014 Controller with 8 Slot Chassis              |    |

| Figure 2.5.1   | : University of Kansas Shuttle Bus Data Acquisition System | 22 |

| Figure 2.7.1   | : Main Battery Pack Voltage                                |    |

| Figure 2.7.2   | : Main Battery Pack Current                                | 26 |

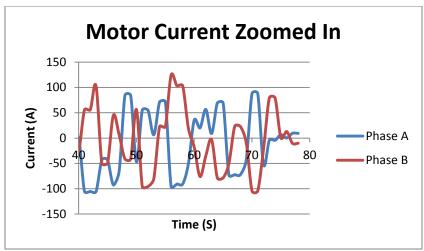

| Figure 2.7.3   | : Phase A and B Motor Current                              | 27 |

| Figure 2.7.4   | : Zoomed in Motor Current                                  | 28 |

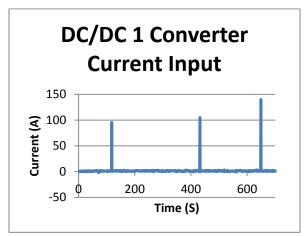

| Figure 2.7.5   | : DC/DC 1 Input Current                                    | 28 |

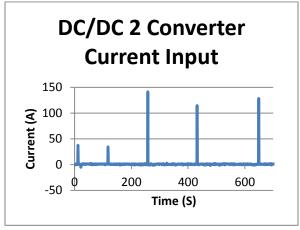

| Figure 2.7.6   | : DC/DC 2 Input Current                                    | 28 |

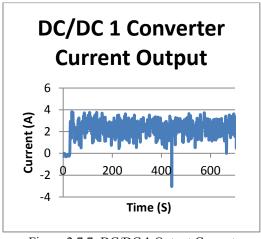

| Figure 2.7.7   | : DC/DC 1 Output Current                                   | 29 |

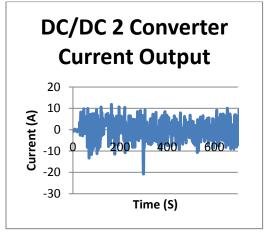

| Figure 2.7.8   | : DC/DC 2 Output Current                                   | 29 |

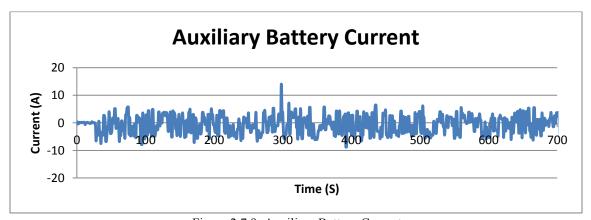

| Figure 2.7.9   | : Auxiliary Battery Current                                | 29 |

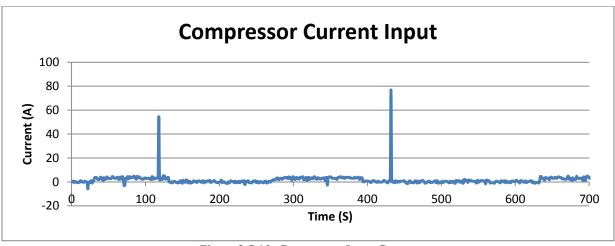

| Figure 2.7.10  | : Compressor Input Current                                 | 30 |

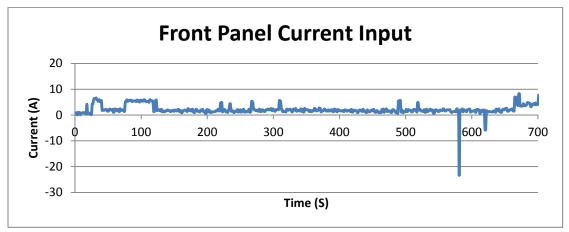

| Figure 2.7.11  | : Front Panel Input Current                                | 31 |

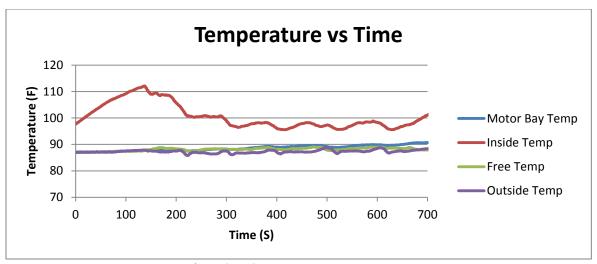

| Figure 2.7.12  | : Temperature Measurements                                 | 32 |

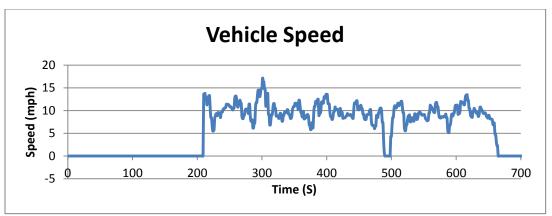

| Figure 2.7.13  | : Vehicle Speed                                            | 33 |

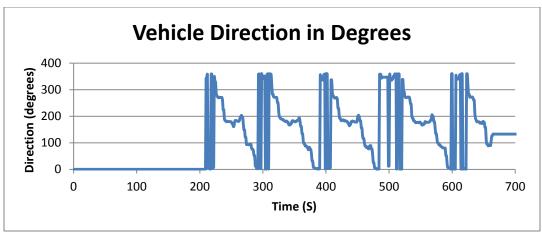

| Figure 2.7.14  | : Vehicle Direction                                        | 34 |

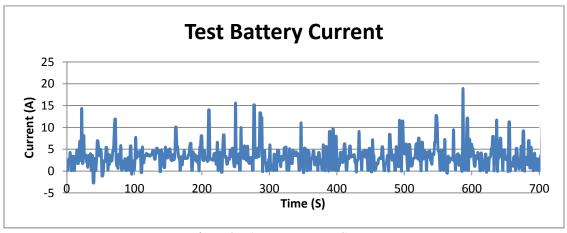

| Figure 2.7.15  | : Test Battery Current                                     | 34 |

| Figure 3.1.1   | : Electric Mass Transit Vehicle – Design Target            | 39 |

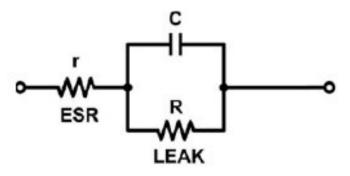

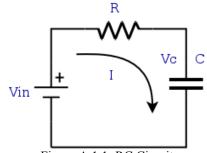

| Figure 3.3.1.1 | : EDLC Circuit Model                                       | 44 |

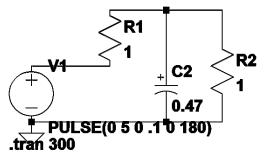

| Figure 3.3.1.2 | : Constant Voltage Model                                   | 45 |

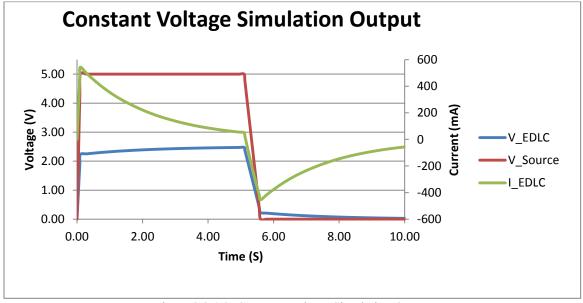

|                | : Constant Voltage Simulation Output                       |    |

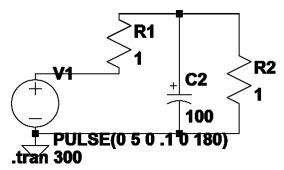

| Figure 3.3.1.4 | : Constant Voltage 100 F Cell Model                        | 46 |

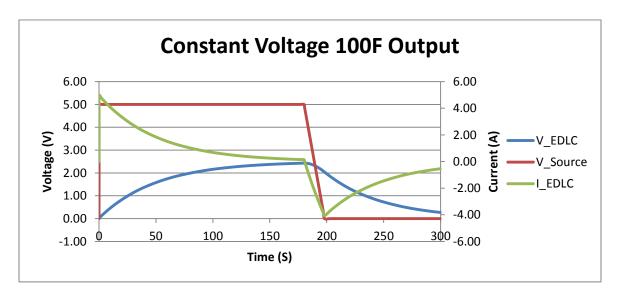

| Figure 3.3.1.5 | : Constant Voltage Simulation 100 F Output                 | 46 |

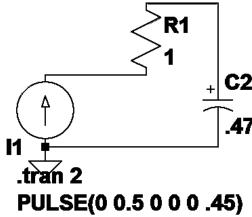

| Figure 3.3.2.1 | : Constant Current Model                                   | 48 |

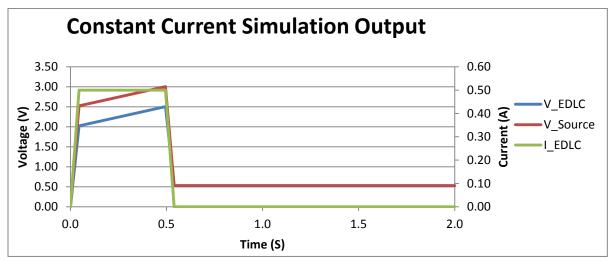

| Figure 3.3.2.2 | : Constant Current Simulation Output                       | 48 |

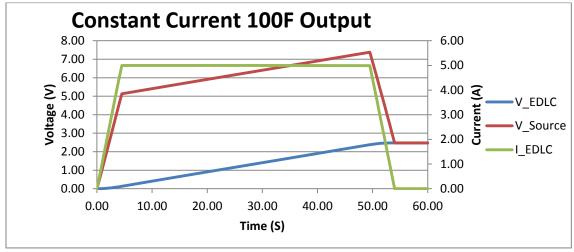

| Figure 3.3.2.3 | : Constant Current 100 F Output                            | 49 |

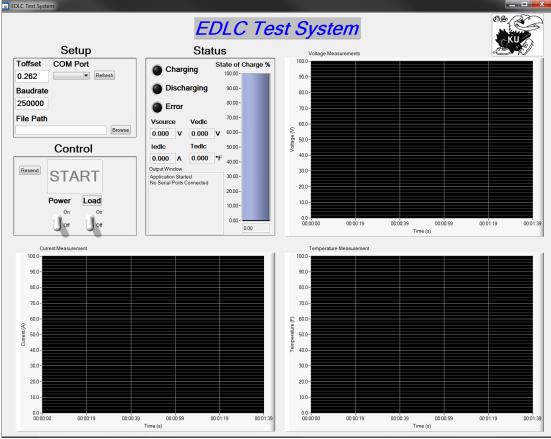

| Figure 3.4.2.1 | : LabVIEW CVI User Interface for EDLC Test System          | 54 |

|                | : Programmable Load                                        |    |

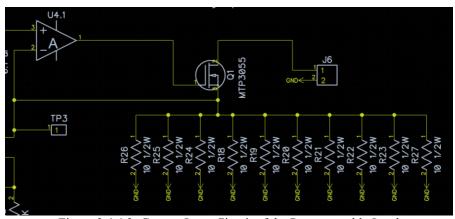

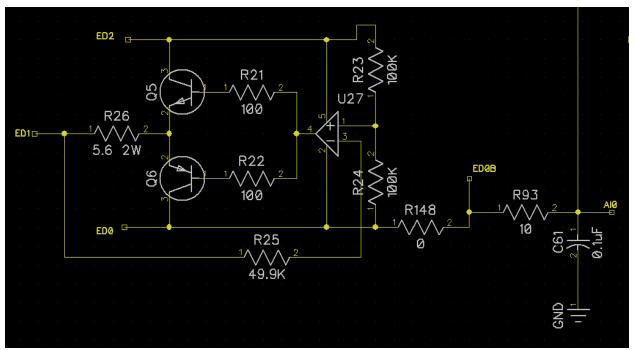

| Figure 3.4.4.2 | : Current Loop Circuit of the Programmable Load            | 56 |

| Figure 3.5.1   | : Test System Constant Voltage Simulation Model            | 58 |

| Figure 3.5.2   | : Simulation Results for Test System Model                 | 59 |

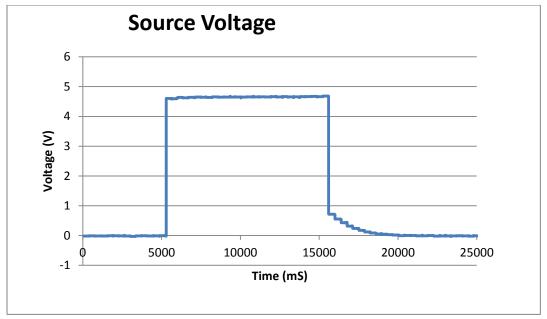

| Figure 3.5.3   | : Source Voltage for Constant Voltage Validation Test      | 59 |

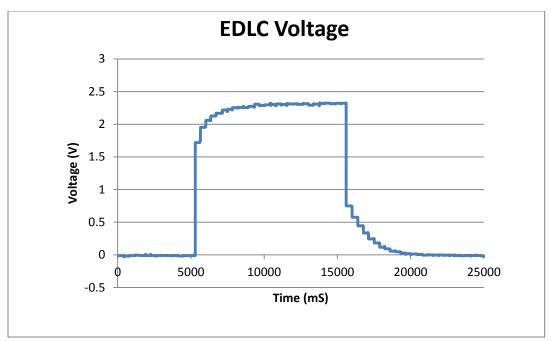

| Figure 3.5.4   | : EDLC Voltage Measurement                                 | 60 |

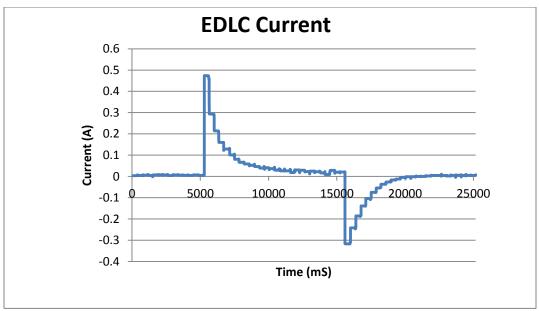

| Figure 3.5.5   | : EDLC Current Measurement                                 | 60 |

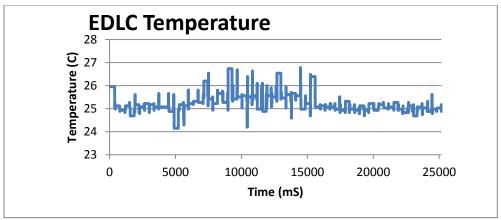

| Figure 3.5.6   | : EDLC Temperature Measurement                             |    |

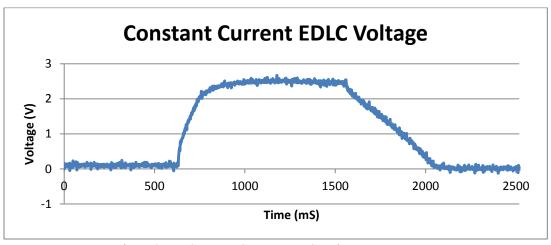

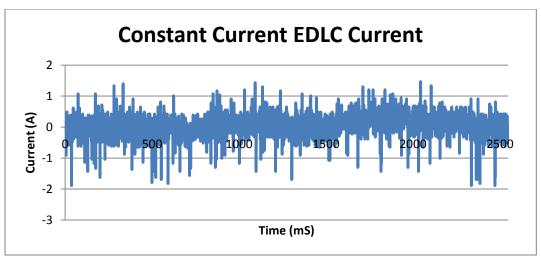

| Figure 3.5.7   | : Constant Current EDLC Voltage Measurement                | 61 |

| Figure 3.5.8   | : Constant Current Discharge EDLC Current Measurement      | 62 |

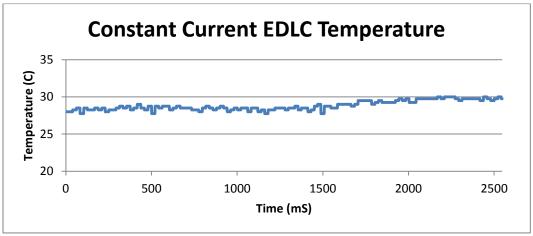

| Figure 3.5.9   | : Constant Current Discharge EDLC Temperature              | 62 |

| Figure 4.2.1   | : Cell Balancing Circuit in EDLC Management System         | 72 |

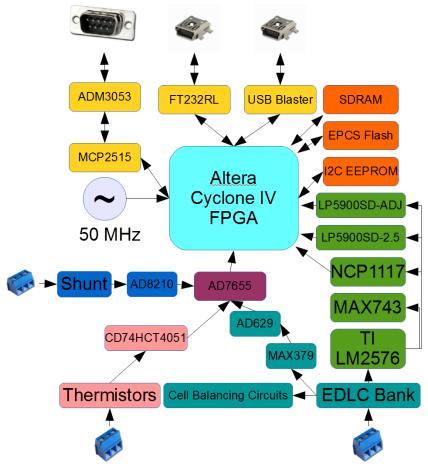

| Figure 4.2.2   | : EDLC Management System Hardware Flowchart                | 73 |

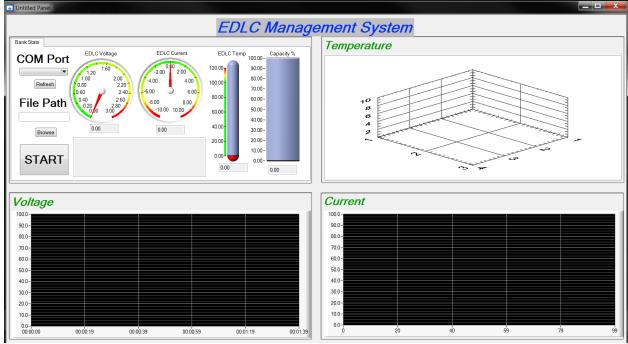

| Figure 4.3.1   | : EDLC Management System Front Panel                       | 76 |

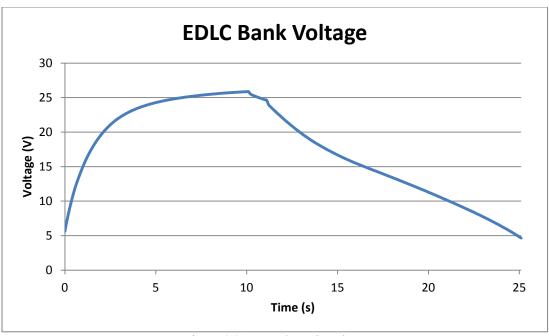

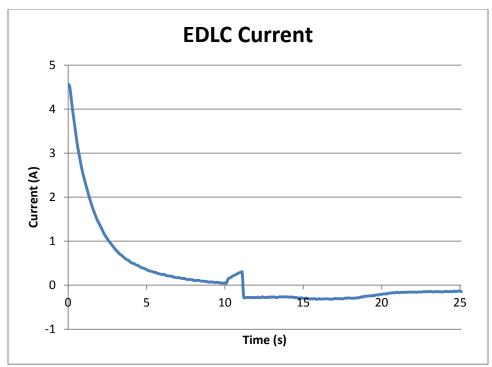

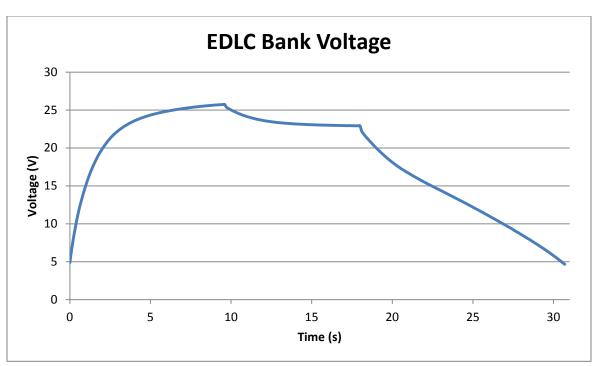

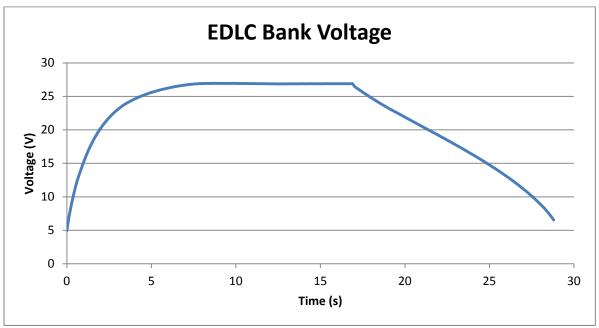

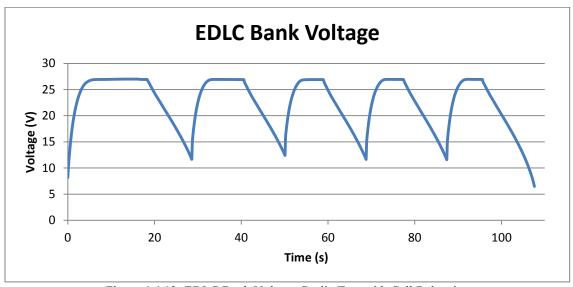

| Figure 4.4.1   | : EDLC Bank Voltage                                        | 78 |

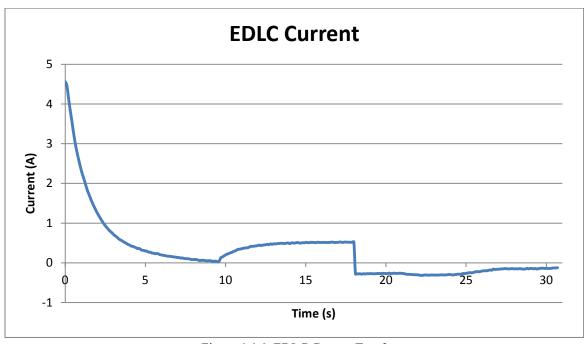

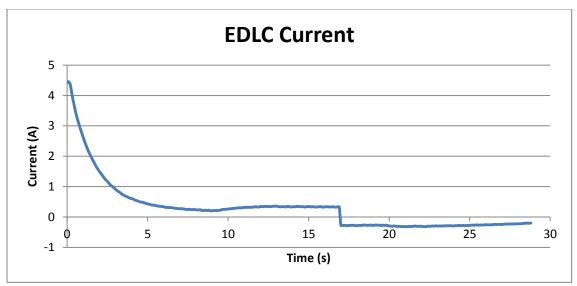

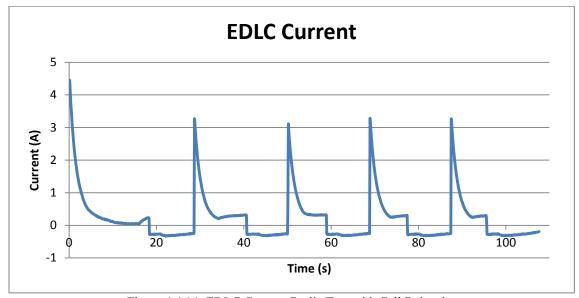

| Figure 4.4.2  | : EDLC Bank Current                                                      | 79   |

|---------------|--------------------------------------------------------------------------|------|

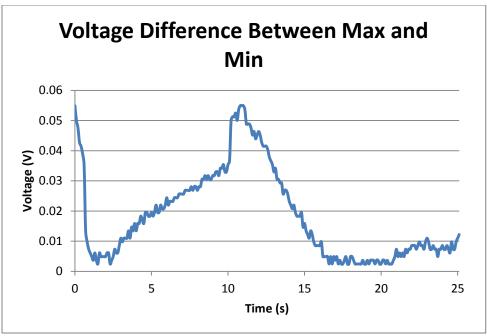

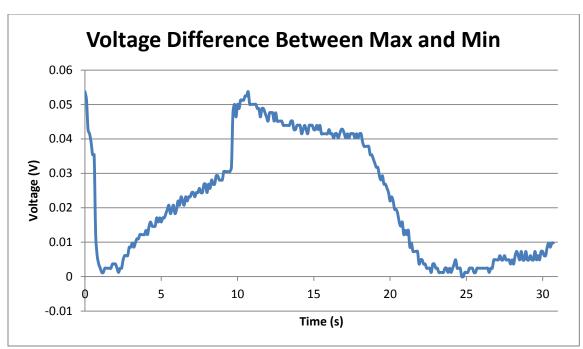

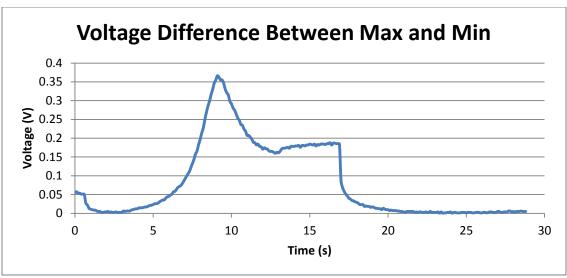

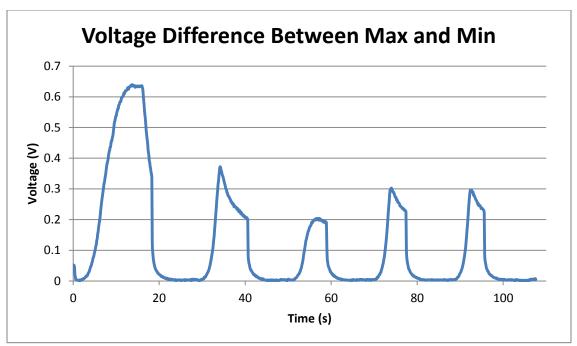

| Figure 4.4.3  | : Voltage Difference Between Max and Min EDLCs                           |      |

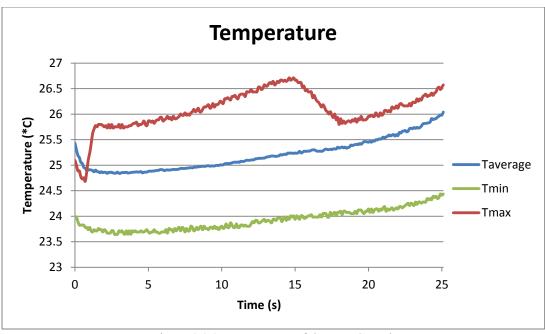

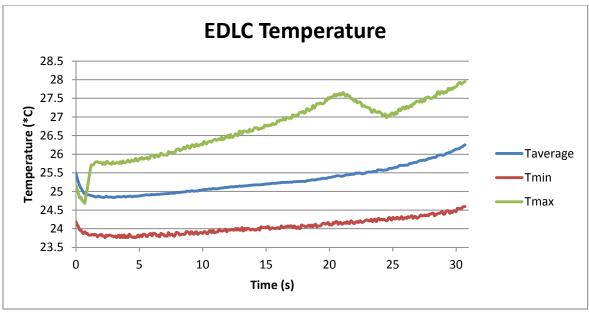

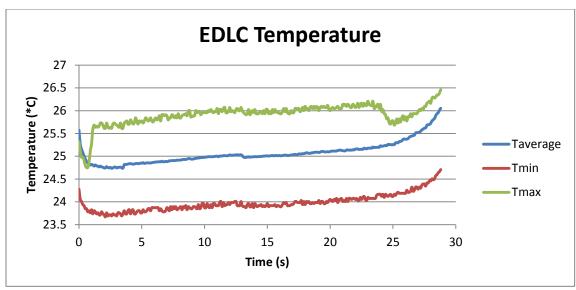

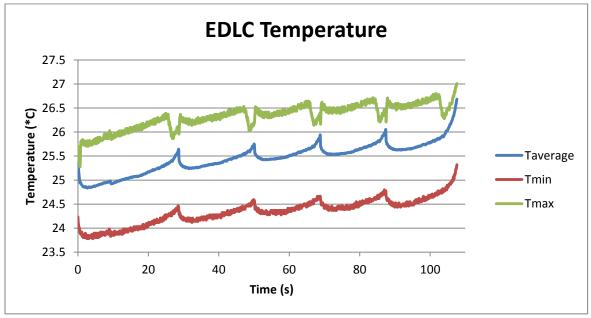

| Figure 4.4.4  | : Temperature of the EDLC Bank                                           |      |

| Figure 4.4.5  | : EDLC Bank Voltage Test 2                                               | 83   |

| Figure 4.4.6  | : EDLC Current Test 2                                                    |      |

| Figure 4.4.7  | : Voltage Difference Between Max and Min EDLC Test 2                     | 84   |

| Figure 4.4.8  | : EDLC Temperature Test 2                                                |      |

| Figure 4.4.9  | : EDLC Bank Voltage Basic Test with Cell Balancing                       | 85   |

| Figure 4.4.10 | : EDLC Current Basic Test with Cell Balancing                            |      |

| Figure 4.4.11 | : Voltage Difference Between Max and Min Basic Test with Cell Balancing  | 87   |

| Figure 4.4.12 | : EDLC Temperature Basic Test with Cell Balancing                        | 88   |

| Figure 4.4.13 | : EDLC Bank Voltage Cyclic Test with Cell Balancing                      | 88   |

| Figure 4.4.14 | : EDLC Current Cyclic Test with Cell Balancing                           | 89   |

| Figure 4.4.15 | : Voltage Difference Between Max and Min Cyclic Test with Cell Balancing | 90   |

| Figure 4.4.16 | : EDLC Temperature Cyclic Test with Cell Balancing                       | 90   |

| Figure A.1.1  | : RC Circuit                                                             | 98   |

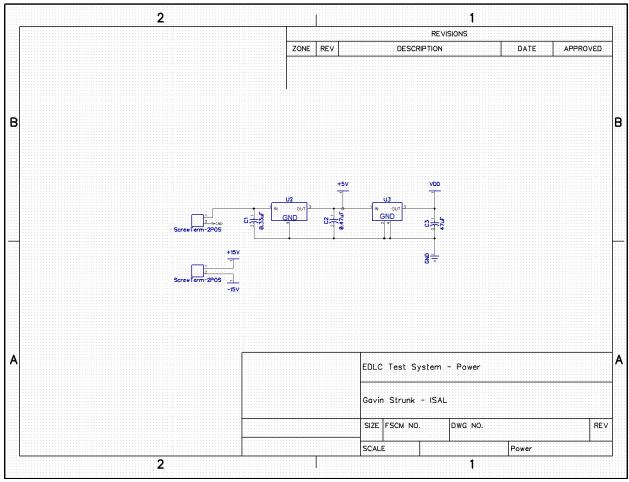

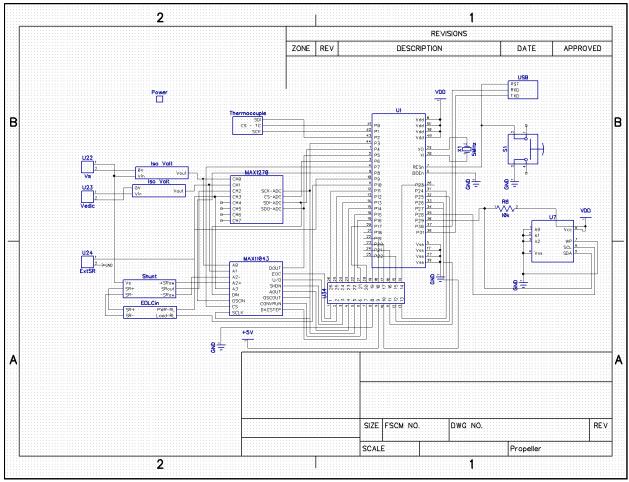

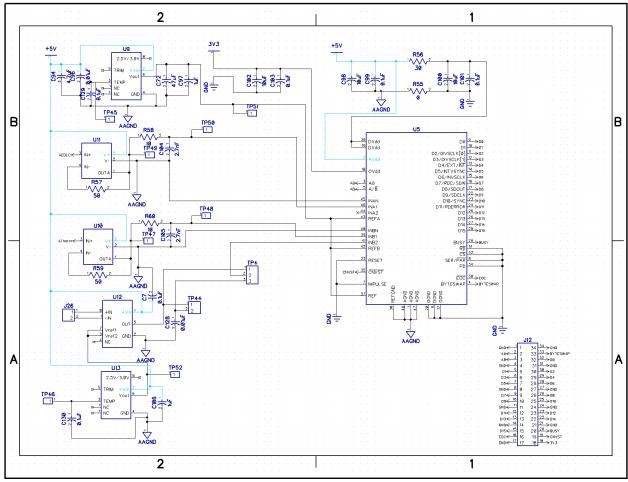

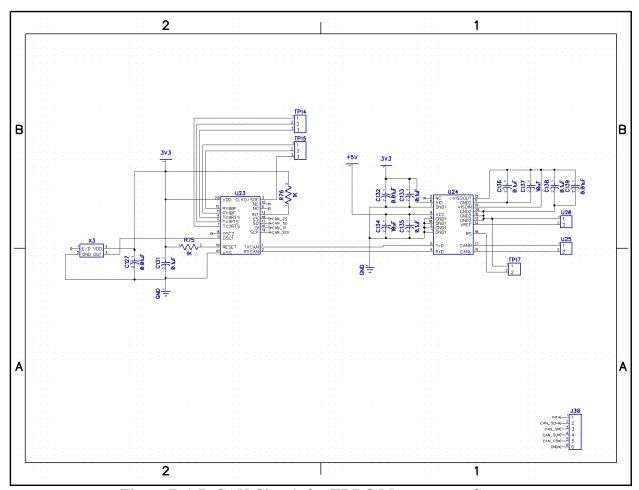

| Figure B.1.1  | : Power Schematic for EDLC Test System                                   | .100 |

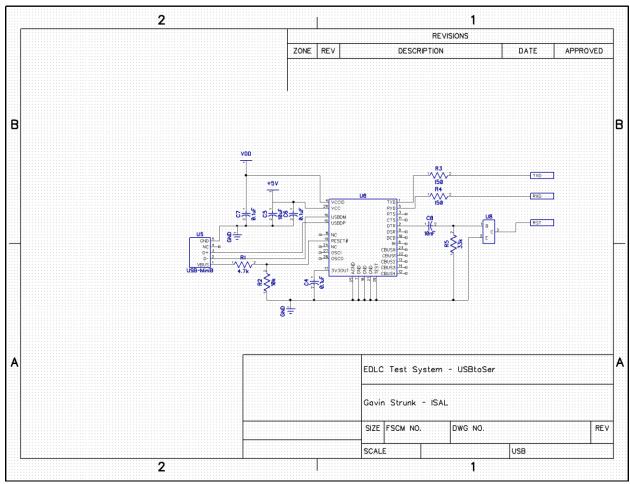

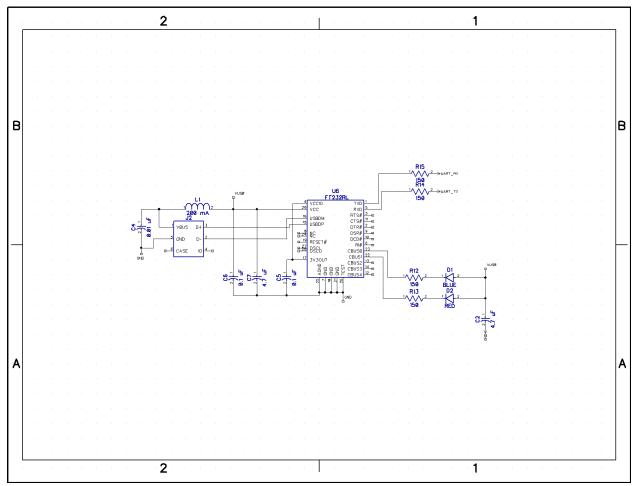

| Figure B.1.2  | : USB to Serial Circuit for EDLC Test System                             | .101 |

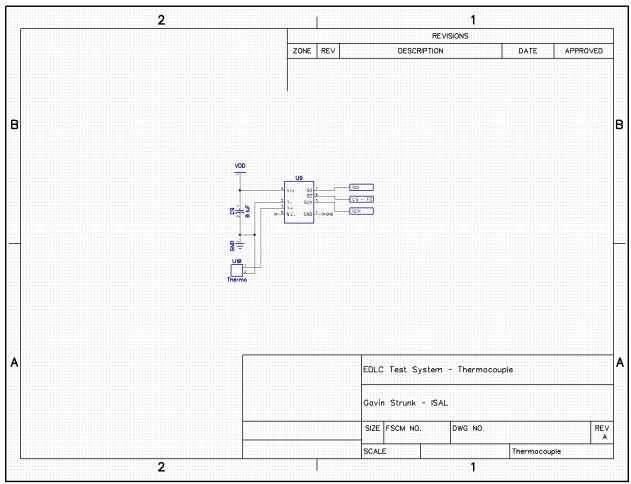

| Figure B.1.3  | : Thermocouple Circuit for EDLC Test System                              | .102 |

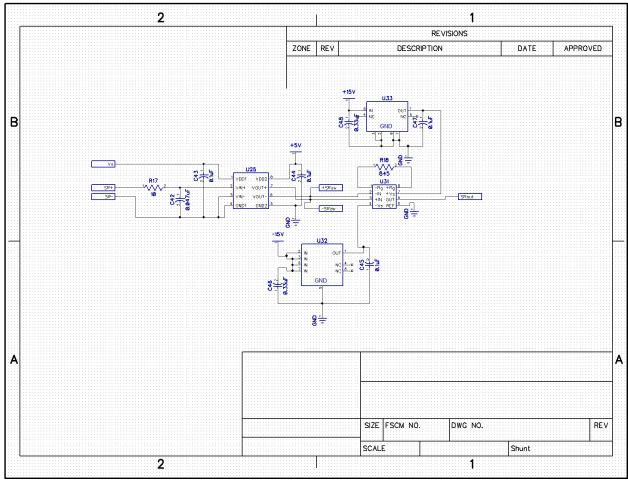

| Figure B.1.4  | : Current Shunt Interface Circuit for EDLC Test System                   | .103 |

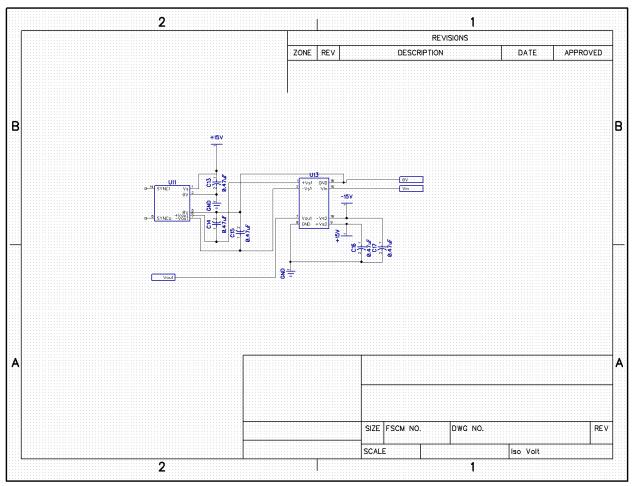

| Figure B.1.5  | : Voltage Isolation Circuit for EDLC Test System                         | .104 |

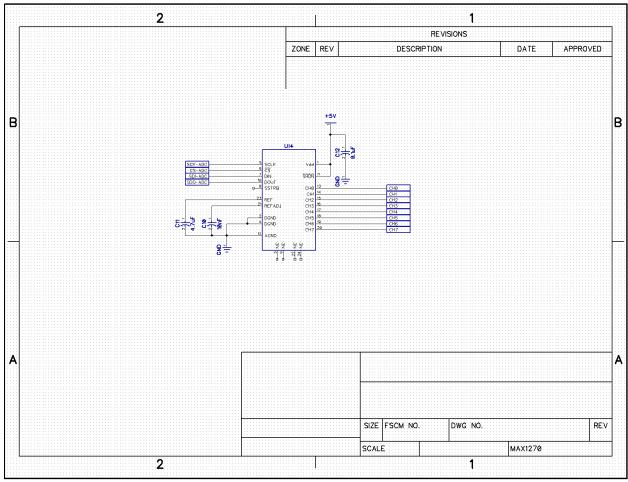

| Figure B.1.6  | : MAX1270 A/D Circuit for EDLC Test System                               | .105 |

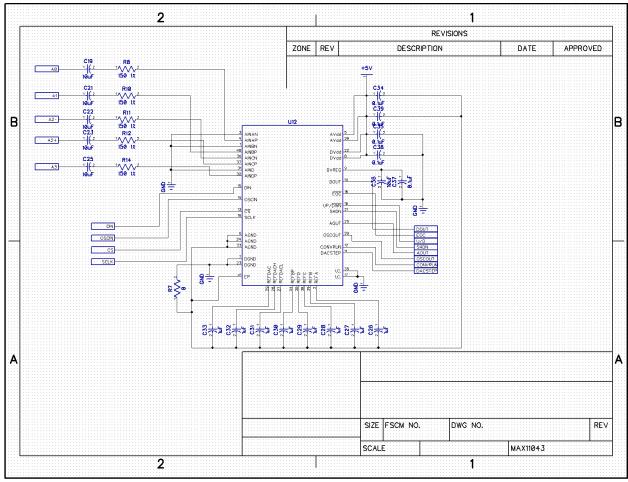

| Figure B.1.7  | : MAX11043 A/D Converter Circuit for EDLC Test System                    | .106 |

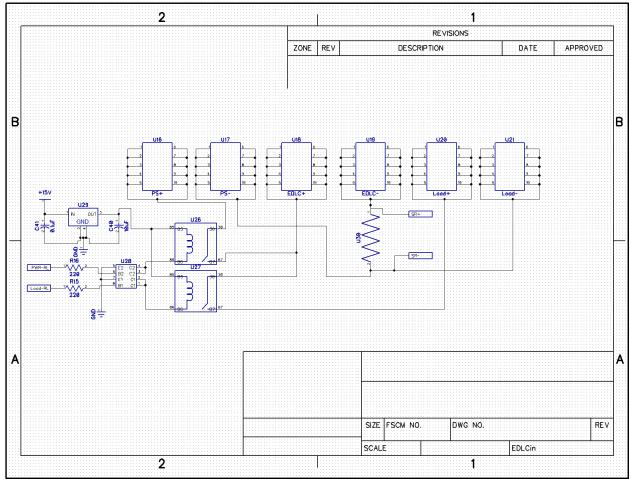

| Figure B.1.8  | : EDLC, Power Source, and Load Interface for EDLC Test System            | .107 |

| Figure B.1.9  | : Propeller Circuit for EDLC Test System                                 | .108 |

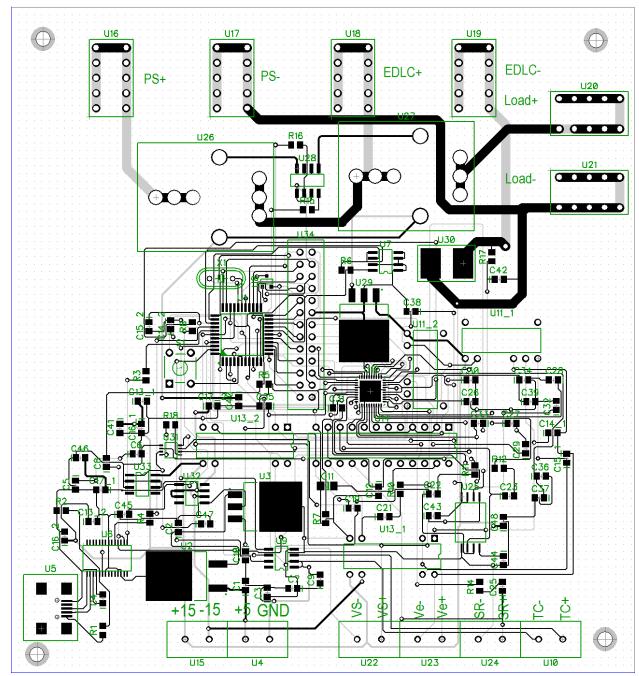

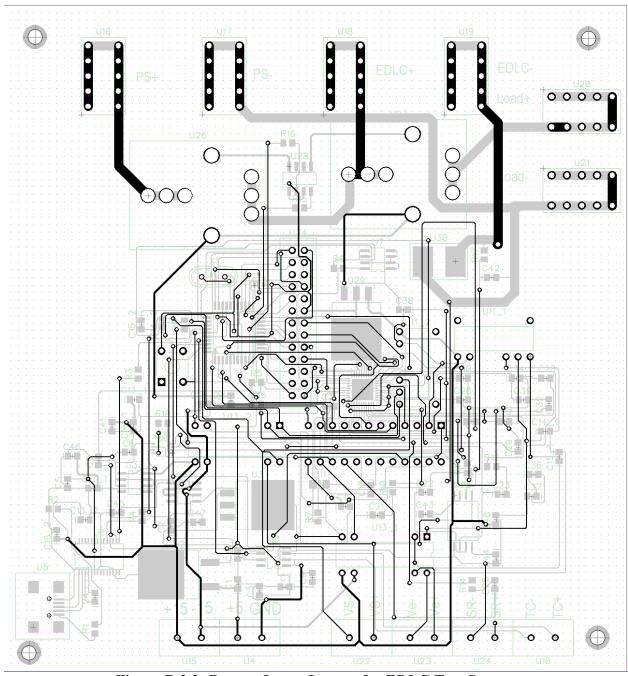

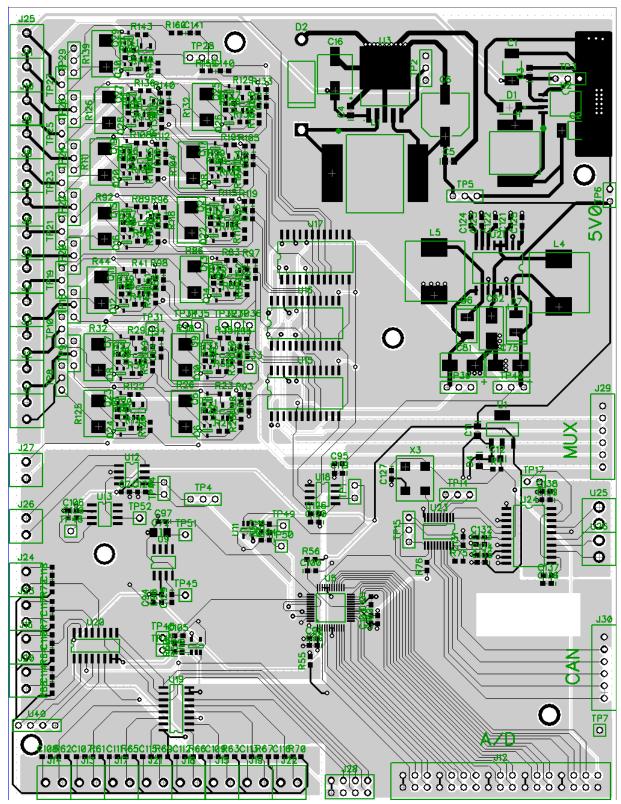

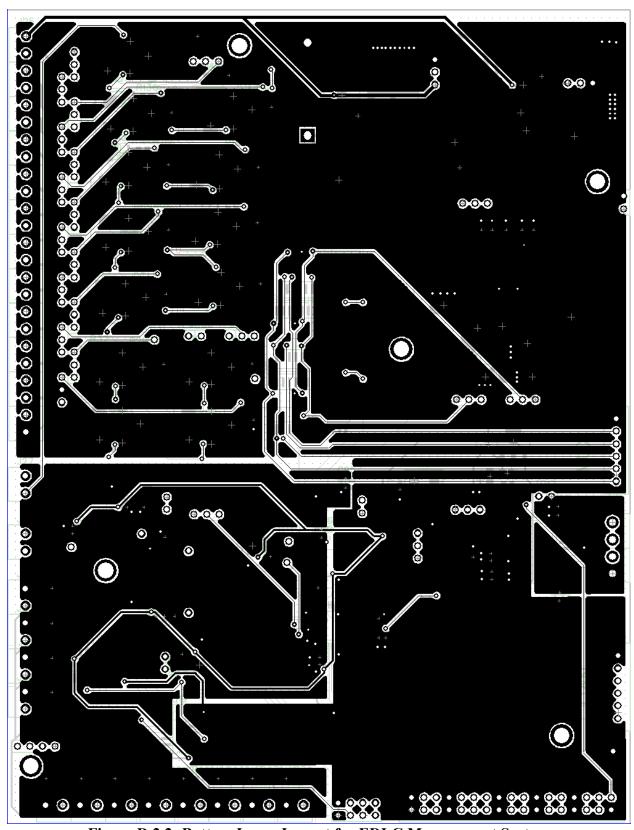

| Figure B.2.1  | : Top Layer Layout for EDLC Test System                                  | .109 |

| Figure B.2.2  | : Bottom Layer Layout for EDLC Test System                               | .110 |

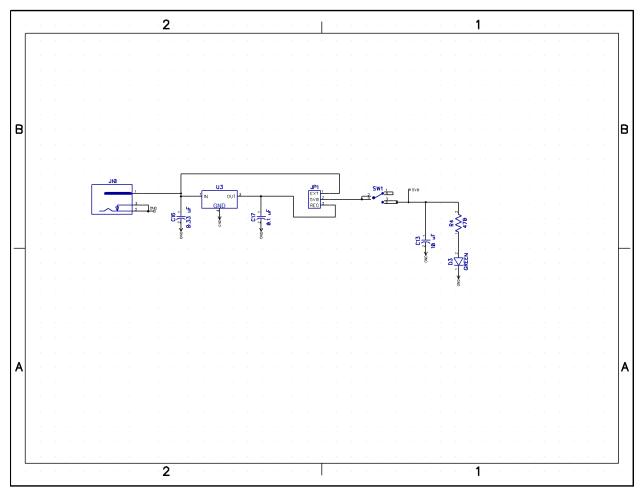

| Figure C.1.1  | : Power Circuit for Programmable Load                                    | .133 |

| Figure C.1.2  | : USB to Serial Circuit for Programmable Load                            | .134 |

| Figure C.1.3  | : PIC, LCD, and Circuit Loop Circuits for Programmable Load              | .135 |

| Figure C.2.1  | : Top Layer Layout for Programmable Load                                 | .136 |

| Figure C.2.2  | : Bottom Layer Layout for Programmable Load                              | .137 |

| Figure D.1.1  | : Power Circuit for EDLC Management System                               | .154 |

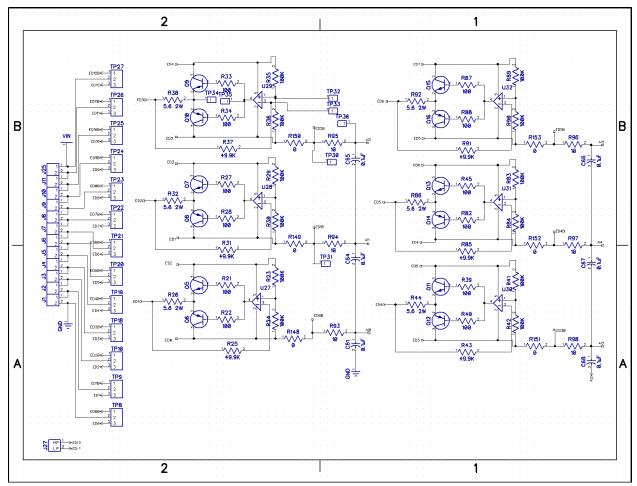

| Figure D.1.2  | : EDLC Interface and Cell Balancing Circuit for EDLC Management System . | .155 |

| Figure D.1.3  | : Cell Balancing Circuit Cont. for EDLC Management System                | .156 |

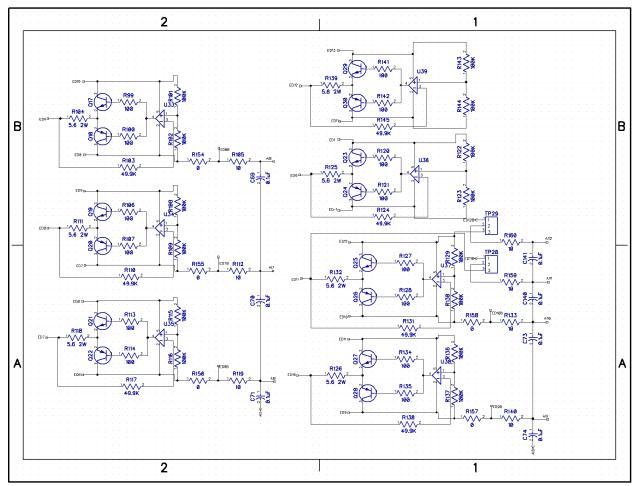

| Figure D.1.4  | : EDLC Multiplexor Circuit for EDLC Management System                    | .157 |

| Figure D.1.5  | : Thermistor Interface for EDLC Management System                        | .158 |

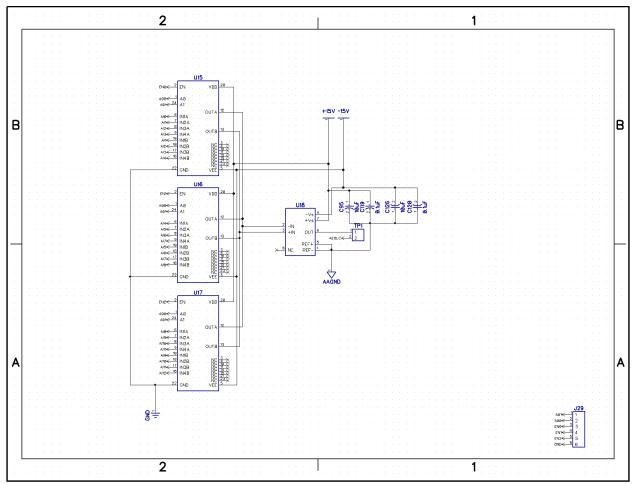

| Figure D.1.6  | : AD7655 A/D Circuit for EDLC Management System                          |      |

| Figure D.1.7  | : CAN Circuit for EDLC Management System                                 | .160 |

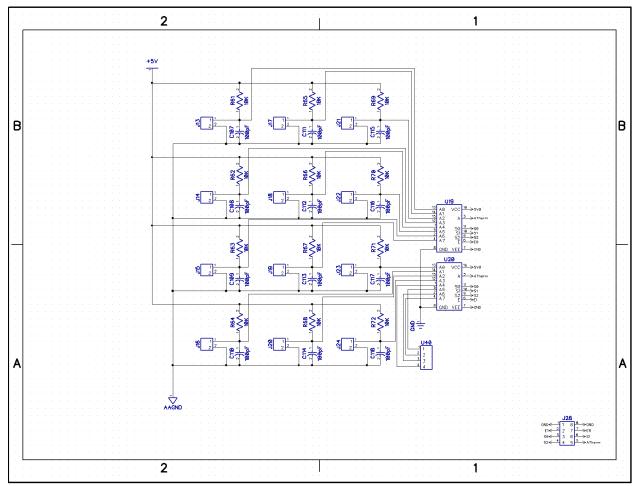

| Figure D.2.1  | : Top Layer Layout for EDLC Management System                            |      |

| Figure D.2.2  | : Bottom Layer Layout for EDLC Management System                         | .162 |

# **NONMENCLATURE**

A/D Analog to Digital

CAN Controller Area Network

D/A Digital to Analog

DRAM Dynamic Random-Access Memory

EDLC Electrochemical Double Layered Capacitor

FPGA Field Programmable Gate Array

I<sup>2</sup>C Inter-Integrated Circuit KSPS Kilo Samples Per Second

LDO Low-Dropout

MSPS Million Samples Per Second

OTG On-The-Go

PCB Printed Circuit Board

PCI Peripheral Component Interface SPI Serial Peripheral Interface TTL Transistor Transistor Logic

UART Universal Asynchronous Receiver/Transmitter

### 1. INTRODUCTION

### 1.1 Hybrid Electric Vehicles and Control

Alternative fuel vehicles have been ever increasing in interest and performance with companies such as Tesla leading the way. The need to reduce vehicle emissions, improve vehicle efficiency, reduce road noise, and fossil fuel dependency are all reasons that alternative fuel vehicles are being researched by companies and academia alike [1]. Pure electric vehicles have not been widely accepted; however, because they typically suffer from one of the following shortcomings: insufficient range, insufficient power for large vehicles, or high cost. To combat these issues, many companies and researchers have come up with the intermediate solution of hybrid vehicles. Hybrid vehicles have the ability to have longer ranges, deliver more power as compared to a typical vehicle grade electric motor with batteries, and reduced cost by not requiring as many batteries, which comprises one-third of the vehicle cost [2]. One example of this is using ultracapacitors and batteries to satisfy the peak power needs thus no longer requiring the battery pack to be oversized for these situations [3][4]. This reduces the cost, as well as, improving the cycle life of the batteries extending the maintenance time of the vehicle [4]. Typical current commercially available hybrids involved batteries and a gasoline or diesel motor to extend the driving range of the vehicle. These hybrid vehicles address some of the issues such as increasing the vehicle range and efficiency, but do not eliminate the use of fossil fuels. Therefore, they are serving as an intermediate step to a more favorable solution to the problem.

The commercially available hybrid vehicles typically use a simplistic control strategy by using strictly the available battery power until it is depleted and then switching to the motor.

More sophisticated blended strategies have been a focus of many current researchers to further improve efficiency [5]. A variety of studies have shown improvements in range by using

blended strategies suggesting there is room for efficiency increases using intelligent control methods not only in this style of hybrid vehicle but in others as well [5].

Along with the infancy of the control strategies, current vehicles typically provide very little information to the driver regarding power consumption or potentially hazardous conditions to the vehicle components. Current gasoline cars have implemented features such as displaying the real time miles per gallon to the driver in an attempt to have more informed drivers to increase driver efficiency. Equivalent features have not been as successfully integrated in the commercial hybrid vehicle technologies.

Safety measures are also in a relatively new state for these vehicles. There have been various accidents involving battery packs melting or exploding in vehicles without warning. This drives the assumption that there is also a need for improved safety systems implemented in the hardware as well as the vehicle controller. It is typical that the pack has to be physically removed and disassembled to find the cause of the failure. This approach does not always reveal the true cause of the failure; however, as many times the pack is destroyed beyond allowing troubleshooting. This is due to minimal or no data being recorded and communicated to a system outside the pack itself. The failure modes also have room for improvement in not only detection, but preemptive action to attempt to stop the failure from occurring. An example is the recent Tesla fire [6]. The vehicle warned the drive to pull over and exit the vehicle before the vehicle caught on fire resulting in no casualties as a result of the failure. Many power systems monitor the basic voltage, current, and temperature readings, but these are typically described in a binary state of safe or not safe. A better approach is to realize these limits are being approached and the velocity at which they are being approached, so preventative actions can be implemented to attempt to correct the failing conditions. Despite these shortcomings, hybrid

vehicles represent a huge opportunity to increase efficiency and reduce carbon emissions. A newer style of hybrid involving all electrochemical components has also started receiving more research attention. These vehicles typically involve some combination of batteries, electrochemical double layered capacitors (EDLC), and/or fuel cells [7].

#### 1.2 Current Power Sources

The three most common electrochemical power sources are batteries, EDLCs, and fuel cells. They vary in properties, cost, size, and availability. Batteries have not only been around the longest commercially, but are also the most popular choice of power source in pure electric and hybrid electric vehicles. Currently lithium based batteries are the most popular choice. Lithium batteries have a good balance of energy and power properties by having good energy density and good power density. They also have a good balance of cost [8][9][10]. For these reasons they are the best choice for most single source applications. There is still considerable room for improvement in batteries to have higher capacities and ability to deliver more power. Current batteries also suffer from low cycle-life compared to other energy forms, especially when subjected to pulse current loads like those in vehicle applications. Typically batteries also require much longer recharge times than current gasoline tanks, which can be an annoyance for the user [11][12][13].

Fuel cells are the newest of the power sources discussed here but offer some advantages over batteries. They have very good energy density compared to lithium batteries as well as the ability to be refilled much quicker than current batteries charge times [14]. This is very appealing in vehicle applications where vehicle range is directly related to energy density. Recharge time is also a variable that has to be considered in vehicle applications because this relates to the user experience. We have become accustom to refilling gasoline vehicles in a few

minutes, so having to wait hours for batteries to charge seems like a large burden to many vehicle owners. Fuel cells have the ability to be refilled in a similar fashion as current gasoline vehicles, which would solve this problem. Fuel cells are not without their own disadvantages though. They have very poor power density and are damaged easily when excessive power is drawn from them resulting in fuel starvation and irreversible damage to the system [15]. Fuel cells also suffer from low efficiency at very low power levels and are unidirectional so they cannot recapture regenerative breaking energy. Finally, they have to have been charged before they can deliver power so they display very slow dynamics [15]. It has also been shown that peak power conditions cause a significant voltage drop resulting in inconsistent power [16]. This is a large problem when running an electric motor because electric motors require a large spike of current at the start of their response. Future breakthroughs will likely address many of these problems, but in their current state fuel cells are not viable power sources for vehicle applications by themselves.

The final power source is electrochemical double layered capacitors. These are also commonly referred to as ultracapacitors or supercapacitors. EDLC's have excellent power density and are capable of charging and discharging very quickly due to their low internal resistance [17][18]. EDLC's also typically have several orders of magnitude higher cycle life than batteries. This makes them ideal in applications that either require or deliver bursts of power, such as capturing regenerative breaking energy and power balancing [19]. Another advantage of an EDLC is a wider temperature operating range than batteries. In addition to operating over a wider range, they are also much more consistent in the efficiency of their output over their thermal operating range [20]. They do however suffer from low energy density compared to batteries, which rarely allows them to be a viable option as a sole power source.

Despite this, EDLCs have the ability to improve performance of both battery and fuel cell hybrid vehicles. When combined with batteries the EDLCs would be able to absorb the power spikes seen from electric motors, deliver more stable power, as well as reduce the harsh conditions the battery pack sees. This would improve the overall lifetime of the battery system and increase the overall power density of the hybrid source [21][22]. In tandem with fuel cells, EDLCs would again be able to make up for the poor power density as well as allowing the fuel cell time to charge while power is delivered from the EDLC bank. These advantages make EDLC an ideal candidate for hybrid sources when combined with batteries or fuel cells.

### 1.3 Problem Identification

A significant amount of research effort is focused on component research on the previously mentions sources. There has also been some research on proper implementation of the battery systems, but significantly less revolving around EDLCs. The need exists for development tools to not only characterize EDLC cells, but then provide a means to scale the cells up to a full size bank without sacrificing safety or reliability. Trends have shown that EDLCs are rarely a viable single source of power especially in vehicles. Therefore, in addition to implementing these systems, the design work needs to be conducted in a way that allows the final bank to be easily integrated with other power sources, such as batteries or fuel cells. This lays the groundwork for a layered approach to hybrid power source control, which not only makes the complexity more manageable but modular as well. Modularity in a power source management design is a must because of the rapid rate of research progression in the area and the varying requirements from application to application.

Current efforts in this area have been focused on algorithms and simulations. As this is typically the first step, this research has laid some ground work as to a variety of approaches to

implementing such a system [5][7][9]. The major problem with the simulations is that they lack the depth of accounting for many losses associated with physical implementation of such a system. Examples of this include losses through power electronics and thermal models. They also typically do not account for subsystems such as cooling or heating systems that are required. These losses do not typically change the effectiveness of an algorithm, but they cannot be overlooked when implementing a physical system as they directly affect the safety and reliability of the bank. There have been a couple of researchers working on concepts of how to implement systems that provide information feedback from a vehicle, but these systems are normally a means to test algorithms with less emphasis on robust implementation for a commercial application [23][24].

### 1.4 Research Objective

The overall research objective is to design development tools for EDLCs that allow an implementer to test all phases of a design from a single cell all the way to a complete bank with a management system, as well as a platform to perform these tests to validate and improve existing models. This is accomplished in three parts: a full vehicle test platform, a single cell test system, and a multi-cell management system.

The full vehicle test platform will have to be versatile and modular as well so testing a variety of systems can be conducted. The vehicle will also need a data acquisition system that is capable of characterizing the systems to demonstrate improvements or faults in the designs [25]. This system will provide the driver with feedback as well as show the information about the rest of the vehicle so any dependent behavior can also be identified and proper comparisons between systems can be made without bias from other vehicle systems.

The single test cell system will need to support a large variety of tests and testing environments so it will also be modular in nature. This will include a modular power supply, EDLC connection, and modular load. In addition, the measurements will be isolated from the power path. This keeps the measurement system from affecting the behavior of the cell. This will also protect the measurement circuitry, which allows the user to test fault conditions as well as push cells to the point of failure without damaging the test system. This will also ensure the measurement system will continue to operate even after a cell has failed to allow the user to identify the conditions that caused the failure. This provides a huge advantage by allowing safety systems to be tested to ensure robustness [26].

Finally, a multi-cell management system will be developed. This system needs to be self-contained in terms of power and scalable in terms of the number of cells. This design will provide a generic controller that can be used to build any combination of cells in series or parallel to provide the desired amount of capacity and power density. By drawing the power from the bank itself, the management system can be packaged with the bank without requiring addition wiring to operate. It should, however, also allow an additional external power source to be added as a backup in case of a pack failure. This, like the test system, would allow the management system to continue to operate even if there is a failure in the pack. This offers several safety advantages, such as the ability to continue operating systems that may still be running. For example, if a short in the bank causes a thermal spike that melts a cell the cooling system may continue to be operational and the continued cooling operation could prevent additional cells from damage.

## 1.5 Future Impact

The solution to the proposed problem holds a variety of positive future impacts for hybrid vehicle development. First, it will decrease time and complexity of implementing an EDLC bank into a power source. This will encourage more designers to implement this technology when appropriate. It will allow researchers to conduct simultaneous research at all levels of integration moving forward. This ultimately will allow more customization of hybrid electric power sources to properly fit the application, rather than having the user accept the shortcomings of the system. The modularity of the system will allow for integration with current technologies as well as leave room to support future power sources that have not been developed or commercialized yet. These systems allow the designer to test operating and extreme conditions, which will aid in designing more efficient packaging and cooling systems. This in turn will reduce the overall size of the system and the parasitic power consumption. The ability for robust testing will inevitably lead to more intelligent safety systems that not only improve the way failures are handled, but take preemptive action to avoid the failure conditions. Finally, further implementation and testing will reveal flaws in the cells and can be passed down to component researchers to help design better cells at the component level.

#### 1.6 References

- [1] Li, Q., et al. (2012). "Energy management strategy for fuel cell/battery/ultracapacitor hybrid vehicle based on fuzzy logic." <u>International Journal of Electrical Power & Energy</u> Systems **43**(1): 514-525.

- [2] Tie, S. F. and C. W. Tan (2013). "A review of energy sources and energy management system in electric vehicles." Renewable and Sustainable Energy Reviews **20**(0): 82-102.

- [3] Adib, E. and H. Farzanehfard (2009). "Soft switching bidirectional DC–DC converter for ultracapacitor–batteries interface." <u>Energy Conversion and Management</u> **50**(12): 2879-2884

- [4] He, H., et al. (2013). "Energy management strategy research on a hybrid power system by hardware-in-loop experiments." Applied Energy **112**(0): 1311-1317.

- [5] Chen, Z., et al. "Energy Management of a Power-Split Plug-in Hybrid Electric Vehicle

- Based on Genetic Algorithm and Quadratic Programming." Journal of Power Sources(0).

- [6] Musk, Elon. (2013). "Model S Fire." http://www.teslamotors.com/blog/model-s-fire

- [7] Yu, Z., et al. (2011). "An innovative optimal power allocation strategy for fuel cell, battery and supercapacitor hybrid electric vehicle." <u>Journal of Power Sources</u> **196**(4): 2351-2359.

- [8] Sharma, P. and T. S. Bhatti (2010). "A review on electrochemical double-layer capacitors." Energy Conversion and Management **51**(12): 2901-2912.

- [9] Chao, C.-H. and J.-J. Shieh (2012). "A new control strategy for hybrid fuel cell-battery power systems with improved efficiency." <u>International Journal of Hydrogen Energy</u> **37**(17): 13141-13146.

- [10] Payman, A., et al. (2008). "Energy control of supercapacitor/fuel cell hybrid power source." Energy Conversion and Management **49**(6): 1637-1644.

- [11] Erdinc, O., et al. (2009). "A wavelet-fuzzy logic based energy management strategy for a fuel cell/battery/ultra-capacitor hybrid vehicular power system." <u>Journal of Power Sources</u> **194**(1): 369-380.

- [12] Paladini, V., et al. (2007). "Super-capacitors fuel-cell hybrid electric vehicle optimization and control strategy development." <u>Energy Conversion and Management</u> **48**(11): 3001-3008.

- [13] Yuchen, L., et al. (2007). <u>Adaptive Control of an Ultracapacitor Energy Storage System for Hybrid Electric Vehicles</u>. Electric Machines & Drives Conference, 2007. IEMDC '07. IEEE International.

- [14] Thounthong, P., et al. (2006). "Control strategy of fuel cell/supercapacitors hybrid power sources for electric vehicle." <u>Journal of Power Sources</u> **158**(1): 806-814.

- [15] Lin, W.-S. and C.-H. Zheng (2011). "Energy management of a fuel cell/ultracapacitor hybrid power system using an adaptive optimal-control method." <u>Journal of Power Sources</u> **196**(6): 3280-3289.

- [16] Thounthong, P., et al. (2009). "Energy management of fuel cell/battery/supercapacitor hybrid power source for vehicle applications." <u>Journal of Power Sources</u> **193**(1): 376-385.

- [17] Jung, D. Y., et al. (2003). "Development of ultracapacitor modules for 42-V automotive electrical systems." <u>Journal of Power Sources</u> **114**(2): 366-373.

- [18] Farzanehfard, H., et al. (2008). "A bidirectional soft switched ultracapacitor interface circuit for hybrid electric vehicles." <u>Energy Conversion and Management</u> **49**(12): 3578-3584.

- [19] Wu, C. H., et al. (2012). "On-line supercapacitor dynamic models for energy conversion and management." <u>Energy Conversion and Management</u> **53**(1): 337-345.

- [20] Gualous, H., et al. (2010). "Supercapacitor ageing at constant temperature and constant voltage and thermal shock." Microelectronics Reliability **50**(9–11): 1783-1788.

- [21] Burke, A. and M. Miller (2010). "Testing of electrochemical capacitors: Capacitance, resistance, energy density, and power capability." <u>Electrochimica Acta</u> **55**(25): 7538-7548.

- [22] Burke, A. and M. Miller (2011). "The power capability of ultracapacitors and lithium batteries for electric and hybrid vehicle applications." <u>Journal of Power Sources</u> **196**(1): 514-522.

- [23] Jianfeng, H., et al. (2008). <u>Application and study of novel electronic technologies on vehicle control system of fuel cell bus</u>. Vehicle Power and Propulsion Conference, 2008. VPPC '08. IEEE.

- [24] Zhu, D. and H. Xie (2008). Control strategy optimization of the hybrid electric bus based on

- <u>remote self-learning driving cycles</u>. Vehicle Power and Propulsion Conference, 2008. VPPC '08. IEEE.

- [25] Baker, B. C., et al. (2012). Electric transit bus for variable grade terrain. Electric Vehicle Conference (IEVC), 2012 IEEE International.

- [26] Strunk, G. K., M; Baker, B.; Faddis, T (2012). Ultracapacitor Test System. Electric Vehicle Symposium. Los Angeles, CA.

# 2. Electric Shuttle Bus Data Acquisition Retrofit

#### 2.1 Introduction

Research into hybrid electric and pure electric vehicles has been a major focus of many groups around the world for a significant period of time. More commercial entities have also started offering hybrid vehicles as an alternative to gasoline vehicles with many beginning to offer viable pure electric vehicles for everyday use [1]. These vehicles typically offer increased gas mileage, decreased environmental footprint, and reduced road noise. These have all been factors that have driven consumers and researchers to pursue this technology with vigilance [2]. Despite the increasing maturity of small cars, progress in applying this same technology has been slower in larger vehicles [3]. This is due to a variety of issues including: large amounts of electrical storage required, larger power output, and higher cost to develop. Because it is expensive to implement this technology in a shuttle bus sized vehicle, it is useful to develop a means for numerous people to test ideas on a single platform [4].

This is the aim at the University of Kansas Intelligent Systems and Automation Lab. A shuttle bus has already been acquired that is currently in a pure electric configuration implementing lead acid batteries. The shuttle bus is shown in Figure 2.1.1.

Figure 2.1.1: University of Kansas Electric Shuttle Bus

This will serve not only as the validation system for the data acquisition system, but provide a full scale platform to continue research into large vehicle electrification [4].

## 2.2 Design Requirements

The first step in maturing this vehicle platform is to develop a data acquisition system that can characterize the current technology implemented and track the improvements of more advanced technology as upgrades are made. There are several requirements to implement an effective system that will support not only the current needs of the research, but include future plans as well. These include: isolation from the vehicle systems, ease of use, ease of maintainability, expandable, high performance, and portable to another vehicle. These serve as high level requirements to the system design. More specific requirements are discussed later. It was also vital to consider that the system should be able to feed a mathematical model used to predict a variety of characteristics to aid in making design decisions in the future [4]. This means it is also important to have deterministic and time aligned sampling so as not to introduce timing errors when calculating models. Next, further justification for these individual requirements will be given.

The data acquisition system needs to be isolated from the vehicle systems for several reasons. First, it is desirable that the system simply observes the behavior of the vehicle, but does not influence its behavior. If the data acquisition system is electrically coupled to that of the vehicle it will introduce extra loads that would not be present in a production setting giving less accurate results. An isolated system is also beneficial because it can more easily be changed, removed, or implemented into a different vehicle. This criterion also affects the portability of the system. As various components are upgraded, it is imperative that the new

components can easily be incorporated into the system. This will allow much faster implementation time and help to ensure a more consistent system when making comparisons.

Ease of use and maintainability are also vital since the system is likely to be supported for a considerable period of time. A system that is easy to use from an interface standpoint allows researchers to perform tests without the need for an intimate knowledge of the data acquisition system. This will also aid in increasing the efficiency and speed at which research is performed. Undoubtedly, the system requirements are going to evolve with the research so a system that is simple to learn and maintain is crucial.

High performance and expandable can mean a variety of things, but for our purposes it is referring to throughput of sampling and the number of samples capable of being taken. Again with the anticipation of a changing project is the need to allow room for growth in the system in the form of extra channels of acquisition for common sensors. Next, the two systems that were considered will be introduced as well as more detailed specifications of the systems.

### 2.3 Data Acquisition System

In general, the system is broken down into two pieces. First is the embedded system that takes care of interfacing to the various sensors and doing some preliminary signal processing. This embedded system then transmits the data to a computer that decodes the data, displays it on three monitors mounted in the rear of the vehicle, and saves the data to a file for post processing. Two versions of the data acquisition system were developed both on the computer portion and the embedded portion. The first was based around a custom designed PCB built around a PIC32 microcontroller and a custom interface via USB programmed in JAVA on the computer side. The second was built around a CompactRIO from National Instruments and LabVIEW software on the computer side.

The first system to be discussed is the embedded system that was designed around the PIC32MX460F512L microcontroller. This microcontroller includes a variety of serial communication interfaces including SPI, UART, I2C, parallel interface, and several memory options. It also included 512 KB for program memory, 32 KB RAM, 12 KB of auxiliary flash for configuration setting storage, and a USB OTG interface. These were all desirable features as the wide selection of interfaces matches those that are typically found in automotive sensors.

Two that were not present were a sufficient A/D converter and CAN. The PIC32 includes a 16 channel 10 bit 1 MSPS onboard A/D converter. This was not used because 10 bits did not provide enough resolution to measure the analog sensors to the desired precision. Although CAN is one of the most popular automotive interfaces, none of the sensors that were implemented in the system communicated via the CAN bus. Therefore, a CAN bus was not implemented in the system. It is relatively straight forward to add one by selecting from a variety of transceivers that communicated via another serial protocol such as UART or SPI.

The MAX1132 was the A/D converter chosen for the system. It is a 16 bit 200 KSPS bipolar chip. This provides several advantages over other options. It operates from a single 5 V supply, but can measure either 0 to 12 V or ±12 V ranges. This eases the implementation circuitry by not requiring an external resistor divider and voltage bias circuits. It also provided the sufficient precision of 0.366 mV/bit for the ±12 V range. To increase the number of available channels, a DG406 analog multiplexor was placed in front of the A/D to provide 16 single ended channels. It was anticipated that some current shunts would be used to measure a variety of low voltage bus currents, so the system also included four AD8293G160 fixed gain amplifiers. This instrument amplifier had excellent noise properties and rail-to-rail operation with a fixed gain of 160. This gain was chosen to allow shunts up to ± 31.25 mV output to be

used in the system. This does not make use of the full scale range of the A/D, but there was a trade-off between board space of adding additional amplifiers for each of the four current measurement channels and the reduced precision. For a shunt rated to measure 10 A and output 31.25 mV results in a resolution of 1.464 mA/bit, which is sufficiently precise for all the measurements taken on the vehicle.

Next on the board was a MAX6675 cold joint compensated type K thermocouple digital converter. This allowed type K thermocouples to be easily converter to a digital value with guaranteed accuracy to 3 °C. It reads with a resolution of 0.25 °C from 0 to 700 °C. The high end of the measurement range is well beyond the operating conditions that would ever be seen in the vehicle, but the low end may cause some problems. As this vehicle operates in Lawrence, KS it is not improbable that temperatures would drop below 0 °C in the winter months. This does not cause a component failure, but it does need to be understood that the guaranteed accuracy does not extend to temperatures that cold. Again, a single thermocouple interface is not sufficient for the entire vehicle, so an ADG709 quadruple differential multiplexor was placed in front of the MAX6675 to allow up to four thermocouples to be connected to the system. This multiplexor has very low resistance (< 3 Ohms), which is important to switch the thermocouples because their raw voltage output is 41  $\mu$ V/°C. The low resistance minimizes the voltage drop through the switch reducing the noise introduced into the measurement caused by the multiplexor.

Several different voltage rails were required to supply power to the various components. The MAX743 supplied  $\pm$  12 V to power the bipolar multiplexor to the A/D converter. The  $\pm$ 5 V rail was supplied by LM2940-5.0 LDO regulator. That rail also fed a MAX828 which inverted

the rail and supplied -5 V for the current shunt instrument amplifiers. Finally, a MC33269 supplied +3.3 V for the PIC32 and other peripherals.

The communication interface to the computer system was USB as this is a common standard. A FT232RL UART to USB chip was used to not only ease the interface from the embedded side, but can be detected as a serial COMM port making the computer side interface easier as well. This interface is typically limited to a maximum baud rate of 115,200 baud so that was the chosen communication rate.

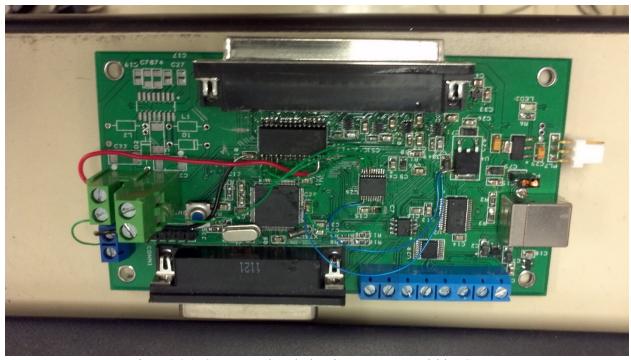

This design had a variety of appealing advantages, such as, very cost effective (<\$200) compared to off-the-shelf solutions costing in the thousands of dollars. The custom board also had a small form factor fitting in a 5" x 2.5" footprint as seen in Figure 2.3.1.

Figure 2.3.1: Custom Designed Electric Bus Data Acquisition System

It did present some disadvantages compared to an off-the-shelf solution including: more difficult to implement the software, more difficult to change to include unforeseen features, and more difficult to maintain software. The custom solution required several applications, all the device

drivers, and a communication schema be developed. This resulted in a more significant programming effort than an off-the-shelf product that includes some code and drivers. Also, the board was designed to support extra features without needing revision, however if for instance a CAN sensor was implemented it would require designing a new board to incorporate it because there is not a CAN transceiver on the custom board. This would require more effort to update the schematic, re-layout a PCB, and could require multiple revisions to get new features working robustly. Although this solution is still inexpensive in terms of hardware cost, this requires a significant amount of researcher time which would ultimately slow the ability of the system to adapt to changes. Finally, this system is harder to maintain because making firmware changes require an in-depth knowledge of the current application to implement new features without sacrificing the performance and reliability of the current features. Again this is not preferred because the system should support basic changes with minimal effort to allow more researchers to use the system and focus on their research rather than programming. Ultimately, it was decided that this system simply did not meet enough of the original design criteria. Therefore, commercial options were explored and a product line from National Instruments was chosen.

The CompactRIO was designed to allow users to have maximum flexibility when choosing peripherals for their system. It is also aimed at making this an integrated and easy process, as well as providing rugged systems that can stand up to a wide variety of environments [5]. The cRIO-9014 was the controller chosen as the heart of the second system and is shown in Figure 2.3.2.

Figure 2.3.2: NI cRIO-9014 Controller with 8 Slot Chassis http://www.dbm.com.vn/?page=products&catid=211

It is an ultra-rugged, high performance, controller that included a 400 MHz PowerPC hard core processor, 2 GB nonvolatile memory, 128 MB DRAM, and an 8-slot Virtex-5 LX 30 FPGA for the reconfigurable peripheral portion. To provide communication the cRIO-9014 has 10/100 BASE-T Ethernet, RS-232 port, and a USB Host port for external memory devices. A major benefit to this system was the ability to buy I/O modules and simply plug in the desired modules to the chassis. This connected through a PCI bus on the backplane of the chassis and could be controller with the real-time controller, the FPGA, or a combination of both.

The analog module chosen was the NI 9205. It is a 32 channel 16-Bit 250 KSPS converter that has a configurable gain to adjust the input range from ± 200 mV to ± 10 V. This was a much needed feature because it allowed the gain to be programmatically turned up for the current shunt channels to increase the precision of the measurement by utilizing more of the modules full scale range without requiring any external circuitry. The digital module was the NI 9403. It was a 32 channel 5V TTL bidirectional module. This module was used for basic switching I/O functions as well as connecting serial interfacing sensors. This module provided flexibility to connect to any sensor that a microcontroller would be capable of connecting to. Among other options, a CAN transceiver was available as one of the modules. It was not implemented do to the lack of requirement to have one, but as there is a reasonably high probability that it will be needed at some point and it will be easy to buy the module and simply

plug it into the chassis. Finally, the NI 9211 was used to interface the thermocouples. It is a four channel thermocouple input module that supports a variety of thermocouple types. The module is also accurate to 1.7 °C over the range of -40 to 70 °C, which is an improvement not only in guaranteed accuracy but the range extended below 0 °C. The final component that needed to be addressed was the onboard RS-232 port. This was used to communicate with the GPS module, as will be discussed later, but the GPS unit was unable to directly connect to the port as it followed the RS-232 standard and the GPS module communicated with a +3.3 V TTL UART. Therefore, a simply interface board was build that included a MAX232 chip to bridge the GPS UART output and the cRIO RS-232 input. Next, the various sensors that were implemented in the vehicle will be discussed.

#### 2.4 Sensor Selection

The first group of sensors installed was various current measurements. Hall effect sensors provide a means to obtain a non-contact current measurement. They work on the principal of sensing the induced inductance created by the current flowing through a wire. Therefore, these sensors are installed with the wire running through them, but they are not part of the circuit. Two hall effect sensors were installed on two phases of the induction motor. The third phase does not require a measurement because it can be calculated from the other two phases. Another hall effect sensor was used to measure the main battery pack current. The compressor for the air system was the original and suspected to be a significant load on the battery pack so a hall effect sensor was installed to measure the current drawn by the compressor. Two more hall effect sensors were placed in the inputs to the DC/DC converters. A major reason for this selection is to be able to obtain an estimate of the efficiency of the converters. Finally, the bus front panel gauges and lights were the originals and require

significantly more current than today's LED lights and low power gauges. To track the gains new gauges will provide, a hall effect sensor was also installed on the main power line leading to all of the front panel systems. Using hall effect sensors was a necessity to keep high current and voltage systems decoupled from the data acquisition system for protection.

For low voltage and lower current readings current shunts were used. These sensors do require the circuit to be broken and placed in series in the circuit. This violated one of the original design criteria by not being completely decoupled from the vehicle itself. Due to the lower cost of the current shunts, these were selected as a tradeoff. They could easily be upgrade to hall effect sensors to achieve the original criteria. Current shunts were installed to measure the output current of both DC/DC converters that step down the battery pack voltage to +13.8 V used for subsystems in the vehicle. The vehicle also has a 12 V auxiliary battery to start the vehicle, so a current shunt was also used to measure that batteries current. Another current shunt was used to measure the data acquisition systems batteries. This was used to detect if power to the data acquisition system was dropping to low. In the event of this happening, the system was designed to enter a controlled shutdown to make sure the data was saved and closed in a known manner. The final use of this measurement was to empirically find the power consumption of the data acquisition system as a whole and calculate the needed amount of battery capacity to run for a desired amount of time.

Next, the main battery pack voltage needed to be measured. This was done by using a high power resistor to step down the voltage and then another type of hall effect sensor was used to measure that voltage. Careful attention to the heat dissipation of this sensor was vital. The entire sensor was installed in a custom aluminum box with the power resistor connected to the box with thermal compound. Bolt patterns were also drilled into the box to support a small fan

in case forced cooling was required. It was shown that forced cooling was not required with the aluminum box

In addition to voltages and currents, three temperatures were measured all with type K thermocouples. These were outside temperature, inside temperature, and the motor compartment temperature. The outside temperature was measured not only to provide data to compare tests with ambient temperature, but also to eventually use this measurement to make smarter control decisions. The inside temperature was primarily taken for use with the plans to upgrade the air conditioning and heating systems. This ensures that the inside vehicle temperature can be controlled to keep the vehicle comfortable for passengers. Finally, a thermocouple was placed in the motor compartment near the inverter. This was done because a serious pitfall of the current vehicle is an inverter over-heating problem. We wanted to deduce whether this problem was contained to purely the inner components of the inverter, or if the entire motor compartment was increasing in temperature. This was important information because two solutions arose to either increase the liquid cooling system size for the inverter or increase the air flow in the motor compartment. This will be discussed further later in this paper.

Other sensors include a GPS module to track where the vehicle was and had been, as well as, used to coarsely calculate speed of the vehicle. Lastly an inclinometer was installed because a major design goal for the vehicle was the ability to climb hills without a significant reduction of speed.

### 2.5 Software

The software for the embedded system and the computer system were programmed in LabVIEW. The embedded system took advantage of the new LabVIEW FPGA module to implement the serial protocols to interface the various sensors. This provided faster access to the

digital module than using the real-time controller, which allowed for performance gains on the order of 10 times faster using the FPGA. Once the device drivers were programmed, the rest of the embedded system was programmed in the real-time host environment to support deterministic timing. This data was collected, processed, and then streamed over the Ethernet connection to the computer.

The computer side then grabbed the data packets and decoded the packets. These were then streamed into shared memory between three monitors. The three monitors were all mounted in the rear of the vehicle as shown below in Figure 2.5.1.

Figure 2.5.1: University of Kansas Shuttle Bus Data Acquisition System

The middle monitor was designed to look like a normal gauge panel a driver would see when driving the vehicle. This included a speedometer, tachometer, temperature gauges, and the main controllers to start and stop acquisition. The center monitor also includes the main battery pack voltage because this can be used as an estimated gas gauge for the lead acid batteries. Finally, the incline information is display by a sliding bar.

The left monitor was programmed to show detailed information about the sensor data streams in several forms. First, there is an option to see the data streams as either graphs or as

gauges with green, yellow, and red zones. The graphs allow the researcher to observe the data as it is streaming over the last approximate minute. This feature makes it easier to detail fast events or hold enough information if a researcher is looking for a particular event to occur. The gauges provided a higher level view of the data and by properly setting the green, yellow, and red zones make it easy to see values that are approaching damaging levels. This view was necessary due to the large amount of information being streamed continuously.

The right monitor displays information regarding location, slower occurring events, and a customizable graph. First, the GPS data latitude and longitude are parsed and plotted in a graph on the right monitor. The idea is a future improvement would be to connect this data to a google maps interface and plot the real route as it is occurring. Surrounding the coordinates graph is a variety of fill gauges. These are used for displaying slower occurring information such as battery capacity for the main pack, auxiliary battery, and the data acquisition battery. Finally, on the right monitor is a customizable graph. The graph supports a drop down menu for both the x and y axis that contains a list of all of the data streams. These can then be selected and it will update by plotting any two selected variables against each other. This allows the researcher to view potential correlations in variables. Plotting against time is also an option on the x axis only for completeness, but is a little redundant as most variables are plotted on the left screen against time.

The final feature implemented on the computer side of the system was saving all of the raw data to a text file for post processing. The next section will discuss in more detail the tests that were run and present some examples of this data.

#### 2.6 Test Procedures

Two test tracks were used to test the vehicle. This allowed tests to be conducted with as consistent routes as possible. Because drive cycles have variability even when driving the same route, driving different routes would have added more complexity to the analysis when attempting to compare hardware performance. The first track was a short square loop track. It was approximately 1200 feet total and had very low inclines (< 3% grade). This track was used to make a large number of loops, also helping to average out the variability between individual laps.

A second course mapped was an approximate 4000 feet rectangle that included a short but steep hill with a grade of 14%. This course had a few advantages of over the first course. First, it had two longer straight sections that allowed the vehicle to be driven at speeds that correspond with normal city driving conditions. Second, the hill provided data on the vehicles ability to climb a relatively steep grade. Thirdly, driving the course in reverse allowed the vehicle to be coasted down the hill and strong regeneration data was attainable. This is an important future requirement as there are plans to recapture more regeneration energy.

In general, the test procedure for acquiring data remained the same. First, the data acquisition system was powered on and recording was started. Then the vehicle was turned on and the test was run. Then the vehicle was parked and turned off. Finally, the data acquisition stopped and the data was saved to an external memory device for post processing. The results from the tests presented in this paper are primarily for operational validation of the data acquisition system.

#### 2.7 Results

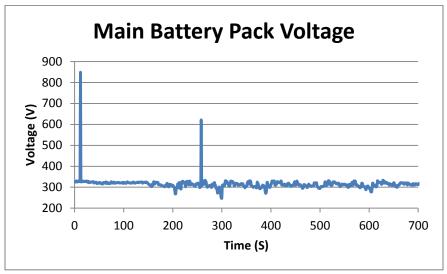

The data below is shown in its raw form. These tests were meant to evaluate the overall operation of the system before adding any extra post processing software filtering. By characterizing the system this way the first upgrades will be to help improve the hardware. This makes the system more robust, and after that then software filters can be applied to smooth the data. The data below is a trial run from the shorter course driven for five laps. Additional data from other tests can be found in Appendix A. Figure 2.7.1 shows the main battery pack voltage during the test.

Figure 2.7.1: Main Battery Pack Voltage

It can be seen that there were two spikes in the battery pack voltage measurement. This is likely to be due to noise in the wires from the sensor. With the exception of those two points, the data follows an expected trend. Overall, the data is trending downward since these are lead acid batteries that have a faster voltage drop as they are discharged compared to newer technologies. The final voltage averaged 12.7 V lower than the starting voltage value. The dips in the data are also expected because as the system comes under high load, such as when the electric motor

starts, the voltage dips momentarily. The Figure 2.7.2 shows the main battery pack current measurement.

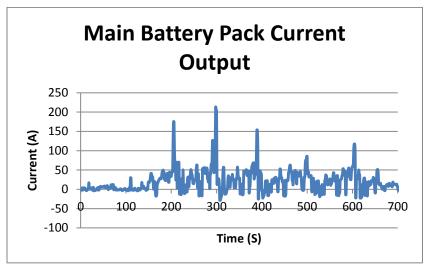

Figure 2.7.2: Main Battery Output Current

The battery pack current provides several interesting results. First, it can be seen that negative current is occurring, so when the vehicle is coasting it is regenerating energy. It can also be seen from the graphs this regeneration is a relatively low amount of recaptured energy. A second observation is the spikes in the current values. Several of these values have multiple non-repeating data points in the region, which suggest they are neither outliers nor noise. This observation is further support below as the spikes in the battery pack current are time aligned with the spikes in the motor current shown in Figure 2.7.3.

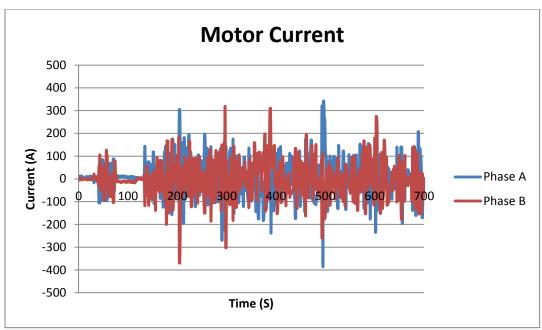

Figure 2.7.3: Phase A and B Motor Current

The motor current appears at first to have a significant amount of noise. It is important to remember that the sampling rate of the system is 10 Hz, so we are not even close to 10 times the motor current frequency required to accurately measure the current frequency and amplitude according to Nyquist frequency and Shannon's sampling theory. Therefore, it was not expected to be able to recreate perfectly the current waveform. This measurement is taken to get a general average of motor current usage after the inverter and potentially to be used for control in the future with a faster acquisition rate. Figure 2.7.4 below is a zoomed in window of values taken from the beginning of the test.

Figure 2.7.4: Zoomed in Motor Current

To validate the measurement, the observation can be made that the behavior of the two phases does seem to be similar but shifted in phase. That is exactly what was expected. Again, the waveforms do not follow precisely due to the low sampling rate.

Next, the DC/DC current input measurements are displayed in Figures 2.7.5 and 2.7.6.

Figure 2.7.5: DC/DC 1 Input Current

Figure 2.7.6: DC/DC 2 Input Current

Again like the motor current the DC/DC converters show several large spikes. It was noticed throughout testing that when the compressor for the compressed air system starts a current spike can be seen. It is believed that the two spikes are outliers; however, because they are not time aligned with each other and both are bussed together. Three spikes are time aligned which would suggest that there is possibly a vehicle condition that is causing a large current draw,

likely due to the compressor starting. The output side of the converters is shown in Figures 2.7.7 and 2.7.8.

Figure 2.7.7: DC/DC 1 Output Current

Figure 2.7.8: DC/DC 2 Output Current

The output side of the DC/DC converters shows a relatively steady current response. The measurement does appear to have significant amount of noise. This is likely due to the fact that these sensors are the current shunts rather than the hall effect sensors. This causes noise in the measurement because it is a low voltage signal (± 50 mV max), and it is connected to the data acquisition with 5 to 8 feet of wire that run through the vehicle. This signal is then amplified by the data acquisition system, so any noise introduced from the sensor to the system is also amplified. Several alternatives to help alleviate some of this noise will be discussed in the recommendations.

Figure 2.7.9: Auxiliary Battery Current

The auxiliary battery behavior, in Figure 2.7.9, displays similar noise characteristics as the DC/DC converters output, and this is also likely due the current shunt sensor. The behavior of this signal varies depending on the charge level of the battery. Because the auxiliary battery is bussed together directly with the DC/DC converters it can be in one of several "modes". First, is full charged (around 14 V) and the graph will show positive current leaving the battery. The second state is almost full charged where the open circuit voltage of the battery is very close to the output of the DC/DC converters. In this case, the battery will either be float charging or if the load on the bus suddenly increases it will help make up the current draw for the voltage dip. Thirdly is a partially or mostly discharged battery state. During this state, the auxiliary battery has enough capacity to start the vehicle and as soon as it does the DC/DC converters begin charging the battery and the data is seen as negative current flowing into the battery. This becomes important because the DC/DC converters need to be slightly oversized when designing to account for the fact that they may not only be supporting the worst case load on the low voltage system, but may also be charging the auxiliary battery. This test had a state that was lower than the bus voltage because the average current was -0.62 A. The next measurement was the compressor input current shown in Figure 2.7.10.

Figure 2.7.10: Compressor Input Current

The compressor is used to keep the air system charged for the air brakes and suspension system. Not surprisingly current spikes are observed when the compressor turns on. The relatively low current draw is deceiving because it is powered from the high voltage side, so the overall power consumption is substantial. Another parasitic load on the system is the front panel gauges and display. Their current input graph is shown below in Figure 2.7.11.

Figure 2.7.11: Front Panel Input Current

It was expected that the front panel gauges would consume a large amount of energy because they are older technology lights, gauges, and peripherals. It was decided that it was unnecessary to have finer grain measurements than simply the total current consumption because these will be replaced with low energy lights and gauges in the future, and it is only interesting to know the overall energy savings. The front panel does show two low spikes in the data that have no explanation. Because the front panel consists of only parasitic loads, it is not possible for the front panel to put energy back into the system. Although this measurement is taken with a hall effect sensor it does run almost the entire length of the bus (22 feet), so there are additional noise reduction considerations to try and eliminate those erroneous spikes. These considerations will be discussed in the recommendations section.

Figure 2.7.12: Temperature Measurements

The four thermocouples were measured and the results are shown in Figure 2.7.12. They behaved as expected and the readings were validated with weather data corresponding to the time and location. A very important observation is the original hypothesis of the motor bay heating being the cause of the inverter overheating can be disproven from this data as the temperature did not increase significantly. This shows for certain that the overheating is contained within the inverter, likely from the IGBTs. A final note would be the vehicle would benefit from an air conditioning system as the temperature suggests this was not a particularly comfortable riding experience.

Now that the internal measurements have been discussed the measurements pertaining to the vehicle as a whole will be discussed. This mainly consists of data that is read and parsed from the GPS module. The first chart, Figure 2.7.13, shows the vehicle speed as measured by the GPS.

Figure 2.7.13: Vehicle Speed

Right away it is important to mention that this test as described previously began taking data before moving the vehicle. This is relevant because the vehicle started in a metal garage, and the GPS was unable to lock a satellite until it left the garage. After leaving the garage, the GPS module still required a significant amount of time before finally locking a sufficient satellite signal. Despite the pitfalls, the GPS module was accurate to within a few miles per hour over its update rate of 1 Hz. This was validated by simultaneously watching the speedometer and the GPS read out for dynamic scenarios. To provide a more scientific validation, the vehicle was put into cruise control on the flattest portion of road and the GPS value was compared to the vehicle speed and was found to be within 4 mph at all times. This resolution is sufficient to build drive cycles to feed a simulation model. The next measurement captured from the GPS module was the course of the vehicle in degrees as seen in Figure 2.7.14.

Figure 2.7.14: Vehicle Direction

The course is measured where compass north is at 0 or 360 degrees. This measurement was primarily used to provide the compass direction indication that many vehicles now incorporate. It was captured as it may be useful in future research if the speed and direction of the vehicle are required.

Figure 2.7.15: Test Battery Current

The last measurement is the test battery current, shown above in Figure 2.7.15, which is decoupled from the vehicle electrical system. It can be seen that the power draw from the test battery was significant. This is due to the fact that it was powering three monitors, a computer, and the data acquisition system. A major update needed is a high capacity source for the test system. It was consistently seen that the data acquisition system power ran out before the vehicle power ran out. This does not allow endurance testing on the vehicle if the data

acquisition system cannot outlast the vehicle. Fortunately this measurement provides the necessary data to calculate the amount of energy needed to fulfill that requirement, and additional batteries can easily be added in parallel to support the desired run time.

### 2.8 Conclusions

There were two options that were explored throughout the development of the data acquisition system for the electric shuttle bus. The first was a custom embedded system built around the PIC32 microcontroller. This system offered a large amount of flexibility and significant cost reduction over off-the-shelf solutions. Despite these advantages, the custom system suffered from increased difficulty to implement, maintain, and use. Therefore, a CompactRIO from National Instruments was chosen as the platform to design the system around.

The system also completely satisfies the original design requirements. It is able to support current and future research because there are extra analog, digital, and thermocouple channels for use on future sensors. The system is easy to implement and maintain because it is written in LabVIEW, which is a common language and relatively easy to learn. The system is simple to expand because the CompactRIO chassis allows modules to be plugged in to add additional functionality and then leverage LabVIEW for quick application development. The system has sufficient performance being able to sample with a throughput of 10 Hz. The ability to feed a model with deterministic data is handled through the use of the real-time module.

The only two requirements that are not fully met is isolation from the vehicle, which in turn does not make the system completely portable from one vehicle to another without being invasive. The data acquisition system only violates this criterion with the current shunts on the low voltage side current measurements. These were chosen over hall effect sensors for cost reasons, but can very easily be upgraded to fully meet the isolation requirement. Although the

system meets the design goals, there are some areas of improvement that will help the system be more robust in measurement quality.

#### 2.9 Recommendations

The current shunts have the highest amount of noise in their measurement so they are addressed first. Ideally, the solution is to replace these with hall effect sensors because they are more immune to noise and would isolate the measurement. If that is not possible then twisted pair wire with a shield could be used to connect the shunt and the system. The shield will help reduce the amount of induced noise, and the twisted pair wire will typically see noise on both wires which makes filtering it out with a differential measurement more effective. The same wire scheme can be used to reduce the noise in the front panel measurement since it has a relatively long wire length. The inclinometer originally chosen was a magnetometer that uses the magnetic field of the earth to detect orientation in two axes. There was an unanticipated major flaw in this sensor because it assumes the largest magnetic field is the earth. The sensor was installed at the back of the vehicle so the motor was creating a stronger magnetic field and causing huge errors in the sensor. The inclinometer was switched to a fluid version, and future tests will validate that this completely resolved the problem.

The GPS module worked well once it locked a satellite signal, which in many cases took several minutes. Therefore, it is recommended to add an additional external antenna and mount it on top of the vehicle to maximize the antenna gain and minimize the objects blocking line of site of the antenna. This will help the GPS lock a signal faster. The battery system powering the data acquisition system was also found to be insufficient to power the system longer than the vehicle battery system. Therefore, a future upgrade will include calculations to identify the required capacity of the batteries and implement the additional batteries to allow endurance

testing of the vehicle. Finally, the system relied too heavily on the communication with the computer. Occasionally the real time module would lose communication with the computer causing it to lock up and would require a reset to bring it out of lock up. This presented a problem because we lost the data collected when this happened because the computer program also crashed. To fix this problem a buffer should be implemented on a future software version to store data until the communication returns on the real time module side. The computer side should then run the communication in its own thread and the file I/O operations in a separate thread so these are decoupled. This way if communication is locked the data is not lost, and if a restart is required the file can be saved.

## 2.10 References

- [1] Qiang, S. and L. Chenguang (2012). "Data Acquisition System for Electric Vehicle's Driving Motor Test Bench Based on VC++." Physics Procedia 33(0): 1725-1731.

- [2] Baghli, L., et al. (2012). Optimal hybrid vehicle, embedded data acquisition and tracking. Environment Friendly Energies and Applications (EFEA), 2012 2nd International Symposium on.

- [3] Hairr, M. E. G., Paul; Bailey, J. Ronald; Madden, Woodlyn (2009). Data Acquisition System for Electric- and Hybrid-Electric Buses. <u>EVS24</u>. Stavanger, Norway.

- [4] Baker, B. C., et al. (2012). Electric transit bus for variable grade terrain. Electric Vehicle Conference (IEVC), 2012 IEEE International.

- [5] Coosemans, T. B., Ricardo; Timmermans, Jean-Marc; Mulders, Frederik Van; Mierlo, J. Van (2009). Data Acquisition System for Optimization of Series Hybrid Propulsion Systems. <u>EVS24</u>. Stavanger, Norway.

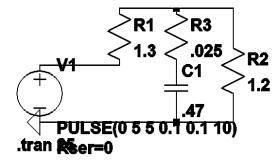

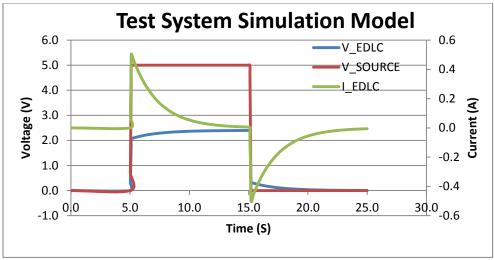

# 3. EDLC TEST SYSTEM