# Hardware/Software Co-Design via Specification Refinement

By

## Wesley G. Peck

Submitted to the graduate degree program in Electrical Engineering & Computer Science and the Graduate Faculty of the University of Kansas School of Engineering in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Dr. Perry Alexander, Chairperson

Dr. Andy Gill

**Committee members**

Dr. Prasad Kulkarni

Dr. Xin Fu

Dr. Caroline Bennett

Date defended: \_\_\_\_\_

The Dissertation Committee for Wesley G. Peck certifies that this is the approved version of the following dissertation :

Hardware/Software Co-Design via Specification Refinement

Dr. Perry Alexander, Chairperson

Date approved: \_\_\_\_\_

## Abstract

System-level design is an engineering discipline focused on producing methods, technologies, and tools that enable the specification, design, and implementation of complex, multi-discipline, and multi-domain systems. System-level specifications are as abstract as possible, defining required system behaviors while eliding implementation details. These implementation details must be added during the implementation process and the high effort associated with this locks system engineers onto the chosen implementation architecture.

This work provides two contributions that ease the implementation process. The Rosetta synthesis capability generates hardware/software co-designed implementations from specifications that contain low level implementation details. The Rosetta refinement capability extends this by allowing a system's functional behavior and its implementation details to be described separately. The Rosetta Refinement Tool combines the functional behavior and the implementation details to form a system specification that can be synthesized using the Rosetta synthesis capability. The Rosetta refinement capability is exposed using existing Rosetta language constructs that have, previous to this work, never been exploited.

Together these two capabilities allow the refinement of high level, architecture independent specifications into low level, architecture specific hardware/software co-designed implementations. The result is an effective platform for rapid prototyping of hardware/software co-designs and provides system engineers with the novel ability to explore different system architectures with low effort. Page left intentionally blank.

# Contents

|   | Abstract                                                                                                                                                                                             | iii                                                                  |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|   | Contents                                                                                                                                                                                             | v                                                                    |

|   | List of Figures                                                                                                                                                                                      | vii                                                                  |

|   | List of Tables                                                                                                                                                                                       |                                                                      |

|   | List of Code Examples                                                                                                                                                                                |                                                                      |

| 1 | <ul><li>Introduction</li><li>1.1 Motivation</li><li>1.2 Research Contribution</li></ul>                                                                                                              | <b>1</b><br>4<br>4                                                   |

| 2 | <ul> <li>Related Works</li> <li>2.1 Ad-Hoc Program Transformation</li> <li>2.2 Program Transformation Tools</li> <li>2.3 Program Synthesis</li> <li>2.4 Approaches to System-Level Design</li> </ul> | 5<br>6<br>7<br>14                                                    |

| 3 | The Rosetta Specification Language3.1 Domains3.2 Facets3.3 Requirements Modeling and Specification                                                                                                   | 17<br>17<br>19<br>20                                                 |

| 4 | <ul> <li>Synthesis of Rosetta Specifications</li></ul>                                                                                                                                               | 23<br>24<br>29<br>39<br>48<br>50<br>51<br>51<br>54<br>56<br>56<br>56 |

| 5 | <ul> <li>HW/SW Co-Design of Top-Level Designs</li> <li>5.1 Processing Refinements</li> <li>5.2 Implementation Resources</li> <li>5.2.1 Target Physical Resources</li> </ul>                          | <b>65</b><br>68<br>71<br>73                                          |

|   | 5.2.2 Bridge Physical Resources                                                        | 74       |  |  |

|---|----------------------------------------------------------------------------------------|----------|--|--|

|   | 5.2.3 Memory Physical Resources                                                        | 76       |  |  |

|   | 5.3 System Partitioning                                                                | 77       |  |  |

|   | 5.3.1 Target Attributes                                                                | 77       |  |  |

|   | 5.3.2 I/O Parameters                                                                   | 78       |  |  |

|   | 5.3.3 I/O Partitioning for Software                                                    | 79       |  |  |

|   | 5.3.4 Default Partitionings                                                            | 81       |  |  |

|   | 5.4 Component Implementation                                                           | 81       |  |  |

|   | <ul><li>5.5 Project Generation</li><li>5.6 Top-Level Design Example</li></ul>          | 82<br>84 |  |  |

|   |                                                                                        | 84       |  |  |

| 6 | Rapid Prototyping Refinements                                                          | . 89     |  |  |

|   | 6.1 Refinement Discovery and Application                                               | 90       |  |  |

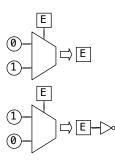

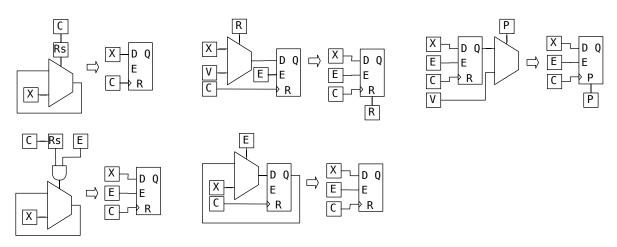

|   | <ul><li>6.2 Behavior Refinement</li><li>6.2.1 Hardware Clocks via Refinement</li></ul> | 92<br>00 |  |  |

|   | 6.2.2 Hardware Resets via Refinement                                                   | 92<br>05 |  |  |

|   | 6.2.3 Hardware Enables via Refinement                                                  | 95<br>96 |  |  |

|   | 6.3 Data Refinement                                                                    | 90<br>98 |  |  |

|   | 6.3.1 Refinement of Integer Types                                                      | 100      |  |  |

|   | 6.3.2 Refinement of Algebraic Data Types                                               | 101      |  |  |

|   | 6.3.3 Refinement of Declarations                                                       | 107      |  |  |

|   | 6.3.4 Data Type Refinement Limitations                                                 | 108      |  |  |

|   | 6.4 Communication Refinement                                                           | 109      |  |  |

|   | 6.4.1 Communication Refinement in the Top-Level Design                                 | 110      |  |  |

|   | 6.4.2 Fast Simplex Link Protocol                                                       | 111      |  |  |

|   | 6.4.3 Go/Done Protocol                                                                 | 116      |  |  |

| 7 |                                                                                        | . 119    |  |  |

|   | 7.1 RS-232 Loop-Back Example                                                           | 121      |  |  |

|   | 7.2 State Machine Example                                                              | 125      |  |  |

|   | 7.3 Trusted Platform Module Design                                                     | 131      |  |  |

| _ | 7.4 Evaluation Summary                                                                 | 137      |  |  |

| 8 | Future Work                                                                            | . 139    |  |  |

| 9 | Conclusion                                                                             | . 141    |  |  |

|   | References                                                                             | . 143    |  |  |

| A | Synthesis Constraints                                                                  | . 146    |  |  |

|   | MicroBlaze LLVM Backend                                                                |          |  |  |

|   | Hardware Example VHDL Output                                                           |          |  |  |

|   | Software Example MicroBlaze Output                                                     |          |  |  |

|   | <b>E Top-Level Design Resource Definitions</b>                                         |          |  |  |

|   | Xilinx Platform Studio Project Files       154                                         |          |  |  |

|   | TPM Specification                                                                      |          |  |  |

|   | -                                                                                      | -        |  |  |

# **List of Figures**

| Formal Specification in Program Synthesis Literature        | 7                                        |

|-------------------------------------------------------------|------------------------------------------|

| Example Square Root Formal Specification                    | 8                                        |

| Square Root Proof as Program Example                        | 8                                        |

| Example Less-All Formal Specification                       | 9                                        |

| Example Less-All Program using Transformational Synthesis   | 10                                       |

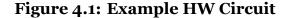

| Example Synthesized Hardware Circuit                        | 27                                       |

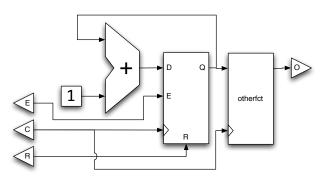

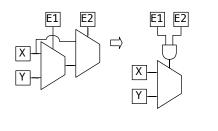

| Graph Comparator Canonicalization                           | 43                                       |

| Graph Multiplexer Canonicalization                          | 44                                       |

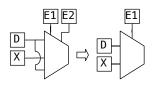

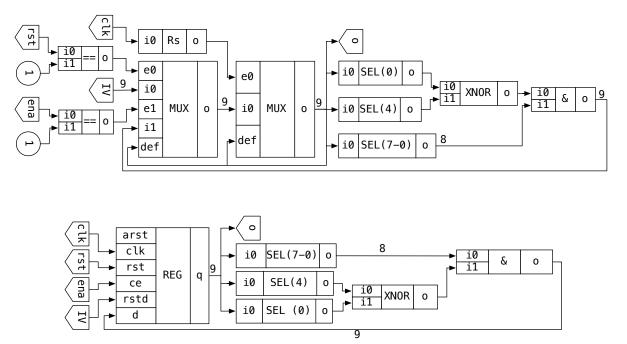

| Graph Register Canonicalization                             | 46                                       |

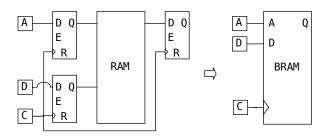

| Graph RAM Canonicalization                                  | 47                                       |

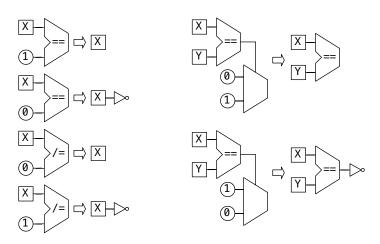

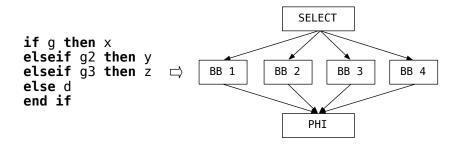

| Rosetta If-Expression LLVM-IR                               | 53                                       |

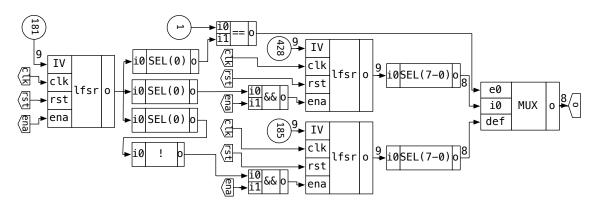

| Rosetta Linear Feedback Shift Register Graph Representation | 60                                       |

| Rosetta Pseudo-Random Number Generator Graph Representation | 61                                       |

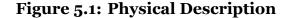

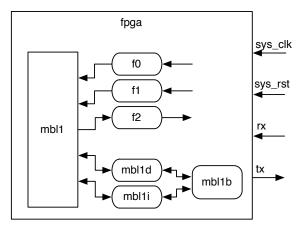

| Top-Level Design Physical Description                       | 86                                       |

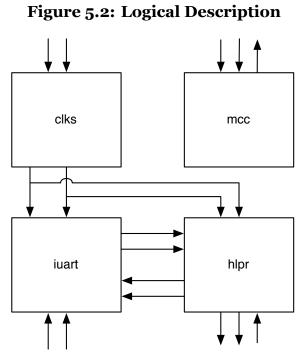

| Top-Level Design Logical Description                        |                                          |

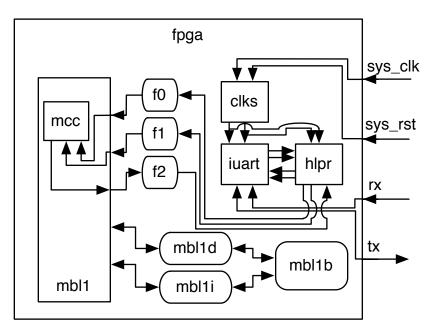

| Resulting Top-Level Design Implementation                   | 87                                       |

|                                                             | Example Square Root Formal Specification |

# **List of Tables**

| 4.1 Types Supported by Rosetta HW Synthesis 2                               |    |

|-----------------------------------------------------------------------------|----|

| 4.2 Parameters Supported by Rosetta HW Synthesis 2                          | 25 |

| 4.3 Expressions Supported by Rosetta HW Synthesis 2                         | 26 |

| 4.4 Representation of RTL Nodes                                             | 30 |

| 4.5 RTL Intermediate Form Type Representation                               | 31 |

| 4.6 RTL Intermediate Form Parameter Representation                          |    |

| 4.7 Conversion of Rosetta Expressions into RTL Nodes                        | 36 |

| 4.8 Representation of Graph Nodes                                           | 40 |

| 4.12 Conversion of Explicit Graph into VHDL                                 | 49 |

| 4.13 Software Representation of Facet State                                 | 51 |

| 4.14 Conversion of Rosetta into LLVM-IR                                     | 52 |

| 4.15 Rosetta Linear Feedback Shift Register RTL Intermediate Form           | 58 |

| 4.16 Rosetta Pseudo-Random Number Generator RTL Intermediate Form           | 59 |

| 6.1 Guided Data Type Refinement Representations                             | 04 |

| 6.2 Definitional Data Type Refinement Representation                        | 07 |

| 6.3 Refinement of Abstract Communication into Fast-Simplex Link Signaling 1 | 14 |

| 6.4 Refinement of Abstract Communication into Go/Done Signaling 1           | 18 |

| 7.1 RS-232 Rapid Prototyping Changes 12                                     | 22 |

| 7.2 RS-232 Example Implementation Efficiency                                |    |

| 7.3 State Machine Rapid Prototyping Changes 12                              | 28 |

| 7.4 State Machine Example Implementation Efficiency                         | 29 |

| 7.5 Trusted Platform Module Rapid Prototyping Changes                       |    |

| 7.6 Trusted Platform Module Example Implementation Efficiency               |    |

|                                                                             | 00 |

# **List of Code Examples**

| 3.1<br>3.2<br>3.3                             | Subtle Difference Between Implementation and SpecificationObvious Difference Between Implementation and SpecificationUnderspecified Rosetta Function                                                                                                                                    | 20<br>21<br>21                         |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7 | Example of a Synthesizable Rosetta FacetExample Synthesis AttributesImporting Libraries for Hardware SynthesisExample of Synthesizable Behavioral TermsRosetta Hardware Synthesis ExampleRosetta Software Synthesis ExampleRosetta Multiply-Accumulate LLVM Intermediate Representation | 28<br>29<br>34<br>34<br>57<br>62<br>63 |

| 5.1                                           | Shared Facet Definitions                                                                                                                                                                                                                                                                | 69                                     |

| 5.2                                           | Specialized Facet Definitions                                                                                                                                                                                                                                                           | 69                                     |

| 5.3                                           | Top-Level Design Resource Instantiation                                                                                                                                                                                                                                                 | 72                                     |

| 5.4                                           | Rosetta Implementation Target                                                                                                                                                                                                                                                           | 73                                     |

| 5.5                                           | Rosetta Communication Bridge                                                                                                                                                                                                                                                            | 75                                     |

| 5.6                                           | Rosetta Memory Resource                                                                                                                                                                                                                                                                 | 76                                     |

| 5.7                                           | System Partitioning in a Top-Level Design                                                                                                                                                                                                                                               | 78                                     |

| 5.8                                           | Full Top-Level Design Example                                                                                                                                                                                                                                                           | 85                                     |

| 6.1                                           | Refinement Discovery Example                                                                                                                                                                                                                                                            | 91                                     |

| 6.2                                           | Hardware Clock Refinement                                                                                                                                                                                                                                                               | 92                                     |

| 6.3                                           | Refined Hardware Clock                                                                                                                                                                                                                                                                  | 93                                     |

| 6.4                                           | Hardware Reset Refinement                                                                                                                                                                                                                                                               | 95                                     |

| 6.5                                           | Refined Hardware Reset                                                                                                                                                                                                                                                                  | 96                                     |

| 6.6                                           | Hardware Enable Refinement                                                                                                                                                                                                                                                              | 97                                     |

| 6.7                                           | Refined Hardware Enable                                                                                                                                                                                                                                                                 | 98                                     |

| 6.8                                           | Data Representation in a Counter                                                                                                                                                                                                                                                        | 99                                     |

| 6.9                                           | Data Refinement of Integer                                                                                                                                                                                                                                                              | 100                                    |

| 6.10                                          | Refined Integer Data Type                                                                                                                                                                                                                                                               | 101                                    |

| 6.11                                          | Algebraic Data Type in Rosetta                                                                                                                                                                                                                                                          | 102                                    |

|                                               | Guided Algebraic Data Type Refinement                                                                                                                                                                                                                                                   | 103                                    |

| 6.13                                          | Definitional Algebraic Data Type Refinement                                                                                                                                                                                                                                             | 106                                    |

|                                               | Data Type Refinement of Declarations                                                                                                                                                                                                                                                    | 108                                    |

| 6.15                                          | Incorrect Application of Data Type Refinement                                                                                                                                                                                                                                           | 108                                    |

| 6.16                                          | Abstract Communication in Rosetta                                                                                                                                                                                                                                                       | 100                                    |

| 6.17 | Fast-Simplex Link Communication Refinement   | 111 |

|------|----------------------------------------------|-----|

| 6.18 | Refined Fast-Simplex Link Communication Link | 112 |

| 6.19 | Go/Done Communication Refinement             | 116 |

| 6.20 | Refined Go/Done Communication Link           | 117 |

|      | RS-232 Loop-Back Specification               |     |

## 1 Introduction

System-level design is an engineering discipline focused on producing methods, technologies, and tools that enable the specification, design, and implementation of complex, multidiscipline, and multi-domain systems. Modern computer systems are composed of thousands to millions of heterogeneous components so technologies and tools for system-level design are aimed at helping engineers deal with the complexity of requirements, design, implementation, and integration when creating systems of this scale.

Traditionally, complexity is reduced by introducing abstractions. These abstractions, if chosen properly, prune unimportant details from the engineer's view and focus them on important details. For instance, when designing a large hardware system by composing together multiple hardware components, all of the individual components in the system are abstracted into input/output interfaces by throwing away the internal implementation details. Because the implementation details are no longer present, the engineer composing the system must reason about system behavior by examining the interaction of components via their input/output protocols. The abstraction is appropriate in this instance because it is focusing the engineer on the task at hand, component composition. Focusing on how every component in the system computes its outputs from its inputs would be needlessly complicated. However, abstractions must eliminated if systems are to be realized as concrete products. There are two ways that this can be done.

First, a compiler or synthesizer can be used to remove abstractions by filling in the details needed for a concrete implementation. Expanding on the example above, a synthesizer will fill in an instantiated component's interface with the internal implementation details producing a complete hardware circuit for the design. This approach is highly desirable because it reduces engineering effort, reduces time-to-market, and controls design and implementation costs. However, completely automated concretization via compilation and/or synthesis can produce inefficiencies. For many products, especially software products, these inefficiencies are tolerable and can be worked around by increasing the performance of the underlying

hardware. At the system-level, however, these inefficiencies add up quickly due to the scale of the problems. The resulting implementations are either undesirable or incorrect due to nonfunctional requirements not expressed in the design and not taken into account during the compilation process.

Second, an engineer can manually eliminate abstractions by replacing them with low-level equivalents. This method is common in system-level design due to inefficiencies introduced by automated synthesis. Highly abstract system models are developed using a system-level language so system properties can be accurately understood. It is then converted into an implementation by developing an equivalent low-level model containing only implementation-level abstractions. Any unsupported abstractions in the abstract model must be replaced with their low-level equivalents. Abstractions are never completely removed by a system engineer, they are simply iteratively refined until the engineer is content with the results produced via automated synthesis. The problem with first approach is not that tools are incapable of producing efficient implementations. Indeed, compilers for many languages produce more efficient code than most engineers are capable of and they do so without introducing errors. The problem is the size of the semantic gap between abstract specifications and concrete implementations.

The size of this semantic gap is dependent on the language being used and is caused by the classic trade-off in language design: expressiveness versus interpretability. Common languages, such as C/C++ and Java, sacrifice expressiveness so that they can easily be interpreted by a computer. The semantic gap for languages that lean towards interpretability is small because the abstraction levels are low. The semantic gap between a C/C++ design and the interpretation of that design at the microprocessor level is small. A compiler can easily navigate this gap on behalf of the engineer because there are few intelligent choices that need to be made. A good compiler could easily test all of the available choices and pick the best choice based on some optimization criteria set by the engineer. Most compilers for these languages already do this to some extent. Languages that lean towards expressiveness sacrifice interpretability to gain high levels of abstraction. As the abstraction level rises, however, the semantic gap between design and implementation becomes larger and the number of intelligent decisions that a compiler must make grows. Eventually it is either impossible or undesirable for a compiler to make these decisions. For instance, expressive specification languages allow system engineers to purposefully underspecified systems by omitting the definition of a function. Obviously there is no way for a compiler to "fill in implementation details" for a function that is never specified.

Even when a compiler is able to provide the required details, their use may still be undesirable. To be desirable, the compiler must make implementation decisions on behalf of an engineer that the engineer considers both correct and intelligent. Compilers are typically very good about making correct decisions and, as such, they rarely introduce errors into an implementation. However, in highly abstract designs, compilers are not always capable of making intelligent decisions because *they lack the information needed to make intelligent implementation decisions* because this information is often elided in specifications.

The system design as described by a specification is ambiguous with respect to desired implementations because specifications are *suppose* to be ambiguous in this respect. Modern compilers are poorly suited to these highly abstract specification languages because the intentional ambiguity leads to poor implementation decisions. To achieve synthesizability, the most often used system-level design methodologies are built upon low-level abstractions with system engineers often hand-coding software components in C/C++ and hardware components in VHDL or Verilog. Even the next generation of system-level design tools only use moderate levels of abstraction. For instance, SpecC, SystemC, and SPARK are all next generation system-level synthesis tools that take C/C++ designs in various forms and synthesize systems from them [8, 10, 19, 20]. While C/C++ provides much more abstraction for hardware design than the traditional VHDL or Verilog, even these abstraction levels are far below those provided by specification languages such as Rosetta.

## 1.1 Motivation

The motivation for this work comes from personal experience in system-level design and implementation. System engineers want to raise abstraction levels because it eases the development effort by reducing the overwhelming amount of information in a system design into approachable chunks. Raising abstraction levels helps produce correct designs quicker and cheaper. In contrast, system engineers also desire control over every aspect of a product's final implementation so that non-functional requirements can be met. These non-functional requirements vary depending on the engineering domain, but include things such as minimizing computational latency, maximizing computational throughput, minimizing transistor counts, minimizing memory requirements, minimizing jitter, maximizing battery life, reducing cost, etc.

The great conundrum in system-level design, especially when multiple engineering domains are involved, is how to produce methods, technologies, and tools that promote rapid creation of functionally correct specifications and designs without compromising control over nonfunctional requirements.

## **1.2 Research Contribution**

This work provides two major contributions, one to the engineering community and another to the research community. First, a Rosetta synthesis capability is provided that allows a subset of the Rosetta specification language to be automatically and efficiently implemented either as hardware circuits via VHDL or software programs via LLVM. Second, a system-level refinement capability is provided that supports rapid transformation of abstract, architecture independent specifications into low-level, architecture specific implementations. Together these two contributions provide an effective rapid prototyping platform for hardware/software codesign using the Rosetta specification language and give system engineers the novel ability to rapidly explore different implementation architectures without sacrificing control over the design of those architectures.

## 2 Related Works

The refinement capability developed in this work is implemented as a program transformation system that refines system-level specifications into HW/SW co-designed implementations. The transformation system identifies declarative refinements present in a system specification and then mechanically applies those refinements, creating a new system specification in the process.

Program transformation has a long and varied history in computing. Modern programming language compilers are built as complex program transformation systems that iteratively transform the high-level language syntax into low-level machine implementations. Many formal languages, specify evaluation, type-checking, and proof systems as term-rewriting systems and can be considered program transformation systems. Additionally, some modern programming languages include program generation facilities implemented as program transformation systems.

## 2.1 Ad-Hoc Program Transformation

Ad-hoc program transformation techniques facilitate user directed transformation using tool specific techniques often expressed outside a language's normal syntax. These techniques typically focus on providing program optimization transformations or on providing program generation capabilities aim at eliminating boilerplate code.

The Glasgow Haskell Compiler (GHC) supports program transformation by applying user defined rewrite rules on any code that matches a rewrite condition [21]. The rules themselves are specified and applied using GHC specific extensions to the Haskell programming language. The authors make it clear that this rule-based program transformation system should only be used to facilitate program optimizations beyond the capabilities of the compiler. For instance, short-cut deforestation is a common optimization applied using GHC's rule based program refinement [12]. As another example, the Groovy [6] programming language makes use of declarative annotations to support transformation of the compiler's internal AST representation. The program refinements are created by implementing custom Groovy compiler plugins. These refinements are most often applied by matching annotations that are specified declaratively within the Groovy program. The Groovy compiler uses these program transformations mainly to facilitate program generation targeted at eliminating boilerplate code. For instance, lazy field instantiation can be used for a Groovy object simply by annotating the object. The compiler will then transform the implementation of the object to include the necessary code to facilitate lazy instantiation.

These ad-hoc program transformations systems focus on performing transformation that preserve the functional behavior of a program but alter the performance or memory requirements of the program. In contrast, this work's transformation system focuses on the process of refining specifications into implementations via the addition of implementation details used to iteratively refine high-level specifications into low-level specifications. These additional implementation details are concerned chiefly with the process of mapping behaviors at the specification level onto resources at the implementation-level. Additionally, the process of mapping functional behavior onto implementation-level resources allows specification of specific implementation architectures, something not supported in existing program transformation tools.

### 2.2 Program Transformation Tools

Program transformation tools use program transformation techniques to aid in the development of a program. These tools range from standalone tools that transform specific languages, such as KBEmacs[36] and Inject/J[11], to transformation languages such as Stratego[35, 5] that help designers create custom transformations for any language, to runtime transformation engines that enable the construction of custom program transformation tools such as the ubiquitous byte-code engineering libraries for Java or the generic programming libraries Scrap Your Boilerplate[24] and Strafunski[23] for Haskell. There are two classes of tools presented here. First, KBEmacs and Inject/J provide program transformation capabilities that aid in the development of a program. When using these tools a programmer will typically intermingle manual coding with automated program transformation to create the desired final program implementation. The second class of tools aid in the creation of custom program transformation tools. In the case of Stratego, a domain specific language is exposed that aids in the development of abstract syntax trees, rewrite rules, and traversals. This domain specific language can be compiled into a C program that implements the transformation system. Strafunski and Scrap Your Boilerplate are similar in that they aid in the development of as languages.

In comparison to the first class of program transformation tools, this work is chiefly concerned with providing rapid prototyping and hardware/software co-design. Instead of intermingling manual coding and automated program transformation, the approach is to expose transformations as special language constructs that are intermingled within the specification. This approach provides better support for rapid prototyping because refinements are kept separate allowing them to be easily modified to achieve different results.

In comparison to the second class of program transformation tools, this work is not concerned with aiding in the development of transformation systems. Indeed, this work's transformation system is built with the aid of Uniplate[29], a Haskell transformation library in the same spirit as Strafunski and Scrap Your Boilerplate.

## 2.3 Program Synthesis

Program synthesis refers to a class of research that deals with automating software development with the goal of meFigure 2.1: Formal Specification[32, 22]

function F(x::D) where I(x)returns  $z::R|O(x,z) \equiv Body$

chanically deriving correct and efficient programs from formal specifications. Research in this area can be broken down into three major categories: proofs as programs, transformational synthesis, and knowledge based program synthesis[22].

All of the program synthesis research operates over formal specifications that can be represented as a quadruple  $F = \langle D, R, I, O \rangle$  where *D* is the input type constrained by the input condition  $I : D \mapsto boolean$  and *R* is the output type constrained by the output condition  $O : D \times R \mapsto boolean$ [32, 31, 22]. Syntactically, these specification can written as shown in figure 2.1. For a specification to be consistent, the expression *Body* and the output definition *O* must produce the same solutions for any input deemed valid by *I*.

#### **Proofs as Programs**

In the proofs as programs approach to program synthesis, specifications are hypotheses of the form  $\forall (x :: D) . \exists (z :: R)$  Figure 2.2: Square Root Specification

function  $sqrt(x :: \mathbb{N})$  where  $x \ge 0$ returns  $z :: \mathbb{N} | (z^2 \le x \land x < (z+1)^2)$

.  $(I(x) \implies O(x,z))$ . In words, hypotheses of this form state that for all valid inputs there exists a valid output. Program synthesis then proceeds by performing a constructive proof of the conclusion O(x,z) using the premise I(x). Because the proof is constructive, a program can be automatically extracted from the proof[22]. Proofs as programs techniques and tools include: QA3[18], Coq[25, 27], NuPrl[7], and Isabelle/HOL[4].

As an example of the proofs as programs approach, Kreitz[22] presents the formal specification of an integral square root algorithm as  $\forall (x :: \mathbb{N}) . \exists (z :: \mathbb{N}) . (x \ge 0 \implies z^2 \le x \land x < (z+1)^2)$ . The syntactic representation of this formal specification is given in figure 2.2.

The constructive proof of this formal specification can be done inductively. The base case of the inductive proof, x = 0, is proved by supplying the witness 0 for  $z_0$ . The inductive case uses the inductive hypothesis "assume

#### Figure 2.3: Square Root Proof[22]

function  $sqrt(x :: \mathbb{N})$  where  $x \ge 0$ returns  $z :: \mathbb{N} | (z^2 \le x \land x < (z+1)^2) \equiv$ if x = 0 then 0 else let z = sqrt(x-1) in if  $z^2 = x-1$  then z+1 else z

$\exists (z_{i-1} :: \mathbb{N}) \cdot z_{i-1} = sqrt(x-1)$ ". To prove the inductive case a case analysis is done on  $z_{i-1}$ . In the first case  $z_{i-1}^2 = x - 1$  and the witness  $z_{i-1} + 1$  can be supplied for  $z_i$  to discharge the proof. In the second case  $z_{i-1}^2 \neq x - 1$  and the witness  $z_{i-1}$  can be supplied for  $z_i$  to discharge the proof.

The complete specification with accompanying proof is shown syntactically in figure 2.3. It should be clear that a program could be extracted from the proof of the formal specification of *sqrt*. Research in the proofs as program domain focuses on the development of strong, constructive theorem proving languages and the extraction of efficient programs from these constructive proofs[22].

#### **Transformational Synthesis**

Transformational synthesis techniques typically view formal specifications as executable programs that are simply inefficient. Starting with these easily written but inefficient formal specifications, an efficient executable program is derived through the application of correctness preserving term rewriting rules. Efficiency is achieve by applying simplification and abstract data type removal, often at the expense of complicating the formal specification[26]. DEDALUS[30] is an example of a program synthesis tool in this area.

As an example, Manna and Waldinger[26] introduce a formal specification for the *lessall* predicate and give the derivation

#### Figure 2.4: Less-All Specification

function  $lessall(x :: \mathbb{N}, l :: List(\mathbb{N}))$  where true returns  $z :: Bool|z = all(\lambda i \mapsto x < i, l)$

of an efficient program. Figure 2.4 shows the same specification using the notion of a specification as a quadruple  $\langle D, R, I, O \rangle$ . This specification states that *lessall* is true only when the natural valued input *x* is less than all of the natural values in the input list *l*.

The DEDALUS[30] transformation system contains many generic rewrite rules allowing for things such as arithmetic simplification and case analysis. In addition to the generic rules, domain specific rewrite rules can be introduced. These rewrite rules could be considered axiomatic function definitions rather than operational function definitions. For instance, the following domain specific rewrite rules are used to transform this specification:

**Vacuous All Rule:** all(P,l) | (l = nil) = true**All Decomposition Rule:**  $all(P,l) | (l \neq nil) = P(head(l)) \land all(P,tail(l))$  The first transformation done to the *lessall* specification is to apply a case analysis rule over the input list *l* with the cases being l = nil and  $l \neq nil$ . This rule introduces a conditional into the specification transforming the body of the specification into *if* l = nil *then* all(P,nil) *else* all(P,l) where  $P = \lambda i \mapsto x < i$ .

At this point the vacuous rule can be applied to the then branch of the conditional and the decomposition rule can be applied to the else branch of the condi-

#### Figure 2.5: Less-All Program[26]

$\begin{array}{l} \mbox{function } lessall(x::\mathbb{N},l::List(\mathbb{N})) \mbox{ where } true \\ \mbox{returns } z::Bool|z=\mbox{if } l=nil \mbox{ then } true \\ \mbox{else } (x < head(l)) \wedge lessall(x,tail(l)) \end{array}$

tional. Application of these two rules produces *if* l = nil *then true else*  $P(head(l)) \land all(P,tail(l))$ . If the operations < and *head* are considered primitive then the expression P(head(l)) cannot be simplified any further. Thus, further transformation concentrates on the expression all(P,tail(l))

Noticing that all(P,tail(l)) is an instance of the original expression all(P,l) with a smaller list, a recursion introducing rule can be applied to transform the expression all(P,tail(l)) into simplified expression lessall(x,tail(l)). The final program representation for the *lessall* specification is shown in figure 2.5. This program representation implements the original specification of *lessall* correctly and efficiently.

#### **Knowledge Based Program Synthesis**

Knowledge based program synthesis focuses on program synthesis as a development process requiring intimate knowledge of both software engineering and of the specification's engineering domain. Typically, knowledge based program synthesis tools provide formally defined, generic synthesis strategies that automatically construct algorithms via analysis of the specification. These algorithms can then be made more efficient though the application of optimizing transformations. The Kestrel Interactive Development System (KIDS) is representative of this category of program synthesis tools[32]. A modern, commercially supported descendent of KIDS is available in the form of SpecWare[28]. Consider the abstracted specification given in figure 2.1. In the KIDS nomenclature, this specification defines a problem F with a domain of D and a range of R. The expression *Body* of the problem F may be omitted if the problem specification is abstract. If the expression is present, however, it defines how solutions to the problem F can be computed from the inputs. The input condition I and the output condition O can be considered constraints over valid inputs and constraints over valid solutions for a given input. In effect, I and O allow tighter input and output constraints for a problem specification than the implicit input and output constraints due to the problem's domain and range types.

From this definition, KIDS provides interactive support for automatic derivation of correct and efficient programs. To accomplish this a KIDS users typically goes through six steps, though the steps are not prescribed by the KIDS tool[31]. First, the user will develop a domain theory that describes the relevant concepts, operations, relationships, and properties of the problem that is being solved. Domain theories are constructed in KIDS by importing existing domain theories and then adding additional type definitions, function specifications, laws, and rules of inference.

Second, a problem specification will be created that uses the definitions provided by the domain to describe solutions to a specific problem. The problem specification is provided in the form shown in figure 2.1. The initial problem specification omits the expression Body with valid solutions specified solely via the output constraints O. Then a design tactic us applied to the problem specification to create an initial operational definition (i.e. the design tactic provides an initial definition of Body). KIDS' design tactics are generalized problem solving algorithms such as divide-and-conquer, local search, or global search. These generalized algorithms are then specialized, using the KIDS tools, to solve a particular problem.

For example, a KIDS user may decide that global search is a good algorithm for solving their problem. To provide the initial operation definition for their problem *F* the user would:

1. Select a global search theory  $G_b$  from a library of existing general global search theories such that  $G_b$  enumerates all possible values for the range of F. Because  $G_b$  enumerates all values in the range of F we can be sure that solutions to F as defined by O are in the set of values enumerated by  $G_b$ .

- 2. Produce a specialized global search theory  $G_f$  from the global search theory  $G_b$  with respect to the problem specification F by finding a mapping  $\theta$  that maps inputs x of problem F into inputs  $\theta(x)$  of  $G_b$  such that  $\forall (z :: R_f) . O_f(x, z) => O_b(\theta(x), z)$ . This mapping can be determined automatically by the KIDS tools.

- 3. Derive a *necessary filter* to prune the search space of invalid partial solutions and use it to create a global search program *Body*. This provides the initial operational definition for the problem specification *F*.

The initial operational definition formed during these first three steps is a correct behavioral description of the specification, however, the definition is typically far from efficient. To complete the process of generating a correct and efficient executable from the specification, the user would:

- 4. Apply optimizations to the initial operational definition of the problem *F* to create a more efficient operational definition. During this step the KIDS user manually identifies expressions within the operational definition of *F* and then applies optimizations to those expressions. The optimizations are performance automatically by KIDS and include operations such as simplification, partial evaluation / specialization, finite differencing, and case analysis[31].

- 5. Apply data type refinement to the operational definition to eliminate abstract data types. The abstract data types are replaced with specialized representations that efficiently represent the data used by the operational definition. It is important to note that the elimination of abstract data types respects the correctness properties of that data type. For example, when replacing a set with a list representation the transformation must ensure that an element does not appear in the list twice.

- 6. Compile the operational definition of the problem specification into an executable that will compute solutions to the problem when given inputs.

After completing these six steps, the KIDS users has automatically derived a correct and efficient executable representation of their specification.

#### **Comparison to Proposed Work**

Program synthesis tools, are related to this work in the sense they all desire to produce efficient program representations from high-level, difficult to synthesize specifications. Each of the categories of program synthesis also have some notion of how engineers interact with the program synthesis tool to achieve the desired results. In the proofs as programs category, engineers interact with the program synthesis tool via the creation of a proof where the choice of a particular proof construct will influence the eventual outcome. Tools in the transformational synthesis category vary on the level of engineer interaction with some tools being highly automated and other tools being mainly engineer driven[9]. Knowledge based transformation systems try to strike a balance by giving engineers control over the application and composition of transformations that are then mechanically applied.

Another relation between all program synthesis tools is that program transformations are describe either formally or semi-formally so that the result of applying the transformation is wellknown to the engineer. The transformations supplied by this work are not formally defined but the intention is that the result of applying the transformations is well-known. Formalizing the transformations is left as future work.

The main difference between this work and existing program synthesis tools is the scope of the transformations that are provided. Existing program synthesis tools aim to produced a single, efficient, software implementation from abstract specifications. This work is concerned primarily with providing a rapid-prototyping capability that is capable of iteratively refining abstract specifications into one of many low-level, hardware/software co-designed implementations.

## 2.4 Approaches to System-Level Design

There are many existing tools and techniques for performing system-level design. Generally, these tools and techniques fall into one of two categories. First, some tools ease system-level design by generating hardware components from high-level programming languages. Tools such as Catapult C[15], Handle-C[16], and SPARK[20] generate circuits from algorithmic descriptions written in languages like C, C++, or SystemC[19]. BlueSpec[3] and Kansas Lava[13] take the abstraction levels used to implement hardware circuits even higher by leveraging functional programming techniques to describe circuit elements.

As an example, Kansas Lava is capable of producing hardware circuits from descriptions written in a domain specific language that is hosted in Haskell. During this process the system engineer describes functional behavior and communication using highly abstract constructs, manually refines behavior using worker/wrapper[14] transformations, and then produces a VHDL implementation using the Kansas Lava tools. The end result is a hardware system that implements the described functional behavior.

Compared to these tools, this work supports HW/SW co-designed implementations and rapid prototyping. Support for HW/SW co-design means that this work is capable taking a high level system specification and generating a system implementation composed of interacting hardware and software components. The tools described previously only support generation of hardware systems. To support rapid prototyping, a tool must allow rapid generation of many system implementations from a single system description. This work achieves this by separating high level functional behavior from low level implementation details. When using the tools described previously, functional behavior and implementation details are intermingled, making it difficult to produce different implementations from a single description.

The second category of tools generate HW/SW co-designed system implementations from a single source language. SpecC[10] and Impulse C[33] support HW/SW co-design of systems by synthesizing hardware circuits and software instruction streams from ANSI-C like languages while Kiwi[17] is capable of generating HW/SW system by analyzing .NET C# programs.

As an example, Kiwi is capable of producing HW/SW system implementations from descriptions written in C# and compiled to the .NET virtual machine. During this process, a C# program is written to describe a system's functional behavior and communication and then compiled to the .NET virtual machine. Partitioning of this C# program's instruction stream is then done, with some components partitioned onto Xilinx FPGAs for implementation and other components left on the .NET virtual machine. Integration of the hardware and software components into a complete system implementation is done by connecting the components using some form of physical communications link, Ethernet switches being one example.

The main difference between this work and the second class of tools is that this work provides better support for rapid prototyping and design space exploration by separating high level functional behavior and low level implementation details. In this work, a system's implementation is derived from its behavioral specification by adding implementation details in the form of easily changed, declarative, system-level refinements. Different implementations can be generated rapidly by changing the refinements used to derive the implementation. The second class of tools conflate the behavioral specification of a system and the implementation of that system. Because of this, changes in a system's implementation must be achieved by changing the system's described behavior, making it difficult to rapidly generate different implementations.

15

Page left intentionally blank.

# **3** The Rosetta Specification Language

Modern system design is increasingly complex and makes use of heterogeneous models of computation so that individual components in a system can be designed and implemented in the most appropriate domain Additionally, modeling an understanding system-level properties, such as security or power consumption, is increasingly important. The Rosetta[1, 2] system-level design language is designed to meet the needs of modern system engineers. It places special emphasis on support for multi-domain modeling to support heterogeneous models of computation and allows the precise, formal expression of requirements in ways that are natural to the domain. Additionally, system-level properties can be expressed succinctly using behavior composition that is a core feature of the language.

## 3.1 Domains

The specification, design, and implementation of modern systems requires expertise in a wide variety of engineering and scientific domains. Consider for example, a modern mobile phone. Even the most basic modern mobile phone requires many components:

- 1. ADC and DAC Conversion from and to analog representation.

- 2. DSP and CPU Computation including processing of audio and video data.

- 3. RF, Bluetooth, and WiFi Wireless communication using analog signals.

- 4. LCD Video display and user interface.

- 5. Battery Power for all of the components in the mobile device.

Expertise in many domains is needed to support all of these components. Expertise in analog signals, analog circuitry, digital signals, and digital circuitry is needed for the requirements modeling, specification, design, and implementation of most of the components. Expertise in electrical power sub-systems is required if the mobile device is to meet its power requirements. Expertise in networking is needed so that the device can communicate using its wireless communications components. Expertise in audio and video processing is required to support voice communications and audio/visual media. Expertise in wireless communications is needed to support the analog transmission and reception of signals. Additionally, expertise in computer security is needed to ensure a reasonable standard of privacy on behalf of the user. Even this

long list is not exhaustive because the amount of expertise needed is vast due to the number of system domains covered by the components in the device.

Modern systems necessitate support for the multi-domain requirements modeling, system specification, design, and implementation. At the design and implementation level this has traditionally been done by providing separate tools that target one specific domain. Integration of the separately designed and implemented components is normally done by hand in a separate, ad-hoc integration phase. This works well enough for many products, as evidenced by the number of complex yet working systems on the market, but recomposition of components during the integration phase can have a significant time and cost impact.

Using separate tools for requirements modeling and system specification is difficult to the point of being infeasible because of the complex interactions among different components in the system. For example, when modeling power requirements in a system the power usage of one component will affect the power usage and/or requirements of another component. Modeling the requirements using separate tools and integrating them by hand would quickly become too burdensome.

Rosetta proposes a solution to the problem by directly exposing multi-domain support in a single language. This has not been done traditionally because each domain uses different vocabulary for expressing requirements and constraints, a different model of computation, and different abstractions. For instance, requirements and constraints in the power domain would be expressed using terms such as *volt*, *current*, *ampere*, and *watt*, whereas terms such as *cy-cles*, *register*, *mux*, and *bit* would be used in the digital circuits domain.

Rosetta provides support for multiple engineering domains by allowing vocabularies, models of computation, and abstractions to be defined inside of the Rosetta language in the form of a Rosetta domain. Domains are hierarchical in natural in that one domain can inherit the vocabulary, model of computation, and abstractions provided by another domain and extend or constrain them as appropriate. System components are constructed using the vocabularies, models of computation, and abstractions provided by the component's domains. Additionally, Rosetta allows engineers to express how different domains interact with one another so that system-level properties can be understood across domain boundaries.

### 3.2 Facets

Rosetta facets build upon Rosetta domains to describe one model in a system of models. The facet is expressed using the vocabulary, model of computation, and abstractions provided by the domain. For instance, a behavioral model of a JK flip-flop could be constructed in the *state based* Rosetta domain by expressing the next state, Q', of the JK flip-flop in terms of its current input bits *J* and *K* and its current state, *Q*:

$$Q' = (J \text{ and } (\text{not } Q)) \text{ or } (K \text{ and } Q)$$

In this definition the model of computation, the notion of *current state, next state, bit*, and the behavior of the *and*, *or*, and *not* operations are defined by the domain *state based*. We could just as easily provide a power model of the JK flip-flop:

$$P' = P + (\text{if } (J \text{ or } K) \text{ then } switch \text{ else } leak \text{ endif})$$

Likewise, *switch* and *leak* might be definitions that come from a power domain modeled in Rosetta. Their definitions could come from either a simple, generic model of power or from a more complex model of power that takes into account some fabric implementation technology, for instance 45*nm* CMOS. The simple, generic model would be faster to construct and could be used during the initial requirements and specification phases to get coarse grained estimates on power usage in the system while the more complex 45 *nm* model could be used once a more complete model has been produced to provide tighter bounds on the power consumption estimate.

Each different facet expresses some model of the component using the vocabulary, model of computation, and abstractions that are most convenient when developing that model. A final model of the component can then be created by composing the individual facets together to provide a new model using the compositional features of the Rosetta language.

Facet definitions permit both requirements modeling and specification of functional and nonfunctional properties. In addition, facets requiring pre-conditions and implications can be expressed using an extension of facets known as components.

## 3.3 Requirements Modeling and Specification

Inside Rosetta facets, requirements modeling and specification development is done using a rich expression language. This expression language is similar to most programming languages in that it supports primitive operations and values with which additional constructs can be derived using the available methods of composition. Unlike most programming languages, Rosetta is declarative. Models in declarative languages are defined by equations, in contrast to imperative programming languages where models are constructed by algorithms. Because of this, Rosetta, like most requirements modeling and specification languages, deviates from programming languages in two important aspects. First, expressions in the Rosetta language are used to represent properties of the system. This is in contrast to traditional programming language where expressions are used to represent computations. The distinction here can be subtle, as in listing 3.1, or obvious, as in listing 3.2.

In listing 3.1 there are two expressions with the first representing a property constraint in a system and the second representing a computation in a system. The first expression is stating that if x is equal to one in the current state then y is equal to one in the next state otherwise y is equal to zero in the next state. The second expression is stating

Listing 3.1: Subtle Difference

| 1 (1) | <b>if</b> x == 1   |

|-------|--------------------|

| 2     | <b>then</b> y' = 1 |

| 3     | <b>else</b> y' = 0 |

| 4     | end if             |

| 5     |                    |

| 6 (2) | <b>if</b> x == 1   |

| 7     | then $y = 1$       |

| 8     | <b>else</b> y = 0  |

| 9     | end if             |

that the storage location named *y* is updated to the value one if the storage location named *x* contains the value one otherwise *y* is updated to the value zero. The difference is subtle because the computation that updates *y* is effectively forming a new state in a way that is entirely consistent with the system properties stated in the first expression.

Listing 3.2 shows a more obvious distinction between expressing properties and expressing computation. The first expression in this example states that if *command* is not equal to *NOTHING* then the next state of the system is one of two different states, either *READING* or *WRITING*. The second equation is instead expressing a computation that computes a single next state by combining the data representation of *READING* with the data representation of *WRITING* using the *or* operator. More than likely the computation represents an invalid next state assignment whereas the expressed property is completely valid.

The second major deviation is a by-product of the first: expressions in Rosetta may be underspecified. Underspecification, in the context of requirements modeling and system specification, means that some details are omitted from the specification because they are deemed unimportant by the engineer. An engineer may even completely un-

```

1 (1) if command != NOTHING

then state' = READING or

2

state' = WRITING

3

else state' = IDLE

4

end if

5

(2) if command != NOTHING

then state = READING or

8

WRITING

9

10

else state = IDLE

end if

11

```

derspecify something to express the notion that they are only interested in the existence of something and are uninterested in any of its properties. In most cases underspecification is used so that system properties can be expressed axiomatically rather than definitionally.

Consider, for example, the specification given in listing 3.3. This specification defines the function *sin* but does not give a definition of how to compute the output of *sin* from its

#### Listing 3.3: Underspecification

input *value*. Instead the specification simply constrains the range of the function *sin* to be between -1.0 and 1.0 using a declarative axiom.

Underspecification can be seen as a double edged sword. It is useful because complex specification logic can be reserved for the parts of system model that are unknown and must be explored. The parts of the model that are well known and have established behaviors can be underspecified and their behaviors can be encoded axiomatically. However, if important parts of a model are left underspecified, then model exploration can be unintentionally constrained and important system properties may be missed or misunderstood. This is because engineers rarely understand complex systems in enough detail a-priori to known which parts of the system are well known, especially because interactions among different models are complex and not well defined.

Currently, engineers deal with this a-priori knowledge problem using manual specification refinement. A highly underspecified system is initially created and used to gain more insight into the problem. This additional knowledge is used to refine the original specification by removing some of the underspecification to gain more insight in to the problem. This process is repeated until the engineer finds that the model describes the system at the correct level of detail.

## **4** Synthesis of Rosetta Specifications

The system-level design tools developed in this work proceed through several steps during the refinement of high-level Rosetta specifications into low-level hardware/software co-design implementations. First, complex data-types, abstract communication, and functional behaviors are refined into lower level representations. Second, a specification's top-level design is partitioned and mapped to resources at the implementation level. Finally, each partition in the design is synthesized to either hardware circuits via VHDL or software programs via LLVM.

The goal of the low-level synthesis support is to be as close as possible to the eventual target implementation (either VHDL or LLVM). There are two major reasons for having this goal. First, having the directly synthesizable subset close to the implementation target means that an engineer can accurately predict the performance and area consumption of the low-level specification. This is important for a system-level design tool as the turn around time for pushing an implementation into a form that can be loaded into a physical system is much longer than for simple software programs. As such, system engineers want to know what the results will be like before this process begins. Second, being close to the implementation target eases the implementation of the synthesis engine, helping ensure that the implementation of the synthesis engine is free of bugs.

There are several implications of the close proximity between the synthesizable subset and the synthesis target. First, there are relatively few types and expressions in a specification language like Rosetta that are directly synthesizable to low-level hardware or software implementations. The purpose of the first two refinement steps is to ease this restriction, allowing a much richer set of Rosetta constructs to be synthesized.

Second, the subset of Rosetta that is synthesizable to hardware via VHDL is different than the subset of Rosetta that is synthesizable to software via LLVM. One reason for this is that we want to support all of the low-level constructs in the synthesis target in some form at the Rosetta specification level. This ensures that system engineers are not artificially constrained at the specification level and can achieve the desired implementation even if it means that they must manually refine the specification. It is important to allow manual refinement as it is infeasible for the refinement system to support all possible refinements that the system engineer may want to perform.

Another reason that the synthesizable subset differs between hardware and software targets is that we do not want to force abstractions on the system engineer or impose a model-ofcomputation before the design process begins. If the synthesizable subset for both hardware and software targets were the same then there would necessarily be abstractions or models-ofcomputation in one or both targets that would not be present in the underlying implementation fabric. This is because the underlying model-of-computation for hardware and software components are vastly different. Software models-of-computation are inherently sequential because microprocessors force sequential execution of instructions while hardware models-ofcomputation are inherently parallel because current flows through all elements of the circuit at the same time. Forcing hardware to be sequential or software to be parallel would require the introduction of abstractions beyond the control of the engineer and beyond the ability of synthesis tools to eliminate efficiently.

Furthermore, allowing the synthesizable subsets to differ is precisely what allows this work's synthesis tool to be used efficiently and effectively for hardware/software co-design. Hard-ware/software co-design is an activity in optimizing system efficiency by leveraging the unique capabilities of software resources and hardware resources. In effect, by partitioning a system intelligently, we can gain all of the advantages of hardware over software or software over hardware while mitigating or eliminating the disadvantages. By doing so we gain system efficiency that would not be possible using exclusively software or exclusively hardware solutions.

### 4.1 Synthesizable Hardware Components

The Rosetta Synthesis Tool (RST) synthesizes Rosetta facets into hardware circuits via VHDL in four phases. First, the synthesizable Rosetta specification is lowered into an intermediate representation in register-transfer level form. Second, the intermediate form is converted into an explicit graph representation. Third, the graph representation of the circuit is optimized

| Rosetta Type | VHDL Type                                 |

|--------------|-------------------------------------------|

| bit          | <pre>std_logic</pre>                      |

| word( $W$ )  | <pre>std_logic_vector(W-1 downto 0)</pre> |

| integer      | <pre>std_logic or std_logic_vector</pre>  |

| array(W,D)   | array( $D$ -1 downto 0) of                |

|              | <pre>std_logic_vector(W-1 downto 0)</pre> |

Table 4.1: Supported Types

and inferencing is done to discover high-level circuit constructs. Fourth, the graph representation is transformed into VHDL code.

The first step in this process, producing an RTL intermediate form, requires that the input specification already be in hardware synthesizable form. To be in this form, the synthesizable specification must only use the types given in table 4.1. This table lists the Rosetta types that are supported by the hardware synthesis process and gives the VHDL types used for their implementation.

The lowering of Rosetta types into VHDL types is extremely simple with bit and word(W) representing bits and bit-vectors at the circuit level. The array(W,D) Rosetta type is lowered into the VHDL array type. These three type transformations, though simple, are all that is needed to support all implementation level constructs for hardware circuits: wires, registers, logic gates, RAMs, and ROMs. The hardware synthesis transformation supports one additional type, integer. This Rosetta type is used to support the notion of an elastic width bit-vector. The exact width of these bit-vectors is determined automatically during the synthesis process, as discussed in section 4.1.2. The notion of elastic sizes could be extended to other types as well, if additional flexibility is required in the synthesis process.

| Table 4.2: Supported Modes |           |

|----------------------------|-----------|

| Docotto Modo               | VIDI Mode |

| Rosetta Mode | VHDL Mode |

|--------------|-----------|

| design       | generic   |

| input        | in        |

| output       | out       |

|              | inout     |

All Rosetta facets in the synthesizable specification must meet certain requirements. First, the domain must be one of static, state\_based, resource, memory, target, bridge, or system. The domains re-

source, memory, target, bridge, and system are used to describe the top-level system design and the resources instantiated within. They are discussed further in section 5. The domains static and state\_based are used to represent functional behavior in Rosetta specifications. These two domains are the only supported domains because they neatly capture the two different types of circuits at the implementation level. The static domain is used to describe stateless behavior. Stateless behaviors compute their output solely based on their current input, capturing the notion of combinational circuits. Comparatively, the state\_based domain allows the description of stateful behavior and captures the notion of sequential circuits. RST ensures that any specification being synthesized meets the requirements on the domain but it performs no correctness checks. In particular, it assumes that the Rosetta type checking capability assures static and state\_based facets meet their definitions according to the Rosetta language definition.

In addition to the domain requirements, all synthesizable Rosetta facets must only make use of the parameter modes given in figure 4.2. Like the transformation of Rosetta types into VHDL types, the transformation of Rosetta parameter modes into VHDL parameter modes is straight-forward. Rosetta design parameters become VHDL generics, Rosetta input parameters become VHDL in parameters, Rosetta output parameters become VHDL out parameters, and Rosetta parameters with no explicit mode become VHDL inout parameters. The types of these parameters must be one of the types given earlier with one exception, design parameters

**Table 4.3: Supported Expressions**

| var | : | Rosetta variable                    |

|-----|---|-------------------------------------|

| lit | : | [09]*   bottom                      |

| seq | : | b" (0 1)* "                         |

|     |   | o" [07]* "                          |

|     |   | x" [AF,09]* "                       |

| pre | : | %   not                             |

| inf | : | +   -   *   /   &   =               |