# A LINEARIZATION METHOD FOR A UWB VCO-BASED CHIRP GENERATOR USING DUAL COMPENSATION

BY

Daniel Gomez Garcia Alvestegui

Submitted to the graduate degree program in Electrical Engineering and the Graduate Faculty of the University of Kansas in partial fulfillment of the requirements for the degree of Master of Science.

Chairperson: Dr. Carl Leuschen

Dr. Fernando Rodriguez-Morales

Dr. Sivaprasad Gogineni

Date Defended: November 9<sup>th</sup>, 2011

The Thesis Committee for Daniel Gomez Garcia Alvestegui certifies that this is the approved version of the following thesis:

# A LINEARIZATION METHOD FOR A UWB VCO-BASED CHIRP GENERATOR USING DUAL COMPENSATION

Chairperson: Dr. Carl Leuschen

Dr. Fernando Rodriguez-Morales

Dr. Sivaprasad Gogineni

Date approved: \_\_\_\_\_

## ABSTRACT

Ultra-Wideband (UWB) chirp generators are used on Frequency Modulated Continuous Wave (FMCW) radar systems for high-resolution and high-accuracy range measurements. At the Center for Remote Sensing of Ice Sheets (CReSIS), we have developed two UWB radar sensors for high resolution measurements of surface elevation and snow cover over Greenland and Antarctica. These radar systems are routinely operated from both surface and airborne platforms. Low cost implementations of UWB chirp generators are possible using an UWB Voltage Controlled Oscillator (VCO). VCOs possess several advantages over other competing technologies, but their frequency-voltage tuning characteristics are inherently non-linear. This nonlinear relationship between the tuning voltage and the output frequency should be corrected with a linearization system to implement a linear frequency modulated (LFM) waveform, also known as a chirp. If the waveform is not properly linearized, undesired additional frequency modulation is found in the waveform. This additional frequency modulation results in undesired sidebands at the frequency spectrum of the Intermediate Frequency (IF) stage of the FMCW radar. Since the spectrum of the filtered IF stage represents the measured range, the uncorrected nonlinear behavior of the VCO will cause a degradation of the range sensing performance of a FMCW radar. This issue is intensified as the chirp rate and nominal range of the target increase.

A linearization method has been developed to linearize the output of a VCO-based chirp generator with 6 GHz of bandwidth. The linearization system is composed of a Phase Lock Loop (PLL) and an external compensation added to the loop. The nonlinear behavior of the VCO was treated as added disturbances to the loop, and a wide loop bandwidth PLL was designed for wideband compensation of these disturbances. Moreover, the PLL requires a loop filter able to attenuate the reference spurs. The PLL has been designed with a loop bandwidth as wide as possible while maintaining the reference spur level below 35 dBc. Several design considerations were made for the large loop bandwidth design. Furthermore, the large variations in the tuning sensitivity of the oscillator forced a design with a large phase margin at the average tuning sensitivity. This design constraint degraded the tracking performance of the PLL. A second compensation signal, externally generated, was added to the compensation signal of the PLL. By adding a compensation signal, which was not affected by the frequency response effects of the loop compensation, the loop tracking error is reduced. This technique enabled us to produce an output chirp signal that is a much closer replica of the scaled version of the reference signal. Furthermore, a type 1 PLL was chosen for improved transient response, compared to that of the type 2 PLL. This type of PLL requires an external compensation to obtain a finite steady state error when applying a frequency ramp to the input. The external compensation signal required to solve this issue was included in the second compensation signal mentioned above.

Measurements for the PLL performance and the chirp generator performance were performed in the laboratory using a radar demonstrator. The experimental results show that the designed loop bandwidth was successfully achieved without significantly increasing the spurious signal level. The chirp generator measurements show a direct relationship between the bandwidth of the external compensation and the range resolution performance.

# ACKNOWLEDGMENTS

This investigation was possible thanks to the Center for Remote Sensing of Ice Sheets at the University of Kansas and its great mission.

All the members of the thesis committee have been instrumental in the successful development of this research project.

First, I would like to thank Dr. Gogineni for giving me the opportunity to work on this research project and other projects that gave me invaluable experience.

I also would like to thank Dr. Leuschen for guiding me and always suggesting thoughtful ideas. As my adviser, Dr. Leuschen has provided me with knowledge about RF and digital systems that have helped me with this investigation.

I am also very thankful to Dr. Rodriguez for all the guidance throughout this research project. Dr. Rodriguez has spent countless hours explaining me concepts and teaching me about hardware implementation.

I would like to thank Reid for teaching me how to run the milling machine. This has made a huge difference in the progress I made. I thank Ben for explaining me how FMCW radars work and Kevin for all the suggestions on PCB layouts. I also would like to thank Jenna Collins for editing this document.

# **TABLE OF CONTENTS**

| ABSTRACT                                                  | iii  |

|-----------------------------------------------------------|------|

| ACKNOWLEDGMENTS                                           | V    |

| TABLE OF CONTENTS                                         | vi   |

| LIST OF FIGURES                                           | viii |

| LIST OF TABLES                                            | xi   |

| CHAPTER 1: INTRODUCTION                                   |      |

| 1.1 SCIENCE BACKGROUND                                    | 1    |

| 1.1.1 Laser Altimeters                                    |      |

| 1.1.2 Radar altimeters                                    | 2    |

| 1.2 CRESIS UWB RADARS                                     | 2    |

| 1.3 THESIS OUTLINE                                        |      |

| CHAPTER 2: BACKGROUND                                     | 4    |

| 2.1 UWB FMCW RADAR BACKGROUND                             | 4    |

| 2.1.1 Radar Overview                                      | 4    |

| 2.1.2 FMCW Waveform Quality                               |      |

| 2.1.3 FMCW Waveform Generation and Frequency Synthesizers |      |

| 2.2 PHASE LOCK LOOP OVERVIEW                              |      |

| 2.2.1 PLL Analysis as a Linear System                     |      |

| 2.2.2 PLL Components Overview                             |      |

| 2.3 LOOP TRACKING ERROR REDUCTION TECHNIQUES              |      |

| CHAPTER 3: DESIGN AND IMPLEMENTATION                      | 53   |

| 3.1 CHIRP GENERATOR DESIGN REQUIREMENTS                   | 53   |

| 3.2 PROPOSED LINEARIZATION TECHNIQUE                      |      |

| 3.3 UWB VCO: HMC733                                       | 55   |

| 3.4 PLL DESIGN                                            | 61   |

| 3.4.1 PLL Design Requirements and Considerations          | 61   |

| 3.4.2 Reference Frequency and Divider Selection         |

|---------------------------------------------------------|

| 3.4.3 Phase Frequency Detector Selection                |

| 3.4.4 Differential Amplifier Design                     |

| 3.4.5 Adder Design                                      |

| 3.4.6 Loop Filter Design71                              |

| 3.4.7 PLL Circuit Implementation                        |

| 3.5 PRE-DISTORTED VOLTAGE                               |

| 3.5.1 Pre-Distorted Waveform                            |

| 3.5.2 Level Shifter Amplifier Design and Implementation |

| 3.5.3 Start up Loop Filter Design and Implementation    |

| 3.5.4 Pre-Distorted Signal Generation Procedure         |

| CHAPTER 4: MEASUREMENTS AND RESULTS 101                 |

| 4.1 PHASE LOCK LOOP PERFORMANCE MEASUREMENTS            |

| 4.2 PRE-DISTORTED SIGNAL MEASUREMENTS 104               |

| 4.3 CHIRP GENERATOR MEASUREMENTS 111                    |

| CHAPTER 5: CONCLUSIONS AND FUTURE WORK 122              |

| REFERENCES                                              |

| APPENDIX A: 2-CHANNEL DDS BOARD130                      |

| APPENDIX B: PLL SPECTRAL MEASUREMENTS                   |

# LIST OF FIGURES

| Figure 2-1: Block Diagram of FMCW Radar7                                                          |

|---------------------------------------------------------------------------------------------------|

| Figure 2-2: a. FMCW Frequency Plots of Reference (Ref) and Received (Rx) signals for a            |

| stationary target. b. FMCW beat frequency (fb) resulting from the difference of the reference and |

| receive signal frequencies                                                                        |

| Figure 2-3: Frequency of Reference and Receive Signals for similar triangle analysis to           |

| determine the beat frequency                                                                      |

| Figure 2-4: Example of a Chirp Waveform with no amplitude modulation                              |

| Figure 2-5: Example of a Chirp Waveform with amplitude modulation                                 |

| Figure 2-6: Simulation Plot for the Effects on the video signal caused by amplitude modulation    |

| on the chirp waveform                                                                             |

| Figure 2-7: Simulation Plot for the Effects on the video signal caused by amplitude modulation    |

| on the chirp waveform using a Hanning Weighting 17                                                |

| Figure 2-8: Root Mean Squared of The Phase Modulation Function                                    |

| Figure 2-9: Video Signal Frequency Spectrum for Case 1                                            |

| Figure 2-10: Video Signal Frequency Spectrum for Case 2                                           |

| Figure 2-11: Video Signal Frequency Spectrum for Case 2 with Windowing for Sidelobe               |

| Suppression                                                                                       |

| Figure 2-12: Video Signal Frequency Spectrum for Case 3                                           |

| Figure 2-13: Block Diagram of PLL Transfer Function                                               |

| Figure 2-14: Simple Control System Block Diagram Showing Error Signal                             |

| Figure 2-15: Control Loop with Added Signal for Type 1 Steady State Error Improvement 35          |

| Figure 2-16: Tuning Curve of a Voltage Controlled Oscillator                                      |

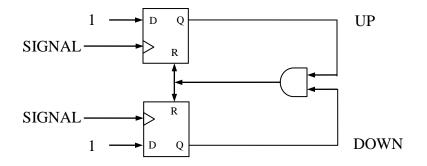

| Figure 2-17: Phase Frequency Detector Typical Digital Circuit                                     |

| Figure 2-18: a. Phase Frequency Detector Waveforms for the two Cases: a. Phase Difference         |

| Only. b. Phase and Frequency Difference                                                           |

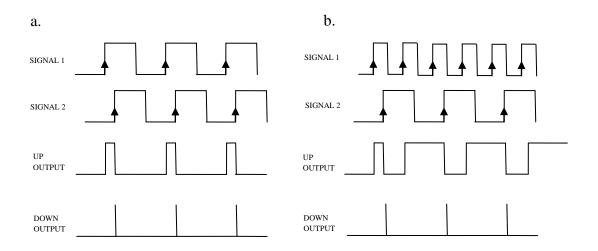

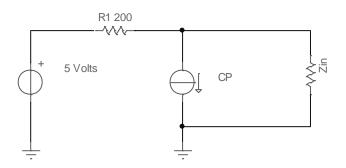

| Figure 2-19: Charge Pump Circuits for UP and DOWN outputs                                         |

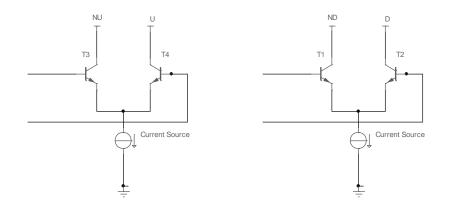

| Figure 2-20: Phase Frequency Detector Output using Integrator                                     |

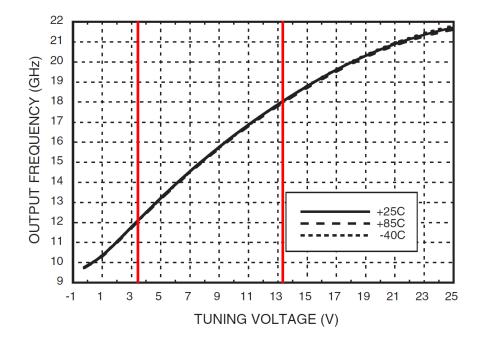

| Figure 2-21: Example Bode Plots for a Type 2 Loop Filter Transfer Function                        |

| Figure 2-22: Example Bode Plots for an Uncompensated PLL Open Loop Transfer Function47            |

| Figure 2-23: Example Bode Plots for a Compensated PLL Open Loop Transfer Function 48              |

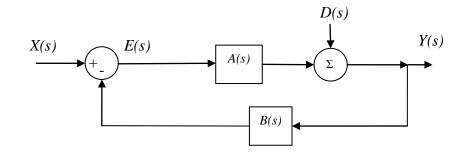

| Figure 2-24: Closed Loop System Block Diagram with Added Disturbances                             |

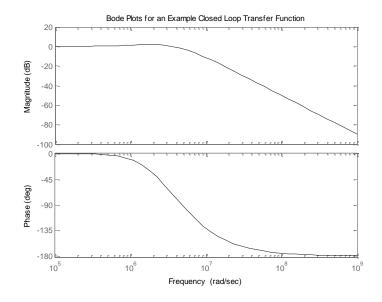

| Figure 2-25: Bode Diagram of an Example Closed Loop Transfer Function for a PLL 50                |

| Figure 2-26: Example of a Closed Loop Control System Block Diagram with Disturbance and           |

| External Compensation                                                                             |

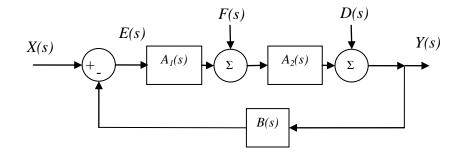

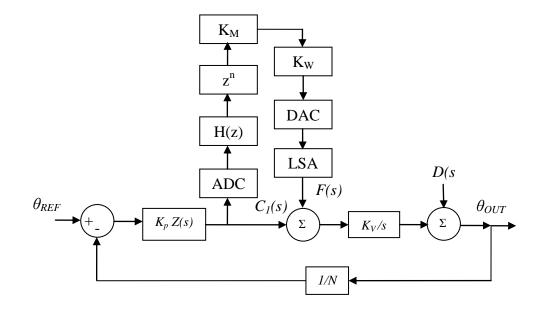

| Figure 3-1: VCO Based Chirp Generator Dual Compensation System                                    |

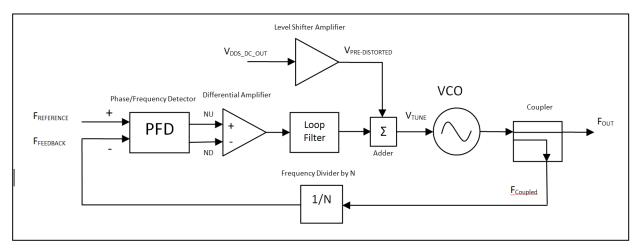

| Figure 3-2: Typical Tuning Curve for the HMC733 VCO [41]                                          |

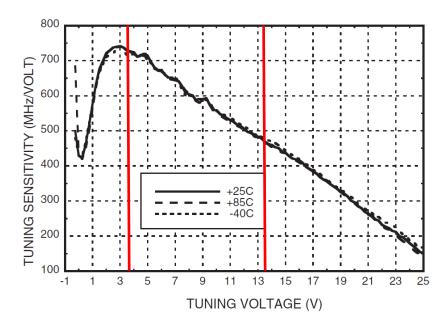

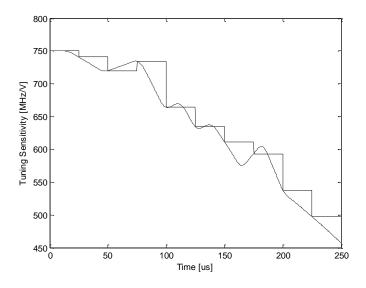

| Figure 3-3: Typical Tuning Sensitivity Curve for the HMC733 VCO [41]                        | 57      |

|---------------------------------------------------------------------------------------------|---------|

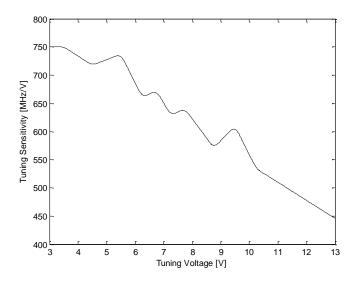

| Figure 3-4: Tuning Sensitivity Curve                                                        | 57      |

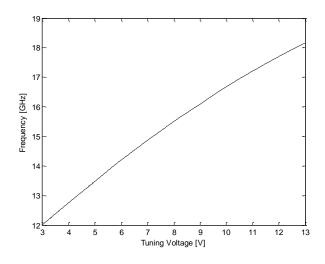

| Figure 3-5: Tuning Curve Generated from Sensitivity                                         | 58      |

| Figure 3-6: Tuning Voltage Required To Linearize the Tuning Curve given by the HM           | AC733   |

| Datasheet                                                                                   | 58      |

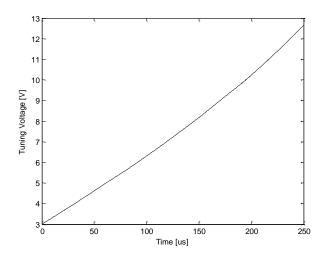

| Figure 3-7: Voltage Rate of Change over Time Plot                                           | 59      |

| Figure 3-8: Tuning Sensitivity over the Expected Sweep Time                                 | 60      |

| Figure 3-9: PLL Block Diagram with Added Disturbance                                        | 61      |

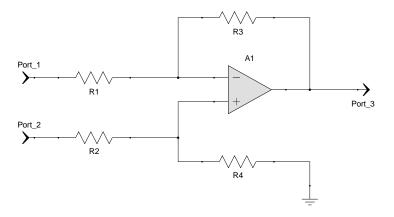

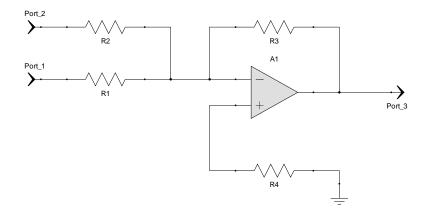

| Figure 3-10: Schematic Circuit for a Differential Amplifier Circuit                         | 64      |

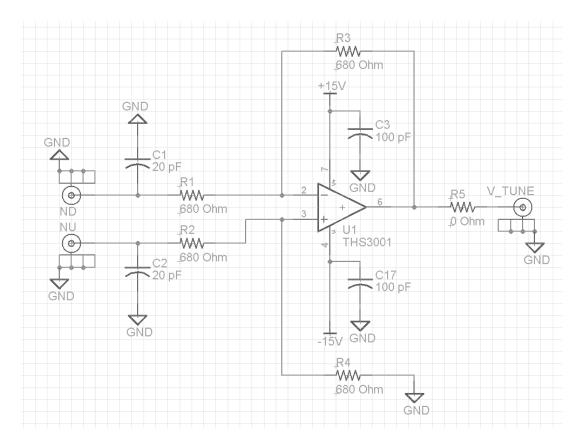

| Figure 3-11: Schematic Circuit of the Differential Amplifier                                | 67      |

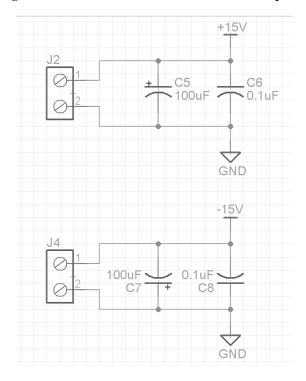

| Figure 3-12: Differential Amplifier Power Supply Capacitor Bank                             | 67      |

| Figure 3-13: Equivalent Phase Detector Output and Differential Amplifier Input Impedance    | e69     |

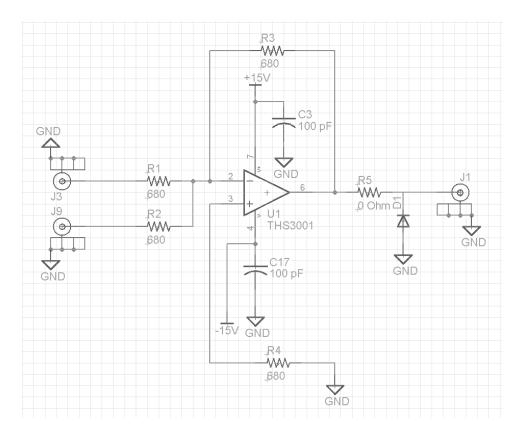

| Figure 3-14: Basic Circuit Schematic for an Inverting Adder Amplifier                       | 70      |

| Figure 3-15: Circuit Schematic of the Adder                                                 | 71      |

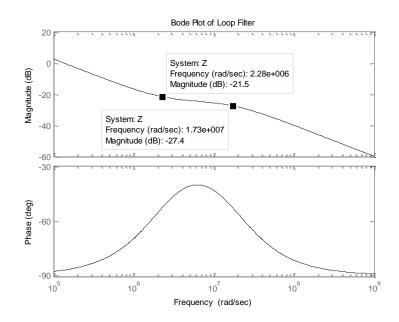

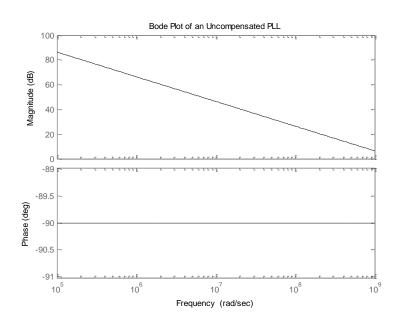

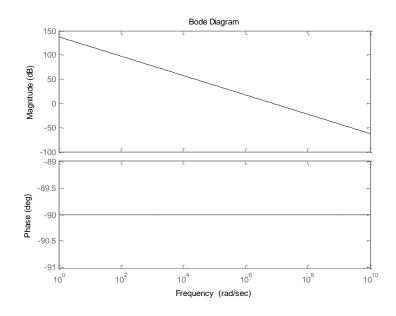

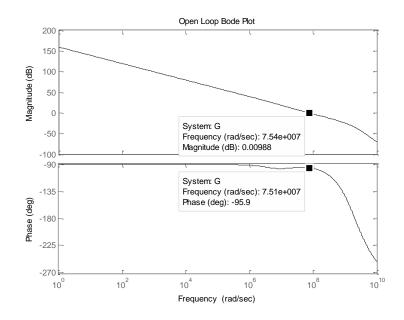

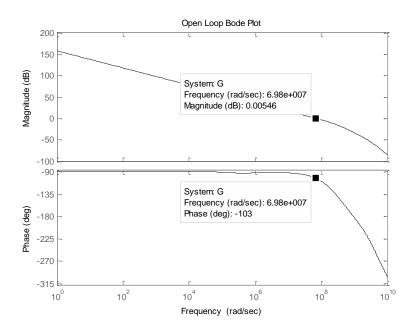

| Figure 3-16: Simulated Uncompensated Open Loop Transfer Function                            | 72      |

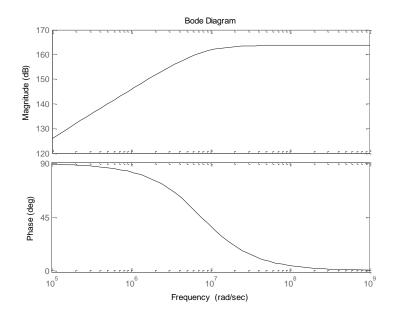

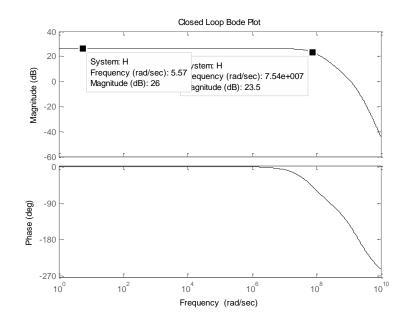

| Figure 3-17: Simulated Bode Plots for the Closed Loop Transfer Function of the Uncompe      | ensated |

| PLL                                                                                         | 73      |

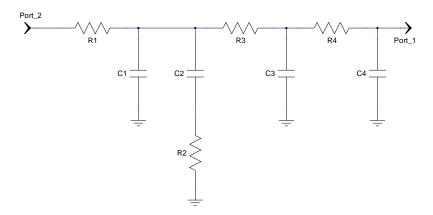

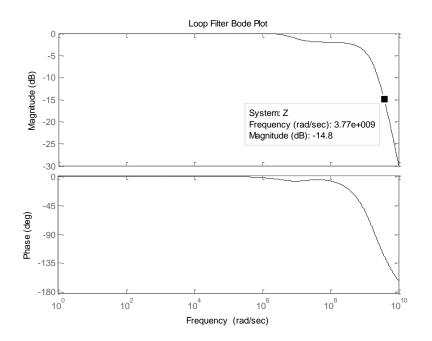

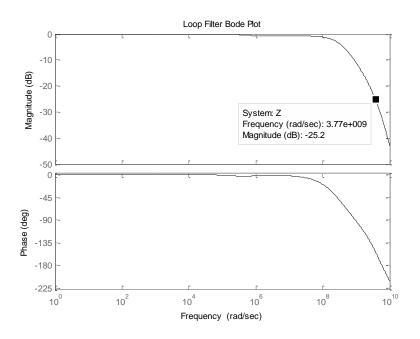

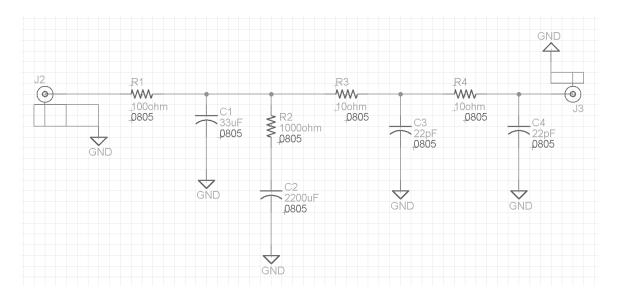

| Figure 3-18: Circuit Schematic of the Proposed 4 <sup>th</sup> Order Loop Filter            | 74      |

| Figure 3-19: Simulated Bode Plots for the Designed Loop Filter                              | 76      |

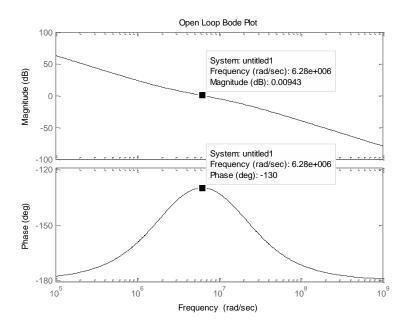

| Figure 3-20: Bode Plots for the Compensated Open Loop Transfer Function                     | 77      |

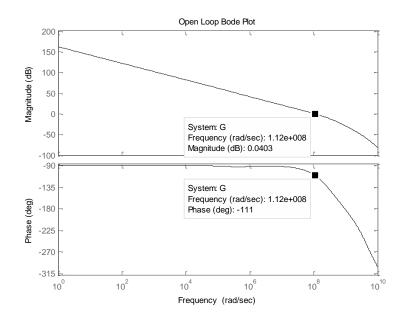

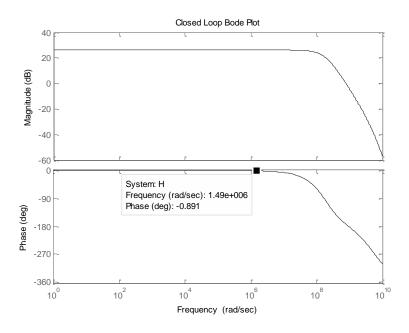

| Figure 3-21: Bode Plots for Compensated Closed Loop Transfer Function                       | 78      |

| Figure 3-22: Simulated Bode Plots for the Final Design of the Loop Filter Transfer Function | n79     |

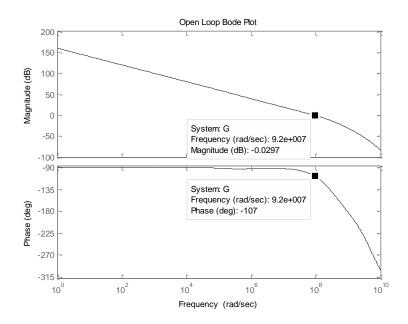

| Figure 3-23: Simulated Bode Plots for Compensated Open Loop Transfer Function for           | r Final |

| Loop Filter Design (KV=600MHz/V)                                                            | 80      |

| Figure 3-24: Simulated Bode Plots for Compensated Open Loop Transfer Function for           | r Final |

| Loop Filter Design (KV=450MHz/V)                                                            | 80      |

| Figure 3-25: Simulated Bode Plots for Compensated Open Loop Transfer Function for           | r Final |

| Loop Filter Design (KV=750MHz/V)                                                            |         |

| Figure 3-26: Simulated Bode Plots for Compensated Closed Loop Transfer Function for         | r Final |

| Loop Filter Design (KV=600MHz/V)                                                            | 81      |

| Figure 3-27: Circuit Schematic for the Final Design of the Loop Filter                      |         |

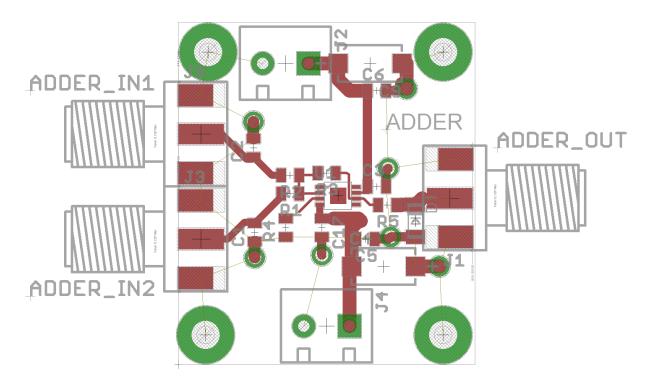

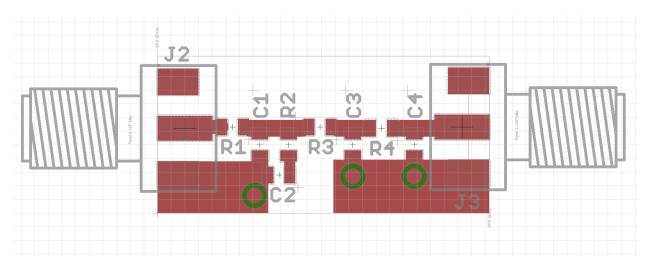

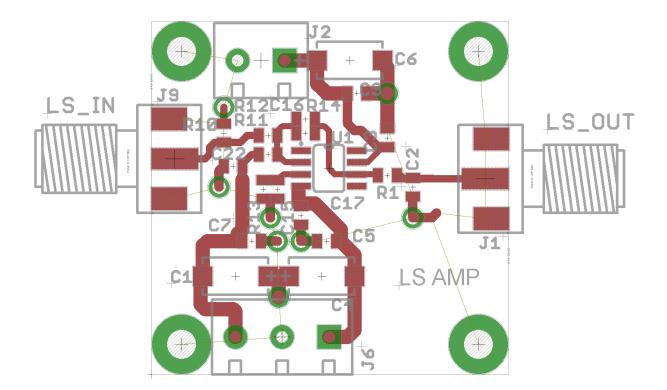

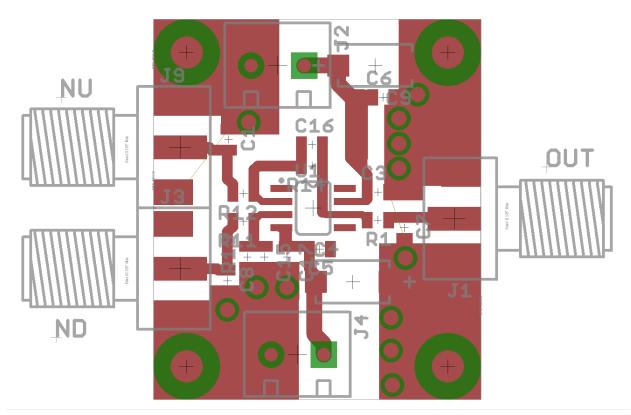

| Figure 3-28: Adder Printed Circuit Board Layout                                             | 84      |

| Figure 3-29: Bottom Layer of Adder Printed Circuit Board Layout                             | 85      |

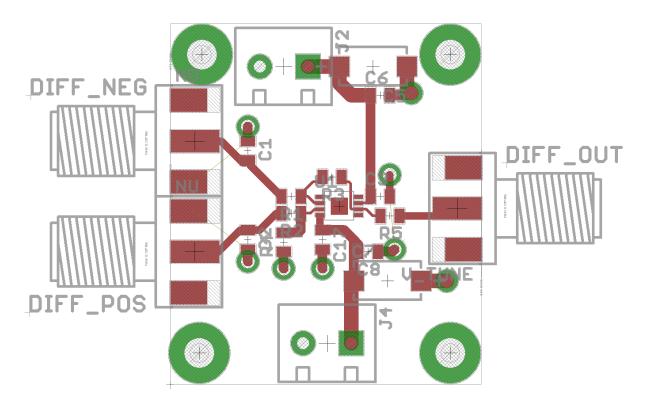

| Figure 3-30: Differential Amplifier Printed Circuit Board Layout                            | 85      |

| Figure 3-31: Bottom Layer of Adder Printed Circuit Board Layout                             | 86      |

| Figure 3-32: Loop Filter Printed Circuit Board Layout                                       | 86      |

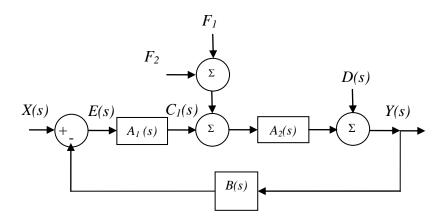

| Figure 3-33: Proposed Dual Compensation Control System Block Diagram                        |         |

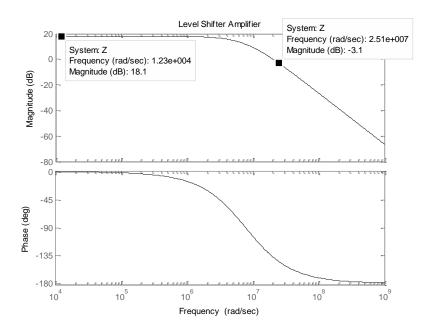

| Figure 3-34: Simulated Bode Plots for the Level Shifter Amplifier                           |         |

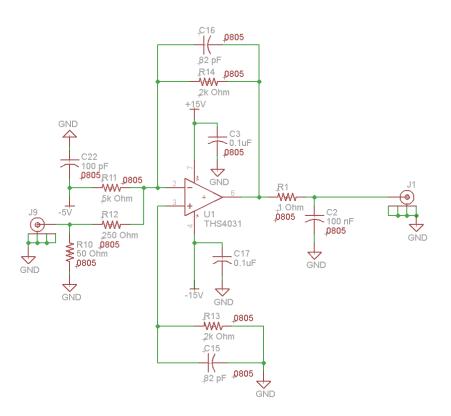

| Figure 3-35: Circuit Schematic of the Level Shifter Amplifier                               |         |

| Figure 3-36: Printed Circuit Board Layout for Level Shifter Amplifier                       | 94      |

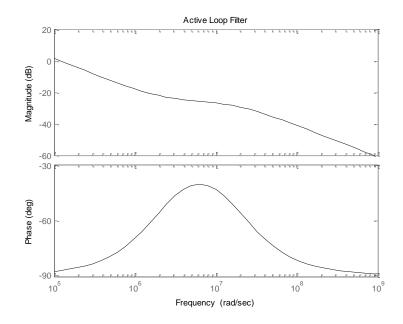

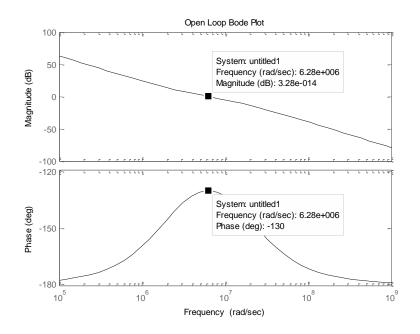

| Figure 3-37: Bode Plots for Start-up Active Loop Filter Transfer Function           | . 95     |

|-------------------------------------------------------------------------------------|----------|

| Figure 3-38: Bode Plots for the Open Loop Compensated with the Start-up Loop Filter | . 96     |

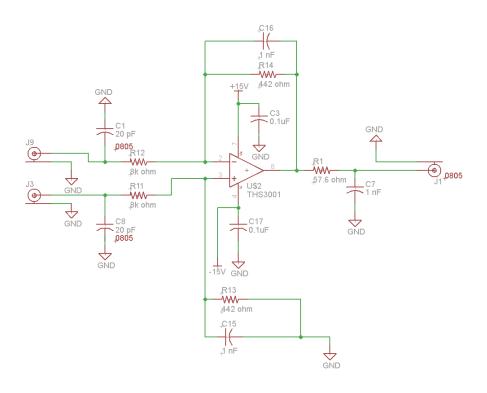

| Figure 3-39: Start-up Active Loop Filter Schematic                                  | . 97     |

| Figure 3-40: Start-up Active Loop Filter Layout                                     | . 97     |

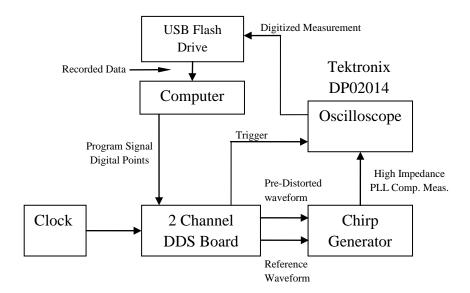

| Figure 3-41: System Level Block Diagram for the Pre-Distorted Voltage Generation    | . 98     |

| Figure 3-42: PLL Compensation Signal Measurement Setup                              | . 99     |

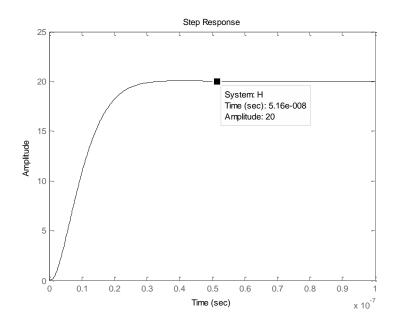

| Figure 4-1: Simulated Step Response for PLL with a KV of 600 MHz/V                  | 102      |

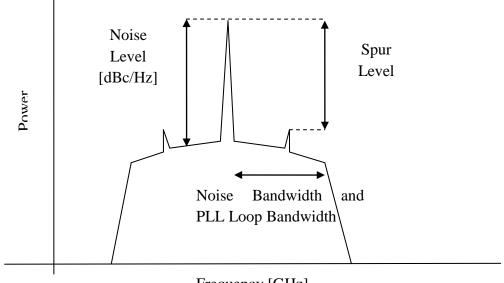

| Figure 4-2: Typical Phase Noise Spectral Plot for a PLL                             | 102      |

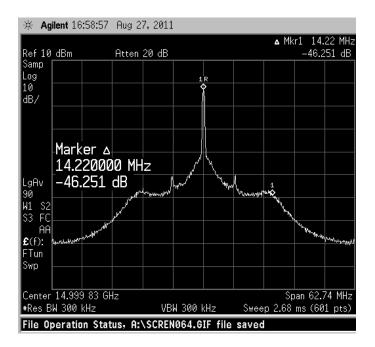

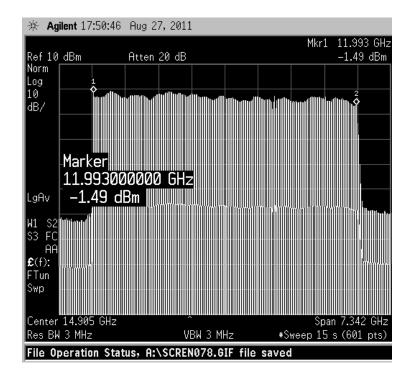

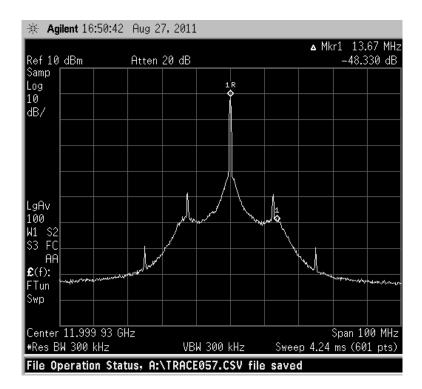

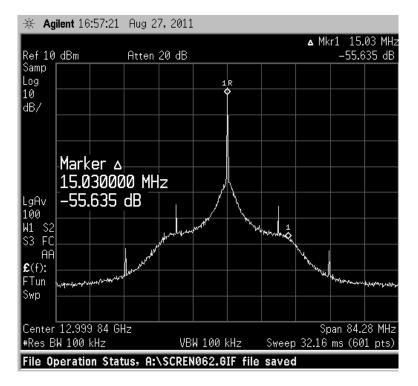

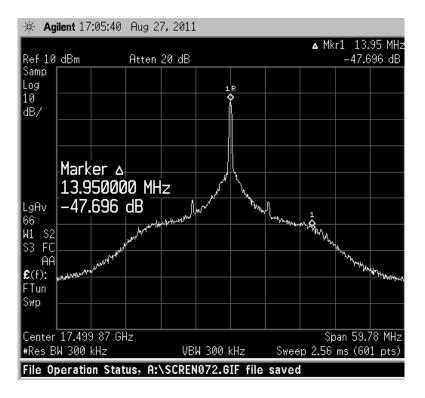

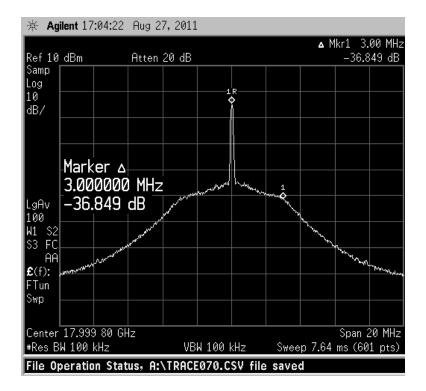

| Figure 4-3: PLL Spectral Measurement at 15 GHz                                      | 103      |

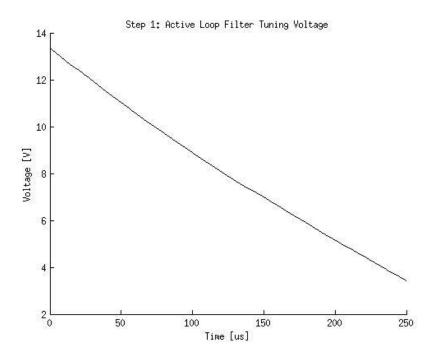

| Figure 4-4: Active Loop Filter Tuning Voltage                                       | 106      |

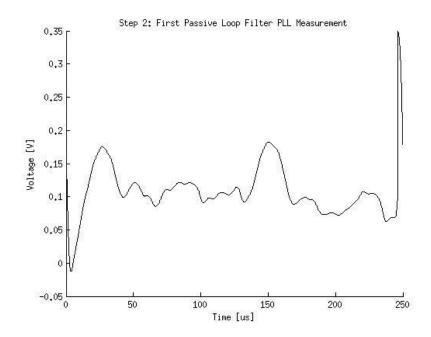

| Figure 4-5: Processed Compensation Signal Measurement Step 2                        | 106      |

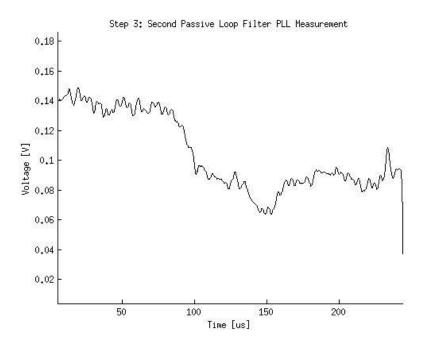

| Figure 4-6: Processed Compensation Signal Measurement Step 3                        | 107      |

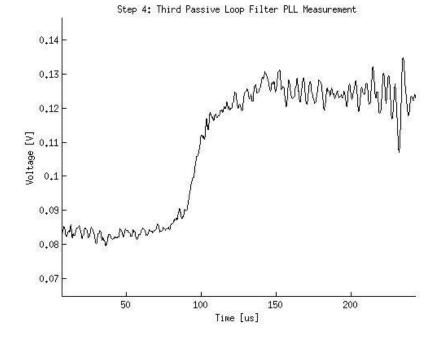

| Figure 4-7: Processed Compensation Signal Measurement Step 4                        | 107      |

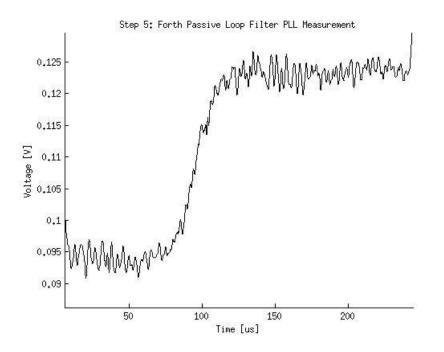

| Figure 4-8: Processed Compensation Signal Measurement Step 5                        | 108      |

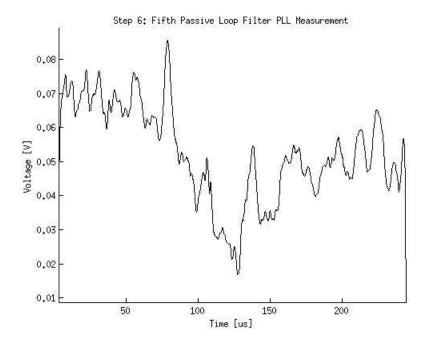

| Figure 4-9: Processed Compensation Signal Measurement Step 6                        | 108      |

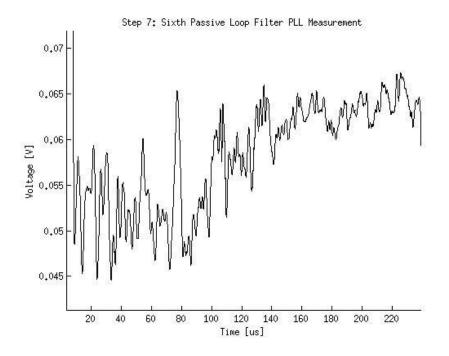

| Figure 4-10: Processed Compensation Signal Measurement Step 7                       | 109      |

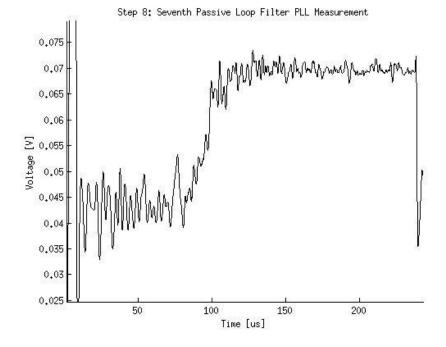

| Figure 4-11: Processed Compensation Signal Measurement Step 8                       | 109      |

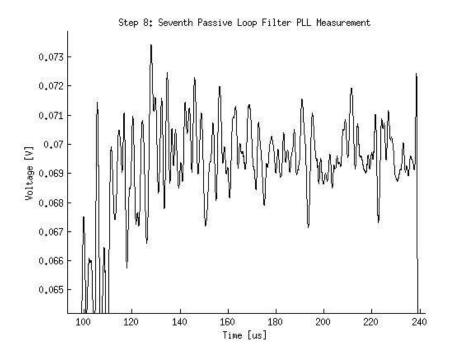

| Figure 4-12: Zoomed in Version of Processed Compensation Signal Measurement Step 8  | 110      |

| Figure 4-13: Block Diagram of the Set-up for the Measurements of the Chirp Ge       | enerator |

| Performance                                                                         | 111      |

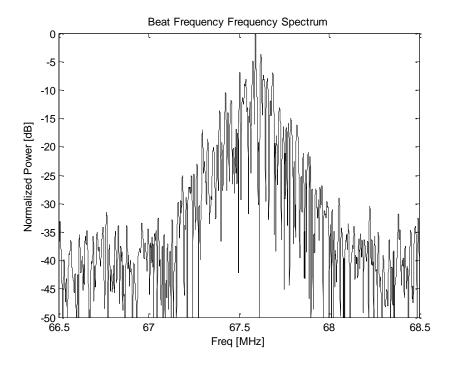

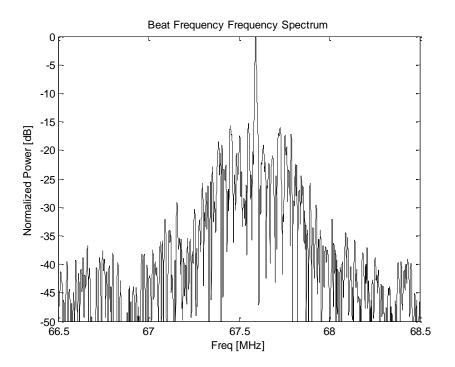

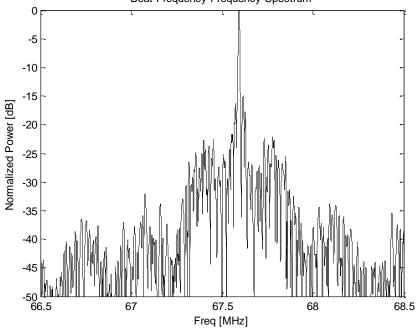

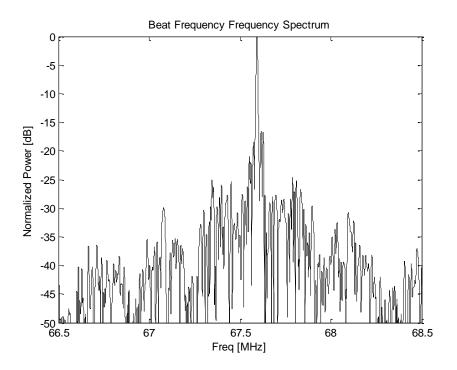

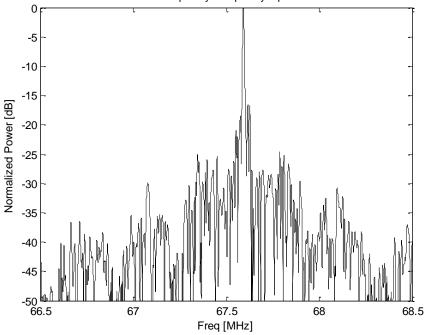

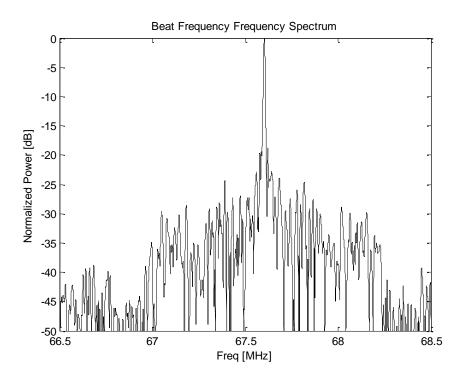

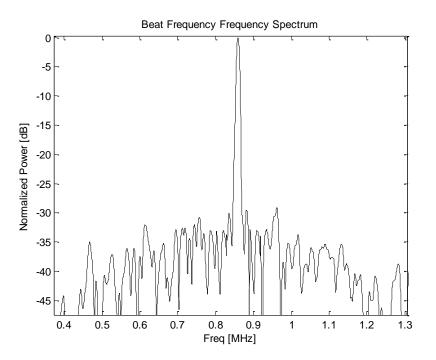

| Figure 4-14: Measured Video Signal Recorded at Step 1                               | 113      |

| Figure 4-15: Measured Video Signal Recorded at Step 2                               | 114      |

| Figure 4-16: Measured Video Signal Recorded at Step 3                               | 114      |

| Figure 4-17: Measured Video Signal Recorded at Step 4                               | 115      |

| Figure 4-18: Measured Video Signal Recorded at Step 5                               | 115      |

| Figure 4-19: Measured Video Signal Recorded at Step 8                               | 116      |

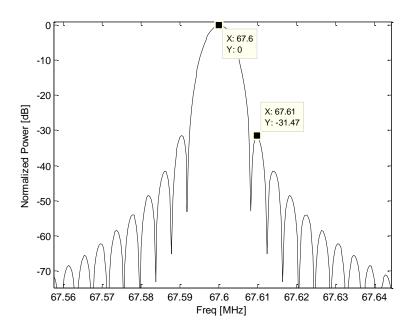

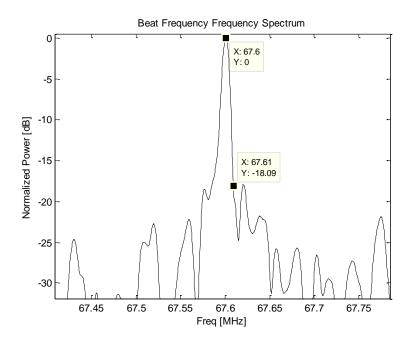

| Figure 4-20: Ideal Sidelobe Performance with Hanning Weighting                      | 118      |

| Figure 4-21: Video Signal Sidelobe Performance                                      | 118      |

| Figure 4-22: Video Signal at 35.8 ns of roundtrip delay                             | 120      |

| Figure 4-23: Chirp Frequency Spectrum                                               | 121      |

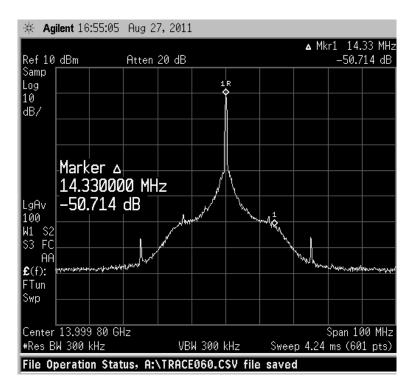

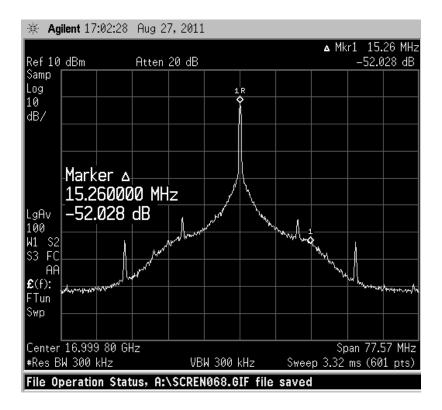

| Figure B-1: Measured PLL Spectrum at 12 GHz                                         | 131      |

| Figure B-2: Measured PLL Spectrum at 13 GHz                                         | 131      |

| Figure B-3: Measured PLL Spectrum at 14 GHz                                         | 132      |

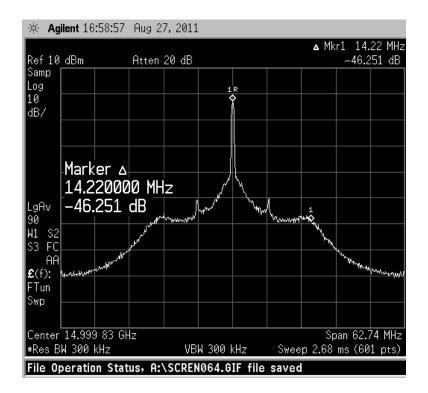

| E' and D. A. Manager and D. L. Constanting of 15 Cills                              | 132      |

| Figure B-4: Measured PLL Spectrum at 15 GHz                                         |          |

| Figure B-4: Measured PLL Spectrum at 15 GHz                                         | 133      |

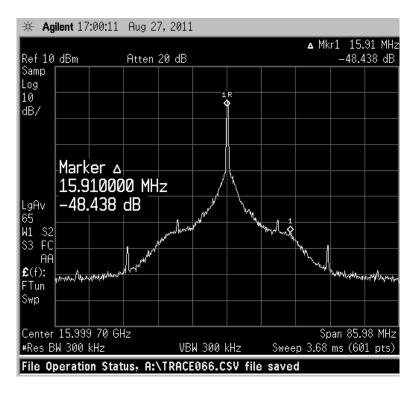

|                                                                                     |          |

| Figure B-5: Measured PLL Spectrum at 16 GHz                                         | 133      |

# LIST OF TABLES

| Table 2-1: List of Amplitude Waveforms                                           | 15          |

|----------------------------------------------------------------------------------|-------------|

| Table 2-2: Parameters for a FMCW Radar Simulation using a Chirp Waveform         | with Added  |

| Amplitude Modulation                                                             | 16          |

| Table 2-3: Radar Parameters for a FMCW Radar Simulation using a Chirp Way        | veform with |

| Added Frequency Modulation                                                       |             |

| Table 2-4: Steady State Error for Different Types of PLLs                        | 35          |

| Table 3-1: Chirp Generator Parameters                                            | 54          |

| Table 3-2: Average PLL Component Gains                                           | 72          |

| Table 3-3: Solved Time Constants, Zero and Poles of the Final Loop Filter Design | 82          |

| Table 3-4: Solved Lumped Component Values of the Final Loop Filter Design        | 82          |

| Table 3-5: Solved Gains and Resistor Values for Level Shifter Amplifier Circuit  | 91          |

| Table 3-6: PLL Parameters for Start-Up Active Loop Filter                        |             |

| Table 4-1: PLL Spectral Performance Measurements                                 | 104         |

| Table 4-2: Digital Low Pass Filter Bandwidth List                                | 105         |

|                                                                                  |             |

# **CHAPTER 1: INTRODUCTION**

## **1.1 SCIENCE BACKGROUND**

According to recent studies, the polar ice sheets' contribution to sea level rise due to mass loss has increased by 40% in the last decade [1]. Surface elevation changes constitute an important indicator in estimates of mass balance changes [1][2][3]. To estimate mass balance changes on the ice sheet from surface elevation measurements, corrections for the variable firn compaction and the bedrock motion should be applied [4][5]. A wide range of measurement techniques have been developed in past decades to monitor surface elevation changes in Polar Regions. These include the use of radar and laser altimeter instruments with high-resolution measurement capabilities.

## 1.1.1 Laser Altimeters

Laser altimeters operating from both aircraft and satellite platforms are used for topographic mapping of various targets with vertical range resolution of tens of centimeters or less. Their principle of operation relies on measuring the round-trip propagation time of nanosecond pulses emitted by solid state laser sources [6]. Laser altimetry represents a valuable tool for precise mapping and monitoring of Polar Regions [7].

In 2003, the National Aeronautics and Space Administration (NASA) launched the Ice, Cloud and Land Elevation Satellite (ICESat) carrying the Geoscience Laser Altimeter System (GLAS). The laser altimeter GLAS' primary mission was to measure the elevation changes in the Antarctic and Greenland ice sheets. Many different methods have been developed for deriving surface elevation changes using ICESat data [4][5]. Moreover, ICESat's unprecedented level of accuracy of elevation measurements has been used to characterize for range errors in satellite radar altimeters, such as the European Remote Sensing 2 Satellite (ERS-2) and the Environmental Satellite (Envisat) [8].

## 1.1.2 Radar Altimeters

Although laser altimeters such as GLAS possess high accuracy and high precision, they do not operate well when fog, smoke or any precipitation is present in their line of sight [9]. In contrast, radar altimeters, with the exception of some frequency ranges of operation, have the ability to perform measurements under these conditions [10].

An example of a system designed for altimetry measurements from a satellite platform is the Synthetic-Aperture-Radar Interferometric Radar Altimeter (SIRAL). SIRAL is an instrument on board the European Space Agency's (ESA) Cryogenic Satellite 2 (CryoSat-2), which provides altimetry information with a range resolution of 40 m/pixel [11].

Satellite radar altimeters are not devoid of shortcomings, as they are affected by both topography and penetration [12]. Radar altimeter signals may penetrate through snow, firn and ice, causing an accuracy error in the elevation measurement [12][14]. The backscatter signals for subsurface interfaces can be stronger than the actual surface return [14]. The CryoSat-2 altimeter includes a delay-Doppler technology to overcome the steep-slop error common on typical radar altimeters, such as the ESR-2 and Envisat [11][13].

Ground based and airborne radar altimeters with higher accuracy can be used to characterize and validate data from satellite altimeter radars. Ground based altimeters have been developed to provide high accuracy elevation data, but they are not very practical for large coverage measurements as airborne altimeters. Airborne altimeters validated by ground based systems would provide accurate measurements of surface elevations, as long as they have the sufficient resolution to resolve subsurface layers and identify the actual surface return.

## **1.2 CRESIS UWB RADARS**

The Center for Remote Sensing of Ice Sheets (CReSIS) has developed two Ultra-Wideband (UWB) Microwave Radars for airborne and surface-based platforms: The Snow Radar, which operates over the 2-8 GHz range and the Ku-Band Radar, which operates over the 12-18 GHz range. The Snow Radar was primarily developed for measuring the thickness of snow over sea ice [16]. The Ku-band radar altimeter is used for high-accuracy surface elevation measurements over land and sea ice [16]. Both the Snow and Ku-Band Radars also provide high resolution information about the near-surface internal layers. Both systems are operated as part of the CReSIS instrumentation package and operate routinely on board of various airborne platforms, such as the NASA P-3 and DC-8 Airborne Science Laboratories, as well as a DHC-6 Twin Otter [16][17]. Measurements on board of the NASA aircraft are conducted in the context of Operation IceBridge (OIB), an airborne program launched to operate on the period between the loss of ICESat I and the launch of ICESat II [17].

An essential component of these radars is the UWB chirp generator, which synthesizes the transmit waveform at microwave frequencies. This thesis discusses the development of an UWB chirp generator with improved frequency linearity implemented with high-speed analog design techniques. The linearization scheme relies on a PLL operating in conjunction with an external compensation added to the loop.

## **1.3 THESIS OUTLINE**

This thesis is composed of 5 Chapters: Chapter 2 provides the theoretical framework that has been considered for the design of the proposed chirp generator. The background concepts described in Chapter 2 include theory of radar systems, linear control systems, and phase lock loops. Chapter 3 describes the design and implementation of the chirp generator. Specifically, Chapter 3 explains the design and implementation considerations for the phase lock loop and the pre-distorted voltage generator. Chapter 4 presents the results from the performance characterization of system. Lastly, Chapter 5 presents the conclusions and discusses suggestions for future work.

# **CHAPTER 2: BACKGROUND**

## 2.1 UWB FMCW RADAR BACKGROUND

2.1.1 Radar Overview

2.1.1.1 Radar Basics and Impulse Radar

The word RADAR is the acronym for Radio Detection And Ranging. It is the standard name for the technology that uses electromagnetic signals to detect distant targets and to measure their range. In radar terminology, a target is the object detected and the range is the distance of the object to the sensor. Radar sensors can detect targets beneath certain materials which would not be detected with optical techniques. Besides detecting objects and measuring their range, modern radar systems have the ability to measure other properties of the target such as radial speed and radar cross section [18].

A typical impulse radar waveform is composed of a train of narrow pulses modulated by a sinusoidal carrier [18]. The radar system transmits the waveform as an electromagnetic signal. The signal propagates through the medium, gets reflected at the target and then travels back to the receiver. The range (*R*) of the target can be determined from the roundtrip signal delay ( $T_R$ ) and the speed of the signal in the propagation medium (v) using equation (2.1) [18].

$$R = \frac{v \cdot T_R}{2} \tag{2.1}$$

On an impulse radar system, the roundtrip delay of the received signal is measured directly with respect to the transmit signal. On this type of radar, the time between pulses is known as the pulse repetition interval (PRI). During this interval, the radar transmits a pulse for a limited amount of time known as the pulse length. The radar then listens during the rest of the

PRI for the received signal. It can be shown that there exists range ambiguity for targets with roundtrip delays larger than the PRI [18].

The carrier tone that modulates the pulse signal can be modulated further in frequency and amplitude. The most common technique to improve range resolution, which also improves the signal to noise ratio of the signal, is to frequency modulate the signal. If the waveform is linearly frequency modulated, it is also known as a chirp. Regardless of the shape of the signal, a technique known as pulse compression uses a matched filter to improve the range resolution and the signal to noise ration. If the waveform is a chirp, the signal to noise ratio gets improved by the bandwidth-pulse-length product and the range resolution becomes inversely proportional to the bandwidth [18].

Impulse radar systems apply pulse compression either with a real-time processor or at a post-processing stage after having recorded the received data. The pulse compression can be applied with digital, analog or mixed signal devices [19][20][21]. However, digital post processing of the recorded raw data continuous being the most robust method since it allows the ability to reprocess the data with improved techniques. In order to apply any type of pulse compression by digital means, the digitizer's sampling rate should be at least twice the signal bandwidth [22]. This fact poses a limitation on the bandwidth of impulse radars.

### 2.1.1.2 Continuous Wave Radar

Typical continuous wave (CW) radars or unmodulated continuous wave radars have a signal composed of an unmodulated single tone. CW radars make use of the Doppler Effect to measure radial speed of targets. The Doppler Effect is the description of the behavior of the frequency content of a signal when it is reflected off a moving target [18]. The frequency content on a signal reflected off a moving target gets shifted by the Doppler frequency ( $f_d$ ). The Doppler frequency depends on the wavelength ( $\lambda$ ) of the carrier signal and the radial speed (v) of the moving target with respect to the sensor. Equation (2.2) describes this relationship.

$$f_d = \frac{2 \cdot v}{\lambda} \tag{2.2}$$

CW radar sensors are used when the target velocity is the main parameter to be measured. CW radar sensors for short range and moderate ranges are much simpler systems than pulse radar systems [18]. However, the transmit power of CW radar systems is limited by the amount of transmit leakage to the receiver that can be tolerated. Moreover, CW radars with a single transmit tone do not have the ability to unambiguously measure range. Multi-tone CW radars have the ability to measure range with accuracy and ambiguity limited by the number of tones selected and their frequencies [23][18].

## 2.1.1.3 Frequency Modulated Continuous Wave RADAR

Frequency Modulated Continuous Wave (FMCW) Radar, as the name implies, uses a frequency modulated waveform. Typically, this waveform is linearly frequency modulated, also known as a chirp. In contrast to the unmodulated CW radars, the frequency content of the received signal from FMCW radars may be used to extract both the range and the radial speed of the target [18].

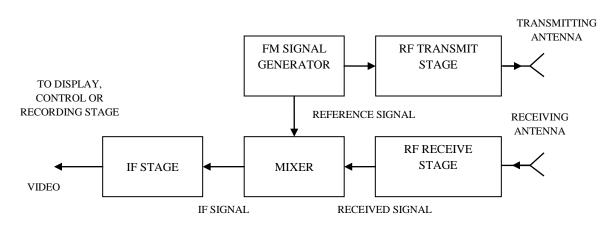

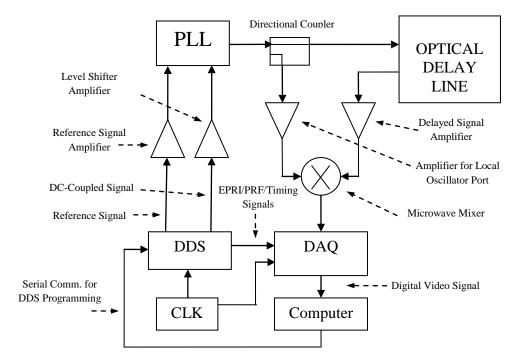

The block diagram shown in Figure 2.1 represents a typical FMCW system and illustrates the paths which the FMCW waveform goes through. Each stage on the paths has a frequency dependent system response that will affect the waveform signal. The FMCW waveform goes through two paths: the reference path and the transmit/receive path. The transmit/receive path comprises the radio frequency transmit (RF TX) stage, the antenna, the roundtrip channel to and from the target, the target return loss and the radio frequency receive (RF RX) stage. The reference path includes the conditioning stage for the waveform to drive the Local Oscillator (LO) port on the mixer.

Figure 2-1: Block Diagram of FMCW Radar

The output signals of both paths, the reference and the received signals, are applied to the mixer followed by the Intermediate Frequency (IF) stage. The output of the IF stage goes to a display, control or recording stage.

The FMCW radar makes use of the ideal behavior of the mixer as a signal multiplier. The output of the mixer becomes the multiplication of the reference and the received signals. The IF stage then filters and conditions the IF signal which contains information about the range and radial speed of the target.

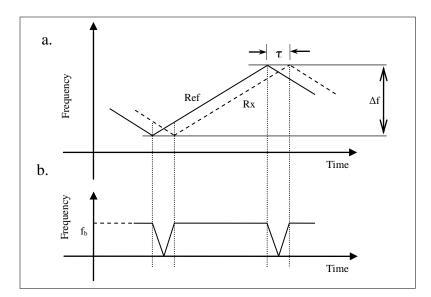

The chirp waveform is the most common one for FMCW radars. A plot of the frequency behavior over time for the reference and receive signals is shown in Figure 2.2. For simplicity, both amplitude and frequency modulations that may affect the shape of the frequency signals are neglected. The frequency of the reference signal is an identical copy of that of the FMCW generated waveform delayed by the reference path delay. The reference path delay is the time it takes the waveform to go from the waveform generator to the LO port of the mixer. Similarly, the frequency waveform of the received signal is also an identical copy of the generated waveform delayed by the transmit-receive path delay. The difference between these two delays is represented by  $\tau$  in Figure 2.2.

On the bottom plot of figure 2.2, the beat frequency  $(f_b)$  is shown. The beat frequency is the difference between the reference and the received frequencies [18]. The difference between both delays can be extracted from the beat frequency by considering the similar triangles formed.

Figure 2-2: a. FMCW Frequency Plots of Reference (Ref) and Received (Rx) signals for a stationary target. b. FMCW beat frequency (fb) resulting from the difference of the reference and receive signal frequencies

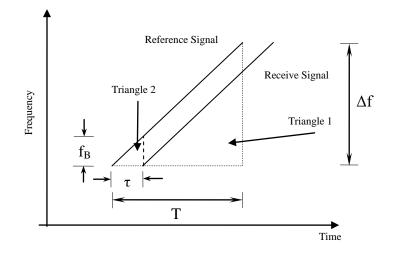

Figure 2-3: Frequency of Reference and Receive Signals for similar triangle analysis to determine the beat frequency

As shown in Figure 2.3, two right-angled similar triangles are formed out of the frequency plots of the received and reference signals. Triangle 1 is formed by the chirp bandwidth ( $\Delta f$ ) as the height cathetus and the chirp time length (T) as the base cathetus. Triangle 2 is formed by the beat frequency ( $f_B$ ) as the height cathetus and the delay difference between the reference and received signals ( $\tau$ ) as the base cathetus. The beat frequency ( $f_B$ ) can be solved as shown on equation (2.3).

$$f_B = \tau \cdot \frac{\Delta f}{T} \tag{2.3}$$

On equation (2.4),  $\tau$  corresponds to the delay difference between the reference and the received signal. The reference and received signals are delayed from the waveform generator output by  $\tau_{REF}$  and  $\tau_{RX}$  respectively. Moreover, the target range may be inferred from the delay difference between the delay to the transmit antenna ( $\tau_{TX\_ANTENNA}$ ) and the delay to the receive antenna ( $\tau_{RX\_ANTENNA}$ ).

$$\tau = \tau_{RX} - \tau_{REF} \tag{2.4}$$

$$\tau_o = \tau_{RX\_ANTENNA} - \tau_{TX\_ANTENNA} \tag{2.5}$$

Typically for analysis purposes, we may assume the following approximation:

$$\tau_o \approx \tau$$

(2.6)

In practice, all the previously mentioned delays should be measured and a delay correction should be applied to the data for accurate range measurements.

Once the actual roundtrip delay to the target is found, the target range can be calculated using equation (2.1).

For the case when the target range is not stationary, either the receiver or the target moves with a radial speed towards or away from each other, the beat frequency will be shifted by the Doppler frequency ( $f_D$ ) [18]. The Doppler frequency is added or subtracted to the range component of the beat frequency depending on the sign of the chirp rate ( $\mu$ ). Both cases are illustrated on equations (2.7) and (2.8).

$$f_B(\mu > 0) = f_R - f_D \tag{2.7}$$

$$f_B(\mu < 0) = f_R + f_D \tag{2.8}$$

On equations (2.7) and (2.8),  $f_R$  corresponds to the range part of the beat frequency and can be extracted by averaging the beat frequency of two chirps with chirp rates equal in magnitude but opposite sign.

As mentioned earlier, FMCW radar systems use the ideal behavior of the mixer as a multiplier to extract range and radial speed information. To do so, it only needs to extract the beat frequency using the reference and receive signals. Normalizing the amplitude terms for simplicity and setting the reference initial phase as zero, both signals may be described by equations (2.9), (2.10) and (2.11) for a linear frequency modulated waveform.

$$S_{REFERENCE} = \cos\left[2\pi\left(f_o \cdot t + \frac{1}{2}\mu \cdot t^2\right)\right]$$

(2.9)

$$S_{RECEIVE} = \cos\left[2\pi \left(f_o \cdot (t-\tau) + \frac{1}{2}\mu \cdot (t-\tau)^2\right)\right]$$

(2.10)

$$S_{\text{RECEIVE}} = \cos\left[2\pi \left(-f_o \cdot \tau + \frac{1}{2}\mu \cdot \tau^2 + (f_o - \mu \cdot \tau)t + \frac{1}{2}\mu \cdot t^2\right)\right]$$

(2.11)

$$S_{IF} = S_{RECEIVE} \cdot S_{REFERENCE} \tag{2.12}$$

$$S_{IF} = \frac{1}{2} \left\{ \cos \left[ 2\pi \left( f_o \tau - \frac{1}{2} \mu \cdot \tau^2 + \mu \cdot \tau \cdot t \right) \right] + \cos \left[ 2\pi \left( f_o \tau - \frac{1}{2} \mu \cdot \tau^2 + (2f_o + \mu \cdot \tau) \cdot t + \mu \cdot t^2 \right) \right] \right\}$$

(2.13)

Equations (2.12) and (2.13) describe the resulting IF signal ( $S_{IF}$ ) out of the ideal mixer. The resulting IF signal has two components. The first component is a tone with frequency ( $\mu \cdot \tau$ ) and initial phase ( $f_o \tau - \frac{1}{2} \mu \cdot \tau^2$ ). This component signal is also known as the beat frequency signal. The second component is a chirp waveform with initial phase ( $f_o \tau - \frac{1}{2} \mu \cdot \tau^2$ ), initial frequency ( $2f_o + \mu \cdot \tau$ ) and chirp rate ( $2 \cdot \mu$ ). The IF stage filters this IF signal so that only the beat signal passes. The beat frequency then may be used to extract range and radial speed information.

For FMCW radars that measure single stationary targets, the frequency modulation need not be linear. The range of the target can be found by the average frequency of the video signal. However, FMCW radar sensors for multi-target measurements need to have a linear frequency modulated waveform. The importance of having a linear chirp with no additional frequency or amplitude modulation is explained on the next section.

### 2.1.2 FMCW Waveform Quality

On the previous section, the effects caused by the amplitude and phase response at each stage have been neglected to simplify the analysis. Moreover, the chirp-based FMCW signal has been assumed to be a perfectly linear frequency modulated waveform. However, the amplitude and phase responses of each stage may affect significantly the performance of the radar. Since the waveform frequency is swept over a time period, the amplitude and phase responses over frequency gets mapped over the chirp period and then delayed for each path. In addition, the frequency nonlinearity and amplitude modulation at the generation point will also affect the radar range resolution performance.

The range resolution is the minimum range difference between two distinguishable targets. In other words, the range resolution defines the ability of a radar sensor to distinguish close targets. For an FMCW radar system, the target range response is described by the frequency spectrum of the video signal over the overlapping interval ( $T_{OL}$ ) between the reference and the received signals.

$$T_{OL} = T_{chirp} - 2 \cdot \tau \tag{2.14}$$

Equation (2.14) describes the overlapping interval of the reference and the received chirp signals. On equation (2.14),  $T_{chirp}$  is the chirp time length or just chirp length and  $\tau$  is the difference in time delay between the reference and the received signals. The value of  $\tau$  will be approximated to the roundtrip time delay of the transmitted signal to simplify the analysis on this section.

For a digitally recorded video signal over the overlapping time interval, the frequency spectrum of the video signal can be computed using the Fast Fourier Transform (FFT) [22]. For the FFT of the video signal time gated by the overlapping time interval, the FFT frequency

resolution equals the inverse of the overlapping time interval. This relationship is described on equation (2.15).

$$\delta f = \frac{1}{T_{OL}} \tag{2.15}$$

$$\delta f_B = \frac{\Delta f \cdot \delta \tau}{T} = 2 \cdot \frac{\Delta f \cdot \delta R}{T v}$$

(2.16)

Equation (2.16) shows the relationship between a small difference on the beat frequency  $(\delta f_B)$  and the range resolution  $(\delta R)$ . On equation (2.16),  $\Delta f$  is the bandwidth of the chirp, v is the signal propagation speed, T is the overlapping time interval and  $\delta \tau$  is a small difference in the roundtrip.

$$\delta R = \frac{v}{2 \cdot \Delta f} \tag{2.17}$$

Since the minimum frequency difference will be described by the frequency resolution of the FFT output, the range resolution can be solved by combining equations (2.15) and (2.16). The range resolution is shown on equation (2.17).

Equation (2.17) describes the range resolution as the equivalent range difference between two FFT bins, known as range bins. Another way to define the range resolution performance of a radar system is to define the difference in range between two distinguishable peaks. Thus, by measuring a single target response two distinguishable peaks can be defined as the distance between the mainlobe and the first sidelobe. The sidelobe level dictates the dynamic range for close targets. As it will be seen on the next section, the sidelobe performance can be degraded by sidebands added by the system's imperfections. Moreover, the sidelobes can be suppressed using weighting techniques on the time gated video signal at the expense of widening the range resolution. Therefore, a more complete description of the range resolution performance can be expressed by indicating the mainlobe to first sidelobe range difference, the first sidelobe level and the weighting being used.

This section discusses the amplitude and frequency modulation applied by system imperfections to the chirp and their effects on the range resolution performance on an FMCW radar system.

#### 2.1.2.1. Amplitude Modulation

Assuming a perfectly linear chirp and ideal phase responses at each stage, only the effects from amplitude are considered. From communication theory, double sideband amplitude modulation occurs when a high frequency carrier gets multiplied by a Direct Current (DC) biased low frequency signal [24]. Thus, the low frequency signal appears on the envelope of the carrier. A chirp has amplitude modulation when its envelope magnitude varies with time.

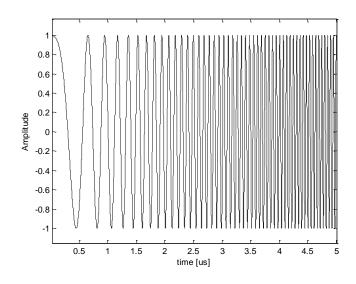

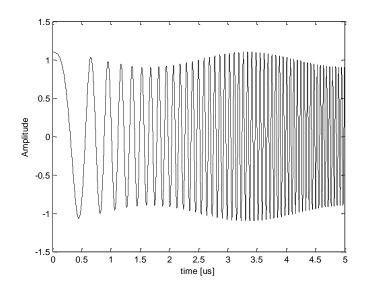

Figure 2-4: Example of a Chirp Waveform with no amplitude modulation

Figure 2-5: Example of a Chirp Waveform with amplitude modulation

Figure 2-4 and Figure 2-5 show examples of an unmodulated chirp and an amplitude modulated chirp, respectively.

The chirp may contain amplitude modulation at the generation stage or it may be added at one of the FMCW signal paths. Each stage's amplitude response will modulate the amplitude of its input waveform which may already be modulated. Then, the amplitude modulation can be analyzed in terms of many amplitude waveforms, where each amplitude waveform will be multiplied to its input signal.

| Source of Amplitude Modulation                         | Amplitude Waveform Variable |  |

|--------------------------------------------------------|-----------------------------|--|

| Chirp Generator amplitude waveform at the Ref. Point   | a <sub>CG_REF</sub>         |  |

| Chirp Generator amplitude waveform at the Rx. point    | $a_{CG_Rx}$                 |  |

| Transmit Stage and Transmit antenna amplitude response | $a_{TX}$                    |  |

| Channel amplitude response                             | a <sub>CH</sub>             |  |

| Target Reflection amplitude response                   | $a_{TR}$                    |  |

| Receive Stage and Receive antenna amplitude response   | a <sub>RX</sub>             |  |

| Reference Path Amplitude Waveform                      | $a_{REF}$                   |  |

| Mixer Conversion Factor amplitude response             | K                           |  |

| IF Stage amplitude response                            | a <sub>IF</sub>             |  |

#### Table 2-1: List of Amplitude Waveforms

Assuming a linearly frequency modulated signal, the amplitude waveforms in Table 2-1 correspond to the gain or attenuation that gets added (in dB) by each stage over the sweep time. The amplitude waveforms in Table 2-1 are related to the amplitude response over frequency that gets mapped for the chirp frequency sweep. To simplify the analysis, the amplitude waveforms take into account the delay of the chirp up to that point.

Then the amplitude waveform of the IF stage output signal can be expressed as follows:

$$a_{VIDEO} = a_{IF} \cdot k \cdot (a_{CG_{RX}} \cdot a_{TX} \cdot a_{CH} \cdot a_{TR} \cdot a_{RX}) \cdot (a_{CG_{REF}} \cdot a_{REF})$$

(2.18)

As shown on equation (2.18), the amplitude waveforms corresponding to the different stages on the radar become a chain of potential amplitude modulation signals.

In order to analyze the effects of a generated amplitude modulated chirp waveform on the radar range resolution, the following example neglects any added amplitude modulation caused by the amplitude response at any other stage.

As an example, a generated amplitude modulated chirp, which has an amplitude waveform  $a_{CG}$ , is mixed with its delayed version to result in the amplitude waveform of the

video signal ( $a_{video}$ ). For this example, the amplitude waveform of the generated chirp is composed of a DC-biased tone signal with a DC offset of 1 and a tone frequency of 1 MHz. The amplitude modulation index that scales the tone signal has been set to a value of 0.1. The amplitude waveform of the chirp is described on equation (2.19).

$$a_{CG} = 1 + 0.1 \cdot \cos(2 \cdot \pi \cdot f_o \cdot t) \tag{2.19}$$

$$a_{VIDEO} = a_{CG}(t) \cdot a_{CG}(t-\tau) \tag{2.20}$$

$$a_{VIDEO} = 1 + 0.1 \cdot \cos(2\pi f_o t) + 0.1 \cdot \cos[2\pi f_o (t - \tau)] + \frac{0.01}{2} \{\cos[2\pi f_o (2t - \tau)] + \cos[2\pi f_o \tau]\}$$

(2.21)

Equation (2.20) and (2.21) describe the resulting amplitude waveform of the video signal for this example.

A computer simulation for a single target response has been completed to illustrate the effects of an amplitude modulated chirp to the frequency spectrum of the video signal. The simulation uses the amplitude modulation waveform described on the example above. The relevant radar parameters used for the simulation are shown in Table 2-2. The FMCW radar simulation assumes an ideal mixer. The computer simulation was realized using Matlab [25].

Table 2-2: Parameters for a FMCW Radar Simulation using a Chirp Waveform with Added Amplitude Modulation

| Parameter                             | Value | Units |

|---------------------------------------|-------|-------|

| Start Frequency (f <sub>start</sub> ) | 12    | GHz   |

| Stop Frequency (f <sub>stop</sub> )   | 18    | GHz   |

| Chirp Length (T)                      | 5     | μs    |

| Roundtrip Delay $(\tau)$              | 44    | ns    |

| Chirp Amplitude Modulation Index      | 0.1   |       |

The simulation used a single target with a roundtrip delay of 44  $\mu$ s, which is 4.4% the modulation signal wavelength. Since the roundtrip delay is much shorter than the wavelength of the modulation signal in this case, the amplitude waveform of the video signal may be approximated as shown on equation (2.22).

$$a_{VIDEO} \approx 1.005 + 0.2 \cdot \cos(2\pi f_o t) + 0.005 \cdot \cos[2\pi (2f_o)t]$$

(2.22)

Figure 2-6: Simulation Plot for the Effects on the video signal caused by amplitude modulation on the chirp waveform

Figure 2-7: Simulation Plot for the Effects on the video signal caused by amplitude modulation on the chirp waveform using a Hanning Weighting

Figure 2-6 and Figure 2-7 show the frequency spectrum of the video signal for the radar parameters described in Table 2-2. The approximated frequency spectrum plots have been computed using the FFT. Figure 2-6 shows the FFT plot of the video signal with no weighting. Figure 2-7 shows the FFT of the same waveform weighted by a Hanning window for sidelobe suppression.

In Figure 2-6, the sidebands caused by the amplitude modulation are at 17 dBc as expected by the first modulation term on equation (2.22). In Figure 2-7, the sidelobes have been suppressed by the amplitude weighting. The sidelobes decreased from 13 dBc to about 32 dBc. However, the sidebands, caused by amplitude modulation, decreased only by about 3 dB. The sidelobe suppression also uncovered the sidebands caused by the second amplitude modulation term on equation (2.22).

For these results, it can be seen that the amplitude modulation of the chirp waveform translates into amplitude modulation at the video signal. This amplitude modulation on the video signal forms sidebands around the target response. Since the video signal on an FMCW radar represents the targets response, these sidebands degrade the target response. For a multi-target FMCW radar, these sidebands may be erroneously interpreted as targets if they are not expected. If the sidebands have been measured on a single target and they are expected, they degrade the dynamic range for close targets. Moreover, the simulations show that the sidelobe suppression by weighting techniques does not significantly reduce the sidebands caused by amplitude modulation.

#### 2.1.2.2 Frequency Modulation

Frequency modulation added at any point on the signal paths also affects the range performance of an FMCW radar. Like amplitude modulation, frequency modulation may get introduced at any stage of the radar paths. If the phase response on any of the components has a linear shape, the component only adds a group delay to the input signal [22]. When the phase response of a component is non-linear over frequency and the input corresponds to a linear chirp, the output signal will have some phase modulation. This phenomenon is also known as dispersion [18]. Since frequency is the rate of change of the phase with time, nonlinear phase modulation also leads to frequency modulation. Moreover, if the chirp is not a perfectly linear frequency modulated waveform, this could also be seen as a form of frequency modulation added to the linear chirp. Since any stage containing a non-linear phase response will change the frequency linearity of the chirp, the chirp will not have a direct mapping from the frequency response to the sweep time. Therefore the compound effects of the frequency modulation cannot be analyzed with a simple multiplication or addition of frequency waveforms. The equations and analysis required to do so are beyond the scope of this document.

On the other hand, the effects caused by a single source of frequency modulation will be analyzed. The most significant source of frequency modulation is encountered at the chirp generator.

$$f(t) = f_o + \mu \cdot t + f_m(t)$$

(2.23)

$$f_m(t) = \beta \cdot f_c \cdot m(t) \tag{2.24}$$

$$x(t) = \cos[2 \cdot \pi \cdot \int (f_o + \mu \cdot t + f_m(t))dt]$$

(2.25)

On equation (2.23),  $f_m(t)$  is the frequency modulation signal,  $f_o$  is the chirp start frequency, t is the time variable, and  $\mu$  is the chirp rate. The waveform  $f_m(t)$  can be further decomposed with the factors shown on equation (2.24). On equation (2.24),  $\beta$  is the frequency modulation index,  $f_c$  is the chirp center frequency and m is the frequency modulation signal. Equation (2.25) corresponds to the normalized chirp with frequency modulation.

The video signal then becomes the multiplication of the reference signal with the received signal. Using the analysis assumption that the delay difference at the mixer ports equals the target roundtrip delay, the video signal is described on equation (2.26) after being filtered at the IF stage.

$$x_{video}(t) = \cos\{2 \cdot \pi \cdot [f_o \cdot \tau - \frac{1}{2}\mu \cdot \tau^2 + \mu \cdot \tau \cdot t + \int_{t-\tau}^t f_m(t)dt]\}$$

(2.26)

On equation (2.26), the last term in the cosine argument corresponds to the resultant phase modulation caused by the chirp frequency modulation. To analyze the effect of the frequency modulation on the chirp to the output video signal, the next example uses a single tone signal with frequency  $f_X$  for the frequency modulation signal. The frequency modulation signal (*m*) is described on equation (2.27).

$$m(t) = \cos(2 \cdot \pi \cdot f_X \cdot t) \tag{2.27}$$

$$pm(t) = \int_{t-\tau}^{t} f_m(t)dt = \int_{t-\tau}^{t} \beta \cdot fc \cdot m(t)dt$$

(2.28)

$$pm(t) = \frac{\beta \cdot f_c}{2\pi \cdot f_X} \cdot [\sin(2\pi \cdot f_X t) - \sin(2\pi \cdot f_X (t - \tau))]$$

(2.29)

Equations (2.28) and (2.29) show the equivalent expression for the phase modulation on the video signal caused by a single tone frequency modulation on the chirp. By calculating the root-mean-square (RMS), the magnitude of the varying phase modulation can be measured.

$$PM_{RMS}(\tau) = \frac{\beta \cdot f_c}{2\pi \cdot f_x} \cdot \sqrt{\frac{1}{1/f_x}} \int_{0}^{1/f_x} [\sin(2\pi \cdot f_x t) - \sin(2\pi \cdot f_x (t - \tau))]^2 dt}$$

(2.30)

$$PM_{RMS}(\tau) = \frac{\beta \cdot f_c}{2\pi \cdot f_X} \sqrt{1 - \cos(2 \cdot \pi \cdot f_X \cdot \tau)}$$

(2.31)

Equation (2.30) and (2.31) show the RMS expression for the phase modulation on the video signal caused by the single tone frequency modulation on the chirp. This RMS is dependent on the roundtrip delay of the FMCW signal. From equation (2.31), it can be inferred that the RMS peaks at every odd multiple of half the frequency modulation tone period.

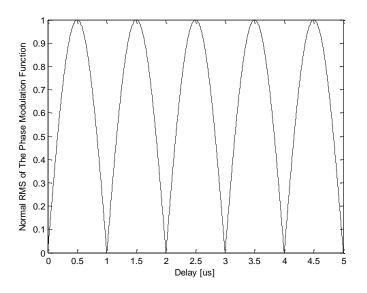

For a 5  $\mu$ s sweep time and a frequency modulation given by a single tone at 1 MHz, the RMS of the phase modulation as a function of the roundtrip delay is plotted and shown in Figure 2-8. The plot in Figure 2-8 shows that the RMS increases as a function of the delay from the origin up to half the period. The RMS also peaks at odd multiples of 0.5  $\mu$ s, which corresponds to half the period.

This example shows that the phase modulation effects on the video signal are a function of the roundtrip delay where the RMS changes periodically for the given periodic frequency modulation waveform. For non-periodic frequency modulation waveforms, the RMS will continue to increase as the delay increases. This example shows that for applications with large roundtrip delay relative to the chirp time length, the effects caused by frequency modulation added to the chirp waveform translate on a phase modulation of a larger magnitude on the video signal. This is an important concept to have in mind when designing FMCW chirp generators for large range applications.

Figure 2-8: Root Mean Squared of The Phase Modulation Function

A computer simulation has been run to see the effects on the video signal caused by frequency modulation on the chirp at the chirp generator stage for various cases. The parameters shared by all cases are shown in Table 2-3. The simulations have been performed using Matlab [25].

| Parameter                             | Value | Units |

|---------------------------------------|-------|-------|

| Start Frequency (f <sub>start</sub> ) | 12    | GHz   |

| Stop Frequency (f <sub>stop</sub> )   | 18    | GHz   |

| Chirp Length (T)                      | 5     | μs    |

Table 2-3: Radar Parameters for a FMCW Radar Simulation using a Chirp Waveform with Added Frequency

Modulation

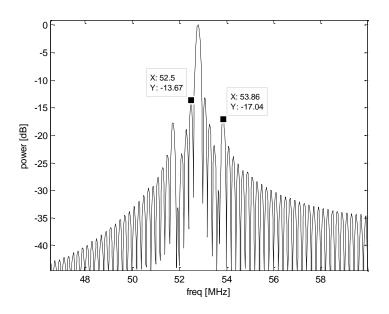

For all the simulated cases, the frequency modulation signal is a single tone with a carrier frequency of 1 MHz. For a first case, the chirp has a frequency modulation with index ( $\beta$ ) of

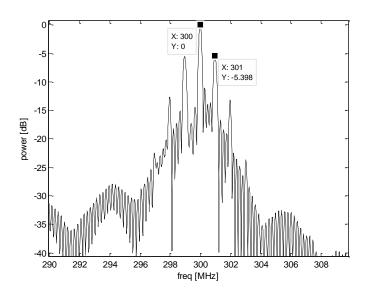

$5 \times 10^{-5}$ . This first case has been simulated with a target roundtrip delay of 250 ns, which equals a quarter of the period of the frequency modulation waveform. Figure 2-9 is a plot of the resulting video signal frequency spectrum for the first case simulation. The plot shows sidebands at 1 MHz apart from the mainlobe. The sidebands which correspond to the frequency modulation have a power of about 5.4 dBc. The example uses a delay of only a quarter of the period of the frequency modulation signal and an FM index of only  $5 \times 10^{-5}$  and the effects on the resolution performance of the video signal are already unsatisfactory for most multiple-target applications.

Figure 2-9: Video Signal Frequency Spectrum for Case 1

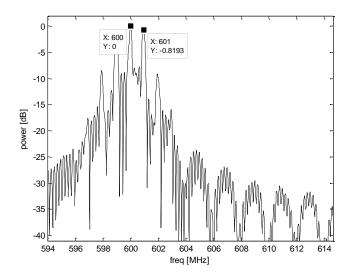

For a second case, the simulation uses a roundtrip delay of 500 ns, which is equivalent to half the period of the modulating signal. As it has been shown, this is the delay for which the effects caused by the phase modulation are maximized. This second case uses the same modulation index as the first case.

Figure 2-10 shows the frequency spectrum of the video signal for the second case. The power of the sidebands from the frequency modulation has been increased up to about 0.8 dBc.

Figure 2-10: Video Signal Frequency Spectrum for Case 2

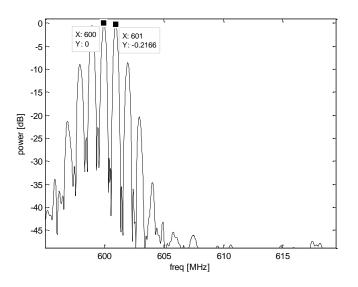

The frequency spectrum plot in Figure 2-10 uses no weighting in time to improve sidelobe performance. Figure 2-11 shows the frequency spectrum for case 2 using a Hanning window on the video waveform. The plot shows that windowing techniques may reduce the power on the sidelobes, but it has little effect on the sidebands caused by frequency modulation. This is an example of how the effects of the non-linear behavior of the chirp may not be improved with standard sidelobe reduction techniques.

Figure 2-11: Video Signal Frequency Spectrum for Case 2 with Windowing for Sidelobe Suppression

For the applications we are interested in, the delay is nowhere near half the period of the frequency modulation waveform. These two simulation cases are illustrated to show how the phase modulation effects on the video signal worsen as the roundtrip delay increases. Although the previous examples used fairly long relative delays, the modulation index was very small.

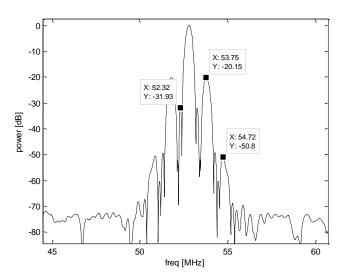

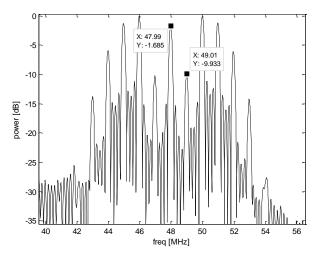

A third case considers a roundtrip delay of only 50 ns which corresponds to a twentieth of the period. The frequency modulation index in this case is  $5 \times 10^{-4}$ . A plot of the video signal for this case is shown in Figure 2-12. This example uses a fairly small relative delay and a very small frequency modulation index. This example shows that the video signal is very sensitive to the effects of frequency modulation added to the chirp at the generation point.

Figure 2-12: Video Signal Frequency Spectrum for Case 3

From these examples it has been seen that frequency modulation added to the chirp waveform degrades the target range response performance. As in the amplitude modulation case, sidebands close to the mainlobe degrade the range resolution and dynamic range for close targets. Moreover, the simulations showed that standard sidelobe suppression techniques using amplitude weighting does not have a significant effect on these sidebands.

#### 2.1.2.3 Amplitude and Frequency Modulation Treatment

As explained on the previous sections, amplitude and frequency modulation added to the chirp waveform at any point on the signal paths can greatly degrade the range resolution performance of FMCW radar systems. In addition, it has been shown that the effects caused by the frequency modulation on the chirp increase with the roundtrip delay. Thus, the design of FMCW radars with nominal ranges that correspond to large roundtrip delays relative to the chirp length should have more severe linearity requirements on the chirp waveform.

Amplitude modulation can be improved by using Variable Gain Amplifiers (VGAs). By measuring the resultant amplitude waveform at each path of the FMCW radar, the effects of amplitude modulation can be compensated using VGAs. By forcing an amplitude modulation with the inverse amplitude waveform of each path, the VGAs would compensate for the amplitude effects on each path.

The frequency and amplitude modulations may also be improved with digital signal processing (DSP). DSP techniques can be applied both in real-time and post processing. If there are measuring tools available to digitize the chirp waveform for each FMCW path, both the resulting amplitude and frequency modulation on the video signal may be estimated at any delay. This information can be used to correct the frequency and amplitude on the video signal. Unfortunately, digitizing tools for wideband radars are expensive and may not be available. For this case, the video signal can be digitized and used for processing. By measuring a single target response at the nominal delay, both the resulting amplitude and frequency modulation on the video signal can be extracted for the nominal delay. Then, the amplitude and frequency corrections can be applied on the data. Using the video signal to correct for modulation effects is not optimal due to the range dependent nature of the modulations.

Considering the drawbacks of the signal processing techniques and their limitations, the quality of the data of FMCW radar systems depends to a great extent on the hardware performance.

## 2.1.3 FMCW Waveform Generation and Frequency Synthesizers

FMCW waveforms generators use some kind of frequency synthesis which may include digital, analog or both techniques. This section describes direct frequency synthesis methods and synthesis methods requiring a voltage controlled oscillator (VCO).

## 2.1.3.1 Direct Analog Synthesis

A Direct Analog Synthesizer (DAS) generates a coherent wideband signal using only analog devices and no closed loop operations. A DAS uses a stable source such as a crystal oscillator and a variety of components for the application of arithmetic operations in the frequency domain of the source signal. A DAS may include a crystal oscillator, comb generators, frequency multipliers, frequency dividers, frequency mixers and filters [26].

By applying frequency operations to the source signal, very wideband frequency waveforms can be obtained. However, depending performance of the filters used, the frequency operations may add spurious noise to the signal. Thus, the synthesizer will be limited to a number of operations for a given spur level requirement. Since the DAS usually requires many components for the frequency operations, this type of synthesizer is often costly, bulky and has high power requirements [26].

### 2.1.3.2. Direct Digital Synthesis

A Direct Digital Synthesizer uses digital data processing blocks to generate a frequency or phase tunable output signal. The DDS has a phase accumulator, which is basically a digital ramp generator implemented with an address counter. The digital output of the address counter represents the current phase. On a frequency-tunable DDS, the update rate of the counter is controlled by a frequency tuning word that may vary with time. The tuning word defines the frequency of the output signal. The output of the phase accumulator then gets fed to a phase-toamplitude converter. Finally, a Digital-to-Analog converter takes the amplitude data to generate the analog signal [26][27].

Since the Nyquist Theorem indicates that at least two samples per cycle are required to reconstruct a waveform, the sampling rate should be at least twice that of the DDS output bandwidth. The DDS output signal spectrum contains images of the positive and negative frequency components of the fundamental spaced by multiples of the sampling frequency. The images that correspond to the negative component of the fundamental are considered the odd numbered images whereas the images from the positive component of the fundamental are the even numbered images. Thus, the first image corresponds to the first image of the negative component of the fundamental. The frequency spacing between these images becomes half of the sampling rate or the Nyquist Bandwidth. Then, a reconstruction filter may be used to filter frequencies on any of the images of the fundamental. Moreover, the power amplitude of the spectrum harmonics follows a sinc function envelope with nulls at multiples of the sampling rate. The main drawback of using frequencies on one of the images is the amount of attenuation caused by the sinc function envelope response [27].

DDS synthesizers have many advantages with respect to other synthesizers. DDS systems allow a high frequency tuning resolution. The digital nature of a DDS makes it independent of aging and temperature drift, common on analog devices. However, the DDS signal output bandwidth is limited by the reference clock. DDS systems are considered a very good choice for chirp generators with bandwidth lower than half the sampling rate [27].

As of the October 2011, the digital to analog data converters with highest sampling rate available in the market are the MAX5881, the AD9739A and the DAC5670-SP with 4.3 Giga Samples per Second (GSPS), 2.5 GSPS and 2.4 GSPS respectively. These three products are manufactured by Maxim Integrated Products, Analog Devices Inc. and Texas Instruments Inc, respectively. Thus, the maximum bandwidth attained for a synthesizer with available data converters is less than 2.15 GHz.

### 2.1.3.3 Phase Lock Loops and other VCO based Frequency Synthesizers

As mentioned previously, digital synthesize is mainly limited by bandwidth and direct analog synthesis by its spurious performance, power requirements and cost. As alternative to these techniques, a common indirect wideband synthesizer uses a wideband voltage controlled oscillator on a frequency control loop also known as a Phase Lock Loop (PLL). A PLL-based synthesizer uses a direct synthesizer as the reference signal. A description of the PLL system and its components is given in Section 2.2.

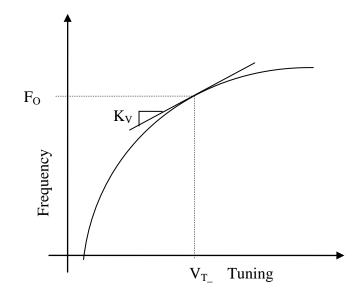

An FMCW signal with the desired frequency waveform can be implemented by controlling the tuning voltage of the VCO, as will be discussed in Section 2.2.2. The tuning characteristic is the curve that describes the mapping between the tuning voltage and the output frequency. Since this relationship is nonlinear, a ramp voltage input will not output a linear frequency modulated output as it is required for chirp-based FMCW radars. Then, either an open loop or a closed loop system should be used to control the tuning voltage to output the required waveform.

Different open loop techniques have been implemented to linearize the VCO output depending on the resources available at the time.

Burke P.E. implemented an open loop VCO linearization technique based on a circuit realization of a pre-distorted voltage [28]. The system uses a third order polynomial function generator based on a voltage controlled voltage ramp generator. The ramp slope, which corresponds to the first polynomial coefficient, is controlled both externally and by a feedback signal. The quadratic and cubic terms are outputted by a quadratic and a cubic generator respectively. These two terms are added to the ramp, where the second and third polynomial coefficients are given by the potentiometers used for the adder. Thus, the system works as a polynomial regression system that tries to generate the required non-linear tuning voltage to match that of the inverse function of the tuning characteristic. The system also uses a PLL synchronized to the chirp repetition rate to maintain a coherent output.

Since wideband voltage controlled oscillators have tuning characteristics with several small variations, a polynomial fitting that matches exactly the inverse function would require

several coefficients. Moreover, the number of coefficients that can be implemented is limited by the circuit and coefficient calibration complexity.

An example of an earlier open loop linearization technique implemented at the CReSIS is described on [29]. The linearization technique uses a frequency counter to measure the output frequency to discrete input voltages. The measured relationship between voltage and output frequency of the VCO is then used to find the inverse function. Lastly, the inverse function is directly applied to the VCO [29]. This technique has many drawbacks. First, in order to account for small variations in the VCO tuning curve, the measurement should be made with very small voltage steps. Since many measurement repetitions are taken and averaged to account for time variations, it would require a very long time to take all the necessary measurements. Moreover, this technique takes static measurements of the output frequency. However, the tuning characteristic of the VCO for static voltages may not be the same as that for a ramp input voltage. The tuning characteristic may even vary for different chirp rates.

Closed loop techniques have also been implemented to linearize the output frequency of the voltage controlled oscillator. By using a phase lock loop, as explained previously, the output frequency of the VCO may follow a multiple of the reference frequency. A PLL based chirp generator previously developed at CReSIS is described on [30]. This system uses a third order type 2 PLL. The type 2 nature of the PLL implemented with a differential amplifier makes it possible to achieve all the required voltage levels for the designed amplifier bandwidth. A differential amplifier is used for error compensation as well as for driving the VCO. This technique was demonstrated as part of a microwave altimeter operating with 1 GHz of bandwidth. The performance of the chirp generator using this implementation suffered from high range sidelobes for bandwidths larger than 1 GHz. Since not enough considerations were taken to improve the tracking performance of the synthesizer, the PLL designed was not able to compensate for the VCO nonlinearity using higher chirp bandwidths.

# **2.2 PHASE LOCK LOOP OVERVIEW**

This section discusses the analysis of phase lock loops using linear system techniques. It also describes the functionality of the main PLL components as to determine their system response.

#### 2.2.1 PLL Analysis as a Linear System

A Phase Lock Loop (PLL) is a Frequency and Phase control system. Linear control system techniques can be used to analyze linear time invariant control systems. Each linear system is represented with a transfer function, which is the Laplace transform of the output to input ratio [31]. Since the VCO has a non-linear input-output relationship, as will be explained, a PLL system may be considered a non-linear control system. However, it can be approximated to be linear over a narrow bandwidth of the VCO. Also, the response of most devices will vary with time due to temperature and aging. These changes will not be significant and will be neglected for the analysis. Applying these linear approximations, the PLL may be analyzed using linear control system theory.

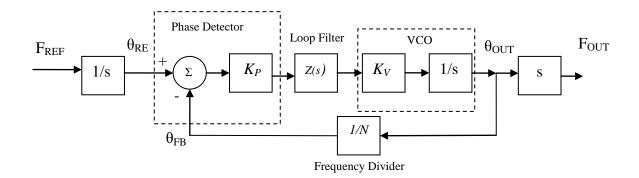

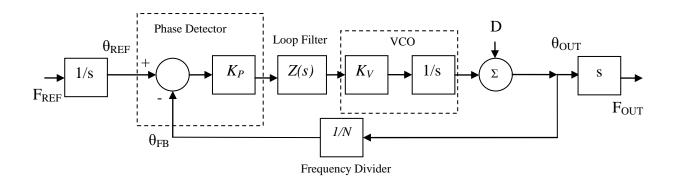

A PLL is composed of essentially three components: the phase detector, the loop filter and the Voltage controlled Oscillator (VCO). Frequency synthesizers based on PLLs use a frequency divider in the feedback path to output a multiple of the reference frequency. Figure 2-13 shows a linear system block diagram of a simple PLL.

Figure 2-13: Block Diagram of PLL Transfer Function

When the PLL is in the lock state, the output phase tracks the input phase. Either a change in the input phase or a change in the output phase is sensed by the phase detector. The phase detector outputs a signal which average is proportional to the phase difference between the input signal and the feedback signal. The phase detector gain is symbolized by  $K_P$ . The functionality of the phase detector is further explained in Section 2.2.2.2.

$K_V$  represents the voltage-to-frequency conversion gain of the VCO, also known as the frequency sensitivity of the VCO. The frequency divider block shows the division factor equal to N. Z(s) corresponds to the transfer function of the PLL compensator, also known as the PLL loop filter. The use of the letter Z for the loop filter transfer function comes from the fact that the typical charge pump PLLs use trans-impedance loop filters. However, the letter Z will be used throughout this document regardless the type of input signal of the loop filter.

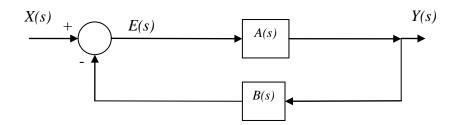

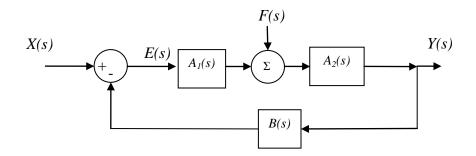

Equations (2.32) through (2.35) show the forward path A(s), feedback path B(s), open loop G(s) and closed loop H(s) transfer functions for the PLL described in Figure 2-13.

$$A(s) = \frac{K_P \cdot Z(s) \cdot K_V}{s}$$

(2.32)

$$B(s) = \frac{1}{N} \tag{2.33}$$

$$G(s) = A(s)B(s) = \frac{K_P \cdot Z(s) \cdot K_V}{s \cdot N}$$

(2.34)

$$H(s) = \frac{A(s)}{1 + A(s)B(s)} = \frac{\frac{K_p \cdot Z(s) \cdot K_v}{s}}{1 + \frac{K_p \cdot Z(s) \cdot K_v}{s \cdot N}} = N \cdot \frac{\frac{K_p \cdot Z(s) \cdot K_v}{N}}{s + \frac{K_p \cdot Z(s) \cdot K_v}{N}}$$

(2.35)

The open loop gain transfer function is the product of the forward and feedback paths transfer functions [31]. The closed loop transfer function is then solved to the standard negative feedback loop equation shown on equation (2.35) [31][32]. An effective closed loop control system has more poles than zeros and its frequency response resembles that of a low-pass filter [31][33]. By inspection of equation (2.35), the closed loop transfer function of the PLL has a

gain equal to the division factor (N) over its pass band. The PLL impulse response is the Laplace inverse transform of the closed loop transfer function. The step, ramp and parabola responses may also be calculated by integrating the designed closed loop transfer function. The closed loop transfer function may be designed to fit the transfer function of a specific function. For instance, a Gaussian response is used to design a fast settling type 2 PLL on [34].

The linear approximation used to apply linear system analysis techniques to PLLs assumes a constant value for the VCO sensitivity ( $K_V$ ). This is not the case for wideband applications. Therefore, the time performance of the PLL will also vary with respect to the output frequency. Thus, the PLL should be designed such that an acceptable time response is maintained for all possible values of  $K_V$ .

## 2.2.1.1 Type and Order of a PLLs

The type of a transfer function refers to the number of integrators or poles at the origin. In the PLL terminology, the type of the PLL refers to the type of the open loop transfer function and not the closed loop transfer function [35].

The order of a transfer function refers to the number of poles. Similar to the type, the order of the PLL is the order of the open loop transfer function.

#### 2.2.1.2 Transient Response and Stability of PLLs

Instability in a control system occurs when the open loop transfer function equals negative 1 [31]. This means that the open loop gain equals 0 dB at -180 degrees. Even though the open loop does not reach this point, there are parameters that measure the degree of stability. The phase margin indicates the difference between the open loop phase and -180 degrees when the gain crosses 0 dB. Similarly, the gain margin is the gain of the open loop at -180 degrees [31]. The former occurs at the gain crossover frequency and the latter at the phase crossover

frequency. The gain crossover frequency will be referred to as only the crossover frequency on this document.

Designs where the PLL open loop crosses the phase crossover frequency more than once are rarely found. According to the Bode stability criterion, the system is stable if the open loop gain is less than 0 dB over the phase crossover frequency [31]. Thus, the Bode stability criterion can be used to claim stability on a PLL.