## Marquette University e-Publications@Marquette

Dissertations (2009 -)

Dissertations, Theses, and Professional Projects

# Dynamic Lifetime Reliability and Energy Management for Network-on-Chip based Chip Multiprocessors

Milad Ghorbani Moghaddam Marquette University

#### Recommended Citation

Ghorbani Moghaddam, Milad, "Dynamic Lifetime Reliability and Energy Management for Network-on-Chip based Chip Multiprocessors" (2018). *Dissertations* (2009 -). 834. https://epublications.marquette.edu/dissertations\_mu/834

# DYNAMIC LIFETIME RELIABILITY AND ENERGY MANAGEMENT FOR NETWORK-ON-CHIP BASED CHIP MULTIPROCESSORS

by

Milad Ghorbani Moghaddam, B.S., M.S.

A Dissertation Submitted to the Faculty of the Graduate School, Marquette University, in Partial Fulfillment of the Requirements for the Doctor of Philosophy

Milwaukee, Wisconsin

December 2018

#### ABSTRACT

# DYNAMIC LIFETIME RELIABILITY AND ENERGY MANAGEMENT FOR NETWORK-ON-CHIP BASED CHIP MULTIPROCESSORS

#### Milad Ghorbani Moghaddam, B.S., M.S. Marquette University

In this dissertation, we study dynamic reliability management (DRM) and dynamic energy management (DEM) techniques for network-on-chip (NoC) based chip multiprocessors (CMPs). In the first part, the proposed DRM algorithm takes both the computational and the communication components of the CMP into consideration and combines thread migration and dynamic voltage and frequency scaling (DVFS) as the two primary techniques to change the CMP operation. The goal is to increase the lifetime reliability of the overall system to the desired target with minimal performance degradation. The simulation results on a variety of benchmarks on 16 and 64 core NoC based CMP architectures demonstrate that lifetime reliability can be improved by 100% for an average performance penalty of 7.7% and 8.7% for the two CMP architectures. In the second part of this dissertation, we first propose novel algorithms that employ Kalman filtering and long short term memory (LSTM) for workload prediction. These predictions are then used as the basis on which voltage/frequency (V/F) pairs are selected for each core by an effective dynamic voltage and frequency scaling algorithm whose objective is to reduce energy consumption but without degrading performance beyond the user set threshold. Secondly, we investigate the use of deep neural network (DNN) models for energy optimization under performance constraints in CMPs. The proposed algorithm is implemented in three phases. The first phase collects the training data by employing Kalman filtering for workload prediction and an efficient heuristic algorithm based on DVFS. The second phase represents the training process of the DNN model and in the last phase, the DNN model is used to directly identify V/F pairs that can achieve lower energy consumption without performance degradation beyond the acceptable threshold set by the user. Simulation results on 16 and 64 core NoC based architectures demonstrate that the proposed approach can achieve up to 55% energy reduction for 10% performance degradation constraints. Simulation experiments compare the proposed algorithm against existing approaches based on reinforcement learning and Kalman filtering and show that the proposed DNN technique provides average improvements in energy-delay-product (EDP) of 6.3% and 6% for the 16 core architecture and of 7.4% and 5.5% for the 64 core architecture.

#### ACKNOWLEDGEMENTS

Milad Ghorbani Moghaddam, B.S., M.S.

I would like to sincerely thank my advisor Dr. Cristinel Ababei who was the most impactful person throughout my Ph.D. study at Marquette University. I will always be grateful for his advice and encouragement, which were essential to the completion of this dissertation. I would like to thank him not only for helping me with his tremendous academic support, knowledge, trust and encouragement, but also for sharing his compassionate advice and experience that motivated me to take more professional steps in my future life. I cannot thank him enough for all his support and devotion throughout my study.

I would also like to thank Dr. Richard Povinelli, Dr. Henry Medeiros and Dr. Iqbal Ahmed for serving on my committee, reviewing my dissertation and providing very helpful suggestions that enriched the quality of my dissertation.

My gratitude expands to Dr. Fabian Josse, Dr. Edwin Yaz, Dr. Majeed Hayat, Dr. James Richie, Dr. Susan Schneider, Mrs. Katie Tarara and all the members of the department of Electrical and Computer Engineering for their guidance and support during my study at Marquette University.

I would like to express my gratitude to all my friends at Marquette University, specially my colleagues at Marquette Embedded Systems Lab (MESSLab): Wenkai Guan, Nathan Zimmerman, Kellen Carey, Ian Barge, Shaun Duerr and Alim Ahsan for all their help and possitive feedback.

I would also like to thank Dr. Kiarash Bazargan, in the department of Electrical and Computer Engineering of University of Minnesota, whose support, guidance and recommendations opened a new window to my future.

Most importantly, I'm grateful beyond words to my mother and father and my brothers, Mehrad and Masoud, who are the most important people in my world and I cannot thank them enough for all their support, positive thoughts, patience and understanding in each moments of my life. I sincerely dedicate my dissertation to them.

## TABLE OF CONTENTS

| ACKN   | OWLEDGEMENTS                                           | i |

|--------|--------------------------------------------------------|---|

| TABLI  | E OF CONTENTS                                          | i |

| LIST ( | OF TABLES                                              | V |

| LIST ( | OF FIGURES                                             | V |

| LIST ( | OF NOMENCLATURE AND ACRONYMS                           | X |

| CHAP   | TER 1 Problem Statement, Objective and Contributions . | 1 |

| 1.1    | Problem statement                                      | 1 |

| 1.2    | Objectives                                             | 3 |

| 1.3    | Related Work                                           | 3 |

|        | 1.3.1 Reliability Management Techniques                | 4 |

|        | 1.3.2 Energy Management Techniques                     | 8 |

| 1.4    | Contributions                                          | 3 |

|        | 1.4.1 Dynamic Reliability Management                   | 3 |

|        | 1.4.2 Dynamic Energy Management                        | 4 |

| 1.5    | Dissertation Organization                              | 6 |

| 1.6    | Related Publications                                   | 7 |

| CHAP   | TER 2 Background                                       | 9 |

| 2.1    | Aging Mechanisms                                       | 9 |

|        | 2.1.1 Time Dependant Dielectric Breakdown              | 9 |

|        | 2.1.2 Negative bias temperature instability            | 1 |

| 2.2    | Reliability Estimation Tool                            | 3 |

| 2.3    | Kalman Filtering                                       | 6 |

| 2.4    | Neural Networks                                        | 9 |

|        | 2.4.1 Feed-Forward Neural Networks                     | 0 |

|        | 2.4.2 Recurrent Neural Networks                        | 2 |

|        | 2.4.3 Long Short Term Memory                           | 3 |

|        | 2.4.4 Deep Neural Networks                             | 3 |

| CHAP | TER 3  | B Proposed Dynamic Reliability Management        | 36  |

|------|--------|--------------------------------------------------|-----|

| 3.1  | Introd | luction                                          | 36  |

| 3.2  | DVFS   | based Technique                                  | 36  |

| 3.3  | Hybric | d DVFS and Thread Migration based Technique      | 40  |

| 3.4  | Simula | ation Results                                    | 46  |

|      | 3.4.1  | Simulation Setup                                 | 47  |

|      | 3.4.2  | DVFS based Technique                             | 50  |

|      | 3.4.3  | Hybrid DVFS and Thread Migration based Technique | 53  |

| 3.5  | Discus | ssion                                            | 56  |

| CHAP | TER 4  | 4 Proposed Dynamic Energy Management             | 62  |

| 4.1  | Introd | luction                                          | 62  |

| 4.2  | Delaye | ed Instruction Count Performance Estimation      | 62  |

| 4.3  | Kalma  | an Filtering based Technique                     | 68  |

| 4.4  | LSTM   | I based Technique                                | 71  |

| 4.5  | Dynar  | nic Energy Management using DNN                  | 73  |

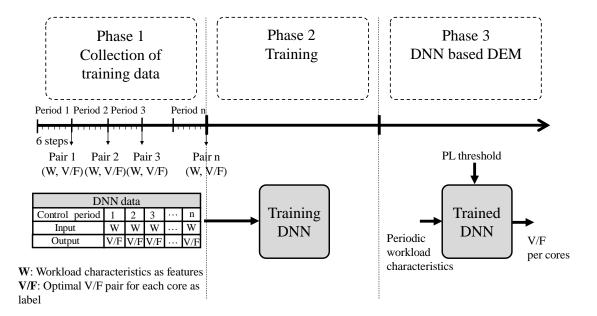

|      | 4.5.1  | Phase 1: Collection of Training Data             | 77  |

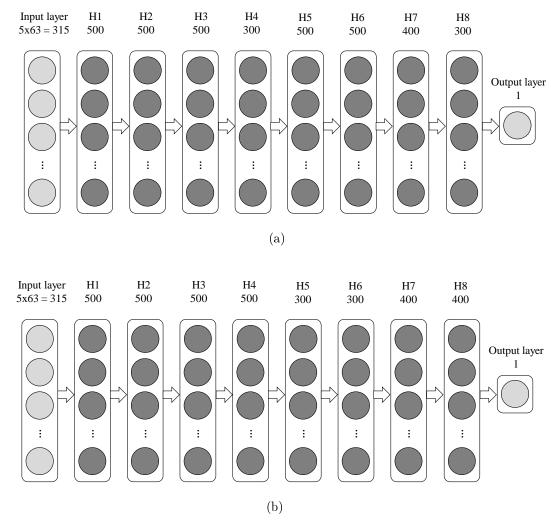

|      | 4.5.2  | Phase 2: Training of the DNN Model               | 80  |

|      | 4.5.3  | Phase 3: Prediction Using the DNN Model          | 81  |

| 4.6  | Simula | ation Results                                    | 81  |

|      | 4.6.1  | Simulation Setup                                 | 82  |

|      | 4.6.2  | Kalman Filtering based Technique                 | 83  |

|      | 4.6.3  | LSTM based Technique                             | 93  |

|      | 4.6.4  | Dynamic Energy Management using DNN              | 94  |

| 4.7  | Discus | ssion                                            | 104 |

| CHAP | TER 5  | 5 Conclusion and Future Work                     | 112 |

| REFE | RENC   | ES                                               | 115 |

## LIST OF TABLES

| 3.1 | Architectural configuration parameters                               | 50  |

|-----|----------------------------------------------------------------------|-----|

| 3.2 | Summary of simulations shown in Fig. $3.9 - \text{Fig. } 3.11 \dots$ | 53  |

| 4.1 | Architectural configuration parameters                               | 82  |

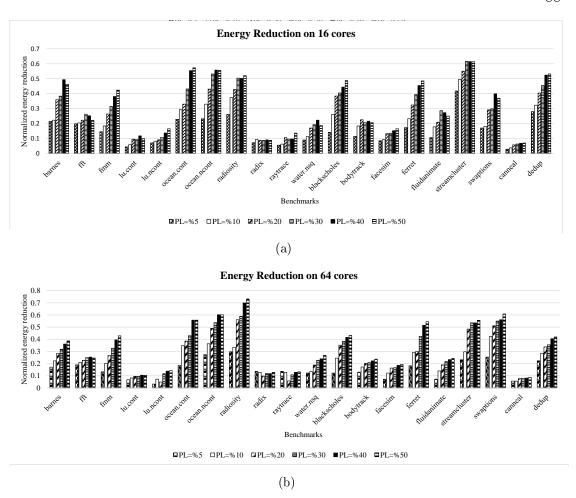

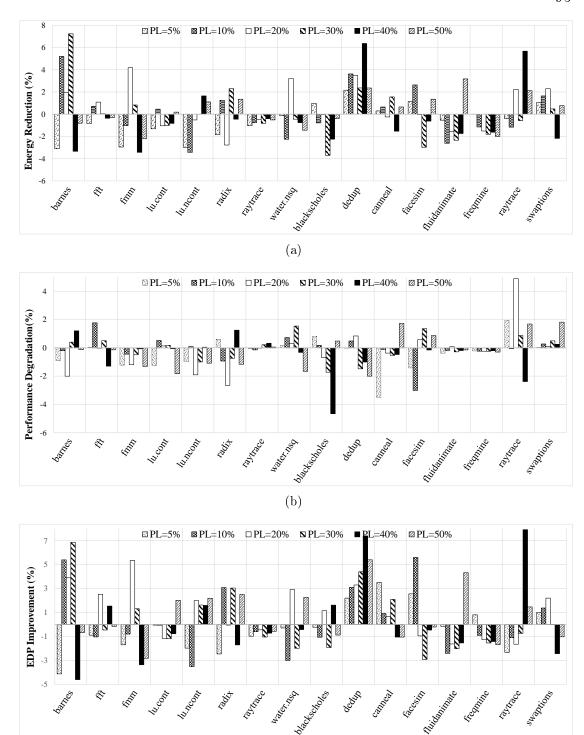

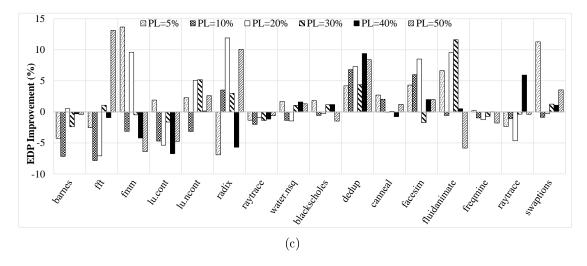

| 4.2 | Average EDP improvement of data from Fig. 4.15.c and Fig. 4.16.c $$  | 94  |

| 4.3 | Average EDP improvement of data from Fig. 4.17.c and Fig. 4.18.c $$  | 97  |

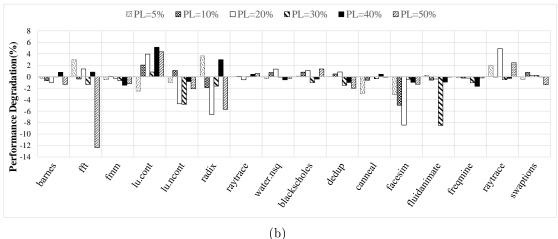

| 4.4 | Average improvement in terms of EDP values                           | 106 |

# LIST OF FIGURES

| 1.1 | A taxonomy of approaches employed in energy and reliability management techniques.                                                                                                                                                                                                                                                                                                                                                                                                                            | 4  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

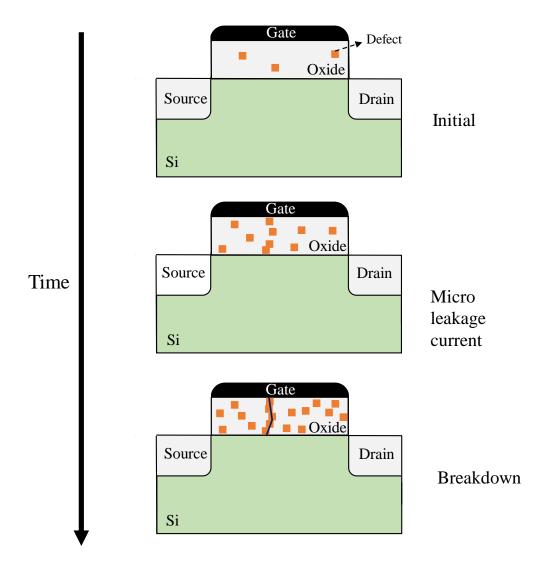

| 2.1 | Time dependent dielectric breakdown process                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 21 |

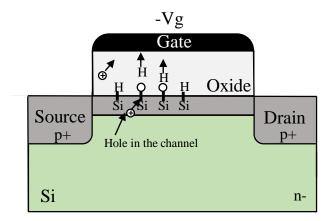

| 2.2 | Negative bias temperature instability process                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 22 |

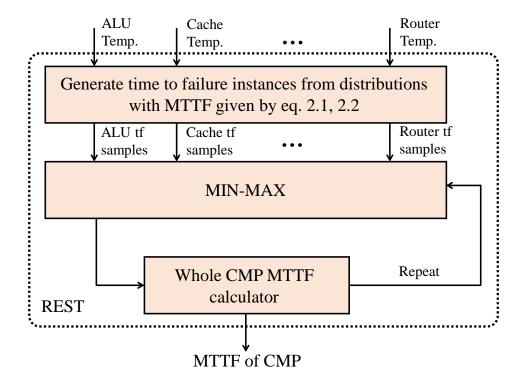

| 2.3 | Block diagram of the Monte Carlo simulation based time to failure evaluation methodology for CMPs                                                                                                                                                                                                                                                                                                                                                                                                             | 24 |

| 2.4 | Pseudocode description of the Monte Carlo simulation implemented by the reliability estimation, REST tool                                                                                                                                                                                                                                                                                                                                                                                                     | 26 |

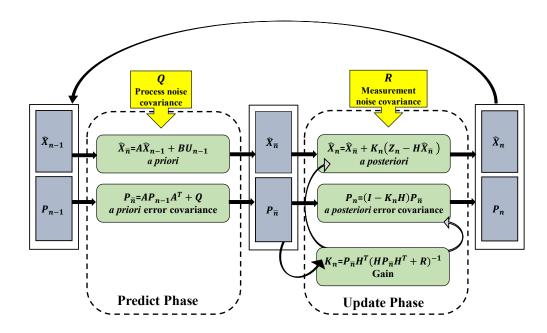

| 2.5 | Kalman filter predict phase and update phase procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29 |

| 2.6 | Typical neural network architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31 |

| 2.7 | Simplified diagram of a recurrent neural network                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 32 |

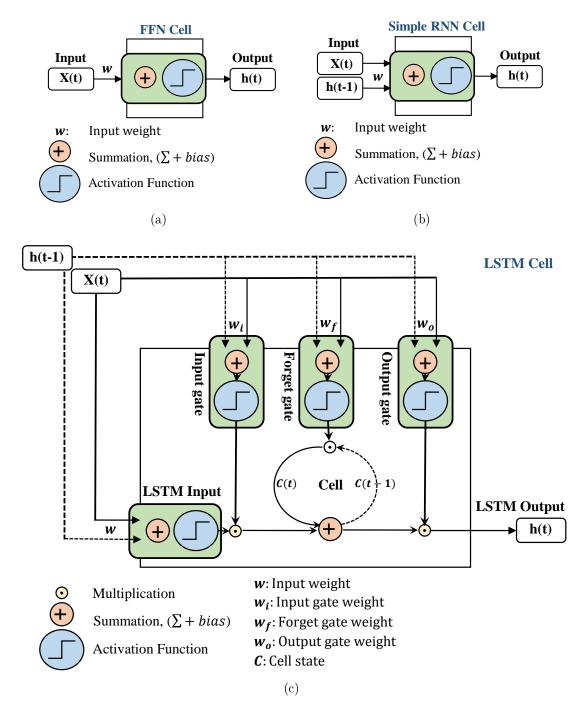

| 2.8 | Simplified diagrams of three different cells (a) feedforward NN cell, (b) RNN ell, and (c) LSTM cell                                                                                                                                                                                                                                                                                                                                                                                                          | 34 |

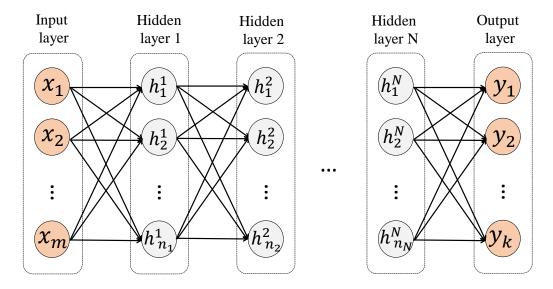

| 2.9 | A deep neural network is a neural network with many hidden layers                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35 |

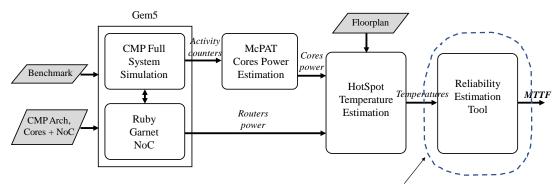

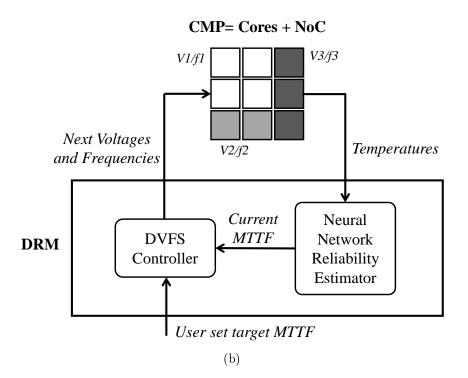

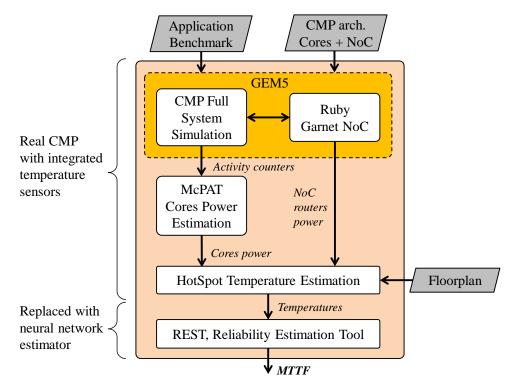

| 3.1 | (a) Block diagram of complete flow to <i>statically</i> estimate lifetime reliability (measured as MTTF) of the whole system as combination of cores plus network-on-chip, (b) The proposed dynamic reliability management scheme uses DVFS controller to set voltages and frequencies of individual tiles in the next control period such that <i>current</i> MTTF approaches <i>target</i> MTTF. The CMP systems is composed of a number of tiles. A tile is the combination of one core and one NoC router | 38 |

| 3.2 | Pseudocode of the DVFS based DRM scheme. This control algorithm is implemented as a callable routine inside the Gem5 simulation framework. Parameters $\delta$ and $\gamma$ can be set by user to allow for calibration of how $aggressive$ the DRM policy is                                                                                                                                                                                                                                                 | 40 |

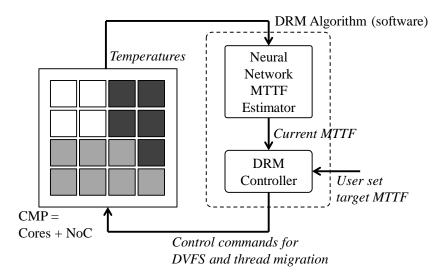

| 3.3 | The proposed dynamic reliability management algorithm has two components, the MTTF online estimator and the DRM controller. The CMP is composed of a number of tiles and each tile contains a core and a NoC router                                                                                                                                                                                                                                                                                           | 41 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

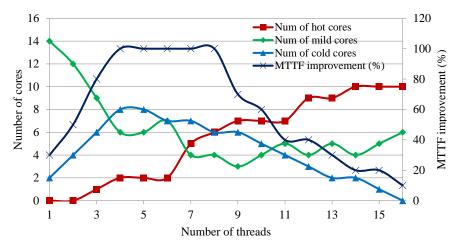

| 3.4  | Plot showing the amount of MTTF improvement using a thread migration based DRM scheme over the reference case when no DRM scheme is used at all. A tile is denoted as cold if its temperature $T < 40^{\circ}C$ , as mild if $40^{\circ}C \leq T \leq 60^{\circ}C$ , and hot if $T > 60^{\circ}C$ .                                                                                                                                               | 44 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.5  | Pseudocode of the proposed DRM algorithm. In our experiments, this algorithm is implemented as a callable routine inside the Gem5 simulation framework. Parameters $\delta$ , $\gamma$ , and $K$ can be set by the user to allow for calibration of how $aggressive$ the DRM strategy is. The thread migration and DVFS techniques are described in Fig. 3.6 and Fig. 3.7. The values 0.8 and 1.2 were found empirically to provide good results. | 45 |

| 3.6  | Pseudocode of routine describing the thread migration technique called by the proposed DRM algorithm from Fig. 3.5                                                                                                                                                                                                                                                                                                                                | 47 |

| 3.7  | Pseudocode of routine describing the DVFS technique called by the proposed DRM algorithm from Fig. 3.5                                                                                                                                                                                                                                                                                                                                            | 47 |

| 3.8  | Block diagram of the complete simulation framework to simulate a given application benchmark and to estimate lifetime reliability, measured as MTTF, of the entire system as combination of cores plus network-on-chip. Note that when the REST tool is replaced by the neural network MTTF estimator, supply voltages are also provided together with temperatures as inputs to the estimator.                                                   | 48 |

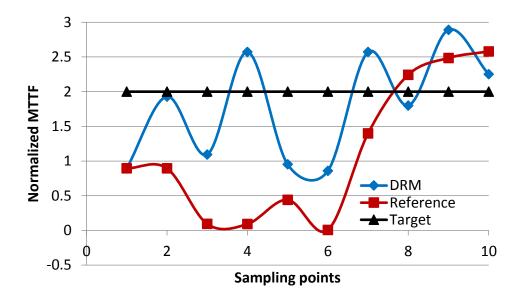

| 3.9  | Gem5 with DVFS based DRM simulation of $blackscholes$ benchmark                                                                                                                                                                                                                                                                                                                                                                                   | 51 |

| 3.10 | Gem5 with DVFS based DRM simulation of canneal benchmark                                                                                                                                                                                                                                                                                                                                                                                          | 52 |

| 3.11 | Gem5 with DVFS based DRM simulation of $bodytrack$ benchmark                                                                                                                                                                                                                                                                                                                                                                                      | 52 |

| 3.12 | Gem5 with DVFS based DRM simulation of $dedup$ benchmark                                                                                                                                                                                                                                                                                                                                                                                          | 53 |

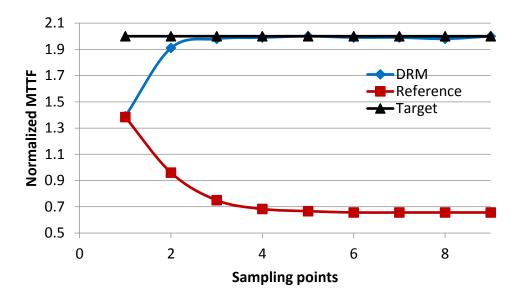

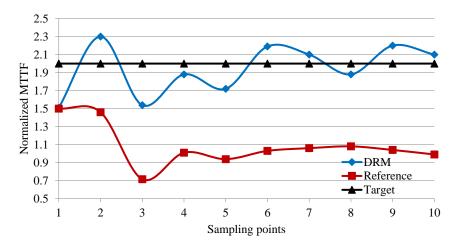

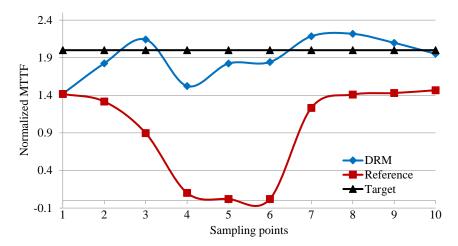

| 3.13 | Simulation results for $blackscholes$ benchmark on an architecture with $4 \times 4$ tiles (i.e., 16 cores). Similar results were obtained for the other benchmarks                                                                                                                                                                                                                                                                               | 55 |

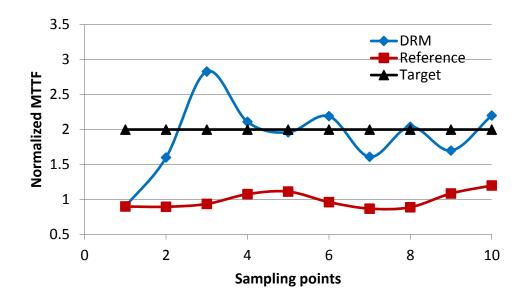

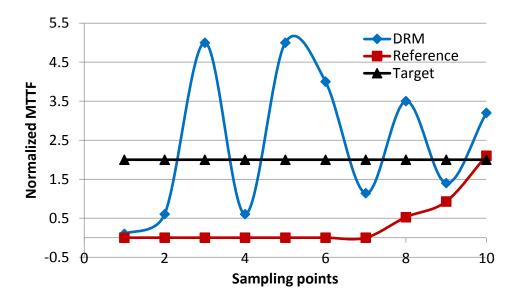

| 3.14 | Simulation results for <i>cholesky</i> benchmark on an architecture with $8 \times 8$ tiles (i.e., 64 cores). The MTTF of the reference case improves in the second part of the ROI because the actual workload decreases (some threads finish much earlier) for this particular benchmark                                                                                                                                                        | 56 |

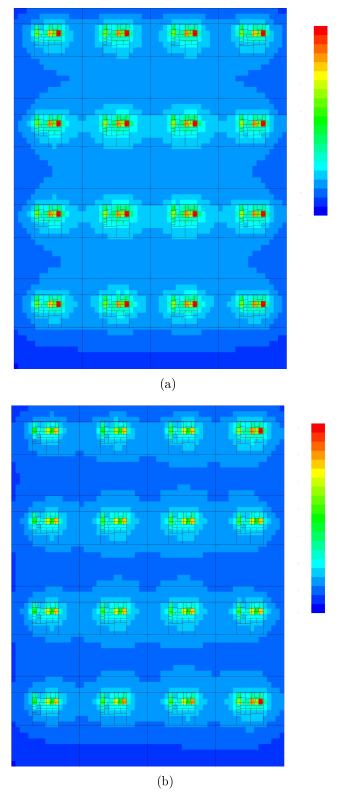

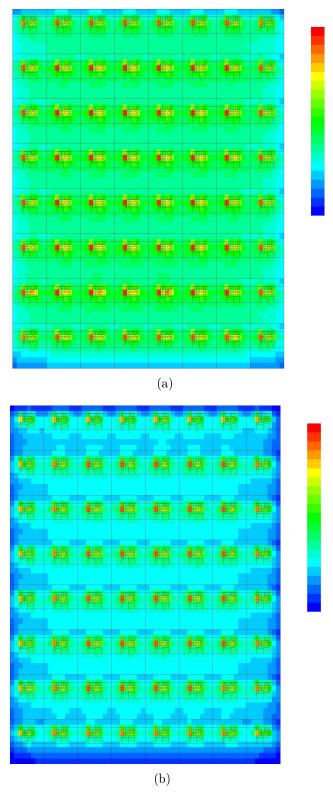

| 3.15 | (a) Thermal profile of the $4 \times 4$ CMP architecture running blackscholes benchmark with no DRM algorithm, (b) Thermal profile of the same architecture when the proposed DRM algorithm is used. The color-coded temperature range is $20^{\circ}C$ (blue) to $120^{\circ}C$ .                                                                                                                                                                | 57 |

| 3.16 | (a) Thermal profile of the 8 × 8 CMP architecture running <i>cholesky</i> benchmark with no DRM algorithm, (b) Thermal profile when the proposed DRM algorithm is used                                                                                                        | 58 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

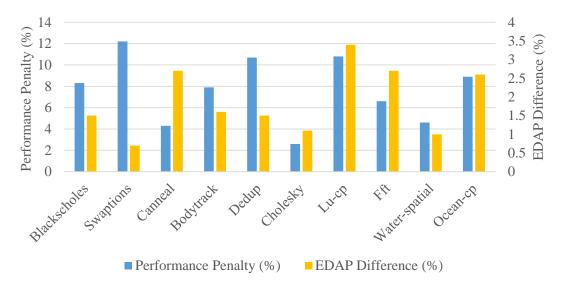

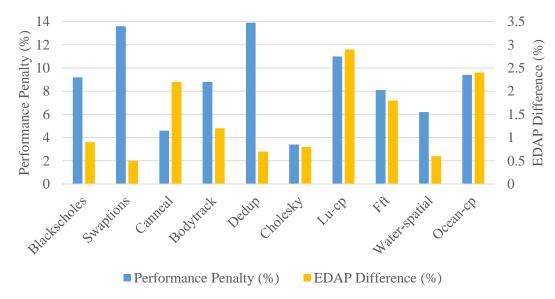

| 3.17 | Summary of simulations results for $4 \times 4$ CMP architecture for a target MTTF improvement of 100% (i.e., double lifetime). Each data point is the average of all values obtained during the hold times or sampling points illustrated in Fig. 3.13 for a given benchmark | 59 |

| 3.18 | Summary of simulations results for $8 \times 8$ CMP architecture for a target MTTF improvement of $100\%$                                                                                                                                                                     | 59 |

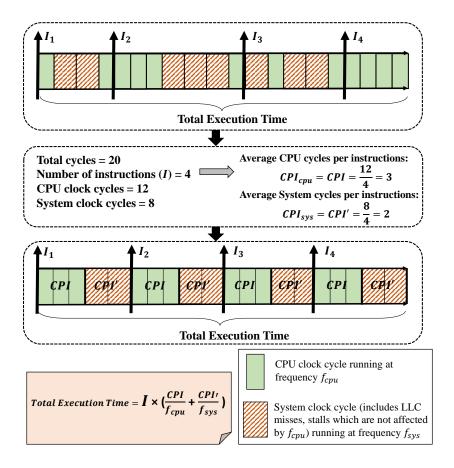

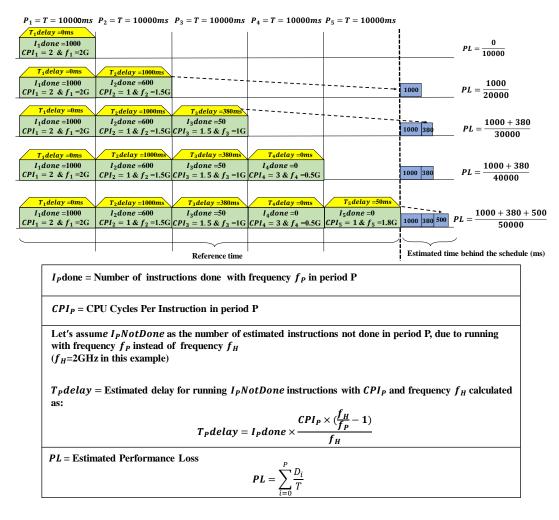

| 4.1  | Example utilized to illustrate the two different average cycles per instruction, $CPI$ and $CPI'$ , which are used to estimate the total execution time                                                                                                                       | 64 |

| 4.2  | Example utilized to illustrate the estimation of total performance loss (PL) so far, up to and including the currently completed control period and just before the start of a new control period for a given core                                                            | 65 |

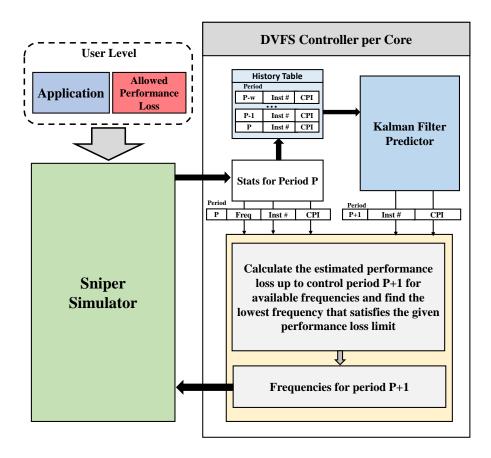

| 4.3  | Block diagram of the proposed DVFS based dynamic energy management (DEM) scheme as implemented inside our custom Sniper simulator.                                                                                                                                            | 69 |

| 4.4  | Pseudocode of the DVFS algorithm. This control algorithm is implemented as a callable routine inside our modified Sniper CMP simulator. It corresponds to the block at the bottom in Fig. 4.3. The parameter $\alpha$ is set by the user                                      | 70 |

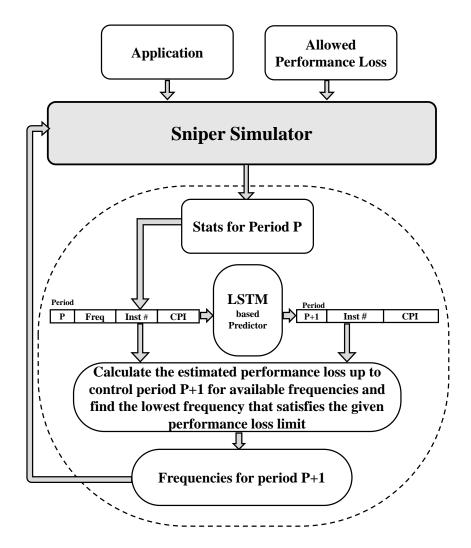

| 4.5  | Block diagram of the DVFS based dynamic energy management scheme as implemented inside our custom Sniper simulator                                                                                                                                                            | 72 |

| 4.6  | Pseudocode of the<br>LSTM based algorithm. This algorithm is implemented as a callable routine inside our modified Sniper CMP simulator. The parameter<br>$\gamma$ is set by the user                                                                                         | 74 |

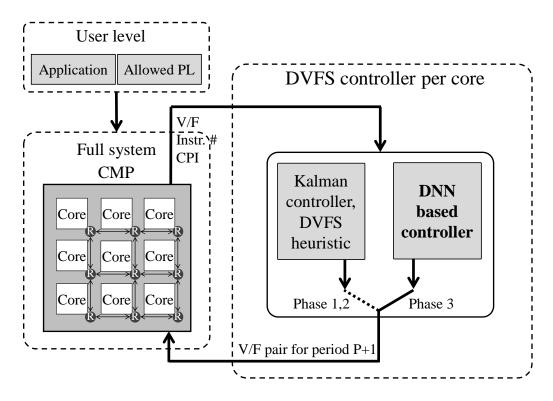

| 4.7  | The proposed dynamic energy optimization algorithm switches to DNN based prediction once the DNN model has been constructed. The Kalman filtering based controller block operates similarly to that in Fig. 4.3                                                               | 75 |

| 4.8  | Illustration of the three phases of the implementation and usage of the DNN model                                                                                                                                                                                             | 77 |

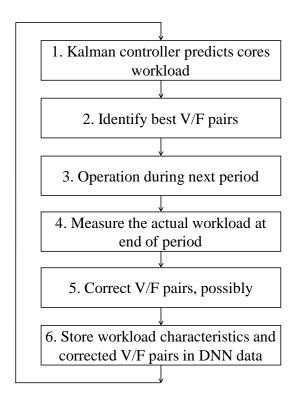

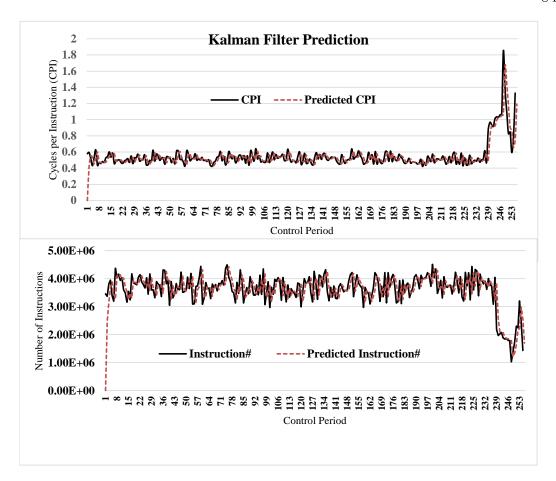

| 4.9  | Steps of the procedure to generate one training data point during one control period in Phase 1                                                                                                                                                                               | 78 |

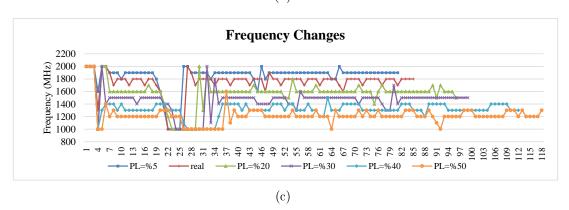

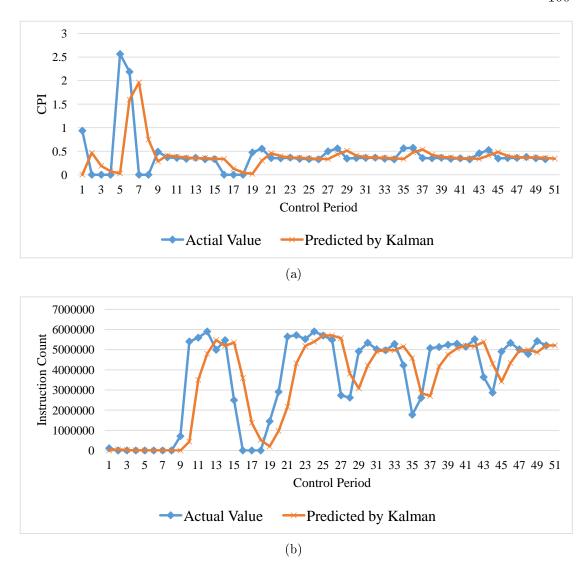

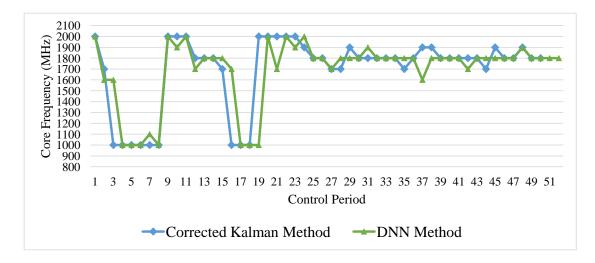

| 4.10 | and the instruction count for the next control period and the actual values that occurred and were observed at the end of the next control period. These traces are for a sample core (out of 64 cores) during the execution of radiosity benchmark                                                 | 84  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.11 | Simulation results for a sample run of the <i>barnes</i> benchmark. The x axis represents the index of the control periods. Note that when the frequency is higher, the total execution time, measured as <i>walltime</i> , is shorter and therefore the total number of control periods is smaller | 87  |

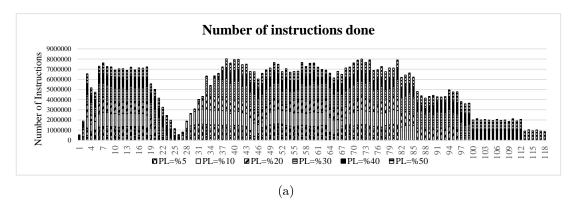

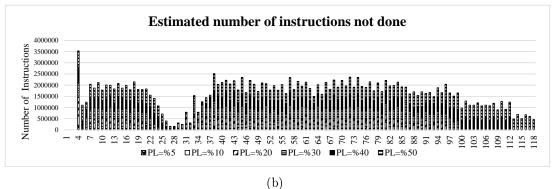

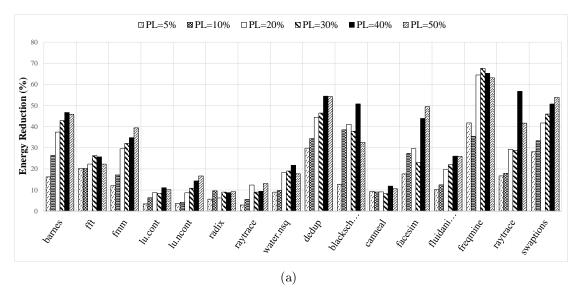

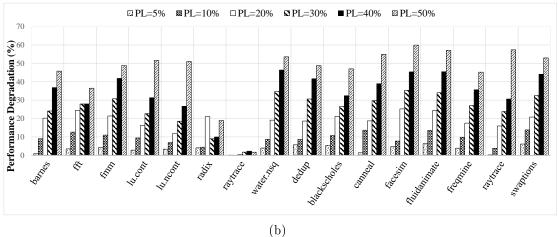

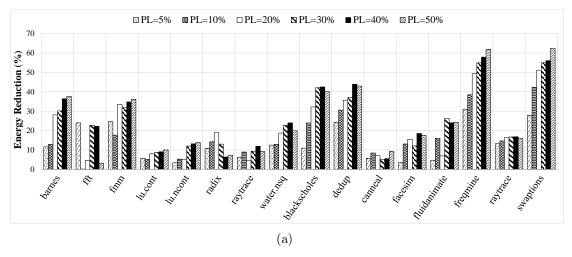

| 4.12 | Energy reduction percentages. (a) 16 core architecture with 4x4 mesh NoC. (b) 64 core architecture with 8x8 mesh NoC                                                                                                                                                                                | 88  |

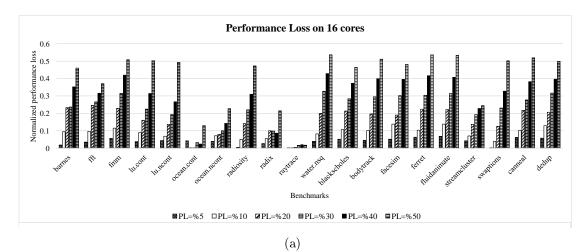

| 4.13 | Performance loss percentages. (a) 16 core architecture with 4x4 mesh NoC. (b) 64 core architecture with 8x8 mesh NoC                                                                                                                                                                                | 89  |

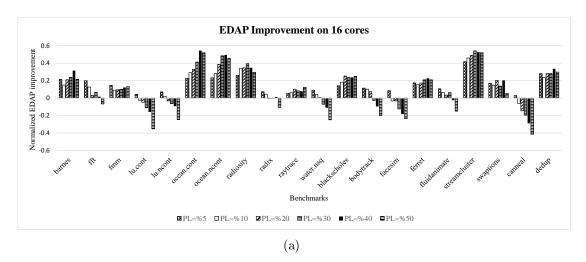

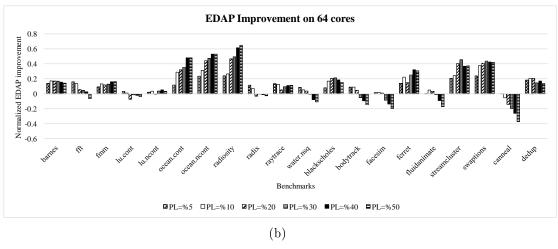

| 4.14 | Energy Delay Area Product (EDAP) percentages. (a) 16 core architecture with 4x4 mesh NoC. (b) 64 core architecture with 8x8 mesh NoC                                                                                                                                                                | 90  |

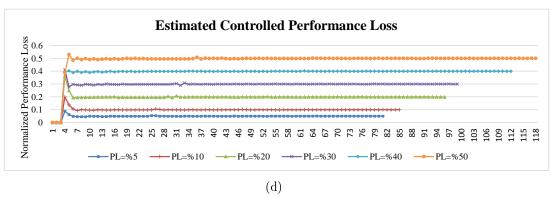

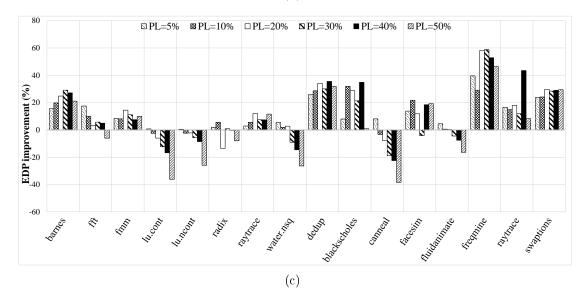

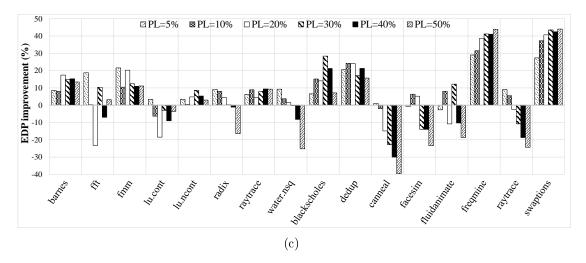

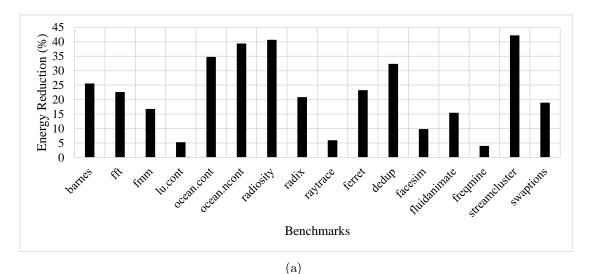

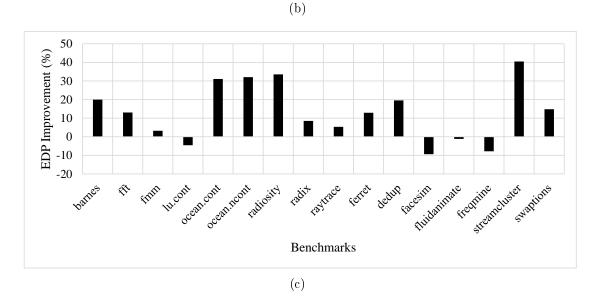

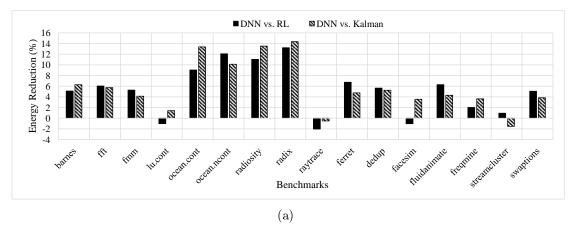

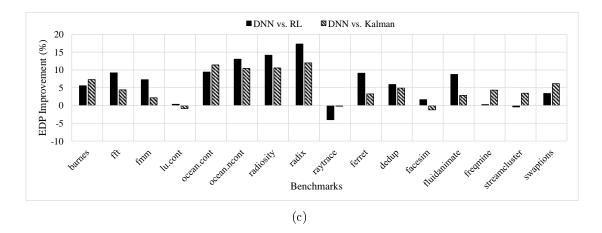

| 4.15 | Simulation results for the 16 core CMP: (a) energy reduction percentages, (b) performance degradation percentages, and (c) EDP improvement percentages. Comparison is done versus the case when no DEM is used.                                                                                     | 91  |

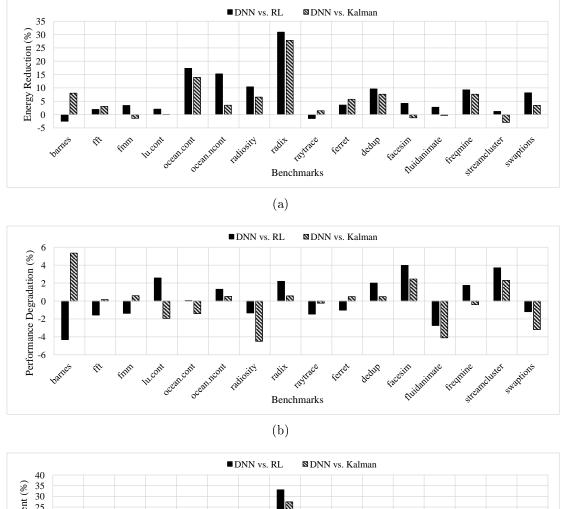

| 4.16 | Simulation results for the 64 core CMP: (a) energy reduction percentages, (b) performance degradation percentages, and (c) EDP improvement percentages. Comparison is done versus the case when no DEM is used                                                                                      | 92  |

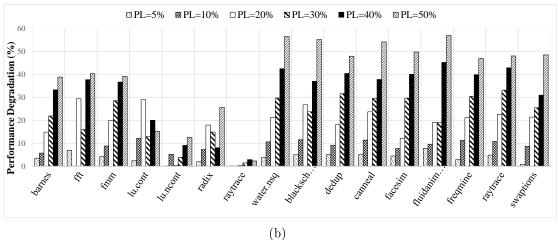

| 4.17 | Simulation results for the 16 core CMP: (a) energy reduction percentages, (b) performance degradation percentages, and (c) EDP improvement percentages. Comparison is done versus the DEM algorithm that uses Kalman filtering for prediction from Sec. 4.3                                         | 95  |

| 4.18 | Simulation results for the 64 core CMP: (a) energy reduction percentages, (b) performance degradation percentages, and (c) EDP improvement percentages. Comparison is done versus the DEM algorithm that uses Kalman filtering for prediction from Sec. 4.3                                         | 96  |

| 4.19 | CPI and instruction count values collected during step 1                                                                                                                                                                                                                                            | 100 |

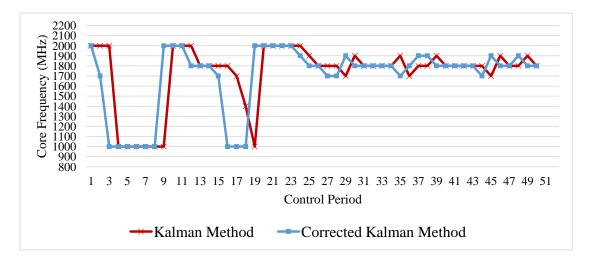

| 4.20 | Frequency values calculated in step 2 from Fig. 4.9                                                                                                                                                                                                                                                 | 101 |

| 4.21 | Topologies of the DNN models for a) 16 core CMP architecture and b) 64 core CMP architecture                                                                                                                                                                                                        | 102 |

| 4.22 | Comparison of the predicted frequencies by the DNN model to those calculated by the Kalman filtering technique                                                                                                                                                              |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

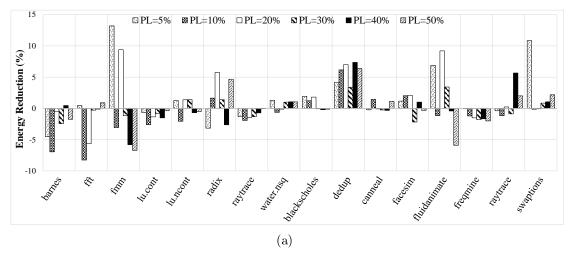

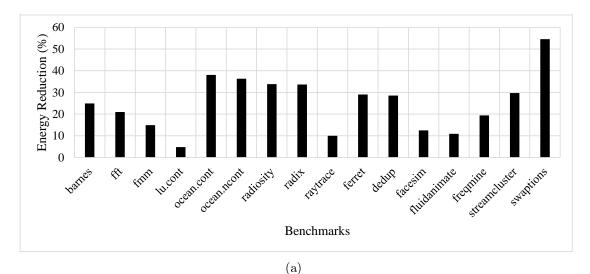

| 4.23 | Comparison of the proposed DNN model based energy optimization algorithm vs. no optimization at all for 16 core CMP. (a) percentage of energy reduction, (b) percentage of performance degradation, and (c) percentage of EDP improvement                                   |

| 4.24 | Comparison of the proposed DNN model based energy optimization algorithm vs. no optimization at all for 64 core CMP. (a) percentage of energy reduction, (b) percentage of performance degradation, and (c) percentage of EDP improvement                                   |

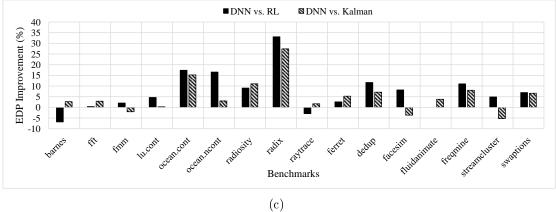

| 4.25 | Comparison of the proposed DNN model based energy optimization algorithm against the RL and the Kalman filtering based approaches for 16 core CMP. (a) percentage of energy reduction, (b) percentage of performance degradation, and (c) percentage of EDP improvement 110 |

| 4.26 | Comparison of the proposed DNN model based energy optimization algorithm against the RL and the Kalman filtering based approaches for 64 core CMP. (a) percentage of energy reduction, (b) percentage of performance degradation, and (c) percentage of EDP improvement 111 |

#### LIST OF NOMENCLATURE AND ACRONYMS

Acronym Definition

ANN: Artificial Neural Network.

CMP: Chip Multiprocessor.

CPI: Cycles per Instruction.

DBN: Deep Belief Network.

DEM: Dynamic Energy Management.

**DIC:** Delayed Instructions Count.

**DNN:** Deep Neural Network.

**DRM:** Dynamic Reliability Management.

**DVFS:** Dynamic Voltage and Frequency Scaling.

**EDAP:** Energy Delay Area Product.

**EDP:** Energy Delay Product.

KNN: K-Nearest Neighbor.

LSTM: Long Short Term Memory.

MC: Monte Carlo.

MTTF: Mean Time To Failure.

**NBTI:** Negative Bias Temperature Instability.

NN: Neural Network.

**NoC:** Network-on-Chip.

**PUE:** Power Usage Effectiveness.

**RBM:** Restricted Bultzman Machine.

**REST:** Reliability Estimation Tool.

**RNN:** Recurrent Neural Network.

**ROI:** Region of Interest.

**SVM:** Support Vector Machine.

**TDDB:** Time Dependent Dielectric Breakdown.

**V/F:** Voltage/Frequency.

WSC: Warehouse Scale Computer.

#### CHAPTER 1

#### Problem Statement, Objective and Contributions

This dissertation addresses new challenges in designing chip multiprocessors which include lifetime reliability and energy consumption. It proposes effective solutions based on novel ideas to address these challenges. In this chapter, the problem statement and the main objectives are described in Sec. 1.1 and Sec. 1.2 respectively. Sec. 1.3 briefly discusses related work in area of lifetime reliability and energy management for CMPs. The contributions to be drawn from this research are then presented in Sec. 1.4. This chapter concludes with an outline and organization of the remainder of the dissertation in Sec. 1.5.

#### 1.1 Problem statement

Chip multiprocessors have become popular in most computing systems, including desktop computers, portable devices, servers and datacenters also called warehouse scale computers (WSCs). While adopting CMPs provides better computational capability, there are new challenges and concerns for the designers as well.

A primary challenge that the designers face in this context is lifetime reliability which worsens with technology downscaling. Two of the most adverse wearout or aging mechanisms in deep submicron technologies include time dependent dielectric breakdown (TDDB) and negative bias temperature instability (NBTI). The impact of these failure mechanisms has become increasingly adverse due to the increased power densities and system complexity. Faster aging leads to earlier performance degradation with eventual device breakdown and thus system failure due to errors. The shift from singlecore to multicore processors has somewhat alleviated the issue of increasingly large power densities. However, this issue persists especially with the advent of chip multiprocessors that integrate tens and hundreds of cores¹ on the same chip; some cores must be shut off to keep power densities under control, thereby not utilizing fully the available computational power of chip multiprocessors. This is commonly referred to as dark silicon problem. Consequently, researchers from both industry and academia recognize that lifetime reliability is becoming a primary design concern and have been investigating methods to mitigate the negative impact of these aging effects in order to increase the mean-time-to-failure (MTTF) of the devices and circuits. Moreover, given that the most important factor through which these aging mechanisms affect chips is the temperature, it is the chip multiprocessors' lifetime reliability that is especially affected — because their operation temperatures have been increasing due to the increased power densities.

On the other hand, also a big concern in CMPs is energy consumption, which is desired to be minimized without affecting the achievable performance. This is increasingly important due to the advent and wide spread of mobile devices but also due to the increasingly large energy consumption footprint of datacenters. Thus, we are interested in reducing energy consumption in mobile devices in order to prolong battery life. Reducing energy consumption in datacenters reduces costs and can have a beneficial impact of the environment. For example, in 2013, U.S. datacenters consumed an estimated 91 billion kilowatt-hours of electricity, enough

<sup>&</sup>lt;sup>1</sup>It is predicted that actually future CMPs will integrate thousands of cores.

to power twice the households in New York City. By 2020, estimated consumption will increase to 140 billion kilowatt-hours, costing American businesses \$13 billion per year in electricity bills and causing the emission of nearly 150 million metric tons of carbon pollution annually [1]. According to the U.S. Energy Information Administration, that is about 7% of total commercial electric energy consumption and it is projected that this number will increase [2]. Therefore, improving energy efficiency is not only important for the cost to companies, but for the environmental footprint of these WSCs as this computing domain rapidly expands [3]. Reducing energy consumption in CMPs has the additional benefit of reducing power dissipation, which in turn lowers chip temperatures that have a beneficial impact on the lifetime reliability of these devices and systems.

#### 1.2 Objectives

The main objective of this work is to provide more efficient techniques to improve the lifetime reliability and energy consumption of the future network-on-chip based chip multiprocessors in order to have more reliable and cost efficient servers, data centers and portable devices.

#### 1.3 Related Work

In this section, the previous work is discussed and classified into two major categories. The techniques that focus on improving the reliability of the chip multiprocessors and the techniques developed to manage the energy consumption of

Figure 1.1: A taxonomy of approaches employed in energy and reliability management techniques.

the CMPs. Fig. 1.1 illustrates the main approaches and techniques that are emplyed in energy and reliability management in computation and communication components of a processor. These techniques are described next.

#### 1.3.1 Reliability Management Techniques

Generally, we can classify reliability oriented design methods into two categories. The first category is that of *static approaches*, which address the problem of reliability at design time. Static design methods include guardbanding and fault tolerance techniques. For example, supply voltages are selected high enough to guarantee

correct functionality despite variation in threshold voltage or in temperature and supply noise. In this way energy gained from downscaling is sacrificed to combat reliability problems. However, if this sacrifice becomes too large, downscaling may become detrimental [4]. Fault tolerance techniques are based on fault detection and recovery mechanisms, which require energy and area overheads. Previous work employed fault tolerant techniques based on 1) error detection implemented through coarse grained replication or redundancy [5-7], 2) failure prediction used to take preventative measures to avoid, or at least mitigate the effects of device failures [8–10], and 3) error masking [11]. Simulated annealing is used to optimize both energy and reliability in [12]. A sequential quadratic programming based approach is proposed in [13] to maximize the lifetime of a multiprocessor system considering the electromigration effects in communication links. A wearout aware schedulability analysis technique is introduced in [14] for real-time independent tasks mapped to processor with dynamic voltage and frequency scaling capabilities. A convex optimization based approach is proposed in [15] to maximize the lifetime reliability of the cores of a multiprocessor system subject to electromigration wearout. The study in [16] uses genetic algorithms to identify voltages and frequencies of the cores of a multiprocessor system to maximize the lifetime and minimize the soft-error susceptibility. The main challenge of this category of methods is to reduce the energy and area overheads while reliability is still improved.

The second category of reliability oriented design methods is that of dy- $namic\ approaches$ . The main idea of this class of approaches is to dynamically

monitor the system during runtime and by using either reactive or proactive techniques to change the operation of the system such that reliability is improved. Note that these approaches may use support from the first category of static approaches discussed in the previous paragraph. A two phase dynamic reliability management algorithm to address various aging mechanisms is introduced in [17]. In the first phase, an application is profiled to find the maximum performance at which each hardware configuration can run while still maintaining the desired mean time to failure. In the second phase, the configuration with the highest performance and satisfying MTTF is selected for the remaining application's run. Dynamic reliability banking is proposed in [18] to address aging due to electromigration. Reliability slack is introduced in [19] and used for dynamic reliability management during periods of high processing demand. The authors of [20] exploit the natural variation in workloads to assign jobs to cores in a manner that minimizes the impact of NBTI and TDDB on lifetime reliability. The authors of [21] introduce Facelift, a technique to hide aging through aging-driven application scheduling and to slow it down by applying voltage changes at key times. A dynamic voltage and frequency scaling (DVFS) control and look-up table reliability estimation based DRM scheme is introduced in [22] for singlecore processors to address process variation aware oxide breakdown. The impact of job scheduling based power management on reliability is investigated in [23]. A dynamic tile partition algorithm is introduced in [24] to balance workload among active cores while relaxing stressed ones. A system level HW/SW reliability management scheme where a chip dynamically adjusts its own operating frequency and supply voltage over time as the devices age due to NBTI is introduced in [25]. The authors of [26] study a control theoretic approach that uses data from aging sensors to compute the wearout degradation and to maximize the lifetime of homogeneous multicore systems. The same authors introduce a complete software implementation, working on a real mobile hardware platform, of a workload-aware dynamic reliability management technique to address TDDB wearout [27]. A reinforcement learning algorithm is proposed in [28] to optimize the lifetime of a multicore system by controlling the average temperature and thermal cycling. While the majority of previous work focus with their reliability oriented design methods only either on the computational portion of the system (i.e., singlecore or multicores) or on the communication component (i.e., buses or networks-on-chip), the authors of [29] concentrate on the combination of both. They use a neural network based reliability estimator and thread migration for dynamic reliability management of chip multiprocessors. The study in [30] introduces a wearout-decelerating scheme to mitigate the impact of NBTI and hot-carrier injection (HCI) in NoCs. Online adaptive aging-aware routing algorithm to avoid highly aged routers in NoCs was studied in [31]. The study in [32] presents a reliability management solution for dark silicon chips. The solution considers soft errors, process variations, and the thermal design power constraint. Simulation results were reported for 80x80 grid cells chips of LEON3 processors. This work is further extended in [33]. The same research group proposed in [34] a run-time approach that harnesses dark silicon to decelerate and balance temperature-dependent aging. Their solution also considered variability to improve the system performance for a given lifetime. They focus on NBTI and did not report if the communication among cores is via the NoC.

Furthermore, the study in [35] proposed a process variation- and aging-aware dynamic hierarchical mapping solution to maximize lifetime reliability of manycore systems while satisfying performance, power, and thermal constraints. The authors reported improved system lifetime reliability by up to 2 years for 64-core and 256-core systems. For discussion of additional reliability studies, we kindly refer the reader to the recent survey in [36].

#### 1.3.2 Energy Management Techniques

Energy optimization in single and multicore processors received a lot of attention in the previous literature. The most popular techniques utilized by previous optimization solutions include DVFS, job scheduling and task migration. Among all these methods, DVFS has been the most effective one, since power consumption is related to the clock frequency and the square of the voltage supply, and energy consumption is the product of power consumption in time. Lowering only the clock frequency of a core helps to reduce the average power consumption for a given application while the total energy consumption remains the same to execute the application. Reducing the average power consumption in turn lowers the chip temperature, however, at the expense of longer execution times for the application. Lowering the supply voltage helps to reduce the total power consumption and this helps in turn to reduce the total energy consumption that is needed for the execution of a given application. DVFS changes both voltage and frequency dynamically and can be used to exploit both above benefits. However, it usually comes at the price of performance degradation due to frequency throttling. In the case of multicore processors, per-core DVFS is not yet widely supported (Intel Haswell-EP and Samsung Exynos processors are said to support it). However, many recent studies have shown the benefits of per-core or per-cluser-of-cores DVFS capabilities [37–42]. Our work is under the assumption that such per-core DVFS may be possible in the future multicore processors and it is under this assumption that we implement and test the proposed ideas using the Sniper system simulator. All these techniques are used as primary control mechanisms to drive the operation of processors toward low energy consumption and such that performance is not significantly degraded. The control decisions are made based on estimations or predictions of the energy or other related variables in a reactive or proactive manner as part of the algorithm or strategy that implements the optimization solution. System monitoring and decision making are usually done periodically, at intervals called control periods or epochs. It is the prediction mechanism that differentiates the impact of a given energy optimization solution.

Previous work has employed a variety of methods including machine learning [43–45], game theory [46], and convex optimization [47] to find the optimal voltage-frequency pairs to manage the energy consumption of homogeneous (i.e., formed by identical cores) processors. More recently, heterogeneous processors are exploited towards additional optimization opportunities [48–50]. For example, the study in [49] proposed a joint temperature and energy management solution for heterogeneous multicore processors. Their heuristic uses both DVFS and temperature- and performance-aware task assignment strategy that maximizes the energy savings, while maintaining the temperature at safe levels.

Some of the previous studies focused on developing performance estimation techniques for DVFS enabled devices and then used them as heuristics inside the control mechanism to find the best voltage-frequency pairs to achieve energy optimization, considering the performance constraints. For example, the study in [51] presented a DVFS that automatically adapted the voltage and frequency for energy savings at runtime in high performance computing clusters formed by four Athlon64-based compute nodes connected via Gigabit Ethernet and another four-node quad-CPU cluster based on the Celestica A8440 server. Similarly, the study in [52] presented a performance-prediction model that is used by a per-CPU DVFS algorithm that makes DVFS decisions based on the index of CPU intensiveness. They verified the algorithm in a 9-node power-aware cluster formed by dual core processors. Other DVFS algorithms applied at the cluster of CPU nodes level include [53,54]. Some recent work also took a more holistic approach and applied DVFS to both CPU and the DRAM subsystem to achieve additional energy savings [55, 56]. They reported for a server platform with an Intel i5-4590 quadcore processor and 8 GB of main memory as much as 22% energy savings with a low performance loss of only 4.8%. While the above previous performance-aware studies focused mainly on the cores inside a CMP, recent studies focused also on the interconnects and the shared last level caches (collectively called the uncore) to estimate the performance of the CMP and use that in DVFS based energy optimization algorithms. For example, the study in [57] uses the number of cache misses while the study in [58] uses the number of non-speculative reads that result in last-level cache misses (called leading loads), and the study in [59] extends that

for variable memory access latencies. Similarly, the authors in [60] take into consideration the off-chip (L2) I-cache misses and off-chip (L2) D-cache load misses in their estimation processes. The study in [61] proposed a DVFS policy for the uncore. The policy uses a technique similar to the TCP Vegas congestion control and was shown to result in significant energy savings.

Developing DVFS algorithm based on the future predicted workload has been another strategy for energy reduction in some studies. Previous work employed different types of predictors to periodically predict the next control period workload for the device and then select a lower voltage/frequency (V/F) pair, if the workload is lower than a threshold, to assure reducing energy consumption while not exceeding the performance limitations. One of the simplest prediction techniques is history prediction. Such predictions can be used to trigger frequency throttling early on in upstream NoC routers in order to lower the rate at which data is sent to downstream routers [62,63]. The study in [64] proposes a multinomial logistic regression-based classification technique, that classifies the workload at runtime, into a fixed set of classes, which are then utilized to design a DVFS algorithm. In [65], a multinominal logistic regression classifier is built using a large volume of performance counters for offline workload characterization. This classifier is queried at run-time for a given application to predict the workload, and then selection of the frequency and thread packing are done to maximize performance under a given power budget. The techniques in [43,66,67] use online learning to select the most appropriate frequency for the processing cores based on the workload characteristic of a given application. Another approach for the data classification or regression problems is the k-nearest neighbor algorithm (KNN) [68]. The study

in [69] uses supervised learning in the form of a Bayesian classifier for processor energy management. This framework learns to predict the system performance from the occupancy state of the global service queue. The predicted performance is then used to select the frequency from a pre-computed policy table. Reinforcement learning (RL) based optimization algorithms are proposed in [28, 70–72]. For example, the study in [28] used RL to learn the relationship between the mapping of threads to cores, clock frequencies, and temperatures, and employed that mapping information to develop better task mapping and DVFS solutions. The work in [70] used RL to learn the optimal control policy of the V/F levels in manycores and then exploited that to develop an efficient global power budget reallocation algorithm. The authors of [72] proposed an online DVFS control strategy based on core-level modular reinforcement learning to adaptively select appropriate operating frequencies for each individual core. Q-learning was used by the work in [73] to develop an algorithm that identifies V/F pairs for predicted workloads and given application performance requirements. In the context of dynamic VFI control in manycore systems with different applications running concurrently, the study in [74] investigated imitation learning and reported higher quality policies.

The authors of [75] develop an artificial neural network (ANN) based mechanism for network-on-chip power management. The offline training of the ANN is augmented with a simple proportional integral (PI) controller as a second classifier. The ANN is used to predict the NoC utility, which is then used to make DVFS decisions that lead to improvements in the energy-delay product. A neural network (NN) based model with eight outputs for different interface configurations of a mobile device was presented in [68] to do classification. Such classification

is used as the basis for setting the mobile device into the configuration state that reduces energy consumption. It was reported that NN and support vector machine (SVM) models provided the best prediction accuracy. The study in [76] proposed a deep neural network (DNN) model to model plant performance and to predict power usage effectiveness (PUE) in datacenters. Testing and validation at Google's datacenters showed that the DNN model can be an effective approach to exploit existing sensor data to model datacenter performance and to identify operational parameters that improve energy efficiency and reduce the PUE [76].

#### 1.4 Contributions

The main contributions of this dissertation is to provide novel and efficient techniques for dynamic reliability and energy management that are described here in more details.

#### 1.4.1 Dynamic Reliability Management

The majority of the previous work suffers from two limiting characteristics. On one hand, previous studies focus separately on either the *computational* component of a processor (i.e., single core or multicore) or the *communication* component, typically the network-on-chip. Not considering either of these components introduces significant errors, because both computational and communication units of multicore processors may become a reliability bottleneck. Such errors can mislead any lifetime reliability optimization method and result into suboptimal solutions. To address this issue, in [29, 83], we considered the study of CMPs in a unified

manner, as the combination of both computational and communication units. We found that when we do not consider for example the NoC unit in the reliability optimization, the errors in MTTF values, as the most popular way to measure lifetime reliability, may be off by as much as 60%. On the other hand, usually only one technique, such as DVFS, scheduling or thread migration, is used as the main optimization technique. Indeed, employing only one technique can miss further optimization opportunities that can be offered by hybrid approaches that typically combine multiple cross-layer techniques, to construct algorithms that are more versatile and applicable to a wider variety of benchmark applications and workloads. It is our intent with this dissertation to address this issue. Specifically, we propose and study a hybrid dynamic lifetime reliability management algorithm for CMPs that combines thread migration and dynamic voltage and frequency scaling techniques. The proposed algorithm uses a simple yet effective approach in order to seamlessly use the two techniques to adaptively change the CMP operation such that the lifetime reliability of the overall system is increased to the desired target with minimal performance degradation.

#### 1.4.2 Dynamic Energy Management

The majority of the previous approaches rely on the performance estimation and workload prediction/classification based techniques. The effectiveness of all these methods is significantly affected by the estimation, prediction or classification accuracy. In most cases, complex relationships exist across long histories of processor usage that may not be detected by current techniques, which increases the number of mispredictions when using current prediction based solutions. While there

has been significant work, it is not clear how far the existing DVFS based energy optimization techniques are from the optimal solutions. We believe there is still room for improvement, and generally, we see this as the main limitation of previous work. As such, our main motivation is to investigate whether DNN models can be of any help in pushing the frontier of energy optimization in chip multiprocessors. This idea in turn is motivated by the immense success that DNN models have had in the last decade in many application domains including speech and pattern recognition, image processing, and datacenter operation.

First of all, we present a new heuristic algorithm for dynamic energy management of chip multi-processors that proposes a performance estimation based technique called delayed instruction count (DIC) which increases the estimation accuracy by eliminating the issues related to counting the misses and stalls. It also employs the DVFS technique to identify the best V/F pairs for all cores of the CMP. This is done using accurate and efficient estimations of the average cycles per instruction and the instruction count, which are done using a Kalman filtering as well as long short-term memory (LSTM) techniques. Then, we propose DNN models and develop related self-adaptive supervised learning methods to identify optimal V/F pairs in chip multiprocessors. Since the supervised learning needs labeled data for the training process, the Kalman filtering based DEM that we developed earlier is used to collect workload characteristics and their corresponding corrected V/F pairs as the labels for the training data. Using DNN models offers the advantages of being able to handle heterogeneity and to capture deep and complex relationships across long histories of processor usage. We see deep

learning techniques, such as the one we propose in this dissertation, as a new enabler in pushing the frontier of energy optimization in computing systems because they have the ability to model and predict complex behavior and relations between workload and hardware that otherwise currently is not possible.

#### 1.5 Dissertation Organization

Chapter 2 presents background information on system failure mechanisms and then describes a technique to estimate the reliability of a network-on-chip based chip multiprocessor. In addition, the prediction/classification methods including Kalman filtering, long short term memory and deep neural network that we later use in the proposed dynamic energy management techniques are discussed next.

Chapter 3 describes the proposed techniques to dynamically manage the reliability of the network-on-chip based chip multiprocessors. These techniques employ DVFS and thread migration wisely to achieve reliability improvement without imposing significant penalty on the performance. The effectiveness of these techniques are then evaluated on various benchmarks via full-system simulations.

The proposed dynamic energy management techniques for CMPs are discussed in Chapter 4. The discussion starts with a mechanism to predict the performance loss when using various V/F pairs instead of executing with the maximum V/F pair all the time and then proposes effective techniques with the help of Kalman filtering, LSTM and DNN to find energy saving opportunities during the execution time without degrading performance beyond the user set threshold. The simulation results for each technique on different benchmarks are then presented

in the rest of the chapter.

Finally, Chapter 5 overviews the findings of this dissertation and discusses future work.

#### 1.6 Related Publications

The topics discussed in this dissertation have been published in several conference and journal papers as follows:

- [77] M.G. Moghaddam and C. Ababei, "Dynamic lifetime reliability management for chip multiprocessors," *IEEE Trans. on Multiscale Computing Systems*, 2018.

- [78] M.G Moghaddam, W. Guan and C. Ababei, "Dynamic energy minimization in chip multiprocessors using deep neural networks," *IEEE Trans. on Multiscale Computing Systems*, 2018.

- [79] C. Ababei, and M.G. Moghaddam, "A Survey of Prediction and Classification Techniques in Multicore Processor Systems," *IEEE Trans. on Parallel and Distributed Systems*, 2018.

- [80] M.G. Moghaddam, C. Ababei, "Dynamic energy management for chip multiprocessors under performance constraints", *Microprocessors and Microsystems*, vol. 54, pp. 1-13, Oct. 2017.

- [81] M.G Moghaddam, W. Guan and C. Ababei, "Investigation of LSTM based prediction for dynamic energy management in chip multiprocessors," *IEEE Int. Green and Sustainable Computing Conference (IGSC)*, 2017.

- [82] M.G Moghaddam, "Dynamic energy and reliability management for NoC-based chip multiprocessors," *IEEE Int. Green and Sustainable Computing Conference (IGSC)*, 2017.

- [83] M.G. Moghaddam, A. Yamamoto, and C. Ababei, "Investigation of DVFS based dynamic reliability management for chip multiprocessors," *IEEE Int. Conference on High Performance Computing & Simulation (HPCS)*, 2015.

#### CHAPTER 2

#### Background

In this chapter, we discuss the foundational concepts and materials used later in this dissertation. In Sec. 2.1, we talk about the main mechanisms that lead to device breakdown and system failure. Sec. 2.2 explains the reliability estimation technique that we employ in our work. An effective prediction technique using the Kalman filtering is described in Sec. 2.3. In addition, in Sec. 2.4, neural networks related concepts including feedforward neural network, recurrent neural network (RNN), long short term memory and deep neural network are described that we use later for accurate and fast prediction/classification purposes.

#### 2.1 Aging Mechanisms

Aging mechanisms including time dependent dielectric breakdown and negative bias temperature instability are among the most increasingly adverse factors that can lead to delay errors and device breakdowns. In this section, we briefly describe these mechanisms.

#### 2.1.1 Time Dependent Dielectric Breakdown

The growth in demand for faster devices has lead to technology downscaling in CMOS transistors. As a drawback, over the last years, the thickness of the gate oxide in CMOS transistors has been decreased dramatically, consequently having smaller threshold to electric field, which can cause dielectric breakdown in transistors. The reason is that the oxide can no longer properly insulate the gate terminal

and causes the charges to tunnel through in it and eventually become trapped in it, as shown in Fig. 2.1. The number of trapped charges in the oxide increases in time and after getting to a certain amount, the oxide breaks down and conducts the current from gate to substrate. Transferring current heats up the oxide and causes it to conduct even more current and consequently this feedback loop will eventually destroy the dielectric. Thus, due to having this characteristics, a device can suffer various soft breakdowns or a hard breakdown before the final hard breakdown occurs [84].

So, by the increase in temperature, the tunneling current will increase and consequently, the number of the trapped charges will increase as well. Therefore, it can be deduced that as the device gets hotter, the MTTF of a device decreases due to the TDDB mechanism.

As described in [17], the  $MTTF_{TDDB}$  can be modeled by the following expression:

$$MTTF_{TDDB} \propto \left( \left( \frac{1}{V} \right)^{a-bT} \times e^{\frac{X + \frac{Y}{T} + ZT}{KT}} \right)$$

(2.1)

where V is the Voltage supply, T is the temperature in Kelvin, k is the Boltzmann's constant and a,b,X,Y, Z are model parameters that are determined experimentally. These values are set in this model as a=78, b=-0.81, X=0,759eV, Y=-66.8eV, and  $Z=-8.37e^{-4}eV$  based on the experimental data from [85].

Figure 2.1: Time dependent dielectric breakdown process.

#### 2.1.2 Negative bias temperature instability

When negative voltages have applied to the gate in MOSFET devices (especially in PMOS), it gradually degrades the performance in time. That is due to increasing the threshold voltage of the transistor, degrading the drain current and consequently degrading the speed [86,87]. Experimental analysis shows that this problem, which is known as negative bias temperature instability, increases exponentially with rise in temperature [88,89]. In other words, as described in [90],

Figure 2.2: Negative bias temperature instability process.

this mechanism is characterized by a positive shift in the absolute value of the PMOS, which occurs when a device is biased in strong inversion, but with a small, or no lateral electric field. The shift is generally attributed to hole trapping in the dielectric bulk, and/or to the breaking of Si-H bonds at the gate dielectric interface by holes in the inversion layer, which generates positively charged interface traps as shown in Fig. 2.2.

MTTF due to the NBTI mechanism is modeled as shown in 2.2, where  $A=1.6328,\,B=0.07377,\,C=0.01,\,D=0.06852,\,\beta=0.3$  and T is the temperature in Kelvin as in [29], and K is Bultzman's cost.

$$MTTF_{NBTI} \propto ([ln(\frac{A}{1+2e^{\frac{B}{kT}}}) - ln(\frac{A}{1+2e^{\frac{B}{kT}}} - C)]\frac{T}{e^{\frac{D}{kT}}})^{\frac{1}{\beta}}$$

(2.2)

### 2.2 Reliability Estimation Tool

According to Sec. 2.1.1 and 2.1.2, the temperature of the silicon has a significant impact on the MTTF of the system. Since in a CMP, the temperature of the components changes based on the assigned workload, we need a mechanism to estimate the MTTF of a CMP with the given components' temperature. In this section we briefly introduce the lifetime reliability estimation tool (REST) described in [29], which we use it later in section 3.

The REST tool is based on a Monte Carlo (MC) algorithm that works with failure times for TDDB and NBTI aging mechanisms modeled as Weibull distributions. What distinguishes Rest from the previous work is that both the computational and communication components of the studied chip multiprocessor system are considered in a unified manner to compute the lifetime reliability (as MTTF) of the CMP. The flow chart of the MC algorithm is shown in Fig. 2.3.

The input to the REST tool is a list of temperatures for all routers and blocks of each processor core as computed by HotSpot [105]. These temperatures are utilized during each iteration of the MC algorithm to generate samples (or instances) from the probability distributions associated with each router and core block forming the CMP system. The generation of these samples is based on equations in described in Sec. 2.1.1 and 2.1.2 that model the mean time to failure for each type of wearout or aging mechanism and which have been derived by the materials science and reliability engineering communities.

The pseudocode description of the MC algorithm is shown in Fig. 2.4. It

Figure 2.3: Block diagram of the Monte Carlo simulation based time to failure evaluation methodology for CMPs.

consists of the following steps 1) for each failure mechanism run  $N=10^5$  simulations: (a) for each block, generate failure time instances from the corresponding distribution, and (b) use MIN-MAX analysis of these times according to the system's configuration to calculate the time to failure  $tf_{min}^j$  during simulation iteration j=1,...,N. 2) calculate the time to failure for the current failure mechanism as  $tf_l = (\sum_{j=1}^N tf_{min}^j)/N$ . 3) calculate the value of the overall MTTF or time to failure of the CMP as the minimum among the failure times due to each failure mechanism. We selected  $N=10^5$  because in our experiments we found that this number is a good tradeoff between computational runtime and statistical significance of results.

During each MC simulation iteration, we need to generate random instances of failure times for each subblock. This is realized by the  $generate\_instance(MTTF_l)$  procedure called in line number 8 in Fig 2.4, which draws samples from Weibull distributions whose means are given by equations (2.3) and (2.4). Because the Weibull cumulative distribution function is given by:

$$F(x) = 1 - e^{-\left(\frac{x}{\alpha}\right)^{\beta}} \tag{2.3}$$

$$x_{sample} = \alpha \cdot \left[-\ln(1-u)\right]^{\frac{1}{\beta}} \tag{2.4}$$

where u = rand(0,1) is a random number generated uniformly from the interval [0, 1].  $\alpha$  and  $\beta$  are the scale and the shape factors characterizing the Weibull distribution. In our implementation of  $generate\_instance(MTTF_l)$ , we utilize a value of  $\beta = 1.64$  as in [91] while  $\alpha$  is derived from the expression of the mean of the Weibull distribution:

$$\alpha = \frac{MTTF_l}{\Gamma(1 + \frac{1}{\beta})} \tag{2.5}$$

where  $\Gamma(.)$  is the Gamma function.

```

Algorithm: Monte Carlo algorithm of REST tool

1: In: CMP floorplan and temperature of all blocks

2: Out: Estimate of MTTF of whole CMP

for l \leftarrow 1 to F do // F: number of failure wearout types

Calculate MTTF_l using equations that model wearout mechanisms

for j \leftarrow 1 to N do // N = 10^5 Monte Carlo iterations

5:

tf_{min}^{j} \leftarrow INF //  Initialize

6:

for k \leftarrow 1 to S do // S: number of blocks

7:

tf_k \leftarrow generate \ instance(MTTF_l)

8:

if tf_k < tf_{min}^j then // Generalization: MIN\_MAX

9:

tf_{min}^j = tf_k

10:

end if

11:

end for

12:

end for tf_l = \frac{\sum_{j}^{N} t f_{min}^{j}}{N}

13:

14:

15: end for

16: return tf = MIN\{tf_l\} // Estimate of MTTF of whole CMP

```

Figure 2.4: Pseudocode description of the Monte Carlo simulation implemented by the reliability estimation, REST tool.

# 2.3 Kalman Filtering

In this section, we present a description of Kalman filtering, which we use later in this work as an estimation technique to estimate the future workload on the cores of the CMP. The Kalman filter uses a set of recursive equations and employs a feedback control mechanism in a way that minimizes the variance of the estimation error [92]. It is an adaptive filter applied to predict the state x of a discrete-time controlled process. Using the notation from [93], the process can be described by the following state and output equations.

$$x_n = Ax_{n-1} + Bu_{n-1} + w_{n-1} (2.6)$$

$$z_n = Hx_n + v_n \tag{2.7}$$

where A, B, and H are matrices. A is the state transition model applied to the previous state  $x_{n-1}$ . It relates the states at time steps n-1 and n, in the absence of process noise or control input. B relates the optional control input u to the state x, and the matrix H relates the state x to the measurement or observation z. The random variable  $w_{n-1}$  models the process noise assumed to be a white Gaussian noise with zero mean and covariance Q,  $w \sim N(0,Q)$ . Similarly, the random variable  $v_n$  is the measurement noise also assumed to have a Gaussian distribution with zero mean and covariance R, that is independent from Q,  $v \sim N(0,R)$ .

Then, we define the *a priori* and *a posteriori* estimate errors as  $e_{\bar{n}} = x_n - \hat{x}_n^-$  and  $e_n = x_n - \hat{x}_n$ , where  $\hat{x}_n^-$  is our a priori state estimate given the knowledge on the process prior to step n and  $\hat{x}_n$  is our a posteriori state estimate after measurement  $z_n$  has been made. Based upon these estimates, the a priori and a posteriori estimate error covariances are given by the following expressions:

$$P_n^- = E[e_n^- e_n^{-T}] (2.8)$$

$$P_n = E[e_n e_n^T] (2.9)$$

To estimate the states of a process with measurements, the Kalman filter employs a feedback control technique in which the state at some time is estimated first and feedback is then provided in the form of noisy measurements. Thus, a Kalman filter is constructed in two phases. The first phase is called the *predict* phase (also called the time update phase), and here the state x is predicted a priori

as  $\hat{x}_n^-$ . The second phase is called the *update phase* (also called the measurement update phase). This is where the predicted  $\hat{x}_n^-$  is updated a posteriori as  $\hat{x}_n$ .

In the predict phase, the filter first projects the state ahead from the previous state  $\hat{x}_{n-1}$  and certain input matrix  $Bu_{n-1}$ . The filter then projects the error covariance ahead with process noise covariance Q. The two equations that accomplish that are:

$$\hat{x}_n^- = A\hat{x}_{n-1} + Bu_{n-1} \tag{2.10}$$

$$P_n^- = A P_{n-1} A^T + Q (2.11)$$

Where  $P_n^-$  and  $P_n$  represent the estimated error covariance for a priori and a posteriori errors, respectively, at time n. They are calculated as shown in equations (2.8) and (2.9).

The update phase starts right after the predict phase with the measurement of the actual state value at time n. The three equations utilized in this phase are:

$$K_n = P_n^- H^T (H P_n^- H^T + R)^{-1}$$

(2.12)

$$\hat{x}_n = \hat{x}_n^- + K_n(z_n - H\hat{x}_n^-) \tag{2.13}$$

Figure 2.5: Kalman filter predict phase and update phase procedure.

$$P_n = (1 - K_n H) P_n^- (2.14)$$

The Kalman gain,  $K_n$ , is first computed by using the a priori estimate error covariance  $P_n^-$  and measurement noise covariance R. It is chosen to maximize the a posteriori error covariance  $P_n$ . The filter then updates the current state vector  $\hat{x}_n$  and a posteriori estimate error covariance  $P_n$ , using the Kalman gain. Fig. 2.5 summarizes how Kalman filter works.

### 2.4 Neural Networks

Among different machine learning models, the NN model is one of the most popular ones. The idea behind NN is to model the human brain architecture to mimic the learning process of the brain, but on computers. The human brain is modeled

as a network of millions of neurons connected to each other. The input signals provided by the body sensors are given to some of the neurons. These neurons process the signals and then pass their decisions to other connected neurons. It is assumed that final decisions are made by the last connected neurons. The NN model simplifies this process by proposing an architecture composed of connected layers of nodes and transfer functions as neurons. The nodes communicate with each other through weighted signals whose weights are adjusted via a repetitive computational process called learning.

#### 2.4.1 Feed-Forward Neural Networks

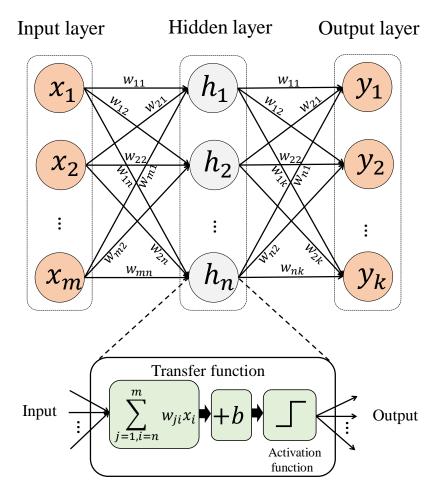

The simplest and most popular NN architecture is the feed-forward neural network, which is illustrated in Fig. 2.6. The information in this network is transferred from one layer to the next in the forward direction only and no cyclic connections exist between layers. Each node represents a neuron that receives its weighted inputs from the nodes on the previous layer and calculates the output (i.e., decision) that is passed to the next layer. The transfer function of the node sums together all the decisions from the nodes in the previous layer and adds them to a bias value. The result then is passed through an activation function to generate the output. This process takes place in the forward direction through all layers up to the output layer, which produces the final output decisions. The values of the weights and biases are crucial as they affect the accuracy of the final decision. These values are determined during the training process of the network.

In supervised training, for a set of known features and labels (i.e., inputs

Figure 2.6: Typical neural network architecture.

and their corresponding output decisions), the final decisions produced by the NN model are compared to the labels by means of a cost function. Then, an optimizer is employed to minimize the generated cost by updating the weights through the network going in the backward direction as a backpropagation process. Usually, the optimizer uses a gradient descent optimization approach [94]. The training process is repeated on different sets of features and labels, thereby determining the optimized weights and biases. Once trained, the NN model can be utilized to provide estimations on new data of interest. That is, the outputs of the final layer can be used directly for classification purposes.

Figure 2.7: Simplified diagram of a recurrent neural network.

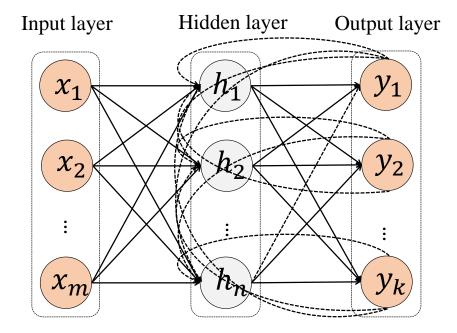

#### 2.4.2 Recurrent Neural Networks