# Marquette University e-Publications@Marquette

Master's Theses (2009 -)

Dissertations, Theses, and Professional Projects

# Uncertainty Aware Mapping of Embedded Systems for Reliability, Performance, and Energy

Wenkai Guan Marquette University

**Recommended** Citation

Guan, Wenkai, "Uncertainty Aware Mapping of Embedded Systems for Reliability, Performance, and Energy" (2018). *Master's Theses* (2009 -). 468. https://epublications.marquette.edu/theses\_open/468

# UNCERTAINTY AWARE MAPPING OF EMBEDDED SYSTEMS FOR RELIABILITY, PERFORMANCE, AND ENERGY

by

Wenkai Guan

A Thesis Submitted to the Faculty of the Graduate School Marquette University, in Partial Fulfillment of the Requirements for the Degree of Master of Science

Milwaukee, Wisconsin

May 2018

#### ABSTRACT

#### UNCERTAINTY AWARE MAPPING OF EMBEDDED SYSTEMS FOR RELIABILITY, PERFORMANCE, AND ENERGY

#### Wenkai Guan Marquette University

Due to technology downscaling, embedded systems have increased in complexity and heterogeneity. Increasingly large process, voltage, and temperature variations negatively affect the design and optimization process of these systems. These factors contribute to increased uncertainties that in turn undermine the accuracy and effectiveness of traditional design approaches. In this thesis, we formulate the problem of uncertainty aware mapping for multicore embedded system platforms as a multi-objective optimization problem. We present a solution to this problem that integrates uncertainty models as a new design methodology constructed with Monte Carlo and evolutionary algorithms. The solution is uncertainty aware because it is able to model uncertainties in design parameters and to identify robust design points that limit the influence of these uncertainties onto the objective functions. The proposed design methodology is implemented as a tool that can generate the robust Pareto frontier in the objective space formed by reliability, performance, and energy consumption.

**Keyword:** Embedded systems; Uncertainties; Robust mapping; Reliability; Performance; Energy consumption.

#### ACKNOWLEDGEMENTS

The last two years of my Master study life leave me indelible memories. With ups and downs, all the past days are still as fresh as yesterday. As the proverb says: "Feel appreciated when life does not forget". I feel so grateful for a lot of bright people practically or mentally supported and helped me during my Master study. Here, I would like to express my thanks to all these people.

First, I would like to thank my advisor: Dr. Cristinel Ababei. I feel fortunate that I have Cris to supervise my Master study! Cris provided me with an excellent working environment, which is full of trust and freedom. With this environment, I was able to pursue and explore my interested research areas and come up with my own ideas. In addition, Cris was always willing to make time for me for problem discussion, weekly meeting, paper revision, and so on. With his guidance, I was able to gain the ability of problem formulation and solution in doing research. What is more, apart from providing excellent scientific support and advice, Cris also taught me as to have a warm family and enjoy the happiness of the life. I can never thank him enough for his selfless dedication and guidance to me.

I would like to thank Dr. Richard Povinelli, who laid the foundation for my understanding of evolutionary algorithms in the Evolutionary Computing Course. Dr. Povinelli provided me many useful suggestions for improving my writing skills. Thanks for serving as one of my committee members and taking time to review my thesis.

I would also like to thank Dr. Henry Medeiros, who laid the foundation for my knowledge of advanced algorithms during the Algorithm Course. Dr. Medeiros shared his research experience with me: "Research needs focus". Many times I saw Dr. Medeiros focused on his research at late night in his lab. His research experience helped me leaped over the obstacles in front of my research areas fast and efficient. Thanks for being one of my committee members and spending time on reviewing my thesis.

An excellent thanks go out to Milad Ghorbani Moghaddam. From the start of my Master study, I spent most of my time working together with Milad in the MESS Lab. Thanks for helping me all the time! Furthermore, I would like to thank all the other colleagues in our lab: Ian Barge, Kellen Carey, Nate Zimmer, Shaun Duerr, Brandon Kupczyk, Jarrett Smalley, and Masoud Ghorbani Moghaddam. Thanks for all of you!

Meanwhile, I want to appreciate the friendship with many great Chinese and International friends during my stay in the USA. Thanks for helping me and making my life enjoyable in the past two years. They are: Jiangbiao He, Chen Li, Xiangyu Zhou, Tianyu Liu, Yun Bai, Jiao Qiao, Hao Chen, Yue Sun, Jiayi Su, Yuqin Wong, Dan Tong, Ann Li, Greg Merkel, Elizaveta Grushnikova, Reza Mdh, Yevgeniy Reznichenko, David Kaftan, Samuel Amoako-Frimpong, Philipe Dias and so on.

Finally, I would like to thank my parents and my cousin Weihua Guan, who supported my decision to study overseas. I owe my most profound gratitude to my wife, Qin Zhang, who supported and stood behind me all the time, through every hill, every valley. Without her, this thesis would not have been possible.

## TABLE OF CONTENTS

| ABST   | RACT                                                   | i         |

|--------|--------------------------------------------------------|-----------|

| ACKN   | OWLEDGEMENTS                                           | ii        |

| TABL   | E OF CONTENTS                                          | iii       |

| LIST ( | OF TABLES                                              | vi        |

| LIST ( | OF FIGURES                                             | vii       |

| CHAP   | TER 1 Problem Statement, Objective and Contributions . | 1         |

| 1.1    | Problem Statement                                      | 1         |

| 1.2    | Objectives                                             | 3         |

| 1.3    | Contributions                                          | 4         |

| 1.4    | Thesis Organization                                    | 5         |

| CHAP   | TER 2 Background                                       | 7         |

| 2.1    | Electronic System-Level Design                         | 7         |

| 2.2    | Design Space Exploration                               | 8         |

| 2.3    | Reliability Evaluation of Embedded Systems             | 9         |

|        | 2.3.1 Combinatorial Models                             | 10        |

|        | 2.3.2 Markov Model                                     | 12        |

| 2.4    | Uncertainty Aware Optimization of Embedded Systems     | 13        |

|        | 2.4.1 Monte Carlo (MC) Simulation                      | 13        |

|        | 2.4.2 Evolutionary Algorithms for Optimization         | 15        |

| 2.5    | Previous Work                                          | 16        |

| 2.6    | Summary                                                | 21        |

| CHAP   | TER 3 Motivating Example                               | <b>22</b> |

| 3.1    | ABS Testcase Study                                     | 22        |

| 3.2    | Motivation                                             | 24        |

|        | 3.2.1 Answering Question 1                             | 25        |

|        | 3.2.2 Answering Question 2                             | 28        |

| CHAP   | TER 4 Proposed Design Methodology                      | 30        |

| 4.1    | Approach Overview                                      | 30        |

| 4.2     | Uncert  | tainty Modeling                                           | 32 |

|---------|---------|-----------------------------------------------------------|----|

| 4.3     | Applic  | eation Modeling                                           | 36 |

| 4.4     | Archit  | ecture Modeling                                           | 38 |

| 4.5     | Gener   | ation of Initial Candidates                               | 39 |

| 4.6     | Design  | Space Exploration Using Genetic Algorithms                | 39 |

|         | 4.6.1   | Objective 1: Reliability                                  | 40 |

|         | 4.6.2   | Objective 2: Execution Time as Measure of Performance     | 43 |

|         | 4.6.3   | Objective 3: Energy Consumption                           | 44 |

|         | 4.6.4   | Solving the Multi-objective Problem                       | 45 |

| 4.7     | Selecti | ion                                                       | 49 |

| 4.8     | Estima  | ation Under Uncertainty                                   | 50 |

|         | 4.8.1   | Consideration of Uncertainty Correlations                 | 51 |

|         | 4.8.2   | Consideration of Different Levels of Uncertainty          | 53 |

|         | 4.8.3   | Robust Estimation of the Reliability                      | 54 |

|         | 4.8.4   | Robust estimation for Performance and Energy Consumption  | 57 |

| 4.9     | Robus   | tness of Design Solution Points                           | 58 |

| 4.10    | Conclu  | usions                                                    | 59 |

| CHAP    | TER 5   | 5 Simulation Experiments - Comparison to Traditional      |    |

| Metho   | d       |                                                           | 60 |

| 5.1     | Exper   | imental Setup and Testcases                               | 60 |

| 5.2     | Archit  | ecture Platform                                           | 62 |

| 5.3     | Robus   | t and Deterministic Estimation                            | 63 |

| 5.4     | Pareto  | Frontiers                                                 | 64 |

| 5.5     | Conclu  | usion                                                     | 67 |

| CHAP    | TER 6   | <b>5</b> Simulation Experiments - Proposed Robust Method, |    |

| Scalabi | ility A | nalysis                                                   | 68 |

| 6.1     | Testca  | ISES                                                      | 68 |

|         | 6.1.1   | Architecture Platform                                     | 71 |

|         | 6.1.2   | Pareto Frontiers                                          | 75 |

|         | 6.1.3   | Different Levels of Uncertainty                           | 78 |

|      | 6.1.4      | Consideration of Both Different Levels of Uncertainty and |    |

|------|------------|-----------------------------------------------------------|----|

|      |            | Uncertainty Correlations                                  | 82 |

|      | 6.1.5      | Scalability of the Computational Runtime and Convergence  | 84 |

| 6.2  | Conclu     | usion                                                     | 87 |

| CHAP | TER 7      | Conclusions                                               | 89 |

| 7.1  | Conclu     | usions and Future Work                                    | 89 |

| REFE | REFERENCES |                                                           |    |

### LIST OF TABLES

| 4.1 | Rules for defining mean and variance of distributions from which sam-    |    |

|-----|--------------------------------------------------------------------------|----|

|     | pling must be done to achieve a certain degree of uncertainty injection. | 35 |

| 5.1 | Parameters of NSGA-II.                                                   | 61 |

| 6.1 | Listing of the testcases used for simulations.                           | 69 |

| 6.2 | Detailed description of the ABS testcase                                 | 69 |

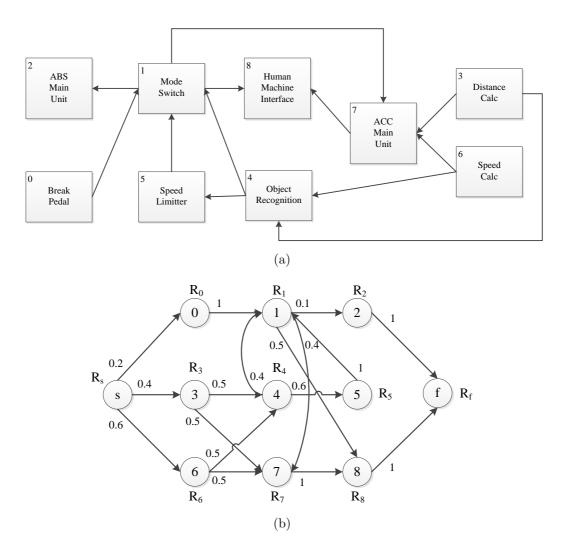

| 6.3 | Detailed description of the ACC testcase                                 | 70 |

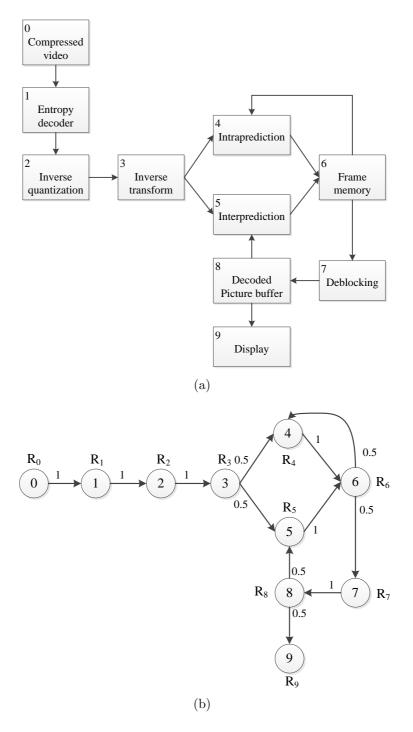

| 6.4 | Detailed description of the H.264 testcase.                              | 70 |

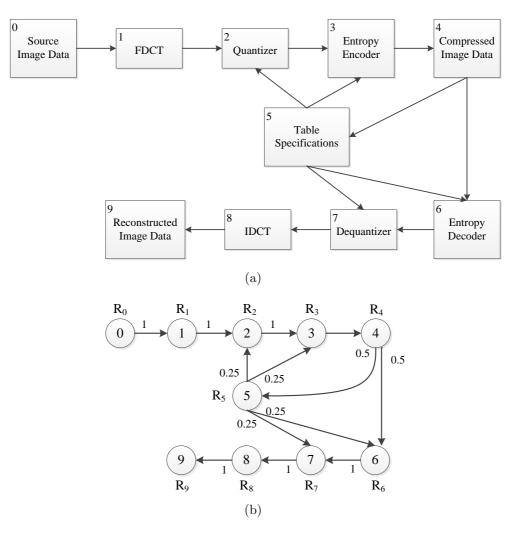

| 6.5 | Detailed description of the JPEG testcase                                | 71 |

# LIST OF FIGURES

| 2  | Conventional design flow for embedded systems. In this thesis, we focus on the problem of mapping. Dashed arrows labeled 1,2,3 indicate possible routes to go back in the design flow to change design decisions in order to improve the design.                                                                                                           | 1.1 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3  | (a) Pareto frontier surface in traditional embedded systems design. (b)<br>Uncertain Pareto surface where a design point degenerates into multiple<br>solutions.                                                                                                                                                                                           | 1.2 |

| 6  | Thesis outline.                                                                                                                                                                                                                                                                                                                                            | 1.3 |

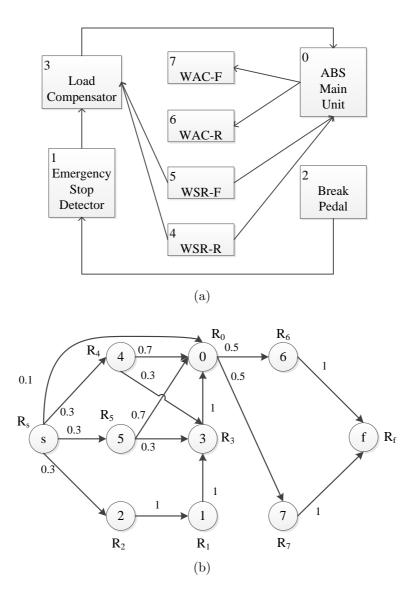

| 23 | ABS software components and interactions.                                                                                                                                                                                                                                                                                                                  | 3.1 |

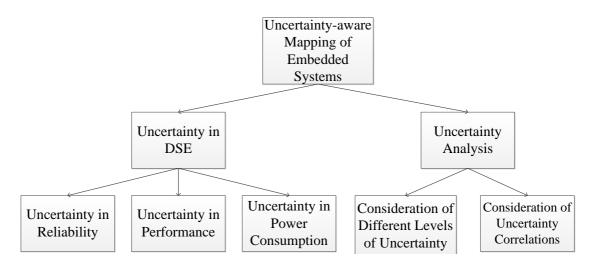

| 24 | Motivation of this thesis.                                                                                                                                                                                                                                                                                                                                 | 3.2 |

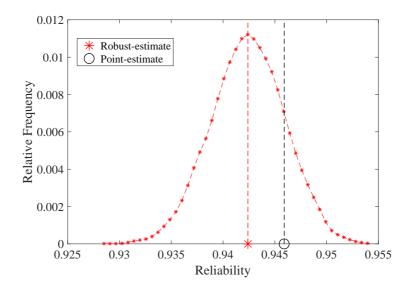

| 25 | Histogram of system reliability. All histograms are obtained using $10^5$ parameter samples during the estimation process.                                                                                                                                                                                                                                 | 3.3 |

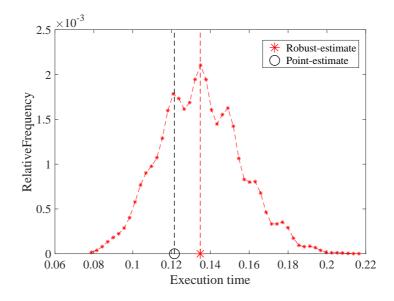

| 25 | Histogram of execution time. All histograms are obtained using $10^5$ parameter samples during the estimation process.                                                                                                                                                                                                                                     | 3.4 |

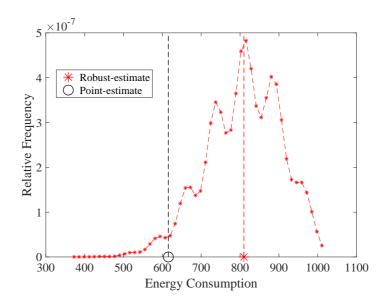

| 26 | Histogram of energy consumption. All histograms are obtained using $10^5$ parameter samples during the estimation process                                                                                                                                                                                                                                  | 3.5 |

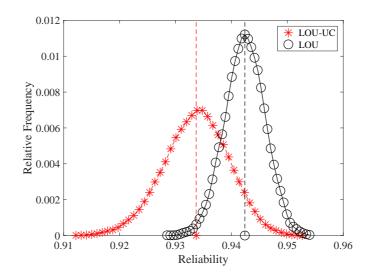

| 28 | Histogram of system reliability for LOU and LOU-UC techniques                                                                                                                                                                                                                                                                                              | 3.6 |

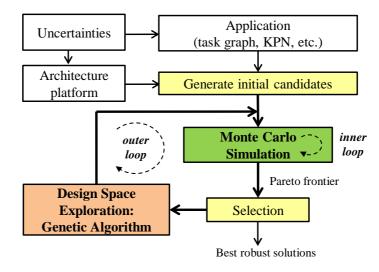

| 31 | Block diagram of the proposed design method for embedded systems mapping under uncertainties.                                                                                                                                                                                                                                                              | 4.1 |

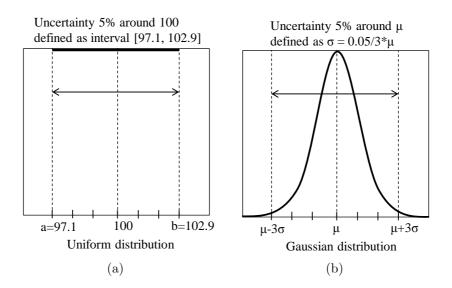

| 34 | (a) To inject 5% uncertainty for a parameter characterized by a uniform distribution whose mean is 100 for example, we generate samples from a uniform distribution defined on the interval $[a = \mu - 0.05 \cdot \mu/\sqrt{3}, b = \mu + 0.05 \cdot \mu/\sqrt{3}]$ . (b) The interval used for the case of a Gaussian distribution whose mean is $\mu$ . | 4.2 |

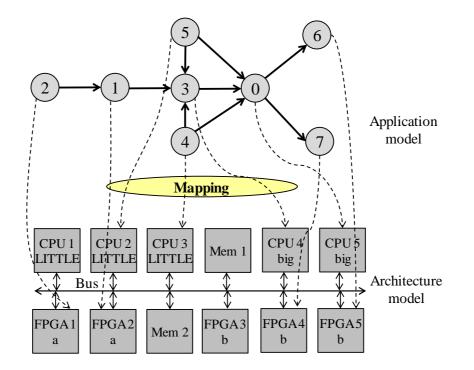

| 36 | ABS application mapping problem. We only show the mapping of the tasks for simplicity.                                                                                                                                                                                                                                                                     | 4.3 |

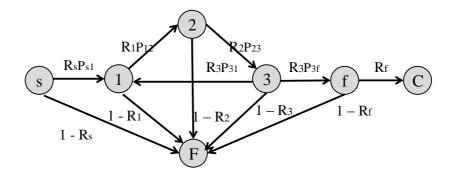

| 41 | DTMC model when states C and F are added                                                                                                                                                                                                                                                                                                                   | 4.4 |

| 52 | Definitions of different correlation groups.                                                                                                                                                                                                                                                                                                               | 4.5 |

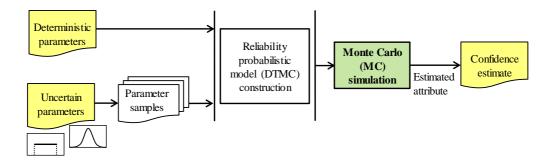

| 54 | Block diagram of the Monte Carlo simulation based technique to esti-<br>mate reliability                                                                                                                                                                                                                                                                   | 4.6 |

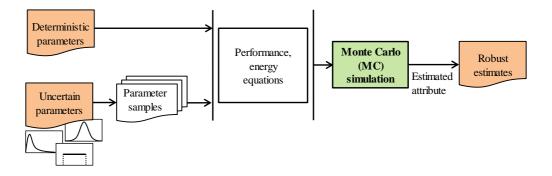

| 57 | Block diagram of the Monte Carlo simulation based technique to esti-<br>mate execution time, and energy consumption                                                                                                                                                                                                                                        | 4.7 |

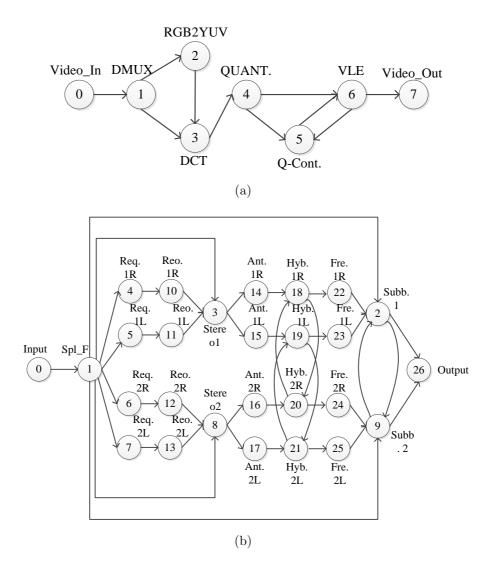

| 5.1  | The KPN of (a) MJPEG testcase. (b) MP3 testcases                                                                                     | 62 |

|------|--------------------------------------------------------------------------------------------------------------------------------------|----|

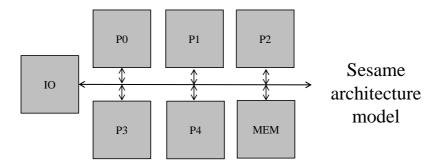

| 5.2  | Architecture platform used in simulations done with the Sesame tool                                                                  | 63 |

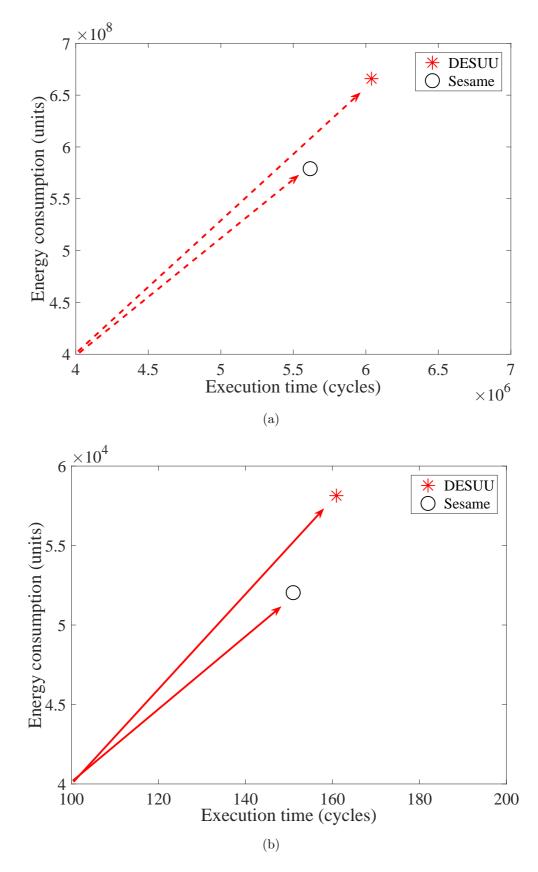

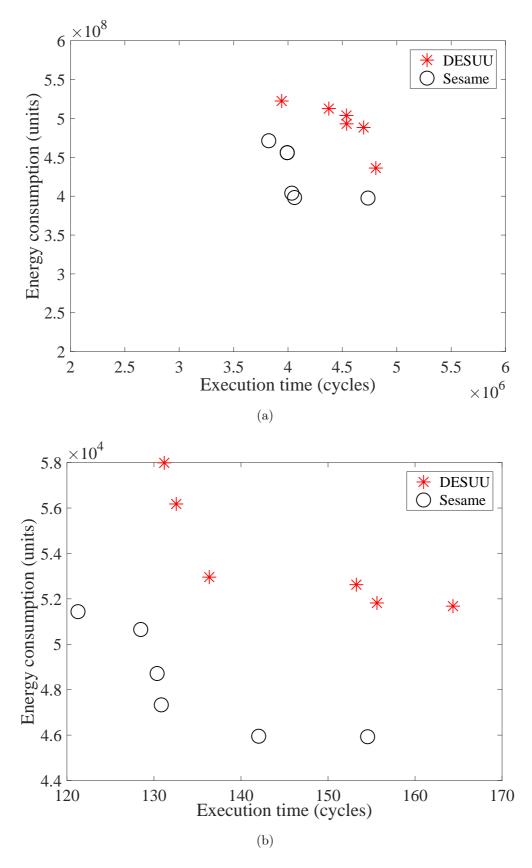

| 5.3  | The comparison estimation between the Sesame approach and the DESUU approach for (a) MJPEG testcase (b) MP3 testcase                 | 65 |

| 5.4  | Pareto frontiers generated by the Sesame approach and the DESUUU approach for (a) MJPEG testcase (b) MP3 testcase                    | 66 |

| 6.1  | (a) Block diagram of the ABS testcase. (b) The DTMC model with states $C$ and $F$ removed                                            | 72 |

| 6.2  | (a) Block diagram of the ACC testcase. (b) The DTMC model with states $C$ and $F$ removed                                            | 73 |

| 6.3  | (a) Block diagram of the H.264 testcase. (b) The DTMC model with states $C$ and $F$ removed                                          | 74 |

| 6.4  | (a) Block diagram of the JPEG testcase. (b) The DTMC model with states $C$ and $F$ removed                                           | 75 |

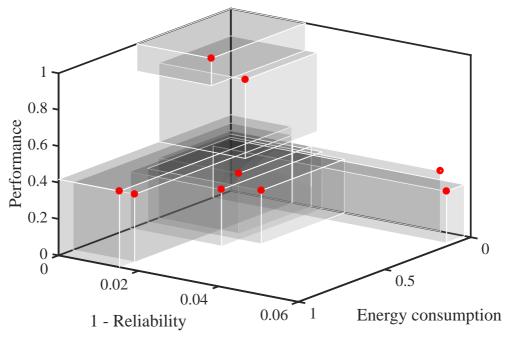

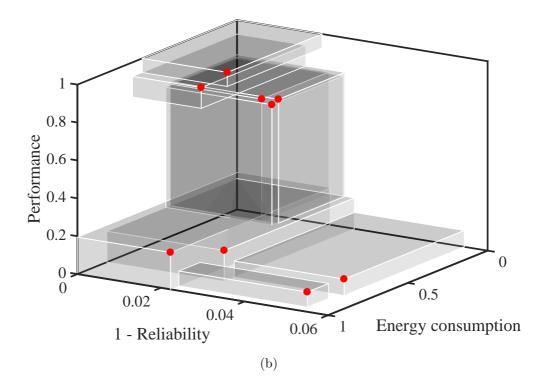

| 6.5  | Robust Pareto frontiers of the simulated testcases for 5% injected uncertainty: (a) ABS, (b) ACC.                                    | 76 |

| 6.6  | Robust Pareto frontiers of the simulated testcases for 5% injected uncertainty: (a) H.264, and (b) JPEG.                             | 77 |

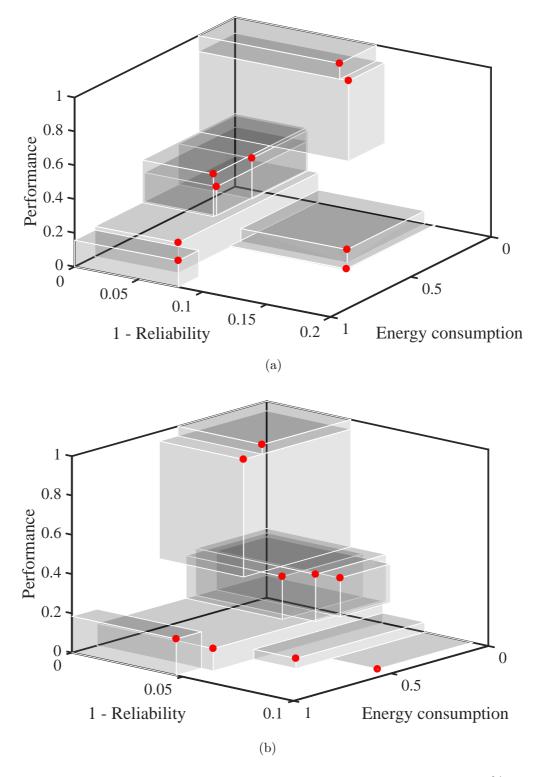

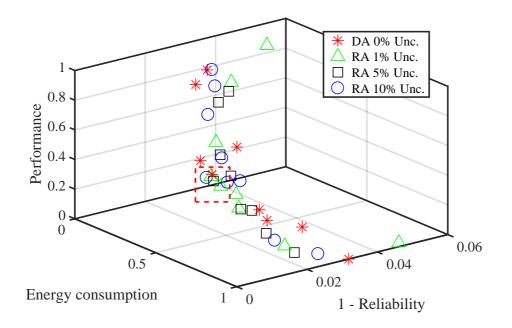

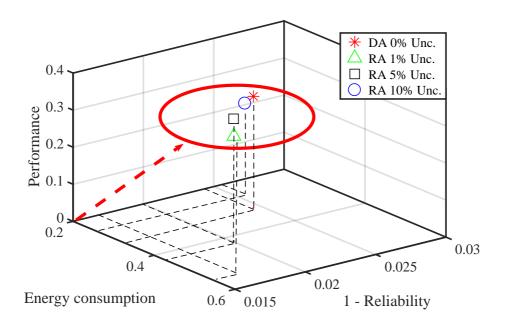

| 6.7  | Pareto frontiers of the ABS testcase for different levels of injected uncertainty: 0%, 1%, 5%, and 10%.                              | 80 |

| 6.8  | Comparison between the deterministic approach (DA) and the robust approach (RA).                                                     | 80 |

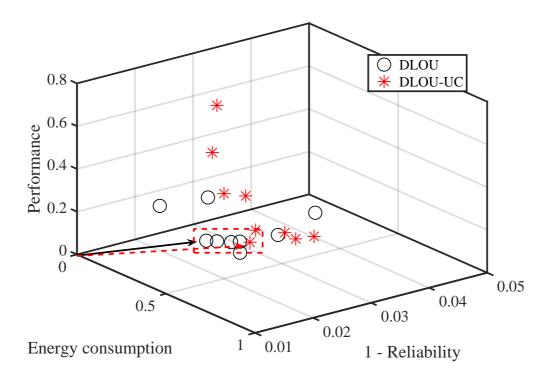

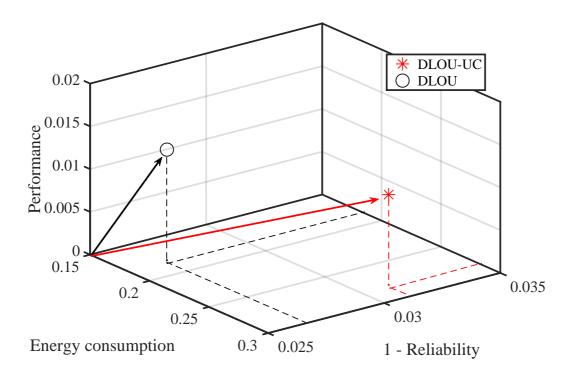

| 6.9  | Pareto frontiers of the ABS testcase for DLOU and DLOU-UC                                                                            | 83 |

| 6.10 | Comparison between the optimal solutions obtained by the DLOU technique and the DLOU-UC technique.                                   | 83 |

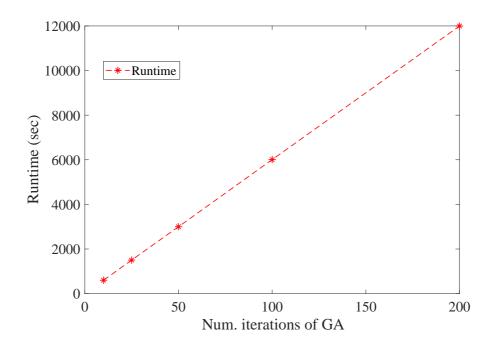

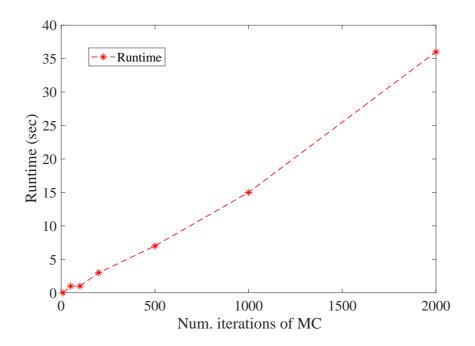

| 6.11 | Computational runtime of our tool versus the number of iterations of the NSGA-II genetic algorithm.                                  | 85 |

| 6.12 | Computational runtime of only one iteration of the top-level outer loop versus the number of runs inside the Monte Carlo simulation. | 86 |

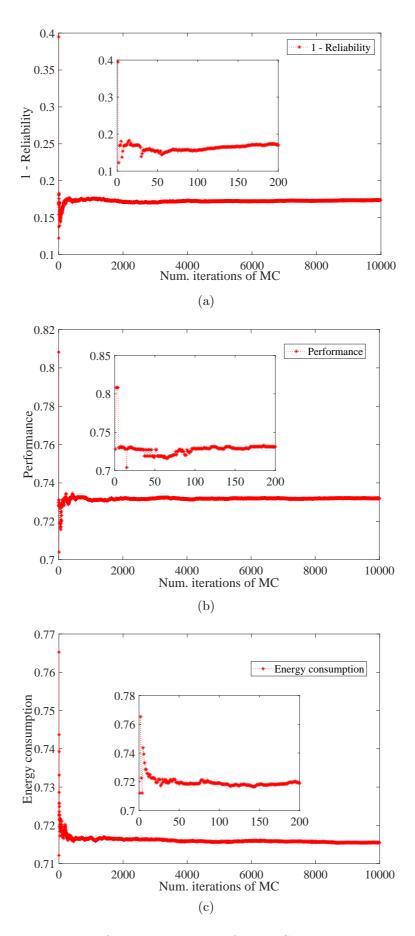

| 6.13 | Illustration of the convergence of the MC simulation based estimation.                                                               | 88 |

#### CHAPTER 1

#### **Problem Statement, Objective and Contributions**

#### 1.1 Problem Statement

Today, embedded systems can be found in many application domains, ranging from safety and mission-critical systems in avionics, automotive, nuclear plant control, and medical devices for multimedia, gaming, and communications. Future embedded systems will be increasingly complex and will contain tens to hundreds of heterogeneous cores. Due to continuous technology downscaling of fabrication processes, the design of embedded systems will face new challenges including: (1) increased design uncertainties due to variations in fabrication processes, supply voltages, and temperatures [1; 2]; (2) poor reliability and performance degradation caused by elevated rates of faults and increasingly adverse aging mechanisms [3; 4]; and (3) increased design complexity caused by heterogeneity of the hardware platform, diversity in hardware and software components, and new communication infrastructures such as networks-on-chip [5; 6].

In this thesis, we assume increased design uncertainties due to variations in fabrication processes, supply voltages, and temperatures, which have been discussed and modeled in recent literature [7; 8; 9]. Factors like these make for various design parameters or variables not to be deterministic anymore; instead, they become less precisely known or more uncertain, and many researchers started

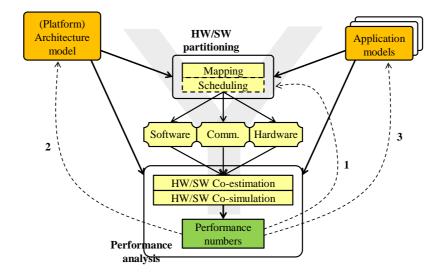

Figure 1.1: Conventional design flow for embedded systems. In this thesis, we focus on the problem of mapping. Dashed arrows labeled 1,2,3 indicate possible routes to go back in the design flow to change design decisions in order to improve the design.

to model them statistically rather than as fixed deterministic values. This uncertainty increases as we go to deeper nanometer technology nodes.

The traditional design process of embedded systems involves an automated design space exploration (DSE). DSE is an iterative process built mainly around the problem of mapping and scheduling of the application onto the architecture platform. The process typically follows a "Y-chart" design flow as illustrated in Fig. 1.1. During this DSE, the solutions generated and evaluated are as good and accurate (i.e., close to what they would be in reality in terms of different attributes such as reliability, execution time, and power consumption) as the accuracy of the model-based estimations that are employed. These estimations, in turn, rely on the accuracy of parameters that are used in the estimation models. If these design parameters become uncertain – increasingly so due to the reasons listed earlier – then, the optimization path during the design space exploration may become

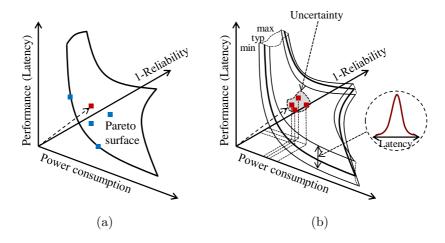

Figure 1.2: (a) Pareto frontier surface in traditional embedded systems design. (b) Uncertain Pareto surface where a design point degenerates into multiple solutions.

uncertain and diverge from the path towards the true optimal design solution.

In this context, it becomes desirable to be able to quantify such divergence and to develop a design methodology capable of finding design solutions that are the most likely, with a certain confidence, to be robust against uncertainties. These design solutions represent points on the Pareto frontier generated during the design space exploration, an example of which is shown in Fig. 1.2.a. However, when one considers uncertainties in the design process, the traditional Pareto surface in the solution space becomes uncertain as shown in Fig. 1.2.b. *This is the problem addressed in this thesis. As it will be described next, we propose a solution to the problem of mapping under uncertainties.*

#### 1.2 Objectives

In this thesis, we propose a design method that is able to identify robust design points on the uncertain Pareto frontier. The proposed method models and handles uncertainties directly. This method is implemented as a computer program (i.e., a design tool) that integrates uncertainty models and algorithms to solve the problem of mapping for hardware/software (HW/SW) design of embedded systems. These algorithms are capable of performing robust multi-objective optimization to effectively balance reliability, performance, and energy consumption. This tool will help embedded systems designers to identify the best design solution points on the uncertain surface from Fig. 1.2.b under assumed levels of uncertainties. This tool chooses as the best final solution the one closest to the "origin" of the 3D objective space from Fig. 1.2.b. The chosen solution represents a compromise among all three objectives. However, the designer can pick a different solution. For example, if performance is the most important for some application, then, a design point with the best performance can be selected, but likely with worse reliability and power consumption.

#### 1.3 Contributions

This thesis proposes a solution to the problem of mapping for embedded systems under uncertainties. To this end, the main contributions of this thesis include:

- A solution to the mapping problem for general purpose embedded systems while considering simultaneously reliability, execution time, and energy consumption. The solution is implemented as a design space exploration framework tool called DESUU (Design of Embedded Systems Under Uncertainty), which uses the Non-dominated Sorting Genetic Algorithm (NSGA-II).

- Models of uncertainty in design parameters. We investigate different levels of injected uncertainty and provide simulation results.

- A novel uncertainty aware analysis technique with consideration of both uncertainty correlations and different levels of uncertainty. The proposed uncertainty aware analysis technique is implemented as a framework tool called DESUU-II.

- Simulation results that demonstrate the advantages of the proposed techniques and solutions. In this thesis, we analyze an architecture platform constructed with both hardware and software components.

To the best of our knowledge, this work is the first to address the problem of multi-objective (reliability, performance, and energy) mapping for general purpose embedded systems under uncertainties.

#### 1.4 Thesis Organization

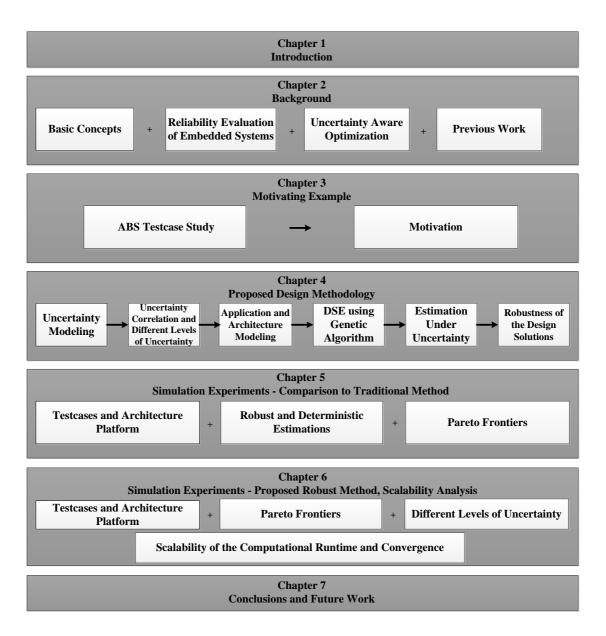

The organization of this thesis is depicted in Fig. 1.3. Chapter 2 provides background information. It starts with the overview of Electronic System-Level (ESL) design and the principle of Design Space Exploration (DSE). Then, it continues with a more detailed discussion of recent work on uncertainty aware and reliability oriented embedded systems design. Chapter 3 presents a description of the Anti-lock Brake System (ABS) application testcase, which is used in the motivating discussion for the proposed method. In Chapter 4, we present the uncertainty models. Then, we present the proposed method for solving the problem of mapping in embedded systems design under uncertainty. Chapter 5 presents the comparison simulation experiments with the traditional method. Chapter 6 presents the simulation experiments of the proposed robust method, as well as a computational

Figure 1.3: Thesis outline.

complexity analysis to study the scalability of the implemented tool. Finally, Chapter 7 concludes the thesis and discusses future work ideas.

#### CHAPTER 2

#### Background

In this chapter, we first introduce an overview of Electronic System-Level (ESL) design, which points out the level of abstraction for our target problem. Then, we introduce the Design Space Exploration (DSE) and the main challenges in this domain. In the third section, we review traditional classes of widely-used reliability evaluation approaches for embedded systems. In the fourth section, we introduce the basic techniques that are used for uncertainty aware optimization of embedded systems. Finally, we review the previous work related to the problem of mapping of embedded systems with the design objectives that include reliability, performance, and energy consumption.

#### 2.1 Electronic System-Level Design

The term hardware/software codesign appeared in the early 1990s to describe the confluence of hardware and software in Integrated Circuit (IC) design [10; 11]. Due to technology downscaling, the ICs have increased in complexity, time-to-market pressure, and development costs, the abstraction level at which the systems under design are expressed must be solved [12; 13]. The term Electronic System-Level (ESL) design, at which interfacing and reusing designs across different abstraction levels are facilitated, is resulted by these challenges. Hardware/software codesign at ESL reduces the time-to-market and design risks through the simultaneous

analysis, exploration, and design of hardware and software [14]. Nowadays, the major challenges in the design of electronic systems as stated in [15; 16] are:

- Allocation or architecture synthesis: It is the process of selecting a set of system resources such as processors, hardware intellectual property (IP) blocks, and their interconnects that compose the system architecture.

- *Mapping:* It is the process of mapping system functionality using tasks, processes, functions, and so on, onto the system architecture.

- *Scheduling:* It is the process of ordering the execution of functions, memory accesses, and communications on individual resources.

The set of all permutations of allocations, mapping, and scheduling decisions determines the design space of embedded systems.

#### 2.2 Design Space Exploration

The task of system synthesis is defined as the allocation of resources from the architectural model, mapping of the tasks onto the allocated resources, and scheduling the execution order of the tasks [17]. The feasible design solutions are represented by the permutations of allocations, mappings, and scheduling decisions that satisfy the given design constraints. The process of finding these feasible design solutions is called Design Space Exploration (DSE). Regarding a large number of design alternatives, such as the type and the number of processors, memory units, and interconnections, the design space is usually extremely huge, prohibiting manual search. In addition, the design objectives, such as reliability, performance, and energy consumption, of DSE are usually complex and related to each other, increasing the DSE complexity. Therefore, it is important to have a systematic DSE that is automated as much as possible at the early stage of embedded system design. Such automatic DSE is an iterative process built mainly around the problem of mapping and scheduling of the application tasks onto the architecture platform. For instance, Fig. 1.1 in Chapter 1 illustrates the "Y-chart" design flow. The main challenges in the DSE domain are:

- *Exploration techniques:* DSE requires good exploration algorithms which are suitable for large discrete search spaces with a large number of alternative solutions and multiple design objectives. For instance, in this thesis, we investigate the performance of an evolutionary algorithm to find design solutions for DSE with multiple design objectives.

- Evaluation of design solution points: How to model and evaluate the flexibly and efficiency of different design objectives is another challenging problem.

For example, in this thesis, we customize the evaluation function with a Monte Carlo simulation technique, to evaluate the design solution points with injected levels of uncertainty in design parameters.

#### 2.3 Reliability Evaluation of Embedded Systems

Reliability has been a primary design objective of DSE of embedded systems. Research into reliability evaluation of architecture platform has led to a variety of models, each of which focuses on a specific level of abstraction or system characteristics. This section reviews essential classes of widely-used and well-accepted reliability evaluation models for embedded systems.

#### 2.3.1 Combinatorial Models

Combinatorial models usually decompose the complex system into functional entities, such as units or subsystems, for reliability evaluation. Some of the classic combinatorial models are Reliability Block Diagram (RBD) and Fault Trees (FT).

#### **Reliability Block Diagram**

RBD is a reliability modeling approach in reliability evaluation of embedded systems architecture platform. An RBD models the structural relationship of how the sub-system failure and the components failure combine to lead to system failure. When a RBD approach is used, the system is decomposed into *Reliability Blocks* that have particular failure characteristics. The connections between the reliability blocks construct the path of the system behavior. If it is possible to find at least one way from the start of the RBD to a particular component through operational components, the particular component is considered functional. These components can be organized in series, parallel or other structure. An organization of a set of blocks of components that are configured in parallel within the blocks is called Series-Parallel (SP) system [18]. In SP systems, we call *subsystem* for a component with its parallel redundancies, and we compute the reliability of the subsystems independently from the other parts of the system. Therefore, in SP RBDs, the overall system becomes a series of connected subsystems whose reliability is known. Hence, the overall reliability of the system can be analytically computed under SP assumption. RBD is a reliability modeling approach in reliability evaluation of embedded systems architecture platform. An RBD models the structural relationship of how the sub-system failure and the components failure combine to lead to system failure. When a RBD approach is used, the system is decomposed into *Reliability Blocks* that have particular failure characteristics. The connections between the reliability blocks construct the path of the system behavior. If it is possible to find at least one way from the start of the RBD to a particular component through operational components, the particular component is considered functional. These components can be organized in series, parallel or other structure. An organization of a set of blocks of components that are configured in parallel within the blocks is called Series-Parallel (SP) system [18]. In SP systems, we call *subsystem* for a component with its parallel redundancies, and we compute the reliability of the subsystems independently from the other parts of the system. Therefore, in SP RBDs, the overall system becomes a series of connected subsystems whose reliability is known. Hence, the overall reliability of the system can be analytically computed under SP assumption.

#### Fault Trees

FT is another reliability evaluation approach that is widely used in the literature [19; 20]. FT construction is a deductive, top-down process where the failure events are organized into a tree structure. In the analysis of the reliability of the target architecture platform, the effects of lower-level faults and events are systematically propagated by quantifying the reliability of a higher-level abstraction. Different types of FTs, such as Component Fault Trees (CFT) [21] and State Event Fault

Trees (SEFT) [22], are used in the reliability evaluation in different contexts and abstraction levels.

#### 2.3.2 Markov Model

Markov modeling is used for analyzing complex probabilistic systems taking into consideration of repair mechanisms and the order of events in the system. A Markov model is constructed by a set of equations that describe the probabilistic transitions among the states and initialization probability distributions of the starting states. One important property of a Markov model is that the current state transitions are independent of the history of the state transitions, *i.e.* transition from state i to state j depends only on the state i, and is independent of the history that led to state i. This property indicates that the complete history in Markov model is summarized in the current state of the process.

#### Discrete Time Markov Chains (DTMC)

DTMCs are finite state machine formalisms with probabilities of transitions between states that are widely used in modeling discrete-time dynamic systems. A DTMC can be applied to represent all the relevant states of software execution and the probability to transfer from one state to another. Among all the states, the starting state is called the *initial state* and one or more among the other states represent successful completion of execution or occurrence of a failure. The formal definition of a DTMC can be expressed as a tuple  $(S, s_0, P, L)$  where,

• S is a finite set of states

- $s_0$  is the *initial state*

- $P: S \times S \rightarrow [0, 1]$  is the transition probability matrix

- $L: S \to 2^{AP}$  is the labeling function

DTMCs can be used to model both a single transition system and the synchronous composition of many systems. The labeling function describes the mapping process from the states to the set of atomic propositions (AP). P(s, s')denotes the probability of making a transition from state s to the states s'. In a DTMC,  $\sum_{s' \in S} P(s, s') = 1$  for all state  $s \in S$ , which implies that even terminating states should have an outgoing transition to itself with a probability 1. When a system is modeled as a DTMC, the execution is represented by a path through the DTMC.

#### 2.4 Uncertainty Aware Optimization of Embedded Systems

Uncertainty aware optimization methods for embedded systems have been proposed only recently. The work in [23; 24] are the latest attempts to address the problem of uncertainty in reliability evaluation. Both [23; 24] use a Monte Carlo Simulation techniques to handle uncertainty in design parameters, and evolutionary algorithms for optimization of reliability.

#### 2.4.1 Monte Carlo (MC) Simulation

The MC simulation takes samples from the input parameters of the architectural elements, which vary in the probability distribution. Any sampled parameter of an architectural element may be contributed to more than one parameter in the evaluation model. Every time a sample is taken from an input distribution, all model parameters dependent on this parameter are updated. The steps that are involved in the MC simulation are as follows:

- Sample: A sample is taken from the probability distributions of each parameter. We draw a sample from these distributions as follows:

(a) Obtain the Cumulative Distribution Function (CDF) of the parameter from its PDF.

- (b) Generate a random number x from the uniform distribution (0, 1).

- (c) Obtain  $CDF^{-1}(x)$ .

- Update: From the samples obtained from the input distributions, the numerical values for the evaluation model parameters are updated. Since more than one parameter of the probabilistic model may refer to a setting in the architecture, a subscription mechanism is proposed. Parameters of the evaluation model are subscribed to uncertain parameters in the architecture platform. When we sample a parameter from the input distribution for a specific architectural setting, all the subscribing model parameters are updated and recomputed.

- Compute: Analytically simulate the model and obtain the computed results.

#### 2.4.2 Evolutionary Algorithms for Optimization

For the design of embedded systems with multiple conflicting design objectives, one can provide either a weight function to combine multiple objectives or a multiobjective exploration technique to scan the search space simultaneously. The former method needs to choose the proper weight coefficients for the optimization function and results in a single optimized solution. In contrast, the later method determines not only one optimized solution but rather a set of Pareto frontiers. Therefore, population-based methods, such as evolutionary algorithms, have received a lot of attention in this area. Among them, the Non-dominated Sorting Genetic Algorithm (NSGA)-II has been shown to perform efficiently for systemlevel synthesis.

For the optimization process, NSGA-II uses an initial population of chromosomes consisting of alleles. Each allele in a chromosome represents a mapping of a task from the application to a component in the architecture platform. The initial population of deployment architectures is generated at random. The crossover and mutation operators are used to create new chromosomes by combining existing ones or changing the mapping of a single task to another component on the architecture platform. Then, all the chromosomes are evaluated, according to the evaluation function in NSGA-II, and selected to form the new parents' population. Details about the NSGA-II will be discussed in Chapter 4.

#### 2.5 Previous Work

In this thesis, we focus on the problem of mapping of embedded applications to multicore systems-on-chip (SoCs) platforms with consideration of specified levels of uncertainty and with the primary objectives that include reliability, performance, and energy consumption. The problem of HW/SW co-design for embedded systems has been studied extensively in the past.

It was formulated as multi-objective optimization in studies of systemlevel synthesis [25; 26; 27; 28] as well as of platform configuration [29]. The former focuses on solving the problem of mapping a task-level application onto a heterogeneous architecture constructed with both hardware and software components. The latter includes parameter tuning for the platform architecture and its configuration space exploration. The work in [25] solves this multi-objective optimization problem by using multi-objective evolutionary algorithms (MOEAs). Simulation results showed that MOEAs provide the designer with a set of solutions in a reasonable amount of time. The authors of [27] apply a *divide-and-conquer* approach to solve the multi-objective mapping problem. The study in [26] focuses on evaluating the performance of various state-of-the-art task mapping heuristics, both at design time and at runtime, by using the rSesame framework on a reconfigurable architecture. The work in [28] proposes a hybrid task mapping algorithm, which combines a static mapping exploration and a dynamic mapping optimization for heterogeneous MPSoCs, and achieves an overall improvement of system efficiency. However, that work only considers performance as the main design objective. The study in [29] focuses on exploring architectural parameters, such as processor type, memory subsystem, and bus communication, that make up the hardware kernel of a parameterized SoC platform for the design of embedded systems with the consideration of power consumption and performance constraints.

Several previous solutions to the mapping problem have been integrated into computer-aided design (CAD) automation tools. For instance, these tools include architectural exploration environments, such as those described in the following paragraphs:

Metropolis [30] is an integrated electronic system design environment for simulation, formal analysis, and synthesis of embedded systems. It is based on the *metamodel* concept, which can support not only functional capture and analysis but also architecture description and the mapping of functionality to architectural elements. The Metropolis metamodel's formal semantics allow embedding computation models into a rigorous framework that favors design reuse and design chain support. It was used for applications from automotive to wireless communication and video applications.

MESH [31] is a performance modeling environment which captures software-on-hardware in concurrent, layered thread relationships in SoC designs. It provides a primary interface between functional and *instruction set simulator* (ISS) models and allows for early and high-level performance modeling without the need for the knowledge of ISS or complete software models. It also efficiently tracks heterogeneous design trade-offs while considering design objectives that include performance. However, as an interface between the high-level functional model and the low-level ISS model, it has an increased development complexity. SCE [32] is a system-level design framework, which uses the SpecC specification language. It follows a *specify-explore-refine* methodology, with support for heterogeneous platforms constructed of both hardware and software components, IP blocks, and buses for communication. It is an automated design flow with a toolchain from specification down to hardware/software implementation. It allows rapid and extensive design space exploration and thus can find out an optimal implementation quickly.

Artemix [33] is a workbench that provides modeling and simulation methods and tools for evaluating performance efficiently and for exploring design space of heterogeneous embedded multimedia systems. By transforming dataflow actors in the intermediate mapping layer, and transforming coarse-grained application events into finer grained architecture events, it can bridge the abstraction gap between application and architecture models. It is composed of mainly two system-level modeling and simulation environments, which make it powerful but complicated.

ESPAM [34] aims at automating multiprocessor system design, programming, and implementation. It transfers the design specification and programming from the Register Transfer Level (RTL) and C level to a higher level of abstraction of the system level. When it is applied, it first specifies a multiprocessor system at a high abstraction level. Then, it refines this specification down to a real implementation. ESPAM reduces the design time beginning from the system-level specification and going down to complete implementation.

SHARA [35] is a scenario-based hierarchical run-time adaptive resource

allocation framework. This framework integrates a hierarchical resource management mechanism, where a global resource manager controls the workload distribution among tiles and the local resource manager optimizes the resource allocation for the assigned applications to reduce the complexity of the task mapping problem at runtime. It also includes a hybrid approach, which combines the design-time optimization of DSE with run-time mapping re-optimization, for mapping applications to the underlying resources, and thus handle the complex and dynamic application workloads for MPSoC systems. In addition, SHARA includes a selfadaptive scheduler for adaptivity throttling. SHARA can support large numbers of workload scenarios with near-optimal mappings. It can also adapt its behavior according to the user behavior. However, it does not consider the power consumption and reliability or uncertainty as design objectives.

These tools facilitate flexible system-level performance evaluation by providing support for mapping a behavioral application specification to an architecture specification. *However, most of these tools have not considered reliability or uncertainty.* Reliability has become a primary design concern in optimization techniques of embedded systems. The review in [36] discussed several studies that focused on architectures constructed only with software components. The authors pointed out that, at that time, only a few researchers directly considered uncertainty and/or reliability as design objectives. The study in [37] formulates a framework to evaluate the system reliability under uncertainty. The work in [38] introduces a simulation-based method which uses Discrete Time Markov Chains (DTMC) and probabilistic model checking to accommodate a diverse set of parameter range distribution when measuring the uncertainty. The work in [39] proposes to automatically incorporate Imperfect Fault Coverage (IFC) into the reliability model, in order to accurately analyze the reliability of complex systems including nested redundancies and repeated components. Their approach can evaluate system reliability more accurately at reasonable computation time and memory overhead compared to previous IFC-aware approaches.

Reliability has become a primary design concern also in networks-on-chip (NoC) and multicore processors as well. As such, it started to be considered alongside more traditional design objectives like performance and energy consumption. For example, the study in [40] presented a run-time resource manager that finds the most effective mapping of tasks on the processing nodes to optimize system reliability while leveraging on performance and communication energy in NoC-based many-core architectures. Similarly, the study in [41] presented a neural network based reliability estimator and thread migration for dynamic reliability management for chip multiprocessors. Furthermore, the work in [42] investigates the use of dynamic voltage and frequency scaling (DVFS) as a mechanism for dynamic reliability management for chip multiprocessors.

However, the majority of the previous work did not consider uncertainty or reliability in the design process of embedded systems. The studies in [23; 24] are recent attempts to capture uncertainty in the process of optimization of embedded systems. The work in [23] proposed a novel robust optimization approach that deals with uncertain parameters during the design phase of software-intense systems. But, reliability was the only objective considered during the optimization process. In addition, the authors only focused on architecture platforms constructed with software components. The study in [24] proposed an uncertainty-aware reliability model for the design space exploration of embedded systems. But, similarly to the study in [23], reliability was considered as the only uncertain parameter. In addition, the authors made an unstated assumption that the components are affected by one uncertainty source (e.g., one correlation group). In fact, the components are usually affected by multiple uncertainty sources with different levels of uncertainty, and the uncertainty in design parameters is the combination of the influence of different uncertainty sources. For instance, the failure rates of the components of an embedded system from the automotive application domainshich are located close to both the engine and the cooling fan can be affected by both the engine heat and the cool air from the fan. Moreover, the authors did not explore the impact of different levels of uncertainty on the design parameters.

Therefore, while these works focused on formulating reliability estimation techniques with consideration of uncertainties, in this thesis, we take that further and integrate such techniques in a more comprehensive approach that also considers performance and energy consumption, not only reliability. In addition, we investigate different levels of uncertainties and analyze both uncertainty correlation and different levels of uncertainty.

#### 2.6 Summary

This chapter presented the background and the related work for uncertainty aware mapping of embedded systems for reliability, performance, and energy consumption. In next chapter, we will introduce the motivation of this thesis.

#### CHAPTER 3

#### Motivating Example

In this chapter, we introduce the Anti-lock Brake System (ABS) application testcase. The ABS testcase study represents a specific problem from the automotive industry. It maps the components of the ABS application to the heterogeneous architecture of the embedded system. We use it to present the motivation for the work proposed in this thesis. We use both the traditional point-estimate and the proposed robust-estimate approaches to evaluate the system reliability, execution time, and power consumption of the ABS testcase. Simulation results show that there is a significant difference between these two estimation approaches. Therefore, we conclude that a new design method, which is capable of modeling uncertainty to provide reliable and robust design solutions, is needed for the design of future high performance heterogeneous embedded systems.

#### 3.1 ABS Testcase Study

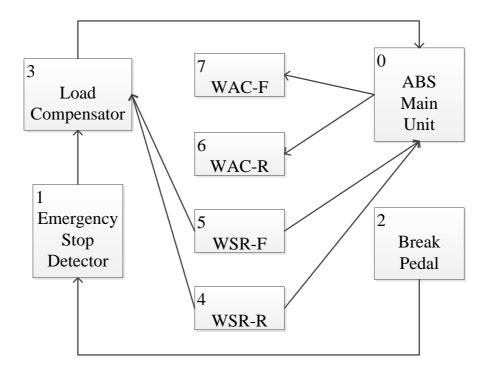

The ABS is designed to optimize the braking effectiveness in order to keep wheels rolling on the road and to reduce the breaking distance [43; 44]. It is important for the car control as it is used to prevent the lockup of the wheels during the braking action [45]. The block diagram of a typical ABS is shown in Fig. 3.1. It includes the blocks labeled from 0 to 7, as components that interact as shown by the arrows. The block labeled 0 is called the ABS main unit. Its role is to

Figure 3.1: ABS software components and interactions.

prevent skidding and to help drivers control the wheels on wet and slippery roads. Block 1 is the Emergency Stop Detector, whose role is to maximize the brake pressure if it detects any sudden pedal action associated with an emergency stop. Block 2 is the Brake Pedal Sensor, whose role is to read from the pedal sensor and send the data through to Block 1. Block 3 is the Load Compensator, which is used to improve the braking performance by compensating uneven braking due to the heavy or unbalanced loading of the vehicle [46]. Blocks 4 to 7 represent the transceiver software components dedicated to each wheel, which communicate with sensors and brake actuators. More specific, WAC stands for wheel actuator controllers and WSR represents wheel sensor readers.

Figure 3.2: Motivation of this thesis.

#### 3.2 Motivation

If we used traditional design methods to map the ABS testcase described above, then, in such methods we would work with point-estimate parameters. However, these parameters can become uncertain as discussed in Chapter 1. If design parameters become uncertain (e.g., the failure rate of CPUs who are located close to the engine or the cooling fan can be significantly affected by the different temperatures), then, the design space exploration to solve the mapping problem may lead to suboptimal solutions. In building the motivation for this thesis, we ask ourselves two questions, as illustrated hierarchically in Fig. 3.2:

- 1. Why do we need to consider uncertainty in design parameters of embedded systems? In addition, why do we need to consider uncertainty in the estimation of reliability, performance, and energy consumption?

- 2. Why do we need to consider both different levels of uncertainty and uncertainty correlations?

Figure 3.3: Histogram of system reliability. All histograms are obtained using  $10^5$  parameter samples during the estimation process.

Figure 3.4: Histogram of execution time. All histograms are obtained using  $10^5$  parameter samples during the estimation process.

#### 3.2.1 Answering Question 1

In answering the first question, we used the proposed mapping algorithm described later in this thesis to map the ABS testcase to a platform architecture also described later in Chapter 6. The proposed method has the ability to model uncertainty in design parameters. We use it to estimate the reliability, which we consider

Figure 3.5: Histogram of energy consumption. All histograms are obtained using  $10^5$  parameter samples during the estimation process.

to be affected by uncertainty. Details about the estimations under uncertainty for reliability, performance, and power consumption will be described later in Chapter 4.

In order to report the difference obtained when considering uncertainty in design parameters of embedded systems, we implement both the robust-estimate approach and the point-estimate approach in our framework which will be discussed later in Chapter 5. In this experiment, we use the same given mapping (e.g., round-robin mapping) when estimating the design objectives such as system reliability, execution time, and energy consumption through both approaches. The reliability, execution time, and energy consumption of the system as estimated by our tool are shown in Fig. 3.3, Fig. 3.4, Fig. 3.5. This figure also shows the estimated reliability, execution time, and energy consumption when design parameters are estimated using the traditional point-estimate approach. Fig. 3.3 depicts the histogram of reliability obtained using 10<sup>5</sup> samples during the Monte

Carlo estimation. It can be seen that the mean value of the estimated reliability is 0.9424, while the point-estimate reliability is 0.9459. This represents a 13.4% difference between these two estimations. From this experiment, it can be concluded that when design parameters are subject to uncertainty, estimation of reliability with the traditional point-estimate approach may be significantly inaccurate. In other words, if we use traditional point-estimate values for reliability, we would overestimate it. This may lead to suboptimal solutions.

Similarly, if we consider uncertainty in design parameters that affect performance and energy consumption, the proposed tool provides the estimations shown in Fig. 3.4 and Fig. 3.5 Again, we can see significant differences between these estimations and the estimated values with the traditional approach. Fig. 3.4 shows that the mean value of the estimated execution time is 0.1348s, while the execution time of the point-estimate approach is 0.1215s. This represents a 9.5% difference. Similar results are found for the estimation of energy consumption. The energy consumption estimated with the proposed tool is 809.9774uJ, while the point-estimate is 615.51uJ. This represents a 29.9% difference between these two estimation approaches. Therefore, in answering the question why to consider uncertainty in design parameters, we find out that there are significant differences between the traditional point-estimate and the robust-estimate of reliability, execution time, and energy consumption estimations. Large differences in these estimations may lead to suboptimal design solutions when design parameters are affected by uncertainties.

To address that, the next chapter proposes a design method capable of

Figure 3.6: Histogram of system reliability for LOU and LOU-UC techniques.

robust multi-objective optimization. This method is implemented as a computeraided design (CAD) automation tool constructed with Monte Carlo and evolutionary algorithms, which can overcome the issues described earlier.

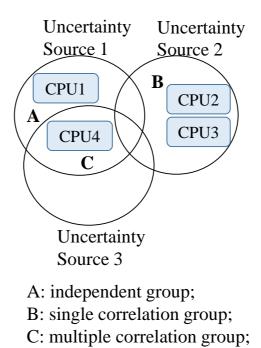

# 3.2.2 Answering Question 2

Existing uncertainty-aware analysis techniques consider either only Uncertainty Correlations (UC) or different Levels of Uncertainty (LOU). However, in practice, it is possible that factors like temperature may affect several system components simultaneously. This introduces uncertainty correlations between system components. In addition, these components are usually affected by multiple uncertainty sources with different levels of uncertainty. Thus, different levels of uncertainty exist between these system components. Therefore, we need to consider different levels of uncertainty as well as uncertainty correlations when we analyze uncertainty in design parameters.

In order to report the difference obtained with and without the consideration of uncertainty correlations, we implement in the proposed tool the capacity to model both situations: different levels of uncertainty and uncertainty correlations. We use the same ABS testcase and the same mapping as in Section 3.2.1 to evaluate the design solution in both situations. Fig. 3.6 shows the histogram of reliability obtained with LOU (DESUU-I) and LOU-UC (DESUU-II) techniques using  $10^5$  samples during the Monte Carlo estimation. We can see that there exists a significant difference between the two mean values of the estimated reliability. This shows that when we consider only different levels of uncertainty, the estimated reliability spans a relatively small range with high probability. In the case of the LOU-UC, there exists a much smaller difference in the relative frequency value of bounds and of the mean value of the estimated reliability. This shows that the components affected by the same uncertainty sources, which is captured as uncertainty correlations, may result in a reliability distribution significantly different. In other words, if we consider only the different levels of uncertainty of the components in our modeling, we may overestimate the system reliability, which can lead to inaccurate reliability estimation.

To address this issue as well, in the next chapter, we propose a novel uncertainty-aware analysis technique to consider or capture both aspects: different levels of uncertainty and uncertainty correlations of the components.

#### CHAPTER 4

# Proposed Design Methodology

How can we design high performance heterogeneous embedded systems that are reliable and robust to uncertainty in design parameters? This chapter seeks to answer this question by laying the foundation for uncertainty modeling and robust multi-objective optimization for embedded systems design. A design flow, which is capable of robust multi-objective optimization incorporated within a CAD automation tool constructed with Monte Carlo and evolutionary algorithm, is developed. The proposed design flow is uncertainty-aware in the sense that it is able to capture and directly deal with uncertainty in design parameters. It is reliabilityoriented as reliability is included as a design concern in addition to performance and energy consumption. The proposed probabilistic uncertainty models and algorithmic innovations to solve the multi-objective mapping problem are discussed in the following sections.

### 4.1 Approach Overview

The proposed design flow is essentially an iterative process that uses an enhanced evolutionary algorithm, to solve the problem of mapping. The problem of mapping is the problem of finding the best placement of application tasks and communications between tasks onto the architecture platform.

The block diagram of the proposed design flow under uncertainties is

Figure 4.1: Block diagram of the proposed design method for embedded systems mapping under uncertainties.

shown in Fig. 4.1. The *outer loop* represents the iterative process of the design space exploration. The *inner loop* represents the iterative process of the Monte Carlo simulation technique that we employ for the estimation of objective functions under uncertainty. The primary objectives that we consider in this thesis include reliability, performance (measured as execution time), and energy consumption. Thus, the problem we attempt to solve is a multi-objective problem under specified levels of uncertainty. The output of the optimization process illustrated in Fig. 4.1 is a set of robust solution points that form the robust Pareto frontier in the three dimensional objective space (1-reliability) vs. performance vs. energy consumption. In the next sections, we describe the primary steps of the proposed design flow. These steps correspond to different blocks from the diagram in Fig. 4.1.

### 4.2 Uncertainty Modeling

The proposed design flow directly considers the uncertainty in design parameters and variables. The design parameters in embedded systems can be grouped into system-specific parameters (e.g., hardware and software failure rates, throughput metrics) and environment-related parameters (e.g., operational and usage profile of the system). The accuracy of these parameters is adversely affected by various kinds of uncertainties. Generally, it is difficult to determine accurate values of some of these parameters. Other parameters require information that is only available in later stages of the design process or depend on application-specific workloads, and thus are only available at runtime. Hence, the parameter values used in design-time optimizations represent estimations that are subject to uncertainty.

Uncertainty arises from the lack of knowledge regarding the true value of a quantity of interest. Uncertainty implies that optimization decisions might be non-optimal because one might expect one outcome but something quite different might in fact occur. Generally, uncertainty is heterogeneous and diverse. Sources of uncertainty include: uncertainty of data and model parameters, uncertainty about model choice, and uncertainty about the future. In the nanometer scale domain, uncertainty arises from temperature and voltage gradients, variations in application workloads, and from fabrication process and circuit parameter variations. Many design parameters and variables can be affected by uncertainties. For instance, failure rates of software components depend on the amount of testing and complexity of the algorithms contained in the component. Likewise, the failure rate of a hardware component can depend on the operational environment. Hence, capturing parameter uncertainty into hardware platform and application description is difficult.

In the proposed design flow, we employ probability distributions to specify design parameters affected by uncertainty. This approach allows the design parameters to be given as probability distributions (continuous or discrete) in any mixture. The use of probability distributions entails the support for conversion from other complementary approaches. For example, interval estimation can be represented as a uniform distribution while the mean-variance estimation methods can be replaced with a normal distribution with the same mean and variance [23].

The Uncertainties block on the top left-hand side from the diagram in Fig. 4.1 represents the uncertainty injection process. There has been significant work studying uncertainty in various fields including engineering, mathematics, and other sciences [47; 48; 49]. However, it is generally agreed that there is no single model for handling any type of imperfect information. Therefore, similarly to [23], we propose to adopt the most general approach to capture uncertainty: design parameters and their variation can be specified as generalized, continuous or discrete, probability distributions in any mixture. Aside from its generality and ability to accommodate any probability distribution, this approach has the advantage of being able to accommodate complementary approaches as well. For instance, we can use uniform distributions to convert interval estimates into the proposed framework. On the limitations side, combining different probability distributions is usually analytically intractable, and therefore we must resort to Monte Carlo simulation based techniques in order to quantify figures of merit of interest

Figure 4.2: (a) To inject 5% uncertainty for a parameter characterized by a uniform distribution whose mean is 100 for example, we generate samples from a uniform distribution defined on the interval  $[a = \mu - 0.05 \cdot \mu/\sqrt{3}, b = \mu + 0.05 \cdot \mu/\sqrt{3}]$ . (b) The interval used for the case of a Gaussian distribution whose mean is  $\mu$ .

(described later). This, in turn, may increase the computational runtime.

Uncertainty can be injected into the application or/and the architecture, depending on what design parameters are assumed to be affected by uncertainties and to what degree. This injection will be done in different amounts or degrees during the design space exploration depicted in Fig. 4.1. The injection process amounts to generating samples from pre-specified probability distributions during the Monte Carlo simulation technique used to evaluate reliability, execution time, and energy. Because we allow working with any type of probability distribution, we must define what is meant by *injecting a given percentage of uncertainty* into the design parameters of interest. We do that by pre-specifying the mean and the variance of the probability distributions out of which the sampling is done according to the rules listed in Table 4.1.

The rationale behind the rules presented in Table 4.1 can be explained

with the help of Fig. 4.2. For example, let us assume that the uncertainty is modeled for some design parameter with a uniform distribution. Then, modeling 5% of uncertainty in this design parameter during the design space exploration is achieved by having the MC simulation (discussed later in a different section) generate samples from an interval as shown in Fig. 4.2.a for the case when, for example, the mean is  $\mu = 100$ . That is because the variance (whose square root is the standard deviation,  $\sigma$ ) is given by the expression  $Var = (b - a)^2/12$ . In the case of a Gaussian distribution, samples are generated randomly from a distribution  $Gaussian(\mu, \sigma)$  but only samples falling inside the interval  $[\mu - 3\sigma, \mu + 3\sigma]$ , as shown in Fig. 4.2.b are accepted, which represent 99.7% of all generated samples. The case of the beta distribution is similar to that of the Gaussian case. The difference is only in the actual confidence level, which can be different from 99.7%. Note that similar rules can be derived for any other type of distribution that we may be interested in using to model parameter uncertainty. For simplicity, in this thesis, we restrict ourselves to using uniform and Gaussian distributions for modeling the execution time and the power consumption of architecture components and for modeling the transition probabilities inside the reliability model (discussed later). In addition, beta distribution is used to model failure rates of components, similarly to the study in [23]. However, our framework is flexible and can easily

Table 4.1: Rules for defining mean and variance of distributions from which sampling must be done to achieve a certain degree of uncertainty injection.

| Probability             | Uncertainty                            | Uncertainty                            | Uncertainty                           |

|-------------------------|----------------------------------------|----------------------------------------|---------------------------------------|

| Distribution            | 1%                                     | 5%                                     | 10%                                   |

| $Uniform(\mu, \sigma)$  | $\sigma = 0.01 \cdot \mu_1 / \sqrt{3}$ | $\sigma = 0.05 \cdot \mu_2 / \sqrt{3}$ | $\sigma = 0.1 \cdot \mu_3 / \sqrt{3}$ |

| $Gaussian(\mu, \sigma)$ | $\sigma = 0.01 \cdot \mu_1/3$          | $\sigma = 0.05 \cdot \mu_2/3$          | $\sigma = 0.1 \cdot \mu_3/3$          |

| $Beta(\mu, \sigma)$     | $\sigma = 0.01 \cdot \mu_1/3$          | $\sigma = 0.05 \cdot \mu_2/3$          | $\sigma = 0.1 \cdot \mu_3/3$          |

Figure 4.3: ABS application mapping problem. We only show the mapping of the tasks for simplicity.

accommodate other probability distributions if embedded designers find their data to fit better such distributions.

# 4.3 Application Modeling

To be able to formulate the mapping problem in a computer program like the one developed in this thesis, one must work with models for both *Application* and *Architecture* in Fig. 4.1. In this thesis, we adopt the notation from [50; 51; 52] and model applications using Kahn Process Networks (KPNs), which are among the most popular models of computation used in embedded systems design [27; 33]. A KPN is represented as an application directed graph  $G_{AP}(V_{AP}, E_{AP})$ . Each node or vertex  $v_i, i \in \{1, ..., |V_{AP}|\}$  corresponds to a process or task of  $G_{AP}$ . For each vertex  $v_i$ , we define  $B_i = \{e_j \in E_{AP}\}$  to be the set of application channels connected to vertex  $v_i$ . When a vertex is mapped to a hardware component,  $ht_i$  represents the hardware execution time. When the task can be executed on multiple hardware cores,  $ht_i$  becomes a set  $ht_i = \{ht_{i1}, ht_{i2}, ..., ht_{iU}\}$ , where U is the number of hardware cores on which the task can be executed. When a vertex is mapped to a software component,  $st_i$  is the software execution time. When the task can be executed on multiple software components,  $st_i$  becomes a set  $st_i = \{st_{i1}, st_{i2}, ..., st_{iV}\}$ , where V is the number of software components on which the task can be executed. Each edge  $e_j, j \in \{1, ..., |E_{AP}|\}$  corresponds to a data or control link between two different tasks of  $G_{AP}$ . If a communication link is mapped onto a memory core,  $mt_j$  represents the memory access time, which will be added to the path delay. When the link can be mapped to multiple memory components,  $mt_j$  becomes a set  $mt_j = \{mt_{j1}, mt_{j2}, ..., mt_{jW}\}$ , where W is the number of memory components on which the link can be mapped to.

For example, Fig. 4.3 shows the application graph of the ABS testcase. It includes 8 tasks and 9 communication channels. The graph  $G_{ABS}$  includes the nodes set  $V_{ABS} = \{v_i | i \in \{1, 2, ..., 8\}\}$  and the edges set  $E_{ABS} = \{e_j | j \in \{1, 2, ..., 9\}\}$ . Since there are 5 hardware components in the architecture platform shown in Fig. 4.3, when a node  $v_i$  is mapped to a hardware component, the hardware execution time  $ht_i$  becomes a set  $ht_i = \{ht_{i1}, ht_{i2}, ..., ht_{i5} | i \in \{1, 2, ..., 8\}\}$ . Similarly, since there are also 5 software components in the target architecture for the ABS application, when a vertex is mapped to a software component, the software execution time  $st_i$  becomes a set  $st_i = \{st_{i1}, st_{i2}, ..., st_{i5} | i \in \{1, 2, ..., 8\}\}$ . Likewise, if a communication link is mapped onto a memory core, the memory access time  $mt_j$  becomes a set  $mt_j = \{mt_{j1}, mt_{j2} | j \in \{1, 2, ..., 9\}\}$ .

### 4.4 Architecture Modeling

The architecture model is also represented by a graph  $G_{AR}(V_{AR}, E_{AR})$ , where the sets  $V_{AR}$  and  $E_{AR}$  denote the architecture components and the connections between them. The set of architecture components consists of two disjoint subsets: the set of processing cores (P) that include hardware and software elements and the set of memories (M),  $V_{AR} = P \cup M$ . The delay of a communication link between two different architecture components is denoted as  $lt_{pq}$ , with  $p, q \in \{1, ..., |E_{AR}|\}$ . The power dissipations are denoted as  $p_c$  for the core c during execution, as  $p_m$  for the memory core m, and as  $p_l$  for the communication links. In this thesis, we assume that the architecture platform is given because we do not address the problem of architecture synthesis.

For instance, Fig. 4.3 also shows the architecture platform, onto which the ABS application will be mapped. It includes 5 hardware components (e.g., FPGAs) and 5 software components (e.g., CPUs). These architecture components communicate through the common bus link. The software (SW) components are represented by general central processing units (CPUs) but can also include (application specific) digital signal processors (DSPs) as well. These are referred to as "software" because they are supposed to run application tasks compiled into software executables that will be run as programs. Components like field programmable gate arrays (FPGAs) and application specific integrated circuit (ASICs) are referred to as hardware (HW) components. Memories represent the third category of components, to which application communications can be mapped to.

## 4.5 Generation of Initial Candidates

With regard to Fig. 4.1, the GA algorithm requires a set of limited solutions. This is indicated with the corresponding "Generate initial candidates" block in Fig. 4.1. Therefore, in the proposed method, an initial set of candidate solutions needed by the evolutionary algorithm (discussed later in this chapter) is first generated. We randomly generate the initial set of candidate solutions for simplicity. The idea is to generate a starting point that captures specific requirements on the amount of hardware resources used and which is not much different from a design solution arrived at via a completely manual approach. Because the hardware platform is fixed, the initial candidate solutions represent different mappings of the application on to the hardware platform.

# 4.6 Design Space Exploration Using Genetic Algorithms

The "Design Space Exploration" block from Fig. 4.1 is where new solutions are generated and where design optimization takes place. This is a challenging step not only because of the complexity of the mapping problem but also because it must accommodate uncertainty as well. We propose to use the stochastic optimization algorithm: Non-dominated Sorting Genetic Algorithm (NSGA-II) to solve this problem. The NSGA-II is designed and instrumented to guide the search process toward robust and optimal solutions and is achieved by closing the outer loop shown in Fig. 4.1, hence implicitly taking into consideration the searched solution's reaction to uncertain parameter variations. The mapping problem is a multi-objective optimization problem whose objective functions or *quality attributes* often conflict. In this thesis, we consider the three objectives described next.

#### 4.6.1 Objective 1: Reliability