# Worcester Polytechnic Institute Digital WPI

Masters Theses (All Theses, All Years)

**Electronic Theses and Dissertations**

2006-12-20

# Design and Implementation of the Precision Personnel Locator Digital Transmitter System

Hauke C. Daempfling Worcester Polytechnic Institute

Follow this and additional works at: https://digitalcommons.wpi.edu/etd-theses

#### Repository Citation

Daempfling, Hauke C., "Design and Implementation of the Precision Personnel Locator Digital Transmitter System" (2006). Masters Theses (All Theses, All Years). 1134.

https://digitalcommons.wpi.edu/etd-theses/1134

This thesis is brought to you for free and open access by Digital WPI. It has been accepted for inclusion in Masters Theses (All Theses, All Years) by an authorized administrator of Digital WPI. For more information, please contact wpi-etd@wpi.edu.

## <u>Design and Implementation of the Precision</u> <u>Personnel Locator Digital Transmitter System</u>

## **A Thesis**

submitted to the Faculty

of the

WORCESTER POLYTECHNIC INSTITUTE Worcester, Massachusetts, USA

in partial fulfillment of the requirements of the

Degree of Master of Science

in

Electrical and Computer Engineering

by

Hauke C. Dämpfling

December 2006

| Approved:                               |

|-----------------------------------------|

| Prof. R. James Duckworth, Major Advisor |

| Prof. David Cyganski, Committee Member  |

| Prof. John A. Orr, Committee Member     |

### **Abstract**

The *Precision Personnel Locator* project is an ongoing research project funded by the Department of Justice, the goal of which is to provide sub-meter accuracy tracking and location of first responders inside of buildings with no pre-existing infrastructure, especially in emergency situations. The PPL system consists of wearable, battery-powered *Locator* devices that transmit a multi-carrier "ranging signal" waveform and *Reference Units* that receive this ranging signal and relay the information to a *Base Station* for location estimation processing and display.

This thesis describes the design and implementation of a subset of the Locator devices' functionality, including: the digital generation of the ranging signal waveform; the coordination of the transmissions of many Locator devices using time-sharing methods to prevent overlap of the signals; and finally, the gathering of environmental data such as temperature and movement of the wearer and the relaying of this data back to the Base Station.

To perform these tasks, two subsystems were designed and implemented as printed circuit boards. The first of these is the *Data Channel*, which is a low power, general-purpose communications platform that is capable of controlling the transmissions of the Locator devices with support for up to 100 Locators transmitting every second, and it can control the power of the Locator devices by switching portions of the system off when they are not in use. It also includes sensors to measure the ambient temperature, movement of the device, and a "distress button" that a first responder can press to trigger a distress signal to be transmitted to the outside of the building. The second subsystem is the *Digital Waveform Generator*, which consists of a Field-Programmable Gate Array (FPGA) and Digital-to-Analog Converter (DAC) that are capable of generating waveforms of up to 200 MHz bandwidth. The new Locator hardware can operate on battery power for many days.

The two subsystems were successfully tested and will serve as an important step towards the goal of developing a deployable location and tracking system.

## **Acknowledgements**

I would like to thank my advisor, Prof. James Duckworth, for his support and guidance throughout my time as a graduate student and my work on this project, and especially for his contributions and help reviewing this thesis. I would also like to thank Prof. John Orr and Prof. David Cyganski for serving as my thesis committee members.

I am grateful to the many people who have directly contributed to my work on this thesis: Robert Boisse, Jeffrey Cho, Jack Coyne, Gerry Harringon, Thomas Lui, Candemir Orsan, and Hemish Parikh all assisted me greatly during the design and evaluation process.

I would like to thank the rest of the Precision Personnel Locator team for their support of the overall project and their input to my work: Prof. Sergey Makarov, Prof. William Michalson, Vincent Amendolare, Jason Farmer, David Holl, Jason Huang, Shashank Kulkarni and Benjamin Woodacre have all greatly contributed to the success of the PPL project.

Finally, I would like to thank the National Institute of Justice at the Department of Justice, who funded this research project.

Hauke Daempfling

December 2006

## **Table of Contents**

| Abstract                                           | i  |

|----------------------------------------------------|----|

| Acknowledgements                                   | ii |

| List of Figures                                    | V  |

| List of Tables                                     | Vi |

| Chapter 1. Introduction                            | 1  |

| Chapter 2. Background                              | 6  |

| 2.1. Overall System Requirements                   | 6  |

| 2.1.1. Meeting with Worcester Firefighters         | 8  |

| 2.1.2. PPL Workshops                               | 9  |

| 2.2. PPL Project History                           | 10 |

| 2.3. Existing Digital Hardware Design              | 12 |

| 2.4. Locator Design Requirements                   |    |

| Chapter 3. Data Channel and Communication Protocol | 18 |

| 3.1. Multi-Transmitter Support                     | 18 |

| 3.2. Time-Division Multiplexing                    | 20 |

| 3.3. Free-Running Transmitter Calculations         |    |

| 3.4. Random Transmissions                          | 27 |

| 3.4.1. Conclusions                                 | 31 |

| 3.5. Bi-Directional Communication                  | 32 |

| 3.6. Hardware Specifications                       | 34 |

| 3.7. Hardware Implementation                       | 38 |

| 3.8. Communications Protocol                       | 41 |

| 3.8.1. Data Format                                 | 43 |

| 3.8.2. Communications Concept                      | 46 |

| 3.9. Protocol Implementation                       | 48 |

| 3.9.1. Synchronization and Timing                  | 51 |

| Chapter 4. Digital Waveform Generation             | 57 |

| 4.1. Digital-to-Analog Converter Design            | 58 |

| 4.1.1. Sampling Clock                              | 60 |

| 4.2. Data Supplying System Design                  | 62 |

| 4.2.1. High Speed Memory and CPLD                  | 63 |

| 4.2.2. Field Programmable Gate Array               | 63 |

| 4.2.3. FPGA Configuration                          | 65 |

| 4.2.4. Package Selection                           | 66 |

| 4.3. Hardware Implementation                       | 67 |

| 4.3.1. Power Supply Design                         | 68 |

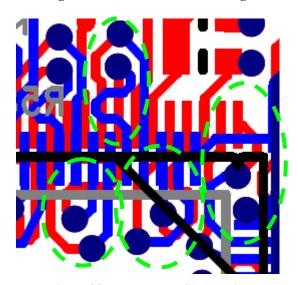

| 4.3.2. PCB Design                                  | 71 |

| 4.3.3. FPGA Digital Design                         | 74 |

| Chapter 5. Experimental Results                    |    |

| 5.1. Data Channel                                  | 77 |

| 5.1.1. Hardware Performance                        | 77 |

| 5.1.2. Outdoor / Indoor Range Tests                |    |

| 5.1.3. Outdoor Range Test                          | 84 |

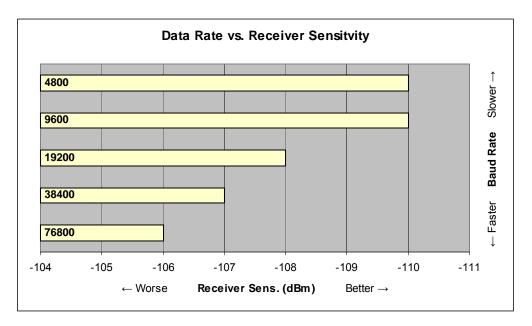

| 5.1.4. Data Rate vs. Receiver Sensitivity Test     | 85 |

| 5.1.6. Timer Accuracy Test                             | 36 |

|--------------------------------------------------------|----|

| 5.1.7. Timer Drift Test                                | 8  |

|                                                        |    |

| 5.1.8. Synchronization Accuracy Test                   | 0  |

| 5.1.9. Time Division Multiplexing Protocol             |    |

| 5.2. Digital Waveform Generator9                       |    |

| 5.2.1. RF Characterization                             |    |

| 5.2.2. Power Analysis                                  | 0  |

| Chapter 6. Conclusion and Future Work                  |    |

| 6.1. Future Work                                       |    |

| Chapter 7. References10                                |    |

| Appendix A. Detailed Data Channel Experimental Results |    |

## **List of Figures**

| Figure 1: PPL System Concept                                                    | 2  |

|---------------------------------------------------------------------------------|----|

| Figure 2: Locator Unit Concept Drawings                                         |    |

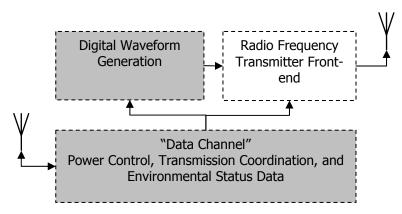

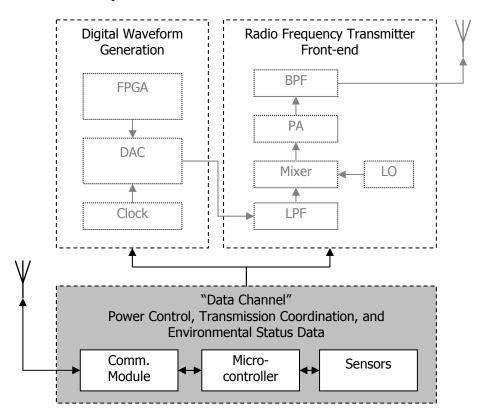

| Figure 3: Locator Overview                                                      |    |

| Figure 4: PPL System Overview                                                   | 7  |

| Figure 5: Audio Proof-of-Concept System                                         |    |

| Figure 6: RF Proof-of-Concept Receiver                                          |    |

| Figure 7: Current Transmitter Hardware                                          |    |

| Figure 8: Multi-Carrier Signal                                                  |    |

| Figure 9: Previous Digital Waveform Generation Hardware                         | 14 |

| Figure 10: Overview of Locator Hardware Design                                  |    |

| Figure 11: Data Channel as Part of Overall Locator Design.                      |    |

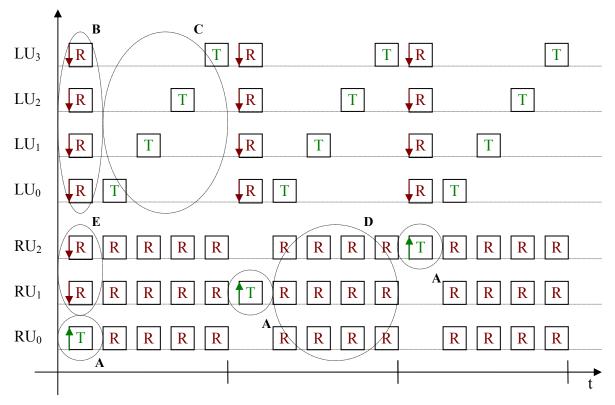

| Figure 12: Time-Division Multiplexing                                           | 19 |

| Figure 13: Frequency-Domain Multiplexing, Bands (left) vs. Interleaving (right) |    |

| Figure 14: TDM Overview                                                         |    |

| Figure 15: Clock Drift                                                          | 24 |

| Figure 16: Sample Failure Times                                                 | 26 |

| Figure 17: Random Transmission Scheme                                           |    |

| Figure 18: General Locator Block Diagram                                        |    |

| Figure 19: Data Channel Hardware Block Diagram                                  |    |

| Figure 20: Completed Data Channel Hardware                                      | 39 |

| Figure 21: Data Channel Movement Detection Circuit                              |    |

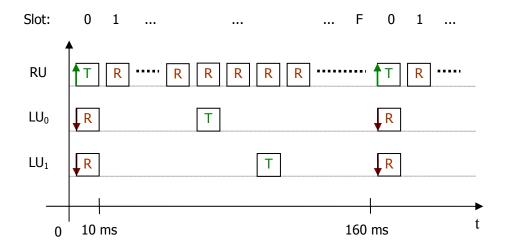

| Figure 22: System Overview                                                      |    |

| Figure 23: Packet Format                                                        |    |

| Figure 24: Protocol Overview                                                    |    |

| Figure 25: Basic Protocol Overview                                              |    |

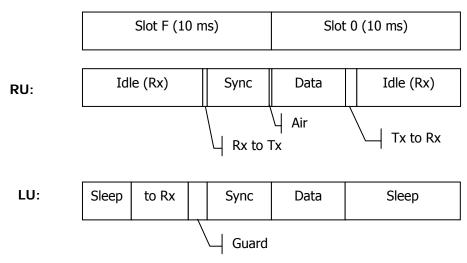

| Figure 26: Timeslot Overview                                                    |    |

| Figure 27: Synchronization                                                      |    |

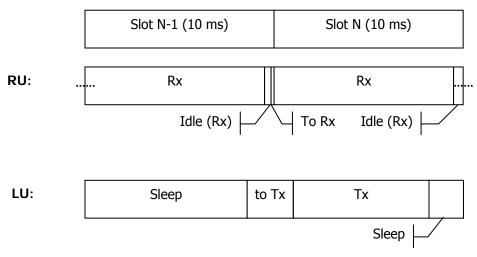

| Figure 28: Data Transmission                                                    |    |

| Figure 29: Digital Waveform Generator as Part of Overall Locator Design         |    |

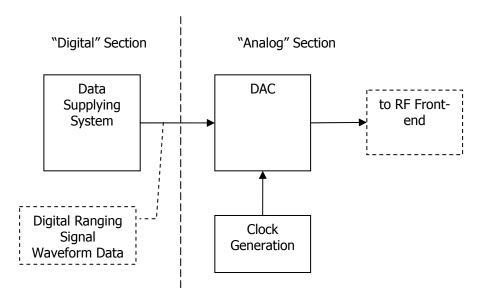

| Figure 30: Digital Waveform Generator Concept                                   |    |

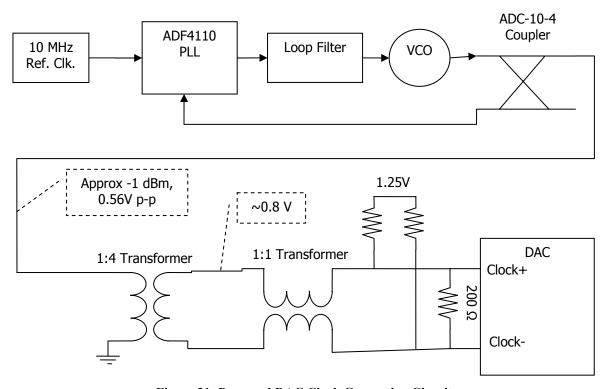

| Figure 31: Proposed DAC Clock Generation Circuit                                |    |

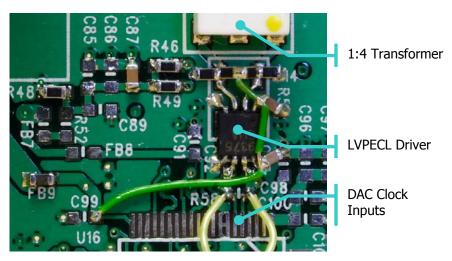

| Figure 32: Modifications to Clock Circuit                                       |    |

| Figure 33: Xilinx Spartan-3 Configuration Times (Source: Xilinx XAPP452)        | 64 |

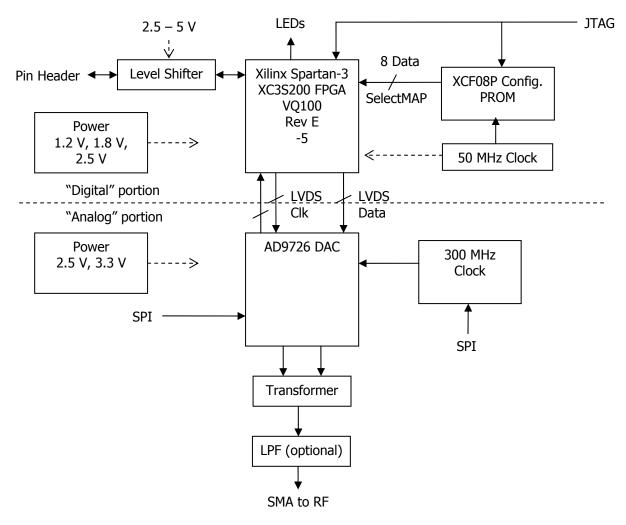

| Figure 34: Digital Waveform Generator Block Diagram                             |    |

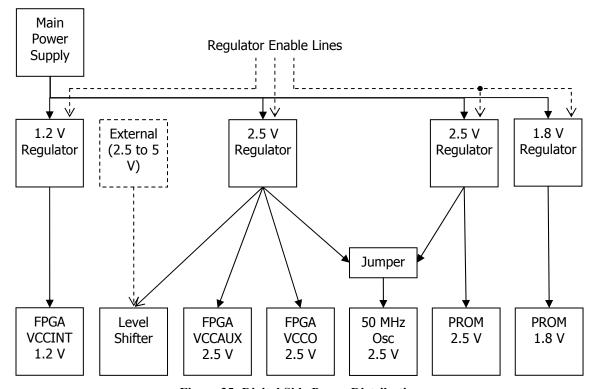

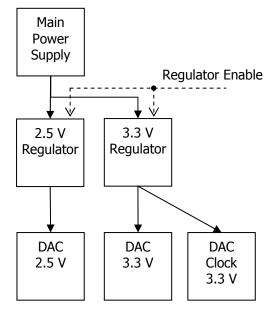

| Figure 35: Digital Side Power Distribution.                                     |    |

| Figure 36: Analog Side Power Distribution                                       |    |

| Figure 37: DAC and FPGA Packages                                                |    |

| Figure 38: Routed LVDS Data Lines                                               |    |

| Figure 39: Completed Digital Waveform Generator Board, Top (Digital) Side       |    |

| Figure 40: Completed Digital Waveform Generator Board, Bottom (Analog) Side     |    |

| Figure 41: DDR Timing Diagram (Source: AD9726 Data Sheet)                       |    |

| Figure 42: FPGA Internal Hardware Design                                        |    |

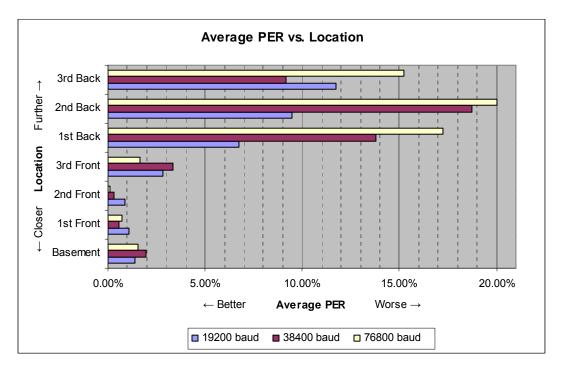

| Figure 43: Slave "Street" (left) and "Back" (right) Location                    |    |

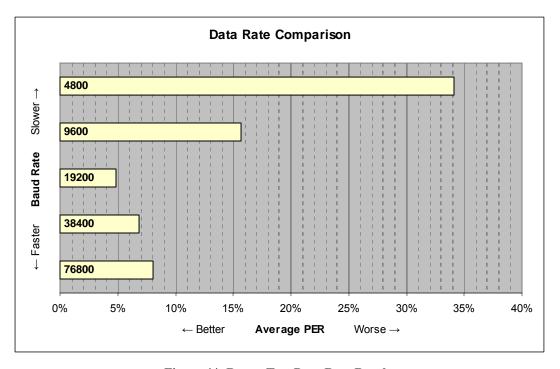

| Figure 44: Range Test Data Rate Results                                         |    |

|                                                                                 |    |

| Figure 45: Range Test Distance Results                           | 81  |

|------------------------------------------------------------------|-----|

| Figure 46: Range Test Antenna Results                            | 82  |

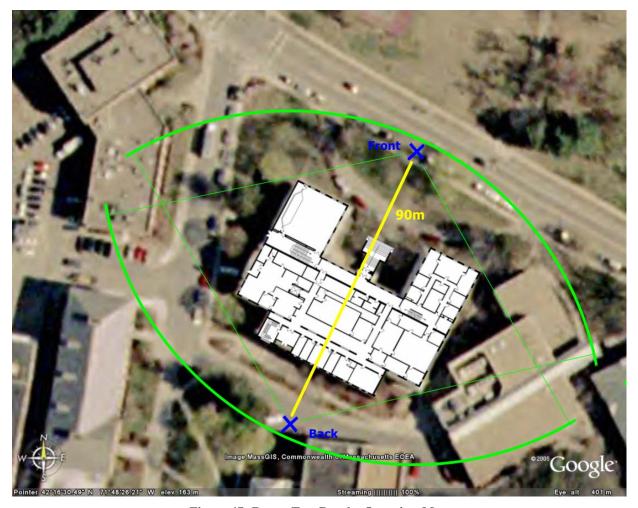

| Figure 47: Range Test Results Overview Map                       | 83  |

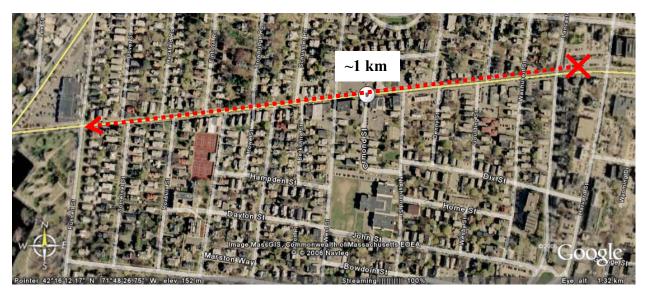

| Figure 48: Outdoor Range Test Locations                          | 84  |

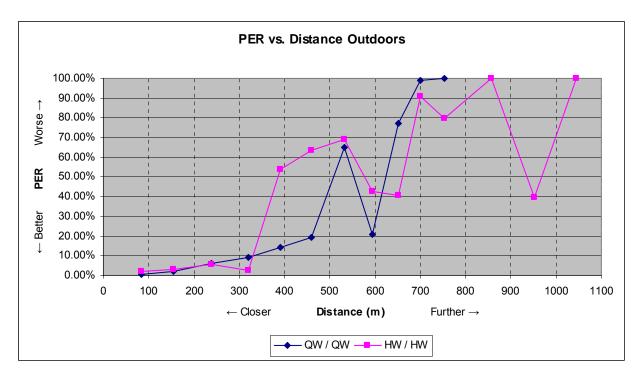

| Figure 49: Outdoor Range Test Results                            | 85  |

| Figure 50: Data Rate vs. Receiver Sens. Results                  | 86  |

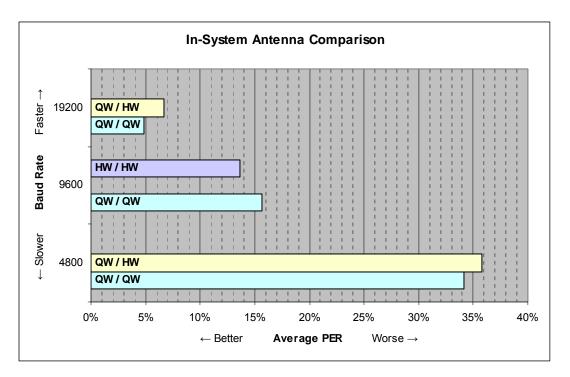

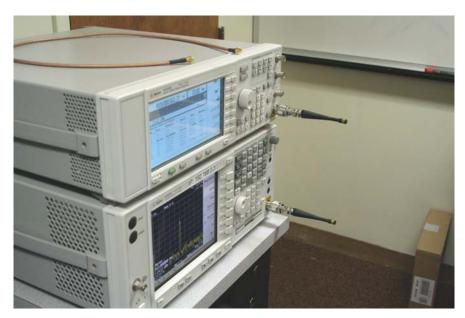

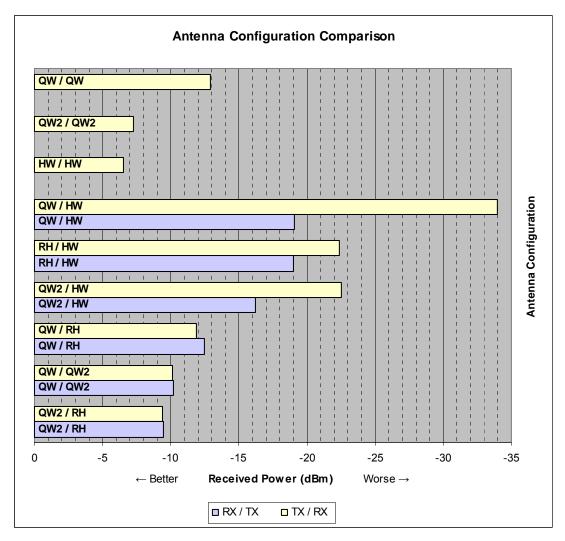

| Figure 51: Antenna Configuration Test Set-Up                     | 87  |

| Figure 52: Antenna Configuration Test Results                    | 88  |

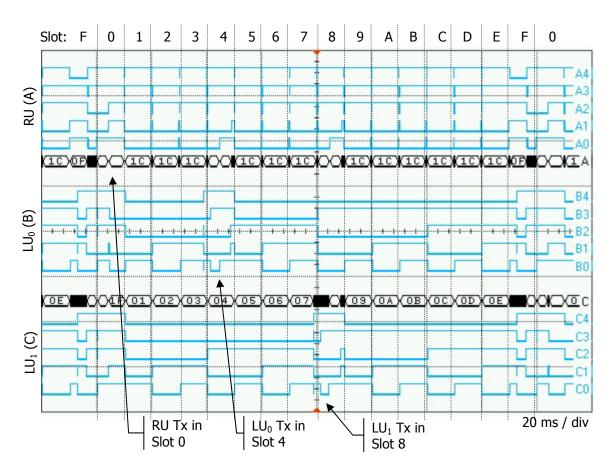

| Figure 53: Actual Protocol Overview                              | 92  |

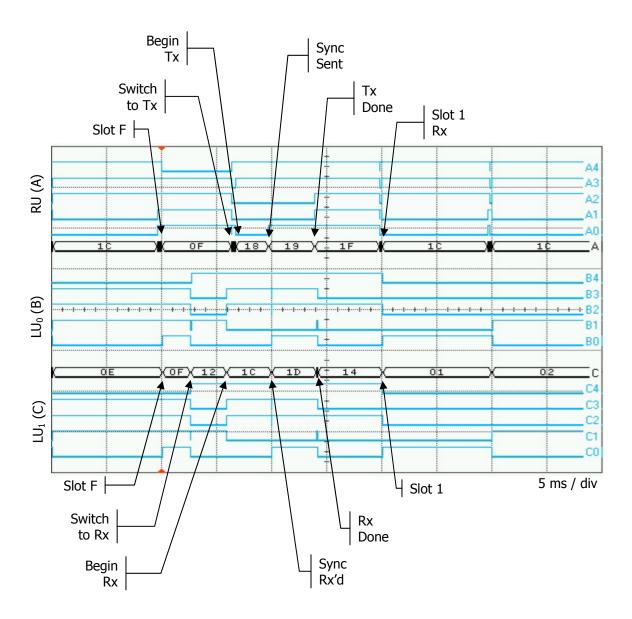

| Figure 54: Actual Synchronization                                | 93  |

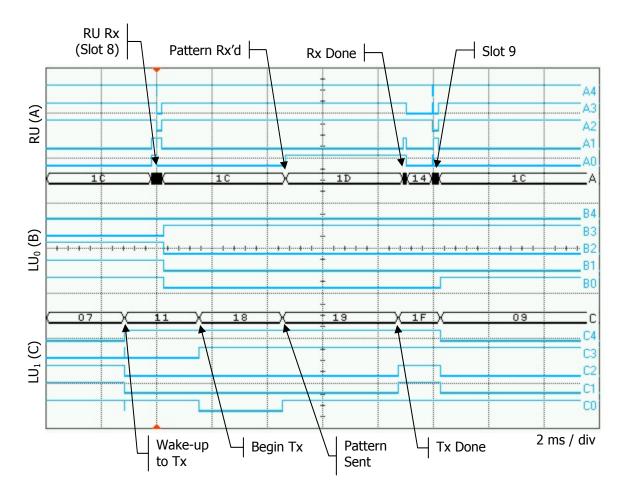

| Figure 55: Actual Data Transmission                              | 94  |

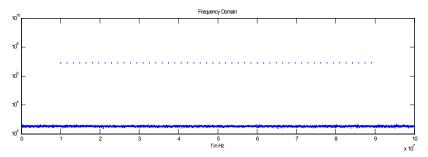

| Figure 56: Multi-Carrier Test Waveform                           | 95  |

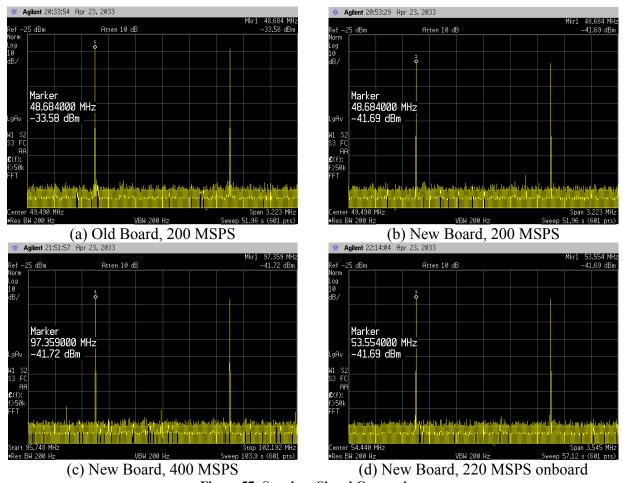

| Figure 57: Spurious Signal Comparison                            | 97  |

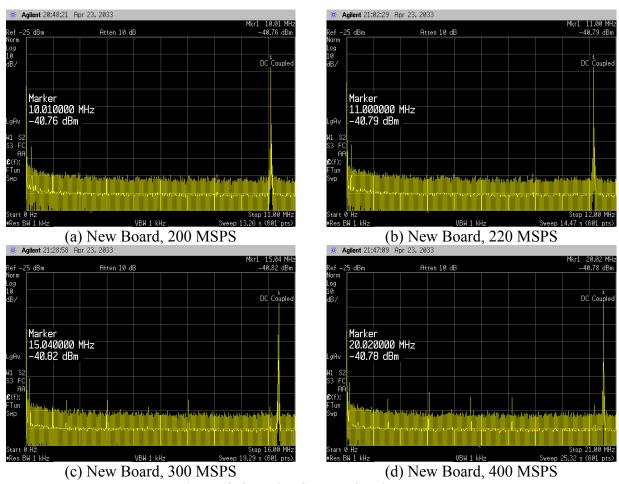

| Figure 58: Sampling Clock vs. Spurious Levels                    | 98  |

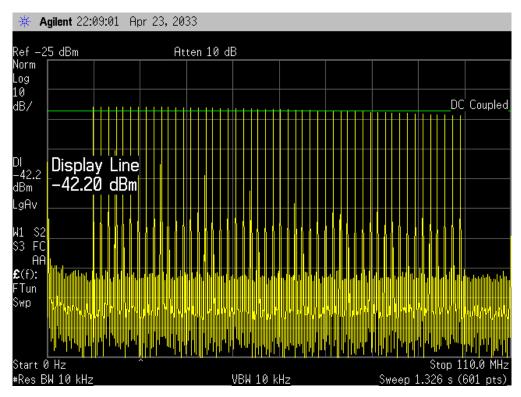

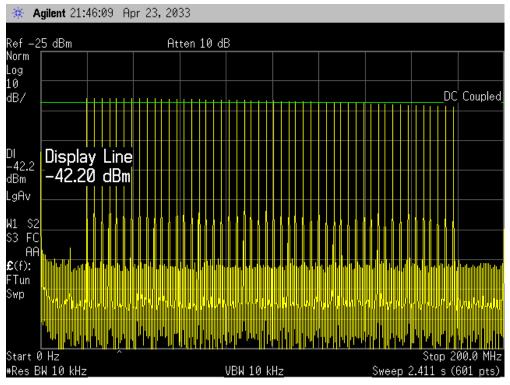

| Figure 59: Output Spectrum at 220 MSPS with On-board clock       | 99  |

| Figure 60: Output Spectrum at 400 MSPS                           | 99  |

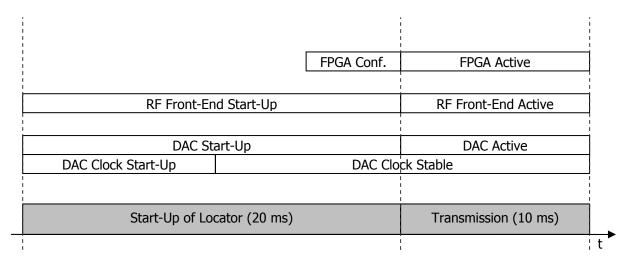

| Figure 61: Locator Power-Up Sequencing                           | 101 |

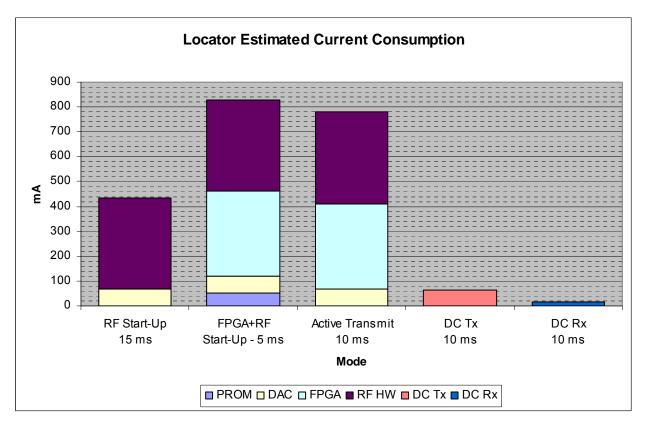

| Figure 62: Power Consumption and Timing                          | 102 |

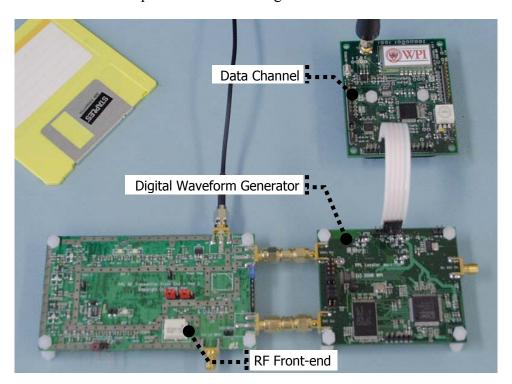

| Figure 63: Newly Developed Locator Hardware                      | 106 |

| List of Tables  Table 1: Allotted Frequency Bands                | 11  |

| Table 2: Symbols Used                                            |     |

| Table 3: Sample Failure Times (h:mm:ss)                          |     |

| Table 4: Required Frequency Stability for Specific Failure Times |     |

| Table 5: Simulation Verification Results                         |     |

| Table 6: Sample Probability Calculations                         |     |

| Table 7: Transceiver Modules                                     |     |

| Table 8: Data from Locator to Base Station                       |     |

| Table 9: Data from Base Station to Locator                       |     |

| Table 10: Xemics Module Mode Switch Times                        | 52  |

| Table 11: DAC Comparison                                         | 60  |

| Table 12: Current Consumption Estimates                          |     |

| Table 13: Regulator Selection                                    | 70  |

| Table 14: Outdoor / Indoor Test Runs                             | 80  |

| Table 15: Timer Drift Test Results                               | 89  |

| Table 16: SNR Comparison Results                                 | 95  |

| Table 17: Harmonic Distortion Test                               |     |

| Table 18: Signal Power Levels                                    | 96  |

| Table 19: Battery Life Calculation                               |     |

| Table 20: Outdoor / Indoor Range Test Raw Results                |     |

| Table 21: Outdoor Range Test Raw Results                         |     |

| Table 22: Synchronization Accuracy Test Results                  | 114 |

## **Chapter 1. Introduction**

On December 3, 1999, six firefighters were killed in a disastrous fire at the Worcester Cold Storage and Warehouse in Worcester, Massachusetts [3, 26, 27, 30]. Most, if not all, of these deaths could possibly have been prevented if the firefighters had had some better way to navigate inside the building despite the thick smoke and complicated layout of the corridors. This event led to the authoring of a whitepaper by Prof. John Orr [17] outlining the basic requirements for a system to locate and track first responders inside of buildings, and the subsequent launch of the *Precision Personnel Locator* research project, or *PPL*, which has been funded with a total of about \$3 million by the US Department of Justice.

In general, precise location estimation of persons inside of buildings without preexisting infrastructure for such purposes is a highly useful yet technically challenging problem. As will be described in more detail later, this is due largely to the fact that radio signals reflect from metal objects, creating multiple copies of the same signal and obscuring the direct path to the radio transmitter. Currently, there are no commercially available systems that can accomplish precise location and tracking. If such systems can be developed, the applications include uses for law enforcement, correctional facilities, and emergency first responders, such as firefighters [28]. The Precision Personnel Locator research project aims to develop technology for these applications by building an RF-based location and tracking system.

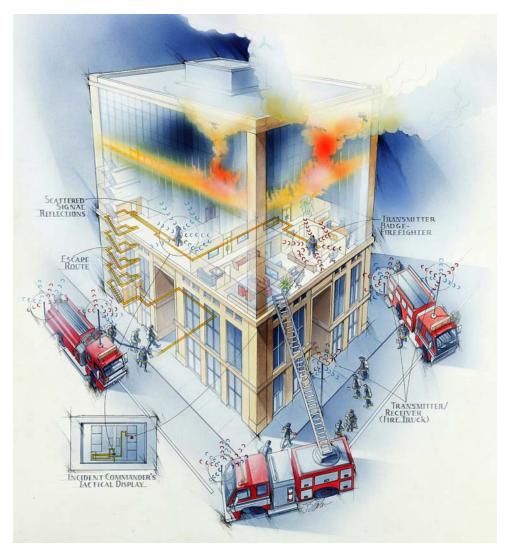

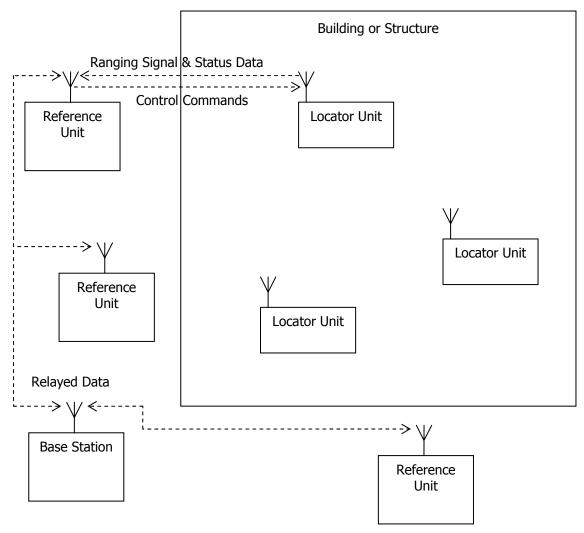

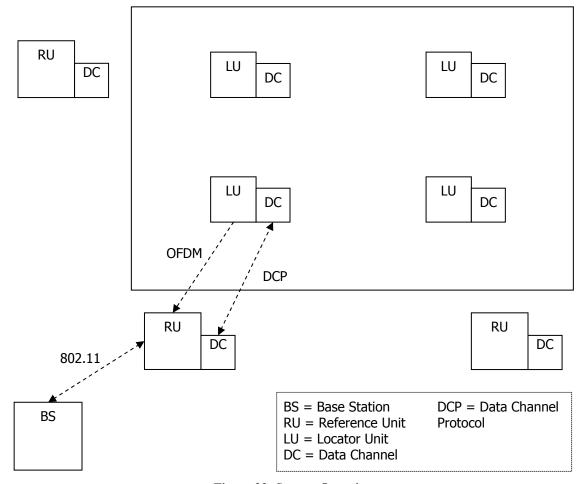

The PPL system consists of wearable *Locator* devices that transmit a multi-carrier "ranging signal" waveform that spans as much as a few hundred MHz and *Reference Units* that receive this ranging signal and relay the information to a *Base Station* for processing and location estimation. Figure 1 depicts this situation for the case of firefighters. The concept is that every person to be tracked wears a Locator unit (in the figure these are referred to as "transmitter badges"), most likely as part of their standard turnout gear. The Reference Units either are mounted directly on the first responders' vehicles or are deployed from them, allowing for a rapid setup of the entire system. The incident commander has a tactical display as part of the Base Station, most likely on their command vehicle, to view the positions of the persons being tracked. This tactical display would have the capability to display the location of all or only a few selected Locator units in real-time and the paths they have followed over time. Such information could in turn be disseminated off-site or to hand-held units such as PDAs. The location and path

information could then be used either to guide a lost user out on the path they entered the building, or to guide a rescue team into the building and directly to the person in need of assistance.

**Figure 1: PPL System Concept**

The figure above makes another important point, which is that the signal transmitted by the Locator devices is reflected by metal objects and scatters. This effect is called *multipath*, because each reflected signal that reaches the receiver is seen as a different "path" to the transmitter. The receiver then has the difficult task of selecting the true path, which is usually the shortest path, but not necessarily the strongest signal. Multipath effects can also cause certain frequencies in the signal to be faded out and others to be amplified. This problem is solved by the unique signal structure, algorithms and system architecture of the PPL system [6].

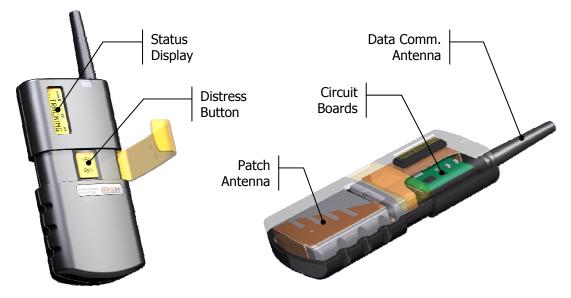

The function of the Locator units is to transmit the "ranging signal", consisting of many carriers, at pre-determined time intervals, so that multiple units may time-share their transmissions. Figure 2 shows a concept drawing of what a Locator device might look like. The units would be hand-held, being the size of a cell phone or walkie-talkie. They feature a distress button that can be used by a first responder to trigger a distress call to be sent to the outside of the building in case of emergency, and a status display for information such as battery charge status. As can be seen in the figure, there are two separate antennas — a PIFA-type antenna for the ranging signal, and a monopole antenna for data communication. Note that the reasons for implementing these two radio channels separately will be discussed in this thesis.

**Figure 2: Locator Unit Concept Drawings**

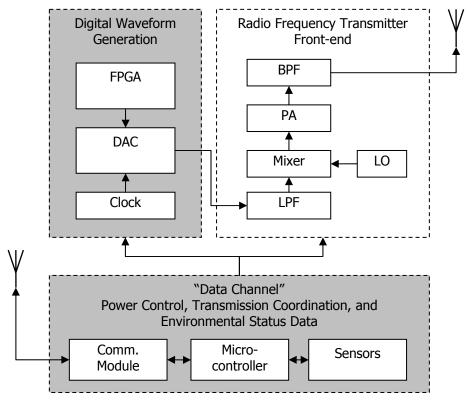

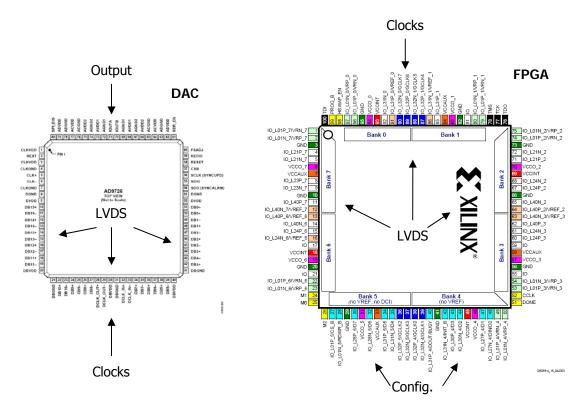

The ranging signal is generated on the Locators by a "software radio" type system. Digital samples of the signal waveform are generated by a Field Programmable Gate Array (FPGA) and provided to a Digital-to-Analog Converter (DAC) at a high speed – at least twice the bandwidth of the signal, i.e. a few hundred MHz. The DAC passes the generated signal to a radio frequency (RF) front-end, which up-converts the signal in the analog domain to the desired center frequency. In addition, the entire Locator must be able to be switched off when it is not in use to conserve power and in order to allow for the time-sharing of ranging signal transmissions. Figure 3 shows this system, in which the Locator has been divided into three subsystems: the digital generation of the ranging signal waveform via the FPGA and DAC, the radio frequency front-end that upconverts and transmits this signal, and lastly a control module that handles tasks such as

powering the other two parts of the Locator on and off as necessary and communicating commands and status data. This control module is known as the *Data Channel*.

Figure 3: Locator Overview

The focus of the work described in this thesis lies in the design, implementation and testing of the digital portion of the Locator units, consisting of the power control, transmission coordination, and digital waveform generation subsystems shown (shaded) above. Some additional tasks of the Locator units are to monitor the status of the environment, the physiological status of its wearer and to provide limited communication capabilities, such as a "distress call" to the outside of the building. There are several challenges in these tasks. The Locator units must be capable of running on battery power for several days. The waveform generation system must be capable of supplying data to the DAC at a high speed and still have a low power consumption, for example by enabling the circuit for only short periods of time. In addition, the transmissions of multiple Locators must be coordinated, and the status information and possible distress call must be communicated to the Base Station.

In order for the Locator to be modular for testing and to be able to better shield the different systems from one another in case of problems, it was decided to implement the subsystems shown above as three separate printed circuit boards (PCBs). The first PCB is the

Data Channel, which is intended to take over the power control, transmission control, status monitoring, and general data communication tasks of the Locator, and the second PCB is the Digital Waveform Generator, which is intended to replace the existing prototype waveform generators and produce the ranging signal waveform for the RF front-end. Note that the RF front-end is currently being developed as a third subsystem by other members of the PPL team.

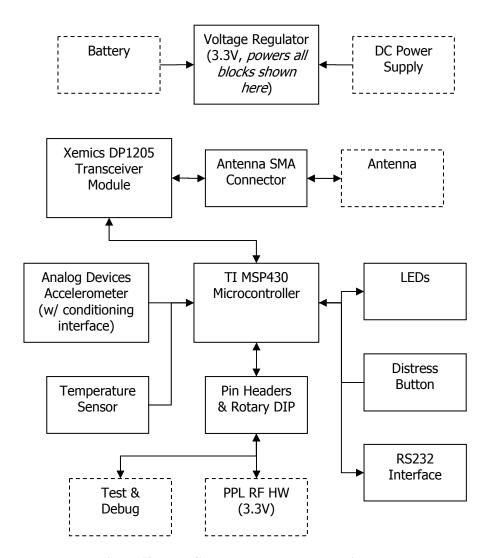

The Data Channel subsystem was developed as a more general-purpose platform for two-way wireless communications on an RF band separate from the ranging signals. It was implemented as a small, battery powered printed circuit board (PCB). The PCB includes a low-power microcontroller, a communications module capable of communications in the license-free 900 MHz "Industrial, Scientific and Medical" (ISM) radio band, and several peripherals such as an accelerometer for movement detection and a temperature sensor. The hardware is capable of operating on battery power for several days and has several interface ports to connect to other parts of the Locator, such as for overall power control of the Locator device. Because the PCBs operate on a wireless channel separate from the ranging signal, they could even be used as a backup for basic communication in case the ranging signal fails, for example to communicate the distress signal.

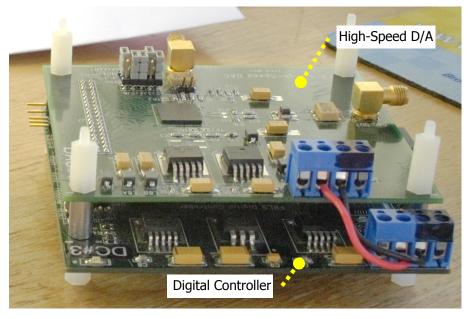

The Digital Waveform Generator subsystem is a redesign of an existing version of waveform generator hardware and is intended to be used in conjunction with a new RF transmitter front-end currently under development. It was implemented as a small PCB that attaches directly to the new RF front-end. The boards' major components are a Xilinx Spartan-3 FPGA and an Analog Devices DAC, accompanied by supporting circuitry such as clock generation for the DAC. This new hardware was developed to better approximate a final product in terms of size, power consumption, and sampling rate, as the previous generation of hardware was larger, and the FPGA and DAC were not optimal compared to the required sampling rate, and therefore also consumed more power.

This thesis presents the design, implementation and testing of the Data Channel and Digital Waveform Generator subsystems. In the next chapter, the background of the PPL project will be presented, including its history and the overall design requirements. Then, in the following chapters, the design of each subsystem will be discussed, followed by the implementation and testing of each.

## **Chapter 2. Background**

In this chapter, the requirements for the different portions of the PPL system with a focus on the Locator device will be presented, followed by a brief history of the PPL project. The previous generation of Locator hardware is presented, followed by the design requirements for the new Locator hardware, with a focus on the digital subsystems of the Locator.

#### 2.1. Overall System Requirements

At the beginnings of the PPL project in 1999 [17], several requirements for the system were laid out, many of which evolved over time to meet the requirements of users and the technical realities of implementing the system [18]. This section describes the system requirements as they stood at the time of writing, with some mention to the origins of these requirements. It should be noted that, in several cases, there were two sets of requirements for two different goals: the theoretical "final production system" level requirements, and the prototype system requirements that apply to the systems described in this thesis, which represent a step towards the final requirements.

An overview of the PPL system is presented in Figure 4. The Locator units transmit the ranging signal, which is received by the Reference Units, which in turn relay the data back to the Base Station. For this reason, the Locators are often referred to simply as transmitters, and the Reference Units as receivers. The Locator units are worn by the first responders entering the building or structure, and the units collect environmental and psychological status information and transmit it outside the building, in addition to transmitting the ranging signal. The Reference Units could be mounted on a first responder vehicle (such as a fire truck), or they could be deployed from the vehicles as mobile reference units. The Base Station could be mounted on, for example, the vehicle of the incident commander. It is obvious that the Locator units must be completely free to operate on their own, with "no wires attached" and powered by a battery.

It should be noted that many of the discussions of the PPL project are in the context of firefighters, but the system is actually very general-purpose. Market studies and focus groups were conducted [28] that showed that there is interest in this kind of technology from groups such as law enforcement and correctional facilities as well. In some cases, the requirements differ, but the basic work being done on the PPL systems and algorithms can be adapted to meet these different needs.

**Figure 4: PPL System Overview**

The most obvious requirements for the system are accuracy and reliability. The system must be able to provide real-time location information in three dimensions for each separate user of the system. The accuracy of the position should be good enough to let the users know which side of a wall a person is on, to be able to direct a search and rescue team to the correct room, so the positioning requirement calls for  $\pm 1$  foot accuracy. The system must support up to 100 users simultaneously, allowing for use in large-scale emergencies where this number of first responders is likely.

The operating rage of the system was originally specified to be at least 2000 ft (about 610 m), so that it would be able to cover an entire city block. However, in order to stay within FCC regulations and because such a range is not yet required for testing, the prototype system specifications stated that a range of 100 m is enough. This range covers the Atwater-Kent

building at WPI, which is often used for testing, and is representative of other large, commercial buildings. In addition, it can be assumed that the existing transmitters would need to only be modified for a higher transmission power to achieve a greater range.

The system should track the path users have taken over time by periodically recording their location. In order to acquire this tracking information, and in order to provide real-time location information to the users, the system must update the position of each Locator device at least once a second. The path information that is gathered could be displayed on the Base Station, and it could also be relayed to hand-held units, possibly even ones carried by the first responders themselves. This would allow for a "self-rescue" type operation, where users who may have become lost or disoriented could find their own way out.

Finally, the Locator devices should collect environmental and psychological information, so that this information can be relayed to the Base Station and the status of the person inside the building is better known. This should include a "distress signal" that a first responder can trigger when in need of assistance in emergencies.

#### 2.1.1. Meeting with Worcester Firefighters

In October 2005, researchers from the WPI PPL project met with officials from the Worcester Fire Department to discuss both system requirements and to get an idea of existing firefighter equipment [29]. Several important insights into how the PPL system might integrate into fire departments' equipment and routines were gained. In general, one must realize that typical fire departments may not have a great deal of funding and that most firefighters operate without "high-tech gadgets" – the standard *turnout gear* includes only boots, pants, a jacket, a helmet, a flashlight and possibly a radio. Other equipment, such as axes, is taken from the fire truck only when needed. So-called "self contained breathing apparatuses" (SCBAs) are also part of the equipment of a fire department, but there may not be enough for every firefighter. SCBAs are also sometimes forgotten, or even abandoned by firefighters when they are out of air. The SCBAs typically also include a "Personal Alert Safety System" (PASS), which is a device that emits a loud beeping noise when it detects non-movement of the firefighter, allowing for other firefighters to find a downed colleague.

The main theme that became apparent at this meeting was that the Locator devices must be very simple to use, hard to lose or forget, and be robust. When arriving at the scene of an incident, firefighters should not need to remember to pick up a Locator device (in case it is

attached to some kind of charging station or something similar), or to turn it on. This means that it would be preferable to be able to issue a Locator device to every firefighter so that it can be worn at all times, or even that it is sewn into or otherwise securely attached to the firefighter's turnout gear, such as the jacket. This shows the need for two more requirements: The devices must be low-cost, so that one could be issued for every firefighter in a department, and they must be very low-power, preferably even with the ability to remotely turn off a device when it is not at the scene of an incident. However, another important point is that if a device is so low-power that it does not need to be recharged often, this might actually be a disadvantage, as it does not build a habit for firefighters to regularly recharge their devices.

In respect to the possible "self-rescue" feature of the system, the point was made that inside a burning building there is often very low or absolutely no visibility, due to thick smoke and/or the power being cut off to the building. Therefore, it would be difficult for a firefighter to see the screen of a device providing self-rescue information, or the device could be dropped and easily lost. In addition, the environment can often be very noisy, making audio clues also somewhat troublesome.

In summary, the meeting with the firefighters confirmed that the top priorities for the Locator devices are small size, robustness, as well as low cost. In addition, the fact that every fire is an "organized chaos" makes it clear that rapid deployment and ease-of-use are especially important to the system as well.

#### 2.1.2. PPL Workshops

The first workshop concerning the PPL project was held in June of 2004 [22] and was attended by representatives from government, fire departments, law enforcement offices, and correctional facilities. At this workshop, the system requirements and priorities for the PPL system were established; many of these requirements are reflected in the above sections.

In August 2006, a workshop entitled "Precision Indoor Personnel Location and Tracking for Emergency Responders" was held at WPI [21]. At this workshop, representatives from industry and research gathered to present their different approaches to the issue of indoor location and tracking, and discussed common requirements for such systems. Through working group sessions, several conclusions for requirements were reached [31]. Many of these conclusions simply confirm the need for reliability, accuracy, etc. and underline the different requirements for different end users. However, one point differs from the previous discussion here, which is that

self-rescue could actually be a very important feature. This is because a firefighter is not always in a zero-visibility environment, and may easily be in a situation where he or she must escape from a building or structure, without the time for a rescue team to enter the building. So, although for the design of the Locator devices, self-rescue was not deemed a required functionality, this feature should not be eliminated from the list of general, future system requirements.

To summarize all these requirements for the focus of this thesis, which is on the Locator devices, it is clear that the Locators must be small and low-power, able to reliably transmit the ranging signal, and to communicate status information back to the Base Station.

#### 2.2. PPL Project History

The PPL project has benefited much from the work being done at WPI in the areas of radio navigation, radar sensing, and super-resolution techniques. In a paper by Professors Cyganski, Orr, and Michalson of WPI, a novel approach to range estimation is described [6]. This approach uses a multi-carrier signal structure and a matrix decomposition algorithm to analyze the relative phase shifts of each carrier to determine the time difference of arrival (TDOA) which can in turn be used to calculate the distance to the transmitter from two receivers. In addition, this algorithm allows for the separation of the direct-path and multipath signals, and its multi-carrier structure allows it to be robust against frequency selective fading.

This algorithm was implemented in a proof-of-concept system that used audio waves instead of RF frequencies [13]; this allowed for rapid prototyping with standard PC hardware. The original signal consisted of 101 carriers generated at 44100 samples per second, and the wavelengths of the kHz-range audio signals in air correspond to the wavelengths of an RF signal in the GHz range. This system, shown in Figure 5, showed that this approach is feasible, and thus paved the way for the next stage of the project, which was an RF-based prototype system.

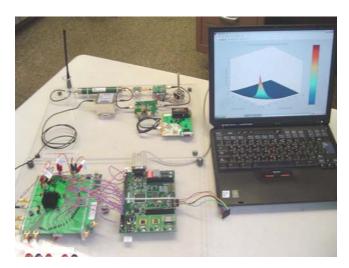

Figure 5: Audio Proof-of-Concept System

The first RF prototype system consisted of off-the-shelf components connected to form the transmitter and receiver portions of the system. A photo of the receiver portion of this prototype system is shown in Figure 6. This prototype served as the basis for the "second generation" custom prototype system presented in the following section.

Figure 6: RF Proof-of-Concept Receiver

Originally, the RF prototypes operated at a center frequency of about 440 MHz, depending on the experimental set-up. However, the FCC recently granted the PPL project more frequencies to use, as listed in Table 1. Band 1 is the previously allotted frequency span around the 440 MHz center frequency. As can be seen, the new "bands" that have been granted, Bands 2 and 3, can actually be seen as a continuous band with a gap in the middle.

| Band | Lower Freq. (MHz) | Upper Freq. (MHz) |  |  |  |

|------|-------------------|-------------------|--|--|--|

| 1    | 410               | 470               |  |  |  |

| 2    | 512               | 608               |  |  |  |

| 3    | 614               | 698               |  |  |  |

**Table 1: Allotted Frequency Bands**

Since the implementation of the second generation of prototype hardware, many tests to evaluate system performance using the TODA algorithms have been performed, and improvements and additions to the hardware and algorithm software have been made. Some of the improvements and tests are described here:

The TDOA range estimation algorithm originally required that one must specify the number of multipath reflections to solve for. Since one cannot know the number of reflections in a real-world multipath environment, and solving for the wrong number of

signals may perturb the correct solution, an addition to the algorithm known as "auto-Nsig" allowed for it to automatically determine the best number of signal paths to solve for.

- The initial versions of the algorithms used only one of the sidebands of the received signal. Algorithm improvements that allowed processing of both sidebands of the signal meant a doubling of the bandwidth available for range estimation.

- A Windows-based GUI for data collection was developed. This had previously been done

with tedious manual editing and execution of MATLAB scripts. This GUI made the

process of collecting data during testing much more efficient, allowing more tests to be

performed.

An important point that is raised above is increasing the bandwidth. It has been shown [7, 20] that, generally speaking, increased bandwidth results in better range estimates. Therefore, tests were performed in which the original transmitter bandwidth of 25 MHz was increased to 50 MHz and above, which allowed for better range estimation.

During the testing of the TDOA algorithm, some important benchmarks were reached, for example, a first test was performed that showed that the TDOA algorithm could be used to accurately locate a transmitter in two dimensions in an outdoor environment. An important element of this test was that the transmitter did not share any clock signals with the receivers, i.e. it was completely free-running "with no wires attached", as a transmitter in the real world would be.

## 2.3. Existing Digital Hardware Design

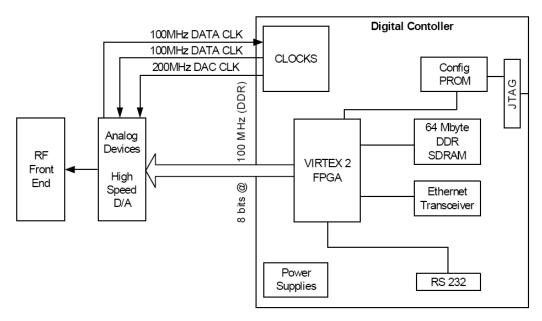

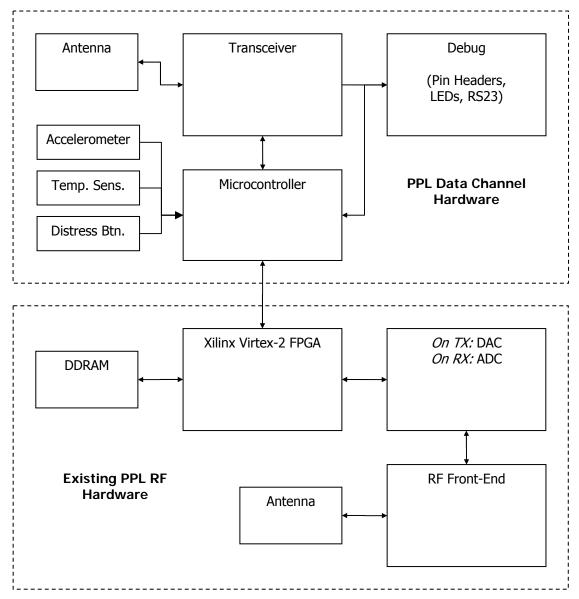

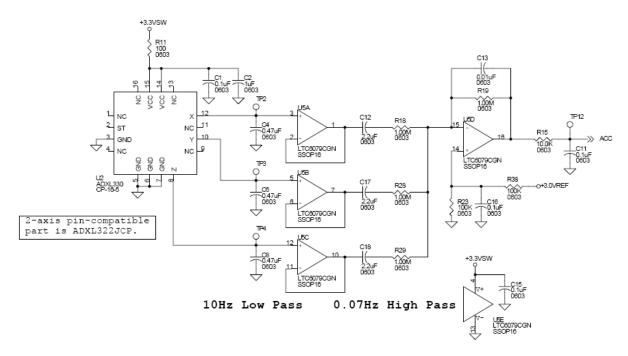

The work described in this thesis involved improving the design of the Locator devices, which was based on the previous generation of simple transmitter hardware described in [8]. Because this thesis focuses on the digital hardware of the Locator devices, we will describe this portion of the previous version of hardware, a diagram of which is reproduced from [8] in Figure 7. The "Digital Controller" and "High Speed D/A" portions were completely redesigned as part of the work on this thesis, and a redesign of the RF front-end is currently underway by other members of the PPL team.

Figure 7: Current Transmitter Hardware

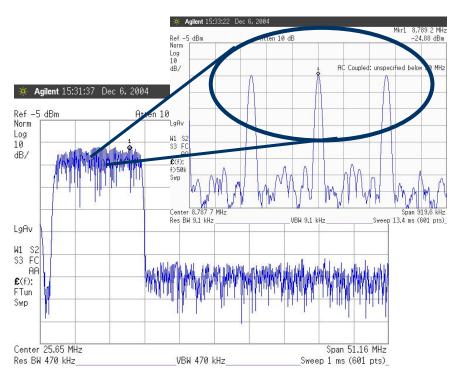

The digital portion of the previous transmitter prototype was responsible for generating a 100 MHz bandwidth signal that contains the multi-carrier waveform. This waveform normally is adapted for different bandwidths in different experiments, but in general, it consists of 50 or 51 equally spaced carriers. In [8], 50 carriers are spaced 244 kHz apart, beginning at 2.44 MHz, resulting in about 12.2 MHz total bandwidth (see Figure 8).

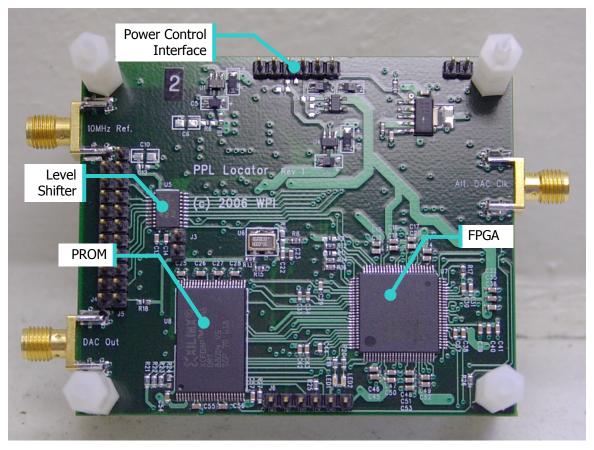

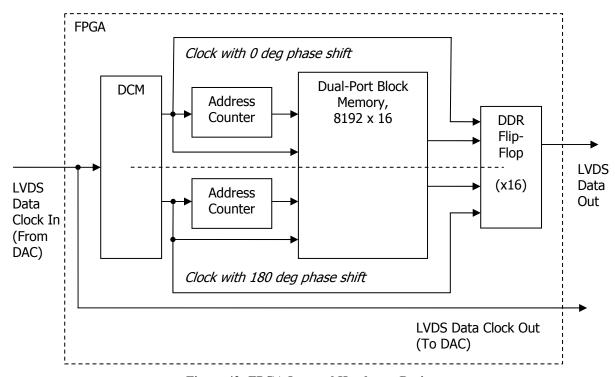

The transmitter hardware consists of two separate boards as shown in Figure 9, a general-purpose digital controller board (bottom) that was also used on the receiver, and a digital-to-analog conversion board (top). The digital controller board features a Xilinx Virtex-2 FPGA with the required configuration PROM and power supplies. In addition, it has a 64 MB SDRAM, an Ethernet transceiver, and an RS232 interface. A number of FPGA pins are present on pin headers to provide for up to 16 bits of data or 14 bits of data and two clock signals using the low-voltage differential signaling (LVDS) standard to interface to the DAC board.

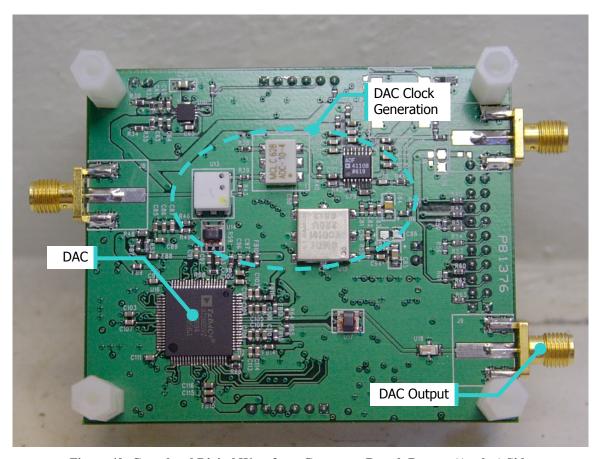

The digital-to-analog conversion board contains an Analog Devices AD9736 DAC, which is capable of sampling rates of up to 1.2 GSPS with 14 bits of resolution. The DAC receives its sampling clock from either an external clock via an SMA connector or a clock from the digital controller board. The DAC features an LVDS interface, and expects an input of 14 bits of data together with an additional data clock signal from the FPGA. In addition, the DAC can optionally provide a clock signal to the FPGA.

Figure 8: Multi-Carrier Signal

Figure 9: Previous Digital Waveform Generation Hardware

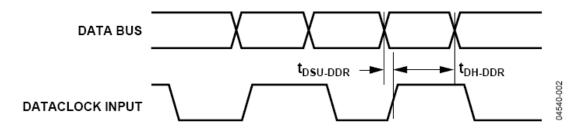

The ranging signal generated by these boards consisted of 8192 samples, making up a *symbol*, that were sampled at 200 MSPS, giving a symbol duration of 40.96 µs. The samples were stored in the FPGA's block memory and were provided to the DAC using double data rate (DDR) transfer, in which data is sampled on both the rising and falling clock edge, allowing for a clock frequency of half the data rate. The signal generated by this digital waveform generation system

was passed along to the RF front-end, which upconverted the signal to a center frequency depending on the experimental set-up.

The disadvantage of this previous version of hardware was that it was unnecessarily powerful for a deployable system, because it was intended as a general-purpose platform. For example, the digital controller board contains features such as a large SDRAM and an Ethernet controller, which are not necessary for the final Locator device. Also, the FPGA contains much more logic than is actually needed to generate the waveform (only 1% of its logic resources were actually used, and only 17% of its Block RAM), and the entire design had not been tested for use with higher bandwidths than 100 MHz. In addition, the boards are large and do not show what a final Locator device might look like in terms of size.

Another large disadvantage was that the previous version of the hardware was not optimized in terms of current consumption. The hardware was not designed to enable easy or fast power control, meaning that the boards were powered either completely on or completely off. In addition, as will be shown in a later chapter, supporting multiple Locators requires time-sharing of the transmission of the ranging signal. This means that the Locator should be switched off when it is not needed, both to prevent overlap of two transmitters' signals, and to conserve power. However, the previous design required too much time to power on and off, effectively preventing duty cycling of the hardware and preventing support for multiple transmitters.

One should note that the previous generation of hardware was purely a transmitter for the ranging signal and did not include any provisions for several of the features that have been described as requirements in the previous sections, such as environmental status information, or any other kind of data communication ability that would allow for implementation of a time-sharing scheme. This was one of the reasons for developing a new version of the hardware, with the requirements as set forth in the following section.

## 2.4. Locator Design Requirements

In late 2005, the existing prototype transmitter and receiver hardware worked well and many tests had been performed with it. However, this hardware had several shortcomings, as described in the previous sections. Therefore, it was decided to develop the new Locator hardware described in this thesis. This section presents the specifications for this new generation of hardware.

It was decided to implement the new Locator hardware subsystems as three separate printed circuit boards. These subsystems, as described in the Introduction and pictured in Figure 10 below, are the Digital Waveform Generation of the ranging signal waveform, the RF transmission of the waveform, and lastly the control of the transmissions and communication of commands and data, which was named the "Data Channel". The work done for this thesis concerned the digital portions of the Locator, which are the *Digital Waveform Generation* and the *Data Channel* (shaded in figure).

Figure 10: Overview of Locator Hardware Design

The separation of the prototype Locator hardware into these subsystems had the advantage of one being able to develop and test each subsystem individually, it allowed the hardware to be modular, and it additionally prevented any errors in one design, such as excessive electrical noise or other faults, from leaking into another board. The PCBs of each subsystem were designed to be small, with the ability to be connected together to best approximate a final Locator design.

For the ranging signal generation by the Digital Waveform Generator, a signal bandwidth of 150 MHz was required in order to generate a signal spanning the new frequency bands granted by the FCC (described as Bands 2 and 3 in Section 2.2), which span from 512 MHz to 698 MHz, with a gap from 608 to 614 MHz. The same number of samples as in previous versions, 8192, was selected, except the signal was now be sampled at the new rate of 300 MSPS. The output levels of the waveform generator were required to be -40 to -50 dBm per subcarrier (but the design should be able to produce more than this) with low spurious levels. The DAC was required to provide for at least 14 bits of resolution and its sampling clock should be generated on-board.

The system had to support up to 100 simultaneous users, giving location updates at least once a second. In addition, the Locators were required to be low-power, consuming as little power as possible when running, to provide detailed power control for individual portions of the circuits, and to have rapid turn-on times for power saving through duty cycle reduction. The system was required be able to operate continually on battery power for at least several (on the order of 6-12) hours. Some additional requirements were that the Locator must be able to measure ambient temperature and detect non-movement of the device, and be able to transmit a user-triggered "distress signal" to the Base Station (via the Reference Units). The minimum communication range was at specified to be least 100 m.

In the following two chapters, we will show how these design requirements were implemented in the Data Channel, followed by the Digital Waveform Generation.

## **Chapter 3. Data Channel and Communication Protocol**

In this chapter, the design process will be presented that addresses the issues of supporting multiple users and gathering and communicating status data, which ultimately led to the development of the Data Channel hardware. The relationship of the Data Channel subsystem to the other hardware in the Locator is shown in Figure 11. First, the theory behind supporting multiple Locator devices will be addressed, followed by possible implementations. This will be narrowed down to the system that was finally implemented, and details on the hardware as well as protocol software will be presented.

Figure 11: Data Channel as Part of Overall Locator Design

## 3.1. Multi-Transmitter Support

In order to support multiple users, the PPL system must be able to receive signals from multiple Locators, which in turn means that multiple Locators must be able to operate in parallel. This section discusses the two basic approaches to supporting such parallel operation: frequency-domain multiplexing (FDM) and time-domain multiplexing (TDM). For completeness, we also briefly discuss code-division multiplexing (CDM).

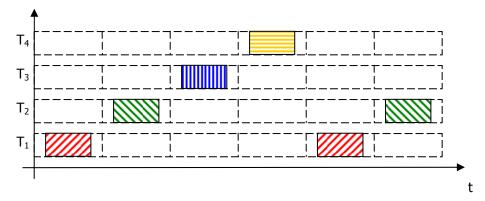

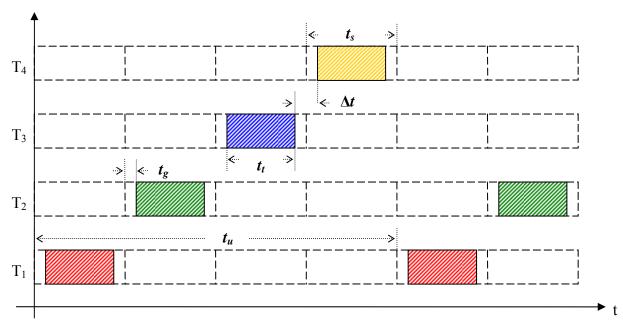

In TDM, the Locators, or simply transmitters (as their main function is to transmit the ranging signal), do not actually transmit in parallel, but a "virtual parallelism" is achieved by having the transmitters transmit for short durations in rapid succession. An overview of this situation with four transmitters, T<sub>1</sub> through T<sub>4</sub>, is shown in Figure 12. The major advantage of this approach is that it is very straightforward to implement, and can be used to conserve power as well, as the transmitter's duty cycle is much reduced. However, this requires the circuitry to be able to power on and off quickly, otherwise this power-saving advantage disappears. In addition, a trade-off must be made between the minimum time to transmit for each transmitter, number of transmitters in the system, and messaging frequency. This means that this approach may require the active coordination of the transmitters, depending on the restrictions on clock drift, which will be discussed in detail in later sections.

Figure 12: Time-Division Multiplexing

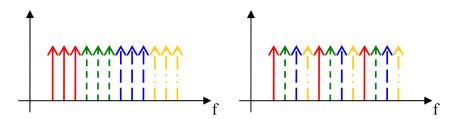

In FDM, the different transmitters transmit at different frequencies, allowing for concurrent operation. This is theoretically possible because the PPL signal consists of individual carriers, each of which takes theoretically zero bandwidth. Figure 13 shows two approaches: on the left, the different transmitters' carriers are consecutive and use completely different frequency bands; on the right, the different transmitters' carriers are interleaved.

Figure 13: Frequency-Domain Multiplexing, Bands (left) vs. Interleaving (right)

The advantage to this approach is that one does not have to worry about turning a transmitter on and off and coordinating between different transmitters, so no control hardware is needed for these tasks. However, there are also several disadvantages. This approach is harder to implement on both the transmitter and receiver: The transmitter has to span a larger number of possible transmission frequencies, while the receiver has the added task of dissembling the received signal into its different transmitter components. Also, and most importantly, implementing such a system for a large number of transmitters (up to 100) with the current waveform (at least 50 carriers) means that five thousand carriers would have to fit in a frequency range limited by the bandwidth of the receiver, which may only be a few hundred MHz. Such tight packing of the waveform carriers may lead to other problems, such as a reduction of the multipath-resistant characteristics of the ranging signal due to the chance of different transmitters interfering with each other (for example through clock drift or harmonics). Hence, it may be that in order to support the targeted number of transmitters (100), the system would have to employ some kind of control hardware to manipulate the transmitted signals to prevent interference, similar to what is needed for TDM, which eliminates this advantage of FDM and raises the question of whether it would not just be simpler to only implement TDM.

A final approach that is used for multiplexing data together is CDM (also known as CDMA, or code-division multiple access), the very basic idea of which is that two transmitters transmit at the same time and on the same frequencies, and only by a special encoding scheme can a receiver recover the data transmitted from each source. One of the disadvantages of this scheme is that the transmit power of each unit must be closely controlled, otherwise one transmitter might "drown out" another. However, the major disadvantage is that for our purposes, it is unacceptable to overlap two different carriers, as this disrupts the phase information that is required for the range estimation. Therefore, it is clear the CDM is useful only for binary data transmission and not for our system.

In conclusion, while FDM may offer advantages for systems with a smaller number of transmitters, it is clear that TDM is the best approach due to its simplicity. The following section investigates this multiplexing method.

## 3.2. Time-Division Multiplexing

In time-division multiplexing, it is clear that the transmitter's emissions must be controlled so that no two transmitter's transmissions overlap. For example, the system

specifications state that 100 transmitters should be able to provide location updates once a second, so each transmitter has only 10 ms to transmit. In this section, we will verify that TDM is indeed feasible in this situation, and then discuss different schemes that allow this kind of control.

We will verify that our goal of multiplexing 100 transmitter units to provide updates once a second is realistic, considering that each transmitter only has 10 ms to transmit. There are several factors to keep in mind: whether this time allows for enough of the ranging waveform to be transmitted, how much data can be transmitted during this time (assuming some kind of data communication is taking place), and whether this provides a tight enough resolution for tracking.

The current signal consists of "symbols" of 8192 samples, sampled at 200 MSPS, which gives a symbol period of 40.96 µs. This allows for 244 symbols to be transmitted in a 10 ms period. Although the capture of a single symbol is sufficient for range estimation, multiple symbols can be "time fused" to provide better SNR: each doubling of the number of symbols gives a SNR boost of about 3 dB. However, one must keep in mind that clock drift might cause transmitters to drift, which means a guard time should be implemented in the beginning and end of the 10 ms period – this will be discussed in detail in the following section. Therefore, while a balance between the number of symbols transmitted and the required guard time has to be found, we can assume that 10 ms is sufficient time to transmit a ranging signal.

Assuming that some kind of data communication other than the transmitters' ranging signal waveforms is implemented, we can quickly calculate that at a relatively slow baud rate of 19.2 kbits/second, 24 bytes could be transferred in a 10 ms period. For a simple control/command protocol, this may be sufficient, but may not be if larger amounts of data needed to be transferred. This issue will be discussed in more detail in a later section, but one can see that this time period does allow for a transfer of a small amount of data.

Finally, we would like to know what resolution an update rate of once per second gives. A human walks at a normal rate of about 1.2 m/s [15] (for reference, the fastest human running speed is about 10 m/s [10], while a human falling at terminal velocity is about 60 m/s [9]), and we can assume that a firefighter who is loaded down by heavy gear may not walk as quickly. In addition, firefighters often crawl along the floor, below any smoke that may be in the air, further reducing their rate of movement. So, we can see that a position update of once per second should give a resolution of better than one meter. In addition, we can imagine that a future system might be able to dynamically adjust the number of updates per second depending on the actual number

of users that require accurate tracking. This would mean that certain users' positions (such as those who are outside the building or who are not moving often) could be updated less frequently, resulting in a higher resolution for other users. Similar variations on this scheme to further increase accuracy could also be implemented, but in general, a tracking resolution of typically better than one meter is on the order of the overall system accuracy and is therefore sufficient.

We must now discuss methods with which to implement a TDM scheme. There are many medium access control schemes in existence for communications on shared mediums, such as ALOHA, Slotted Time (with beacons or shared clocks), Carrier Sense Multiple Access (CSMA) with Collision Avoidance or Detection, Bit-Map or Binary Countdown protocols, and so on [25]. Current widely used communications standards such as Wireless LAN (802.11 [12]), Bluetooth (802.15.1 [5]) or ZigBee (802.15.4 [33]) all use variations of the previously listed medium access control methods. However, these protocols all have one thing in common that make them unsuited for direct application to the current system: they assume that every station is a transceiver, or at the very least a transmitter with the capability to detect communications or collisions on the medium.

The previous generation of transmitter/receiver hardware allowed only for one-way communication. The multi-carrier waveforms were generated on the transmitter by feeding data from a static memory inside an FPGA into a DAC, and on the receiver end, the waveforms were digitized by an ADC and FPGA and transferred to a MATLAB script to extract the range information. This means that modulating or in any way actively manipulating the generated waveform on the transmitter side would involve complex calculations and therefore complex hardware on the transmitter FPGA. Another issue is the power question: the transmitter chain of FPGA plus DAC plus RF front-end consumed on the order of many hundred milliamps, and constantly running this system would require a large battery or the run time would be reduced to unacceptably. Similarly, the receivers in this system required a large amount of hardware (RF front-end, ADC, etc.) that make it unfeasible to add receiver hardware to each transmitter. Therefore, it is clear that the previous version of transmitter hardware was only fitting to generate a ranging signal waveform and not for bi-directional or data communication.

Therefore, in the following two sections, we will investigate the question of how a system in which the transmitters have no receive capability might function.

### 3.3. Free-Running Transmitter Calculations

We seek to investigate an "open-loop" system where the transmitters do not have any form of receive capability. Therefore, the transmitters will have free-running clocks with only the possibility of synchronization through some kind of physical connection with a base station. In this kind of a system, the issue of clock drift becomes crucial, because it defines how much time it takes for this system to fail. In this section, we will delve into some more detail on the TDM system, and then derive a "time until failure" equation for this scheme, and show some calculation examples.

In a TDM system, time is divided into "time slots", with each slot having a guard time at its beginning and end to allow for some amount of clock drift. This system will fail when clock drift causes transmissions to drift over the bounds of the guard time and to overlap. In the worst case, if n transmitters are at the upper and lower bounds of their frequency range given by their ppm rating ppm, and they make an update every  $t_u$  seconds consisting of s symbols (each symbol being of duration  $t_d$ ), we shall derive the worst-case time until failure  $t_f$ . Figure 14 shows an overview of this situation using four transmitters as an example, and Table 2 shows the symbols used for these calculations.

Figure 14: TDM Overview

| Symbol     | Description                | Notes & Relationships                                              |

|------------|----------------------------|--------------------------------------------------------------------|

| n          | Number of Transmitters     |                                                                    |

| S          | Symbols per Transmission   | $s \ge 1$                                                          |

| $t_d$      | Symbol Duration            | Currently: 8192 samples at 200 MSPS gives 40.96 µs symbol duration |

| $t_u$      | Update Period              | (see Figure 14) updates per second = $1/t_u$                       |

| ppm        | Crystal ppm Rating         | Example: A 50 ppm crystal is $ppm = 50 \times 10^{-6}$             |

| $t_s$      | Time Slot                  | (see Figure 14) $t_s = \frac{t_u}{n}$                              |

| $t_g$      | Guard Time                 | (see Figure 14)                                                    |

| $t_t$      | Transmit Time              | (see Figure 14) $t_t = t_d \cdot s = t_s - 2 \cdot t_g$            |

| $\Delta t$ | Time Between Transmissions | (see Figure 14) $\Delta t = 2 \cdot t_g$                           |

Table 2: Symbols Used

We should note that throughout this analysis we ignore the propagation delay of signals through the air. The propagation delay of a radio signal through air is the distance traveled divided by c, the speed of light (299792458 m/s). The propagation delay over 1 m is therefore 3.3356 ns and 333.56 ns over 100 m. Because the guard times we will consider below are higher than this by several orders of magnitude, this delay is negligible for our applications.

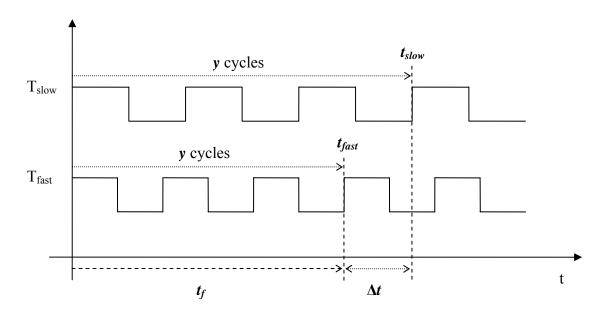

Figure 15: Clock Drift

We will investigate two transmitters whose clocks are at the lower and higher end of their allowable frequency range as given by their ppm rating, as shown in Figure 15. In other words, given a nominal frequency of  $f_0$  and a frequency range  $\pm \Delta f = \pm f_0 \cdot ppm$ , the "slow"

transmitter's ( $T_{slow}$ ) clock frequency is  $f_{slow} = f_0 - \Delta f$  and the "fast" transmitter's ( $T_{fast}$ ) clock frequency is  $f_{fast} = f_0 + \Delta f$ .

After y clock cycles,  $T_{slow}$  and  $T_{fast}$  will "think" they are at the same point in time, however their actual times (the times at which they actually complete y clock cycles) are, respectively,  $t_{slow} = \frac{y}{f_0 - \Delta f}$  and  $t_{fast} = \frac{y}{f_0 + \Delta f}$ . We are interested in the point in time when the

difference in these two times,  $\Delta t = t_{slow} - t_{fast}$ , grows too large, because at this time the guard time will be overstepped and transmissions will begin to overlap. Since the "fast" transmitter will cause an error (overlapping transmission) first, this point in time is  $t_{fast}$ , and we shall call this the time until failure,  $t_f$ .

Using the above information, we derive  $t_f$  as follows. First, we will combine the above equations for the difference in the two clocks:

$$\Delta t = \frac{y}{f_0 - f_0 \cdot ppm} - \frac{y}{f_0 + f_0 \cdot ppm}$$

Solving  $t_f = t_{fast} = \frac{y}{f_0 + f_0 \cdot ppm}$  for y and substituting:

$$\Delta t = \frac{t_f \cdot (f_0 + f_0 \cdot ppm)}{f_0 - f_0 \cdot ppm} - \frac{t_f \cdot (f_0 + f_0 \cdot ppm)}{f_0 + f_0 \cdot ppm}$$

Simplifying and solving for  $t_f$ :

$$t_f = \Delta t \cdot \frac{1 - ppm}{2 \cdot ppm}$$

Equation 1

Now we would like to express this time until failure in terms of the system parameters ppm, n, s,  $t_d$ , and  $t_u$  (see Table 2). We can derive an expression for  $\Delta t$  using the relationships given in Table 2 as follows:

Solving  $t_d \cdot s = t_s - 2 \cdot t_g$  for  $2 \cdot t_g$  and substituting into  $\Delta t = 2 \cdot t_g$ :

$$\Delta t = t_s - t_d \cdot s$$

Substituting the given equation for  $t_s$ :

$$\Delta t = \frac{1}{n} \cdot t_u - t_d \cdot s$$

Finally, inserting this into the above equation for  $t_f$ .

$$t_f = \left(\frac{1}{n} \cdot t_u - t_d \cdot s\right) \cdot \frac{1 - ppm}{2 \cdot ppm}$$

Equation 2

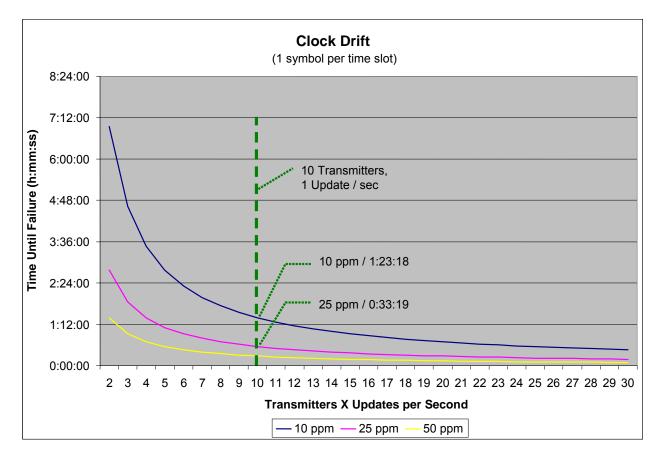

We can now use this formula to calculate some sample failure times for different system configurations. For example, we can see how different crystals and a different number of updates per second and/or number of users (transmitters) affect failure times; this is shown in Table 3. The crystal ppm rating ppm is varied over the rows while the number of updates per second multiplied by the number of transmitters (i.e.  $n / t_u$ ) is varied over the columns of the table. Note that currently, we use 50 ppm crystals as the default for these calculations, however we assume that down to 10 ppm crystals can be used at an acceptable price. Similarly, Figure 16 shows a plot of the failure times for smaller numbers of  $n / t_u$ . The number of symbols is fixed at s = 1. Note that varying this parameter does not affect these calculations by a significant amount, however at a higher number of transmitters and/or updates per second, it may not be possible to transmit a larger number of symbols (~256) per time slot and a smaller number of symbols must be used (~16).

Figure 16: Sample Failure Times

| Tx's x Upd/s | 2       | 5       | 10      | 25      | 50      | 100     | 250     | 500     | 1000    |

|--------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| 10 ppm       | 6:56:38 | 2:46:38 | 1:23:18 | 0:33:18 | 0:16:38 | 0:08:18 | 0:03:18 | 0:01:38 | 0:00:48 |

| 25 ppm       | 2:46:39 | 1:06:39 | 0:33:19 | 0:13:19 | 0:06:39 | 0:03:19 | 0:01:19 | 0:00:39 | 0:00:19 |

| 50 ppm       | 1:23:19 | 0:33:19 | 0:16:40 | 0:06:40 | 0:03:20 | 0:01:40 | 0:00:40 | 0:00:20 | 0:00:10 |

| 100 ppm      | 0:41:40 | 0:16:40 | 0:08:20 | 0:03:20 | 0:01:40 | 0:00:50 | 0:00:20 | 0:00:10 | 0:00:05 |

Table 3: Sample Failure Times (h:mm:ss)

To learn what ppm ratings would be required to enable the system to run for a certain amount of time, the above equation can be solved for *ppm*. Table 4 shows some sample systems and the required crystal ppm rating. It shows five different system configurations that may be likely to be used in different situations such as an actual production system (System 3), a system with lower update frequency (i.e. no tracking; System 4), and systems that may be used during demonstration and testing (Systems 1, 2, and 5).

| Parameters                              | Sys. 1 | Sys. 2 | Sys. 3  | Sys. 4 | Sys. 5 |

|-----------------------------------------|--------|--------|---------|--------|--------|

| Number of Transmitters (n)              | 10     | 10     | 100     | 100    | 3      |

| Update Period $(t_u)$                   | 1 sec  | 10 sec | 1 sec   | 60 sec | 1 sec  |

| Symbols per Transmission (s)            | 256    | 256    | 16      | 256    | 256    |

| Calculations                            | -      | -      | -       | -      | -      |

| Time Until Failure ( $t_f$ ) for 50 ppm | 15 min | 2.8 hr | 1.6 min | 1.6 hr | 54 min |

| Required ppm Ratings                    | -      | -      | -       | -      | -      |

| 1 hour                                  | 12     | 137    | 1.3     | 81     | 45     |

| 6 hours                                 | 2      | 23     | 0.2     | 13     | 8      |

| 24 hours                                | 0.5    | 6      | 0.05    | 3      | 2      |

Table 4: Required Frequency Stability for Specific Failure Times

We can see from these results that in any case, a long system run time is only achievable through a very high-quality crystal. In addition, a system with no feedback other than the ranging signal transmissions is vulnerable to failure in case any one unit loses its synchronization through some kind of software or hardware fault. Therefore, we wish to investigate a system that would not suffer from such a problem.

### 3.4. Random Transmissions

A radically different approach to a time-multiplexed system is one where the transmitters do not attempt to stay synchronized at all. In other words, the transmitters choose a random time within their update period at which to transmit. To be able to perform calculations, a simplified model is used where the update period  $t_u$  is divided into N slots, each slot having the duration of a transmission (i.e. no guard time). Note that this section re-uses several symbols from Table 2 in Section 3.3. We will derive the probability  $p_a$  that none of the n transmissions will overlap in one

update period. In order to calculate the probability that a certain number of transmitters will be successful in one update period, simulations were performed and the results are given below.

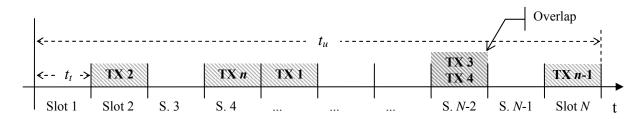

For simplicity, these calculations will assume that the update period is divided into discrete "slots" of length  $t_t$ , making the calculations possible in discrete time. This situation is pictured in Figure 17. Note that this definition of "slot" is slightly different as compared to the previous sections, as these time slots do not include a guard time at the beginning and end of each slot.

Figure 17: Random Transmission Scheme

Each transmitter would need to encode a unique ID into its transmitted signal so that the receiver can tell the different transmissions apart. This could be accomplished by encoding the transmitter ID into the transmitted waveform via a kind of OFDM modulation, or a separate data channel could be used to communicate the transmitter's ID (more discussion on both these methods will be given in following sections).

If we make the assumption that a receiver can detect when multi-symbol transmissions have overlapped partially, and that the receiver can use only the non-overlapping part of each transmission for its calculations, then the above "slots" assumption can still be used when a transmission drifts partially into an adjacent slot that contains another transmission. Hence, we can simplify the state of transmissions as being either completely overlapping (or so closely overlapping that they cannot be recovered), or non-overlapping (or partially overlapping, so that they can be recovered), and the "slots" assumption holds. For this reason, compression or expansion of the update period  $t_u$  of each individual transmitter due to clock drift is ignored in these calculations.

We will now derive the probability  $p_a$  that none of the n transmissions will overlap in one update period. As stated above, the update period  $t_u$  is divided into N slots of length  $t_t$ , so the number of slots is given by  $N = \left\lfloor \frac{t_u}{t_t} \right\rfloor = \left\lfloor \frac{t_u}{s \cdot t_d} \right\rfloor$ . During the update period, each of the n

transmissions fills exactly one slot, and these transmissions are uniformly distributed over the *N* slots. Two questions can be asked: First, what is the probability that, for each transmitter's transmission, no other transmissions will fall in that same slot, and second, what is the probability that there will be no two transmissions in the same slot during an update period? This is very similar to the "Birthday Pairing" problem in [19] (Example 2-20, pp. 39), and the derivation is as follows:

For one transmission, there are N-1 slots for other transmissions, so for each of those n-1 other transmissions the probability of falling in those other slots is (N-1)/N. Therefore, the probability that none of those other transmissions will fall in the same slot as this transmission is  $p_s = \left(1 - \frac{1}{N}\right)^{n-1}$ . Note that this does not address the question of whether or not the other transmissions will overlap; this will be addressed below. However, we can use this probability to show that in subsequent update periods, the chance of one transmitter being repeatedly overlapped becomes very low. The chance that a specific transmitter's transmission is overlapped by at least one other transmission is the inverse of the above event, i.e.  $1 - p_s$ . The chance that this happens in k subsequent update periods is  $\left(1 - p_s\right)^k$ . In the situation of 100 transmitters updating with 16 symbols once a second, we see that the probability of one transmitter being overlapped is 6.3%. In the following three update periods, we see that this probability drops to 0.4%, 0.03% and 0.002% respectively; showing that for one transmission to be corrupted repeatedly becomes very unlikely.

The second question that can be asked is, what is the probability that no two of n independent transmissions will fall into the same of N slots? There are a total of  $N^n$  ways of arranging n transmissions into N slots. However, if we take overlap into account, then the first transmission has a choice of N slots, while the second transmission has a choice of N-1 slots, the third N-2, and so on, up to N-n+1 slots for the last transmission. This gives a probability that no two transmissions will overlap of:

$$p_a = \frac{N \cdot (N-1) \cdots (N-n+1)}{N^n} = \prod_{k=1}^{n-1} \left(1 - \frac{k}{N}\right)$$

Equation 3

While  $p_a$  analytically gives the probability that none of the transmissions will overlap (and this analytical result is confirmed by simulations, as will be shown below), we may wish to learn what the probability that most (say, 90%) of the transmissions in one update period will not

overlap with others. In order to calculate these numbers, the following simulations were performed.

Since it is very impractical to calculate all the ways n transmissions can be arranged into N slots (there are  $N^n$  possible arrangements), we must approximate such calculations by randomly assigning n transmissions into N slots a large number of times (in these simulations 1,000 to 100,000 times) and drawing our statistics from these samples.

The computer model used is an *N*-element array to represent the "slots", with *n* "transmissions" randomly assigned to elements of the array. Each of the slots begins at a count of zero and is incremented when a transmission falls into that slot, allowing for overlapping transmissions. This set-up can be visualized as in Figure 17. This assignment is performed ("run") a large number of times, and each time the number of slots that contain exactly one transmission is counted as the "number of successful transmissions". Over the large number of runs, statistics on how many transmissions are successful can be calculated.

To verify these simulations, a small number of slots and transmitters were chosen to be able to accurately calculate the above statistics for all  $N^n$  arrangements. If one chooses N = 6 and n = 5, one can visualize this as five dice being thrown, with each die representing a transmitter and the number it shows as being the slot that the transmitter has chosen. There are  $N^n = 7776$  ways to arrange the transmissions into the slots.

Table 5 shows the results of the accurate calculations and the simulations. Clearly the simulation results (acquired over 100,000 runs) match well with the calculations. Note that if one wishes to know, for example, the probability that "three or more transmitters succeed", one must sum the probability of three, four and five successful transmissions (i.e. 0.463 + 0 + 0.0926 = 0.556). Also, note that the probability that all transmitters succeed matches exactly with the analytical result for this system,  $p_a = 0.0926$ . (This match was checked and held true for all systems investigated.)

| Successful<br>Transmissions | Calculated Probability | Simulated Probability |

|-----------------------------|------------------------|-----------------------|

| 0                           | 0.0394                 | 0.0388                |

| 1                           | 0.251                  | 0.251                 |

| 2                           | 0.154                  | 0.156                 |

| 3                           | 0.463                  | 0.461                 |

| 4                           | 0                      | 0                     |

| 5                           | 0.0926                 | 0.0942                |

**Table 5: Simulation Verification Results**

Table 6 shows some sample calculations and simulations of the above probabilities for more realistic systems (the same systems as in Table 4 in Section 3.3). All simulations had 100,000 runs.

| Parameters                               | Sys. 1 | Sys. 2 | Sys. 3 | Sys. 4 | Sys. 5 |

|------------------------------------------|--------|--------|--------|--------|--------|

| Number of Transmitters (n)               | 10     | 10     | 100    | 100    | 3      |

| Update Period $(t_u)$                    | 1 sec  | 10 sec | 1 sec  | 60 sec | 1 sec  |

| Symbols per Transmission (s)             | 256    | 256    | 16     | 256    | 256    |

| Calculations                             | -      | -      | -      | -      | -      |

| Number of Slots (N)                      | 95     | 953    | 1525   | 5722   | 95     |

| All transmitters succeed $(p_a)$         | 0.612  | 0.954  | 0.0362 | 0.419  | 0.969  |

| 90% of transmitters succeed (simulation) | 0.614  | 0.954  | 0.908  | 0.9998 | 0.969  |

**Table 6: Sample Probability Calculations**

#### 3.4.1. Conclusions

Using the argumentation from Sections 3.3 and 3.4, several conclusions were drawn that reflected on the design of the Data Channel. The calculations above showed that a system where the transmitters have no receive capability may be practical depending on the requirements for the number of transmitters and number of updates per second.