# Worcester Polytechnic Institute **Digital WPI**

Masters Theses (All Theses, All Years)

**Electronic Theses and Dissertations**

2002-04-30

# Versatile Montgomery Multiplier Architectures

Gunnar Gaubatz Worcester Polytechnic Institute

Follow this and additional works at: https://digitalcommons.wpi.edu/etd-theses

#### Repository Citation

$Gaubatz, Gunnar, "Versatile Montgomery Multiplier Architectures" (2002). Masters Theses (All Theses, All Years). 538. \\ https://digitalcommons.wpi.edu/etd-theses/538$

This thesis is brought to you for free and open access by Digital WPI. It has been accepted for inclusion in Masters Theses (All Theses, All Years) by an authorized administrator of Digital WPI. For more information, please contact wpi-etd@wpi.edu.

# Versatile Montgomery Multiplier Architectures

by

Gunnar Gaubatz

A Thesis Submitted to the Faculty of the

Worcester Polytechnic Institute

in partial fulfillment of the requirements for the Degree of Master of Science in

Electrical Engineering

by

April, 2002

Approved:

Dr. Berk Sunar Thesis Advisor ECE Department Dr. Fred J. Looft Thesis Committee ECE Department

Dr. John A. McNeill Thesis Committee ECE Department Dr. John A. Orr Department Head ECE Department

### Abstract

Several algorithms for Public Key Cryptography (PKC), such as RSA, Diffie-Hellman, and Elliptic Curve Cryptography, require modular multiplication of very large operands (sizes from 160 to 4096 bits) as their core arithmetic operation. To perform this operation reasonably fast, general purpose processors are not always the best choice. This is why specialized hardware, in the form of cryptographic co-processors, become more attractive.

Based upon the analysis of recent publications on hardware design for modular multiplication, this M.S. thesis presents a new architecture that is scalable with respect to word size and pipelining depth. To our knowledge, this is the first time a word based algorithm for Montgomery's method is realized using high-radix bit-parallel multipliers working with two different types of finite fields (unified architecture for GF(p) and  $GF(2^n)$ ).

Previous approaches have relied mostly on bit serial multiplication in combination with massive pipelining, or Radix-8 multiplication with the limitation to a single type of finite field. Our approach is centered around the notion that the optimal delay in bit-parallel multipliers grows with logarithmic complexity with respect to the operand size n,  $\mathcal{O}(\log_{3/2} n)$ , while the delay of bit serial implementations grows with linear

complexity  $\mathcal{O}(n)$ .

Our design has been implemented in VHDL, simulated and synthesized in  $0.5\mu$  CMOS technology. The synthesized net list has been verified in back-annotated timing simulations and analyzed in terms of performance and area consumption.

### **Preface**

In this thesis I describe research work I performed in the Cryptography and Information Security Lab during my graduate studies at WPI. This work would not have been possible without the support of many people. I would like to use this place to express my most sincere gratitude to all those who have made this possible.

First and foremost I would like to thank my advisor Prof. Berk Sunar for the advice, guidance, trust, and—last not least—the funding he has provided me with. I feel honored by being able to work with him and look forward to a continued research relationship for my Ph.D.

I became involved with Cryptography in my first semester of graduate studies at WPI, when I took my first course on the subject with Prof. Christof Paar. I would like to thank him for his excellent lectures, his enthusiasm and the opportunity to work with him.

I am very grateful to the members of my thesis committee, Prof. Fred Looft and Prof. John McNeill, for their support, advice and time, especially since the latter is usually in short supply.

Thanks must also go out to my colleagues in the CRIS lab Colleen O'Rourke, Adam Elbirt, Selçuk Baktir and Seth Hardy, for the good spirit and friendship. A big "Thank you!" to my friends and roommates Jens-Peter Kaps and Pavan Reddy for interesting night-long discussions and general friendship.

Finally, and most importantly, I want to thank my parents Erwin and Ingeborg Gaubatz and my sister Corinna for their unconditional love and support they provide me with. It means a lot to me.

To all of you thank you very much!

Worcester, Massachusetts, May 2002

Gunnar Gaubatz

# Contents

| 1 | Intr | oduction                                                 | 1  |

|---|------|----------------------------------------------------------|----|

|   | 1.1  | Motivation                                               | 2  |

|   |      | 1.1.1 Modular Multiplication in Public Key Cryptosystems | 3  |

|   |      | 1.1.2 Keysizes and Complexity of Public Key Schemes      | 4  |

|   | 1.2  | Algorithm Agility and Reusability                        | 5  |

|   | 1.3  | Scalability                                              | 6  |

|   | 1.4  | Thesis Outline                                           | 8  |

| 2 | Fini | te Field Arithmetic                                      | 9  |

|   | 2.1  | Definitions                                              | 9  |

|   | 2.2  | Arithmetic over Prime Fields $GF(p)$                     | 11 |

|   | 2.3  | Arithmetic over Binary Extension Fields $GF(2^n)$        | 12 |

|   |      | 2.3.1 Addition                                           | 12 |

|   |      | 2.3.2 Multiplication                                     | 13 |

| CONTENTS | vi |  |

|----------|----|--|

|          |    |  |

| 3 | Pre | vious ' | Work                                                | 14 |

|---|-----|---------|-----------------------------------------------------|----|

|   | 3.1 | Montg   | gomery Based Multiplier Designs                     | 14 |

|   |     | 3.1.1   | Bitserial Integer Multiplier                        | 15 |

|   |     | 3.1.2   | Unified Bitserial Integer and Polynomial Multiplier | 17 |

|   |     | 3.1.3   | Radix-8 Integer Multiplier                          | 17 |

|   | 3.2 | Altern  | native Schemes for Modular Multiplication           | 19 |

|   | 3.3 | Scalab  | ole versus Fixed Precision Architectures            | 21 |

|   | 3.4 | Unifie  | d Architectures                                     | 22 |

| 4 | Moi | ntgom   | ery Multiplication                                  | 23 |

|   | 4.1 | Gener   | al Algorithm                                        | 26 |

|   | 4.2 | Word-   | based Algorithms                                    | 27 |

|   | 4.3 | Finely  | Integrated Operand Scanning (FIOS) Algorithm        | 28 |

|   |     | 4.3.1   | Bitserial FIOS Method                               | 29 |

|   |     | 4.3.2   | High-Radix FIOS Method                              | 31 |

|   |     | 4.3.3   | Complexity Comparison                               | 33 |

| 5 | Inh | erent l | Parallelism                                         | 34 |

|   | 5.1 | Unifie  | d Digit Multiplier Core                             | 36 |

|   |     | 5.1.1   | A Detailed Look at Integer Multiplication           | 37 |

|   |     | 5.1.2   | Special Case: Carryless Multiplication              | 42 |

| CONTENTS |      |         |                                         | vii |

|----------|------|---------|-----------------------------------------|-----|

|          | 5.2  | Paralle | el Computation of Product and Reduction | 44  |

|          | 5.3  | Pipelii | ning                                    | 45  |

|          |      | 5.3.1   | Pipelining of Multiple Arithmetic Units | 45  |

|          |      | 5.3.2   | Pipelining within Arithmetic Units      | 46  |

| 6        | Syst | tem A   | rchitecture                             | 48  |

|          | 6.1  | Unifie  | d Digit Multiplier                      | 49  |

|          |      | 6.1.1   | Partial Product Array                   | 49  |

|          |      | 6.1.2   | Column Compression                      | 50  |

|          |      | 6.1.3   | Selective Carry Propagation             | 52  |

|          |      | 6.1.4   | Final Adder                             | 52  |

|          | 6.2  | MM E    | Engine                                  | 54  |

|          | 6.3  | Pipelii | ne Stage (MM Unit)                      | 56  |

|          |      | 6.3.1   | Initialization Phase                    | 57  |

|          |      | 6.3.2   | Execution Phase                         | 58  |

|          | 6.4  | FIFO    | Buffer Queue                            | 60  |

| 7        | Imp  | olemen  | tation                                  | 63  |

|          | 7.1  | Design  | Methodology                             | 63  |

|          |      | 7.1.1   | Functional Verification                 | 64  |

|          |      | 7.1.2   | Synthesis                               | 65  |

| C0 | ONTE | ENTS   |                                                                                                 | viii |

|----|------|--------|-------------------------------------------------------------------------------------------------|------|

|    |      | 7.1.3  | Back-Annotated Timing Simulation                                                                | 66   |

|    | 7.2  | Test P | Pattern Generation                                                                              | 67   |

| 8  | Res  | ults   |                                                                                                 | 68   |

|    | 8.1  | Perfor | mance Evaluation                                                                                | 69   |

|    |      | 8.1.1  | Influence of Pipelining on Performance                                                          | 70   |

|    |      | 8.1.2  | Influence of the Word Size on Performance                                                       | 73   |

|    | 8.2  | Analys | sis of Results                                                                                  | 78   |

|    |      | 8.2.1  | Speed                                                                                           | 80   |

|    |      | 8.2.2  | $\label{eq:time-time-time} \mbox{Time} \times \mbox{Area Product}  .  .  .  .  .  .  .  .  .  $ | 80   |

| 9  | Con  | clusio | ns                                                                                              | 84   |

|    | 9.1  | Furthe | er Research                                                                                     | 85   |

# List of Tables

| 6.1 | Pipeline organization and timing             | 6. |

|-----|----------------------------------------------|----|

| 8.1 | Number of clock cycles for 256-bit operands  | 72 |

| 8.2 | Number of clock cycles for 1024-bit operands | 73 |

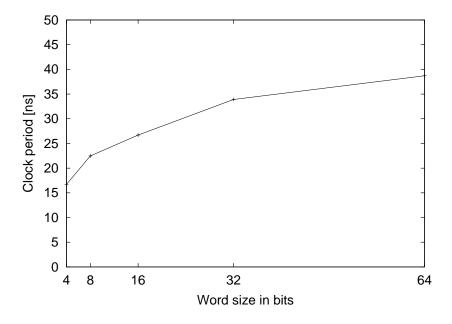

| 8.3 | Clock periods for different word sizes       | 75 |

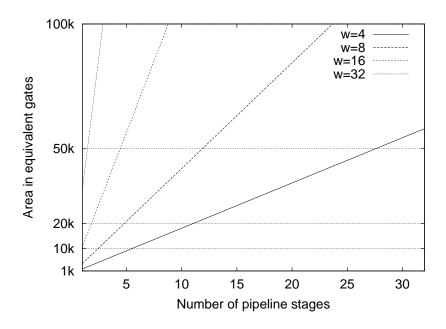

| 8 4 | Area for different word sizes                | 77 |

# List of Figures

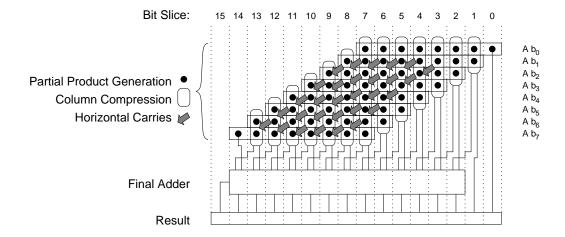

| 5.1 | $8 \times 8$ -bits digit multiplier                                     | 39 |

|-----|-------------------------------------------------------------------------|----|

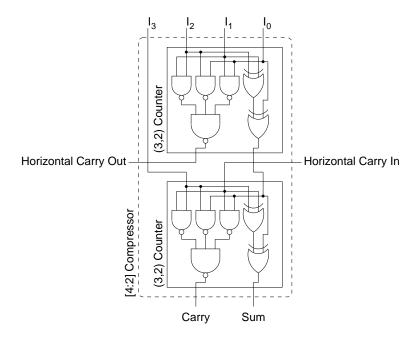

| 5.2 | [4:2] Compressor constructed from two (3,2) counters                    | 40 |

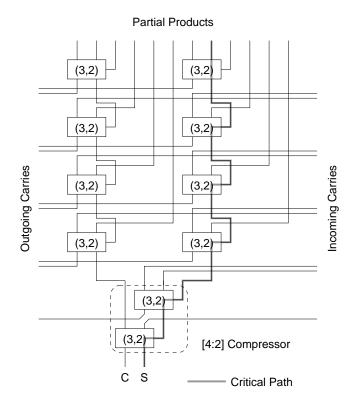

| 5.3 | Double array column compression topology                                | 41 |

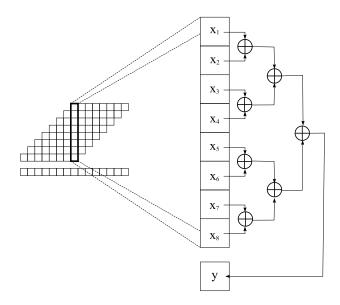

| 5.4 | Optimal topology for binary polynomials: XOR Tree                       | 43 |

| 5.5 | Pipelining of multiple arithmetic units                                 | 46 |

| 5.6 | Pipelined arithmetic unit                                               | 47 |

| 6.1 | Wallace tree for reducing 9 PP's (5 horiz. carries)                     | 51 |

| 6.2 | Pipeline structure                                                      | 59 |

| 8.1 | Clock period with respect to word size                                  | 76 |

| 8.2 | Area requirements of different (w,p) configurations $\dots \dots \dots$ | 78 |

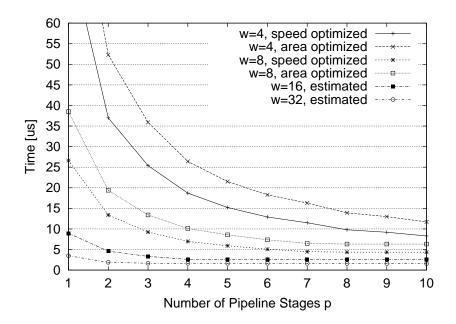

| 8.3 | Total time for 256 bit operands                                         | 79 |

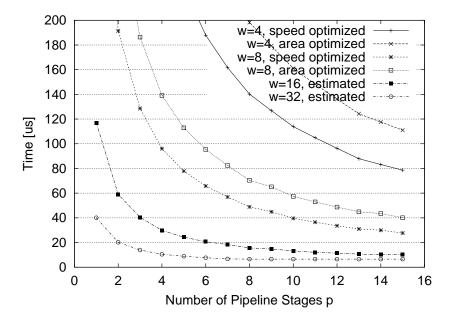

| 8.4 | Total time for 1024 bit operands                                        | 79 |

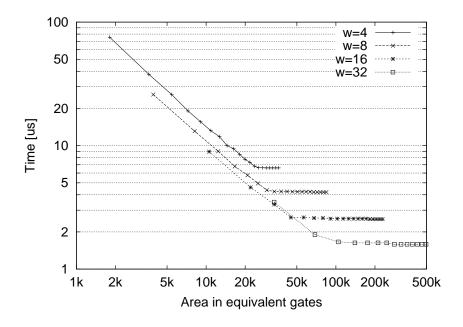

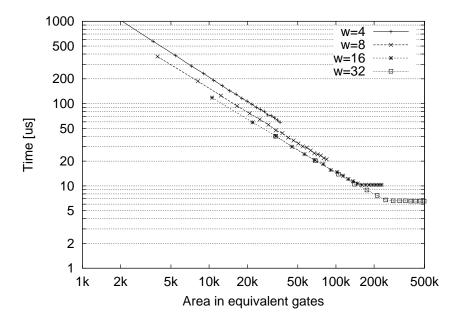

| 8.5 | Time - area tradeoff for 256 bit operands                               | 81 |

| 8.6 | Time - area tradeoff for 1024 bit operands                              | 81 |

# Chapter 1

## Introduction

Many Public Key Cryptographic (PKC) algorithms, such as RSA, Diffie-Hellman, and Elliptic Curve Cryptography, require modular multiplication of very large operands (sizes from 160 to 4096 bits) as their core arithmetic operation. To perform this operation reasonably fast, general purpose processors are not always the best choice. This is why specialized hardware, e.g. in the form of cryptographic co-processors, become more attractive.

Based upon the analysis of recent publications on hardware design for modular multiplication, this M.S. thesis presents a new architecture that is scalable with respect to word size and pipelining depth. To our knowledge this is the first time a word based algorithm for Montgomery's method is realized using high-radix bit-parallel multipliers that can perform two different types of arithmetic, (1) integer arithmetic

for operations in rings  $\mathbb{Z}_n$  or finite fields GF(p), and (2) binary polynomial arithmetic for finite fields  $GF(2^n)$  in a single unified architecture.

Earlier designs have relied mostly on bit serial multiplication in combination with massive pipelining, or Radix-8 multiplication with a limitation to integer arithmetic. Our approach is centered around the notion that the optimal delay in bit-parallel multipliers grows with logarithmic complexity with respect to the operand size n, e.g.  $\mathcal{O}(\log_{3/2} n)$ , while the delay of bitserial implementations grows with linear complexity  $\mathcal{O}(n)$ . Based on this observation we expect our design to be comparable in performance with other designs, and ultimately outperform them for large values of w.

### 1.1 Motivation

Since its conception in 1976 by Whitfield Diffie and Martin Hellman [DH76] Public Key Cryptography has come a long way. Many competing algorithms and standards have been proposed and implemented. The entire concept of "eCommerce" is based on the availability of reliable and secure methods for not only encryption, but also authentication, and integrity.

With the ongoing digital revolution and advances in high performance computing, powerful desktop computer systems are available to almost everybody at low cost. While there has always been a demand for hardware implementations of public key cryptography, the volume has risen dramatically in recent years, due to a paradigm

shift in communications, from wirebound to wireless. New and small handheld devices with low power consumption and more and more features keep appearing. Those devices do not possess the computing power of desktop computers, but still require strong security mechanisms. Here is where specialized cryptographic hardware comes into play. With the aforementioned multitude of different algorithms and standards, it is essential for any such hardware to support the necessary arithmetic primitives needed by those algorithms.

#### 1.1.1 Modular Multiplication in Public Key Cryptosystems

The majority of the currently established Public-Key Cryptosystems (RSA, Diffie-Hellman, Digital Signature Algorithm (DSA), Elliptic Curves (ECC), etc.) require modular multiplication in finite fields as their core operation which accounts for up to 99% of the time spent for encryption and decryption. In order to improve the performance of the overall cryptosystem, it is therefore crucial to optimize modular multiplication.

One method of modular multiplication that is particularly suitable for those cryptosystems mentioned above is Montgomery Multiplication. It is a method that avoids the division that is usually necessary for finding the remainder, at the cost of an additional multiplication. Since division is much more costly than multiplication, this method represents a significant improvement over regular modular multiplication.

#### 1.1.2 Keysizes and Complexity of Public Key Schemes

Current Public Key schemes are computationally very expensive. On one side this has to do with the complexity of the operations involved, e.g. modular multiplication, modular inversion, etc. On the other hand, the length of the operands involved in such operations is much larger than the word size of traditional microprocessors. They range between 160 bits for Elliptic Curve-based cryptosystems and 2048 bits or more for RSA or Diffie-Hellman.

Operations on such large operands naturally need to be broken down into word based multi-precision operations. The speed complexity of operations like multiplication is given as  $\mathcal{O}(n^2)$ , meaning that the time necessary for multiplication grows quadratically with the operand length n in words.

To illustrate the complexity a little more, the following short example shows an estimate x of the number of integer multiplications necessary for the central operation of two popular Public Key Schemes. One is a 160 bit Elliptic Curve scalar point multiplication and the other a 1024 bit RSA modular exponentiation. For more information on selecting key sizes for cryptographic applications, see [LV00]. For simplicity we assume a word size w of 32 bits and only count simple integer multiplications and nothing else. Although modular squaring can be implemented faster than multiplication, no distinction is made in this case. The number of integer multiplications p necessary for one full precision modular multiplication can be approximated as  $2n^2$ ,

where  $n = \lceil N/w \rceil$ . The average number K of modular multiplications necessary for either ECC or RSA is based on simple shift-add-methods.

|                                | ECC      | RSA       |

|--------------------------------|----------|-----------|

| Operand length N               | 160 bits | 1024 bits |

| Words / operand n              | 5        | 32        |

| # ModMul K                     | 2,280    | 1,536     |

| # Integer Mul $p \approx 2n^2$ | 50       | 2048      |

| Total # Mul $x = pK$           | 114,000  | 3,145,728 |

This table shows that the number of integer multiplications necessary to perform a single encryption is 114,000 for ECC and over 3 million for RSA. From these numbers it should be evident that public key cryptography is a time consuming application, especially on low-powered hardware for mobile use.

### 1.2 Algorithm Agility and Reusability

A number of different public key algorithms are in use today. To ensure compatibility with the rest of the world, cryptographic applications have to support a large portion of those algorithms. While software implementations are often easy to upgrade and to adapt to new algorithms or larger key sizes, the same is not necessarily true for hardware implementations.

Algorithm agility, the ability to support many different algorithms with the same architecture, is an important concept in the field of cryptography. The security of most cryptographic algorithms is not proven, but merely presumed to be intractable with currently available computing power. Moore's law therefore plays an important role in estimating key lengths for long term security. Also, one can never be entirely sure that better methods for cryptanalysis, than those currently known, do not exist. Quite recently a theoretical attack on RSA, based on an improved scheme for factoring integers, has been proposed in [Ber01] which, if practical, could render RSA keys of less than ~1500 bits insecure.

Instead of implementing a complete cryptographic algorithm in hardware, it is often better to simply build universal arithmetic units. Several of such units for certain complex operations commonly found in cryptographic algorithms, can be integrated into a microcontroller or microprocessor. The programmability of the processor provides the flexibility of this approach, the specialization of the arithmetic unit provides the performance, and the universality of the arithmetic primitives enhances the reusability.

### 1.3 Scalability

Another benefit of our design is that it is a fully scalable architecture, meaning on one hand, that parameters like wordsize and pipelining depth can be chosen arbitrarily.

This gives implementors the flexibility to fit the design for various applications with differing area, timing or power constraints.

Consider the example of a network processor inside a stand-alone router. While power consumption is not much of an issue here, high-speed performance certainly is, so a large word size and deep pipeline would be the appropriate choice of parameters.

Consider a different example, like a handheld device. It should be small for easy handling, consume as little power as possible for long battery life and have a different purpose than just encrypting data. In such a setting there is not much room left for an area intensive modular multiplier. But since we have a scalable architecture, it is possible to fit in a small scale version of the design which can then assist the main CPU leaving more processing power for the actual handheld applications.

A second meaning of scalability refers to the concept of arbitrary operand size, even after implementation in hardware. The operand size is directly related to the security level of the crypto algorithm. If, for example, a certain security level of a crypto algorithm becomes inadequate due to improved computing power available to attackers, increasing the operand size usually increases the security level, given the algorithm itself is unbroken. Therefore scalable hardware is less prone to become obsolete due to demands for higher security.

#### 1.4 Thesis Outline

After a short introduction into the mathematics of finite field arithmetic in the second chapter, the third chapter will present some of the earlier works in this field. Different concepts will be analyzed for useful ideas as well as for possible drawbacks.

Following that, the general idea of Montgomery's algorithm and more specific details of its implementation will be presented in chapter four. Chapter five will explore the different levels of parallelism that the algorithm offers to hardware designers.

Chapter six follows a bottom-up scheme of presenting the reader with the system architecture of the design that has been developed as part of this thesis. Chapter seven talks briefly about implementation issues and details, before the performance results and the analysis thereof are thoroughly discussed in chapter eight and summarized with the conclusions in chapter nine.

# Chapter 2

# Mathematical Background: Finite

## Field Arithmetic

The purpose of this chapter is to give the reader a short introduction into the mathematics of finite field arithmetic, without getting into too many details. A basic knowledge of set theory and abstract algebra is assumed.

### 2.1 Definitions

**Definition 1 (Rings)** [MvOV97] A ring  $(R, +, \times)$  consists of a set R with two binary operations + (addition) and  $\times$  (multiplication) on R, satisfying the following axioms:

- 1. (R, +) is an Abelian group with identity denoted 0.

- 2. The operation  $\times$  is associative. That is,  $a \times (b \times c) = (a \times b) \times c$  for all  $a, b, c \in R$ .

- 3. There is a multiplicative identity denoted 1, with  $1 \neq 0$ , such that  $1 \times a = a \times 1 = a$  for all  $a \in R$ .

- 4. The operation  $\times$  is distributive over +. That is,  $a \times (b+c) = (a \times b) + (a \times c)$  and  $(b+c) \times a = (b \times a) + (c \times a)$  for all  $a,b,c \in R$ .

The ring is a commutative ring if  $a \times b = b \times a$  for all  $a, b \in R$ .

An example of a ring is the set of integers  $\mathbb{Z}$ .

**Definition 2 (Fields)** [MvOV97] A field is a commutative ring in which all non-zero elements have multiplicative inverses.

This means that for all elements  $a \in R \setminus \{0\}$  there is another element  $a^{-1}$  from the same set such that  $a \times a^{-1} = 1$ . Any ring for which this condition is not fulfilled is therefore not a field. The set of integers  $\mathbb{Z}$ , for example, is not a field, since the only two elements that have a multiplicative inverse in  $\mathbb{Z}$  are -1 and 1. On the other hand, the ring  $\mathbb{Z}_p$  with addition and multiplication performed modulo p is a field if and only if p is prime.

**Definition 3 (Field Characteristic)** [MvOV97] The characteristic of a field is 0 if  $1+1+\cdots+1$  is never equal to 0 for any  $m \ge 1$ . Otherwise, the characteristic of the field is the least positive integer m such that  $\sum_{i=1}^{m} 1$  equals 0.

**Definition 4 (Polynomial Rings)** [MvOV97] If R is a commutative ring, then a polynomial in the indeterminate x over the ring R is an expression of the form

$$f(x) = a_n x^n + \dots + a_2 x^2 + a_1 x + a_0$$

where each  $a_i \in R$  and  $n \geq 0$ . The element  $a_i$  is called the coefficient of  $x^i$  in f(x).

The largest integer m for which  $a_m \neq 0$  is called the degree of f(x), denoted deg f(x);  $a_m$  is called the leading coefficient of f(x).

**Definition 5 (Finite Fields)** [MvOV97] A finite field is a field F which contains a finite number of elements. The order of F is the number of elements in F.

Some facts about finite fields [MvOV97]:

- 1. If F is a finite field, then F contains  $p^m$  elements for some prime p and integer  $m \ge 1$ .

- 2. For every prime power order  $p^m$ , there is a unique (up to isomorphism) finite field of order  $p^m$ . This field is denoted by  $\mathbb{F}_{p^m}$ , or sometimes by  $GF(p^m)$ .

### 2.2 Arithmetic over Prime Fields GF(p)

Arithmetic over prime fields GF(p) is in principle simply a combination of integer arithmetic with intermittent modular reduction steps whenever the result grows larger than the modulus M. Just like regular integer arithmetic it depends on carry propagation. Modular multiplication in its simplest form requires trial division for finding the multiple of the modulus that needs to be subtracted from the result and is therefore inherently slow. For this reason the Montgomery multiplication algorithm is used in this thesis as a faster alternative.

### 2.3 Arithmetic over Binary Extension Fields

$$GF(2^n)$$

Finite fields  $GF(p^m)$  with m > 1 are often represented in polynomial basis representation. The special case where p = 2 is usually referred to as binary extension fields. This class of finite fields is particularly suitable for arithmetic on digital computers because of the straightforward representation of coefficients as binary bit strings.

Arithmetic in binary extension fields has different properties than prime fields, but is structurally very similar. The role of the prime modulus is adopted by an irreducible polynomial f(x) of degree m.

#### 2.3.1 Addition

Addition of two binary polynomials is performed as the addition of its coefficients modulo two without any carries

$$A(x) + B(x) = \sum_{i=0}^{m} (a_i + b_i)x^i \mod 2$$

which in terms of logic circuits directly translates into XOR combinations of the coefficients

$$A(x) + B(x) = \sum_{i=0}^{m} (a_i \oplus b_i) x^i$$

It is obvious that addition of binary polynomials can be implemented in hardware very efficiently. Subtraction is the exact same operation, since each coefficient is its own additive inverse.

#### 2.3.2 Multiplication

Multiplication in  $GF(2^n)$  is only slightly more complex:

$$A(x)B(x) = \sum_{i=0}^{m} \sum_{j=0}^{m} (a_i b_j) x^{i+j} \mod f(x)$$

With p = 2 the partial products  $a_i b_j$  are the outputs of simple logical AND gates in hardware and summed up as before by XOR gates, according to their position in the resulting polynomial.

Modular reduction takes place by adding (subtracting)  $f(x)x^{k-m}$  repetitively to the result, as long as the degree of the result  $k \geq m$ . This approach is very simplistic, but achieves the desired effect. A more efficient method for modular reduction is available in form of Montgomery's algorithm. Only a couple of minor adaptions are necessary to make this integer arithmetic algorithm work in conjunction with binary polynomials, as shown in [KA98].

In conclusion it can be said that except for the modular reduction, binary polynomial arithmetic is very similar in structure to integer arithmetic. The only big difference is the absence of any sort of carry propagation, which makes this type of arithmetic so attractive for high speed hardware implementations.

# Chapter 3

## **Previous Work**

There have been numerous designs implementing modular multiplications over the years. This chapter describes some of them and contains a detailed analysis of their merits and drawbacks.

Not all of these designs are based on Montgomery multiplication, and are therefore not directly comparable to our design. Still there are other aspects in those designs that are worthy of further investigation, like scalability issues and the use of systolic arrays.

### 3.1 Montgomery Based Multiplier Designs

Three of the proposed architectures that will be discussed in this section are based on Montgomery's algorithm for modular multiplication. It is not surprising that they appear almost identical, given the fact that they all originated from the same team of researchers at Oregon State University and are based one upon the other. Still there are a couple of details distinguishing the three designs which are worth mentioning.

#### 3.1.1 Bitserial Integer Multiplier

The foundation for this series of multiplier architectures was laid in 1999 by A. Tenca and Ç. Koç's original paper [TK99]. It was centered around the ideas of the word based Montgomery Multiplication algorithm for finite fields GF(p) known from traditional software implementations, but the multiplication itself was performed in a bitserial fashion. Two design choices play a key role in why the design performs adequately fast despite the fact that the use of bitserial multiplication requires a lot of clock cycles:

- 1. Carry propagation during the addition of partial products is deferred until the very end of the algorithm by using Carry Save Adders extensively and keeping the result in redundant representation throughout most of the algorithm. This makes it possible to use wordsizes of up to 128 bits without causing a significant degradation of the clock frequency.

- 2. Massive pipelining achieves a high degree of parallelization at the cost of a negligible start-up latency.

One of the outstanding advantages of this architecture is the level of scalability that it displays. First of all the wordsize of the datapath is configurable and no major re-design is necessary. Secondly the number of pipeline stages is configurable as well, and adding a stage comes at nearly no cost, since it only requires an instantiation of one further macro-cell. These two parameters, wordsize and pipeline-depth, give the implementor a lot of choice with regards to area and speed. The notion of scalability also plays an important role once the design is manufactured. The word based algorithm around which this design is based does not, in principle, limit the maximum operand size it can handle. In practice, of course, issues like the size of certain storage elements and counters do impose a maximum wordsize. For practical applications, however, the demand for larger operands is predictable for the near future, so that provisions to accommodate them can be made easily.

The main drawbacks of the architecture are the fact that operand conversions from integer to the Montgomery domain representation and vice-versa are necessary before, respectively, after the multiplication. This, however, is a general drawback of Montgomery's method in opposition to other techniques. Also, this becomes negligible once a sufficient number of modular multiplications need to be performed in a row, e.g. like in a modular exponentiation for the RSA cryptosystem.

Another flaw of the design is the high number of clock cycles needed to compute a full modular multiplication in comparison to that of other techniques. This has to do mainly with the bitserial approach that was chosen in favour of a high radix design.

Finally, this first version of the design is suitable only for integer arithmetic modulo N in a ring  $\mathbb{Z}_N$ . It does not address other types of finite field arithmetic in use by modern cryptosystems like arithmetic over binary extension fields  $GF(2^n)$ . This type of arithmetic is frequently used in *Elliptic Curve Cryptosystems (ECC)*.

#### 3.1.2 Unified Bitserial Integer and Polynomial Multiplier

The first extension of this basic architecture by E. Savaş was published in August 2000 [STK00]. The paper describes a modification of the architecture's arithmetic kernel which, in addition to integer arithmetic, also allows computation on binary extension fields  $GF(2^n)$  at the cost of only a slight increase of the gate count.

Despite this added functionality the basic drawbacks mentioned in connection with the original design remain. Conversion between number systems are still necessary and the number of clock cycles is high.

### 3.1.3 Radix-8 Integer Multiplier

G. Todorov et. al. [TTK01] published another modification in May 2001. As before it is based upon the original architecture by Tenca and Koç, but this time investigates the use of high radix multiplication as an alternative to bitserial multiplication.

Unfortunately the radix chosen by the team is fixed to 8, so that w bits of one

operand are multiplied by only 3 bits of the second operand in each arithmetic unit. The speed improvements over the bitserial design are only marginal, considering that the radix-8 design was synthesized using  $0.5\mu$  CMOS technology instead of  $1.2\mu$  as in the earlier paper. The results do not show the anticipated performance improvement over bitserial multiplication that are expected from high-radix designs, simply because the increase in radix was not high enough. The attempt at reducing the increased complexity of adding up partial products by using Booth-Recoding [Boo51] on the multiplier input, produces such a huge overhead in delay that it hides the benefits of the higher throughput in bits per clock cycle.

Apart from the controversial [OVL96] benefits of Booth recoding for reducing the delay of small multipliers, it additionally makes the design of a unified Montgomery multiplier tremendously complicated. Techniques like Booth recoding conceptually rely on the notion of carry propagation, and don't work for multiplication of binary polynomials. As a consequence the proposed design had to drop the support of  $GF(2^n)$  arithmetic, which prevents its use in algorithm agile cryptographic processing units.

# 3.2 Alternative Schemes for Modular Multiplica-

### tion

In August 2000 J. Großschädel presented his work [Gro00] on an alternative modular multiplier architecture, which is based on Barrett's technique for modular reduction.

The main advantage of Barrett's method is that it operates in the regular number system and no transformation into a residue number system is necessary. The basic principle behind this technique is to compute an estimated quotient  $\tilde{q} = \lfloor \frac{P}{M} \rfloor$  which is used to subtract a multiple of the modulus  $\tilde{q}M$  from the most significant bits of the product P. This produces a nearly complete reduction of the product. The full reduction is computed in the final step by repeatedly subtracting the modulus and comparing the result.

The drawback of this technique is the fact that the quotient estimation works on the most significant portion of the result, which makes it very difficult to come up with a scalable architecture to allow arbitrary precision modular multiplication. As expected the design proposed by Großschädel turns out to be fixed in precision to a maximum of 1024 bit operands.

The main purpose of this architecture was to serve as the core for modular exponentiation in an RSA crypto accelerator chip. The limitation to this specific application essentially prevented a more flexible design capable of operating on both types

of fields GF(p) and  $GF(2^n)$ .

On the other hand, concentrating on one particular application brought about a very fast architecture which only needs 227 clock cycles to perform one modular multiplication, while running at a clock frequency of 200 MHz. This is made possible by a very large partial parallel multiplier of size  $1056 \times 16$  bits, based on a systolic array structure. The huge area requirements of this design approach, however, are obvious.

In May 2001 the same author presented an entirely new architecture [Gro01] that completely relies on a bitserial shift-add method for multiplication combined with repetitive subtraction of the modulus. Like in the previous design, the subtraction of the modulus is based on estimations made from the most significant portion of the intermediate result. This time, however, the architecture provides the necessary mechanisms to perform multiplication on two different types of fields, the afforementioned Galois Fields GF(p) and  $GF(2^n)$ . Similar to the bitserial multiplication in the Tenca-Koç design, carry propagation is deferred until the end of the multiplication by using Carry Save Adders and keeping the result in redundant representation.

Once again, one of the main drawbacks of the design is the evaluation of the most significant portion of the result for modular reduction, which resulted in a full-precision data-path implementation. Again the design is not scalable with respect to arbitrary precision operand sizes. Due to the bitserial multiplication strategy the

number of clock cycles is larger than that of the previous architecture.

On the positive side this increase in the clock cycle count also greatly reduces the area requirements. Additionally this design also works with a regular number representation.

#### 3.3 Scalable versus Fixed Precision Architectures

As is evident from the last section, the general algorithm of how to perform modular multiplication is irrelevant – a lot of different methods exist and all of them work. The real issue is the flexibility that an architecture provides in terms of scalability and choice of parameters like area requirements, speed and support of different types of arithmetic.

The cost-effectiveness of a hardware architecture is determined not only through the cost associated with development and manufacturing, but also through the duration of its use. This in turn is highly dependend on the flexibility the architecture exhibits in different circumstances. If, hypothetically speaking, advances in crypt-analysis suggest that the RSA cryptosystem with keylengths of 1024 bits prove to be not adequate for long term security any more, then the keysize needs to be extended. Architectures which do not scale to meet the new demands have to be replaced and thus create costs.

#### 3.4 Unified Architectures

The flexibility of an architecture to work with different types of arithmetic is a key feature for modern information security applications. A wealth of competing cryptographic algorithms exist and have been standardized. Supporting a broad range of these algorithms is no longer optional, but a necessity. The most promising model of addressing this issue in the design of a cryptographic co-processor is to add efficient arithmetic and logic primitives to a standard microprocessor / -controller architecture. This ensures an upgrade path to support future algorithms and changes to existing schemes, while preserving the speed advantages of a specialized design.

By combining the support for integer and binary polynomial arithmetic into one single unified architecture, as done in [STK00] and [Gro01], less area is needed for the same functionality.

## Chapter 4

# Montgomery Multiplication

In 1985 Peter L. Montgomery proposed a method [Mon85] for modular multiplication using Residue Number System (RNS) representation of integers. It replaces the costly division operation usually needed to perform modular reduction by simple shift operations, at the cost of having to transform the operands into the RNS before the operation and re-transforming the result thereafter.

A radix R is selected to be two to the power of a multiple of the machine word size and greater than the modulus, i.e.  $R = 2^{kw} > M$ . For the algorithm to work R and M need to be relatively prime, i.e. must not have any common non-trivial divisors. With R a power of two, this requirement is easily satisfied by selecting an odd modulus. This also fits in nicely with the cryptographic algorithms that we are targetting, where the modulus is either a prime – always odd with the exception of 2

– or the product of two primes and therefore odd as well.

RNS representations of integers are called M-residues and are usually denominated as the integer variable name with a bar above it. An integer a is transformed into its corresponding M-residue  $\bar{a}$  by multiplying it by R and reducing modulo M. The back-transformation is done in an equally straight-forward manner by dividing the residue by R modulo M. Thus we have the following equations as transformation rules between the integer and the RNS domain:

$$\bar{a} = aR \pmod{M} \tag{4.1}$$

$$a = \bar{a}R^{-1} \pmod{M} \tag{4.2}$$

Montgomery Multiplication can be written simply as the product of two M-residues divided by the radix modulo M:

$$\bar{c} = \bar{a}\bar{b}R^{-1} \pmod{M} \tag{4.3}$$

Division by the Radix is necessary to make the result again an M-residue. This becomes more obvious as we expand the equation in the following way, in which we also introduce the function name  $MM(Op_1, Op_2)$  for the Montgomery Multiplication algorithm:

$$\bar{c} = MM(\bar{a}, \bar{b})$$

$$= \bar{a}\bar{b}R^{-1} \pmod{M}$$

$$= aRbRR^{-1} \pmod{M}$$

$$= (ab)R \pmod{M}$$

$$= cR \pmod{M}$$

Assuming we have an implementation for of the MM algorithm at our disposal, it looks as if we still need a method to perform regular modular reduction if we want to transform integer variables into their respective M-residues. However, once the precision, and therefore the radix R, is fixed for the implementation, we can use the pre-computed constant  $R^2 \pmod{M}$  in conjunction with the MM algorithm for transformation purposes:

$$\bar{a} = MM(a, R^2)$$

$$= aR^2R^{-1} \pmod{M}$$

$$= aR \pmod{M}$$

(4.4)

$$a = MM(\bar{a}, 1)$$

$$= aRR^{-1} \pmod{M}$$

(4.5)

The benefits of Montgomery Multiplication over classical methods involving division are not overly evident for applications with only a few modular multiplications. However, for algorithms in which a lot of modular multiplications need to be performed with respect to the same modulus, the performance gain is much more obvious, since the ratio between transformation overhead and actual modular arithmetic is much lower.

For the sake of simplicity we will drop the "bar" notation for distinguishing M-residues from integers throughout the remainder of this thesis, since the transformation to and from the RNS is not of significance here. When it becomes necessary to distinguish the two domains, extra indication will be provided.

# 4.1 General Algorithm

Algorithm 1 outlines an implementation of Montgomery's method for the single precision case. A multiple precision word based version will be presented later. This particular example illustrates well the separate multiplication and reduction steps of the method.

As a prerequisite this algorithm expects a value M' that like the modulus M itself, may be treated as a constant, because it rarely changes. This value M' is part of the main trick behind Montgomery's method: it is used in conjunction with the lower half of the product P to compute the number of multiples U of the modulus M that need to be added to P to make its lower half become zero. Note that an addition of an integer multiple of the modulus does not change the congruence between the result and the product P. Since now the lower half is all zero, we can safely shift the

Algorithm 1: Single precision Montgomery multiplication

**Require:**

$$a, b \in \mathbb{Z}_M$$

,  $n = \lceil \log_2 M \rceil$ ,  $R = 2^n$ ,  $M' = -M^{-1} \pmod{R}$

- 1: P = ab

- 2:  $U = (P \mod R)M' \mod R$

- 3: c = (P + UM)/R

- 4: if  $c \geqslant M$  then

- 5: c = c M

#### 6: end if

result to the right, which is equivalent to a division by R.

It must be noted without going into any further details that the result c might not always be fully reduced with respect to the modulus M. Therefore it might be necessary to perform a final subtraction of the modulus. Depending on the algorithm employing Montgomery Multiplication, however, in some cases this may be delayed until the final step which transforms the M-residue result back to integer form.

## 4.2 Word-based Algorithms

In practice, primitive arithmetic operations such as multiplication and addition are limited to a certain word size w. Operands of cryptographic algorithms, on the other hand, tend to be very large, so that multiple precision arithmetic comes into play.

The simplest way of adapting Montgomery's algorithm to large operand sizes would hence be, to just replace every arithmetic operation by its multi-precision equivalent.

More efficient ways to achieve the same are analyzed and presented in [KAK96].

The criteria for selecting the most suitable algorithm is not limited to the number of multiplication operations alone. The specific architecture targeted for the implementation also plays an important role. While the "Coarsely Integrated Operand Scanning" (CIOS) method is the most suitable one for implementation on a standard PC, certain Digital Signal Processors (DSPs) feature special arithmetic operations and multiple memory busses which make an implementation of the "Finely Integrated Product Scanning" (FIPS) method a much better choice.

# 4.3 Finely Integrated Operand Scanning (FIOS) Algorithm

In a custom hardware implementation the amount of speed-up compared to general purpose processors and software mostly relies on the level of parallelization that can be achieved. For the selection of a particular Montgomery Multiplication algorithm this means that data dependencies between parallel arithmetic units and storage of intermediate results need to be kept to a minimum and local. From this perspective the most suitable algorithm is a slight variant of the "Finely Integrated Operand"

Scanning" (FIOS) method.

#### 4.3.1 Bitserial FIOS Method

A bitserial word based version of the FIOS Montgomery algorithm has first been proposed in [TK99]. It was later refined to also work on binary extension fields [STK00] with only minor architectural changes.

The following conventions are used in the explanation of the algorithm: Entire words of an operand are type-set in upper-case and referenced with their index in square brackets starting from zero. Thus A[3] stands for the fourth word of A. Single operand bits are indicated using lower-case operand names with the index as a subscript, i.e.  $b_8$  references the ninth bit in B.

As can be seen in Algorithm 2 the multiplication and reduction steps are tightly integrated. First one word of A is multiplied by a single bit of operand B and added with the previous round's intermediate result D. The least significant bit is examined and stored for use during the remainder of the inner i-loop. In case the bit is set, the odd modulus M will be added to the product in order to zero out the least significant bit. This makes it possible to shift the result one bit to the right without losing information. Writing back a word of the intermediate result D to memory is delayed by one step (line 8) in order to include the next round's least significant bit that gets shifted in.

### Algorithm 2: Bitserial word based version of the Montgomery algorithm

1: D = 0 {initialize all words of the result}

2: **for**

$$j = 0$$

to  $n - 1$  **do**

3:

$$(c,S) = A[0]b_j + D[0]$$

4:

$$u = s_0$$

5:

$$(c, S) = (c, S) + M[0]u$$

6: **for**

$$i = 1$$

to  $e - 1$  **do**

7:

$$(c,T) = c + A[i]b_j + D[i] + M[i]u$$

8:

$$D[i-1] = (t_0, S_{w-1...1})$$

9:

$$S = T$$

10: end for

#### 11: end for

The low area requirements of this algorithm make it very attractive for hardware implementations in which size and/or power consumption are the critical constraints. Bitwise multiplication can be implemented by a single AND gate per bit position. Furthermore the costly propagation of carries produced by the additions can be postponed until the very end of the algorithm by keeping intermediate results in Carry Save notation.

## 4.3.2 High-Radix FIOS Method

Algorithm 2 can be easily modified from bitserial multiplication to high radix digit multiplication, as shown in Algorithm 3. The intrinsic complexity of digit multipliers, however, significantly increases the area requirements of hardware implementations. On the other hand it also helps to decrease the number of clock cycles it takes to complete the algorithm. Furthermore, as the word size w of the digit multiplier increases, the clock period only grows logarithmically due to parallelizable addition of partial products.

Apart from multiplier complexity, the major change in the new algorithm is that not only the least significant bit of the result is to be made zero by adding M. An additional multiplication is necessary to compute the factor U, which represents the number of multiples of M to be added, to zero out the entire least significant word of the result. Accordingly the result can be shifted w bits to the right without losing

#### Algorithm 3: High Radix version of the Montgomery algorithm

1: D = 0 {initialize all words of the result}

2: **for**

$$j = 0$$

to  $e - 1$  **do**

3:

$$(C,S) = A[0]B[j] + D[0]$$

4:

$$U = SM_0' \pmod{2^w}$$

5:

$$(C,S) = (C,S) + M[0]U$$

6:

$$(C,S) >> w$$

7: **for**

$$i = 1$$

to  $e - 1$  **do**

8:

$$(C,S) = (C,S) + A[i]B[j] + D[i] + M[i]U$$

9:

$$D[i-1] = S$$

$$10: \qquad (C,S) >> w$$

11: end for

$$12: \quad D[n-1] = S$$

13: **end for**

data.

## 4.3.3 Complexity Comparison

As it has been stated before, the more complex structure of digit multipliers significantly increases the area requirements of a hardware implementation of Montgomery's Algorithm. That said, however, it is also true that more data can be processed in fewer clock cycles, and that the clock period grows logarithmically instead of linearly. These observations lead to the conclusion that a Montgomery architecture based on high radix digit multipliers can perform asymptotically better than its bitserial counterpart. The emphasis of the last sentence is on asymptotical, since additional overhead in practical implementations of digit multipliers might obscure this theoretical observation for word sizes below a certain threshold.

# Chapter 5

# Inherent Parallelism in

# Montgomery Multiplication

The common trade-off when it comes to implementation of an algorithm in hardware versus one in software is that flexibility is sacrificed for speed. In many cases, however, the use of a particular algorithm is very specific to a certain application, so that a loss of flexibility is a low price to pay for the performance improvement. An additional benefit is that the hardware solution can be optimized for reduced power consumption, since only a subset of all the features available on general purpose processors will be necessary.

There are a number of different ways to improve on the performance of complex operations in hardware. While logic and arithmetic operations take at least one clock

cycle each in software implementations, multiple logic operations can be combined into a single clock cycle in custom built hardware. Intermediate results can be stored in fast local registers instead of in a standard register file which may be placed far away. Loop-Unrolling may be used to perform multiple iterations of a task in a single clock cycle where this would help in balancing the critical paths of different tasks. Data independent shift operations or even permutations can be hardwired and therefore cost virtually nothing, while they are slow in software.

Perhaps the most efficient way of speeding up complex operations in hardware, however, is through the utilization of inherent parallelisms that a particular algorithm offers. Identifying these parallelisms is only the first step, during which automated tools for algorithm analysis and transformation might be helpful. It should be noted, however, that the success rate of such tools is limited and often even thorough analysis by hand is difficult.

In the following sections three possible ways are identified, how to parallelize the Montgomery algorithm at different levels. The degree of parallelism that can be achieved varies with the data dependency of a particular level. Sometimes, when real simultaneity is impossible due to dependence on output from an earlier step, processes can still be overlapping in time, e.g. through the use of pipelining. Depending on the definition this can still be viewed as a form of parallelism, so it is included in this chapter.

The first and innermost level of parallelism can be found inside the high radix digit multiplier, which is a core component of this architecture. One level higher the parallel computation of the product A[i]B[j] and the product used for reduction UM[i] are computed completely in parallel, once the initialization phase is over. Finally, pipelining of multiple MM Units constitutes yet another level of parallelism.

# 5.1 Unified Digit Multiplier Core

Multiplication as an arithmetic operation in hardware has been studied well. Many different methods and architectures have been proposed and built. A very general characterization shows serial multipliers on one side and bit-parallel designs on the other side of the area-delay trade off spectrum.

Bitserial multiplication is usually very easy to implement, requires little area and introduces very little delay into the critical path. However, due to the iterative nature of the operation the number of clock cycles needed for a  $n \times n$  bit multiplication grows linearly with the operand size n. Even if we ignore the problem of carry propagation for a moment, there are physical limits to the fastest clock speed that can be achieved in a particular technology, and it is thus doubtful if bitserial multiplication is the best choice when it comes to performance.

Parallel multiplier designs are typically much more complex and tend to have a longer critical path which in turn limits the maximum clock speed. However, the parallel generation of partial products also enables their addition in a parallelized fashion, using tree structures. The addition of all partial products can be performed in one single long clock cycle. The delay introduced, e.g. by a Wallace tree structure for n partial products, has the lowest bound of  $\log_{3/2} n$  levels of full adders.

This observation leads to the conclusion that parallel multipliers can outperform serial architectures in terms of speed, at the cost of more complex hardware. On the other hand increased complexity and irregularities in the hardware design also introduce additional delays due to longer wires. Obviously there must be an optimum operand size for the parallel multiplier.

#### 5.1.1 A Detailed Look at Integer Multiplication

In very generic terms the process of multiplication can be broken up into two basic steps, (1) generation of partial product terms, and (2) addition of partial products.

Partial Product Generation The first step basically consists of multiplying each bit of the first operand with each bit of the second operand and aligning the result in the correct bit position (column) for the second step. Single bit multiplication is a very inexpensive operation as it only takes a simple AND gate.

Addition of Partial Products Compared to the simplicity of step one, the second step is much more complex. Adding up partial product words involves carry propa-

gation which is a classic problem in computer arithmetic. The problem of designing fast and efficient adder structures has been studied over a long time and many architectures have been proposed. Common to them all is again the trade-off between area and delay.

Digit Multipliers As we move from bitserial towards high radix digit multipliers, the problem of adding the partial products becomes even more complex. Fully propagating all carries up to the most significant bitposition in each addition step is not feasible and also not necessary. Alternative solutions make use of partial carry propagation through a technique known as Carry Save Addition which defers the full carry propagation until the end of the operation. Partial carries that are generated at one level along the way are only passed on to the immediate next stage, one level lower. These partial carries are sometimes also called horizontal carries. The addition process of step (2) can therefore be split up into the two sub-processes (a) column compression, and (b) final addition. The typical architecture of a digit multiplier is depicted in Figure 5.1

Column Compression The amount of delay that is introduced by column compression greatly depends on the topology of the compression network. These compression networks are typically constructed from so-called (3,2) counters, which are technically the same as full adders. The name is derived from the number of in-

Figure 5.1:  $8 \times 8$ -bits digit multiplier

puts and outputs, respectively, and the fact that the two output bits, sum and carry, interpreted as a two bit integer give the count of active input bits.

The combination of two (3,2) counters as shown in Figure 5.2 constitutes an element known as a [4:2] compressor. Note that in actuality it has five inputs and three outputs, but one of each is used for horizontal carry propagation and not counted towards compression ratio. Higher order compressors can be built in a similar way.

Most of the regular topologies proposed for column compression are based upon these two building blocks. A good example is the double array topology shown in figure 5.3. The problem with simple regular topologies is that, although they often improve the delay of column compression, it is still linearly dependend on the multiplier word size.

The more complex types of regular topologies are tree topologies, such as *Binary*

Figure 5.2: [4:2] Compressor constructed from two (3,2) counters

Tree, Balanced Delay Tree and Overturned Staircase Tree. In the case of a balanced delay tree, for example, the delay only grows with complexity  $\mathcal{O}(2\sqrt{n})$ .

The biggest problems of more complex topologies compared to simpler ones are their increased wire lengths. As the feature sizes of technologies shrink below  $0.5\mu$ , the delay caused by parasitic resistance and capacitance of long wires begin to dominate the gate delay.

Complex compression topologies would ideally require a three dimensional layout in which each column can accommodate a two dimensional tree structure. The floorplan for current VLSI technologies, however, is limited to two dimensions, and so the layout has to be flattened into a single bit slice, moving components away from

Figure 5.3: Double array column compression topology

each other. This problem becomes even more apparent with irregular topologies, like  $Wallace\ Trees.$

Wallace trees are composed entirely of (3,2) counters and were first proposed in [Wal64]. They achieve the highest degree of parallelization possible and their delay only grows with complexity  $\mathcal{O}(\log_{3/2} n)$ . Traditionally Wallace Trees were not embraced by designers, because they are much harder to design and layout due to their irregular structure, as mentioned before.

In recent times, however, algorithmic layout and placement has been investigated

as a possible solution to this problem. Oklobdzija et al. [OVL96] were the first to propose an algorithm that honors the difference between fast and slow inputs and outputs of (3,2) counters. However, it did not consider the influence of different wirelengths on the overall delay along the critical path. Later versions of such an algorithm that also address wire delays were presented in [FO01].

Final Adder Column compression produces as output the product  $A \times B$  in redundant Carry Save form, i.e. each column ends with two outputs, carry and sum. To bring it back into non-redundant binary integer representation, all sum outputs must be added to the carry outputs using the Final Adder which completes the task of fully propagating all the remaining carries up to the MSB.

Since the Carry output is one bit position more significant than the Sum, it has to enter the final adder shifted to the left by one. In hardware this is easily done by appropriately wiring the two components, as can be seen in Figure 5.1.

## 5.1.2 Special Case: Carryless Multiplication

In our goal to build an architecture that is suitable for multiplication of integers as well as binary polynomials, we have to modify the digit multiplier slightly. As has been pointed out in chapter 2 the main difference between integer and binary polynomial arithmetic is that the latter does not have to deal with carries at all.

All computations between coefficients of the same order are performed modulo

Figure 5.4: Optimal topology for binary polynomials: XOR Tree

2. This property has the beneficial effect that addition can be performed by simply XOR'ing the two operands.

The modifications to the multiplier circuit which allow both integer and polynomial operations are relatively simple and only affect the column compression section and, to a lesser degree, the final adder. Since carries are not relevant for arithmetic modulo 2, we must take care that they are not propagated from one bit slice to the next-otherwise they would get added to the result. We therefore insert controlled gates between neighboring columns that form a sort of carry blockade for each horizontal carry that is generated in a bit slice. The cost for this modification is nearly negligible. An AND gate controlled by the mode signal for each horizontal carry is all that is needed. If the value of the mode signal is a logical zero, any incoming

carry will be inhibited from passing through. The final adder is not necessary either. We therefore pick the final result straight from the sum output of the column compression section instead from the final adder. A multiplexer controlled by the mode signal delivers the correct result to the output.

# 5.2 Parallel Computation of Product and Reduction

Going back to algorithm 3 we see that the main operation performed in the inner loop is an addition of four terms, of which two are multiplications. Once the initialization phase—where the factor U is computed—is over, both products can be computed completely independent from one another, as they have no common terms. The first product A[i]B[j] is the actual product of the M-residues  $\bar{a}\bar{b} = aRbR \mod M$ , while the second product is responsible for the reduction  $\bar{a}\bar{b}R^{-1} \pmod{M}$ . It performs the reduction by adding such a multiple of M to the first product that the lowest word becomes zero and shifting right by w bits is possible. The right shift essentially is a partial division by R, which is a multiple of the word size (see Alg. 1).

Since both products are completely independent from one another, it is possible to build an MM unit that sports two separate unified multiplier cores. Computing the two products in parallel reduces the clock period significantly and also simplifies the control logic, since the multipliers are dedicated to one task.

# 5.3 Pipelining

Closer examination of the word based Montgomery algorithm shows that each iteration of the inner loop only works on a limited data set. More specifically, for any iteration  $i = 0 \dots e - 1$  the intermediate result D[i - 1] is only dependent on the previous value of D[i]. While the output of the first iteration is all zero from the reduction, the second iteration produces the new value for D[0], the third iteration computes D[1], and so forth, until the inner loop is finished.

## 5.3.1 Pipelining of Multiple Arithmetic Units

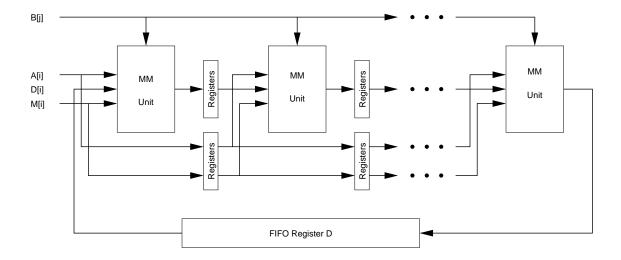

In a software implementation on a processor with only one arithmetic unit D[i-1] would have to be stored in memory temporarily, until the next iteration of the *outer* loop. Since all memory operations impose a speed penalty on the algorithm, it is better if it can be avoided. In a hardware implementation where the number of available arithmetic units is in the hand of the designers, this is much easier to do. A couple of arithmetic units can be placed in a row, connecting the in- and outputs with the intermediate results, as in Figure 5.5. A new iteration of the outer loop is started whenever the first result of a preceding unit enters the next.

This process is called *pipelining* and apart from minimizing memory accesses its

Figure 5.5: Pipelining of multiple arithmetic units

biggest advantage is that it also parallelizes the execution of an algorithm. For a pipeline depth of p arithmetic units or pipeline stages, p iterations are started one after another with a short delay, thereby overlapping them in time. Only when the first result D[0] leaves the last stage, it has to buffered in memory until the first stage becomes available again, for a new round.

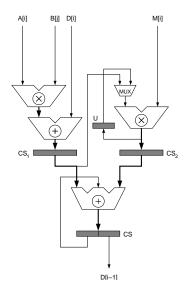

# 5.3.2 Pipelining within Arithmetic Units

Pipelining Montgomery's algorithm is not restricted to combining several arithmetic units alone. Albeit shorter, another pipeline can be created by splitting the datapath inside the unit into two separate stages, like shown in Figure 5.6. The first stage contains the two parallel multipliers, while the second stage adds the results of the

multipliers and a shifted version of the previous result. Partitioning the task in such a way reduces the critical path to that of one multiplier. It also increases the number of clock cycles necessary for executing the inner loop by one. For a sufficiently large number of iterations in the inner loop, however, the effects of this additional cycle on the total delay become negligible and the overall benefit of having a shorter clock period prevails.

Figure 5.6: Pipelined arithmetic unit

As can be seen from Algorithm 3, the inner loop is preceded by an initialization step in which the value U is computed. Data dependencies that are present only during this initialization step, introduce a start-up latency of five clock cycles before the first value D[0] is passed on to the next pipeline stage. Once initialization is complete, however, a new word D[i] is computed with each cycle.

# Chapter 6

# System Architecture

In this chapter architectural details of an actual implementation of a unified high radix Montgomery multiplier design will be discussed. Some of these details have already been mentioned in the previous chapter, but only to a degree that was necessary to convey the ideas about differences to other architectures.

Since the algorithm after which this Montgomery multiplier was modeled, has already been explained in some detail, the following sections will present detailed views of the hierarchical building blocks in a bottom-up order. In other words, the core function blocks at the bottom of the hierarchy will be presented first, followed by the next higher blocks which are based around the core elements or combine them, and so on.

# 6.1 Unified Digit Multiplier

At the center of the architecture is the double core of unified digit multipliers. As indicated in the previous chapter the two multipliers compute the product and its reduction modulo M completely in parallel, once the initialization phase is over.

#### 6.1.1 Partial Product Array

At one point during the initialization phase, which will be discussed a little later in this chapter, it is necessary to add the 2w bits wide product A[i]B[j] and the w bits wide intermediate result D[i] within the same clock cycle. Using a separate adder circuit to accomplish this would result in an increased clock period with a negative impact on performance. One alternative would be to add it one cycle later, but that would increase the start-up latency.

The best solution therefore is to incorporate the operand that has to be added into the partial product array of the digit multiplier. Since the delay only increases logarithmically with the height of the partial product array, one additional term in the array is insignificant. The only part of the multiplier affected by this modification is the column compression tree. The final adder remains entirely unchanged. On the other hand this "little trick" avoids the complexity of having another adder circuit with its own carry propagation related issues. The difference between a regular digit multiplier and one that incorporates an additional w bits wide word in the array is

that the maximum depth of the extended array is increased by one and this difference becomes less significant as w increases.

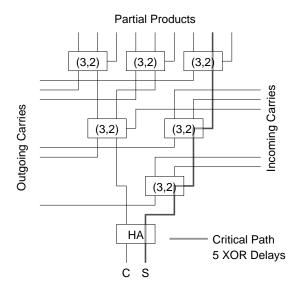

#### 6.1.2 Column Compression

The column compression layer of the unified digit multiplier is implemented using modified Wallace trees for each bit slice. These sum up the partial products using Carry-Save addition and produce the result in redundant sum and carry representation. Each level of the trees has a certain number of horizontal carries coming in from the neighboring bit slice and produces outgoing horizontal carries entering the next bit slice. The number of incoming and outgoing carries depends largely on which half of the partial product array the considered bit slice is in. For the first half in which the height h of the array increases from left to right, the incoming carries is h-4, or 0 for the first three bit slices. The number of outgoing carries is exactly one more h-3, except for the first two columns. For the second half of the array the height suddenly drops by two, because the additional w bits wide word only covers the lower half of the array, and continues to decrease linearly by one per column. Here the number of incoming carries is h-1, and that of outgoing carries h-2. As an example Figure 6.1 shows the Wallace tree for compression of the center column in an  $8 \times 8$  bit multiplier's extended partial product array.

The Wallace trees for each bit slice have been designed by hand in a fashion that

Figure 6.1: Wallace tree for reducing 9 PP's (5 horiz. carries)

follows the principles of the algorithm proposed in [OVL96]. This algorithm does not consider the influence of wire lengths on the delay of the tree, but since this thesis does not cover the entire design flow including place and route, it does not matter. Evaluation of the designs was based on the number of XOR delays that any given path contains. The path between the two inputs A, B and the Sum output of a full adder were counted as two XOR delays, while the path from the Carry input to the Sum output only contributes a single XOR delay. In cases where only two partial trees had to be connected, a half adder was used instead of a full adder to further reduce the path delay.

Even though this design methodology does not yield the optimal result for the binary polynomial case, it achieves the desired bound of  $\mathcal{O}(\log_{3/2} w)$  XOR delays for

integer multiplication. Nevertheless, polynomial multiplication is still faster than the integer case, since the final adder can be bypassed.

#### 6.1.3 Selective Carry Propagation

In the case of polynomial multiplication the horizontal carries generated in any bit slice must not be passed on to the following columns. In order to control this behavior by a signal specifying the type of arithmetic, additional circuitry is necessary. As already described in the previous chapter, the simple solution is to insert rows of AND gates between bit slices that are controlled by the field selection signal  $F\_SEL$ . Horizontal carries are propagated through the gates only if  $F\_SEL = 1$ . Otherwise the outputs will be zero.

Compared to the large number of gates that the multiplier consumes in its regular configuration, the increase in number of gates caused by the addition of this feature is irrelevant, yet the functionality of the whole circuit is improved dramatically.

#### 6.1.4 Final Adder

The purpose of the Final Adder is to convert the redundant carry-save representation of the product back into non-redundant form. To do so it has to add the sum outputs from all columns but the first to all the carry outputs shifted left by one position. The first sum output from column 0 is directly taken as the final result. The carry

vector is 2w-1 bits long and the sum vector 2w-2 bits. The final non-redundant result is of length 2w.

The straightforward approach to implement this final adder would be to simply choose the fastest available adder circuit for 2w-1 bits and place it after the column compression network. The usual choice of adders would include Carry-Select adders and members of the Carry-Look-Ahead family. The problem of this approach is, however, that the fast adder architectures consume a much higher number of logic gates per bit than simpler circuits such as Ripple Carry Adders.

The typical delay given for these fast adders relies upon the assumption that all input operands are available at the same time. However, if we take a closer look at the arrival time profile of the column compression outputs, we realize that the middle columns have the largest delay, while the columns at the edges arrive first. Based on this observation that were first made in [OVL96] we can build a hybrid final adder based on the arrival profile of the column compression layer.

For this purpose we partition the delay profile into a zone with growing delay, a plateau section where the delay is nearly constant, and a region of decreasing delay. For the first region we can use a simple ripple adder for as long as the carry ripple time is less than the delay of the compression tree. As soon as both delays approach the same value, a fast adder such as a Carry-Look-Ahead continues the addition and covers the rest of the plateau section and a little of the zone with decreasing arrival

times. For the last section a simpler adder type can be used in conjunction with a Carry Select type of mechanism. Two simple adders of the same type can start adding up the same inputs, with the only difference being the value of the incoming carry. When the real carry in is available from the fast adder, it can be used to select the correct result using a multiplexer.

This technique helps reduce both the delay and the gate count of the final adder, by overlapping the final addition with column compression and reducing the size of the adder in the critical section of the delay profile.

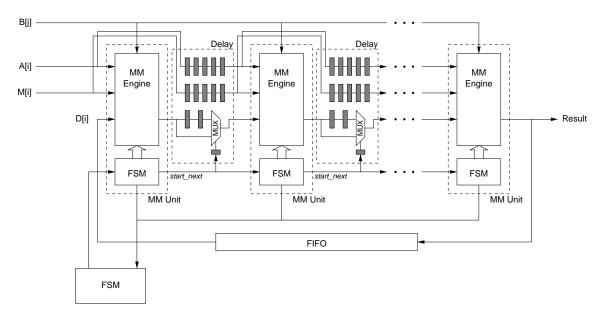

# 6.2 MM Engine

The MM Engine is the combination of the two unified digit multipliers with a three input adder into a two stage pipelined block. The name was chosen, because this component delivers the computational power of the arithmetic unit, but it relies on control signals coming in from the outside, much like the engine of a car delivers the movement, but needs to be controlled by either the driver or the cruise control.

Each of the two digit multipliers is followed by a register. A *mul\_enable* signal for each of these is used to control its behavior to either accept a new result from the multiplier at the time of a clock edge, or preserve its value. These two registers mark the boundary of the first pipeline stage of the engine.

In the second stage, a three input unified adder sums up the results of both

multipliers of width 2w along with a third value, which is the feed-back of the upper w+1 bits of the previous cycle's result shifted to the right by w positions. The adder operates in two steps:

- 1. One row of half and full adders combine the three input operands into carrysave notation. Since one operand is only w + 1 bits long, half adders combine

the upper w 1 bits of the full-size operands, while full adders combine the

common portion. The sum outputs of the adder cells now contain the pure

XOR sum as necessary for the polynomial arithmetic mode.

- 2. In order to provide carry propagation as needed in the integer arithmetic mode, a carry select adder of width 2w adds the sum outputs with the carries shifted left by one bit position, much in the same way it was done with the multipliers' final adders. The only difference here is that the arrival of the operands is close to homogeneous and using a combination of different adders does not give any advantage.

The final 2w + 1 bits wide result is selected to be either the sum outputs of the half/full adders in step 1, or the outputs of the carry select adder, depending on the  $F\_SEL$  signal. Again, the added functionality requires only very little additional gates, in this case the multiplexers necessary for bypassing the carry select adder.