### Worcester Polytechnic Institute Digital WPI

Masters Theses (All Theses, All Years)

**Electronic Theses and Dissertations**

2007-05-04

# Design of Tunable Low-Noise Amplifier in 0.13um CMOS Technology for Multistandard RF Transceivers

Wassim Khlif Worcester Polytechnic Institute

Follow this and additional works at: https://digitalcommons.wpi.edu/etd-theses

**Repository Citation**

Khlif, Wassim, "Design of Tunable Low-Noise Amplifier in 0.13um CMOS Technology for Multistandard RF Transceivers" (2007). Masters Theses (All Theses, All Years). 714. https://digitalcommons.wpi.edu/etd-theses/714

This thesis is brought to you for free and open access by Digital WPI. It has been accepted for inclusion in Masters Theses (All Theses, All Years) by an authorized administrator of Digital WPI. For more information, please contact wpi-etd@wpi.edu.

#### Design of Tunable Low-Noise Amplifier in 0.13 $\mu$ m CMOS Technology for Multistandard RF Transceivers

by

Wassim Khlif

A Thesis Submitted to the Worcester Polytechnic Institute In Partial Fulfillment of the Requirements of the Degree of Masters of Science in Electrical Engineering

by

April 2007

Approved

Eichold Luder

Professor Reinhold Ludwig Thesis Advisor ECE Department

Professor John Mcneill Thesis Committee ECE Department

1 ene

Dr. Gene Bogdonov Thesis Committee ECE Department

Hake

Professor Hossein Hakim Associate Department Head ECE Department

#### Abstract

The global market of mobile and wireless communications is witnessing explosive growth in size as well as radical changes. Third generation (3G) wireless systems have recently been deployed and some are still in the process. 3G wireless systems promise integration of voice and data communications with higher data rates and a superior quality of service compared to second generation systems. Unfortunately, more and more communication standards continue to be developed which ultimately requires specific RF/MW and baseband communication integrated circuits that are designed for functionality and compatibility with a specific type of network. Although communication devices such as cellular phones integrate different services such as voice, Bluetooth, GPS, and WLAN, each service requires its own dedicated radio transceiver which results in high power consumption and larger PCB area usage. With the rapid advances in silicon CMOS integrated circuit technology combined with extensive research, a global solution which aims at introducing a global communication system that encompasses all communication standards appears to be emerging. State of the art CMOS technology not only has the capability of operation in the GHz range, but it also provides the advantage of low cost and high level of integration. These features propel CMOS technology as the ideal candidate for current trends, which currently aim to integrate more RF/MW circuits on the same chip. Armed

with such technology ideas such as software radio look more attainable than they ever were in the past. Unfortunately, realizing true software radio for mobile applications still remains a tremendous challenge since it requires a high sampling rate and a wide-bandwidth Analog-to-Digital converter which is extremely power hungry and not suitable for battery operated mobile devices. Another approach to realize a flexible and reconfigurable RF/MW transceiver that could operate in a diverse mobile environment and provides a multiband and multistandard solution. The work presented in this thesis focuses on the design of an integrated and tunable low-noise amplifier as part of software defined radio (SDR).

# List of Figures

| 1.1 | Simplified heterodyne RF front end                               |    |  |

|-----|------------------------------------------------------------------|----|--|

| 1.2 | Ideal software radio featuring RF amplification, analog to dig-  |    |  |

|     | ital conversion, and digital baseband processing                 | 17 |  |

| 1.3 | Programmable LNA block diagram                                   | 20 |  |

| 2.1 | Resistor noise model                                             | 26 |  |

| 2.2 | Noisy resistor attached to a noiseless load resistor $R_{load}$  | 27 |  |

| 2.3 | Noise spectral density of a device having both thermal and       |    |  |

|     | flicker noise.                                                   | 32 |  |

| 2.4 | Single noisy two-port network $j$ with gain $G_j$ and internally |    |  |

|     | generated noise power $N_j$                                      | 33 |  |

| 2.5 | Cascade of three noisy two-port networks                         | 34 |  |

| 2.6 | NMOS cross sectional view.                                       | 45 |  |

| 2.7 | Illustration of impedance field method applied to an N-channel   |    |  |

|     | device                                                           | 48 |  |

| 2.8 | Equivalent circuit approach                                      | 51 |  |

| 2.9  | Representation of noise in two-port networks                                           | 57 |

|------|----------------------------------------------------------------------------------------|----|

| 2.10 | Illustration of 1-dB compression point.                                                | 66 |

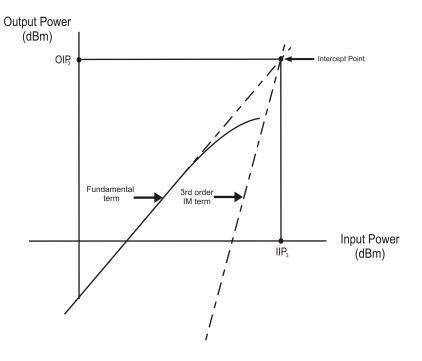

| 2.11 | Definition of third order intercept point.                                             | 69 |

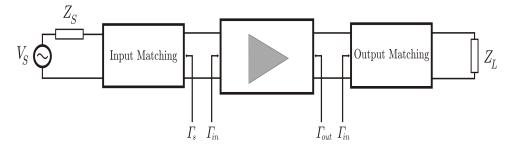

| 3.1  | General high frequency transistor amplifier.                                           | 71 |

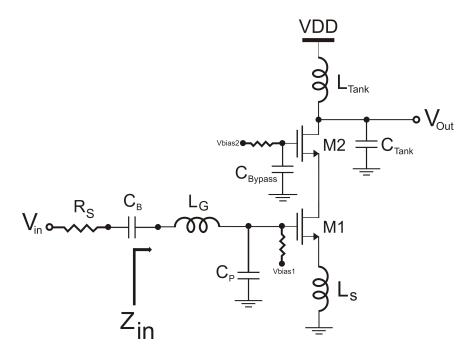

| 3.2  | Narrowband common-source LNA architecture using two ele-                               |    |

|      | ment input matching network and a cascode stage                                        | 74 |

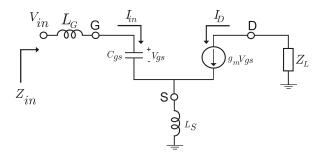

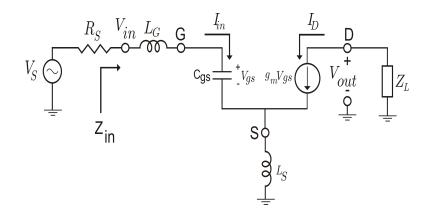

| 3.3  | NMOS small-signal model employing source degeneration and                              |    |

|      | gate inductances                                                                       | 75 |

| 3.4  | NMOS small-signal model with load impedance and voltage                                |    |

|      | source                                                                                 | 77 |

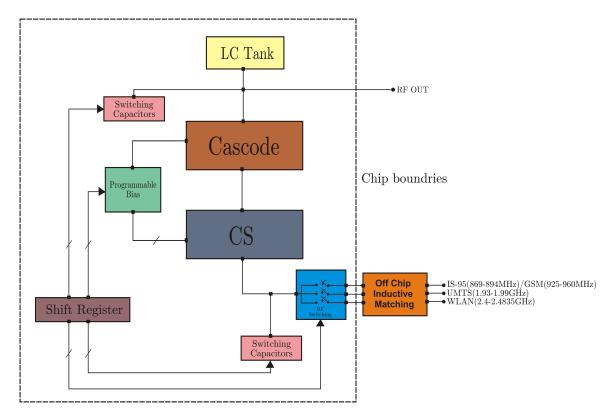

| 4.1  | Detailed programmable LNA block diagram                                                | 87 |

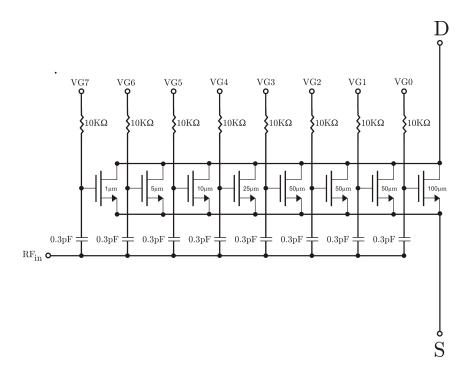

| 4.2  | Input common source device consisting of a parallel connection $\label{eq:constraint}$ |    |

|      | of eight NMOS transistors                                                              | 88 |

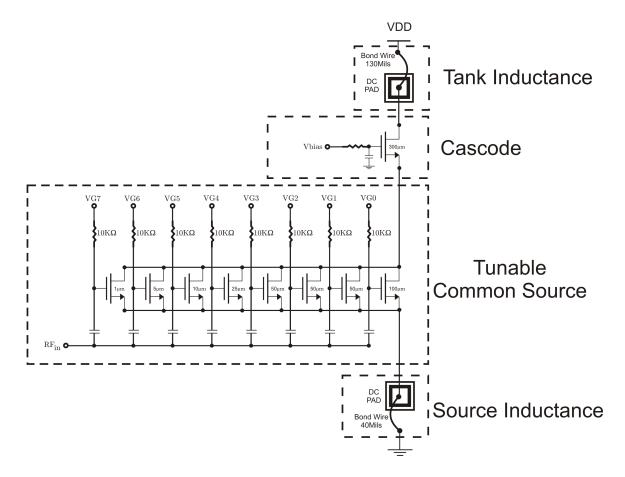

| 4.3  | Tunable common source transistor configuration with cascode                            |    |

|      | device and bondwire inductors.                                                         | 91 |

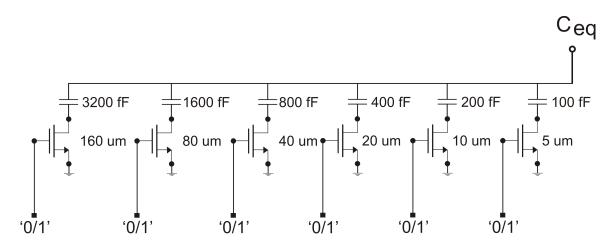

| 4.4  | Input switching capacitor circuit.                                                     | 93 |

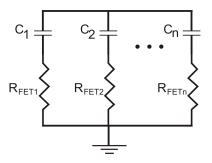

| 4.5  | Switched capacitor network equivalent circuit when all switches                        |    |

|      | are turned on                                                                          | 94 |

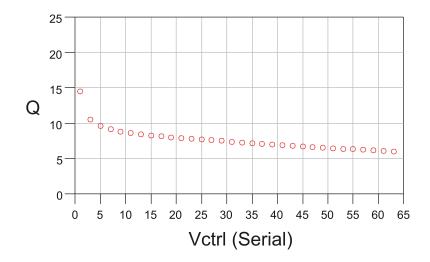

| 4.6  | Input switched capacitor network quality factor (Q) versus Vctrl.                      | 96 |

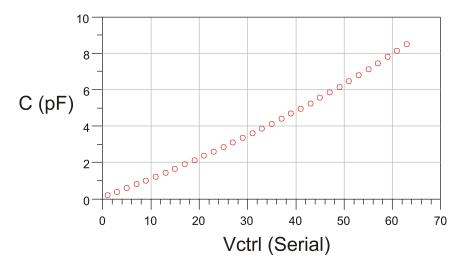

| 4.7  | Effective capacitance as a function of serial control voltage for                      |    |

|      | the input switched capacitor circuit                                                   | 97 |

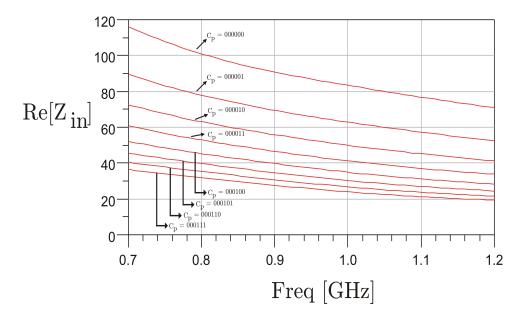

| 4.8  | Real part of input impedance vs. frequency and $C_P$ for com-                                   |

|------|-------------------------------------------------------------------------------------------------|

|      | mon source with W = 185 $\mu$ m and L = 0.13 $\mu$ m 99                                         |

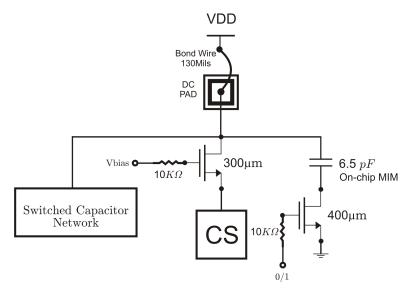

| 4.9  | Block diagram of load LC tank circuit using a switched capac-                                   |

|      | it<br>or network as well as a switchable 6.5pF MIM capacitor. $\ . \ . \ 100$                   |

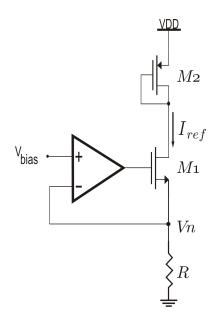

| 4.10 | Circuit topology used as a current reference for transistor DC                                  |

|      | biasing                                                                                         |

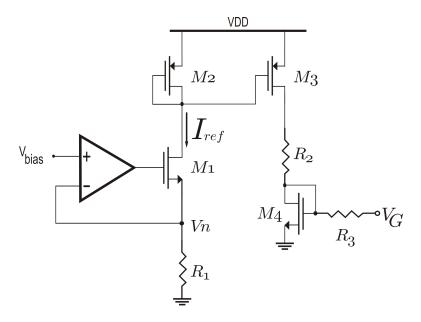

| 4.11 | Current reference circuit including current mirror PMOS and                                     |

|      | NMOS devices for providing a gate bias voltage 103                                              |

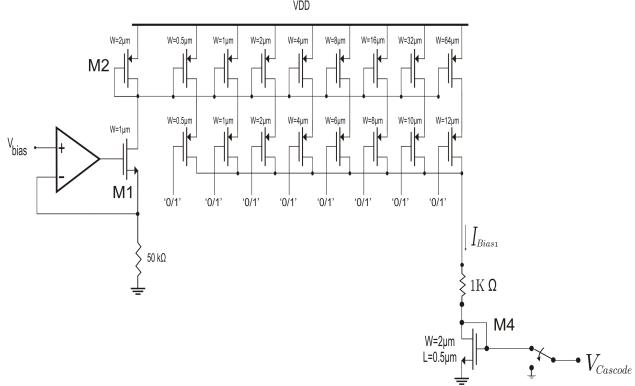

| 4.12 | Complete cascode bias circuitry employing binary weighted                                       |

|      | PMOS devices and on/off switches. $\hfill \ldots \ldots \ldots \ldots \ldots \ldots \ldots 105$ |

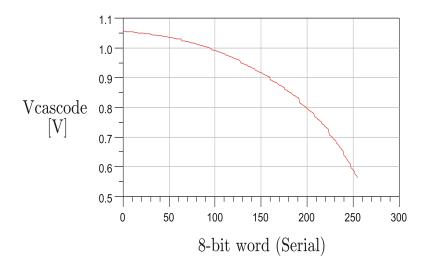

| 4.13 | Casocde bias voltage vs. serial programming bits. The X-axis                                    |

|      | represents the serial integer representation of the 8-bit word. 106                             |

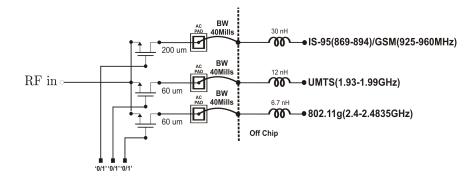

| 4.14 | NMOS RF input switches (biasing not shown) and off chip                                         |

|      | inductors                                                                                       |

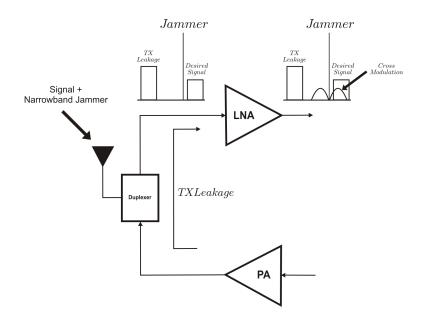

| 4.15 | $Illustration\ of\ cross\ modulation\ distortion\ in\ a\ CDMA\ transceiver$                     |

|      | [63]                                                                                            |

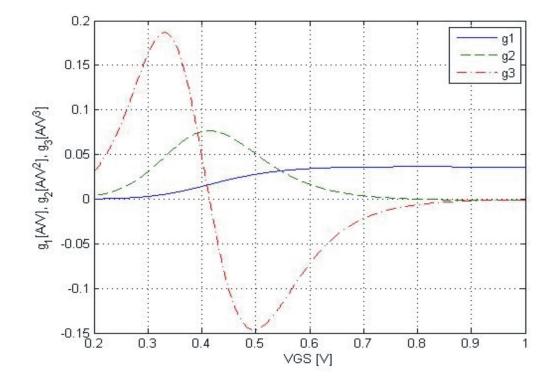

| 4.16 | First, second, and third order transconductance terms ex-                                       |

|      | tracted from $I_D$ vs $V_{GS}$ curve for a FET with dimensions of:                              |

|      | $W = 50 \mu m$ and $L = 0.13 \mu m$ . $V_{DS} = 0.7 V$                                          |

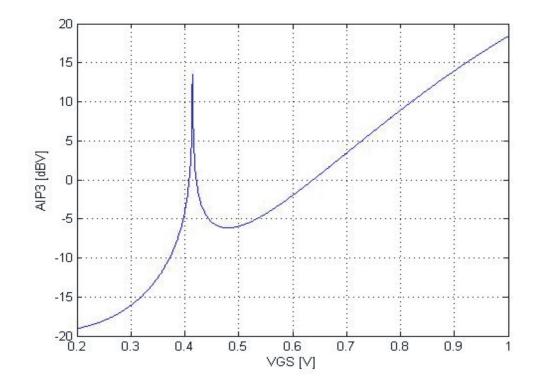

| 4.17 | Theoretical $IIP_3$ curve in dBV at DC as a function of $V_{GS}$ for                            |

|      | a width of $50\mu m$ and length of $0.13\mu m$                                                  |

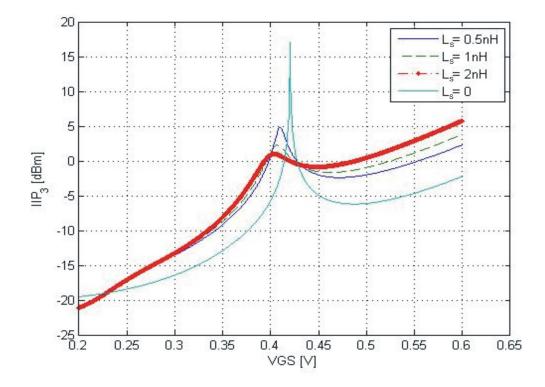

| 4.18 | Theoretical $IIP_3$ curves as a function of FET source degener-                                 |

|      | ation at $f = 900 MHz$                                                                          |

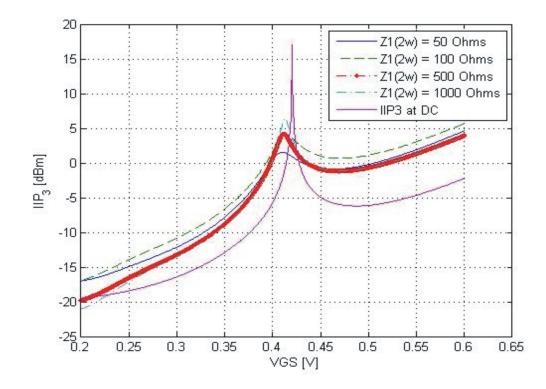

| 4.19 | Theoretical $IIP_3$ curves as a function of $Z_1(2\omega)$ for $L_S = 1nH$ 116 |

|------|--------------------------------------------------------------------------------|

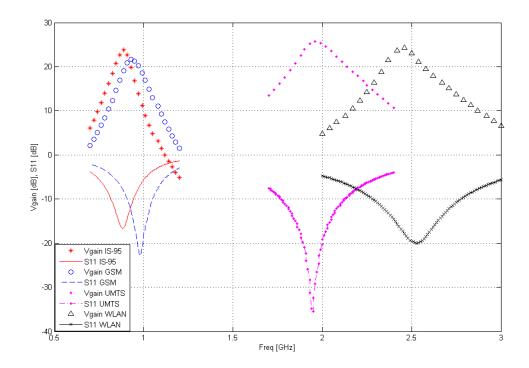

| 5.1  | LNA baseline simulation results: voltage gain and S11 for IS-                  |

|      | 95, GSM, UMTS, and WLAN                                                        |

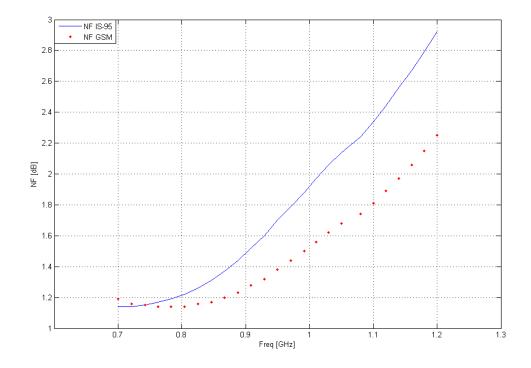

| 5.2  | LNA baseline simulation results: noise figure (NF) for IS-95 $$                |

|      | and GSM bands                                                                  |

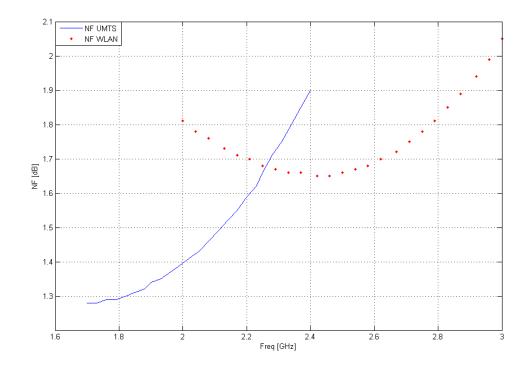

| 5.3  | LNA baseline simulation results: noise figure (NF) for UMTS                    |

|      | and WLAN bands                                                                 |

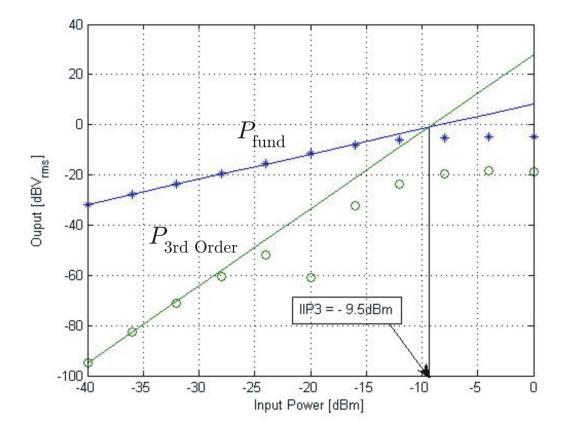

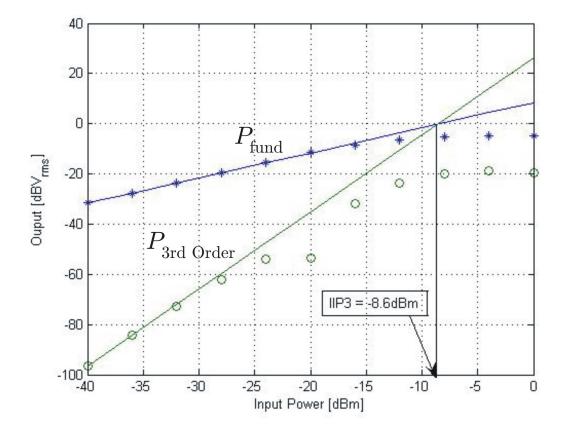

| 5.4  | Simulated IIP3 point at 880MHz                                                 |

| 5.5  | Simulated IIP3 point at 930MHz                                                 |

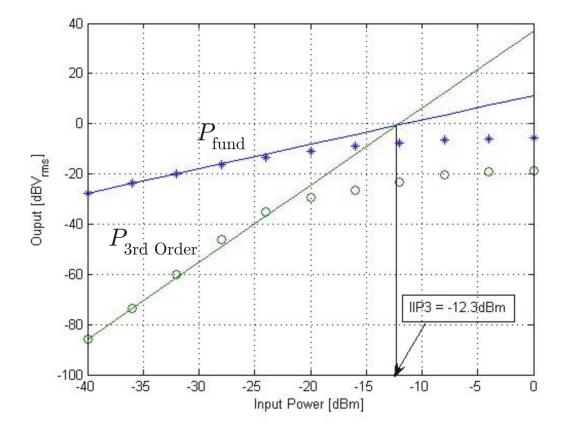

| 5.6  | Simulated IIP3 point at 1960MHz                                                |

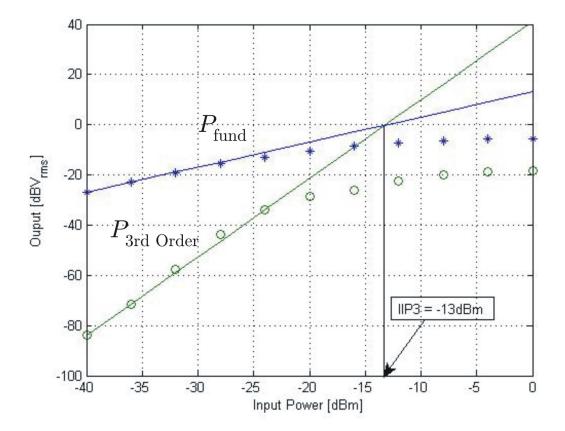

| 5.7  | Simulated IIP3 point at 2440MHz                                                |

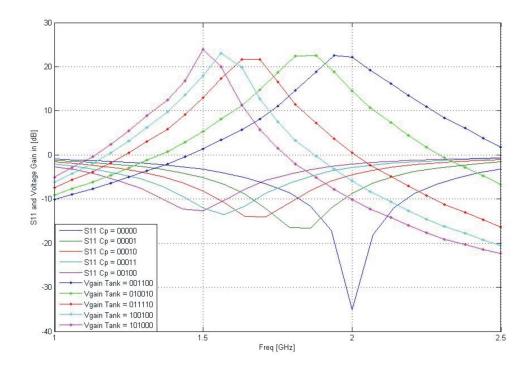

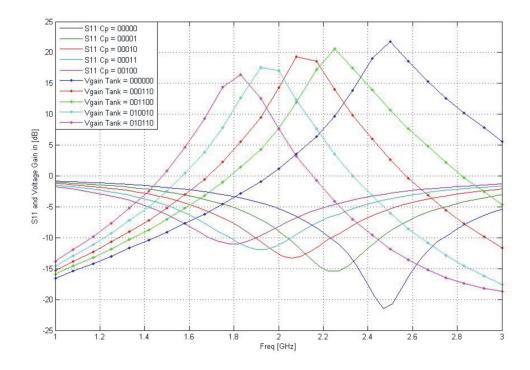

| 5.8  | Simulation results for voltage gain and input match tuning in                  |

|      | the UMTS mode of operation                                                     |

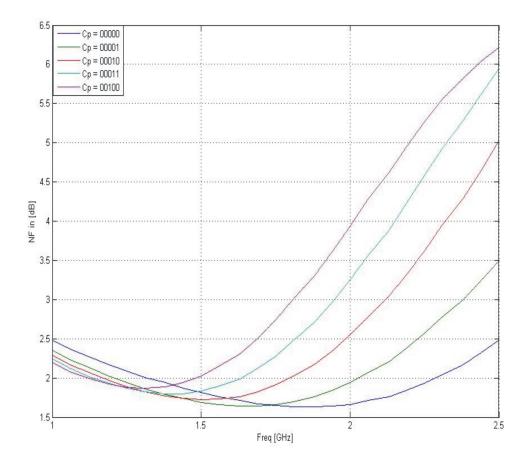

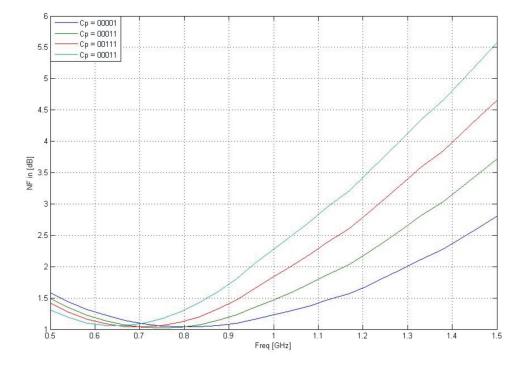

| 5.9  | Simulation results for noise figure (NF) as $C_p$ is varied in the             |

|      | UMTS mode of operation                                                         |

| 5.10 | Simulation results for voltage gain and input match tuning in                  |

|      | the WLAN mode of operation                                                     |

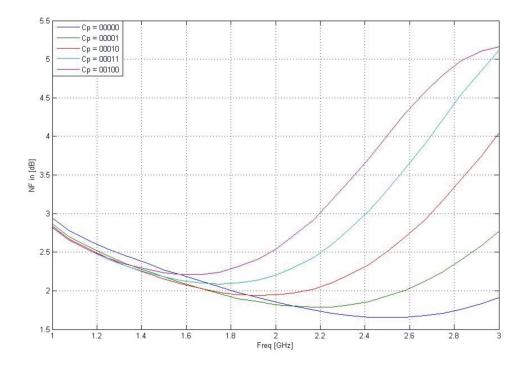

| 5.11 | Simulation results for noise figure (NF) as $C_p$ is varied in the             |

|      | WLAN mode of operation                                                         |

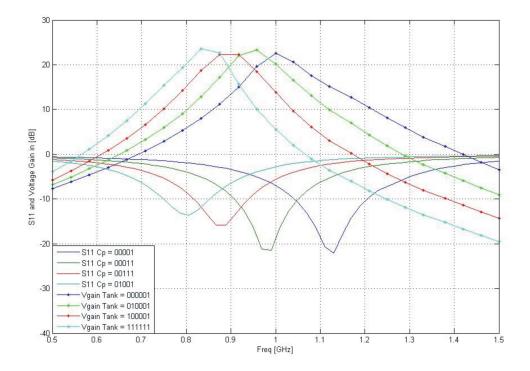

| A.1  | Simulation results for voltage gain and input match tuning in                  |

|      | the IS-95 and GSM modes of operation                                           |

|      | *                                                                              |

| A.2 | Simulation results for noise figure (NF) as $C_p$ is varied in the |  |  |  |  |  |

|-----|--------------------------------------------------------------------|--|--|--|--|--|

|     | IS-95 and GSM modes of operation                                   |  |  |  |  |  |

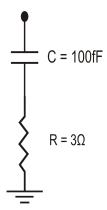

| B.1 | AC Pad with Shielding model                                        |  |  |  |  |  |

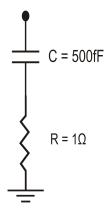

| B.2 | DC pad model                                                       |  |  |  |  |  |

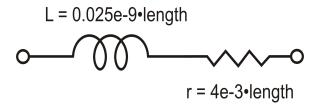

| B.3 | Bondwire model                                                     |  |  |  |  |  |

# List of Tables

| 4.1 | m IS-95/GSM900/UMTS/IEEE~802.11g~LNA~performance~spec-   |    |  |  |  |

|-----|----------------------------------------------------------|----|--|--|--|

|     | ifications.                                              | 86 |  |  |  |

| 5.1 | Summary of programmable LNA performance specifications 1 | 31 |  |  |  |

# Contents

| 1        | Intr | roduction                                  | 10 |

|----------|------|--------------------------------------------|----|

|          | 1.1  | Cellular Phones: Past, Present, and Future | 10 |

|          | 1.2  | Motivation                                 | 13 |

|          | 1.3  | Objective                                  | 20 |

| <b>2</b> | Bac  | kground Research                           | 22 |

|          | 2.1  | Introduction                               | 22 |

|          | 2.2  | Noise                                      | 24 |

|          |      | 2.2.1 Thermal Noise                        | 25 |

|          |      | 2.2.2 Shot Noise                           | 29 |

|          |      | 2.2.3 Flicker Noise                        | 30 |

|          |      | 2.2.4 Noise Factor of Cascaded Networks    | 33 |

|          |      | 2.2.5 Noise in MOSFETs                     | 36 |

|          |      | 2.2.6 Noise Modeling Methodologies         | 39 |

|          |      | 2.2.6.1 Klaassen-Prins Model               | 41 |

|          |      | 2.2.6.2 Impedance Field Method             | 47 |

|   |     |         | 2.2.6.3 Equivalent Circuit Method          | 50  |

|---|-----|---------|--------------------------------------------|-----|

|   |     | 2.2.7   | Noise Theory in Two-Port Networks          | 56  |

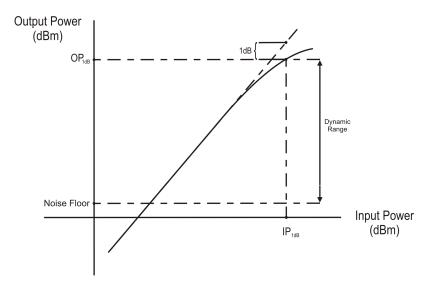

|   | 2.3 | Gain (  | Compression and Intermodulation Distortion | 62  |

|   |     | 2.3.1   | Gain Compression                           | 63  |

|   |     | 2.3.2   | Intermodulation Distortion                 | 67  |

| 3 | Low | -Noise  | e Amplifier Design                         | 70  |

|   | 3.1 | Gener   | al Considerations                          | 70  |

|   | 3.2 | The N   | arrowband CMOS LNA                         | 73  |

|   |     | 3.2.1   | Input Match                                | 74  |

|   |     | 3.2.2   | Output Matching and Gain                   | 76  |

|   |     | 3.2.3   | Noise Performance                          | 78  |

| 4 | Mul | ltistan | dard CMOS LNA Implementation               | 84  |

|   | 4.1 | Desigr  | Specifications                             | 84  |

|   | 4.2 | Detail  | ed LNA Architecture                        | 86  |

|   |     | 4.2.1   | Common Source Stage                        | 87  |

|   |     | 4.2.2   | Cascode Stage                              | 89  |

|   |     | 4.2.3   | Switched Capacitor Networks                | 92  |

|   |     | 4.2.4   | Input/Output Matching                      | 98  |

|   |     | 4.2.5   | Programmable Bias                          | .01 |

|   |     | 4.2.6   |                                            | 06  |

|   |     | 1.2.0   | Input RF Switching                         | 100 |

|              |                | 4.3.1 Distortion in RF CMOS Devices and the Optimum Bi- |

|--------------|----------------|---------------------------------------------------------|

|              |                | asing Technique                                         |

| 5            | $\mathbf{Sim}$ | ulation Results 118                                     |

|              | 5.1            | Baseline Simulation Results                             |

|              | 5.2            | Tuning                                                  |

| 6            | Con            | clusions 13:                                            |

| $\mathbf{A}$ | Tun            | ing Simulation Results 130                              |

|              | A.1            | IS-95 and GSM                                           |

| в            | Circ           | cuit Component Models 139                               |

|              | B.1            | AC Pad with Shielding                                   |

|              | B.2            | DC Pad                                                  |

|              | B.3            | Bondwires                                               |

|              | B.4            | BSIM3v3.24 ADS Model Parameters                         |

|              |                | B.4.1 NMOS Parameter File                               |

|              |                | B.4.2 PMOS Parameter File                               |

## Chapter 1

# Introduction

## 1.1 Cellular Phones: Past, Present, and Future

Very few technological advances have had such a profound impact on our daily lives as the cellular phone. It was more than twenty years ago when the first analog cellular network was introduced to the public in the United States. After decades of research and development based on an idea that originated in the late 1940s. This analog cellular network, also known as the Advanced Mobile Phone System (AMPS), was later labeled as the first generation, or 1G, wireless cellular network. While deploying such a network was a major achievement, the first generation of mobile telephones had very little popularity among the general public, mainly due to the high costs of handsets and subscriptions. In spite the financial burden, analog cellular networks soon became overcrowded and eventually services were deemed unreliable. The solution was digital transmission techniques in order to improve quality of service, increase network capacity, and reduce operating costs. This marked the birth of the second generation (2G) cellular networks with the introduction of new standards such as Global System for Mobile Communications (GSM) and IS-95. Although these new standards all relied on the advantages digital transmission techniques, they used different air interfaces. GSM uses Time Division Multiple Access (TDMA), while IS-95 uses Code Division Multiple Access (CDMA). The rise of the 2G cellular networks around the world was the turning point for the cellular telephone industry. In the United States, the number of subscribers increased from a few hundred thousands in the late 1980s to tens of millions by the in the mid 90s. Nowadays it is estimated that there are more than 1 billion cellular phone subscribers around the world.

Second generation cellular systems were mainly designed to handle voice communication. In addition, they were also designed to support low data rate transfers at 14.4 kbps [50]. The long-term vision, however, was to create a global cellular network that supports voice, data, and even video services, essentially turning the cellular phone into a multi-media global communication device that could serve as a pocket PC. Indeed, with the explosive growth and popularity of the Internet, demand rose for higher data rates over the air waves. This market demand was one of the major forces behind establishing new wireless systems that could support higher data rates such as General Packet Radio Service (GPRS), Enhanced Data Rates for GSM Evolution (EDGE), High Performance Radio LAN (HIPERLAN), International Mobile Telecommunications-2000 (IMT-2000), Wireless Local Area Networks (WLAN), Bluetooth, and many more [52]. The integration of these standards with the existing 2G standards was viewed as an evolution to the next generation of cellular networks, or 3G.

The migration to pure 3G cellular networks was a very gradual and slow progression. At first, systems such as GPRS and EDGE were developed and deployed merely as an extension to the 2G networks; they did not offer the full capabilities and services that were initially promised by 3G cellular networks. In fact, true deployment of 3G networks has just been initiated by major cellular service providers such as Verizon and Nextel, who are currently in the process of deploying 3G networks that offer average data rates between 400 and 700 kbps [53]. The essence of 3G networks is to merge voice and high-speed data services as well as to provide access to the Internet and encompass a wide range of multi-media services.

3G networks present a major and significant leap forward from the 2G networks, especially in regards to the inclusion of IP-based services. Unfortunately, with the evolution of 3G networks, many different wireless standards have been developed targeting different kinds of applications such as voice, data, images, broadcast and online gaming [52]. Some of these standards have been designed to support communications over a long distance such as Wideband CDMA (W-CDMA) while others have been developed for short range applications such as Bluetooth. The existence of all these different

standards makes it difficult for users to roam across diverse networks that provide different types of services. In many cases consumers are compelled to purchase more than one handset in order to have concurrent cellular service in the United States and Europe.

It appears clear that the telecommunication industry is moving towards a global solution. Researchers are exploring a more expanded network which may ultimately span the entire globe, and the development of a single architecture that will encompass all the different platforms that exist today. The long term vision is to have networks which are completely IP-based and allow the consumer access to any kind of service, anytime and anywhere [54]. This is the essence of the next generation of mobile systems, the 4G networks. Research into fourth generation standards has just been initiated, and according to many authorities in this field, 4G systems could become a reality as early as 2010. Although such a forecast could be considered optimistic, it is never too early to start looking into the major areas which require considerable amount of research in order for such a network to exist one day. And one of these issues is the underlying technology that is required to realize such a system.

## 1.2 Motivation

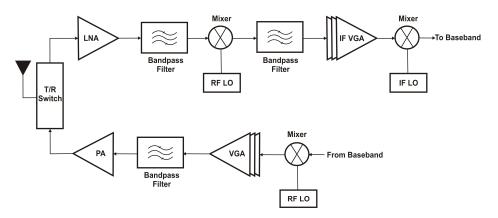

The push towards a global system requires the development of flexible, reconfigurable, and multistandard radio transceivers. In other words, there is an emerging need for radio transceivers that can support multiple wireless standards. For example, a flexible hand-held mobile device would enable a user to access the Internet through a WLAN as well as place a phone call on a GSM network. For hand-held devices to reach such flexibility requires major modifications applied to traditional RF/MW transceivers such as the one shown in Figure 1.1.

Figure 1.1: Simplified heterodyne RF front end.

The simplified architecture in shown in Figure 1.1 uses the commonly known heterodyne design introduced by E.H. Armstrong in 1918 for short wave reception [8]. It is necessary in modern digital communication circuits to use numerous types of data and channel encoding before converting the signal to higher frequency for transmission. The main point of interest here is the RF front end, hence, baseband encoding/decoding is not shown in Figure 1.1. The encoded data is upconverted by the mixer to a higher frequency which is suitable for radio transmission. An ideal mixer produces signals centered at frequencies which are the sum and differences of the data signal's center frequency and the carrier sine wave frequency generated by the RF local oscillator. The variable-gain amplifier (VGA) provides variable and controllable gain to the upconverted signal, which serves many purposes such as supplying adequate signal power at the antenna and ensuring transmitter power efficiency. In practical circuitry, mixers and amplifiers produce distortion and unwanted signals in a broad range of frequencies which can cause interference to neighboring users and other wireless systems. For this reason a bandpass filter is used to attenuate undesired frequency components and to ensure proper selection of the desired signal to be transmitted. After filtering, a power amplifier is used to boost the signal power level in order to deliver sufficient amount of power to the antenna while achieving maximum attainable power efficiency.

The receiver part of the RF front-end essentially reverses the process undergone in the transmitter. A signal in the form of an electromagnetic wave is received by the receiver antenna, in Figure 1.1 the same antenna is used for both transmission and reception. A low-noise amplifier (LNA) is used to provide power gain while adding the minimum noise power to the RF signal. The bandpass filter is used to suppress undesirable frequency components, particularly at the image frequency, produced after amplification from the LNA. A mixer downconverts the signal to a desired intermediate frequency (IF) with the aid of the local RF oscillator. Bandpass filtering is used again after the mixer to ensure selection of the desired signals while attenuating all other unwanted frequency components. The final stage consists of another amplification-mixing stage comprised of the IF VGA and the IF mixer which eventually produces a baseband signals ready to be digitized and decoded. The transceiver illustrated in Figure 1.1 operates in a half duplex mode which means that transmit and receive operations do not occur at the same time. It is for this reason that a T/R switch is needed.

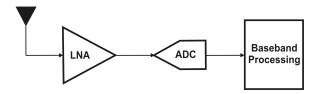

The demand for multistandard handheld devices raises the need for flexible and reconfigurable RF front-ends that are controlled by means of software. The Software Radio (SWR) concept is not a novel one [20], and over the years it has grown in scope to encompass many evolving ideas. In fact, it is somewhat difficult to present a comprehensive definition of SWR. However, in the context of realizing transceivers for the next generation of mobile networks, SWR can be defined as an emerging technology which aims at designing multiband, multistandard, reconfigurable RF front-ends that are programmed by software [20]. It is also important to mention that the SWR concept extends beyond the realm of realizing multistandard and multiband transceivers; the ideal SWR is sometimes perceived as a radio device that operates totally in the digital domain, i.e., a radio device with no analog components. This simply implies the idea of migrating the digital signal processing part of the transceiver more and more towards the antenna side. In other words, an ideal SWR would convert the RF signal received from the antenna as early as possible, see Figure 1.2.

Figure 1.2: Ideal software radio featuring RF amplification, analog to digital conversion, and digital baseband processing.

The main reason for such an approach is that the RF and analog circuitry in transceivers are most of the time the bottleneck in the design process and consume almost 70% of the total power. Nevertheless, the notion of creating a complete digital radio is beyond reach at present due to technological limitations, such as issues pertaining to the required dynamic range and bandwidth of the Analog to Digital converters (ADCs). Simply put, even with state of the art technology, ADCs which can sample a GSM or UMTS signal in the upper MHz and lower GHz range are not realizable with reasonable power consumption in battery operated mobile devices. On the other hand, advances in microelectronic fabrication has made innovative architectures possible and within reach such as single chip phones. The migration to deep sub-micron technologies has enabled the use of standard CMOS technology for RF applications. With transistor gate lengths being scaled down to 0.13- $\mu$ m and lower, the unity gain frequency of MOS transistors has exceeded the 100 GHz mark, making them very suitable for RF/MW circuit design. Unfortunately, integrated passive components such as inductors and capacitors remain one of the drawbacks of today's IC technologies due to their low quality factors [10].

On-chip inductors have been by far the most prominent challenges of conventional IC technologies. The most commonly used inductor structure is the hallow spiral, which is simply constructed by using metal traces to form a spiral shape. As the size of the metal spiral increases so does the series resistance of the structure due to the skin effect, and thus degrading the quality factor [69]. Another major issue associated with on-chip spiral inductors is the capacitive coupling to the substrate. This capacitance reduces the self resonance frequency of the inductor, and combined with a fairly conductive substrate, limits the frequency range in which the inductor can be used effectively.

Modern IC technologies offer the advantage of having several metal layers. Using spirals of identical structures constructed from different layers and connecting them in a parallel configuration helps reduce the series resistance, since the thickness of the inductor is effectively the sum of all the layers [69]. Using higher layer metals also help reduce the capacitive coupling to the substrate. Moreover, highly doped substrates featured in many modern CMOS technologies contribute to lower eddy current losses and effectively improved inductor quality factors. The combination of all these factors has boosted quality factor numbers from 5 to 20 and higher at frequencies as high as high as 5 GHz [69].

The use of on-chip inductors still remains a matter of a trade-off analysis on the part of the circuit designer. Modern technology and improved layout techniques offer significant improvements, but in many cases designers will opt to use off-chip inductors due to their superior performance and in the interest of saving space on the silicon wafer. An alternative approach is the use of bond-wire inductors which have lower resistive losses and higher self-resonance frequencies [7]. The use of these types of inductors will be discussed in more detail in later chapters.

In light of the previous discussion we realize the critical need for developing flexible, reconfigurable transceivers which can operate in a diverse environment, and CMOS technology has presented itself as the perfect candidate for such a challenge. As expected, developing multistandard RF front ends implies a considerable amount of new design challenges in transceiver building blocks such as RF filters, low-noise amplifiers, mixers, VCOs, etc. The low-noise amplifier (LNA) is an important building block of modern day transceivers since it has a major role in determining overall receiver sensitivity and noise performance. LNAs intended for cellular applications present a considerable design challenge since they are required to provide sufficient amount of power gain, add minimal noise to the received signal, maintain linear transfer characteristics over a wide dynamic range, and consume a minimal amount of power. This thesis will address the design of a multistandard LNA in a standard CMOS process. Specifically, the proposed LNA will be programmed to operate in four different operational bands for four different standards, namely GSM, IS-95, UMTS, and IEEE 802.11g.

### 1.3 Objective

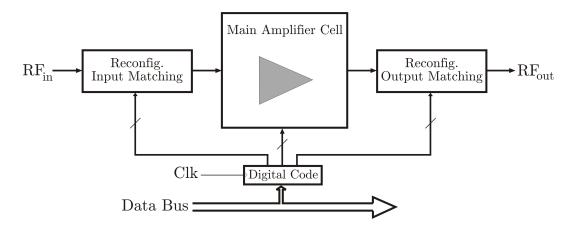

This thesis will focus on designing a multistandard and multiband programmable low-noise amplifier in a standard CMOS technology. This programmable LNA will target functionality and performance specifications of devices that are needed in next generation, multistandard software defined transceivers on a single RF CMOS chip. A top level block diagram of the LNA structure is shown in Figure 1.3. The design will comply with four different bands of operation and will incorporate mixed signal design techniques in order to enable band selection by reading a digital code. Embedded in the design process will be the understanding of major RF CMOS integrated circuit design implications and limitation, including analysis of noise behavior in MOSFET devices, the use of bond-wires in tuning/matching, linearity analysis of short channel MOSFETs, and reconfigurable matching networks.

Figure 1.3: Programmable LNA block diagram.

Reconfigurable input matching is used to provide the LNA with flexible

input impedance matching, which should provide suitable power and noise match over the entire frequency band of operation. The main amplifier cell consists of the active devices which provide the small signal gain and buffering operations. Reconfigurable output matching is implemented to provide optimum power transfer over the entire frequency band of operation to the following stage in the receiver chain. The LNA design that will be presented in thesis will target a voltage gain of no less than 20 dB, an input return loss no higher than -10 dB, and a noise figure no higher than 2 dB.

# Chapter 2

## **Background Research**

## 2.1 Introduction

The boom in wireless and mobile communications in the past two decades has spurred an enormous demand for higher performance RF products. From a designer's point of view, this translates into achieving higher performance at lowest cost, which naturally leads to the idea of more and more integration of electronic components on a single die. This is one of the major reasons why RF IC design is a very exciting and growing field of interest nowadays. The push towards integration with the aid of advances in IC technology has revolutionized RF front end design. With the growing complexity of today's mobile communication protocols and standards, the RF transceiver becomes more and more of a design challenge, especially with the growing demand for multimode, software-defined transceivers. Radio communication can simply be described as a process in which a signal is transmitted and received through the air while maintaining acceptable signal quality. In case of a receiver, for example, the RF circuitry connected to a transducer (usually an antenna) must be able to detect the desired signal, while blocking out all other interfering signals and introducing as little distortion as possible at minimal cost. In many cases, such as cellular networks, desired signal power might be lower than -100 dBm, requiring the receiver to have high sensitivity and also provide very high power gain, anywhere between 120 and 140 dB in order to detect such weak signals [7]. In a wireless environment, especially in urban areas, many interfering and blocking signals coexist alongside a weak desirable signal; this puts stringent selectivity demands on a radio receiver. In many cases receivers have to deal with large signals as well, such a case may occur when a mobile station is operating very near a base station. A receiver is still expected to accurately detect such strong signals without being driven into saturation.

Transmitters have stringent requirements, especially for power amplifiers driving the antenna. Most modern cellular handsets require a transmit power of several hundred milliwatts. This requires the power amplifier to provide 30 dB of power gain or more depending on the cellular phone standard. A power amplifier must achieve such a gain while introducing minimal distortion and keep out-of-band radiation emission as low as possible in order to comply with FCC regulations. Meeting these requirements usually involves high power consumption and/or using very high quality off-chip bandpass filters prior to the antenna, which also contribute to more power consumption and use of die or PCB space [18].

From this discussion we can see that there are many issues in RF IC design that need to be carefully addressed. This chapter will introduce some of the issues involved in designing reliable and efficient RF ICs such as noise and linearity.

### 2.2 Noise

Noise can be defined in many different ways depending on context and application. However, generally the term noise refers to anything that is undesired or interfering. In electrical engineering, noise refers to everything besides the desired signal. Noise essentially puts an upper limit on electronic system performance. In the specific case of a radio communication system, noise puts an upper limit on receiver sensitivity and complicates signal detection. Noise can be man-made such as a 60 Hz hum from power lines, or it could be intrinsic in the system itself. Such noise is random in nature and requires statistical characterization [7].

The source of noise in electronic systems was unknown in the beginning and remained a mystery until J.B. Johnson published a paper in 1927 describing noise behavior in conductive materials [31]. This noise is commonly known as thermal noise and is the fundamental source of noise in electronic devices. Other noise mechanisms in electronic devices include so-called shot noise and 1/f noise. The following sections will be a brief discussion of several types of noise mechanism in electronics devices and more specifically in MOSFETs.

#### 2.2.1 Thermal Noise

As the name implies, thermal noise is directly related to the thermal properties of materials. J. B. Johnson found that charged particles in a resistor exhibit random motion defined as Brownian motion or random walk at temperatures above 0 K. Thermal noise has a direct dependence on absolute temperature T since the random motion of charged particles is a function of temperature itself. A random current can be directly associated with random movement of charged particles and by Ohm's law we expect to observe a random voltage or noise voltage across open circuit resistors in thermal equilibrium. Indeed, Johnson found that this random voltage depends on temperature, bandwidth, and the resistance of the conducting material as follows [7]

$$\overline{v_n^2} = 4kTR\Delta f \tag{2.1}$$

where k is Boltzmann's constant, T is the absolute temperature in Kelvins, R is the resistor value in  $\Omega$ , and  $\Delta f$  is the noise bandwidth in Hz.  $\overline{v_n}$  is defined as the root mean square (rms) noise voltage. Hence,  $\overline{v_n^2}$  by definition would be the total noise power over a given bandwidth  $\Delta f$ . In the context of low frequency analog engineering, noise is usually measured in units of  $\frac{V}{\sqrt{Hz}}$ in which case (2.1) is averaged over the measurement noise bandwidth  $\Delta f$ yielding what is usually referred to as noise spectral density. As an example, a 1 K $\Omega$  resistor would have an rms noise spectral density of  $\frac{4nV}{\sqrt{Hz}}$  at room temperature. A noisy resistor is modeled as a noiseless resistor R in series with a noise voltage source as shown in Figure 2.1.

Figure 2.1: Resistor noise model.

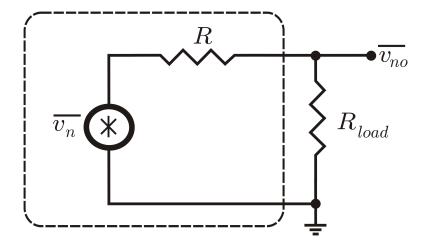

In RF engineering, units of power are recorded in decibels. They are typically used since constant reference impedances are deployed throughout the circuit interfaces such as 50  $\Omega$  or 75  $\Omega$ . Hence, a term known as available noise power is more commonly used when expressing noise in RF/MW systems. The available noise power concept arises from a very common situation in RF/MW engineering where it is important to find the power that is delivered to a certain load by a generator. In the specific case of a noisy resistor, it is simple, yet very essential, to find the noise power delivered to a load, or the available noise power at the load. This situation is depicted in Figure 2.2 where the model of a noisy resistor is loaded with a noiseless

resistor  $R_{load}$ .

Figure 2.2: Noisy resistor attached to a noiseless load resistor  $R_{load}$ .

For simplicity we assumed that the load resistor does not contribute any noise, although in a practical case the load resistor would add noise as well. If we attempt to find the available noise power at the load, we have to realize that this is a simple voltage divider circuit in which case  $\overline{v_{no}} = \frac{R_{load}}{R_{load}+R}\overline{v_n}$ . For maximum power delivery, a perfect power match is required and this implies  $R_{load} = R$ . The expression for  $\overline{v_{no}}$  simplifies to  $\overline{v_{no}} = \frac{1}{2}\overline{v_n}$ , and the output noise power is found by

$$P_o = \frac{\left(\frac{1}{2}\overline{v_n}\right)^2}{R} = \frac{\overline{v_n}^2}{4R} = \frac{4kTR\Delta f}{4R} = kT\Delta f \tag{2.2}$$

The previous result proves important in modeling many types of noisy circuits. The most relevant example in our case would be the amount of noise delivered by an antenna to a matched load. Using the same model as the one shown in Figure 2.2, here the noisy resistor models the antenna and the load resistor models a second component in the RF link such as a filter or an amplifier. If we choose a narrow-band signal, let us say 200 kHz, this means that the amount of noise power in dBm available at the load at T = 290 K is found as follows

$$P_{no} = 1.38 \times 10^{-23} (J/K) \times 290 (K) \times 200 (kHz) = 8.004 \times 10^{-16} W \approx -121 dBm$$

(2.3)

which is defined as the noise floor. The noise floor simply indicates the minimum power a 200 kHz signal can have in order to be detected in a perfect, noiseless receiver circuit. This is directly related to the concept of signal to noise ratio (SNR) which is the most prominent means of analyzing communication circuits, and is defined in dB as

$$SNR_{dB} \equiv 10 \log_{10} \left[ \frac{SignalPower(W)}{NoisePower(W)} \right]$$

(2.4)

From the previous analysis we can see that the minimum SNR is 0 dB in the case of an ideal noiseless receiver. Modern day digital communication systems require a specific SNR for reliable bit detection. Accuracy of bit detection is expressed using bit error rates (BER) in digital communication theory. BER varies depending on the type of signal (voice or data) and on the type of standard used. For example, a DECT system requires a minimum SNR of about 10 dB for a BER of  $10^{-3}$  for a 700 KHz signal [4]. Using (2.2) and adding the required SNR we obtain the following noise floor for a DECT system assuming noiseless circuitry

Noise Floor =

$$10 \log_{10} \frac{1.38 \times 10^{-23} (J/K) \times 290(K) \times 700(kHz)}{1mW} + 10 \approx -106 \, dBm$$

(2.5)

This indicates that the minimum detectable signal should be at a level no lower than -106 dBm in a noiseless receiver. Unfortunately, noiseless circuits do not exist in practice. This means that the noise performance of a receiver must be analyzed and quantified in order to determine the minimum detectable signal in a communication system. In Section 2.2.4 we analyze the effect of cascading noisy two-port networks on the system's overall noise performance.

#### 2.2.2 Shot Noise

Shot noise was discovered by Walter Schottky in 1918 while conducting experiments on vacuum tubes [71]. Shot noise has similar statistical characteristics as thermal noise since they are both described using a Gaussian distribution (white noise). However, shot noise is generated by a different mechanism. As Schottky discovered, shot noise occurs only when there is a constant (DC) current flow and a potential or energy barrier over which charged particles leap [7]. A good example of where such noise would occur would be a p - n junction. DC current is a continuous flow of charge, so on a microscopic level these charges are described as discrete particles. When these discrete particles reach a boundary where an energy barrier exists (depletion region) they will overcome the energy barrier and thus give rise to a small pulse of current. The total current measured at terminals of the device is a collection of a large number of current pulses. However, charge exhibits random motion as well. Therefore, the time of arrival of each charge to the energy barrier is random and is independent of the time of arrival of any other charged particle [27]. This is what gives rise to the random nature of shot noise. Shot noise cannot exist in linear devices such as resistors since no potential barrier exists. Shot noise current has a mean square value which was formulated by Schottky as [7]

$$\overline{i_n^2} = 2qI\Delta f \tag{2.6}$$

where q denotes the electron charge in C, I is the DC current in A, and  $\Delta f$  is the noise bandwidth in Hz.

#### 2.2.3 Flicker Noise

This type of noise is a phenomenon present in all active devices as well as some passive devices. Flicker noise is a mysterious source of noise since its origin remains a topic of debate and scrutiny among researchers. One explanation for flicker noise is the capturing and releasing of charged particles by traps in contaminated or defected crystals in integrated circuits [3]. A time constant can be associated with this trap and release process; it has been shown from measurements that a noise signal rising from such mechanism has a density concentrated at low frequencies, and hence the term 1/f noise which indicates that the noise density rises as frequency decreases. As mentioned previously, flicker noise still remains a mystery and for this reason efforts to characterize this type of noise are based on observations and measurements. Consequently, many empirical forms have been introduced which sometimes include several fitting parameters that are deduced by statistical means. In the interest of simplicity, flicker noise can be modeled using the following equation [7]

$$\overline{v_{1/f}} = \frac{K}{f^n} \Delta f \tag{2.7}$$

where  $\overline{v_{1/f}}$  is the rms voltage, K is a fitting parameter which is process and device dependent, n is a constant exponent usually close to unity, and  $\Delta f$ is the noise bandwidth. The parameter K has also been shown to depend on bias conditions, i.e., DC current flowing in the device. For this reason, another form that incorporates this is shown in (2.8) [3]

$$\overline{i_{1/f}} = K_1 \frac{I^a}{f^b} \Delta f \tag{2.8}$$

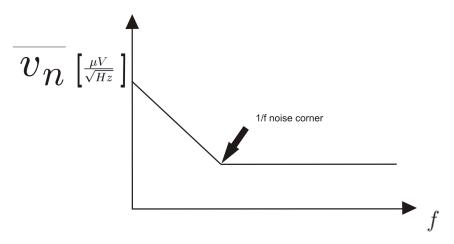

where I denotes the DC current,  $K_1$  is a fitting parameter,  $\Delta f$  is the noise bandwidth, and a and b are constant exponents. In some cases flicker noise can be referred to as excess noise in resistors since this appears to be in excess of thermal noise. Therefore, depending on operating frequency we expect to see certain noise mechanisms dominate more than others. Taking the example of a linear resistor, we expect flicker noise to dominate at low frequency and thermal noise to dominate at higher frequencies. This is illustrated in Figure 2.3 as noise voltage root spectral density of a certain component such as a resistor or a MOSFET.

Figure 2.3: Noise spectral density of a device having both thermal and flicker noise.

A common term associated with such a measurement is flicker  $(\frac{1}{f})$  noise corner which simply refers to the intersection of the  $\frac{1}{f}$  curve and the thermal noise curve. It indicates the point along the frequency scale where the  $\frac{1}{f}$  noise starts to dominate. Given the  $\frac{1}{f}$  dependence of flicker noise, its amplitude distribution is not Gaussian and cannot be described as white noise; in fact flicker noise is sometimes referred to as pink noise since it has a large low frequency content [5].

# 2.2.4 Noise Factor of Cascaded Networks

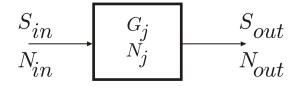

The goal of this analysis is to quantify the effect of the noise power from a generator's source resistance on the overall noise power at the output of an RF transceiver system. We first start by analyzing a single two-port network as the one shown in Figure 2.4. From this we express the total noise factor of the network as

$$F_{j} = \frac{N_{out}}{N_{in}} = \frac{G_{j}N_{in} + N_{j}}{G_{j}N_{in}} = 1 + \frac{N_{j}}{G_{j}N_{in}}$$

(2.9)

where  $N_j$  is the internally generated noise power by the network j and  $G_j$  is the network gain. We can relate the noise factor to  $N_j$  as

$$F_j - 1 = \frac{N_j}{G_j N_{in}} \tag{2.10}$$

Figure 2.4: Single noisy two-port network j with gain  $G_j$  and internally generated noise power  $N_j$ .

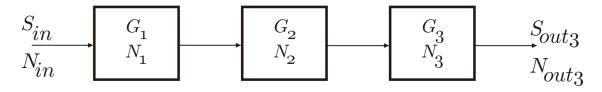

We next consider a system of multiple cascaded networks, say three, as shown in Figure 2.5. Without loss of generality, the noise factor in this case is expressed as the ratio of overall output noise power to the output noise power due to the source resistance as follows

$$F_{total} = \frac{N_{out3}}{N_{out3(source)}} \tag{2.11}$$

We can write the overall noise power,  $N_{out3}$ , at the output for the three-block configuration as

$$N_{out3} = G_3(G_2(G_1N_{in} + N_1) + N_2) + N_3$$

$$G_3G_2G_1N_{in} + G_3G_2N_1 + G_3N_2 + N_3$$

(2.12)

Figure 2.5: Cascade of three noisy two-port networks.

The noise power at the output due to the source resistance is:  $N_{out3(source)} = G_1G_2G_3N_{in}$ . Inserting this expression along with (2.12) in (2.11), we obtain

$$F_{total} = 1 + \frac{N_1}{G_1 N_{in}} + \frac{N_2}{G_1 G_2 N_{in}} + \frac{N_3}{G_1 G_2 G_3}$$

(2.13)

Using the result in (2.10), we can rewrite (2.13) as

$$F_{total} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2}$$

(2.14)

This result can be generalized for k networks by writing the total noise power at the output, and the total noise power at the output due to the source resistance of the kth stage is given by

$$N_{out(total_k)} = (G_1 \dots G_k)N_{in} + (G_2 \dots G_k)N_1 + (G_3 \dots G_k)N_2 + \dots + G_k N_{k-1} + N_k$$

(2.15)

$$N_{out(source_k)} = G_1 \dots G_k N_{in} \tag{2.16}$$

Using (2.11) and (2.10) we can write the generalized noise factor for k networks as

$$F_{total(k)} = 1 + \frac{F_1 - 1}{G_1} + \frac{F_2 - 1}{G_1 G_2} + \dots + \frac{F_{k-1}}{G_1 \dots G_{k-2}} + \frac{F_k}{G_1 \dots G_{k-1}}$$

(2.17)

From the previous analysis we can see the importance of having a first stage which provides sufficient gain and, more importantly, has a relatively low noise factor. This is the reason why LNAs are most of the time used as the first component in a receiver chain. The expression in (2.17) was obtained assuming all stages have the same input and output resistance. The result can be extended for cases where this is not a valid assumption [26]

## 2.2.5 Noise in MOSFETs

Analysis of noise in MOSFETs is essential, especially in the context of designing low noise CMOS circuits. Noise mechanisms in MOS transistors are similar in nature to other active devices such as bipolar transistors. Since FETs are essentially voltage controlled resistors, we expect thermal noise to exist in the observed drain current. Van der Ziel was the first to analytically formulate drain thermal noise current in MOSFETs and his work resulted in a simple expression for drain noise current spectral density as follows [31]

$$\overline{i_{nd}^2} = \gamma 4kTg_{d0} \bigtriangleup f \tag{2.18}$$

where  $\gamma$  is a bias dependent parameter and  $g_{d0}$  is the drain-source conductance at zero  $V_{DS}$ . Based on the fact that the gate terminal of a MOSFET is coupled to the channel via the oxide capacitance and at high frequencies the gate impedance becomes small, drain noise current induces a gate noise current given by the following [32]

$$\overline{i_{ng}^2} = \delta 4kTR_{gs}\omega^2 C_{gs}^2 \Delta f \tag{2.19}$$

where  $\delta$  is another bias dependent parameter, similar to  $\gamma$  used in (2.18),  $R_{gs}$  is the gate series resistance, and  $C_{gs}$  is the gate-source capacitance. More simplified forms of the gate noise are usually presented where the term  $(R_{gs}\omega^2 C_{qs}^2)$  is lumped into a single parameter  $g_g$ . Hence, (2.19) becomes

$$\overline{i_{ng}^2} = \delta 4kTg_g \Delta f \tag{2.20}$$

It is important to note that both drain and gate noise currents described in equations (2.18) and (2.20) arise from the same source, which is the random thermal charge motion in the channel [12]. In a statistical sense this implies that the gate and drain noise currents are correlated with a correlation factor usually denoted by C; it is defined as

$$C \equiv \frac{\overline{i_{ng}i_{nd}^*}}{\sqrt{\overline{i_{ng}^2}.\overline{i_{nd}^2}}}$$

(2.21)

where (\*) denotes the complex conjugate operation.

The equations presented above model the thermal noise behavior in MOS transistors. Other noise mechanisms exist in MOS devices such as flicker noise and shot noise. As described in Section 2.2.3, flicker noise is a dominant source of overall device noise at low frequencies, and thus will not be considered here since we are only interested in the high frequency noise behavior of the MOS transistor (it has been shown that thermal noise is dominant at such frequencies). Also shot noise will not be considered since MOS transistors do not exhibit such kind of a noise mechanism when biased in saturation, which is the bias condition commonly used for MOS transistors in RF amplifier design.

The bias dependent parameters,  $\gamma$  and  $\delta$ , have been well documented for long channel devices. Van der Ziel found that  $\gamma$  is unity at  $V_{DS} = 0$  and decreases to about 2/3 in saturation. The parameter  $\delta$  has a value of approximately twice that of  $\gamma$  (4/3) for long channel devices [7]. As technology has advanced and device size has continued to scale down into the submicron regime, early research efforts, such as [58] and [59], reported significant enhancement of drain thermal noise and induced gate noise in submicron MOSFETs. The enhancement factors of drain and gate noise in submicron devices are usually related to long channel devices via the  $\gamma$  and  $\delta$  parameters. In the case of drain noise current,  $\gamma$  was found to be 12 times larger than the classical long channel value for an n-channel device of 0.7- $\mu m$  of gate length in [58]. An enhancement factor of 30 was reported for induced gate noise in devices with 0.25- $\mu$ m gate length [17]. Numerous models were developed to explain the dramatic increase in channel thermal noise and induced gate noise, most of which invoke the effect of hot electrons in the device's conducting channel and non-quasi static effects. Other research efforts [13] have shown that the main contributor to the increase in channel thermal noise in short channel devices is the velocity saturation and mobility degradation of charge carriers in the channel due to the effect of high electric fields in short channel devices. The noise enhancement factors reported in |12| were no more than 3 or 4 times the classical long channel values; this shows significant contrast to earlier values as reported in [58] and [17]. A combined approach was taken in [11] where the device noise model included both velocity saturation and hot electron effects, and results also show moderate enhancement of channel thermal noise and induced gate noise.

In general, noise modeling of short channel devices shows several inconsistencies which could be attributed to many factors, but it is mainly due to the inconsistencies that arise from numerous and somewhat contrasting mobility and channel conductivity models, which include the effects of high electric fields on charge carriers in the conducting channel of a FET device. The notion of hot electrons and electron temperature has been a source of confusion as well. In an effort to shed more light on this matter, in the following section we will describe three different techniques that are widely used in noise modeling in semiconductor devices in general, and MOSFETs in particular. We will briefly discuss the major differences between all three.

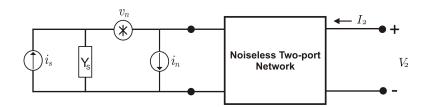

# 2.2.6 Noise Modeling Methodologies

The study and characterization of noise from a circuit designer's point of view mainly involves the description of certain devices such as a transistor by means of classical two-port noise theory. Here devices and circuits are characterized by equivalent noise sources such as voltages and currents. Using the classical two-port noise theory and the equivalent noise sources, a designer can then analyze a device or circuit and predict the noise performance between the input and output ports of the network. The treatment of this topic will be handled later in this chapter. In this section we provide a brief treatment of noise at the microscopic level where its characteristics are related to device-intrinsic parameters. Studying and modeling a device's noise behavior at such a scale is essential for designing efficient low-noise high frequency circuits.

Noise analysis techniques can be divided into two categories: a) an equivalent circuit approach and b) a physics based approach. An equivalent circuit based approach simply models the device's noise behavior by using lumped two port elements such as resistors, capacitors, and inductors which connect the input and output ports of the device [30]. Of course, in the case of an active device, nonlinear and bias dependent elements need to be added to the model in order to accurately describe the small signal characteristics between input and output. A physics based approach to noise modeling is deeply involved in describing the device behavior at the microscopic level. Using such an approach produces either microscopic variables like electron transport, carrier velocity, charge distributions, or external variables such as voltages and currents [29]. The latter is more relevant and more beneficial since it facilitates the extraction of compact noise modeling parameters used circuit simulators. Physical modeling relies on the evaluation of Boltzmann's equation describing charge distribution in a non-equilibrium state in conjunction with Poisson's equation relating charge to the electric field [29]. Details of the evaluation of Boltzmann's equation is beyond the scope of this thesis and can can found in several references, including [29]. Several methods have been developed for compact noise modeling in solid state devices, and for MOSFETs we can identify the following [14]

1. Klaassen-Prins method

- 2. Equivalent circuit method, and

- 3. Impedance field method

The following is a brief discussion of each method.

#### 2.2.6.1 Klaassen-Prins Model

The Klaassen-Prins approach is utilized by many to describe noise in semiconductor devices, including Van der Ziel [31]. The procedure of obtaining the general Klaassen-Prins equation for drain thermal noise current for long channel FETs will be briefly described here based on derivation steps developed in [31] and [13].

The current in a semiconductor device can be described using the the nonquasi-static one-dimensional as follows

$$I = g \frac{dV}{dx} \tag{2.22}$$

where g is the conductivity and V(x) is the voltage or potential at a certain point x along the channel. The reader is referred to [3, App. J] for the details on the derivation of (2.22). Equation (2.22) can be used to model the drain current in an n-channel MOSFET. In the presence of thermal agitation, charges will undergo random motion as they travel across the channel; this is seen at the terminals of the device as minor fluctuations around the drain DC current level. We can model the drain current with a DC component  $I_D$  and a small signal component  $i_d$  representing fluctuations due to thermal noise. The noise current source in a FET channel must also be modeled, which is usually done by using a Langevin equation with current source  $i_n(x)$ , having a zero ensemble average [13]. The Langevin equation is a stochastic differential equation describing Brownian motion of particles [72]. It is essential to remember that random motion of charges will perturb the channel potential, this is expressed by a small signal noise voltage term,  $v_n(x)$ , added to the DC channel potential V(x) and the channel conductance term (g) in (2.21), since it is a function of the channel potential. Adding the small signal component  $v_n(x)$  and the Langevin noise component to (2.22) results in

$$I_D + i_d = g(V(x) + v_n(x)) \frac{d(V(x) + v_n(x))}{dx} + i_n(x)$$

(2.23)

Since we are interested in the noise component of the drain current, only small signal components of equation (2.23) are kept, and the resulting expression for  $i_d$  is integrated over the length of the channel, i.e. L. Using the boundary conditions: v(0) = v(L) = 0, we obtain

$$i_d = \frac{1}{L} \int_0^L i_n(x) dx$$

(2.24)

By definition, the spectral density of a random process with zero time or ensemble average is given by  $S_{id} \equiv \frac{\overline{i_d i_d^*}}{\Delta f}$ . Using this definition for  $S_{id}$  and (2.24) the drain noise current spectral density is

$$S_{id} = \frac{1}{L^2} \int_0^L \int_0^L \overline{i_n(x)i_n^*(x')} dx dx'$$

(2.25)

At this point an assumption can be made regarding the nature of the noise source  $i_n(x)$ . The classical Klaassen-Prins equation was derived using a thermal noise source where the noise density of a section  $\Delta x$  of the FET's channel; it is given by [31]

$$S_n = \frac{4kTg(x)}{\Delta x} \tag{2.26}$$

As  $\Delta x \to 0$  in (2.26) we can approximate the discontinuity by a Dirac delta function in the form

$$S_n = 4kTg(x)\delta(x - x') \tag{2.27}$$

Consequently

$$\overline{i_n(x)i_n^*(x')} = 4kTg(x)\Delta f\delta(x-x')$$

(2.28)

where  $\delta$  is the Dirac delta function, not to be confused with the bias dependent parameter of gate noise current in (2.19). Substituting (2.28) into (2.25) and using (2.22) to switch the variable to V instead of x results in the classical Klaassen-Prins equation [12]

$$S_{id} = \frac{4kT}{I_D L^2} \int_{V_0}^{V_L} g^2(V) dV$$

(2.29)

If (2.22) is solved for the current term, I, or  $I_D$  in the case of drain current of a FET, the general expression for DC drain current is obtained

$$I_D = \frac{1}{L} \int_{V_0}^{V_d} g(V) dV$$

(2.30)

Substituting (2.30) into (2.29) and introducing the term  $g_0$ , defined as the conductance per unit length at the source, the drain current spectral density becomes [60]

$$S_{id} = \frac{4kTg_0}{L} \frac{\int_{V_0}^{V_D} (\frac{g(V)}{g_0})^2 dV}{\int_{V_0}^{Vd} (\frac{g(V)}{g_0}) dV} = \gamma 4kTg_{d0}$$

(2.31)

where  $g_{d0}$  has already been introduced in (2.18) and is defined as [31]

$$g_{d0} = \frac{g_0}{L} \tag{2.32}$$

From the previous derivation we can see how the Klaassen-Prins equation was simplified by Van der Ziel in order to obtain an analytical, closed form equation for drain noise current formulated in (2.20) and (2.18).

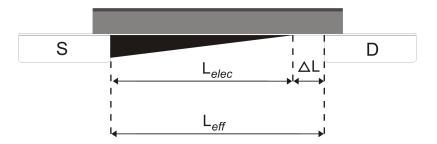

The Klaassen-Prins equation is a simple, but powerful, equation which is used widely in compact MOSFET noise modeling today. The original form of (2.29) has undergone several modifications in an effort to extend its use to submicron devices, for which channel length modulation and the dependence of charge mobility and channel conductivity on the electric field must be included for accurate modeling. Inclusion of channel length modulation effect (CLM) is adopted in [61] using the channel segmentation model, which divides the conducting channel into two parts: the gradual channel region and the pinch-off region, as shown in Figure 2.6 where  $L_{eff}$  is the effective length of the channel,  $L_{elec}$  is the electric length of the channel (which is also the length of the gradual channel region), and  $\Delta L$  is the length of the pinch-off region.

Figure 2.6: NMOS cross sectional view.

It has been shown that the noise contribution from the pinch-off region of the channel is negligible [61]. This assumption is widely accepted and used in [12], [16], and [14]. Building on this, velocity saturation of charge carriers in the presence of strong electric fields is incorporated into the formulation of channel conductivity by [13]. This results in a new DC current differential equation similar to (2.22) in the form

$$I_D = \frac{g_0(V)}{\left[1 + \left(\frac{\mu_0}{v_{sat}}\frac{d\psi}{dx}\right)^p\right]^{-\frac{1}{p}}}\frac{dV}{dx}$$

(2.33)

where  $g_0(V)$  is the conductivity neglecting velocity saturation,  $\mu_0$  is the zerofield mobility, p is a power value of 2 for NMOS devices,  $v_{sat}$  is the saturation velocity, and  $\psi$  is the electrostatic potential at the surface (consequently  $\frac{d\psi}{dx}$  denotes the electric field). In [13] proper steps are taken from this point in order to obtain the modified Klassen-Prins equation where the final result for drain noise current spectral density is given by

$$S_{I_D} = \frac{4kT}{I_D L_{vsat}^2} \int_{V_0}^{V_L} g_c^2 dV$$

(2.34)

where  $g_c$  denotes the corrected channel conductivity taking into account velocity saturation, and  $L_{vsat}$  is the length corresponding to corrections on the position x due to velocity saturation as well. Finding an expression for the induced gate noise follows the same steps which were taken in [29] in order to obtain (2.19). The key step in this process is to model the MOSFET as a distributed RC network in which the distributed resistance models the conducting channel and the distributed capacitance models the gate oxide coupling to the gate. A general expression used to calculate gate noise current is given by [13]

$$i_G = -j\omega W \int_0^L C_{gc}(x)v(x)dx \qquad (2.35)$$

where v(x) is the distributed voltage across the channel,  $C_{gc}$  is the local gate to channel capacitance, and W is the channel width. The final expression for gate noise current and the correlation coefficient defined in (2.21) can be found in [13].

The result obtained in (2.34) is a generalization to the classical Klaassen-

Prins equation in (2.29), in which the channel conductivity was corrected to include dependencies on voltage as well as position along the channel, and finally velocity saturation and CLM effects were included. In the next section the impedance field method will be briefly introduced and discussed.

#### 2.2.6.2 Impedance Field Method

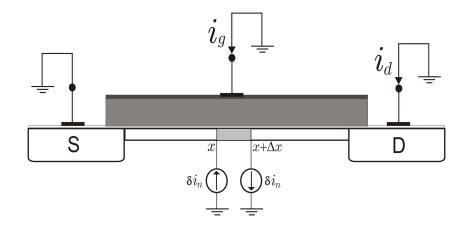

The impedance field method is similar to the Klaassen-Prins approach where the MOSFET is also regarded as a distributed RC network and Langevin stochastic sources are used in order to model the local noise sources in small channel segments. The Langevin noise sources,  $\delta i_n$ , are slightly modified and are modeled as one component injecting current in a noiseless channel segment between x and  $x + \Delta x$ , and another component drawing current from the noiseless channel segment as shown in Figure 2.7. Currents  $i_g$  and  $i_d$  denote the short circuit gate and drain currents resulting from the local microscopic noise source  $\delta i_n$  [62].

The noise transfer from the microscopic level,  $\delta i_n$ , to the device terminals,  $i_{d(g)}$ , is calculated using the vector impedance field term denoted as  $\Delta A_{d(g)} \equiv [A_{d(g)}(x) - A_{d(g)}(x + \Delta x)] = dA_{d(g)}(x)/dx$  and the resulting terminal noise current for gate or channel can be found by [14]

$$i_{d(g)}(t) = \int_0^L \frac{dA_{d(g)}(x)}{dx} \delta i_n(x, t) dx$$

(2.36)

This shows that the terminal noise current is found by simply adding the

Figure 2.7: Illustration of impedance field method applied to an N-channel device.

noise contributions of all the small segments as shown in Figure 2.7. The general equation in (2.36) requires some modifications in order to account for velocity saturation and CLM effects. Similar to the generalized Klaassen-Prins method described in the previous section, the noise from the pinch-off region of the channel is assumed to be negligible. Therefore, (2.36) is integrated over the electric length of the channel,  $L_{elec}$ . The microscopic noise source used in this case is given by the diffusion noise [31]

$$\delta i_n^2 = 4q^2 D_n n(x) \frac{W}{\Delta x} \Delta f \tag{2.37}$$

where q is the charge carrier, n(x) is the electron concentration , and  $D_n$ is the electron diffusion coefficient given by the Einstein relation in thermal equilibrium as

$$D_n = \frac{kT}{q}\mu_n \tag{2.38}$$

where  $\mu_n$  is the electron mobility. Einstein's relation holds only in situations where thermal equilibrium exists. If this is the case, then inserting (2.38) into (2.37) simply produces the thermal noise current equation for a resistor. This implies that thermal noise in semiconductors is a special case of diffusion noise in which thermal equilibrium conditions are assumed. Following the derivation steps outlined in [11], the differential DC drain current equation is used, including mobility degradation effect as

$$I_D = g_0(V) \frac{\frac{dV}{dx}}{1 + \frac{\frac{dV}{dx}}{E_c}}$$

(2.39)

where  $E_c$  is the critical electric field at which carrier velocity saturates,  $g_0(V) = \mu_{eff}WC_{ox}(V_{od} - \alpha V)$ ,  $\alpha$  accounts for bulk charge effects,  $V_{od}$  is the gate overdrive voltage,  $C_{ox}$  is the gate oxide capacitance per unit area, and  $\mu_{eff}$  is the effective mobility of charge carriers. Using (2.39) the impedance field is formulated with the aid of circuit analysis on the small channel segment between x and  $\Delta x$  as shown in Figure 2.7. Using the formulated impedance field, the noise contribution of all the segments are summed to find the total drain noise current as described mathematically in (2.36), with the assumption that the noise contributions of all the small segments are uncorrelated. A key assumption made in [11] is that the diffusion coefficient  $D_n$  is constant along the gradual channel, the justification being that the decrease of carrier mobility due to high electric fields is compensated by the increase in electron temperature. The diffusivity equation is only modified to incorporate mobility degradation effects where the term  $\mu_n$  is replaced by  $\mu_{eff}$ . The final equation for drain noise current spectral density is found as [11]

$$S_{id} = \frac{4kT}{I_D L_{elec}^2 (1 + \frac{V_{DS}}{L_{elec} E_c})^2} \int_0^{V_{DS}} g_0^2(V) (1 + \frac{E}{E_c}) dV$$

(2.40)

which shows similarities to the classical and modified Klaasen-Prins equations in (2.29) and (2.34), respectively. The procedure of finding the induced gate noise current follows directly from (2.35).

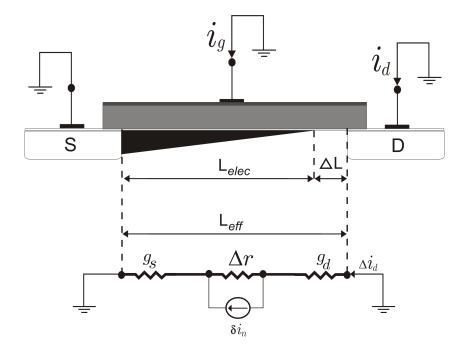

#### 2.2.6.3 Equivalent Circuit Method

A circuit based approach models the distributed channel using lumped components: a differential resistance  $\Delta r$ , and two channel conductances  $g_s$  and  $g_d$  looking toward the source and drain terminals as shown in Figure 2.8.

Figure 2.8: Equivalent circuit approach.

Based on this type of model, the terminal response to the fundamental noise source  $\delta i_n$  in spectral density form is [15]

$$S_{\Delta i_d^2} = S_{\delta i_n^2} \Delta r^2 g_{eq}^2 \tag{2.41}$$

where

$$\frac{1}{g_{eq}} \equiv \frac{1}{g_s} + \frac{1}{g_d} \tag{2.42}$$

Obtaining  $S_{\Delta i_d^2}$  requires the calculation of all three terms in (2.41). The procedure is found in [14]. What is most significant is the formulation of the  $S_{\delta i_n^2}$  term. The channel segment between x and  $x + \Delta x$  is not assumed to be

in equilibrium due to the presence of the electric field. Therefore, Einstein's relation cannot be used. Similar to the impedance field method adopted by [11] in the previous section, Einstein's relation is modified so that it can be used for non-equilibrium conditions as follows

$$D_n = \frac{kT_n}{q} \mu_{diff} \tag{2.43}$$

where  $\mu_{diff}$  denotes the differential mobility which is defined as  $\mu_{diff} = \frac{dv}{dE}$ , v is the electron velocity, and  $T_n$  is the noise temperature which is eventually shown to be equal to the carrier temperature,  $T_c$ , in situations specific to MOSFET device operations. Also, the carrier temperature is different from the lattice temperature,  $T_L$ . Since it is more convenient to use lattice temperature, an approximate closed form relation between carrier and lattice temperature is used, which is consistent with the field dependent carrier mobility. Under these assumptions the power spectral density of the microscopic noise source is found as [15]

$$S_{\delta i_n^2} = 4kT_L \Delta g(\frac{\mu_0}{\mu_{eff}})^2 \tag{2.44}$$

With the assumption that the microscopic noise sources are uncorrelated, the total drain noise current power spectral density, denoted as  $S_{I_d^2}$  in [15], is found by integrating over the effective channel length. The gate induced noise current is found using the same approach as employed by the other two noise modeling methods. It is important to realize that the carrier heating effect is taken into account. This is in contrast to [11] where increase in carrier temperature was considered to be balanced by the decrease in carrier mobility. Carrier heating effects were not considered in the formulation of the generalized Klaassen-Prins equation by [13]. The definition of diffusivity and its relation to the carrier mobility in the channel is similar in all three methods presented, the difference occurs in the modeling of mobility and conductance and their dependence on the electric field. This in turn translates into differences in the fundamental or microscopic noise models.

The three methods calculate drain noise current by applying different techniques to model the distributed MOSFET channel. In principle, the Klaassen-Prins derivation utilizes the Langevin method in which a macroscopic differential equation describing the transfer characteristics of the system is used and a random source function is added to describe the random fluctuations of the noise sources [31]. Boundary conditions are then used to obtain drain and gate noise currents. The impedance field method breaks down the distributed channel into small noiseless segments with two microscopic noise current sources drawing from and injecting current into the channel segment. A channel segment between  $x_1$  and  $x_1 + \Delta x$  is unaffected by the presence of a noise source in an adjacent channel segment between  $x_2$ and  $x_2 + \Delta x$ . This assumption allows the use of superposition in order to find the total drain noise current.

The equivalent circuit approach lumps the entire channel into one resistance, including a microscopic noise source, and a drain and source conductance. The noise transfer to the device terminals is found using linear circuit techniques [15]. These noise modeling methods described seem to have a great degree of similarity. Indeed, a generalization of all three methods was performed in [14] where it was shown that all three methods eventually produce the same integral equations for drain noise current and induced gate noise current. The generality of these forms proves to be very useful since they were derived assuming an arbitrary mobility and microscopic noise source models.

As mentioned previously, these noise modeling methodologies have been developed for use in compact transistor modeling for use in circuit simulators. Several MOSFET models have been developed and are used as an industry standard, such as the Berkeley Short-Channel IGFET Model (BSIM), developed by the BSIM Research Group at UC Berkeley. The BSIM3 has been widely adopted and used by many corporations since its release in 1995. The third version of the BSIM3, namely the BSIM3v3 model, is the model that will be used throughout all circuit simulations that will be presented in this work.

Later extension of the BSIM3v3 model, such as the BSIM3v3.2.4, model the drain thermal noise current as follows [65]

$$S_{id} = \frac{4kT\mu_{eff}}{L_{eff}^2 + \mu_{eff}|Q_{inv}|R_{ds}}|Q_{inv}|$$

(2.45)

where  $Q_{inv}$  is the inversion layer charge and  $R_{ds}$  is the drain to source resis-

tance. In [16], a similar expression for the drain noise current was found by simplifying the drain noise current expression in (2.40) as

$$S_{id} = 4kT \frac{\mu_{eff}}{L_{elec}^2} Q_{inv} \tag{2.46}$$

which is similar to (2.45). It was shown in [11] that (2.46), albeit originally developed for long channel devices, is still valid in the submicron regime. The BSIM3v3 model incorporates the effects of the drain to source resistance,  $R_{ds}$ , whereas (2.46) uses the electric length of the channel instead of the effective length. The effective mobility,  $\mu_{eff}$ , in (2.45) and (2.46) does not take into account the degradation due to the lateral electric field [11]. Nevertheless, the simple expression in (2.46) was shown in [11] to be practically accurate even in short channel devices, with deviations from (2.40) of less than 5% for channel lengths down to 0.18  $\mu$ m.

Induced gate noise is not modeled in the BSIM3v3.2.4 model. Many publications, such as [39], have addressed this issue by introducing lumped component extensions, namely a gate resistance which is used to model the induced gate thermal noise and the non-quasi-static effects of the distributed channel. Induced gate noise tends to dominate the overall measured noise at high frequencies [62]. Flicker noise dominates the observed noise at low frequencies, whereas observed noise at mid-range frequencies is dominated by the channel thermal noise. The mid-range to high frequency break-point is usually assumed to be around one tenth of  $f_t$  [17], [62]. With a 0.13  $\mu$ m CMOS process, which will be assumed throughout this work,  $f_t$  exceeds 100 GHz. Assuming a long-channel device operating in the saturation region,  $f_t$  is approximated as [7]

$$f_t \approx \frac{3}{2} \frac{\mu_n (V_{gs} - V_t)}{L^2}$$

(2.47)

From (2.47) we can see that  $f_t \propto \frac{1}{L^2}$ , indicating that technology scaling has the effect of increasing  $f_t$ . The highest frequency targeted in this work will be below 3 GHz. Hence, it is fair to assume that the lack of an induced gate noise formulation in the BSIM3v3.2.4 model will not have a significant effect on the accuracy of noise figure simulations.