#### Worcester Polytechnic Institute Digital WPI

Major Qualifying Projects (All Years)

Major Qualifying Projects

May 2014

Alexander Joseph Ryan Worcester Polytechnic Institute

Harrison Chabot Williams Worcester Polytechnic Institute

Rayce Colemen Stipanovich *Worcester Polytechnic Institute*

Follow this and additional works at: https://digitalcommons.wpi.edu/mqp-all

#### **Repository Citation**

Ryan, A. J., Williams, H. C., & Stipanovich, R. C. (2014). *Intelligent LED Display*. Retrieved from https://digitalcommons.wpi.edu/mqp-all/2213

This Unrestricted is brought to you for free and open access by the Major Qualifying Projects at Digital WPI. It has been accepted for inclusion in Major Qualifying Projects (All Years) by an authorized administrator of Digital WPI. For more information, please contact digitalwpi@wpi.edu.

# **Intelligent LED Display**

A Major Qualifying Project

Submitted to the Faculty of Worcester Polytechnic Institute

In partial fulfillment of the requirements for the

Degree in Bachelor of Science

In

Electrical and Computer Engineering

By

Harrison Williams

Rayce Stipanovich

Alex Ryan

Date 04/12/2012: Sponsoring Organization: Worcester Polytechnic Institute: Project Advisors:

Professor William R. Michalson, Advisor

This report represents work of WPI undergraduate students submitted to the faculty as evidence of a degree requirement. WPI routinely publishes these reports on its web site without editorial or peer review. For more information about the projects program at WPI, see http://www.wpi.edu/Academics/Projects.

#### Abstract

The goal of this project is to increase the overall redundancy, and ease-of-use during installation and operation, of large-format LED video displays for the professional touring and outdoor display industry. Using design concepts found in large-scale redundant networks, the system dynamically scales video output to the LED display and provides adaptive real-time fault detection and failover behaviors to ensure reliability in rigorous outdoor environments. This ultimately simplifies installation of a system, eliminating the need for the individual addressing of panels and alignment of video content. The designed system is inherently redundant and the ability to sustain failure of its components increases with the size of the display making it ideal for live applications. The developed display also possesses a dynamic run-time scaling ability of the video output, removing any need for image alignment and manual configuration.

### Acknowledgements

The team would like to acknowledge and express our gratitude towards several individuals for their contribution to the project – it is likely we would not have succeeded as much as we did without their help.

We would like to thank our advisor, Professor William Michalson, for his keen engineering insight that helped us avoid pitfalls.

We would also like to thank Paulo Carvalho (BME/RBE '15) for his assistance with the project as an extra member – his manufacturing, hardware design and documentation skills were extremely helpful.

We would lastly like to thank Joe Germain for his assistance in creating the LED panel cases with his 3D printer.

## **Executive Summary**

With the arrival of multicolored Light Emitting Diodes (LEDs), large format displays used for both informational and entertainment purposes have become a reality. Arrayed LED matrix panels exist in many shapes and sizes. Often times installed in static locations, these large format displays that consist of several smaller panels (32x32 or 40x40 LEDs) are commonly used as dynamic billboards, and can be found in sporting venues to show the score and live video of the game as well as in the entertainment industry for backlighting of the stage or to create dynamic performance elements on stage. Typically these displays are bulky and need to be installed in a certain order for them to work and interface with the software that processes the video that will be displayed on the screen. These drawbacks leads to a time consuming and costly installation executed by specially trained personnel.

The goal was to develop a unit that could be easily installed without advanced training through the use of self-addressing technology, be robust by use of fault detection and redundant data paths whilst still minimize the cost per panel. Note that common manufacturers' units run in the price range of \$1,700 to \$5,200 depending on the distance between LEDs as well as the number and quality of the colors that can be reproduced. The proposed system would addresses many of the shortcomings of today's mainstream panels that still suffer from lacks in redundancy, reliable life tracking, and the restrictions of addressing.

The large scale of the project required it to be divided into four main sections: The panel chassis and rigging hardware; the architecture type which determines the powering scheme of the LEDs; the firmware of the individual panels; and, the main video processing software. The independent nature of the tasks would allow for work to proceed in all simultaneously. A networking protocol both for communication between panels and to the controller was decided early in the developed and would allow for the different sections of the project to work together once completed.

Two unique sets of hardware were developed and differed in the LED powering scheme. The first used multiplexing of LED drivers to illuminate each row briefly before scanning on to the next one whilst the second used a direct driven method, where each of the LEDs in the matrix were given their own driver. Even though the later allowed for

4

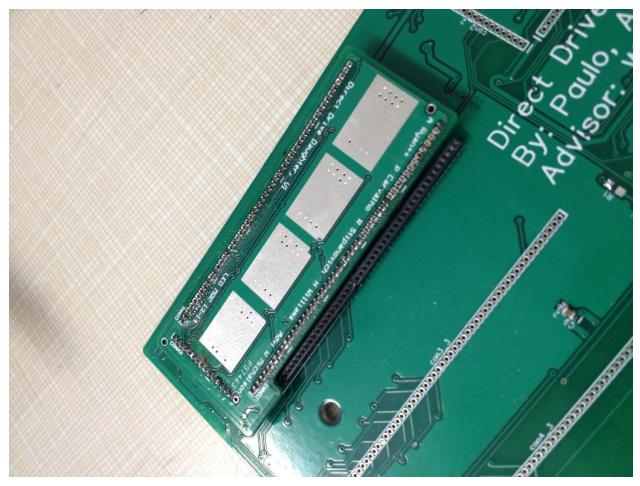

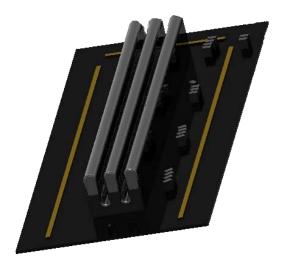

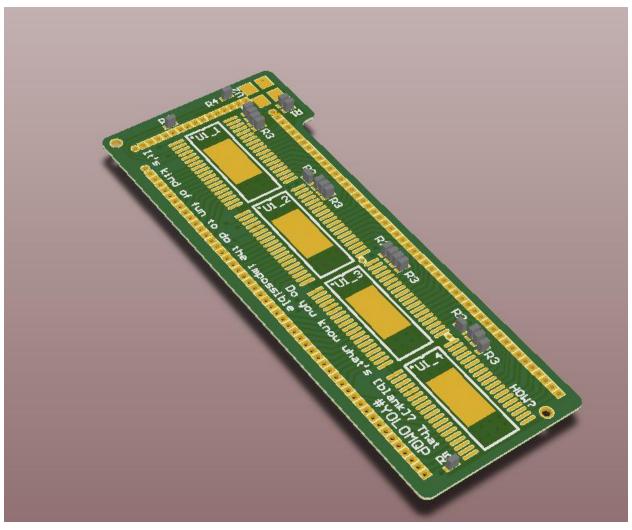

an increase in the panel lumen output, provided better color fidelity and eliminated issues that would be traditionally encountered when trying to film the panel with a camera that has a rolling shutter function the direct drive has low power efficiency and requires a larger physical space to achieve these benefits. The direct-drive powering topology can be observed in figure 0.1.

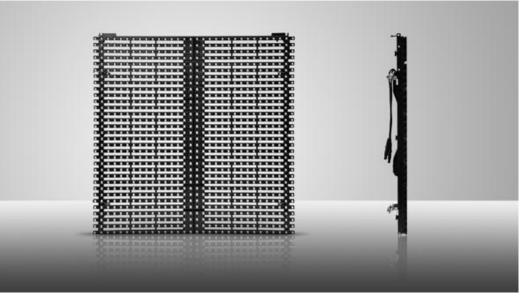

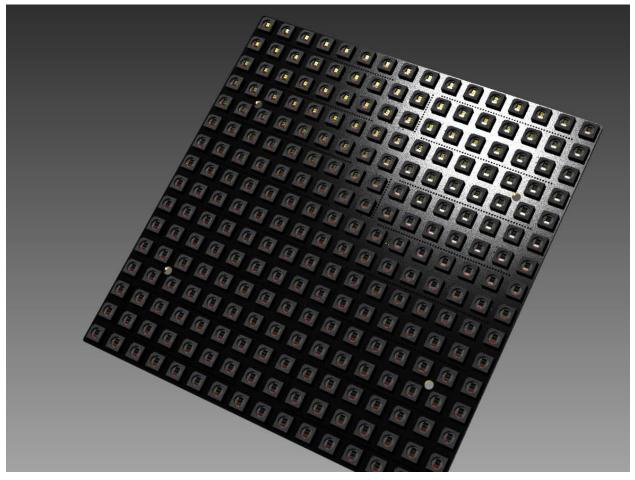

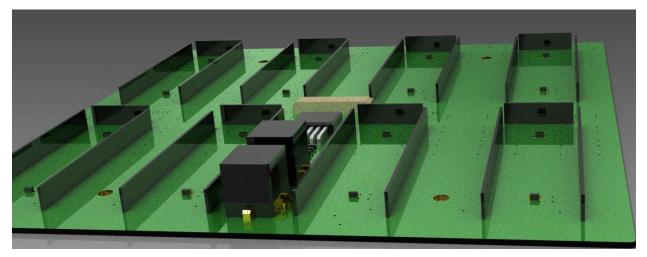

Figure 0 - 1: A 3D rendering of a panel design, showing eight LED driver boards connected to the LED matrix PCB below.

Regardless of the LED driving scheme a firmware capable of managing both the communication between the panels and the controller was required. The panels needed to not only receive and forward video at a high speed but also to report back fault conditions to the host. To implement this, the traditional IEEE Ethernet protocol was employed with a few layers removed in order to decrease overhead. Ethernet allowed for the routing of video packets in conditions where there are panel faults in the network and onto the proper destination. The IEEE Ethernet stack would provide the project with a well-documented and widely used standard as a foundation for further development.

The fourth constituent of the project was the video host and management server. This machine centralizes the control and management of all panels to a single easily operated interface. It constantly send data to all operational panels while monitoring their status. In case a failure is detected the software takes care of performing the necessary changes in the video output in order to maintain the system running.

Aligned with the goal of creating an easy to use and robust system through the use of self-addressing and fault detection techniques, the team divided the project into four main areas. Each of the project areas, which included panel configuration, architecture, firmware and higher level code, were tackled simultaneously to ensure completion of the project within the stipulated deadline. The final result was a product that provides innovative solutions to common industry problems at a low cost and that is under way to become market ready through more extensive testing and hardware iterations.

# Table of Contents

| Abstract                                                | 2  |

|---------------------------------------------------------|----|

| Acknowledgements                                        | 3  |

| Executive Summary                                       | 4  |

| Table of Contents                                       | 7  |

| List of Figures                                         | 12 |

| List of Tables                                          | 15 |

| List of Equations                                       | 15 |

| Chapter 1: Introduction                                 | 16 |

| 1.1 Motivation                                          | 16 |

| 1.2 Current State of the Art                            | 19 |

| 1.3 Proposed Contributions                              | 21 |

| 1.4 Report Organization                                 | 22 |

| Chapter 2: Network-Distributed Video Systems            | 24 |

| 2.1 Professional Video Standards and Protocol Selection | 24 |

| 2.2 Distributed Redundant Networks                      | 27 |

| 2.3 Large-Format Display Topologies                     | 31 |

| 2.4 Video Processing Systems                            | 34 |

| 2.5 Summary                                             | 35 |

| Chapter 3: Proposed Design and Project Logistics        | 36 |

| 3.1 Main Project Goals                                  | 36 |

| 3.2 Project Objectives and Specifications               | 37 |

| 3.2.1. Video Output:                                    | 38 |

| 3.2.2. Networking:                                      | 38 |

| 3.2.3. Ruggedized:                                      | 39 |

| 3.2.4. Power:                                           | 39 |

| 3.3 Project Management and Tasks                             | 40 |

|--------------------------------------------------------------|----|

| 3.4 Design Decisions and Research                            | 42 |

| 3.5 Design Summary                                           | 47 |

| Chapter 4: Implementation                                    | 48 |

| 4.1 System Hardware Configuration                            | 48 |

| 4.1.1 Host Video Processing Rack                             | 48 |

| 4.1.2 Development Network Topology                           | 49 |

| 4.1.3 Video Input Hardware                                   | 52 |

| 4.2 Display Controller and Shield Implementation             | 53 |

| 4.2.1 Display Controller Implementation                      | 53 |

| 4.2.2 Display Controller Shield Implementation               | 54 |

| 4.3 Multiplexing Panel Architecture                          | 54 |

| 4.3.1 Multiplexing Panel Design Overview                     | 54 |

| 4.3.2 Multiplexing Panel Functional Block Diagram            | 55 |

| 4.3.3 Multiplexing Panel Theory of Operation                 | 56 |

| 4.3.4 Multiplexing Panel Component Selection and Description | 59 |

| 4.3.5 Multiplexing Panel Power Consumption                   | 64 |

| 4.4 Direct Drive Panel Architecture                          | 66 |

| 4.4.1 Direct-Drive Panel Overview                            | 66 |

| 4.4.2 Direct-Drive Panel Functional Block Diagram            | 67 |

| 4.4.3 Direct-Drive Panel Theory of Operation                 | 68 |

| 4.4.4 Direct-Drive Panel Component Selection and Description | 69 |

| 4.4.5 Direct-Drive Panel Thermal Design Problem and Solution | 72 |

| 4.5 LED Panel Embedded Software Design                       | 75 |

| 4.5.1 Embedded Software Overview                             | 75 |

| 4.5.2 Embedded Software Operating System Development         | 76 |

| 4.5.3 Embedded Software Operation Description                | 77 |

| 4.5.4 Embedded Software Task and ISR Details                 | 78 |

| 4.6 Video Processing Software Design                              | 81  |

|-------------------------------------------------------------------|-----|

| 4.6.1 Overview                                                    | 81  |

| 4.6.2 Pixel Sampling Theory                                       | 82  |

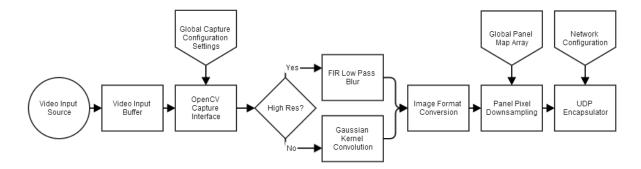

| 4.6.3 Video Processing Overview                                   | 83  |

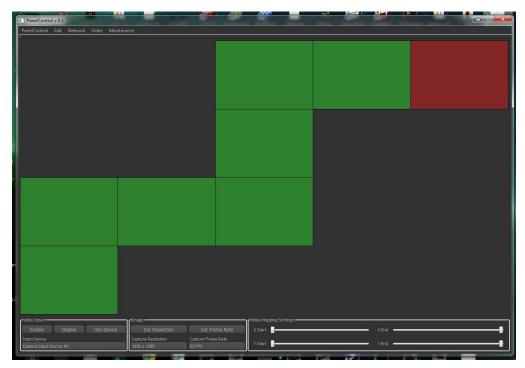

| 4.6.4 User Interface Design                                       | 84  |

| 4.6.5 Self-Addressing Protocol Implementation                     | 86  |

| 4.7 Implementation Summary                                        | 93  |

| 4.7.1 Physical Design Verification and Manufacturability Analysis | 93  |

| 4.7.2 Chassis Design and Manufacturing                            | 95  |

| Chapter 5: Results                                                | 102 |

| 5.1 Still Image Calibration                                       | 102 |

| 5.2 Video Frame rate                                              | 103 |

| 5.3 Self-Addressing Stability                                     | 104 |

| Chapter 6: Conclusions and Future Work                            | 105 |

| 6.1 Project Outcomes                                              | 105 |

| 6.2 Future Design Suggestions                                     | 106 |

| References                                                        | 108 |

| Appendix A: Video Processing Top-Level UML                        | 109 |

| Appendix B: Shield Board Reference Manual Content                 | 110 |

| B-1 Pin Mapping                                                   | 110 |

| B-1.1 InterBoard FPC Connector                                    | 110 |

| B-1.2 InterPanel RJ45 Connectors                                  | 111 |

| Type 1: Connectors 1/2                                            | 111 |

| Type 2: Connectors 3/4                                            | 111 |

| B-1.3 Shield Board to Ethernet Shield Connector: CON2             | 112 |

| B-2 Schematics, Copper and Diagrams                               | 114 |

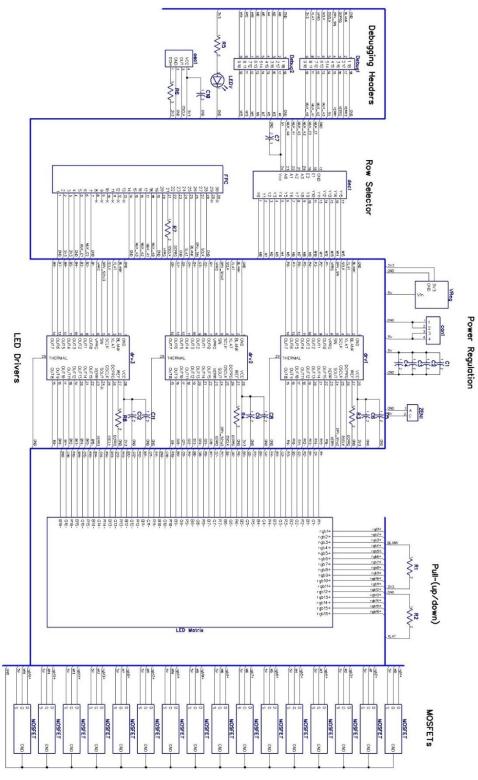

| B-2.1 High Level Block Diagram                                    | 114 |

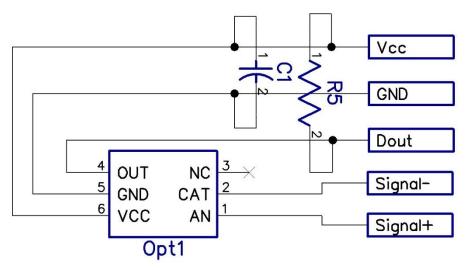

| B-2.2 Optocoupler Schematic                                       | 115 |

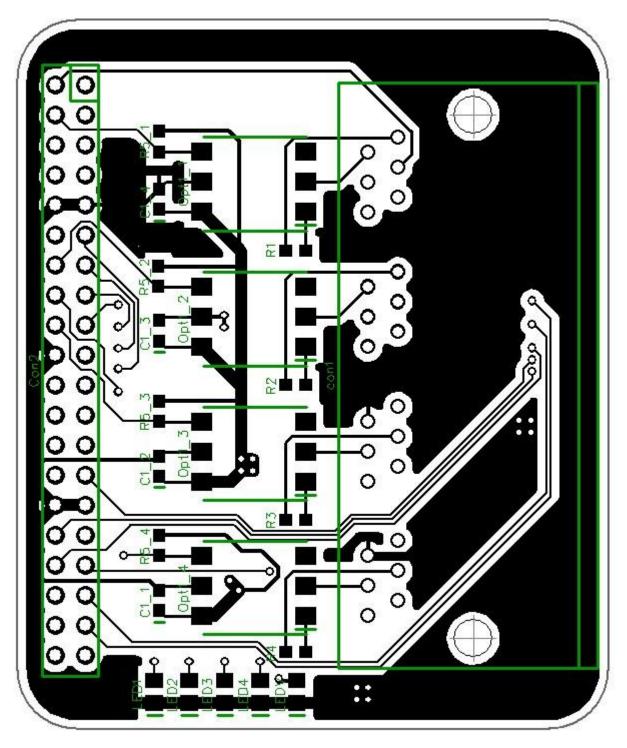

| B-2.3 Copper Top Layer                              | 116 |

|-----------------------------------------------------|-----|

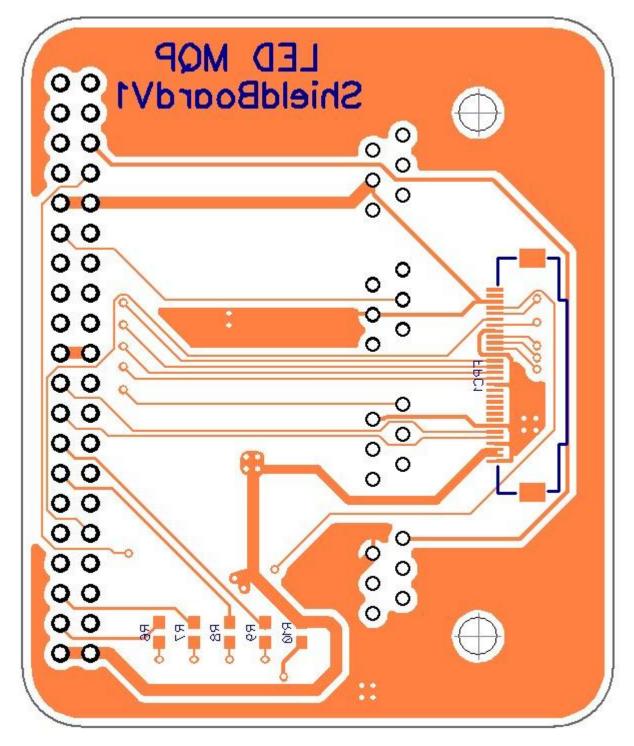

| B-2.4 Copper Bottom Layer                           | 117 |

| B-3 Component List                                  | 118 |

| B-4 Errata                                          | 119 |

| Appendix C: Multiplexing LED Panel Reference Manual | 120 |

| C-1 Component/Connector Pin Out and Description     | 120 |

| C-1-1 LED Drivers: TLC5940                          | 120 |

| C-1-2 Decoder: CD74HC154M                           | 120 |

| C-1-3 FPC Connector                                 | 121 |

| C-1-4 Debug1 Connector                              | 122 |

| C-1-5 Debug2 Connector                              | 122 |

| C-2 Schematic and Description                       | 123 |

| C-2-1 High Level Diagram                            | 123 |

| C-2-2 Voltage Regulator                             | 124 |

| C-2-3 LED Matrix                                    | 125 |

| C-3 Copper Artwork                                  | 126 |

| C-3-1 Top Layer                                     | 126 |

| C-3-2 Inner 1                                       | 127 |

| C-3-3 Inner 2                                       | 128 |

| C-3-4 Bottom Layer                                  | 129 |

| C-4 Component List                                  | 130 |

| Appendix D: Direct-Drive LED Panel Reference Manual | 131 |

| D-1 Component/Connector Pin-Out and Description     | 131 |

| D-1-1 FPC Connector                                 | 131 |

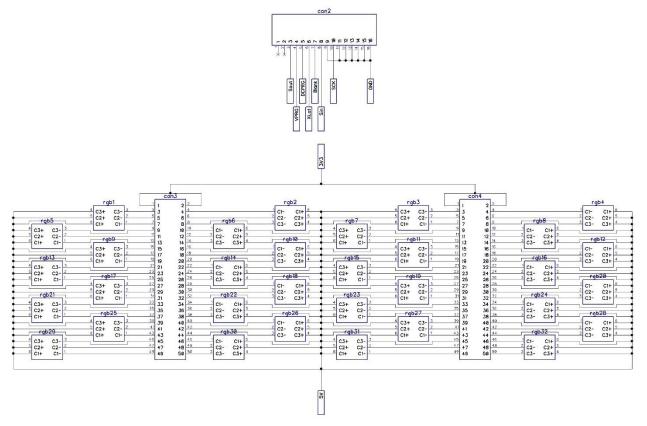

| D-1-2 Daughter Board Connectors CON2_n              | 131 |

| D-2 Schematics and Description                      | 132 |

| D-2-1 High Level Diagram                            | 132 |

| D-2-2 Voltage Regulator                             | 133 |

| D-2-3 Capacitor Block                                      | 134 |

|------------------------------------------------------------|-----|

| D-2-4 LED Block                                            | 135 |

| D-3 Copper Artwork                                         | 136 |

| D-3-1 Top Layer                                            | 136 |

| D-3-2 Bottom Layer                                         | 137 |

| D-4 Component List                                         | 138 |

| Appendix E: Direct Drive Daughterboard Reference Documents | 139 |

| E-2 PCB Layer Prints                                       | 142 |

| E-3 Daughterboard Render                                   | 148 |

| E-4 Component List                                         | 149 |

# List of Figures

| FIGURE 0 - 1: A 3D RENDERING OF A PANEL DESIGN, SHOWING EIGHT LED DRIVER BOARDS CONNECTED TO   | THE   |

|------------------------------------------------------------------------------------------------|-------|

| LED MATRIX PCB BELOW.                                                                          | 5     |

| FIGURE 1 - 1: PIXLED LINX-18F OUTDOOR PANEL FROM [2]                                           | 16    |

| FIGURE 1 - 2: AN EXAMPLE OF ARRAYED LED MATRIX PANELS, WHICH EXIST IN MANY FORMS AND CATER T   | 0     |

| MANY MARKETS. FROM [4]                                                                         | 18    |

| FIGURE 1 - 3: DIGILED NAVIGATOR PANEL HOST INTERFACE [5]                                       | 19    |

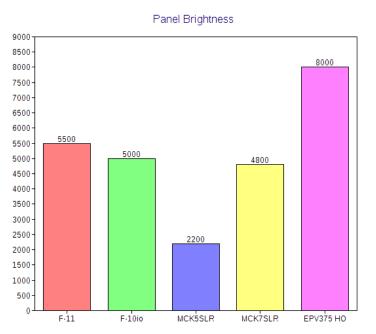

| FIGURE 1 - 4: CURRENT MARKET PANEL BRIGHTNESS'S. FROM [6]                                      | 20    |

| FIGURE 2 - 1: HD-SDI AND SDI PROTOCOLS UTILIZE BNC CONNECTORS. FROM [7]                        | 24    |

| FIGURE 2 - 2: AN HDMI TYPE A CONNECTOR. FROM [8]                                               | 25    |

| FIGURE 2 - 3: A TABLE REPRESENTATION OF THE OSI MODEL. FROM [9]                                | 27    |

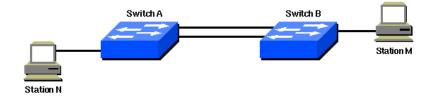

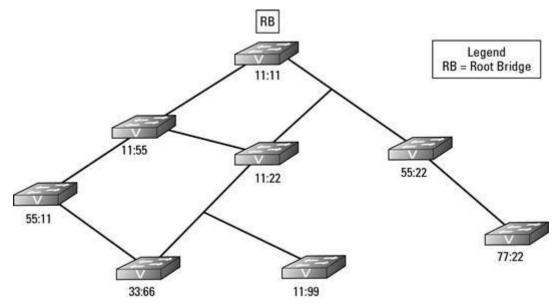

| FIGURE 2 - 4: A PHYSICAL CONNECTION BEFORE RSTP. FROM [10]                                     | 28    |

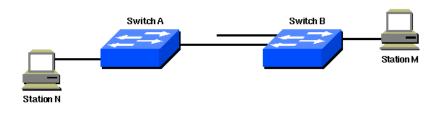

| FIGURE 2 - 5: A VIRTUALLY-REMOVED CONNECTION AFTER RSTP. FROM [10]                             | 29    |

| FIGURE 2 - 6: IN A STP-ENABLED NETWORK, SWITCHES ARE ASSIGNED VARIOUS WEIGHTS, AND PATHS ARE   |       |

| ASSIGNED VARIOUS WEIGHTS AS WELL. PATHS WITH THE LONGEST WEIGHTS ARE DISABLED UNTIL LO         | OWER- |

| WEIGHT PATHS BECOME UNUSABLE DUE TO NETWORK TOPOLOGY CHANGES OR OTHER PATH FAILUF              | ₹E.   |

| FROM [10]                                                                                      | 29    |

| FIGURE 2 - 7: THE ABC TIMES SQUARE STUDIO IN NYC, NEW YORK. FROM [12]                          | 31    |

| FIGURE 2 - 8: THE YAS MARINA HOTEL IN ABU DHABI ILLUMINATED IN A SHADE OF PURPLE. FROM [14]    | 32    |

| FIGURE 2 - 9: A RECTANGULAR SET OF PANELS MOUNTED ON A WALL. FROM [15]                         | 33    |

| FIGURE 2 - 10: ELATION IMAGE VSC 2.0 IMAGE PROCESSOR USED TO CONDITION VIDEO TO BE FED TO A PA | NEL   |

| CONTROLLER. FROM [16]                                                                          | 34    |

| FIGURE 3 - 1: PROPOSED HIGH-LEVEL SYSTEM BLOCK DIAGRAM.                                        | 37    |

| FIGURE 3 - 2: PROPOSED GENERAL TIMELINE AND PROJECT SCHEDULE.                                  | 41    |

| FIGURE 3 - 3: ACTUAL DEVELOPMENT SCHEDULE AND TIMELINE.                                        | 41    |

| FIGURE 3 - 4: NETWORK PATH REPRESENTATION IN A TYPICAL CONFIGURATION.                          | 44    |

| FIGURE 4 - 1: THE 24 PORT MANAGED SWITCH USED IN THE RACK. FROM [19]                           | 48    |

| FIGURE 4 - 2: AN IMAGE OF THE PROCESSING RACK.                                                 | 49    |

| FIGURE 4 - 3: BLACKMAGIC SDI INPUT CARD. FROM [20]                                             | 52    |

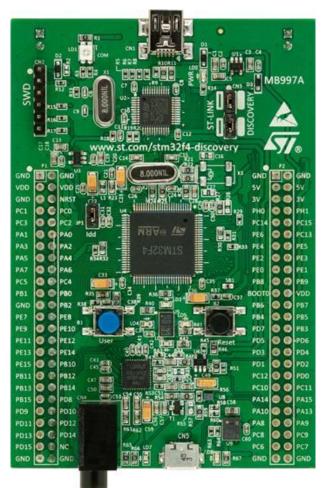

| FIGURE 4 - 4: STMF4 DISCOVERY DEVELOPMENT BOARD. FROM [21]                                     | 53    |

| FIGURE 4 - 5: A 3D CONCEPT OF THE OUTPUT MATRIX FACE OF THE MULTIPLEXING AND DIRECT DRIVE PCBS | S. IT |

| SHOULD BE NOTED THAT THE MOUNTING HOLES POSITION ON THE MULTIPLEXING DESIGN DIFFERS            |       |

| SLIGHTLY FROM THAT OF THE DIRECT-DRIVE DESIGN DISCUSSED IN LATER SECTIONS.                     | 55    |

| FIGURE 4 - 6: FUNCTIONAL BLOCK DIAGRAM OF A PROPOSED 32X32 LED MULTIPLEXING PANEL.             | 56    |

| FIGURE 4 - 7: LED BRIGHTNESS CURVE. FROM [21]                                                  | 58    |

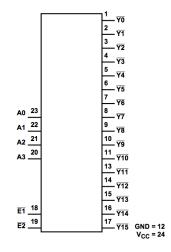

| FIGURE 4 - 8: PIN CONNECTIONS FOR THE DECODER USED. FROM [23]                                        | 62   |

|------------------------------------------------------------------------------------------------------|------|

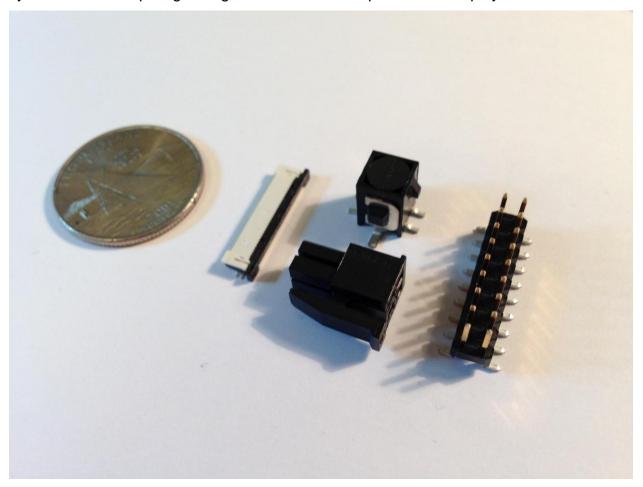

| FIGURE 4 - 10: REFERENCE SCALE FOR SMT CONNECTORS SELECTED FOR THE FINAL DESIGN.                     | 63   |

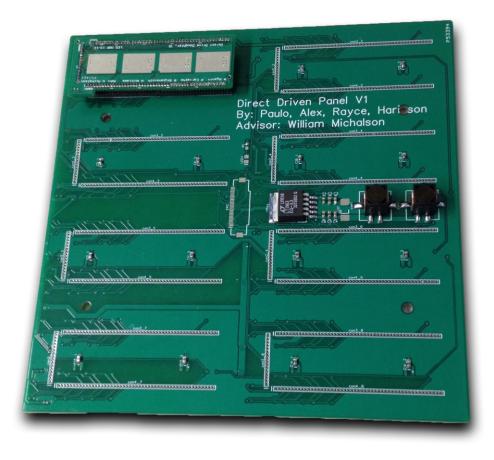

| FIGURE 4 - 11: FINAL IMPLEMENTATION OF THE DIRECT-DRIVE BOARD DESIGN.                                | 67   |

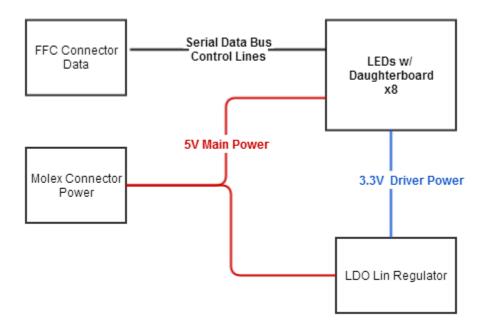

| FIGURE 4 - 12: DIRECT-DRIVE LED PANEL FUNCTIONAL BLOCK DIAGRAM                                       | 68   |

| FIGURE 4 - 13: DIRECT-DRIVE DAUGHTER BOARD FUNCTIONAL BLOCK DIAGRAM                                  | 68   |

| FIGURE 4 - 14: TIMING DIAGRAM OF COUNTER, BLANKING AND SERIAL OPERATION FROM [22].                   | 69   |

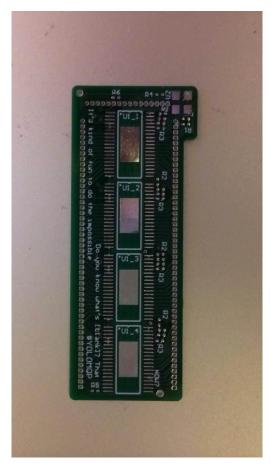

| FIGURE 4 - 15: PICTURE OF A FINISHED DAUGHTER BOARD. NOTE THE SIZE OF THE LED DRIVERS AND HEADERS.   | 72   |

| FIGURE 4 - 16: PROPOSED BOTTOM COPPER LAYOUT AND PLACEMENT FOR REJECTED DIRECT-DRIVE LED PANEL       | - 73 |

| FIGURE 4 - 17: IMAGE OF THE EXPOSED COPPER PADS ON THE OPPOSITE SIDE OF THE LED DRIVER IC'S TO BE US | SED  |

| FOR HEAT SINK ATTACHMENT.                                                                            | 75   |

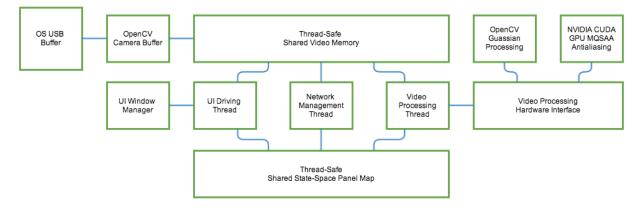

| FIGURE 4 - 18: PC SOFTWARE FUNCTIONAL DIAGRAM                                                        | 81   |

| FIGURE 4 - 19: FLOW DIAGRAM FOR A SINGLE VIDEO FRAME.                                                | 83   |

| FIGURE 4 - 20: HEALTHY ARRAY REPRESENTATION OVER VIDEO UI.                                           | 85   |

| FIGURE 4 - 21: UI INDICATING THAT A FAULT IS OCCURRING AT A SPECIFIC PANEL.                          | 85   |

| FIGURE 4 - 22: A DISPLAY OF A PANEL THAT IS DISCONNECTED FROM THE NETWORK                            | 91   |

| FIGURE 4 - 23: EXAMPLE OF THE PC SOFTWARE REMOVING A PANEL FROM A NETWORK IF NO RESPONSE IS          |      |

| RECEIVED                                                                                             | 92   |

| FIGURE 4 - 24: INTERMEDIATE STEP OF BOARD EXTRUSION FOR DESIGN VERIFICATION.                         | 93   |

| FIGURE 4 - 25: ORIGINAL LED DIRECT-DRIVE DAUGHTER BOARD DESIGN                                       | 94   |

| FIGURE 4 - 26: MODIFIED FINAL LED DIRECT-DRIVE DAUGHTER-BOARD DESIGN                                 | 94   |

| FIGURE 4 - 27: DIRECT-DRIVE LED PANEL DESIGN SHOWN IN 3D FOR VERIFICATION PURPOSES                   | 95   |

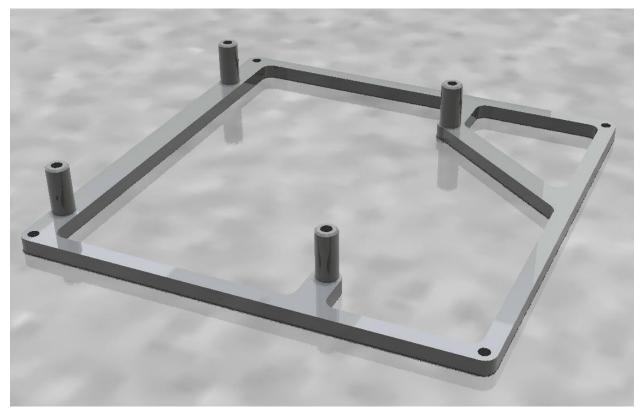

| FIGURE 4 - 28: 3D RENDERING OF STANDOFF DEVELOPMENT FRAME                                            | 96   |

| FIGURE 4 - 29: STANDOFF POSITIONING                                                                  | 97   |

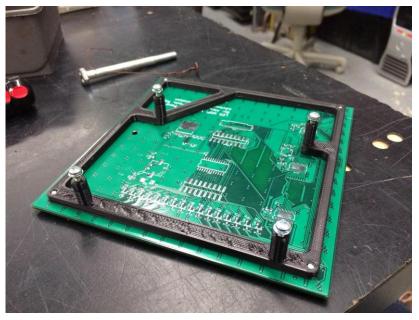

| FIGURE 4 - 30: DEVELOPMENT CHASSIS IMPLEMENTATION                                                    | 97   |

| FIGURE 4 - 31: 3D RENDERING OF FINAL PANEL CHASSIS.                                                  | 98   |

| FIGURE 4 - 32: CHASSIS POPULATED WITH LOGIC ELECTRONICS AND DEVELOPMENT BOARD.                       | 99   |

| FIGURE 4 - 33: CHASSIS WITH MULTIPLEXING PANEL INSTALLED AND SEALED ON FRONT FACE.                   | 99   |

| FIGURE 4 - 34: NEUTRIK DATA CONNECTORS CHOSEN TO IMPROVE RUGGEDNESS.                                 | 100  |

| FIGURE 4 - 35: LOCKING POWER CONNECTORS CHOSEN TO FULFIL INDUSTRY CONVENTIONS.                       | 101  |

| FIGURE 4 - 36: REAR CONNECTOR HOUSING AND RIGGING POINTS.                                            | 101  |

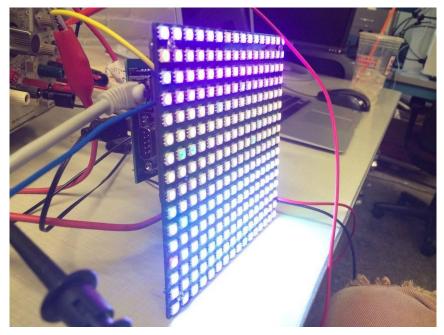

| FIGURE 5 - 1: TESTING COLOR VARIATIONS OF THE INDIVIDUAL LEDS OF A MULTIPLEXING PANEL.               | 102  |

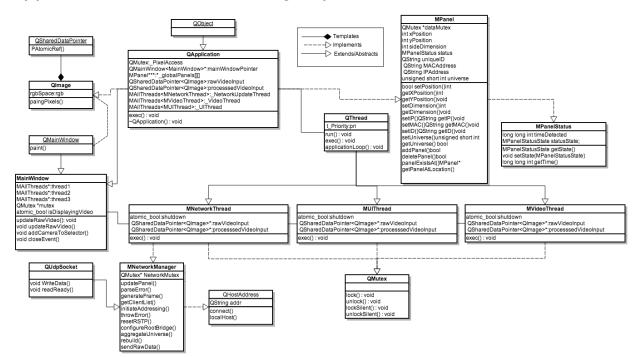

| FIGURE A - 1: VIDEO PROCESSING TOP-LEVEL UML DIAGRAM                                                 | 109  |

| FIGURE B - 1: SHIELD BOARD HIGH LEVEL DIAGRAM                                                        | 114  |

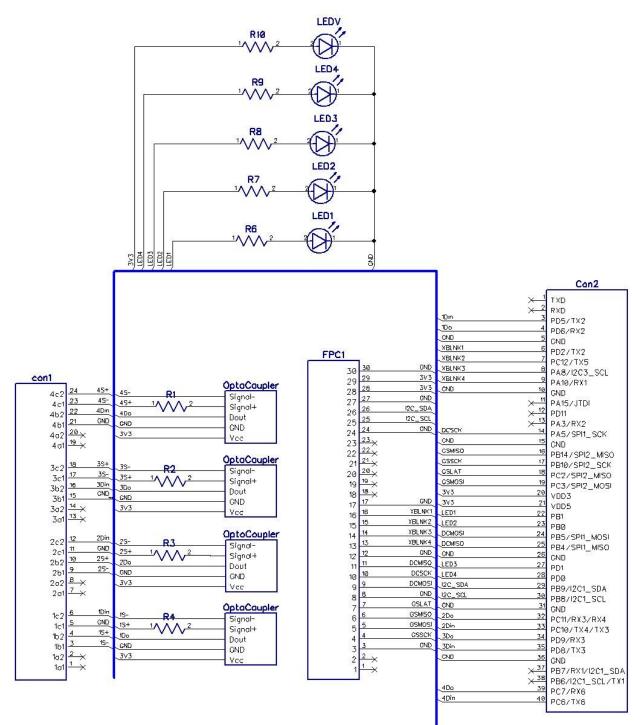

| FIGURE B - 2: OPTOCOUPLER SCHEMATIC                                                                  | 115  |

| FIGURE B - 3: TOP VIEW OF COPPER ARTWORK WITH SILKSCREEN.                                            | 116  |

|                                                                                                      |      |

| FIGURE B - 4: BOTTOM VIEW OF COPPER ARTWORK WITH SILKSCREEN.              | 117 |

|---------------------------------------------------------------------------|-----|

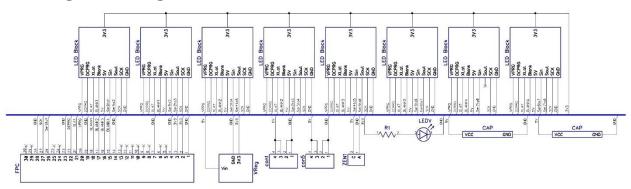

| FIGURE C - 1: MULTIPLEXING LED PANEL HIGH-LEVEL SCHEMATIC                 | 123 |

| FIGURE C - 2: MULTIPLEXING LED PANEL VOLTAGE REGULATOR SCHEMATIC          | 124 |

| FIGURE C - 3: MULTIPLEXING LED PANEL LED MATRIX SCHEMATIC                 | 125 |

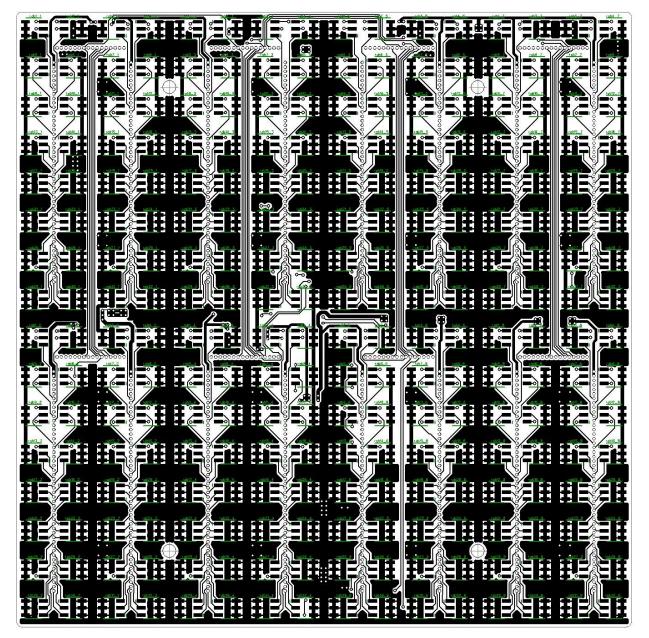

| FIGURE C - 4: MULTIPLEXING LED PANEL TOP-LAYER COPPER AND SILKSCREEN      | 126 |

| FIGURE C - 5: INNER LAYER 1 COPPER                                        | 127 |

| FIGURE C - 6: INNER LAYER 2 COPPER                                        | 128 |

| FIGURE C - 7: BOTTOM LAYER COPPER AND SILKSSCREEN                         | 129 |

| FIGURE D - 1: DIRECT-DRIVE LED PANEL HIGH-LEVEL SCHEMATIC                 | 132 |

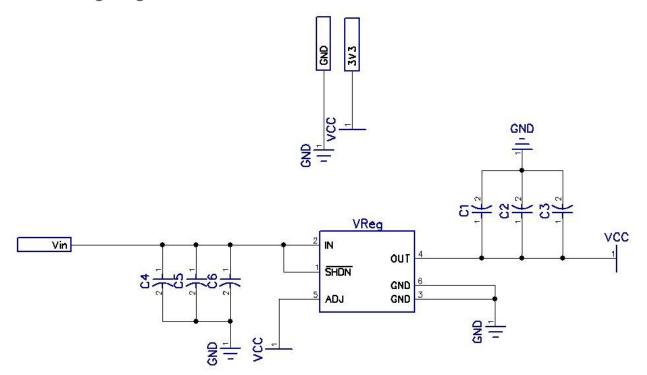

| FIGURE D - 2: DIRECT-DRIVE LED PANEL VOLTAGE REGULATOR SCHEMATIC          | 133 |

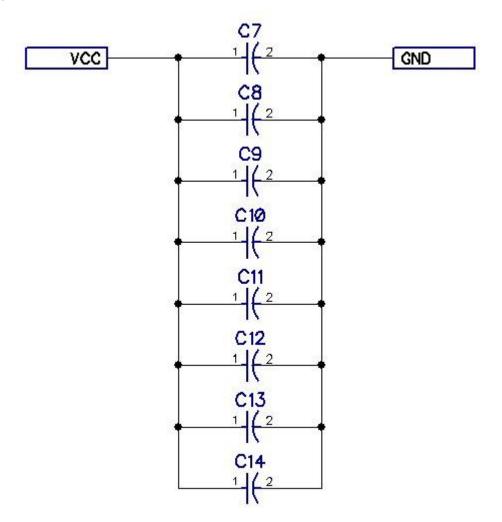

| FIGURE D - 3: DIRECT-DRIVE LED PANEL DECOUPLING CAPACITOR ARRAY SCHEMATIC | 134 |

| FIGURE D - 4: DIRECT-DRIVE LED PANEL LED BLOCK SCHEMATIC                  | 135 |

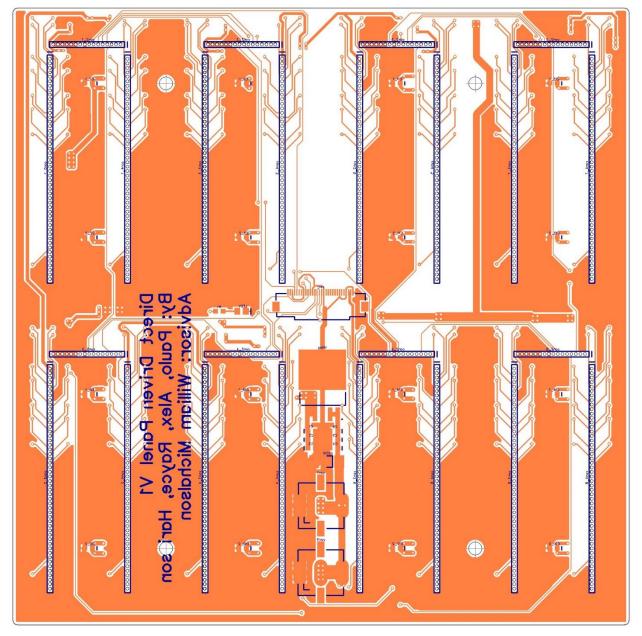

| FIGURE D - 5: DIRECT-DRIVE LED PANEL TOP LAYER COPPER AND SILKSCREEN      | 136 |

| FIGURE D - 6: DIRECT-DRIVE LED PANEL BOTTOM LAYER COPPER AND SILKSCREEN   | 137 |

| FIGURE E - 1: DIRECT DRIVE DAUGHTERBOARD DRIVER CONNECTION SCHEMATIC      | 139 |

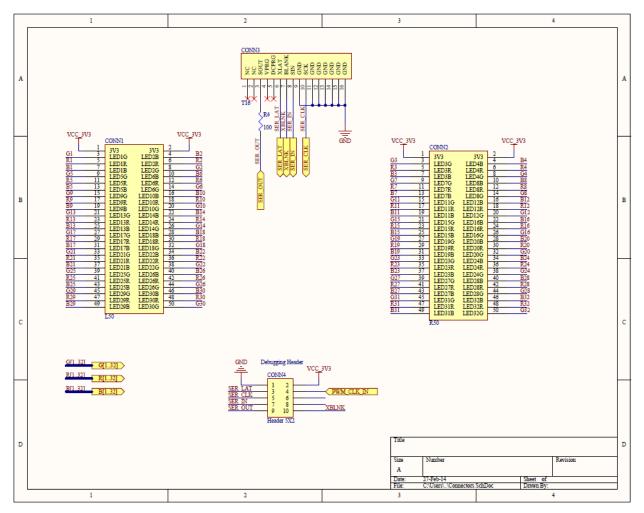

| FIGURE E - 2: DIRECT DRIVE DAUGHTERBOARD PIN CONNECTIONS SCHEMATIC        | 140 |

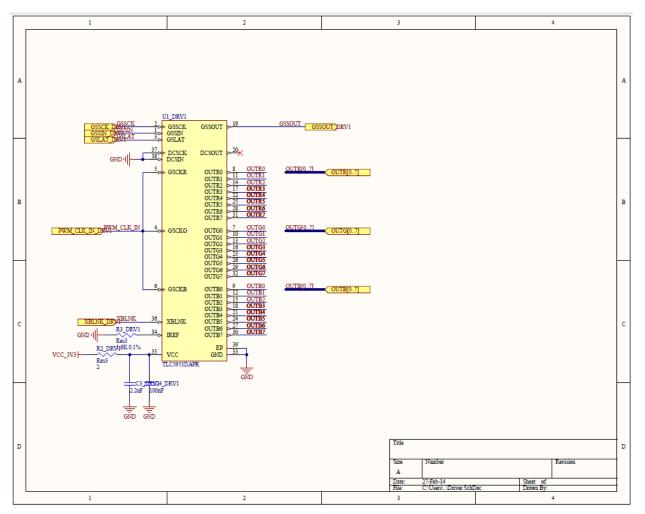

| FIGURE E - 3: DIRECT DRIVE DAUGHTERBOARD MAIN OVERVIEW SCHEMATIC          | 141 |

| FIGURE E - 4: DIRECT DRIVE DAUGHTERBOARD TOP COPPER                       | 142 |

| FIGURE E - 5: DIRECT DRIVE DAUGHTERBOARD BOTTOM COPPER                    | 143 |

| FIGURE E - 6: DIRECT DRIVE DAUGHTERBOARD TOP SILKSCREEN                   | 144 |

| FIGURE E - 7: DIRECT DRIVE DAUGHTERBOARD BOTTOM SILKSCREEN                | 145 |

| FIGURE E - 8: DIRECT DRIVE DAUGHTERBOARD TOP SOLDERMASK                   | 146 |

| FIGURE E - 9: DIRECT DRIVE DAUGHTERBOARD BOTTOM SOLDERMASK                | 147 |

| FIGURE E - 10: DAUGHTERBOARD ALTIUM 3D RENDER                             | 148 |

# List of Tables

| TABLE 2 - 1: A TABLE SHOWING DIFFERENT DIGITAL VIDEO STANDARDS AND SOME OF THEIR SPECIFICATIONS. | . 26 |

|--------------------------------------------------------------------------------------------------|------|

| TABLE 4 - 1: AVERAGE RSTP CONVERGENCE TIMES                                                      | 50   |

| TABLE 4 - 2: MULTIPLEXING PANEL POWER CONSUMPTION BY COMPONENT                                   | 65   |

| TABLE 4 - 3: UDP PROTOCOL SPECIFICATION TABLE                                                    | 87   |

| TABLE 4 - 4: VIDEO FRAME PAYLOAD ENUMERATIONS                                                    | 88   |

| TABLE 4 - 5: STATUS UPDATE PAYLOAD ENUMERATIONS                                                  | 88   |

| TABLE 4 - 6: CONTROL MESSAGE PAYLOAD ENUMERATIONS                                                | 89   |

| TABLE B - 1: SHIELD FFC CONNECTOR PIN-OUT                                                        | 110  |

| TABLE B - 2: RJ11 UART CONNECTOR PIN-OUT, CONNECTORS 1-2                                         | 111  |

| TABLE B - 3: RJ11 UART CONNECTOR PIN-OUT, CONNECTORS 3-4                                         | 111  |

| TABLE B - 4: STM32F4-BASEBOARD TO SHIELD PIN-OUT                                                 | 112  |

| TABLE B - 5: COMPONENT BOM FOR THE SHIELD BOARD                                                  | 118  |

| TABLE B - 6: SHIELD MANUAL ERRATA LIST                                                           | 119  |

| TABLE C - 1: MULTIPLEXING LED DRIVER PIN-OUT                                                     | 120  |

| TABLE C - 2: MULTIPLEXING DECODER PIN-OUT                                                        | 121  |

| TABLE C - 3: FFC CONNECTOR PIN-OUT                                                               | 121  |

| TABLE C - 4: DEBUG HEADER #1 PIN-OUT                                                             | 122  |

| TABLE C - 5: DEBUGGING HEADER #2 PIN-OUT                                                         | 122  |

| TABLE C - 6: MULTIPLEXING LED PANEL BOM                                                          | 130  |

| TABLE D - 1: DIRECT-DRIVE LED PANEL FFC CONNECTOR PIN-OUT                                        | 131  |

| TABLE D - 2: CON2_N HEADERS PIN-OUT                                                              | 132  |

| TABLE D - 3: DIRECT-DRIVE LED PANEL BOM                                                          | 138  |

| TABLE E - 1: COMPONENT LIST OF DIRECT DRIVE DAUGHTERBOARD                                        | 149  |

# List of Equations

| (3-1) | 45 |

|-------|----|

| (3-2) | 46 |

| (4-1) | 57 |

| (4-2) | 57 |

| (4-3) | 82 |

|       |    |

## Chapter 1: Introduction

#### 1.1 Motivation

Large format video displays are used in a variety of different applications. With the advent of power-efficient Light Emitting Diode (LED) technologies, displays that are normally comprised of projection-based video systems are often replaced by lower-maintenance, more efficient LED display systems. Large format LED video displays commonly referred to as "video walls" [1] are now considered to be a staple in the professional touring music industry as well as in the advertising industry. These video walls are comprised of individual panels that are electrically and mechanically connected to form a larger display. As video resolutions increase to those that are above Full-HD 1080p video, the size and complexity of video walls increases, often adding multiple points of failure to a system and increasing setup time. Larger video resolutions generally result in a requirement to add more panels to an array, as increasing the pixel density of an array is often too expensive to consider as a viable option. In addition to the inherent complexity of large systems, in many situations within the professional touring music industry, a setup crew may only have a few hours to unpack, assemble, hang, and test a video wall.

Figure 1 - 1: PixLED Linx-18F Outdoor Panel From [2]

LED video displays have also penetrated the advertising markets and are seen on the sides of buildings, billboards, or other installations. These offer great flexibility to advertisers, but often incur substantial maintenance costs. These arrays are often found outside and are exposed to harsh weather conditions [2]. Because of this, these systems require routine maintenance and the occasional repair. This can be difficult or dangerous depending on the location and installation type. The industry has pushing to develop robust panels as to decrease the rate of failure, but there are currently no solutions on the market to offer a significant amount of failure redundancy. Many systems only offer one-way communication from the controller handling the video processing and the individual panels. If there is a fault in the system, it usually be discovered by an individual observing the array and noticing a flaw in the video output. This likely has many desirability's for advertisers using video walls in remote locations, as faulty displays could potentially go unrepaired for significant amounts of time. As some systems rely on standard communications protocols such as TCP/IP to operate [3], two-way communication can be implemented to provide various forms of fault detection.

In the context of a live musical performance, if a system fails, it will be noticed by thousands of people. Discretely making repairs on such systems becomes very difficult, as the work environments are often poorly-lit, confined spaces. The ability to quickly diagnose, repair, and replace panels in an array becomes critical, both from the perspective of visual aesthetics as well as safety. The industry has pushed to develop weatherproof solutions for the LED output panels themselves, but the control interfaces and network infrastructure are often less fault-tolerant and are more-likely to fail. In many systems, a loss in a single connection can affect a large portion of an array or even the entire array itself. In systems with large numbers of connections, repairing and maintaining such a system requires elaborate methods of personal transport to replace broken panels. The ideal solution is to prevent large-scale faults that require such repairs in the first place.

The goal of this project is to build upon common technologies used in current video display systems by implementing inter-panel and panel-to-host communication, allowing for fault detection and other reliability improvements. These technologies will also be used to improve setup times by eliminating the need to address individual panels and align video content. This report will examine the design approach and methods used to achieve a redundant and "intelligent" large format video display array. Notable applications for LED panels include large format outdoor displays for touring video production, roadside advertisements, architectural displays, and large format reference displays for cinematography. In most cases, the panels consist of ruggedized and sealed PCB's and enclosures that are designed to interlock in such a way as to allow for tessellation. In some cases, panels such as the DigiLED FLEX dFX10, shown in figure 1.2, are designed to be flexible, enabling construction of curved surfaces.

Figure 1 - 2: An example of arrayed LED matrix panels, which exist in many forms and cater to many markets. From [4]

#### 1.2 Current State of the Art

There are several main focuses of research within the current industry. These are primarily power efficiency and video output quality. Many panel manufactures pursue methods to remain power efficient, ultimately enabling larger displays to be implemented for the same power budget. This has some inherent drawbacks. Having more panels within an array requires many more electrical connections. This, in itself, introduces multiple points of failure. Most panel manufacturers are currently exploring faster methods of data transfer [3] such as using the physical layer of the TCP stack, but few panels use the full IEEE Internet Protocol for communication.

Currently, panel manufacturers such as PixLED and DigiLED are pursuing methods of reducing the bandwidth required to send video content over Cat5 cables to a video panel. This allows for faster data transfer, but also introduces an issue of more points of failure. Panels such as the DigiLED MCK series use differential signaling to transmit data, but do not rely on the IP stack to transmit full-duplex data. These panels only offer methods of daisy-chaining panels in a row. While this ultimately simplifies the complexity and reduces the amount of cables required to transmit data, it introduces multiple points of failure. Often times, a failure in a panel early in the signal chain results in a cascading failure to a large section of the array. This is undesirable, as not only is the fault not localized, but it affects neighboring panels as well, causing large visible faults to the viewing audience.

Figure 1 - 3: DigiLED Navigator Panel Host Interface [5]

When combined with DigiLED panels, the DigiLED Navigator [5], shown in Figure 1.3, allows for real-time scaling and switching of video content. This is then sent to the array through Cat5e cables through a broadcast network. Each panel then reads only its part of the entire array's video frame based on its pre-determined address. In addition to this, the Navigator has the ability to send control signals to the panels to perform actions such as running diagnostics or the ability to remotely power-down the panels. These features add a significant amount of convenience to the product, but as these communications are only one-way, information cannot be received from the panels. Because of this, the typical solution for detecting faults is to have a physical observer or camera monitoring the panels form the audience's perspective. This ultimately is inefficient, as it is still prone to human error and requires an individual to detect an error or fault.

Figure 1 - 4: Current market panel brightness's. From [6]

The high-end panels currently on the market generally have a brightness output of around 5,000 lumens. This is a suitable brightness for most outdoor applications, and is even viewable in direct sunlight. Panel resolution and brightness are the two largest areas researched by panel manufacturers [6], and as shown by the Figure [x]. Because of this, little research has been conducted into redundancy, which is where this projects aims to focus on.

#### **1.3 Proposed Contributions**

This project aims to create an array of LED panels that are capable of displaying real-time video content. These panels will possess the ability to self-address in order to dynamically map their output to video content. This will be achieved by developing an algorithm that uses both the IEEE Ethernet stack and a proprietary inter-panel communication protocol. The panels will also feature redundant mesh networking through the implementation of IEEE 802.1w to prevent failures due to damaged cables or other interruptions to the signal path from the video server to the panels. The panels will use these systems to communicate with a central video processing host and will possess the ability to notify an operator of the existence of and location of faults in a panel array.

This project overcomes the current shortcomings in the current state-of-the-art by the following approaches:

- 1. Remove the need for the individual addressing of panels in an array, allowing the array to self-address upon startup.

- 2. Automatically and dynamically scale video content to match the dimensions of the video wall.

- 3. Alert maintenance staff of a failure and provide the location of the fault.

- 4. Offer inherent network redundancy through multi-point RSTP-supported mesh networks.

- 5. Offer higher-quality video output for rolling-shutter cameras through directly driving each LED individually as opposed to cycling through rows.

- 6. Offer an intelligible user interface that is straightforward.

- 7. Perform video processing on consumer-grade computers instead of expensive proprietary system processors.

This project will prove the benefits and viability of implementing redundant systems to improve the quality of large format video displays over those currently on the market. This design will be realized through a combination of common development boards, peripheral resources, and custom designed electrical and mechanical hardware. In addition to this, custom video processing and array control software will be written to handle the majority of the self-addressing and failover behavior logic.

#### 1.4 Report Organization

This report is comprised of 6 chapters. They are: Chapter 1: Introduction, this chapter introduces the project, its design goals and methods, and explores our motivation to work on this project. This chapter also takes a look into the preexisting products and other implementations in the market today. This leads into Chapter 2: Network-Distributed Video Systems where it discusses how video can be transported across networks and how the data interacts with the network topology as a whole. It also looks into how to design a network specific to this project and how to select a video encoding method that is optimal for the given network configuration. In order to get video from the main server, or the host, a network had to be designed such that the video data could be transported quickly, without loss and with fault redundancy. The first step is to analyze different methods of video encoding and determine which would be most common and easy to use given that it would be implemented on a network of our choosing. Once the video encoding format had been chosen, a network format needed to be selected so as to optimize the transport of video, and be able to address the concerns stated previously. Use of the IEEE network protocol 802.1w was selected due to its ability to provide a decent solution to a majority of these issues. This lays the foundation that the other portions of the project could be designed to, and gives hard targets for code and hardware to perform at.

After that was done, Chapter 3: Proposed Design and Project Logistics takes a look in detail at the project goals and objectives with an emphasis on design criteria and decisions made while the project progressed in order to meet the standards. It also looks at which decisions had to be made so that the rest of the project could be designed. It will also explore the project management and tasks necessary for the project to be a success. Also this chapter will provide a design summary for the project as a whole.

As the report moves into Chapter 4: Implementation, it discusses in detail how each portion of the project was created and made to work with one another. Both the multiplexing and direct drive architectures are described along with the details necessary for how both styles interface with the panel embedded operating system. Details as to the software running on all of the panels is discussed and reviewed. The host controller software is also looked at in detail. Moving on to Chapter 5: Results sees the report

22

addressing the project as it stands today and the status of completion in the various target areas, and any improvements that had to be made to the original designs in order to realize completion. This chapter looks at panel calibration with regards to still images, and the final frame rate of the panel. Also discussed is the panel interaction with rolling shutter cameras and the network utilization and stability. Finally, Chapter 6: Conclusions and Future Work looks into suggestions and techniques that could be utilized for continued work on the subject, and where improvements can be made should work be continued at a subsequent time.

## Chapter 2: Network-Distributed Video Systems

This section provides a general background of the concepts used in the final design and describes the current technologies implemented in the project. It discusses some of the advantages and disadvantages of such that led to the overall design decisions chosen further discussed in Chapter 3.

#### 2.1 Professional Video Standards and Protocol Selection

Most video walls in existence today use only a few video input standards. HDMI HD-SDI, and DVI are three of the most common protocols in use in the industry today. HD-SDI or High Definition Serial Digital Interface is used as a digital video link that was first designed in 1998 by the Society of Motion Picture and Television Engineers for use in high-definition broadcast grade video. It offers a nominal data rate of about 1.5-Gbps (1080i) over a distance of about 300 meters, far longer than traditional analog video standards can possibly provide. For example, VGA is able to produce a maximum resolution of just 640x480 pixels. SDI and its variants provide uncompressed unencrypted video data via a serial byte stream with intermittent timing bits.

Figure 2 - 1: HD-SDI and SDI protocols utilize BNC connectors. From [7]

Also in use is HDMI or High-Definition Multimedia Interface. Like HD-SDI, HDMI is a digital video transmission protocol that supports the communication of a fully HD (1080p or greater) video signal along with different types of digital audio. An HDMI cable is shown in figure 2.2. Unlike any of the SDI protocols, HDMI provides packetized data. While running over HDMI cables, signals are typically encrypted with HDCP or High-bandwidth Digital Content Protection. This is an encryption scheme to ensure that video data running over the cable is difficult or impossible to listen in on or copy. Originally developed by Intel, HDCP has seen widespread use in the market today. In theory, as long as the input video card in the server supports and is compatible with HDCP, the end user will have no issues using the system.

Figure 2 - 2: An HDMI Type A connector. From [8]

Due to the intrinsic nature of large format displays as a whole, any input protocol must be able to support the amount of video data a very high pixel count display would call for. Also a sizable amount of high quality video production and transmission gear has already adopted digital interfaces. A comparison chart expanding on the details and differences between the various digital video standards is found below.

| Standard: | Max Image Size:   | Max Data<br>Speed: (Mbps) | Audio: |

|-----------|-------------------|---------------------------|--------|

| SD-SDI    | 470i, 576i        | 360                       | No     |

| ED-SDI    | 480p, 576p        | 540                       | No     |

| HD-SDI    | 720p, 1080i       | 1520                      | No     |

| 3G-SDI    | 1080p             | 3041                      | No     |

| DVI-D     | UXGA (1600x1200)  | 5068                      | No     |

| HDMI      | WQXGA (2560×1600) | 18432                     | Yes    |

Table 2 - 1: A table showing different digital video standards and some of their specifications.

The third most common digital video standard is DVI or Digital Visual Interface. DVI is flexible standard can accommodate both analog and digital either separately, DVI-A or DVI-D, or together, in DVI-I. There is no maximum cable length specified in the DVI standard, though in general for best performance, cables should be kept shorter than 15 feet. HDMI and DVI are very compatible with one another with some exceptions. For instance, DVI lacks the ability to carry digital audio, a main feature of HDMI. HDMI also lacks the ability to carry VGA, something found standard in DVI.

#### 2.2 Distributed Redundant Networks

As networks become larger, their inherent complexity grows as well. Often times, larger networks also demand large amounts of up time and reliability. However, as size increases, so do the number of potential points of failure. Redundancy must be built into large networks to maintain stability and a high level of fault tolerance. Adding in redundant nodes is relatively simple, as networks are designed to handle multiple clients. However, adding multiple paths for data to flow becomes difficult when traditional network ARP tables are used. Using the OSI (Open Systems Interconnection) network model, shown in figure 2.3, hardware must keep a record of what devices it is connected to via Layer 1. This occurs on Layer 2 of the OSI model. As switches have many devices connected to them, they must maintain a large table of connections, called an ARP (Address Resolution Table), which. Associates an IP address on Layer 3 with the hardware addresses found on Layer 2.

|                                                                                                                                            | OSI (Open Source Interconnection) 7 Layer Mod                                                                                                                                                                                                                                                | lel                                 |                 |                                                                                                  |                 |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------|--------------------------------------------------------------------------------------------------|-----------------|--|

| Layer                                                                                                                                      | Application/Example                                                                                                                                                                                                                                                                          | Central<br>Pro                      | Devic<br>tocols | e/                                                                                               | DOD4<br>Model   |  |

| Application (7)<br>Serves as the window for users and<br>application processes to access the network<br>services.                          | End User layer Program that opens what was sent or creates what is to be sent<br>Resource sharing • Remote file access • Remote printer access • Directory services • Network management                                                                                                     | Use<br>Applicat<br>SMT              | ions            |                                                                                                  |                 |  |

| Presentation (6)<br>Formats the data to be presented to the<br>Application layer. It can be viewed as the<br>"Translator" for the network. | Syntax layer encrypt & decrypt (if needed)<br>Character code translation • Data conversion • Data compression •<br>Data encryption • Character Set Translation                                                                                                                               | JPEG/AS<br>EBDIC/TIF<br>PICT        | F/GIF           | GIF<br>Cts<br>A<br>Ts<br>A<br>T<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C | Process         |  |

| Session (5)<br>Allows session establishment between<br>processes running on different stations.                                            | Synch & send to ports (logical ports)<br>Session establishment, maintenance and termination • Session<br>support - perform security, name recognition, logging, etc.                                                                                                                         | RPC/SQL<br>NetBIOS n                | /NFS            |                                                                                                  | A<br>T          |  |

| Transport (4)<br>Ensures that messages are delivered<br>error-free, in sequence, and with no<br>losses or duplications.                    | TCP Host to Host, Flow Control     F       Message segmentation • Message acknowledgement •     P       Message traffic control • Session multiplexing     C                                                                                                                                 | TCP/SPX                             | /UDP            |                                                                                                  | Host to<br>Host |  |

| Network (3)<br>Controls the operations of the subnet,<br>deciding which physical path the<br>data takes.                                   | Packets ("letter", contains IP address)<br>Routing · Subnet traffic control · Frame fragmentation ·<br>Logical-physical address mapping · Subnet usage accounting                                                                                                                            | Route                               |                 | Y<br>Can be<br>used                                                                              | Internet        |  |

| Data Link (2)<br>Provides error-free transfer of data frames<br>from one node to another over the<br>Physical layer.                       | Frames ("envelopes", contains MAC address<br>[NIC card — Switch — NIC card] (end to end)<br>Establishes & terminates the logical link between nodes • Frame<br>traffic control • Frame sequencing • Frame acknowledgment • Frame<br>delimiting • Frame error checking • Media access control | Switch<br>Bridge<br>WAP<br>PPP/SLIP | Land            | on all<br>layers                                                                                 | Network         |  |

| Physical (1)<br>Concerned with the transmission and<br>reception of the unstructured raw bit stream<br>over the physical medium.           | Physical structure Cables, hubs, etc.<br>Data Encoding • Physical medium attachment •<br>Transmission technique - Baseband or Broadband •<br>Physical medium transmission Bits & Volts                                                                                                       | Hub                                 | Layers          |                                                                                                  | HELWOIK         |  |

Figure 2 - 3: A table representation of the OSI model. From [9]

In a conventional network, switches maintain a small local ARP table of clients and their respective port location, as only one IP address can be assigned to a port. This ensures that data requests can be routed efficiently and accurately. When redundant paths are added in between two switches, a phenomenon known as a bridge loop occurs. Multiple paths can cause an overflow of the ARP tables in extreme cases. However, as switching hardware and clients generally send broadcast packets at regular intervals, having loops in a network would cause the packet to travel the network forever. As these packets are exclusively routed over Layer 2, the packets cannot have a TTL (Time to Live) value, and therefore are only dropped when the network reaches full capacity due to an exhaustion of switching capacity. The net effect of this situation is commonly referred to as a "runaway network." The network soon becomes consumed with broadcast packets that cannot be destroyed, rendering the network unusable for standard traffic.

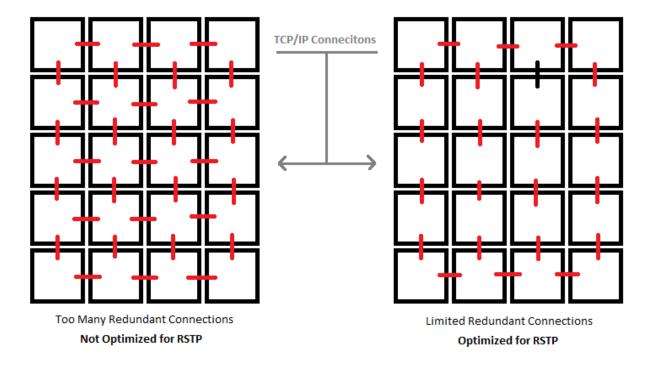

Solutions exist in the IEEE 802 specification to allow for path redundancy while eliminating the ability for the network to be consumed with superfluous packet traffic. Spanning-Tree Protocol, defined by IEEE standard 802.1d, adds a lightweight framework for switching hardware to virtually connect and disable various redundant pathways as needed by the network topology. As this protocol takes time to converge and disable the appropriate paths, the specification was revised to IEEE 802.1w or Rapid Spanning-Tree Protocol. RSTP is capable of optimizing a network full of redundant pathways within 30 seconds, making it Ideal for time-critical setup applications. This works by examining the redundant physical paths, and virtually disabling some paths until they are required to be activated again due to a failure of another neighboring path. Examples of this operating are visible in figures 2.4 and 2.5.

Figure 2 - 4: A physical connection before RSTP. From [10]

Figure 2 - 5: A virtually-removed connection after RSTP. From [10]

RSTP works by first selecting a central switch called the root bridge. In traditional network, this is configured on the hardware manually by a system technician. In some cases, there may also be redundant root bridges if the initial root bridge fails. In a context where the network topology is constantly changing, however, this may not be practical, as the network would require manual configuration for every major topology change that affected the presence of the root bridge.

Figure 2 - 6: In a STP-enabled network, switches are assigned various weights, and paths are assigned various weights as well. Paths with the longest weights are disabled until lower-weight paths become unusable due to network topology changes or other path failure. From [10]

802.1d/w allow for options that support the automatic determination of a root bridge, however. In this situation, during the initialization of a network, every switching device undergoes what is aptly named, a "root war." During the root war, the switch with the lowest MAC address is determined to be the root bridge. After this occurs, the rest of the path optimization occurs. A configuration such as this is ideal for large networks with highly-varying topologies from initialization to initialization. While this technology is commonly implemented in enterprise-level network infrastructures, this is seldom implemented in live audio and video applications. This can be primarily attributed to the fact that few video systems actually transmit video content over IP and secondarily attributed to the fact that the primary considerations of the industry have been improving individual panel reliability over network reliability.

Spanning-Tree also offers some protection features to ensure a fast recovery form a failed network. One such method implemented is Unidirectional Link Detection or UDLD [11]. This operates by regularly sending out packets on a specific port, querying neighboring hardware. If the hardware fails to respond before a timeout occurs, the link can be assumed to be unidirectional. In the context of an LED array, this is undesirable, as although video content may be able to still be displayed, any traffic returning to a controller to notify the system of a fault might be blocked. If a link is determined to be unidirectional, it is thrown into an error state, and any redundant pathways are enabled, ensuring bidirectional connectivity between nodes.

#### 2.3 Large-Format Display Topologies

Large format displays come in many different shapes and sizes. Most displays in use today are flat and rectangular. This is the easiest format to implement due to the intrinsic issues that start to arise when curved or other non-quadrilateral formats are used. However making large format displays curved is not impossible. The ABC Times Square Studio, shown in Figure 2.7, is one such example where multiple different curves can be incorporated into one whole display. Displays such as the one in Times Square are traditionally purpose built for a single installation and are rarely used in different configurations once installation is complete.

Figure 2 - 7: The ABC Times Square Studio in NYC, New York. From [12]

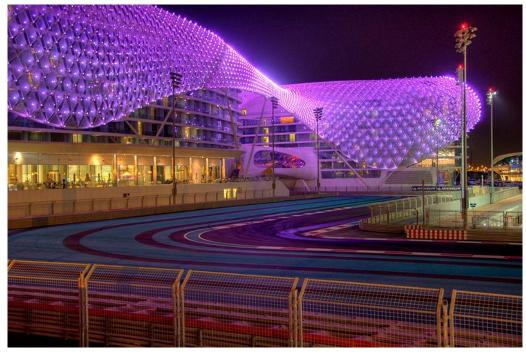

Other curved displays include the Yas Marina Hotel, shown in Figure 2.8, which is an example of a large LED display taken on a massive scale. The 85,000 square foot hotel is built over the top of the Abu Dhabi F1 Racetrack, and sports a multi-color LED exo-skeleton, allowing the hotel management to put on a massive light show at night. With 5,389 pivoting square LED panels, the hotel can display any manor of video or color on its exterior. The hotel remains today as one of the only of its kind in the world. [13]

Figure 2 - 8: The Yas Marina Hotel in Abu Dhabi illuminated in a shade of purple. From [14]

While curved displays are a portion of the market, rectangular-based displays are most common in use today. Square panel based displays have the highest configurability and customization due to their building-block like nature, and their ability to be easily broken down into smaller units. The nature of square panels also have a positive impact in tessellation, in that most displays will have a rectangular aspect ratio, and building any rectangular display with square panels is quite simple. Square panels also ease the task of creating redundant networking connections. Each and every square panel can have 4 straight-line neighbors for connections plus an additional 4 diagonal neighbors if more connections are needed. With the 4 connections per panel situation, any two panels can fail without distinctly interrupting the connection to another.

Figure 2 - 9: A rectangular set of panels mounted on a wall. From [15]

In addition to the ease of redundancy, square panels also add the convenience of rigging options. Because there are four flat edges to every panel, each neighboring panel can be brought flush together, increasing overall display coherency and decreasing the need for unique or difficult hardware for attachment. This makes square panels the unit of choice in most road shows and performances. One such setup is shown in Figure 2.9.

#### 2.4 Video Processing Systems

In any application, it would be inefficient to route a video input source directly into each panel and perform the processing individually. To optimize efficiency, panel manufacturers often design a companion controller that serves to take in a video input source and convert it into a data format that the panels can then easily interpret. These devices usually also provide some form of transport layer and output system to directly connect to the panels. Generally, these devices do not provide power to the panels directly, although they usually are stored in close proximity to the power distribution systems for the panels.

Figure 2 - 10: Elation Image VSC 2.0 Image processor used to condition video to be fed to a panel controller. From [16]

Manufacturers such as Elation [X] have proprietary video scaling and conversion hardware that is used to drive their panels. One of their image processing systems is shown in Figure 2.10. The typical system consists of a hardware video processor that conditions a video signal a resolution and color depth that is usable by the panels. This signal is then fed through conventional video cables to a panel controller that is responsible for taking in the processed video signal and converting to network frames that are routed to the array. This is usually done through implementation of differential signaling through RJ-45 twisted pairs. These devices usually only implement unidirectional communication protocols, and very few on the market implement full IP-based communication.

#### 2.5 Summary

This chapter has shown some of the many different design points and pre-existing technology used in this project. In the first section an explanation of digital video protocols as well as a comparison of their strengths and weaknesses. Specifics to the most common protocols in use today were explained and a comparison of those details was made as well. The second section took a look at networking protocols and redundancy, and how to find network resilience in existing IEEE protocols. The IEEE specifications of 802.1D and 802.1w were explained and their effectiveness in the scope of this project was demonstrated. The third section saw an overview of large format display topologies and how the sizes and shapes of displays can affect the properties of the display as a whole. The fourth section showed how video processing has an impact on large format displays and the rolls that it plays in live video displays. This section also gave an example of a proprietary video processing rig and briefly explained how it functions.

# Chapter 3: Proposed Design and Project Logistics

This section will describe the projects design constraints, overall system specification, and the methodology in determining these specifications and constraints.

## 3.1 Main Project Goals

LED video walls require large, complex networks that often fail. In addition to this, they require substantial amounts of effort during setup to properly address, arrange, and connect each panel. In a large network that is prone to failures, especially those in the live entertainment market, failures are visible instantly to thousands of people, making it incredibly desirable to resolve faults efficiently and quickly without compromising safety.

The goal of this project was to develop a self-addressing array of LED panels capable of recovering from network faults introduced by damaged or faulty connections. This would allow for such recovery and operator notification through the use of Rapid Spanning-Tree Protocol as a network backbone for a proprietary UDP-based protocol to relay control signals and video data to and from panels. In addition to enabling various improvements to network reliability and panel diagnostics, a secondary goal of the project was to improve the overall video quality of the output stage of the panels by investigating the viability of directly driving individual LED's, removing the need for multiplexing LED output.

This design has a significant amount of technical challenges to overcome in its implementation. They are as follows:

- Integrating RSTP into a Compact Solution RSTP must be successfully implemented on each panel to effectively provide redundancy.

- Designing a Robust UDP Layer 7 Protocol There currently exists no nonproprietary protocol for transmitting video frames to panels. There is also no protocol in place to handle the automatic addressing of panels and bi-directional communication to the controller.

- Designing Fault-Tolerant, Ruggedized Hardware Implementation of all of the required features defined by the project will require the design and implementation of significantly specialized hardware.

Implementing Video Processing/Optimization – Specialized host software will need to be written in order to efficiently control the array and provide a point of user feedback to indicate faults in a system.

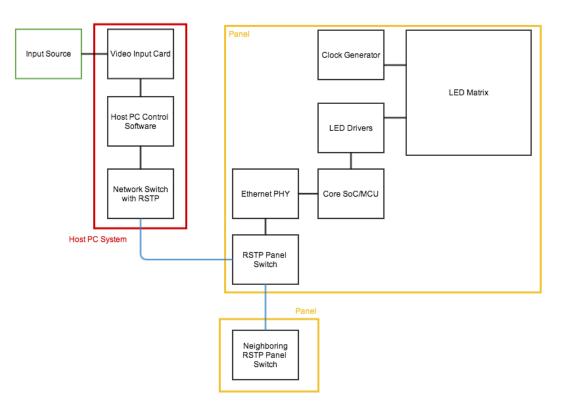

Figure 3 - 1: Proposed high-level system block diagram.

The above diagram, figure 3.1, illustrates a high-level implementation of the required subsystems of the project. As the purpose of the project is to illustrate the viability of a self-addressing, redundant panel array, only several panels will constructed to prove the concept. If required, more panels can be constructed to create larger networks. To decrease production time, a panel size of 16x16 pixels will be chosen. Larger video resolutions will be implemented by arraying multiple panels in various configurations and observing the behavior of the video content.

# 3.2 Project Objectives and Specifications

The primary objective for the project is to improve the redundancy and reliability of LED video walls and to remove the need to individually configure panels to work as a

larger array. This will be achieved through the use of multiple network protocols, and the final system must be capable of several objectives:

- The system will use an algorithm to determine the relative location of panels in an array and dynamically map video content to the size and shape of such array.

- The system must be able to recover from a failure and be able to dynamically remap video content to the new array shape.

- The system must be able to display visually pleasing and accurate video output relative to the video input.

- The system must be able to be quickly setup and configured.

- The system must be able to notify an operator of a fault through methods other than visual detection of the failure.

These primary objectives will be reached through the design and development of several component subsystems that will be integrated together into a singular, streamlined final product. The systems designed will serve as a panel replacement as opposed to a supplemental system that could be installed onto another pre-built panel. This will enable granular control of the final design and will enable the team to develop a finished, efficiently optimized product.

The technical specifications for the final product in the areas of video quality, networking, robustness and power are defined in the subsections below.

3.2.1. Video Output:

- Variable size and shape panels

- Tri-color RGB LED with 24-bit color-depth

- At least 1000 total lumen output per panel

- Supports at least 30 frames per second

- Automatic color and brightness calibration

- Minimal effects on rolling-shutter type cameras.

# 3.2.2. Networking:

- Self-addresses for relative position in display configuration

- Automatic routing of video signals

- Fault-aware and diagnosing abilities

- Dead pixel detection

- Inter-panel fault communication

- Standard RJ-45 Ethernet connection to controller

- 3.2.3. Ruggedized:

- IP65 weatherproof and intrusion resistance certification.

- Riggable or stackable modular chassis

- Shock-resistant to at least IK04 [17] specifications.

# 3.2.4. Power:

- Accepts 60-Hz, 90-250V AC Mains input with a bypass (out) connector

- Output capability >= 60W

- Noise filtering from/to mains to acceptable EMC standards levels

- Power monitoring and fault detection/reporting

- Protection from surges for display/logic systems

- All power rails created on-board

- Achieves >80% efficiency, 0.95 power factor

#### 3.3 Project Management and Tasks

To optimize efficiency and improve the amount of work that could be done at any one time, the project was broken up into separate discrete sections that could be completed alone or in tandem with one or more other team members. Initial planning was done mostly to get the project started and on task with the major portions. The development strategy consisted mainly of the four team members working on four separate sections every week until the task at hand was done. This would continue until the project was completed. For some sections however, it was necessary for team members to work on their sections together and complete some tasks that were interdependent. In those cases, the team was able to communicate and coordinate times for meeting and work to be completed together. The team was able to hold numerous meetings and work sessions in the lab.

In addition to this planning, the team created a Gantt chart to mark out progress and define target dates and deadlines. The chart provided a broad task and gave it a specified time range in which to be completed in. This original chart the team designed is shown below in Figure 3.2. This shows the major sections that needed to be completed for project success. Both the major design and the research needed to be completed early and quickly. Next came a simulation of the circuit and software portions of the project. Extensive client simulation was also to be performed to ensure the successful deployment of RSTP and host video software. After that designs for the specific hardware was done and assembly of units began. Once that had been completed, unit testing and whole systems testing was performed.

|                         |           | ۲.  |         |         |         |         |         |         |       | 2013    |         |         |         |         |         |       |         |         |         |         |         | 2014    |         |       |        |

|-------------------------|-----------|-----|---------|---------|---------|---------|---------|---------|-------|---------|---------|---------|---------|---------|---------|-------|---------|---------|---------|---------|---------|---------|---------|-------|--------|

|                         |           |     |         |         |         |         | October |         |       |         | Nover   | nber    |         |         | Dec     | ember |         |         |         | Janua   | ry      |         |         | Feb   | ruary  |

|                         |           | 37  | 38      | 39      | 40      | 41      | 42      | 43      | 44    | 45      | 46      | 47      | 48      | 49      | 50      | 51    | 52      | 1       | 2       | 3       | 4       | 5       | 6       | 7     | 8      |

| Project stages          | Resources | -13 | 16 - 20 | 23 - 27 | 30 - 04 | 07 - 11 | 14 - 18 | 21 - 25 | 28-01 | 04 - 08 | 11 - 15 | 18 - 22 | 25 - 29 | 02 - 06 | 09 - 13 | 16-20 | 23 - 27 | 30 - 03 | 06 - 10 | 13 - 17 | 20 - 24 | 27 - 31 | 03 - 07 | 10-14 | 17 -21 |

| MQP                     | ~         |     |         |         |         |         |         |         |       |         |         |         |         |         |         |       |         |         |         |         |         |         |         |       |        |

| Research                |           |     |         |         |         |         |         |         |       |         |         |         |         |         |         |       |         |         |         |         |         |         |         |       |        |

| Major Design            |           |     |         |         |         |         |         |         |       |         |         |         |         |         |         |       |         |         |         |         |         |         |         |       |        |

| Simulation              |           |     |         |         |         |         |         |         |       |         |         |         |         |         |         |       |         |         |         |         |         |         |         |       |        |

| First Board Spin        |           |     |         |         |         |         |         |         |       |         |         |         |         |         |         |       |         |         |         |         |         |         |         |       |        |

| First Working Display   |           |     |         |         |         |         |         |         |       |         |         |         |         |         |         |       |         |         |         |         |         |         |         |       |        |

| Initial Software        |           |     |         |         |         |         |         |         |       |         |         |         |         |         |         |       |         |         |         |         |         |         |         |       |        |

| Second Board Spin       |           |     |         |         |         |         |         |         |       |         |         |         |         |         |         |       |         |         |         |         |         |         |         |       |        |

| Initial Systems Testing |           | 1   |         |         |         |         |         |         |       |         |         |         |         |         |         |       |         |         |         |         |         |         |         |       |        |

| Multi-Panel Testing     |           |     |         |         |         |         |         |         |       |         |         |         |         |         |         |       |         |         |         |         |         |         |         |       |        |

Figure 3 - 2: Proposed general timeline and project schedule.

Unfortunately not everything always goes to plan, and some adjustments had to be made. An updated and more detailed schedule can be found below in figure X. Note that the first working display was achieved on February 8th with the successful completion of a multiplexing panel.

|                            |           |                |    |    |      |      |    |    | Ja | anuar | y 201 | 14 |    |      |      |      |    |      |      |       |      |    |     |    |    |    |     |    |    |    |    |     |    |      |    | Febr | uary | 201 | 1    |    |    |    |    |

|----------------------------|-----------|----------------|----|----|------|------|----|----|----|-------|-------|----|----|------|------|------|----|------|------|-------|------|----|-----|----|----|----|-----|----|----|----|----|-----|----|------|----|------|------|-----|------|----|----|----|----|

| Activity                   | Resource  | Status         | 07 | 08 | 09 1 | 0 11 | 12 | 13 | 14 | 15 1  | 6 17  | 18 | 19 | 20 2 | 1 22 | 2 23 | 24 | 25 2 | 26 2 | 27 21 | 8 29 | 30 | 31  | 01 | 02 | 03 | 04  | 05 | 06 | 07 | 08 | 09  | 10 | 11 1 | 12 | 13 1 | 14 1 | 5 1 | 5 17 | 18 | 19 | 20 | 2. |

| Mechanical Designs         |           | In- Progress 🗸 | -  |    |      |      |    |    |    |       |       |    |    |      |      |      |    |      |      |       |      |    |     |    |    |    |     |    |    |    | Ĩ  |     |    |      |    |      |      |     |      |    |    |    | Ĩ  |

| Develop 3D Driver Files    | Alex      | Done           |    |    |      |      |    |    |    |       |       |    |    |      |      |      |    |      |      |       |      |    |     |    |    |    |     |    |    |    |    |     |    |      |    |      |      |     |      |    |    |    |    |

| 3D LED Matrix Board Mod    | Paulo     | In- Progress   |    |    |      |      |    |    |    |       |       |    |    |      |      |      |    |      |      |       |      |    |     |    |    |    |     |    |    |    |    |     |    |      |    |      |      |     |      |    |    |    |    |

| Mechanical Analysis / Tole | Rayce     | In- Progress   |    |    |      |      |    |    |    |       |       |    |    |      |      |      |    |      |      |       |      |    |     |    |    |    |     |    |    |    |    |     |    |      |    |      |      |     |      |    |    |    |    |

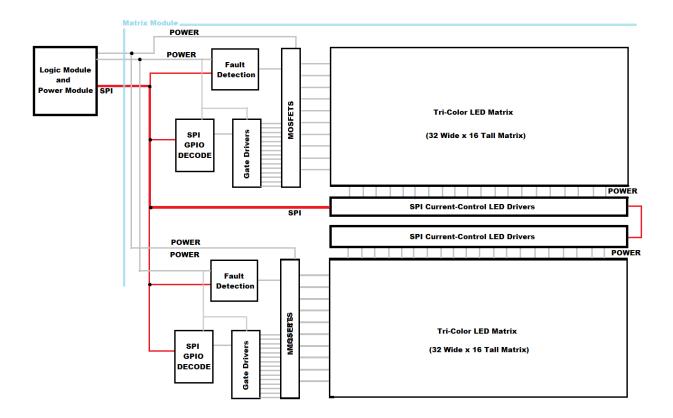

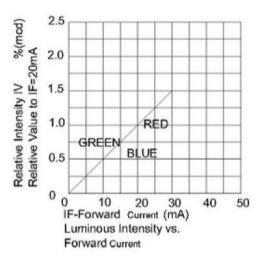

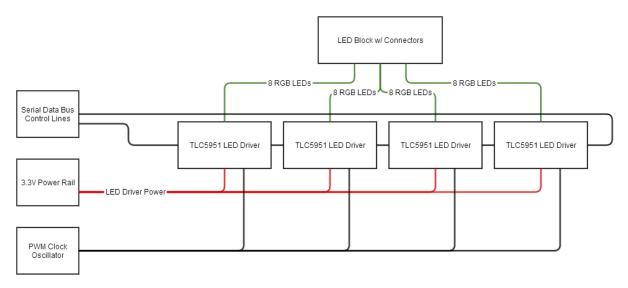

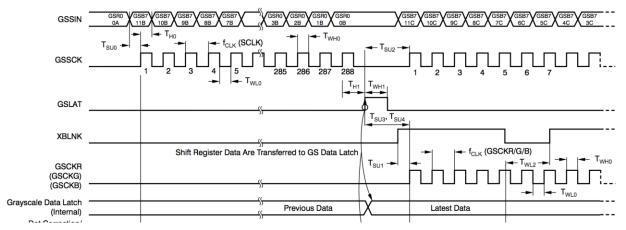

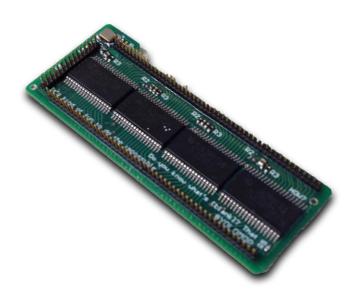

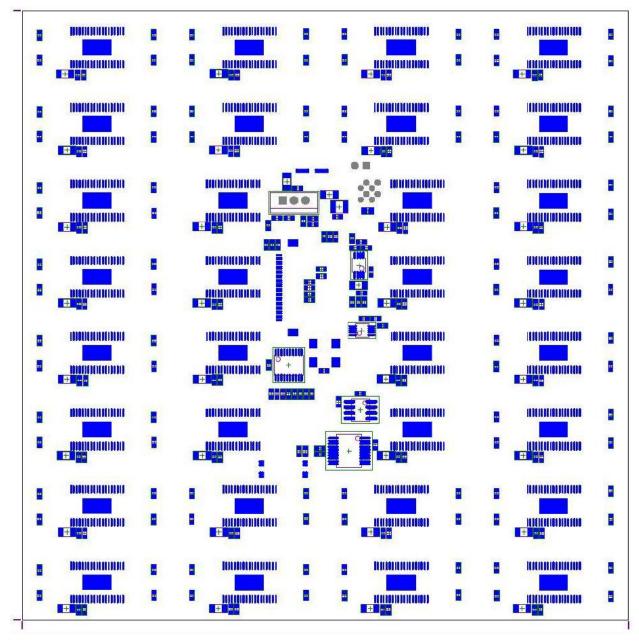

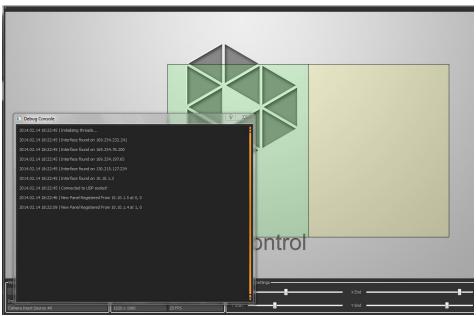

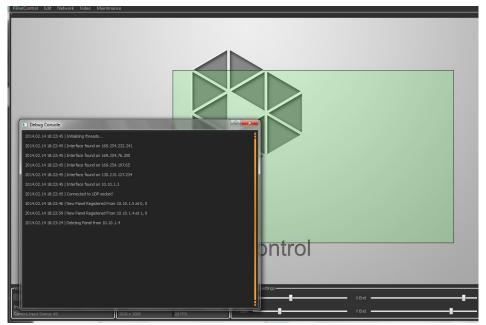

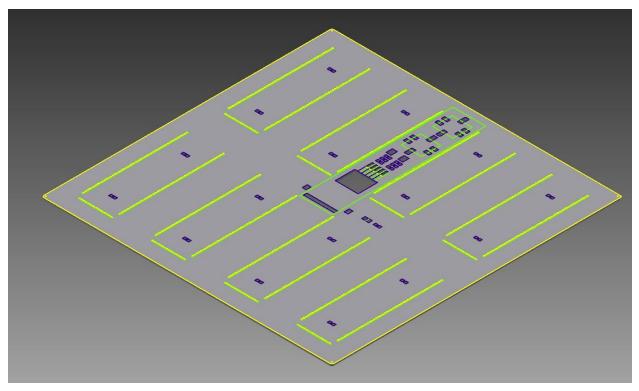

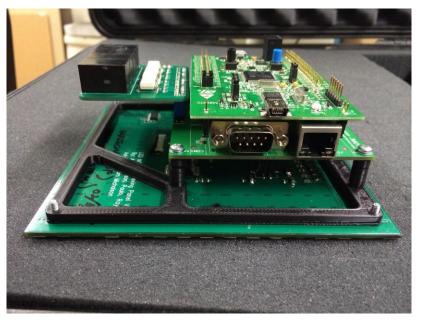

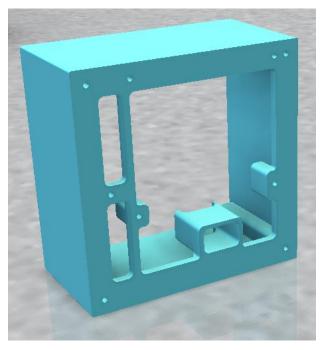

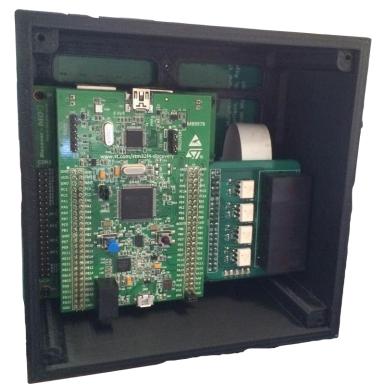

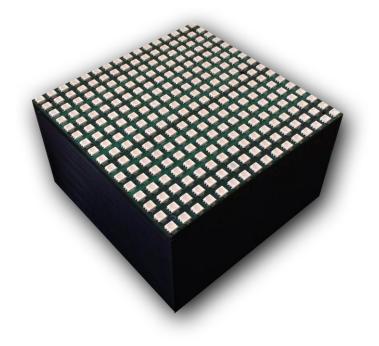

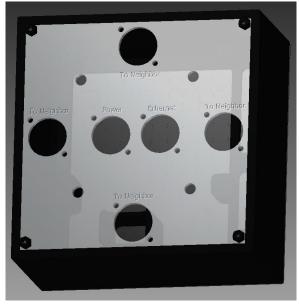

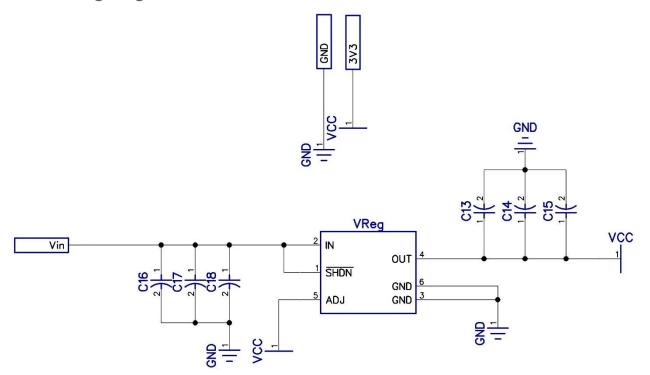

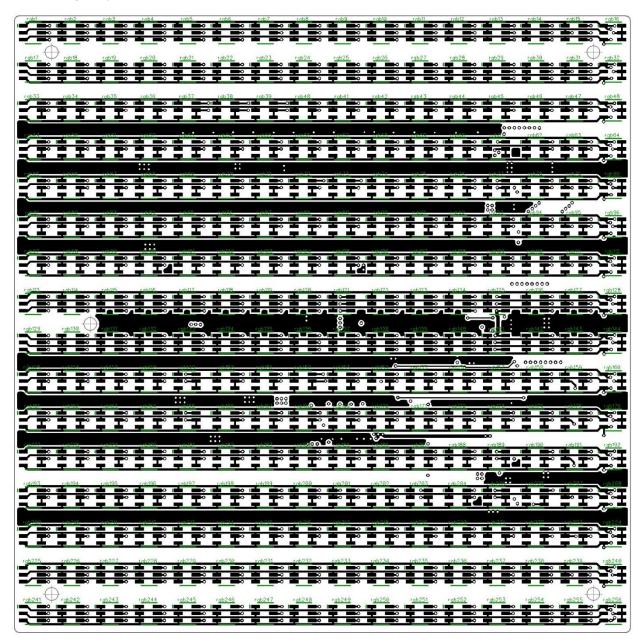

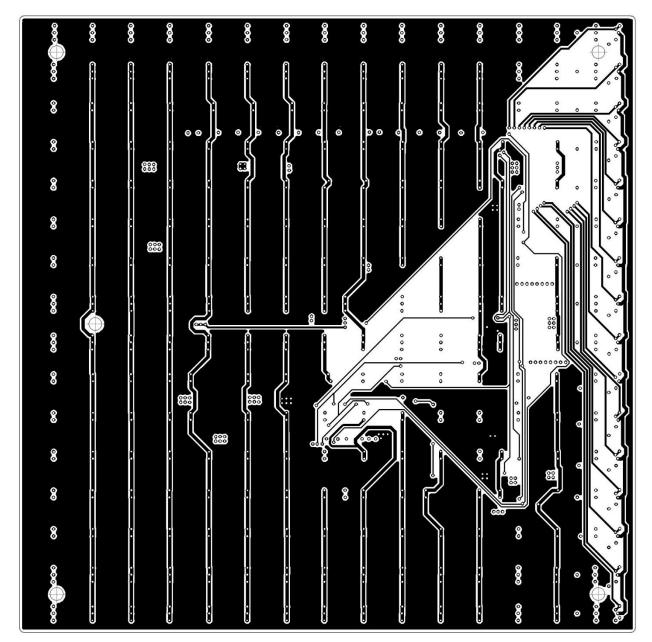

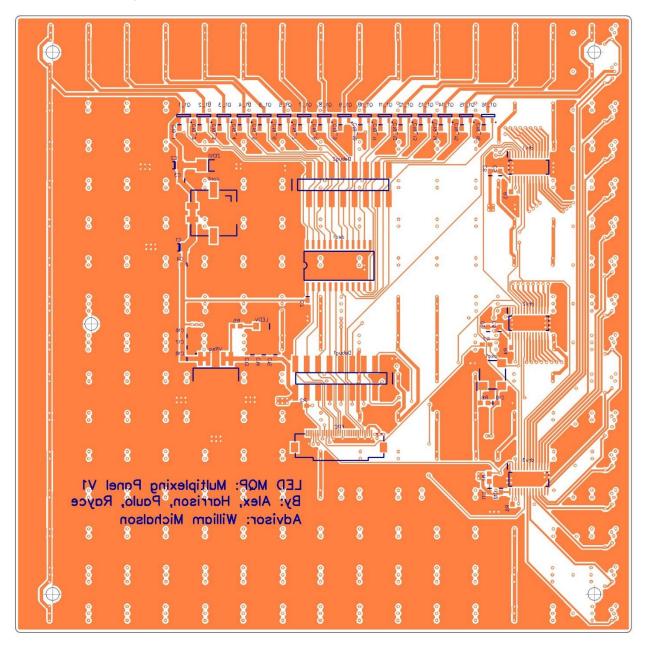

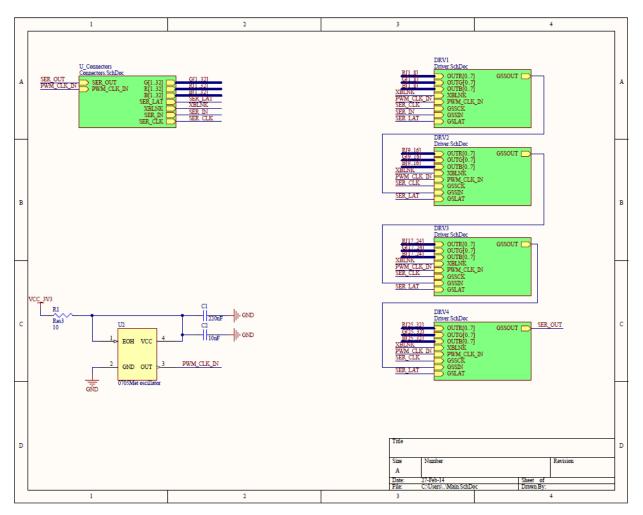

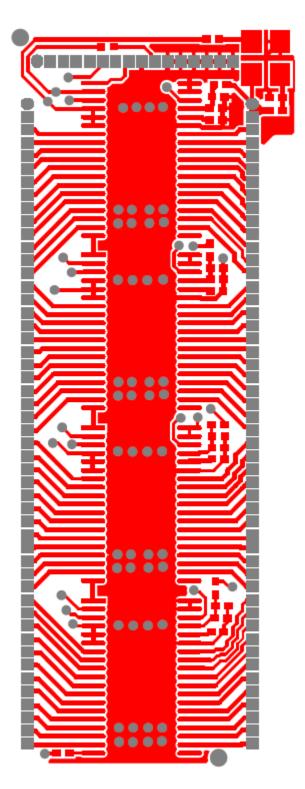

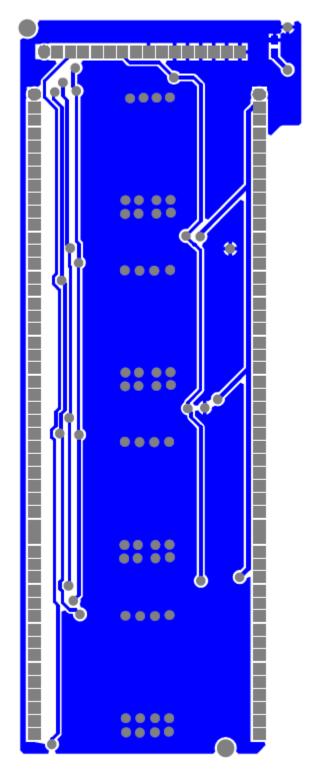

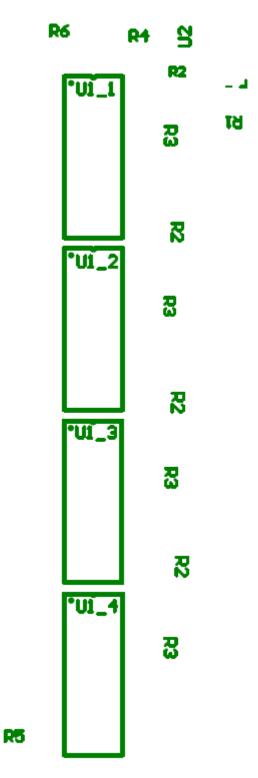

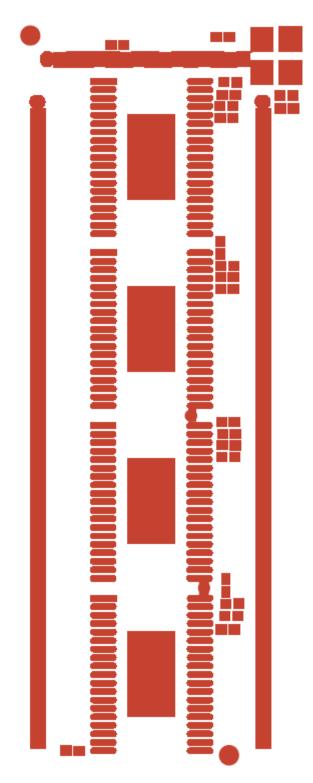

| Design Enclosure/Mount     | Rayce     | In- Progress   |    |    |      |      |    |    |    |       |       |    |    |      |      |      |    |      |      |       |      |    |     |    |    |    |     |    |    |    |    |     |    |      |    |      |      |     |      |    |    |    |    |