## Worcester Polytechnic Institute Digital WPI

Major Qualifying Projects (All Years)

Major Qualifying Projects

April 2016

# Nonlinear Load Compensation

Joseph Harry Keogh Worcester Polytechnic Institute

Follow this and additional works at: https://digitalcommons.wpi.edu/mqp-all

#### **Repository Citation**

Keogh, J. H. (2016). Nonlinear Load Compensation. Retrieved from https://digitalcommons.wpi.edu/mqp-all/1430

This Unrestricted is brought to you for free and open access by the Major Qualifying Projects at Digital WPI. It has been accepted for inclusion in Major Qualifying Projects (All Years) by an authorized administrator of Digital WPI. For more information, please contact digitalwpi@wpi.edu.

# Nonlinear Load Compensation

Project #: AAZC

Author: Joseph Harry Eisenberg Keogh

Advisor: Professor Alexander Emanuel Co-Advisor: Professor Alexander Wyglinski

## Abstract

Nonlinear loads pose significant problems to power engineers, and have proliferated in occurrence over the past few decades. This project seeks to design and simulate a process by which one might mitigate the harmful consequences that result from their usage, employing signals processing techniques, logical decision-making processes, and currently available power electronics hardware.

# Table of Contents

| 1 | Introduc | tion                                                          | 1  |

|---|----------|---------------------------------------------------------------|----|

|   | 1.1 Pro  | posed Solutions                                               | 5  |

|   | 1.1.1    | Analog Pre-Processing                                         | 6  |

|   | 1.1.2    | Digital Processing and Control                                | 7  |

|   | 1.1.3    | Power Delivery                                                | 9  |

| 2 | Backgrou | und Information                                               | 10 |

|   | 2.1 Sigr | nal-Processing Theory                                         | 10 |

|   | 2.1.1    | Waveform Parameters                                           | 10 |

|   | 2.1.2    | Waveform Superposition                                        | 13 |

|   | 2.1.3    | Continuous-Time, Discrete-Time, and Digital Signals           | 14 |

|   | 2.1.4    | Complex Magnitude and Phase, and Euler's Identity             | 15 |

|   | 2.1.5    | Complex-Frequency Domain                                      | 16 |

|   | 2.2 Circ | uit Theory                                                    | 17 |

|   | 2.2.1    | Loads                                                         | 17 |

|   | 2.2.2    | Simple Semiconductors                                         | 20 |

|   | 2.2.3    | The H-Bridge                                                  | 26 |

| 3 | Propose  | d Approach                                                    | 28 |

|   | 3.1 Solu | ution Concept                                                 | 28 |

|   | 3.1.1    | Analog Voltage Preprocessing                                  |    |

|   | 3.1.2    | Analog Current Preprocessing                                  | 32 |

|   | 3.1.3    | Digital Processing and Controls                               |    |

|   | 3.1.4    | Controls Units                                                | 41 |

|   | 3.1.5    | Power Delivery                                                | 44 |

|   | 3.1.6    | Output Monitor Triggering                                     | 45 |

|   | 3.2 Fina | alists                                                        | 45 |

|   | 3.2.1    | Analog Preprocessing and Analog-to-Digital Conversion         | 45 |

|   | 3.2.2    | Power Delivery                                                | 45 |

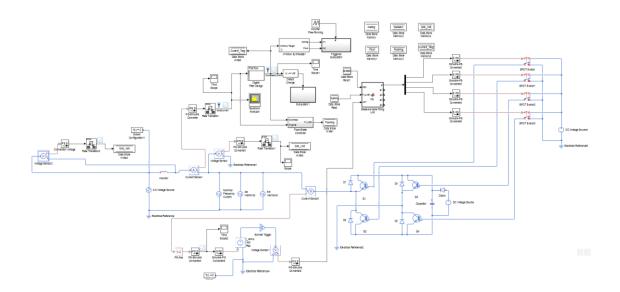

|   | 3.2.3    | Logical State-Decisions: The Decision Engine and Gating Codes | 51 |

|   | 3.2.4    | Nominal Frequency Separation                                  | 57 |

|   | 3.2.5    | Window Comparison                                             | 66 |

|   | 3.2.6    | Transience Control                                            | 72 |

| 4 | Expe  | erime  | ents and Results                   | 74 |

|---|-------|--------|------------------------------------|----|

|   | 4.1   | Filte  | r Transience Experiment            | 74 |

|   | 4.2   | Early  | y Warning Signs                    | 76 |

|   | 4.3   | The    | (Almost) Final Model               | 79 |

|   | 4.3.2 | 1      | Significant Limitations            | 79 |

|   | 4.3.2 | 2      | Running the Final Simulation       | 80 |

|   | 4.4   | The    | (Actual) Final Model               | 83 |

| 5 | Con   | clusio | ons and Future Work                | 90 |

| 6 | App   | endic  | ces                                | 91 |

|   | 6.1   | Арре   | endix A: Supporting MATLAB Scripts | 91 |

|   | 6.1.2 | 1      | Circuit Theory                     | 92 |

|   | 6.2   | Арре   | endix B: Simulink Model Diagrams   | 94 |

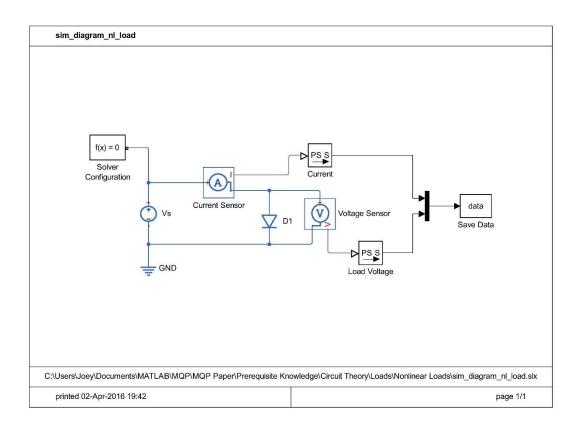

|   | 6.2.2 | 1      | Nonlinear Load                     | 94 |

| 7 | Bibli | ograp  | phy                                | 95 |

# List of Figures

| Figure 1: SMPS Nonlinear Load [4]                                                                            | 2    |

|--------------------------------------------------------------------------------------------------------------|------|

| Figure 2: Example Current Waveform for a 6-Pulse Rectifier [7]                                               | 3    |

| Figure 3: Single-Phase Inverter Implementation of Compensator, Applied at a Central Node [8]                 | 4    |

| Figure 4: Compensator's Fundamental Frequency Reconstruction Diagram Using Power Calculations and Energy     |      |

| Detection [9]                                                                                                | _ 5  |

| Figure 5:Power Circuit Shown with Waveform Reconstruction Compensator [9]                                    | 5    |

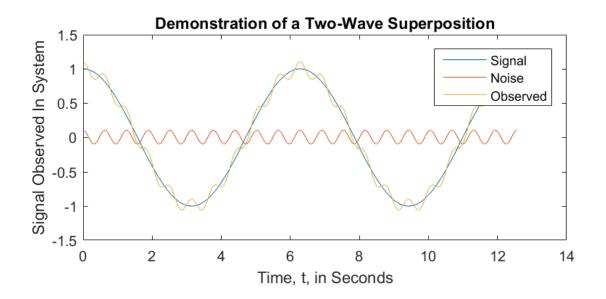

| Figure 6:Illustration of the Superposition Principle                                                         | 13   |

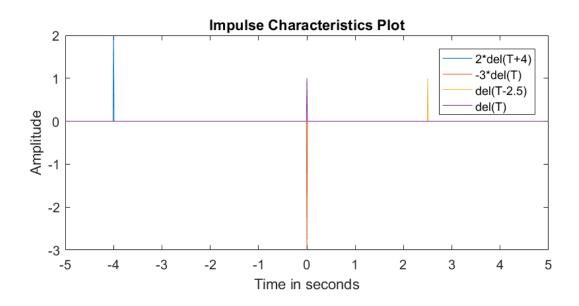

| Figure 7:Behaviors of the Impulse Function                                                                   | 15   |

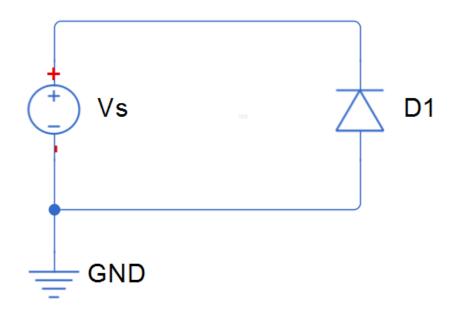

| Figure 8: Circuit Diagram for Nonlinear Load Demo                                                            | 18   |

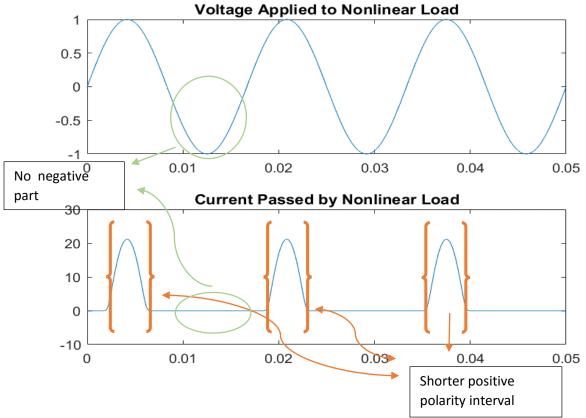

| Figure 9: Simulated Voltage Drop and Current of an Exponential Diode Load                                    | 19   |

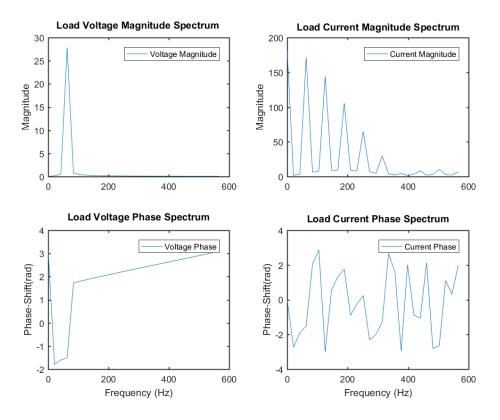

| Figure 10: Nonlinear Load Demo Frequency Domain                                                              | _ 20 |

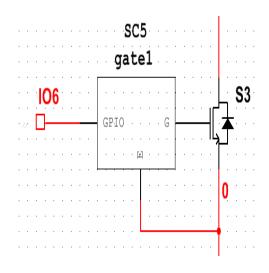

| Figure 11: Simscape Power Systems "Specialized Technology" IGBT                                              | _ 22 |

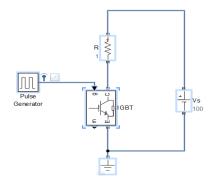

| Figure 12: IGBT Switching Demo Circuit Diagram                                                               |      |

| Figure 13:IGBT Switching Current and Voltage Behaviors                                                       | _ 23 |

| Figure 14: Current-Amplitude Controlled Switching Demo, Current Waveform                                     | _ 24 |

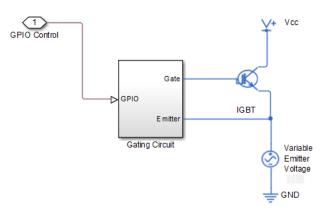

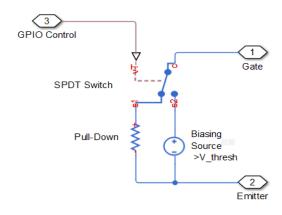

| Figure 15: Simulink Emitter-Following Gating Circuit IGBT Configuration                                      | _ 26 |

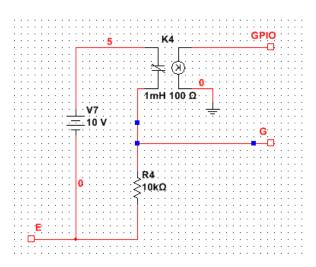

| Figure 16:Simulink Emitter-Following Gating Circuit                                                          | 26   |

|                                                                                                              | 26   |

| Figure 18: Multisim Application of Gate Circuit                                                              | 26   |

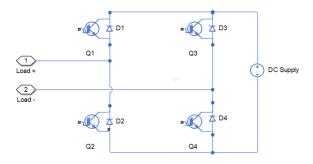

| Figure 19: Project H-Bridge IGBT Configuration                                                               | _ 27 |

| Figure 20: Top-Level Block Diagram of Proposed Solution                                                      | _ 29 |

| Figure 21: Analog Voltage Preprocessor Circuit Diagram                                                       |      |

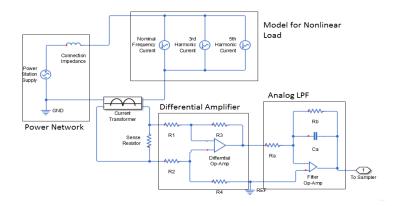

| Figure 22: Top-Level Diagram of Analog Current Preprocessing                                                 | _ 33 |

| Figure 23: Symbol for Current Transformer [8]                                                                | _ 34 |

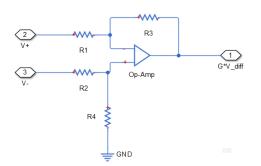

| Figure 24: Difference-Amplifier Schematic [11]                                                               | 35   |

| Figure 25:Proposed Circuit Schematic for Analog Preprocessing                                                | _ 36 |

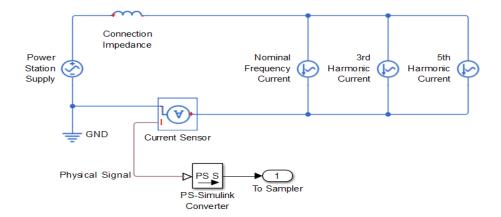

| Figure 26: Reading Grid Current in SimElectronics Environment                                                |      |

|                                                                                                              |      |

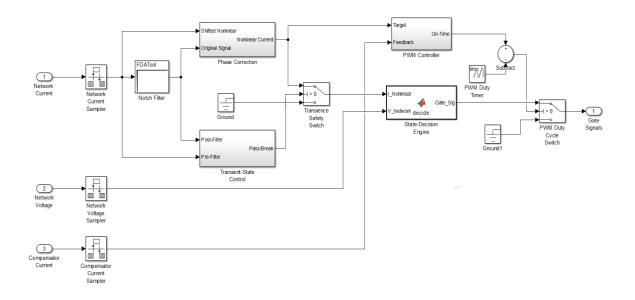

| Figure 28: Processing and Controls Example, Uses Notch-Filter Base-Elimination, Preemptive Transience        |      |

| Measurement, and Pulse-Width Control System                                                                  | _ 44 |

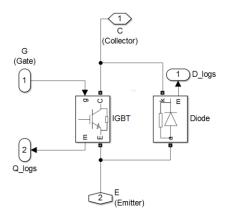

| Figure 29: IGBT Block Reference and Equivalent Circuit                                                       | _ 46 |

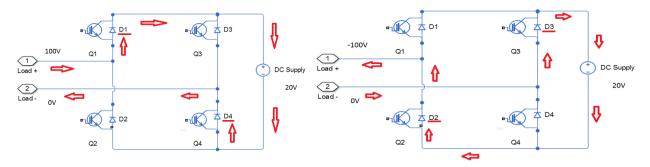

| Figure 30: Current Path Through Bridge Diodes for Insufficient Supply, Negative Network Case                 | _ 47 |

| Figure 31: Current Path Through Bridge Diodes for Insufficient Supply, Positive Network Case                 | _ 47 |

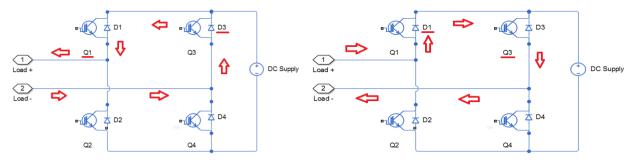

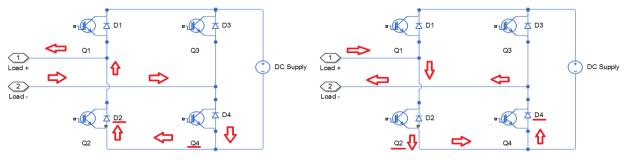

| Figure 32: High-Side, Ground to Power-Line Current Path                                                      | _ 49 |

| Figure 33: High-Side, Power-Line to Ground Current Path                                                      | 49   |

| Figure 34:Low-Side Short-Circuit State, Power-Line to Ground Current Path                                    | _ 49 |

| Figure 35: Low-Side Short-Circuit State, Ground to Power-Line Current Path                                   | _ 49 |

| Figure 36: IGBT/Diode Subcircuit in Power Delivery Bridge Converter                                          | _ 50 |

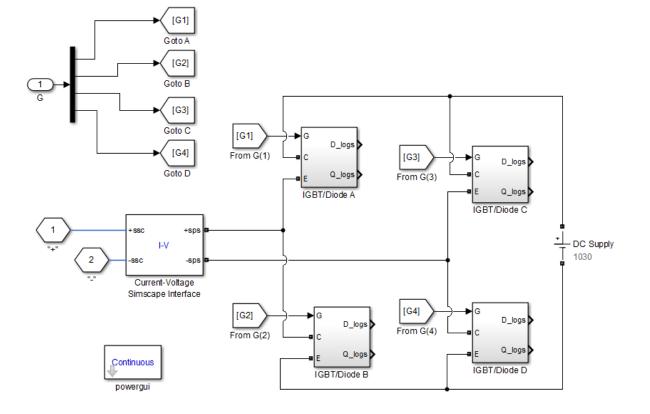

| Figure 37: The Bridge-Converter Simulation Configuration                                                     | _ 50 |

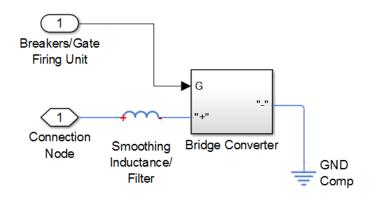

| Figure 38: Simulation Diagram of Bridge Converter's Connection to System and Environment                     |      |

| Figure 39: Logical Structure of Decision Engine                                                              | 53   |

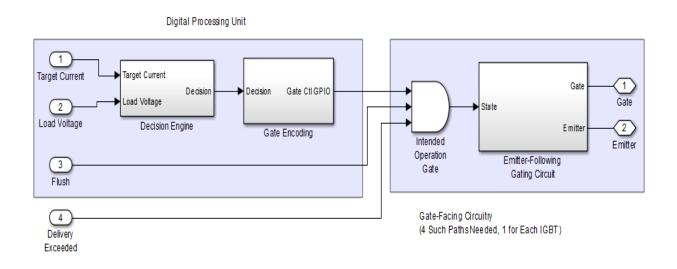

| Figure 40: Proposed Physical Implementation of Logical Decision Making and Gate-Signal Generation and Contro | ol54 |

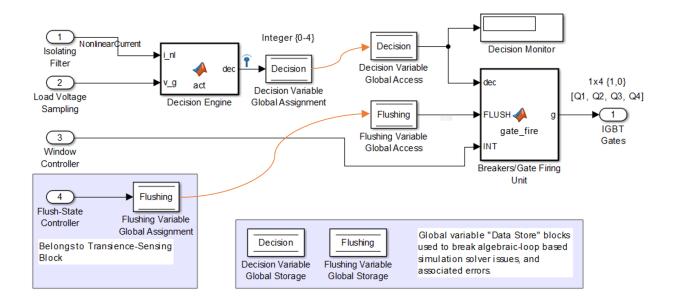

| Figure 41: Simulation Implementation of Decision-Making and Gate-Signal Generation and Control Units         | _ 55 |

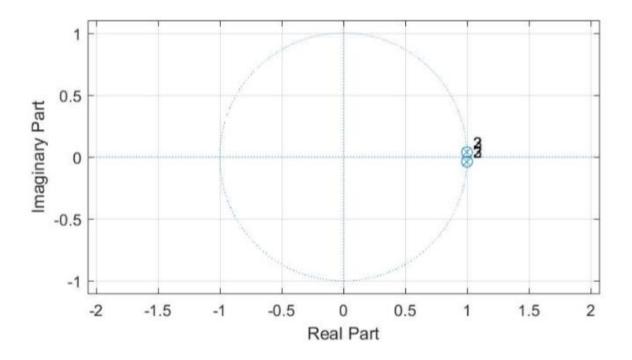

| Figure 42: Pole-Zero Plot of Nonlinear Current Isolation Filter                                              | _ 59 |

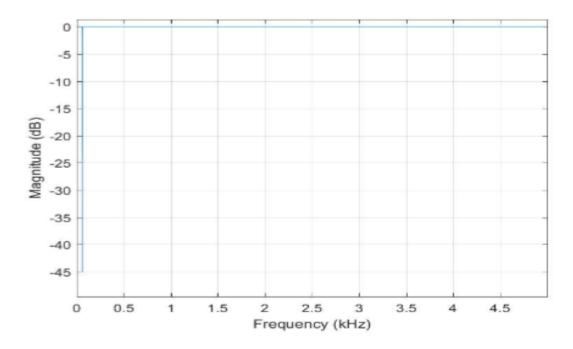

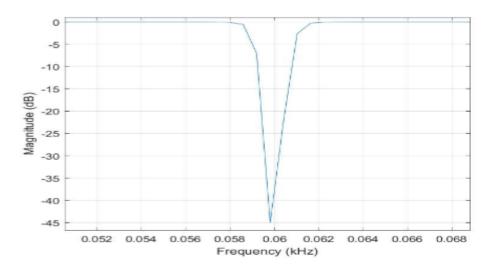

| Figure 43:Magnitude Response of Nonlinear Current Isolation Filter                                           | _ 60 |

| Figure 44: Detailed View of Magnitude Notch in Nonlinear Current Isolation Filer                             | _ 60 |

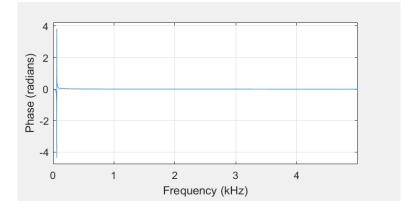

| Figure 45: Phase Response of Nonlinear Current Isolation Filter                                 | 61 |

|-------------------------------------------------------------------------------------------------|----|

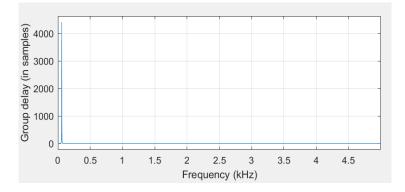

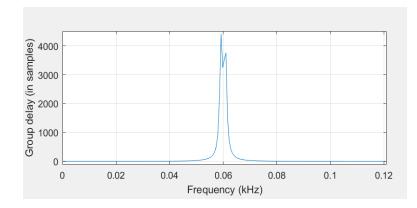

| Figure 46: Group Delay of Nonlinear Current Isolation Filter                                    | 61 |

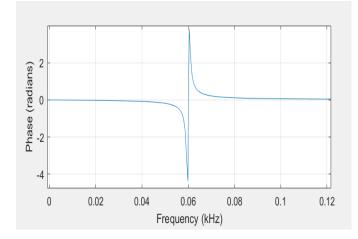

| Figure 47: Phase Response of Nonlinear Current Isolating Filter Scaled to Show Distortion Range | 62 |

| Figure 48: Group Delay of Nonlinear Current Isolating Filter Scaled to Show Distortion Range    | 63 |

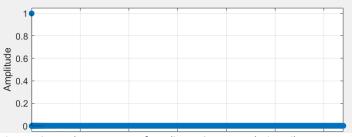

| Figure 49:Impulse Response of Nonlinear Current Isolating Filter                                | 64 |

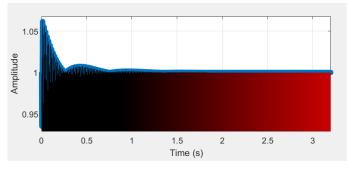

| Figure 50: Step Response of Nonlinear Current Isolating Filter                                  | 65 |

| Figure 51: Proposed Physical Implementation of Window Monitoring and Control                    | 67 |

| Figure 52: Proposed Implementation of Analog Compensator Current Preprocessing                  | 68 |

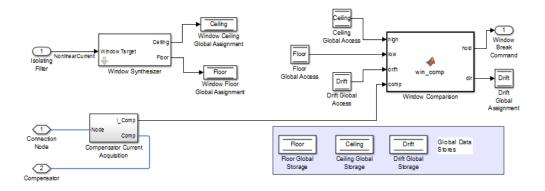

| Figure 53: Simulation Model for Window Synthesiizer                                             | 69 |

| Figure 54:Window Synthesizer Block Parameters Mask                                              | 69 |

| Figure 55: Simulation Diagram of Compensator Current Acquisition Block                          | 70 |

| Figure 56: Final Simulation Window Comparator Control Diagram                                   | 71 |

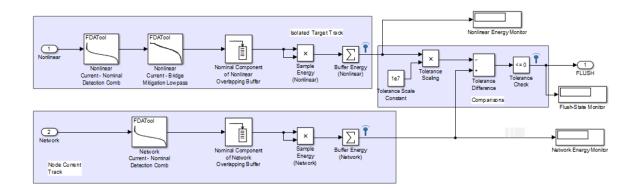

| Figure 57: Flush-State Controller Diagram                                                       | 73 |

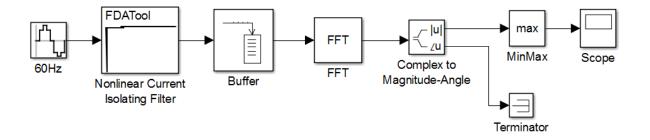

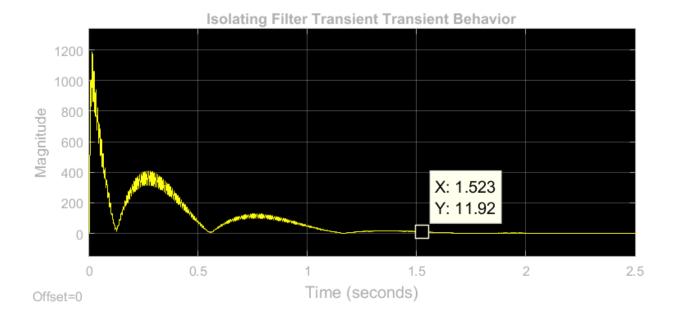

| Figure 58: Simulation Diagram for Isolating-Filter Relevant Transient Response                  | 75 |

| Figure 59: 60Hz Transient Adjustment Period for Isolating Filter                                |    |

| Figure 60: Simulation Diagram of H-Bridge Transience Experiment                                 | 76 |

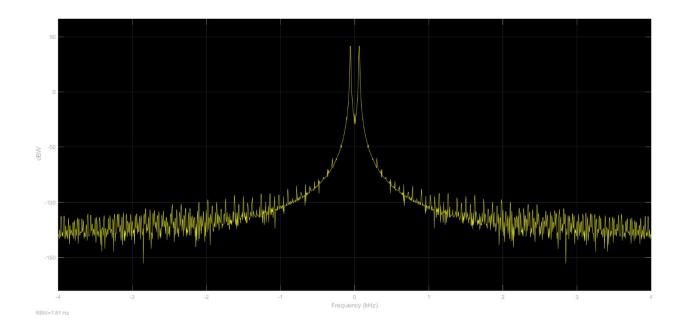

| Figure 61: Spectrum of H-Bridge Switching Transience Experiment                                 | 77 |

| Figure 62: Grid Current in H-Bridge Switching Transience Experiment                             | 78 |

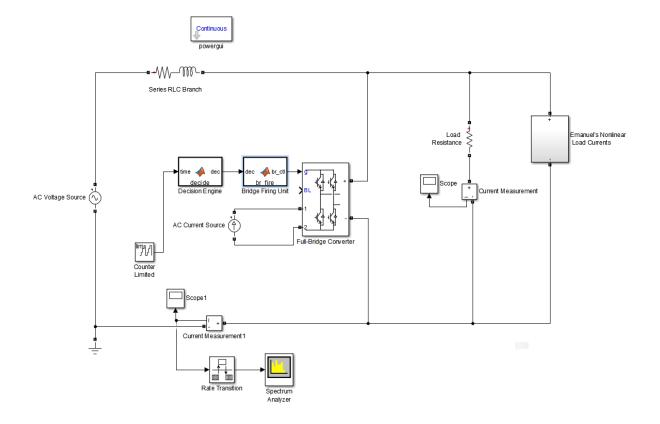

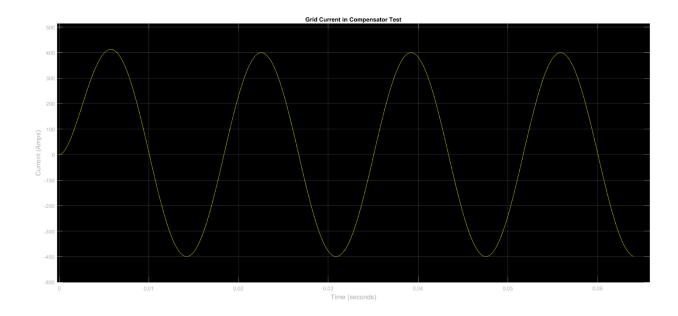

| Figure 63:Final Compensator Simulation Diagram With Monitoring Configuration                    |    |

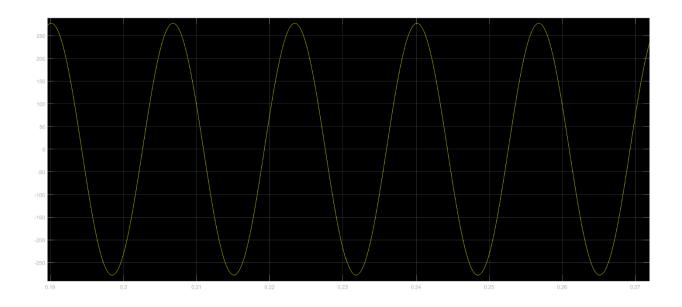

| Figure 64:Startup Grid Current with Provided Model and Final Compensator Design                 |    |

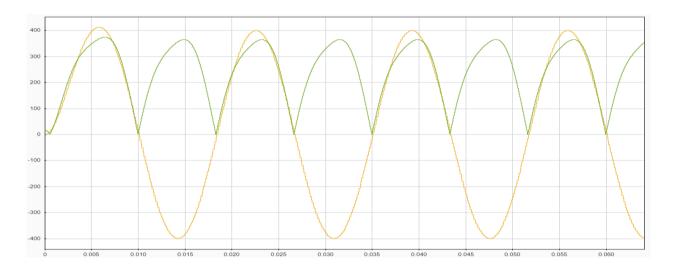

| Figure 65: Comparison of Grid Current and the Compensator's Delivered Current                   |    |

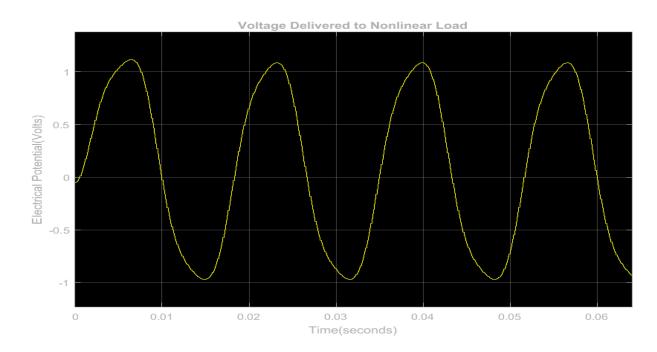

| Figure 66: Load Voltage in Simulation of Final Compensator with Provided Test Model             |    |

| Figure 67: Load Voltage and Connection Impedance Voltage Drop                                   |    |

| Figure 68: Outlining the critical error in the (Almost) Final Compensator                       | 84 |

| Figure 69: Final Compensator Simulation Diagram                                                 |    |

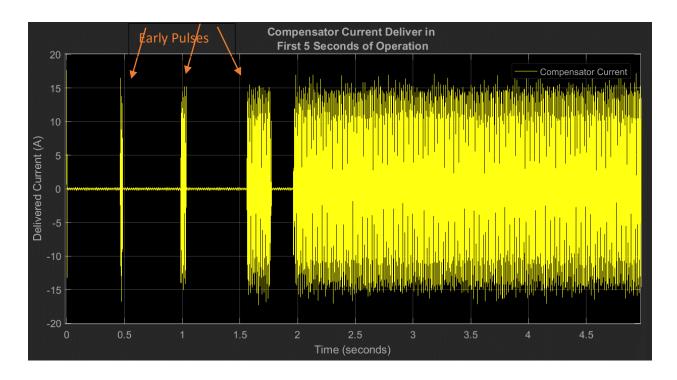

| Figure 70: Compensator Current from 0 to 5 Seconds, Early Pulses Indicated                      |    |

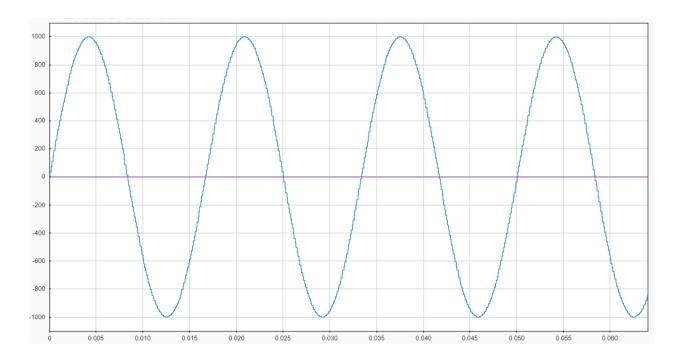

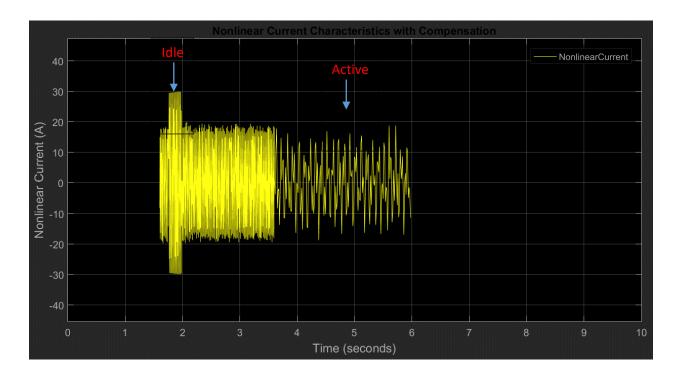

| Figure 71:Nonlinear Current of Most Recent Simulation under Compensator Operation               |    |

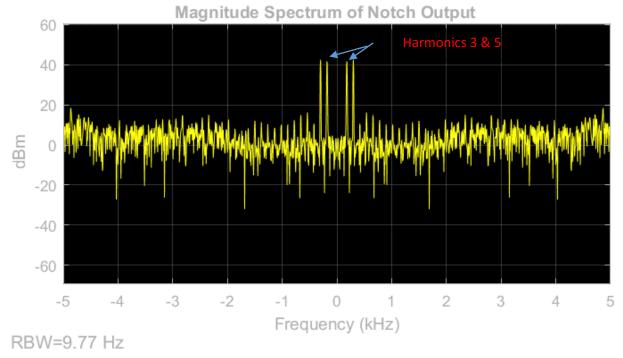

| Figure 72:Magnitude Spectrum of Nonlinear Current                                               |    |

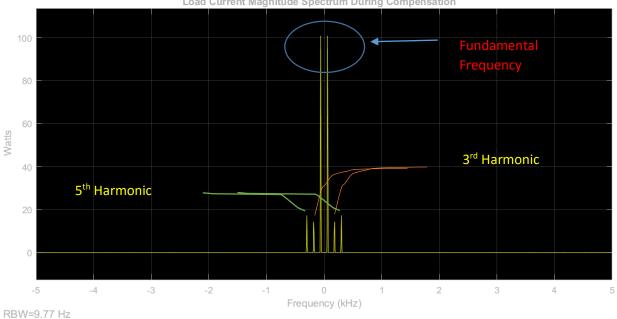

| Figure 73: Linear Scaling of Harmonic Magnitudes in Load Current During Compensation            | 88 |

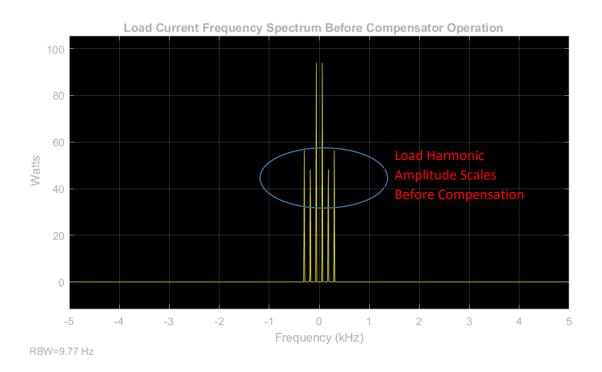

| Figure 74: Load Current Linear Magnitude Spectrum Prior to Compensator Operation                |    |

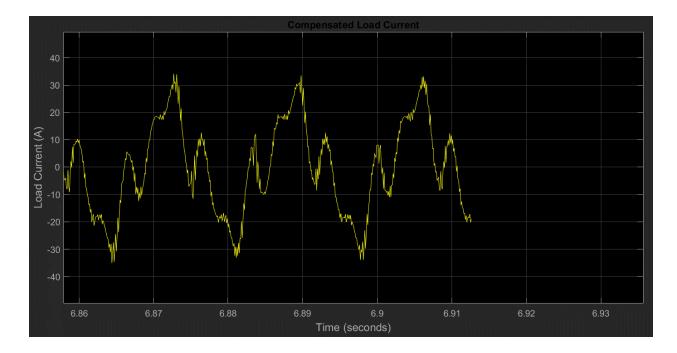

| Figure 75: Compensated Load Current                                                             |    |

| Figure 76: Simulation Diagram for Nonlinear Load Demo                                           |    |

|                                                                                                 |    |

# List of Tables

| Table 1 : Sliding Rules for Active Gate Impulse Dependency on Network Power States [4] | 4  |

|----------------------------------------------------------------------------------------|----|

| Table 2: Decision State Integer Handles and Descriptions                               | 52 |

| Table 3 Gate Encoding for Each Implemented Decision:                                   | 53 |

### **Executive Summary**

This project strives to improve power quality in a power distribution network, one user at a time. One measure of the quality of power is the degree to which harmonics are present. As harmonic currents may propagate throughout a network and cause harmful effects at neighboring nodes. [1]

The target behavior of the process designed in this project is to eliminate nonlinear current by superimposing the inverse waveforms of each harmonic into the current being returned to the network from the load. Instead of a physical device, the process was modelled in Simulink. This enabled more-idealized development of the device while maintaining certain physical behaviors modelled to be realistic.

The process proposed within, and implemented in Simulink, involves sampling of the current in, and voltage applied to the load. An H-Bridge configuration of four IGBTs was provided to be used as a power delivery mechanism, switching in different configurations, or states, left to the designer to find and implement, along with a model for a power distribution network paired with a model for a nonlinear load, constructed of ideal current sources. Around these two mechanisms and the provided model for the device's environment, instructions were provided to create a mixed-signal system to counteract all harmonics produced by the load to counteract, or deliver the inverse or 180°-shifted copy of those harmonics (all are equivalent), to prevent their propagation and protect other nodes in the network from absorbing them.

The proposed design has not yet been proven as effective as it should be, but highlights a relatively novel approach due to its foundation in mixed-signal processing. While it likely requires adjustment in the parameters of the physical systems comprising the device, is expected to enjoy the advantages of near-agnosticism relative to the nonlinear load, and its produced harmonics, over many other active processes currently existing. With relation to passive equivalents, such as RLC filters, power-loss is less extreme, and the as impedance is variable with respect to voltage, is less vulnerable to issues of

resonance.

### 1 Introduction

In recent decades, new nonlinear loads in power delivery networks have proliferated at a rapid rate, where they used to be primarily found in heavy requirement and industrial settings. Nonlinear loads are those whose power requirements or characteristics vary with time, or those that exhibit impedances that are non-constant with regard to applied voltage. They have become ubiquitous within modern life, and the average user of power networks likely has numerous devices that, in various contexts, serve as nonlinear loads.

Linear components include, primarily, resistances, capacitances, and inductances. But the defining circuit elements of electronics, in both consumer devices, and others, are now semiconducting components such as diodes and transistors which enable digital technology. As this report is being written, in addition to many other relevant devices, the author has both a laptop computer and a smart-phone charging on this very desk, which make extensive use of semiconductor switching technology. With the direct-current charging requirements for these devices, power must be supplied by a rectifier circuit, which also exhibits nonlinear voltage-current characteristics.

The trend towards semiconductor switching and digital technologies shares the responsibility for increase in harmonic generation in power networks with other phenomena such as the move to clean energy sources, which can also introduce a need for harmonic compensation. Connection of photovoltaic power production often requires DC-AC inverters. Harmonic currents generated by nonlinear loads can cause losses in devices that utilize ferromagnetic cores or electromagnetic induction to store or transfer energy, such as inductors, transformers and generators [2] [3]. Magnetic-core devices and impedance of conductors, due to the skin effect<sup>1</sup> suffer greater consequences of harmonic power, the primary culprits are rectifier loads whose leads are crossed with smoothing pulse. AC-to-DC charging devices now frequently include power electronic elements drawing directly from the network, like the common SMPS<sup>2</sup>, like that in Figure 1. [4] [5]

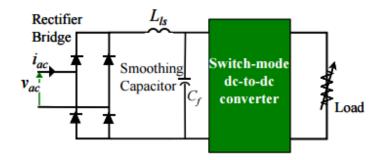

#### Figure 1: SMPS Nonlinear Load [4]

The smoothing capacitor exacerbates the situation. It stores energy to smooth the transition between half-waves, usually meaning at least two charge-discharge cycles per period of the fundamental frequency. During the charging portion of the cycle, the SMPS absorbs some current to charge the capacitor for shorter an interval than the period of the waveform. This misshapes the waveform, imposing current dips when the capacitor charges. As these dips occur periodically, and at a frequency exceeding that of the network, they may be represented as a higher frequency waveform superimposed on the pure alternating current signal. [4] [6]

<sup>&</sup>lt;sup>1</sup> The phenomenon of increased current density towards the outer boundaries of the conductor, packing greater like-charge density into a narrower cross-section, increasing power losses and thus impedance.

<sup>&</sup>lt;sup>2</sup> Switch-Mode Power Supply

Figure 2: Example Current Waveform for a 6-Pulse Rectifier [7]

This work is intended to provide a method by which the harmful effects of nonlinear loads in such a network may be corrected on the user-side. This is beneficial, not to just the power companies who might suffer efficiency problems as a result, and not just to neighboring users who may suffer issues rooted in the concept of resonance at certain current frequencies, but the users themselves, who might responsibly compensate for their own nonlinear loads or reintroduction of power back into the grid.

Other models attempting active-compensation in single-phase power distribution networks do exist, but for the most part appear to differ from the proposed implementation in a few key details. These details vary from system-to-system, they are not static industry-wide, suggesting a dynamic area of the field, still being explored, and with much room for experimentation with new approaches.

Instead of compensation at the load's connections, one model targets a centralized-node. The bridge-converter, operated in a "Sliding-Mode" control pattern, similar to that used in the design produced by this project. Applicable transistor gate impulses are given as the result of a logical determination, which follows the sensed current and voltage signals, presented in Table 1 far more eloquently than was achieved within this document, but presented in a manner stipulated on exclusion of certain circuit states not occurring naturally within the network. Further key differences include a

pulse-width modulation pattern driving the active gates. The duty-cycle is the result of a calculation involving attributes of physical components, namely a supply capacitor (implemented as a DC voltage supply in this design) and a lowpass RL filter, or rather just an inductor, to smooth sharp transitions and extend their transition times. [8]

|   |            | i | , < kv,            | is > kvs  |

|---|------------|---|--------------------|-----------|

|   | <b>u</b> 1 |   | 0                  | 1         |

| 1 | 42         |   | 1                  | 0         |

| ī |            |   |                    | , <u></u> |

|   |            |   | v <sub>s</sub> < 0 | v., > 0   |

|   | U;         | 3 | 1                  | 0         |

|   | u.         | 4 | 0                  | 1         |

Table 1 : Sliding Rules for Active Gate Impulse Dependency on Network Power States [8]

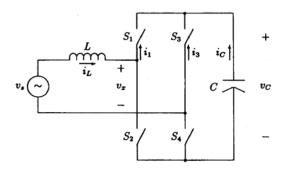

Figure 3: Single-Phase Inverter Implementation of Compensator, Applied at a Central Node [8]

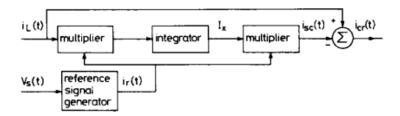

Another model, using a single-phase IGBT bridge converter, prefers a more signals theory based approach, and successfully implements an approach towards nonlinear current separation once attempted in this project due to the utter-lack of phase effects involved. By reconstructing a waveform representation of the fundamental frequency component of the signal, this waveform might be subtracted from the network's electrical current signal, and effective isolate the nonlinearities with zero phase-shift and unity gain at other frequencies. This well-obtained current is however also delivered with a PWM pattern, with a duty cycle determined by a PI controller. [9]

Figure 4: Compensator's Fundamental Frequency Reconstruction Diagram Using Power Calculations and Energy Detection [9]

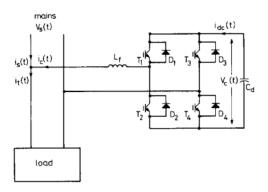

Figure 5: Power Circuit Shown with Waveform Reconstruction Compensator [9]

#### 1.1 Proposed Solutions

The proposed solution may be broken down into three major components: Analog Pre-Processing, the Digital Processing and Controls Unit, and the Power Delivery System. The Analog Pre-Processing Unit exists to provide the Digital Processing and Controls with information on the relevant information regarding the network's operation at a given moment. The Digital Processing and Controls Unit is included to take the information from Analog Pre-Processing, separate desired behaviors from undesired behaviors, and turn these into the controlling impulses for operation of the Power Delivery Unit. The Power Delivery Unit takes these firing impulses, and from them delivers the power necessary to correct network behaviors.

#### 1.1.1 Analog Pre-Processing

Given that the yield of this project is intended as a supporting simulation, this unit has been paid the least attention. Simulation software provides the means with which to work around this unit's necessity, and the absence of physical reality in this instance has very limited consequence to the process as a whole.

If simplified, more abstract, means for this functionality exists in simulation, full-advantage was to be taken until the process itself could be refined. With use of the Simscape Power Systems library, which possesses its own current measurement block, design of these components proved unnecessary.

Refined, more realistic implementation, is intended to have two primary processes involved. First, some indication of the current being fed between the greater network and the load must be obtained. This is done, first, through a current transformer. Current transformers obtain the current metric through electromagnetic induction, with a strong inverse-gain. As they are not connected in-line, they are essentially lossless. [1011]

As the output of the current transformer which encapsulates the desired information is a current and not a voltage, yet information may only be captured for digital processing purposes as a voltage, a component is required to transform this current into a voltage. This component is a current-sense amplifier. If the first stage of Analog Pre-Processing exhibits behaviors of a current-source, the voltage across a conductor of known resistance is going to be proportional to the currents produced by the network and nonlinear load. Thus a difference amplifier connected across a known resistance helps accurately and safely transform this current signal into a voltage that may be sampled by an Analog-to-Digital Converter.

Sampling Theory mandates that amplitude is not the only variable important in moving a waveform into the digital domain. Frequency is critical to the process as well, and for accurate control,

the signal must be effectively band-limited to half of the sampling rate. In other terms, the largest frequency to be sampled must be half of the frequency at which the ADC captures samples. If, at installation, one cannot ensure that the highest persistent frequency present does not meet these constraints, a lowpass filter must be installed. It is recommended that such a filter be active, as opposed to passive, to mitigate loss in a low-power environment. It is critical that the phase-response of this filter be easily modelled or approximated, and that the group delay of the filter be small for precise, accurate, and rapidly responding compensation. To this end, a low-order Bessel filter is recommended due to its maximally flat phase-response.

#### 1.1.2 Digital Processing and Control

This is the most complicated and sensitive unit in the design. Requirements for its operation dictate that the firing impulse outputs accurately reflect the relevant information in the input waveform, with limited delay. As a result, preservation and protection of phase information are an enormous concern, as the potential exists for the waveform to be significantly reshaped in the midst of phase-affective processes.

The first stage in any digital unit that makes decisions based on real-world continuous information must always be sampling, the collection of this data. Done via an Analog-to-Digital Converter (ADC), this captures values of the waveform at fixed-interval time instances at a pace called the *sampling rate*. It is theoretically possible to sample a waveform, under certain conditions, so that it can be perfectly reconstructed. These conditions, outlined in the Sampling Theory section, dictate that the sampling rate must be at least twice the maximum-supported frequency, and that no higher frequencies should exist, in significant quantities, above this.

The next step in solving this problem is waveform isolation, achieved by isolating the nonlinear current. This can be done subtractively, if the amplitude and phase of the network's nominal-frequency

current are expected to be constant, where a fixed sinusoidal waveform is used as a reference to be subtracted from the read current. If variations are expected, and very narrow bandpass filter with equalization for the group delay can be implemented. This has the benefit of a narrow phase distortion at frequencies intended for elimination anyways, and a less generalized phase-correction technique. Alternatively, if a sufficiently narrow phase response can be achieved in a notch filter, this can be exploited to remove the nominal frequency, and isolate the elements introduced by the nonlinear load, although one must pay careful attention to the phase response to be sure that phase-distortion is not reshaping the wave to any significant degree.

As filters exhibit transient responses, one must be careful to ensure that one is not injecting transient information into the feedback loop. Testing has shown that memory of the 60Hz signal can be retained in the filter and feedback loop, when operating in transience, in such a manner that the device never ceases to attempt to compensate not just for nonlinear patterns, but for the nominal-frequency as well. Proposed solutions for this include a "flush-state" break in the loop, where compensation is idled while the transient information is flushed out of the system. This would be implemented as an energy detector, placed after waveform isolation, that would assess the presence of the nominal frequency in the output signal, and disconnect compensation until this presence is reduced to tolerably low levels.

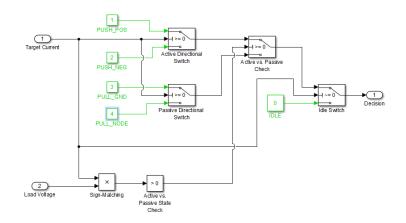

The second to last block is the "decision engine" where all determinations regarding the state of the Power Delivery apparatus are performed. Numerous such states must exist in order to achieve practically lossless compensation to a high degree of precision. Such a block must make such decisions off of a number of indicators including voltage in the grid (if it is in the wrong direction, current may be delivered in the wrong direction as well), and the current it intends to deliver. Furthermore, due to the highly sensitive and transient nature of the Power Delivery apparatus, to be seen, requires a greater real-time determination to determine if the bounds have been surpassed, upon which it must idle the compensator.

Finally, once the decisions have been determined, the final block is the "gate-firing unit", which from each state-decision, generates a series of firing impulses that will control the physical Power Delivery unit.

#### 1.1.3 Power Delivery

As the ability to drive negative and positive current to the grid are essential for the application, an H-Bridge configuration seems an obvious choice. This portion of the document cannot effectively address the operation of this solution sufficiently considering the uncommon states with which the Hbridge is to be driven, these methods are addressed in the Background Information chapter.

Several useful states have been identified, including one that connects a power supply in the same direction as the grid's reference polarity "push +", in the opposite direction "push –", and one in which no power is delivered or sunk, "idle". The novel implementation in this design are the identification of two bridge configurations each, for two rarely seen actions. Each action is a polarity-sensitive short-circuit, where direct passage of current from the power rail of the network, to ground, are enabled. The states in which the bridge allows passage from the rail to ground are "pull –", and the states allowing passage of current from ground to the rail are "pull +".

Given the high-power nature of this environment, implementation of this grid is too taxing on most semiconductor devices. Thus, the H-bridge configuration uses IGBT/Diode pairs.

## 2 Background Information

#### 2.1 Signal-Processing Theory

#### 2.1.1 Waveform Parameters

The basic waveforms of signals theory, and the basic units of analysis in this project, are composed of the periodic sine and cosine functions. For a proper understanding of the concepts active in this work, one must understand the non-atomic variables used in the analysis of the controlled variable. For the purposes of this work, we describe the fundamental units of the controlled variable to each exist as parameters of "cosine" functions. The parameters which all periodic functions have in common, each entirely independent of the others, are thus: amplitude, frequency, and phase. These parameters' fit into a waveform are represented in the following mathematical model:

$$y(t) = A \times \cos(2\pi \times f \times t + \phi).$$

<sup>(1)</sup>

In this model, amplitude is represented as A, frequency as f (often represented as angular frequency,  $\omega$ ), and phase as  $\phi$ . Each affects the specifications of the wave, but to fully realize how, one must first know the base specification of the waveform in question, modelled as the cosine periodic function.

The most basic form of the cosine function, stripped of all parameters to their unit equivalents, is represented in the following mathematical model:

$$y_{basic}(t) = \cos(t). \tag{2}$$

These parameters evaluate, for reference, to amplitude A = 1, angular frequency  $\omega = 1$ , and phase  $\phi = 0$ .

As might be observed, the range of this function is from 1 to its negative. One cycle, or *period* is measured from peak to same-peak, i.e. from  $y(t_0) = 1$ , to  $y(t_1) = 1$ , where  $t_0 < t_1$ . As the wave is *periodic* (repeats), the waveform over one period  $T = t_1 - t_0$  will be identical to that over any other period, measured at the same *phase* (details to follow), in the cycle. The period of the basic cosine form is  $T = 2\pi$ .

The first parameter examined here is *amplitude*. The amplitude parameter is represented as *A* in the generalized cosine function representation.

One observes that adjusting the amplitude parameter scales the value of the waveform, at all time instances, proportionally to the magnitude of the parameter's change. As previously mentioned, the amplitude of the most basic cosine function, cos(t), is 1. Thus in-phase cosines of the same frequency, with amplitude values A = 2 and A = 0.5 respectively double and halve each value of the waveform.

As seen subsequently in the section on superposition and the Fourier Transforms, amplitude is valuable to signal analysis as this is the parameter responsible for the energy or the prominence of a signal component, and ultimately informs the shape of more complex waveforms for which certain analyses are desired within the scope of this project.

More complex signals are commonly analyzed and manipulated in the frequency domain, rather than the time-domain format, more common in most other applications. The *frequency* parameter, denoted as f in the basic cosine function, denotes how many periods of the cosine exist per unit time.

Frequency adjustment is akin to a time-scaling operation. For a single cosine waveform, the two operations are synonymous. The period of a waveform, as mentioned earlier where the period of the basic cosine function was given as  $T = 2\pi$ , is related to waveform frequency by  $f = \frac{1}{T}$ . If one cycle occurs per second, the period is one second. If two occur, the period is half a second. Continued exploration of behavior reveals that the inverse-proportional behavior holds, and no other information exists in the relation.

Frequency information may be expressed in either Hertz (Hz, inverse seconds) or in radians per second, as an angular velocity,  $\omega = 2\pi f$ . Multiples of a given frequency of interest are referred to as *harmonics*. In the above frequency demonstration plot, the double-frequency wave is the 2<sup>nd</sup> harmonic, which is in turn such to the half-frequency wave.

There exist two special cases of the cosine function that are exhibited with frequency, at those points where either f and  $\omega$ , or their limits, converge. The first occurs at  $f = \omega = 0$ , where no oscillation occurs. We derive the formula for this case from that of the generalized cosine function, yielding:  $y_0 = A \times \cos(\phi)$ , a constant dependent upon the other two parameters, also known as the DC (from electrical engineering's "direct current") case. The second exists at  $\lim_{f \to \infty} \omega = \infty$ . This case is physically impossible to achieve (at least in the context of this project) as the waveform value, unlike a mathematical function, does not possess a singular value for every instance in time, yet persistently exhibits two constant values.

The third parameter, *phase*, is often considered rather more of a nuisance than the other two which provide solid means of analysis and manipulation. In much of signals processing, phase exists as a non-ideal reality, more to be matched or corrected for than to be used to one's advantage.

Subtractive phase-shifting makes a wave occur earlier in time, and additive shifting delays its occurrence, respectively called *lag* and *lead*. Phase can be expressed in angular degrees, radians, an in

rare occasions may even be represented in units of time. Phase-shift is also the relational operator between the sine function, cosine, and each of their negative, where cosine is a copy of sine with a lag of 90 degrees, or  $\frac{\pi}{2}$  rad. Finally, the negative of any periodic function, with a bias (average value) of zero, is a copy of itself, either lead or lagged (equivalent in this case and the identity case) by 180 degrees, or  $\pi$  rad.

#### 2.1.2 Waveform Superposition

The principle of *superposition* states that the result of the presence of two independent sources in a linear system results in the algebraic sum of those sources. Sinusoidal waveforms are, mathematically, linear functions, and thus the effects sinusoidal sources superimpose to define the behavior of the system.

In the time domain, this is perhaps most visible using two waveforms with a high order of magnitude difference in frequency, with the lower frequency waveform possessing a far greater amplitude. We might think of this as a noise-interference introduced to a desired signal.

Figure 6:Illustration of the Superposition Principle

A copy of the noise waveform oscillates around the signal as if it were using the signal as its own private time axis (which it is). Some variation on the wave "Observed" will result in any linear system in which multiple waves of different frequencies are present.

#### 2.1.3 Continuous-Time, Discrete-Time, and Digital Signals

A continuous-time signal is represented as a mathematical function defined for every realvalued time instance. A discrete-time signal may exist for any full-continuum range of values, but is only defined for fixed-integer discrete-time values in the domain. A digital signal, like a discrete signal, is only defined for a number of fixed-integer indices, but may only have a finite set of values.

Suppose a signal x is to be sampled over fixed length intervals to yield the sampled signal  $x_s$ . There exists a difference in how these two signals are annotated. The continuous-time original is written as x(t), whereas the sampled copy is  $x_s[n]$ . The index, n, may only possess integer values. For instance,  $x_s[1.3]$  is, by definition, undefined.

The unit-impulse function,  $\delta(t)$  (continuous time) or  $\delta[n]$  is used to model significant events, which occur over very short periods of time. For both continuous or discrete-time models of the function, non-zero value only occurs when its parameter is zero.

The impulse function can be easily delayed and scaled in a manner shown in the following equation, and can be seen for c = 5 and  $n_0 = 2$  in the subsequent demonstration plot.

$$c \times \delta[n - n_0] = \begin{cases} c, & n = n_0 \\ 0, & t \neq 0 \end{cases}$$

(3)

Figure 7:Behaviors of the Impulse Function

The unit step function models a square-step transition:

$$u(t) = \begin{cases} 1, & t > 0\\ 1/2, & t = 0.\\ 0, & t < 0 \end{cases}$$

(4)

It scales and time-shifts just as the unit-impulse function and is used to model the introduction of new information to a system. By multiplying another function by the unit-step, and shifting both function appropriately in time, one can dictate when the function appears.

#### 2.1.4 Complex Magnitude and Phase, and Euler's Identity

Complex numbers are those numbers of the form:

$$c = a + j \cdot b \tag{5}$$

This relation is labelled complex as it contains the *imaginary number*:

$$j = \sqrt{-1} \tag{6}$$

Such a value is said to exist in the *complex plane*, in which the vertical axis is the real-part of the value a, and the horizontal is the scale of the imaginary part b. The representation above is a

rectangular coordinate, but like any value on a two-dimensional plane, it has a polar representation as well, containing the value's magnitude, ||c|| = r, and phase  $\angle c = \theta$ , (length of vector from the origin to the value, and the angle between the vector and the positive x-axis.)

$$c = r(\sin\theta + j\sin\theta) \tag{7}$$

By introducing *Euler's Formula*, one allows for an even simpler representation of complex numbers. Euler's formula and its application to the task at hand are as follows:

$$e^{j\theta} = \cos\theta + j\sin\theta \tag{8}$$

$$c = r e^{j\theta} \tag{9}$$

This representation of complex numbers informs the ability to be able to transform a set of time-domain information into the complex-plane in a manner reflecting any periodicities present. For each value in the range of the function, there is an associated magnitude and phase. As the periodicities are accounted for, this concept enables a view of mathematical functions as super-positions of sinusoids, and the parameters each carries.

#### 2.1.5 Complex-Frequency Domain

Building on the principle of superposition, one posits that, as a continuum of frequency values exist, that any mathematical function may be expressed as a superposition with varying parameters. The mathematical concept resulting from this line of research is the *Fourier Transform* of a mathematical function, and happens to lead the user through the complex plane. As a representation for complex numbers exists, with a dependency upon the magnitude and phase of its Euler's representation, a single-frequency waveform's magnitude and phase are encoded as a complex number and each waveform in a superposition is represented as a continuum of such numbers, each assigned to the corresponding point on the frequency continuum.

#### 2.2 Circuit Theory

As the motivation for this project is to design a process able to compensate, in physical circuits, in physical currents. Given the high-power demands at output, digital control of a DAC will not suffice. The process must be able to measure large-analog currents, and prepare it to be sampled by an ADC. At output, a configuration of eight semiconductors must be supplied with power, which is to be delivered to the network through proper control of this bridge converter.

#### 2.2.1 Loads

If an electrical system is not intended for information and signal processing and analysis, be it either sensory or manipulative, then this system has a *load*. The load is the system's raison d'être. It is the intended target for electrical energy or power in the system, where the remainder of the system exists to cater its power delivery to the specifications required by the load, at a given moment in time, to match the most practical level of efficiency and operational requirements. A prime example is the battery in a mobile phone, for which there are AC-DC conversion systems to turn the available power into that most useful to charge the battery. Other common examples include lights, motors, and heating elements.

Introductory circuit theory largely focuses on linear components, such as resistors, capacitors, and inductors. The shared attribute of these components that makes them linear, is a constant impedance regardless of the supply characteristics.

In electrical engineering, a *linear load* is defined<sup>3</sup> as an electrical load exhibiting an impedance independent of applied voltage [10]. As impedance is frequency dependent, this implies that the

<sup>&</sup>lt;sup>3</sup> Defined inversely from the definition of non-linear load in the cited MIRUS International, Inc. document

current passed by a circuit branch consisting of a linear load will contain only frequency elements present in the voltage applied.

Inversely, a *nonlinear load* is defined as an electrical load for which "impedance changes with applied voltage" [10]. As such, these loads cannot, in theory, be accurately represented by impedance phasors, or any series-parallel configuration of such mathematical models that would otherwise enable introductory AC circuit analysis techniques.

Figure 8: Circuit Diagram for Nonlinear Load Demo

There exist wide varieties of nonlinear loads, with wild variation between their behaviors, or characteristics. An early-taught nonlinear element, the diode, makes an acceptable and accessible example. Tutorial information for this device is provided in a closely subsequent section devoted to their behaviors, within their own passages in the Simple Semiconductors tutorial segment. The load's current and voltage are related in manners that are not expressible as fading or phase-shifting of existing frequency components.

Figure 9: Simulated Voltage Drop and Current of an Exponential Diode Load

The example simulation results provide intuitive ability to directly tie the concepts of nonlinear loads and *linearity* (whether scaled and time-shifted inputs yield proportionally scaled and identically time-shifted outputs). If this were a linear load at the simulated steady-state, a purely sinusoidal 60Hz load would produce a purely 60Hz sinusoidal load current with affected magnitude and phase.

Figure 10: Nonlinear Load Demo Frequency Domain

Linearity implies that frequency components in the current could only exist where there were frequency components in the load voltage. One can observe from Figure 10 that the load current contains five prominent frequency components at, not just 60Hz, but at 0, 120, 240Hz, 360Hz, and 420Hz. Given the 60Hz applied voltage, this translates to the 0<sup>th</sup>, 1<sup>st</sup>, 2<sup>nd</sup>, 4<sup>th</sup>, and 6<sup>th</sup> harmonic incident in the load current. This document often refers to *nonlinear current*, which is, in the scope of this document, to current signal of all components excluding the 1<sup>st</sup> harmonic.

#### 2.2.2 Simple Semiconductors

Diodes exhibit a couple of useful behaviors relevant to the scope of this project. These twoterminal devices are composed of doped semi-conductors that grant it a monopolar electrical operation. The two terminals are referred to as the "anode" and the "cathode". The anode is connected to a chip composed of a semiconducting material, such as silicon, chemically altered, or "doped", to be of the "ptype". The semiconducting chip at the cathode is doped to be "n-type", and these chips are directly joined in series.

Because of the electrical properties introduced through the chemical doping process, electrical current may only flow in one direction through the diode's ""pn-junction", from the anode to the cathode. This gives the diode a very useful application as a sort of one-way valve. It is useful in rectification processes, where current may only be allowed to flow in one direction. AC-DC converters commonly found in laptop, phone, or other battery charging devices make use of a configuration of two diodes to project the negative half of an alternating-current waveform into positive current, so as to effectively output the absolute value of the electrical current and voltage waveforms.

Due to the electrical properties of the junction, there is some distortion in this rectification process that is relevant to operation. There is a voltage threshold in the positive region that must be met for the diode to become active. This pattern is more continuous than suggested, with a more complex exponential mathematical model where any "forward-bias" voltage does increase current flow, significant current flow only occurs one the forward-bias voltage inhabits the neighborhood of 700mV. Due to exponential dependency the current displays with relation to the biasing voltage, even very large currents correspond to a bias-voltage of little over this 700mV threshold, making them an effective voltage-limiter even in forward bias.

Where diodes act as directional valves for current and set a stable voltage drop when correctly biased, devices called *transistors* build upon this behavior, combining doped junctions to exhibit certain circuit behaviors. Like diodes, current may only pass in one direction through a transistor's *channel*, the path between the two pins (called the *drain* and *source* in FETs, and emitter and base in others.

Unlike diodes, transistors possess a third pin used for control of the device. Electrical signals at this pin control how much current may pass through this channel. Different transistors use different

mechanisms to implement this pin. For some, transistor operation is more dependent upon the current at this pin (usually called the *base* in such cases). For others, such as those relying on more capacitive behavior at this pin (called the *gate* for these devices), voltage is more determinant.

One of the primary applications of transistors is *switching*, or allowing and restricting the passage of larger current with a low-powered signal. Gated transistors are commonly used for switching

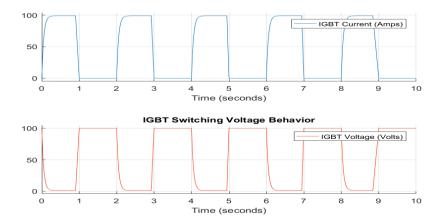

applications due to desirable switching speeds. For this demo, an *insulated-gate bipolar transitor*, or IGBT, is used to demonstrate switching. The Specialized Technology in SimPowerSystems is used, and instead of being fed a real voltage at

Figure 11: Simscape Power Systems "Specialized Technology" IGBT its gate, is activated by a Simulink signal of '1', and turned off at a Simulink signal of '0'.

Figure 12: IGBT Switching Demo Circuit Diagram

The IGBT's three terminals are the gate, the collector, and the emitter, labeled "g", "C", and "E",

respectively<sup>4</sup>. The collector and emitter are the terminals to this device's channel. For the n-type transistor shown above, significant current may only flow from the collector to emitter. For this block,

<sup>&</sup>lt;sup>4</sup> The fourth terminal, "m", shown is simply a carrier of monitoring and logging data. This has no bearing on its electrical behavior, but provides an easy read-only handle on the voltage drop across- and current through the channel.

current is permitted easy passage if, and only if, a "1" is sent to the gate. By this method, electrical voltage may be restricted or given a path by a controller signal as seen in the demo.

This enables a system to control the average power delivered to a load, in this case the resistance. Lower power analog and digital systems alike commonly take advantage of this with the *pulse-width modulation* (PWM) technique. Pulse-width modulation entails a periodic square-wave pulse where the pulse-width, the time for which the transistor's channel enables the passage of current, is handled as a percentage of the square wave's period.

$$duty \ cycle = \frac{t_{on}}{t_{on} + t_{off}} \times 100\% = \frac{t_{on}}{T} \times 100\%$$

(10)

Figure 13:IGBT Switching Current and Voltage Behaviors

The demo shows a 50% duty cycle with a period of two seconds. When the channel is closed, a high voltage drop is exhibited across the collector and emitter of the device. As it opens, its effective resistance decreases rapidly and the voltage across the channel drops sharply as an electrical current rushes through what is now effectively a small resistor. The parameters of the IGBT used in the demo have been altered to exaggerate a behavior of interest to this project. Notice the transition times, for

both current and voltage, are finite and non-zero. The capacitive gate takes some time to charge. Thus the channel sweeps through varying degrees of "open" after the moment of switching.

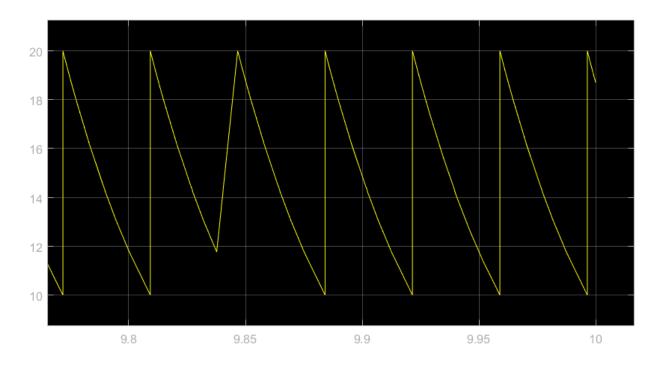

This behavior allows, if a sufficiently fast mechanism can be achieved for current monitoring purposes, the capacity for control to keep it within a determined range. The demo can be altered to never allow the passage of more than a certain threshold. By measuring the current, determining if it is less than or equal to 10A, and performing a logical and with a constant 1 for reference, one achieves the current waveform in Figure 14.

Figure 14: Current-Amplitude Controlled Switching Demo, Current Waveform

Use of the Simscape Power Systems  $\rightarrow$  Specialized Technology IGBT is highly recommended if Simulink is to be used further, as these are the only IGBT models that have been observed to allow this behavior in simulation, as a number do not.

This block also allows for some simplification not provided in others, as operation perfectly corresponds to gate input "1" for the active state, and "0" for the off state. This does not reflect gated-

transistor realities. Physical gated transistors, and all Simulink IGBT blocks excluding the one used here, activate if the gate voltage, the emitter or collector voltage (emitter for the n-types used here), and the device's threshold voltage meet the condition:  $v_q - v_e \ge V_{Th}$ .

In an AC environment this can cause issues if the gating signals are, themselves, absolute with reference to ground, supposing the emitter voltages are not, as was the case in the project. This case caused substantial issues for the project, as its effects were being observed without the root-cause being realized. The compensator was passing substantial current when all transistors were thought to be closed, and checking each transistor's pins voltage and current was a sufficiently daunting task that either debugging was implemented through other means, misattributed, or forewent altogether in early test environments as it was assumed the behavior would not follow to actual implementations.

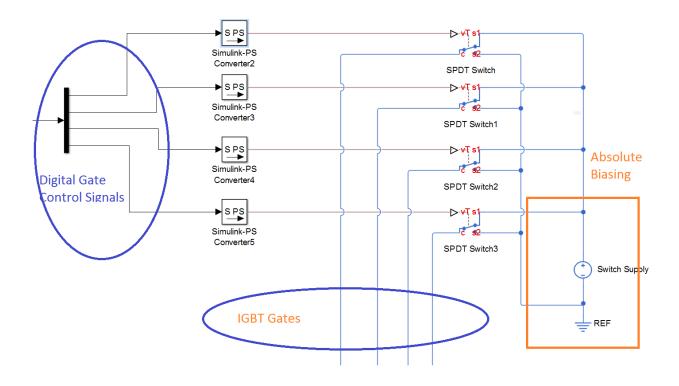

The gate control signals must follow the emitter's voltage, this is an easy enough task if the emitter is grounded, or for a p-type transistor if its collector is tied to a steady, lower magnitude, DC voltage. But at large or highly variable n-type emitter or p-type collector voltages, generation of these control signals may not be a trivial task. To make matters more difficult, the only viable IGBT or IGBT/Diode block candidates in Simulink are n-type. Thus the gates must be tied to and biased from the transistor. The solution was implemented by, instead of offsetting the transistor gate voltages from ground, tying them to the devices' emitters through more current sensitive relays, themselves tied to ground, allowing for a grounded digital device to switch signals in an environment offset significantly.

The exact circuit natures are yet undetermined, but Simulink and Multisim schematics and their application to the IGBTs may be seen below, for simulation purposes only. More design work is required to provide further realization.

Figure 16:Simulink Emitter-Following Gating Circuit

Figure 17: Gate Emitter-Following Circuit Using Relays

Figure 18: Multisim Application of Gate Circuit

The Simulink gating-circuit possesses a nontrivial abstraction. The single-pole double-throw switch is not a physical reality. With limited experience working with the relevant replacements, relays, the following circuits were designed as possible more realistic equivalents.

#### 2.2.3 The H-Bridge

The H-Bridge is a configuration of four switching transistors, each coupled with a flyback diode to mitigate the consequences a transistor experience when switching power to an inductive load. The

bridge converters and h-bridges are most famous for their applications in electromechanical controls, where they are used to control motors that require the ability to rotate in both forward and reverse directions, and current moving in opposite directions for each state.

This configuration essentially allows, when a controller or equivalent circuit is applied to the gates, for the DC supply to be inserted into a circuit, in either polarity, without manual reconfiguration. The convenience, and greater switching speeds than are available with manual reconfiguration, come at the light cost of a small increase in the internal resistance of the supply equivalent to the H-bridge circuit.

Given the very common bi-directional motor application, two states are typically used for this device (forward, reverse, and off), and two are usually avoided. The undesirable "shoot-through" states, are those for which the bridge effectively allows a short-circuit across the terminals of the DC supply. The transistors are not intended to be active at the same time as those with which they are paired vertically. Gated transistors typically exhibit very low resistances in their active states. In any given moment, one transistor is supposed to pass current, and the other to block it so that it may be

redirected to the load, shown by the connection ports for the circuit in Figure 19. If transistors Q1 and Q2, or Q3 and Q4 are in any degree of active simultaneously, these two states, in which nothing is achieved but senseless power loss, are the current operating condition of the device.

The three standard operating states are equivalent to the voltage across "Load +" and "Load –" having positive polarity, having negative polarity, and exhibiting an effective open circuit. For the opencircuit, "off", "inactive", or "idle" state, no transistors are on, and the load no power should be delivered unless the transistor gates are incorrectly biased, or a diode is active. Voltages should be thoroughly examined should such problems occur.

The positive polarity case is achieved by setting active control signal to transistors Q1 and Q4. The current path, from connection port "Load -" flows through transistor Q4 into the negative lead of the supply. It exits the positive terminal and leaves the sub-circuit through "Load +" via Q1. For the opposite polarity, Q2 and Q3 are set to active. Current is drawn through Q2 via "Load +" through the supply, and is ejected via Q3 when presented with an inactive Q4.

# 3 Proposed Approach

#### 3.1 Solution Concept

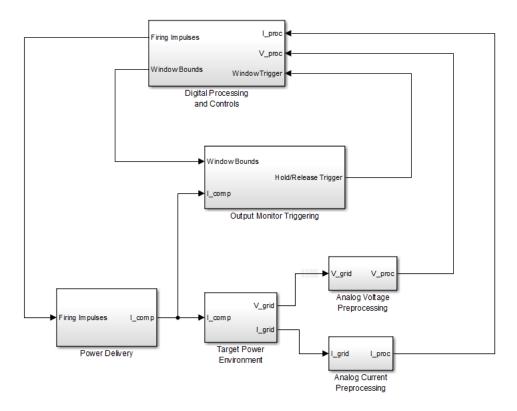

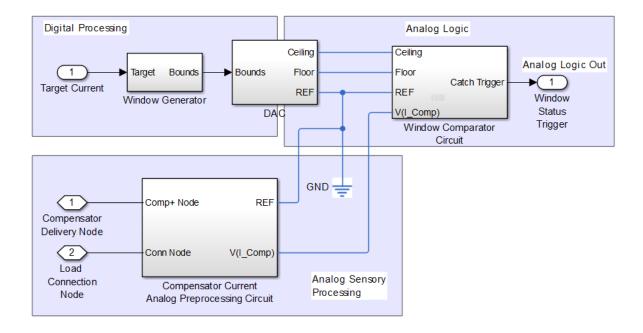

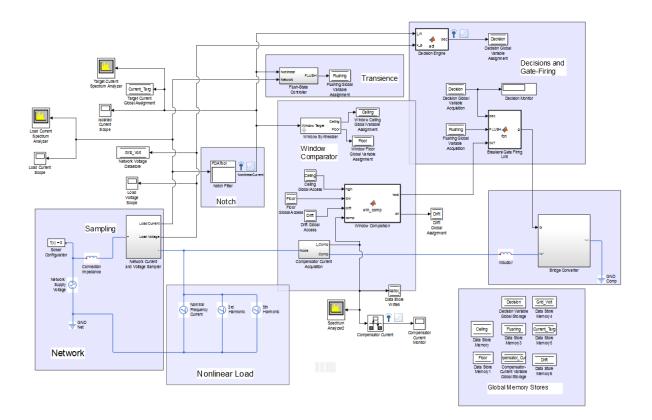

The proposed approach has five top-level units of which the operation is composed. These stages are referred to as the "Analog Current Preprocessing", "Analog Voltage Preprocessing", "Digital Processing and Controls", "Output Monitor Triggering", and "Power Delivery" units.

The Analog Preprocessing blocks monitor the voltage and current present in the grid, and operate on them in a manner to increase their compatibility with digital processing. The Digital Processing and Controls stage collects this data at fixed-interval time instances, generates a target current to be delivered, and determines the state of operation for the Power Delivery system for any given interval. The Power Delivery circuitry takes the control signals from the Digital Processing and Controls unit and operates to deliver thusly controlled current into the device's environment, and the Output Monitor Triggering block monitors the output current and sends an alert to the Digital Processing and Controls Unit should the output current drift from an acceptable tolerance in the boundaries, upon which the receiving unit will make appropriate corrections.

Figure 20: Top-Level Block Diagram of Proposed Solution

Here one can see the anatomy of the system. One block, the "Target Power Environment", has not yet been discussed under this handle due to the fact that it is external to the device. It is the environment which the device is intended to control. From this power network, we attain two necessary measurements, grid voltage "V\_grid" and grid current "I\_grid", which are fed to the inputs of Analog Voltage Preprocessing and Analog Current Preprocessing, respectively. These blocks turn these indicators into forms the Digital Processing and Controls block can handle, the preprocessed currents and voltages. These are respectively denoted as "I\_proc" and "V\_proc".

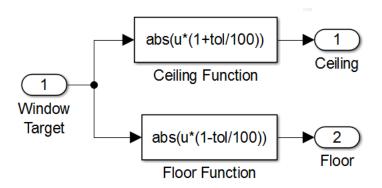

The Digital Processing and Controls unit produces the gate "Firing Impulses" signals which run to the gates of the IGBT/Diode pairs in the H-Bridge that constitutes the Power Delivery system. It also produces a window of acceptable instantaneous delivery current, calculated to be a fixed tolerance above and below that sample interval's target compensator current.

The power delivery apparatus makes no internal decisions of its own, nor does it perform any processing, but simply enters the state intended to supply the desired current. Passive lowpass filtering is applied to prevent undesirably swift current transitions, mitigating high-power spikes.

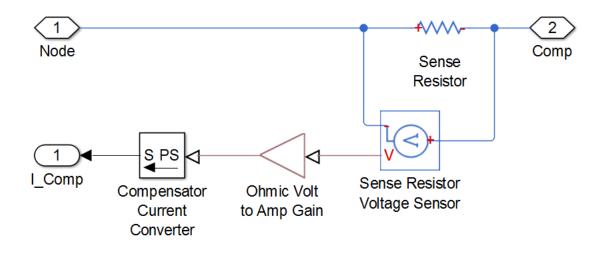

To further mitigate the high-power current spikes, analog circuitry is included to monitor the compensator current "I\_comp" in real-time. A scaled version of the compensator current is compared to the window boundaries supplied by a DAC in the Digital Processing and Controls block. If it drifts past the outer-bound of the window, the block sends an asynchronous "hold" trigger, to be received as a hardware interrupt by the digital block, which dictates that the Power Delivery exit all operation. This condition remains true until the compensator current drifts closer to the origin than the floor of the window, at which point the unit sends a "release" trigger, also to be received as a hardware interrupt, that allows the digital unit to resume regular operation of the bridge.

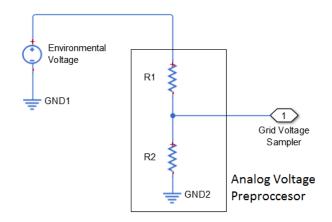

#### 3.1.1 Analog Voltage Preprocessing

Each Power Delivery state, with the exception of the "idle" state, is intended for use at a particular bias, refined by further determinations. Thus, the device must have some level of awareness of the grid voltage, one of the conditions under which the bridge operates. This is the justification for generating a digital handle on the grid's voltage.

This proposed solution implements no predictive functions for further refining of targeted power delivery, thus needs no phase-locked-loop with regards to the voltage, nor any memory of past grid voltages. As instantaneous sampled voltage is all that is used, there are no aliasing concerns. Aliasing concerns would likely be unnecessary in any case, as in power applications, voltage oscillation is restricted to low frequencies, such as 60Hz in most US applications, and 50Hz in most European.

Figure 21: Analog Voltage Preprocessor Circuit Diagram

Thus, the only necessary function for this block to perform is a linear scaling of the voltage. Analog Voltage Preprocessing is accordingly simplified to a basic voltage divider circuit. 3.3V is a ubiquitous supported voltage scale for ADCs so the voltage is scaled appropriately. Instantaneous highvoltages are made safe by scaling to use only 60% of the ADCs range, splitting the 20% on either end to allow for unexpected voltages, considered damaging to the device.

The nominal voltage of a given target environment is unknown in the scope of this project, whose purview is the design of the process. Yet the objective is to scale the maximum expected voltage amplitude to 30% of 3.3V, producing an expected maximum voltage of just under 2V, close enough to make this the new metric.

The voltage divider equations, under this requirement produce a relationship between the shown variables  $R_1$ ,  $R_2$ , and the expected environmental peak voltage  $V_a$ :

$$\frac{V_g}{2V} = \frac{R_1}{R_2} + 1$$

(11)

For the simulated power grid used in this project, with a 1kV amplitude voltage, this would give the relation:

$$R_1 = 499R_2 \tag{12}$$

This block should also behave with near-zero loss, given the environment,  $100\mu$ W of power loss is deemed acceptable. Thus, for the purposes of this project, this block tolerates 100nA of current draw. To achieve this, the series resistance should be at least  $10G\Omega$ , giving resistor values of:

$$R_1 = 9.98G\Omega, \qquad R_2 = 20M\Omega \tag{13}$$

#### 3.1.1.1 In Abstract Simulation

As attention was primarily focused on other units for the scope of this project, this has yet to be fully implemented. Rather, both the SimPowerSystems and SimElectronics libraries of Simulink provide "Voltage Measurement" or "Voltage Sensor" blocks that may be used in-stead, without voltage scaling. These were leaned on heavily throughout the project as this particular aspect was deemed a detail of the larger task, in which the true technical difficulties lay elsewhere.

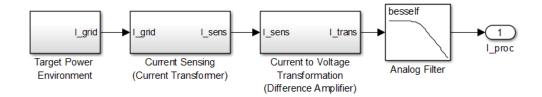

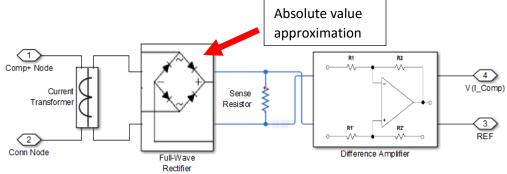

#### 3.1.2 Analog Current Preprocessing

The Analog Preprocessing Unit exists to measure the grid's current in the analog continuoustime domain, and process it in a manner where it may be effectively analyzed by the Digital Processing and Controls Unit. Three stages are used in this process, and while variations in their functionalities may exist, these three functionalities cannot, in general real applications, be removed, mitigated, or replaced, while maintaining an expectation of a functioning device. The three stages are current sensing, currentvoltage transformation, and antialiasing filtration.

#### Figure 22: Top-Level Diagram of Analog Current Preprocessing

To this end, for general applicability of the process, three variables must be left unspecified, and all three must be accounted for, primarily, in this stage of the process. All three stages can affect the target parameters, *gain* and *cutoff frequency*.

The first of such variables are the maximum expected in the environment or portion of the power network in which the device is applied. This is critical to device operation, as if this value is exceeded significantly, irreversible and function-prohibitive damage can and will be done to the device. This is best illustrated when examining the *gain* variable of the Analog Preprocessing unit.

The second unspecified variable is the maximum supported frequency for which the device is intended to accurately compensate. Beyond the often band-limited nature of semiconductors, sampling theory dictates that accurate processing may only occur for a range of frequencies wholly dependent upon the sampling rate utilized. Thus, the Analog Preprocessing Unit must be tailored to sufficiently suppress information at frequencies existing beyond this range. This is relevant to determinations of the *cutoff frequency* of the Analog Preprocessing Unit's filtration-type sub-processes.

The third is the frequency response of the grid current, itself. This variable is strongly tied to determination of an effective cutoff frequency, but is distinct, in its own right, from the concept of maximum supported frequency. It is possible for certain high-magnitude components to survive a filter's nominal *break frequency* to a degree that could result in aliasing when the Analog Preprocessing unit's output is sampled. In designing the filters used, it is important to ensure that no such case exists persistently in standard operation.

As suggested above, the two targeted design parameters for this unit are *gain* and *cutoff frequency*. Design requirements for this block include minimal *operational delay*, and *phase-distortion characteristics*. Operational delay refers to the real-time delay between the existence of a current measurement in the grid, and the moment at which that information appears at the output of this unit. Phase-distortion characteristics apply primarily to the filter's phase response, but also to any frequency domain responses of any nonlinear semiconductor devices, such as the operational-amplifiers that must necessarily appear in this process.

This is a simpler process than its current-focused counterpart, but no less crucial to providing accurate output. Given the high-power target environments and the requirement of minimal loss, only one device can effectively perform this job: the current transformer.

A very low winding current transformer, installed around the line of interest (not in-line), will provide, to the Analog Current Preprocessing Circuit, a down-stepped current proportional to current present in the grid. This contributes to the targeted gain parameter.

Figure 23: Symbol for Current Transformer [8]

As the sampling process commonly reads voltage, and not current, it is necessary to set change the independent variable of the circuit from current to voltage. The enabling principle behind this block is, that as the independent variable of a series loop at the secondary winding of the current transformer is current, the voltage across a resistance in this loop will vary proportionally to the secondary winding's current, and thus to the grid current. Measuring this voltage difference across a known, constant resistance in the series loop gives a current indicator, in volts, calibrated to the resistance across which it is measured.

A very simple version of the common methods for performing such a conversion in a low-power environment, such as the one this section is describing for the purpose of transitioning from the highpower grid to the low-power, sensitive interface with the digital unit, is a differential amplifier.

Figure 24: Difference-Amplifier Schematic [11]

This is a viable solution for simplicity's sake, where  $V_{diff} = V_- - V_+$  (this configuration is inverting), and G is this block's gain parameter. Resistances should be set such that  $R_1 = R_3$ , and  $R_2 = R_4$ . Following this the voltage gain parameter is the result of  $G = \frac{R_2}{R_1}$ . For purposes of isolating the sensitive semiconductor circuitry, the operational amplifier, it may be advantageous to connect the reference

node to the digital unit's ground port, rather than that of the high-power target environment.

The difference amplifier is installed with the "V-" input lead on the positive-reference side of the resistance in the loop of the secondary current transformer winding, and with "V+" on the other side. As the current transformer will attempt to fix the current in the loop, and vary voltage, minimal losses occur with the lowest possible sense resistance, if an actual component must be wired in to serve this purpose.

This circuit, in such a configuration, will output the voltage drop across the resistor, multiplied by the gain. With the sense-resistance known, the output voltage of the difference amplifier might be divided by this current in the digital unit to obtain a current value. The compensation process must depend upon past states regarding the grid current. Nonlinearities are most easily recognized in the frequency domain. As frequency is the inverse of time, time-varying data is necessary to manipulating the signal in the frequency domain. Thus the information delivered to the Digital Processing and Controls unit must be conducive to conversion into discrete timesamples that allow some precision in analysis.

Calling back to the sampling theory, the signal presented at the output of Analog Preprocessing must be bandlimited to the highest supported frequency of the compensator, *at most* half of the sampling frequency. To ensure this, an analog lowpass filter must precede sampling, in-order to condition the signal to be sampling friendly.

Total elimination of certain frequency components is usually not possible, but sufficient mitigation will be close enough to prevent prohibitive aliasing. An active filter (using operational amplifiers) is recommended, instead of passive (relying on resistors, inductors, and capacitors), as this unit's low power environment permits their use, and they usually enjoy significant power-loss advantages over passive filters.

The circuit diagram for this stage of the process is pictured below, attached to a copy of this project's simulated test grid assembled in the SimElectronics and Simscape Foundation Libraries.

Figure 25: Proposed Circuit Schematic for Analog Preprocessing

The differential amplifier is connected in such a manner to output a voltage proportional to the current through the Sense Resistor, at the same polarity as the grid current it is involved in sensing. The lowpass filter, however, inverts the signal. This is acceptable as ultimately it is the inverse signal that must be delivered, and the inversion would need to be performed, if not here, then at some later stage of the compensation process.

#### 3.1.2.1 Within the Project Scope

This is all essentially moot in the context of the work done for this project. This system was conceptualized in the early days of the project, but never fully designed for a duality of reasons. First, it is more application-specific than any other unit in the project, which seeks to design a process to achieve its goal in a more generalized range of applications. Secondly, it proved entirely unnecessary in the simulation environment.

The functional simulation equivalent can be designed with one or two blocks depending on the libraries used, and the continuous-time signal format one hopes to see at the Analog Preprocessing block's output. Functional equivalents in the Simscape electrical environment is shown below.

Figure 26: Reading Grid Current in SimElectronics Environment

The current sensor outputs the current as a "Physical Signal" type, which is then converted into a more standard Simulink continuous-time signal.

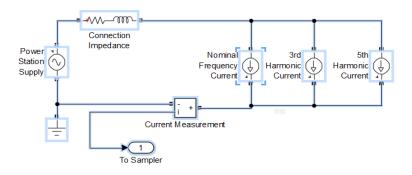

Another environment frequently used in this project is one only used in Simulink's "SimPowerSystems"  $\rightarrow$  "Specialized Technology" sub-library.

Figure 27: Reading Grid Current in "SimPowerSystems" --> "Specialized Technology" Environment

The only action detailed in the realization, but skipped in simulation, is filtering. As the nonlinear load used here only displays current at three relatively low frequencies, aliasing was no issue provided that sampling was performed at a rate of 700Hz or faster.

## 3.1.3 Digital Processing and Controls

This is the block that performs any cognitive digital processes needed to achieve precise

compensation. The tasks required from this unit are:

- Sampling processed grid current and voltage

- Accurate isolation of current behaviors resulting from load nonlinearities

- Calculating integrity indicators for resulting waveform

- Making integrity-based determinations

- Determining state at which to operate the Power Delivery block

- Generating operating signals for Power Delivery block

- Interacting with Output Monitor Triggering

Only two real design question are present in sampling. The first, which system values to sample, is a parameter of the process used in compensation. The second, how often new samples should be obtained for each indicator, or each signal's sampling frequency, is a question more relevant to the environment it is intended to operate.

For the project, the utility of digitally attaining each of three variables was closely considered. The three variables were the current in the grid, the voltage in the grid, and the current delivered by the compensator. The determination regarding which to sample was based on where they were needed in the system, the benefit different system blocks might receive by their inclusion, and the time-sensitivity of the system component functions that would operate on these variables.

Grid current, the target variable, is non-negotiable. Digital operations were required on the basis of this metric, and thus sampling was of the utmost importance.

Grid voltage seemed too low-frequency to attain for digital determinations. It was later realized that the decision engine would ultimately need a digital representation of this variable for H-Bridge state determinations.

Compensator current was more complicated, as the Output Monitor Triggering relied on this variable. As is later to be seen, an even partially implementation of this variable involves sampling of either this particular variable, or some derivative thereof. An analog implementation, however, requires only an interrupt-enabled port or digital logic circuitry. As interrupts typically arrive along general-purpose input, or GPIO, ports, sampling would be ultimately unnecessary in this case, and the time-sensitivity involved in control of the transient states used would be better addressed if an analog

representation of this variable were available for processing, regardless of whether or not it were sampled in addition.

The question of sampling frequency is, as has been mentioned, directly application and hardware specific. Tradeoffs are involved in both lower and higher sampling frequencies.

Benefits of higher sampling rates include:

- Greater supported frequency range.

- Higher sampling rate mitigates impact of group and sample delays.

- As much of such a system could be forced to wait for samples at run-time, a higher sampling rate could improve response-time.

Benefits of lower sampling time include:

- Greater isolation filter complexity or consequences.

- The critical filters employed in most designs have incredibly narrow selective or distortive bands.

- Higher sampling frequency requires either higher-order filters, or far greater floating-point support, to capture such narrow responses.

- Higher floating-point requirements jeopardize stability on less powerful computing platforms.