# Worcester Polytechnic Institute Digital WPI

Major Qualifying Projects (All Years)

Major Qualifying Projects

March 2014

# Demonstration of SRAM Design with LED Cube Display

Anthony Michael Cicchetti Worcester Polytechnic Institute

Patrick K. Smalcuga Worcester Polytechnic Institute

Sarah Elizabeth Brooks Worcester Polytechnic Institute

Follow this and additional works at: https://digitalcommons.wpi.edu/mqp-all

# **Repository Citation**

Cicchetti, A. M., Smalcuga, P. K., & Brooks, S. E. (2014). *Demonstration of SRAM Design with LED Cube Display*. Retrieved from https://digitalcommons.wpi.edu/mqp-all/3089

This Unrestricted is brought to you for free and open access by the Major Qualifying Projects at Digital WPI. It has been accepted for inclusion in Major Qualifying Projects (All Years) by an authorized administrator of Digital WPI. For more information, please contact digitalwpi@wpi.edu.

# Design of a Low Power Latch Based SRAM Sense Amplifier

A Major Qualifying Project

Submitted to the Faculty

of the

# WORCESTER POLYTECHNIC INSTITUTE

In partial fulfillment of the requirements for the

Degree of Bachelor of Science

in

Electrical and Computer Engineering

by

Sarah Brooks

Anthony Cicchetti

March 27, 2014

APPROVED:

Professor John McNeill, MQP Project Advisor

### Abstract

There is a constant push to reduce power consumption and increase speed in transistor memory devices. The goal of this project is to improve Allegro MicroSystems current Static Random Access Memory technology by designing and implementing a new sense amplifier. The final design is latch based and uses positive feedback to quickly display data at the output, which stops static current flow and dramatically reduces power consumption.Additionally a three-dimensional LED structure was designed and built to display a series of letters, characters or visual effects.

# Acknowledgments

Sarah would like to thank the following people for their guidance, support and contributions to this project.

- Mu Sarwar (Allegro MicroSystems) for his countless hours of mentoring me and motivating me to learn as much as I have about SRAM, and also for taking the time to help with designs, teach me layout, and guide this project to completion.

- Jim McClay (Allegro MicroSystems) for offering guidance on the direction of the project.

- Frank Towey (Allegro MicroSystems) for sharing his knowledge about memory testing equipment and procedures.

- **Prof. John McNeill** for creating this project, providing feedback, and guiding me through this process.

- **Prof. Steve Bitar** for being a sounding board and providing encouragement throughout this project.

- **Ben Dwyer** for his support, editing assistance, and for helping me to keep the big picture in mind.

I would especially like to thank everyone at Allegro MicroSystems and Worcester Polytechnic Institute, for without them this project would not have been possible.

# **Executive Summary**

The original focus of this project was to improve Allegro Microsystems' SRAM technology by designing and implementing a new sense amplifier. The goal of the new design was to decrease the power consumption of the SRAM chip and decrease the access time during a read cycle. The design would then be fabricated and tested for errors and compared to the previous differential sense amplifier design. After the testing was complete, the SRAM chip could be interfaced with a micro-controller and a three-dimensional LED display.

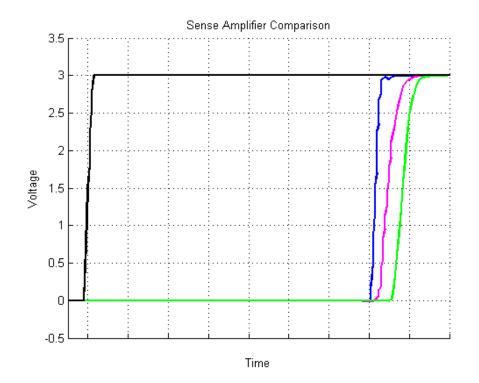

SRAM sense amplifier options were researched after determining design constraints and requirements. A basic latch based design was chosen as no static current flows in the amplifier once a value is read from an SRAM cell. By decreasing the current flow during the read cycle, the power consumption will also decrease. After deciding upon the design, a sizing analysis was run to determine the transistor sizes that are used in the amplifier. The final sizes produced an amplifier with a high stability, low power consumption, and low access time.

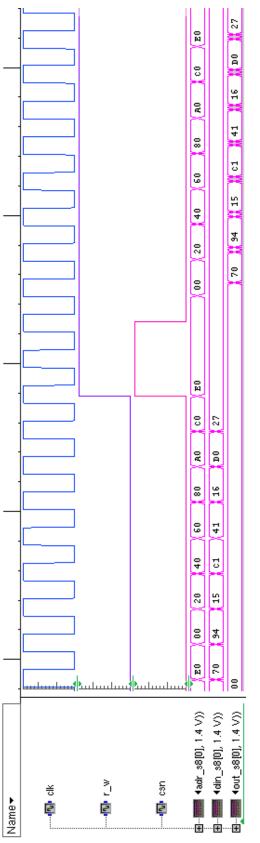

Next, the amplifier was tested through three different testing phases. First, the amplifier was tested on a stand alone basis to verify its ability to read values correctly that are stored within an SRAM cell. Next, the amplifier was integrated into the top-level SRAM layout and tested with the full chip. These tests were used to verify the timing requirements and analyze the amplifiers behavior when parasitic capacitances were added to the system. The parasitic values were extracted from the SRAM layout and were used to mimic real world performance of the chip. Finally, the system was tested as a whole to verify that the chip was accurately writing, storing and reading values stored within the memory.

In parallel to the testing, the layout was created for the SRAM chip. The layout is the silicon level design for the chip which will be used when the chip is fabricated. The layout was compared to the transistor level schematic to verify that the two designs were identical, and was also checked to make sure that it met all design constraints for the CMOS fabrication process. Although a test chip will still be made of the SRAM chip with the new sense amplifier design, the physical device was not able to return from fabrication within the time frame of this project. When the design does return in the future, the simulation results and collected data will be compared. After any necessary changes are made, the new sense amplifier design may be phased into production.

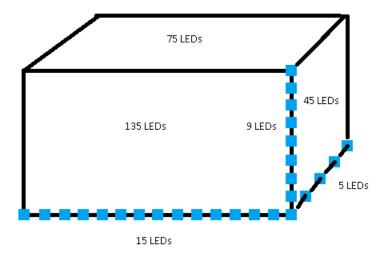

There were many things to think about when designing the orientation and structure of the LED display. There were three separate ways that the LEDs could be connected, all with their own pros and cons. Some of the things to look at were the addressing of the LEDs, the current needed to turn on a certain number of LEDs, and the way the LEDs would need to be bent to build the physical structure. After analyzing the advantages and disadvantages of each the final design was chosen. The next step was to start the actual construction of the display, after many different methods of bending the LEDs and soldering them together a proficient method was found. Once the 675 LEDs were all soldered together the beginning of coding would start. The way the coding works is described in the report.

# Contents

| 1        | Intr | roducti | ion                         | 1  |

|----------|------|---------|-----------------------------|----|

|          | 1.1  | Repor   | t Overview                  | 3  |

|          | 1.2  | Time    | Management                  | 3  |

| <b>2</b> | SRA  | AM Ba   | ackground Research          | 5  |

|          | 2.1  | Introd  | luction to Memory           | 5  |

|          |      | 2.1.1   | Terms and Sizing            | 5  |

|          |      | 2.1.2   | Address Decoders            | 5  |

|          |      | 2.1.3   | Data Input and Output       | 6  |

|          |      | 2.1.4   | Intro to the SRAM Cell      | 7  |

|          |      | 2.1.5   | Read and Write Peripherals  | 8  |

|          |      | 2.1.6   | SRAM Timing                 | 10 |

|          | 2.2  | Memo    | ry Testing                  | 12 |

|          |      | 2.2.1   | Types of Tests              | 13 |

|          |      | 2.2.2   | What Digital Tests Test For | 13 |

|          |      | 2.2.3   | Hard Errors                 | 13 |

|          |      | 2.2.4   | Fault Models                | 13 |

|          |      | 2.2.5   | Test Equipment              | 17 |

|          |      | 2.2.6   | Digital Testing Patterns    | 18 |

|          |      | 2.2.7   | Analog Testing              | 21 |

|          |      | 2.2.8   | Soft Errors                 | 25 |

| 3        | SRA  | AM Se   | ense Amplifier Design       | 28 |

|          | 3.1  | Sense   | Amplifier Project Goals     | 28 |

|          | 3.2           | Sense A  | Amplifier Designs                                   | 29 |

|----------|---------------|----------|-----------------------------------------------------|----|

|          |               | 3.2.1    | Differential Amplifier                              | 30 |

|          |               | 3.2.2    | Basic Latched Sense Amplifier                       | 32 |

|          |               | 3.2.3    | Basic Latched Sense Amplifier with Pass Transistors | 33 |

|          |               | 3.2.4    | Current Controlled Latched Sense Amplifier          | 33 |

|          |               | 3.2.5    | Amplifier Characteristics                           | 35 |

|          |               | 3.2.6    | Sense Amplifier Choice                              | 37 |

|          | 3.3           | Sizing . | Analysis                                            | 37 |

|          |               | 3.3.1    | Sizing Overview                                     | 37 |

|          |               | 3.3.2    | The Inverter                                        | 39 |

|          |               | 3.3.3    | The Access Transistor and Current Source            | 45 |

| <b>4</b> | SRA           | AM Re    | sults                                               | 49 |

|          | 4.1           | Layout   |                                                     | 50 |

|          | 4.2           | Testing  | g                                                   | 52 |

|          |               | 4.2.1    | Unit Testing                                        | 53 |

|          |               | 4.2.2    | Integration Testing                                 | 54 |

|          |               | 4.2.3    | System Testing                                      | 57 |

|          | 4.3           | Final C  | Comparison                                          | 59 |

| 5        | $\mathbf{SR}$ | AM Co    | nclusion                                            | 61 |

| 6        | LEI           | D Displ  | ay                                                  | 62 |

|          | 6.1           | Overall  | l Setup                                             | 62 |

|          | 6.2           | Flashin  | ng                                                  | 64 |

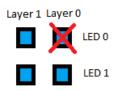

|          | 6.3           | Positio  | n and Layer Scheme                                  | 67 |

|          | 6.4           | Constr   | uction of LED Structure                             | 68 |

|          | 6.5           | Code E   | Explanation                                         | 70 |

|          |               |          |                                                     |    |

# List of Figures

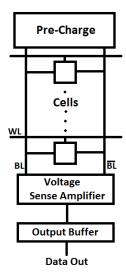

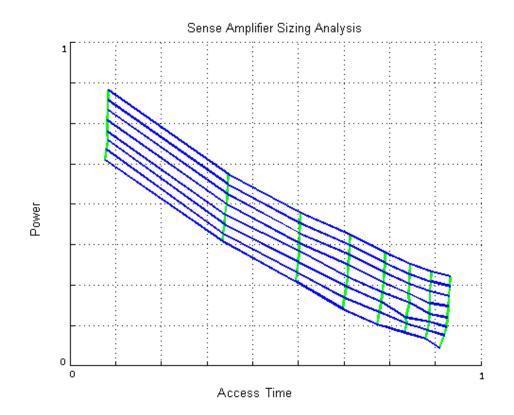

| 2.1  | SRAM Overview                                 | 6  |

|------|-----------------------------------------------|----|

| 2.2  | Tri State Buffer                              | 7  |

| 2.3  | SRAM Cell                                     | 7  |

| 2.4  | Example Precharge Circuitry                   | 8  |

| 2.5  | SRAM Column with Sense Amplifier              | 9  |

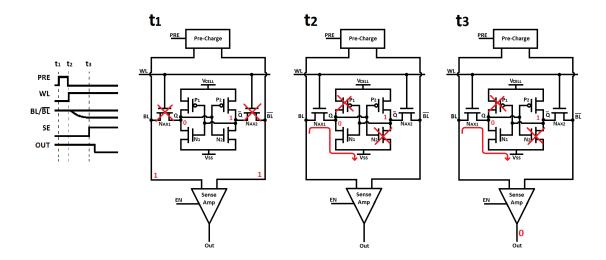

| 2.6  | SRAM Read Cycle                               | 10 |

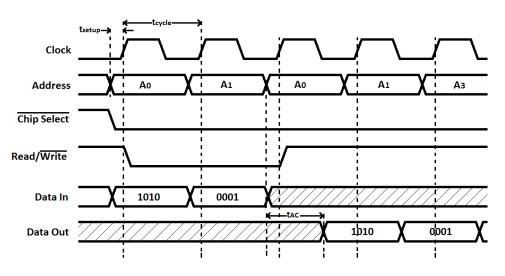

| 2.7  | SRAM Timing Diagram                           | 11 |

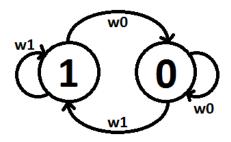

| 2.8  | Fully Functional SRAM cell                    | 14 |

| 2.9  | Two Fully Functioning SRAM Cells              | 14 |

| 2.10 | ) Stuck-At Faults                             | 14 |

| 2.11 | Transition Fault                              | 15 |

| 2.12 | 2 Inversion Coupling Fault                    | 16 |

| 2.13 | 3 State Coupling Fault                        | 16 |

| 2.14 | 4 GALPAT Pattern for a Four Cell Memory Block | 20 |

| 2.15 | 5 6T SRAM Cell Configuration                  | 21 |

| 2.16 | 3 Static Noise Margin Butterfly Curve         | 22 |

| 2.17 | 7 Example Static Noise Margin Curves          | 23 |

| 2.18 | 8 Read Margin                                 | 24 |

| 2.19 | Bitline Write Margin                          | 24 |

| 2.20 | ) Wordline Write Margin                       | 25 |

| 0.1  |                                               | 20 |

| 3.1  | Differential Voltage Sense Amplifier          | 30 |

| 3.2  | Basic Latched Voltage Sense Amplifier         | 32 |

| 3.3  | Latch Based Amplifier VTC                     | 32 |

| 3.4  | Latch Based Amplifier with Pass Transistors                    | 34       |

|------|----------------------------------------------------------------|----------|

| 3.5  | Current Controlled Latched Sense Amplifier                     | 34       |

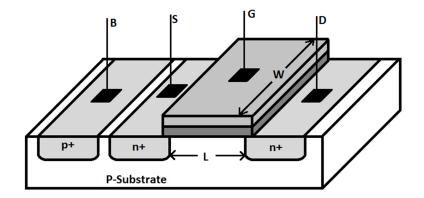

| 3.6  | MOSFET Cross-Section View                                      | 38       |

| 3.7  | Latch Based Sense Amplifier                                    | 39       |

| 3.8  | Highlighted Latch in Sense Amplifier                           | 40       |

| 3.9  | Inverter Circuit Diagram and Charictoristic Voltage Curve      | 40       |

| 3.10 | Inverter Curves                                                | 42       |

| 3.11 | Example Static Noise Margin Curves                             | 42       |

| 3.12 | Inverter Parametric Analysis Results                           | 43       |

| 3.13 | Final Inverter Voltage Transfer Characteristic Curve           | 44       |

| 3.14 | Inverter Static Noise Margin                                   | 44       |

| 3.15 | Current Source and Access Transistor                           | 45       |

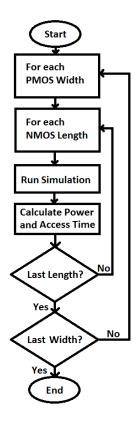

| 3.16 | Ocean Flowchart                                                | 46       |

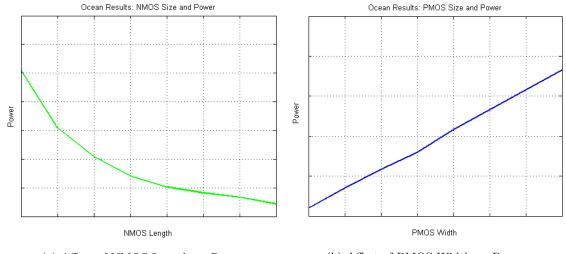

| 3.17 | Size and Power Consumption                                     | 47       |

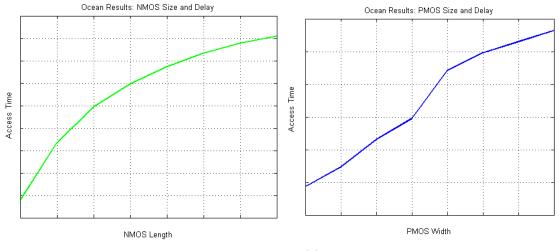

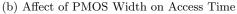

| 3.18 | Size and Access Time                                           | 47       |

| 3.19 | Current Source and Access Transistor Sizing                    | 48       |

| 4.1  | SRAM Final Block Diagram                                       | 50       |

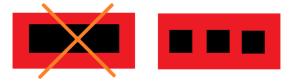

| 4.2  | DRC Example                                                    | 50       |

| 4.3  | Incorrect and Correct Setup for Larger Structure with Set Size | 51       |

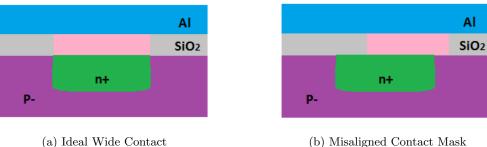

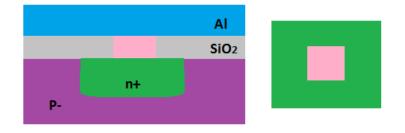

| 4.4  | Issues of Large Contact Area                                   | 52       |

| 4.5  | DRC Overlap Rule                                               | 52<br>52 |

| 4.6  | Unit Testing Results                                           | 54       |

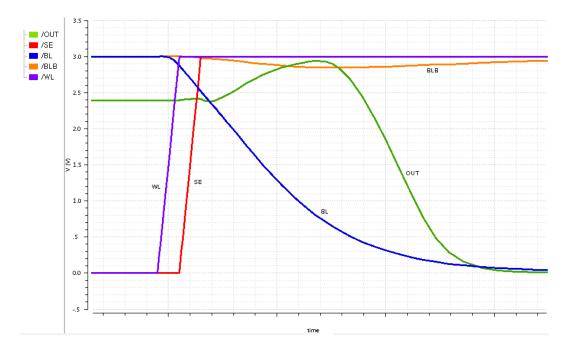

| 4.7  | Integration Testing Results                                    | 54<br>56 |

| 4.8  | System Testing Results                                         | 58       |

| 4.9  | Access Time Reading a Logic High                               | 60       |

| 4.0  |                                                                | 00       |

| 6.1  | LED Display Setup                                              | 62       |

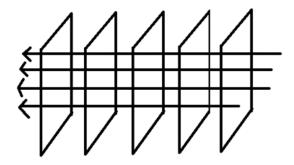

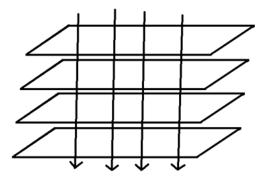

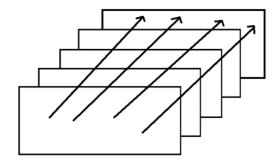

| 6.2  | 15 Layers by 45 Columns                                        | 63       |

| 6.3  | 9 Layers by 75 Columns                                         | 63       |

| 6.4  | 5 Layers by 135 Columns                                        | 64       |

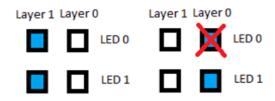

| 6.5  | Drawing an L: Step 1                                           | 65       |

| 6.6  | Drawing an L: Step 2                  | 65 |

|------|---------------------------------------|----|

| 6.7  | Drawing an L: Errors                  | 65 |

| 6.8  | Drawing an L: Flashing                | 66 |

| 6.9  | Drawing an L: Final                   | 66 |

| 6.10 | Scrolling Letter A                    | 67 |

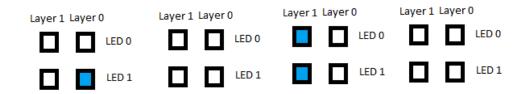

| 6.11 | Switching Layers: Step 1              | 68 |

| 6.12 | Switching Layers: Final               | 68 |

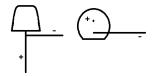

| 6.13 | LED Front and Side View               | 69 |

| 6.14 | LED First Bend Side and Bottom View   | 69 |

| 6.15 | LED First Solder Bottom View          | 69 |

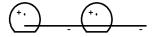

| 6.16 | LED Second Bend Bottom and Side Views | 70 |

| 6.17 | LED Second Bend with First Solder     | 70 |

| 6.18 | Final Soldering                       | 70 |

# List of Tables

| 2.1 Common March Tests | 19 |

|------------------------|----|

|------------------------|----|

# Authorship

This major qualifying project is comprised of two main sub-projects: the design of an SRAM sense amplifier and the design and implementation of a three-dimensional LED display. The three project partners focused on different aspects of the project and report as is listed below.

**Sarah Brooks:** Sarah focused on the SRAM sense amplifier design and all SRAM-related aspects of the project and report. The chapters she wrote are listed below.

- Chapter 2: SRAM Background Research

- Chapter 3: SRAM Sense Amplifier Design

- Chapter 4: SRAM Results

- Chapter 5: SRAM Conclusion

Anthony Cicchetti: Anthony focused on designing and building the hardware to construct the LED display as well as the coding and addressing scheme. The chapters he wrote are listed below.

• Chapter 6: LED Display

# Chapter 1

# Introduction

This Major Qualifying Project includes two subprojects; the design and fabrication of a sense amplifier for an SRAM chip, and the design of a three dimensional LED display. This project is sponsored by Allegro MicroSystems LLC and NECAMSD Labs.

In many applications, Static Random Access Memory (SRAM) arrays make up a large area of high-performance integrated circuits [1]. There is a constant push to increase a chips speed and to reduce its power consumption. As memory sizes increase and transistor sizes decrease, a trade-off must be made between reducing the layout area and adding peripherals to increase the performance of the chip [1]. Designs should work as efficiently as possible while minimizing complexity.

Allegro MicroSystems SRAM designs come in various sizes and configurations, but all use a 6T cell and a differential voltage sense amplifier to read the value stored in the cell during a read cycle [2][3][4]. Although the differential amplifier is very reliable, constant current must be applied throughout the entire read cycle causing a large static power loss. The goal of this project is to design a new sense amplifier that uses less power during a read cycle. The scope of this project includes determine the most suitable sense amplifier design, sizing the amplifier transistors for minimum area, maximum stability, and minimum power consumption, testing the amplifier to confirm functionality and performance, and integrating the new sense amplifier with a current SRAM chip design.

After various sense amplifiers were evaluated, a latch-based design was chosen because it will

have no static current flow after the amplifier latches and reads the value stored in the memory [5][6]. There will be multiple steps in testing the sense amplifier. Initially, the stand-alone performance and characteristics of the design will be analyzed. Next, the amplifier will be tested with a simplified SRAM model. Finally, the amplifier will be integrated into Allegros top-level SRAM schematic, where the amplifier performance will be verified with as close to real world operating conditions as possible. The simulations and testing will be performed using Cadence Virtuoso Design Suite.

In addition to designing and testing the amplifier, the physical transistor layout must be created so that a test chip can be fabricated using CMOS technology. The layout determines the total area that the chip will use, and is an exact model of what will be fabricated. The different connections at the silicon level will impact the parasitics that will exist in the SRAM chip, which can negatively affect the device performance if not correctly placed [5][6]. Although the actual SRAM chip will not arrive back from fabrication in time for real world measurements to be made, parasitic values may be extracted from the layout, allowing the simulated results to provide a realistic estimate for the expected behavior.

The second set of goals for this Major Qualifying Project are to design and implement a scalable and power efficient three dimensional LED display. Gaining experience from design process is one of many things that will be accomplished through the completion of this MQP. There are many aspects of the design process that must be considered such as continuously adapting to variations within the project. The purpose of this MQP is to obtain a thorough and beneficial learning experience. For this MQP we are going to design and build an LED display. To do this we will need to not only design and build the physical structure, but also to develop an addressing scheme. This scheme will give us access to each of the 675 LEDs. This will allow for the structure to display three-dimensional letters or images. A Printed Circuit Board (PCB) layout will also be fabricated as a base for the LED display circuitry. An MSP430 microcontroller will be used to drive the LED display by providing the digital logic to control the state of all of the LEDs.

The overall project begins with research of current models of the LED display. Aspects such as the multiplexing scheme, microcontroller, and part selection were identified from different working LED cube models. Next, display features, driving technique, and microcontroller options are assessed to determine the necessities of the prototype. Many calculations went into determining design parameters such as power consumption and frequency requirements. These parameters and the final prototype display size were chosen so that the design could be easily scaled. Once the design parameters had been set one of the final steps of the design process was to begin the selection of parts. The selection process consists of selecting a pool of appropriate parts for the prototype. A filtering process is done to eliminate less compatible components that do not meet the design qualifications. Finally, a value analysis will be done on the remaining pool to determine the optimal set of parts. Once all of the parts are chosen and a final design is completed, the final step is to design the PCB layout and assemble the working prototype.

# 1.1 Report Overview

This report is divided into two main sections that represent the two overarching goals of the project. Chapter 2 to Chapter 4 covers the design of a sense amplifier for a Allegro Microsystems' SRAM chip. Chapter 2 includes the background research for this project. This section includes an introduction to Static Random Access Memory (SRAM) and its components as well as memory testing options for both before and after fabrication. Chapter 3 explains the the project goals for the new sense amplifier design, multiple sense amplifier options, and a sizing analysis for the chosen design. Chapter 4 reviews the top-level SRAM design, explains the SRAM layout, and examines test results and compares the new amplifier to the preexisting design. The second part of the report contains the design process of the LED structure as well as the coding and addressing schemes. This is shown in Chapter 6.

# **1.2** Time Management

Over the course of this project, unforeseen issues and changing deadlines have altered the plans and goals. Initially, the goal of the project was to improve Allegro MicroSystems SRAM technology by designing a new sense amplifier. This new sense amplifier would be implemented into an existing SRAM design and the chip would be fabricated, tested, and interfaced with a microcontroller and a three-dimensional LED display. However, the fabrication of the SRAM chip will not be completed before the final project deadline. Due to this delay, testing the SRAM chip and interfacing it with the microcrontroller and LED display is no longer feasible. This unforeseen circumstance prevents the original plan from being completed and has altered the direction of the project. Now, the SRAM portion of the project will focus on final simulation and layout results that are as close to the real world behavior as possible. The LED display is now driven by an alternate microcontroller that that does not require external memory.

# Chapter 2

# **SRAM Background Research**

# 2.1 Introduction to Memory

# 2.1.1 Terms and Sizing

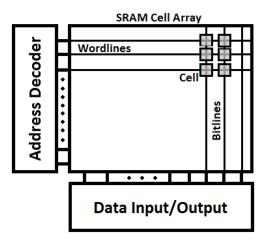

A memory chip can be thought of as a matrix of locations that are each able to store one binary bit – either a 1 or a 0. Each location that is able to store a bit is known as a cell. To simplify the design and to save space, the memory matrix usually has a set width of bits that is usually one or more bytes long. This group has one complete unit of information and is known as the memories word length. The entire word of memory is stored at a specific location known as its address, and all actions performed on the memory such as reading and writing values will be done to the entire word at a specific address at the same time. The size of a memory describes how many different locations are available to store bits of information. The memory size can be calculated by multiplying the word length by the number of addresses [6][3]. Figure 2.1 shows an example SRAM memory array.

# 2.1.2 Address Decoders

Large memory arrays can have hundreds of different rows of cells. Since only one word of data is selected at a time, having every address assigned to only one pin is a waste of space. To decrease the number of pins needed in order to choose an address, most memory chips use address decoders [3][6]. Address decoders use combinations of logic 1's and 0's on the input to choose a

Figure 2.1: SRAM Overview

unique address. This allows n pins to access  $2^n$  locations. In certain cases, pre decoders may also be added to further reduce the number of pins needed to access each address. Some synchronous chips will also integrate the clock signal in with the address decoders so that cells are only selected during a certain portion of the clock cycle.

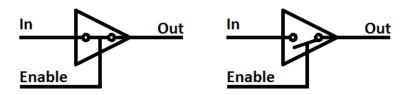

# 2.1.3 Data Input and Output

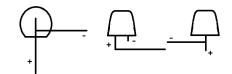

Data busses are needed to carry input and output information to and from each memory cell. Memory chips can either have separate data input and output buses or they can share one bus. Sharing an input/output bus saves space on the chip, but using separate lines is simpler to design and implement. In both cases, the data available at the output is only important during a read cycle, and the data at the input is only important during a write cycle. If chips share one bus, tri state buffers are needed at the output so that data is only seen during a read cycle and a output enable pin is needed to enable the buffers [6]. Tri state buffers act like switches. If the buffer is enabled, the switch is closed, and the output follows the input. If the buffer is disabled, the switch is open and the output is in a high impedance or high z mode [2]. Figure 2.2 below shows a tri state buffer along with a representation of how it works.

Figure 2.2: Tri State Buffer

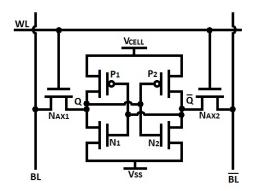

# 2.1.4 Intro to the SRAM Cell

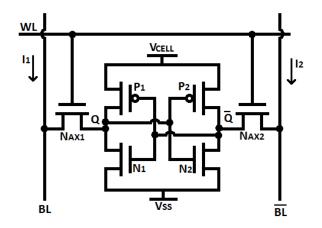

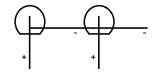

Static Random Access Memory, or SRAM, is a type of volatile memory with a nondestructive read cycle. Figure 2.3 shows an example of an SRAM cell in standard 6T configuration [2][3][6]. The SRAM cell contains two access transistors ( $N_{AX1}$ ,  $N_{AX2}$ ), and two cross coupled inverters ( $N_1$ ,  $P_1$  and  $N_2$ ,  $P_2$ ) comprised of a PMOS load transistor, and an NMOS driver transistor. The cross coupled inverters constantly reinforce which value is stored on each side of the cell. Node Q holds the cells value and node  $\overline{Q}$  holds its complement.

Figure 2.3: SRAM Cell

The cell is powered by the voltage applied at  $V_{CELL}$ . As long as power is supplied to  $V_{CELL}$ , the SRAM cell can hold its value indefinitely. The wordline (WL) selects the cell and allows values to be read from or written to the cell [6]. When the wordline is not selected, the cell is in standby mode. Selecting an address brings a wordline to a logic high, selecting all of the cells in that word. This brings the cells out of standby by enabling the access transistors, which allows the cells to be read from or written to. The cell also has two bitlines which control both the input and output of the data from the cell. The first bitline (BL), known as bitline, holds the same value that is stored in the cell. The second bitline  $\overline{BL}$ , known as bitline bar, or  $\overline{bitline}$ , or bitline not, holds the inverse of the value that is stored in the cell.

# 2.1.5 Read and Write Peripherals

Since only one row of SRAM cells can be accessed at the same time, only one cell per column requires the use of the read and write peripherals. Because of this, all of SRAM cells in one column are able to share the same peripherals, allowing for space to be saved on the chip.

# Write Circuitry

The SRAM write circuitry connects directly to the bitlines and is used to write a value to the SRAM cell. The value stored in the SRAM cell is stored at node Q, while the inverse of the value is stored at node  $\overline{Q}$ . The cell can be seen above in Figure 2.3. Instead of writing either a logic 1 or a logic 0 to side Q, a 0 is written to either Q or  $\overline{Q}$  depending on which value should be stored in the cell. To write a value to the cell, one bitline is held at V<sub>DD</sub> while the other is held at V<sub>SS</sub>. Holding the bitline at V<sub>SS</sub> will cause the inverter to be pulled past its trip point, which will cause the cell to latch and hold the new value [6].

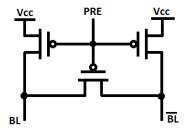

# **Precharge Circuitry**

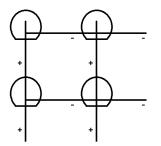

The precharge circuitry brings the bitline and  $\overline{bitline}$  to be the same voltage before a read cycle. The simplest version of precharge circuitry consists of three transistors that can be either NMOS or PMOS devices. Two of the transistors are used to connect the bitlines to  $V_{CC}$ , and the third transistor is connected between the two bitlines to ensure that the lines end up being the same voltage [6]. Figure 2.4 shows an example of a precharge circuit that uses three PMOS transistors. To precharge the bitlines, the signal PRE is brought to a logic 0. This turns on all three transistors which then charge and equalize BL and  $\overline{BL}$  to be  $V_{CC}$ .

Figure 2.4: Example Precharge Circuitry

## Sense Amplifier

The sense amplifier is in charge of detecting what value is stored in an SRAM cell during a read cycle and displaying that value at the output. Since only one row of data is accessed during each read cycle, each column of cells within the SRAM array requires only one sense amplifier [3].

A sense amplifier works by sensing a relatively small difference between the voltages of the two bitlines, then amplifying the difference at the output to show if a cell is storing either a logic 1 or 0 [3][6][4]. The bitlines are precharged before each read cycle to ensure that the difference between the bitline voltages are caused by the value that is stored in the cell. If the bitlines are not precharged, there is a chance that the sense amplifier could misread and present an incorrect value at the output. Often times sense amplifiers are followed by an output buffer to ensure that the full logic level is shown at the output. There are two main sense amplifiers [7]. This report mainly focuses on voltage sense amplifiers. Figure 2.5 shows an example of an SRAM column setup with a voltage sense amplifier.

Figure 2.5: SRAM Column with Sense Amplifier

In order to understand how a sense amplifier works, it is important to first understand how an SRAM cell behaves during a read cycle. An example of the behavior of one cell during a read cycle may be seen in Figure 2.6 along with an example timing chart. The read cycle begins after the bitlines are precharged to the supply voltage but before the cell is activated. This may be seen in Figure 2.6 on the left at time t1. When the precharge cycle is complete, the cells bitlines are both the same value.

Next a wordline is selected which activates a certain cell or row of cells. This can be seen in Figure 2.6 in the middle which corresponds to time t2. For this example, the SRAM cell is storing a logic 0, which can be seen at node Q. This means that a logic 1 is stored at  $\overline{Q}$ . Due to the nature of the cell, only two of the cell transistors remain activated once a value is stored. Transistors

$N_2$  and  $P_1$  are both off because of the values that appear at their gates. When the wordline is selected, the access transistors,  $N_{AX1}$  and  $N_{AX2}$  connect the SRAM cell to the precharged bitlines. The value stored in node  $\overline{Q}$  is approximately the same value as the voltage that the bitlines were precharged to, transistor  $P_2$  helps to maintain this value and bitline  $\overline{BL}$  does not discharge. The value stored in node Q is much less than the value that the bitlines were precharged to. Transistor  $N_1$  creates a path to ground which causes the bitline voltage to drop. The bitline and the selected cell have paracitic resistances and capacitances which form an RC time constant that causes the voltage to discharge exponentially.

Figure 2.6: SRAM Read Cycle

Instead of waiting for the cell to completely discharge the bitline, the sense amplifier is used to amplify the small difference between the two lines. Depending on the design that is used, the sense amplifier may be activated as soon as the cell is selected, or it may be selected after a certain amount of time has passed to allow the voltage difference between the bitlines to be large enough to not cause a misread of the cell. The final step where the sense amplifier is activated can be seen in Figure 2.6 on the right which corresponds to t3 on the timing chart. Later in this report in section 3.2 specific sense amplifier designs will be explained.

# 2.1.6 SRAM Timing

The timing parameters of an SRAM chip must be known in order to have the device perform successfully. The timing defines the maximum frequency that can be used for a synchronous device, and lets the user know how fast they should expect to see values at the output.

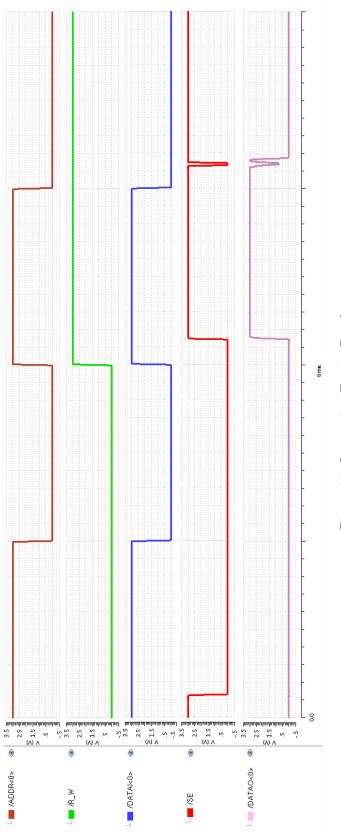

Figure 2.7 shows an example timing diagram for a synchronous SRAM chip. The timing diagram shows six different parameters that affect the timing performance of an SRAM chip. The first line shows the clock input which is usually an input from an external source. All of the other timing information relates back to the clock speed. The period of the clock can be seen in the figure as  $t_{CYCLE}$ , and is the minimum amount of time that the memory needs to perform consecutive read or write operations. The minimum amount of time needed for a read cycle is not necessarily the same as the amount of time needed for a read cycle. Despite this, a system will usually use the same unit of time to execute either operation in order to simplify the design [3]. The maximum clock frequency that an SRAM chip can handle can be seen in Equation 2.1.

$$f = \frac{1}{t_{cycle}} \tag{2.1}$$

The setup timing, shown as  $t_{SETUP}$ , is the amount of time needed to set up the system before executing a read or write operation. The set up time accounts for things such as pre-charging the bitlines before reading, and readying the data to be written to the cells.

Figure 2.7: SRAM Timing Diagram

The second row in the timing diagram shows the addresses for the memory locations. Some of the other timing parameters, such as the read access time are measured with respect to the time when a valid address first appears. The third line shows the chip select. The bar represents that chip select is enabled when the voltage is brought low. A chip must be selected to operate. If chip select is left high, the SRAM is in standby mode.

The fourth line shows the read and write control for the chip. When the signal is low, data will be taken from the input, which can be seen on line five, and will be written to certain cells that are selected by the address. When the cells are not being written to, it does not matter what data is seen on the input.

On the other hand, when the read and write signal is high, data will be read from the cells that correspond to the selected address. The amount of time that it takes to display the data from the selected cells once a valid address is accessed is known as the read access time. This can be seen as  $t_{AC}$  in the timing diagram. The read access time is usually between 20% to 80% of the cycle time [6]. If the read access time were to exceed the cycle time, incorrect data would b seen at the output and the SRAM chip would not be able to successfully prepare for another read or write procedure. While data is not being read from the SRAM chip, it does not matter what data is seen at the output.

# 2.2 Memory Testing

Testing is used to ensure both the reliability and quality of a physical product. The test chip that is fabricated by Allegro Microsystems must be tested before it can be implemented with the LED cube. For large scale production, testing must be done to separate out defective devices and to verify that those that pass testing behave as expected within the specifications they were designed for [8]. Due to the decrease in transistor sizing and the condensing of layouts, it is extremely likely that a defect will occur in an SRAM chip. Defects can be caused by design flaws, manufacturing and packaging errors, in-the-field errors, and process variations. A seemingly small variance in device parameters can be the difference between a functioning and failing chip. Since each SRAM chip is made up of millions of transistors, it is not physically or financially possible to exhaustively test the memory. To conserve both time and money, testing should ideally have maximum fault coverage with minimum complexity [1].

# 2.2.1 Types of Tests

Memory chips can be tested using both digital and analog techniques. Digital testing also known as logical testing is done after fabrication and makes sure that the memory functions like it should. Analog testing is usually done through simulation during the design phase and looks at how the chip behaves under certain operating conditions.

# 2.2.2 What Digital Tests Test For

When a defect is present in an SRAM chip, incorrect outputs will be produced under certain conditions. For digital testing, the inputs and outputs of a memory chip are explored on a functional level. Fault models have been created so that a representation of possible physical defects can be understood at a functional level. Each fault model only explains a functional fault, but many different defects at the transistor level can lead to the same functional fault [1]. All memory faults are caused by either hard (permanent) or soft (transient) defects [1] [9].

# 2.2.3 Hard Errors

Hard or permanent errors are caused by a physical defect and will occur under all SRAM operating conditions. These errors are caused during manufacturing, or later during use. Errors from manufacturing can be caused by extra or missing material, oxide breakdown, imperfections or impurities in the wafer, missing contacts, and packaging mistakes [10].

### 2.2.4 Fault Models

Below common fault models that are caused by hard errors are explained [1][11][12][13].

# Functional SRAM Cell

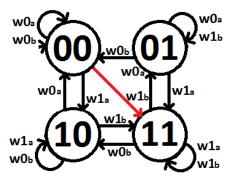

Before explaining how a faulty SRAM cell behaves, it is important to understand the behavior of fully functional cells. Figure 2.8 shows the state diagram for a single fully functional cell. The cell has two states; it can either be holding a logic high or 1 or a logic low or 0. Reading is non-destructive to the cell so it is not included in the diagram. Writing to the cell is denoted with a w followed by the state that is being written to the cell –either a 1 or 0. Writing the same value to a cell will cause the state to stay the same, writing the opposite value will cause the state to

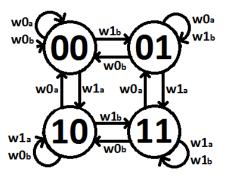

Figure 2.8: Fully Functional SRAM cell

Figure 2.9: Two Fully Functioning SRAM Cells

switch. Figure 2.9shows the state diagram for the interactions between two fully functional cells, a and b.

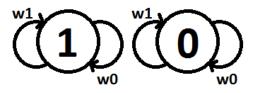

### Stuck-At Fault

Stuck-at faults are models for cells whose values are unable to change from either the logic 0 or 1 state. This fault only affects one cell. The cell value is permanently stuck and will stay the same no matter what is done to the rest of the system. Figure 2.10 shows the state diagrams for both a stuck-at 1 cell (on the left) and a stuck-at 0 cell (on the right). As the diagram shows, the cell will not be able to change out of its original value. Stuck-At faults are one of the most common faults to appear in memory testing [1].

Figure 2.10: Stuck-At Faults

During testing, stuck-at faults can be found by writing all of the cells to a specific value (either logic 0 or logic 1), reading the cell, and then repeating with the inverse value. If a stuck at fault exists, that cell will not change its value when a new one is written to it. Both logic values must be checked as cells can be stuck at either logic state.

### **Stuck Open Fault**

A stuck open fault only affects one cell. This fault simply means that a cell that cannot be accessed. It is said to be stuck open because no actions can reach the cell. This fault is usually caused by an issue with the bitline or wordline. Stuck Open faults can be found in the same way as stuck at faults as can be seen above.

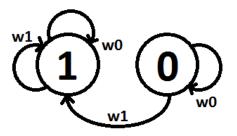

#### **Transition Fault**

Cells with transition faults are unable to transition from  $0\rightarrow 1$  or from  $1\rightarrow 0$ . This fault only affects one cell. Failure to transition from  $0\rightarrow 1$  is known as a rising transition fault and failure to transition from  $1\rightarrow 0$  is known as a rising transition fault. Transition faults differ from stuck at faults because it is possible for the cell to be in either state, it is just not possible for it to switch into its complementary state from a certain position [1]. Transition faults do not have to exist in both directions. Figure 2.11 shows a cell with a falling transition fault.

Figure 2.11: Transition Fault

Transition faults can be found by having each cell undergo both transitions and reading the results. This is done by writing the cell to one state, writing the cell to the opposite state and then reading the value out of the cell [14]. Since SRAM is volatile, the value of a cell is random when the system first powers on. If a cell with a transition fault initializes to the state where it cannot transition from, it may look like a stuck-at fault [1].

# **Coupling Fault**

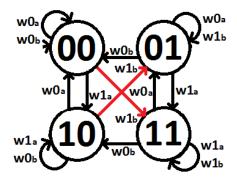

In addition to single cell faults, some faults can be caused by coupling between two or more cells. These faults are modeled as an interaction between an aggressor cell and a victim cell. When the aggressor cell switches state, it will cause a change in the victim cell. An Inversion coupling

Figure 2.12: Inversion Coupling Fault

Figure 2.13: State Coupling Fault

fault causes the victim cell to invert values when the aggressor cell goes through a transition [10]. An idempotent coupling fault forces the victim cell to be either a 1 or a 0 when the aggressor cell goes through a transition. A state coupling fault forces the victim cell to become a certain state depending on what the aggressor cell is. Coupling faults can only happen between cells that are physically near each other in the memory. Figure 2.12 shows an example of an inversion coupling fault. When cell b, the aggressor, goes through a transition from 0 to 1, cell a, the victim, switches state. Figure 2.13 shows an example of a state coupling fault. When cell b, the aggressor, is a 1, cell a, the victim is also forced to be a 1. Please refer to Figure 2.9 for the interactions between two fully functional SRAM cells.

Coupling faults can be found by writing one value to the victim cell, writing first one value, then the inverse to the aggressor cell, then reading back the value from the victim cell. Because the victim and aggressor cells are not known initially, this test will take a longer time to test out.

#### Neighborhood Pattern Sensitive Fault

Neighborhood pattern sensitive faults (NPSF) are faults between many cells. The victim cell in this case is known as the base cell and will have its value changed when the other cells surrounding it are a certain pattern. There are three different kinds of NPSFs. an active fault will cause the cell to change value, a passive fault will cause the cell to stay at a certain value even if a different value is written to the cell, and a static fault will cause the cell to change to one specific state [14]. NPSF can only happen between cells that are physically near each other in the memory.

The base cell is read after changing the neighboring cells to different sets of patterns that could

possibly cause the fault to appear. Because each cell can act as a base cell, testing for a NPSF can be very complicated and will take a large amount of time. Due to the large amount of time and the fact that NPSF are not very common, they are not usually tested for [14].

#### Address Decoder Fault

Address Decoder Faults (AF), are faults within the address decoder that lead to issues when the memory cells are selected. Address Decoder faults include cells that are never accessed, addresses that access no cells, multiple cells accessed by one address, and certain cells accessed by multiple addresses.

# 2.2.5 Test Equipment

In order to logically test an SRAM chip, set input values are written to the cells, stored in the memory, read from the cells, and checked on the output. The logical tests are made of different sequences that can be used to check for issues in the memory. There are many different varieties of test equipment that can be used to test for errors in memory. In this section pattern generators and logic analyzers will be covered.

#### Pattern Generator

Pattern generators are used to create and run a sequence of logic 1s and 0s known as a test vector. The pattern generator can control what voltages correspond to a logic 1 and 0, when a logic 1 or 0 will be written to a cell, when the read and write cycles will take place, and which row of cells are accessed. They can also be used as an external clock for the chip during testing.

# Logic Analyzer

Logic Analyzers are used for viewing digital waveforms. They display the voltages that they observe in the time domain which produces something very similar to a timing diagram. Logic Analyzers usually have between 34 and 136 channels that are each able to record and display information from a different digital input at the same time [15]. Logic analyzers only display two logic levels logic low and logic high. These values are set by the user before collecting data along with a threshold voltage. Any value below the threshold will be interpreted as logic low and any value above the threshold will be interpreted as logic high. A logic analyzer interfaces with

the device under test (DUT) through acquisition probes. Each connection on the probe has an internally compares the threshold voltage to an incoming voltage to decide if it is logic high or low [15]. Logic analyzers have many different trigger options including the ability to trigger off of a pattern in the data that the user defines, or an edge which looks for a threshold crossing [16]. In addition, the triggering position can be set to determine how much post and pre data is kept with respect to the trigger point. Logic analyzers use either a timing mode or a state mode when they collect data. Timing mode is used for asynchronous data collection. It uses an internal clock and will sample the incoming data at a preset sampling rate. State mode is used for synchronous data collection and will use one of the inputs as a clock to decide when to sample the data [16]. Logic analyzers can be used with pattern generators to test memory by displaying input and output logic information. The inputs and outputs can then be compared to find data errors which can be cell faults.

# 2.2.6 Digital Testing Patterns

This section covers the digital testing patterns used during the logical tests in order to find certain memory faults.

#### March Tests

A march test is a technique for sequentially reading and writing data to every SRAM cell in a certain address order. There are many different varieties of march tests that cover a wide range of fault models. A single march test is made up of many different march elements that consist of either a read or write operation [Pavlov]. Each operation is performed on every call and can be carried out in either increasing address order (starting at row 0 and ending on row n-1), or decreasing address order (starting at row n-1 and ending on row 0). Performing an operation in increasing order is denoted with an up arrow ( $\uparrow$ ), decreasing order with a down arrow ( $\Downarrow$ ), and either order with a double arrow ( $\uparrow$ ). A write operation is indicated with a w followed by either a 1 or 0 to show which logic level is being written to the cell. A read operation is notated the same way but with an r followed by a 1 or 0. The read operation tells you what value you should expect to see at the output. Some examples of this notation are w0, which means write a 0 to the cells and r1 which means read a 1 from the cells. One of the simplest march tests is known as the Modified Algorithmic Test Sequence, or MATS. Below is the MATS testing sequence [1][11].

MATS: (w0); (r0, w1); (r1);

The test starts by writing a value of 0 to all of the SRAM cells in either increasing or decreasing address order. Next, the first line of cells are read in either address order and the value 0 is expected at the output. After reading, a value of 1 is written to all of the SRAM cells in that location. After this the address is either increased or decreased depending on the chosen order, and the same read and write cycle is applied to the next set of cells. Finally, the cells are read in either address order and the value 1 is expected at the output. Each march test has different fault coverage and test length. The test length is usually measured in terms of the memory size, where N represents the number of cells. For example, the MATS test has a test length of 4N, because it goes through the memory a total for four times. Table 2.1 describes some of the more common march tests, their testing sequence, their test length, and some of the faults that they are able to cover [1]. In the table, AF stands for Address Decoder Fault, SAF stands for Stuck At Faults, TF stands for Transition Faults, and CF stands for Coupling Faults.

| Table 2.1: Common March Tests | 5 |

|-------------------------------|---|

|-------------------------------|---|

| Name            | Sequence                                                                                                                                                                                                                                                                    | Length | Coverage                 |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------|

| MATS            | (w0); (r0,w1); (r1);                                                                                                                                                                                                                                                        | 4N     | Some AFs, SAFs           |

| MATS+           | $\label{eq:w0} \ensuremath{\left( \mathrm{w0} \right)}; \ensuremath{\left( \mathrm{r0}, \mathrm{w1} \right)}; \ensuremath{\left( \mathrm{r1}, \mathrm{w0} \right)};$                                                                                                        | 5N     | AFs, SAFs                |

| MATS++          | $\label{eq:w0} \ensuremath{\left( \mathrm{w0} \right)}; \ensuremath{\left( \mathrm{r0}, \mathrm{w1} \right)}; \ensuremath{\left( \mathrm{r1}, \mathrm{w0}, \mathrm{r0} \right)};$                                                                                           | 6N     | AFs, SAFs, TFs           |

| March Y         | $\label{eq:constraint} \ensuremath{\left( \mathrm{w0} \right)}; \ensuremath{\left( \mathrm{r0}, \mathrm{w1}, \mathrm{r1} \right)}; \ensuremath{\left( \mathrm{r1}, \mathrm{w0}, \mathrm{r0} \right)}; \ensuremath{\left( \mathrm{r0} \right)};$                             | 8N     | AFs, SAFs, TFs, Some CFs |

| March C-        | $ \begin{array}{l} \Uparrow(w0); \Uparrow(r0,w1); \Uparrow(r1,w0); \Downarrow(r0,w1); \\ \Downarrow(r1,w0); \Uparrow(r0); \end{array} $                                                                                                                                     | 10N    | AFs, SAFs, TFs, Some CFs |

| March C         | $ \begin{array}{l} \label{eq:product} (\texttt{w0}); \Uparrow(\texttt{r0},\texttt{w1}); \Uparrow(\texttt{r1},\texttt{w0}); \updownarrow(\texttt{r0}); \\ \Downarrow(\texttt{r0},\texttt{w1}); \Downarrow(\texttt{r1},\texttt{w0}); \updownarrow(\texttt{r0}); \end{array} $ | 11N    | AFs, SAFs, TFs, Some CFs |

| March SS $[12]$ | (w0); (r0,r0,w0,r0,w1); (r1, r1, w1, r1, w0); (r0,r0,w0,r0,w1); (r1, r1, w1, w1, r1, w0); (r0,r0,w0,r0,w1); (r1, r1, w1, r1, w0); (r0);                                                                                                                                     | 22N    | AFs, SAFs, TFs, CFs      |

Many other march tests exist and more are constantly being created. March tests are one of

the shortest but most efficient tests for finding memory faults in SRAM.

### **Galloping Pattern Test**

Another common test pattern is known as the Galloping Pattern Test, or GALPAT. The GAL-PAT test has a longer test length than many of the march tests, but is able to cover more faults. There are two different variations of the GALPAT test; gallop a 1 through a background of 0s, or gallop a 0 through a background of 1s. Below is an explanation of the GALPAT test [11].

# GALPAT

- 1. Write a background 0 (1) to all of the memory cells.

- 2. Invert one cell to be a 1(0)

- 3. Repeat the following sequence for all the memory cells, incrementing the non-inverting cells address with each iteration:

- (a) Read the inverted cell

- (b) Read a non-inverted cell

- 4. Switch back the inverted cell to be a 0 (1)

- 5. Invert the next cell to be a 1(0)

- 6. Repeat sequence from Step 3 for all memory cells

Figure 2.14 shows an example of the GALPAT test for a four cell memory block. As the figure shows, the 1 appears to gallop across the cell. GALPAT covers all Address Decoder Faults, Stuck At Faults, Transition Faults, and Coupling Faults, with a test length of  $4N^2+2N$ .

| 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

Figure 2.14: GALPAT Pattern for a Four Cell Memory Block

# 2.2.7 Analog Testing

In order to understand the analog testing procedures, soft errors, and the remaining SRAM cell faults, the stability of the SRAM cell must first be explored.

### Cell Stability

Stability is one of the most important factors in an SRAM cell design [17]. An unstable cell is unreliable and can cause incorrect data to be read from, written to, or stored within a memory cell. Modeling the noise margins of a cell can help to determine the stability and define the limits to which the cell will behave normally before it is fabricated. A total of five simulations can be run in each case, one for each process corner in order to show the extreme process parameter variations that could occur within the cell. The combinations were TT, FF, SS, FS, and SF, where the first letter stands for the NMOS device and the second letter stands for the PMOS device, with possible options being T-Typical, F-Fast and S-Slow process parameters. In addition to varying the process parameters, parametric analysis can be run to vary the cell temperature and supply voltage under each testing condition.

This section will explain how to determine the read, write and static noise margin for an SRAM memory cell in the standard 6T configuration, which may be seen below in Figure 2.15. As was explained in Section 2.1.4 The cell contains two access transistors ( $N_{AX1}$ ,  $N_{AX2}$ ), and two cross coupled inverters ( $N_1$ ,  $P_1$  and  $N_2$ ,  $P_2$ ) comprised of a PMOS load transistor, and an NMOS driver transistor.

Figure 2.15: 6T SRAM Cell Configuration

The wordline (WL) of the cell is connected to the gate of both access transistors which are used to enable the cell when the wordline is connected to  $V_{DD}$ , so that values can be written to or read from the inverters via the bit line and its complement (BL and  $\overline{BL}$ ). The read cycle should be non-destructive so that the cell will maintain its value unless it is overwritten. When the WL is brought low, the access transistors will turn off and the cell will hold a written value as long as  $V_{CELL}$  has a sufficient voltage to power the inverters. The inverters are bi-stable and their configuration causes a value to be stored at Q while its complement is stored at  $\overline{Q}$ .

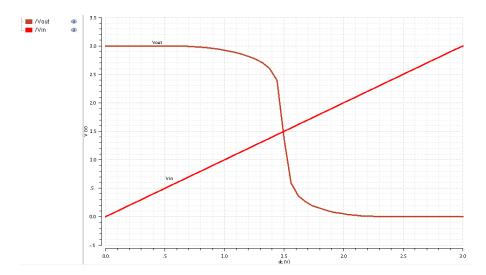

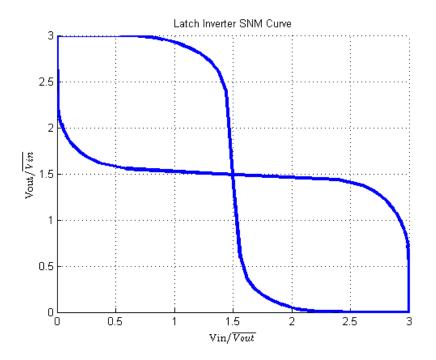

# Static Noise Margin

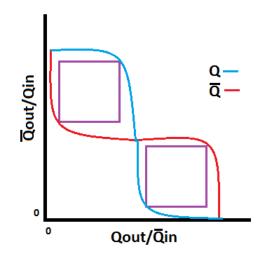

The static noise margin (SNM) of an SRAM cell is determined by how well the cell inverters will maintain their given state. The SNM is defined as the maximum voltage noise that can be tolerated by the inverter outputs without causing the cell to change states [17] [18]. The SNM can be found by looking at the Voltage Transfer Characteristic (VTC) of the cells inverter and its mirror, known as the butterfly curve, and drawing the largest square that can fit between the two curves [17] [18] [19]. Figure 2.16 shows an example butterfly curve with the boxes used to find the SNM.

Figure 2.16: Static Noise Margin Butterfly Curve

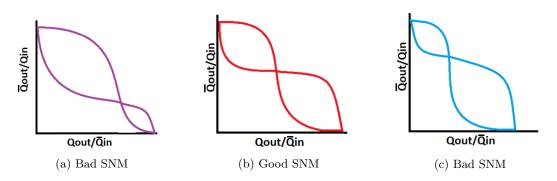

Figure 2.17 shows some example Static Noise Margin Curves. Figure 2.17a has a poor noise margin. The upper half of the butterfly curve is significantly larger than the lower half which will cause the latch to tend towards node Q storing a logic high and node  $\overline{Q}$  storing a logic low. Figure

Figure 2.17: Example Static Noise Margin Curves

2.17c also has a poor noise margin. For this case, the inverters will have the opposite problem, causing the latch to tend towards node Q storing a logic low and node  $\overline{Q}$  storing a logic high. Figure 2.17b is an example of an even inverter with a high static noise margin. This case will cause the latch to not be biased towards either logic level. If the SRAM cells do not have a high static noise margin, there is a higher chance of storing incorrect values within the memory array.

#### **Read Stability**

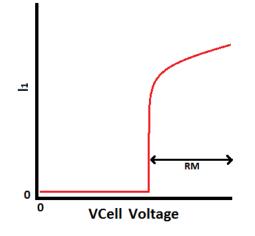

Determining an SRAM cells read stability can be done in a number of ways. One technique frequently used determines the Read Static Noise Margin (RSNM) by looking at the VTC of the inverters during a read cycle [19] [20]. Because the RSNM depends on the voltage supplied to the SRAM cell, the RSNM can also be measured by setting initial values so that a 0 stored at node Q, and a 1 at node  $\overline{Q}$ , then sweeping the cell supply voltage downwards while monitoring the current, I<sub>2</sub> [20]. When the cell supply voltage is no longer sufficient to power the inverters, the SRAM cell cannot store a state in its memory, which will cause the current, I<sub>2</sub>, to steeply drop off. The RSNM is then measured as the difference between this voltage and V<sub>DD</sub>. An example curve for measuring the RSNM may be seen below in Figure 2.18

#### Writability

This section explains the two different tests that can be run to determine the SRAM cells writability. The two tests find the bitline write margin and the wordline write margin.

**Bitline Write Margin** During a write cycle, the SRAM cell is enabled by bringing the WL high, while the bit line on the side of the inverter where the logic 1 was previously stored is pulled

Figure 2.18: Read Margin

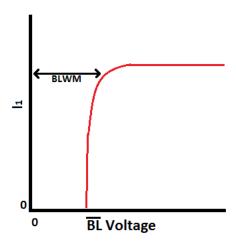

below the trip point, causing the cell to change state and write a 0. This method can be applied to either bitline to write a 0 or a 1 to Q. The first stability measurement for the write cycle is the Bit Line Write Margin (BLWM) and is defined as the highest bitline voltage that will still cause the inverter to change state [19]. To find the BLWM, the cell is set to initial values so that a 0 stored at node Q, and a 1 at node  $\overline{Q}$ , then the current, I<sub>1</sub>, is observed while the voltage at BL was swept from V<sub>DD</sub> to V<sub>SS</sub>. Both the WL and BL are kept at V<sub>DD</sub> during the sweep. The voltage at  $\overline{BL}$  that causes the current at I<sub>1</sub> to drop significantly is the BLWM [20]. Figure 2.19 shows an example of the curve that the BLWM is measured from.

Figure 2.19: Bitline Write Margin

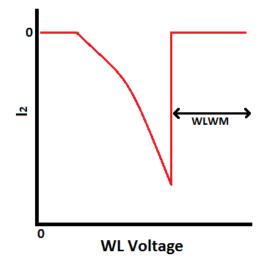

Wordline Write Margin The second stability measurement for the write cycle is the Wordline Write Margin (WLWM) and is defined as the maximum difference between  $V_{DD}$  and the WL voltage that occurs when the current curve returns to zero [20]. This point on the current curve corresponds to the inverters changing state. To find the WLWM, the cell is initialized so that a 0 stored at node Q, and a 1 at node  $\overline{Q}$ , then I<sub>2</sub> is observed during a WL sweep from V<sub>SS</sub> to V<sub>DD</sub>, while BL is held at V<sub>DD</sub> and  $\overline{BL}$  was held at V<sub>SS</sub>. Figure 2.20 shows an example curve that the WLWM is measured from.

Figure 2.20: Wordline Write Margin

## 2.2.8 Soft Errors

Soft or transient errors are non-permanent errors that will cause a cell to act in a defective way under certain operating conditions. Soft errors will disrupt the stability of the cell, causing it to fail to maintain its proper state. They can be caused by alpha radiation and fabrication mistakes [1].

#### **Stabilty Fault**

Stability faults are caused by weak SRAM cells. Weak cells have issues with one of their noise margins. If the cell is not operating under ideal conditions, it will cause the cell to fail to retain its value. There are different degrees of stability faults, some cells may become unstable under almost all conditions, and other cells may only have issues under very specific circumstances. Some factors that will affect cell stability include the voltage of the cell, temperature, and noise [1]. When the static noise margin is small for one value it will cause the inverter to flip states even when it should not [1]. Data retention faults are one of the most sever stability faults so they are considered in a category of their own. Stability faults are difficult to find because parametric analysis must be run with controlled testing conditions that can precisely vary the cell operating conditions.

#### **Data Retention Fault**

An SRAM cell should hold the value written to it as long as it has sufficient power. Data retention faults happen when a cell fails to hold its value even though there is still sufficient power to the cell. A cell that has a data retention fault will not be able to keep its correct value stored after a certain amount of time passes [1]. Data retention faults can happen for only one value, or for both values that a cell can store. Data retention faults are difficult to find because most tests will read the value saved to the cell shortly after writing it.

#### IDDQ Test

Another technique that is used to test semiconductor devices is known as the IDDQ test. The IDDQ test is able to find soft errors that do not affect the logical output, such as certain types of coupling and shorts in the system [1]. These errors often waste the power of the system and can lead to more severe issues such as data retention faults. The IDDQ test works by monitoring the quiescent current of the circuit, which is the current drawn by the system when it is fully powered but not active. This current is usually extremely small. If there is an error, such as a break, in the system, the current will rise by a few orders of magnitudes [1]. By monitoring the current for this change, certain defects that are otherwise undetectable can be found.

The IDDQ test is not commonly used in SRAM testing for a number of reasons including sizing and scaling. Due to the decreasing transistor size, the leakage current and parameter variation make it very difficult to accurately detect errors [1]. The IDDQ test has only been successfully used for devices that have a channel length of 0.25m and above, which is much larger than the current technology [1]. In addition to this, changes must be made to either the SRAM cell or the row decoders in order to access the whole memory cell which increases the footprint of the chip [21]. Despite this fact, several methods have been proposed for adapting the IDDQ test for current technology, but as sizing continues to decrease, the IDDQ test is becoming less reliable for accurate fault detection [21][1].

Although it is not always a useful method for determining faults, IDDQ testing is still used to evaluate current flow and power consumption within memory devices.

## Chapter 3

# SRAM Sense Amplifier Design

One of the main goals for this Major Qualifying Project is to improve Allegro MicroSystems SRAM technology by designing and testing a new sense amplifier design. Before determining what changes can be made to improve the current sense amplifier design, the overall system level requirements must be defined outlined as is shown in section 3.1. Next, the operating characteristics and design limitations of existing sense amplifiers will be researched in section 3.2. After this, a new SRAM sense amplifier design will be chosen, sized, and tested as may be found in section 3.3.

## 3.1 Sense Amplifier Project Goals

Allegro Microsystems most significant goals are to decrease the total power consumption and access time of their SRAM chips. The focus of this project is to design a new sense amplifier that will be both faster and more power efficient than the current design. To meet this goal, the new sense amplifier design must consume less power than the current differential sense amplifier, The sense amplifier must be at least as fast as the current design. If the amplifier is too slow, it will increase the access time (as was discussed in Section 2.1.6), and decrease the maximum clock frequency that may be used with the chip.

Although these are the main objectives, the sense amplifier must meet certain other criteria as well. These requirements are listed below.

The sense amplifier must be modular and able to fit into the current SRAM design without

significantly affecting the other peripherals. Although slight modification may be necessary, the new design should make as small of an impact on the rest of the design as possible.

The layout area must be reasonable. Since each column must have a sense amplifier, any change in the footprint will have a dramatic impact on the overall size of the chip. A larger overall layout area also increases the parasitic capacitance. If the new design consumes too much physical space, the chip will become impractically large and it will not be worth the improvements it introduces

The sense amplifier must perform reliably during the read cycle and be resistant to noise within the system. In order for the sense amplifier to function properly, it must accurately read the values stored in the SRAM cells. If values are misread the majority of the time, the sense amplifier is useless.

Although the main goals of the new design are to reduce the power consumption and increase the performance of the amplifier, the modularity, layout footprint, and accuracy must be examined and considered during the design process. By taking into account all of these requirements, a robust and reliable sense amplifier will be created.

## **3.2** Sense Amplifier Designs

There are two main categories of sense amplifiers Differential sense amplifiers, also known as voltage mode sense amplifiers, and non-differential amplifiers, also known as current mode sense amplifiers [7]. Within the category of voltage sense amplifiers there are both static designs, which are latch based and read the difference between the bitlines once and hold that output, and dynamic designs, which constantly watch the difference between the bitlines and adjust their output accordingly [5].

Voltage mode sense amplifiers are connected directly to the bitlines. At the beginning of a read cycle, the bitlines are precharged. As one bitline begins to discharge, the difference between the bitline voltages determines the output logic value that is seen at the output. The performance of voltage mode sense amplifiers depends on the bitline capacitances. The larger the bitline capacitance, the larger the RC time constant of the system, and the larger the delay between enabling the cells and having a large enough difference between the bitlines for a voltage mode sense amplifier to detect the value and show it at the output [5].

If the bitline capacitance is too large and the bitlines cannot be discharged in a reasonable amount of time, current mode amplifiers are sometimes cascaded and used as a buffering stage to disconnect the excessively capacitive bitlines and voltage mode sense amplifier inputs [5]. Because of this, current mode sense amplifiers are often found in large memory arrays that have significantly larger bitline capacitances. Current mode sense amplifiers may also be used independently. The amplifier inputs are connected to the bitlines, and after precharge, the discharging bitline causes a decrease in current flow which is used to determine the output voltage level.

Below are examples of some amplifier types, along with their pros, cons and characteristics.

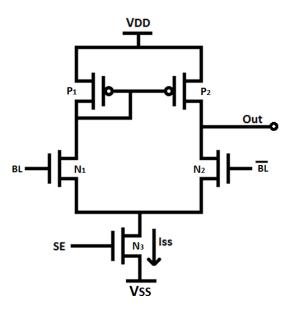

## 3.2.1 Differential Amplifier

The differential sense amplifier is a dynamic voltage mode amplifier. Allegro Microsystems also currently uses this design in their SRAM chips. Figure 3.1 shows an example circuit diagram for the differential sense amplifier. The amplifier is composed of a differential pair (Transistors N<sub>1</sub> and N<sub>2</sub>) with an active current mirror load (P<sub>1</sub> and P<sub>2</sub>) and a biasing current source (N<sub>3</sub>). The bitlines are connected to the gates of the differential pair transistors and the output is taken from the same side as  $\overline{BL}$ .

Figure 3.1: Differential Voltage Sense Amplifier

The differential sense amplifier is commonly used because it is simple and reliable [2][5]. The sense amplifier may be enabled at the same time as the wordline during a read cycle, making timing requirements for this amplifier very easy. The differential amplifier is resistant to supply noise variations due to its ability to reject common mode voltages; only differences between the inputs are amplified. Any noise that appears on both inputs of the amplifier will not affect the output.

In addition to this, the differential sense amplifier will almost never misread the cell because the output is constantly adjusted depending on the input voltage. A read cycle begins when the signal SE is brought high. This causes a constant biasing current,  $I_{SS}$ , to flow through the biasing current source (N<sub>3</sub>). If both input voltages are exactly equal, this will cause a current equal to  $\frac{I_{SS}}{2}$  to flow through both halves of the amplifier. To ensure that the current is divided equally, the PMOS devices P<sub>1</sub> and P<sub>2</sub> must be sized identically. The NMOS devices N<sub>1</sub> and N<sub>2</sub> must also be sized identically.

When the amplifier is first enabled, the input voltages are approximately equal because the bitlines are precharged. After the SRAM cells are enabled, one bitline will begin to discharge as was explained in Section 2.1.5. As the bitline discharges, the voltage supplied to the gate of the transistor on that side of the amplifier will decrease, causing the drain current to decrease as the transistor begins to turn off. Because the current source is supplying a total current to the amplifier equal to  $I_{SS}$ , the decrease in drain current on one side will cause the current in the opposite side of the amplifier to increase. As the transistor continues to turn off, the output voltage will rise to equal the supply voltage,  $V_{DD}$ . A relatively small difference between the bitlines will produce a large difference in output voltages.

In order for the sense amplifier to work properly, the biasing current source must remain on throughout the entire read cycle. If the biasing current stops flowing, a valid value will no longer appear at the output and the amplifier will not function[2]. This constant current flow causes the device to consume a significant amount of power throughout the entire read cycle.

Figure 3.2: Basic Latched Voltage Sense Amplifier

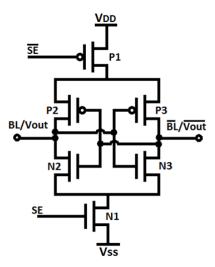

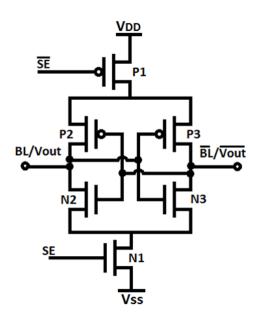

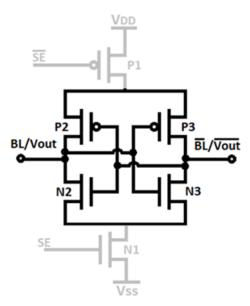

## 3.2.2 Basic Latched Sense Amplifier

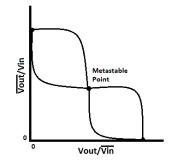

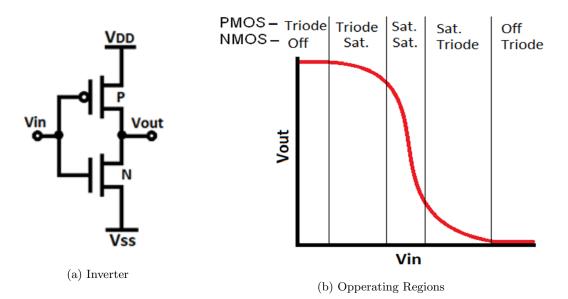

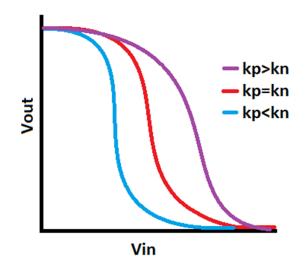

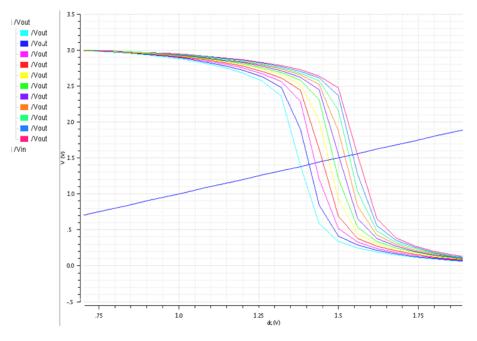

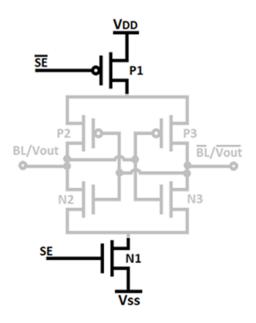

The basic latch based sense amplifier is a static voltage mode sense amplifier. An example schematic for the basic latch based sense amplifier may be seen in Figure 3.2. There are many variations of the basic latched sense amplifier, but this original design is one of the simplest and reliable choices [7][6]. The latch mechanism for the sense amplifier is composed of two cross coupled inverters (N<sub>1</sub>, P<sub>1</sub> and N<sub>2</sub>, P<sub>2</sub>) which use positive feedback to cause latching behavior. The latched sense amplifiers voltage transfer characteristic curve may be seen in Figure 3.3. This plot shows that the amplifier has two stable points where V<sub>OUT</sub> and  $\overline{V_{OUT}}$  are at opposite rails and one metastable state in the middle of the transition region where V<sub>OUT</sub> and  $\overline{V_{OUT}}$  are at the same voltage.

Figure 3.3: Latch Based Amplifier VTC

Before a read cycle, the bitlines which are connected to the amplifier inputs are precharged to

the supply voltage. If the amplifier were to be turned on right after the precharge stage, there would not be a sufficient voltage difference between the bitlines, which could cause the amplifier to stay at its metastable point or latch incorrectly. To solve this issue, the bitlines are allowed to discharge until they have created a large enough voltage difference for the sense amplifier to correctly identify the value stored in the memory cell. The discharging bitlines are connected to the inverter inputs, allowing a small bias to develop on the MOSFET gates before the sense amplifier is enabled and the inverters are turned on. To turn on the amplifier, the signal SE is brought high, which turns on the NMOS current source  $(N_3)$  and the PMOS access transistor  $(P_3)$ . After being enabled, the bias allows the sense amplifier to latch the correct output value.

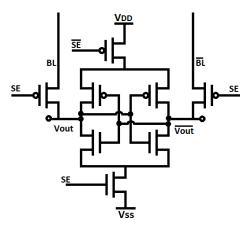

#### 3.2.3 Basic Latched Sense Amplifier with Pass Transistors

One common variation of the basic latch based sense amplifier includes the addition of pass transistors [5]. Figure 3.4 This addition effectively decouples the amplifier inputs and outputs from the bitlines. Because the inputs and outputs of the sense amplifier are the same physical node, the sense amplifier will attempt to further discharge the bitlines while its reading the value stored in the SRAM cell. The pass transistors connect the input and output of the sense amplifier to the bitlines and are active when the sense amplifier is disabled. This allows the bias to still develop on the gates while the sense amplifier is off and the bitlines are discharging. Once the sense amplifier is enabled, the pass transistors turn off and the bitlines are decoupled from the sense amplifier inputs. Once the amplifier is enabled, the bitlines can no longer discharge. Unlike the amplifier without the pass transistors, this amplifier must account for the voltage drop over the pass transistors. This may lead to issues if one pass transistor is fabricated with a slight sizing error, as it may potentially bias the amplifier towards one logic value.

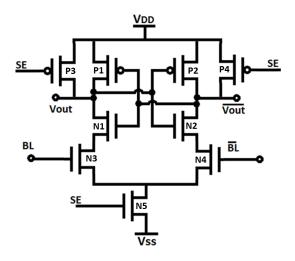

#### 3.2.4 Current Controlled Latched Sense Amplifier

Another common voltage sense amplifier is the Current Controlled Latched Sense Amplifier. This design combines asspects from the latch based voltage mode sense amplifier and the differential pair amplifier. An example schematic may be seen below in Figure 3.5. This design was introduced in 1993 by T. Kobayashi, and is a popular choice in SRAM memory [22][23][5]. The amplifier uses the same latch based design as the basic latch based amplifier that was described above in 3.2.2, but has the bitlines attached to the gates of transistors  $N_3$  and  $N_4$ . This causes an extremely high

Figure 3.4: Latch Based Amplifier with Pass Transistors

impedance to be seen at the input, and the bitlines to be decoupled from the output . The two inverters are made from the MOSFET pairs  $N_1,P_1$  and  $N_2,P_2$ . When the amplifier is off, the signal SE is at a logic low. This turns on the reset transistors  $P_3$  and  $P_4$ , clearing the previous latched value and holding the latch at its metastable point. The bitline inputs are connected to the gates of MOSFETS  $N_3$  and  $N_4$ . When the sense amplifier is enabled, the reset transistors turn off, and the current source N5 turns on, causing an even current to flow through each half of the amplifier. The bitline that is discharging causes the gate voltage to drop, which decreases the current flowing through that side of the amplifier and causes the voltage to rise. This will cause the amplifier to latch, which will stop the static flow of current and display a valid value at the output.

Figure 3.5: Current Controlled Latched Sense Amplifier

#### 3.2.5 Amplifier Characteristics

Before determining which amplifier should be used, it is important to understand its overall characteristics and how it compares to the other amplifier options. Below, different properties of the various amplifiers are outlined.

#### **Output Voltage Levels**