# Worcester Polytechnic Institute Digital WPI

Major Qualifying Projects (All Years)

Major Qualifying Projects

April 2009

# Widely Tunable RF Frontend for the Universal Software Radio Peripheral: the MMP9000

Matthew Brian Murdy Worcester Polytechnic Institute

Michael Carpenter Bruno Worcester Polytechnic Institute

Peter J. Perreault Worcester Polytechnic Institute

Follow this and additional works at: https://digitalcommons.wpi.edu/mqp-all

#### **Repository Citation**

Murdy, M. B., Bruno, M. C., & Perreault, P. J. (2009). Widely Tunable RF Frontend for the Universal Software Radio Peripheral: the MMP9000. Retrieved from https://digitalcommons.wpi.edu/mqp-all/3837

This Unrestricted is brought to you for free and open access by the Major Qualifying Projects at Digital WPI. It has been accepted for inclusion in Major Qualifying Projects (All Years) by an authorized administrator of Digital WPI. For more information, please contact digitalwpi@wpi.edu.

# Widely Tunable RF Frontend for the Universal Software Radio Peripheral: the MMP9000

A Major Qualifying Project Report Submitted to the Faculty of the

WORCESTER POLYTECHNIC INSTITUTE

in partial fulfillment of the requirements for the Degree of Bachelor of Science in Electrical and Computer Engineering by

Michael Bruno

Matthew Murdy

Peter Perreault

Sponsoring Organization: NECAMSID Project Advisors:

Professor Alexander Wyglinski, Advisor

Professor John McNeill, Co-Advisor

April 30, 2009

# Abstract

This report presents the design and construction of a wideband transceiver in the context of an RF frontend for a software radio development platform, the Universal Software Radio Peripheral (USRP). This daughterboard is designed to operate at either full or half duplex modes over a frequency range of 100 MHz to 1.3 GHz or greater. It is fully integrated with both the USRP and GNU Radio, a free software radio development toolkit, to fully control the daughterboard via software.

# Acknowledgements

The accomplishments made by this team throughout this project would not have been possible without the help of several very important people. First, we would like to thank Professor Wyglinski, our advisor. He set up our team, gave us ideas to choose from and guided us towards developing our own project. Throughout the project, he set high standards for our team, which kept us on the track to meeting our goals.

A project like this needed funding from the school and more specifically, these funds came from NECAMSID. The team would like to thank Professor McNeil for sponsoring our project and allowing our team to use his lab resources throughout our project.

The team would also like to thank Bob Boisse for soldering components on two different revisions of the board for us. Mr. Boisse soldered down several of the components that have pads underneath them, a task that would not have been too difficult for us. We would not have been able to test or debug our systems in a timely fashion without his help.

A large portion of the development for this project was facilitated through the use of evaluation boards which were supplied to the team free of charge. For this, the team would like to thank Lon Cecil from RFMD for giving the team a free RF2051 Evaluation Board, test software, and free samples of the RF2052. We would like to point out that at the time we asked for all of this, the RF2052 was not even available for sale. We would also like to thank Lauren Stieh from Minicircuits for providing us with a free evaluation board of their GVA-84+ evaluation board. Both of these boards were extremely helpful and we would not have been able to afford them on our budget without the generosity of these two people.

Finally, we would like to thank any other company that sent us samples throughout the project. Many of these companies give samples to students and we just want to point out how invaluable such generosity can be. Also, thank-you to anyone else who helped answer our questions at one point or another or provided any kind of assistance with this project.

# **Executive Summary**

Historically, the field of radio and communications has been an ever changing and thriving field, both culturally and technologically. Improvements in radio technology have brought about their widespread use through all facets of society, for countless purposes, enabling communication between consumers, public utilities, military entities, and more. Unfortunately, one of the side effects of the Communication Age is a scarcity of the main resource enabling radio communications; the wireless spectrum. Recent developments in the field of radio communications have sought to address this problem, increasing spectral efficiency through technological developments in software defined radio (SDR) and cognitive radio.

This Major Qualifying Project seeks to extend the capabilities of software defined radio through the design and creation of a wideband RF frontend for a software defined radio development platform called the Universal Software Radio Peripheral (USRP). The RF frontend created in this project extends the frequency range available to software radio applications designed for the USRP, and is compatible with the accompanying open source software platform, GNU Radio. In addition, because all the designs for the USRP daughterboards and motherboards are available under the GPL license, the schematics, PCB designs and layout, and other information for this project will be available under the same license.

The main motivation for creating a wideband transceiver lies in the convenience of having a large frequency range available for software radio applications. Existing daughterboards available for the USRP cover smaller frequency ranges and thus severely limit possible wideband applications that can be made on this platform. The creation of a wideband transceiver is truly a step in the direction of a perfect cognitive radio; able to operate over all frequencies and change any operating parameter, such as transmission power, modulation type, or bandwidth. Design elements of this daughterboard can also be abstracted and applied to other software radio applications, with this report serving as a guide to possible software radio engineers.

Once the general idea of the project was agreed upon, a few objectives were established to make sure the design criteria were met. The first and most important objective was to create a wideband transceiver that can operate over a large range of frequencies with an accurate tunable resolution. Initial plans were to make it tunable between 100 MHz and 1.3 GHz, but after finding components with a larger available range, the final version of the transceiver is tunable between 50 MHz and 2.5 GHz. The second objective was to make the transceiver completely compatible with GNU Radio and the USRP. This includes both physical connections to the USRP and software to allow GNU Radio to control the daughterboard. As the last objective, the transceiver had to be able to operate in full or half duplex modes, again controllable through GNU Radio. To meet these objectives the MQP team had three academic terms with a possible fourth, and a budget of one thousand dollars.

Initial designs of this wideband transceiver explored the possibility of using relays and switches to control the signal path between various VCOs, mixers, or even separate daughterboards; a technique often used for wideband radio applications. This project takes a different approach by interconnecting various wideband components to save board space, reduce power consumption, and decrease complexity compared to an exhaustive system consisting of multiple RF frontends.

Once the initial design was generally determined, simulation had to be used where possible to help improve the design and ensure its feasibility. Unfortunately, there is no conceivable way to simulate the entire design, so only the amplifier and antenna switching stages could be simulated before the PCB design. The design of the low noise amplifiers, power amplifier, and antenna switches used in the design were simulated using S-Parameter data in Agilent's ADS software. Though simulating these components aided in the overall design, the values of the discrete components were difficult to determine because small changes in these component values would lead to drastic changes on the overall shape of the gain of the amplifier stage. Since the simulation did not take into account the effects of trace length and other non-idealities of the final design, the usefulness of the simulation results were brought into question. In the end, the best component values were chosen, and the design remained open to any changes in these values. The design of other daughterboards was also taken into account, with some design aspects of the transceiver similar to other daughterboards wherever possible.

Where simulations fell short in aiding in the design process, evaluation boards provided by generous contributors to this project greatly aided in verifying the overall design of the transceiver. An evaluation board for the RF2051 wideband frequency synthesizer and mixer, along with an evaluation board of the GVA-84+ power amplifier, allowed the creation of a basic prototype tunable between 300 MHz and 2.5 GHz. Experiments in transmitting a simple FM signal over frequencies in this range were successful, with the signal being received by other USRP daughterboards, commercial FM radio receivers, amateur radio receivers, and even the other mixer on the same evaluation board.

With confidence gained from a successful prototype, the first schematic layouts and PCB designs were created using Mentor Graphic's PADS software. This software was chosen because of its features such as stitching vias, impedance calculations, copper pouring, and trace shielding. The design process in this program was relatively straightforward. First, the design is created in schematic form in PADS Logic, linking each schematic component to a footprint file. This schematic is then imported into PADS Layout, where the footprint information is used to create a PCB design and Gerber files needed to fabricate the PCB. Changes to the schematic would be reflected in the PCB design, allowing easy manipulation of the overall design.

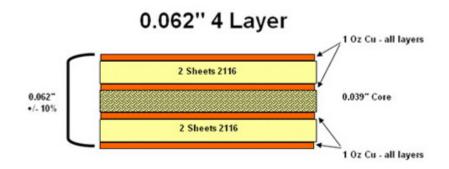

A four layer PCB was used for the transceiver, with a signal layer, ground layer, power layer, and another signal layer. Utilities in the PADS software suite allowed the design parameters, such as minimum trace width and via size, to be changed so the PCB would fit in an affordable price bracket. These features were especially helpful to keep the project within budget, leaving enough money for a PCB revision to fix complications that arose from the initial PCB design.

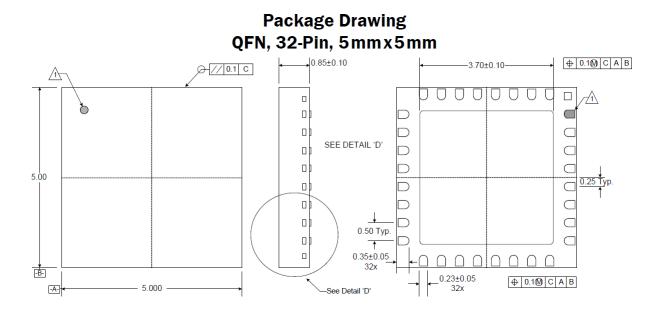

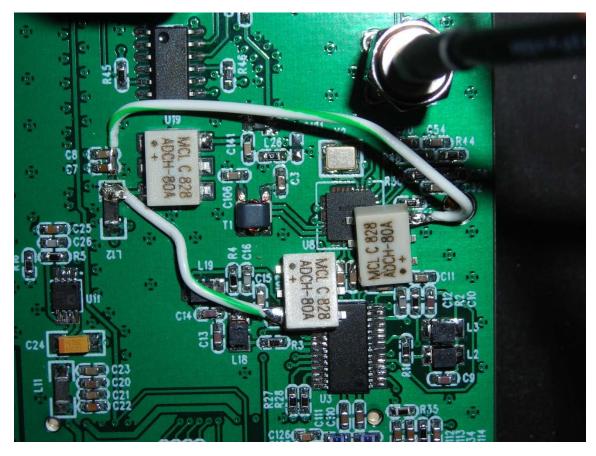

Throughout the entire design process, a common concern was the small package sizes of some of the components, since the VCOs and modulators/demodulators were designed to be soldered by machines. Thankfully, Bob Boisse, a staff member in the ECE department, was able to solder these components to the PCBs. All components on the PCBs were placed by hand with a fine tipped soldering iron under a microscope.

To save time and parts, the components soldered to the PCB were tested at various opportunities to make sure everything was working as planned. In addition, the transmitter side was soldered first. Due to time constraints, if the transmitter half of the board was not functional, the problem would be diagnosed, appropriate changes would be made to the PCB, and a fixed PCB would be ordered. Unfortunately, this was the case. Connecting the USRP's general purpose input/output lines to the voltage regulators caused IO across the entire motherboard to stop working. A quick email to Matt Ettus, creator of the USRP and its daughterboards, revealed that the voltage regulators used in the design could not be controlled by the IO pins; they needed to always be on. A cut trace and jumper wire solved this problem, but further debugging revealed that a PLL filter was left out of the design, ensuring that another PCB revision would be needed.

The second PCB addressed both problems faced with the first PCB, but it was still to be determined if there were any additional problems. Also, the receive side of the first PCB was not soldered or tested because the RF2052 was missing the same PLL loop filter. More problems were expected to be encountered in the second PCB revision, but both time and budget would not allow for a third PCB to be fabricated.

After soldering the transmitter side of the PCB, it was verified that the changes to the design were successful and the transmitter was operating as expected. Connecting the transmitter to the spectrum analyzer revealed that the daughterboard operated over a range of frequencies that is much larger than the initial goals, but expected given the operating frequency of the components used in the design. Unfortunately, tests on the receiver revealed what is most likely a damaged demodulator, but other receiver components were verified to be functional. Software control over the antenna path circuitry also demonstrated that the daughterboard could indeed operate in both full duplex and half duplex mode if both the transmitter and receiver were fully functional. In short, even though the receiver was not functional in time for the deadline, the other objectives were technically met and the project was, overall, a success.

# Table of Contents

| 1  | Introduc        | tion                                                               | 1  |

|----|-----------------|--------------------------------------------------------------------|----|

| 1  | .1 Rac          | lio History                                                        | 1  |

| 1  | .2 The          | Emergence of Software Defined Radio (SDR)                          |    |

| 1. |                 | Testbed: The Universal Software Radio Peripheral (USRP)            |    |

| 1  |                 | Project: A Wideband Transceiver for the USRP                       |    |

|    | 1.4.1           | Objective 1: Tunable between 100 MHz and 1.3 GHz                   |    |

|    | 1.4.2           | Objective 2: Compatible with USRP and GNU Radio                    |    |

|    | 1.4.3           | Objective 3: Full Duplex and Half Duplex Transceiver               |    |

| 2  | Backgro         | und                                                                | 7  |

| 2  | -               | tware Defined Radio                                                |    |

|    |                 | nitive Radio                                                       |    |

|    |                 | Spectrum                                                           |    |

|    |                 | Hardware                                                           |    |

| 3  |                 | on and Prototyping                                                 |    |

|    |                 | plifier Design Simulation                                          |    |

|    |                 | ic Prototype - RFMD RF2051 Evaluation Board and GVA-84+ Amplifier  |    |

| 5  | .2 Dus<br>3.2.1 | Experimentation with RF2051 Evaluation Board                       |    |

|    | 3.2.2           | Upconversion of Basic TX Board Output from 30 MHz to 2.4 GHz       |    |

|    |                 |                                                                    |    |

|    | 3.2.3           | Downconversion of Basic RX Board Input from 2.4 GHz to 30 MHz      |    |

|    | 3.2.4           | Upconversion and Downconversion on the Two Evaluation Board Mixers |    |

|    | 3.2.5           | Evaluation Board Test Results                                      | 17 |

| 3. | .3 Inte         | rfacing the RF2051 with GNU Radio                                  | 19 |

| 3. |                 | pter Summary                                                       |    |

| 4  |                 | ver Design                                                         |    |

| 4  |                 | al Design Overview                                                 |    |

| 4  |                 | al Design Details                                                  |    |

|    | 4.2.1           | Transmit Path                                                      |    |

|    | 4.2.2           | Receive Path                                                       | 39 |

|    | 4.2.3           | Transmit/Receive Switches                                          | 41 |

| 4  | .3 Pov          | ver Analysis of Final Design                                       |    |

| 5  |                 | sign                                                               |    |

| 5  |                 |                                                                    |    |

| 5  |                 | out                                                                |    |

| 5  | 5               | duction                                                            |    |

|    |                 | ial Tests                                                          |    |

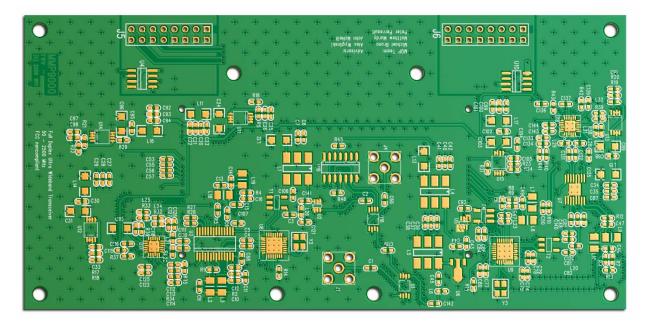

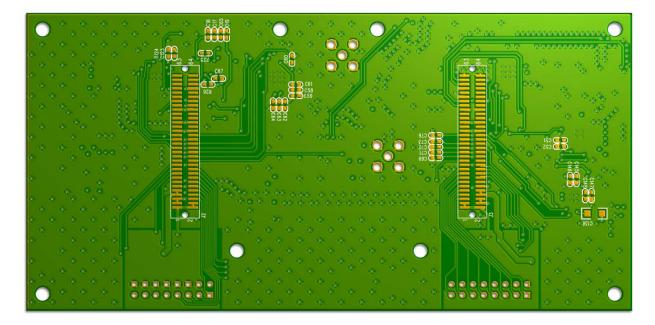

| 5  |                 | rd Renderings                                                      |    |

|    |                 | pter Summary                                                       |    |

| 6  |                 | ction, Debugging, and Testing                                      |    |

| 6  |                 | dering and Component Placement                                     |    |

| 6.1.1 Second Soldered PCB (rev. A)      | 53 |

|-----------------------------------------|----|

| 6.2 Testing and Debugging the first PCB |    |

| 6.3 Second PCB                          |    |

| 6.4 Chapter Summary                     |    |

| 7 Results                               |    |

| 7.1 Transmitter                         |    |

| 7.2 Receiver                            |    |

| 7.3 Chapter Summary                     | 71 |

| 8 Conclusion                            |    |

| 9 Bibliography                          |    |

| 10 Appendix A - Source Code             |    |

| 10.1 fmtx_mmp.py                        |    |

| 10.2 fmrx_mmp.py                        |    |

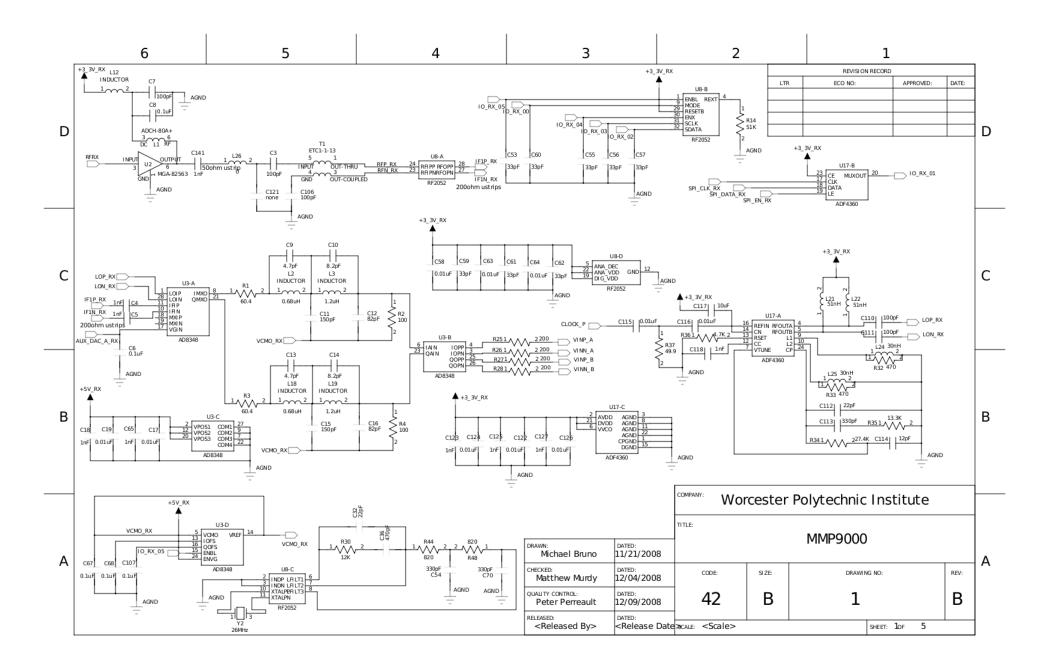

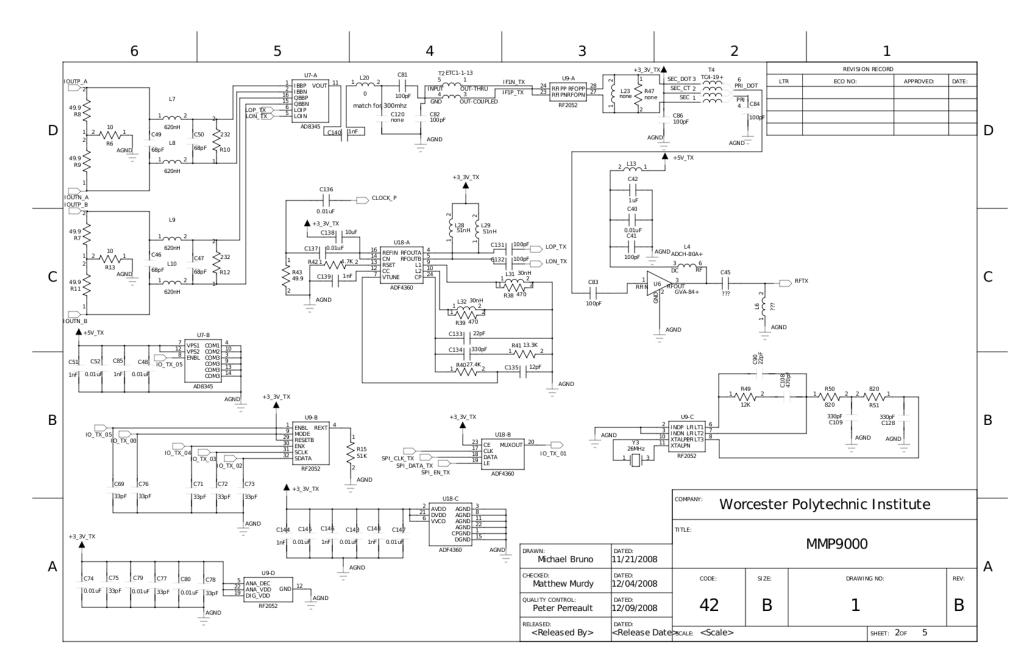

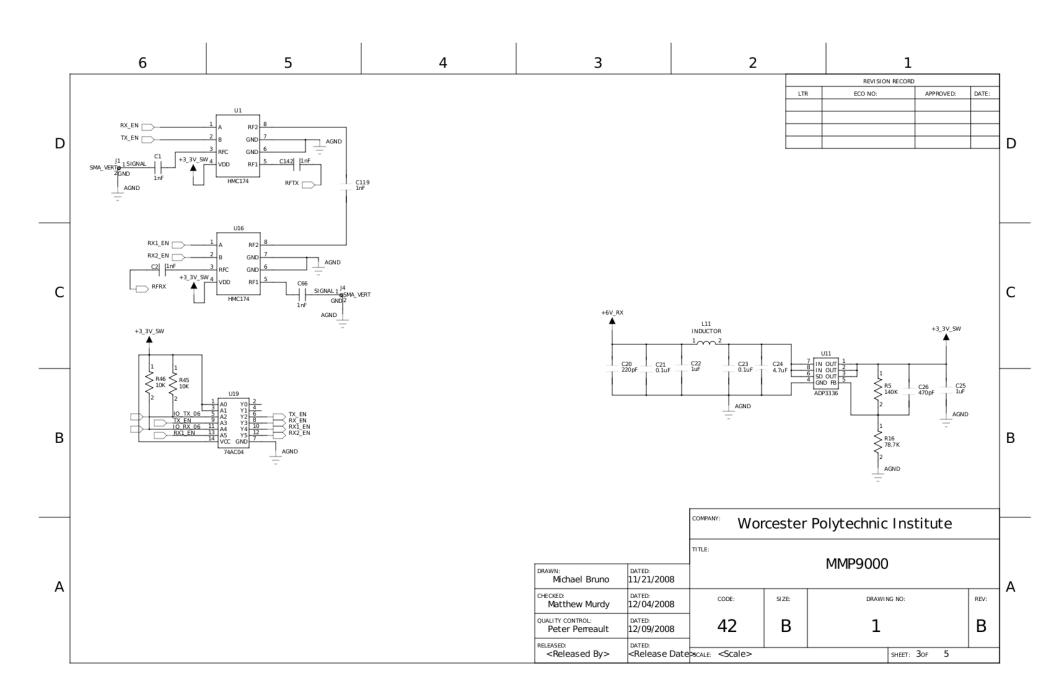

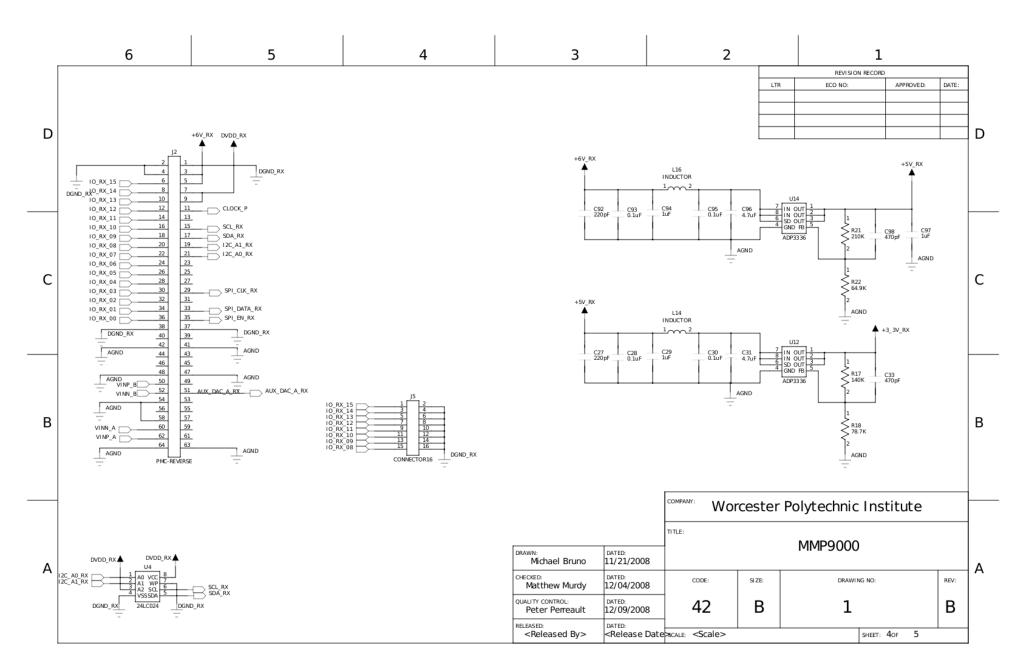

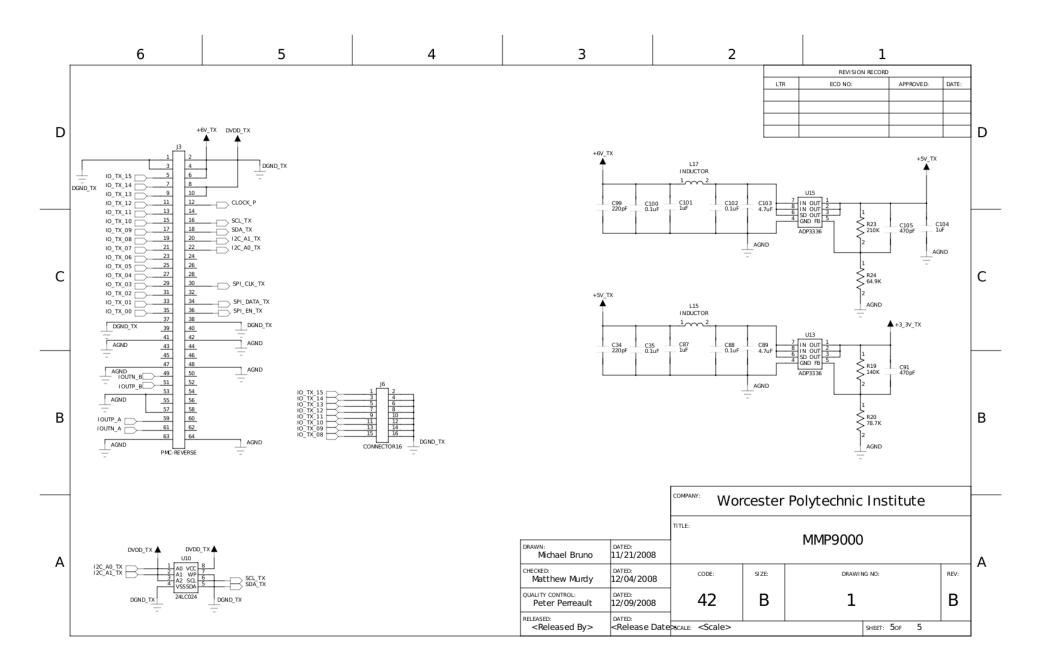

| 11 Appendix B – Schematic               |    |

| 12 Appendix C – Parts List              |    |

# Table of Figures

| Figure 1 - The Electromagnetic Spectrum from long waves to gamma-rays. (Image released                 |  |

|--------------------------------------------------------------------------------------------------------|--|

| under Creative Commons Share Alike 3.0)                                                                |  |

| Figure 2- Spectral Occupancy Measured at Seven Locations - study done by the Shared                    |  |

| Spectrum Company (reprinted with permission from the Shared Spectrum Company) [2]                      |  |

| Figure 3 - The USRP motherboard components and layout, including the mixed signal                      |  |

| processors, FPGA, connectors for daughterboards, and DC power and USB connections                      |  |

| Figure 4 – An example of a USRP Daughterboard, the RFX2400. The RFX2400 board features a               |  |

| transmit and receive range from 2.3 to 2.9 GHz, with an output power of up to 50 mW                    |  |

| Figure 5 - Software Defined Radio block diagram of a transmitter and receiver7                         |  |

| Figure 6 - 1.7 GHz to 2.7 GHz on the frequency allocation chart 10                                     |  |

| Figure 7 - MMP9000 amplifier stage simulation schematic for both transmit and receive                  |  |

| amplifier sections of the design. The transmit side includes the MGA82563 low noise amplifier          |  |

| and the GVA-84+ 5 V power amplifier, while the receive side incorporates only the low noise            |  |

| amplifier. Also included are the DC biasing circuits to power the amplifiers and the antenna           |  |

| switch. The input and output of the amplifier section are both connected to $50 \Omega$ terminators to |  |

| match the impedance of the rest of the circuit                                                         |  |

| Figure 8 – RF2051 evaluation board                                                                     |  |

| Figure 9 - GVA-84+ power amplifier evaluation board                                                    |  |

| Figure 10 - Mixing a signal up and then back down using the RF2051 evaluation board 16                 |  |

| Figure 11 – Transmitted signal directly out of the RF2051 mixer                                        |  |

| Figure 12 - Transmitted signal directly out of the GVA-84+ amplifier                                   |  |

| Figure 13 - Transmitted signal amplified by the GVA-84+ and transmitted over the air 19                |  |

| Figure 14 - RF2051 evaluation board connected to the USRP                                              |  |

| Figure 15 - RF2051 serial read timing diagram                                                          |  |

| Figure 16 - RF2051 serial write timing diagram                                                         |  |

| Figure 17 - Block diagram of the RFX daughterboard series transmit path                                |  |

| Figure 18 - Block diagram of the RFX daughterboard series transmit/receive switch                      |  |

| configuration                                                                                          |  |

| Figure 19 - Block diagram of the RFX daughterboard series receive path                                 |  |

| Figure 20 - Initial design idea with switchable, narrowly tunable transceiver frontends                |  |

| Figure 21 - Block diagram of the final design transmit path                                            |  |

| Figure 22 - Block diagram of the final design transmit/receive switch configuration 29                 |  |

| Figure 23 - Block diagram of the final design receive path                                             |  |

| Figure 24 - Block diagram of the final design transmit path with actual components 30                  |  |

| Figure 25 - Block diagram of the final design transmit/receive switch configuration with actual        |  |

| components 30                                                                                          |  |

| Figure 26 - Block diagram of the final design receive path with actual components                      |  |

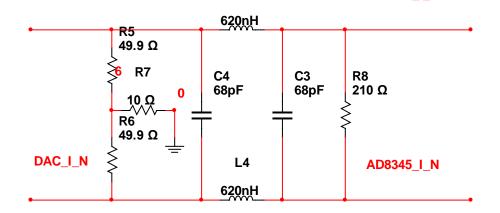

| Figure 27 - 25 MHz Low pass filter between DACs and the AD8345 quadrature modulator 32                 |  |

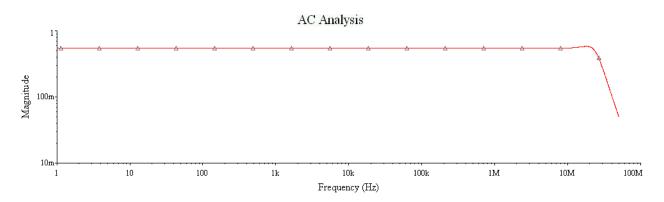

| Figure 28 - AC analysis of the low pass filter between the DACs and AD8345 quadrature                  |

|--------------------------------------------------------------------------------------------------------|

| modulator. The 3dB bandwidth is about 25 MHz. The passband magnitude is about 600 mV,                  |

| which corresponds to 1.2 Vp-p                                                                          |

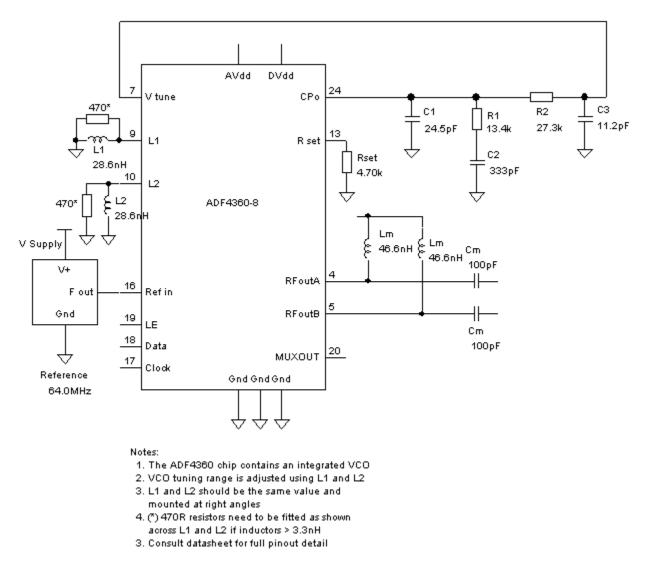

| Figure 29 - Schematic for the local oscillator using the ADF4360-8 IC, tuned for 280 MHz to            |

| 320 MHz at 1 MHz intervals. Generated by ADIsimPLL                                                     |

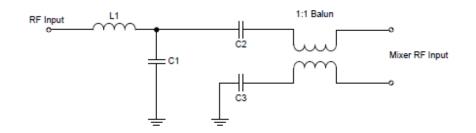

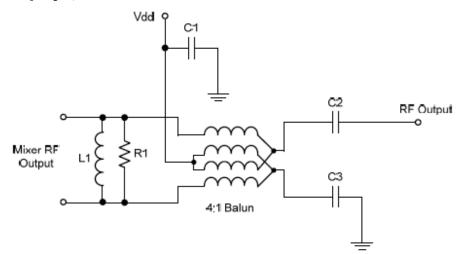

| Figure 30 - Matching circuit for the RF2052's RF mixer input port. It converts the differential        |

| inputs to a 50 $\Omega$ single ended input. Initially the board will be tested with C2 and C3 equal to |

| 1000 pF, and L1 a 0 $\Omega$ jumper, and C1 not fitted. The 1:1 Balun is an M/A-COM ETC1-1-13. 35      |

| Figure 31 – Matching circuit for the RF2052's RF mixer output port. It converts the differential       |

| outputs to a 50 $\Omega$ single ended output. Initially the board will be tested with C1, C2, and C3   |

| equal to 100 pF, and L1 and R1 not fitted. The 4:1 Balun is Minicircuits' TC4-19+                      |

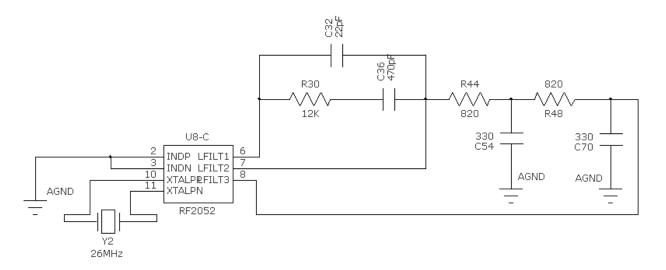

| Figure 32 - The loop filter for the RF2052, configured for a wideband design. This is the same         |

| loop filter as used for the RF2051 evaluation board                                                    |

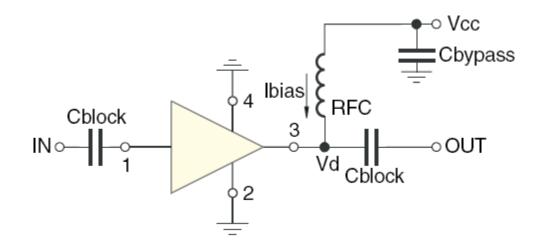

| Figure 33 - Schematic for the recommended power amplifier circuit. The amplifier is powered            |

| with $V_{CC}$ through the RF choke at the output. This DC power is blocked by Cblock, while the        |

| AC output is allowed through                                                                           |

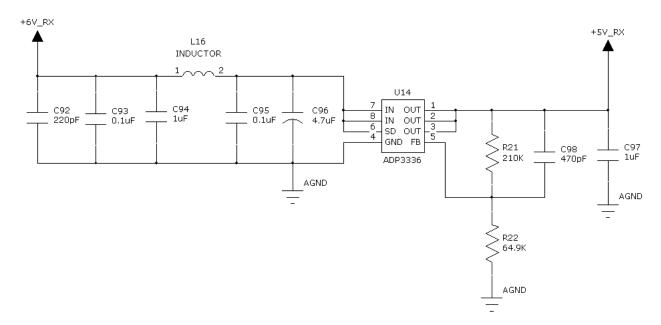

| Figure 34 - Voltage regulator circuit using the ADP3336. The input voltage is 6 V and the output       |

| voltage is 5 V. R21 and R22 set the output voltage. L16 and all the capacitors clean the input and     |

| output voltages by removing any ripple present                                                         |

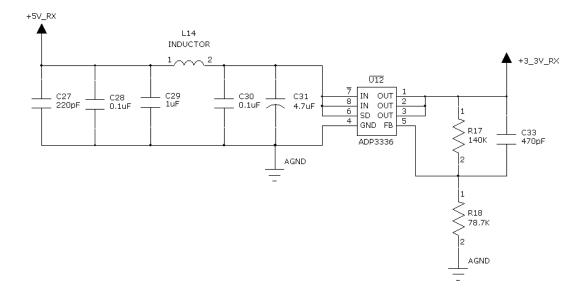

| Figure 35 - Voltage regulator circuit using the ADP3336. The input voltage is 5 V and the output       |

| voltage is 3.3 V. R17 and R18 set the output voltage. L14 and all the capacitors clean the input       |

| and output voltages by removing any ripple present                                                     |

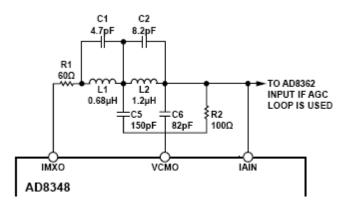

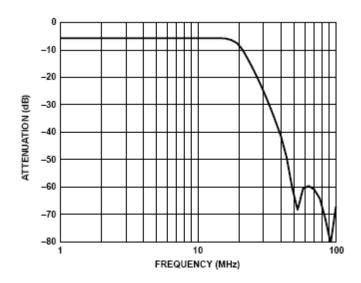

| Figure 36 - Antialiasing filter used for the ADCs on the USRP. This filter is a 100 $\Omega$ , fourth- |

| order elliptic low-pass filter with a 3 dB cutoff frequency of 20 MHz 40                               |

| Figure 37 - Frequency response of the antialiasing filter. Note that the cutoff frequency is           |

| 20 MHz                                                                                                 |

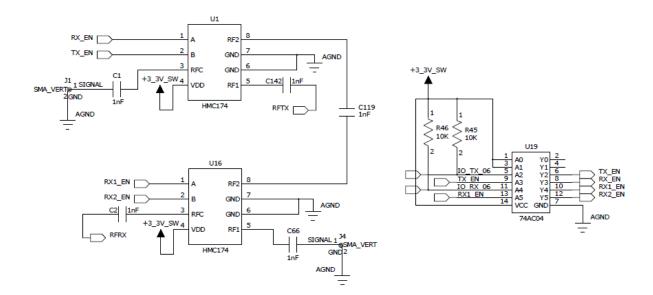

| Figure 38 - T/R switch circuit allowing both half and full-duplex operation                            |

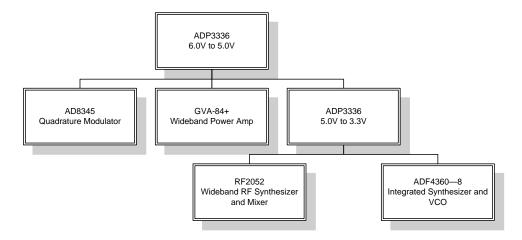

| Figure 39 - Transmit path power hierarchy. The top row is the first voltage regulator powered          |

| with 6V by the USRP. The second row is powered with 5V provided by the first voltage                   |

| regulator. The third row is powered with 3.3V provided by the second voltage regulator                 |

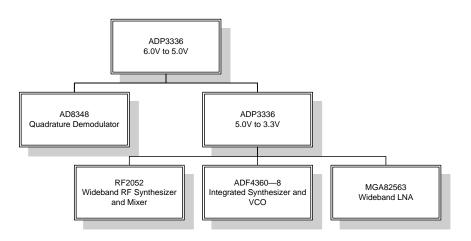

| Figure 40 - Receive path power hierarchy. The top row is the first voltage regulator powered           |

| with 6V by the USRP. The second row is powered with 5V provided by the first voltage                   |

| regulator. The third row is powered with 3.3V provided by the second voltage regulator                 |

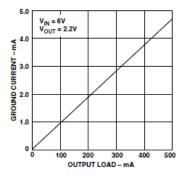

| Figure 41 - Ground Current vs. Load Current                                                            |

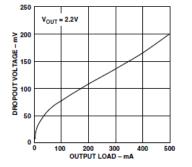

| Figure 42 - Dropout Voltage vs. Load Current                                                           |

| Figure 43 - Internal stack-up of PCB                                                                   |

| Figure 44 - The top layer of the PCB                                                                   |

| Figure 45 - The bottom layer of the PCB                                                                |

| Figure 46 - QFN Package Drawing for the RF2052                                                         |

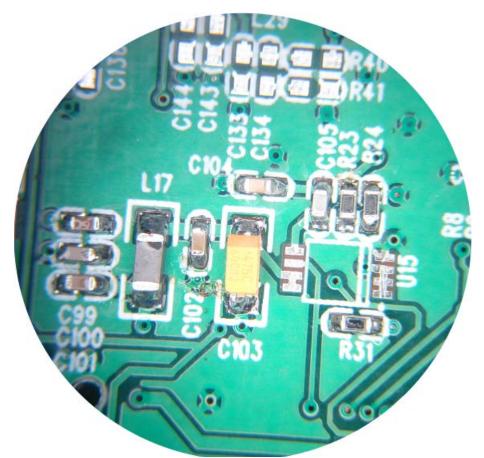

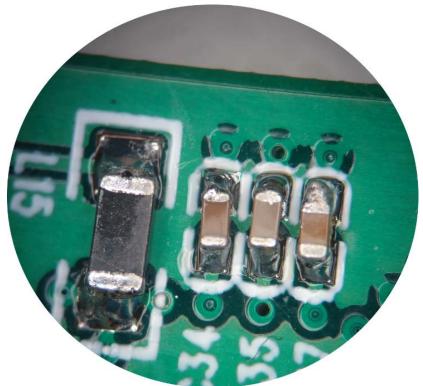

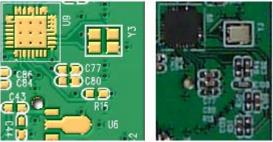

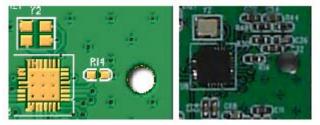

| Figure 47 - Microscope view of the PCB while soldering down components                                 |

| Figure 48 - Microscope view of solder joints for three capacitors and an inductor           | . 53 |

|---------------------------------------------------------------------------------------------|------|

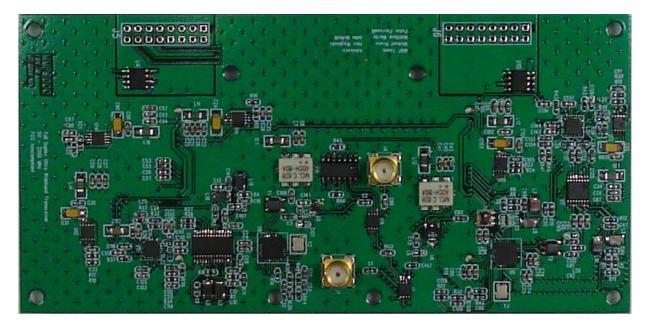

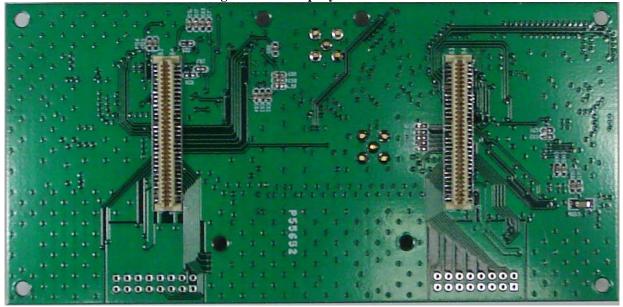

| Figure 49 -The top layer of the PCB                                                         | . 54 |

| Figure 50 - The bottom layer of the PCB.                                                    | . 54 |

| Figure 51 - Segment of the PCB with and without the PLL loop filter for the RF2052 on the   |      |

| transmit side on the first and second PCBs                                                  | . 56 |

| Figure 52 - Segment of the PCB with and without the PLL loop filter for the RF2052 on the   |      |

| receive side on the first and second PCBs.                                                  | . 56 |

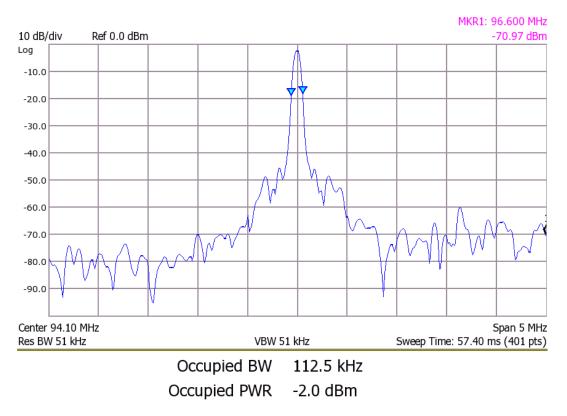

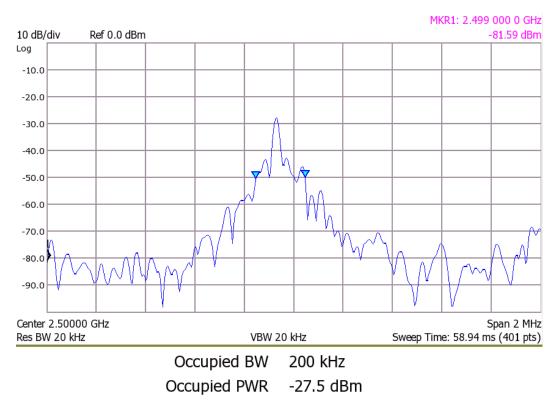

| Figure 53 - Spectrogram of FM transmission test at 94.1 MHz.                                | . 58 |

| Figure 54 - Spectrogram of FM transmission test at 2.5 GHz.                                 | . 59 |

| Figure 55 - Marker designates what was considered to be the next peak when making the       |      |

| measurements found in Table 3                                                               | 61   |

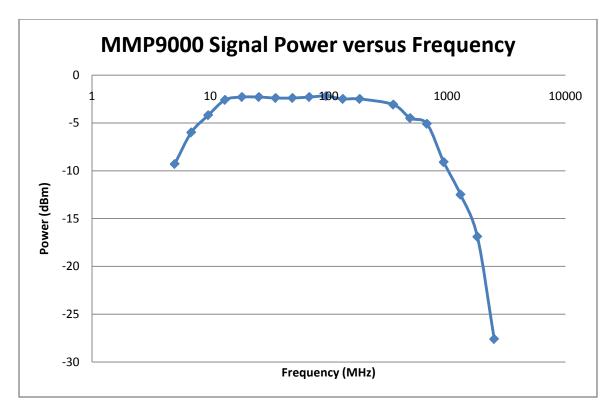

| Figure 56 - Signal frequency versus power from 5 MHz to 2500 MHz.                           | . 62 |

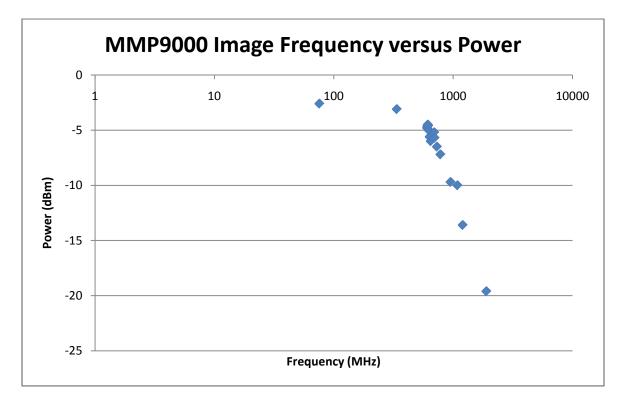

| Figure 57 - Signal image frequency versus power for signals ranging from 5 to 2500 MHz      | . 62 |

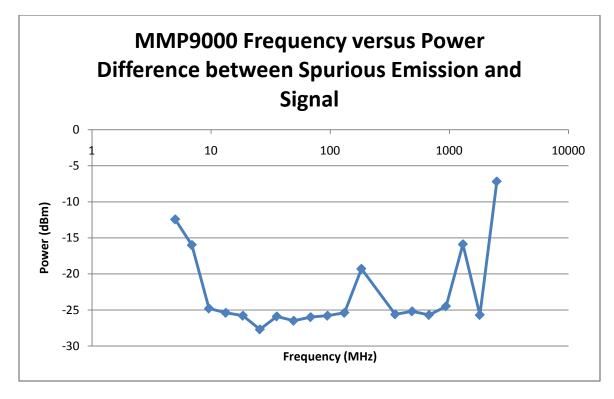

| Figure 58 - Difference between signal power and spurious emission power for signals ranging |      |

| from 5 MHz to 2500 MHz.                                                                     | . 63 |

| Figure 59 - Transmission with RF2052 LO frequency set to 493 MHz using VCO2                 | . 64 |

| Figure 60 - Transmission with RF2052 LO frequency set to 493 MHz using VCO1                 | . 65 |

| Figure 61 - Addition of RF chokes to the output of the RF2052 mixer                         | . 67 |

| Figure 62 - 100 MHz signal from Basic TX board generated for testing the receiver           | . 68 |

| Figure 63 - 100 MHz signal mixed to 300 MHz. This shows that the LO and mixer in the recei  | ive  |

| side RF2052 are both working                                                                | . 69 |

| Figure 64 - Local oscillator signal for the AD8348 quadrature demodulator at 295 MHz. This  |      |

| shows that the ADF4360-8 frequency synthesizer is working correctly                         | . 70 |

| Figure 65 - Output from the AD8348 quadrature demodulator. The input signal is at 300 MHz,  | ,    |

| and the LO is at 295 MHz. The output should be a signal at 5 MHz. The fact that it is not   |      |

| indicates that the IC is damaged.                                                           |      |

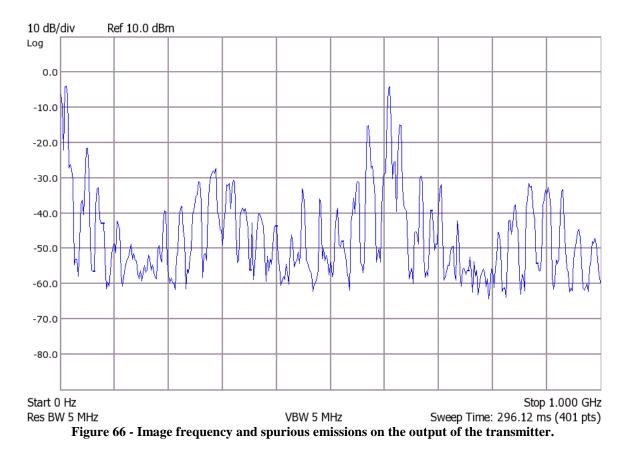

| Figure 66 - Image frequency and spurious emissions on the output of the transmitter         | . 73 |

#### **1** Introduction

#### 1.1 Radio History

The word *spectrum* was initially used to refer to the range of colors observed when light passed through a prism. As an increasing number of radiation types in the electromagnetic spectrum were discovered, the term spectrum began to be used to describe any type of wave. In modern times, the term has found such widespread use that it is often used to describe any type of range of related objects or values, such as the political spectrum. Some years after James Clerk Maxwell predicted the propagation of electromagnetic waves in the mid 1800s, they were put to use in communication using spark gap transmitters. This type of design, which is incredibly impractical according to today's standards, used voltages on the order of tens of thousands of volts to charge an antenna, emitting electromagnetic radiation as the spark gap discharged. Unfortunately, this type of design does not take too much care of spectral usage, and few spark gap stations could be used in the same geographic area without causing interference to each other.

Figure 1 - The Electromagnetic Spectrum from long waves to gamma-rays. (Image released under Creative Commons Share Alike 3.0)

It was around this time that people realized the electromagnetic spectrum is a commodity. However, unlike copper, wool, or corn, the spectrum is, for the most part, invisible, location dependent, and theoretically limitless. In the United States, regulation of this commodity is the responsibility of the Federal Communications Commission (FCC). Without such regulation, interference and other problems communicating would be much more prevalent. Thankfully, we have come a long way since the spark gap transmitter, with advances in transceiver design allowing simultaneous usage of the electromagnetic spectrum between many users. Despite technical advances, the electromagnetic spectrum is still a much sought after commodity. For example, the FCC recently ended an auction on the 700 MHz band with 101 winning bidders awarded 1091 licenses and a total of roughly 19 billion US dollars in bids. [1]

As usage of the electromagnetic spectrum increases steadily, the current approach to spectrum management is beginning to show signs of weakness. The FCC has designated different portions of the spectrum to different uses or services, for example, portions of the electromagnetic spectrum have been sectioned off for use in AM, FM, and TV broadcasting, amateur radio, maritime, satellite use, and many, many other uses. In the recent years, this approach has become more of a problem, since there is a limit to the number of users that can simultaneously use a portion of the spectrum at the same time and in the same geographical area. New applications are found for the spectrum, but there is a limited quantity of spectral space to serve these new uses.

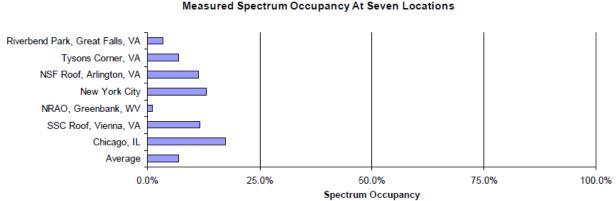

One of the main problems leading to spectral crowding is the inefficient usage of the spectrum. Measurements of spectral occupancy, even in largely metropolitan areas, are incredibly low, at less than 20% (See Figure 2). Despite the low values of spectral occupancy, some frequency ranges are extremely overcrowded, such as the cell phone bands, around 850 MHz and 1800 MHz. [2] An obvious solution would be to allow services that need more bandwidth to take up unoccupied spectrum, but this type of operation is typically disallowed by the FCC because it causes interference.

Figure 2- Spectral Occupancy Measured at Seven Locations - study done by the Shared Spectrum Company (reprinted with permission from the Shared Spectrum Company) [2]

Fortunately, regulating agencies such as the FCC are aware of this problem, and to offset the effects of spectral overcrowding there are a few frequency bands set aside for general use, such as the Industrial, Scientific, and Medical (ISM) band. It is in these bands that services such as Wi-Fi and Bluetooth have thrived, but there is a large amount of interference due to their widespread usage.

There are several techniques to help combat interference due to overcrowding, but in anticipation of changes in spectral laws, the next wave of radio technology seeks to make more efficient use of the electromagnetic spectrum with smarter radios. These radios, called *cognitive radios*,

monitor the wireless channel to choose the best parameters for transmission, such as modulation type or frequency. Clearly, the next step in radio history lies in effective, efficient, and intelligent use of spectral space, along with improvements in licensing and spectral management.

## **1.2** The Emergence of Software Defined Radio (SDR)

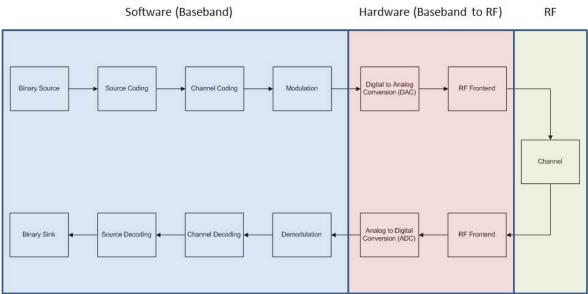

Software defined radio (SDR) is the technology enabling modern advances in cognitive radio. Since the invention of the term in 1991, SDR has generally referred to a radio whose functionality is at least partially controlled or implemented in software. To achieve this, RF components such as mixers and filters are moved to the software domain, where a computer or digital signal processor performs baseband signal processing. An ideal software radio would be able to replicate any waveform on any frequency, most likely by connecting digital-to-analog (DAC) and analog-to-digital converters (ADC) directly to an antenna. [3] The emergence of cheap high speed DACs and ADCs has made the ideal software radio concept closer and closer to a reality, while the ubiquity of personal computers and digital signal processors has caused quite a boom in the development of SDR and, since they are fundamentally related, cognitive radio.

Wireless devices that can be described as SDR have actually been around for quite some time, initially finding their niche in military applications before finding applications in the civilian market. Military programs such as SPEAKeasy sought to enable communication and interoperability between different, conflicting types of military radio. [4] The SPEAKeasy project was very ambitious, and the first prototype worked, but design choices of programming waveforms in low level assembly language meant that the software was not compatible with better processors as they were developed. Note that the Phase I prototype of SPEAKeasy was large enough to fit into the back of a truck. [5]

More recent software radio products and development testbeds take on a more modular approach, as to not have the same fate as the early prototype of the SPEAKeasy project. Commercial products, such as Vanu Inc.'s Anywave software radio, incorporate multiple cellular access standards into a simpler interface by using a software defined radio architecture. Since the cellular standards are implemented in software, they can be changed on the fly to adapt to different user needs of each cell, rather than by the costly approach of replacing RF hardware. This also means that they can easily be upgraded to match new standards. [6] To increase the effectiveness and improve the aging process of a software radio platform, most developers seek to use portable code for their software, reusable components that can work under different waveform configurations and generic hardware that can easily be upgraded. [7]

### **1.3 The Testbed: The Universal Software Radio Peripheral (USRP)**

This project is based on the Universal Software Radio Peripheral, a research testbed and hardware development tool for software defined radio. The USRP, developed by Matt Ettus of Ettus Research LLC, has found significant popularity in cognitive radio research and general SDR studies and applications due to its relatively low cost, simple configuration, and its ability to work with GNU Radio, an open source software suite for SDR development. In addition to working with open source software, the schematics and PCB layouts for the USRP are also available online, free of charge.

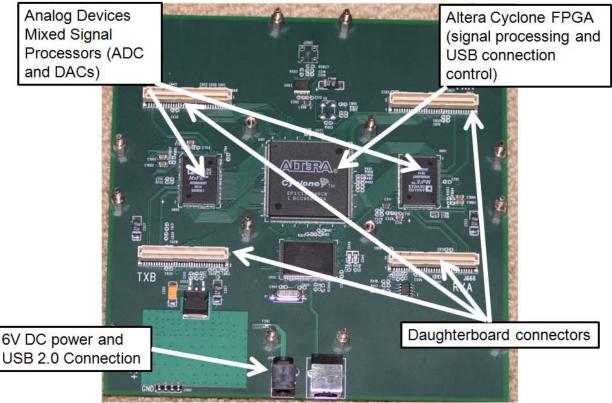

The USRP is based on a motherboard/daughterboard concept. Daughterboards serve as a radio interface for the USRP motherboard, which is mainly concerned with providing a connection between the daughterboards and a PC. The motherboard connects to a PC by a USB 2.0 connection, giving it the ability to send up to 16 MHz of RF bandwidth in either direction. The motherboard contains 4 ADCs and 4 DACs, along with digital I/O lines to control connected daughterboards. Two daughterboard transceivers can be connected to the motherboard. Figure 3 and Figure 4 below show the design of the motherboard, along with an example of a daughterboard.

Figure 3 - The USRP motherboard components and layout, including the mixed signal processors, FPGA, connectors for daughterboards, and DC power and USB connections.

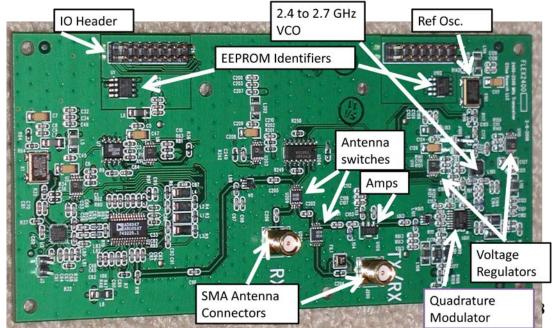

Figure 4 – An example of a USRP Daughterboard, the RFX2400. The RFX2400 board features a transmit and receive range from 2.3 to 2.9 GHz, with an output power of up to 50 mW.

#### 1.4 The Project: A Wideband Transceiver for the USRP

This project is concerned with building a daughterboard for the USRP, specifically, a wideband transceiver that would allow the USRP to operate over a frequency range greater than what current daughterboards can offer. The following objectives were established at the beginning of the project to ensure success:

#### 1.4.1 Objective 1: Tunable between 100 MHz and 1.3 GHz

The main objective of this project is to have a wideband transceiver that could operate in a large range of frequencies with an accurate resolution of operating frequencies. The initial range was rather arbitrarily chosen by examining a frequency chart and the acceptable frequency range for use on the discone antenna that is available in the lab. In the end, based on components that were chosen, it is expected that the transceiver will be able to operate over an even greater range, but the design will also have to take parasitic effects of high frequency signals into consideration, which will have a negative effect on the performance of the prototype.

#### 1.4.2 Objective 2: Compatible with USRP and GNU Radio

In order to ensure correct operation, the prototype must properly interface with the USRP. This means the prototype must physically connect with the USRP and be controlled by software through GNU Radio, in order to change frequency and other parameters of the daughterboard. In addition, the prototype needs to be recognized the same way other available daughterboards are recognized by GNU Radio.

#### **1.4.3** Objective 3: Full Duplex and Half Duplex Transceiver

The prototype needs to be able to act as a transceiver, such that it can both transmit and receive according to the needs of the user. Since the USRP has an ADC and DAC for receiving and transmitting, this functionality is a natural extension of the capabilities of most daughterboards. The mode of transceiver operation, whether half duplex or full duplex, will be controlled through software.

### 2 Background

This chapter will expand upon required background information needed to understand the motivation behind this project. A brief explanation of topics such as software defined radios, cognitive radio, the RF spectrum, and RF hardware is provided to aid the reader in understanding topics relevant to this project and provide more information on topics touched upon in the introduction.

## 2.1 Software Defined Radio

Since software defined radio is such a relatively new concept, it is difficult to find a consensus on a single definition. Essentially, it is a radio whose functionality is at least partially implemented in or controlled by software. The SDR Forum, in collaboration with IEEE, has defined it as "radio in which some or all of the physical layer functions are software defined." [8] To help get a better idea of what software defined radio is, it's helpful to examine its applications. Traditionally, radios were designed with a single target application in mind, such as receiving music, making a phone call, or receiving GPS data, but as technology advances, along with wireless standards and protocols, the need for multipurpose radios to support different types of information, modulation types, frequency ranges, bandwidth, and other aspects of radio design is ever increasing. [9] See Figure 5 for a block diagram representation of a software radio system.

Figure 5 - Software Defined Radio block diagram of a transmitter and receiver.

As software radio concepts become more advanced, the trend is to move digital signal processing aspects closer and closer to the antenna, both to support radio flexibility and to drive down costs of expensive RF stages. Alternatively, another solution would be to design a completely flexible software controlled RF front end. Both approaches have their limitations, so current solutions lie

somewhere in between the two. Practical software radios keep signal processing in the digital domain as much as possible [9]. A typical approach for receivers is to digitize the signal at the intermediate frequency stage of a super heterodyne receiver, so the signal travels through the antenna, is filtered, amplified, and mixed with a local oscillator. After this stage, the signal is fed into an analog to digital converter, where the digital baseband processing is done on the sampled signal. This approach is advantageous because it is often cheaper and easier to do signal processing in the digital domain, as costs for microprocessors and FPGAs continue to drop while they increase in processing power.

The number of applications for software defined radio is nearly endless; since it can be applied anywhere there is a need for greater spectral flexibility or interoperability between radio modes. Software radio has already had success in the military, where people's lives depend on effective communications. For example, a military program called SPEAKeasy employs many aspects of software radio to provide communications interoperability between 10 different types of military radios. The SPEAKeasy radio is "an open architecture, simultaneous multichannel, multiband, multimode software programmable/re-programmable, networked and secure radio system that operates continuously and contiguously in the radio spectrum from 2 MHz to 2 GHz." [10]

Software radio has also seen some success in the consumer market, especially in the mobile phone sector. Vanu's Software Radio is the first wireless infrastructure solution to provide cellular base stations the ability to simultaneously operate in GSM, CDMA, and iDEN modes. Clearly, this technology has the power to vastly change how cellular networks operate, provided better roaming coverage at different cell sites and increasing interoperability between different carriers and service types. [7] As DAC/ADC sample rates and processing speeds continue to improve, it is only a matter of time until software defined radios break into the consumer market to provide better features and services to the consumer.

#### 2.2 Cognitive Radio

The term cognitive radio was first coined in the year 2000 by Joseph Mitola in his doctoral thesis entitled "Cognitive Radio: An Integrated Agent Architecture for Software Defined Radio." [11] According to Mitola, cognitive radio technology is the "intersection of personal wireless technology and computational intelligence." Mitola also defines a cognitive radio as "a really smart radio that would be self-aware, RF-aware, user-aware, and that would include language technology and machine vision along with a lot of high-fidelity knowledge of the radio environment." [12] Cognitive radio clearly goes hand in hand with software defined radio; together, they can efficiently manage communications to provide greater throughput and efficient use of the RF spectrum.

Technological advances in cognitive radio have occurred due to the limited resource available in the RF spectrum. As the RF spectrum gets increasingly crowded by various users, the frequency allocation approach used by the FCC begins to show its limitations. According to the FCC's Spectrum Policy Task Force, spectrum policy is not keeping up with increasing demand on the market. [13] Cognitive radio offers a solution to this problem. In order to decrease interference between different users of the spectrum, the FCC has a policy of assigning different frequency bands for different services. Unfortunately, this is not very efficient, with usage not spread evenly across the spectrum. Cognitive radio, along with software defined radio, offers the solution of spectrum sensing, where a smart radio can change a device's frequency and mode of operation to provide efficient use of the spectrum and more effective communication between users.

#### 2.3 RF Spectrum

Methods for accessing the RF spectrum have evolved greatly over time. Since its accidental discovery by Heinrich Hertz in 1887, the overall application for the spectrum has been to relay information over distances too long or inconvenient for wires [14]. There has always been a need to move information between two points. However, an increasing amount of information is transmitted every day since it is becoming easier to do. With many people all transmitting at the same time, using noisy transmitters, the spectrum soon became very crowded. As an answer to this issue, a new technology was developed. By making use of a previously invented piece of technology, the bandpass filter, the FCC began dividing up the spectrum because the new filter allowed people to transmit and receive on isolated parts of the spectrum. It does this by removing all frequencies except the desired one before the signal is amplified and transmitted. The filter removes all frequencies above a certain limit and all frequencies below a certain limit, leaving a gap in the middle. This basically makes it a high pass and a low pass filter that have been stuck together. The gap in the middle is the desired frequencies, called the pass band.

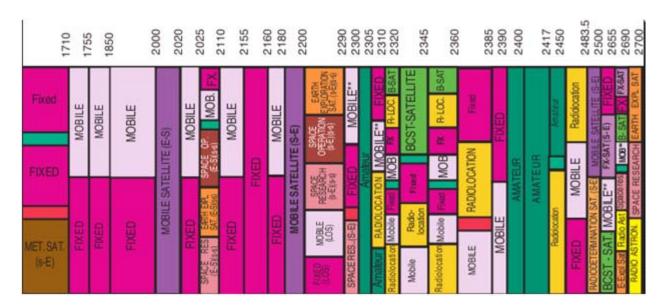

The FCC has carefully divided the spectrum by application. Since there are already so many different applications for radio, the spectrum has quickly become extremely crowded. As a result, the spectrum has been divided to the point where certain parts of cannot be divided again to allow new applications to have their own frequency allocations. Figure 6 shows a small part of the spectrum. This portion includes 2.4 GHz Wi-Fi, Bluetooth, cordless phones and even microwave ovens.

Figure 6 - 1.7 GHz to 2.7 GHz on the frequency allocation chart

The FCC is a U.S. Federal Agency, which means that their frequency allocations are defined by law. In 2005, the Federal Government authorized the FCC to fine stations up to \$325,000 for misuse of their licenses [15]. Since there are strict rules about what can be transmitted on which frequency, the FCC has created a set of frequencies that anyone can use. Examples of services operating on these frequencies are citizens band (CB) radio, the family radio service (FRS) and the industrial, scientific and medical (ISM) bands. All of these services may be used by any person in the United States without a license. These services are very limited, both in the amount of power they are allowed to use and the number of available channels. According to Part 18 of the FCC rules, the ISM band is open for non-licensed use in the United States. However, communications devices must accept any interference they receive from other ISM equipment and may not intentionally cause such interference.

On the other hand, amateur radio is an option available to people who want to get licensed. Anyone interested is allowed to pay a fee to take a certification exam. This allows them to transmit with more power than the other services and on many more frequencies. However, the station operators are still limited in what they are allowed to transmit on the bands. [16].

In a different light, since cognitive radios are much less limited in what they can transmit and what band they are allow to transmit on, there are now people trying to encourage the use of cognitive radios. These are radios which are aware of their surrounds. They know which frequencies are being used and which ones are open. This allows them to make the best use of the available spectrum at a given time. The problem is that this model violates the current FCC rules by operating on unauthorized or private frequencies. Cognitive radios, along with a spectrally agile band plan would allow the general public to use any part of the RF spectrum for any purpose. The difference from the current model is that a cognitive radio would keep things

organized automatically, opposed to the fence-out model currently being employed by the FCC, where access to portions of the spectrum depends on license or ownership. **[17]**

# 2.4 **RF Hardware**

Typical RF frontend hardware is tuned for a narrow range of frequencies. The various filters and components used thus will only operate correctly over that narrow range of frequencies that they are designed to operate on. If a certain application needs to operate on several different radio frequencies, the typical approach is to use multiple RF frontends and switch between them. However, this approach is not ideal, especially for cognitive radio, because it requires an entire RF frontend for each desired narrow range of frequencies. Ideally, a cognitive radio should be able to tune itself to any frequency over a wide range, to facilitate the most efficient communications based on channel conditions [18][19].

Most narrowband RF frontends today use a heterodyne receiver design. This converts the RF signal to an IF (intermediate frequency) signal. This is useful because this uses a process called heterodyning, which mixes the incoming signal with a local oscillator to easily step it down to a more manageable frequency. However, the problem with this design is that it actually shifts two signals to the IF signal: the desired RF signal as well as another frequency called the image frequency. Because of this it requires an image rejection filter to remove the image frequency. For a receiver that must be tunable over a wide range of frequencies, this design would require the image rejection filter to be tunable over that range. **[20]**

Another design is called a direct conversion receiver. This receiver does not require a local oscillator and mixer to help reduce the frequency of the signal. Rather than converting the RF signal to an IF signal, it converts the RF signal directly to baseband. The approach does not shift an image frequency to baseband, and thus does not require an image rejection filter. Therefore this design is more attractive for wideband RF frontend. [20] [18]

To convert the RF signal to baseband, a LO (local oscillator) is required at the frequency of the desired RF signal. If the RF frontend is to be tunable over a wide range, its LO must also be tunable over this wide range. There are a several ways to create a tunable LO. Typically a VCO and PLL are used. A VCO is an a Voltage Controlled Oscillator, which works exactly as one would think; raising the voltage increases the frequency of the oscillator and lowering the voltage decreases the frequency of the oscillator. A PLL is used to keep an oscillator from drifting out of phase by locking it to the set frequency. Numerically (sometimes called digitally) controlled oscillators also exist. While a single tunable oscillator may not cover the entire frequency range, it is possible to combine a few together followed by a programmable frequency division stage to cover the entire desired range. This is the approach taken in RFMDs RF2051 IC, which is what will be used in the design. [18][19]

# **3** Simulation and Prototyping

The application of simulations in the design of this project was limited because of the complexity of the overall design. Simulations of the amplifier and antenna switching stage were utilized to gain a better understanding of the design, but due to sensitivities in component values, the application of these simulations was limited. Instead, evaluation boards were used to create a prototype of the final design to better understand how various components would work in the overall system.

Once the prototype was tested and functional, the final design was laid out in PCB design software. Since every element of the design was not included in the prototype, it was expected that most of the testing and debugging would occur after completion of the PCBs, with an expected revision of the PCB design. Due to budget and time constraints, the second PCB was also the last.

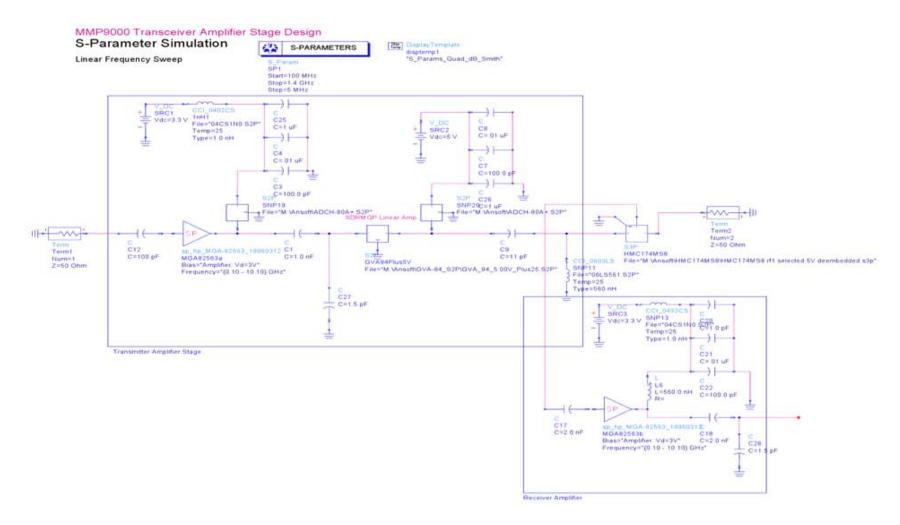

#### **3.1** Amplifier Design Simulation

Since the overall design of the project could not realistically be prototyped, for example, on a breadboard, simulation software had to be utilized wherever possible in order to ensure the design would match the specifications. Agilent's Advanced Design System (ADS) software was used for the simulation of the amplifier circuits in the design.

To simulate the amplifier design, simulation data for the integrated circuits had to be imported into ADS. The antenna switch, the low noise amplifier, and the power amplifier all had simulation data that could be imported into ADS. A design kit was included for the low noise amplifier, MGA82563, so it could be directly imported as a component in ADS. The antenna switch, HMC174M58, and the power amplifier, GVA-84+, both came with .snp files, which is essentially a text file that can be imported into ADS that contains measured s-parameter information for a range of frequencies. The antenna switch came with an .s3p file, which indicated that there are measurements for 3 ports, while the power amplifier came with a .s2p file, which indicates that there are 2 ports. After importing the files for the integrated circuits, the other discrete components in the circuit had to be added. It was a simple matter to simulate the receiver once the transmitter was simulated, since they have the same low noise amplifier.

After implementing the simulation files in ADS, other components, such as resistors and capacitors, needed to be added as well. ADS has these components in its library, but they are ideal. Regardless, substituting these components with design kit models from Coilcraft did not significantly change the results of the simulation. After all of the design was laid out in ADS, the s-parameter simulation simply had to be run to determine what is essentially the frequency response of the system, S21.

Once the frequency response was determined, the simulation results were used to tweak the values of the discrete components surrounding the ICs to achieve the best frequency response. To do this, information in the datasheets for the power amplifier, linear amplifier, and antenna

switch were taken into account, along with comparisons to the design of other daughterboards for the USRP. It seemed that the slightest change in capacitance or inductance in the surrounding circuit had a great impact on the forward voltage gain of the entire system, so the usefulness of these simulations had to be taken into account, given that the capacitive effects of PCB traces could not be simulated. Regardless of the shortcomings of the simulations, components were chosen that matched the simulation circuit as closely as possible. The following figures show the final version of the amplifier circuit, along with the simulation results.

Figure 7 - MMP9000 amplifier stage simulation schematic for both transmit and receive amplifier sections of the design. The transmit side includes the MGA82563 low noise amplifier and the GVA-84+ 5 V power amplifier, while the receive side incorporates only the low noise amplifier. Also included are the DC biasing circuits to power the amplifiers and the antenna switch. The input and output of the amplifier section are both connected to 50  $\Omega$  terminators to match the impedance of the rest of the circuit.

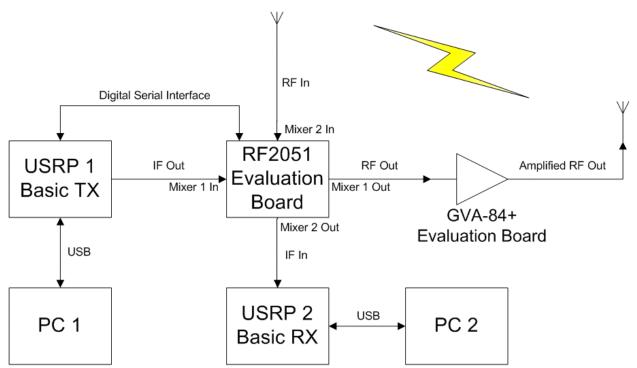

## 3.2 Basic Prototype - RFMD RF2051 Evaluation Board and GVA-84+ Amplifier

RFMD was generous enough to donate an RF2051 evaluation board to the MQP. The RF2051 chip is capable of synthesizing a local oscillator frequency between 300 MHz and 2500 MHz. [21] Two RF mixers are also integrated into the chip that can mix an RF signal between 50 MHz and 2.5 GHz with the local oscillator. The RF2052 is almost identical to the RF2051 except that it has only one mixer. The RF2052 is what was used in the final design. Its exact function in the design is discussed later. Figure 8 shows the evaluation board used in prototype testing and experiments, while Figure 9 shows the evaluation board for the power amplifier.

Figure 8 – RF2051 evaluation board.

Figure 9 - GVA-84+ power amplifier evaluation board.

#### 3.2.1 Experimentation with RF2051 Evaluation Board

When the RF2051 evaluation board arrived, experiments were performed to test how well it worked with receiving and transmitting RF signals over the air with the USRPs. The first test setup used the RF2052 evaluation board to transmit a signal that the RFX2400 daughterboard could receive. The second test setup used the RF2052 evaluation board to receive a signal that the RFX2400 daughterboard sent.

#### 3.2.2 Upconversion of Basic TX Board Output from 30 MHz to 2.4 GHz

For the first setup the output from the Basic TX board was connected to an RF input on the RF2052. The associated RF output on the RF2052 was then connected to the GVA-84+ amplifier, which was in turn connected to an antenna. The local oscillator in the RF2052 was set to 2.47 GHz. GNU Radio on the transmitting computer was then programmed to transmit the Mario 2 Overworld theme in FM at 30 MHz with the Basic TX board. The receiving computer was setup to receive FM audio at 2.5 GHz with the RFX2400 board. It successfully received the

Mario 2 theme song. When the local oscillator was tuned to 2.37 GHz, the receiving computer had to be tuned to receive at 2.4 GHz, as expected, proving that the RF2052 could be used to set the transmit frequency. Due to the way mixers work, the receiving computer could also be tuned to 2.44 GHz and 2.34 GHz for the local oscillator frequencies of 2.47 GHz and 2.37 GHz respectively.

#### 3.2.3 Downconversion of Basic RX Board Input from 2.4 GHz to 30 MHz

For the second setup an antenna was connected directly to the RF input of the RF2052 and the RF output was connected to the input of the Basic RX board. The local oscillator frequency in the RF2052 was set to 2.4 GHz. Then again the Mario 2 Overworld theme was transmitted, this time at 2.43 GHz with the RFX2400 daughterboard on one computer. It was received successfully at 30 MHz with the Basic RX board on the other.

#### 3.2.4 Upconversion and Downconversion on the Two Evaluation Board Mixers

The final test involved mixing the signal up to a certain frequency on one mixer on the evaluation board, then mixing this higher frequency signal back down on the other mixer, to connect two USRPs over the air using the evaluation board. USRP 1 was connected to the first mixer, which mixed the signal to 900 and 960 MHz. The signal then passes through the amplifier and is transmitted over the air to an antenna connected to the second mixer input, which mixes the signal back down to baseband for reception on the second USRP's Basic RX board. This test especially demonstrates that the RF2051 and RF2052's usefulness for over the air transmission over a wide frequency range.

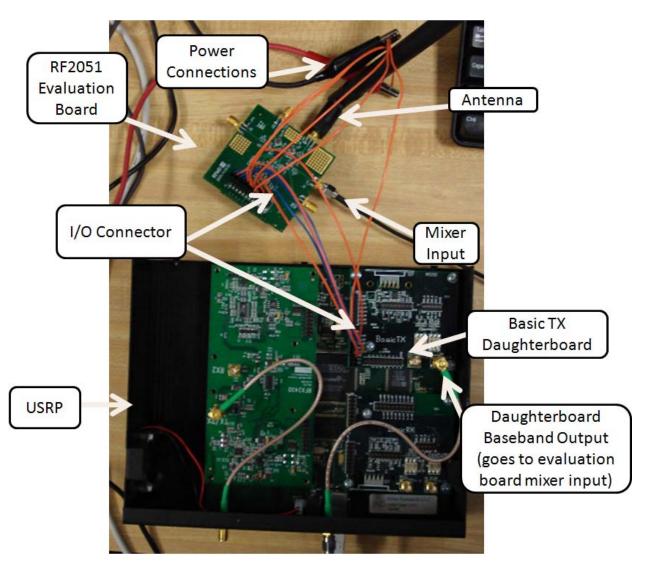

Figure 10 - Mixing a signal up and then back down using the RF2051 evaluation board.

#### 3.2.5 Evaluation Board Test Results

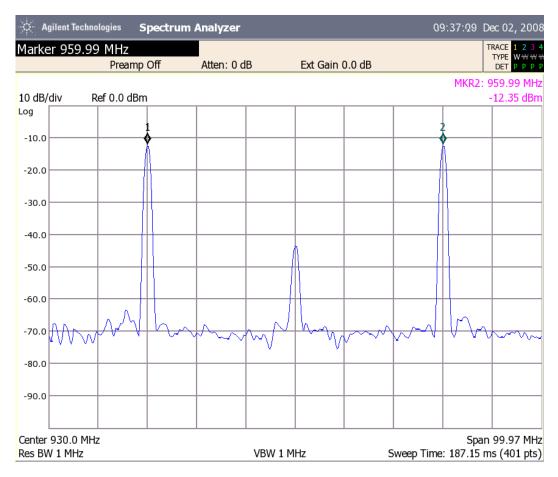

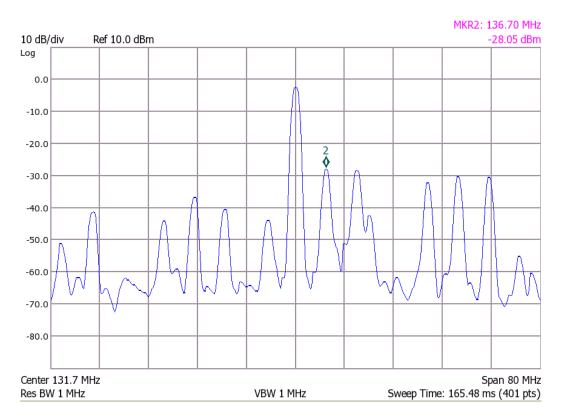

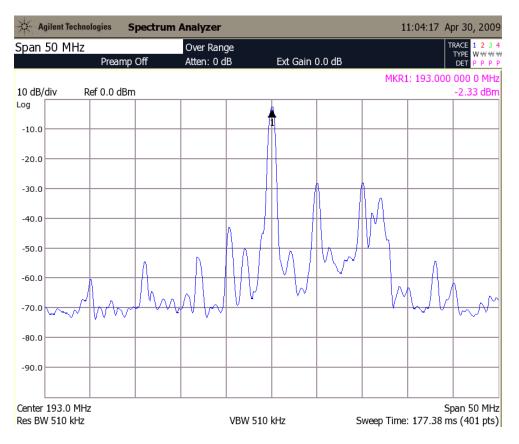

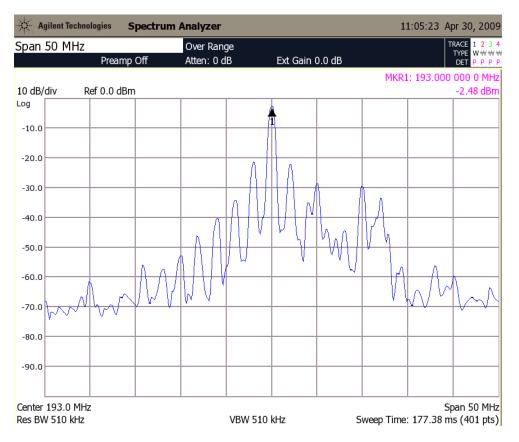

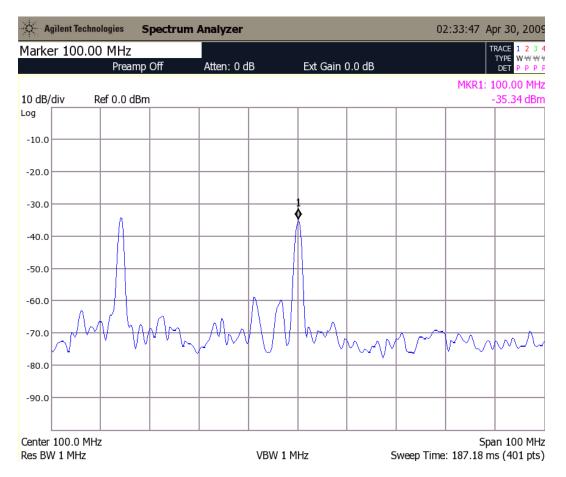

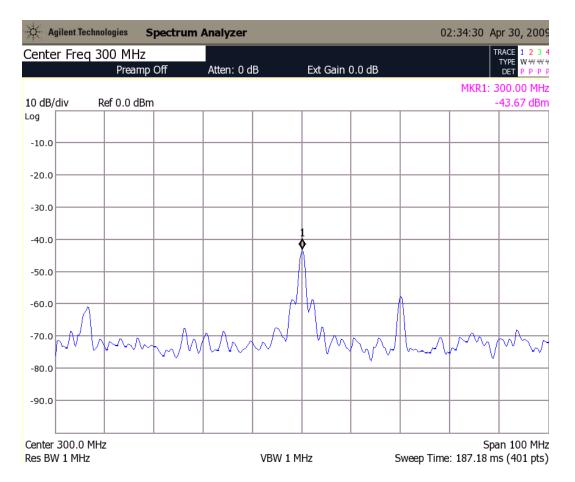

Figure 11 through Figure 13 show a 30 MHz signal from the USRP being mixed with a local oscillator at 930 MHz. In Figure 11 the output is connected directly to the spectrum analyzer. The local oscillator frequency leaks through a bit and can be seen at about -45 dBm. The expected up and down converted signals at 960 MHz and 900 MHz are both seen at about -12 dBm. The local oscillator frequency is seen at about -45 dBm, while the transmitted frequencies at 930 MHz  $\pm$ 30 MHz are at about -12 dBm.

Figure 11 – Transmitted signal directly out of the RF2051 mixer.

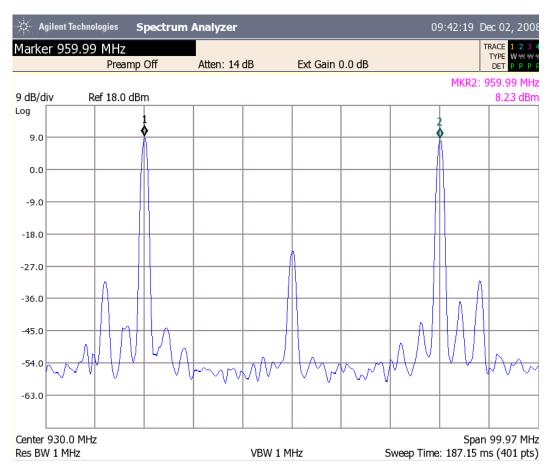

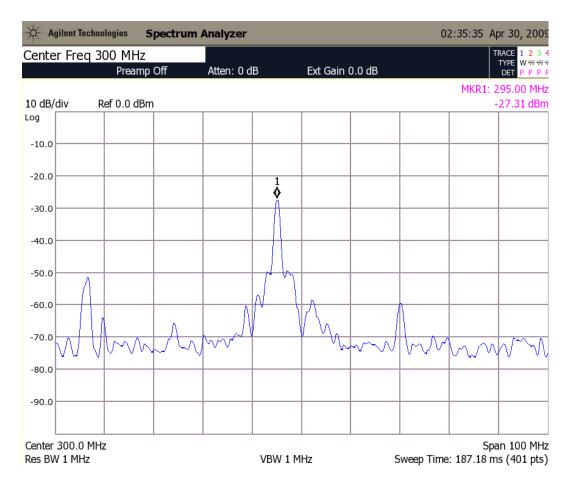

Figure 12 illustrates the same setup as Figure 11, but this time utilizes the GVA-84+ amplifier after the evaluation board. The local oscillator frequency is seen at about -24 dBm, while the transmitted frequencies at 930 MHz  $\pm$ 30 MHz are at about 8 dBm. As can be seen in the figure, there is a slight amount of spectral leakage next to the two signals.

Figure 12 - Transmitted signal directly out of the GVA-84+ amplifier.

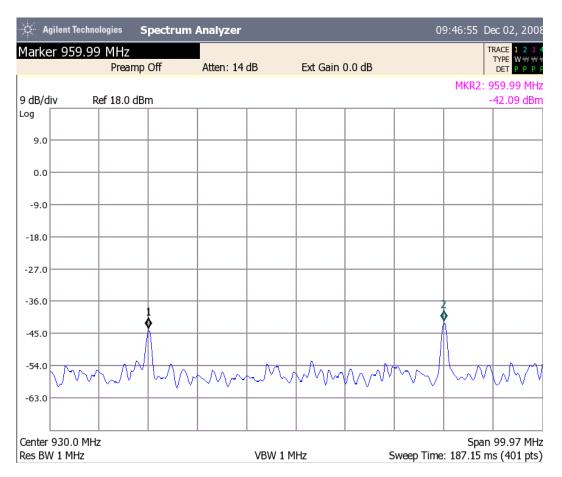

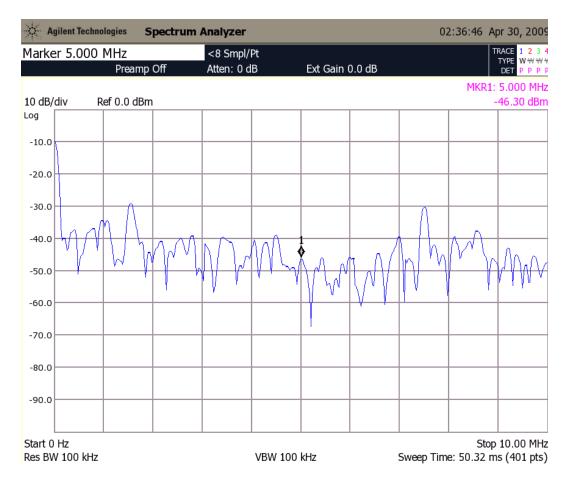

Figure 13 again shows the same signal, but after being transmitted over the air with the GVA-84+. The local oscillator frequency is not visible, while the transmitted frequencies at 930 MHz  $\pm$ 30 MHz are at about -42 dBm.

Figure 13 - Transmitted signal amplified by the GVA-84+ and transmitted over the air.

Figure 13 is significant because it shows that the desired signals at 900 MHz and 960 MHz are visible at the receiver, while the unwanted local oscillator frequency is not. This means that it should not cause any significant amount of interference at the local oscillator frequency, but successfully transmit the signal at the desired frequency. However, since there are two copies of the signal, both above and below the local oscillator frequency, the undesired one should be filtered out before the antenna.

#### 3.3 Interfacing the RF2051 with GNU Radio

The next objective was to figure out how to program the RF2051 with GNU Radio. In the experiments documented above, setting the frequency of the local oscillator in the RF2051 was done by programming it over a USB connection to the evaluation board with software provided by RFMD. For the chip to be useful in the design, it would have to be able to be programmed by GNU Radio while connected to a USRP.

The datasheet for the RF2051 describes the serial programming interface as a "Three-wire Serial Control Interface." Initially it was thought that this would be compatible with Serial Peripheral Interface (SPI). Since the USRP has a SPI bus available to the daughterboards which is easily programmable in GNU Radio, it was thought that it would be no problem to program the chip. Unfortunately, upon further inspection of the protocol described in the datasheet, it was discovered that it was in fact not compatible with SPI. The physical layer is closer to the I<sup>2</sup>C protocol (in that they both only use a single data line) which the USRP also has available to the daughterboards, but it is not exactly the same. In the end it was decided that the serial interface should just be connected to the general purpose digital I/O (GPIO), of which plenty is available, and then simply bit-banged by GNU Radio in a Python program. While it is very likely possible to do this much more intelligently in either a lower level C++ module of GNU Radio or even in the FPGA itself, the Python solution worked and is fast enough.

The first thing that had to be done to begin the testing of programming the RF2051 with GNU Radio was to connect the evaluation board to the USRP. A connector was made to connect the serial interface and other digital control pins to the GPIO on the Basic TX board, and also to connect power to a power supply. Figure 4 shows the evaluation board connected to the USRP and power supply.

Figure 14 - RF2051 evaluation board connected to the USRP

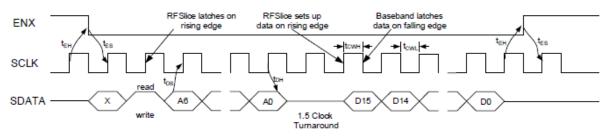

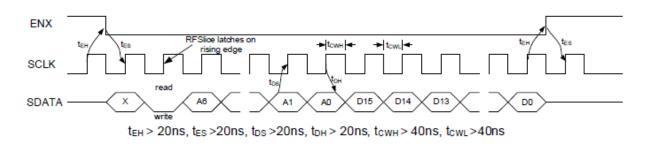

After carefully going over the read and write timing diagrams in the RF2051 datasheet (shown below in Figure 16 and Figure 15 respectively), two Python functions were written: one to write a word to a register in the RF2051, and one to read a word from a register in the RF2051. These timing diagrams show the voltages on the three serial pins on the RF2051 chip (either high or low) over time for one read or write operation. The ENX input enables the serial interface (active low), SCLK is the clock for the data (driven by the host), and SDATA is the data line (driven by either the host or the RF2051 depending on the operation). The slightly tricky part was making sure that the read function was written correctly before testing it. This is because the data line is used as both an input and an output. The host (USRP) first writes the address of the register on the data line. After a short delay the RF2051 then writes the data in the register to the same data line. During the delay it is important that the direction USRP's serial data pin be changed from an output to an input. If both the USRP and RF2051 try to drive the line at the same time, it could potentially cause damage to the RF2051, USRP's FPGA, or both.

t<sub>EH</sub> > 20ns, t<sub>ES</sub> >20ns, t<sub>DS</sub> >20ns, t<sub>DH</sub> > 20ns, t<sub>CWH</sub> > 40ns, t<sub>CWL</sub> >40ns

Figure 15 - RF2051 serial read timing diagram

#### Figure 16 - RF2051 serial write timing diagram

Once it was confirmed that the read and write functions did indeed work (by successfully reading back data that was written) the next thing to do was to write a function to actually tune the local oscillator to any frequency in the range 300 MHz to 2500 MHz. The RF205x Frequency Synthesizer User Guide gave a very nice detailed example on how to program which registers to set the frequency of the local oscillator. Following this information, a function was written that could successfully tune the RF2051's local oscillator to any frequency between 300 MHz and 2500 MHz, which was confirmed by checking the local oscillator leakage on the RF output port on a spectrum analyzer. All the source code of the functions mentioned above can be found in Appendix A - Source Code.

#### **3.4 Chapter Summary**

The final design described here is the result of many different contributions. First the simulation data that was previously discussed was taken into account to verify the part selection. The parts were then put together in a schematic layout software and verified against the datasheets and what the manufacturers suggest. Finally, the design was compared against the design of similar daughterboards for the USRP to check for any large inconsistencies. From this final design, the actual assembly of all the components can begin to take place.

#### 4 Transceiver Design

Once the requirements for the design were identified, much research had to be done before the design process could begin. For starters, the board would have to be compatible with the USRP, and the only way to determine what this required was to read through the USRP documentation and any other related resources. After doing some research into this it was discovered that the USRP hardware is entirely open source and released under the GNU General Public License (GPL). Thanks to this, all existing daughterboard schematics, parts lists, and PCB layouts are freely available on the Internet. This information by far provided the most help for the design, as it not only showed exactly how the existing daughterboards work, but also how they interface with the USRP. Of course it still took quite a bit of time and research to fully understand the schematics. Since the Wireless Innovation Laboratory already had a couple of the RFX2400 daughterboards available for experimenting with, it was decided that it would be the schematics for this board that would be analyzed. After many days of reviewing every part of the schematics for it, reading through the datasheets for all its parts, and reading up on general RF receiver and transmitter theory and design, a detailed working knowledge of its operation was gained. It was decided that it would be helpful for future reference to create a block diagram showing the operation of the RFX2400 board. This diagram appears below in Figure 17 through Figure 19.

Once this existing daughterboard design was understood, it was time to begin researching ways to increase its frequency tuning range. First the schematics for the other daughterboards in the RFX series were examined because they all operate over different small frequency ranges. It was found that they all had very similar designs, mainly only differing in some of the ICs used, which even still were ICs in the same families, just covering different frequency ranges. Since none of the ICs in any of the existing daughterboards were sufficiently wideband enough in order to operate over the desired frequency range of 100 MHz to 1.3 GHz, the search began for ICs with similar functions, namely the local oscillator and quadrature modulator and demodulator.

Almost immediately a quadrature modulator and quadrature demodulator, both from Analog Devices, were found that could cover the frequency range from 50 MHz to 2200 MHz for receiving, and 50 MHz to 2000 MHz for transmitting. They were the ADL5385 and ADL5387 respectively. However, it was a much harder task to find a solution for a local oscillator that could be digitally tunable over the 100 MHz to 1.3 GHz range. After conducting more research, it was found that the most common way to implement a tunable local oscillator is with a phase locked loop (PLL) and a voltage controlled oscillator (VCO). In fact this is what is used in the RFX series of daughterboards. Typically the two components (PLL and VCO) are integrated into a single IC. Unfortunately none were found that operated over the desired frequency range. In fact, the vast majority have to be tuned to a center frequency using discrete components which limits the tunable range to a small subset of the advertised range.

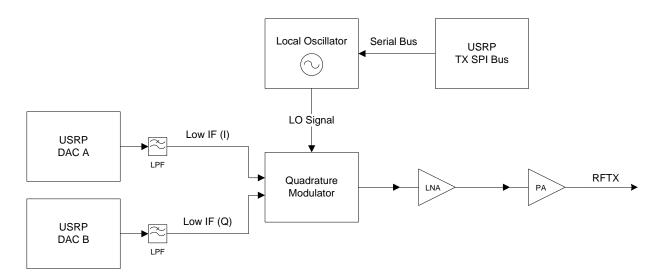

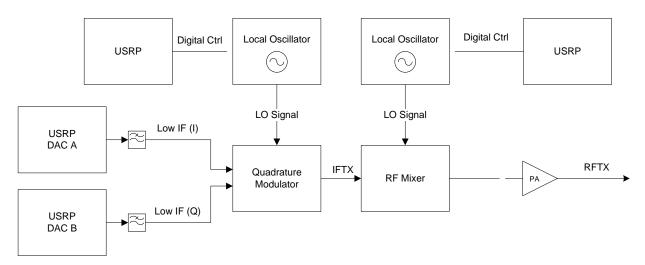

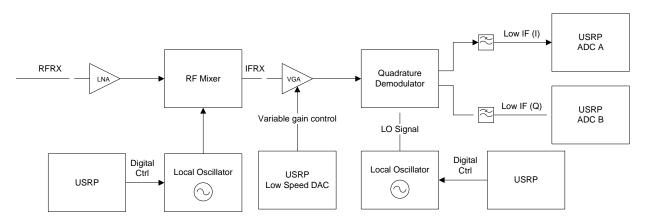

Figure 17 shows a block diagram of the initial design of the transmitter side. The two quadrature signals leave the USRP from the digital to analog converters and pass through anti-aliasing low pass filters to smooth out the DAC transitions. The quadrature modulator then will mix and modulate this signal with the local oscillator, which is controlled by the USRP. After being mixed and modulated to a higher frequency, it will then pass through a low noise amplifier and then a power amplifier. The RF signal then travels to the antenna switching block, shown in Figure 18.

Figure 17 - Block diagram of the RFX daughterboard series transmit path

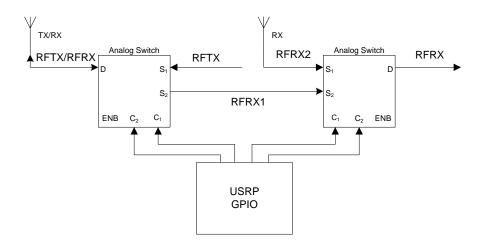

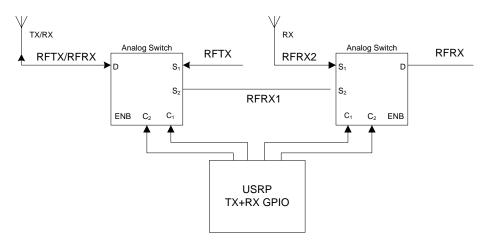

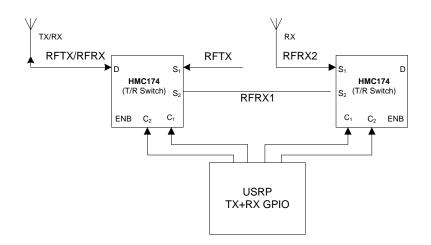

Once the signal has been modulated, it is passed to the antenna switch and antenna logic block, which are essentially two analog switches that control the antenna connections and signal path. In this stage, the software can control whether the board is operating in full duplex mode, transmitting and receiving at the same time, or half duplex mode, either transmitting or receiving.

Figure 18 - Block diagram of the RFX daughterboard series transmit/receive switch configuration

The receive path is also connected to the antenna switch and logic block. Once again the USRP GPIO will control which antenna is connected to the receive blocks based on what mode the transceiver is in.

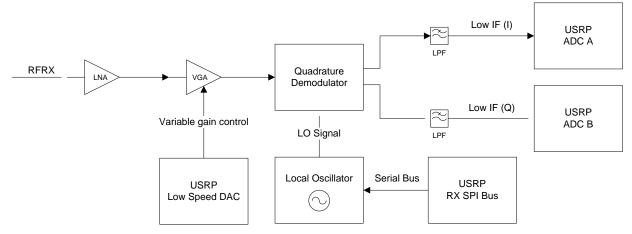

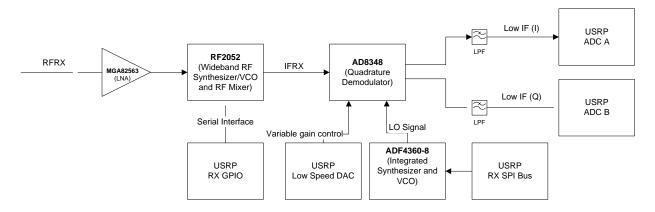

Figure 19 - Block diagram of the RFX daughterboard series receive path

Once the received signal passes through the antenna switches, it is amplified before being mixed down to the correct frequency to be sampled by the analog to digital converter on the USRP. In a similar setup as the transmitter, a local oscillator will be controlled by the USRP SPI bus, which will allow software control over the frequency that the received signal is mixed down to. After exiting the quadrature demodulator, the signal is low pass filtered to remove any noise before it enters the analog to digital converters on the USRP.

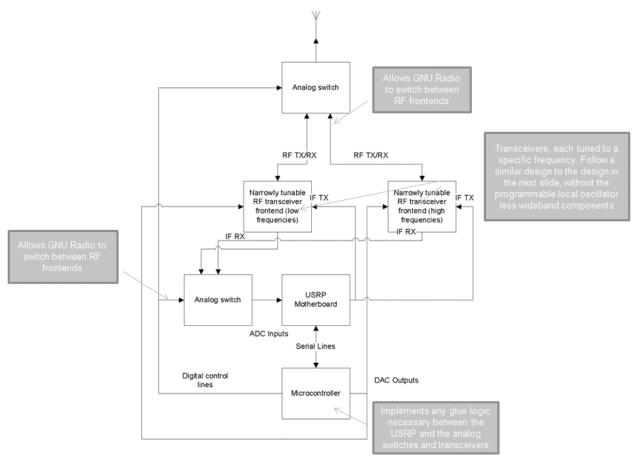

One idea to achieve the local oscillator was to combine several VCO/PLL chips and multiplex them, selecting them based on the required frequency. This approach is often used in truly wideband applications where failure or poor operation is not an option. Figure 20 illustrates this initial design idea. Unfortunately this would have required many chips and lots of extra circuitry.

In the real world this uses up precious board real estate, increases power consumption, and drives up costs. Therefore this potential design only ever existed as a vague idea, and never made it to a more complex schematic.

Figure 20 - Initial design idea with switchable, narrowly tunable transceiver frontends.

Eventually RFMD's RF205x series of chips was discovered. The RF2052 in particular includes a VCO/PLL local oscillator block, and one RF mixer. However it was the VCO/PLL block that was of interest, since it is digitally tunable and able to generate any frequency between 300 MHz and 2500 MHz. After reading about it, it was found that by grounding the input to the RF mixer, its output would be the local oscillator signal, which was exactly what was needed. Furthermore, both the quadrature modulator and demodulator require an input of twice the effective local oscillator frequency, meaning that by tuning the external local oscillator signal. Therefore a tunable local oscillator range of 300 MHz to 2500 MHz meant that the design would be able to transmit and receive RF signals between 150 MHz and 1250 MHz, only 50 MHz off from each end of the desired frequency range.

Sometime during working out the details of the design using the RF2052 solely as the local oscillator, some potential problems came to light. The power output from the RF2052's mixer output port with the mixer input grounded could potentially exceed the maximum power input allowed on both the modulator's and demodulator's LOIN ports. While this could be fixed by using resistors to reduce the power between the chips, it would also require additional impedance matching. Another potential problem was the fact that tuning the board to transmit or receive at 1000 MHz would require tuning the RF2052 to 2000 MHz. While at first this may not seem to be a problem, since the RF2052 is easily tuned to 2000 MHz, in reality it very well could be. Designing a PCB to operate correctly at such high frequencies is very difficult, and requires very close attention to correct impedance matching of traces as well as the placement of both traces and components. Otherwise the signal can be reflected back to the source, can be greatly attenuated, and can interfere with other signal and power lines on the board. It would be rather unfortunate then if the board failed to operate at 2000 MHz, but succeeded at 1000 MHz, since the only thing that would stop it from operating at 1000 MHz would be that it did not operate at 2000 MHz.

Aside from these potential issues, the frequency range would be still slightly narrower than what had initially been decided on. While brainstorming about what to do about all of this, a new design was thought up. It required an additional PLL/VCO IC operating at a fixed frequency, or at least only a very narrow range or tunable frequencies, a new quadrature modulator/demodulator pair, and also took advantage of the mixer in the RF2051. An intermediate frequency stage would be added to the transmit and receive paths to fully utilize the capabilities of the RF2052 chip.

### 4.1 Final Design Overview

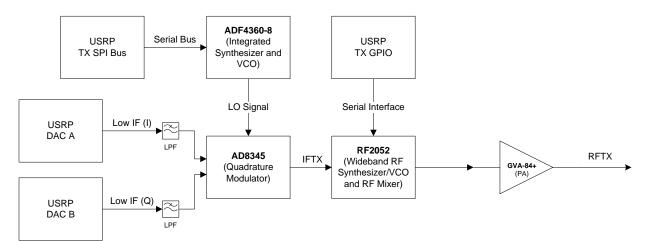

The final design is similar to the design of the RFX daughterboard series, but uses an additional intermediate frequency stage and the RF2052 wideband mixer and frequency synthesizer. Figure 21 through Figure 23 below show a functional block diagram of the design. Figure 24 through Figure 26 show the design with the actual components chosen for each block.

On the transmit side of the design, a low IF (intermediate frequency) signal in quadrature (Q) and in-phase (I) components is sent out of two high speed DACs on the USRP. Before anything else, these signals are put through low pass filters to remove aliases and other noise generated by the DACs. These two filtered signal components are then fed into a quadrature modulator. The quadrature modulator takes as inputs the two low IF signal I and Q components and a local oscillator (LO) signal. These inputs are mixed and combined into a single RF output at the frequency  $f_{IF} + f_{LO}$ . The  $f_{IF} - f_{LO}$  frequency is suppressed by the quadrature modulator's circuitry.

Figure 21 - Block diagram of the final design transmit path