#### Worcester Polytechnic Institute Digital WPI

Major Qualifying Projects (All Years)

Major Qualifying Projects

October 2012

## Control Plane for Embedded DSP

Richard Michael Dennen Worcester Polytechnic Institute

Follow this and additional works at: https://digitalcommons.wpi.edu/mqp-all

#### **Repository Citation**

Dennen, R. M. (2012). Control Plane for Embedded DSP. Retrieved from https://digitalcommons.wpi.edu/mqp-all/3615

This Unrestricted is brought to you for free and open access by the Major Qualifying Projects at Digital WPI. It has been accepted for inclusion in Major Qualifying Projects (All Years) by an authorized administrator of Digital WPI. For more information, please contact digitalwpi@wpi.edu.

# Control Plane for Embedded Digital Signal Processing An Application of Networks-on-Chips for VLSI

Major Qualifying Project Report Submitted to the Faculty of Worcester Polytechnic Institute In partial fulfillment of the requirements for the Degree of Bachelor of Science

> by Richard Dennen on October 22, 2012

#### Abstract

This project is sponsored by MITRE Corporation to develop a scalable and reusable control plane architecture for VLSI design. The main goal of this project is to develop a communication platform for a wide range of applications to reduce the development and testing time associated with the design of a interconnect system. Thorough research has been conducted in the area of network-on-chip designs that are suitable for these types of applications. The necessary components are built and verified in hardware description language. The deliverable components are packaged as reusable and parameterized SystemVerilog code.

#### Acknowledgements

Al Conti and Paul Secinaro from MITRE Corporation for advising this project. Your commitment and dedication to this project allowed to me to succeed in accomplishing the goals of this project. I thank you both for everything you have taught me in my time at MITRE. I appreciate that you committed so much time from your busy schedules to guide me through the design of this project.

Prof. Xinming Huang from Worcester Polytechnic Institute for advising this project, taking the time to ensure that my project was progressing well, offering feedback on the design and opinions in important design decisions, as well as the detailed revisions and corrections made to this report!

Prof. Sergey Makarov from Worcester Polytechnic Institute for introducing me to MITRE Corporation and encouraging me to pursue a project at this new project center.

Joseph Chapman and Adam Woodbury from MITRE Corporation for arranging this new partnership with WPI and for the advice you have offered over the course of the project.

Prof. Stephen Bitar for your advice, motivation, and support over the four years I have spent at WPI.

Joseph DiChiara and Julian de Zulueta for being a part of this incredible experience and for being great friends.

## **Table of Contents**

| 1              | Intr | oducti        | oduction1                      |   |  |  |  |

|----------------|------|---------------|--------------------------------|---|--|--|--|

|                | 1.1  | .1 Background |                                |   |  |  |  |

|                | 1.2  | Probl         | lem Statement                  | 2 |  |  |  |

| 2              | Net  | work-         | on-Chip <sup>2</sup>           | 1 |  |  |  |

| 2.1 Topologies |      |               | logies                         | 5 |  |  |  |

|                | 2.1  | .1            | Shared Bus                     | 5 |  |  |  |

|                | 2.1  | .2            | Ring Bus                       | 5 |  |  |  |

|                | 2.1  | .3            | Mesh Network                   | 7 |  |  |  |

|                | 2.1  | .4            | Star Network                   | 7 |  |  |  |

|                | 2.1  | .5            | Comparison of Topologies       | 3 |  |  |  |

|                | 2.2  | Routi         | ing10                          | ) |  |  |  |

|                | 2.2  | .1            | Deterministic Routing          | ) |  |  |  |

|                | 2.2  | .2            | Adaptive Routing               | 1 |  |  |  |

|                | 2.2  | .3            | Comparison of Routing          | 1 |  |  |  |

|                | 2.3  | Swite         | ching12                        | 2 |  |  |  |

|                | 2.3  | .1            | Circuit Switching              | 2 |  |  |  |

|                | 2.3  | .2            | Packet Switching               | 2 |  |  |  |

|                | 2.3  | .3            | Comparison of Switching        | 3 |  |  |  |

|                | 2.4  | Flow          | Control                        | 1 |  |  |  |

|                | 2.4  | .1            | Stall-and-Go14                 | 1 |  |  |  |

|                | 2.4  | .2            | ACK-NACK                       | 5 |  |  |  |

|                | 2.4  | .3            | Comparison of Flow Control     | 5 |  |  |  |

|                | 2.5  | Com           | plications of Networks-on-Chip | 5 |  |  |  |

|                | 2.5  | .1            | Deadlock                       | 5 |  |  |  |

|                | 2.5  | .2            | Livelock                       | ) |  |  |  |

|                | 2.5  | .3            | Starvation                     | ) |  |  |  |

| 3              | Rec  | luirem        | ents and Specifications        | 1 |  |  |  |

|                | 3.1  | Gene          | ral Goals                      | 1 |  |  |  |

|                | 3.2  | Contr         | rol Plane Specifications       | 2 |  |  |  |

|   | 3.3   | Proje  | ct Deliverables           | . 23 |

|---|-------|--------|---------------------------|------|

| 4 | Me    | thodo  | ogy                       | . 24 |

|   | 4.1   |        | logy                      |      |

|   | 4.2   | Rout   | ing                       | . 24 |

|   | 4.2   | .1     | Bridge                    | . 25 |

|   | 4.3   | Swit   | ching                     | . 27 |

|   | 4.4   | Flow   | Control                   | . 27 |

|   | 4.5   | Netw   | vork Interface            | . 28 |

|   | 4.5   | .1     | Packet Processor          | . 29 |

|   | 4.5   | .2     | Protocol Adapter          | . 29 |

|   | 4.6   | Pack   | et Structure              | . 30 |

| 5 | Imp   | olemei | ntation and Design        | . 32 |

|   | 5.1   |        | Control Buffer            |      |

|   | 5.2   | Rout   | er                        | . 34 |

|   | 5.2   | .1     | Architecture              | . 34 |

|   | 5.2   | .2     | Interfaces                | . 36 |

|   | 5.2   | .3     | Router Inport             | . 37 |

|   | 5.2   | .4     | Router Outport            | . 39 |

|   | 5.2   | .5     | Router Switch             | . 41 |

|   | 5.2   | .6     | Separate Data Path Router | . 44 |

|   | 5.3   | Brid   | ge                        | . 44 |

|   | 5.4   | Pack   | et Processor              | . 47 |

|   | 5.5   | OCP    | Protocol Adapters         | . 49 |

|   | 5.5   | .1     | Packet Protocol           | . 50 |

|   | 5.5   | .2     | Implementation            | . 52 |

| 6 | Tes   | ting a | nd Verification           | . 54 |

|   | 6.1   | Testi  | ng Methods                | . 54 |

|   | 6.1.1 |        | Queues                    | . 55 |

|   | 6.1.2 |        | Mailbox                   | . 55 |

|   | 6.1.3 |        | Interfaces                | . 56 |

|   | 6.2    | Mesł    | n Subsystem Tests             | 56 |

|---|--------|---------|-------------------------------|----|

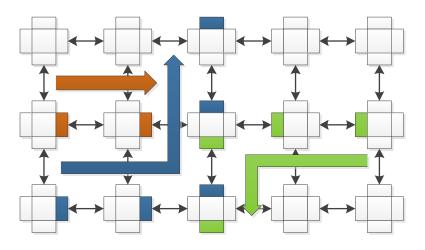

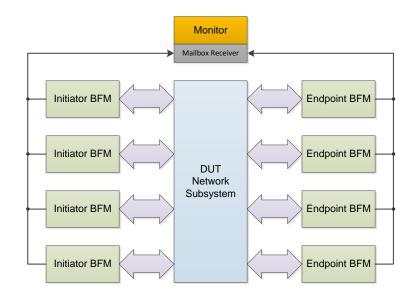

|   | 6.2    | .1      | General Structure             | 56 |

|   | 6.2    | .2      | Packet-based Tests            | 58 |

|   | 6.2    | .3      | Request-based Tests           | 60 |

| 7 | Cor    | nclusio | Dn                            | 63 |

|   | 7.1    | Sum     | mary of Project Contributions | 63 |

|   | 7.2    | Futu    | re Work and Improvements      | 64 |

| R | eferen | ces     |                               | 66 |

## **Table of Figures**

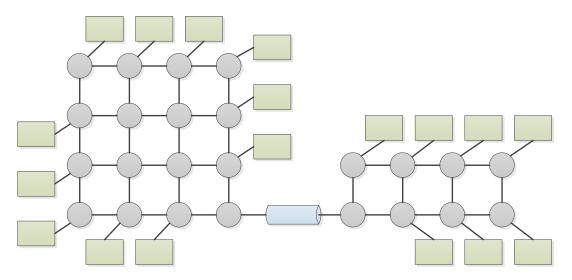

| Figure 1: An example network-on-chip including routers (gray), a bridge (blue), and man  | ny IP |

|------------------------------------------------------------------------------------------|-------|

| cores (green)                                                                            | 4     |

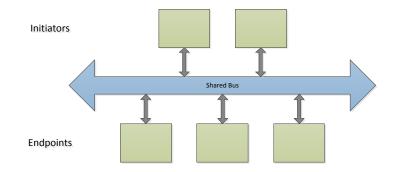

| Figure 2: Shared bus topology.                                                           | 5     |

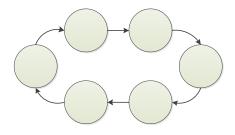

| Figure 3: A ring bus.                                                                    | 6     |

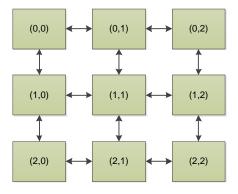

| Figure 4: A mesh network                                                                 | 7     |

| Figure 5: A star network.                                                                | 8     |

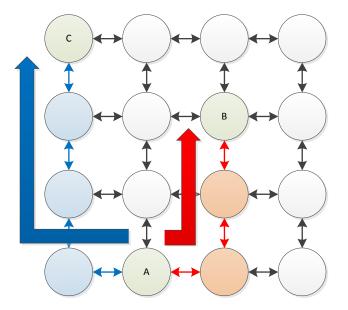

| Figure 6: Routing paths by the XY algorithm for a request from A to B and from A to C    | 10    |

| Figure 7: An example of wormhole switching.                                              | 13    |

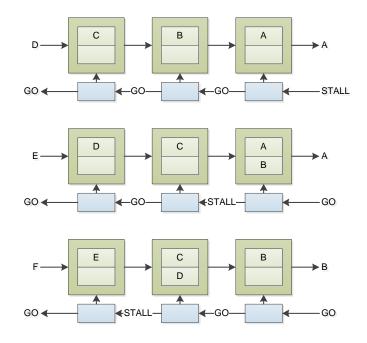

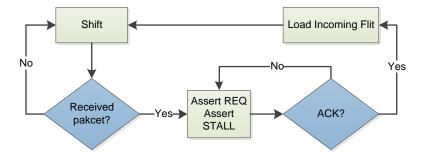

| Figure 8: An example of Stall-and-Go flow control                                        | 15    |

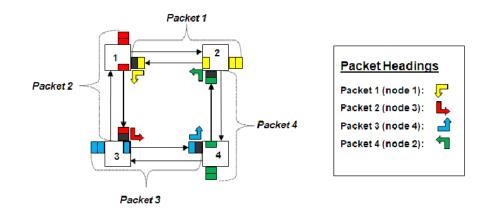

| Figure 9: A classic example of deadlock [8].                                             | 16    |

| Figure 10: Allowed turns in XY routing [8].                                              | 17    |

| Figure 11: An example of dependencies between network messages.                          | 18    |

| Figure 12: Physically-separate request and response networks to break message-based dead |       |

|                                                                                          | 19    |

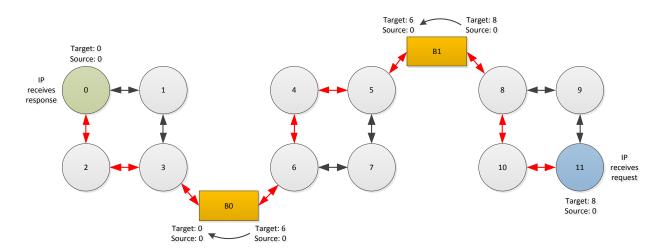

| Figure 13: An example of address translation for initiator requests across a bridge      | 26    |

| Figure 14: An example of address translation for endpoint responses across a bridge      | 26    |

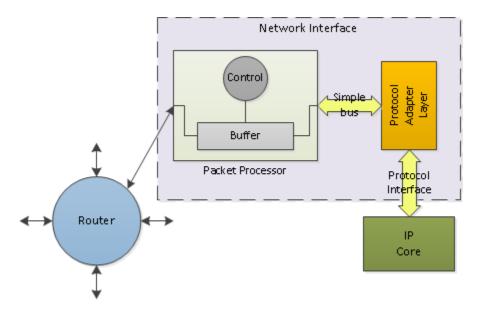

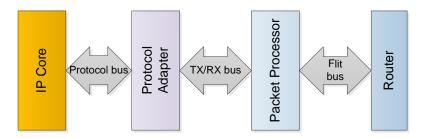

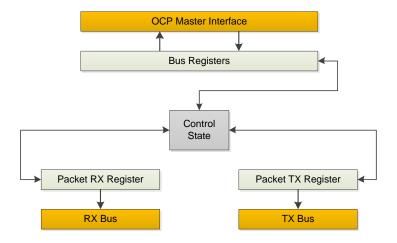

| Figure 15: Composition of the Control Plane network interface (NI).                      | 28    |

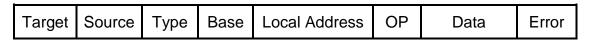

| Figure 16: General packet structure for the MITRE control plane                          | 30    |

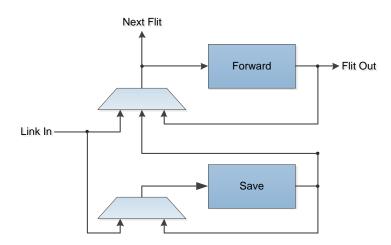

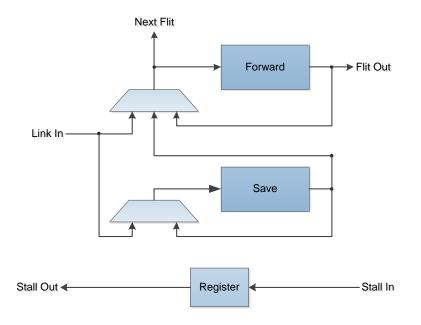

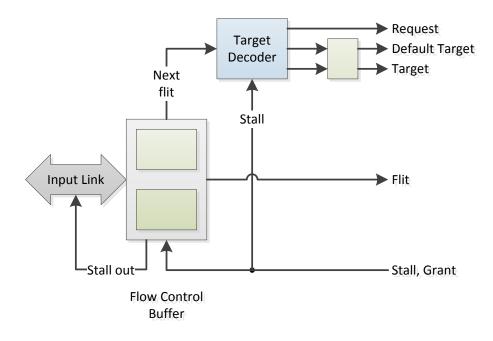

| Figure 17: Block diagram of Flow Control Buffer.                                         | 32    |

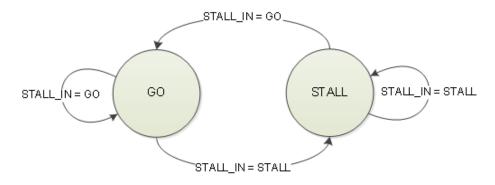

| Figure 18: State transition diagram for the Flow Control Buffer state machine.           | 33    |

| Figure 19: Final block diagram of the Full Control Buffer.                               | 34    |

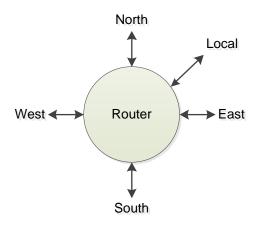

| Figure 20: Router component interconnects.                                               | 35    |

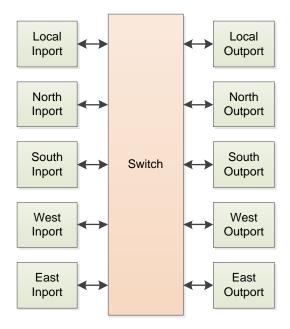

| Figure 21: Routing interconnects and transmission paths.                                 | 36    |

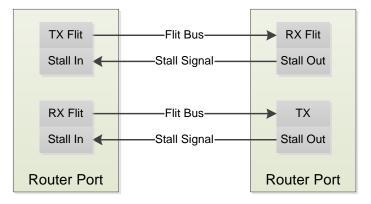

| Figure 22: Links between adjacent routers.                                               |       |

| Figure 23 : Block diagram of the router inport.                                          | 37 |

|------------------------------------------------------------------------------------------|----|

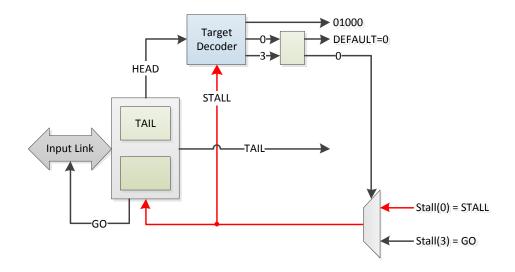

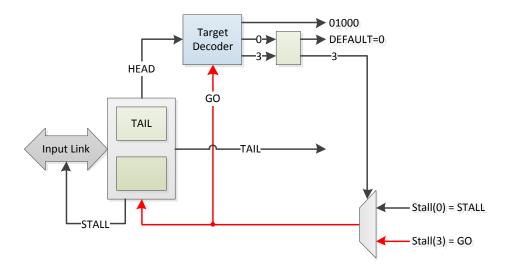

| Figure 24: An example of a misuse of the target selector                                 | 38 |

| Figure 25: The result of the previous example.                                           | 39 |

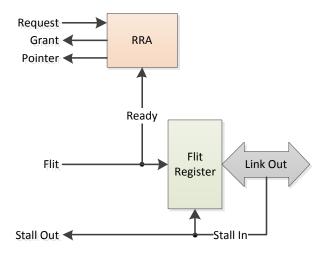

| Figure 26: Block diagram of a router outport.                                            | 39 |

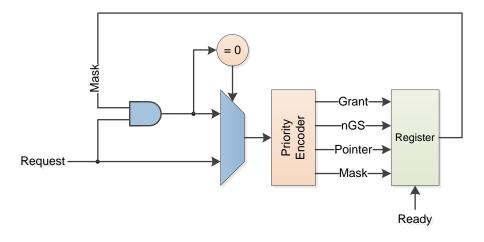

| Figure 27: Block diagram of a mask-based round-robin arbiter                             | 41 |

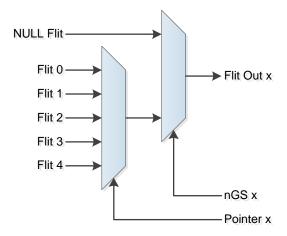

| Figure 28: Flit bus multiplexer in the router switch.                                    | 42 |

| Figure 29: Circuit equivalent of a multiplexer-based stall signal switching.             | 42 |

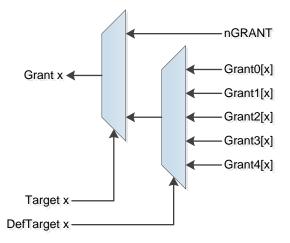

| Figure 30: Circuit equivalent of the grant signal switching                              | 43 |

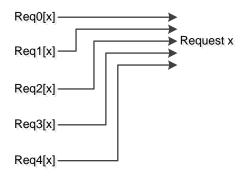

| Figure 31: Outport request signal generation                                             | 43 |

| Figure 32: Block diagram of the Bridge component.                                        | 45 |

| Figure 33: Request data path for the Bridge component.                                   | 46 |

| Figure 34: Response data path for the Bridge component                                   | 46 |

| Figure 35: Block diagram for the Packet Processor                                        | 47 |

| Figure 36: Flow diagram of the Packet Processor transmit bus request cycle               | 48 |

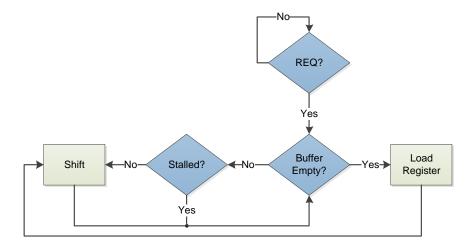

| Figure 37: Flow diagram of the Packet Processor receive bus request cycle                | 49 |

| Figure 38: Layered structure of the Network Interface.                                   | 49 |

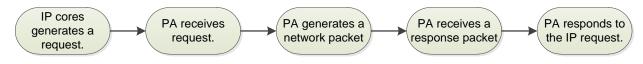

| Figure 39: Control flow of request generation through endpoint Protocol Adapters.        | 50 |

| Figure 40: Control flow of request generation though initiator Protocol Adapters         | 50 |

| Figure 41: Packet structure for the MITRE OCP Memory protocol adapters.                  | 50 |

| Figure 42: State-based packet request to OCP request translation in the Protocol Adapter | 52 |

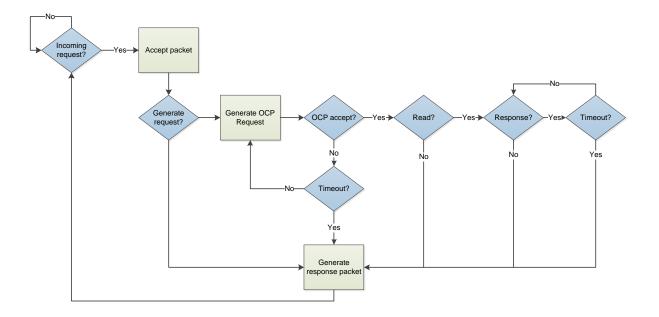

| Figure 43: Flow chart of the OCP Memory endpoint protocol adapter state machine          | 53 |

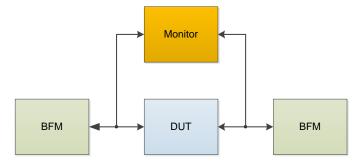

| Figure 44: General structure of a testbench.                                             | 54 |

| Figure 45: General structure of a mesh subsystem test                                    | 57 |

| Figure 46: Packet fields according to network level and protocol depth                   | 58 |

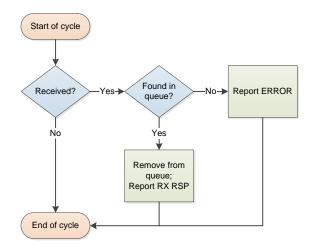

| Figure 47: Mesh subsystem initiator BFM receive flowchart.                     | 59 |

|--------------------------------------------------------------------------------|----|

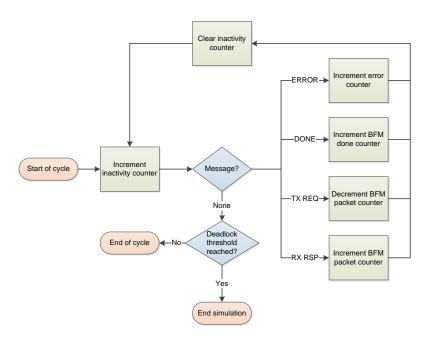

| Figure 48: Flowchart of the mesh subsystem monitor's message processing system | 60 |

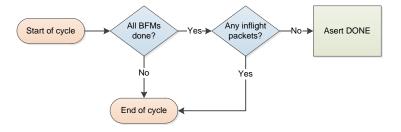

| Figure 49: Flowchart of the mesh subsystem monitor's completion detection      | 60 |

### **Table of Tables**

| Table 1: A comparison of common NoC topologies based on important parameters | 9  |

|------------------------------------------------------------------------------|----|

| Table 2: Supported operations through the OCP Memory Protocol Adapter        | 51 |

| Table 3: Error codes supported in the OCP Memory Protocol Adapter            | 51 |

Introduction

#### **1** Introduction

In recent years there has been much motivation for the design of integrating many capabilities on a single chip. Motives have included smaller package sizes for more portable devices, reduced power consumption, and higher performance for real-time applications [1]. These chips incorporate the functionality of several devices into one die. They are thus called *systems-on-a-chip* (SoC). The SoCs use a higher level of integration which reduces the need for long wires and routing between many chips that often lead to long propagation delays and much power dissipation.

A system-on-a-chip approach is often used in types of embedded digital signal processing, where a system constitutes a potentially large number of interconnected devices. Each processor includes a large number of different *processing elements* that operate on the incoming signal data. Real-time processing performance is often a requirement of such devices, warranting the SoC design paradigm [1]. More recently, such systems have also been composed of predesigned logic blocks, called *intellectual property cores*, or IP cores. These are distributable designs (in the form of synthesizable RTL) that can be inserted into a SoC [2]. This greatly reduces design time for large devices and promotes reusability of designs.

Bus interfaces have been a traditional solution for control commands and the exchange of information in digital systems. A typical microprocessor accesses memory and I/O devices through a bus, often sharing these resources with other microprocessors in a multiprocessor system. While bus systems are typically straightforward designs, they come at the cost of performance and hardware resources. Busses demand a large number of wires to interconnect devices they contain. In addition, central control (arbitration) is required to ensure that data reaches its destination as well as a fairness of resource usage is enforced. Bus-based systems also have a limited capability and bandwidth for simultaneous transfers [2].

The need for alternative communication architecture became apparent as the number of devices connected in such a system increased. A traditional bus system does not offer scalability for systems in the size of potentially hundreds of connected devices. It was at this time that system designers began implementing concepts of computer networking on silicon devices, known commonly as *network-on-chip* (NoC) [2].

Introduction

#### 1.1 Background

A network-on-chip is a tool for communication between processing elements and storage devices in a system-on-chip. They are used to connect large numbers of devices that a traditional shared bus cannot. Early NoC implementations were seen in supercomputers and telecommunication devices [3]. Data moves through a NoC as it would move in a computer network. Elements in the NoC are responsible for locating the destination of transmitted data and assuring its delivery.

NoCs offer the advantages of greatly reducing wiring complexity and much improved scalability. The comparable-sized shared bus implementation could easily result in poorly scalable wiring, as the wire lengths to devices would increase with the devices' distances apart. This stands to be one of the greatest complications in making smaller chips [4]. NoC offer more compact solutions that bring routing elements closer together, offering shorter and more scalable interconnects. Excessive delays from long wires often exhibited in bus-based systems are likely avoided. Also, a NoC implementation relies less on dedicated point-to-point interconnects between devices and the bus. Process elements are connected via common switching and routing elements, over which the devices share the link utilization. Ultimately, better resource utilization is obtained [3].

#### **1.2 Problem Statement**

The MITRE Corporation sponsored this project to replace communication architecture used in the existing embedded digital signal processing chips, called a *control plane*. It is a separate data path reserved for command and control information, such as device configuration and status messages. The control plane is used to configure these waveform devices through writable registers or memories and reading information from these devices. Real-time signal is not handled by the control plane. Such data is routed through dedicated high-performance point-to-point interconnects outside of the control plane. These data paths handle constant data traffic, whereas the control plane oversees infrequent control traffic.

The previous implementation of a control plane suffered from many limitations. The new control plane must exhibit more flexibility, as the requirements having been expanding with each new project. In the past, issues such as latency and throughput were sacrificed in favor of

simplicity and faster development cycles. Future designs may require more scalable architectures with respect to these parameters. The previous control plane was also an application of a network-on-chip. However, its architecture suffered from many issues, such as high latency and poor link utilization, with a large number of interconnected devices. As the MITRE design engineers have experienced, the number of devices needed in these DSP applications will continue to rise and the systems will become increasingly more complex.

#### 2 Network-on-Chip

Network-on-chip (NoC) is an emerging multiprocessor communication architecture in VLSI design. This type of communication replaces a traditional shared bus between the many processing elements on the chip. NoCs use routing elements and switches to pass messages between one another rather than point-to-point connections characteristic of shared busses [2]. This area of VLSI design and research heavily depends upon the development of networking technology. However, they are very distinct fields each containing distinct applications. Network-on-chip for VLSI must take many parameters into consideration, such as chip area and power consumption [4]. The diagram in Figure 1 shows an example of a network-on-chip based design using routing elements to form interconnects between many processing elements.

A NoC implementation is defined by several parameters. These parameters are often selected to fit the needs of a design. For instance, these selections may favor low-power applications or favor high-performance systems. These parameters include (but are not limited to) the following:

- Topology

- Routing

- Switching

- Flow Control

Selections for each of these parameters carry its own advantages and disadvantages. There is no single selection of parameters that is favorable to all systems. General-purpose applications must consider the imposed limitations and the advantages gained by the selection of these parameters.

#### 2.1 **Topologies**

The arrangement and interconnects between network nodes greatly effects a NoC's performance metrics. Such arrangements may send data through many nodes before reaching its destination. Other arrangements may provide more paths between nodes to minimize the number of nodes data must traverse.

#### 2.1.1 Shared Bus

A shared bus is a popular selection for on-chip communication [2]. This is perhaps the simplest communication medium. In this method, the connected devices are divided into two categories: masters and slaves. Masters are capable of initiating requests and slaves respond to these requests. Data busses, often appearing as a collection of grouped wires, transmit data between masters and slaves [2]. In this topology, only one device can drive its data or control information at a given time, as this bus is a shared medium, as shown in Figure 2. Consequently, only one transfer can occur and there is a need for central control to ensure that data and control information are routing correctly.

Shared busses create an issue of scalability. The two prevailing strategies for a shared bus use either multiplexer-based control of the data bus or tri-states. With tri-state implementations the amount of wiring is greatly reduced, as each driver of the bus is connected directly to a bus lines through a small tri-state buffer. The buffer is high-impedance when the device is not

5

selected to drive the bus. Consequences of a tri-state implementation include higher power consumption and lower clock speeds from increased latency [2]. Multiplexer-based busses multiplex the masters' data and control lines out to global busses destined for the slaves. This implementation requires more logic for many multiplexers as well as much more wiring from each of the masters and slaves. This topology also suffers from degrading bandwidth when adding more devices [1]. In terms of power consumption, shared busses tend to consume more power since a bus master has to drive each of the lines connected to slave devices [4].

#### **2.1.2 Ring Bus**

A common communication topology is the ring bus [5]. In this topology routers are connected in a circle; each router node is connected to the previous node as well as the following node, as shown in Figure 3. Messages initiated on the ring are passed from node to node until the message reaches the destination node. This greatly simplifies the decision logic for router nodes resulting in smaller and faster logic.

Figure 3: A ring bus.

Ring busses have the advantage of having shorter interconnects between nodes. By exploiting the nodes' spatial locality, adjacent nodes do not need long wire to connect them. Consequently, shorter wires contribute less latency resulting in higher communication speeds [1].

By nature, the ring bus can be pipelined. Each node in the bus can be considered a stage of the pipeline. This allows multiple messages to be inflight on the network at a given time. The pipelining of ring bus allows for a potentially high throughput in the system but suffers greatly in latency as the number of nodes increases.

#### 2.1.3 Mesh Network

Another common NoC topology is a *mesh* [5]. This type of topology places network nodes in a grid-like configuration, like the network shown in Figure 4. Each node in a mesh is connected to four other nodes and likely a processing block as well. Messages are passed from node to node until reaching the node connected to the target device.

Figure 4: A mesh network.

Like the ring bus, a mesh network can have shorter connections between nodes. This eases wiring routing and placement on silicon as well as controls latency and power consumption through these links [5]. This again allows for higher operational clock speeds.

A particular advantage of the mesh topology is possibility for several messages to be inflight on separate pathways unlike the ring bus with only a single path. While this can reduce congestion and latency in delivery, it can also introduce other issues such as deadlock and out-oforder data.

#### 2.1.4 Star Network

The *star* network topology works quite differently from the ring and mesh topologies. With the ring and the mesh, adjacent nodes are connected to one another to pass information around the network. A star network contains a central node that is connected to each other node. All network traffic must pass through this central node [6]. Figure 5 depicts the star network topology.

#### Network-on-Chip

Figure 5: A star network.

Such a topology greatly simplifies routing. Peripheral nodes will always forward data to the central node. Data will only come from the central node, which eliminates issues of contention for that link. Routing in the central node requires minimal path-making decision, as it is connected to all other nodes. Despite the simpler routing, performance is heavily dependent upon traffic patterns. A busy and congested network will occupy the central node's resources needed by all inflight messages [6].

#### 2.1.5 Comparison of Topologies

Each of the available topologies offers some advantage to NoC designers. For busses and star networks, that advantage is simplicity. The advantage of a ring or mesh network is having a better density (occupying less chip area). The chip area consumed by the NoC is a major factor in the network's scalability—how the network performs as the number of nodes increases. Due to the shorter and more local interconnects on mesh and ring networks, they are amongst the more scalable networks. Star and bus topologies quickly introduce wiring congestion in silicon and thus are limited in scalability. Ring and mesh topologies have been popular NoC choices because of the scalability [5]. However, chip area is not the only constraint on scalability. Table 1 lists the major differences between these common network topologies used in networks-on-chip.

|        | Complexity                   | Scalability            | Wiring                                                                      | Routing                                                       | Connection                                           | Latency                                                                  |

|--------|------------------------------|------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------|

| Shared | Simple                       | Not<br>scalable        | Potentially<br>long<br>interconnects                                        | Simple<br>routing<br>(arbitration)                            | Point-to-<br>point                                   | Dependent on<br>load and<br>traffic                                      |

| Ring   | Simple                       | Not easily<br>scalable | Short<br>interconnects                                                      | Simple<br>routing;<br>one path                                | Packets;<br>forward to<br>destination                | Grows<br>proportionally<br>with number<br>of nodes                       |

| Mesh   | More<br>complex<br>than ring | Fairly<br>scalable     | Short<br>interconnects                                                      | More<br>complex<br>routing<br>than ring;<br>multiple<br>paths | Packets;<br>forward to<br>destination                | Moderate;<br>faster paths<br>than rings                                  |

| Star   | Simple                       | Not easily<br>scalable | Interconnects<br>grow in<br>length and<br>number with<br>number of<br>nodes | Very<br>simple<br>routing                                     | Packets;<br>forward to<br>destination<br>in two hops | Congestion at<br>the central<br>node can lead<br>to excessive<br>latency |

Table 1: A comparison of common NoC topologies based on important parameters.

Other factors in network topology scalability include power consumption, wiring complexity, cost, and latency [5]. The ring bus performs well in each of these categories but latency. A ring bus use short links between nodes and has considerably few links between nodes. This greatly simplifies wiring placement on-chip. Also, routing logic is nearly trivial on a ring bus. However, latency suffers greatly as a result. In the worst case, a message must traverse every node in the network.

The mesh topology reaches a fair compromise across these parameters for control planes similar to the one requested by MITRE. It shares the shorter interconnects as in the ring bus. Routing logic is more complex but not excessively taxing on hardware resources. Having many links per node introduces path diversity, allowing for shorter worst-case routing paths than the ring. Also, latency scales much better than a ring.

#### 2.2 Routing

*Routing* is how nodes decide where to forward data packets. Nodes responsible for routing are typically called *routers*. Strategies for routing come in various degrees of algorithmic and hardware complexity.

#### 2.2.1 Deterministic Routing

A set of routing strategies called *deterministic routing* uses predetermined network paths to route data through the NoC. That is, the path between any two nodes will always be the same. Deterministic routing does not take the condition of the network into account in its decision-making process. This is why it is sometimes called *oblivious routing*. With deterministic routing, simpler algorithms can be developed that require less logic [2].

#### 2.2.1.1 XY Routing

A common type of deterministic routing is *XY routing*. This routing strategy is specific to 2D mesh topologies. Nodes can be thought to have an XY coordinate corresponding to its row and column in the mesh grid. Data is routed to adjacent nodes first in the X direction. That is, data is moved to the right column before navigating to the destination row (the Y direction).

Figure 6: Routing paths by the XY algorithm for a request from A to B and from A to C.

10

Network-on-Chip

#### 2.2.1.2 Source Routing

Another type of deterministic routing is called *source routing*. This method does not require complex routing logic. Routing is determined by the initiator; each node transversal is determined and encoded in the message. This is a computationally light routing protocol but it suffers from increased message size from the overhead of routing bits [6].

#### 2.2.2 Adaptive Routing

The other case of routing strategies is *adaptive routing*. In this class of algorithms, routers analyze the current state of the network. This information is used to find a path to the destination that is less congested than a direct path. The goal of this approach is to gain performance from reducing latency due to network congestion [3].

While in deterministic routing messages can be easily routed to the shortest paths, adaptive routing strategies do not necessarily make this guarantee. Messages can be routed along longer paths on the way to the destination in order to avoid congestion and stalls. These decisions are called *misroutes* and can have negative effects on performance.

A major issue that arises with adaptive routing is *livelock*. When livelock occurs, a message is continually misrouted, never reaching its destination. In applications such as the MITRE control plane, data loss is not acceptable and this issue would have to be resolved. Measures must be taken in the routing algorithm to ensure that all messages are able to eventually reach their destinations [3].

#### 2.2.3 Comparison of Routing

The fundamental tradeoff between routing strategies is the trade of chip area and wire routing for performance. With deterministic routing, messages typically follow minimal paths but are susceptible to network congestion. Their routing logic is typically simpler than with adaptive routing strategies. Adaptive routing can take measures to avoid network congestion but requires more complex logic to ensure the prevention of error conditions such as livelock.

Ultimately, simple routing strategies like XY routing are favorable when hardware size is a concern and performance is not a primary goal. Depending upon traffic patterns this strategy could still give good performance. In a latency-critical system a robust adaptive routing algorithm is likely a good choice.

#### 2.3 Switching

While routing determines *where* messages are sent within a router it does not dictate *how* this data is sent. This is determined by the *switching* method. Two main types of switching techniques are used: *circuit switching* and *packet switching*, described in the following sections.

#### 2.3.1 Circuit Switching

The first major technique, circuit switching, creates a link between the sender node and destination node. Before a message is transmitted, a request must be sent to allocate a physical channel between nodes. The destination node sends a notification back to the sender signaling the sender to transmit its data. The established path (or "circuit") between the nodes remains open until the message is received by the destination node. The intermediary nodes forming the connection are blocked from use in other paths until the current transfer is complete and the nodes along the path are released.

Circuit switching offers high throughput when the channel is allocated. Aside from the initial latency from the setup of the connection, there is no additional latency or stall when the channel is established [2]. Such a method favors low, infrequent traffic, possibly containing large amounts of data. This method would not be suitable for small messages, as the setup overhead would become more significant [1].

#### 2.3.2 Packet Switching

The alternative to circuit switching is known as *packet switching*. This method of switching uses *packets* that carry the information necessary for routing. Rather than setting up the connection prior to transmission, connections are instead made as a packet progresses through the network. It is common that packets are subdivided into smaller units called *flow-control digits*, or *flits*. A packet contains a *head* flit, potentially many *body* flits, and a *tail* flit. The head flit is the beginning of the packet and contains the necessary routing information for the packet. Head flits serve to allocate router channels for the remaining flits of the packet. The final tail flit of a packet frees the router channel [3].

Three main strategies are used in packet switching: *store-and-forward*, *virtual cut-through*, and *wormhole switching* [2]. The simplest of these is store-and-forward (SAF). This technique buffers the entire received packet before transmitting it to the next node. Virtual cut-through (VCT) switching works in a similar manner. The VCT method allows flits to move to the next node as soon as space becomes available. While space is not available, flits are buffer locally.

The final method is wormhole switching (WH). In this method each flit moves one at a time to the next node. This creates a string of nodes carrying individual flits of the packet, as shown in Figure 7. By this method, flits do not accumulate at a single node when stalled. An advantage of this is that each node is not burdened by large buffer requirements [2].

Figure 7: An example of wormhole switching.

#### 2.3.3 Comparison of Switching

The main difference between circuit and packet switch methods is to how well they address network traffic patterns. The overhead of establishing a channel in circuit switching can be wasteful if many messages need to be sent often. This does not harm packet switching, as each packet is capable of routing itself. In packet switching packets do not enjoy the same guaranteed performance as in circuit switching. Since the link is allocated to the inflight transfer in circuit switching, no other transactions can stall it. In packet switching many packets may be contending for a common network resource.

Wormhole switching has the advantage of using less buffering, therefore reducing its footprint on the network. SAF and VCT both require full packet buffers to store backed-up data.

In wormhole switching, only a single flits need to be buffered. Wormhole and VCT switching also offer better throughput and latency as the entire packet does not need to be buffered in each node like in SAF. These two methods, however, have the potential to create more network congestion, as their packets can span many nodes, like in the example in Figure 7. The orange packet is attempting to allocate the North buffer of next router that is held by the blue packet. They also run a greater risk of producing deadlocks [2].

#### 2.4 Flow Control

Link-level flow control is the method by which the network ensures data integrity. It is at this level data loss is prevented. This level of communication must respond appropriately to network conditions such as stalls.

#### 2.4.1 Stall-and-Go

In a Stall-and-Go flow control based system adjacent routers signal one another when they are ready to receive data. There is a stall signal on each channel of the router directed at the incoming data link (the "upstream" router) and another coming in from the outgoing link (the "downstream" router). Routers produce a STALL signal when they are not ready to receive data otherwise a GO signal is given. When a channel is given a downstream STALL signal, the router must suspend transmission until given a GO signal.

In digital logic, such signals would be given as sequential outputs. That is, they are updated on one clock edge by the sender and observed on the next active edge by the receiver. It should be noted that this is not adequate time for the stalled node to pass on the STALL to other downstream routers in the same cycle. For this, each channel requires a small flow control unit.

The input port to a router must have the capability of buffering two flits. In normal operation (GO), only one register is needed. However, since stalls cannot be passed upstream instantaneously the stall router must have a backup register to capture this transmission [2]. Once the STALL signal is captured on an active edge, it can be simply repeated on that channel's upstream stall signal. That is, the incoming stall from the receiving end becomes the next outgoing stall on the transmitting end. This prevents data loss over the link. Figure 8 contains can example of this behavior.

Figure 8: An example of Stall-and-Go flow control.

#### **2.4.2 ACK-NACK**

An alternative strategy to Stall-and-Go flow control is ACK-NACK flow control. This method places the burden of buffering on the transmitter rather than the receiver. The transmitting node must keep the flits that it transmits until receiving an *acknowledgement* (ACK) from the receiver. If a *negative acknowledgement* (NACK) is received, all flits buffered that have received an NACK must be retransmitted [2].

#### 2.4.3 Comparison of Flow Control

The main difference between the two described methods is buffer overhead. Since these flow control units must be a part of each link in the network it is important to reduce their contribution to chip area and power dissipation. The Stall-and-Go method only requires two flit buffers and a simple state machine to maintain data integrity. The ACK-NACK requires more significant buffering requirements to retain several transmitted flits. Also, ACK-NACK potentially retransmits flits that were not lost or corrupted thus adding to the delivery latency. Stall-and-Go introduces no additional latency penalties from stall recovery [2].

Network-on-Chip

#### 2.5 Complications of Networks-on-Chip

Each of the discussed strategies offers many strengths to a NoC but can also introduce vulnerabilities and complications. Each of these shortcomings can have detrimental effects on the functionality of the system or on the integrity of transmitted data. Measures must be taken to address these issues in order for a NoC to be reliable.

#### 2.5.1 Deadlock

A common threat to data integrity in a network-on-chip is *deadlock*. Deadlock occurs when contending packets prevent one another from advancing indefinitely. One should consider two cars facing one another on a narrow road. Neither car can continue until the other moves out of the way. Deadlock can suspend the operation of large portions of the NoC and is thus unacceptable in any NoC-based system. In general, a NoC designer must be acquainted with two types of deadlock: *routing-dependent deadlock* and *message-dependent deadlock* [7].

#### 2.5.1.1 Routing-dependent Deadlock

A *routing-dependent deadlock* condition is caused by contention of network resources as a consequence of message routing [7]. Such deadlocks are purely a consequence of the routing algorithm, network topology, or both. A popularly referenced example of deadlock is depicted in Figure 9. In this example four packets form a square of adjacent nodes in a mesh network. Each packet wants to cycle counterclockwise. However, the channels necessary to do so are already allocated. They will not be available for the requesting device until the new channel is allocated. This produces a deadlock as none of the packets will ever be able to advance.

Figure 9: A classic example of deadlock [8].

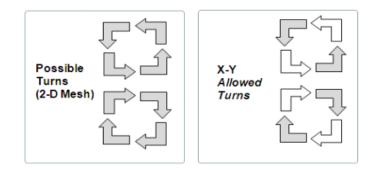

The possibility of a deadlock on a mesh network can be predicted with the *Turn Model*. This method relates the dimension of the mesh to the number of illegal turns (ie. North-East, South-West). For an *n*-dimensional mesh, the number of illegal turns must be at least be n(n - 1). The Turn Model proves that on a 2D mesh network is deadlock-free, as four of the eight possible turns are illegal, as shown in Figure 10 [8]. Since packets must be routed in the X-direction first, the turns South-East and North-West are not legal, for example.

Figure 10: Allowed turns in XY routing [8].

#### 2.5.1.2 Message-dependent Deadlock

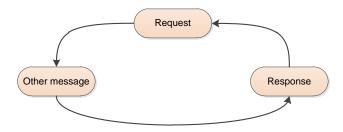

Message-dependent deadlock is the consequence of dependences in higher levels of the NoC protocols [9]. In particular, this occurs from collisions between different types of messages used by network devices [7]. One such example of message-based deadlock is called a *request-response dependency* [9]. This issue arises from an endpoint's response message being stalled in the network by a request message. For instance, in the situation where an initiator is sending a message to an endpoint while the endpoint is responding to a previous message. The endpoint cannot *consume*—or take the message out of the network—until it has transmitted it response message due to buffering requirements. The incoming request to this endpoint is now stalled in the network. Switching implementations such as wormhole switching exacerbate this issue as many routers and channels are blocked until this message can be consumed. In the situation where a second device is sending a message that requires the channels occupied by the first initiator's response. Ultimately, the message from the other device blocks the first endpoint's response. The response message prevents the request from being consumed. The request message prevents the other message from the other device blocks the first endpoint's response.

dependency between the progresses of the three message, guaranteeing deadlock, as shown in Figure 11.

Figure 11: An example of dependencies between network messages.

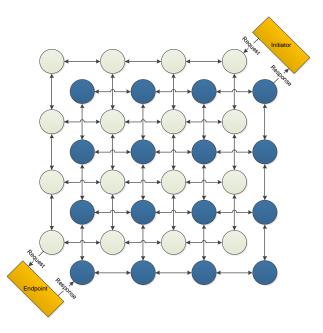

Typically one of the four following solutions is used to avoid message-based deadlock: physically separate networks, virtual networks, buffer-sizing, end-to-end flow control [7] [9]. The first two solutions approach the issue of message-based deadlock by dividing the data flow of request and response messages. This is referred as *strict ordering* [9]. The last two solutions attempt to use buffering to remove the possibility of deadlock.

The buffer sizing solution works on a principle known as the *consumption assumption* [9]. The assumption states that an endpoint must consume all messages it receives. The ideal solution to this problem is an infinitely large buffer to store all incoming messages. Removing the messages from the network deallocate the link resources used by the message and therefore avoid these messages from causing deadlocks with messages dependent upon these links [7]. No such buffer is possible in a real-world application, however, so buffers can only be made adequately large to store incoming messages before responding. This practice is very costly in terms of chip area from the significant buffer requirement and is unknown in network-on-chip applications [9].

End-to-end flow control is also based on the consumption assumption. In particular, credit-based end-to-end flow control dictates that for each connection between a pair of devices a number of credits are issued informing the sender of how many messages the receiver is capable of receiving. As a result, more effective and practical buffer sizes can be attained. However, cost associated with maintaining the credit system in is a burden on the network interface hardware [9].

Using physically separate networks avoids the issue of these dependencies entirely [7]. Since requests and responses do not have to contend for the same resources there are no potential

dependencies and thus no chance of deadlock. Of course, this comes at the expense of additional hardware to construct the second network. A physically separate network resembles the network in Figure 12.

Figure 12: Physically-separate request and response networks to break message-based deadlock.

The other type of strict ordering uses separate virtual channels rather than separate physical channels. In this system a physical channel is divided into several virtual channels. Each virtual channel contains a buffer for storing a portion of a message (such as a flit). Each message type is assigned a virtual channel. The virtual channels composing a physical channel are multiplexed such that one virtual channel drives the physical transmission medium. This requires additional arbitration logic to ensure that the virtual channels are fairly assigned to the physical channel [6]. Like the physically separate network virtual channel cannot use the resources associated with another channel, as they are strictly allocated for that particular resource. Additionally, link utilization suffers from the inability of the channel to transmit simultaneously [9].

#### 2.5.2 Livelock

*Livelock* is an issue that arises in adaptive routing systems. A packet in livelock will be continually routing along a path that will never reach its destination. This could be in response to patterns of congestion in the path to the destination node.

Livelock can be resolved in a number of ways. One simple way to avoid this complication is by using a *time-to-live* (TTL) counter in packets. The counter is decremented at each node traversed. When the counter reaches zero, the packet is discarded. This prevents the packet from wasting network resources. Another solution to livelock is to introduce age-based priority rules. As the packet circles it destination, it will eventually preempt the offending traffic and reach its destination [6].

#### 2.5.3 Starvation

In NoC and bus-based systems some devices may have the ability to initiate enough requests to effectively block another device's requests from being accepted. This is called *starvation*. This is a great vulnerability in purely priority-based systems [6]. Starvation can be avoided by algorithms that consider *fairness*, should as a *round-robin* system. In a round-robin system, the last granted source is set to the lowest priority [2]. This prevents the same source from dominating the request process.

Another way of preventing a starvation is *time division multiple access* (TDMA). This method gives each source the chance to transmit for a certain fixed amount of time. Each source transmits in a fixed order. This ensures that all sources have a chance to access network resources [1]. A disadvantage of this system is that sources without data to send are still allocated bandwidth. This reduces the link utilization of the given channel.

#### **3 Requirements and Specifications**

The previous MITRE CRB control plane is lack of many desirable features for reusable IP. Such issues included a lack of documentation, lack of expandability, and strict limitations on system parameters and characteristics. The sponsors from MITRE Corporation designed this project to build a new IP package for a control plane to suit the needs of both current projects was well as future projects.

#### **3.1 General Goals**

A major requirement for this project is the development of significant documentation. The CRB IP included minimal documentation. It had basic descriptions of the intent of the written RTL code but was difficult for others to understand. No formal specification or user guide was provided. Consequently, the new control plane was required to be thoroughly documented in RTL in form of comments as well as in a formal specification sheet and user guide to assist in deployment. This specification was to include detailed descriptions of component design as well as detailed descriptions of the non-standard protocols and interfaces.

The MITRE Corporation is interested in a general-purpose control plane platform. This new control plane is not intended for a specific application or project. It must be flexible for a wide range of applications. For example, the control plane has to support both high-performance applications as well as low-power applications. As a result, parameters such as power dissipation, wiring delays and latency, and chip area had to be considered in the design.

Another limitation of the previous CRB design is that it only allowed for a single initiator. Only one device could initiate requests onto the bus. The new MITRE control plane is required to allow for not only multiple initiators but for a large number of initiators. The single initiator limitation from the CRB could potentially be an issue in many future projects at MITRE. The new control plane was required to support many initiators to remove this limitation on future systems.

The sponsor's vision of the new control plane includes a priority on the reuse of this IP package. The aforementioned considerations each contributed to the reusability of the new implementation. The control plane is required to be designed with the ability to add additional interface protocols. The sponsor also requests a convenient and well-documented method for

adding other protocol layers over the NoC implementation. This is intended to reduce the design and verification resource needed to modify existing IP (either in the control plane or interconnected IP cores) to conform to new protocols used in future designs.

Another major requirement of the project is the verification of all IPs used in the control plane package. This step is to ensure that any future project to include the control plane IP can be assured that the IP behaves according to specification. This is intended to alleviate design engineers who will be using this IP from the burden of verifying this interconnect logic in each design. The control plane IP is intended to be distributed with detailed tests and test plans that demonstrate its functionality and validation.

#### 3.2 Control Plane Specifications

The design goals for the new control plane in Section 3.1 describe the general goals for the new system and their motivations. These goals shaped a list of specific requirements that guided the design methodology for this IP package. The following list enumerates these design requirements.

- *Scalability* The control plane must be adaptable for a wide range of applications including but not limited to high-performance systems and low-power applications. The design should allow for a multilayered system.

- *Size* The system must support a large number of devices; up to 1024 endpoints and initiators.

- *Performance* Efforts to control congestion and excessive delays due to wiring must be taken to ensure desirable performance and scalability.

- *Reliability* Reliability is possible the most important aspect of this system. It is imperative that no data is lost and all transactions complete. The system must not be vulnerable to complications such as *deadlock*.

- *Interfaces* The control plane must offer the capability to support at least the following standard interfaces to ensure compatibility for commonly used devices:

- MITRE OpenCore Protocol (OCP) Memory<sup>1</sup>

- Serial Peripheral Interface (SPI)

<sup>&</sup>lt;sup>1</sup> MITRE implements a limited subset of the OCP Memory protocol, as described in [12].

- "SRAM" interface providing a basic address-data interface

- AMBA 2.0 Advanced High-Performance Bus (AHB)

It should be noted that the Control Plane is not to be limited to neither a particular interface nor overlying protocol.

- *Error Reporting* A mechanism must be provided for endpoint devices to provide detailed error reporting to requesting initiators.

- *Documentation* The system is to be documented both in RTL code as well extensively in a separate specifications document. This is intended to promote the reuse of the final deliverable.

- Verification Full and thorough verification of this system is greatly important. Guaranteeing correctness of operation prior to deployment will significantly reduce design time of future projects and reduce the required man-hours for adequate verification. A set of tests must be provided with the system demonstrating its correct operation as well as recovery from errors and rare or unforeseen corner cases.

#### 3.3 **Project Deliverables**

The planned deliverables for the new control plane are the following:

- An IP package encapsulating the functionality of the control plane.

- A specification document describing the major functional components and their interfaces.

- A detailed test plan and set of testbenches demonstrating the functionality and correctness of the IP package.

- A user guide to facilitate using and extending the delivered IP package.

- A code repository of all files used to create and test these deliverables.

- A briefing to the MITRE E536 department on the development and use of this IP package.

Methodology

#### 4 Methodology

Careful consideration is taken to ensure that the specifications for the control plane would be sufficient for MITRE's applications and projects in the near future. Each design alternative presented in Chapter 0 was considered for how well it may satisfy the sponsor's needs. This is to ensure finding a sufficient and adaptive solution for on-chip communication architecture.

#### 4.1 Topology

Multiple topologies were made possible in this control plane to comply with the sponsor's requirements. The MITRE control plane was designed to support several *local* mesh networks. The overall structure of the network—the *global* topology—was allowed to be configured by connecting local meshes with a *bridge* component.

The mesh topology was selected because of its balanced parameters with respect to scalability. This topology places routing elements relatively close together, reducing wiring latencies and place-and-routing congestions in synthesis. The mesh topology also offers simpler position-based routing algorithms that simplify hardware design and reduce chip area costs.

The use of a multi-layered topology allowed groups of related devices to be grouped together in an efficient fashion. By dividing into many meshes, the dimensions can be configured in a more efficient fashion. For example, without local meshes the whole NoC would be included in a single mesh. Devices would have to be placed in a larger number of rows and columns, potentially increasing message latencies. Additionally, unused locations in the mesh would be wastefully allocated and synthesized. Hardware efficient can be gained by dividing the NoC into several meshes of related devices hardware efficient can be gained. As these local meshes will likely see infrequent traffic with devices in other groups (meshes) the need for a higher-performance links between mesh routers is unnecessary. Therefore, the system could benefit from connecting these meshes with lower-performance bridge components.

#### 4.2 Routing

The XY routing algorithm was selected for routing within local meshes. Each node in the NoC was decided to be assigned a unique identifier including the following information: the *mesh identifier*, the *x-coordinate*, and the *y-coordinate*.

The local mesh routing algorithm was selected to be simple and fast. The simplest of routing algorithms come from the class of deterministic algorithms. XY routing offers a simple routing strategy that can be efficiently mapped into hardware. Advantageously, XY routing eliminates the possibility of routing-based deadlock.

Adaptive routing strategies have the potential to offer better latency from avoiding congested network paths but introduce many complications. Network devices would have to be concerned with out-of-order received packets, deadlock conditions, and also livelock. Additional hardware in the routers and network interfaces would be needed to prevent or correct these issues. Additional data such as sequence numbers and time-to-live fields would be necessary in packets, increasing the message overhead.

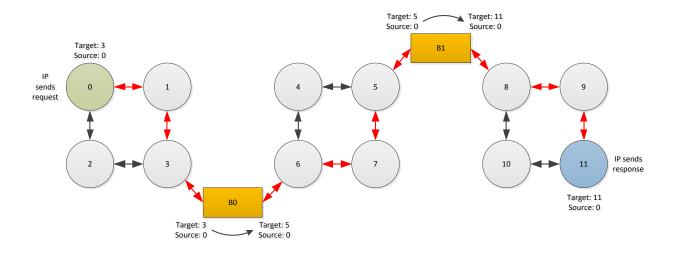

The selection of XY routing greatly simplified the role of the router component. The router routes packets based on a small target address field in the packet. For better latency and buffer performance, this target address field was constrained to be contained in the head flit of the packet. The address field contained the local mesh's identifier number as well as the X and Y locations of the target node. As this implies, the router was only responsible for routing within the local mesh. The router component was effectively unaware of the rest of the NoC to which it was connected. This system-level awareness was built into other NoC components.

#### 4.2.1 Bridge

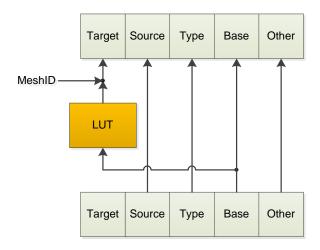

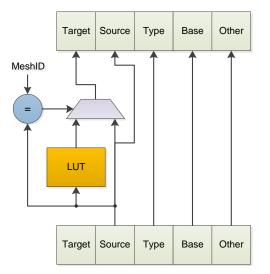

Since the router components could only route within their local meshes an additional component was needed to route data globally. The bridge component was used as a channel between two meshes. Packets entering the bridge from one mesh were passed to the mesh on the other end of the bridge. These packets passing through the bridge were translated to into the addresses known in new local mesh. As a consequence the bridge needed to be aware of the overall system. The target address used in the local mesh addressed the bridge on that network. Additional information, such as the original sender or the request address, was used to find the next bridge to traverse or the destination device. Such routing could be easily achieved through look-up tables (LUT). These look-up tables are generated at design time, likely by a software deployment tool. The simplicity of this solution came at the expense of cost in terms of hardware and chip area. The network diagram in Figure 13 shows an example of the request translation process.

Figure 13: An example of address translation for initiator requests across a bridge.

A concern for the architecture of a bridge component is the ability for a response packet to return to the initiator device. In order for a packet to be able to return to the sender, the sender must be known. This was decided to be encoded in the packet. A separate *Source* would be used to encode the initiator's address. Just as the bridge needed a lookup table to find the next target for a request, it also needs a lookup table for responses. This lookup table, however, uses the *Source* fields rather than the base address. The diagram in Figure 14 shows an example of this response translation process.

Figure 14: An example of address translation for endpoint responses across a bridge.

Methodology

### 4.3 Switching

When the selection for the switching strategy was made the advantages of circuit and packet switching were matched with the sponsor's requirements. It is determined that traffic on the NoC would be considerably infrequent and have potentially large messages. Such a traffic pattern matched the advantages of circuit switching. This type of switching offers better throughput to long messages as the channel is allocated prior to transmission. However, packet switching is selected to simplify hardware. It was determined to be simpler to allow packets to allocate network and channel resources as they progressed through the NoC rather than pre-allocate them as in circuit switching.

The type of packet switching that was selected for the MITRE control plane was wormhole switching. This type of switching was selected because it offered a low buffering cost per router. As each channel of each router would require these packet buffers this buffering cost could become quite significant in the chip area of the entire NoC. Wormhole switching also allowed for better throughput than the SAF and VCT methods. The wormhole switching was implemented without virtual channels. Virtual channels were not implemented in order to avoid the additional complexities of virtual channel allocation. This was motivated by an effort to keep the underlying NoC components simple.

#### 4.4 Flow Control

The most appropriate method of link-level flow control for the control plane NoC was determined to be the Stall-and-Go method. It was selected because of its low overhead implementation and high degree of reliability. Stall-and-Go had the advantage of have low buffering costs which was important in controlling the chip area consumed by the NoC. This was an important consideration as the flow control buffering unit was used on each input link in the NoC.

Additionally, Stall-and-Go offered good stall recovery. In Stall-and-Go, recovering for a stall did not incur additional latency, allowing for fast stall recovery. Unlike the other flow control option ACK-NACK, the Stall-and-Go method did not require the retransmission of packets.

Methodology

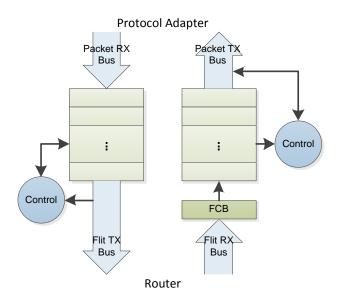

#### 4.5 Network Interface

IP cores needed a way to send and receive data on the NoC. This capability was built into the network interface. IP cores connected to the NoC via dedicated links on the router components called the *local* link. It was through this link that data entered and exited the NoC. Each endpoint or initiator on the NoC was assigned a router on one of the local meshes. For endpoint IP cores the addresses in the endpoint's address range on the NoC would translate to the address router to which the endpoint was connected. When a router received a packet destined for its own address, the packet would be routed to the local port. This system differed from the previous MITRE control plane that implemented the network interface inside the router component. Such an implementation limited the flexibility of the router component as it needed to be connected to an IP cores (consequently required the development of repeater component). Also, only one protocol—OCP Memory—was implemented on the CRB.

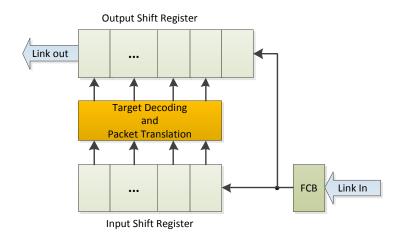

A requirement of the new MITRE control plane was to allow for several standard interfaces connected to IP cores as well as the easy integration of additional protocols in the futures. This was facilitated by decoupling the network interface from the router component as described previously. Additionally, the network interface was divided into two components: the *packet processor* and the *protocol adapter*. The network is illustrated in Figure 15.

Figure 15: Composition of the Control Plane network interface (NI).

Methodology

#### 4.5.1 Packet Processor

The objective when designing the network interface was to make the details of the NoC transparent to the IP core. This was implemented in the packet processor layer. This layer of the system provides two buffers: one for data entering the IP core from the NoC and another for data exiting the IP entering the network. As seen in Figure 15, the packet processor connects to the protocol-specific component called the *protocol adapter* by a simple shared bus. This bus offers a wide data bus for passing the raw packet into the protocol adapter for further processing. A simple handshaking mechanism was provided to allow the protocol adapter to stall incoming data.

#### 4.5.2 Protocol Adapter

The protocol adapter was the layer of the network interface that directly interfaced with IP cores. It was at this level that data would ultimately be exchanged between the network and the IP core. This functionality was isolated to this component to allow for easier and faster integration of additional protocols to the control plane. Design engineers were intended to use the packet processor component to connect to the NoC and follow a basic template for packet generation. The design engineer is responsible for designing the IP interface protocol as well as control logic for the packet processor bus.

As mentioned previously, the lower level packet processor removed many aspects of the underlying network, such as flit headers and stall signals. Other aspects such as packet structure and network node locations, however, were still known to the protocol adapter. Such knowledge of the network was necessary in the packet generation process for initiator IP cores. Such protocol adapters needed the capability to interpret a request address from the IP core and produce a network address that routed the generated packet to the destination node.

The concept of a separate protocol adapter allowed the concept of custom packet structures to become simpler to implement. The packet bits not used in routing were ignored by the routers and bridges. This data was simply passed along to the next routing element. Similarly, this data was not affected by the packet processor. Packet processors were given the potential to process additional application-specific information.

#### 4.6 Packet Structure

The new MITRE control plane offers a flexible packet structure. In order for simple, general-purpose routing elements to be designed, some restrictions had to be imposed, however. Figure 16 illustrates the general packet structure of a packet used in the new NoC control plane. It should be noted that the fields necessary to routing were positioned at the beginning of the packet for minimizing routing buffer costs.

| Target Sour | се Туре | Base | Local Address | Application-specific Data |

|-------------|---------|------|---------------|---------------------------|

|-------------|---------|------|---------------|---------------------------|

#### Figure 16: General packet structure for the MITRE control plane.

The first fixed field in the control plane packet is the *Target* field. This field is a *mesh address*, meaning it contains a mesh identifier number, an X location, and a Y location. This address identifies the node to which the packet is being routed on the current local mesh. This field is positioned at the beginning of the packet so that routers only have to read the head flit in order to allocate the correct channel on which to transmit the packet. The *Source* field identifies the mesh address of the original sender of the packet. This field is used by endpoints and bridges to generate the target address of a response message. The *Type* is used to identify the type of network packet. This system implements two packet types: *requests* and *responses*.

The next two fields are the *base address* and *local address*. This system is very similar to that used in the previous MITRE control plane implementation. Each unique base address identifies a single endpoint IP core. The local address acts as the request address for the endpoint device. This address field is required to be sized according to the largest device address space. The motivation for such as scheme is for smaller decoder logic for the lookup tables for initiator protocol adapters and bridges when determining the new network address from the request address. This makes it necessary for these routing elements to only buffer the base address and not the local address.

The remaining bits of the packet are left open for application-specific use. Bits that would likely reside in these bits are operation codes, read and write data, and error values. By not imposing requirements on these bits additional protocols and functions can be added in the future. For example, a new command can be implemented to perform a write to the target device without generating a response packet. Imposing such packet structure limitations would have hindered much future expansion and alternative use of the MITRE control plane. With reuse and expandability at the forefront of the project requirements, such restrictions are avoided.

## **5** Implementation and Design

This section provides a detailed view of the underlying architecture of the control plane. The methodology developed in Section 4 is implemented with a bottom-up approach. The fundamental components are built and tested first. After successful testing of one layer the next layer is then built over it.

#### 5.1 Flow Control Buffer

The Flow Control Buffer (FCB) is used to ensure that no data would is lost across data links. The buffer uses the Stall-and-Go type flow control to control traffic through the buffer. In this implementation, the buffer is designed with two flit registers. Under normal operation (no stalls) the *forward* register receives flit transmitted across the input flit bus, or link. This register is used as the output register of the block as well. The second register, the *save* register, holds flits that would otherwise be lost in the stall. The block diagram in Figure 17 shows the implementation of the Flow Control Buffer.

Figure 17: Block diagram of Flow Control Buffer.

The need for the component arose from the complications of passing the STALL signals through sequential logic. When a router is signaled STALL from a downstream (receiving) router, the STALL signal is not processed by the stalled router until it has transmitted its flit. Consequently, the downstream router must have buffer space to receive this transmitted packet. This is the purpose of the Save register. The Save register stores the value of the incoming flit when the channel is initially stalled. The value in the Forward register is retained until a GO signal is received, at which point the flit has been accepted and stored by the downstream router. It is also at this point that the Save register is copied into the Forward register.

Aside from its buffer responsibilities the Full Control Buffer must also remember its stall state as well as propagate stall information upstream. A simple state machine retains the stall state of buffer. It contains a single input: the downstream stall signal from the router to which the buffer's output is connected. The state machine always progresses to the STALL state when the input is STALL and always transitions to GO when the input value is GO. The state transition diagram is shown in Figure 18.

Figure 18: State transition diagram for the Flow Control Buffer state machine.

Upstream stalls are an important part of the design of the Flow Control Buffer. When a STALL is received from a downstream router, both registers in the buffer are now occupied and the buffer cannot store any more data. Consequently, the buffer must indicate to the upstream router that no more data can be accepted so a STALL signal is generated back. When the buffer is given the GO signal the save register is now empty. The upstream router can now be signaled that data can be transmitted again. Given these facts, the upstream stall signal can simply be the downstream stall signal. Since it is a registered (sequential) output the downstream input value will not appear on the upstream output at the next clock edge.

A special functionality is built into the Flow Control Buffer. An additional output is provided for use in the router component. This is a combinatorial output supplying the next flit to be transmitted. According to the stall values and current state, the next flit could be either the current flit (in the Forward register), the flit in the Save register, or the flit on the input link. An updated version of the Flow Control Buffer block diagram is shown in Figure 19 reflecting this additional output and the stall state.

Figure 19: Final block diagram of the Full Control Buffer.

## 5.2 Router

The Router component is the fundamental building block of the Control Plane. This component is responsible for transporting packets within local meshes. It is shown in Section 5.3 that this component can serve over utilities as well.

#### 5.2.1 Architecture

Given a local mesh topology each router was designed to connect to four adjacent routers as well as to connect to an IP core through a dedicated fifth link, as shown in Figure 20. Each link was designed to support bidirectional traffic. That is, a router can simultaneously transmit and receive on a link.

**Figure 20: Router component interconnects.**

The Router component is designed with five bi-directional ports. There is a total of five input channels and five output channels. Each of these output channels is capable of establishing a channel. It is the input channels' role to request an output channel. An output channel accepts the input channel's request when it is available to make a connection. From here forth, the terms *inport* and *outport* are used to describe router input channels and output channels, respectively.

Transmission channels within the Router are configured through the *switch*. The switch is responsible for routing the appropriate data and control signals between connected inports and outports. This component allows all five outport channels to have simultaneous transmissions. The block diagram in Figure 21 illustrates the interconnection between inports and outports through the switch.

Figure 21: Routing interconnects and transmission paths.

#### 5.2.2 Interfaces

The Router component interfaces with other Routers through the flit bus links. Two types of information are carried over these links. These are the flit busses and the stall signals. The flit busses carry the divided packet bits for transmission. The stall signals are control signals that indicate whether the receiving node is capable of receiving packet data. It should be noted that these two different kinds of signals travel in opposite directions, as shown in Figure 22. For each router port, the transmit link of one serves as the receive link of the adjacent router port.

Figure 22: Links between adjacent routers.

#### 5.2.3 Router Inport

A router *inport* is a port through which data enters the router. It consists of an input flit link, an FCB, and a target decoder. The FCB is used to maintain data integrity across the link input. The target decoder is used to determine through which outport the new packet should be routed.

Figure 23 : Block diagram of the router inport.

The Router inport is designed to decode the target port with a single flit. This was done to prevent additional buffering needing and avoid the additional latency associated with buffering additional flits. The NextFlit output of the FCB is used to provide the routing information to the target decoder. This allows two packets to be processed back-to-back, preventing a one-cycle between requests. The target decoder produces a request vector, a target selector, and a default target selector. The request vector produces five parallel bits, each one assigned to issue a request to each of the five Router outports. The target selector is used to provide the switch with the desired outport. The default target selector is used to override the target selector. Instead of a routing an outports control signals (stalls and grants) back to the inport default signal values are routed instead. This behavior is desired when no request is made (no packet has entered the inport). Otherwise, an inport would receive control data from any outport. If that outport had an

established channel its signals would reach the inport despite having not requested it. This could result in the propagation of unnecessary stalls in upstream routers and links.