# Worcester Polytechnic Institute Digital WPI

Major Qualifying Projects (All Years)

Major Qualifying Projects

May 2014

# Active Filter for Single-Phase Power System

Brent Daniel McGrath Worcester Polytechnic Institute

Thomas Reidy Powell Worcester Polytechnic Institute

Wesley J. DeChristofaro Worcester Polytechnic Institute

Follow this and additional works at: https://digitalcommons.wpi.edu/mqp-all

#### Repository Citation

McGrath, B. D., Powell, T. R., & DeChristofaro, W. J. (2014). *Active Filter for Single-Phase Power System*. Retrieved from https://digitalcommons.wpi.edu/mqp-all/3871

This Unrestricted is brought to you for free and open access by the Major Qualifying Projects at Digital WPI. It has been accepted for inclusion in Major Qualifying Projects (All Years) by an authorized administrator of Digital WPI. For more information, please contact digitalwpi@wpi.edu.

# Active Filter for Single-Phase Power System

A Major Qualifying Project Report submitted to the Faculty of Worcester Polytechnic Institute in Partial Fulfillment of the Requirements for the Degree of the Bachelor of Science

| By:                  |

|----------------------|

|                      |

| Brent McGrath        |

|                      |

| Wesley DeChristofaro |

| Wester Beemisterate  |

| Thomas Powell        |

| i nomas Powen        |

Submitted On: May 1, 2014

Submitted To:

Professor Alexander Emanuel, Advisor, Electrical and Computer Engineering

### **Abstract**

This study investigates the application and functionality of pure active power filters for current compensation in single-phase power systems. A small scale proof of concept design was constructed, using components which were studied, justified, and chosen based upon desired characteristics. The components were simulated on several different platforms to analyze their potential design feasibility. Based upon the study and simulation of this system the pure active power filter can be confirmed as a reputable form of harmonic filtering for single-phase power systems.

# Acknowledgements

Throughout the undertaking of this project, there have been several people who have proven to be great resources. First, Professor Emanuel, whose overall knowledge of the power realm and step-by-step guidance helped in realizing the important aspects of the project. Next, Radu David, whose background in DSP and experience with dsPIC microprocessing chips were vital in helping the group to understand the thought process behind selecting, using, and coding a dsPIC chip for a real-time DSP application. The team would also like to thank Robert Boise for his assistance during the acquisition of various design components. A final thank you goes out to the other fellow students who have helped provide assistance along the way, without all of you this project would not have been possible.

# **Authorship**

#### Abstract

- Written By

- o Wesley DeChristofaro, Brent McGrath

Chapter One - Introduction

- Written By

- Wesley DeChristofaro

Chapter Two – Background

- Written By

- o Wesley DeChristofaro, Brent McGrath, Thomas Powell

Chapter Three – System Requirements

- Written By

- o Brent McGrath

Chapter Four – Overall Design

- Written By

- o Wesley DeChristofaro(4.2), Brent McGrath(4.1,4.3-6)

Chapter Five – System Requirements

- Written By

- o Brent McGrath

Chapter Six – Digital Control System

- Written By

- o Brent McGrath(6-6.6.1), Thomas Powell(6.2)

Chapter Seven – Simulations

- Written By

- Wesley DeChristofaro(7.2-3), Brent McGrath(7.1)

Chapter Eight – Future Implementation Considerations

- Written By

- o Brent McGrath

Chapter Nine – References

- Written By

- Brent McGrath

# **Table of Contents**

| A  | bstract                                              | i   |

|----|------------------------------------------------------|-----|

| A  | cknowledgements                                      | ii  |

| A  | uthorship                                            | iii |

| 1. | Introduction                                         | 1   |

| 2. | Background                                           | 2   |

| 3. | System Requirements                                  | 13  |

| 4. | Overall Design                                       | 15  |

|    | 4.1 Non-linear Load                                  | 16  |

|    | 4.2 Active Power Filter                              | 16  |

|    | 4.3 Sliding Window Fast Fourier Transform            | 17  |

|    | 4.4 Ideal Current & Harmonic Distortion Calculations | 18  |

|    | 4.5 Duty Cycle Algorithm & PWM Generation            | 18  |

|    | 4.6 MOSFET Gate Driver                               | 18  |

| 5. | System Specifications                                | 19  |

|    | 5.1 MOSFET's                                         | 19  |

|    | 5.2 Digital Microcontroller                          | 21  |

|    | 5.3 MOSFET Gate Driver                               | 25  |

| 6. | Digital Control System Implementation                | 25  |

|    | 6.1 Main Clock & Auxiliary Clock Configuration       | 25  |

|    | 6.2 ADC Configuration                                | 26  |

|    | 6.3 Timer1 Configuration – ADC interrupts            | 27  |

|    | 6.4 Sliding Window FFT                               | 28  |

|    | 6.5 Duty Cycle Algorithm & PWM Generation            | 33  |

|    | 6.6 Alternative Applications                         | 36  |

|    | 6.6.1 PWM Configuration                              | 37  |

| 7. | Simulations                                          | 40  |

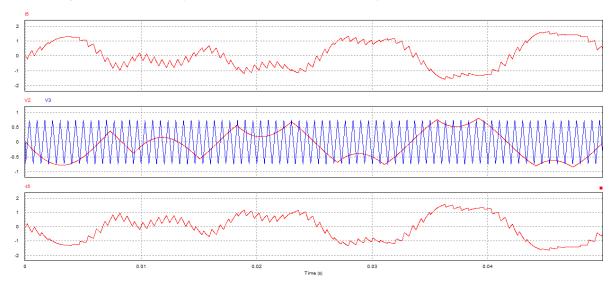

|    | 7.1 Digital Control Algorithm Simulation             | 40  |

|    | 7.2 PSPICE Simulations.                              | 43  |

|    | 7.2.1 Ouarter Bridge                                 | 44  |

| 7.2.2 Half Bridge                                      | 44 |

|--------------------------------------------------------|----|

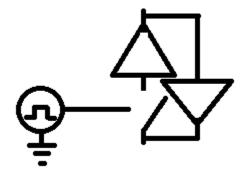

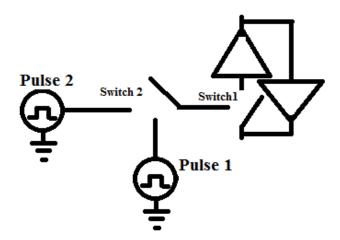

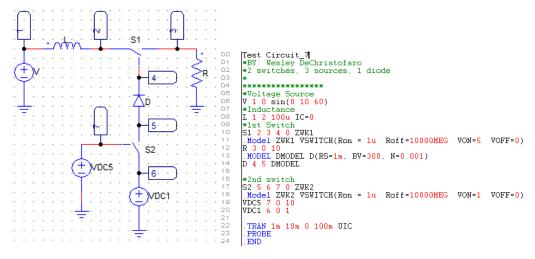

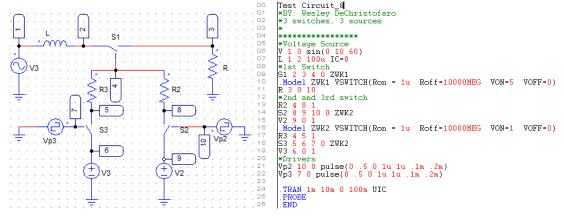

| 7.2.3 The PSPICE Switch                                | 45 |

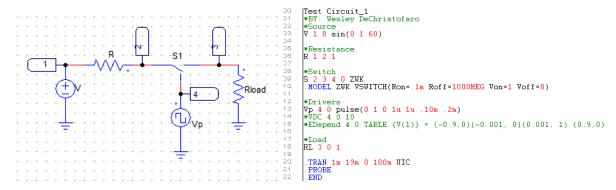

| 7.2.4 Test Circuit 1                                   | 47 |

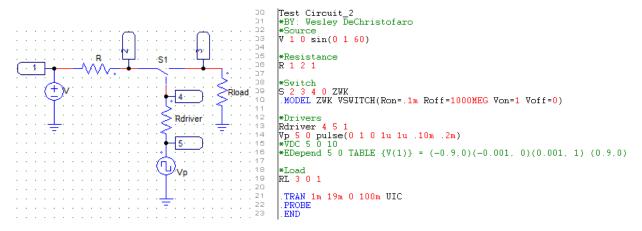

| 7.2.5 Test Circuit 2                                   | 47 |

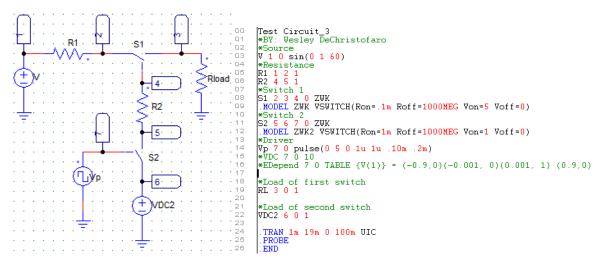

| 7.2.6 Test Circuit 3                                   | 48 |

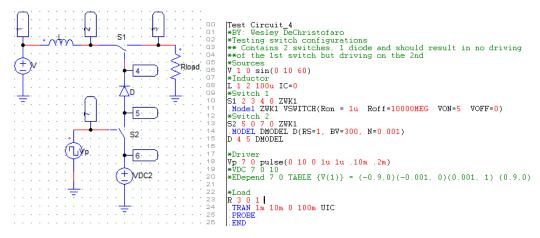

| 7.2.7 Test Circuit 4                                   | 48 |

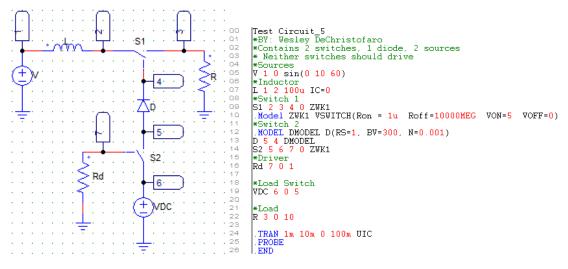

| 7.2.8 Test Circuit 5                                   | 49 |

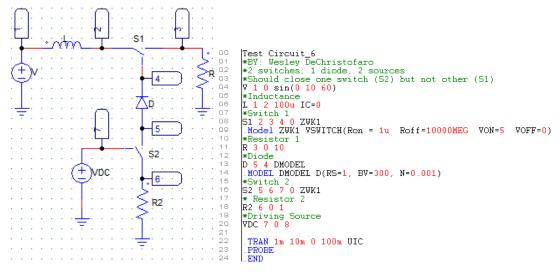

| 7.2.9 Test Circuit 6                                   | 50 |

| 7.2.10 Test Circuit 7                                  | 50 |

| 7.2.11 Test Circuit 8                                  | 51 |

| 7.2.12 Test Circuit 9                                  | 52 |

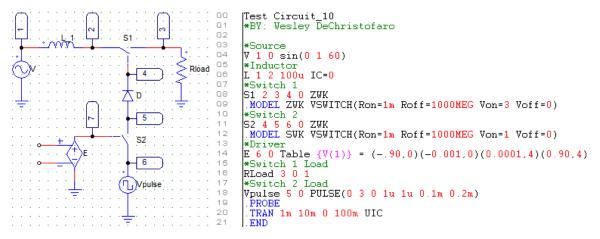

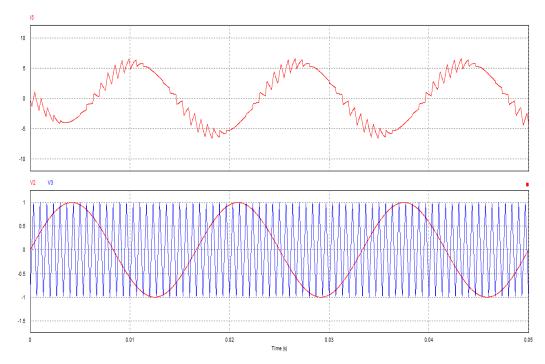

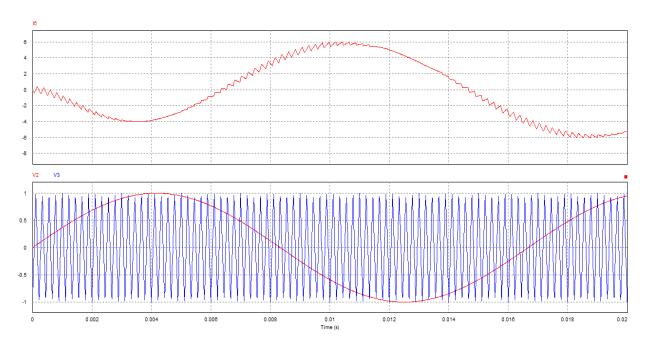

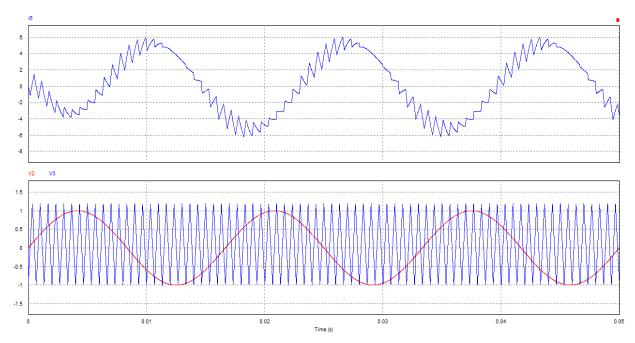

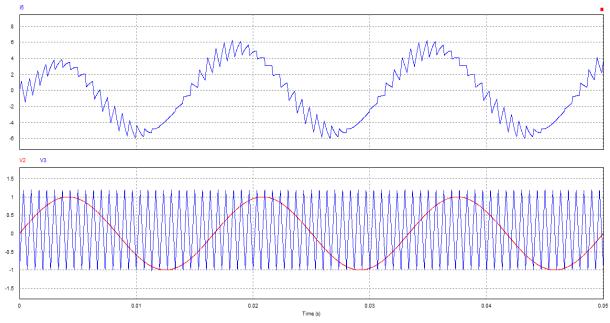

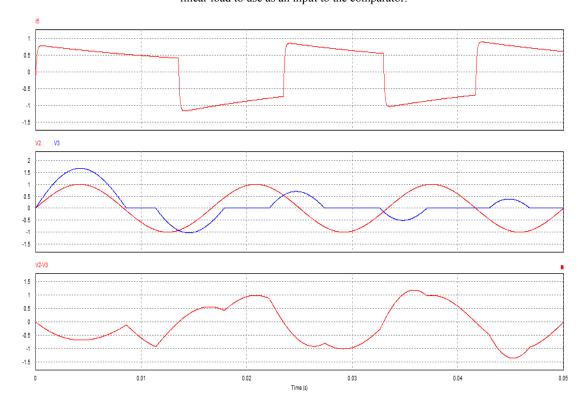

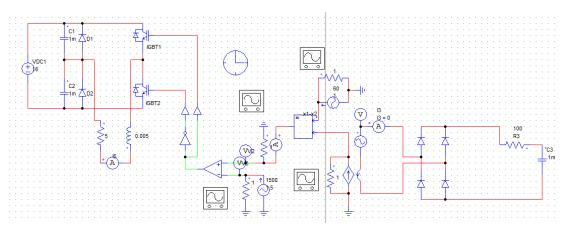

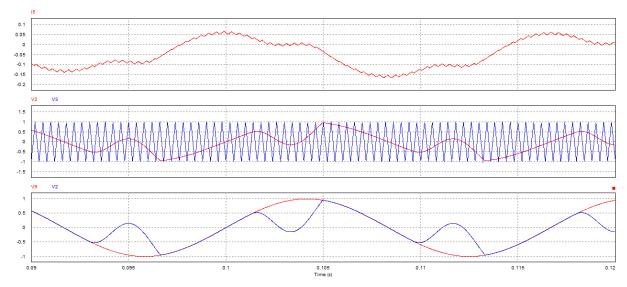

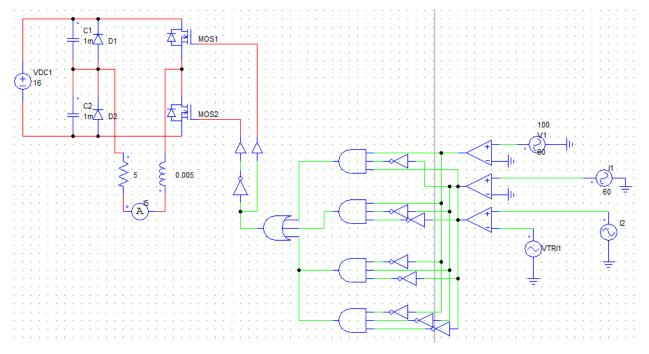

| 7.3 PSIM Simulations                                   | 52 |

| 7.3.1 PWM Creation                                     | 54 |

| 7.3.2 PWM Current Adaptation                           | 56 |

| 7.3.3 System Imperfections                             | 58 |

| 7.3.4 Attaching the Non-Linear Load                    | 59 |

| 7.3.5 Successfully Attaching the Non-Linear Load       | 60 |

| 7.3.6 Issues with PSIM Simulations                     | 62 |

| 7.3.7 Summarized Functionality and Results             | 62 |

| 7.3.8 Additional PSIM Ideas                            | 63 |

| 8. Future Implementation Considerations                | 64 |

| 8.1 Selection of MCU – Resource Management             | 64 |

| 8.2 Complex Duty Cycle Algorithms                      | 65 |

| Appendices                                             | 66 |

| Appendix A: Constants_Globals_Prototypes.h Header File | 66 |

| Appendix B: Init_Functions(GS502).h Header File        | 68 |

| Appendix C: MQP_Code.c Source Code File                | 73 |

| Appendix D: Enum_States.h Header File                  | 78 |

| Appendix E: Digital Control Simulation Matlab Code     | 79 |

| References                                             | 82 |

#### 1. Introduction

Within the world of electrical engineering where silicon chips hold trillions of transistors and billions of people depend on the function of computers there are countless ways that the basic principles of electricity have been applied to human life. Deep within that realm of engineering lives the study of energy transfer, transduction, transmission, and perhaps most importantly – control. Electricity provided to the masses in a common 50 hertz or 60 hertz waveform at some voltage is certainly a blessing to the world of electronics, but not all devices can work with such an input. When there is some device or application that desires a lower/higher voltage, current, frequency, or even a DC characteristic there has to be a change within that device rather than the entire utility grid. This is, in short, part of the job of power electronics. Power electronics includes anything that works to change or control a certain input to attain some different output for the use of a device.[1]

When working within large or small scale power systems however the control of electricity and power flow is no simple feat. Resistors are linear and easy to work with, but most devices contain more complicated non-linear, non-ideal components that by themselves can be difficult to control. Worse still however, are the underlying effects of non-linear components such as diode bridges that can create what are called harmonics. These harmonics exist at frequencies at multiplies of the fundamental or desired frequency with decreasing magnitude as they increase in order. This means that these additional harmonics are added to the original waveform and create some form of undesired distortion. The last harmonic which has a noticeable impact on the original waveform would be the 19<sup>th</sup> harmonic.[2]

In the world of macro power, where the utility has many homes, schools, hospitals, police stations, libraries, and other large buildings to supply it clearly has many connections. All of these buildings are considered non-linear, non-ideal loads which mean they will create harmonics. These harmonics, due to the loads, will feed into the line current and may be "passed down the chain" increasing the distortion. Power electronics involves the study of various ways of rectifying this situation.

Usually it is the responsibility of the consumer, based upon IEEE standard 519, to monitor and reduce the harmonic production of some loads. That production is greater for some than others, but with the correct knowledge it can be filtered. The filtering process depends on the application, but a popular form of filtering is utilizing active filters instead of passive filters to adjust to the changing harmonics to keep consistent filtering. This is important because each time a new consumer is added the harmonics on the line can change and affect what would need to be filtered somewhere else. Passive filters are set to filter a certain type and frequency of waveform (to a certain order of harmonic), while active filters can be made to adapt.[3]

These active filters work based off of a thorough understanding of the frequency and time domains and their relations. This is important since most things that consumers are concerned with can be explained simply in the time domain, while the more intensive concerns of the utility and providers are best handed in the frequency domain. This is because, as previously stated, the harmonic

distortion can be seen on the load lines, but are added to the fundamental. The ability to separate the harmonics from the fundamental exists much more appropriately in the frequency domain than in the time domain since harmonics occur at the same time but different frequencies than the fundamental or desired waveform.

In this report the study of a pure active filter, one without passive components, is centered around the idea that one can filter out harmonics of a non-linear load by understanding the difference between the line current (including harmonics) and what the ideal current would be. If this is the case then an active filter that responds to any change in the line current should be able to filter any change and always result in a clean, clear output waveform.

## 2. Background

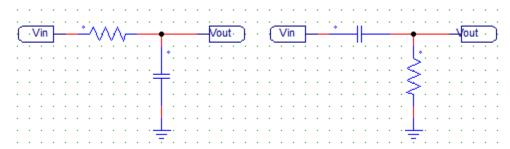

A filter in the most common sense is something that removes an unwanted feature, or aspect of something. This can range from filtering water to filtering your search for MQP parts on any given cite. In signal processing and engineering the only difference is that the unwanted component may be voltage or current distortion. Take for example the low and high pass filters found in basic electrical engineering and E&M theory, as shown in Figure 2.1, these filters can each be used to limit the operating frequencies of a circuit.

Figure 2.1: Passive Low and High Pass Filters

These filters pass low or high frequencies regardless of whether it is a fundamental or a  $13^{th}$  harmonic. This means that these filters, known to be part of the class of passive filters, can be used to filter out higher order frequencies. These filters have an element known as a time constant which is often equal to the resistance multiplied by the capacitance of the "RC" connection. This time constant is called  $\tau$ . The cutoff frequencies of the filters are directly dependent on this constant. A simple equation to represent the cutoff frequencies for both the basic high and low pass RC filters is shown in Equation 2.1.

$$f_c = \frac{1}{2\pi RC} \tag{2.1}$$

It should be noted that there are other kinds of low and high pass filters, such as second and third order filters, but these are the simplest ones.

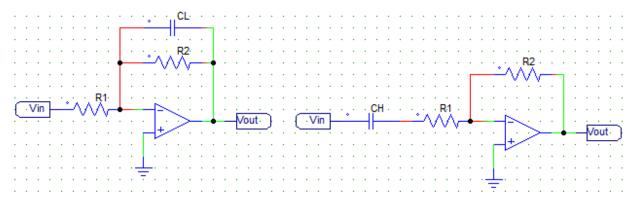

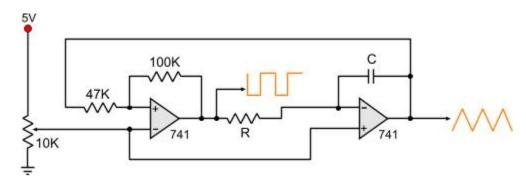

Additionally low and high pass filters exist in the active realm of electrical engineering. Although not referring to the class of active filters that this project pursues. These alternative filters use an operational amplifier in the configurations shown in Figure 2.2 to limit the bandwidth of Op-Amp based filters. The difference between these active filters and the active filter described throughout this report exists in how they are maintained. The filters that this project concerns are based around varying types of bridges and how the transistors in these bridges are driven to compensate for current.

Figure 2.2: Active Low and Active High Pass Filters

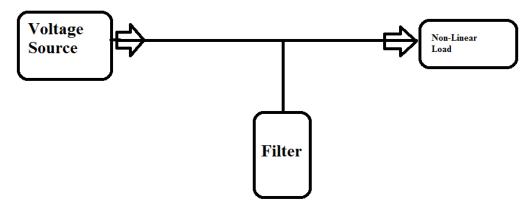

Passive filters, as those shown in Figure 2.1, include any filter that is constructed out of passive components such as inductors, capacitors and resistors. Although these components can at times be quite complex the passive term they earned is not to imply less functionality. They are called passive filters because their bandwidth and use is decided before construction and does not change without physical changing the circuit in which they exist. In other words a passive filter can be created to work with a certain set of frequencies and loads and then forgotten. Passive filters work very well with linear loads. The basic block diagram for such a filter is shown in Figure 2.3. An active filter on the other hand works with some kind of control scheme to allow it to constantly change to its load within certain restrictions. A common type of active filter is one made from an H-bridge of some type of transistor, whether it is a MOSFET, IGBT or BJT. This type of filter operates through the driving of the transistors to create some type of "filtering" or "compensation" current that would cancel out distortion.

Figure 2.3: Block diagram of basic passive filter operation

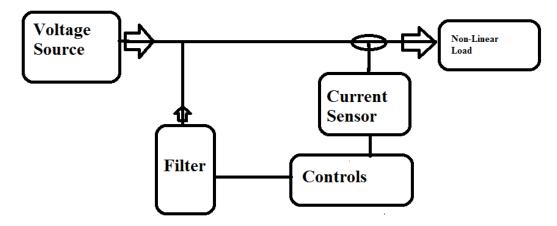

The aforementioned H-Bridge works with a degree of active controls and is referred to as a pure active filter, while those in Figure 2.1 are pure passive filters. There are also hybrid filters which use both passive and active components. This means they take some advantages of both and some disadvantages of both. Pure active filters (APF) work with an entirely active process and are the main concern of this report. Active filters have the benefit of being more controllable and working in a wide range of situations, yet they tend to be more difficult to work with, design and implement because of the many aspects involved in their operation. A simple block diagram for an active filter is shown in Figure 2.4.

There are some tradeoffs between pure and hybrid active filters because otherwise one type would be used for all applications. Hybrid filters require passive components, which work for a limited range of frequency applications. This means that if a system is to be expanded then the filter may need to be made larger with more passive components. This becomes an issue of size and cost. Pure active filters however have the complication of having complex and at times difficult to program and understand control systems. They allow for expandability but are in general just more difficult to produce and implement.[4]

Filters of many various types have very important functions in the day to day lives of mankind. The concern of this report is with the filtering of something previously mentioned called harmonics. Harmonics are the non-fundamental frequencies of a given waveform that are not desirable because they cause distortion in the input signal. For example, the magnitude of an ideal 60 hertz sine wave occurs at the fundamental frequency of 60 hertz. A sine wave with many smaller ripples could be produced by the superposition of the fundamental frequency signal with many other sine waves of higher frequencies, which are all multiples of the fundamental frequency. These higher frequencies are the harmonics. [2]

Filters are also used to filter out what is referred to as "noise". Noise is usually small and semirandom, but can reduce the overall quality of a signal. The noise components pollute a signal as a result of stray inductances, capacitances, heat or by being in the magnetic or electric field of a nearby electronic device. Noise reduction is the process of removing the noise and can be done through filtering, but can also be accomplished by shielding devices from their surroundings. Neither of these ideas are a focal point in this project, so they are not discussed in detail in this report.[5]

Figure 2.4: Example block diagram for an active filter

Referencing the block diagram in Figure 2.4, there are three blocks that require more explanation. This block diagram starts with a voltage source, which is connected to a non-linear load via an input line. The non-linear load is the load for the voltage source. This idea is the basis for the original system design. The non-linear load is a load that produced harmonics as a result of its non-ideal, non-linear response to an input signal. Most real life loads such as appliances, ovens, and even entire homes are non-linear. These non-linear loads would need to have filters applied to reduce the effects of their harmonic distortion on the system in which they exist. Another form of filtering may exist on many of these systems to make sure the load harmonics are filtered in some form or another. As the main concern of this report, line harmonics, is often the responsibility of the manufacture of a device or home based on IEEE standard 519.[3]

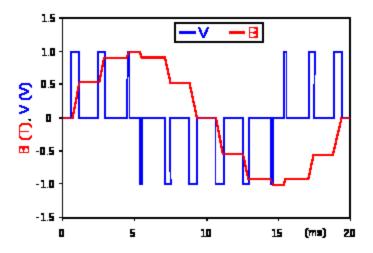

Due to these line harmonics, the non-linear load is responsible for distorting the seemingly ideal line current. Thus a current sensor, or current transformer, is needed to sample what the current is in the system. This sensor, in most applications, would need to be converted from analog to digital in order to be processed by a digital control system. Shown in Figure 2.4, the "controls" block is a general idea, which could represent many different types of control schemes. The "controls" block is where all of the processing and computation necessary to determine how to drive the gate of the transistors in the active power filter occurs. The basic concept behind the control scheme would be to find the difference between the distorted input wave found through the current sensor and the ideal input wave found on the input line. The mathematical difference found between the waveforms can be utilized to help produce the compensation current in the active power filter. There are many limitations and complications in creating a control system for a power system, which contains a large amount of harmonic distortion. In order to provide proper compensation,

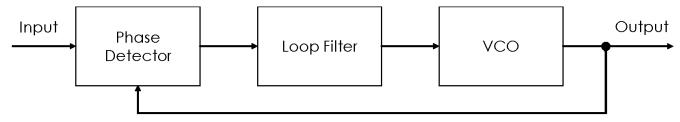

ideas such as the Phase-locked Loop(PLL) and/or power factor correction(PFC) can be implemented as components in the control system.

The method used to implement the control system depends on whether it resides in the digital or analog domain. In short, analog is things such as audio whether it be generated or the human voice. Digital on the other hand is usually things represented with "1" or "0" or "yes" or "no." The Digital domain seems like the best option for the control scheme because the time editing the code should be less than the time necessary to acquire additional analog components for an analog control scheme. An analog design might also require the rewiring of components and more time spent in circuit debugging.

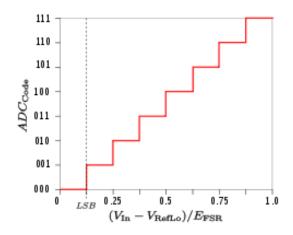

Due to the selection of the digital control for the design, a method of converting the analog signal to the digital domain was necessary. The analog-to-digital converter(ADC) was selected as the component which would take care of that task. The ADC is used to convert analog signals into digital signals. The ADC is an important component in digital devices, such as computers, because these devices cannot process continuous time analog signals. All digital devices operate in the discrete domain, so analog signals need to be sampled and converted into a binary representation before they can be processed. The ADC takes the samples of the analog signal and quantizes them by measuring their voltage values and assigning each a binary value. This is done by breaking down the voltage range of the analog signal into a piece-wise step function.[6] Each "step" of the step function corresponds to a predetermined binary value and an example of this quantization is seen in Figure 2.5.

Figure 2.5: Example of ADC Quantization Voltage Steps[7]

If the measured voltage does not exactly match with a binary value within the range, then the closest representative binary value is assigned. Once all of the samples of the analog signal are converted to binary values by this process, the analog signal is officially converted to the digital domain. Therefore the signal can then be digitally processed in the digital system. The number of steps of the ADC determines how accurate and how precise the conversion can be. If there are not

enough steps present then inaccuracies and loss of data can be introduced because the changes are too large. The analog signal would not be accurately represented in the digital domain when converted to binary.

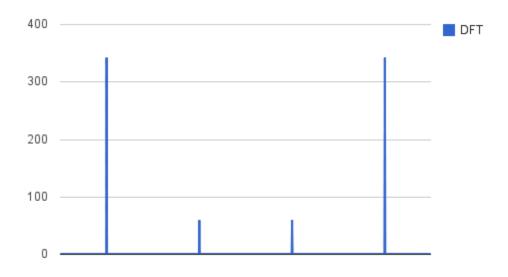

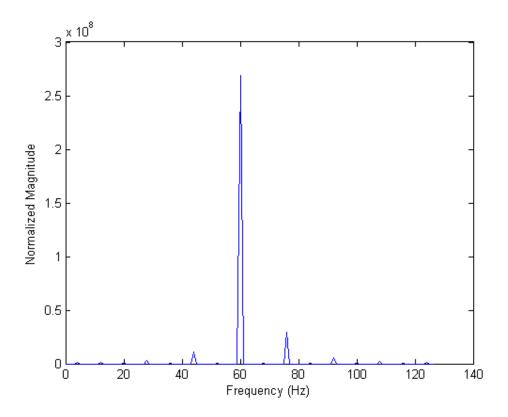

The digital control requires a method of determining the fundamental frequency of the input current signal. A possible method is using either a Discrete Fourier Transform(DFT) or a Fast Fourier Transform(FFT). The DFT and FFT are both mathematical algorithms, which take a signal from the time domain and convert it into the frequency domain. The DFT and FFT both produce the same result, but the FFT algorithm is much faster. The algorithms allow for a time signal to be viewed in the frequency domain, where the magnitudes of the different frequency components in the input signal can be observed. The frequency with the largest magnitude is the fundamental frequency and other frequency components of lower magnitude could be caused by noise, interference, or other harmonic frequency content. By selecting the frequency bin with the highest magnitude, the fundamental frequency can easily be extracted.

The FFT is labeled with the word, "Fast," because the FFT algorithm dramatically cuts down on the number of calculations which occur compared to the DFT. The formula for the DFT is shown in Equation 2.2.

$$X(k) = \sum_{n=0}^{N-1} x[n] \cdot e^{-\frac{j2\pi nk}{N}}, k = 0 \dots N - 1$$

(2.2)

For each new data point k, N multiplications and N-1 additions are completed. This results in roughly  $N^2$  computations after completing the direct Discrete Fourier Transform. By using the Fast Fourier Transform you can perform the same operation in N\*log<sub>2</sub>\*N computations. The difference in the number of total computations may not seem dramatic, but if a large number of samples are being iterated over, the difference can be significant. For example, if you have a set of data with  $N=10^{\wedge 8}$  samples, then a direct Discrete Fourier Transform would take  $10^{\wedge 16}$  calculations, but if you use the Fast Fourier Transform then it would only take  $26.5 \times 10^{\wedge 8}$  calculations. If each calculation took 1 nanosecond then the Fast Fourier Transform would take 2.65 seconds, while the direct Discrete Fourier Transform would take over 115 days! Based on this data, if a large number of samples are being iterated over, the Fast Fourier Transform is the only algorithm which completes in a reasonable amount of time. For this application, the Fast Fourier Transform is essential to achieving a real-time system.

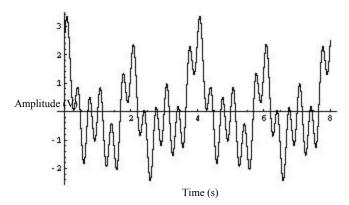

The objective behind the Fast Fourier Transform is divide-and-conquer. The first step in the FFT process is to take the data collected via the ADC and to break it down into parts. This division is done so that each part can be repeated to form a periodic signal of its own. Each of these periodic signals is then passed through its own Discrete Fourier Transform. This results in each signal having its own magnitude results for particular frequencies. The results from each signal are then added together, which results in a complete Discrete Fourier Transform of the input signal, but at a much greater speed then if the entire signal was processed at once. For example, take Figure 2.6, which is a complex signal.[8]

Figure 2.6: Example of a Complex Signal[8]

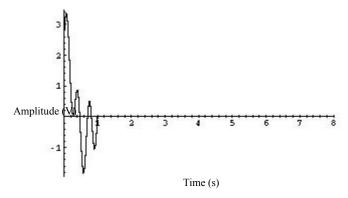

If the complex signal is broken down into smaller parts, each of the smaller parts can be copied and extended to form periodic sequences. This method allows the Discrete Fourier Transform algorithm to become more manageable. An example of a smaller section of the signal found in Figure 2.6 can be seen in Figure 2.7.

Figure 2.7: A smaller section of the signal of Figure 2.6[8]

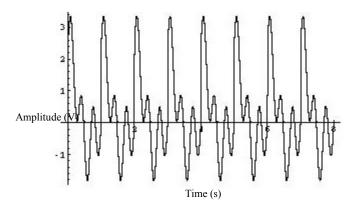

If the smaller section seen in Figure 2.7 was extended to become periodic, the signal would look like the signal seen in Figure 2.8. This signal can be passed through the Discrete Fourier Transform.[8]

Figure 2.8: The signal in Figure 2.7 repeated periodically[8]

The result of the Discrete Fourier Transform, as shown in Figure 2.9, is a set of magnitudes for the different frequencies found in the signal of Figure 2.9.

Figure 2.9: FFT/DFT Frequency Response of the signal in Figure 2.8

Finally, these steps are performed on the rest of the periodic signals and the magnitudes are all added together. This process drastically reduces the time necessary to perform the Discrete Fourier Transform analysis on the original signal.

Another one of the complications with the selection of a digital control is finding a method to extract the phase information from the input current. One of the methods used to determine the phase shift of a signal is the phase-locked loop. A PLL can be implemented as either an analog or digital component, but since the control system is digital the only way the phase can be extracted from the input is through the use of a digital PLL implementation. The PLL is a control system,

which is composed of three different components, including a phase detector, loop filter, and a voltage-controlled oscillator(VCO). A simple depiction of a PLL is seen in Figure 2.10.

Figure 2.10: Simple Phase-Locked Loop Input-Output Diagram

The input signal to the PLL is used as a reference signal into the phase detector. The phase detector compares the phase of the input reference signal to the phase of the output signal produced from the VCO and generates an output which represents the difference between the phases. The input reference signal is a sinusoid and the VCO output signal is also a sinusoid, so the phase detector can be modeled by Equation 2.3.[9]

$$PD_{out} = (A \cdot \cos(\omega_0 t + \phi_A)) \cdot (B \cdot \cos(\omega_1 t + \phi_B)) \tag{2.3}$$

In Equation 2.3,  $PD_{out}$  is the output of the phase detector, the  $\omega$  terms are the frequencies of the two signals input into the phase detector, the t terms are the time variable, the  $\phi$  terms are the phases of the two signals, and A and B represent the magnitudes of the two signals.

When the PLL is in a locked state, the two input signals are at the same frequency, so the product of the two signals can be simplified into Equation 2.4.[9]

$$PD_{out} = \left(\frac{A \cdot B}{2}\right) \cdot \left[\cos(2\omega t + \phi_A + \phi_B) + \cos(\phi_A + \phi_B)\right] \tag{2.4}$$

As seen by Equation 2.4, the output signal of the phase detector can be modeled as the summation of two sinusoids. One of the sinusoids has a frequency double that of the input reference signal and the other sinusoid is proportional to the cosine of the phase difference of the two input signals. The output of the phase detector controls the output of the VCO through the application of a lowpass loop filter. The purpose of the loop filter is to remove the sinusoid component of the phase detector output which has double the input reference signal frequency. The output of the loop filter is the phase difference between the input reference signal and the VCO output signal, which is ideally represented by a DC signal.

The DC signal output of the loop filter is input into the VCO and controls the frequency of the VCO output signal. Since there is a negative feedback loop between the VCO and the phase detector, the output of the VCO is driven to match the phase of the input reference signal. Once the two signals have identical phases, the cosine of the phase difference seen in the output of the phase detector will become zero. Under this condition, in order for the output of the PLL to be the input

frequency, the nominal frequency of the VCO needs to be set to the ideal input frequency beforehand.[9]

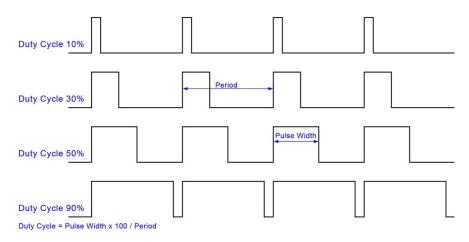

Since in the project a digital control is paired with an analog system, there needs to be a way for the two subsystems to communicate with one another. The purpose of the digital control is to drive the gates of the transistors in the active power filter, so a possible method would be pulse-width modulation(PWM). The PWM waveform applied to the active power filter does not produce a predetermined analog signal; it produces a signal that will dynamically control the on time of the transistors in the active power filter. A PWM waveform is a square wave with a variable duty cycle, which can range from one percent to 99 percent.[10] The idea of varying the duty cycle for square wave signals is shown in Figure 2.11.

Figure 2.11: Varying Duty Cycles in Square Waves[11]

As the duty cycle of the PWM waveform is increased, the average amount of time the square wave stays high increases. Therefore a higher duty cycle PWM waveform will increase the amount of time the transistor stays on. Another way to think about the PWM is in terms of voltages.

For most digital controllers, the PWM output is unipolar and can only be one of two states, either zero volts or 3.3 volts. By switching the output between zero volts and 3.3 volts periodically a square wave can be produced. This square wave only has two levels and with a 50 percent duty cycle has an average value of 1.65 volts. By changing the duty cycle the average value the square wave is on can also be changed. This allows for an average value anywhere between zero volts and 3.3 volts. A system which utilizes a bipolar PWM mode, rather than a unipolar PWM mode, can obtain more drastic changes in the output voltage of the transistors because the dynamic range of the voltages is larger. An example of bipolar PWM mode can be seen in Figure 2.12.

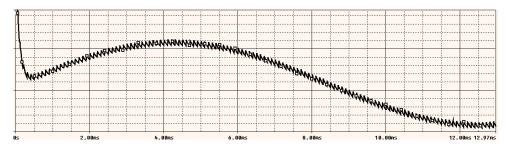

Figure 2.12: Bipolar PWM Application to produce an analog signal [12]

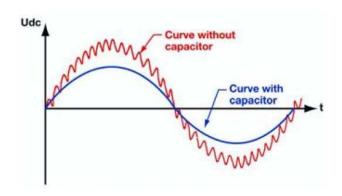

One of the issues with standard PWM methods is that the modulation of the square wave causes the analog output of the transistors to exhibit small step-like voltage deviations. These steps are caused by the lack of an immediate response from the transistors when a PWM waveform is applied. In order to obtain a specific output in the active power filter, the PWM waveform needs to alter its duty cycle to cause the output to go through intervals of increase and decrease. These changes can be smoothed out in the analog output by using components, such as capacitors, which can slow down the changes occurring in the output voltage or by increasing the frequency of the PWM waveform. Therefore the "smoothness" of the output signal produced is determined by both the frequency of the PWM waveform, as well as the capacitance of the capacitors used. An example of capacitor voltage smoothing can be seen in Figure 2.13.

Figure 2.13: Capacitor's smoothing effect on the Output Voltage[13]

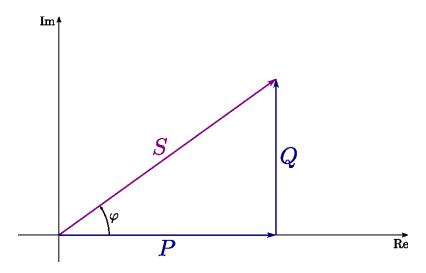

Power factor correction revolves around the idea of the power factor, which is the relationship between the real power and the apparent power in an electrical system. Shown in Figure 2.14 is the power triangle which relates the commonly used real power, or active power (P), with reactive

power (Q), and complex power (S). Power is measured in watts, reactive power is measured in var (volt-ampere reactive) and complex power is measured in volt-amperes. As such, power factor is the ratio between real and apparent power. The power factor figure is important because it tells an electrical engineer many things about the efficiency of a system. For example, with a unity power factor both the voltage and current of the system are in phase, meaning the current leaders or lags the voltage by 90 degrees. A load, non-linear or linear, with a low power factor draws more current than a load with a high power factor for the same amount of "useful" power transfer. Power factor correction is the process by which the output of a system is controlled in such a way that its input power factor does not decrease significantly and stays relatively constant.

Figure 2.14: The standard power triangle

## 3. System Requirements

An understanding of the requirements of the system was necessary before commencing with the design process for the active power filter. The active power filter design contains four major components: input source, non-linear load, active power filter, and a control system. The input source needs to be an AC signal, which is meant to simulate the signal found in a power system. If the necessary AC input voltage is less than the wall outlet voltage of 120 volts, then a variac could be used to scale down the voltage to a more reasonable level for testing purposes. The AC input voltage source is paired with an input inductance, so that there cannot be any instantaneous changes in the system current. The non-linear load needs to be able to produce a distorted input current, which will be added to the input current. In order for the load to be nonlinear, the current drawn by the load needs to be non-sinusoidal as the applied voltage on the load varies. Therefore the load should contain different configurations of at least one energy storage element, such as an inductor or a capacitor, and linear elements, such as a resistor.

The active power filter has a couple possible design options, including the full-bridge implementation and the half-bridge implementation. The full-bridge implementation utilizes four transistors in an h-bridge configuration, while the half-bridge implementation utilizes two transistors stacked on top of one another and they are connected in an h-bridge configuration with a set of series capacitors, which have the same value. For actual application, a DC capacitor would be placed in parallel with the h-bridge configuration of transistors, but for testing purposes a DC voltage supply can be used. The purpose of the DC capacitor or DC voltage supply in the active power filter is to serve as a DC voltage energy source, which can help to produce increasing current levels seen in the compensation current.

The control system component is the most open-ended because there a number of different design options to choose from. The requirement of the control system is to be able to provide the gates of the transistors in the active power filter with the proper control signals. The high-side transistors are driven with signals with duty cycles which are the inverse of the duty cycles used for the signals driving the low-side transistors. For this application, the choice was made to apply a digital control instead of an analog control, so there need to be digital blocks which sample the input current, determine the frequency, phase, and magnitude of the input current, determine the proper duty cycles for the drive signals, and produce the signals to drive the gates of the transistors in the active power filter. These system requirements for the digital control require the digital microcontroller chosen to have a high-resolution ADC, a couple timer modules, and a high-resolution PWM module with immediate duty cycle adjustment capability or a high-resolution digital-to-analog converter(DAC). The output voltage of the digital control would most likely be limited to the range of 3-3.6 volts, which would not be high enough to drive power transistors, so a method to step up the output voltage of the digital control would be necessary.

## 4. Overall Design

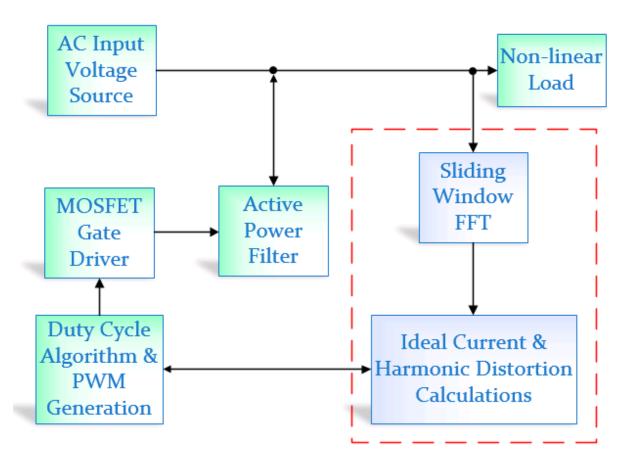

As can be seen in Figure 4.1, the proposed system functional block design consists of combination of analog and digital components which work together to correctly compensate for the harmonic distortion produced by the non-linear load. The main system consists of analog components, such as the MOSFET Gate Drivers, Active Power Filter, Non-linear Load, and Duty Cycle Algorithm and PWM Generation. The digital control system is composed of a DSP chip, which contains software/hardware code to implement a Sliding Window FFT and a method to calculate the Ideal and Harmonic Distortion Waveforms. Some of the key concepts considered when designing the project were phase matching, frequency matching, and a modulation method for driving the gates of the transistors in the active power filter to produce the proper compensation current.

Figure 4.1: Active Power Filter Design Functional Block Diagram

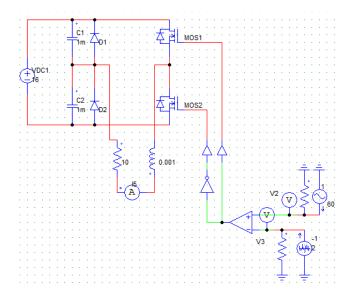

#### 4.1 Non-linear Load

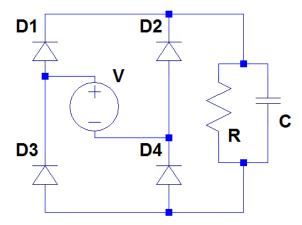

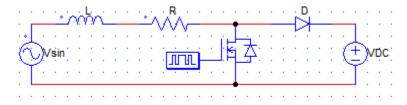

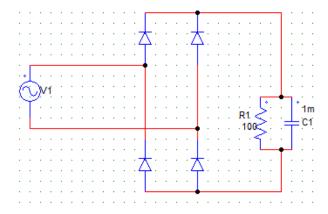

The non-linear load as seen in Figure 4.1.1, consists of a full-bridge rectifier in parallel with a resistor and capacitor.

Figure 4.1.1: Non-Linear Load Circuit Schematic

The full-bridge rectifier in the non-linear load is a set of four diodes connected in an H-Bridge configuration, where the input voltage and ground are connected between two different pairs of diodes that compose the legs of the bridge. The load is considered non-linear instead of linear because as the applied voltage on the load varies, the capacitor causes the current drawn by the load to be non-sinusoidal even if the input source is sinusoidal. The distorted input current produced by the load is added to the input current in order to cause current distortion at the input. The resistance seen in the non-linear load is varied in order to produce various distorted input current levels. These distorted input currents are used to test the overall effectiveness of the system.

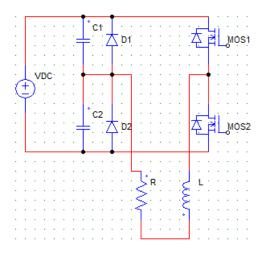

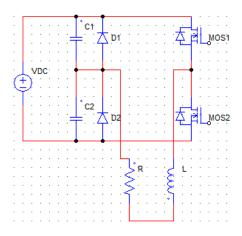

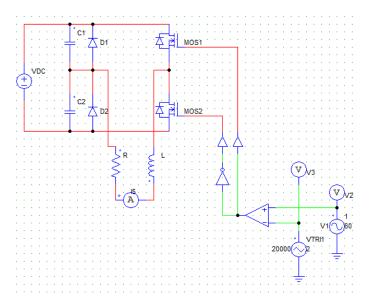

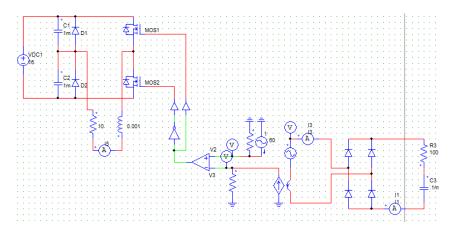

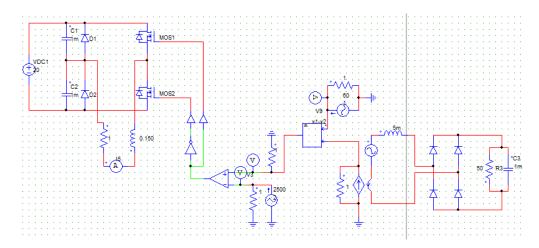

#### 4.2 Active Power Filter

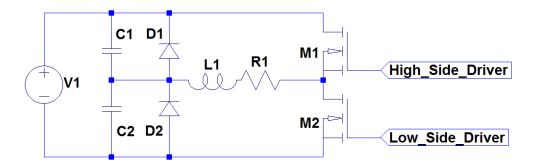

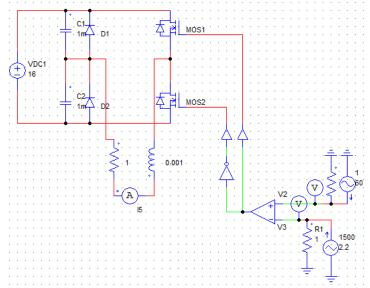

The active power filter, as seen in Figure 4.2.1, designed for this application consists of a half transistor bridge with stacked diodes and capacitors and a DC source. The inner connections of the "H" of the half bridge contain representative inductances and resistances. In designs that utilize an active power filter in this configuration, the two stacked capacitors are used to keep approximately half of the voltage of the DC source on both the high and low sides of the bridge. This, along with the diodes, allows for predictable current states. The MOSFET's, M1 and M2 in the schematic below, are driven such that only one is on at any given time. This allows for current through the resistance and inductance to either rise or decrease under the varying correct conditions. The current states for this bridge can be found along with other information about its performance and functionality in the beginning of Chapter 7.

Figure 4.2.1: Active Power Filter Circuit Schematic

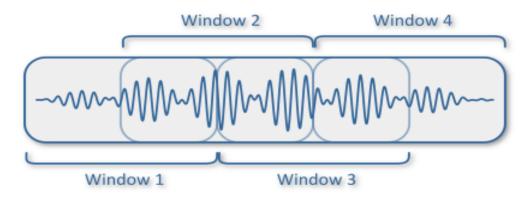

## 4.3 Sliding Window Fast Fourier Transform

Once the ADC collects samples of the distorted input current using a current transformer close to the non-linear load, a Sliding Window Fast Fourier Transform(FFT) is applied to the samples to extract the fundamental frequency of the system. An FFT converts a time-domain signal into the frequency domain, but since the input current of a power system can vary in frequency over time, the sliding window FFT will be used instead of the standard FFT to provide more accurate frequency results. A basic illustration of the Sliding Window FFT can be seen in Figure 4.3.1.

Figure 4.3.1: Visual of the Sliding Window FFT Concept[14]

A fraction of the newest samples in the current FFT window are used in calculating the next FFT window and doing this repeatedly for new samples provides the basic concept behind the Sliding FFT algorithm. Once the Sliding Window FFT calculation is complete, the indices of the output array can be analyzed to determine the fundamental frequency of the input current.

#### 4.4 Ideal Current & Harmonic Distortion Calculations

The Sliding FFT algorithm results in the determination of not only the fundamental frequency, but also the magnitude and phase of the input current. Once these values are extracted, the sin function from the math library can be used to reconstruct the ideal input current. The previous input current sampled from the line is the distorted input current, which is used in calculating the harmonic distortion waveform. The harmonic distortion waveform is used as a comparison waveform in the Duty Cycle Algorithm and PWM Generation block.

## 4.5 Duty Cycle Algorithm & PWM Generation

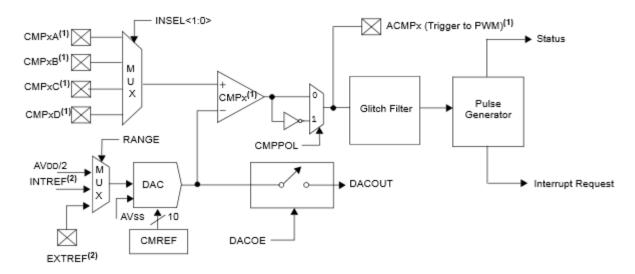

The duty cycle algorithm determines the duty cycle values of the PWM output waveforms, which are necessary to produce the proper compensation current in the active power filter. The duty cycle algorithm used here is relatively simple. An internal high-speed comparator inside the dsPIC33F chip is used to automatically determine the proper duty cycle values of the PWM output produced by the comparator. One of the inputs to the comparator is the harmonic distortion waveform, which is the distorted input current produced by the non-linear load. The harmonic distortion waveform is produced by a DAC inside the dsPIC33F chip. The other input to the comparator is a triangle wave produced by the analog triangle wave generator, which is input through a pin on the dsPIC33F chip. The frequency of the triangle wave can be increased, which would allow for smaller current deviations to be seen in the compensation current.

#### 4.6 MOSFET Gate Driver

Due to the low voltage capability of the output of normal microcontrollers, such as the dsPIC33F chip, which ranges from 3 volts to 3.6 volts, a component which steps up the voltage needs to be used. In this case, the MOSFET gate driver takes the PWM output voltages from the comparator and steps up the voltage to drive the gates of both the low-side and high-side MOSFET's in the active power filter. Since the MOSFET's being used in the active power filter are both NMOS transistors, the gate voltage of the high-side NMOS transistor needs to be approximately 10 volts higher than the low-side NMOS transistor. In order to accomplish this, a MOSFET driver with a bootstrap configuration is utilized to make sure the high-side MOSFET can be driven properly.

In order to set a constant reference voltage at the source of the high-side MOSFET, the supply voltage from the MOSFET driver is used as the reference. The bootstrap configuration at the high-side MOSFET has a capacitor connected between the supply voltage and the bias voltage of the MOSFET gate driver and is in series with a diode. The combination of the storage charge capability of the capacitor and the charge regulation of the diode allows the high-side gate voltage to be kept anywhere between 10 volts to 20 volts higher than the source voltage of the MOSFET. The use of the bootstrap configuration allows the high-side MOSFET to operate in the correct region of operation, while the low-side MOSFET can be driven in relation to ground. The use of

the MOSFET gate driver allows the gates of the MOSFET's in the active power filter to be properly driven by stepping up the voltage from the dsPIC33F microcontroller.[15]

# 5. System Specifications

Since the active power filter for this project is a proof of concept design, lower current and voltages values were used to simulate the effect of the filter on the efficiency of a power system. The maximum voltage chosen for the design of the project was 50 volts, while the maximum current chosen for the design was two amperes. The maximum power dissipation for each portion of the design was found through the completion of PSIM simulations of the active power filter system design. The maximum power dissipation in the non-linear load was determined to be three watts. In addition to the system specifications, since the design is a proof of concept design which would be tested in breadboards, each of the components selected for the design needed to have a DIP pin configuration also known as a through-hole configuration. All of the components selected for the design were found using the previously stated system specifications and the through-hole configuration as search filter parameters.

Most of the components used for the active power filter design were basic circuit components, such as resistors, capacitors, inductors, and diodes, which were chosen for the design based upon the voltage, current, and power dissipation ratings defined for the system. The desired values for the resistors, capacitors, and inductors in the design were determined based upon the simulation results. On the other hand, there were a couple components which were carefully selected based upon the initial system requirements.

#### 5.1 MOSFET's

The first of these carefully searched components were the MOSFET's. The singular MOSFET's were chosen over the IGBT and MOSFET H-bridge modules and the singular IGBT's due to their cost being much lower. The parameters used to perform the value analysis for the MOSFET's can be seen in Table 1.

Table 1: Value Analysis for MOSFET's

| Analysis Criteria |                       | Product | NTD58<br>(N-Cha<br>MOS | annel | IRF61<br>(N-Cha<br>MOS | annel | IPS105I<br>(N-Cha<br>MOS | annel | AOU4<br>(N-Cha<br>MOS | annel | (N-Ch | SN40<br>annel<br>SFET) | AOT2<br>(N-Cha<br>MOS | annel |

|-------------------|-----------------------|---------|------------------------|-------|------------------------|-------|--------------------------|-------|-----------------------|-------|-------|------------------------|-----------------------|-------|

|                   |                       | Weight  | Score                  | Total | Score                  | Total | Score                    | Total | Score                 | Total | Score | Total                  | Score                 | Total |

| 1                 | Breakdown Voltage     | 10      | 2                      | 20    | 4                      | 40    | 1                        | 10    | 4                     | 40    | 4     | 40                     | 4                     | 40    |

| 2                 | Maximum Power         | 8       | 3                      | 24    | 3                      | 24    | 3                        | 24    | 4                     | 32    | 4     | 32                     | 4                     | 32    |

| 3                 | Turn-on Delay Time    | 7       | 4                      | 28    | 4                      | 28    | 4                        | 28    | 3                     | 21    | 3     | 21                     | 3                     | 21    |

| 4                 | Turn-off Delay Time   | 7       | 4                      | 28    | 4                      | 28    | 4                        | 28    | 4                     | 28    | 4     | 28                     | 4                     | 28    |

| 5                 | Diode Forward Voltage | 9       | 3                      | 27    | 2                      | 18    | 3                        | 27    | 4                     | 36    | 4     | 36                     | 4                     | 36    |

| 6                 | Reverse Recovery Time | 4       | 3                      | 12    | 2                      | 8     | 0                        | 0     | 2                     | 8     | 2     | 8                      | 2                     | 8     |

| 7                 | Maximum Current       | 6       | 4                      | 24    | 2                      | 12    | 4                        | 24    | 2                     | 12    | 2     | 12                     | 2                     | 12    |

| 8                 | Price                 | 7       | 4                      | 28    | 4                      | 28    | 4                        | 28    | 4                     | 28    | 4     | 28                     | 4                     | 28    |

|                   | Total                 |         |                        | 191   |                        | 186   |                          | 169   |                       | 205   |       | 205                    |                       | 205   |

Each of the parameters used to perform the value analysis on the MOSFET's were given a different weight, based upon how important the parameters were to the active power filter design. Scores were then given to each of the MOSFET parameters, based on the score breakdown defined in Table 2.

Table 2: Score Breakdown for MOSFET Value Analysis

| Analysis Critoria     | Score Breakdown |             |                   |                |            |  |  |  |

|-----------------------|-----------------|-------------|-------------------|----------------|------------|--|--|--|

| Analysis Criteria     | 0               | 1           | 2                 | 3              | 4          |  |  |  |

| Breakdown Voltage     | Unavailable     | < 30 V      | 30 to 69 V        | 70 to 100V     | > 100V     |  |  |  |

| Maximum Power         | Unavailable     | < 15W       | 15 to 35 W        | 36 to 55 W     | > 55W      |  |  |  |

| Turn-on Delay Time    | Unavailable     | > 200ns     | 200ns to 100ns    | 99ns to 16ns   | < 16ns     |  |  |  |

| Turn-off Delay Time   | Unavailable     | > 400ns     | 400ns to 200ns    | 199ns to 120ns | < 120ns    |  |  |  |

| Diode Forward Voltage | Unavailable     | > 2 V       | 2 to 1.4 V        | 1.39 to 0.8V   | < 0.8V     |  |  |  |

| Reverse Recovery Time | Unavailable     | > 200ns     | 200ns to 100ns    | 99ns to 16ns   | < 16ns     |  |  |  |

| Maximum Current       | Unavailable     | < 2 A       | 2 to 4.99 A       | 5 to 10 A      | > 10 A     |  |  |  |

| Price                 | Unavailable     | > 3 dollars | 2.01 to 3 dollars | 1 to 2 dollar  | < 1 dollar |  |  |  |

The score breakdown seen in Table 2 was created based upon the information gathered from the research of the MOSFET's. The scores given to the MOSFET's in Table 1 resulted in a three way tie at 205 for the best MOSFET choice from the six different MOSFET's chosen for the value analysis. The best MOSFET for the active filter design was chosen to be AOT2N60 because the maximum rated current is close to the 2 amperes system maximum and the price is lower than the other two MOSFET's by \$0.10. The specifications of the AOT2N60, AOI4N60, and AOI5N40 can be seen below in Table 3.

Table 3: MOSFET Ratings used for Value Analysis

| Analysis Criteria |                            | AOI4N60<br>(N-Channel<br>MOSFET)<br>Value | AOI5N40<br>(N-Channel<br>MOSFET)<br>Value | AOT2N60<br>(N-Channel<br>MOSFET)<br>Value |

|-------------------|----------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|

| 1                 | Breakdown Voltage [V]      | 600                                       | 400                                       | 600                                       |

| 2                 | Maximum Power [W]          | 104                                       | 78                                        | 74                                        |

| 3                 | Turn-on Delay Time [ns]    | 17                                        | 16.5                                      | 17.2                                      |

| 4                 | Turn-off Delay Time [ns]   | 34                                        | 24                                        | 27                                        |

| 5                 | Diode Forward Voltage [V]  | 0.76-1                                    | 0.77-1                                    | 0.79-1                                    |

| 6                 | Reverse Recovery Time [ns] | 150-230                                   | 125-200                                   | 154-185                                   |

| 7                 | Maximum Current [A]        | 2.6-4                                     | 2.8-4.2                                   | 1.7-2                                     |

| 8                 | Price [\$]                 | 0.80                                      | 0.81                                      | 0.70                                      |

## **5.2 Digital Microcontroller**

The second of these carefully searched components was the digital microcontroller. Originally the choice for digital microcontrollers was between a FPGA, a standard microcontroller(MCU), and a digital signal processing(DSP) chip. First of all, the group had no experience using FPGA's, so the FPGA was the first option ruled out. Secondly, most standard MCU chips are not capable of performing real-time DSP applications, such as power factor correction, so the DSP chip was chosen as the proper chip for the active power filter application. Based on the digital control requirements previously discussed, a set of specifications was defined to help in the selection of a microcontroller for the active power filter design and can be seen in Table 4.

Table 4: Specifications for Digital Control

| Digital Control Specifications            | Values   |

|-------------------------------------------|----------|

| CPU Speed (MIPS)                          | > 40     |

| Operating Voltage Range (V)               | 3 to 3.6 |

| # of ADC Modules                          | >= 1     |

| ADC Resolution (bits)                     | >= 10    |

| Successive Approximation Registers(SAR's) | >= 2     |

| PWM Outputs                               | >= 4     |

| PWM Resolution (bits)                     | 16       |

| # of DAC Modules                          | >= 1     |

| DAC Resolution (bits)                     | >= 10    |

| # of Timer Modules                        | >= 2     |

| *RAM (bytes)                              | >= 8192  |

| *Program Memory (kilobytes)               | >= 16    |

| Pin Count                                 | <= 28    |

<sup>\*</sup>Parameters were not included in the original chip selection, were added for selection of second chip.

The DSP chips come in two different data formats, which include floating point and fixed-point. A floating point chip has an architecture which allows for floating point arithmetic and has 32-bit containers of type float. The float data type can represent any decimal or integer value between  $\pm 3.4 \times 10^{38}$  and  $\pm 1.2 \times 10^{-38}$ . Since floats have such a large dynamic range, mathematical operations using the float data type allow for almost infinite precision. The process of coding through the use of floating point arithmetic is also quite easy and straightforward. However, the major drawback to floating point chips is that in order to do these floating point mathematical operations quickly, there needs to be dedicated floating point hardware available on the chip. For most floating point architectures this hardware is quite expensive. Therefore a more reasonable low-cost alternative would be a fixed-point chip. The major downside to fixed-point architectures is that they only support fixed-point arithmetic and are normally limited to 16-bit containers. Since the containers to store data are only 16 bits in size, instead of 32 bits or larger, the chips have limited precision, which causes a major tradeoff between overflow and precision. This tradeoff becomes prominent when carrying out mathematical operations where the result can be larger than either of the two variables used in calculating the result.

The two mathematical operations which need to be taken into consideration are multiplication and addition. For integer multiplication, the total number of bits found in the product is represented by Equation 5.2.1.[16]

$$N_z = N_x + N_y - 1 (5.2.1)$$

In order to make sure overflow does not occur in the multiplication step, the calculation of the number of bits from Equation 5.2.1 cannot exceed the container bit limit of 16. For instance if x has 16 bits and y has 8 bits, the corresponding product would need a total of 23 bits to represent the value. However, since the maximum number of representable bits is 16, seven bits need to be "thrown away" to avoid overflow. The bits which need to be "thrown away" will come from the equivalent number of shifts being applied to the two input variables. In order to avoid overflow during the addition step, the number of bits which need to be shifted is determined by Equation 5.2.2.

$$P_m = \lceil \log_2(M) \rceil \tag{5.2.2}$$

In Equation 5.2.2, the M represents the number of additions which will be performed. If there are M additions, then the ceiling of the log base two of M would help to determine the total number of bits which need to be shifted between the two variables before they are added together. Therefore by shifting each of these values by the result calculated via Equation 5.2.2, the total summation will not overflow and can be stored within the 16-bit container. In order to avoid overflow, a carefully developed shifting scheme needs to be created.

Since fixed-point filters can only use integer math operations, floating point operations with decimals cannot be calculated. Therefore in order to represent decimals in fixed-point notation, the idea of fractional bits is introduced. For a binary number N bits long, an invisible decimal point is placed somewhere within the binary number to denote a certain level of precision. The interesting

part about precision in terms of a fixed point system is that the number of fractional bits precision can be larger than the number of bits in the variable and can also be a negative number. Since the decimal is an imaginary idea, the user needs to keep track of the fractional bits to make sure the shifting is carried out properly. The methods explained for shifting above are conservative and will guarantee that there is no overflow in the results, allowing for accurate results to be seen. The number of fractional bits is denoted using the Q-M format, where M is the number of fractional bits within the binary number. This idea is important for integer multiplication because the number of fractional bits in the product is defined by Equation 5.2.3.[16]

$$M_z = M_x + M_y \tag{5.2.3}$$

The number of fractional bits in the product is the addition of the fractional bits of the two input variables, so the M in the Q-M format helps to easily understand how many fractional bits will be seen in the product. This idea is also important for integer addition because the number of fractional bits for the sum should be the same as the two inputs. Therefore if the two inputs into an addition step do not have the same Q-M format, the two numbers will not be added properly causing errors to be introduced into the system.

The other factor considered when optimizing fixed-point code is the idea of precision. The amount of precision found in the system is determined by the number of fractional bits preserved throughout the filtering process. When values are shifted to the right to avoid overflow a certain amount of precision is lost because the fractional bits are shifted out. Losing precision in order to prevent overflow losses creates a cost-benefit relationship between overflow and precision. In order to maximize the result, the optimal balance between overflow prevention and precision loss needs to be obtained.

There are two main companies who sell real-time DSP chips: Texas Instruments(TI) and Microchip. Most if not all of Texas Instrument's DSP chips use floating point architectures, while all of Microchip's DSP chips use fixed-point architectures. Based upon experience, the logical choice would be to use a TI DSP chip in the design for three reasons: the TI Code Composer Studio integrated development environment(IDE) is familiar, the chip would be easier to code, and the chip would allow for higher data accuracy. However, due to the fact that the project was not sponsored and the cost of the project falls back on the ECE Department at WPI, the cost difference between the TI chips and Microchip chips is just too great. Therefore the decision was made to select a Microchip DSP chip, which would meet the system requirements laid out in Table 4.

The original chip chosen for the project was the dsPIC33FJ16GS502 from the DSP33F family of Microchip devices. The Microchip devices are programmed using the MPLAB IDE, but for this project the newer version of MPLAB, MPLABX, was chosen due to its updated user interface and the numerous tutorial videos found online. Once the chip was received, the MPLABX IDE was officially setup, and the code was fixed for compilation bugs an issue arose with building the project. Due to the size of the data structures which were necessary to produce accurate results, there needed to be an adequate amount of data memory(RAM) to store all of these values.

However, the dsPIC33FJ16GS502 chip chosen lacked the appropriate amount of memory to store these data structures. Therefore a search for a new chip, which could support the creation of these large data structures needed to be carried out. In order to make sure the new chip chosen had plenty of RAM; the new chip would need to have at least 4 times the amount of RAM. Since the dsPIC33FJ16GS502 chip had only 2.048kB of RAM, a chip with upwards of 16kB would be ideal. Even though the dsPIC33FJ16GS502 chip did not have enough RAM to support the implementation, the device had all of the proper features and peripherals which were crucial to the success of the project, so a chip with similar features was desirable.

In order to make sure the time which had been spent creating the hardware setup code used for the dsPIC33FJ16GS502 chip was not a waste; a chip of the same family would have to be found. The hope was that a chip from the dsPIC33F family would have similar registers, so when converting the hardware setup code to this new chip most of the conversions would be one-to-one and not many changes would have to be made. The other major limitation was the number of pins the dsP33F chip could have because the prototyping board which was bought to assist in programming the DSP chip could only program chips up to 28 pins in size. Therefore one of the limitations which had to be applied to the search was finding a chip with no more than 28 pins.

By using Microchip's database search engine, four chips were found which fit the specification requirements as stated above. All four of these chips were very similar, but the main difference was that each chip either had a high-resolution DAC or a high-resolution PWM module for motor control applications, but not both. The chips which had the high-resolution DAC's only had PWM modules which were used for input capture. The chips which had the high-resolution PWM module for motor control applications only had 4-bit, low-resolution DAC's. This proposed a dilemma in chip selection because the two duty cycle algorithm implementations under consideration each needed either a high-resolution DAC or a high-resolution PWM for motor applications. If the triangle waveform comparison algorithm was used, the dsPIC33FJ128GP802 chip with the high-resolution digital-to-analog convert would be chosen and if the more complex, mathematically driven duty cycle algorithm was used, the dsPIC33FJ128MC802 chip with the high-resolution PWM for motor applications would be chosen. Originally, the application of a more complex, mathematically driven duty cycle algorithm was the goal, but after much consideration it was determined the proof of concept triangle waveform comparison algorithm was the better approach for the project. However, since the proper chips could not be acquired until the later stages of the project, there was not an adequate amount of time to study the datasheet in order to allow for a quick transition. Therefore the implementation portion of the paper was written referencing the original dsPIC33FJ16G502 chip.

In addition to the digital microcontroller, a dsPIC prototyping development board was acquired, so the project code could be downloaded to the microcontroller. The development board selected from Microchip Technology was a 16-bit, 28-pin starter demo board with part number DM300027. The development board has easy access header pins, so signals output from the dsPIC33F chip can be easily sent to an analog circuit via jumper wires.

#### **5.3 MOSFET Gate Driver**

The final component which needed to be researched was the MOSFET Gate Driver. The output voltage from the dsPIC33F microcontroller was not high enough to drive the gates of the MOSFET's in the active power filter, so a component which could step up the voltage was necessary. One driver is used to provide the voltages necessary to drive both the high and low-side MOSFET's. For simplicity, the MOSFET Gate Drivers with 8 pins were preferred, so the component would be easier to understand and less safety components would be necessary. The other two contributing factors which led to the decision of the MOSFET Gate Driver were cost and thoroughness of the datasheet. The MOSFET Gate Driver with the best price, 8 pins, and had the most thorough datasheet was the IR2011.

## 6. Digital Control System Implementation

This section of the report will provide a more detailed overview of how each element in the digital control system was implemented. If a deeper understanding of the variables used or a better understanding of the code flow is desired please refer to the MQP program files found in Appendices A, B, C, and D. The Constants\_Globals\_Prototypes.h file contains all of the definitions for all of the constants, globals, and prototypes used in the program, the Init\_Functions(GS502).h file contains all of the hardware initialization code used to setup the dsPIC33F chip, the MQP\_Code.c file contains all of the code which comprises the main program, and the Enum\_States.h file contains the state variable used to control when the "filling" and "processing" buffers can be switched in the program.

## 6.1 Main Clock & Auxiliary Clock Configuration

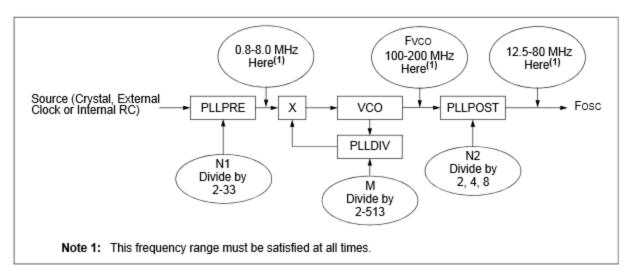

The main clock on the dsPIC33F chip was configured to be 40 Megahertz. This frequency is obtained by using the Internal Fast RC (FRC) oscillator, which provides a 7.37 Megahertz clock frequency, in conjunction with one of the hardware PLL modules found on the dsPIC33F chip. The operating clock frequency of the device, Fcy, is calculated using Equation 6.1.1.

$$F_{CY} = \frac{F_{OSC}}{2} = \frac{1}{2} \cdot \frac{F_{IN} \cdot M}{N1 \cdot N2} \tag{6.1.1}$$

In Equation 6.1.1, Fosc is the output frequency of the PLL, Fin is the input frequency to the PLL, M is the PLL feedback divisor, N1 is the prescale factor, and N2 is the postscale factor. The relationship of how these factors are applied to the FRC oscillator input can be seen in Figure 6.1.1.

Figure 6.1.1: PLL Clock Source Configuration[17]

In order to achieve the ideal operating clock frequency of 40 Megahertz, both the prescale and postscale factors are set to the minimum value of 2 and the value of M is set to 43.

For optimal ADC and PWM performance, the Auxiliary clock needed to be configured to be 120 Megahertz. The FRC oscillator provides the clock source for the ADC and PWM modules. The 7.37 Megahertz is increased to 120 Megahertz by utilizing the Auxiliary PLL, which multiplies the input by 16, and setting the Auxiliary clock divider to 1. Since the Auxiliary PLL was used to obtain the Auxiliary clock frequency, the maximum PWM resolution of 1.04 nanoseconds is achieved.

### 6.2 ADC Configuration

The first crucial component of the digital control system scheme is the ADC. The 10-bit resolution ADC on the dsPIC33F chip operates at a maximum speed of 4 Msps. The ADC has twelve input channels, which are grouped into six different conversion pairs. There are also two different voltage reference monitoring inputs as well. The ADC can sample up to two input channels at the same time because the dsPIC33F chip has two Successive Approximation Registers. Also of note, it has selectable buffer fill modes. Since the ADC has a 10-bit resolution, the samples of the analog signal are converted into 10-bit binary numbers, which can have up to  $2^{\wedge 10}$  or 1024 different voltage step values. Therefore, if a 3 volt reference voltage is used then the 10-bit mode will not be able to detect voltage changes of  $3/(2^{\wedge 10}-1)$  or 29 millivolts or smaller.

The data format for the ADC is initialized to be fractional because in order to use the data samples in this FFT application, the data needs to be in a range of less than -1 to 1. In this case, the data needs to be in the range of -0.5 to 0.5, so the input samples need to be halved in order to get the data to be in the correct range. In this case, the input samples can be shifted by one sample to the right in order to complete the divide by two operation. A cool feature of this dsPIC33F chip is that

the ADC is capable of completing pair conversions, which means the ADC is capable of converting two different ADC channels at one time. This feature is made possible by the chip having two successive approximation registers(SAR), where each SAR can convert a single channel of the ADC. The ADC Conversion Pair 0 allows for the sampling of both CH0 and CH1 at the same time, so in this case the ADC distorted load current is seen on CH0 and if a PLL implementation was pursued then the PLL output could be seen on CH1.

In order to allow an interrupt to occur after both the CH0 and CH1 conversions take place, the early interrupt is disabled. The ADC Conversion Pair 0 interrupt is given a priority of 6 out of 7, where 7 is the highest priority user interrupt. The conversion of the ADC is triggered through the use of a Timer1 period match as explained in the following Timer1 Configuration section.

### 6.3 Timer1 Configuration - ADC interrupts

The period of the Timer1 module is derived from the internal operating clock frequency of the dsPIC33F device, so the Timer1 period is defined as a specific number of internal clock cycles. The value stored in the period match register for the Timer1 module was 3125, which was determined by Equation 6.3.1.

$$T_{Timer1} = N_{Clock} \cdot T_{CY} \tag{6.3.1}$$

In Equation 6.3.1,  $T_{timer1}$  is the desired Timer1 clock period,  $N_{clock}$  is the number of internal clock cycles, and  $T_{CY}$  is the period of the internal clock.

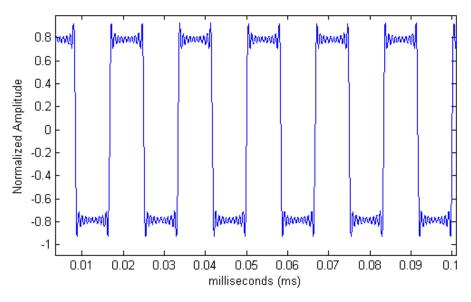

The Timer1 module is configured to be operating in Timer mode, so the Timer1 register will add one to its count for each period of internal clock frequency until the value in the Timer1 register matches the value of the Timer1 period register. When the values of these two registers match, the count of the Timer1 register is reset to 0 and the counting process restarts. The ADC interrupts are generated based upon a Timer1 period match, so when the Timer1 time base register reaches the value of 3125 the ADC interrupt triggers. This allows the ADC interrupts to occur periodically at a frequency of 12.8 kilohertz.

The 12.8 kilohertz sampling frequency not only allows for an accurate digital representation of the input current, but it is also higher than the 2280 hertz frequency necessary to prevent aliasing of the 19<sup>th</sup> harmonic. The 19<sup>th</sup> harmonic occurs at 1140 hertz, so in order to prevent aliasing the sampling frequency needs to be at least twice that frequency according to the Nyquist Theorem, so the minimum sampling frequency would be 2280 hertz. The input current is downsampled by 50, in order to decrease the sampling frequency from 12.8 kilohertz to 256 hertz. The importance of the downsampling exists in the relationship between the sampling frequency and the number of points used in the FFT operation. Since a 256-point FFT is utilized and the input current signal was downsampled to obtain a sampling frequency of 256 hertz, the frequency bins in the FFT operation are one hertz apart. The one hertz resolution seen in the frequency bins of the FFT output should be sufficient to produce an accurate representation of the fundamental frequency, magnitude, and

phase when reconstructing the ideal input current signal. If higher resolution frequency bins were desired, this relationship could be adjusted to acquire frequency bins less than one hertz apart. Another option would be to use a "fine search" algorithm, such as the Maximum Likelihood Estimation algorithm, which acquires a more accurate estimate of the fundamental frequency, magnitude, and phase of the input current through the extrapolation of the FFT output points.

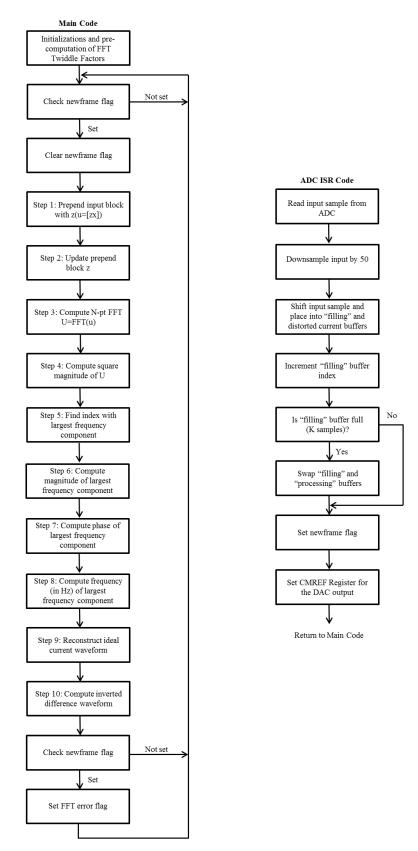

### 6.4 Sliding Window FFT

The Sliding Window FFT implementation used in this project makes use of frame-by-frame processing, where the ADC interrupt is used primarily to collect input samples and the main function is where all of the samples are processed using the complex sliding FFT algorithm. While the ADC is collecting samples to form frames, the main function is processing the previously filled frame of samples. If the main function completes processing before the new frame in the ADC interrupt is filled, then the system will be running in real-time.

The Sliding Window FFT algorithm makes use of two unique ideas which are crucial to the program's success, which are the data type fractcomplex and buffer memory alignment. The data being stored in the buffers are complex, since it contains both real and imaginary parts. The fractcomplex data type stores both the real and imaginary components in sequential memory locations. In order for these buffers to process the samples properly in the main function, all of the buffers involved with the FFT operation need to be aligned in memory. Therefore when the data in the buffers is accessed at a particular index, the correct data is found at the corresponding memory address. The buffers that are aligned are TwiddleF, ProcBuff, and FillBuff.

The basic structure of how the ISR and main code communicate in order to properly perform the frame-by-frame processing for the Sliding FFT algorithm is depicted in the flow diagram seen in Figure 6.4.1.

Figure 6.4.1: Flow Diagram of Project Code relating the ADC ISR to the Main Function

The basic structure of the main code is an if statement, which checks the new frame buffer flag to see if there is a full buffer of samples that needs to be processed. Therefore the main code only runs if there is a buffer which needs to be serviced. The if statement contains all of the code found within the infinite while loop because all of this code is used in processing the ADC samples. Inside the if statement, the new frame buffer flag is reset back to zero indicating the samples are being serviced. Next, the Sliding FFT function is called to perform the sliding window FFT operation with the frame of data coming from the ADC. Following the function call is an if condition, which checks to see if the new frame buffer flag was set while the samples were being processed. This condition is important because if the new frame buffer flag is set, then the ISR improperly switched array pointers in the middle of a calculation which would cause data corruption to occur. Therefore an error flag bit could be set, which would indicate the new frame buffer flag had been updated in the ISR.

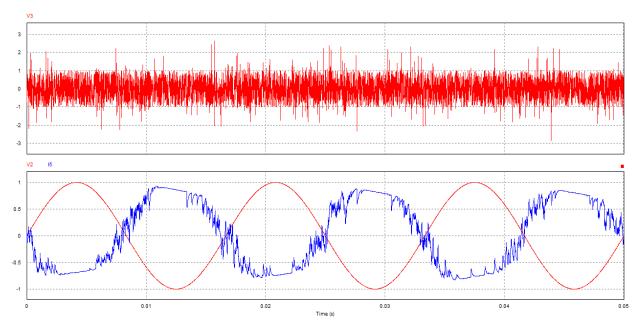

In any real-time system such as this one, the ISR can easily interrupt any calculations occurring in the main function, so care has to be taken in order to make sure data corruption does not occur. Therefore a form of state logic needs to be determined in order to make sure the ISR does not switch array pointers when the program is running the main code critical section. In the implementation, an enumeration state approach was taken to help prevent data corruption. An enumeration variable, status, was defined to have one of four values: EMPTY, RDY, PROC, or FIN. These values are state conditions which keep track of what the current status of the program is at any point in time. The EMPTY state occurs when the buffer being passed to the ISR is empty and has no samples in it. The RDY states occurs in the ISR when the buffer being filled has more than zero samples in it, but less than K samples and the main function is not processing samples. The PROC state is set as the first line in the Sliding FFT function, which tells the ISR that samples are currently being processed and the ISR needs to wait until the processing is done to switch buffer pointers as is explained later in the ISR section. The FIN state notifies the ISR when the main code has completed processing the samples in the buffer. These states help track the progress of the code in order to prevent data corruption in global variables which are accessed in critical sections of code, such as in the main function of this code.