## Worcester Polytechnic Institute Digital WPI

Major Qualifying Projects (All Years)

Major Qualifying Projects

April 2008

# Maximum Peak Power Tracker

Daniel F.C. Butay Worcester Polytechnic Institute

Michael Thomas Miller Worcester Polytechnic Institute

Follow this and additional works at: https://digitalcommons.wpi.edu/mqp-all

#### **Repository Citation**

Butay, D. F., & Miller, M. T. (2008). Maximum Peak Power Tracker. Retrieved from https://digitalcommons.wpi.edu/mqp-all/1987

This Unrestricted is brought to you for free and open access by the Major Qualifying Projects at Digital WPI. It has been accepted for inclusion in Major Qualifying Projects (All Years) by an authorized administrator of Digital WPI. For more information, please contact digitalwpi@wpi.edu.

Maximum Peak Power Tracker:

A Solar Application

A Major Qualifying Project Report

Submitted to the Faculty

Of the

Worcester Polytechnic Institute

In partial fulfillment of the requirements for the

Degree of Bachelor of Science

Ву

Daniel F. Butay

Michael T. Miller

Date: April 24<sup>th</sup>, 2008

Professor Alexander Emanuel, Advisor

## Acknowledgements

We would like to thank Professor Emanuel for his guidance and patience throughout the design process of the MQP. His encouragement and insightful contributions made the project possible. We would also like to thank Professor Bitar for his help with the solar simulator and input about using solar cells.

#### Abstract

The design and implementation of a Maximum Peak Power Tracking system for a photovoltaic array using boost DC-DC converter topology is proposed. Using a closed-loop microprocessor control system, voltage and current are continuously monitored to determine the instantaneous power. Based on the power level calculated, an output pulse width modulation signal is used to continuously adjust the duty cycle of the converter to extract maximum power. Using a Thevenin power source as well as a solar panel simulator, system design testing confirms simulation of expected results and theoretical operation is obtained.

## **Table of Contents**

|     | ntroduction<br>Background<br>2.1 How Solar Cells Work          | 8    |

|-----|----------------------------------------------------------------|------|

|     | 2.2 Solar Cell V-I Characteristic                              | . 12 |

|     | 2.2.1 Effect of Irradiance                                     | . 13 |

|     | 2.2.2 Effect of Insolation Levels                              | . 14 |

|     | 2.2.3 Effect of Temperature                                    | . 16 |

|     | 2.2.3 Efficiency                                               | . 17 |

|     | 2.3 The DC-DC Boost Converter                                  | . 19 |

|     | 2.3.1 Continuous Conduction Mode                               | 20   |

|     | 2.3.2 Boundary between Continuous and Discontinuous Conduction | . 22 |

|     | 2.3.3 Discontinuous Conduction Mode                            | . 23 |

| 3.0 | Methodology<br>3.1 System Block Diagram                        |      |

|     | 3.2 Solar Panel Simulator                                      | . 25 |

|     | 3.3 Input Filter                                               | . 28 |

|     | 3.4 DC-DC Boost Converter Analysis                             | . 29 |

|     | 3.5 Operating Frequency                                        | . 31 |

|     | 3.6 Voltage Sensing                                            | . 31 |

|     | 3.7 Current Sensing                                            | . 32 |

|     | 3.7.1 Series Sense Resistor                                    | . 32 |

|     | 3.7.2 R <sub>DS</sub> Sensing                                  | 33   |

|     | 3.7.3 Filter Sensing the Inductor                              | . 34 |

|     | 3.7.4 Magnetic Sensing-Hall Effect Sensors                     | . 36 |

|     | 3.7.5 Current Sensing Conclusion                               | . 37 |

|     | 3.8 Determining Inductance Value                               | . 39 |

|     | 3.9 Confirming Peak Power Obtained – Thevenin Equivalence      | . 41 |

|     | 3.9.1 Average Current and Ripple                               | . 43 |

|     | 3.9.3 Equivalent Resistance and Power                          | . 47 |

| 4.0 | mplementation<br>4.1 Parts Selection                           |      |

|     | 4.1.1 MOSFET Gate Driver Selection                             | 48   |

| 4.1.2 Power Mosfet Selection                                                                                       | 50                   |

|--------------------------------------------------------------------------------------------------------------------|----------------------|

| 4.1.3 Inductor Selection                                                                                           |                      |

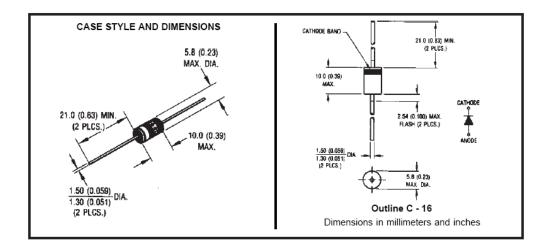

| 4.1.4 Diode Selection                                                                                              |                      |

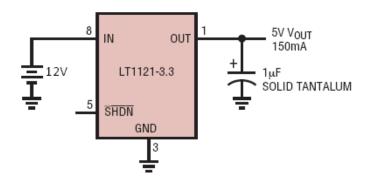

| 4.1.5 Voltage Regulator                                                                                            |                      |

| 4.1.6 Voltage Sensor                                                                                               | 59                   |

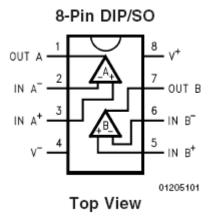

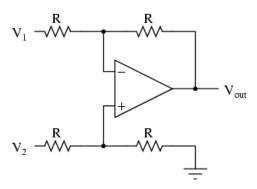

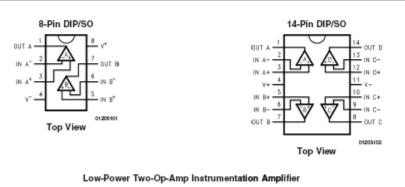

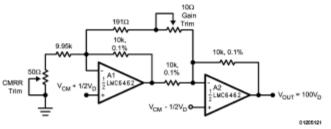

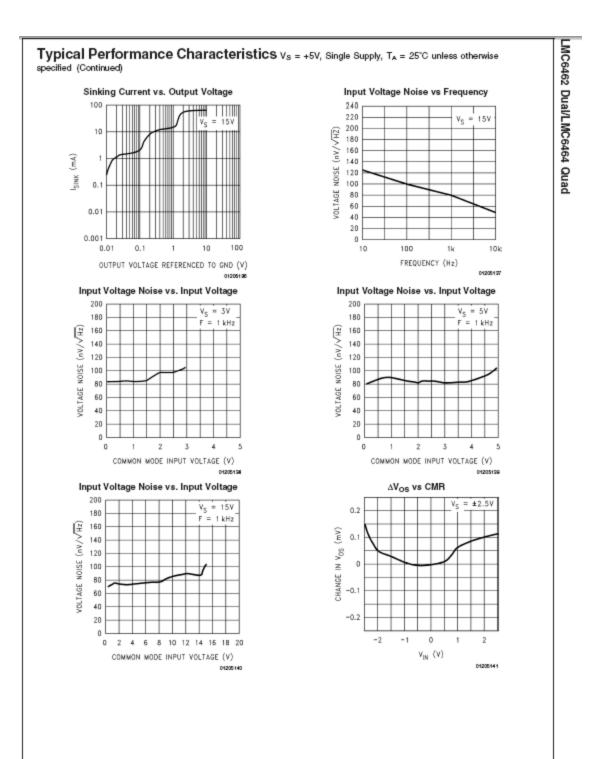

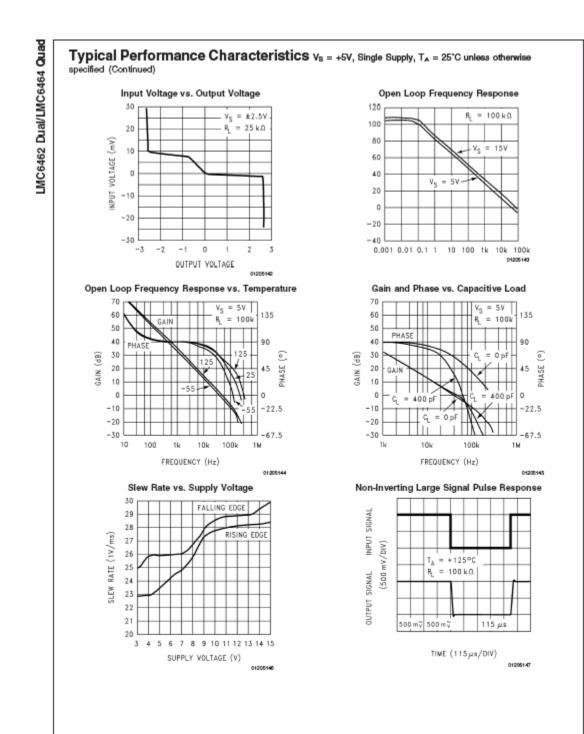

| 4.1.7 Differential Operational Amplifier                                                                           | 60                   |

| 4.1.8 Current Sensor                                                                                               |                      |

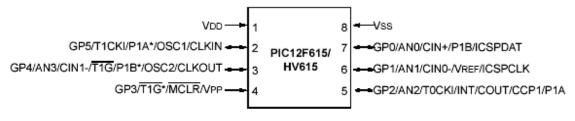

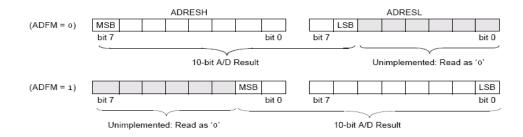

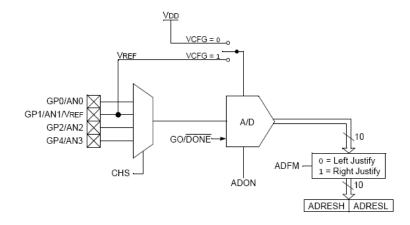

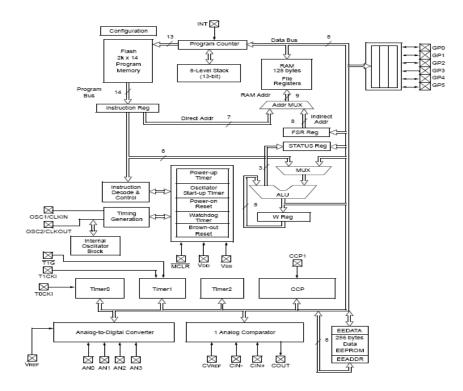

| 4.1.9 Microprocessor Selection                                                                                     |                      |

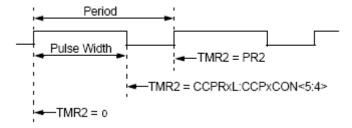

| Pulse Width Modulation (PWM)                                                                                       |                      |

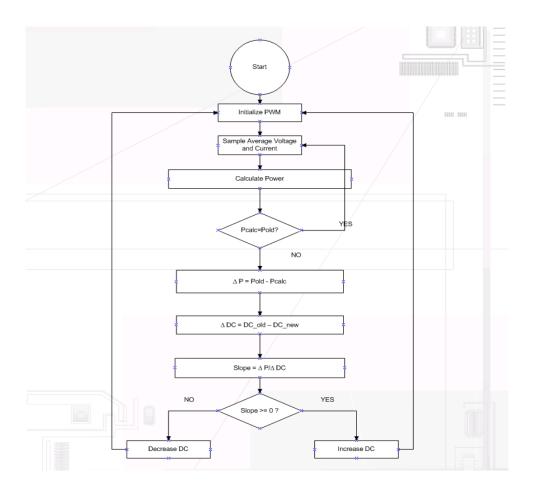

| 4.2 Controls                                                                                                       |                      |

| Algorithm                                                                                                          |                      |

| 5.0 Results<br>Theoretical Operation                                                                               |                      |

| 6.0 Future Recommendations<br>7.0 Conclusion<br>References<br>Full Schematic<br>Datasheets<br>TC4427 MOSFET Driver | 80<br>82<br>83<br>84 |

| FDP6030 MOSFET                                                                                                     |                      |

| Schottky Diode                                                                                                     |                      |

| LT1121 Voltage Regulator                                                                                           |                      |

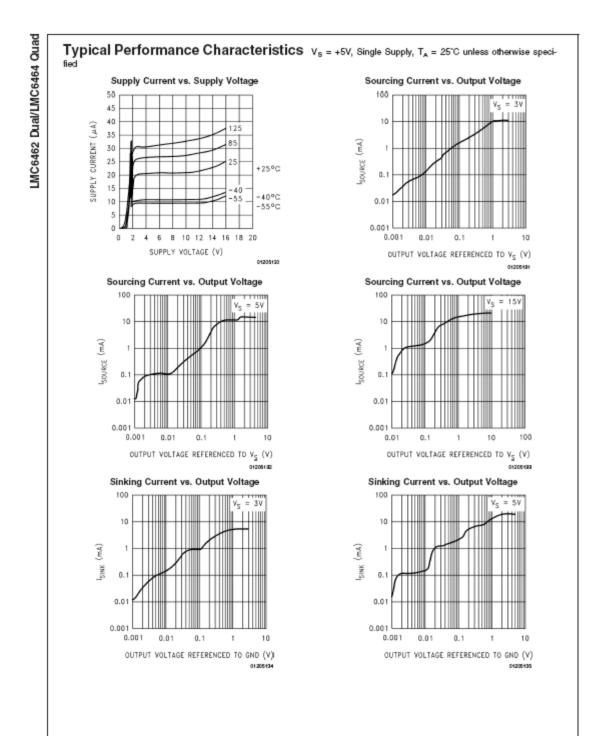

| LMC6462 Differential Operational Amplifier                                                                         |                      |

| PIC12F683 Microprocessor                                                                                           |                      |

| Peak Power Tracking Code                                                                                           | 116                  |

### **1.0 Introduction**

The development of renewable energy has been an increasingly critical topic in the 21<sup>st</sup> century with the growing problem of global warming and other environmental issues. With greater research, alternative renewable sources such as wind, water, geothermal and solar energy have become increasingly important for electric power generation. Although photovoltaic cells are certainly nothing new, their use has become more common, practical, and useful for people worldwide.

The most important aspect of a solar cell is that it generates solar energy directly to electrical energy through the solar photovoltaic module, made up of silicon cells. Although each cell outputs a relatively low voltage (approx. 0.7V under open circuit condition), if many are connected in series, a solar photovoltaic module is formed. In a typical module, there can be up to 36 solar cells, producing an open circuit voltage of about 20V<sup>1</sup>. Although the price for such cells is decreasing, making use of a solar cell module still requires substantial financial investment. Thus, to make a PV module useful, it is necessary to extract as much energy as possible from such a system.

A PV module is used efficiently only when it operates at its optimum operating point. Unfortunately, the performance of any given solar cell depends on several variables. At any moment the operating point of a PV module depends on varying insolation levels, sun direction, irradiance, temperature, as well as the load of the system. The amount of power that can be extracted from a PV array also depends on the operating voltage of that array. As we will observe, a PV's maximum power point (MPP) will be specified by its voltage-current (V-I) and voltage-power (V-P) characteristic curves. Solar cells have relatively low efficiency ratings; thus,

<sup>&</sup>lt;sup>1</sup> Bogus, Klaus and Markvart, Tomas. Solar Electricity. Chichester, New York.Wiley Press, 1994.

operating at the MPP is desired because it is at this point that the array will operate at the highest efficiency. With constantly changing atmospheric conditions and load variables, it is very difficult to utilize all of the solar energy available without a controlled system. For the best performance, it becomes necessary to force the system to operate at its optimum power point. The solution for such a problem is a Maximum Peak Power Tracking system (MPPT).

A MPPT is normally operated with the use of a dc-dc converter (step up or step down). The DC/DC converter is responsible for transferring maximum power from the solar PV module to the load. The simplest way of implementing an MPPT is to operate a PV array under constant voltage and power reference to modify the duty cycle of the dc-dc converter. This will keep operation constant at or around the maximum peak power point.

There have been many different solutions presented for methods of peak power tracking. Our goal is to develop such a system with the purpose of obtaining as much energy from a solar cell as possible. Our secondary goal will be to create such a system that operates with optimum efficiency as well. Implementing such a design will be useful in the future because solar cell use is limited greatly by efficiency limitations and cost factors. If manufacturers took advantage of MPPT systems, it is without a doubt that solar cells will become more commonly used.

We will focus on a specific solution to the problem of peak power tracking and present it in full in this report. It will be important to first learn as much as possible about the operation of solar cells. From there, we will discuss the methodology of the design, the selection of what components to implement, system design and testing, and finally, the results of our project. There are a variety of different options and applications available for our goal. The challenge lies in designing a system with maximum efficiency that will quickly and constantly monitor and change the operation of the system to obtain the optimum performance from a solar cell.

## 2.0 Background

Most solar cells are made of semiconducting multicrystalline silicon cells, which currently have efficiencies of 10 to 15%<sup>2</sup>. Even at these ratings, according to the Encyclopedia of Energy, it would take solar modules covering an area equivalent to just 0.25% of the global area under crops and permanent pasture to meet all the world's primary energy requirements, when most or all of such area would otherwise be unused land<sup>3</sup>. It is numbers like these that demonstrate the importance and potential that solar cells have in becoming one of the most important sources of energy used around the world. This also demonstrates the problem with the use and production of solar cells, limited by low efficiency and high costs.

Despite the limitations, market surveys show that solar cell production is growing rapidly. With the turn of the century, some companies such as Sharp, BP Solar, and Kyocera have nearly doubled their production values<sup>4</sup>.

<sup>&</sup>lt;sup>2</sup> <u>LGBG Technology</u> "Towards 20% Efficient Silicon Solar Cells." 02 Oct 2005.

<sup>&</sup>lt;sup>3</sup> Aldous, Scott. "How Silicon in Solar Cells Works." <u>How Stuff Works</u>. 02 Oct 2005.

<sup>&</sup>lt;sup>4</sup> Neville, Richard C. <u>Solar Energy Conversion</u>. The Netherlands: Elsevier Science, 1995.

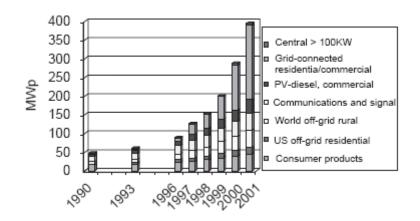

Figure 1: World Solar Cell production from 1988-2002 for the three leading production regions and the rest of the world

Figure 2: World PV market by application from 1990-2001

PV modules are also being applied for a greater variety of different purposes. Although they have not yet broken into the consumer market, as we can see from figure, the use of PV modules is clearly becoming more successful. Solar cell array efficiency has always been an important factor for product selection. However, for most potential users, the capital cost, and the cost of the resultant electricity are much more useful measures on which to base decisions about buying a solar cell. Thus, solar cells that are less efficient, but cheaper per unit area are able to compete in the market.

Solar cells are being valued as a source of energy, but they are also favored for their beneficial effect on the environment. To put this aspect into perspective, consider the carbon dioxide emissions during the operation of other methods of energy production. For example, assuming that U.S. energy generation causes 160 g carbon equivalent of CO<sub>2</sub> per kilowatt-hour of electricity, then a 1-kW PV array in an average U.S. location would produce approximately 1600kWh each year and 48,000kWh in 30 years. This array would avoid approximately (48,000 x 0.95) x 160g/kWh, or approximately 7 metric tons of carbon equivalent during its useful life<sup>5</sup>. A global implementation of solar cell arrays could very well be the solution to many environmental problems. The value of PV arrays is irrefutable, and clearly on the rise. The use of efficiency boosting systems like MPPTs provide a very promising future for solar cell use and the key to success is in understanding how solar cells work.

#### 2.1 How Solar Cells Work

Solar cells produce energy by performing two basic tasks: (1) absorption of light energy to create free charge carriers within a material and (2) the separation of the negative and positive charge carriers in order to produce electric current that flows in one direction across terminals that have a voltage difference. Solar cells perform these tasks with their semiconducting materials. The separation function is typically achieved through a p-n junction. Solar cell regions are made up of materials that have been "doped" with different impurities. This creates an excess of free electrons (n-type) on one side of the junction, and a lack of free

<sup>&</sup>lt;sup>5</sup> Sayigh, A.A.M., ed. Solar Energy Engineering. New York, USA: Academic Press, 1977.

electrons (p-type) on the other. This behavior creates an electrostatic field with moving electrons and a solar cell is essentially, a large-area diode<sup>6</sup>.

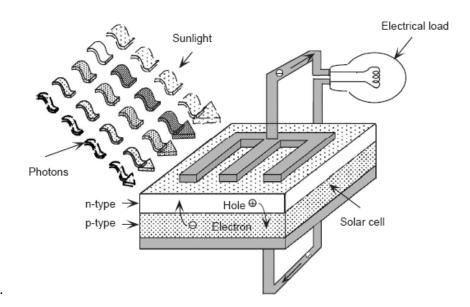

Figure 3 describes the overall process of solar energy conversion. First, photons enter the cell throughout the surface of the array. The photon is absorbed and its energy is transferred to an electron in the semiconductor. This frees the electron from its parent atom, and leaves behind a positively charged vacancy, otherwise known as a "hole." The movement of electrons and holes with the cell responds to the electric field or by diffusion to areas where electrons are less concentrated. Due to a strong electric field, electron-hole pairs generated near the junction are split apart. Minority carriers (electrons in p-type material and holes in ntype), are swept across the junction and become majority carriers. It is this crossing that occurs by the individual carriers that contributes to the cell's output current. Finally, metal contacts on the cell allow connection of the generated current to a load.

Figure 3: Solar cell operation

<sup>&</sup>lt;sup>6</sup> Richard Corkish, Solar Cells (Encyclopedia of Energy, 2004)

#### 2.2 Solar Cell V-I Characteristic

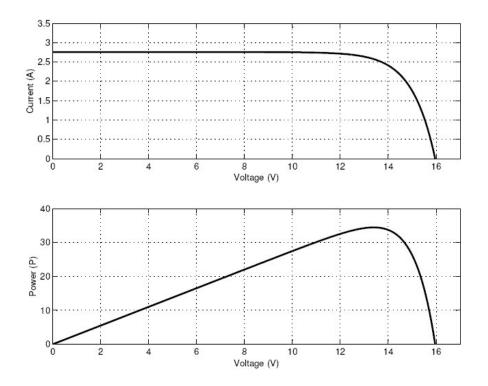

Each solar cell has its own voltage-current (V-I) characteristic. Figure 4 shows the V-I characteristic of a typical photovoltaic cell. The problem with extracting the most possible power from a solar panel is due to nonlinearity of the characteristic curve. The characteristic shows two curves, one shows the behavior of the current with respect to increasing voltage. The other curve is the power-voltage curve and is obtained by the equation (P=I\*V).

Figure 4: Solar panel V-I characteristic and Power curve

When the P-V curve of the module is observed, one can locate a single maxima of power where the solar panel operates at its optimum. In other words, there is a peak power that corresponds to a particular voltage and current. Obtaining this peak power requires that the solar panel operate at or very near the point where the P-V curve is at the maximum. However, the point where the panel will operate will change and deviate from the maxima constantly due to changing ambient conditions such as insolation or temperature levels, which we will discuss further. The result is a need for a system to constantly track the P-V curve to keep the operating point as close to the maxima as much as possible while energy is extracted from the PV array.

#### 2.2.1 Effect of Irradiance

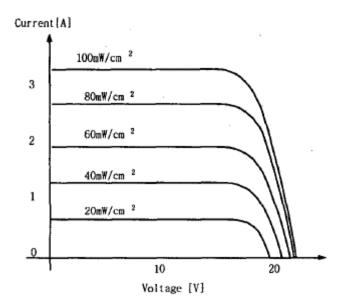

Solar panels are only as effective as the amount of energy they can produce. Because solar panels rely on conditions that are never constant, the amount of power extracted from a PV module can be very inconsistent. Irradiance is an important changing factor for a solar array performance. It is a characteristic that describes the density of radiation incident on a given surface. In terms of PV modules, irradiance describes the amount of solar energy that is absorbed by the array over its area. Irradiance is expressed typically in watts per square meter (W/m<sup>2)</sup>. Given ideal conditions, a solar panel should obtain an irradiance of 100mW/cm<sup>2</sup>, or 1000W/ m<sup>2)7</sup>. Unfortunately, this value that is obtained from a solar panel will vary greatly depending on geographic location, angle of the sun, or the amount of sun that is blocked from the panel because of any present clouds or haze. Although artificial lighting can be used to power a solar panel, PV modules derive most of their energy solely from the energy emitted from the sun. Therefore, changes of irradiance will greatly affect a PV module's performance.

<sup>&</sup>lt;sup>7</sup> Richard Corkish, Solar Cells (Encyclopedia of Energy, 2004)

Figure 5: Different irradiance levels on a solar panel

Figure 5 shows the effect of irradiance on the output of solar panels. Clearly, a smaller level of irradiance will result in a reduced output. The change in output current is due to the reduced flux of the photons that move within a cell, as we have discussed when observing the operation of a solar cell. We can see that the voltage and open circuit voltage is not substantially affected due to changing levels of irradiance. In fact, the changes made to voltage due to irradiance are often seen as trivial and independent of the changing flux of photons.

#### 2.2.2 Effect of Insolation Levels

Insolation is closely related to irradiance and refers to the flux of radiant energy from the sun. Taken as power per unit area, whose intensity and spectral content varies at the earth's surface due to time of day (position of the sun), season cloud cover, and moisture content of the air among other factors much like irradiance, insolation measures how much sunlight energy is delivered to a specific surface area over a single day<sup>8</sup>. Insolation is typically measured as kilowatt-hours per square meter per day (kWh/(m<sup>2</sup>\*day)) or in the case of photovoltaics, as

<sup>&</sup>lt;sup>8</sup> Aldous, Scott. "How Silicon in Solar Cells Works." <u>How Stuff Works</u>. 02 Oct 2005.

kilowatt hours per year per kilowatt peak rating (kWh/kWp\*y). In order to obtain the maximum amount of energy from a PV module, it should be set up perpendicular with the sun straight overhead, with no clouds or shade.

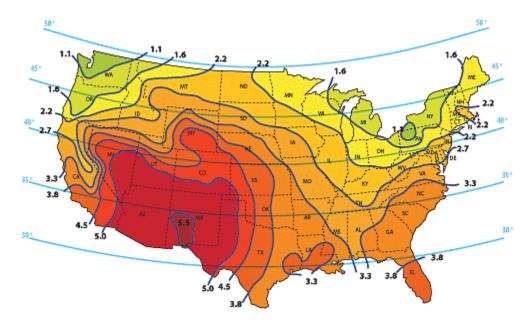

Figure 6: Insolation Levels across the United States

Figure 6\_shows the typical insolation levels across the continental United States during winter peak sun hours. Some solar panel manufacturers use this scale rather than the average annual peak sun hour rating because it ensures that their product will deliver reliable and continuous power in worst-case conditions. Observing this map, we see values varying from 1.1 to 5.5. This encompasses the average values that can be considered low and high for insolation levels, respectively.

| State | City      | Jan  | Feb  | Mar  | Apr  | May  | Jun  | Jul  | Aug  | Sep  | Oct  | Nov  | Dec  | Avg  |

|-------|-----------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| AZ    | Phoenix   | 3.25 | 4.41 | 5.17 | 6.76 | 7.42 | 7.7  | 6.99 | 6.11 | 6.02 | 4.44 | 3.52 | 2.75 | 5.38 |

| MA    | Boston    | 1.66 | 2.5  | 3.51 | 4.13 | 5.11 | 5.47 | 5.44 | 5.05 | 4.12 | 2.84 | 1.74 | 1.4  | 3.58 |

| АК    | Anchorage | 0.21 | 0.76 | 1.68 | 3.12 | 3.98 | 4.58 | 4.25 | 3.16 | 1.98 | 0.98 | 0.37 | 0.12 | 2.09 |

Average Insolation (10 year average) kWh/m<sup>2</sup>/day

Table 1: Insolation Levels (North America)

This table describes the average insolation levels across North America over 10 years. Unlike the worst-case values, these vary from well below 1 to up to 8. The table reflects the difference in levels between areas of very high sunlight, to very low sunlight. The yearly average for Massachusetts is at about the average across the entire nation with a relatively good average of 3.58. Alaska is expected to receive much lower insolation levels due to its geographical location and the shortened length of daytime light received especially during the winter months. Arizona receives better insolation levels because it is located farther south, making it closer to the equator and ideal operating equations. The same can be observed for countries throughout the world. Regions close to the equator will commonly achieve much higher insolation levels than those farther away from the equator.

#### 2.2.3 Effect of Temperature

A PV module's temperature has a great effect on its performance. Although the temperature is not as an important factor as the duration and intensity of sunlight it is very important to observe that at high temperatures, a PV module's power output is reduced. The temperature of a PV module also affects its efficiency. In general, a crystalline silicon PV module's efficiency will be reduced about 0.5 percent for every degree C increase in

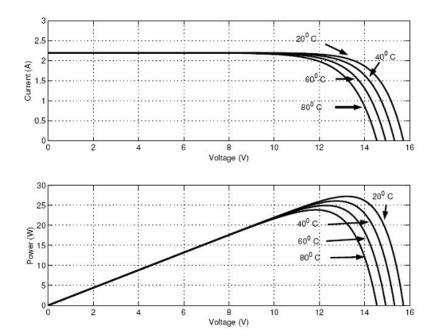

temperature. PV modules are usually rated at module temperatures of 25°C (77°F) and seem to run about 20°C over the air temperature<sup>9</sup>. This means that on a hot day of 100°F, the module will operate at 120°F, or 50°C, and so will have its power reduced by approximately 12.5%<sup>10</sup>. <u>Figure demonstrates the effect of varying temperature on the output of a solar panel.</u> One can easily see a voltage drop with increasing heat. The effect of varying temperature does not have a very large effect on the current developed.

Figure 7:Temperature effect on solar panel power and I-V curves

#### 2.2.3 Efficiency

Efficiency is most definitely one of the biggest issues when observing PV module performance. Different types of solar cells have varying efficiencies that vary depending on several factors. When we discussed the operation of a solar cell, we observed cell operation after photons have already entered into the semiconductor volume. In order to ensure efficient

<sup>&</sup>lt;sup>9</sup> <u>PV Technology</u> "Photovoltaic: Sustainable Power for the World." 08 Oct 2005.

<sup>&</sup>lt;sup>10</sup> <u>LGBG Technology</u> "Towards 20% Efficient Silicon Solar Cells." 02 Oct 2005.

absorption, the reflection from the surface of a solar cell must first be reduced. A semiconductor surface that has already been polished will still reflect a significant fraction of incident photons from the sun. Silicon, for example, will reflect 30% of such photons<sup>11</sup>. Texturing the surface of such cells helps mitigate reflection problems, but the solar panel's efficiency is defined by other factors as well.

A solar panel's efficiency is limited by the bandgap energy of the semiconductor from which a cell is made. Low bandgap materials will allow the threshold energy to be exceeded by a large fraction of the photons in sunlight, allowing a potentially high current. On the other hand, a solar cell will extract from each photon only an amount of energy slightly smaller than the bandgap energy, with the rest being lost as heat. This is because the excess energy from the photon results in the electron energy being higher than the bandgap. This leads to the electron settling in the conduction band and releasing energy as heat. Unfortunately, a semiconductor is transparent to photons with energy less than that of its bandgap and thus cannot capture their energy. In other words, the photons do not contain enough energy to create an electron-hole pair, so the photon simply passes right through the semiconductor. These two factors, thermalization, and transparency, are two of the largest loss mechanisms in conventional cells<sup>12</sup>.

As useful as solar panels can be, it is clear that there are still many problems that affect the overall performance of such an array. This is what contributes to the practicality of the design. If there was a way to ensure the maximum power is constantly taken from a solar panel array, a solar panel's efficiency would increase and the overall usefulness of solar power as a renewable energy source will be invaluable.

<sup>&</sup>lt;sup>11</sup> Nation Center for Photovoltaics. "Turning Sunlight into Electricity." 20 Oct. 2002.

<sup>&</sup>lt;sup>12</sup> Nation Center for Photovoltaics. "Turning Sunlight into Electricity." 20 Oct. 2002.

#### 2.3 The DC-DC Boost Converter

The boost converter will represent one of the most significant portions to the overall design of the Maximum Peak Power Tracker. Ideally, the maximum power will be taken from the solar panels. In order to do so, the panels must operate at their optimum power point. The output of the solar panel will be either shorted or open circuited through the opening or closing of a switch. In the design, the switch will actually be a MOSFET, which will be controlled by our digital controller. For better understanding of the converter, we will model the overall design, with the MOSFET as a simple, ideal switch. The switch will open and close to control the voltage across the inductor, essentially operating the panels at their optimum power level.

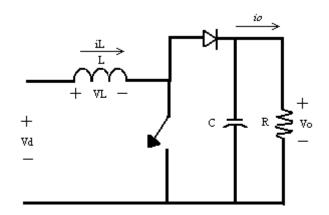

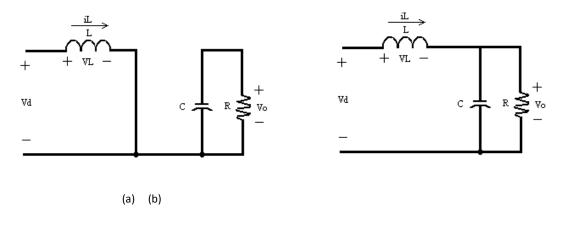

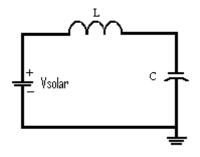

Figure 8: Step-up (Boost) dc-dc converter

Figure 8 shows the basic design of a step-up converter. As the name implies, the output voltage is always greater than the input voltage. The operation of the converter depends on the state of the switch. To better understand the operation of the converter, we will examine the operation of the circuit when the switch is opened or closed while in continuous conduction mode, discontinuous conduction mode, as well as the boundary between the two modes.

#### 2.3.1 Continuous Conduction Mode

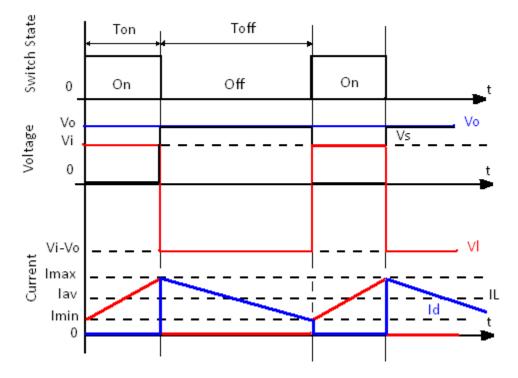

Figure 8: Boost DC-DC converter switch state, and voltage and current waveforms

Figure 8 shows the switch state, voltage, and current waveforms. When the dc-dc converter operates in continuous conduction mode, the inductor current flows continuously when  $[i_L(t) > 0]$ . When the switch is on as shown in Figure 9, the diode becomes reversed biased and the output stage is isolated. At this point, the input is supplying energy to the inductor. When the switch is off as shown in Figure 9, the output stage receives energy from the inductor as well as from the input. In the steady-state analysis we present, the output filter capacitor is assumed to be very large to ensure a constant output voltage  $v_o(t) = V_o$

Figure 9: Boost converter switch on (a), and switch off, (b)

In steady state, the time integral of the inductor voltage over one time period must be zero. Thus:

$$V_d t_{on} + (V_d - V_o) t_{off} = 0$$

Dividing both sides by the switching time,  $T_s$ , and rearranging terms, we obtain the equation that describes the relationship between the input and output voltages, switching time, and duty cycle.

$$\frac{Vo}{Vd} = \frac{Ts}{Toff} = \frac{1}{(1-D)}$$

This equation confirms that the output voltage is always higher than the input voltage. Assuming a lossless circuit,  $P_d = P_o$ , we also have

$$\frac{I_o}{I_d} = (1 - D)$$

#### 2.3.2 Boundary between Continuous and Discontinuous Conduction

At the boundary between continuous and discontinuous conduction,  $i_L$  goes to zero at the end of the off interval by definition. At this boundary, the average value of the inductor current is

$$I_{LB} = \frac{1}{2} i_{L,peak} = \frac{1}{2} \frac{V_d}{L} t_{on} = \frac{T_s V_o}{2L} D (1 - D)$$

In a step-up converter, it is important to recognize that the inductor current and the input current are the same ( $i_d = i_L$ ) and using the equation we can find that the average output current at the boundary of continuous conduction is

$$I_{oB} = \frac{T_s V_o}{2L} D(1-D)^2$$

The output current reaches its maximum when the duty ratio D = 1/3 = 0.333:

$$I_{oB,max} = \frac{2}{27} \frac{TsVo}{L}$$

When operating, the average output current at the edge of continuous conduction is important because for a given D, with constant  $V_o$ , if the average load current drops below  $I_{OB}$ , the current conduction would become discontinuous.

#### 2.3.3 Discontinuous Conduction Mode

Operation at discontinuous conduction mode cannot be fully understood without making several assumptions. In practice, the duty cycle, D, would vary with time in order to keep  $V_0$  constant. It is this common practice that allows the tracking of the peak power point. In discontinuous conduction mode, on the other hand, we must assume that as the output load power decreases,  $V_d$  and D remain constant.

Discontinuous conduction mode is unwanted because it occurs due to a decrease in power and results in a lower inductor current  $I_L$  since  $V_d$  is constant. We will not focus on this operation mode for the dc-dc converter because hopefully it will be completely avoided. Nevertheless, it is important to understand the relationship between the input voltage  $V_d$ , the output voltage  $V_o$ , and the duty cycle, D. Since in practice  $V_o$  is held constant and D varies in response to the variation in  $V_d$ , it is more useful to obtain the required duty ratio as a function of load current for various values of the ratio  $V_o/V_d$ .

$$D = \left[\frac{4}{27} \frac{Vo}{Vd} (\frac{Vo}{Vd} - 1) \frac{I_o}{I_{oB,max}}\right]^{1/2}$$

## 3.0 Methodology

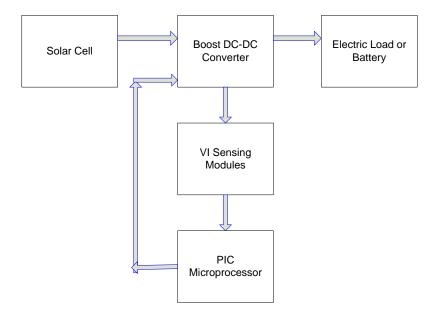

#### 3.1 System Block Diagram

Figure 10: System Block Diagram

Our peak power tracker is a microprocessor controlled DC-DC step up converter used by a solar power system to power some mechanical load. The system will step up the lower solar panel voltage for an application that would require more power. The microprocessor will attempt to maximize the power input from the solar panel by controlling the step up duty cycle to keep the solar panel operating at its maximum power point. This will be accomplished by continuously taking voltage and current samples from the panel and using the microprocessor to either increase or decrease the duty cycle of the converter depending on the wattage from the solar panel. The microprocessor will perform the wattage calculations and when the system reaches its steady state operation, the output from the solar panel will oscillate at its highest output value.

#### **3.2 Solar Panel Simulator**

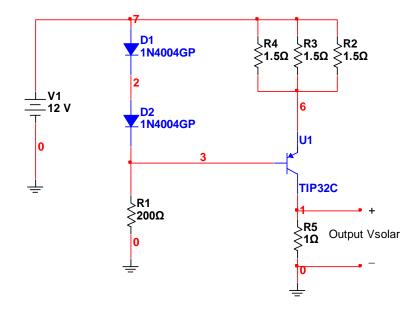

In order to provide power to the design, we will be harnessing a solar panel array. The design will take this power, and operate at the maximum power defined by the panel's P-V and I-V characteristics. Rather than using an actual solar panel array to test the design of our PPT, we will implement a simple solar panel simulator. A solar panel is basically a current source. In designing a solar panel simulator, our goal was to recreate a solar panel as a current source to power our circuit. The advantage of using a solar panel simulator is that we can directly control the output of the solar array, rather than having to deal with the variances that may occur due to changing operating conditions when testing outdoors. This design also rules out the limitation of power from artificial lighting sources directed on a solar panel that would have been used with indoor testing. The following figure is the schematic of the solar panel simulator that will be used in the testing and design of our PPT.

Figure 11:Solar Panel Simulator schematic

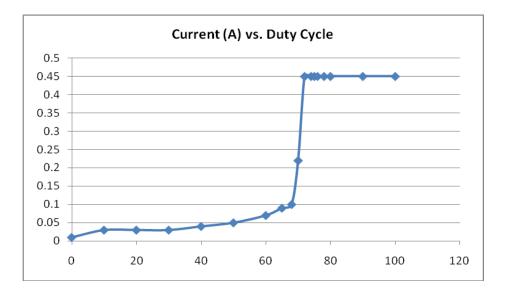

Changing the resistance of the load will simulate the input changes of power that may occur with the varying envinronmental characteristics that a typical solar panel may have to deal with when providing some output power. In other words, varying the ouptut load will effect the voltage being extracted from the panel simulator. Changing the configuration of the resistors R2, R3, and R4 will effect the maximum amount of current from the solar panel simulator. The resistors R2, R3, and R4 are all connected in parallel. The more resistors in parallel, the less resistance is seen by the emitter of the PNP bipolar junction transistor, U1. The smaller the equivalent resistance at the emitter, the higher the current at the collector. The different parallel configurations of the resistances will simulate closely the effect of irradiance—the amont of radiaton density on a given surface—on a typical solar panel.

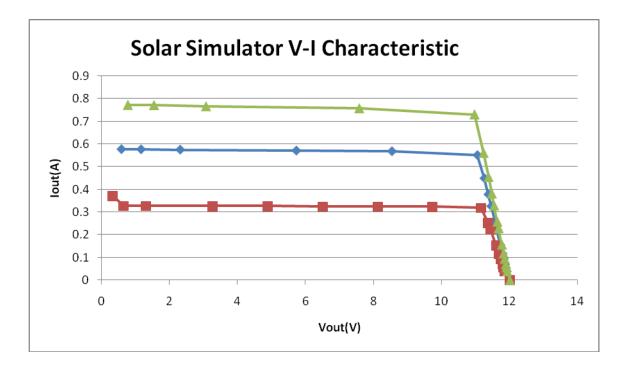

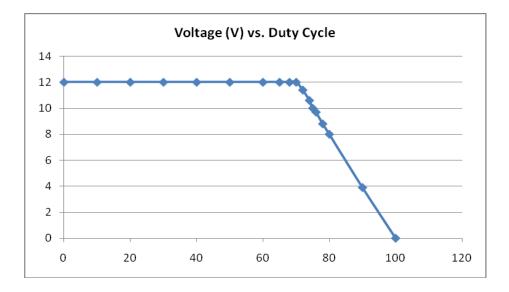

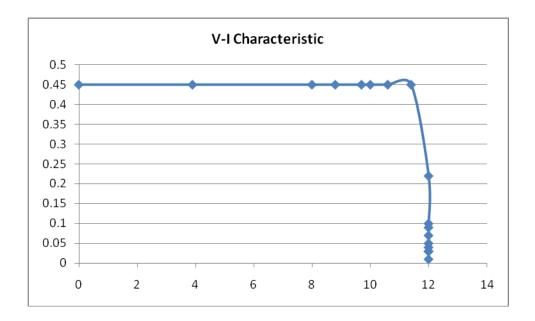

Figure 12:Solar Simulator V-I characteristic

| Load(Ω) | Vout1(V) | lout1(A) | Vout2(V) | lout2(A) | Vout3(V) | lout3(A) |

|---------|----------|----------|----------|----------|----------|----------|

| 1       | 0.578    | 0.578    | 0.327    | 0.372    | 0.772    | 0.772    |

| 2       | 1.155    | 0.5775   | 0.654    | 0.327    | 1.541    | 0.771    |

| 4       | 2.305    | 0.576    | 1.309    | 0.327    | 3.069    | 0.766    |

| 10      | 5.721    | 0.572    | 3.265    | 0.326    | 7.572    | 0.757    |

| 15      | 8.53     | 0.569    | 4.888    | 0.326    | 10.958   | 0.73     |

| 20      | 11.044   | 0.552    | 6.505    | 0.325    | 11.226   | 0.561    |

| 25      | 11.249   | 0.45     | 8.115    | 0.325    | 11.37    | 0.455    |

| 30      | 11.367   | 0.379    | 9.718    | 0.324    | 11.467   | 0.382    |

| 35      | 11.449   | 0.327    | 11.151   | 0.319    | 11.536   | 0.329    |

| 45      | 11.56    | 0.257    | 11.36    | 0.252    | 11.63    | 0.258    |

| 51      | 11.606   | 0.227    | 11.429   | 0.224    | 11.669   | 0.229    |

| 75      | 11.718   | 0.156    | 11.59    | 0.154    | 11.764   | 0.157    |

| 100     | 11.779   | 0.118    | 11.676   | 0.117    | 11.815   | 0.118    |

| 125     | 11.815   | 0.0945   | 11.728   | 0.0938   | 11.846   | 0.0947   |

| 169     | 11.854   | 0.0701   | 11.782   | 0.0697   | 11.879   | 0.0703   |

| 210     | 11.875   | 0.056    | 11.812   | 0.0562   | 11.897   | 0.0566   |

| 300     | 11.902   | 0.0397   | 11.85    | 0.0395   | 11.92    | 0.0397   |

The figure and respective table shows the V-I characteristic of the solar panel simulator. These results were experimental, involving the change of load and variable resistors to determine the outcome. Varying the load resistance resulted in varying levels of output voltage. Varying the resistance configuration resulted in varying levels of output current. The maximum output of about 770 mA corresponds to the configuration of all resistances in parallel, while the output of about 372 mA corresponds to the configuration of just one resistor in series with the PNP BJT. Vout1 corresponds to two  $1.5\Omega$  resistors in parallel, Vout2 corresponds to 3 1.5 $\Omega$ resistors in parallel, while Vout3 corresponds to one 1.5 $\Omega$  resistor in series with the transistor. Observing the V-I characteristic, the solar panel simulator's operation as a typical solar panel is confirmed, with an open circuit voltage of approximately 11.5V and short circuit current from 372mA to 770mA depending on the resistance configuration.

#### **3.3 Input Filter**

Adding an input filter to the design will help increase overall system efficiency and help reduce input noise. The input capacitor applied in our boost design will reduce the current peaks drawn from the input supply and reduce noise injection. The capacitor's value is largely determined by the source impedance of the input supply. High source impedance would require high input capacitance, particularly as the input voltage falls. Since step-up DC-DC converters act as constant-power loads to their input supply, the input current rises as the input voltage falls. In low input voltage designs, increasing the input capacitance or lowering its equivalent series resistance can add as many as five percentage points to conversion efficiency.

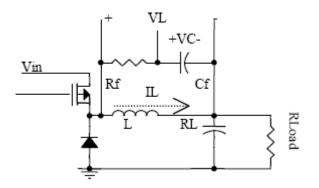

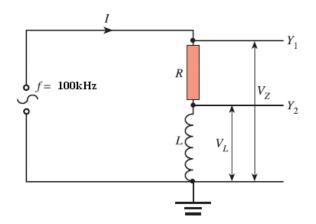

Figure 13: Input LC filter

The DC-DC converter in the design will create a switching circuit. Taking a series circuit with a capacitor, inductor and the MOSFET of the converter as a switch, when the switch is closed, the capacitor of the input filter will start to discharge and the current increases. At this stage, energy is transferred from the capacitor to the inductor. When the capacitor is completely discharged, the current peaks and the capacitor begins to charge the opposite way.

Energy is then transferred back from the inductor to the capacitor. The current alternates between the inductor and capacitor with an angular frequency in radians/second of

$$\omega = \sqrt{1/LC}$$

where L is the inductance in henries, and C is the value of capacitance in farads. The LC filter will be used to decrease the input ripple and improve input efficiency.

**3.4 DC-DC Boost Converter Analysis**

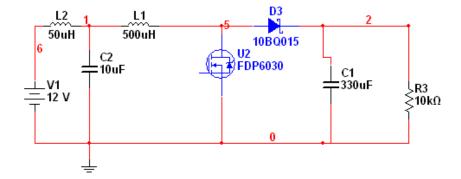

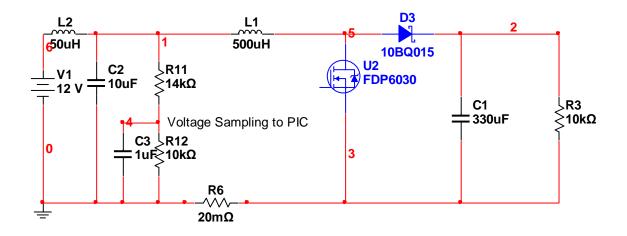

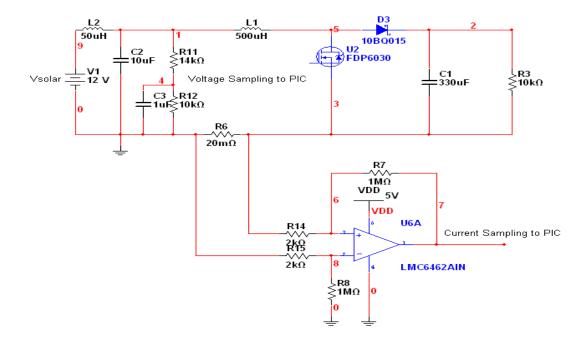

Figure 14: DC-DC converter simulation circuit

In order to understand and obtain the expected results of the DC-DC converter in the design, it is important to first simulate operation with the given parameters. The DC-DC converter is designed with an input voltage of 12V, a boost converter is designed with a 500 $\mu$ H inductor, 330 $\mu$ F capacitor, an ideal switch and diode, output load of 20 $\Omega$ . The input pulse signal to the ideal switch is a 2V pulse with a switching frequency of 100kHz. At a 50% duty cycle, the converter boosts the input voltage from 12V to the input to 20V at the output. With a simulated DC-DC boost converter, it was useful to modify the values of the different components of the circuit as well as the duty cycle in order to obtain the desired results. An input LC filter with a 50 $\mu$ H inductor and 10 $\mu$ F capacitor is also included to observe the effect on the input from adding a filter to the converter.

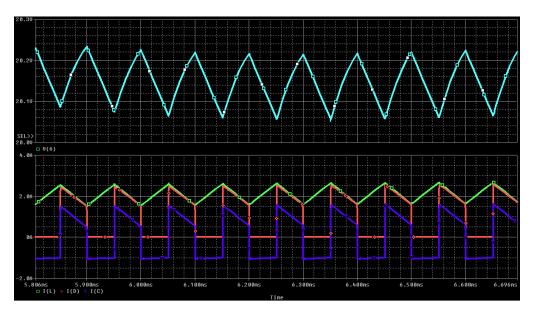

Figure 15: Output load voltage and current across inductor, diode, and capacitor

Here we observe the output voltage at the load, and current through the inductor, diode and capacitor. The average voltage is close to the desired 20V for a duty cycle of 40%. When the inductor is charging, the switch is on, and there is no current across the capacitor or diode because the output stage is isolated. When the switch is off, the inductor discharges energy and there is current through the diode and capacitor.

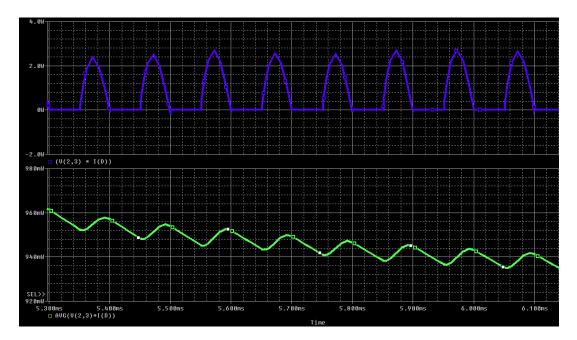

Figure 16: Switching power losses and average power loss

These two plots describe the losses due to switching. When the switch goes to its off state, there are power losses due to a loss in energy. The first plot describes a power loss of a little over 2 watts at each switch. The average power loss is small, less than 1 watt of overall loss for the system.

#### **3.5 Operating Frequency**

The operating frequency of the system will depend on the inductor used and MOSFET selected. An important factor to consider will be the switching losses associated with the switching of the circuit. At higher frequencies, the losses due to switching will increase. In addition, with higher frequencies it is important to keep some resolution in the duty cycle. A switching frequency of 100kHz was chosen. This switching frequency is appropriate to both the inductor and the MOSFET chosen. The MOSFET chosen will easily take this as a switching frequency and resolution is maintained without adding too much in power losses.

#### **3.6 Voltage Sensing**

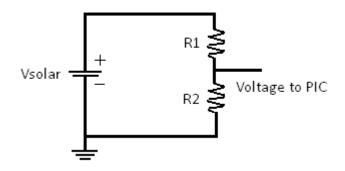

In order for the microprocessor to control the duty cycle of the converter, it needs to obtain voltage samples from the solar panel input. This will be done through a very simple method of voltage sensing. Normally, the microprocessor would be able to take voltage directly from a source to sense the voltage. However, the voltage coming from the solar panel will be much too large for the microprocessor to handle. The maximum amount of voltage that the microprocessor will take will be 5V. Any voltage larger than this amount to the microprocessor would risk destroying it, and the system would fail to monitor and maintain the peak power operating point all together. Knowing this, it is with great care that we implement the voltage divider in such a way that it will always output a voltage that is much less than the threshold voltage of what the microprocessor can handle.

31

Figure 17: Voltage divider

#### **3.7 Current Sensing**

To calculate the power coming from the solar panel simulator, the microprocessor needs to be able to take current samples from the solar panel simulator in addition to the voltage. In theory, there are several different methods of current sensing. These different methods vary in their placement within the circuit design and the method of obtaining a current reading. Because the microprocessor will not be able to take the current from the solar panel simulator directly, an indirect method of current sensing must be used.

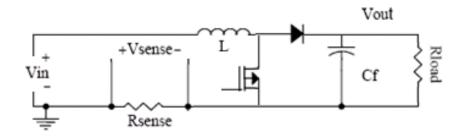

#### **3.7.1 Series Sense Resistor**

Using a series sense resistor is the conventional way of sensing a current. Resistive current sensing is done by inserting a resistance into the circuit. The resistance is typically small, but it used to measure the voltage across the resistor. The voltage seen across the resistor is proportional to the current, making current sensing possible.

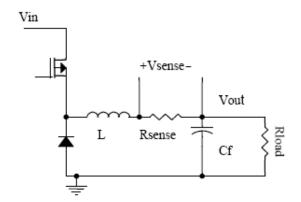

Figure 18: Current resistor sensing

Figure 18 demonstrates the typical use of a current sense resistor with resistive current sensing. This is not the configuration we will be using in the designed circuit, however it demonstrates the simple placement of an added sense resistor. One disadvantage for this method is that it incurs a power loss in R<sub>SENSE</sub>, and therefore reduces the efficiency of the DC-DC converter. In order to keep measurements accurate, the voltage across the sense resistor should be roughly 100mV at full load due to practical limitations. For example, if the full-load current is 1A, 0.1W is dissipated in the sense resistor. For an output voltage of 3.3V, the output power is 3.3W at full-load. This means that the sense resistor reduces the system efficiency by 3.3%. This reduction of efficiency will be detrimental to the overall circuit and power losses should be avoided.

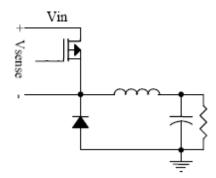

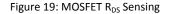

#### 3.7.2 R<sub>DS</sub> Sensing

Current can be sensed through the drain-source resistance of a MOSFET because MOSFETs act as resistors when they are "on" and they are biased on the non-saturated region. Assuming that the voltage across the drain-source,  $V_{DS}$  is relatively small as is the case for MOSFETs used as switches, the equivalent resistance of the device is:

$$R_{DS} = \frac{L}{W \mu C_{OX} (V_{GS} - V_T)}$$

where  $\mu$  is the mobility,  $C_{OX}$  is the oxide capacitance, and  $V_T$  is the threshold voltage. Provided that  $R_{DS}$  is known, the switch current can be determined by sensing the voltage across the drain-source of the MOSFET.

The disadvantage to this technique is low accuracy. This is due to the fact that the R<sub>DS</sub> of the MOSFET is inherently nonlinear and usually has significant variation because of the mobility, capacitance and threshold voltage. The R<sub>DS</sub> is also dependent on the temperature exponentially which can greatly increase the variation of its actual value. Despite low accuracy, R<sub>DS</sub> sensing is useful because it does not add an additional resistance which would result in greater power losses.

#### 3.7.3 Filter Sensing the Inductor

Instantaneous changes in the input voltage are immediately reflected in the inductor current, so it is often useful to observe the current across the inductor for current-mode control in a DC-DC converter. Regardless of the type of feedback control, typically all DC-DC converters sense the inductor current for over-current protection. Filter sensing the inductor uses a simple low-pass RC network to filter the voltage across the inductor and sense the current through the equivalent series resistance (ESR) of the inductor.

Figure 20: Filter Sensing the inductor

The voltage across the inductor is given by

$$V_L = (R_L + sL)I_L$$

where L is the inductor value and  $R_L$  is the ESR of the inductor. The voltage across the capacitor of the filter is

$$V_{C} = \frac{V_{L}}{1 + sR_{f}C_{f}} = \frac{(R_{L} + sL)I_{L}}{1 + sR_{f}C_{f}} = R_{L} \left(\frac{1 + s(\frac{L}{R_{L}})}{1 + sR_{f}C_{f}}\right)I_{L} = R_{L}\frac{1 + sT}{1 + sT_{1}}I_{L}$$

where  $T=L/R_L$  and  $T_1=R_FC_F$ . Forcing  $T=T_1$  yields  $V_C =R_LI_L$ . Because of this relationship,  $V_C$  is directly proportional to the current  $I_L$ . In order to use this technique, L and  $R_L$  must be known, and then R and C are chosen accordingly. Because of the tolerance of the components required, this technique is not appropriate for integrated circuits. The technique is useful for proper design for a discrete, custom solution where the type and value of the inductor is known.

#### 3.7.4 Magnetic Sensing-Hall Effect Sensors

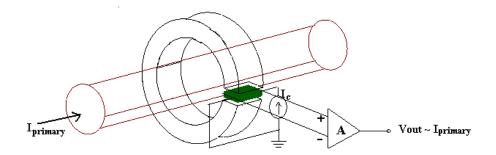

Hall effect sensors sense current by taking advantage of the Hall Effect. According to the Hall effect, a magnetic field passing through a semiconductor resistor will generate a differential voltage proportional to the field. Concentric magnetic field lines are generated around a current carrying conductor. Assuming that the primary current conductor is infinitely long, the magnetic field strength may be defined as  $B=\mu_0I/2pr$ , where  $\mu_0$  is the permeability of free space, I is the current and r is the distance from the center of the current conductor.

To induce a larger signal out of the Hall element the current conductor is wrapped around slotted ferrous toroid N number of times. This yields the equation for the magnetic field,  $B=\mu_0I/2pr$ . In an open loop topology, the hall element output is taken, amplified, and then outputted as a voltage that represents the measured current through a scaling factor.

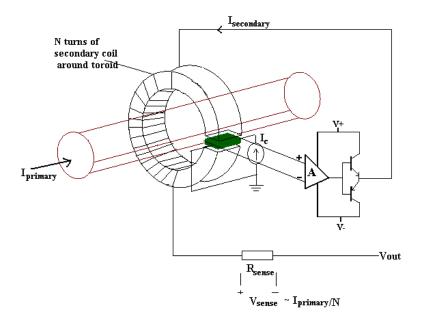

Figure 21: Open-Loop hall effect current sensing

Using a closed loop topology combines Hall effect sensing, resistive sensing, and transformer current behavior. When using closed loop topology, the output of the Hall element drives a secondary coil. This generates a magnetic field to cancel the primary current field. The secondary current, scaled proportionally to the primary current by the secondary coil ratio can then be measured as a voltage across a sense resistor. The advantage to a closed loop topology is fast response time. However, power consumption is increased with the need for a secondary coil to drive up to several milli-amps of current.

Figure 22:Closed-Loop hall effect current sensing

#### 3.7.5 Current Sensing Conclusion

There are many different methods possible for current sensing. However it is clear that some are not necessarily appropriate for our application. R<sub>DS</sub> sensing will not be appropriate because the high switching frequency and operation of our MOSFET as a switch. The current across R<sub>DS</sub> can only be measured when the FET is on, and with a switching frequency of 100kHz, it will be difficult to pinpoint current samples when the switch constantly oscillates between off and on states. Inductor sensing offers proportional current measurement with relatively insignificant power loss, however, the method of inductor current sensing is typically inaccurate. Hall effect sensing is out of the question because of cost considerations, power consumption for operation, and because of the characteristics of the current that we will actually measure. Hall effect sensors are typically applied for AC current, and high current sensing, neither of which apply to our circuit. In fact, typical Hall effect sensors need to sense at least 5A of current before they output a differential voltage.

| Current Sensing Method         | Value  | Accuracy       | Power Dissipation | Relative Cost |

|--------------------------------|--------|----------------|-------------------|---------------|

|                                |        |                |                   |               |

| Open loop Hall effect sensor   | -      | 90-95%         | Low               | Medium        |

|                                |        |                |                   |               |

| Closed loop Hall Effect sensor | -      | >95%           | Moderate-high     | High          |

|                                |        |                |                   |               |

| High Precision Current Sensing | .020 Ω | >95%           | Moderate          | Low           |

| Resistor                       |        |                |                   |               |

|                                |        |                |                   |               |

| Inductor Filter Sensing        | -      | 50%            | Low               | Low           |

|                                |        |                |                   |               |

| R <sub>DS</sub> Sensing        | .024 Ω | Not applicable | Low               | Low           |

|                                |        |                |                   |               |

The method we chose to implement in our circuit is with a high precision current sensing resistor. This method is the most typically used and the easiest to implement in the circuit. The method is highly accurate, relatively inexpensive, and has tolerable power dissipation. The reason why it is defined to have 'moderate' power dissipation is because the power dissipation is relatively insignificant. Inductor filter sensing, for example, relies greatly on just the equivalent resistance of the inductor, which is typically very small. R<sub>DS</sub> also has very small resistance, but the power dissipation is relatively low because no additional resistance is added to the circuit. The addition of a very small resistance and minimal power loss is the only disadvantage of using a current sense resistor, and its ease of application more than makes up for it.

Figure 23: Resistive sensing in the boost dc-dc converter

# 3.8 Determining Inductance Value

In all switching regulator applications, and in our own, the inductor is used as an energy storage device. When the semiconductor switch is on, the current across the inductor ramps up and energy is stored within it. When the switch turns off, the energy stored is released into the load. The inductor's storage and release of energy in conjunction with the output capacitor is what accounts for the average output current and voltages resulting in a steady dc output. The amount of energy stored in an inductor is given by

$$\frac{1}{2}LI^2$$

where L is the inductance in Henrys, and I is the peak value of the inductor current. When selecting an inductor for a buck converter, as with all switching regulators, the most important parameters to calculate will be

- Maximum input voltage

- Output voltage

- Switching Frequency

- Maximum ripple current

- Duty Cycle.

For our dc-dc boost converter, if we assume a switching frequency of 100kHz, an input voltage of 12V, and an output of 20V with a minimum load of 500mA. For an input of 12V, the duty cycle will be determined by:

$$D = 1 - \frac{V_{IN}}{V_O}$$

This will give us a duty cycle of 0.4  $V_{IN}$  and  $V_{O}$  are the input and output voltages respectively. The voltage across the inductor when on is equal to the input voltage of 12V. When off, the voltage across the inductor is the difference between  $V_{O}$  and  $V_{IN}$ , or -8V. The current ripple is given by the equation:

$$\Delta I = \frac{V_{IN}}{L} DT_S = \frac{V_O - V_{IN}}{L} (1 - D)T_S$$

Choosing a current ripple that is twice that of  $I_{IN}$  will allow us to calculate the minimum value of the inductor what will insure continuous current for a given D, R and switching frequency F. The current ripple to find the minimum inductance is determined by:

$$\Delta I = 2 \times I_{IN} = \frac{V_{IN}}{L_{MIN}} DT_S$$

From this simple equation we obtain the minimum inductance:

$$L_{MIN} = \frac{V_{IN}}{I_{IN}} \frac{D}{2F_S} = \frac{(1-D)DV_O}{\frac{1}{(1-D)}I_O f_S} = \frac{(1-D)^2 DR}{2f_S}$$

With  $V_{IN} = 12V$ ,  $I_{IN}=0.5A$ , D=0.4, and  $f_s = 100$ kHz, we obtain the minimum inductance needed for continuous conduction to be 48µH. With this value obtained, we now know that the inductance chosen needs to be greater than 48µH otherwise, the dc-dc converter may enter discontinuous conduction mode and will not operate correctly.

Due to the typically high switching frequencies of the controller, inductors with a ferrite core or equivalent have been recommended, while powdered iron cores are not recommended due to their high losses at frequencies larger than 50kHz. Once we obtain the peak inductor current,  $I_{LPEAK}$ , we must take care to make sure that the inductor's saturation rating meets or exceeds the calculated value for  $I_{LPEAK}$  even though most coil types can operate up to 20% over their saturation rating without experiencing difficulty. In addition, the inductor should have as low a series resistance as possible. While in continuous operation mode, the power loss in the inductor resistance,  $P_{LR}$  is approximated by:

$$P_{LR} \cong (I_{OUT} \times V_{OUT}/V_{IN})^2 \times R_L$$

where  $R_L$  is the inductor series resistance.

## 3.9 Confirming Peak Power Obtained - Thevenin Equivalence

When we design the controller system for the maximum peak power tracker, it is important to have a full understanding of the boost converter circuit operation. Obtaining the average current— $I_{AVG}$ , the average voltage,  $V_{AVG}$ , the equivalent resistance of the circuit,  $R_{EQ}$ , the ripple current, I, and the output power, P—we can predict the outcome of the circuit. To confirm peak power operation, a Thevenin power source can be used.

The solar panel will be modeled as a linear thevenin voltage and resistance. The goal is to operate the circuit near the maximum power point of the non-linear I-V characteristic of the solar panel. Modeling the thevenin power source to have a linear I-V characteristic similar to the

solar panel will allow us to monitor the outcome of the circuit to see if peak power is obtained.

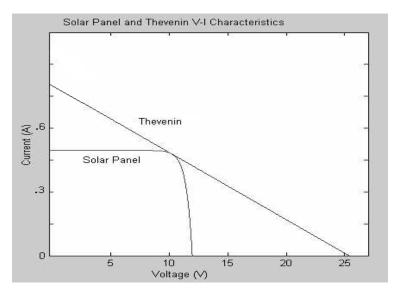

Figure 24: Solar panel and thevenin power characteristic comparison

If the maximum power point of the two curves are basically in line, then it will be beneficial to model the thevenin source. To obtain the correct thevenin voltage and resistance, simply double the voltage at the maximum power point of the non linear model. This is because the maximum power point for the linear model will occur at the midpoint and the the thevenin resistance will simply be the voltage over the current at the maximum power point.

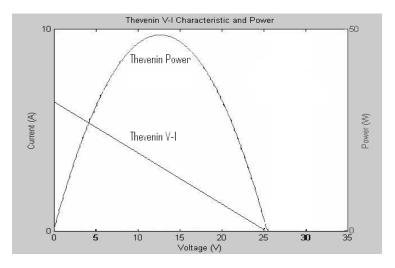

Figure 25: Thevenin power and V-I characteristic

### **3.9.1 Average Current and Ripple**

Implementing a thevenin source and resistance, the maximum current that will flow into

the circuit, I<sub>MAX</sub> is obtained from:

$$I_{MAX} = \frac{V_{TH}}{R_{TH}}$$

where  $V_{TH}$  and  $R_{TH}$  represent the thevenin voltage and resistance.

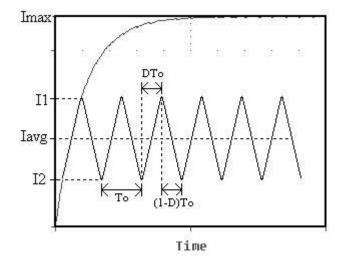

Figure 26: Average current vs. Time

When the duty cycle of the circuit is high, the current will try to reach the maximum current. When the duty cycle is low, the current will try to reach the maximum negative current. Since there is only one source of power in our circuit, there will be no negative power source, and there will be no negative current; the most negative the current can be is zero. The ripple will vary between zero amps and the maximum current and the location and ripple size of the current will be determined by the duty cycle and frequency. The expression for the changing current is given by:

$$l(t) = I_{MAX} - (I_{MAX} - I_2)e^{-t/\tau}$$

When the duty cycle is high, the initial current,  $I_2$  will increase until the duty cycle goes low. This occurs as  $I_1$ . The final current will be  $I_{MAX}$ , when the duty cycle is high. The time constant L/R is represented by  $\tau$ . The time, t, is equivalent to the amount of time in which the duty cycle is high, DT<sub>0</sub>, where D is the duty cycle, and T<sub>0</sub> is the time period. With T<sub>0</sub> much less than the time constant  $\tau$ , the equation for  $I_1$  is given by

$$I_1 = I_{MAX} \left( \frac{DT_0}{\tau} \right) + I_2 \left( 1 - \frac{DT_0}{\tau} \right)$$

There are now two unknowns,  $I_1$  and  $I_2$ . When the duty cycle is low, the initial current will be at  $I_1$ and will drop to  $I_2$  while the duty cycle goes high. With no negative current, the relationship between  $I_2$  and  $I_1$  is given by

$$l_2 = l_1 \left[ 1 - \frac{(1-D)T_0}{\tau} \right]$$

With two equations and two unknowns, we can now solve for the maximum and minimum ripple values,  $I_1$  and  $I_2$  as a function of known values: duty cycle, time period, saturation currents, and  $\tau$ . To obtain the ripple current, it is necessary to obtain expressions for the ripple currents that are independent of each other. Using already obtained equations,  $I_1$  can be obtained as

$$I_1 = I_{MAX} \frac{DT_0}{\tau} + \left[ I_1 \left( 1 - \frac{(1-D)T_0}{\tau} \right) \right] \left( 1 - \frac{DT_0}{\tau} \right)$$

Solving for I<sub>1</sub> and simplifying, we obtain

$$l_1 = \frac{I_{MAX} \frac{DT_0}{\tau}}{1 - \left[ \left(1 - \frac{DT_0}{\tau}\right) \left(1 - \frac{(1-D)T_0}{\tau}\right) \right]}$$

To obtain  $I_2$ , we use the equation

$$I_2 = \left[ I_{MAX} \frac{DT_0}{\tau} + \left[ I_2 \left( 1 - \frac{(1-D)T_0}{\tau} \right) \right] \right] \left( 1 - \frac{DT_0}{\tau} \right)$$

Simplifying, and solving for I<sub>2</sub>,

$$I_{2} = \frac{I_{MAX} \frac{DT_{0}}{\tau} \left(1 - \frac{(1-D)T_{0}}{\tau}\right)}{1 - \left[\left(1 - \frac{DT_{0}}{\tau}\right) \left(1 - \frac{(1-D)T_{0}}{\tau}\right)\right]}$$

Now that we have obtained expressions for  $I_1$  and  $I_2$ , we can now obtain the important value for  $I_{AVG}$ . The average between the two points is simply half of their sum. The average current will be determined as half the sum of the maximum and minimum ripple values,

$$I_{AVG} = \frac{I_1 + I_2}{2}$$

Using the previous equations for the ripple values,  $I_{\text{AVG}}\,\text{can}$  be seen as

$$I_{AVG} = \frac{I_{MAX} \frac{DT_0}{\tau} \left(2 - \frac{(1-D)T_0}{\tau}\right)}{2 \frac{T_0}{\tau} \left[1 - D(1-D)\frac{T_0}{\tau}\right]}$$

With  $T_0$  much less than the time constant,  $\tau$ , any term that depends on either will be approximately zero, if they affect the result significantly. Keeping this in mind, the simple way of obtaining the average current is

$$I_{AVG} = I_{MAX}D$$

Using this equation, we can observe the effect of the duty cycle on the average current. When the duty cycle is high, at 100 percent, the average current will go to the maximum positive saturation value,  $I_{MAX}$ . When the duty cycle is low, going to 0, the average current will also go to 0. This makes sense because if the main switch of the MOSFET is always closed, then the current will try to reach the maximum current, and with the switch constantly closed, the current will drop to the minimum amount of current, in our case, 0. The current ripple,  $\Delta I$ , is simply the final value of the current,  $I_1$ , minus the initial value  $I_2$ :

$$\Delta I = I_1 - I_2$$

#### 3.9.2 Average Voltage and Ripple

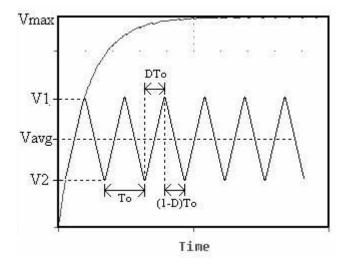

It is now useful to obtain values for the average voltage and the ripple that can be seen in the voltage. When the main switch is closed for a long period of time, the current will gradually build through the inductor, and the voltage will drop exponentially at the same rate of the current increase.

Figure 27: Average voltage vs. time

The maximum negative value that the average voltage can be is zero. This is true because when the current builds to its maximum value, it only depends on the thevenin voltage and resistance, so the voltage at this point must be zero. When the current is at its minimum, the average voltage will simply be equivalent to whatever voltage is obtained from the solar panel. Noting that when the voltage reaches its max, the current reaches its minimum and when the voltage reaches its maximum, the current goes to its minimum, it will be easy to obtain the expression for average voltage. This is because the voltage will decrease at the same rate as the current, but to different points. Thus, the equation for average voltage is very similar to that of the average current:

$$V_{AVG} = V_{MAX}(1-D)$$

With respect to the duty cycle, thevenin voltage and resistance, the inductor, and frequency, voltage ripple is obtained as

$$\Delta V = \frac{DR_{TH}V_{MAX}(1-D)}{Lf}$$

#### **3.9.3 Equivalent Resistance and Power**

The average current and voltage have now been obtained. It is now very simple to derive an expression for the equivalent resistance of the circuit. The equivalent resistance is obtained simply as the relationship of the average current and average voltage:

$$R_{EQ} = \frac{V_{AVG}}{I_{AVG}}$$

The expected average power will also be simple to obtain and also depends on the relationship between the average voltage and current:

$$P_{AVG} = V_{AVG} I_{AVG}$$

When the equivalent resistance of the total circuit equals the Thevenin resistance, maximum peak power can be observed. This is because the maximum load current is obtained when the equivalent resistance is twice the total resistance (or when  $R_{EQ} = R_{TH}$ ):

$$I_{MAX} = \frac{V_0}{2R_0}$$

This will be the main method of determining that peak power is obtained. Although we will observe duty cycle oscillation when peak power is obtained, the method of comparing the equivalent resistance and thevenin resistance is a dependable way to check to see if the circuit is acting properly.

# 4.0 Implementation

## 4.1 Parts Selection

#### **4.1.1 MOSFET Gate Driver Selection**

The MOSFET in our circuit will serve its purpose as a switch. The switching of the FET according to the defined switching frequency and duty cycle will define the output of the circuit. After taking voltage and current samples, the microprocessor will output a pulse width modulated (PWM) signal to modify the duty cycle of the converter. The PWM signal cannot be connected directly to the MOSFET; instead, we will use a MOSFET driver to pass the signal to the gate of the MOSFET.

The advantages of using a MOSFET gate driver made it clear that it was the best choice for implementation. The microprocessor in the circuit can supply only a certain output current. This limits the ability to charge the FET before it can turn on because the gate of the MOSFET is capacitive. The gate driver itself will source the current that our MOSFET will draw, and results with a higher current to the FET. With the higher current, the gate driver decreases propagation delay and allows for a cleaner wave preventing lag in the rise and fall of the FET wave. Another benefit of using a gate driver is that the it has a higher switching speed than the microprocessor can achieve, adding to the overall efficiency of the circuit.

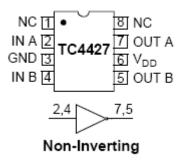

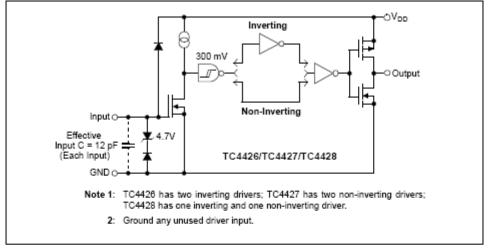

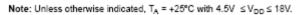

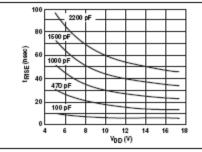

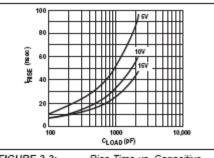

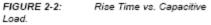

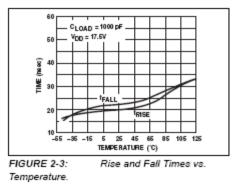

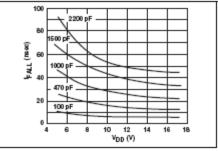

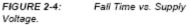

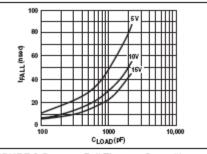

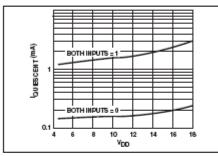

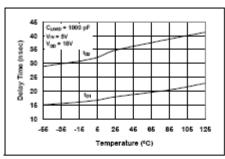

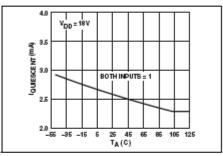

The MOSFET gate driver selected for the circuit is the TC4427 from Microchip Technologies. This driver was chosen for its high switching speed, low current consumption, single supply operation, and low impedance during both 'on' and 'off' states. The low output impedance of 7 $\Omega$  is important to have so that expected state of the switch is not affected by operation, even by large transients. Its high output peak current of 1.5A is more than enough needed to power our FET and provides 4mA with logic '1' input and 400µA with logic '0' input. The wide input supply voltage operating range is from 4.5V to 18V and will always operate given the 5V input from a voltage regulator that will be implemented in the circuit design. The delay times for rise and fall are typically 40nsec and are very short. In addition to the short delay times, the rise and fall times are matched and symmetrical.

Figure 28: TC4427 MOSFET gate driver

Figure shows the pin layout of the TC4427, with two non-inverting drivers. The inverting input of the TC4427 is connected to ground and the non-inverting input is connected to the

PWM signal taken from the microprocessor. The output is connected to the gate of the switching MOSFET of the DC-DC converter.

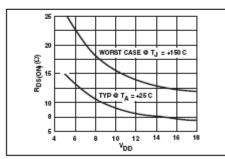

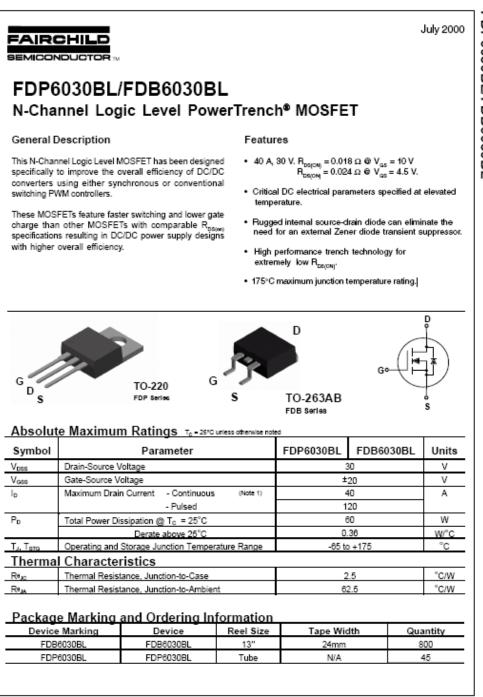

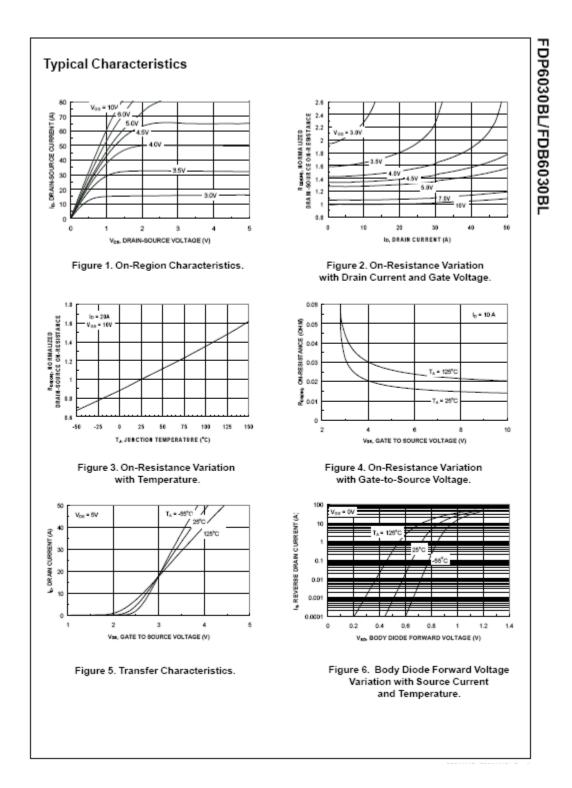

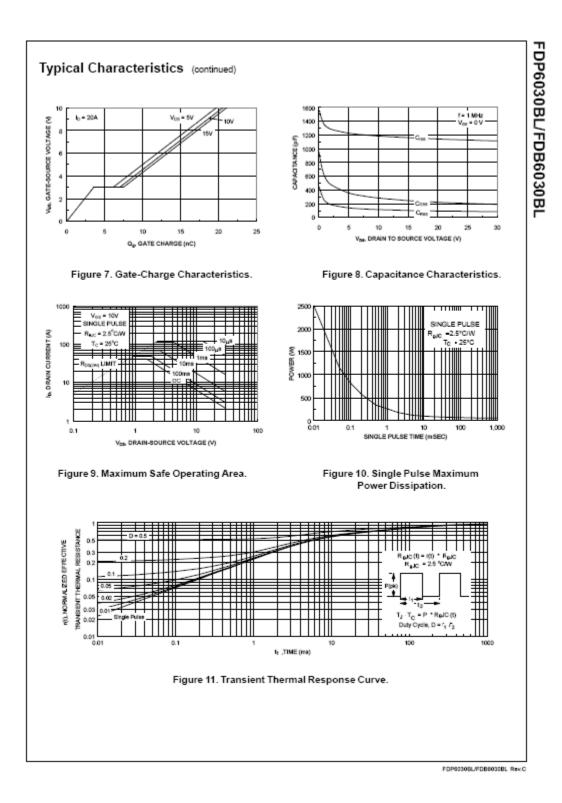

# 4.1.2 Power MOSFET Selection

The MOSFET selection is a key factor of the design. The MOSFET in our circuit will act as the switch that varies the duty cycle of the dc-dc converter, making it possible to step up the input voltage. A low threshold NFET that specify on-resistance with a gate-source voltage ( $V_{GS}$ ) of 2.7V or less is preferred. There are many parameters that must carefully be examined when choosing a FET. These important constraints include:

- 1.) Total gate charge (Qg)  $\rightarrow$  Predicts switching loss

- 2.) Reverse transfer capacitance or charge ( $C_{RSS}$ )  $\rightarrow$  Predicts switching loss

- 3.) On-resistance  $(R_{DS(ON)}) \rightarrow$  Predicts DC losses

- 4.) Maximum drain-to-source voltage (V<sub>DS(MAX)</sub>)

- 5.) Minimum threshold voltage ( $V_{TH(MIN)}$ ).

The most important characteristic to examine will be the FET's expected power dissipation. The amount of power that a FET dissipates relies on many constraints. The MOSFET will have both DC losses and losses due to its constant switching. In order to optimize the efficiency of the design, it is important to minimize these losses as much as possible. It is also important to understand that these losses depend on the switching frequency, current, duty cycle, and the switching rise and fall times. Our goal is to minimize conduction and switching and to choose a device with sufficient thermal properties. The breakdown voltage, current-carrying capability, R<sub>ON</sub>, and the R<sub>ON</sub> temperature coefficient will be important parameters to consider. Before a MOSFET begins to switch, the power dissipation derives from conduction losses. The conduction loss is proportional to the on-state channel resistance,  $R_{ON}$  of the MOS device (Q1):

$$P_C = I_D^2 R_{ON}$$

where  $I_D$  is the drain current, and  $R_{ON}$  is the channel resistance at the manufacturer's specified nominal ambient temperature. The switching losses are contributed by the charging and discharging of the gate capacitance. To close the FET, a charge from the gate to the source builds up to allow current to flow. Once the MOSFET's capacitor achieves a charge equal to its  $Q_G$  value, the MOSFET switch closes and current flows. When the switch is opened again, the capacitor discharges all of  $Q_G$ . This loss of charge results in some power loss which increases with higher switching frequencies:

$$P_G = V_G^2 C_{GS} f$$

where  $V_G$  is the gate-drive voltage,  $C_{GS}$  is the gate-source capacitance, and f is the switching frequency. We can split up the switching losses due to capacitance and switching. The power loss due to the charging of the capacitor is:

$$P_Q = Q_G V_G f$$

While the power lost due to switching is given by:

$$P_S = \frac{1}{2} (t_r + t_f) I_{RMS} V_S f$$

Where  $I_{RMS}$  is the drain current;  $t_r$  and  $t_f$  are the switching rise and fall times, respectively; and  $V_s$  is the input source voltage. The total power dissipation in  $Q_1$  is given by:

$$P(Q_1) = I_{RMS}^2 R_{ON} + f[Q_G V_G + \frac{1}{2}(t_r + t_f)I_{RMS}V_S].$$

In this Equation, the first term reflects the conduction loss, while the second term accounts for the dynamic and gate losses. The dynamic and gate losses are given by the capacitor of the FET and the losses that occur during switching.

Having calculated the power dissipation, it is also important to calculate the temperature rise from the thermal resistances of the package. This will be important for the design once we decide on what heatsink to use (if necessary at all). The temperature rise is as follows:

$$\Delta_T = R_{\varphi}P$$

Where  $\Delta_T$  is the temperature rise over ambient degrees Celsius, P is the device's total power dissipation, and  $R_{\odot}$  is the total thermal resistance taken as the sum of junction-to-case resistance of the FET's package and the heat-sink thermal resistance. There is also a small case-to-sink term, however this term is very small and often negligible especially when more modern thermal interface materials are used.

The MOSFET's power dissipation is complicated due to its reliance on  $R_{ON}$ . For example, a temperature rise of about 80°C causes a 40% increase in the value of  $R_{ON}$ . To find the actual temperature rise, we need to include this behavior in the analysis of conduction losses. Including  $R_{ON}$ 's temperature coefficient to the power loss equation yields:

$$P(Q_1) = I_{RMS}^2 R_{ON} (1 + \delta \Delta_T) D + f[Q_G V_G + \frac{1}{2} (t_r + t_f) I_{RMS} V_S]$$

where  $\delta$  is the temperature coefficient of  $R_{ON}$  in  ${}^{\circ}C^{-1}$ . Substituting these variables into the equation for temperature rise, and solving for the device's  $\Delta_T$ , the temperature rise at the MOSFET  $Q_1$  is given by:

$$\Delta_T(Q_1) = \frac{R_{\Theta}[I_{RMS}^2 R_{ON} D + f[Q_G V_G + \frac{1}{2}(t_r + t_f)I_{RMS} V_S]}{1 - R_{\Theta}I_{RMS}^2 \delta R_{ON} D}$$

| MOSFET   | Cata Charge O (pC)              | Drain-Source                       | Pico Timo + (nc)               | Fall Time, t <sub>f</sub> (ns) |

|----------|---------------------------------|------------------------------------|--------------------------------|--------------------------------|

| IVIOSELI | Gate Charge Q <sub>G</sub> (nC) | Drain-Source                       | Rise Time, t <sub>r</sub> (ns) | Fall fille, (fis)              |

|          |                                 |                                    |                                |                                |

|          |                                 | Resistance, $R_{DS}$ (m $\Omega$ ) |                                |                                |

|          |                                 |                                    |                                |                                |

| FDP6030  | 17                              | 24                                 | 20                             | 16                             |

|          |                                 |                                    |                                |                                |

|          |                                 |                                    |                                |                                |

| IRL7833  | 32                              | 3.8                                | 50                             | 6.9                            |

|          |                                 |                                    |                                |                                |

|          |                                 |                                    |                                |                                |

| IRFU014  | 11                              | 200                                | 50                             | 19                             |

|          |                                 |                                    |                                |                                |

|          |                                 |                                    |                                |                                |

| IRF7401  | 48                              | 22                                 | 72                             | 92                             |

|          |                                 |                                    |                                |                                |

| 500000   | 27                              | 45                                 | 10                             | 22                             |

| FDS6880  | 27                              | 15                                 | 18                             | 23                             |

|          |                                 |                                    |                                |                                |

|          |                                 |                                    |                                |                                |

This table lists several comparable power n-channel MOSFETs that would be ideal for implementation into the circuit. From the data sheets, the most pertinent parameters have been chosen for power loss analysis, including gate charge, drain-source resistance, and the rise and fall times typical of switching operation.

| MOSFET  | P <sub>c</sub> (mW) | P <sub>Q</sub> (mW) | P <sub>s</sub> (mW) | Total Loss (mW) |

|---------|---------------------|---------------------|---------------------|-----------------|

| FDP6030 | 6                   | 8.5                 | 4.5                 | 19.0            |

| IRL7833 | 0.95                | 16                  | 7.1125              | 24.0625         |

| IRFU014 | 50                  | 5.5                 | 8.625               | 64.125          |

| IRF7401 | 5.5                 | 24                  | 20.5                | 50              |

| FDS6880 | 3.75                | 13.5                | 5.125               | 22.375          |

With switching frequency, f = 100 kHz,  $V_s = 5V$ ,  $I_p = 500 \text{mA}$

After using the parameters of each FET to calculate the losses due to R<sub>DS</sub>, the gate charge, and switching rise and fall times, it is clear that the FDP6030 from Fairchild Semiconductors is the best choice. The losses taken from each FET increases as frequency increases, but at our switching frequency of 100kHz, the losses found in the FDP6030 are still relatively insignificant and is definitely the least among comparable MOSFETs.

#### **4.1.3 Inductor Selection**

In an effort to save both money and time, an inductor was tested and designed in the lab. The advantage was that we were able to make an inductor using readily available material that did not have to be purchased from a manufacturer. Also, with given design constraints, we were able to successfully make an inductor with the desired amount of inductance for the circuit. To create the inductor, an experiment was used that would generate highly consistent results with those obtained from theoretical predictions employing formulas derived from Faraday's law, the Biot-Savart law and Ampere's law. An inductor serves its most common purpose in circuits to store energy. Inductance occurs due to a magnetic field that forms around a current-carrying conductor. When an electric current flows through the conductor, magnetic flux proportional to the current is created. A change in the current results in a change in the magnetic flux that generates an electromotive force that acts against the change. Inductance is a measure of the amount of this force (EMF) generated for each unit change in current. There are many parameters that govern the inductance of a given inductor—such as the material wrapped around the inductance, the type of conductor, number of windings or turns, as well as the size of each turn.

An inductor is basically a coil of conducting material, typically copper wire that is wrapped around some sort of core. Inductors come in many different shapes and sizes; a circular wire loop, coaxial cable, air-cored solenoid, and ferromagnetic cored toroids are just some examples. For our purposes, we chose to create a ferromagnetic toroid using a toroid obtained from the Atwater Kent ECE shop and a length of copper wire. The core chosen was of ferromagnetic material with a radius, *a* (from center to the middle of the core) of 20mm, outer radius, *b* of 38mm, and height, *c* of 29mm. The inductance is given by

$$L = \frac{\mu N^2 c}{2\pi} ln \frac{a}{b}$$

where  $\mu$  is the permeability of the core, and N is the number of turns of the wire around the toroid. However  $\mu$  is not known initially. A different method of obtaining the inductance is necessary.