### Florida International University FIU Digital Commons

FIU Electronic Theses and Dissertations

University Graduate School

3-21-2018

### The Thermal-Constrained Real-Time Systems Design on Multi-Core Platforms -- An Analytical Approach

**SHI SHA**

Florida International University, ssha001@fiu.edu

**DOI:** 10.25148/etd.FIDC004089

Follow this and additional works at: https://digitalcommons.fiu.edu/etd

Part of the Computer and Systems Architecture Commons, Hardware Systems Commons, Other Computer Engineering Commons, and the Power and Energy Commons

#### Recommended Citation

SHA, SHI, "The Thermal-Constrained Real-Time Systems Design on Multi-Core Platforms -- An Analytical Approach" (2018). FIU Electronic Theses and Dissertations. 3713.

https://digitalcommons.fiu.edu/etd/3713

This work is brought to you for free and open access by the University Graduate School at FIU Digital Commons. It has been accepted for inclusion in FIU Electronic Theses and Dissertations by an authorized administrator of FIU Digital Commons. For more information, please contact dcc@fiu.edu.

#### FLORIDA INTERNATIONAL UNIVERSITY

Miami, Florida

## THE THERMAL-CONSTRAINED REAL-TIME SYSTEMS DESIGN ON MULTI-CORE PROCESSORS – AN ANALYTICAL APPROACH

A dissertation submitted in partial fulfillment of the requirements for the degree of  ${\color{blue} {\rm DOCTOR~OF~PHILOSOPHY}}$

in

ELECTRICAL ENGINEERING

by

Shi Sha

To: Dean John L. Volakis

College of Engineering and Computing

This dissertation, written by Shi Sha, and entitled The Thermal-Constrained Real-Time Systems Design on Multi-Core Processors – An Analytical Approach, having been approved in respect to style and intellectual content, is referred to you for judgment.

We have read this dissertation and recommend that it be approved.

| -                                        | Arif Selcuk Uluagac                                                               |

|------------------------------------------|-----------------------------------------------------------------------------------|

| -                                        | N :1 D.1                                                                          |

|                                          | Nezih Pala                                                                        |

| -                                        | Raju Rangaswami                                                                   |

| -                                        | Wujie Wen                                                                         |

| -                                        | Gang Quan, Major Professor                                                        |

| Date of Defense: March 21, 2018          |                                                                                   |

| The dissertation of Shi Sha is approved. |                                                                                   |

| _                                        |                                                                                   |

|                                          | Dean John L. Volakis<br>College of Engineering and Computing                      |

|                                          | Andrés G. Gil                                                                     |

| Vice President                           | for Research and Economic Development<br>I Dean of the University Graduate School |

Florida International University, 2018

© Copyright 2018 by Shi Sha All rights reserved.

#### **DEDICATION**

This dissertation is dedicated to my always encouraging, ever faithful parents and other family members. I also want to remember my grandparents. May you find peace and happiness in Paradise! Last but not least, I am grateful to my teachers, colleagues, friends, who assisted, advised and supported my research and efforts over the years.

#### ACKNOWLEDGMENTS

I wish to express my deepest appreciation to my major advisor, Dr. Gang Quan, who inspires and guides me by his encouragement, support and patience. His professional attitude and the passion to science and research have deeply impacted me.

I am grateful to all my Ph.D. committee members, Dr. Wujie Wen, Dr. Arif Selcuk Uluagac, Dr. Nezih Pala and Dr. Raju Rangaswami. Each of the members of my Dissertation Committee has provided me extensive personal and professional guidance and suggestions in improving the quality of this dissertation.

My Ph.D. research was supported in part by US National Science Foundation (NSF) grants CNS-0969013, CNS-0917021 and CNS-1018108.

#### ABSTRACT OF THE DISSERTATION

## THE THERMAL-CONSTRAINED REAL-TIME SYSTEMS DESIGN ON MULTI-CORE PROCESSORS – AN ANALYTICAL APPROACH

by

Shi Sha

Florida International University, 2018 Miami, Florida

Professor Gang Quan, Major Professor

Over the past decades, the shrinking transistor size, benefited from the advancement of IC technology, enabled more transistors to be integrated into an IC chip, to achieve higher and higher computing performances. However, the semiconductor industry is now reaching a saturation point of Moore's Law largely due to soaring power consumption and heat dissipation, among other factors. High chip temperature not only significantly increases packing/cooling cost, degrades system performance and reliability, but also increases the energy consumption and even damages the chip permanently. Although designing 2D and even 3D multi-core processors helps to lower the power/thermal barrier for single-core architectures by exploring the thread/process level parallelism, the higher power density and longer heat removal path has made the thermal problem substantially more challenging, surpassing the heat dissipation capability of traditional cooling mechanisms such as cooling fan, heat sink, heat spread, etc., in the design of new generations of computing systems. As a result, dynamic thermal management (DTM), i.e. to control the thermal behavior by dynamically varying computing performance and workload allocation on an IC chip, has been well-recognized as an effective strategy to deal with the thermal challenges.

Different from many existing DTM heuristics that are based on simple intuitions, we seek to address the thermal problems through a rigorous analytical approach, to achieve the high predictability requirement in real-time system design. In this regard, we have made a number of important contributions. First, we develop a series of lemmas and theorems that are general enough to uncover the fundamental principles and characteristics with regard to the thermal model, peak temperature identification and peak temperature reduction, which are key to thermal-constrained real-time computer system design. Second, we develop a design-time frequency and voltage oscillating approach on multi-core platforms, which can greatly enhance the system throughput and its service capacity. Third, different from the traditional workload balancing approach, we develop a thermal-balancing approach that can substantially improve the energy efficiency and task partitioning feasibility, especially when the system utilization is high or with a tight temperature constraint. The significance of our research is that, not only can our proposed algorithms on throughput maximization and energy conservation outperform existing work significantly as demonstrated in our extensive experimental results, the theoretical results in our research are very general and can greatly benefit other thermal-related research.

#### TABLE OF CONTENTS

| CHAPTER                                                                | PAGE |

|------------------------------------------------------------------------|------|

| 1. INTRODUCTION                                                        | 1    |

| 1.1 The Increasing Power Consumption and Power Density of IC Chips .   |      |

| 1.2 The Temperature Issue on Multi-Core Processors $\dots \dots \dots$ |      |

| 1.3 Research Problems and Our Contributions                            |      |

| 1.4 Structure of the Dissertation                                      | 10   |

| 2. BACKGROUND AND RELATED WORK                                         | 13   |

| 2.1 Real-Time Systems                                                  |      |

| 2.2 Power Consumption                                                  |      |

| 2.2.1 Dynamic Power Reduction                                          |      |

| 2.2.2 Leakage Power Reduction                                          |      |

| 2.3 Thermal Management                                                 |      |

| 2.3.1 The Need for Thermal Management                                  |      |

| 2.3.2 Related Works on Power and Thermal Management                    |      |

| 2.4 Summary                                                            | 23   |

| 3. FUNDAMENTALS ON MULTI-CORE THERMAL-AWARE REAL-TI                    | ME   |

| SCHEDULING                                                             | 24   |

| 3.1 Preliminaries                                                      |      |

| 3.1.1 System Model                                                     | 25   |

| 3.1.2 Thermal Model                                                    |      |

| 3.2 The Properties of the Thermal Model                                | 30   |

| 3.3 Peak Temperature Identification and Bounding                       |      |

| 3.3.1 Related Works                                                    |      |

| 3.3.2 Motivation Example                                               | 37   |

| 3.3.3 Bounding the Peak Temperature                                    |      |

| 3.4 Experimental Results                                               | 48   |

| 3.4.1 Properties of Step-Up Schedules                                  | 48   |

| 3.4.2 Bounding Peak Temperature using Step-Up Schedules                | 50   |

| 3.5 Summary                                                            | 52   |

| 4. PEAK TEMPERATURE MINIMIZATION AND THROUGHPUT MA                     | XI-  |

| MIZATION ON MULTI-CORE PLATFORMS                                       |      |

| 4.1 Related Work                                                       |      |

| 4.2 Peak Temperature Minimization and Throughput Maximization          |      |

| 4.2.1 Choose Two Neighboring Running Modes                             |      |

| 4.2.2 M-Oscillating Schedule on Multi-Core Platforms                   |      |

| 4.3 Throughput Maximization Using Frequency Oscillation                |      |

| 4.4 Experimental Results                                               |      |

| 4.4.1 Peak Temperature Minimization for m-Oscillating Schedule         |      |

| 4.4.2 Performance Comparison of Different Approaches and Speed Levels 81   |

|----------------------------------------------------------------------------|

| 4.4.3 Computation Time Comparison                                          |

| 4.5 Conclusions                                                            |

| 5. ENERGY REDUCTION ON MULTI-CORE PLATFORMS 86                             |

| 5.1 Related Works                                                          |

| 5.2 Preliminaries                                                          |

| 5.2.1 Power/Thermal Model                                                  |

| 5.2.2 Energy Model                                                         |

| 5.2.3 Problem Formulation                                                  |

| 5.3 Temperature-Constrained Energy Minimization on Multi-core Platforms 93 |

| 5.3.1 The Energy Consumption Lower Bound                                   |

| 5.3.2 The Leakage-Aware Load-Balancing Approach                            |

| 5.3.3 The Thermal-Balancing Approach                                       |

| 5.4 Task Partitioning via Bin Packing Approaches                           |

| 5.4.1 Task Partitioning by Variable-Sized Bin Packing Approach 101         |

| 5.4.2 The Enhanced Bin-Packing Method                                      |

| 5.5 Experimental Results                                                   |

| 5.5.1 Lower Bound of Energy Efficiency (WPJ) Comparison 108                |

| 5.5.2 The Feasibility Comparison for Different Heuristics                  |

| 5.5.3 The Computational Time Comparison                                    |

| 5.5.4 Energy Efficiency (WPJ) and Feasibility When Packing Tasks $114$     |

| 5.6 Conclusion                                                             |

| 6. CONCLUSIONS AND FUTURE WORK                                             |

| 6.1 Summary                                                                |

| 6.2 Future work                                                            |

| BIBLIOGRAPHY                                                               |

| VITA                                                                       |

|                                                                            |

#### LIST OF TABLES

| TAB | LE                                                                                                               | łΕ |

|-----|------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Summary of Notations                                                                                             | 25 |

| 3.2 | Motivation Example Task Sets                                                                                     | 37 |

| 3.3 | Different settings for testing peak temperature variations by different phases $(t_p = 6s)$ on a 3-core platform | 51 |

| 3.4 | Peak temperature variations (in °C) by different $m$ for case 1 of Table 3.3.                                    | 52 |

| 4.1 | Performance of different approaches                                                                              | 57 |

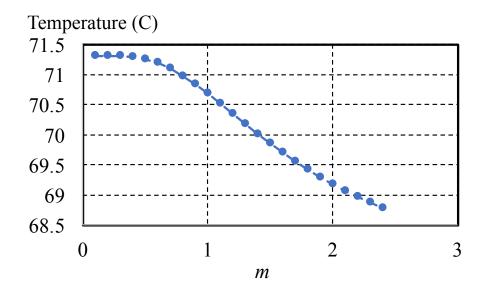

| 4.2 | Peak temperature $T_{peak}$ (°C) monotonically decreases as $m$                                                  | 77 |

| 4.3 | Different numbers of modes with different voltages                                                               | 81 |

| 4.4 | Computation time comparisons with different cores and voltage levels (Seconds)                                   | 85 |

| 5.1 | Computation time comparison (Seconds)                                                                            | 13 |

#### LIST OF FIGURES

| FIGU | JRE PAG                                                                                                                                                                                                                                                                                                      | GE |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

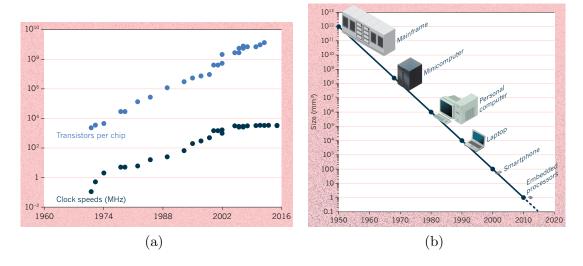

| 1.1  | (a) The "Moore's Law" doubles transistor per chip roughly every two years. The chip's clock speed also increases until 2004 when the speed scaling meets the barrier of the thermal limit. (b) As the IC power and size scaling, each generation of new electronic device emerges about every 10 years. [96] | 4  |

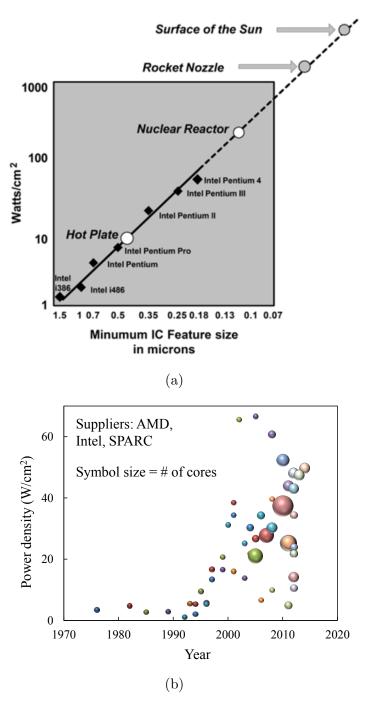

| 1.2  | (a) The power density increases exponentially with the IC feature size and its is comparable with a nuclear reaction. [Source: Intel Corp.] (b) Emerging new electronic devices results in power density increases chronologically [21]                                                                      | 11 |

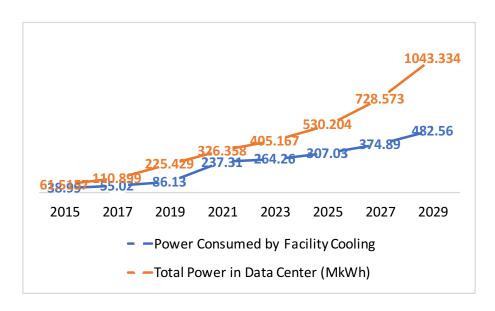

| 1.3  | A global view of cooling power v.s. total power in the data center industry [31]                                                                                                                                                                                                                             | 12 |

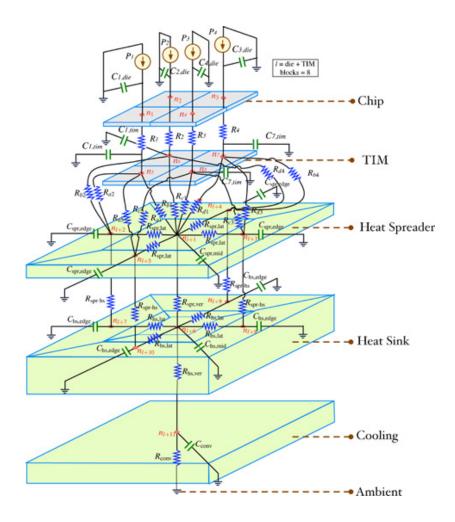

| 3.1  | A HotSpot Thermal Model for a 4-core platform [55]. (Our model adds lateral thermal resistors on the chip level for core-to-core heat transfer.)                                                                                                                                                             | 27 |

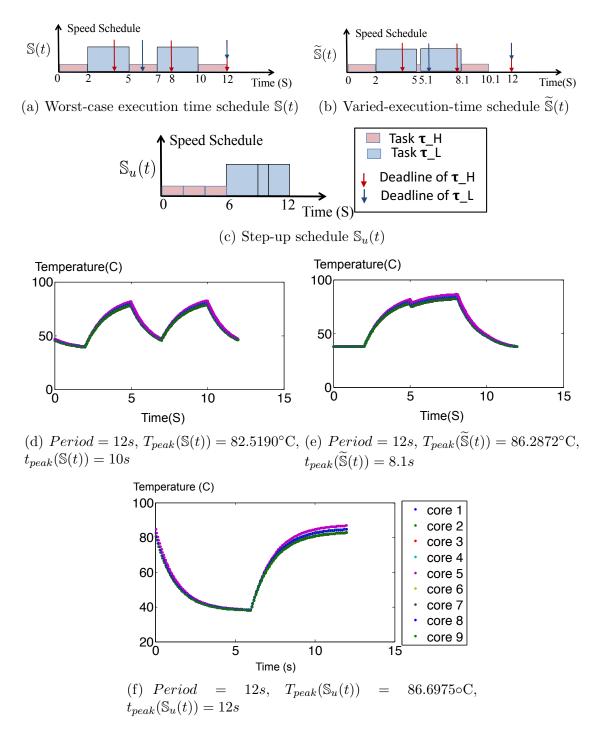

| 3.2  | Temperature trace of different schedules on a 9-core platform                                                                                                                                                                                                                                                | 38 |

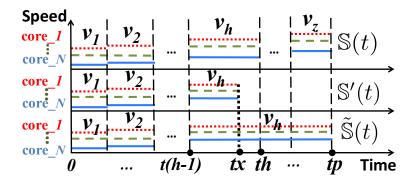

| 3.3  | Step up schedule proof illustration for Theorem 3.3.3                                                                                                                                                                                                                                                        | 42 |

| 3.4  | Lemma 3.3.5 illustration                                                                                                                                                                                                                                                                                     | 44 |

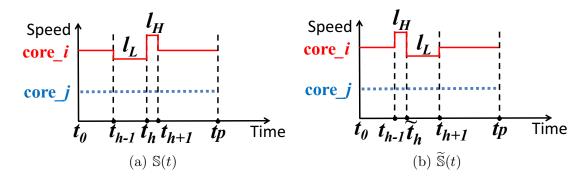

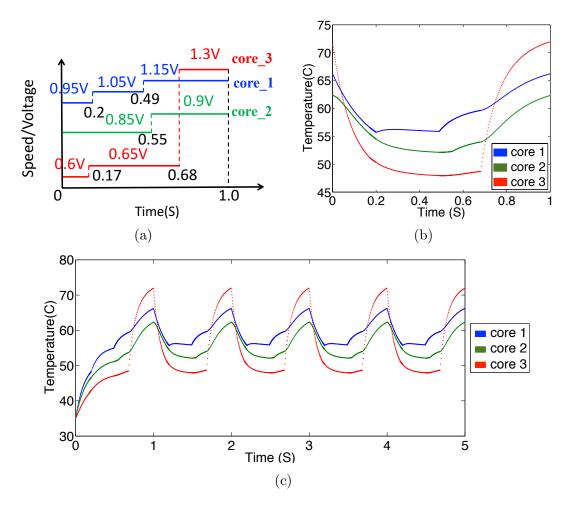

| 3.5  | (a) Speed schedule on a 3-core platform. (b) Temperature trace in the stable status. (c) Temperature trace starting from $T_{amb}=35^{\circ}{\rm C.}$                                                                                                                                                        | 49 |

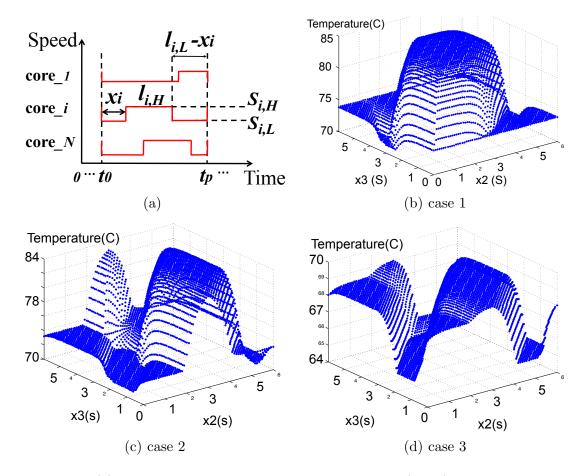

| 3.6  | (a) An N-core schedule with shifting <i>phase</i> . (b,c,d) Peak temperature changes differently according to the <i>phase</i> $(x_i)$ with settings in Table 3.3                                                                                                                                            | 50 |

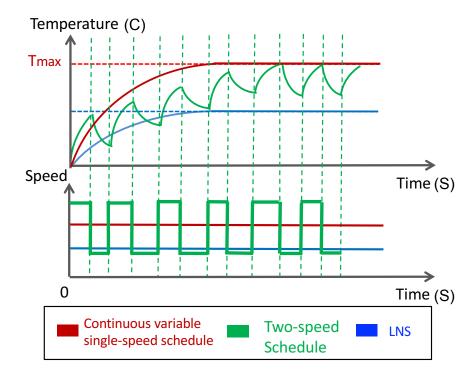

| 4.1  | Illustration of temperature traces of different approaches                                                                                                                                                                                                                                                   | 58 |

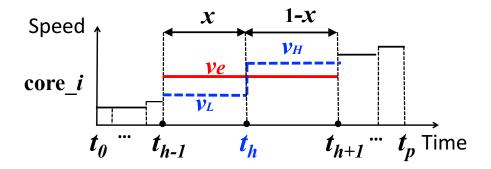

| 4.2  | Illustration for Theorem 4.2.1                                                                                                                                                                                                                                                                               | 59 |

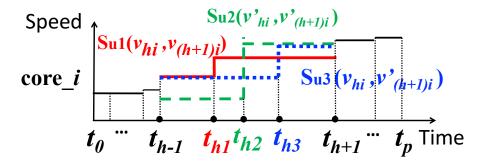

| 4.3  | Illustration for Theorem 4.2.2                                                                                                                                                                                                                                                                               | 62 |

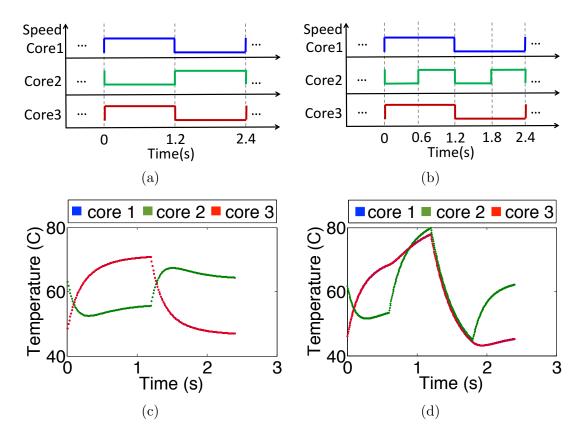

| 4.4  | (a) Core 1 and core 3 run at 1.3V within [0,1.2]s and 0.6V within [1.2,2.4]s; Core 2 runs at 0.6V within [0,1.2]s and 1.3V within [1.2,2.4]s. (b) Core 2 doubles its oscillating frequency from schedule in Fig.4.4(a). (c) Stable status temperature trace for schedule in Fig. 4.4(b)                      | 64 |

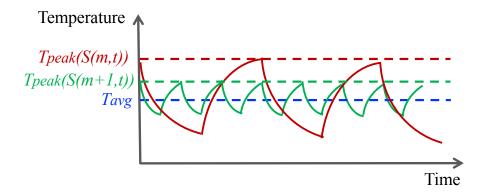

| 4.5  | The peak temperature monotonically decreases with $m$                                                                                                                                                                                                                                                        | 65 |

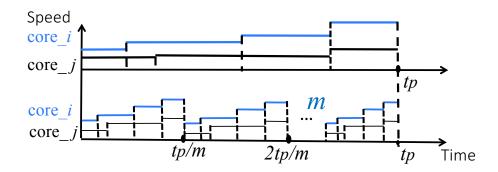

| 4.6  | Illustration of m-Oscillating schedule                                                                                                                                                                                                                                                                       | 65 |

| 4.7  | Illustration for Theorem 4.2.5 Proof                                                                                                                                                                                                                                                                         | 67 |

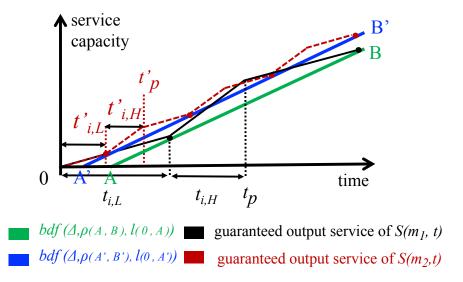

| 4.8  | Real-time calculus illustration of Theorem 4.2.7: the bounded-delay approximation shows a higher service capacity of $\mathbb{S}(m_2, t)$ than $\mathbb{S}(m_1, t)$ , if $m_2 \geq m_1 > 0$                                                  | 72  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

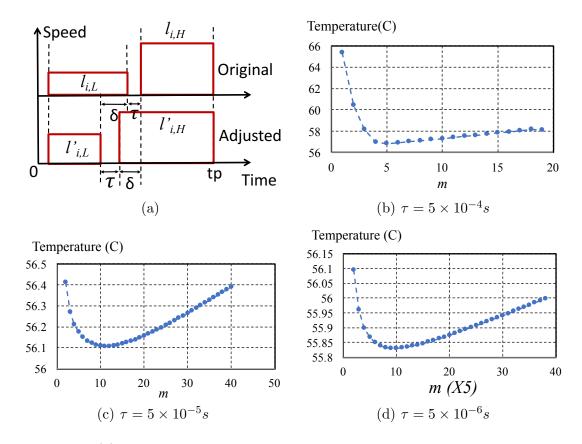

| 4.9  | (a) Speed adjustment on $core_i$ when consider speed transition overhead. (b)(c)(d) Peak temperature varies differently when transition overhead $\tau$ s are different                                                                      | 78  |

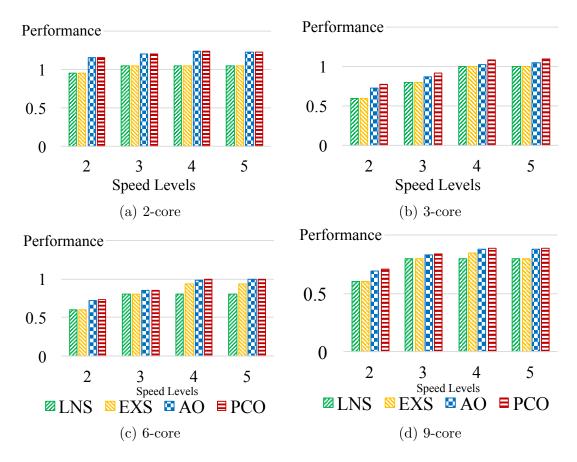

| 4.10 | Performance comparisons with different numbers of cores and voltage levels, when $T_{max} = 55 ^{\circ}\text{C.}$                                                                                                                            | 79  |

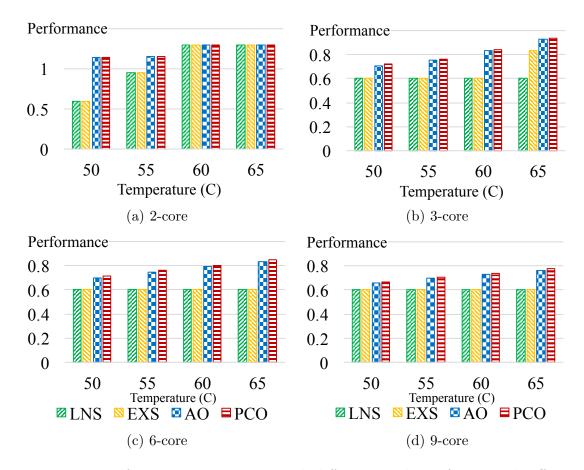

| 4.11 | Performance comparisons with different numbers of cores and different $T_{max}$ on 2 speed-level platforms                                                                                                                                   | 80  |

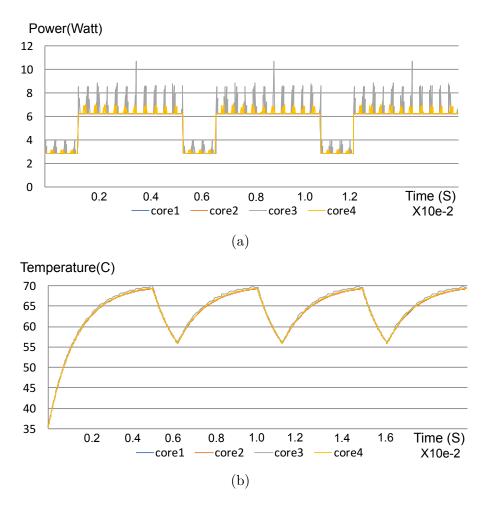

| 4.12 | AO method on a 4-core platform with $T_{peak}=70^{\circ}\mathrm{C}$ (a) Power trace (b) Temperature trace                                                                                                                                    | 83  |

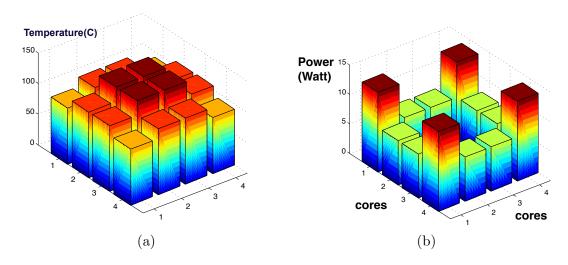

| 5.1  | (a) Different cores exhibit different stable state temperature, when all cores are with the same amount of load. (b) Different cores have different maximal allowed power, when all the cores reach the temperature threshold contemporarily | 96  |

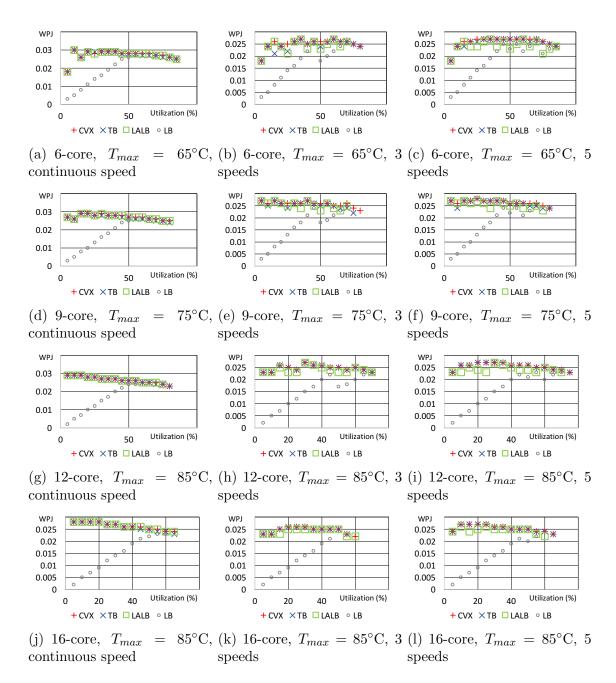

| 5.2  | WPJ comparison for different core configurations and different number of available speed levels                                                                                                                                              | 109 |

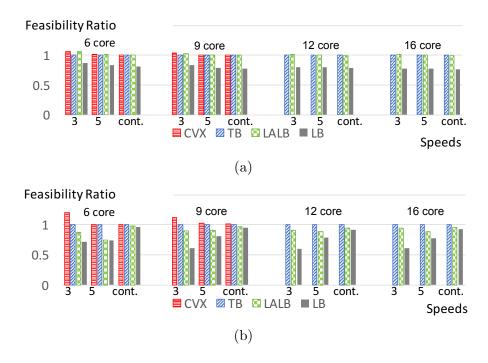

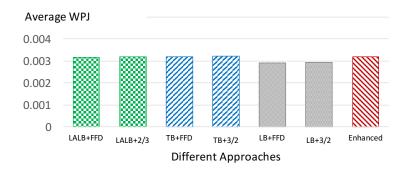

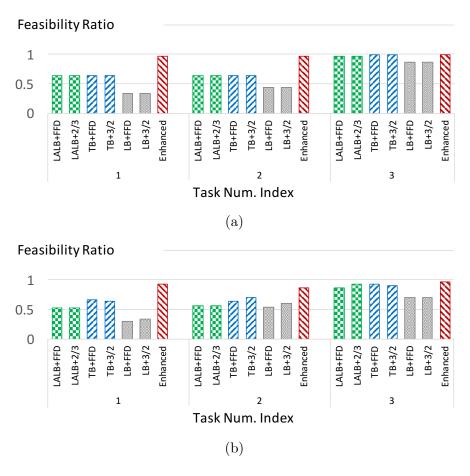

| 5.3  | Feasibility comparison when system utilization lies (a) between $0\%$ and $50\%$ ; (b) between $50\%$ and $100\%$                                                                                                                            | 112 |

| 5.4  | Average Energy Efficiency (WPJ) Comparison on large volumn of random cases                                                                                                                                                                   | 115 |

| 5.5  | Feasibility comparison when packing actual tasks for system utilization lies (a) between $0\%$ and $50\%$ ; (b) between $50\%$ and $100\%$                                                                                                   | 116 |

#### CHAPTER 1

#### INTRODUCTION

As a broad range of innovative applications emerge quickly, such as intelligent transportation systems, Internet of Things (IoT), artificial intelligence (AI) and beyond, the computational demands grow quickly. The explosive increments of data volume and complex workloads also urge the IC industry to create the next computing performance breakthrough in high-performance computing systems (HPC). Nowadays, real-time computing (RTC) has been widely adopted in scientific and industrial areas, e.g. real-time traffic control and medical device operations, etc. A real-time computing system with strict timing constraints in many mission-critical applications also call for guaranteed computing/service capacity, and should be robust enough to cope with unprecedented events and dynamic environments. All these drastically increased computational demands are driving computing systems to achieve a higher and higher computational capability, facing challenges from software complexity, system expansion, and hardware integration, etc.

To achieve a higher performance, the advancement of the IC technology enables more transistors to be integrated into a chip by shrinking the transistor size following the so-called "Moore's Law," i.e. the number of transistors in an IC doubles approximately every two years. Consequently, the power consumption on chip is increasing with the transistor count. Since increasing power consumption can directly translate to the raising temperature, both power and heat dissipations are becoming major obstacles in technology scaling. High temperature can degrade system performance [124], reliability [91], and even damage the chip permanently. For example, it has been reported that every  $10-15^{\circ}$ C temperature increment could result in a 50% reduction in the device's lifespan [140] and triple the hardware failure rate [161].

To alleviate the power/thermal barrier, multi-core processors, by taking advantage of thread or process-level parallelism, have become one of the promising solutions to achieve a better computational efficiency with a slower pace of power increment than single-core architecture. However, as the increasing number of cores continuously push the power density to a higher and higher level, the runtime thermal environment deteriorates, which becomes worse on 3D architectures [84]. The 3D IC technology stacks layers of cores vertically on top of each other to take advantage of shorter wires, higher data throughput, and larger memory bandwidth in comparison with 2D design [89]. However, the higher power density and longer heat removal path has made the thermal problem substantially more challenging than its 2D counterpart [85]. The thermal problem is a critical issue that limits the development of high-performance computing systems [57].

To mitigate the thermal crisis, some mechanical solutions have been explored, such as building heat sinks, heat spreaders, cooling fans or other advanced cooling mechanisms (e.g. embedded micro-channel liquid cooling on 3D processors [141] or using phase change coolant [29]). However, designing such a heat dissipation package is uneconomical if not infeasible [131], and it is unsuitable for hand-held devices [119]. More important, solely relying on the heat dissipation package cannot guarantee the temperature constraints. The violations of the temperature threshold may degrade the system throughput performance and cause real-time violations. Thus, it is not sufficient to be utilized in the real-time computing systems design. To this end, a variety of research efforts have been applied on different abstraction levels, including circuit-level, logic-level, architectural-level and the system-level.

Our research employs real-time scheduling techniques on the system level. In particular, by properly controlling the computational behavior by dynamically varying computing performance and workload distribution on an IC chip, different designoptimization goals can be achieved under the thermal constraint, e.g. energy reduction, reliability enhancement and throughput maximization, etc. In what follows, we first introduce the crisis caused by soaring power and energy consumption in modern computing systems design. We then discuss the opportunities and challenges in addressing the thermal/power issue. Next, we introduce our research problem and our contributions. At last, we describe the organization of the dissertation.

# 1.1 The Increasing Power Consumption and Power Density of IC Chips

In the era of awaiting the ultra-low power of superconducting electronics for Quantum Computing, the pace of pursuing the next generation of high-performance devices never stops. Beyond the conventional technologies and architectures, on one hand, portable and implanted electronic devices, e.g. smartphones and user terminal of Internet of Things (IoT), call for a self-contained functionality within the scope of a small carbon area. On the other hand, high-performance computing devices, e.g. servers used in data centers, drive stationary computers to improve their performances to the next higher level of realizing supercomputing.

Both increasing the computational capability and decreasing the chip sizes, drive the semiconductor industry to keep on increasing the transistor count and transistor density. For example, cellphone application processors have increased the transistor count from 1 Billion in A5 to 2 Billion for A6 to 3 Billion for A6X. It is projected that the upcoming A9 will range from 2.7 to 4.5 Billion [31]. Although the shrinking feature sizes and FinFET technique can realize faster switching and lower the minimal power consumption of transistor operation, the chipset power and power density are still rapidly escalating to silicon limitations.

Figure 1.1: (a) The "Moore's Law" doubles transistor per chip roughly every two years. The chip's clock speed also increases until 2004 when the speed scaling meets the barrier of the thermal limit. (b) As the IC power and size scaling, each generation of new electronic device emerges about every 10 years. [96]

Instead of integrating more transistors and increasing the running frequency on a monolithic single-core to pursue a higher performance, designing multi-core and many-core platforms, by exploring the thread/process level parallelism, help to lower the frequency and power consumption. The multi-core and many-core architecture approaches the "saturation point" of Moore's Law in a slower pace than single-core architecture. For example, the parallel execution scheme lowered the frequency scaling from 41% per year in 2001 to nearly 4% per year in 2011 [72], which substantially mitigated the exponential increments of power consumptions (in Figure 1.1(a)). However, the fast scaling of the processing core count and shrinking size (in Figure 1.1(b)) lead to soaring runtime temperature, which negatively impact system performance, reliability and increase the packaging and cooling cost. It is reported that near the year of 2029, the number of cores used in a data center can reach 10602, which is 30-fold of year 2015 [31]. To this end, the effective power and thermal-aware design methodologies are urgently demanded on multi-core platforms.

#### 1.2 The Temperature Issue on Multi-Core Processors

In a multi-core regime, leveraging the system integration is widely adopted to achieve a higher performance, but building a larger SoCs/NoCs with more processing cores results in thermal issues. For example, the emerging 3D multi-core architecture is recognized as one of the most promising solutions to achieve less delay and lower power consumptions by stacking layers of cores vertically on top of each other to take advantage of shorter wires, higher data throughput, and larger memory bandwidth in comparison with 2D design. However, the higher power density and longer heat removal path made the thermal problem substantially more challenging than a 2D design. As reported in [84], the vertical heat transfer rate of a 3D processor can be 16× that of the lateral one and the longer heat removal path in a 3D architecture may increase its core temperature by  $17^{\circ}\text{C} - 20^{\circ}\text{C}$  compared with its 2D counterpart. As shown in Figure 1.2, the power density beyond the 100nm technology node is comparable with a nuclear reactor, and the power density of future electronics is still increasing. As multi-/many-core systems continuously grow to the level that is limited by the first advent of chip power budget or temperature limit, "dark/grey silicon" leaves a fraction of on-chip processing cores inactive. Then, the resource utilization is developed upon building an effective run-time workload mapping strategy, through a different patterning approach to seek a proper subgroup of active cores, such that thermal and power budget can be fully exploited. As reported in [37], at 22 nm technology node, 21% of a fixed-size chip must be powered off, and at 8 nm, this number grows to more than 50%. Essentially, temperature has become a first-class design constraint in modern computing systems design.

Besides the thermal crisis resulting from soaring transistor/power densities, the thermal management on multi-core processors is also challenged by non-uniformly distributed workload in both temporal and spatial dimensions. For example, on an Intel Xeon E5-2699 v3 CPU [12], the intra-die temperature difference can be up to 10°C and 24°C under balanced and unbalanced workload scenarios, respectively. The high local heat fluxes (known as "hotspot") on multi-core platforms make the thermal management more complicated and urgent, because local hotspots may trigger the self-protection schemes and cause an unpredicted shut down of the processor. Thermal crisis has become one of the primary concerns in modern microprocessor design, because high temperature can substantially degrade system performance [124], reliability [91], and even damage the chip permanently. Every year, a tremendous amount of cooling cost has been spent in the IT industry. For example, as reported in ITRS2015 [31], the power consumption of data centers enters hundreds of Megawatts range. The global cooling power demands for the data center industry raise from 55.02 MkWh of 2017 to 482.56 MkWh around 2029, which takes averagely 55.6% total power in the data center industry in the 10-year holistic view, with the peak percentage of 72.7% at 2021.

To protect the hardware from overheating hazards, modern CPUs are featured with digital thermal sensors to monitor the temperature fluctuations. If the chip temperature exceeds the pre-defined temperature thresholds, it will trigger the automatic shut down scheme, which adversely degrades the system performances. To address the thermal crisis, some mechanical solutions have been explored, such as building heat sinks, heat spreaders, cooling fans or other advanced cooling mechanisms. For example, a 3D liquid tree-like cooling system has been proved to be favorable for minimizing the pumping power in [23]. A channel width modulation methodology has been proposed to enhance the cooling energy efficiency in [116]. The two-phase 3D liquid cooling systems has been studied in [29, 107]. However, such mechanical cooling solutions are expensive and not suitable for the mobile

devices. More important, the mechanical cooling methods cannot guarantee the runtime temperature staying in a safe range.

To manage the runtime temperature and improve the thermal profile, Dynamic Thermal Management (DTM) is also developed on the system-level, which can be realized by adjusting the processing speeds using dynamic voltage/frequency scaling (DVFS) or turning off the unused cores using dynamic power management (DPM). Significant work has been done for DTM strategies, but many of them are based on simple heuristics or intuitions, such as thermal-balancing [100], "hot-and-cold" job swapping [115], allocating hot tasks to cores closer to the heat sink [84], etc. Some other works utilize reactive approaches to dynamically adjust the runtime system settings for upcoming system loads [44, 53, 46]. Although these approaches may work well for some application cases, they either lack of peak temperature guarantee or cannot ensure system performances. Thus, these methods cannot be safely utilized in the real-time systems design.

In this research, we adopt the real-time scheduling methodology and use a proactive DTM approach to guarantee the pre-defined peak temperature constraint. Meanwhile, we also aim to achieve different design optimization goals and ensure the required throughput under the peak temperature constraint at the same time. Furthermore, our rigorous analytical approach intends to have a better understanding of the interplay among different design factors/constraints, which helps to develop more effective thermal management policies.

#### 1.3 Research Problems and Our Contributions

Due to both economic and physical challenges in IC design, power and thermal issues on multi-core platforms call for effective and cost-efficient solutions in devel-

oping next-generation computing systems. In this dissertation, we study the realtime computing system design with power/thermal-awareness. In particular, our research aims to develop a variety of design optimization algorithms (e.g. throughput maximization, energy reduction, peak temperature minimization, etc.) based on the state-of-the-art computer architecture. The research incorporates system-level DTM techniques and takes leakage-temperature dependency and multi-core thermal interference into account. Different from many existing DTM heuristics that are based on simple intuitions, we seek to address the thermal-related optimization problems through a rigorous analytical approach, which intends to understand the fundamental thermal/power-aware design principles. The significance of our research is that, our design emphasizes the guaranteed throughput performance and response time in developing different optimization strategies, which can be safely employed in the real-time system design. Meanwhile, not only our proposed algorithms can outperform existing work significantly as demonstrated in the extensive experimental results, but also the theoretical results in our research are very general and can greatly benefit other thermal-related research.

The contributions of this dissertation are summarized as follows:

1. We analytically prove a series of fundamental principles in the forms of theorems and lemmas for thermal modeling, peak temperature identification and peak temperature reduction, which are key to thermal-constrained computer system design, that based on the well-known multi-core RC-thermal model, which accounts for the temperature-leakage dependency and multi-core heat transfer. These principles are general enough to be applied on 2D and 3D multi-core platforms, and form the theoretical basis for a more rigorous analytical study, which can be used for other thermal-related problems.

- 2. Based on the thermal characteristics on multi-core platforms, we analytically study the throughput maximization problem under the peak temperature constraints. To take advantage of thermal heterogeneity of different cores for performance improvement, we propose to run each core with multiple speed levels and develop a schedule based on two novel concepts, i.e. the step-up schedule and the m-Oscillating schedule, for multi-core platforms. The proposed methodology can ensure the peak temperature guarantee with a significant improvement in computing throughput, up to 89% with an average improvement of 11%. Meanwhile, the computational time reduces orders of magnitude compared to the traditional exhaustive search-based approach.

- 3. Although energy minimization is closely related to temperature reduction, the most energy efficient method may not be the most effective one to meet the temperature constraints, and vice versa. We then study the problem of how to partition periodic hard real-time tasks on a multi-core platform to maximize the overall energy efficiency under a peak temperature constraint. Different from the traditional load-balancing approach, we use a thermal-balancing approach to improve the overall system energy efficiency, especially when the temperature constraints are tight. We further identify the lower bound for energy consumption by this approach, and then transform the task partitioning problem to a variable sized bin packing problem. We further use an enhanced algorithm to optimize the task partitioning results. Our simulation results show that the proposed thermal-balancing approach can greatly improve the energy efficiency and task partitioning feasibility for real-time systems with high system utilizations and tight temperature constraints.

#### 1.4 Structure of the Dissertation

The rest of this dissertation is organized as follows. In Chapter 2, we introduce the pertinent background to this dissertation and discuss existing works that are closely related to our research. In Chapter 3, we formally prove a series of thermal properties on multi-core platforms and study a temperature bounding method, which overturns the traditional peak temperature identification methods that use worst-case execution time to compute peak temperature directly from a given schedule. In Chapter 4, we focus on the throughput maximization problem of multi-core platforms and study a frequency oscillating methodology to fully use the "headroom" of the temperature threshold and enhance the throughput performance and service capability. In Chapter 5, we investigate how to partition periodic hard real-time tasks on a multi-core platform to maximize the overall energy efficiency under a peak temperature constraint. Finally, in Chapter 6, we conclude this dissertation and discuss possible future works.

Figure 1.2: (a) The power density increases exponentially with the IC feature size and its is comparable with a nuclear reaction. [Source: Intel Corp.] (b) Emerging new electronic devices results in power density increases chronologically [21]

Figure 1.3: A global view of cooling power v.s. total power in the data center industry [31]

#### CHAPTER 2

#### BACKGROUND AND RELATED WORK

This chapter covers the background of this research. We first introduce several important concepts on power/energy consumption commonly used in IC design. Then, we introduce several thermal management techniques at different design stages. We further conduct a more specific survey on power, thermal and energy-aware scheduling techniques, which are closely related to our research topic.

#### 2.1 Real-Time Systems

Real-time systems are widely used in the computing systems design, e.g. multimedia systems, embedded automotive electronics, etc.. In a real-time system, the correctness of the system behavior depends not only on the logical results of the computations, but also on the physical instant at which these results are produced [35]. The real-time systems adjust the operating state as a function of physical time. The instant that the result is required to be delivered is called deadline.

Real-time systems can be largely categorized into hard real-time and soft real-time systems. Hard real-time's response time requirement is firm and the violation of such type of deadline can result in a catastrophe. In contrast, a soft real-time system, e.g. multimedia or online reserving systems, is used in non-critical situations that the deadline is met at the best effort. Missing deadline only degrades the quality of service (QoS).

Further, hard real-time scheduling can be categorized into two types: *static* and *dynamic*. The static scheduling makes a decision at the compile time according to the tasks' parameters, e.g. execution time, precedence, deadlines, etc. Since the schedule is generated off-line, static scheduling may tolerate a higher computational

cost. In contrast, the dynamic scheduling makes the decision at the runtime. Although it is more flexible and adaptive to different workload scenarios, creating a runtime schedule steals the computational resources and may cause a large overhead.

There are several uniprocessor real-time scheduling policies. For example, earliest deadline first (EDF) policy always assign the highest priority to the task with the nearest current deadline. In addition, the EDF algorithm can achieve 100% utilization [87]. Rate monotonic (RM) assign the highest execution priority to the task with the shortest period. RM has been proved that a feasible schedule can always be found under the utilizations of ln2 (69.3%) [48].

On multi-core platform, the traditional scheduling policies for uniprocessors, e.g. EDF and RM, may not always lead to the best scheduling results. As the design space becomes larger, judiciously considering the utilization trade-offs that exists in multi-core systems are necessary. For example, according to the degree of allowed task migration, global schedule store all the ready tasks in a single priority-ordered queue and execute the highest priority one in sequence. In contrast, the partitioning approach allows each task only assign to one dedicated core, and join the task ready queue specified on this core. The research shows that some "middle approach" of a combination of global and partitioning methods may be a better choice on multi-core platforms [17].

Real-time has also been been applied in other system settings and architectures. For example, in a distributed real-time systems (DRTS), improving the schedulability by assigning local optimal end-to-end deadline has been explored in [59]. For discrete-event systems, the real-time calculus studied the temporal properties on queuing theory to provide service for incoming task requests [134].

#### 2.2 Power Consumption

In this section, we first introduce the sources of power consumption in digital integrated circuits. Then, we discuss a number of existing power reduction techniques at the system level. The total power consumption in CMOS digital ICs consists of dynamic power and static power.

$$P = P_{dun} + P_{leak}, (2.1)$$

#### 2.2.1 Dynamic Power Reduction

The dynamic power closely relates to the switching activities of the transistor, which is a quadratic function of supply voltage and proportional to the frequency.

$$P_{dyn} = Cv^2 f, (2.2)$$

where C is the equivalent parasitic capacitance. Term v and f are the supply voltage and clock frequency (execution speed), respectively. Modern processors are usually featured with several discrete running modes and for each mode  $v \propto f$ . Thus, dynamic power can be simplified as

$$P_{dyn} = \gamma(v) \cdot v^3, \tag{2.3}$$

where  $\gamma$  is a constant for different running modes.

There are a number of system-level techniques and multi-core designs used to minimize the active power consumption [15]. For example,

**Clock Gating** is selectively shutting off the clock for a circuit to prevent any toggle activity of the clocks or registers to reduce the power dissipation.

Dynamic Voltage and Frequency Scaling (DVFS) is to exploit the opportunity to scale down the voltage and frequency for power saving, when performance requirements can be satisfied in a low loading condition.

- Voltage Island is to realize "Multi-Supply Voltage" (MSV) techniques, that can reduce power consumption of SoCs, when not requiring all blocks to operate at maximum speeds at all times.

- On-Die Voltage Regulator provides a faster response than off-chip modules for adjusting the voltage and current supply in different active states.

- **3D-IC** utilizes Through Silicon Via (TSV) to connect several layers of processors and/or memories over a silicon interposer, which provide a low capacitance signal interconnect between die, thus reducing the I/O active power.

Since total power is a combination of dynamic power and leakage power. In what follows, we introduce the fundamentals for leakage power as well as its optimization strategies.

#### 2.2.2 Leakage Power Reduction

The leakage power, also called *static power* consumption, is caused by a small amount of current flow from power to the ground. The leakage power can be formulated as [86]

$$P_{leak} = N_{oate} \cdot I_{leak} \cdot v_{dd}, \tag{2.4}$$

where  $N_{gate}$  represents the number of gates,  $v_{dd}$  is the voltage level, and  $I_{leak}$  is the leakage current.  $I_{leak}$  varies with both temperature and supply voltage and can be calculated by a circuit-level non-linear and high-order equation. Since leakage current depends on both supply voltage and temperature [10], for system-level analysis with a tolerable complexity, leakage power on the system-level can be approximated as

$$P_{leak} = \alpha(v) + \beta T(t), \tag{2.5}$$

where  $\alpha$  is a constant for different running modes. T(t) is the temperature at time t.  $\beta$  is a constant. Further, the leakage and temperature correlation can be captured by a piece-wise linear function [64], with an average of 0.3% derivation from the circuit level formulation [153, 86]. Some existing static power saving strategies are listed as below [15].

**Power Gating** saves leakage power by shutting off the current to the blocks of the circuit that are standby. However, power gating needs to be applied with caution, because it causes more time delay than *clock gating*.

Multi-Threshold CMOS reduces leakage power by swapping of nominal threshold voltage gates with higher threshold voltage gates. In CMOS the subthreshold leakage is inversely proportional to the threshold voltage. Careful trade-off analysis needs to be done to achieve optimal leakage savings and mitigate delay effects.

Active Back-Bias is an approach that increases the bias voltage of the substrate nodes in CMOS gates to reduce the leakage current. This biasing technique essentially increases the threshold voltage of a unit or the entire chip during standby modes, hence decreasing the leakage power.

Some other techniques are exploit for power saving purpose. For example, as the feature size continues to shrink in each technology node, the voltage scaling approaches a threshold that dynamic and leakage power has a trade-off around the threshold voltage  $(V_t)$ . The optimum operating point is usually slightly above  $V_t$  and is called the near-threshold operating point.

#### 2.3 Thermal Management

In previous section, we introduced that the total power in digital ICs is a combination of dynamic and leakage power consumption with a brief introduction of their optimization methodologies. Since high power consumption leads to the high temperature directly, thermal problem becomes one of the first class constraints in computing systems design. In this section, we first show thermal management is an indispensable part in computing systems design, followed by thermal/power-related works.

#### 2.3.1 The Need for Thermal Management

Temperature, a long-lasting concern, is rooted in every stage of IC design and penetrates to every corner of human lives. For large-scale computing infrastructure, e.g. data centers and servers, the advancement of thermal management saves a tremendous cooling cost globally each year, and it is also an effective way to reduce the environmental impact for green computing purpose. For stationary computers, e.g. desktop or laptop computers, the application driven factors, e.g. internet surfing, video streaming and gaming, encourage IC industry to develop more aggressive thermal control methodologies to meet the application market needs as well as user satisfactory. For portable devices, e.g. mobile phones, implanted electronics and user terminals of IoT, the ultra-low-power design requires effective thermal control strategies either because a thermal-sensitive environment, or due to power/energy concern. For example, every 1°C of temperature increment of implanted devices may cause permanent tissue change. The mobile phone and tablets also need to consider the heat dissipation coming from the battery discharge along with the heat

generated from mobile computing itself; meanwhile, these portable devices need to save the thermal-related leakage power to maintain the battery mission cycle.

However, the soaring power density along with the uncertainty of the work-load, the temporal and spacial non-uniformity of power distribution and the large variation of power dissipations among different applications challenge the thermal controllability in modern computing systems design at the same time. In all perspectives, the research to rethink and explore different ways to improve the effectiveness of the system resources with thermal awareness is indispensable in each design stage.

#### 2.3.2 Related Works on Power and Thermal Management

There have been extensive research efforts for thermal related optimizations on multi-core platforms, including throughput maximization (e.g. [145, 124, 40, 101]), power/energy reduction (e.g. [106, 157, 117]), peak temperature reduction (e.g. [84, 115, 156, 42]) and reliability enhancement (e.g. [138]), etc. Essentially, these works aim at optimizing the resource usage in design of high performance, low power/energy and highly reliable computing systems with chip temperature either as an optimization goal or a design constraint. Based on their approaches, the existing work can be largely categorized into the following three categories.

First, many existing researches are based on simple heuristic or intuitions. For example, for peak temperature minimization purpose, interleaving the hot/cool tasks in 3D platforms temporally and spatially is proposed in [84], properly assigning slacks to split hot tasks is proposed in [156] and assigning hot tasks to cool cores is proposed in [12]. However, in these approaches, to determine the accurate and strongly justifiable metrics to classify hot/cool tasks/cores can be difficult. In addition, without solid analytical analyses, to make other design tradeoffs in the

meantime, such as task migration overhead v.s. scheduling interval length can be challenging. Although these heuristic/intuition methods may work in some application scenarios, it becomes extremely difficult, if not impossible at all, to guarantee the system performance and design constraints such as timing and peak temperature.

Second, some other approaches resort to traditional control techniques or optimization methods, such as machine learning, mathematical programming, or metaheuristic searching methods, to deal with thermal issues. For example, using feedback control technique on multi-core platform, Fu et al. [44] proposed a framework that enforce the desired temperature and CPU utilization bounds of embedded realtime systems through DVFS. Hanumaiah et al. [53] developed a closed-loop controller to predict the desired voltage/frequency settings to achieve maximum energy efficiency without violating the thermal limitations. Xie et al. [147] developed a look-up table based DTM method on a thermal coupled processor/battery model, which considered the space limitation of mobile devices. Machine learning is also explored to learn and make predictions on temperature variations. For example, Ge et al. [46] proposed a machine learning technique to capture the correlation between temperature change and workload switching pattern, and, thus, choose the proper management policy considering performance-temperature tradeoff during runtime. These approaches help to uncover deeper rationales in temperature management better than simple intuitions. However, it is still difficult to employ these approaches to ensure strong guarantee to the temperature and other design constraints.

To this end, mathematical programming methods are also adopted to optimize resource allocation under temperature and other design constraints. For example, Wang et al. [145] proposed an integer linear programming-based approach (ILP) for throughput maximization on a temperature-constrained multi-core platform. Murali et al. [101] used a convex optimization method by a two-phase iterative approach to approximate the solution. When considering discrete processor speed levels, Hanumaiah et al. [56] formulated the task allocation and processor DVFS setting problem as a convex optimization problem to minimize the task completion time. Chantem et al. [19] proposed an optimal ILP method for thermal-aware task assignment and scheduling problem to minimize the peak temperature under a given workload. Singh et al. [129] used ILP methodology for an application-driven approach that considered the communication overhead of video streaming to minimize the peak temperature and energy contemporarily. These approaches based on mathematical programming usually can identify the optimal solution for the given problem and can guarantee that all constraints are satisfied. There are two major drawbacks of these approaches: (i) The solution itself, if it can be obtained, does not provide deep insight to the reasonings and rationales of the problems; (ii) The computational cost increases too fast and can be prohibitive as the system scale becomes larger.

To deal with the computational cost problem, many approaches used metaheuristic searching algorithms. For example, using genetic programming approach, Saha et al. [117] proposed to minimize the energy for periodic tasks under a peak temperature constraint on heterogeneous systems. Fan et al. [40] proposed a metaheuristic approach to boost system performance in a small interval by supplying additional power to the system without exceeding the temperature and power supply limit. For these approaches, to maintain a high quality of the result with a manageable computational cost can be a challenging issue. Also, it is difficult to employ these approaches to unveil the cause-and-effect relations within a complex system.

The third type of approaches (e.g. [42, 106, 124, 147, 130]) intend to ensure strong guarantee to thermal constraints based on formal and analytical thermal analysis, to uncover underlying correlations among different design parameters quantitatively and not qualitatively. This is particularly useful in design of real-time systems, where predictability is critical and complicated resource management policies (such as priority, preemption, resource sharing, etc) cannot be easily formulated in mathematical programming. For example, Fisher et al. [42] formulated a series of schedulability and feasibility conditions for an online thermal-aware global scheduling algorithm for sporadic task sets on homogeneous multi-core platforms. Pagani et al. [106] proposed a new multi-core power budget index, so called thermal safe power (TSP), which can guarantee peak temperature constraints and result in a safer and higher throughput capacity than traditional thermal design power (TDP). Sha et al. [124] proved a series of theorems for peak temperature identification, speed selection, oscillating frequency principles, and based on which, they presented a frequency oscillating method to maximize the throughput with a guaranteed peak temperature on a multi-core platform. To check the thermal-aware feasibility, Ahmed et al. [4] derived a series of necessary and sufficient conditions on a temperature-constrained platform, which considered the performance/temperature trade-off based on different topologies. Assisted with rigorous mathematical analysis, these approaches usually can achieve the goal of strong thermal guarantee without suffering from prohibitive computational cost in mathematical programming approach. Also they help to uncover fundamental principles for more efficient and effective thermal-aware design, which would be otherwise unavailable.

#### 2.4 Summary

In this section, we present the essential pertinent of our research and review some closely related works in the literature. We first introduce the basic concepts and different source of power consumption. Existing power reduction techniques are discussed. Then, we present the need for thermal management on multi-core platforms with an extensive literature review of current technologies. Based on the above discussions, we can see that thermal-aware scheduling under a variety of constraints still poses a tremendous challenge for both academia and industry. Studying the interplay of different design constraints in a comprehensive and systematic way is becoming more and more critical.

In this dissertation, the goal of our research is to develop effective and efficient scheduling methods on multi-core platform to provide deterministic guarantees of thermal constraints under different design objectives, e.g. energy reduction, peak temperature reduction and throughput maximization, etc. In the following chapters, i.e. Chapter 3, 4 and 5, we present our contributions on this subject. We then conclude this dissertation in Chapter 6.

#### CHAPTER 3

# FUNDAMENTALS ON MULTI-CORE THERMAL-AWARE REAL-TIME SCHEDULING

To study the power/thermal management on multi-core platform, the first priority is to build a better understanding of the thermal models, which helps to develop more effective thermal management policies. However, when considering the interdependency between the leakage power and temperature and core-to-core heat transfer, the thermal analysis on multi-core platform becomes substantially complex. To facilitate rigorous analytical thermal analysis, it is our intention to develop some general and provable principles/fundamentals on characteristics of heat dissipation for ease of formal verification and analysis in real-time system design.

The rest of this chapter is organized as follows. Section 3.1 introduces the preliminaries on system model and thermal model used in this research. Section 3.2 utilizes a series of provable lemmas and theorems to unveil the characteristics of the well-known RC-thermal model. Section 3.3 shows that directly using tasks' worst-case execution time to capture the peak temperature can be misleading. To this end, we introduce the new concept of worst-case execution time-based "step-up schedule" and show it can bound the peak temperature not only for an arbitrary real-time schedule with given worst-case execution time, but it is also effective when the schedule's actual execution time varies. Section 3.4 shows the experimental results and Section 3.5 concludes this chapter.

#### 3.1 Preliminaries

We present the models for our multi-core systems. The **bold characters** represent the vectors and matrices and non-bold characters are used for ordinary variables and coefficients. All the matrices/vectors/values are in the real number domain. The notations in Table 3.1 are used in the dissertation.

Table 3.1: Summary of Notations

| Symbol               | Meaning                                                                              |

|----------------------|--------------------------------------------------------------------------------------|

| $\mathbb{S}(t)$      | A periodic multi-core schedule;                                                      |

| $\mathbb{I}_q$       | The $q_{th}$ state interval in $\mathbb{S}(t)$ with time interval $[t_{q-1}, t_q]$ ; |

| $l_q$                | The interval length of $\mathbb{I}_q$ , i.e. $l_q = t_q - t_{q-1}$ ;                 |

| ${f T_0}$            | The starting temperatures;                                                           |

| $\mathbf{T}_{ss}(t)$ | The stable status temperatures at time $t$ ;                                         |

| $1_{N\times 1}$      | An $(N \times 1)$ matrix with all elements being 1;                                  |

| $0_{N\times 1}$      | An $(N \times 1)$ matrix with all elements being 0;                                  |

| $max(\mathbf{X})$    | Find the maximum scalar value from matrix/vector $\mathbf{X}$ ;                      |

| ~.                   |                                                                                      |

Given two matrices  $\mathbf{X}$  and  $\mathbf{Y}$  with the same dimensions (e.g.  $N_1 \times N_2$ ), operators >, <,  $\geq$  and  $\leq$  are defined as element-wise scalar comparisons. For example,  $\mathbf{X} \leq \mathbf{Y}$  means that  $X_{i,j} \leq Y_{i,j}$ ,  $\forall i \in [1, N_1]$  and  $\forall j \in [1, N_2]$ .

# 3.1.1 System Model

We consider a multi-core platform  $\mathfrak{N}$  contains  $N_c$  number of cores,  $\mathfrak{N} = \{core_{\kappa} : \kappa = 1, \dots, N_c\}$ . Each core is DVFS-independent. Also, each core has different running modes and each running mode is characterized by a pair of parameters (v, f), where v is the supply voltage and f is the working frequency  $(v \propto f)$ . For an inactive core, we assume v = f = 0. In this paper, for ease of presentation, we use supply voltage v to denote the processing speed (amount of work performed within a unit time) when there is no confusion.

As different cores may execute in different running modes at different times, a multi-core platform can be regarded as running on a sequence of scheduling intervals, in each of which each core runs only in a unique mode. We call such an interval, e.g.  $[t_{q-1}, t_q]$ , as a **state interval**.

Consider a multi-core periodic schedule  $\mathbb{S}(t) = \{\mathbb{I}_1, \dots, \mathbb{I}_z\}$ , where  $\mathbb{I}_q = [t_{q-1}, t_q]$ , the performance of the multi-core platform can be represented by the average completed workload on each core divided by the length of one hyper-period. The performance (THR) is

$$THR = \frac{\sum_{q=1}^{z} THR_q}{N \sum_{q=1}^{z} l_q} = \frac{\sum_{q=1}^{z} \sum_{i=1}^{N} f_{i,q} \cdot l_q}{N \sum_{q=1}^{z} l_q},$$

(3.1)

where  $f_{i,q}$  is the running frequency of the *i* th core within the *q* th state interval.  $l_q$  is the length of the *q* th state interval.

## 3.1.2 Thermal Model

The thermal model, similar to that in [138, 144, 52], is built upon the duality between heat transfer and electrical phenomena as an RC-lumped circuit. Specifically, the RC-model consists of three vertical, conductive layers for the die, heat spreader, and heat sink, and a fourth vertical, convective layer for the sink-to-air interface. Heat generated from the active silicon device layer is conducted through the silicon die to the thermal interface material, heat spreader and heat sink, then convectively removed to the ambient air [131].

The thermal nodes on die layers are *active* nodes, which represent the processing cores with non-zero power consumptions. In contrast, thermal nodes on other layers are called *inactive* nodes, since they do not consume power. Assume the thermal nodes in the system are  $\Pi = \{\Pi_i, i = 1, \dots, N\}$ , in which the first  $N_c$  elements represent the active nodes. Let  $\Pi_i \in \Pi_{HSK}$  if the thermal nodes lay on the heat sink layer and  $R_{conv}$  represents the thermal resistance from the heat sink to ambient air.

Figure 3.1: A HotSpot Thermal Model for a 4-core platform [55]. (Our model adds lateral thermal resistors on the chip level for core-to-core heat transfer.)

The thermal behavior of a multi-core platform within a state interval can be formulated as

$$\frac{d\mathbf{T}(t)}{dt} = \mathbf{A}\mathbf{T}(t) + \mathbf{B}(\mathbf{v}),\tag{3.2}$$

where  $\mathbf{T}(t)$  vector represents node temperatures at time t. Coefficient matrix  $\mathbf{A} = [A_{i,j}]_{N \times N}$  is an architectural-related constant, thus the system is time invariant.  $\mathbf{A}$  depends only on the thermal capacitance matrix  $\mathbf{C} = diag\{C_1, \dots, C_N\}$  and thermal resistance matrix  $\mathbf{G} = [G_{i,j}]_{N \times N}$  as  $\mathbf{A} = -\mathbf{C}^{-1}\mathbf{G}$ , where  $C_i$  is the thermal

capacitance of the *i*-th thermal node,  $C_i > 0$  and

$$G_{i,j} = \begin{cases} \sum_{\theta \neq i} \frac{1}{R_{i,\theta}} + \xi_i \frac{1}{R_{conv}}, & \text{if } i = j, \\ -\frac{1}{R_{i,j}}, & \text{otherwise,} \end{cases}$$

(3.3)

in which  $\xi_i = 1$  when  $\Pi_i \in \mathbf{\Pi_{HSK}}$ ; otherwise,  $\xi_i = 0$ .  $R_{i,i}$  (or  $R_{i,j}$ ) denotes the thermal resistance of the *i*-th thermal node to itself (or the *j*-th thermal node). The upper left  $N_c \times N_c$  sub-matrix of  $\mathbf{A}$  and  $\mathbf{G}$  contribute to the cores. Existing studies show that matrix  $\mathbf{G}$  has following properties:

#### **Property 3.1.1.** *Matrix* **G** *has following properties:*

- 1. G is a quasi-positive matrix with all of its entries being non-negative except for those on the main diagonal [52];

- 2. **G** is strictly diagonal dominant, real symmetric and nonsingular (Lemma 1 in [144]);

Both  $\mathbf{C}$  and  $\mathbf{G}$  are  $N \times N$  square matrices. Since  $\mathbf{C}$  only contains non-zero elements on the diagonal, it is invertible. Moreover,  $\mathbf{G}$  is also invertible, because it is nonsingular. Then, since  $\mathbf{A} \cdot \mathbf{A}^{-1} = -\mathbf{C}^{-1}\mathbf{G} \cdot (-\mathbf{C}^{-1}\mathbf{G})^{-1} = \mathbf{C}^{-1}\mathbf{G}\mathbf{G}^{-1}\mathbf{C} = \mathbf{I}$ ,  $\mathbf{A}$  is invertible.  $\mathbf{A}$  is neither symmetric nor diagonal dominant.

Coefficient vector  $\mathbf{B} = [B_i]_{N \times 1}$ , a power-related vector, depends on not only the thermal capacitances of the multi-core platform but also the running mode of each core. Assume  $\forall \mathbf{v}_1 \geq \mathbf{v}_2$  leads to  $\mathbf{B}(\mathbf{v}_1) \geq \mathbf{B}(\mathbf{v}_2)$ .

When running a multi-core processor under a constant supply voltage  $\mathbf{v}$  long enough (i.e.  $t \to \infty$ ), it will eventually reach a constant temperature  $\mathbf{T}^{\infty}(\mathbf{v}) = -\mathbf{A}^{-1}\mathbf{B}(\mathbf{v})$  as  $d\mathbf{T}(\infty)/dt = \mathbf{0}$ . For schedules that consist of multiple state intervals, the state intervals may not be long enough for the temperature to be constant. As shown in [52], the transient temperature at time t within a state interval (e.g. the

q-th interval  $[t_{q-1}, t_q]$ ) can be formulated as

$$\mathbf{T}(t) = e^{\mathbf{A}(t - t_{q-1})} \mathbf{T}(t_{q-1}) + (\mathbf{I} - e^{\mathbf{A}(t - t_{q-1})}) \mathbf{T}_q^{\infty}, \tag{3.4}$$

where  $t_{q-1} \leq t \leq t_q$  and  $\mathbf{T}(t_{q-1})$  is the temperature vectors at the beginning of the q-th interval.  $\mathbf{T}_q^{\infty}$  is the constant temperature when running processor using supply voltage  $\mathbf{v}_q$  long enough and  $\mathbf{I}$  is an identity matrix.

For a periodic schedule S(t) with z state intervals and period  $t_p$ , let  $t_{q-1}$  and  $t_q$  be the starting time and ending time of the q-th state interval, respectively. Let  $l_q = t_q - t_{q-1}$ , and from (3.4), we can derive the temperature at  $t_p$  through the temperature at each consecutive scheduling point in the first period as

$$\mathbf{T}(t_{1}) = e^{\mathbf{A}l_{1}}\mathbf{T_{0}} + (\mathbf{I} - e^{\mathbf{A}l_{1}})\mathbf{T}_{1}^{\infty} = (\mathbf{I} - e^{\mathbf{A}l_{1}})\mathbf{T}_{1}^{\infty} + e^{\mathbf{A}l_{1}}\mathbf{T_{0}};$$

$$\mathbf{T}(t_{2}) = e^{\mathbf{A}l_{2}}\mathbf{T}(t_{1}) + (\mathbf{I} - e^{\mathbf{A}l_{2}})\mathbf{T}_{2}^{\infty}$$

$$= \sum_{q=1}^{2} e^{\mathbf{A}\sum_{\theta=q+1}^{2} l_{\theta}}(\mathbf{I} - e^{\mathbf{A}l_{q}})\mathbf{T}_{q}^{\infty} + e^{\mathbf{A}\sum_{\theta=1}^{2} l_{\theta}}\mathbf{T_{0}};$$

$$...$$

$$\mathbf{T}(t_{h}) = e^{\mathbf{A}l_{h}}\mathbf{T}(t_{h-1}) + (\mathbf{I} - e^{\mathbf{A}l_{h}})\mathbf{T}_{h}^{\infty}$$

$$= \sum_{q=1}^{h} e^{\mathbf{A}\sum_{\theta=q+1}^{h} l_{\theta}}(\mathbf{I} - e^{\mathbf{A}l_{q}})\mathbf{T}_{q}^{\infty} + e^{\mathbf{A}\sum_{\theta=1}^{h} l_{\theta}}\mathbf{T_{0}};$$

$$...$$

$$\mathbf{T}(t_{p}) = \sum_{q=1}^{z} e^{\mathbf{A}\sum_{\theta=q+1}^{z} l_{\theta}}(\mathbf{I} - e^{\mathbf{A}l_{q}})\mathbf{T}_{q}^{\infty} + e^{\mathbf{A}\sum_{\theta=1}^{z} l_{\theta}}\mathbf{T_{0}}.$$

$$(3.5)$$

When repeating a periodic schedule with multiple state intervals long enough, the temperature eventually enters the thermal stable status, in which the temperature trace exhibits a repeat pattern. Specifically, for a periodic schedule  $\mathbb{S}(t)$  with z state intervals and period  $t_p$ , let  $t_{q-1}$  and  $t_q$  be the starting time and ending time of the q-th state interval, respectively. The transient temperature in the stable status can

be formulated as [52]

$$\mathbf{T}_{ss}(t_q) = \mathbf{T}(t_q) + \mathbf{K}_q(\mathbf{I} - \mathbf{K})^{-1}(\mathbf{T}(t_p) - \mathbf{T}(0)), \tag{3.6}$$

in which  $\mathbf{T}(t_q)$  and  $\mathbf{T}_{ss}(t_q)$  are the temperature at time  $t_q$  in the first period and in the thermal stable status, respectively.  $\mathbf{T}(0)$  is the starting temperature for the first period and equals to  $\mathbf{T_0}$ . The  $\theta$ -th state interval size  $l_{\theta} = t_{\theta} - t_{\theta-1}$ ,  $\mathbf{K}_q = e^{\mathbf{A} \sum_{\theta=1}^q l_{\theta}}$  and  $\mathbf{K} = e^{\mathbf{A} \sum_{\theta=1}^z l_{\theta}} = e^{\mathbf{A}t_p}$ .

# 3.2 The Properties of the Thermal Model

In this section, we focus on some inherent properties related to the multi-core RC thermal model itself. The thermal model in (3.2) is a linear time-invariant (LTI) system, which captures the thermal dynamics by N first-order differential equations involving N state variables. The system matrix  $\mathbf{A}$  plays an important role in temperature dynamics before and when a multi-core platform reaches its temperature stable status, because  $\mathbf{A}$  relates how the current temperature affects the temperature change  $d\mathbf{T}(t)/dt$  [52] and  $\mathbf{T}^{\infty}$ . Moreover, the property of  $\mathbf{A}$  determines the system stability [13], and its transformations, such as  $-\mathbf{A}^{-1}$ ,  $e^{\mathbf{A}l}$  or  $(\mathbf{I} - e^{\mathbf{A}l})^{-1}$  etc, are closely related to other properties of a system. In this section, we first present some properties related to matrix  $\mathbf{A}$ .

Lemma 3.2.1. Matrix A has all negative real eigenvalues.<sup>1</sup>

Proof. Since  $\mathbf{C} = diag\{C_1, \dots, C_N\}$  and  $C_i > 0$ , we have  $\mathbf{C}^{1/2} = diag\{\sqrt{C_1}, \dots, \sqrt{C_N}\}$  and  $\mathbf{C}^{-1/2} = diag\{1/\sqrt{C_1}, \dots, 1/\sqrt{C_N}\}$  and they are nonsingular. The transpose of  $\mathbf{C}^{1/2}$  and  $\mathbf{C}^{-1/2}$  equal to themselves, respectively.

<sup>&</sup>lt;sup>1</sup>Similar conclusion was mentioned in [13].

**G** is positive definite, because a symmetric diagonally dominant matrix with real non-negative diagonal entries is positive definite [92]. Thus, there exists a  $\mathbf{Y} \neq \mathbf{0}$  such that  $\mathbf{Y}^T \mathbf{G} \mathbf{Y} > \mathbf{0}$ . Let  $\mathbf{Y} = \mathbf{C}^{-1/2} \mathbf{X}$ ,  $\mathbf{X} \neq \mathbf{0}$  and  $\mathbf{X}^T$  denotes the transpose of  $\mathbf{X}$ . Then, we have  $\mathbf{Y}^T \mathbf{G} \mathbf{Y} = (\mathbf{C}^{-1/2} \mathbf{X})^T \mathbf{G} \mathbf{C}^{-1/2} \mathbf{X} = \mathbf{X}^T \mathbf{C}^{-1/2} \mathbf{G} \mathbf{C}^{-1/2} \mathbf{X} = \mathbf{X}^T \mathbf{G} \mathbf{C}^{-1/2} \mathbf{G} \mathbf{C}^{-1/2} \mathbf{G} \mathbf{C}^{-1/2} \mathbf{X} = \mathbf{X}^T \mathbf{G} \mathbf{C}^{-1/2} \mathbf{G} \mathbf{C}^{-1/2}$

Since there exists a nonsingular matrix  $\mathbf{C}^{1/2}$  such that the *similarity transformation* (page 506 in [95]) of  $-\mathbf{A} = \mathbf{C}^{-1}\mathbf{G} = \mathbf{C}^{-1/2}\mathbf{C}^{-1/2}\mathbf{G} = \mathbf{C}^{-1/2}(\mathbf{C}^{-1/2}\mathbf{G}\mathbf{C}^{-1/2})\mathbf{C}^{1/2} = (\mathbf{C}^{1/2})^{-1}\mathbf{\Omega}\mathbf{C}^{1/2}$ ,  $-\mathbf{A}$  is similar to  $\mathbf{\Omega}$  and sharing all the eigenvalues (page 508 in [95]). Thus, all the eigenvalues of  $\mathbf{A}$  are negative real numbers.  $\square$

In control theory, since all the eigenvalues of **A** are strictly negative real values, it is asymptotically stable [16]. Moreover, all the asymptotically stable systems are also bounded-input, bounded-output (BIBO) stable, which means the output will be bounded for every input to the system that is bounded. In other words, there always exists a peak temperature for any schedule executed on a given platform, with its power supply stay below the maximal threshold.

#### Lemma 3.2.2. Matrix A is diagonalizable.

*Proof.* Let  $\tilde{\mathbf{A}} = \mathbf{C}^{1/2}\mathbf{A}\mathbf{C}^{-1/2}$  and  $\tilde{\mathbf{A}}^T$  be the transpose of  $\tilde{\mathbf{A}}$ . Then, we have  $\tilde{\mathbf{A}}^T = (\mathbf{C}^{1/2}\mathbf{A}\mathbf{C}^{-1/2})^T = -(\mathbf{C}^{-1/2}\mathbf{G}\mathbf{C}^{-1/2})^T = -(\mathbf{C}^{-1/2})^T\mathbf{G}^T(\mathbf{C}^{-1/2})^T = -\mathbf{C}^{-1/2}\mathbf{G}\mathbf{C}^{-1/2} = \tilde{\mathbf{A}}$ , which means  $\tilde{\mathbf{A}}$  is symmetric.

Since  $\tilde{\mathbf{A}}$  is real and symmetric, it is diagonalizable (Theorem 7.2.1 in [7]). Thus, there exists an invertible matrix  $\mathbf{Q}$  such that  $\mathbf{Q}\tilde{\mathbf{A}}\mathbf{Q}^{-1} = \mathbf{\Gamma}$ , in which  $\mathbf{\Gamma}$  is a diagonal matrix. We can see  $\mathbf{A} = \mathbf{C}^{-1/2}\tilde{\mathbf{A}}\mathbf{C}^{1/2} = \mathbf{C}^{-1/2}\mathbf{Q}^{-1}\mathbf{\Gamma}\mathbf{Q}\mathbf{C}^{1/2} = (\mathbf{Q}\mathbf{C}^{1/2})^{-1}\mathbf{\Gamma}\mathbf{Q}\mathbf{C}^{1/2}$ .

There exists an invertible matrix  $\mathbf{QC}^{1/2}$  such that  $(\mathbf{QC}^{1/2})\mathbf{A}(\mathbf{QC}^{1/2})^{-1} = \Gamma$  is a diagonal matrix, so  $\mathbf{A}$  is diagonalizable (Page 303 Definition 2 in [7]).

Since **A** is diagonalizable and all of its eigenvalues are negative (Lemma 3.2.1), we can easily calculate its eigenvalues. Let  $-\lambda_i$  be the *i-th* eigenvalue of **A** and  $\lambda_i > 0$ , we have  $\mathbf{A} = \mathbf{W}\mathbf{D}\mathbf{W}^{-1}$ , where  $\mathbf{D} = diag\{-\lambda_1, \dots, -\lambda_N\}$  and  $\mathbf{W} = [\vec{w_1}, \dots, \vec{w_N}]$ .  $\vec{w_i}$  is the independent eigenvectors associated with  $-\lambda_i$ . The matrix exponential of  $e^{\mathbf{A}l}$  can be diagonalized as

$$e^{\mathbf{A}l} = \sum_{h=0}^{\infty} \frac{l^h (\mathbf{W} \mathbf{D} \mathbf{W}^{-1})^h}{h!} = \mathbf{W} \left( \sum_{h=0}^{\infty} \frac{l^h \mathbf{D}^h}{h!} \right) \mathbf{W}^{-1} = \mathbf{W} e^{\mathbf{D}l} \mathbf{W}^{-1}, \tag{3.7}$$

where  $e^{\mathbf{D}l} = diag\{e^{-\lambda_1 l}, \cdots, e^{-\lambda_N l}\}$  and  $e^{-\lambda_i l}$  is the *i*-th eigenvalue of  $e^{\mathbf{A}l}$ .

**Lemma 3.2.3.** Matrix **A** is constant and all the entries of  $-\mathbf{A}^{-1} = [\mathscr{A}_{i,j}]_{N \times N}$  are positive real numbers and  $\mathscr{A}_{i,j} > 0$ .