Wayne State University

Wayne State University Dissertations

1-1-2018

# Doped And Chemically Transformed Transition Metal Dichalcogenides (tmdcs) For Two-Dimensional (2d) Electronics

Sagar Prasad Paudel *Wayne State University,*

Follow this and additional works at: https://digitalcommons.wayne.edu/oa\_dissertations Part of the <u>Physics Commons</u>

#### **Recommended** Citation

Paudel, Sagar Prasad, "Doped And Chemically Transformed Transition Metal Dichalcogenides (tmdcs) For Two-Dimensional (2d) Electronics" (2018). *Wayne State University Dissertations*. 2056. https://digitalcommons.wayne.edu/oa\_dissertations/2056

This Open Access Dissertation is brought to you for free and open access by DigitalCommons@WayneState. It has been accepted for inclusion in Wayne State University Dissertations by an authorized administrator of DigitalCommons@WayneState.

### DOPED AND CHEMICALLY TRANSFORMED TRANSITION METAL DICHALCOGENIDES (TMDCS) FOR TWO-DIMENSIONAL (2D) ELECTRONICS

by

### SAGAR PRASAD PAUDEL

### DISSERTATION

Submitted to the Graduate School

of Wayne State University,

Detroit, Michigan

in partial fulfillment of the requirements

for the degree of

#### **DOCTOR OF PHILOSOPHY**

2018

MAJOR: PHYSICS

Approved By:

Advisor

Date

## © COPYRIGHT BY

## SAGAR PRASAD PAUDEL

2018

All Rights Reserved

## DEDICATION

Dedicated to my parents

JivaNath Padhya and Numala Kumari Sharma.

#### ACKNOWLEDGEMENTS

A lot of people helped and motivated me in my PhD journey. I would like to express my deepest gratitude to all the people who helped and inspired me directly and indirectly in this journey.

I want to thank Wayne State University, Department of Physics & Astronomy for providing me an opportunity to join the department. It is my good fortune to get an opportunity to work with Dr. Zhixian Zhou. I would like to thank him for his expertise guidance, unlimited patience and generous help. I am thankful to Late Prof. Gaven Lawes for giving me a chance to join his lab. Unfortunately, he is no more with us, but the lesson he taught, guidance he provided in short period of time is lifelong lesson for me.

My sincere thank goes to the dissertation committee members: Dr. Boris Nadgorny, Dr. Ashis Mukhopadhyay and Dr. Mark Ming- Cheng Cheng for their highly advice and help. I am grateful to all the teachers who taught me and helped me to understand the fundamentals of physics. I would also like to thank Prof. Ratna Naik and Prof. Jogindra Wadehra for guidance and help.

It is impossible to list name of all the people who have given me help, encouragement, advice and well wishes during this period. I wish to express my sincere thanks to all my friends who help me directly or indirectly to achieve my goal. Special thank goes to Dr. Bhim Chamlagain, Dr. Madusanka Perera, Dr. Hsun Jen Chuang (Ben) for helping me in lab during my starting days. I would like to thank Dr. Qingsong Cui, Mr. Bill Funk and Mr. Dan Durisin from ECE for the help during this journey. I am also thankful to friends Prakash Thapa, Ramesh Tripathi, Ek Adhikari, Nabin Poudyal, Niraj Shrestha, Shiva Pokhrel, Shambhu Pokhrel, Gobin Acharya, Sushil pageni and my current lab mates Arthur, Kraig and Upendra.

Last but not the least, I would like to dedicate this work to my parents who always stood by me in every run of life. I would be nowhere without their support and belief in me. I am grateful to my wife Meena for her support, patience and motivation and to my son Suyog, who brought a lot of happiness in our life.

## TABLE OF CONTENTS

| DEDICATION                                                  |

|-------------------------------------------------------------|

| ACKNOWLEDGEMENTS                                            |

| LIST OF FIGURES ix                                          |

| LIST OF ABBREVIATIONS xiii                                  |

| CHAPTER 1: INTRODUCTION                                     |

| 1.1 Two Dimensional (2D) Materials                          |

| 1.1.1 Graphene                                              |

| 1.1.2 Transition Metal Dichalcogenides (TMDCs)              |

| 1.1.3 Transport Properties and Device applications of TMDCs |

| 1.1.4 Optoelectronic Properties of TMDCs                    |

| 1.1.6 Challenges of TMDCs7                                  |

| 1.1.7 Doping TMDCs7                                         |

| 1.1.8 Metal-Semiconductor Contact                           |

| 1.1.9 Contact Engineering 10                                |

| 1.1.10 High K Di-electric Integration13                     |

| 1.1.11 High-K Dielectrics15                                 |

| 1.2 Scope of the Study                                      |

| CHAPTER 2: EXPERIMENTAL METHODS 19                          |

| 2.1 Device Fabrication                                      |

| 2.1.1 Crystal synthesis                                     |

| 2.1.2 Substrate preparation                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------|

| 2.1.3 Sample Preparation                                                                                                        |

| 2.1.4 Thermal Oxidation                                                                                                         |

| 2.1.5 Electrode Fabrication                                                                                                     |

| 2.2 Characterization Techniques                                                                                                 |

| 2.2.1 Optical microscope                                                                                                        |

| 2.2.2 Atomic Force Microscope (AFM)                                                                                             |

| 2.2.3 Electrical Characterization                                                                                               |

| 2.2.4 Capacitance Voltage (C-V) measurement                                                                                     |

| 2.2.5 X-ray Photoelectron Spectroscopy                                                                                          |

| CHAPTER 3: GATE-TUNABLE P-N JUNCTIONS FORMED BETWEEN DEGENERATELY<br>P-DOPED AND UNDOPED TMDCS                                  |

| 3.1 Background and Motivation                                                                                                   |

| 3.2 Results and Discussion                                                                                                      |

| 3.3 Summary                                                                                                                     |

| CHAPTER 4: THERMALLY OXIDIZED 2D TAS <sub>2</sub> AS HIGH-K DIELECTRIC FOR MOS <sub>2</sub><br>FETS                             |

| 4.1 Background and Motivation                                                                                                   |

| 4.2 Results and discussion                                                                                                      |

| 4.3 Summary                                                                                                                     |

| CHAPTER 5: SYNTHESIS AND CHARACTERIZATION OF ULTRATHIN HFO <sub>2</sub> FROM<br>CHEMICAL TRANSFORMATION OF 2D HFSE <sub>2</sub> |

| 5.1 Background and Motivation |    |  |

|-------------------------------|----|--|

| 5.2 Results and Discussion    | 63 |  |

| 5.3 Summary                   | 78 |  |

| FUTURE WORK                   | 79 |  |

| BIBLIOGRAPHY                  | 81 |  |

| ABSTRACT                      |    |  |

| AUTOBIOGRAPHICAL STATEMENT    |    |  |

## LIST OF TABLES

| Table 1. 1. List of High K dielectrics <sup>89</sup> 17                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 5. 1. Thickness and roughness measurement of HfSe <sub>2</sub> surface at different stages of the oxidation process. Same areas of the sample were chosen for each measurement |

| Table 5. 2. Thickness of Hafnium samples immediately after exfoliation (HfSe2) and after heatingin air for 3 hours at 300° C.72                                                      |

| Table 5. 3. Calculation of conversion factor on the basis of mass density relation                                                                                                   |

| Table 5. 4. Value of applied voltages for the study of leakage current for the device shown in figure         9                                                                      |

## LIST OF FIGURES

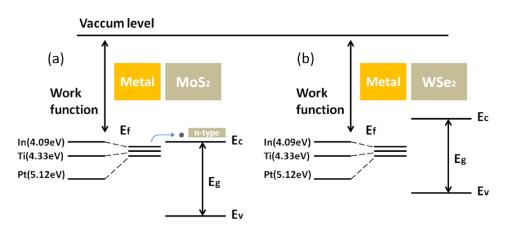

| Figure 1. 1. Schematic diagram of the barrier formation at metal-semiconductor interface <sup>70</sup> . Three metals with different work functions are shown, (a) Metal-MoS2 interface, fermi level of the metal is close to the conduction band allowing n-type transport and (b) Metal-WSe2 interface, fermi levels of metals are close to the middle of the band gap, forming barrier for both type of conduction.                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

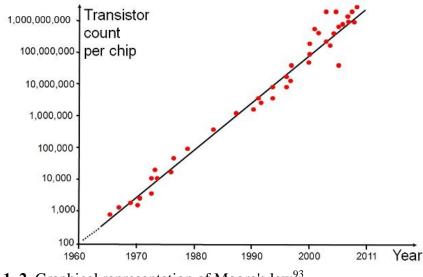

| Figure 1. 2. Graphical representation of Moore's law <sup>93</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 2. 1. ULVAC MILA-5000 annealer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

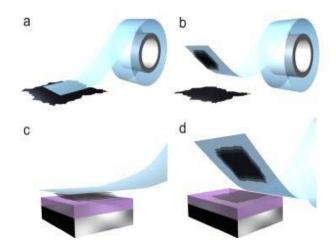

| Figure 2. 2. Schematic diagram representing mechanical exfoliation of two-dimensional TMDCs sample. a) a small portion of bulk material is taken on the scotch tape b) peel off repeatedly the sample until we get few layers thick c) after getting few layers thick sample, scotch tape is stamped over the substrate and pressed uniformly for few minutes d) scotch tape is gently removed, samples are now attached to the substrate. 22                                                                                                            |

| Figure 2. 3. Sylgard 184 silicone curing agent and elastomer (respectively from left to right). A mixture of these two is spin coated and baked to prepare PDMS polymer                                                                                                                                                                                                                                                                                                                                                                                  |

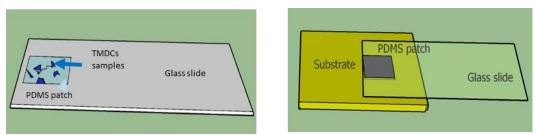

| Figure 2. 4. Schematic diagram showing the process of dry transfer Sample transfer using DMS layer a) PDMS patch with the sample is put on the glass slide b) With the help of micromanipulator, the sample is transferred to the substrate                                                                                                                                                                                                                                                                                                              |

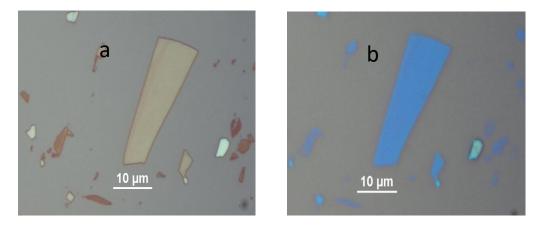

| Figure 2. 5. Thermal oxidation of $TaS_2$ . a) $TaS_2$ sample immediately after exfoliation b) Thermally oxidized $TaS_2$ after heating on a hot plate at 300° C for 3 hours                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 2. 6. Hitachi S-2400 Scanning Electron Microscope attached with E-beam writing column.<br>It has the maximum accelerating voltage of 25 KV                                                                                                                                                                                                                                                                                                                                                                                                        |

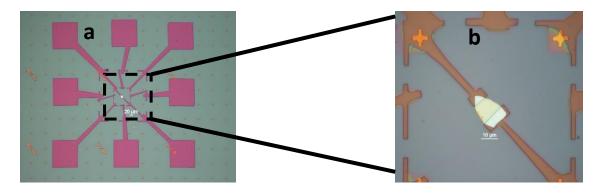

| Figure 2. 7. Optical image of a device showing e-beam pattern a) at 10X magnification b) at 100X magnification. The pattern was developed in MIBK/MKE developer solution for 1 minute after e-beam writing                                                                                                                                                                                                                                                                                                                                               |

| Figure 2. 8. BJD 1800 e-beam metal evaporator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

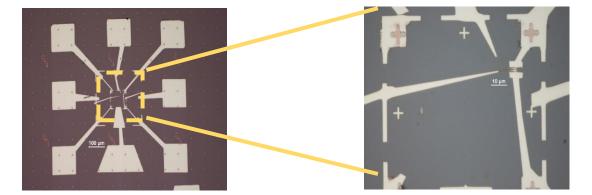

| Figure 2. 9. Optical image of a device after lift-off. The substrate was dipped in acetone for 5-10 minutes to lift-off the metal                                                                                                                                                                                                                                                                                                                                                                                                                        |

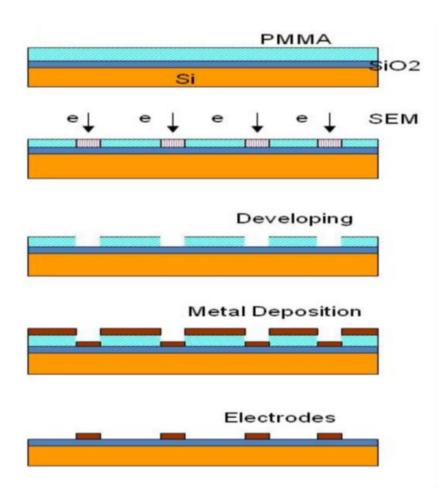

| Figure 2. 10. Flowchart of the electrode fabrication. a) 2/3 layers of PMMA spin coating followed by baking at 180° C for 5 minutes after each layer coating, b) writing pattern on the substrate using electron-beam, c) developing the lithography pattern by dipping the substrate in the developer solution. The cut-out parts are the pattern designed to deposit metal on to form the electrodes, d) depositing Ti/Au:5nm/45nm on the substrate, e) removing the metal from all the area except the electrodes by dipping the substrate in acetone |

| Figure 2. 11. Optical microscope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

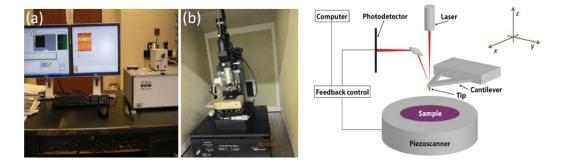

| Figure 2. 12. AFM setup (a) & (b). Schematic diagram of AFM working principle                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2. 13. Lakeshore cryogenic probe station for low temperature measurement system 32                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 2. 14. Alignment 4284A precision LCR meter                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

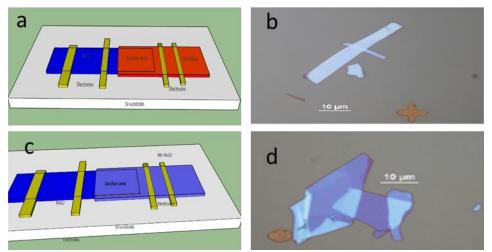

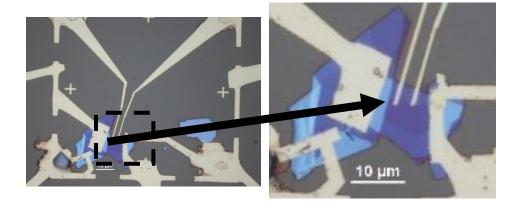

| Figure 3. 1. a) Schematic diagram & b) optical micrograph of the heterojunction p-n junction diode,<br>Nb-doped WSe <sub>2</sub> is stacked on the top of undoped MoS <sub>2</sub> ; c) Schematic diagram & d) optical<br>micrograph of the homojunction p-n junction diode, Nb-doped MoS <sub>2</sub> is stacked on the top of<br>undoped MoS <sub>2</sub> . The overlap area between the doped and undoped sample constitute the p-n<br>junction diode                                                                       |

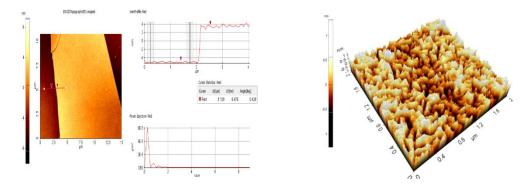

| Figure 3. 2. AFM image of undoped $MoS_2$ . a) Thickness measurement, the thickness of the sample is shown 8.5 nm, b) 3-dimensional view of the 2um X 2um area scan of the same sample, 37                                                                                                                                                                                                                                                                                                                                     |

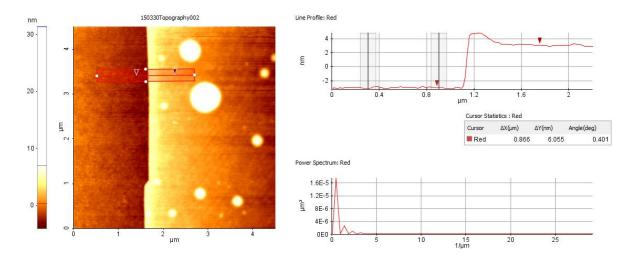

| Figure 3. 3. AFM image of vertically stacked heterojunction diode                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 3. 4. Optical micrograph of homojunction p-n junction diode                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

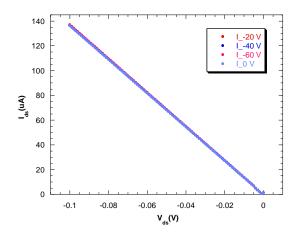

| Figure 3. 5. IV characteristic of Nb-doped MoS <sub>2</sub> contact on homojunction p-n diode                                                                                                                                                                                                                                                                                                                                                                                                                                  |

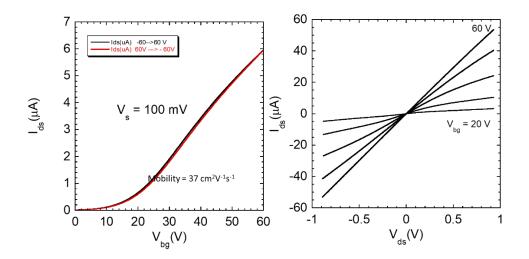

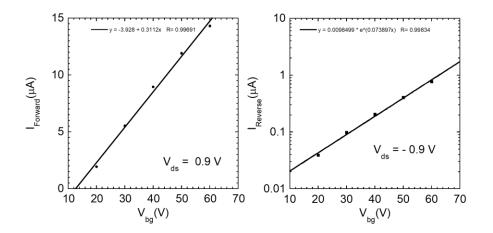

| Figure 3. 6. a) Transfer characteristics and b) I-V characteristics of the undoped MoS <sub>2</sub> sample. 40                                                                                                                                                                                                                                                                                                                                                                                                                 |

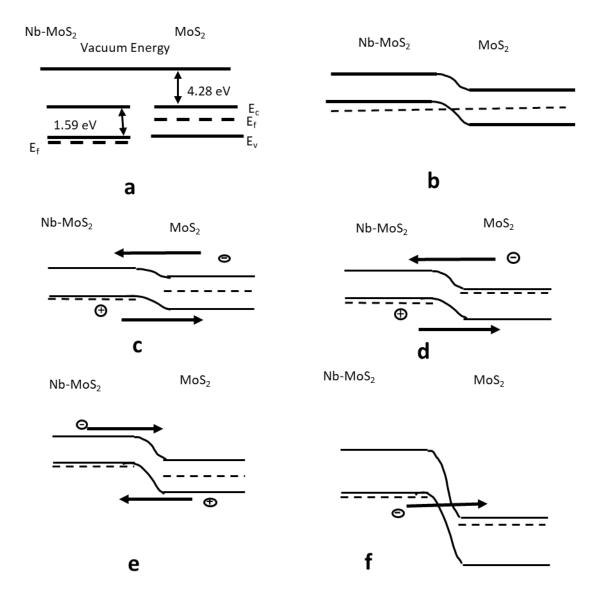

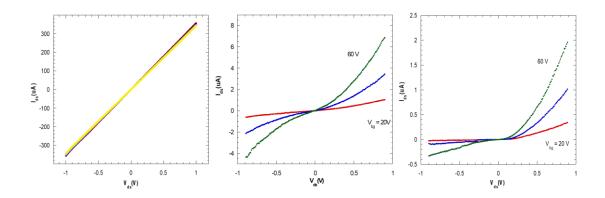

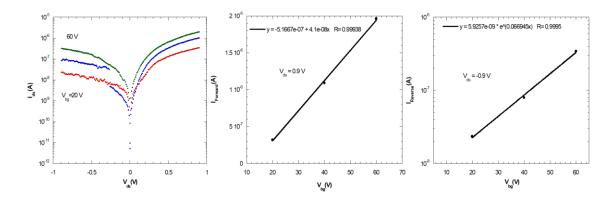

| Figure 3. 7. a) I-V characteristics of homojunction p-n junction diode consisting of Nb-doped $MoS_2$ as p-type and undoped $MoS_2$ as an n-type semiconductor, b) I-V characteristics of the diode in semi-log scale. 42                                                                                                                                                                                                                                                                                                      |

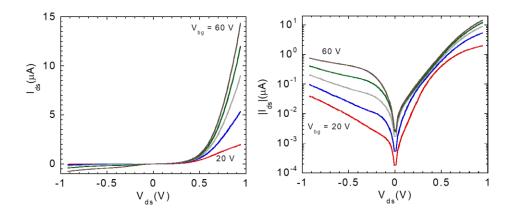

| Figure 3. 8. Band diagram of Nb-Mos <sub>2</sub> /Mos <sub>2</sub> homojunction p-n diode. a) when two semiconductors are not in contact b) in an equilibrium condition, Fermi levels are lined up. c) forward bias at low gate voltage. Due to the forward bias, the interface barrier height is decreased increasing the current. d) forward bias at large voltage. Due to large gate voltage electrostatic doping of the semiconductor increases the carrier concentration in both sides increasing the current. e) reverse |

bias at low gate voltage. The interface barrier height is increased due to the depletion of the carrier and the conduction is solely due to the minority charge carriers. f) reverse bias at large gate voltage. The large gate voltage dopes the channel electrostatically bringing the conduction band of n-side at the energy level below the valence band of p-side giving rise to band to band tunneling current.

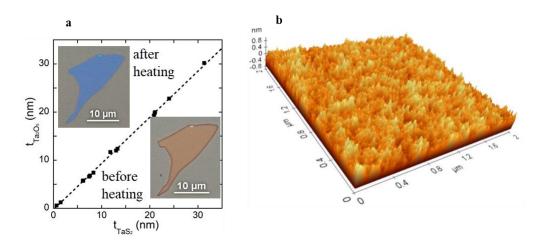

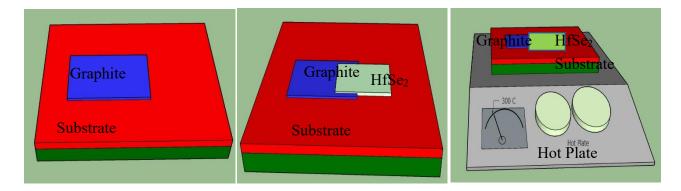

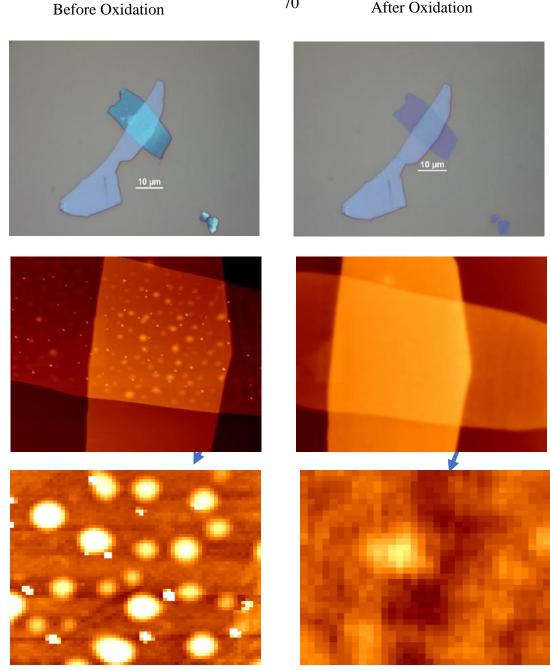

Figure 5. 5. Optical image of  $HfSe_2$  on the top of multilayer Graphite a) immediately after transformation b) After performing oxidation by heating at 300°C in ambient condition for 3 hours.

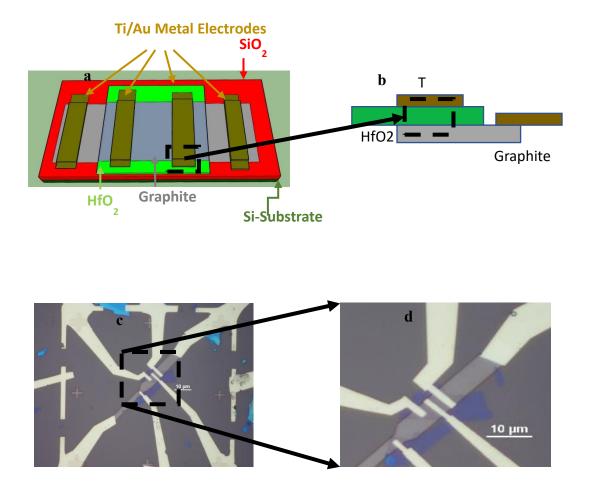

Figure 5. 7. a) Schematic diagram of MIM junction, b) cross-sectional view of MIM junction, which forms a parallel plate capacitor, c) MIM junction with Ti/Pt as a bottom electrode and HfO<sub>2</sub> as a dielectric (insulator) and Ti/Au as a top electrode, d) Magnified part of image c......74

## LIST OF ABBREVIATIONS

TMDC: Transition Metal Dichalcogenide

2D: Two-dimensional

FET: Field-Effect Transistor

h-BN: hexagonal Boron Nitride

SiO2: Silicon dioxide

Al2O3: Aluminum oxide

TaS<sub>2</sub>: Tantalum di-sulfide

TiS<sub>2</sub>: Titanium di-sulfide

Ta2O5: Tantalum pentoxide

TiO2: Titanium dioxide

MoS2: Molybdenum di-sulfide

MoSe2: Molybdenum di-selenide

HfO<sub>2</sub>: Hafnium oxide

HfSe<sub>2</sub>: Hafnium di-selenide

WSe2: Tungsten di-selenide

**BP: Black phosphorus**

Si: silicon

SEM: Scanning electron microscope

AFM: Atomic force microscope

CVD: Chemical vapor deposition

ALD: Atomic layer deposition

NPGS: Nano patterning generation system

PMMA: Polymethyl methacrylate

vdW: van der Waals

HSQ: Hydrogen silsesquioxane

**IPA:** Isoproponal

DFT: Density functional theory

STM: Scanning tunneling microscope

STS: Scanning tunneling spectroscope

MIBK: Methyl isobutylketone

MEK: Methyl ethyl ketone

SS: Subthreshold swing

PDMS: Poly-dimethylsiloxane

RT: room temperature

MIT: Metal insulator transition

SB: Schottky barrier

CMOS: Complementary metal-oxide semiconductor

XPS: X-ray photoelectron spectroscopy

EDS: Energy dispersive spectroscopy

UHV: ultra-high vacuum

BTBT: Band to band tunneling

SCTD: Surface Charge Transfer Doping

### **CHAPTER 1: INTRODUCTION**

In 1904, Jon Ambrose Fleming invented the first Vacuum tube that worked as a rectifier to convert AC into DC current, which marked the beginning of the age of electronics. In 1907, Lee De Forest invented the triode, consisting of two electrodes - anode & cathode and one control grid to amplify weak signals. The cathode was heated, to generate the electrons and the control grid was used to control the flow of electrons to the anode. Thus, the output of the tube could be controlled by the grid current. The first computer was made up of these vacuum tubes. However, these vacuum tubes were not efficient as electronic switches. The vacuum tubes were big in size, needed large amount of the power and gave off large amount of heat. The search for the alternatives of these vacuum tubes led the world towards the modern age of electronics. With the invention of Silicon based transistors, the world witnessed the huge progress in the field of electronics. In 1954, first Silicon transistor was developed at Bell laboratories by controlling the doping of single Silicon crystal while grown from molten Silicon<sup>1</sup>. In 1955, the doping process was refined by using diffusion of donor and acceptor impurities in single Silicon crystal<sup>2</sup>. The continuous process of improvement and development is going on until the present. After the invention of Silicon chip in the late 1950s, the number of transistors in a chip has doubled almost every 18 months<sup>3</sup>. Now, a microprocessor can contain more than two billion transistors. The performance of the chip has been improved with less power consumption and reduced cost. This became possible because of the scalability of Si-based transistor alongside the improvement in speed and energy consumption. These benefits led to the rise of personal computers and mobile computing technologies such as laptops, smart phones etc. However, the scaling down of Si transistor cannot go indefinitely. Transistors are already so small, further shrinking them would compromise the performance of the device. As the traditional scaling of Si transistors is about to reach its limit, suitable alternative

candidate is required to carry the progress of electronics further. In this regard, atomically thin two-dimensional (2D) materials are sought as a post-silicon alternative. These 2D materials exhibit excellent electronic and optoelectronic properties, mechanical flexibility and stability<sup>4–8</sup>. Furthermore, these 2D materials have wide range of applications from Electronics, Optoelectronics, Spintronics, Valleytronics to bio-sensors.

#### 1.1 Two Dimensional (2D) Materials

Two dimensional materials received significant attention because of their atomically thin nature, which makes the scaling possible without giving rise to the detrimental short channel effects. Furthermore, these materials provide an unique platform for several interesting features like exquisite valley physics, excitonic effects, strain induced phase transition effects, efficient quantum mechanical tunneling etc<sup>9</sup>. Since the successful isolation and study of the Graphene<sup>10</sup>, 2D materials have attracted a lot of interest. Two dimensional materials is even projected as a post-silicon alternative<sup>4</sup>. In two dimensional layered materials, the electrons in a plane are bounded by strong covalent force, whereas, the layers are connected by weak inter layer van der Waals (vdW) force. This weak vdW force enables the mechanical exfoliation of atomically thin shits and allows for the formation of different heterostructures vdW assembly. The absence of dangling bonds ensures the high-quality interface and low charge traps across the interface. Graphene is the most studied 2D material.

#### 1.1.1 Graphene

Graphene is a monolayer chain of carbon, packed into hexagonal honeycomb lattice (shown in figure 1.1). The covalent bond within a plane is strong, while the different layers are held together by weak vdW force. Graphene has high mobility (>50,000 cm<sup>2</sup>/Vs at room temper-ature<sup>11,12</sup>) and is thermally stable. It has wide area of applications from electronics, spintronics to

bio-sensing. But, the absence of intrinsic band gap overshadowed its high mobility and small quantum capacitance<sup>13–15</sup>. Due to the absence of band gap, it is not possible to use graphene in logic devices where the device must act like a switch. Due to the zero-band gap, we cannot get low off current to consider it as an off state. Engineering a band gap in Graphene suffered by severe mobility degradation, or required high bias voltages<sup>16,17</sup>. This limitation of the graphene encouraged the scientific community to look for other two-dimensional materials, which have nearly graphene like properties along with an intrinsic band gap.

#### **1.1.2 Transition Metal Dichalcogenides (TMDCs)**

Besides Graphene, a group of 2D materials called Transition metal Dichalcogenides (TMDCs) have been studied heavily, because of the graphene like properties alongside the inherent bandgap they possess. TMDCs offer inherent band gap with good electronic properties, mechanical flexibility, and chemical & thermal stability. TMDCs have layered structure in the form MX<sub>2</sub>, where M refers to metal (eg. Mo, W, Re, Ta, Ti etc.) and X, the chalcogen (eg. S, Se, Te). MX<sub>2</sub> crystals are hexagonally packed with stacking layers of X-M-X. TMDCs possess strong covalent bonds between metal and chalcogen atoms within a layer and those layers are held together by weak vdW force. TMDCs possess dangling bond free surface which helps to minimize the performance degradation due to interface states<sup>18</sup>. Recent studies showed the wide area of application of TMDCs for low energy devices, digital electronics & optoelectronics<sup>19–21</sup>. A lot of studies have done, which resulted in theories for electron-phonon scattering in TMDCs like MoS<sub>2</sub> and WS<sub>2</sub>. Also, strongly correlated electron phenomena such as charge density waves and superconductivity was explored for group V TMDCs like TaS<sub>2</sub>, NbSe<sub>2</sub><sup>22</sup>. TMDCs based on Groups V and VI metals (eg. V, Nb, Ta, Cr, Mo, W etc.) are the most heavily studied due to the diverse permutations of stable compounds and electronic behavior<sup>23</sup>. Furthermore, TMDCs can be prepared at the wafer scale using different deposition techniques like CVD, ALD etc. This increases the practical application prospect of the TMDCs<sup>24</sup>.

#### 1.1.2.1 Semi-conducting TMDCs

The high charge carrier mobilities and presence of inherent band gap that enables large switching ratios in field-effect transistors (FETs) have made semiconducting TMDCs, specifically MoS<sub>2</sub>, WS<sub>2</sub>, and WSe<sub>2</sub> attractive materials for electronic devices<sup>4,19,25,26</sup>. Furthermore, successful large-scale growth and the stability increase their prospects for practical applications. TMDCs possess indirect band gap at bulk state, but the band gap converts to the direct in monolayer limit. This indirect to direct bandgap conversion is important especially in optoelectronic applications like light emitting diode (LED). TMDCs also represent an interesting platform for fundamental studies of light-matter interactions, optoelectronics, and nano-photonics<sup>27–31</sup>. Figure 1.2 shows the hexagonal structure of TMDCs. Figure 1.2b gives the top view of the structure.

#### 1.1.2.1.1 MoS<sub>2</sub>

$MoS_2$  is the most studied 2D TMDCs material.  $MoS_2$  is found in nature and is used as a lubricant because of its lubricating property.  $MoS_2$  has three different structural phases: i) 2Hphase, which has hexagonal symmetry and semiconducting properties, ii) 1T-phase having tetragonal symmetry and metallic properties and iii) 3R-phased  $MoS_2$  with rhombohedral symmetry which has semiconducting properties like 2H-phased  $MoS_2$ .

Semiconducting MoS<sub>2</sub> has indirect band gap with 1.2 eV in bulk state that changes into the direct band gap of 1.8 eV in monolayer due to quantum confinement<sup>5</sup>. Monolayer MoS<sub>2</sub> FET showed the mobility in the range of 0.1-10 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> <sup>32,33</sup>. But, the phonon-scattering room-temperature mobility for bulk MoS<sub>2</sub> was reported 200-500 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1 34</sup>. With HfO2 as high K dielectric for the top gate the mobility of the MoS<sub>2</sub> was found to be about 200 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1 32</sup>.

#### 1.1.2.2 Metallic TMDCs

Layered sulfides of Group IV (i.e., Ti, Hf, and Zr) also possess interesting semi-metallic and semiconducting behavior, but they suffer from a high propensity for non-stoichiometric structure due to the low energy barriers for intercalation of metal atoms. Group V and VII TMDCs are mostly studied for many-body phenomena such as 1T TaS<sub>2</sub> for gate-tunable charge density waves and 1T' ReS<sub>2</sub> for linear anisotropy in electrical and optical properties<sup>5,23,32,35–37</sup>.

Unlike semi-conducting TMDCs, metallic TMDCs are prone to oxidation in presence of air. TMDCs like TaS<sub>2</sub>, TiS<sub>2</sub>, HfS<sub>2</sub>, HfSe<sub>2</sub> surface reacts to air and displace the chalcogenide atoms with oxygen atoms at the atom sites to form oxides. This property of these TMDCs is particularly useful to form atomically flat two-dimensional High K dielectrics.

#### **1.1.3 Transport Properties and Device applications of TMDCs**

Transport properties of 2D semiconductor shows wide variation depending up on the materials, type of charge carriers and dielectric used. Studies showed the exceptional electronic properties of graphene based on the unique band structure including the observation of ambipolar behavior and high mobility exceeding  $15000 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  at room temperature with ballistic transport, and shows quantum Hall effect<sup>10,38</sup>. In case of MoS<sub>2</sub>, the mobility values of monolayer and multilayer MoS<sub>2</sub> devices on SiO<sub>2</sub> reported by multiple groups were substantially below the Hall mobility of bulk MoS<sub>2</sub> (100 - 200 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>)<sup>32,39,40</sup>. Bao et. al. reported ambipolar multilayer MoS<sub>2</sub> with two terminal field-effect mobility attained to  $470 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  at room temperature on PMMA<sup>41</sup>. S. L. Li et.al. presented thickness dependent interfacial charge scattering of MoS<sub>2</sub> FET and showed the improvement of field effect mobility with increase of thickness by suppressing the Coulomb scattering originated from SiO<sub>2</sub> surface and MoS<sub>2</sub> /SiO<sub>2</sub> interfaces<sup>42</sup>. Different efforts to modify the SiO<sub>2</sub> surface, using high-k dielectric such as HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> and h-BN encapsulation have been done for graphene and TMDCs field effect transistor but the mobility values never reached to theoretical phonon limited mobility<sup>12,39,43–46</sup>, which indicates the carrier mobility of 2D channel materials is limited by extrinsic scattering from charged impurities at the channel/substrate interface and charge traps in dielectric, substrate surface roughness, and remote surface optical phonons originating from substrate.

A good transistor layer material should have high enough charge carrier mobility for on state current and fast operation of transistor. The layered materials should have reasonable band gap to maintain enough on/off current for the operation of transistor by electrostatically switching on and off state. On the other hand, sharp switching characteristic is equally important to allow high degree of electrostatic control over devices. Flexibility and transparency are also important characteristics for future electronics. Two-dimensional TMDCs such as MoS<sub>2</sub> and others offer an important advantage when compared with traditional bulk electronic materials: their sub-nanometer thickness. Coupled with a bandgap typically in the 1–2 eV range can result in high on/off ratios, the extreme thinness of TMDCs allows more efficient control over switching and can help to reduce short-channel effects and power dissipation. To achieve these ideal properties, selection of channel materials and dielectric materials is exceptionally important. In addition, devices structures, designs and modification are also important to optimize and modify the 2D thin layer transistor devices properties.

#### **1.1.4 Optoelectronic Properties of TMDCs**

TMDCs have indirect bandgap at multilayer structure, which converts to direct band gap in monolayer<sup>47</sup>. This transition from indirect to direct band gap is quite important as it increases the quantum yield. The direct band gap increases the probability of electron-hole pair generation resulting in better light absorption. The band gaps of the few layered TMDCs depends on the

6

number of layers<sup>48,49</sup>, which allows the absorption of light of different wavelengths. The stacked heterostructure of TMDCs further allows light absorption from wide range of wavelength<sup>50</sup>. The direct band gap monolayer TMDCs exhibit unique properties like strong photoluminescence(PL)<sup>47</sup>, high absorption in the visible range<sup>51</sup>, valley polarization<sup>52,53</sup>, and strongly bound and charged excitons<sup>54–56</sup>. Photodetectors made of Monolayer MoS<sub>2</sub> displayed strong photoresponsivity of 880 AW<sup>-1 57</sup>. The built in electric field of TMDCs is useful to separate photo generated electron-hole pairs. Also, strong exciton energies have been reported for monolayer TMDCs due to the strong coulomb interactions<sup>54–56</sup>.

#### **1.1.6 Challenges of TMDCs**

The channel of 2D materials is thin which needs substrate to support and for the investigation of its properties we must make electrical connections using metal electrodes. The contact metal form barrier with semiconductor channel of 2D materials and the dielectric on substrate plays important role to determine the channel properties of the thin 2D materials. To enhance the performance of  $MoS_2$  (or in general, TMDC channel materials) MOSFET, there are several issues that needs to be resolved<sup>58</sup>:

- Proper doping of the TMDCs

- Metal-semiconductor contact effect

- High K dielectric integration

#### **1.1.7 Doping TMDCs**

The success of conventional Si-semiconductor relies on the ability to achieve ohmic contacts through substitutional/impurity doping profiles for electron (n-type) and hole (p-type) injection respectively. The doping for conventional semiconductors is developed for years and is in excellent condition, but for 2D channel the doping method is still in early phase. In absence of effective doping schemes, early 2D FETs relied on the use of elemental metals with different work functions for carrier injection into the respective bands of 2D channel. There has been some progress in the doping of 2D materials now. Doping in TMDCs has been realized from the impurities used for bulk crystal growth, ambient interaction with intrinsic defects, interaction with substrate impurities, adsorption of metals or charge transferring molecules<sup>44,59–63</sup>. Chalcogen substitution and direct substitution of transition metal have also been demonstrated<sup>64,65</sup>. Some studies doped bulk TMDCs using vapor transport methods but to get monolayers mechanical exfoliation had to be done<sup>66,67</sup>. Mn doping in MoS<sub>2</sub> has been realized using chemical vapor deposition on inert substrate<sup>68</sup>. Suh et al. (2014) researched niobium (Nb) doping on MoS<sub>2</sub> as a p-type<sup>69</sup>. Nb atoms are doped on MoS<sub>2</sub> at the substitutional sites, leading to a degenerating hole density of around  $3\times10^{19}$ cm<sup>-3</sup>. Lin et al. (2014) demonstrated the doping of rhenium (Re) and gold (Au) on monolayer MoS<sub>2</sub> via CVT growth<sup>66</sup>.

Some of these doping methods may be selectively apply to limited areas through lithography processes, they still may damage the channel through ion impacts. None of these methods have applied to degenerately dope the contact area of the 2D materials. Since doping happens during the growth of the crystal, it is impossible to dope selective area. But, we can use these degenerately doped 2D material along with undoped channel for various applications like *p-n* junction or 2D-2D contacts.

#### **1.1.8 Metal-Semiconductor Contact**

The main problem with TMDCs electronic devices is the contact as it often fails to form ohmic contact with the electrode metal. The mismatch in work function between TMDCs channel and the electrode metal forms a barrier at the metal semiconductor interface. With Ti (work function of 4.33 eV) as electrode metal, few layer  $MoS_2$  shows strong electron conduction, while p-

8

type transport is not observed due to the formation of large Schottky barrier (SB) at the interface. In case of WSe<sub>2</sub> FET, ambipolar behavior is seen when contacted with Ti metal. As the fermi level of WSe<sub>2</sub> lies at the middle of the band gap, a relatively small SB forms for both n-type and p-type conduction allowing both n-type and p-type conduction. Fig. 1.3 shows the barrier formation at metal-semiconductor interface for MoS<sub>2</sub> and WSe<sub>2</sub> with three different metals. As shown in 1.3(a) for MoS<sub>2</sub>-metal contact, fermi level of the metal is close to the conduction band of MoS<sub>2</sub> forming small barrier for electron conduction and very large barrier for hole conduction. For WSe<sub>2</sub>, fermi level of metal lies close to the middle of the band gap forming significant barrier for both electron and hole conduction. This explains the n-type behavior of MOS<sub>2</sub> and ambipolar conduction in WSe<sub>2</sub>.

**Figure 1. 1.** Schematic diagram of the barrier formation at metal-semiconductor interface<sup>70</sup>. Three metals with different work functions are shown, (a) Metal-MoS2 interface, fermi level of the metal is close to the conduction band allowing n-type transport and (b) Metal-WSe2 interface, fermi levels of metals are close to the middle of the band gap, forming barrier for both type of conduction.

Low resistive ohmic contacts are essential for FETs. However, semiconductors with large band gap have trouble in formation of ohmic contact with metal electrodes. There are few ways to deal with the problem. Firstly, low resistance ohmic contact can be achieved between metal and semiconductor by suitable choice of metal electrode. For n-type semiconductor like MoS<sub>2</sub>, small work function metal forms ohmic contact. In such case the fermi level of the metal lies close to the conduction band of the semiconductor allowing almost zero barrier. However, the work function of commonly used metal is over 4 eV (Ti, Al) or 5 eV (Pd, Ni). In addition to the small work function, the metal should highly conductive as well as thermally & chemically stable. Ca has low work function (2.9 eV) but oxidizes easily leading to degradation in performance. It is difficult to find the low work function metal satisfying the conditions. Similarly, for p-type semiconductor like WSe<sub>2</sub>, work function of the metal should be large so that the fermi level of the metal aligns close to the valence band of the semi-conductor allowing the formation of low barrier. This is equally difficult to find such metal. Although, high work function metals made good contacts with monolayer WSe<sub>2</sub>, SB has not been eliminated completely<sup>71</sup>. Another way to deal with the problem is to make Schottky junctions narrow, so that the tunneling current defines the contact resistance. Using large ionized impurity doping in semiconductor, the SB height can be decreased and low contact resistance can be achieved<sup>72</sup>. But due to the 2D nature of TMDCs, any attempt to dope it results in deterioration of channel.

#### **1.1.9 Contact Engineering**

Low resistance ohmic contacts between a metal and a semiconductor can be achieved either by a) lowering the SB height by suitable choice of contact metals or by b) degenerately doping the contact area. In subsections below, we are going to discuss both methods in detail:

#### **1.1.9.1** Lowering Schottky Barrier height

Low work function metals like scandium (Sc) have been shown low Schottky barrier height and low resistance in  $MoS_2$  FETs. However, because of the fermi level pinning, the range for the barrier adjustment is small and only applicable if pinning location is close to the band edge. If depinning is complete, ohmic contacts can be obtained easily for all TMDCs by selecting a metal with the fermi level lying above the conduction band or below the valence band for *n*-type or *p*-type FETs. Although the origin of the fermi level is not understood fully, it is at least partially dependent on metal-semiconductor interactions which induce states within the bandgap near the interface<sup>73,74</sup>. Thus, if an ultra-thin layer of insulator is used to separate metal and semiconductor, the insulator attenuates the metal electron wave function before penetrating the 2D semiconductor, reduces the density of induced states, which prevents fermi level to moving from charge neutrality level<sup>75</sup>. The dipole formed at the interface also help to decrease the SB height. However, the insulator layer increases the tunneling barrier for the carrier injection. The specific contact resistivity of MoS<sub>2</sub> channel was found to be reduced in 2-3 orders by the insertion of 1.5 nm Ta<sub>2</sub>O<sub>5</sub> layer due to the reduction in SB height from ~95meV to ~30 meV<sup>75</sup>. But as the thickness of the insulator is increased the resistivity is also found to be increased monotonically.

Local hybridization of 2D semiconductor under metal electrodes also can provide an alternative way to ensure low resistive ohmic contacts. This can be done by using a strongly interacting metal and semi-conductor through covalent bonding. The strong covalent bonding of Mo contacts with monolayer MoS<sub>2</sub> has significantly reduced the SB height and improved contact resistance<sup>75</sup>. In contrary, the covalent bonding between MoS2 and metals like Ti, Ni etc. results in higher contact resistance<sup>76</sup>.

Another approach to reduce SB height is by transforming the 2D semi-conductor underneath the contacts into metal by phase engineering. About 60 -70% area of monolayer MoS<sub>2</sub> converted from semiconducting 2H phase to metallic 1T phase on immersed in n-butyl lithium. The n-butyl lithium donates charge to MOS<sub>2</sub>, converting it to 1T state. The 1T MoS<sub>2</sub> under contact forms sharp boundary with 2H channel and eliminates the SB, improving the contact resistance values as low as 200  $\Omega\mu m^{77.78}$ . Edge contacts are also a favorable option over top contacts for lowering SB heights because of favorable in-plane carrier injection with a high degree of covalency and small tunnel barrier<sup>79,80</sup>. As each layer can form edge contact, charge can be efficiently injected deep into 2D materials. Edge contacts are beneficial for scaling purposes as well as no overlap region is required. However, the fabrication of edge contacts is not easy with current techniques.

#### **1.1.9.2 Doping of Contacts**

Although different doping methods are studied over the years to achieve low resistance ohmic contacts for 2D TMDCs material, most of these methods suffer from the lack of air or thermal stability. Furthermore, selective area doping is not possible as in the case of Si-based FETs. In Si-based devices heavy ion implantation doping of the source and drain area forms highly transparent barrier free contacts with the metal. But in case of TMDCs channel, due to the 2D nature of the material it is not possible without compromising the structural integrity of the channel. In section below, we will discuss the methods that have been used to dope the contacts for 2D TMDCs channel.

#### 1.1.9.2.1 Ionic liquid gating

In this approach to improve the contacts of MoS2 FETs, Ionic Liquid (IL) gating is used, which forms an electric double layer with high capacitance at MoS2/metal interface. As a result, IL gated MoS2 FETs demonstrate high tunneling efficiency and thus low contact resistance due to the strong band-bending occurring at MoS<sub>2</sub>/metal interface.

#### 1.1.9.2.2 Low resistance Graphene contacts tuned by double layer Ionic liquid

In this approach, Graphene has been used as a tunable electrode material to achieve low resistance ohmic contacts for ultrathin channel of TMDCs. Because of the large band gap of TMDCs material, large range tunability is required in order to achieve true ohmic contacts for both

*n*-type and *p*-type conduction. In this method, the large electric double layer (EDL) capacitance of Ionic liquid (IL) tunes the carrier density of graphene and forms low resistance contacts with the TMDC channel. An ionic liquid gate induces high carrier density in graphene in the order of  $10^{14}$  cm<sup>-2</sup>, which is an order more than using a conventional solid-state gate dielectric<sup>71</sup>.

#### 1.1.9.2.3 2D-2D contact electrode

One of the useful advantage of 2D TMDCs is the ability to form heterostructures by stacking different materials in vdW assembly. Since TMDCs do not possess dangling bonds they form ultraclean and sharp interfaces. Thin layers of MoS<sub>2</sub> and WSe<sub>2</sub> have been stacked in vdW assembly to form atomically thin *p*-*n* junction<sup>84–87</sup>. The built-in potential in these thin atomic *p*-*n* junction is dropped across vdW gap due to the absence of obvious depletion region as in the case of bulk *p*-*n* junctions. The charge transport across the junction is dominated by the tunneling current through the vdW gap. This results in fast charge transfer across the junction, which is verified by recent findings of strong photocurrents and quenching of photoluminescence signals in study of MoS<sub>2</sub>/WSe<sub>2</sub> *p*-*n* junctions. Low resistance ohmic contacts have been observed for both electron and hole transport for WSe<sub>2</sub> FETs using substitutionally doped 2D contacts.

#### 1.1.10 High K Di-electric Integration

In past few decades, we experienced a heavy reduction in dimension of electronic devices. This reduction in the size of devices is achieved by reducing the size of key components of those circuits: The 'MOSFET'. This reduction in dimension allows the integration of a large number of transistors on a chip, enabling higher speed and reduced cost. The scaling of MOSFET follows the famous Moore's Law<sup>88</sup>. As shown in figure 2, Moore's law predicts exponential increase of transistors density on a chip.

The scaling of MOSFET results to smaller devices in smaller area, consumption of less power and decrease in cost per transistor. But, this downscaling of MOSFET cannot go forever, as it is limited by short channel effect. Short channel effect depends up on the thickness and dielectric constant of the used dielectric. Gate oxide thickness must be reduced as channel length is reduced in order to avoid short channel effects<sup>89</sup>. As a thickness of SiO<sub>2</sub> gate insulators is reduced to few atomic layers, charge carriers can flow through the gate dielectric by a quantum tunneling mechanism<sup>90,91</sup>. This mechanism involves the tunneling of charge carriers through a trapezoidal energy barrier<sup>92</sup>. It is seen that the tunneling probability increases exponentially as the thickness of SiO<sub>2</sub> layer decreases<sup>90,92</sup>. In addition to the gate leakage current, the reduction in width of gate oxide also causes a reduction in the ON/OFF ratios<sup>89</sup>.

Figure 1. 2. Graphical representation of Moore's law<sup>93</sup>.

During the operation of MOSFETs, charge carriers flow through the device resulting the generation of defects in SiO<sub>2</sub>/Si interface<sup>94–96</sup>. When a critical density of defect is reached, break-down of the gate layer occurs, resulting in the failure of the device<sup>97–99</sup>. The SiO<sub>2</sub> thickness limit was found to be 2.2 nm at room temperature and 2.8 nm at 150° C<sup>94,97</sup>.

#### 1.1.11 High-K Dielectrics

The electrostatic control of the channel by the gate is achieved through capacitive coupling between the gate and channel region through the gate dielectric. Scaling requires reduction in the depth of source and drain regions by the same factor as the gate length, as this would require less control over channel. As the capacitance of the system depends inversely on the thickness of the dielectric, this can also be done by decreasing the thickness of the dielectric. The inefficiency of SiO<sub>2</sub> to decrease further as per device scaling required the replacement of the insulator with high K (Dielectric Strength) dielectric oxides<sup>97</sup>, to increase its thickness and thus preventing the charge carriers from tunneling while retaining the electronic properties of SiO<sub>2</sub> layer. The metal oxide semiconductor structure in MOSFET acts like a parallel plate capacitor. The capacitance of the structure is given as,

$$C = \frac{A\varepsilon_r\varepsilon_0}{t_{ox}}$$

Where, A is the capacitor area,  $\mathcal{E}_r$  is the relative dielectric constant of the material,  $\mathcal{E}_0$ , the permittivity of free space (8.85 x 10<sup>-12</sup> Fm<sup>-1</sup>), and t<sub>ox</sub> is the gate oxide thickness.

As SiO<sub>2</sub> has approached its limit, an alternative way to increase capacitance is to use an insulator with higher relative dielectric constant than SiO<sub>2</sub> ( $\kappa = 3.9$  for SiO<sub>2</sub>). Then we can use the thicker gate layer and hopefully can reduce the leakage current and improve the reliability of the gate dielectric. The thickness of hig- $\kappa$  dielectric is usually expressed in terms of equivalent oxide thickness (t<sub>eq</sub>). The equivalent oxide thickness of a material is defined as the thickness of SiO<sub>2</sub> layer that would be required to achieve the same capacitance density as the high K material in approaches  $\frac{t_{eq}}{r_{eq}} = \frac{t_{high k}}{r_{eq}}$

consideration,  $\frac{t_{eq}}{\varepsilon_{r,SiO2}} = \frac{t_{high \ k}}{\varepsilon_{r,high \ k}}$

Where,  $t_{high k}$  and  $\mathcal{E}_{r,high k}$  are the thickness and dielectric constant of high K dielectric material. Recently, a lot of efforts have focused to investigate high-K gate dielectrics<sup>98–105</sup>. The equivalent oxide thickness is found to be 1.1 nm (for Al<sub>x</sub>Zr<sub>1-x</sub>O<sub>2</sub> layer). Also, the leakage current is reduced by several orders of magnitude. High- $\kappa$  dielectric seemed to be resolving the scaling problem of SiO<sub>2</sub>, but the high K dielectric material, which could replace SiO<sub>2</sub> as a gate dielectric should satisfy few requirements<sup>106</sup>:

- thermal stability

- preventing the formation of thick interfacial low-K dielectric layer

- low density of intrinsic defects at Si interface

- sufficient gate dielectric lifetime

- sufficiently large energy band gap, to reduce leakage current

#### **1.1.11.1 Possible Candidates**

The hexagonal boron nitride (hBN) is an excellent choice for the substrate as it is atomically smooth and have low interface traps but the low dielectric constant limited its use in form of dielectric in FET devices. There are several high- $\kappa$  dielectrics, which have been studied for replacing SiO<sub>2</sub>. A list of dielectrics and their properties is given in table 1.1.

The most likely high  $\kappa$  dielectrics as a replacement of SiO<sub>2</sub> are zirconium dioxide (ZrO<sub>2</sub>)<sup>107</sup>, hafnium dioxide (HfO<sub>2</sub><sup>108,109</sup>), aluminium oxide (Al<sub>2</sub>O<sub>3</sub><sup>110</sup>), titanium dioxide (TiO<sub>2</sub><sup>111</sup>), tantalum pentoxide (Ta<sub>2</sub>O<sub>5</sub><sup>112,113</sup>) etc. The oxide film growth of the dielectric thin films is critical as extremely reliable high quality thin dielectric films are required. Several thin film growth techniques have been used such as thermal evaporation, atomic layer deposition (ALD), chemical vapor deposition (CVD), pulsed laser deposition (PLD), and molecular beam epitaxy (MBE)<sup>114–118</sup>.

| Material                       | Dielectric constant (k) | Band gap $E_{\rm G}$ (eV) | Band offset $\Delta E_{\rm C}$ (eV) to Si | Band offset $\Delta E_{\rm C}$ (eV) to Ge | Crystal structure             |

|--------------------------------|-------------------------|---------------------------|-------------------------------------------|-------------------------------------------|-------------------------------|

| SiO <sub>2</sub>               | 3.9                     | 8.9                       | 3.2                                       |                                           | Amorphous                     |

| $Al_2O_3$                      | 9                       | 8.7                       | 2.8                                       | 2.6 [24]                                  | Amorphous                     |

| Si <sub>3</sub> N <sub>4</sub> |                         |                           |                                           |                                           | Amorphous                     |

| TiO <sub>2</sub>               | 80-100                  | 3.5                       | 1.2                                       |                                           | Tetragonal                    |

| $Ta_2O_5$                      | 26                      | 4.5                       | 1-1.5                                     |                                           | Orthorhombic                  |

| $HfO_2$                        | 25                      | 5.7                       | 1.4                                       | $2.0 \pm 0.1$ [25]                        | Monoclinic, tetragonal, cubic |

| ZrO <sub>2</sub>               | 25                      | 7.8                       | 1.5                                       |                                           | Monoclinic, tetragonal, cubic |

| $La_2O_3$                      | 30                      | 4.3                       | 2.3                                       | 2.56 [24]                                 | Hexagonal, cubic              |

| $Y_2O_3$                       | 15                      | 5.6                       | 2.3                                       | 2.56 [24]                                 | Cubic                         |

| $Gd_2O_3$                      | 24 ± 2 [6]              |                           |                                           | 2.44 [24]                                 |                               |

| MgO                            | 9.8 [7]                 | 7.3 [7]                   |                                           |                                           | Cubic                         |

| $Er_2O_3$                      | 14.4 [8]                | 7.5 [8]                   | 3.5 [8]                                   |                                           |                               |

| $Nd_2O_3$                      |                         | 5.8 [9]                   | 2.2 [9]                                   |                                           |                               |

| PrO <sub>2</sub>               | 25 [10]                 | 3-4 [10]                  | >1 [10]                                   |                                           | Cubic                         |

| CeO <sub>2</sub>               | 52 [11], 26 [12]        | 4.5 [12]                  |                                           |                                           |                               |

| LaAlO <sub>3</sub>             | 26 [13]                 | 6.0 [10]                  |                                           | 2.2 [24]                                  |                               |

| ZrSiO <sub>4</sub>             |                         |                           |                                           |                                           | Amorphous                     |

| HfSiO <sub>4</sub>             |                         |                           |                                           | 2.2 [24]                                  | Amorphous                     |

| $(Dy_2O_3)$                    | 14                      | 4.8                       |                                           |                                           |                               |

Table 1. 1. List of High K dielectrics

89

#### 1.1.11.2 Challenges with High K Dielectric Integration of TMDCs

For the enhancement of the device, TMD as channel, the growth of conformal, uniform high K dielectric is necessary. The high K dielectric integration study so far has been based on different growth methods (CVD, ALD, PLD, MBE, etc.). With these complex growth methods, the interface has always been issue. ALD is supposed to be more reliable deposition in case of TMDs. McDonnell et. al., (2013) deposited of HfO2 on the MoS2 surface using Atomic layer deposition (ALD) method<sup>119</sup>, and found that the ALD on MoS<sub>2</sub> was not uniform. They could not detect covalent bonding between the HfO<sub>2</sub> and MoS<sub>2</sub>. In another study, when 15-17 nm HfO<sub>2</sub> is deposited by ALD, island type growth was observed resulting in non-uniform films<sup>120</sup>. In their study, Lembke et al., (2015) found that, due to the absence of out of plane covalent functional group in MoS<sub>2</sub>, surface functionalization is needed to fabricate scaled two-dimensional layered devices using ALD<sup>8</sup>. The problem of high K dielectric integration of TMDCs has not been resolved yet. In this dissertation, we will discuss a new approach to form atomically thin High K dielectric from thermal oxidation of the semi-metallic TMDCs.

#### **1.2 Scope of the Study**

This dissertation is focused on developing new methods to fabricate TMDC based 2D electronic devices such as p-n junction diodes and FETs. We can divide this work into two parts: i) 2D p-n junction diodes and ii) High K dielectric integration in 2D electronics. In first part, we fabricated 2D p-n junction diodes (homo/hetero structures) using heavily p-doped (Nb-MoS<sub>2</sub>) and slightly n-doped (MoS<sub>2</sub>/WSe<sub>2</sub>) semiconducting TMDCs. Chapter 3 describes in detail the fabrication and characterization of atomically thin p-n junction diodes made from 2D TMDCs. In the second part, we developed a new approach to achieve ultrathin high K dielectric using thermal oxidation process. We chemically transformed the metallic TMDCs into their oxides, characterized them and used them as a dielectric material in FETs with semiconducting TMDCs as the channel. In Chapter 4, we successfully converted TaS<sub>2</sub> into Ta<sub>2</sub>O<sub>5</sub> using thermal oxidation process and used as a high K dielectric in MoS<sub>2</sub> FETs. We followed the same method of oxidation for another metallic semiconductor in Chapter 5, where we successfully converted HfSe<sub>2</sub> into HfO<sub>2</sub> and measured the dielectric constant and the leakage current. Further characterization of chemically converted HfO<sub>2</sub> and its potential application in FETs is described in Future works section.

#### **CHAPTER 2: EXPERIMENTAL METHODS**

This dissertation is focused on the study of two-dimensional materials. During the period of this dissertation, we studied different devices including 2D-2D *p-n* junction diodes, Metal Insulator Metal junction diodes, Field effect transistors etc., based on two-dimensional semiconductors and ultrathin dielectrics converted from 2D semiconductors along with Graphene and hexagonal Boron Nitride (h-BN). We fabricated those devices and characterized to understand them. In this chapter, we will discuss in detail about the fabrication process of the devices that we studied and the techniques used to characterize them. This chapter is divided into two parts; in the first part, we will discuss about the device fabrication and in the second part we will talk about the characterization technique.

#### **2.1 Device Fabrication**

Our study mostly used the two-dimensional materials as a channel or dielectric material for the purpose of device fabrication. We used  $Si/SiO_2$  as the substrate for device fabrication. We cleaned the substrate with Acetone, Isopropanol (IPA) and Deionized (DI) subsequently in ultrasonic bath. After cleaning, the substrate is annealed in ULVAC MILA-5000 annealing tool. We used the mechanical cleavage technique to exfoliate the few-layer samples on low residue scotch tape from the bulk sample and transferred to the substrate. After assembling the required structure of the device, we defined electrodes on the device with the help of e-beam lithography, and finally deposited metal on those electrodes to make electrical connections. The sections below will explain each step of the fabrication in detail.

#### **2.1.1 Crystal synthesis**

WSe<sub>2</sub>, Nb-WSe<sub>2</sub> and Nb-MoS<sub>2</sub> crystals were synthesized by chemical vapour transport using iodine as the transport agent. MoS<sub>2</sub>, Graphite and hBN crystals were purchased from manufacturers SPI Supplies and 2D semiconductor supplies. All TMDC crystals were synthesized by chemical vapour transport using iodine as a transport agent. For our study, high-quality single crystals were provided by Dr David Mandrus' group at the University of Tennessee. In case of doped samples, 0.5% of Niobium (Rhenium) was used as substituent atoms for p-doping (n-doping)<sup>69</sup>.

#### **2.1.2 Substrate preparation**

We used degenerately doped silicon substrate with 270 nm thick oxide layer with prefabricated gold alignments, as a substrate. We first cleaned the substrate by sonicating it in acetone for 20 minutes followed by sonicating in Isopropanol (IPA) for another 20 minutes. acetone helps to remove organic polar residues, while Isopropanol helps to remove non-polar residues. Both acetone and IPA evaporates at a faster rate and in the process may redeposit remnants. In the end, we cleaned the substrate with deionized (DI) water to completely wash out those residues and then dried by the jet of inert gas (N<sub>2</sub>/Ar). After cleaning the substrate, we examined them under optical microscope to ensure the condition of the substrate. The substrate having residue on it, or without alignment marks, or having some other problems were eliminated. The well dried substrate was then further cleaned by annealing in vacuum. Annealing of the substrate helps to remove the organic residues and moisture absorbed at the surface of the substrate from the atmosphere. We used ULVAC MILA-5000 annealing tool to anneal the substrate. The substrate were then annealed at 600° C for 10 minutes with passing forming gas for 2 minutes, when temperature of the substrate just reaches 600° C.

Figure 2. 1. ULVAC MILA-5000 annealer.

### 2.1.3 Sample Preparation

Two-dimensional layered materials are strongly bounded in the plane by a covalent bond, but the inter-layer attraction is weak due to the presence of long-range van der Waals force. Due to the weak interlayer attraction, the layers can be peeled off easily. We used mechanical cleavage method<sup>10</sup> to exfoliate few layers TMDCs material on scotch tape. For this, we took a small bulk crystal of the material and peeled off the layers repeatedly for several times until we get sample thinned to few layers. We then transferred the samples to the substrate in different ways per the need. The different methods we used to transfer sample to substrates are explained below:

### 2.1.3.1 Exfoliation on substrate

Most of the time, we transferred the exfoliated sample on cleaned Si/Sio<sub>2</sub> substrate directly. We placed the substrate on the scotch tape with the alignment side of the substrate over the sample and pressed gently for few minutes. This will transfer the sample from scotch tape to the substrate. Then we examined the substrate under the optical microscope and located thin uniform samples based on colour contrast. To get the exact information about thickness and uniformity, we did AFM characterization later.

**Figure 2. 2**. Schematic diagram representing mechanical exfoliation of two-dimensional TMDCs sample. a) a small portion of bulk material is taken on the scotch tape b) peel off repeatedly the sample until we get few layers thick c) after getting few layers thick sample, scotch tape is stamped over the substrate and pressed uniformly for few minutes d) scotch tape is gently removed, samples are now attached to the substrate.

# 2.1.3.2 PDMS assisted transfer

When we need to transfer one 2D sample over another, we cannot use direct exfoliation to the substrate method. In such cases, we used PDMS assisted transfer method. PDMS is a Siliconbased organic polymer, known for its viscoelastic properties. PDMS can be used as an elastic stamp to transfer samples of nanometer dimension. The PDMS patches were prepared from SYL-GARD 184 SILICONE ELASTOMER kit. It has two parts: Elastomer base, and curing agent as shown in Fig. 2.3.

**Figure 2. 3**. Sylgard 184 silicone curing agent and elastomer (respectively from left to right). A mixture of these two is spin coated and baked to prepare PDMS polymer.

A mixture of 184 silicone elastomer and curing agent with the weight ratio of 10:1 is thoroughly mixed and the mixture is placed in a vacuum chamber for 20 minutes to remove air bubbles from the mixture. For one batch, we mixed 7 gm of elastomer with 0.7 gm of the curing agent. After 20 minutes in vacuum, the mixture is spin coated onto a clean polished 4 inches silicon wafer at a spin rate of 350 rpm for 35sec. The thickness of PDMS was approximately 300-500µm. We placed the coated wafer onto a hot plate to bake at 80°C for 30 minutes in air and left another 30 minutes to cool down<sup>121</sup>. As the PDMS patch is prepared on the wafer, we cut down the patch into small pieces for the ease of handling.

**Figure 2. 4**. Schematic diagram showing the process of dry transfer Sample transfer using DMS layer a) PDMS patch with the sample is put on the glass slide b) With the help of micromanipulator, the sample is transferred to the substrate.

We placed small patches of PDMS above the exfoliated layer of the sample on scotch tape, this would transfer the sample from scotch tape to the PDMS patch. We located the sample under an optical microscope and transferred to the precise location with the help of micromanipulator. After transfer, we annealed the substrate at 250° C for 30 minutes in vacuum to remove any residue introduced during the transfer and increase the attachment.

#### 2.1.3.3 PC pickup

Another method, we extensively used for sample transfer is PC pickup method. This method enables to transfer sample which is already on the substrate, to the precise location of another substrate. This method is very useful when you needed thinner samples to transfer. Usu-

ally, the sample exfoliated on PDMS are thicker than those exfoliated on the substrate. We prepared PC solution by dissolving 0.18 gm Polycarbonate (PC) on 3 gm of Chloroform uniformly. We applied a layer of PC on the substrate and kept a patch of PDMS covering the sample containing a portion of the substrate. We carefully removed the PC layer from the substrate except the area covered by the PDMS patch. We scratched along the edge of PDMS and applied Deionized (DI) water. The substrate surface being hydrophobic, DI water helps to pick up the sample from the substrate. Then, we carefully picked up PDMS along with the PC layer containing the sample. We transferred the sample to the desired location with the help of micromanipulator. For this method, we applied heat after touching down to melt the PC layer. Then the substrate was immersed in chloroform for 10-15 minutes to remove PC layer. The substrate was then blow dried with inert gas jet and annealed at 250° C for 30 minutes in vacuum.

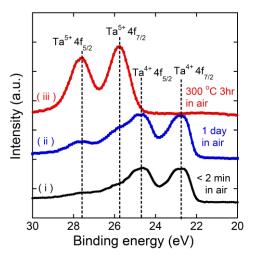

#### 2.1.4 Thermal Oxidation

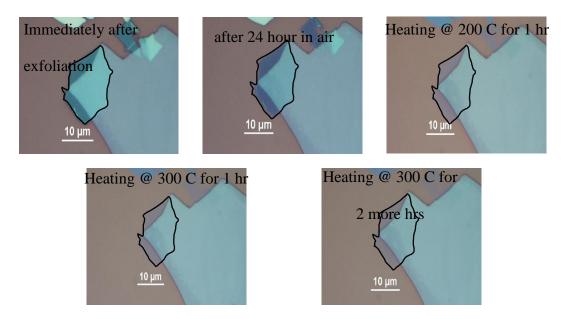

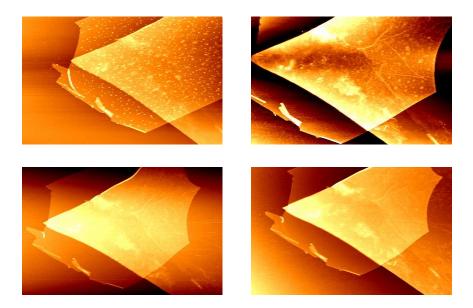

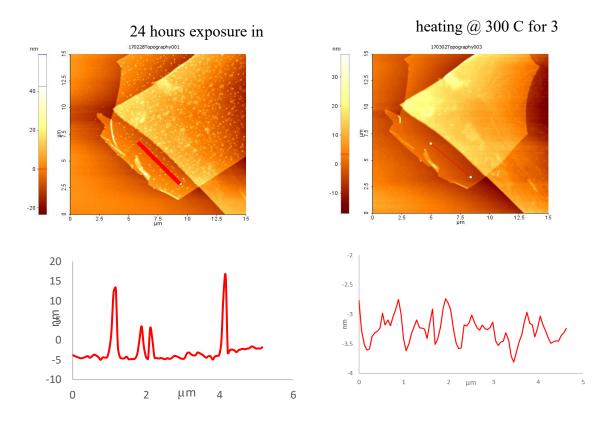

Some of our projects are based on the thermal oxidation of TMDCs material. We used the heating method to oxidize TaS<sub>2</sub> (HfSe<sub>2</sub>). We heated the TaS<sub>2</sub> (HfSe<sub>2</sub>) of different thickness for a different period. We monitored the change in colour contrast and thickness of the sample. After few trials, we realized, for TaS<sub>2</sub> (HfSe<sub>2</sub>) heating at 300° C for 3 hours is sufficient to convert it to oxide. We exfoliated sample on the substrate and located them with the help of an optical microscope. We heated the substrate with the sample in it to 300° C for 3 hours in ambient condition. The sample was characterized by AFM before and after heating. Figure 2.5 shows an optical image of the sample before and after heating. Figure 2.5a shows the TaS<sub>2</sub> sample immediately after exfoliation. The sample is then heated on a hot plate for 3 hours at 300° C. Figure 2.5b is the image of the same sample after oxidation. Significant change in color contrast of the sample is seen due to the phase change of the sample. This fact is supported by TEM, XPS characterization as well.

**Figure 2. 5.** Thermal oxidation of  $TaS_2$ . a)  $TaS_2$  sample immediately after exfoliation b) Thermally oxidized  $TaS_2$  after heating on a hot plate at 300° C for 3 hours.

# 2.1.5 Electrode Fabrication

To measure the electrical properties of the device, we fabricated the electrodes on the sample to make electric connections. The fabrication process involves several steps: coating resist, designing electrodes, printing those designs on the resist, removing resist from the selective area, metal deposition and finally lift off metal from the area except the electrodes. These steps are explained in detail below:

# 2.1.5.1 PMMA coating

Polymethyl methacrylate (PMMA) is a polymeric material that is commonly used for various imaging and non-imaging microelectronic applications. It is used as a positive resist for ebeam lithography. Upon exposed with an electron beam, the polymer chain will be broken. That broken chain will be easily dissolved in developer solution exposing the area to deposit metal on. In this way, we can selectively choose the area and deposit metal for electrode fabrication. The substrate was spin-coated with 2 layers of 495A4 PMMA followed by a single layer of 950A2 PMMA at 4500 rpm. Each coating layer was followed by baking the substrate on a hot plate at 180° C for 5 minutes. The thickness of 3 layers of PMMA was 360 nm.

## 2.1.5.2 Electrode design and E-beam lithography

We used Nano-pattern generation system (NPGS) AUTOCAD software to draw the electrode pattern that needed to write on the sample. With the help of the optical image, we defined the area of the sample, to be written electrode upon. We used the graph, generated using NPGS, to write electrodes on the substrate by e-beam lithography. E-beam lithography uses an electron beam to write a specific pattern on the substrate as directed by the design provided. Although e-beam lithography system is slow and little costly, it has already been commonly used in semiconductor industry for patterning a smaller feature size. The dedicated e-beam lithography instruments are expensive. Alternatively, SEM with dedicated e-beam writing column provides the solution at moderate pricing. Figure 2.6 shows the SEM system with the dedicated e-beam writing column attached to it.

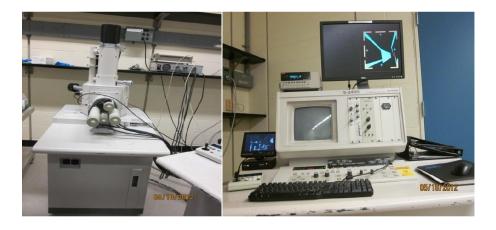

**Figure 2. 6**. Hitachi S-2400 Scanning Electron Microscope attached with E-beam writing column. It has the maximum accelerating voltage of 25 KV.

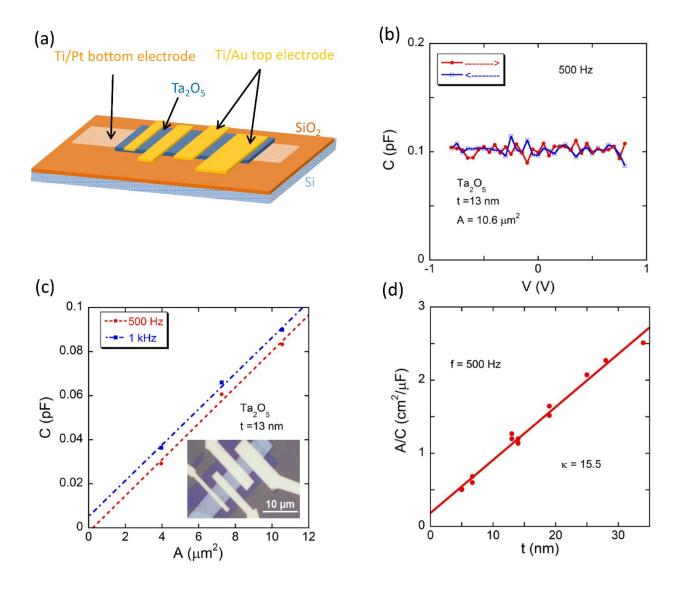

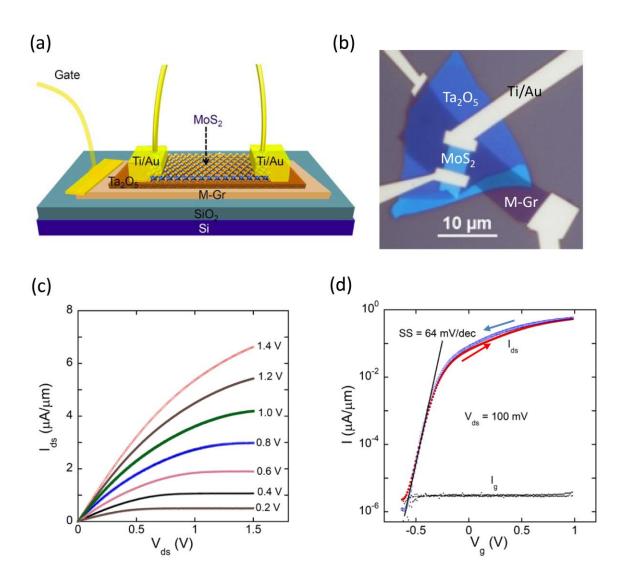

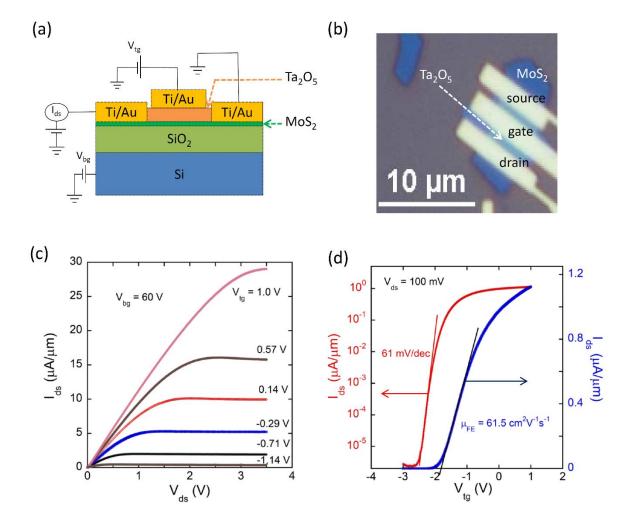

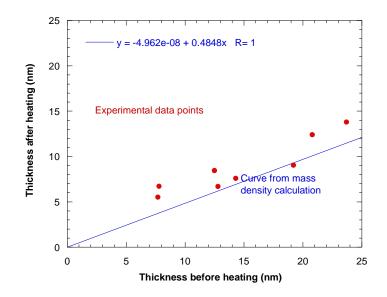

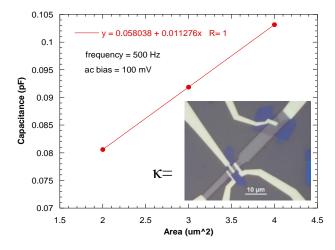

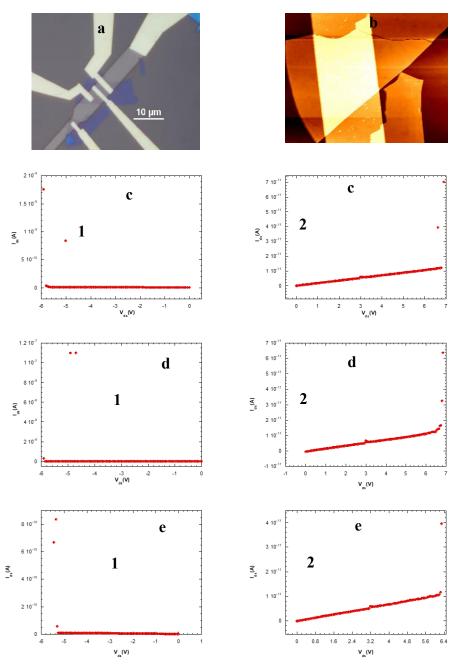

We used Hitachi S-2400 SEM system equipped with dedicated e-beam writing column to write the lithography patterns. In an SEM, a highly focused beam of electrons emitting from an electron gun travels through a vacuum and are guided by electromagnetic lenses. The electrons beam hit the substrate surface coated by polymer and interact with it to break its bond. The polymer area which is interacted with electrons beam is easily soluble in organic solvent. We optimized the SEM by adjusting beam current, fine focus with minimizing astigmatism of the focused electron beam and aligning the alignment marks on the substrate. We used the area dose of  $350 \,\mu c/cm^2$  and line dose 15  $\mu c/cm$  to write the pattern. When electron beam hits a certain area of the substrate, the polymer chain of the PMMA covering that area will be broken, which reacts with the developer solution and dissolves in the solution exposing the area. After e-beam writing is done, the substrate was dipped in MIBK/MEK developer solution for 1 minute to dissolve the broken loose PMMA particles and open the specific design electrodes. Figure 2.7 shows the e-beam pattern written on a substrate.