**ABSTRACT**

Title of Dissertation: EFFECTS OF GLASS/EPOXY

INTERPHASES ON ELECTRO-

CHEMICAL FAILURES IN PRINTED

**CIRCUIT BOARDS**

Bhanu Pratap Sood

Doctor of Philosophy (2018)

Dissertation directed by: Professor Michael Pecht

Department of Mechanical Engineering

Reduction in printed circuit board line spacing and via diameters and the increased density of vias with higher aspect ratios (ratio between the thickness of the board and the size of the drilled hole before plating) are making electronic products increasingly more susceptible to material and manufacturing defects. One failure mechanism of particular concern is conductive anodic filament formation, which typically occurs in two steps: degradation of the resin/glass fiber bond followed by an electrochemical reaction. The glass-resin bond degradation provides a path along which electrodeposition occurs due to electrochemical reactions. Once a path is formed, an aqueous layer, which enables the electrochemical reactions to take place, can develop through the adsorption, absorption, and capillary action of

moisture at the resin/fiber interphase. This study describes the experimental and analytical work undertaken to understand the glass-resin delamination and the methods used for analyzing this critical interphase.

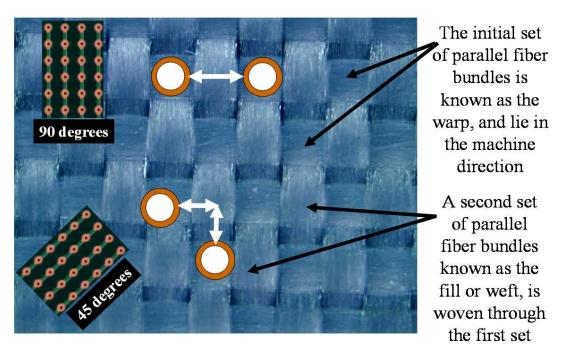

This study shows that a smaller conductor spacing in reduces the time to failure due to conductive anodic filament formation and that the plated-through-hole to plated-through-hole conductor geometry is more susceptible to conductive anodic filament-induced failures than plated through hole to plane geometries. The results also show that laminates with similar materials and geometries with a 45-degree angle of weave demonstrate a higher resistance to conductive anodic filament formation compared with a 90-degree angle of weave.

The study is the first of its kind conducted on FR-4 printed circuit board materials where the pathway formation due to breakage of the organosilane bonds at the glass/resin interphase was evaluated. Using techniques such as force spectroscopy, micro-Fourier transform infrared spectroscopy, scanning quantum interface device microscopy and focused ion beam, evidence of bond breakage and a pathway formation was revealed, poor glass treatment, hydrolysis of the silane glass finish (adsorption of water at the glass fiber/epoxy resin interphase) or repeated thermal cycling contribute to the bond breakage. The technique of applying in-situ resistance measurements during cross-sectioning analysis of printed circuit boards suspected of conductive anodic filament is the first time this method is described in the open literature. This solution addresses the potential problem in destructive physical analysis of grinding away the evidence of the CAF filament and ultimately loosing evidence at the failure site.

By applying a subset of the evaluation criteria described in this research, an upfront evaluation of printed circuit board materials can be performed for susceptibility to electro-chemical migration and other failure causes in PCBs that are attributable to the glass/resin interfacial adhesion. Manufacturers can identify board suppliers based on answers to and validation of a series of questions. These questions focus on the necessary requirements of reliable board material manufacturing and are independent of the specifications of the product.

# EFFECTS OF GLASS/EPOXY INTERPHASES ON ELECTRO-CHEMICAL FAILURES IN PRINTED CIRCUIT BOARDS

by

### Bhanu Pratap Sood

Dissertation submitted to the Faculty of the Graduate School of the

University of Maryland, College Park, in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

2019

### Advisory Committee:

Professor Michael Pecht, Chair

Professor Peter Sandborn

Professor Patrick McCluskey

Professor Bongtae Han

Professor Lourdes Salamanca-Riba

Dr. David McElfresh

© Copyright by

Bhanu Pratap Sood

2018

# Dedication

I dedicate this thesis to my wife Reena, and my children Zoya and Yuvaan. Thank you Reena for believing in me, you are a constant source of support and encouragement. I am truly thankful for having you in my life.

A special feeling of gratitude to my loving parents, Mrs. and Col. Bhupender Kumar Sood and my sister Bhawna whose words of encouragement and push for tenacity ring in my ears.

## Acknowledgements

In many ways, this dissertation reflects the culmination of the last fourteen years of my time spent at the University of Maryland as a staff member, as CALCE Laboratory Director and as a student. I would be remiss not to thank those who have provided guidance and have helped shape me into the person I am today. Without question, I would like to start by acknowledging the support and guidance provided to me by my advisor, Professor Michael Pecht, for helping me with his technical acumen, challenging me and constantly providing new perspectives. I would like to thank my committee members, Professor Bongtae Han for his encouragement, Professor Patrick McCluskey, Professor Peter Sandborn, Professor Lourdes Salamanca-Riba and Dr. David McElfresh for their valuable guidance and agreeing to become my dissertation committee members.

Thanks to Dr. Carlos Morillo for his support with Fourier transform infrared spectroscopy measurements, Dr. Babak Eslami and Mr. Miead Nik for assistance with force spectroscopy. Thanks are in order to the "Pecht group" staff, faculty and students, Dr. Michael Osterman, Dr. Michael Azarian, Dr. Diganta Das.

Special thanks to Alisha Willis, NASA Academic Investment for Mission Success program, Dr. John Evans and Anthony Diventi at NASA Office of Safety and Mission Assurance and, Nancy Lindsey, Reliability and Risk Analysis Branch at NASA Goddard for their support.

# Table of Contents

| Dedica  | ationii                             |

|---------|-------------------------------------|

| Ackno   | w ledgementsiii                     |

| Table   | of Contentsiv                       |

| List of | Tablesviii                          |

| List of | Figuresix                           |

| Chapte  | er 1: Introduction1                 |

| 1.1.    | Printed Circuit Boards              |

| 1.2.    | Materials and Processes             |

| 1.3.    | Constituents6                       |

| 1.3.1.  | Glass Reinforcements                |

| 1.3.2.  | Resin System9                       |

| 1.3.3.  | Interphases Between Resin and Glass |

| 1.3.4.  | Sizing Agents                       |

| 1.3.5.  | Curing Agents                       |

| 1.3.6.  | Flame Retardants                    |

| 1.4.    | Lamination Process                  |

| 1.5.   | PCB Fabrication Process                                             |  |

|--------|---------------------------------------------------------------------|--|

| 1.5.1. | Single Sided Boards                                                 |  |

| 1.5.2. | Multilayer Boards                                                   |  |

| 1.6.   | Process Control and Inspections                                     |  |

| 1.7.   | Faults in Multi-layer Manufacturing Process                         |  |

| 1.8.   | Cost of Multi-layered Boards                                        |  |

| 1.9.   | Printed Circuit Board Failure Modes and Causes                      |  |

| 1.9.1. | Open Circuit                                                        |  |

| 1.9.2. | Short Circuit                                                       |  |

| 1.9.3. | Delamination                                                        |  |

| 1.10.  | Lead-Free Solder and Effects on PCBs                                |  |

| 1.11.  | Summary                                                             |  |

| Chapte | er 2: Conductive Anodic Filaments in Printed Circuit Boards         |  |

| 2.1    | Introduction                                                        |  |

| 2.2    | Literature Review                                                   |  |

| Chapte | er 3: Experiments to Characterize CAF Behavior in Laminated PCBs 58 |  |

| 3.1    | Introduction and Experimental Procedure                             |  |

| 3.2    | Test Sample Fabrication                                             |  |

| 3.3  | Sample Preconditioning and Testing                                      | 62   |

|------|-------------------------------------------------------------------------|------|

| 3.4  | Results and Discussion                                                  | 65   |

| 3.5  | Summary                                                                 | 71   |

| Chap | ter 4: Experiments to Characterize the Effect of Epoxy/Glass Interphase | s on |

| CAF  | Failures in Printed Circuit Boards                                      | 73   |

| 4.1  | Introduction and Experimental Procedure                                 | 73   |

| 4.2  | Nano-indentation Study                                                  | 86   |

| 4.3  | Results and Discussion                                                  | 88   |

| Chap | ter 5: Experiments to Inspect Epoxy/Glass Interphases Using FT-IT and   | l    |

| AFM  | Atomic Force Spectroscopy                                               | 92   |

| 5.1  | Introduction and Experimental Procedure                                 | 92   |

| 5.2  | Fourier Transform Infrared (FTIR) spectroscopy Analysis                 | 93   |

| 5.3  | AFM Force Spectroscopy Analysis                                         | 97   |

| 5.4  | Summary of FT-IR and AFM Studies                                        | 102  |

| Chap | ter 6: Focused Ion Beam Inspection of Glass-Resin Interphases           | 105  |

| 6.1  | Introduction                                                            | 105  |

| 6.2  | Focused Ion beam (FIB) Inspection                                       | 108  |

| Chap | ter 7: Path Formation in CAF                                            | 113  |

| 7.1    | Path Caused by Mechanical Degradation                        |  |

|--------|--------------------------------------------------------------|--|

| 7.2    | Path Caused by Hollow Fibers                                 |  |

| 7.3    | Path Caused by Cracks in Resin Filler Particles              |  |

| 7.4    | Path Caused by Chemical Degradation                          |  |

| 7.4.1  | Halogen-free and Lead-free                                   |  |

| 7.5    | Path Formation – Summary                                     |  |

| 7.6    | Influence of Path Formation on CAF Time-to-Failure           |  |

| Chapte | er 8: Conclusions                                            |  |

| Chapte | er 9: Contributions                                          |  |

| Chapte | er 10: Future Work                                           |  |

| 10.1   | Further Studies on Quantifying the Reduction in Modulus      |  |

| 10.2   | In-situ Humidity Exposures                                   |  |

| 10.3   | Variations in Glass Transition Temperature of the Interphase |  |

| Appen  | dix A: Controlling Moisture in Printed Circuit Boards        |  |

| Appen  | dix B: Use of SQUID Microscopy for CAF Site Isolation155     |  |

| Biblio | graphy159                                                    |  |

# List of Tables

| Table 1 Basic NEMA classification for commonly used materials [2]   | 4         |

|---------------------------------------------------------------------|-----------|

| Table 2: Typical constituents of FR-4 laminates [69].               | 5         |

| Table 3: Typical composition of E-grade glass                       | 7         |

| Table 4: Typical bond energies                                      | 18        |

| Table 5 Cost Comparison for PCB (Approx. Cents per Hole) [13]       | 30        |

| Table 6: Test Conditions                                            | 64        |

| Table 7: Experimental Results                                       | 67        |

| Table 8: Effect of Reflow on CAF Failures in PTH-PTH Geometries for | · Various |

| Laminate Types.                                                     | 69        |

| Table 9: Diffusion Coefficients (cm <sup>2</sup> /s)                | 143       |

# List of Figures

| Figure 1 Schematic representation of single, double, and multi layer boards 2                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2: FR-4 Laminate Fabrication [69]5                                                                                                                        |

| Figure 3 Schematic showing the glass fiber fabrication steps [8][9]                                                                                              |

| Figure 4: Typical glass-weave styles                                                                                                                             |

| Figure 5: Formation of DGEBA                                                                                                                                     |

| Figure 6: Tetra-functional and multi-functional epoxy monomers                                                                                                   |

| Figure 7 Schematic illustration of the glass-resin interphase                                                                                                    |

| Figure 8 Schematic showing the glass fibers being drawn from the forming bushings (top) into the sizing applicator roll (bottom) and further for processing [5]. |

| Figure 9: Typical structure of dicy and phenolic cured systems                                                                                                   |

| Figure 10 Tetrabromobisphenol A (TBBPA)                                                                                                                          |

| Figure 11 Typical 6-ply 7628 weave stack up. 21                                                                                                                  |

| Figure 12 An overview of the time, temperature and pressure relationship used during the lamination process [9] [10]                                             |

| Figure 13 Inner layer process steps for multi layer boards [55]                                                                                                  |

| Figure 14 Outer layer process steps for multilayer boards [55]                                                                                                   |

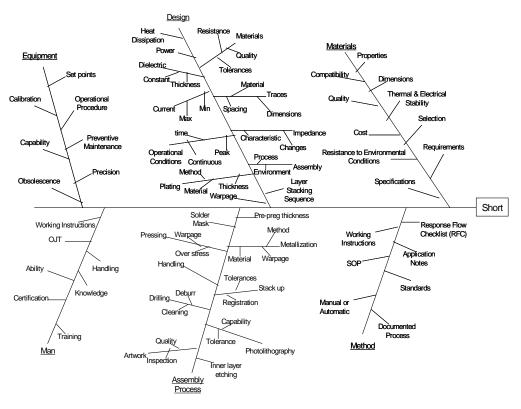

| Figure 15 Cause and effect diagram for open circuit on a PCB [55]                                                                                                |

| Figure 16 Cause and Effect Diagram for Short Circuit on a PCB [55]                                                                                               |

| Figure 17 Cause and Effect Diagram for Delamination [55] [20][21][22] 35                                                                                         |

| Figure 18 Photograph showing the phenomenon of dendritic growth, which occurs                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| on the surfaces of a PCB                                                                                                                                                             |

| Figure 19: Schematic describing CAF growth                                                                                                                                           |

| Figure 20: CAF growth along the fiber/resin interphase                                                                                                                               |

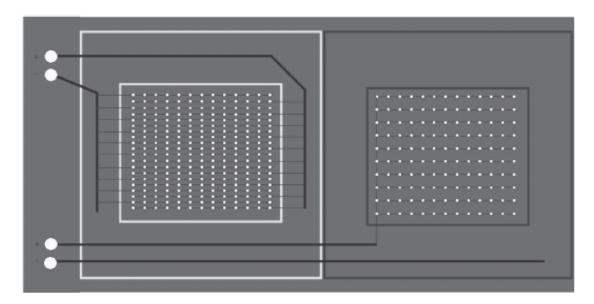

| Figure 21: Test board design. 59                                                                                                                                                     |

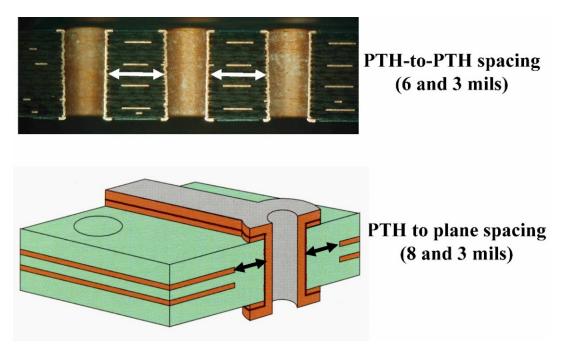

| Figure 22: Conductor spacing in the test samples                                                                                                                                     |

| Figure 23: Fabric weave orientations                                                                                                                                                 |

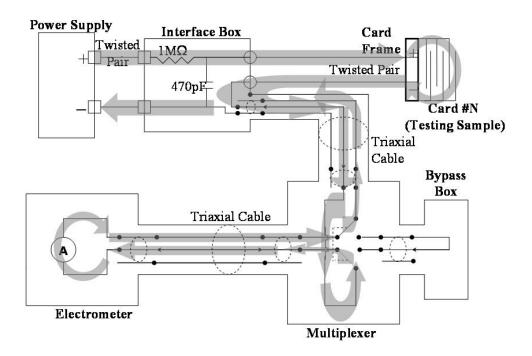

| Figure 24: Schematic of setup used for measuring insulation resistance 63                                                                                                            |

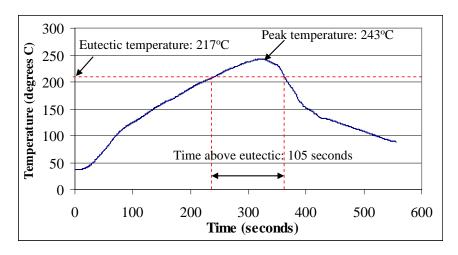

| Figure 25: A typical lead-free reflow profile                                                                                                                                        |

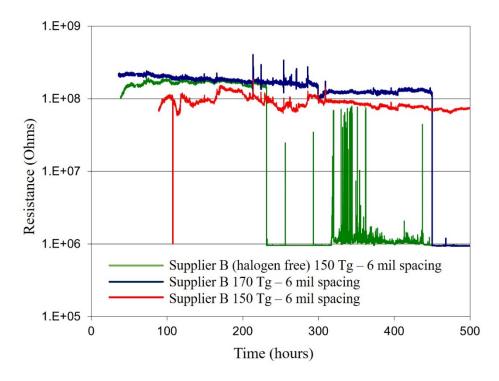

| Figure 26: Plot showing PTH-PTH insulation resistance monitored at 10V for three of the Supplier B samples                                                                           |

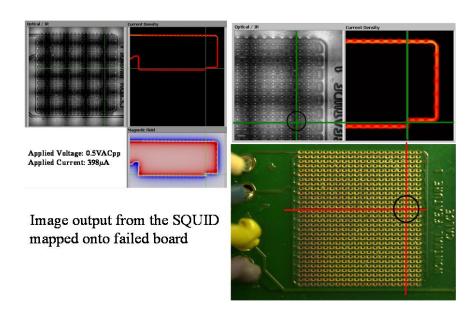

| Figure 27: Overlaying the shorted site as predicted by the SQUID current mapping images, the respective conductor locations on the test boards were identified for cross-sectioning. |

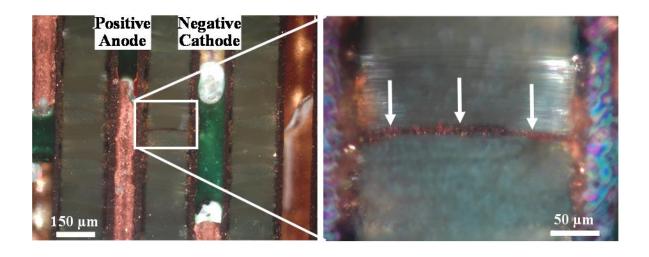

| Figure 28: Filament formation in the PTH-PTH geometry                                                                                                                                |

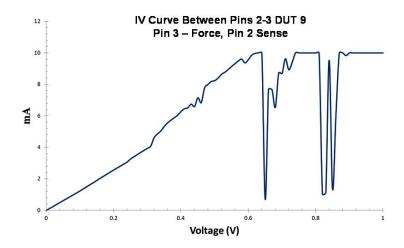

| Figure 29 Current-voltage relationship between pins 2 and 3 of device under test sample #9                                                                                           |

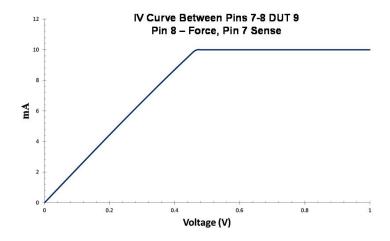

| Figure 30 Current-voltage relationship between pins 7 and 8 of device under test sample #9                                                                                           |

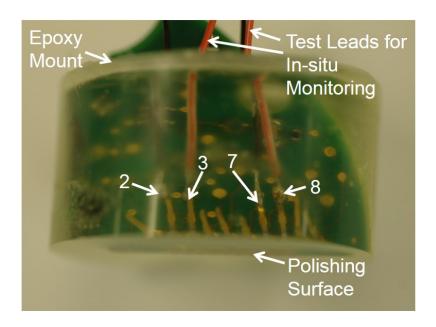

| Figure 31 Photo of the potted section of device under test sample #9 with soldered leads                                                                                             |

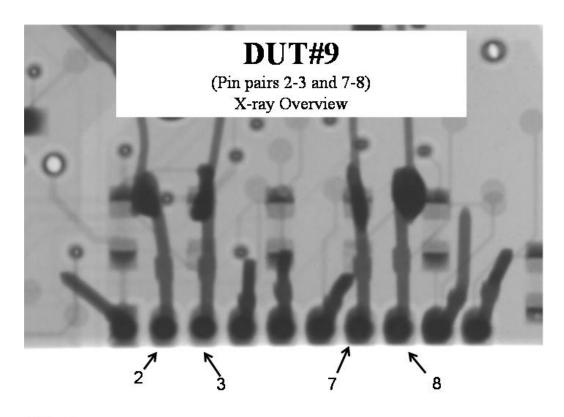

| Figure 32 X-ray radiograph obtained during the grinding with 800-grit abrasive paper                                                                                                 |

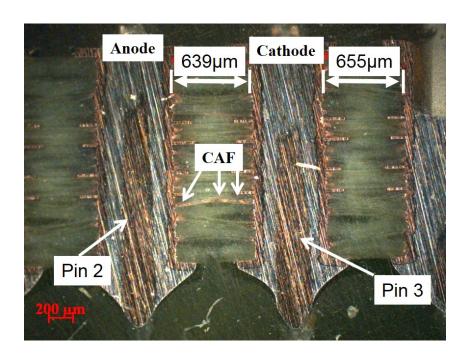

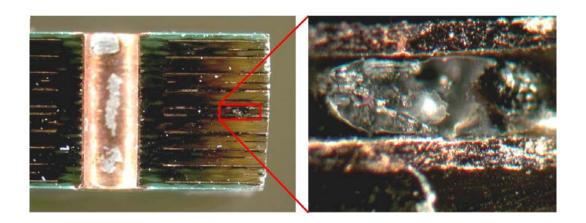

| Figure 33 Formation of CAF on device under test sample $\#9$ between pins 2 and 3 |

|-----------------------------------------------------------------------------------|

| Note that the surface of the mount appears rough and striated. Once the           |

| resistance fluctuations are observed, any further grinding or polishing will      |

| extract the residual materials and result in recovery of the low impedance        |

| pathway83                                                                         |

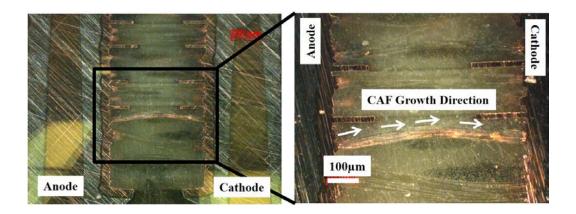

| Figure 34 Optical micrographs of CAF observed between the glass fibers and the    |

| epoxy resin. Note the surface of the mount appears rough and striated. Once       |

| the resistance fluctuations are observed, any further grinding or polishing will  |

| extract the residual materials and result in recovery of the low impedance        |

| pathway84                                                                         |

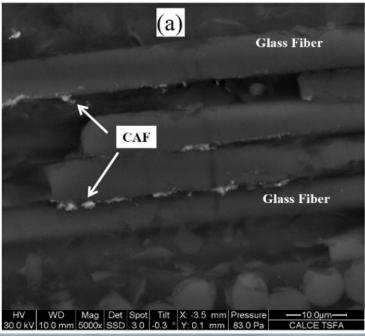

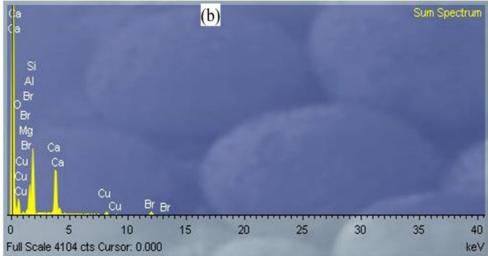

| Figure 35 (a) Scanning electron microscope image of CAF observed between the      |

| glass fibers and the epoxy resin. Note, as opposed to the optical viewgraph.      |

| the SEM images show a fragmented pathway. The brightfield optical                 |

| viewgraph, due to the higher depth of field, captures details from the focal      |

| planes that are beyond the viewing range with the SEM; (b) an EDS area            |

| elemental scan of the region shown in (a). Spectrum shows presence of             |

| elements such as copper, bromine and magnesium along with calcium                 |

| aluminum and oxygen                                                               |

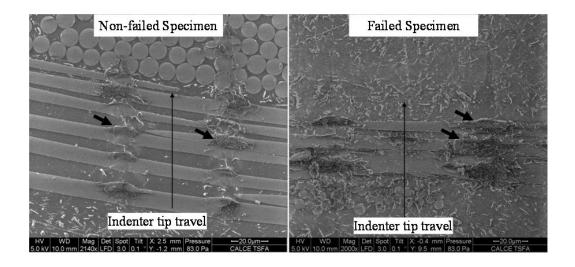

| Figure 36 Wipe and accumulation seen in the non-failed specimen (left) is not     |

| observed on the failed specimen (right)                                           |

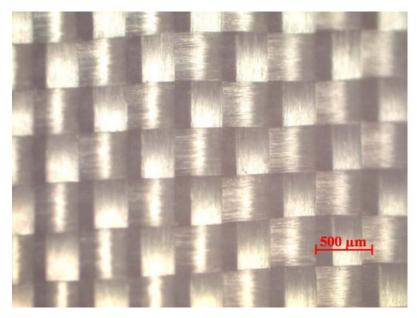

| Figure 37 Laminate material thermally etched at 530 °C. Only glass bundle         |

| remained. The epoxy and the coupling agent were removed                           |

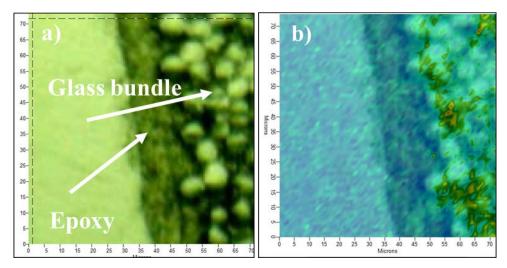

| Figure 38 a) Optical image and b) IR image of cross section view of non-coated    |

| siloxane sample                                                                   |

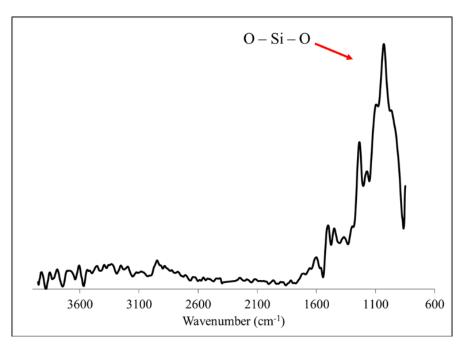

| Figure 39 IR spectrum of dried uncoated sample. Evidencing the presence of Si-O   |

| bonds from the glass fiber                                                        |

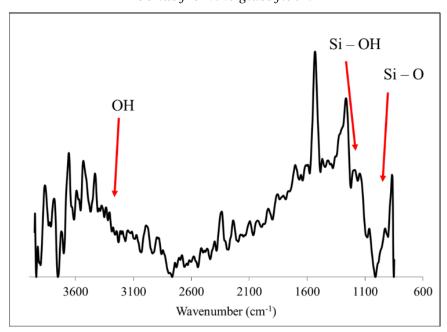

| Figure 40 IR spectrum of uncoated sample after humidity test                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

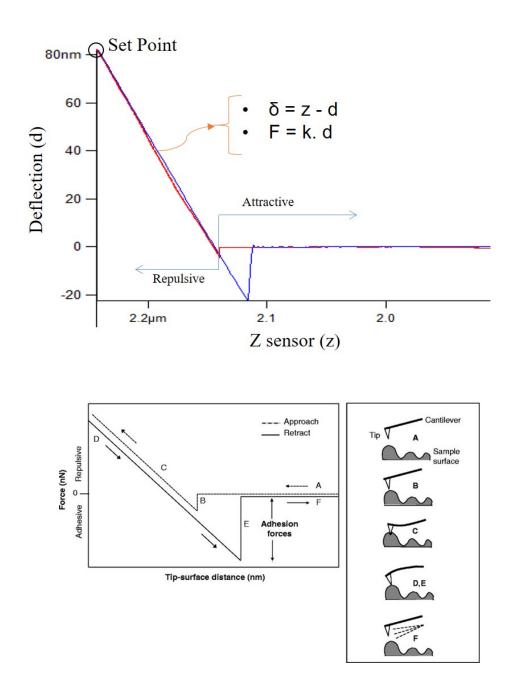

| Figure 41 Schematic illustration of the static force spectroscopy principle [75] 98                                                                                                                                                                                  |

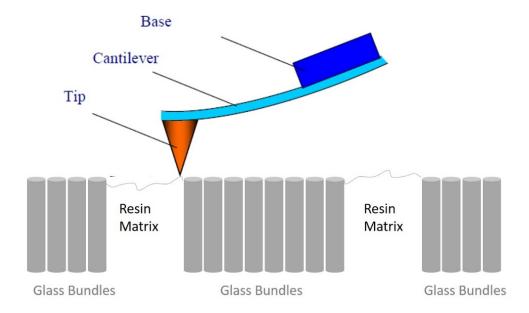

| Figure 42 Schematic illustration of the AFM cantilever on the cross-sectioned PCF sample                                                                                                                                                                             |

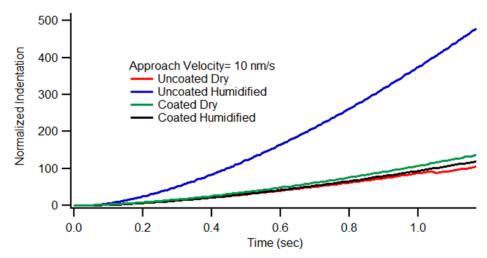

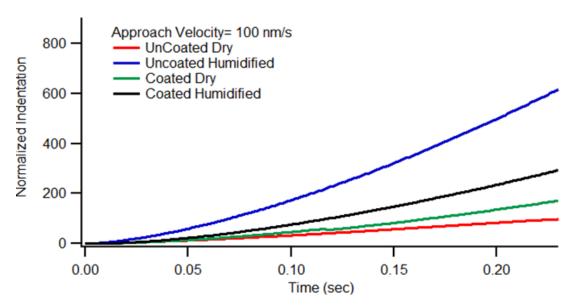

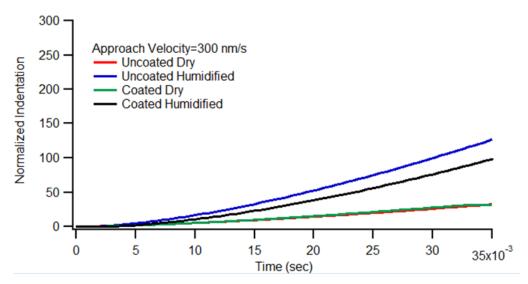

| Figure 43 Comparison between the normalized indentation of dried and humidified samples at 10nm/s                                                                                                                                                                    |

| Figure 44 Comparison between the normalized indentation of dried and humidified samples at 100nm/s                                                                                                                                                                   |

| Figure 45 Comparison between the normalized indentation of dried and humidified samples at 300nm/s                                                                                                                                                                   |

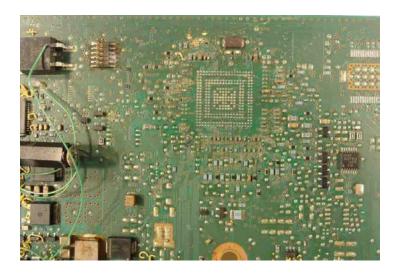

| Figure 46 Overview of front side of a PCB module showing the region which contains the suspect nodes KCP+ and RST_DRV. Note: the microprocessor was removed for the purpose of this experiment                                                                       |

| Figure 47 Closer view of suspect KCP+ node via and trace which was cut for the purpose of fault isolation. Blue arrows indicate the locations for electrical probing while monitoring with curve tracer. No leakage was observed between the vias, circled in yellow |

| Figure 48 Bottom side (microprocessor side) view of PCB during preparation for planar sectioning. Copper layer #4 was removed to allow backside lighting. This exposed suspect vias RST_DRV and CKP+ for measurement of the drill size and via spacing.              |

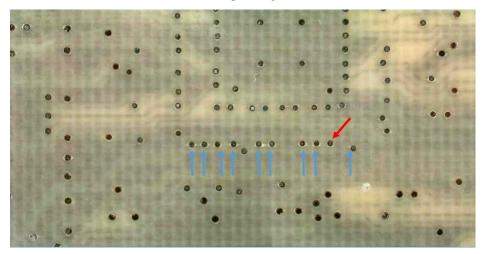

| Figure 49 Overall top down view of the laminate after removal of copper layer number 4. Suspect KCP+ via is highlighted by red arrow. A line of glass fiber to epoxy delamination was observed along this row of vias, highlighted by blue arrows                    |

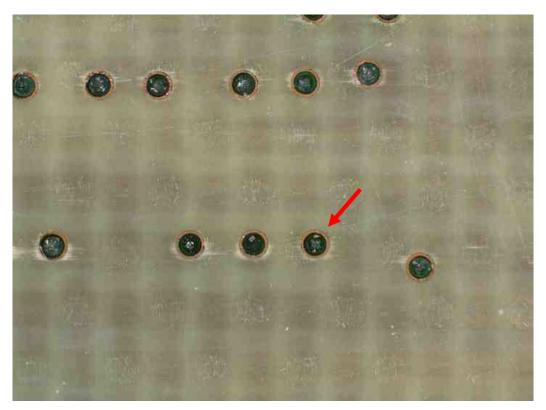

| Figure 50 Closer view laminate after removal of copper layer #1 with suspect KCP+                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| via highlighted by red arrow108                                                                                                                                                                                                                                                                                                     |

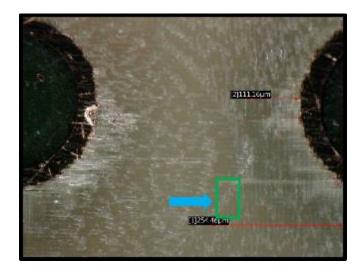

| Figure 51 Closer view of RST_DRV and CKP+ vias with selected measurements of suspect paths. The green box indicates the location of the FIB cutting, with the blue arrow indicating viewing orientation                                                                                                                             |

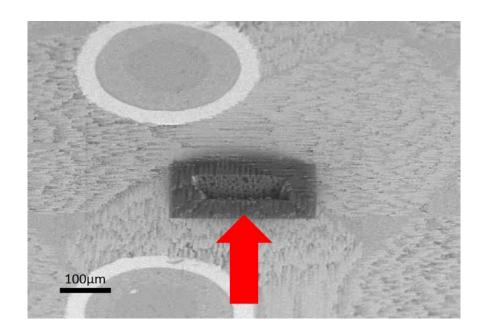

| Figure 52 Rotated and angled SEM view of RST_DRV and CKP+ vias with suspec gap highlighted by arrow within the FIB cut                                                                                                                                                                                                              |

| Figure 53 Closer view of suspect glass fiber bundle                                                                                                                                                                                                                                                                                 |

| Figure 54 Closer SEM view of the separation between a single fiber and the epoxy.                                                                                                                                                                                                                                                   |

| Figure 55: Common CAF pathway configurations are shown. Hollow fibers car also contribute to CAF by allowing an open pathway [37]114                                                                                                                                                                                                |

| Figure 56. This optical darkfield photo shows a conductive anodic filament close to but under the polished cross-sectional resin plane, connecting and electrically shorting two adjacent PTHs.                                                                                                                                     |

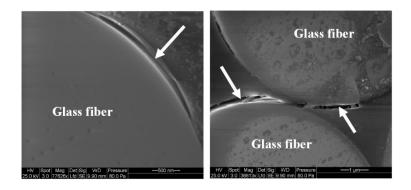

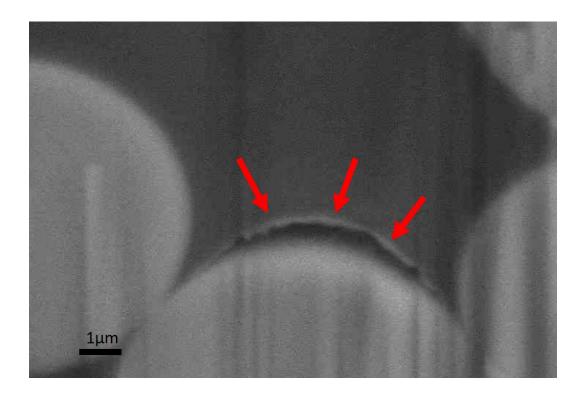

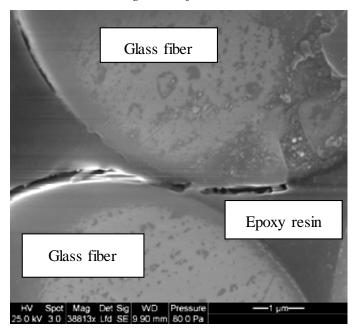

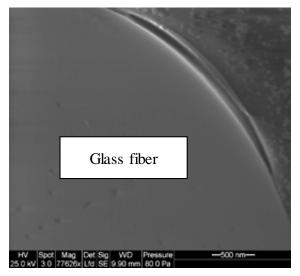

| Figure 57. These E-SEM photos show physical delamination at the interphases of the glass fibers and epoxy resin matrix. De-bonding can occur due to mechanical stresses arising due to the coefficient of thermal expansion (CTE) mismatches in the properties of the epoxy resin and the glass fibers during thermal cycling. [54] |

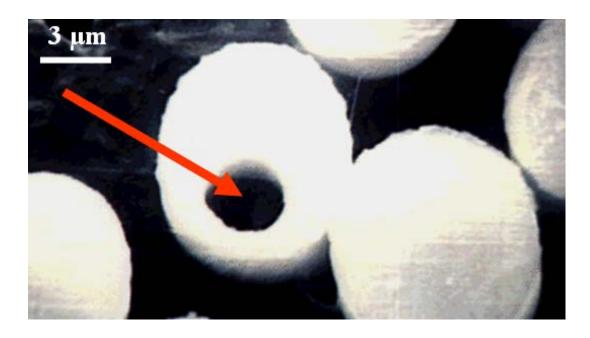

| Figure 58. Image of a hollow fiber (red arrow) [36]                                                                                                                                                                                                                                                                                 |

| Figure 59. Optical photo of conductive filament formed in the vertical direction between cracked Cabosil filler particles [29]                                                                                                                                                                                                      |

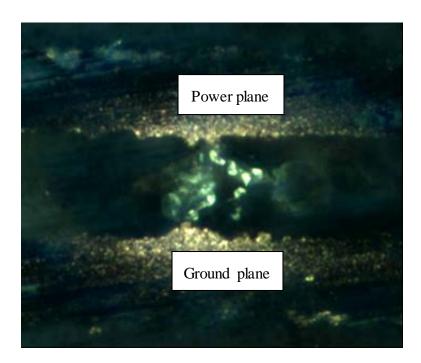

| Figure 60. Optical photos show a charred burnt area between the power and ground plane in a printed wiring board due to vertical filament formation [29]120                                                                                                                                                                         |

| Figure 61 Alkoxysilane coupling agent and its hydrolysis reaction122                                                 |

|----------------------------------------------------------------------------------------------------------------------|

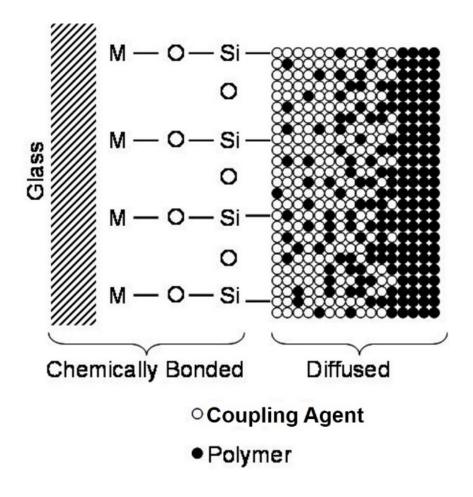

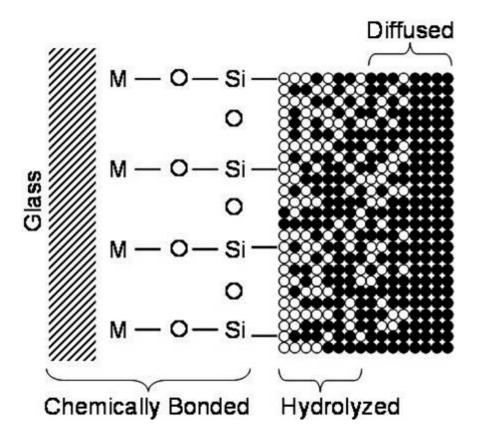

| Figure 62 Schematic for conventional interdiffusion and IPN [54] [66] [67]124                                        |

| Figure 63 Schematic for hydrolyzed diffused interphase after aging in water in a silane-treated glass fiber [66][67] |

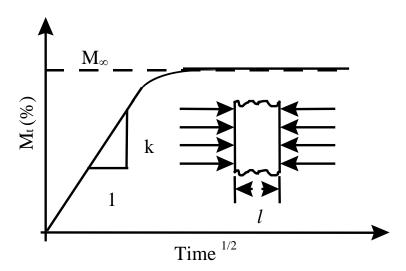

| Figure 64: Fickian sorption by a plane sheet exposed on both sides to the same environment                           |

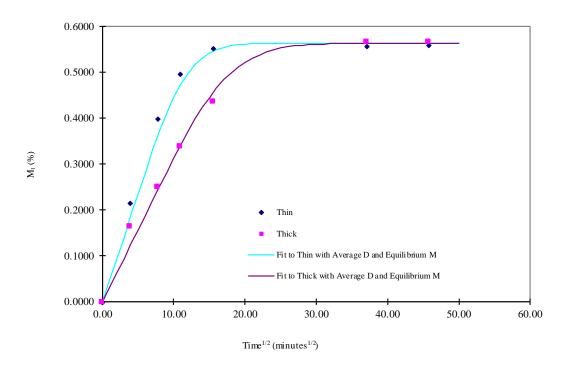

| Figure 65: Diffusion curves with theoretical fit (CE-A laminates at 50°C/85% RH).                                    |

| Figure 66 MAGMA -C10 scanning SQUID Microscope                                                                       |

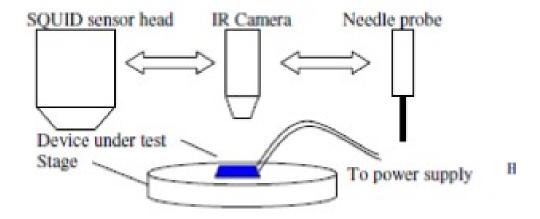

| Figure 67 Schematic of scanning SQUID microscope test station                                                        |

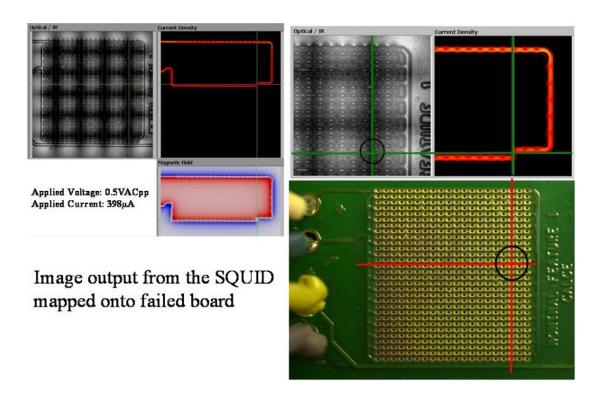

| Figure 68 Overlaying the shorted site as predicted by the SQUID current mapping                                      |

| images, the respective conductor locations on the test boards were identified                                        |

| for cross-sectioning158                                                                                              |

# Chapter 1: Introduction

#### 1.1. Printed Circuit Boards

Printed circuit boards (PCBs) are the baseline for electronic packaging upon which electronic components are formed into electronic systems. PCBs are used in a variety of electronic circuits from simple one-transistor amplifiers to large super computers. A PCB serves three main functions:

- 1) it provides the necessary mechanical support for the components in the circuit

- 2) it provides the necessary electrical interconnections, and

- 3) it bears some form of legend that identifies the components it carries.

Printed circuit boards can be classified into three categories based on their construction and physical characteristics, namely rigid, flexible and rigid-flex boards. Rigid circuit boards are basically a composite layered structure in which solid copper sheets are laid down and separated with a dielectric material, which is commonly an epoxy resin system. Rigid boards represent the most widely used category and they can be built from different materials systems. Flexible printed circuits consist of thin copper foil bonded to a thin plastic base. The base material most frequently used is polyester film. This type of board is usually limited to a single- or double-sided board and only for very small components. The third category is the rigid-flexible boards which is a combination of rigid and flexible

boards bonded together. The rigid portion supports the components while the flex portion allows the structure to be folded. Attention will be given to the rigid printed circuit boards since they represent the highest volume and it is within this category that the major challenges in terms of fabrication, materials, and applications are encountered.

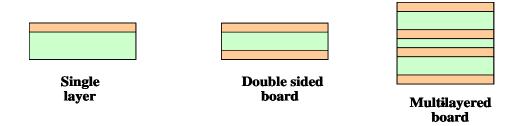

Rigid printed circuit boards can be further categorized in terms of circuit complexity and base materials. Circuit density can force the design to be single-sided, double-sided, or multi-layer. A single sided board has circuit layout on one side only, while the double sided board has artwork on both sides. On double sided boards, connections between the two layers are made with small conductive holes called "vias". A multilayer board has artwork on one or more internal layers in addition to the top and bottom. Schematic drawings of the three types of boards are shown in

Figure 1.

Figure 1 Schematic representation of single, double, and multi layer boards.

#### 1.2. Materials and Processes

Rigid printed circuit boards can be made up of different base materials combinations. Each material group provides key characteristic parameters and important advantages for different applications. Ceramic materials such as aluminum oxide, aluminum nitride, and glass ceramic are used as substrates and metal circuit traces are screen printed on top of the substrate. The whole system is then fired to obtain a single monolithic ceramic circuit board. Boards with silicone resin based substrates are used mainly when low characteristic impedance is required at high frequencies, for example in transmission lines, filters, and oscillator circuits. The third type of base material used for PCB fabrication is from the organic family, where the low cost phenolic resin reinforced with paper is used for low end applications and epoxy resin reinforced with woven glass cloth is used for mid and high end applications.

The epoxy glass composite is manufactured by impregnating rolls of woven glass cloth with resin, and then laying up the necessary number of layers of impregnated cloth between sheets of copper foil and pressing in hydraulic presses. In today's electronics, glass based materials are generally used. These are covered by NEMA (National Electrical Manufacturers Association) specifications and summarized in Table 1: G<sub>2</sub>, G<sub>3</sub> (Phenolic resins), G<sub>5</sub>(Melamine), G<sub>10</sub>(Epoxy), G<sub>11</sub>(heat resistant epoxy), FR4 and FR5 which are flame retardant versions of G<sub>10</sub> and G<sub>11</sub>

respectively. The most common material system is the FR4 which gives the best balance of electrical and mechanical properties, with the best bond between the resin and the glass fibers and between the resin and copper cladding [1].

Table 1 Basic NEMA classification for commonly used materials [2].

| XXXP            | Phenolic / Paper                                                |

|-----------------|-----------------------------------------------------------------|

| XXXPC           | Phenolic / Paper, cold punching                                 |

| $FR_2$          | Phenolic / Paper, flame resistant                               |

| FR <sub>3</sub> | Epoxy / Paper, flame resistant                                  |

| $G_{10}$        | Epoxy / Glass, general purpose                                  |

| G <sub>11</sub> | Epoxy / Glass, temperature resistance                           |

| FR <sub>4</sub> | Epoxy / Glass, general purpose, flame resistant                 |

| FR <sub>5</sub> | Epoxy / Glass, general purpose, temperature and flame resistant |

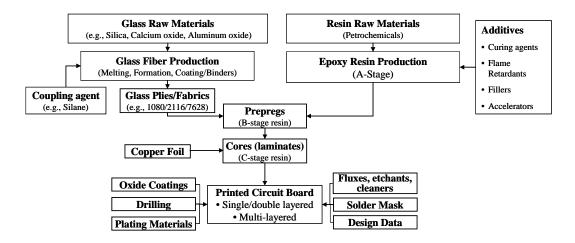

FR-4 is a composite of epoxy resin with woven fiberglass reinforcement and is the most commonly used PCB laminate material type. The typical constituents of a FR-4 laminate is given in Table 2. In addition to these constituents, copper is generally used as the conductor material in a built up circuit board. The steps involved in FR-4 laminate fabrication are shown in Figure 2 [3]. Glass fibers are made out of glass raw materials and a coupling agent is coated onto them prior to weaving the glass fabric. A single ply of glass cloth when impregnated with the semi-cured resin is called prepreg. Multiple prepregs are thermally pressed to obtain a core or laminate.

Copper foil is then electrodeposited to obtain a copper clad laminate. The laminate is further processed with solder mask and design data to obtain a single or a double layered PCB. Several prepregs and cores are stacked together under temperature and pressure conditions prescribed by laminate manufacturer to obtain a multi-layered PCB [4].

Figure 2: FR-4 Laminate Fabrication [69]

Table 2: Typical constituents of FR-4 laminates [69].

| Constituents    | Major Function(s)                                                                  | Example Material(s)                                                                                                                            |  |

|-----------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Reinforcement   | Provides mechanical strength                                                       | Woven glass (E, S, A or C grade) fiber                                                                                                         |  |

| Resin           | Acts as a binder and load transferring agent                                       | Epoxy (DGEBA)                                                                                                                                  |  |

| Curing Agent    | Enhances linear/cross<br>polymerization between the res in<br>and reinforcement    | e.g., Dicyandiamide, Phenol<br>novlac, Xylok                                                                                                   |  |

| Coupling Agent  | Bonds inorganic glass with organic res in and transfers stresses across the matrix | e.g.,Organo silanes<br>Y-(CH <sub>2</sub> ) <sub>n</sub> -Si (OX) <sub>3</sub><br>(Y-organo functional group;<br>OX- silicon functional group) |  |

| Flame Retardant | Reduces flammability of the material                                               | Halogenated (TBBPA) or<br>Halogen-free (Phosphorous<br>compounds)                                                                              |  |

| Fillers         | Reduces thermal expansion, increases flame retardancy e.g., Aluminum silicate, Mi  |                                                                                                                                                |  |

| Accelerators    | Increases reaction rate, reduces curing temperature, controls crosslink density    | e.g., Organophosphine,<br>Imidazole, BF3 amine complex                                                                                         |  |

#### 1.3. Constituents

The constituents of FR-4 laminates are discussed below. Each of these constituents are important in its own, and in combination they determine the properties of the laminates.

### 1.3.1. Glass Reinforcements

Glass fibers are widely used in reinforced PCBs because they are inexpensive to produce and have relatively good strength to weight characteristics. In addition, glass fibers also exhibit good chemical and fire resistance. Electrical (E) glass, a low-alkali composition which exhibits an excellent balance of electrical insulation

properties and good resistance to water, is the most widely used reinforcement material for cost effective electronic applications (see Table 3 for typical composition of e-glass).

Table 3: Typical composition of E-grade glass

| Constituent                                                          | Composition (%) |

|----------------------------------------------------------------------|-----------------|

| Silicon dioxide (SiO <sub>2</sub> )                                  | 52-56           |

| Calcium oxide (CaO <sub>2</sub> )                                    | 16-25           |

| Aluminumoxide (Al <sub>2</sub> O <sub>3</sub> )                      | 12-16           |

| Boron oxide (B <sub>2</sub> O <sub>3</sub> )                         | 5-10            |

| Sodiumoxide (Na <sub>2</sub> O) + Potas siumoxide (K <sub>2</sub> O) | 0-2             |

| Magnesiumoxide (MgO)                                                 | 0-5             |

| Iron oxide (Fe <sub>2</sub> O <sub>3</sub> )                         | 0.05-0.4        |

| Titaniumoxide (TiO <sub>2</sub> )                                    | 0-0.8           |

| Flourides                                                            | 0-1             |

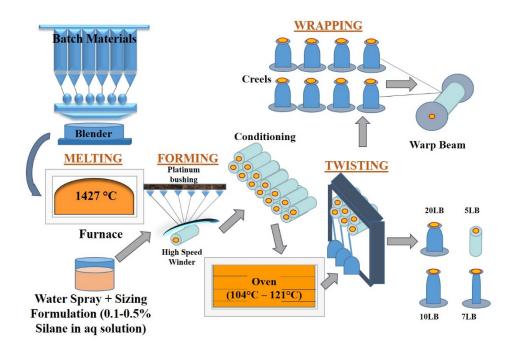

Manufacturing of glass fiber begins with the dry mixing of silicas, limestone, clay, and boric acid in appropriate proportions. A homogeneous melt composition with negligible impurities is necessary for the successful manufacture of glass fibers. Solid inclusions of even sub-micron dimensions can act as stress concentrators that reduce the fiber strength.

After the molten glass is poured into the bushing, glass fibers are produced by drawing a solidified filament of glass from a molten drop. The diameter of a glass fiber is typically between 5 and 25 microns. During drawing, any seeds present will become attenuated and elongated, forming capillaries several meters long in the glass filaments and effectively creating hollow fibers. These hollow fibers provide

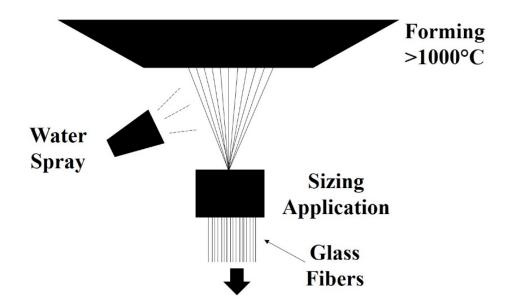

a path for conductive anodic filament formation [3][59]. A schematic of the glass fiber fabrication steps in shown in Figure 3. Sizing agents, which are applied to the individual glass fibers after they are formed (binder formulations) are discussed later in this chapter.

Figure 3 Schematic showing the glass fiber fabrication steps [8][9].

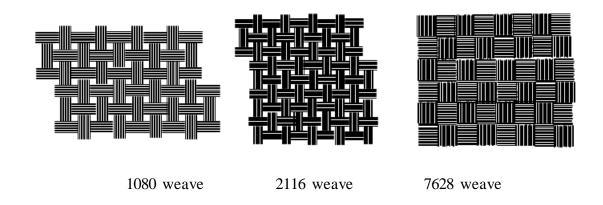

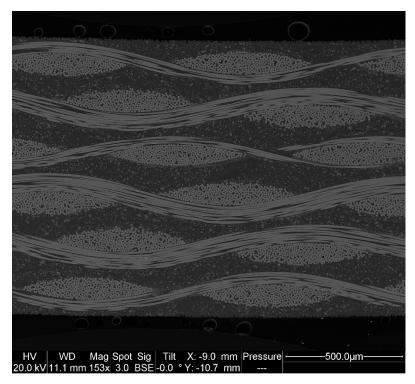

Glass fabric consists of two sets of fiber bundles, warp bundles are the initial set of parallel fiber bundles and fill bundles are woven through the first set to form a fabric. Changes in the tension and spacing of these bundles during weaving result in varying degrees of crimp (waviness) and hence different properties along both directions. Parameters such as glass fiber bundle diameter, number of fiber bundles

used and linear density of the fabric define the type of glass-weave style. Typical glass-weave style numbers used in PCBs are 1080, 2116 and 7628. The difference in their fabric styles is represented in Figure 4.

Figure 4: Typical glass-weave styles

#### 1.3.2. Resin System

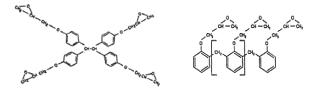

The function of a resin system in a laminate is to hold the fibers in place, bind the fibers, provide thermal stability to the composite structures and provide interlaminar toughness. The resin system used in FR-4 laminates primarily consist of bi, tetra or multi-functional epoxy groups. The resin is derived from the reaction of Bisphenol-A with Epichlorohydrin which creates a "Diglycidyl Ether of Bisphenol A" called DGEBA. It is also referred to as an oxirane (shown in Figure 5).

Figure 5: Formation of DGEBA

The epoxy groups present in DGEBA react in subsequent resin polymerization and result in curing of the resin system [3]. Higher cross-linking in the cured system is achieved by the use of epoxy monomers with more than two epoxy functional groups per molecule (shown in

Figure 6). Additives such as curing agents, flame retardants and fillers are added to the resin system to improve the performance of the laminate.

Figure 6: Tetra-functional and multi-functional epoxy monomers.

#### 1.3.3. Interphases Between Resin and Glass

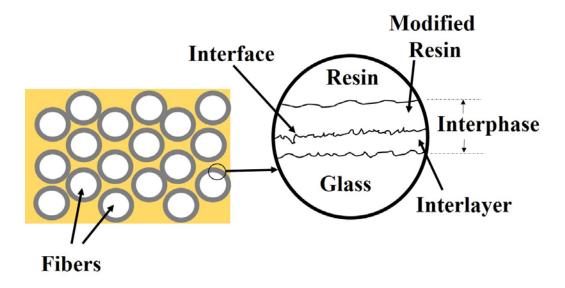

The interphase between the glass and resin is a three-dimensional region between the bulk fiber and bulk resin. It includes not only the area of contact (interface) between the fiber and the matrix, but also a region of some finite thickness extending on both sides of the interface in both the fiber and resin matrix (interphase) [4]. A schematic illustration of the glass-resin interphase is shown in Figure 7 with a cross-section of PCB shown on left and a detail of the region at the fiber surface shown on the right.

The interphase comprises the functional interlayer and the part of the epoxy resin affected by the presence of the silane coated fiber. The coated interlayer improves compatibility between the glass fiber and the resin matrix by forming a strong but tough link between both phases. This interphase will be the subject of further discussion in chapters 2, 3, 4 and 5.

Figure 7 Schematic illustration of the glass-resin interphase.

Various types of interphases can exist such as mechanical, chemical or physical. A mechanical interphase between the glass and resin matrix comprises of a lock and key (based on the surface morphology) mechanism which is dictated by surface roughness, porosity, resin viscosity etc. For example in a physical interphase, phenomenon such as interdiffusion entanglement, electrostatic energy, polar and Van-der-Waal bonding can act on the surface of the fibers.

Glass fiber to resin matrix adhesion quality will vary for different systems. The surfaces of the glass fibers can be roughened which improves adhesion and improves friction with the resin matrix. The roughening can be done by methods such as chemical etching, which produces microscopic and macroscopic features that enhance adhesion with the resin matrix. Other treatments include argon induced roughening, and oxygen plasma based cleaning of the glass fiber surfaces. The glass resin adhesion is necessary because this interphase dictates transverse mechanical properties of the PCB laminate, its through thickness or bulk properties including delamination resistance, fatigue resistance, resistance against CAF. Sources of residual stresses along the glass resin interphase are the thermal mismatches that exist along the interphase, glass with a smaller coefficient of thermal expansion (CTE) is subject to compressive residual stresses and resin which has a larger CTE is subject to tensile residual stresses.

Glass fiber treatments tend to be geared towards the removal of weak fiber boundaries, removal of contaminants and offer to moderate the excessively high interphase stresses. The coatings can add an intermediate modulus layer or add an elastomer layer. Treatments of the glass can also provide variations in the surface topography or mechanical locking. Wettability of the surface is important, in case the glass fiber surface is wettable, the matrix angle  $\Theta$  is less than  $90^{\circ}$ , when the matrix angle  $\Theta$  is greater than  $90^{\circ}$ , the fiber to matrix adhesion is poor.

Resin to glass interactions include molecular adsorption into the matrix, penetration into the matrix, fiber catalytic effects and fiber surface induced crystallization of the resin matrix.

#### 1.3.4. Sizing Agents

The sizings are a multifunctional coating applied to perform a number of functions. The application process of the sizings consists of creating a form of a suspension in an aqueous solution and this mix limits the constituents that can be mixed in with the sizing agents. A schematic showing the glass fibers that are being drawn from the forming bushings into the sizing applicator roll for processing is shown in Figure 8. Within a few seconds after the glass fibers are formed and drawn out of the platinum bushings, water is sprayed on the glass fibers. Water is preferred as it wets glass easily and fast yielding a good dispersion of the sizing [5].

Figure 8 Schematic showing the glass fibers being drawn from the forming bushings (top) into the sizing applicator roll (bottom) and further for processing [5].

The primary function of the sizing is to protect the glass fiber surface against damage due to fiber-fiber contact when the glass is wound into a strand in order to continue the processing and handling, other attributes include reduction in fuzz during handling, provide good wetting during laminate manufacture with a low void content as a result, facilitate high fiber matrix interaction for successful stress transfer and low cost [6] [7]. While the exact recipes of the sizing agents are proprietary within individual companies, the types can broadly be classified as follows:

- Aminosilanes

- Epoxy Silanes

- Vinyl Silanes

- Methacryl Silanes

- Alkylsilane

- · Phenyl Silane

- Chlorosilane

Most sizing consists as a minimum of a film former and a coupling agent, but often many more components. The film former protects against fiber-fiber damage and protects the whole fabric during production. A sizing is often chosen to be similar to the PCB epoxy matrix in order to obtain a good wetting. Anti-static agents, emulsifiers and lubricants are added to reduce fuzziness, to stabilize insoluble components in the suspension and to further improve the dispersion and protect the fibers. When the reaction of this sizing and the glass takes place, a covalent bond is formed between the silane coupling agent to the fiber surface.

It is known that the process of pre-curing the sizing agent further condenses the Si-OH groups of the coupling agent to Si-O-Si linkages [73]. The results of the above reactions between the coupling agent and the epoxy resin indicate that the physical state and processing conditions of the coupling agent can drastically effect the reaction. First, the coupling agent should not be pre-heated before the epoxy resin is added [74]. Pre-heating only further condenses the coupling agent interphase

reducing the penetration of the resin into the coupling agent interphase. Second, the reaction temperature must be kept under 115°C or some of the primary amines of the coupling agent will be oxidized to imine groups [74]. Third, as a corollary of the first two, penetration of the resin into the silane interphase along with the chemical reaction is important and these two processes must be optimized to improve the mechanical properties of the composite materials.

#### 1.3.5. Curing Agents

Curing agents are added into the resin matrix to enhance cross-linking thereby thermosetting the composite structure [3]. They are usually aliphatic or cycloaliphatic amines and polyamines or amides. The most widely used curing agents in the PCB industry are dicyandiamide (commonly known as dicy) and phenol novolac (phenolic). The chemical formulae of dicy and phenolic curing agents and typical molecular structures of the cured resin systems are shown in Figure 9.

Figure 9: Typical structure of dicy and phenolic cured systems.

The properties of dicy and phenolic cured systems differ because of the nature of their molecular structures. Dicy and its cured resin systems are linear aliphatic molecules compared to the aromatic structure of phenolic and its cured epoxy systems. This makes the phenolic cured systems more thermally stable than dicy cured systems. Dicy cured systems are more hygroscopic than phenolic cured systems due to the presence of highly polar carbamidine-carbamide bond in their chemical structure. At higher temperatures the strong polar nitrogen atom present in the dicy cured system can destabilize the brominated epoxy resin resulting in the production of corrosive bromide ions [11]. Overall, phenolic cured resin systems offer better thermal resistance, chemical and humidity resistance as well as, improved mechanical properties but poor processability (e.g., drilling) when compared to dicy cured systems.

#### 1.3.6. Flame Retardants

Flame retardants are added into the epoxy matrix to reduce flammability of the laminate material. Tetrabromobisphenol A (TBBPA) (Figure 10) is the most commonly used halogenated flame retardant for epoxy resin systems. Bond energies of the various bonds in the polymer matrix are as shown i

Table 4.

Figure 10 Tetrabromobisphenol A (TBBPA).

Table 4: Typical bond energies

| Bond                  | Bond energy<br>(kJ/mol) | Temperature above which degradation starts (°C) |

|-----------------------|-------------------------|-------------------------------------------------|

| Carom – Br            | 335                     | 360                                             |

| C <sub>aliph</sub> –  | 340-370                 | 400                                             |

| Caliph _ H            | 390-436                 | >500                                            |

| C <sub>arom –</sub> H | 469                     | >500                                            |

Brominated flame retardants (BFRs) are halogenated flame retardants that break down and releases bromine radicals (Br•) because of the lower C-Br bond energy

compared to other bonds [15][16]. These radicals react with the surrounding polymeric material (RH) and the resulting reaction releases hydrogen (H) from the functional group (R•) to form hydrogen bromide (HBr). Hydrogen bromide (HBr) in turn interferes with the radical chain mechanism by reacting with the high energy H• and OH• radicals. Highly reactive H• and OH• radicals are trapped and chain reaction leading to combustion is stopped. Thus, BFRs decompose during ignition, and retard combustion by trapping radicals generated from resins and by forming gas-phase barriers against oxygen [14].

Halogen-free flame retardant epoxy systems are gaining importance because of the environmental concerns involved with halogenated flame retardants. Phosphorous compounds (organophosphate esters or inorganic red phosphorous) and metal hydroxides (hydroxides of aluminum and magnesium) are some of the commonly used halogen-free flame retardants. Organophosphate esters works by forming flame retarding glass-like barriers on the resin surface during ignition thereby cutting off oxygen necessary for combustion. Metal hydroxides retard flames by absorbing the heat during ignition.

Fillers are added in the laminate systems for specific performance requirements such as reducing out-of-plane coeffecient of thermal expansion (CTE) and to prevent barrel cracks in plated through holes. Fillers are also added to enhance the

flame retardancy to meet UL 94V-0 flammability rating and to reduce material costs (as they replace resin) [19].

### 1.4. Lamination Process

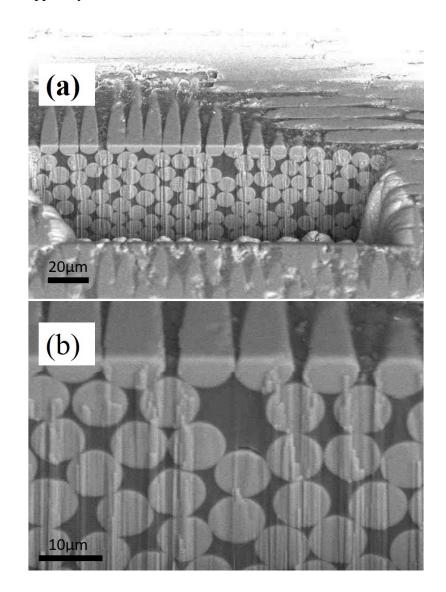

The weave fabric is impregnated with epoxy to form a laminate. Environmental scanning electron microscope (ESEM) micrograph of a 6 ply 7628 glass weave laminate is shown in Figure 11. During the lamination process the thin-core innerlayers are subjected to heat and pressure and compressed into a laminated panel. Sheets of material consisting of glass fibers impregnated with epoxy resin, known as pre-preg or b-stage, are slipped between the layers and bond the layers together. Pre-preg is available in different styles with varying ratios of resin to glass fibers. This choice of differing epoxy resin to fiber glass ratios allows the manufacturer to control the thickness between layers and to provide the appropriate amount of resin between circuitry. Lamination steps are fairly consistent among manufacturers. In lamination, the pressing parameters must closely match what the laminator recommends. If the heat rise of the pressed book is not maintained as per manufacturer's specifications, the resin will not have enough time to properly wetout the cores that are being pressed [1]. Laminate voids or other lamination defects may occur as a result.

One lamination process is a Standard Hydraulic Lamination. Steam press, hot oil press, or electrical resistance heaters are common elements used in this process to

provide heat to the stack. Using the steam and hot oil method allows for a higher heat rate to be achieved but the maximum temperature reached is relatively low. A caution for the steam press is the lamination temperature may not be met during a typical lamination process.

Figure 11 Typical 6-ply 7628 weave stack up.

The second process is Vacuum-Assisted Hydraulic Lamination (VAHL). This is the most widely accepted process practice in the industry today. Before the lamination process occurs a vacuum cycle 15 to 60 minutes occurs where moisture, air, and other volatiles are pulled out from the PCB stack. Note that this is very different from a pushing out method as utilizing a pushing out method can still

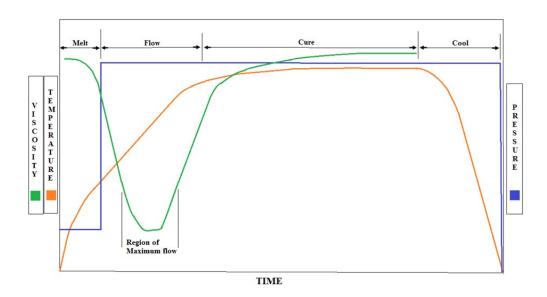

cause volatiles to be trapped in the finished PCB. Then follows a typical Hydraulic Lamination process. An overview of the time, temperature and pressure relationship used during the lamination process is shown in Figure 12. The vacuum cycle helps lower the pressure need for lamination. A lower pressures can help reduce the effect of misregistration by roughly a thousandth to two thousandth of an inch. In the world of electronic packing this is very substantial and can allows even smaller traces to be created and increase the amount of signals in a layer on a board.

Figure 12 An overview of the time, temperature and pressure relationship used during the lamination process [9] [10].

The third process is an Autoclave Lamination. The PCB is sealed in a vacuum chamber with high pressure heated gas. This creates a uniform hydrostatic pressure

force. The downfall to this process is the pre-vacuum cycle will take much more time than a VAHL and the heat up rate is slower compared to the other lamination process.

### 1.5. PCB Fabrication Process

Rigid PCBs can be categorized as single-sided, double-sided, or multilayer depending on the circuit complexity. Different process steps are required for each of these technologies, with single-sided having the simplest process and multilayer the most complex and costly process.

# 1.5.1. Single Sided Boards

The basic steps for manufacturing single sided boards is presented along with the critical parameters [9]. More complex technologies use these steps as the base for constructing the more sophisticated structures.

A screen printing process step creates the master pattern from which the traces on the board are derived. The image is screen printed using a fine silk screen or a stainless steel wire mesh. The precision of the screen printed image depends on the mesh and the viscosity of the used ink.

In the photo resist step the board is coated with a thin uniform layer of photoresist material. The master created in the first step is then placed over the board and exposed to UV light. The resist is then developed and leaves the tracked pattern coated with the resist material; the remainder uncured resist material is washed

away. A rigorous inspection is required to detect "pin holes" in the ink or photoresist to avoid unwanted etching of the protected material, failure in this stage can result in out of specification traces or even an open trace line. Process mistakes at this step can potentially impact the reliability of the board causing an instantaneous failure or affecting then the performance over time. Once this stage is completed, the board can be etched.

During the etching process, all the unwanted copper that is unprotected by the photoresist material is attacked and removed, leaving only the metal traces and contact pads. There are three commonly used etching fluids used in PCB fabrication: ferric chloride, ammonium persulphate, and chromic acid. The etching operation is followed by a washing and subsequent a drying operation. The board is then inspected and the ink or resist is removed from the just created traces.

In the solder mask application process, the exposed copper traces are protected and electrically isolated with a dielectric coating known as solder mask. The solder mask protects the traces from mechanical damage and provides protection during the metallization and soldering processes.

Exposed board features such as pads, through holes, and any other specified contact points are now plated with a metal system (specified in the drawings) by any of the available metallization process. This metal finish will provide an oxidation barrier to the copper base metal. It will also serve as an interdiffusion barrier, and will

provide the metallurgical base to form a sound interconnection. The most common metallization materials for PCBs are gold over nickel, tin-lead, tin, silver, nickel, and bare copper protected with an organic preservative coating (such as Organic Surface Protect or Organic Copper Coating). The ultimate usage, criticality of the product, and cost must be considered when selecting the material and the method. The most common plating methods are electroless plating, electrolytic plating, immersion, and hot air surface leveling (HASL).

## 1.5.2. Multilayer Boards

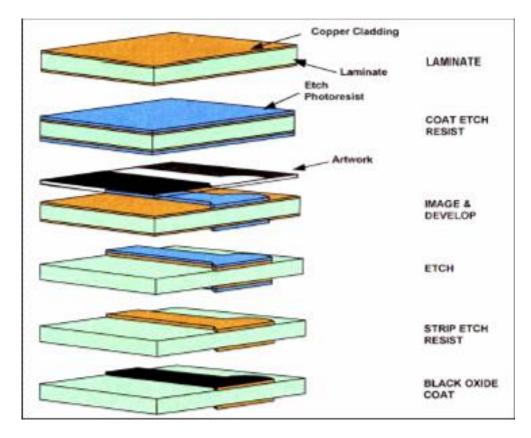

Multilayer boards are made by a combination of the processes used for single sided boards and double sided boards with plated through holes. The individual internal layers, which may be single or double sided, are first etched in the same manner as single boards (after being punched and drilled for locating dowels), and then the layers are bonded together. The layers are laid up with a prepreg between the etched layers on the alignment dowels and the assembly is placed in a powerful press to obtain a blank. This sequence is known as inner layer fabrication and is illustrated in Figure 13.

Figure 13 Inner layer process steps for multi layer boards [55].

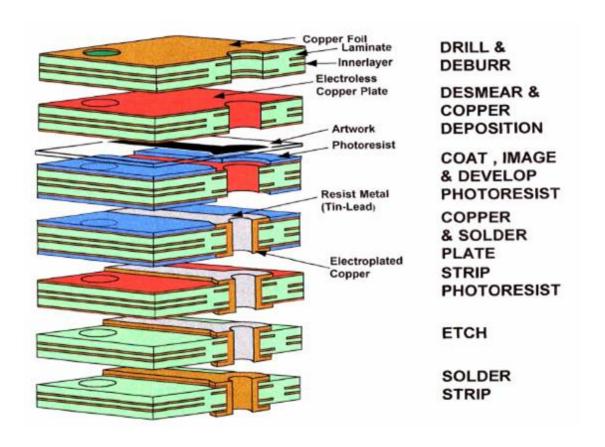

Initially a light pressure is applied to close the layers together, and then the system is heated up. The full bonding pressure is applied and the resin is cured at elevated temperature. Once this stage is complete, the blank is ready for the outer layer process that can be seen in Figure 14.

Figure 14 Outer layer process steps for multilayer boards [55].

# 1.6. Process Control and Inspections

Some PCB manufacturers use a special control pattern that is outside the finish board area to monitor all the processes. Microsections for characterization are taken from this area. Other suppliers make an extra boards or coupons on each lot, and this is used for process monitoring purposes and cross-sectional analysis. The inspection procedures normally applied throughout the process include visual inspections at every stage with "touch up" operations whenever necessary.

Regular analysis of all plating and etching baths form an important part of inspection procedures. Quantitative chemical analysis is obtained from the laboratory and compared to the standards. Plating thickness and undercutting are usually monitored on a batch basis by cross-sectioning or XRF techniques to inspect plating composition. Diameters of selected number of holes on each board are checked with pin gauges. Pad diameters, trace widths, and clearances are verified with an optical microscope. Electrical continuity testing for all PTHs should be applied. This test indicates whether a hole is an open circuit or not. It can not detect poor plating, roughness, or porosity, which would only be detected by visual inspection or destructive testing [16].

The inspection of multi-layer boards follows the same pattern of simpler boards, but as there are more process steps, more inspection is required. Electrical testing for internal short circuits and continuity is conducted. The boards are also inspected in x-ray to check for internal trace integrity. Thermographic testing can be used to locate short circuits between layers, which may be due to a single metal flake trapped between two layers, that had penetrated the B-stage on the bonding process.

### 1.7. Faults in Multi-layer Manufacturing Process

Wider tolerances are usually preferred for multilayer boards to allow for the extra processes involved and the misregistration problems that are encountered. A drilled hole that is out of the capture pad in the outer layer is a detectable problem, but on

an inner layer it could leave a hairline gap in which the plating material may induce an internal short. The risk of material movement is also increased in multilayer boards. This means that larger pads are used to guarantee that the hole will be within the pad area of all the stacked layers. To avoid the risk of board distortion, the layup at the board should be symmetrical, i.e. the stacking sequence must be a mirror image with respect to the middle layer [1].

The biggest problem in the manufacture of multilayer boards is the possibility of material movement during processing. A slight lack of balance in the lay-up can result in a locked-in stress which will cause the board to bow or warp. The pressure involved in laminating may cause an inner layer trace to slip sideways. This condition should not happen if the layout is uniform and the initial light pressure is properly applied. If there is a slight fault in the process and a trace moves over to bridge a narrow clearance, the whole board is lost.

# 1.8. Cost of Multi-layered Boards

The biggest disadvantage to multilayer boards, when compared to double sided boards of comparable size, is the high cost. After being bonded, the multilayer goes through the same processes as does a double-sided board, in addition to the etch back of the base material. Each inner layer has to have its traces pattern etched, with all the cleaning and intermediate inspection involved. Then the layers must be stacked carefully on the dowels and bonded together. Due to the incremental

number of process steps and the more rigorous inspection, the cost of multilayer boards goes up dramatically as the number of layers and drill count goes up. The following table provides a cost comparison in cents per hole.

Table 5 Cost Comparison for PCB (Approx. Cents per Hole) [13]

| Board Type   | Process | Cost  |

|--------------|---------|-------|

| Single-sided | Punched | 1.0   |

| Double-sided | Punched | 2.5   |

| Double-sided | Drilled | 5.2   |

| Multilayer   |         |       |

| 4 layers     | Drilled | 22.0  |

| 10 layers    | Drilled | 120.0 |

| >10 layers   | Drilled | 380.0 |

### 1.9. Printed Circuit Board Failure Modes and Causes

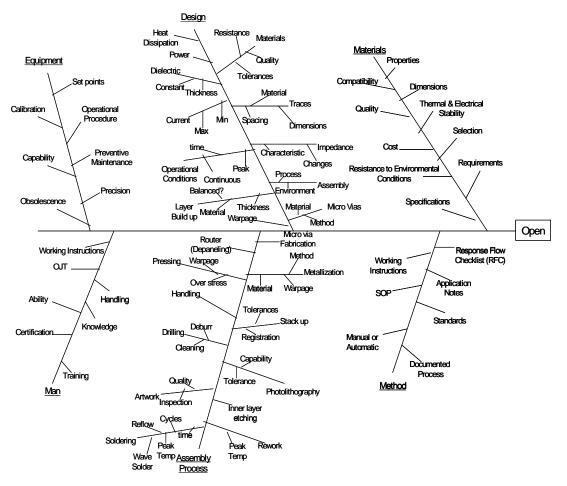

The failure modes on the PCBs can be categorized in a hierarchical structure, in which the mechanisms and causes are site or location dependent. In this section, the most critical failures modes will be presented along with possible causes, in order to provide a synthesized analysis. A fish bone diagram is used.

# 1.9.1. Open Circuit

The electric path of a signal is defined on a PCB by the circuit traces. The continuity of these paths is critical for the functionality and reliability of circuit boards. An open circuit is defined as an electrical discontinuity, and will adversely affect the functionality of the board. This well known failure mode can be induced by multiple causes, and the physical processes by which the causes transforms into the

observed effect (mechanism) will depend on the life cycle conditions as well as the location (site) on the PCB. Figure 15 provides a detailed cause and effect diagram for the Open Circuit defect. On this diagram the main categories are divided in materials, design, equipment, method, man, and assembly process. For the equipment, man, and method sections, the analysis focuses on the practices on the manufacturing floor for the printed circuit board as well as on the circuit assembly manufacturing site. Materials, design, and assembly process represent the areas in which engineering knowledge along with failure analysis can provide the biggest contribution. Materials' compatibility with the environmental conditions as well as with the other materials used has been identified as a key element in product reliability. This is especially true in applications above ambient temperature where CTE mismatches are the cause for internal residual stresses, which could cause delamination resulting in an open circuit. Figure 15 provides a visual aid for the complexity and interrelated nature of the failure analysis.

Depending on the site, open circuits can be observed by visual inspection, non destructive x-ray analysis, or destructive cross section. The industry standard responsible for providing the acceptability guidelines for PCBs is the IPC-A-600G, where the different conditions are presented and evaluated based on the criticality of the product.

Figure 15 Cause and effect diagram for open circuit on a PCB [55].

# 1.9.2. Short Circuit

A short circuit will occur whenever a low resistance path is formed between conductors in the presence of a voltage potential. This can sometimes result in catastrophic damage to the PCB or the whole system with fire or explosion in the worst case. This type of defect is also known to cause intermittent failures in electronic devices, which can be tedious to troubleshoot. A short circuit can be the

start of a propagating fault that will burn or melt the PCB material leaving no evidence of the root cause.

As can be observed from Figure 16, there are multiple causes for its formation and there are multiple causes for its formations. Thre are also a whole range of failure mechanisms that are activated by different factors occurring throughout the life cycle environment of the product. A short circuit is the observed effect or failure mode, but there are multiple possible causes for this to happen and a variety of associated failure mechanisms. Figure 16 provides a cause and effect diagram for the short circuit problem.

Figure 16 Cause and Effect Diagram for Short Circuit on a PCB [55].

Three categories on the above cause and effect diagram namely, Man, Method, and Equipment are mainly associated with the quality of manufacturing practices on the shop floor. Areas such as Materials are associated with the design practices. The assembly process can be associated with both quality and design issues, and deficiencies in these areas could have a detrimental effect on the product. The assembly process can be associated with both quality and design issues, and deficiencies in these areas could have a detrimental effect on the product.

### 1.9.3. Delamination

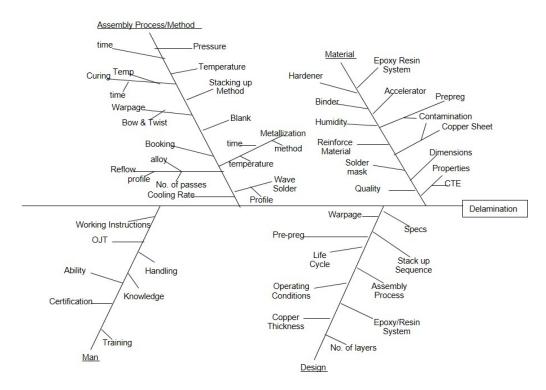

As previously discussed, multi-layer boards are basically a stack-up composite system in which a series of laminates are bonded together by means of a pre-preg dielectric layer impregnated with semi-cured epoxy-resin. The bonding strength of all of these interlayers depends on the strength of the thermo set material, which in turn is a function of thermo-mechanical properties such as glass transition temperature, CTE, and stiffness of the epoxy. The bonding capacity of these materials will also depend upon the curing time and temperature as well as the presence and efficiency of the accelerators, binders, and catalysts in the epoxy system. Failure to hold the stacked layers in the out of plane "z" direction will result in a failure mode known as delamination, which is a non-acceptable condition on PCB integrity. Figure 17 provides a cause and effect diagram for this

failure mode, where the main categories can be listed as Assembly Process/Method, Materials, Man, and Design.

Causes related to human behavior during the manufacturing process must be controlled in order to reduce the probability of occurrence. Materials, specifically the properties and cross compatibility among them, along with the resistance to environmental conditions are the most critical factors. The assembly process/methods are basically the source for energy, which is required for the failure mechanism to activate.

Figure 17 Cause and Effect Diagram for Delamination [55] [20][21][22].

Delamination has been historically attributed to high levels of humidity absorbed in the dielectric material. Investigations which were part of this research have shown that the increased build up of humidity was caused by under curing of the epoxy resin. It was observed that delamination occurred in samples where the epoxy was not fully polymerized.

# 1.10. Lead-Free Solder and Effects on PCBs

With the European Union's ban of lead from electronic devices, manufacturers of PCBs have developed new formulations of resin systems to withstand the increased thermal load on the laminate materials when using lead-free solders. Factors that are taken into account include risk to functionality, changes in processing techniques, material changes, and effects on the applicability of the new PCBs [3] [12] [51].

The functionality of new lead-free compatible PCBs is to withstand the increase temperatures produced during a lead-free soldering process (which is roughly a 30°C temperature increase). They have to be able to retain the same structural integrity as PCBs manufactured for lead-based soldering. The newer boards must be able to withstand the delaminating of the glass and epoxy used in FR-type boards. Also, warpage of the board must be kept to a minimum to reduce the risk of connection failure on the surface-mounted components during the PCB assembly process. Another function of a lead-free compatible PCB is to maintain proper

structural integrity for a longer soldering and reflow period, which is about 2 minutes longer overall and 30 seconds more in the reflow process compared to the conventional lead-based soldering process.

Most PCB manufacturers have already developed modified FR-4-type PCBs that are capable of withstanding the increased temperatures of the lead-free soldering processes. The key to the successful replacement of traditional FR-4 boards with new modified boards is that the same assembly process techniques can still be used on the new boards, thereby reducing the risk of increased cost from development of new assembly process techniques.

The materials that are used for the production of lead-free compatible FR-4 type PCBs are formulated with the addition of new polymers and epoxy resins with higher glass transition temperatures than conventional epoxy resins. One such example of a higher Tg epoxy resin is bismaleimide triazine, with a glass transition temperature of 205°C, which is close to the maximum reflow temperature of a tincopper-silver solder (244°C) to prevent significant damage to the new lead-free compatible modified FR-4.

The new lead-free compatible PCBs can still be applied in exactly the same manner as current lead-based compatible boards. These applications are in the consumer, military, communication, and aerospace electronics fields to name a few.

# 1.11. Summary

Material makeup and fabrication of PCBs was discussed, along with the manufacturing processes for different types of boards. Process control and inspection techniques used for PCB fabrication along with an overview of common failure modes and causes were also covered. An overview of cost structure was provided, and overall impact of introduction of lead-free processing conditions was discussed.

# Chapter 2: Conductive Anodic Filaments in Printed Circuit Boards

### 2.1 Introduction

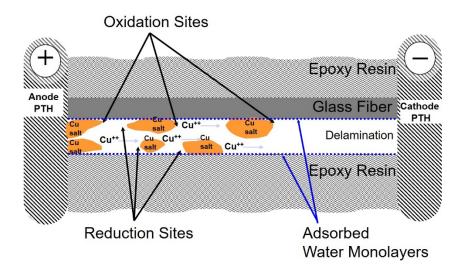

Conductive anodic filament formation, a major cause of failures in printed circuit boards, is an electrochemical process that involves the transport of a metal through or across a nonmetallic medium under the influence of an applied electric field. With an increasing potential to market "green" electronics, environmental and health legislations, and the advent of lead-free and halogen-free initiatives, newer types of printed circuit board materials are being exposed to ever higher temperatures during solder assembly. The higher temperatures can weaken the glass-fiber bonding, thus enhancing conductive anodic filament formation. The effects of the inclusion of halogen-free flame retardants on conductive anodic filament formation in printed circuit boards are not completely understood. Previous studies, along with analysis and examinations conducted on printed circuit boards with failure sites that were due to conductive anodic filament, have shown that the conductive path is typically formed along the delaminated fiber glass and epoxy resin interphases.

The spacing between plated-through-hole edges is estimated to approach 2 mil and even closer. With increases in design density and tighter spacing between

conductors, the possibility of CAF failure in PCB electronic assemblies has also increased. CAF is a failure observed within glass-reinforced epoxy PCB laminates that is caused by an electrochemical process involving the ionic transport of a metal through or across a non-metallic medium under the influence of an applied electric field [24].

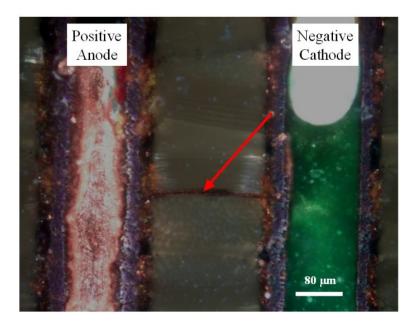

Failures in PCBs account for a significant percentage of field returns in electronic products and systems. The occurrence of CAF deep within the PWB can easily be diagnosed as "Failure Unknown." The Test Services and Failure Analysis Laboratory at CALCE has examined numerous electronic assembly failures due to permanent and intermittent PWB shorts [46] [47] [54]. Many of these failures in assemblies that were sent back after customer complaints could only be duplicated in a relatively high humidity environment since moisture was required to complete the electrical path. CAF is difficult to detect in the field because, once it occurs, sufficient heat is generated to "vaporize" the conductive anodic filament and "clear" the failure. Furthermore, observation of a partial filament formation requires destructive analysis. The growth of the metallic filament is a function of temperature, humidity, voltage, laminate materials, manufacturing processes, and the geometry and spacing of the conductors [25]. The growth of these filaments can cause an abrupt loss of insulation resistance between the conductors under a DC voltage bias.

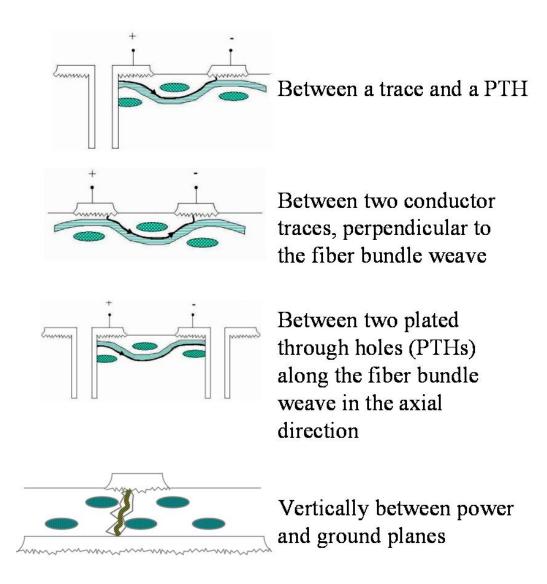

Studies on CAF have found that path formation in a PCB is often along the glass fiber to epoxy matrix interphase (Figure 19). Delamination along the fiber/resin interphase can occur as a result of stresses generated under thermal cycling due to coefficient of thermal expansion (CTE) mismatch between the glass fiber (CTE~5.5 ppm/°C) and the epoxy resin (CTE~65 ppm/°C) (Figure 20). CAF can take place in the plated-through-hole to plated-through-hole (PTH-PTH), PTH-plane, and trace-trace geometries.

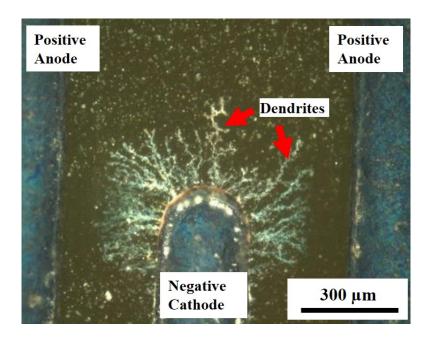

It is also important to differentiate between CAF, which occurs inside of a printed circuit board, and dendritic formation, a phenomenon that occurs on the surface of a printed circuit board, as shown in Figure 18.

Figure 18 Photograph showing the phenomenon of dendritic growth, which occurs on the surfaces of a PCB.

A key characteristic of CAF is that it grows from the positively biased electrode to the negatively biased one inside the circuit board. In contrast, the dendrites from electrochemical reactions grow from the negative to the positively biased electrode. The phenomenon of dendritic formation, which is outside the scope of this research, is often confused with CAF and the terms are used interchangeably. It should be stressed that the growth of surface dendrites is promoted by the presence of contaminants on the board surface, the sources of such contaminants include residues from the PCB fabrication, solder mask application or from the printed circuit board assembly processes, such as the presence of flux residues which are not completely activated.

### 2.2 Literature Review