## ABSTRACT

Title of dissertation: NEW (ZERO-KNOWLEDGE) ARGUMENTS

AND THEIR APPLICATIONS TO VERIFIABLE COMPUTATION

Yupeng Zhang

Doctor of Philosophy, 2018

Dissertation directed by: Professor Charalampos Papamanthou

Department of Electrical and Computer Engineering

Professor Jonathan Katz

Department of Computer Science

We study the problem of argument systems, where a computationally weak verifier outsources the execution of a computation to a powerful but untrusted prover, while being able to validate that the result was computed correctly through a proof generated by the prover. In addition, the zero-knowledge property guarantees that proof leaks no information about the potential secret input from the prover. Existing efficient zero-knowledge arguments with sublinear verification time require an expensive preprocessing phase that depends on a particular computation, and incur big overhead on the prover time and prover memory consumption.

This thesis proposes new constructions for zero-knowledge arguments that overcome the above problems. The new constructions require only a one time preprocessing and can be used to validate any computations later. They also reduce the overhead on the prover time and memory by orders of magnitude. We apply

our new constructions to build a verifiable database system and verifiable RAM programs, leading to significant improvements over prior work.

# NEW (ZERO-KNOWLEDGE) ARGUMENTS AND THEIR APPLICATIONS TO VERIFIABLE COMPUTATION

A dissertation presented by

Yupeng Zhang

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2018

Advisory Committee:

Professor Charalampos Papamanthou, Chair/Advisor

Professor Jonathan Katz, Co-Advisor

Professor Dana Dachman-Soled

Professor Gang Qu

Professor Lawrence Washington

© Copyright by Yupeng Zhang 2018

## Acknowledgments

I would like to begin by thanking my advisors Charalampos (Babis) Papamanthou and Jonathan Katz. Babis recruited me in my first year of PhD and led me to the exciting area of applied cryptography. He always made himself available to answer my questions and discuss the research projects. We usually had several meetings a week, through which I learnt quickly both the theory and the practice of cryptography. He always believed in my ability and encouraged me to come up with better solutions for many research problems, some of which led to papers included in this thesis. He provided great help for me on research, paper writing, presentation and gave me good advice for my future research career. I could not have had such an enjoyable life during my PhD without his guidance.

Jonathan's course on cryptography was the first time I got to know the area. I developed strong interest and fundamental skills during the course and I always believe it is the most important course for my PhD research. During our weekly meetings, he always understood the problems deep and fast, challenged my ideas and made helpful suggestions based on his broad knowledge and rich experience in the research areas. These were essential for me to develop thorough and rigorous solutions in many work. It is my great fortune to have him as my co-advisor. I am also very grateful that my advisors provided full financial support for my PhD and travels to conferences and workshops, so that I can focus on my research, and had opportunities to interact with leading researchers in the field.

I also want to thank the mentors of my summer internships, Nikos Trian-

dopoulos, Payman Mohassel, Ranjit Kumaresan and Melissa Chase. I spent several wonderful summers with them working on various topics that were different from my research at the graduate school. These great experiences helped my learn knowledge and develop interest on other areas such as secure computation and machine learning, and I also enjoyed the opportunities to live and work at different locations, RSA at Boston, Visa Research at the Bay area and MSR at Seattle.

I am also thankful to my collaborators and lab-mates. Dimitris and Daniel provided great help developing the ideas and writing several papers included in this thesis. I want to thank Xiao, Ahmed and Kartik for having interesting discussions on research and life, and senior students Alex, Aishwarya, Chang and Andrew for their advice and help during the early years of my PhD.

Finally, I would like to thank my parents. I would not have started my PhD without their important advice and they have always been showing love, understanding and support during my PhD. I also want to thank my girlfriend, Xi, for her accompany during my graduate school. We have visited many great places all around the world and she made my life outside research wonderful during my PhD.

# Table of Contents

| A | cknow | vledgements                                                 | ii |

|---|-------|-------------------------------------------------------------|----|

| 1 | Intr  | oduction                                                    | 1  |

|   | 1.1   | Related Work                                                | 3  |

| 2 | Prel  | iminaries                                                   | 7  |

|   | 2.1   | Bilinear Pairings and Assumptions                           | 7  |

|   | 2.2   | 1                                                           | 9  |

|   | 2.3   | Interactive Proofs                                          | 11 |

|   |       | 2.3.1 The Sum-Check Protocol                                | 11 |

|   |       | 2.3.2 The CMT Protocol                                      | 13 |

|   | 2.4   | Security Definitions                                        | 17 |

| 3 | Con   | structions                                                  | 20 |

|   | 3.1   | Verifiable Polynomial Delegation                            | 20 |

|   | 3.2   | Improving the Expressiveness of the CMT Protocol            | 30 |

|   | 3.3   | The Construction of Our Argument System                     | 32 |

| 4 | App   | olications: Verifiable Databases                            | 41 |

|   | 4.1   | SQL Queries                                                 | 43 |

|   | 4.2   | Related Work on Verifiable Databases                        | 45 |

|   | 4.3   | Definitions of Verifiable Databases                         | 46 |

|   | 4.4   | Our Construction of Verifiable Databases                    | 49 |

|   | 4.5   | Optimizations for SQL Queries                               | 61 |

|   |       | 4.5.1 Optimizing Equality Testing                           | 62 |

|   |       | 4.5.2 Supporting Inputs/Outputs at Arbitrary Circuit Layers | 65 |

|   |       | 4.5.3 Verifying Set Intersections                           | 67 |

|   |       | 4.5.4 Supporting Expressive Updates                         | 71 |

|   |       | 4.5.5 Efficient Value Insertions                            | 72 |

|   | 4.6   | Experimental Results                                        | 73 |

|   |       | 4.6.1 Experimental Setup                                    | 73 |

|   |       | 4.6.2 Performance Comparison: Selection Queries             | 76 |

|    |        | 4.6.3    | Performance Comparison: Update Queries                 | <br>82  |

|----|--------|----------|--------------------------------------------------------|---------|

|    |        | 4.6.4    | Scalability of Our Construction                        | <br>84  |

|    |        | 4.6.5    | Microbenchmarks                                        | <br>85  |

| 5  | App    | licatior | ns: Verifiable RAM Programs                            | 87      |

|    | 5.1    | Prelin   | ninaries on RAM programs                               | <br>90  |

|    |        | 5.1.1    | A Canonical RAM Architecture                           | <br>90  |

|    |        | 5.1.2    | Previous Reductions from RAM to Circuit Satisfiability | <br>92  |

|    | 5.2    | Our N    | New RAM to Circuit Reduction                           | <br>96  |

|    |        | 5.2.1    | Ensuring Correct Instruction Execution                 | <br>97  |

|    |        | 5.2.2    | Verifying Instruction Fetches                          | <br>98  |

|    |        | 5.2.3    | Ensuring Memory Accesses                               | <br>100 |

|    |        | 5.2.4    | Checking Consistency                                   |         |

|    | 5.3    | Exper    | imental Results                                        | <br>103 |

|    |        | 5.3.1    | Comparison with vnTinyRAM and Buffet                   | <br>104 |

|    |        | 5.3.2    | Comparison to Other RAM-based VC systems               | <br>113 |

|    |        | 5.3.3    | Just-in-Time Architecture                              | <br>115 |

|    |        | 5.3.4    | Microbenchmarks                                        | <br>116 |

| 6  | Zero   | Know     | $_{ m ledge}$                                          | 119     |

|    | 6.1    | Buildi   | ing Blocks                                             | <br>120 |

|    | 6.2    |          | Knowledge Polynomial Commitment                        |         |

|    | 6.3    | Zero-I   | Knowledge CMT Protocol                                 | <br>136 |

|    |        | 6.3.1    | A Sum-Check Protocol over Homomorphic Commitments .    | <br>136 |

|    |        | 6.3.2    | A CMT Protocol over Homomorphic Commitments            | <br>142 |

|    | 6.4    | Zero-I   | Knowledge with Function Independent Preprocessing      | <br>152 |

| 7  | Con    | clusion  | s and Future Work                                      | 160     |

|    | 7.1    | Concl    | usions                                                 | <br>160 |

|    | 7.2    | Futur    | e Directions                                           | <br>161 |

| Bi | bliogr | aphy     |                                                        | 163     |

# Chapter 1: Introduction

With the advent of cloud computing, there has been significant interest in techniques for ensuring correctness of computations performed by an untrusted server on behalf of a client. Protocols for verifiable computation (VC) allow a computationally weak verifier to outsource the execution of a computation to a powerful but untrusted prover (e.g., a cloud provider) while being assured that the result was computed correctly. Somewhat more formally, a verifier  $\mathcal{V}$  and prover  $\mathcal{P}$  agree on a function f and an input x. The prover then sends a result y to the verifier, together with a proof that y = f(x), and the verifier can validate that the result is indeed correctly computed. In addition, it is particularly interesting when the time to validate the result on the verifier side is less than the time to compute f(x) on its own.

VC protocols can be constructed from succinct argument systems, where the prover  $\mathcal{P}$  convinces the verifier  $\mathcal{V}$  the validity of a statement, and the proof size and verification time are smaller than the statement itself. See Section 2.4 for formal definitions of argument systems. There is a long line of work constructing VC protocols from argument systems for arbitrary computations, the most prominent of which rely on succinct non-interactive arguments of knowledge (SNARKs) [20,46].

This has resulted in several implemented systems; see Section 1.1 for an overview. However, SNARKs rely on a preprocessing phase, where a trusted party (possibly the verifier) generates a set of public parameters corresponding to a circuit for a specific function f. This preprocessing phase is orders of magnitude slower than evaluating f itself, and can only be used later to prove and verify the results of the same function f on different inputs. In addition, these SNARK-based protocols introduce a big overhead on the running time and the memory consumption of the prover to generate the proof.

In this thesis, we propose a new construction of a argument system for arbitrary computations. At a high level, our construction builds on top of prior work in interactive proofs (IP), and combines them with a verifiable polynomial delegation (VPD) scheme to extend the supported class of computations from P to NP, allowing computations to take auxiliary inputs from the prover without sending them back to the verifier. Compared to existing SNARK-based protocols, the preprocessing phase of our construction is independent of the function and can be used to validate any computation later. Our construction also reduces the overhead on the prover time and memory consumption by orders of magnitude. We apply our new argument system to build VC protocols for verifiable databases and verifiable RAM programs, and show that they lead to significant improvements upon prior work. We also present a variant of our new argument that is zero-knowledge.

## 1.1 Related Work

Verifiable computation was formalized in [45, 72], but research on constructing interactive protocols for verifying general-purpose computations began much earlier with the works of Kilian [57] and Micali [66]. While those works have good asymptotic performance, and follow-up works further optimized those approaches (e.g., [10, 13, 54]), subsequent implementations revealed that the concrete costs of those approaches are prohibitively high for the prover [75].

SNARKs. The next big breakthrough in general-purpose verifiable computation and argument systems came with the work of Gennaro et al. [46] (building upon earlier work by Groth [50] and Lipmaa [63]), which introduced quadratic arithmetic programs (QAPs) and showed that they can be used to capture the correct evaluation of an arithmetic program. QAPs have since been the de-facto tool for constructing efficient succinct arguments of knowledge (SNARKs) [20,23] that can be used to verify arbitrary NP computations. This has led to a long line of research providing both highly-optimized systems [16, 35, 37, 41, 61, 71, 74, 76, 81, 93] and significant protocol refinements [17, 39, 52, 64]. We refer to [85] for a detailed survey.

The major disadvantage of SNARK-based approaches is the extremely high prover time they currently impose. The prover time is  $O(m \log^2 m)$ , with O(m) cryptographic operations (modulo exponentiations in a bilinear group) where m is the number of gates in a arithmetic circuit for a particular function. In our new argument system, the prover time is  $O(m \log m)$  (O(m) for highly regular circuits)

with only O(n) cryptographic operations, where n is the number of inputs and usually much less than m.

In addition, the fastest existing implementations of SNARKs assume a circuitspecific preprocessing step, something that is not practical (and may be impossible) in a scenario where multiple queries that cannot be predicted in advance will be made on a given data. In contrast, our new construction requires only a one-time circuitindependent preprocessing, and can later be used to validate arbitrary computations.

Finally, we remark that the systems mentioned above are all "natively" designed to support verification only when the input is known to the verifier, which is enough for argument systems as defined in Section 2.4. However, in verifiable computation, the verifier also wants to outsource the storage of the input to the prover. Support for outsourced data can be handled by having the verifier compute a succinct hash of its data, and then verifying the hash computation along with verification of the result. However, this adds additional overhead as the hash computation needs to either be computed as part of the arithmetic circuit [29], or checked by an external mechanism [12,41]. Alternatively, one could hard-code the data into the circuit being evaluated, but then the circuit-specific preprocessing needs to be executed after each data update. Instead, our new argument system naturally supports outsourcing data through a commitment and we can also support dynamic data efficiently.

While some other works also aim at verifying arbitrary computations over remotely stored data [27,31,33,55], these approaches are only of theoretical interest at this point.

Interactive Proofs. Interactive proofs were introduced by Goldwasser et al. [49], and have been studied extensively in complexity theory. More recently, proverefficient interactive proofs for log-depth circuits were introduced in [48]. Subsequent works have optimized and implemented this protocol, demonstrating the potential of interactive proofs for practical verifiable computation [36, 78, 81].

#### Structure of the Thesis:

- Chapter 2 introduces background on bilinear groups, circuits, polynomials and the details of the sum-check protocol and the interactive proof protocol of Cormode, Mitzenmacher, and Thaler [36] (that we call the *CMT protocol*). In addition, it formally defines an argument system for verifiable computation and its correctness, soundness and zero-knowledge.

- Chapter 3 presents the detailed construction of our new argument system for verifiable computation. We first show our verifiable polynomial delegation scheme, and an improvement of the CMT protocol that supports a larger class of computation efficiently. Then we present our new argument system combining the VPD and the CMT protocol, followed by the security proofs and complexity analysis.

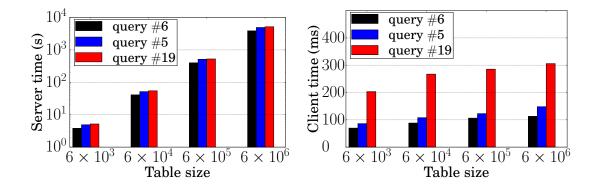

- In Chapter 4, we present a verifiable database system, vSQL, using our new argument protocol. We introduce background on SQL queries, definitions, and our construction of a verifiable database system. We also show several optimizations of our argument system for common SQL queries, followed by experimental results, showing that vSQL improves the prover time by two orders of magnitude and can be used to validate arbitrary SQL queries [88].

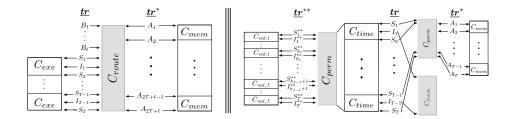

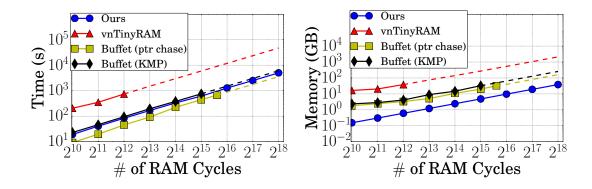

- Chapter 5 describes our construction of verifiable RAM programs using our new argument system as a backend. By utilizing the function-independent preprocessing feature of our argument system, we propose a tighter RAM-to-circuit reduction, and show that the prover time and the memory usage are improved by up to two orders of magnitude upon prior work [90].

- In Chapter 6, we present a variant of our argument system that is zero-knowledge. We show the construction of a zero-knowledge version of the VPD protocol, and show how to run the interactive proof protocol on commitments without leaking intermediate values. We give formal proofs for soundness and zero-knowledge of the construction [89].

- Chapter 7 concludes the thesis, gives a more detailed survey on related work in the literature of verifiable computation, zero-knowledge proofs, verifiable databases and verifiable RAM programs, and describes future research directions.

# Chapter 2: Preliminaries

In this chapter, we present background material on bilinear maps, circuits, polynomials and interactive proofs.

We use  $\lambda$  to denote the security parameter. For a multivariate polynomial f, the degree of each monomial in f is the sum of the powers of its variables; the total degree of f is the maximum degree of any of its monomials.

## 2.1 Bilinear Pairings and Assumptions

We denote by  $(p, \mathbb{G}, \mathbb{G}_T, e, g) \leftarrow \mathsf{BilGen}(1^\lambda)$  generation of bilinear-map parameters, where  $\mathbb{G}$ ,  $\mathbb{G}_T$  are groups of prime order p, with g a generator of  $\mathbb{G}$ , and where  $e: \mathbb{G} \times \mathbb{G} \to \mathbb{G}_T$  is an efficient map, i.e., for all  $P, Q \in \mathbb{G}$  and  $a, b \in \mathbb{Z}_p$  it holds that  $e(P^a, Q^b) = e(P, Q)^{ab}$ . For simplicity we assume symmetric pairings in this thesis, but our scheme can be adapted to use asymmetric pairings as well.

Let PPT stand for "probabilistic polynomial-time". We rely on the following cryptographic assumptions.

Assumption 1 ([24] q-Strong Bilinear Diffie-Hellman (q-SBDH)). For any PPT

adversary Adv, the following probability is negligible:

$$\Pr\left[\begin{array}{c} (p,\mathbb{G},\mathbb{G}_T,e,g) \leftarrow \mathsf{BilGen}(1^\lambda);\\ s \overset{R}{\leftarrow} \mathbb{Z}_p^*;\\ \sigma = ((p,\mathbb{G},\mathbb{G}_T,e,g),g^s,\ldots,g^{s^q});\\ (a,h) \leftarrow \mathsf{Adv}(1^\lambda,\sigma); \end{array}\right].$$

We use  $\mathcal{W}_{\ell,d}$  to denote the collection of all multisets of  $\{1,\dots,\ell\}$  where the cardinality of each element is at most d. The next assumption states the following. Assume a polynomial time algorithm that receives as input two ordered sequences of elements of  $\mathbb{G}$  such that each element contains in the exponent a multivariate monomial with at most  $\ell$  variables and of total degree at most  $\ell \cdot d$ , for some d, and for every ordered pair of elements (across the two sequences) it holds that the elements differ in the exponent by a fixed multiplicative factor  $\alpha$ . Then, if the party outputs a new pair of elements that differ in the exponent by  $\alpha$ , then it must hold that the first of these two elements was computed as a linear combination of the elements of the first sequence (and likewise for the second and the same linear combination). This fact is captured by the existence of a polynomial-time extractor  $\varepsilon$  that, upon the same input outputs this linear combination.

This knowledge-type assumption is a direct generalization of Groth's q-PKE assumption [51] for the case of multivariate polynomials. In fact, q-PKE is by definition the same as (1,q)-PKE, using our notation. Note that  $\mathcal{W}_{\ell,d}$  has size  $O(\binom{\ell+\ell d-1}{\ell d})^1$ . In our construction, we will be using this assumption for the case where  $\binom{\ell+\ell d-1}{\ell d} = \operatorname{poly}(\lambda)$ . The results of [22,28] show the impossibility of knowledge

<sup>&</sup>lt;sup>1</sup>This is the number of multisets of cardinality  $\ell d$ , with elements taken from a set of  $\ell$  elements.

assumptions with respect to arbitrary auxiliary inputs. In the following definition we use the notion of a benign auxiliary input (or, alternatively, a benign state generator), similar to [37,41,53], to refer to auxiliary inputs that make extraction possible, avoiding these negative results. Concretely, our proofs hold assuming the auxiliary input of the extractor comes from a benign distribution.

**Assumption 2**  $((d, \ell)$ -Power Knowledge of Exponent (PKE)). For any PPT adversary Adv there is a polynomial-time algorithm  $\mathcal{E}$  (running on the same random tape) such that for all benign auxiliary inputs  $z \in \{0, 1\}^{poly(\lambda)}$  the following probability is negligible:

$$\Pr\left[\begin{array}{ll} (p,\mathbb{G},\mathbb{G}_{T},e,g)\leftarrow \mathsf{BilGen}(1^{\lambda});\tau_{1},\ldots,\tau_{\ell},\alpha\overset{R}{\leftarrow}\mathbb{Z}_{p}^{*}; & e(h,g^{\alpha})=e(\tilde{h},g)\\ \sigma=(p,\mathbb{G},\mathbb{G}_{T},e,\{g^{\prod_{i\in W}\tau_{i}},\ g^{\alpha\cdot\prod_{i\in W}\tau_{i}}\}_{W\in\mathcal{W}_{\ell,d}},g^{\alpha}); & : & \wedge\\ \mathbb{G}\times\mathbb{G}\ni(h,\tilde{h})\leftarrow \mathsf{Adv}(1^{\lambda},\sigma,z); & \prod_{W\in\mathcal{W}_{\ell,d}}g^{a_{W}\prod_{i\in W}\tau_{i}}\neq h\\ (a_{0},\ldots,a_{|\mathcal{W}_{\ell,d}|})\leftarrow\mathcal{E}(1^{\lambda},\sigma,z); & W\in\mathcal{W}_{\ell,d} & \\ \end{array}\right].$$

# 2.2 Circuit and Polynomial Notations

An arithmetic circuit C is a directed acyclic graph whose vertices are called gates and whose edges are called wires. Every in-degree 0 gate in C is labeled by a variable from a set of variables  $X = \{x_1, \dots, x_n\}$  and is referred to as an input gate. All other gates in C have in-degree 2, are labeled by elements from  $\{+, \times\}$ , and referred to as addition and multiplication gates, respectively. Every gate of out-degree 0 is called an output gate. In the following, we focus only on layered circuits and we assume that the output gates are ordered. We say that a circuit is

layered if it can be divided into disjoint sets  $L_1, \dots, L_k$  such that every gate of g belongs to some set  $L_i$  and all the wires of C connect gates in two consecutive layers (i.e., between  $L_{j+1}$  and  $L_j$  for some j). We write  $C: \mathbb{F}^n \to \mathbb{F}^m$  to indicate that C is an arithmetic circuit with n inputs and m outputs evaluated (as defined in a natural way) over a field  $\mathbb{F}$ . We denote by |C| the number of gates in the circuit C, by width $_i(C)$  the number of gates in the i-the layer of C and by width $_i(C)$  the maximum width of C, i.e., width $_i(C) = \max_i \{ \text{width}_i(C) \}$ .

**Polynomial decomposition.** We use the following lemma for polynomial decomposition.

**Lemma 1** ([69]). Let  $f: \mathbb{F}^{\ell} \to \mathbb{F}$  be a polynomial. For all  $t \in \mathbb{F}^{\ell}$  there exist efficiently computable polynomials  $q_1, \ldots, q_{\ell}$  such that:  $f(x) - f(t) = \sum_{i=1}^{\ell} (x_i - t_i) q_i(x)$  where  $t_i$  is the ith element of t.

**Multilinear extensions.** For any function  $V:\{0,1\}^{\ell}\to\mathbb{F}$  we define the multilinear extension,  $\widetilde{V}:\mathbb{F}^{\ell}\to\mathbb{F}$ , of V as follows:

$$\widetilde{V}(x_1, \cdots, x_\ell) = \sum_{b \in \{0,1\}^\ell} \prod_{i=1}^\ell \mathcal{X}_{b_i}(x_i) V(b)$$

(2.1)

where  $b_i$  is the *i*-th bit of b,  $\mathcal{X}_1(x_i) = x_i$  and  $\mathcal{X}_0(x_i) = 1 - x_i$ . Note that  $\widetilde{V}$  is the unique polynomial that has degree at most 1 in each of its variables that satisfies  $\widetilde{V}(x) = V(x)$  for all  $x \in \{0,1\}^{\ell}$ .

Multilinear extensions of arrays. An array  $A = (a_0, \dots, a_{n-1})$  where  $a_i \in \mathbb{F}$  can be viewed as a function  $A : \{0, 1\}^{\log n} \to \mathbb{F}$  such that  $A(i) = a_i$  for all  $0 \le i \le n-1$ . In the sequel, we abuse terminology by defining (in the natural way) the multilinear

extension  $\tilde{A}$  of an array A.

### 2.3 Interactive Proofs

An interactive proof [49] is a protocol that allows a prover  $\mathcal{P}$  to convince a verifier  $\mathcal{V}$  of the validity of some statement. We phrase this in terms of  $\mathcal{P}$  trying to convince  $\mathcal{V}$  that f(x) = 1, where f is fixed and x is the common input. Of course, an interactive proof in this sense is only interesting if the running time of  $\mathcal{V}$  is less than the time to compute f. Let  $\langle \mathcal{P}, \mathcal{V} \rangle(x)$  denote the output of  $\mathcal{V}$  after the interactions with  $\mathcal{P}$  on input x.

**Definition 1.** Let f be a boolean function. A pair of interactive algorithms  $(\mathcal{P}, \mathcal{V})$  is an interactive proof for f with soundness  $\epsilon$  if the following holds.

• Completeness: For every x such that f(x) = 1 it holds that

$$\Pr[\langle \mathcal{P}, \mathcal{V} \rangle(x) = 1] = 1.$$

•  $\epsilon$ -Soundness: For any x with  $f(x) \neq 1$  and any  $\mathcal{P}^*$  it holds that

$$\Pr[\langle \mathcal{P}^*, \mathcal{V} \rangle(x) = 1] \le \epsilon.$$

Note that the above can be easily extended to prove that g(x) = y (where x, y are common input) by considering the function f defined as f(x, y) = 1 iff g(x) = y.

### 2.3.1 The Sum-Check Protocol

A fundamental interactive protocol that serves as an important building block for our work is the *sum-check protocol* [65]. Here, the common input of the prover and verifier is an  $\ell$ -variate polynomial  $g(x_1, \ldots, x_{\ell})$  over a field  $\mathbb{F}$ ; the prover's goal is to convince the verifier that

$$H = \sum_{b_1 \in \{0,1\}} \sum_{b_2 \in \{0,1\}} \dots \sum_{b_\ell \in \{0,1\}} g(b_1, b_2, \dots, b_\ell).$$

Note that direct computation of H by  $\mathcal{V}$  requires at least  $2^{\ell}$  work. Using the sumcheck protocol, the verifier's computation is exponentially smaller. The protocol proceeds in  $\ell$  rounds, as follows. In the first round, the prover sends the univariate polynomial  $g_1(x_1) \stackrel{\text{def}}{=} \sum_{b_2,\dots,b_{\ell} \in \{0,1\}} g(x_1,b_2,\dots,b_{\ell})$ ; the verifier checks that the degree of  $g_1$  is at most the degree of  $x_1$  in g, and that  $H = g_1(0) + g_1(1)$ ; it rejects if these do not hold. Next,  $\mathcal{V}$  sends a uniform challenge  $r_1 \in \mathbb{F}$ . In the ith round  $\mathcal{P}$  sends the polynomial  $g_i(x_i) \stackrel{\text{def}}{=} \sum_{b_{i+1},\dots,b_{\ell} \in \{0,1\}} g(r_1,\dots,r_{i-1},x_i,b_{i+1},\dots,b_{\ell})$ . The verifier checks the degree of  $g_i$  and verifies that  $g_{i-1}(r_{i-1}) = g_i(0) + g_i(1)$ ; if so, it sends a uniform  $r_i \in \mathbb{F}$  to the prover. After the final round,  $\mathcal{V}$  accepts only if  $g(r_1,\dots,r_{\ell}) = g_{\ell}(r_{\ell})$ . We have [65]:

**Theorem 1.** For any  $\ell$ -variate, total-degree-d polynomial g over  $\mathbb{F}$ , the sum-check protocol is an interactive proof for the function f(H) = 1 (where f(H) = 1 iff  $\sum_{b_1 \in \{0,1\}} \dots \sum_{b_\ell \in \{0,1\}} g(b_1,\dots,b_\ell) = H$ ) with soundness  $d \cdot \ell/|\mathbb{F}|$ . Moreover,  $\mathcal{V}$  performs  $poly(\ell)$  arithmetic operations over  $\mathbb{F}$  and one evaluation of g on a random point r.

**Remark 1.** When g is a multilinear polynomial (the degree of each variable is at most 1, and the total degree is  $\ell$ ), the running time of  $\mathcal{P}$  in round i of the sum-check protocol is  $\min\{O(m), O(2^{\ell-i})\}$ , where m is the total number of distinct monomials in g [36, 78, 81].

### 2.3.2 The CMT Protocol

Cormode et al. [36, 80], building on work of Goldwasser et al. [48], show an efficient interactive proof for a certain class of functions.

**High-level overview.** Let C be a depth-d layered arithmetic circuit over a finite field  $\mathbb{F}$ . The CMT protocol processes the circuit one layer at a time, starting from layer 0 (that contains the output wires) and ending at layer d (that contains the input wires). The prover  $\mathcal{P}$  starts by proposing a value y for the output of the circuit on input x. Then, in the ith round,  $\mathcal{P}$  reduces a claim (i.e., an algebraic statement) about the values of the wires in layer i to a claim about the values of the wires in layer i+1. The protocol terminates with a claim about the wire values at layer d (i.e., the input wires) that can be checked directly by the verifier  $\mathcal{V}$  who knows the input x. If that check succeeds, then  $\mathcal{V}$  accepts.

Notation. Before describing the protocol more formally we introduce some additional notation. Let  $S_i$  be the number of gates in the ith layer and set  $s_i = \lceil \log S_i \rceil$  so  $s_i$  bits suffice to identify each gate at the ith layer. The evaluation of C on an input x assigns in a natural way a value in  $\mathbb{F}$  to each gate in the circuit. Thus, for each layer i we can define a function  $V_i: \{0,1\}^{s_i} \to \mathbb{F}$  that takes as input a gate g and returns its value (and returns 0 if g does not correspond to a valid gate). Using this notation,  $V_d$  corresponds to the input of the circuit, i.e., x. Finally, we define for each layer i two boolean functions  $\operatorname{add}_i$ ,  $\operatorname{mult}_i$ , which we refer to as wiring predicates, as follows:  $\operatorname{add}_i: \{0,1\}^{s_{i-1}+2s_i} \to \{0,1\}$  takes as input three gates  $g_1, g_2, g_3$ , where  $g_1$  is at layer i-1 and  $g_2, g_3$  are at layer i, and returns 1 if and only if  $g_1$  is an

addition gate whose input wires are the output wires of gates  $g_2$  and  $g_3$ . (We define  $\operatorname{\mathsf{mult}}_i$  for multiplication gates analogously.) The value of a gate g at layer i < d can thus be recursively computed as

$$\begin{split} V_i(g) &= \sum_{u,v \in \{0,1\}^{s_{i+1}}} \Big( \mathsf{add}_{i+1}(g,u,v) \cdot (V_{i+1}(u) + V_{i+1}(v)) \\ &+ \mathsf{mult}_{i+1}(g,u,v) \cdot (V_{i+1}(u) \cdot V_{i+1}(v)) \Big). \end{split}$$

**Protocol details.** One idea is for  $\mathcal{V}$  to verify that y = C(x) by checking that  $V_i(g)$  is computed correctly for each gate g in each layer i. Since  $V_i(g)$  can be expressed as a summation, this could be done using the sum-check protocol from Section 2.3.1. However, the sum-check protocol operates on polynomials defined over  $\mathbb{F}$  and therefore we need to replace terms with their multilinear extensions. That is:

$$\tilde{V}_{i}(z) = \sum_{\substack{g \in \{0,1\}^{s_{i}} \\ u,v \in \{0,1\}^{s_{i}} \\ u,v \in \{0,1\}^{s_{i}} \\ u,v \in \{0,1\}^{s_{i}} \\ 1}} \tilde{\beta}_{i}(z,g) \cdot \left( \tilde{\text{add}}_{i+1}(g,u,v) \cdot (\tilde{V}_{i+1}(u) + \tilde{V}_{i+1}(v)) + \tilde{\text{mult}}_{i+1}(g,u,v) \cdot (\tilde{V}_{i+1}(u) \cdot \tilde{V}_{i+1}(v)) \right), \tag{2.2}$$

where  $\tilde{\mathsf{add}}_i$  (resp.,  $\tilde{\mathsf{mult}}_i$ ) is the multilinear extension of  $\mathsf{add}_i$  (resp.,  $\mathsf{mult}_i$ ) and  $\tilde{\beta}_i$  is the multilinear extension of the selector function that takes two  $s_i$ -bit inputs a, b and outputs 1 if a = b and 0 otherwise. However, this approach would incur a cost to the verifier larger than the cost of evaluating C, as it requires one execution of the sum-check protocol per gate.

<sup>&</sup>lt;sup>2</sup>Although using  $\tilde{\beta}$  is not strictly necessary here [79], we use it in our construction to improve efficiency when C is composed of many parallel copies of different smaller circuits in Section 3.2.

Instead, by leveraging the recursive form of  $\tilde{V}_i$ , correctness of the circuit evaluation can be checked with a single execution of the sum-check protocol for each layer i, as follows. Assume for simplicity that the output of the circuit is a single value. The interaction begins at level 0, with the prover claiming that  $y = \tilde{V}_0(0)$  (i.e., the circuit's output) for some value y. The two parties then execute the sum-check protocol for the polynomial  $f_{0,0}$  in order to check this claim. Recall that, at the end of this execution,  $\mathcal{V}$  is supposed to evaluate  $f_{0,0}$  at a random point  $\rho \in \mathbb{F}^{s_0+2s_1}$  (the randomness generated by the sum-check verifier). Since  $f_{0,0}$  depends on  $\tilde{V}_1(u)$  and  $\tilde{V}_1(v)$ , in this case  $\mathcal{V}$  has to evaluate  $\tilde{V}_1$  on the random points  $q_1,q_2\in\mathbb{F}^{s_1}$  where  $q_2$  consists of the last  $s_1$  entries of  $\rho$ , and  $q_1$  the previous  $s_1$  entries. If the verifier had access to all the correct gate values at layer 1, it could compute these evaluations himself. Since he does not, however, it must rely on the prover to provide it with these evaluations, say  $v_1, v_2$ . This effectively reduces the validity of the original claim that  $y = \tilde{V}_0(0)$  to the validity of the two claims that  $\tilde{V}_1(q_1) = v_1$  and  $\tilde{V}_1(q_2) = v_2$ . The two parties can now execute the sum-check protocol for these two claims. By repeatedly applying this idea, the final claim by the prover will be stated with respect to  $\tilde{V}_d$  (i.e., the multilinear extension of the circuit's input), which can be checked locally by the verifier who has the input x.

Unfortunately, this approach still potentially requires  $2^d$  executions of the sumcheck protocol, since the number of claims being verified doubles with each level.

Condensing to a single evaluation per layer. Efficiency can be improved by reducing the proof that  $v_1 = \tilde{V}_1(q_1)$  and  $v_2 = \tilde{V}_1(q_2)$  to a single sum-check execution,

as follows. Let  $\gamma: \mathbb{F} \to \mathbb{F}^{s_1}$  be the unique line with  $\gamma(0) = q_1$  and  $\gamma(1) = q_2$ . The prover sends a degree- $s_1$  polynomial h that is supposed to be  $\tilde{V}_1(\gamma(x))$ , i.e., the restriction of  $\tilde{V}_1$  to the line  $\gamma$ . The verifier checks that  $h(0) = v_1$  and  $h(1) = v_2$ , and then picks a new random point  $r'_1 \in \mathbb{F}$  and initiates a *single* invocation of the sumcheck protocol to verify that  $\tilde{V}_1(\gamma(r'_1)) = h(r'_1)$ . Proceeding in this way, it is possible to obtain a protocol that uses only O(d) executions of the sum-check protocol.

We assumed so far that there is a single output value y. Larger outputs can be handled efficiently [81] by adapting the above approach so that the initial claim by the prover is stated directly about the multilinear extension of the claimed output.

The CMT protocol is formally described in Construction 1.

Construction 1 (CMT protocol). Let  $\mathbb{F}$  be a prime-order field, and let  $C : \mathbb{F}^n \to \mathbb{F}^k$  be a depth-d layered arithmetic circuit.  $\mathcal{P}$  and  $\mathcal{V}$  hold x, y, and  $\mathcal{P}$  wants to convince  $\mathcal{V}$  that y = C(x). To do so:

- 1. Let  $V_0: \{0,1\}^{\lceil \log k \rceil} \to \mathbb{F}$  be such that  $V_0(j)$  equals the jth element of y. Verifier  $\mathcal{V}$  chooses uniform  $r_0 \in \mathbb{F}^{\lceil \log k \rceil}$  and sends it to  $\mathcal{P}$ . Both parties set  $a_0 = \tilde{V}_0(r_0)$ .

- 2. For i = 1, ..., d:

- (a)  $\mathcal{P}$  and  $\mathcal{V}$  run the sum-check protocol for value  $a_{i-1}$  and polynomial  $f_{i-1,r_{i-1}}$  as per Equation (2.2). In the last step of that protocol,  $\mathcal{P}$  provides  $(v_1, v_2)$  for which it claims  $v_1 = \tilde{V}_i(q_1)$  and  $v_2 = \tilde{V}_i(q_2)$ .

- (b) Let  $\gamma : \mathbb{F} \to \mathbb{F}^{s_i}$  be the line with  $\gamma(0) = q_1$  and  $\gamma(1) = q_2$ . Then  $\mathcal{P}$  sends the degree- $s_i$  polynomial  $h(x) = \tilde{V}_i(\gamma(x))$ . Next,  $\mathcal{V}$  verifies that  $h(0) = v_1$  and

$h(1) = v_2$ , and rejects if not. Then  $\mathcal{V}$  chooses uniformly at random  $r'_i \in \mathbb{F}$ , sets  $r_i = \gamma(r'_i)$ ,  $a_i = h(r'_i)$  and sends them to  $\mathcal{P}$ .

3. V accepts iff  $a_d = \tilde{V}_d(r_d)$ , where  $\tilde{V}_d$  is the multilinear extension of the polynomial representing the input x.

Throughout the paper, when reporting asymptotic complexities we omit a factor that is polylogarithmic in the field/blinear group size, implicitly assuming all operations take constant time.

**Theorem 2** ([36, 48, 78, 81]). Let  $C : \mathbb{F}^n \to \mathbb{F}^k$  be a depth-d layered arithmetic circuit. Construction 1 is an interactive proof for the function computed by C with soundness  $O(d \cdot \log S/|\mathbb{F}|)$ , where S is the maximal number of gates per circuit layer. It uses  $O(d \log S)$  rounds of interaction, and the running time of  $\mathcal{P}$  is  $O(|C| \log S)$ . If  $\tilde{\mathsf{add}}_i$  and  $\tilde{\mathsf{mult}}_i$  are computable in time  $O(\operatorname{polylog} S)$  for all layers  $i \leq d$ , then the running time of the verifier  $\mathcal{V}$  is  $O(n+k+d \cdot \operatorname{polylog} S)$ .

**Remark 2** ([78]). If C can be expressed as a composition of (i) parallel copies of a layered circuit C' whose maximum number of gates at any layer is S', and (ii) a subsequent layered "aggregation" circuit C'' of size  $O(|C| \log |C|)$ , the running time of  $\mathcal{P}$  is  $O(|C| \log |S'|)$ .

# 2.4 Security Definitions

In this section, we give the formal definitions of (zero-knowledge) argument systems. Let R be an NP relation. An argument system for R is a protocol between computationally bounded prover  $\mathcal{P}$  and a verifier  $\mathcal{V}$  at the end of which  $\mathcal{V}$

is convinced in the validity of a statement made by  $\mathcal{P}$  of the form "there exists w such that  $(x; w) \in R$ " for some input x. In the sequel we focus on arguments of knowledge which have the stronger property that if the prover manages to convince the verifier of the statement's validity, then the prover must know w. We use the definition of [46] which includes a parameter-generation phase executed by a trusted party, the preprocessor. Formally, consider Definition 2 below.

**Definition 2.** Let R be an NP relation and let  $\lambda$  be a security parameter. A tuple of algorithms  $(\mathcal{G}, \mathcal{P}, \mathcal{V})$  is a zero knowledge argument for R if the following holds.

- Completeness: For every (pk, vk) outout by  $\mathcal{G}(1^{\lambda})$  and all  $(x; w) \in R$  we have  $\langle \mathcal{P}(pk, w), \mathcal{V}(vk) \rangle (x) = 1.$

- Knowledge soundness: For any PPT prover  $\mathcal{P}^*$  there exists a PPT extractor  $\mathcal{E}$  which runs on the same randomness as  $\mathcal{P}^*$  such that for any x it holds that  $\Pr[\langle \mathcal{P}^*(\mathsf{pk},\mathsf{vk}), \mathcal{V}(\mathsf{vk}) \rangle(x) = 1 \land (x,w) \notin R : (\mathsf{pk},\mathsf{vk}) \leftarrow \mathcal{G}(1^{\lambda}), w \leftarrow \mathcal{E}(\mathsf{pk},x)] \leq \mathsf{neg}(\lambda).$

- **Zero knowledge:** There exists a PPT simulator S such that for any PPT adversary A, and auxiliary input  $z \in \{0,1\}^{\mathsf{poly}(\lambda)}$ , the following probability is negligible:

$$\Pr\left[(\mathsf{pk},\mathsf{vk}) \leftarrow \mathcal{G}(1^{\lambda}); (x;w) \in R; \langle \mathcal{P}(\mathsf{pk},w), \mathcal{A}(\mathsf{pk},\mathsf{vk}) \rangle(x) = 1 : (x,w) \leftarrow \mathcal{A}(z,\mathsf{pk},\mathsf{vk})\right] - \\ \Pr\left[(\mathsf{pk},\mathsf{vk},\mathsf{trap}) \leftarrow \mathcal{S}(1^{\lambda}); (x;w) \in R; \langle \mathcal{S}(\mathsf{trap},\mathsf{pk}), \mathcal{A}(\mathsf{pk},\mathsf{vk}) \rangle(x) = 1 : (x,w) \leftarrow \mathcal{A}(z,\mathsf{pk},\mathsf{vk})\right] \\ \text{the definition can be extended in a straight-forward manner for statistical and} \\ \text{perfect zero-knowledge}.$$

We call  $(\mathcal{G}, \mathcal{P}, \mathcal{V})$  a succinct argument system if the running time of  $\mathcal{V}$  is  $poly(\lambda, |x|, \log |w|)$ .

# Chapter 3: Constructions

In this chapter, we present the basic construction of our new argument system for NP that is complete and sound. We defer the zero-knowledge version of our protocol to Chapter 6.

Recall that the CMT protocol, and interactive proof protocols as defined in Definition 1, only allow the prover  $\mathcal{P}$  to convince the verifier  $\mathcal{V}$  that f(x) = 1 for a fixed f and a common input x. It does not allow auxiliary input w to f, limiting the supported class of computation to P. To extend the interactive proof protocols to prove statements in NP, we propose a new scheme for *verifiable polynomial delegation*, which allows the prover  $\mathcal{P}$  to commit a polynomial defined by w efficiently, and later open it to a random evaluation point, as required by the CMT protocol.

## 3.1 Verifiable Polynomial Delegation

In the last step of the CMT protocol, the verifier  $\mathcal{V}_{cmt}$  evaluates a polynomial  $\widetilde{V}_d$  on a random point  $r_d$ . Since the number of terms in  $\widetilde{V}_d$  is equal to the number of input gates of C, this makes the verifier's work linear not only in the size of the input x but also the length of the witness w. We propose a verifiable polynomial delegation (VPD) scheme to address this problem. We give the formal definition of

a VPD scheme here.

**Definition 3.** Let  $\mathbb{F}$  be a finite field,  $\mathcal{F}$  a family of  $\ell$ -variate polynomials over  $\mathbb{F}$ , and d a variable-degree parameter. (KeyGen, Commit, Evaluate, Ver) constitute an extractable VPD scheme for  $\mathcal{F}$  if:

• Perfect completeness. For any polynomial  $f \in \mathcal{F}$  it holds that

$$\Pr\left[\begin{array}{ll} (\mathsf{pp},\mathsf{vp}) \leftarrow \mathsf{KeyGen}(1^\lambda,\ell,d); & \mathsf{Ver}(\mathsf{com},t,y,\pi,\mathsf{vp}) = 1 \\ \\ \mathsf{com} \leftarrow \mathsf{Commit}(f,\mathsf{pp}); & \land \\ \\ (y,\pi) \leftarrow \mathsf{Evaluate}(f,t,\mathsf{pp}); & y = f(t) \end{array}\right] = 1.$$

• Soundness. For any PPT adversary Adv the following probability is negligible:

$$\Pr\left[ \begin{array}{ll} (\mathsf{pp},\mathsf{vp}) \leftarrow \mathsf{KeyGen}(1^\lambda,\ell,d); & \mathsf{Ver}(\mathsf{com},t^*,y^*,\pi^*,\mathsf{vp}) = 1 \\ \\ (f^*,t^*,y^*,\pi^*) \leftarrow \mathsf{Adv}(1^\lambda,\mathsf{pp}); & \land \\ \\ \mathsf{com} \leftarrow \mathsf{Commit}(f^*,\mathsf{pp}); & y^* \neq f^*(t^*) \end{array} \right].$$

Extractability. For any PPT adversary Adv there exists a polynomial-time algorithm ε with access to Adv's random tape such that for all benign auxiliary inputs

z ∈ {0,1}<sup>poly(λ)</sup> the following probability is negligible:

$$\Pr \left[ \begin{array}{ll} (\mathsf{pp},\mathsf{vp}) \leftarrow \mathsf{KeyGen}(1^\lambda,\ell,d); & \mathsf{CheckCom}(\mathsf{com}^*,\mathsf{vp}) = 1 \\ \\ \mathsf{com}^* \leftarrow \mathsf{Adv}(1^\lambda,\mathsf{pp},z); & \land \\ \\ f' \leftarrow \mathcal{E}(1^\lambda,\mathsf{pp},z); & \mathsf{com}^* \neq \mathsf{Commit}(f',\mathsf{pp}) \end{array} \right].$$

where CheckCom checks if a commitment is well-formed.

There are several works in the literature on verifiable polynomial delegation [19,42,56,69]. Our construction extends the scheme of Papamanthou et al. [69] (which itself extends prior work [56] to the multivariate case) to achieve a "knowledge" property, i.e., to ensure that if the server can successfully prove that y is the correct output relative to **com** for some input t, then the server in fact knows a polynomial f of the correct degree for which f(t) = y. Thus, our construction can be viewed as a special-purpose SNARK for polynomial evaluation.

As our starting point we use the selectively secure VPD scheme of Papamanthou et al. [69]. Unfortunately, selective security means that the parameters used for the VPD protocol are computed as a function of the specific point  $r_d$  on which the VPD will be executed. This is insufficient for our application since VPD's parameters will be generated once during the preprocessing phase which happens before the CMT protocol.

To overcome this limitation, we modify this scheme to require the prover to provide additional "extractability" terms as part of the evaluation proof. Our modified VPD scheme is given in Construction 2. We define the *variable degree* of a multivariate polynomial f be the maximum degree of f in any of its variables, and use  $W_{\ell,d}$  to denote the collection of all multisets of  $\{1,\ldots,\ell\}$  for which the multiplicity of any element is at most d.

Construction 2 (Verifiable Polynomial Delegation). Let  $\mathbb{F}$  be a prime-order field, and  $\ell$ , d variable and degree parameters such that  $O(\binom{\ell+\ell d-1}{\ell d})$  is  $poly(\lambda)$ . Consider the following protocol for the family  $\mathcal{F}$  of  $\ell$ -variate polynomials of variable-

degree d over  $\mathbb{F}$ .

- 1. KeyGen( $1^{\lambda}$ ,  $\ell$ , d): Select uniform  $\alpha$ ,  $s_1, \ldots, s_{\ell} \in \mathbb{F}$ ,  $run(p, \mathbb{G}, \mathbb{G}_T, e, g) \leftarrow BilGen(<math>1^{\lambda}$ ) and compute  $\mathbb{P} = \{g^{\prod_{i \in W} s_i}, g^{\alpha \cdot \prod_{i \in W} s_i}\}_{W \in \mathcal{W}_{\ell,d}}$ . The public parameters are  $\mathsf{pp} = ((p, \mathbb{G}, \mathbb{G}_T, e, g), \mathbb{P}, g^{\alpha})$ , and the verifier parameters are  $\mathsf{vp} = ((p, \mathbb{G}, \mathbb{G}_T, e, g), g^{s_1}, \cdots, g^{s_{\ell}}, g^{\alpha})$ . For every  $f \in \mathcal{F}$  we denote by  $\mathsf{pp}_f \subseteq \mathsf{pp}$  the minimal subset of the public parameters  $\mathsf{pp}$  required to invoke Commit and Evaluate on f.

- 2. Commit $(f, \mathsf{pp}_f)$ : If  $f \notin \mathcal{F}$  output null. Else, compute  $c_1 = g^{f(s_i, \dots, s_\ell)}$  and  $c_2 = g^{\alpha \cdot f(s_i, \dots, s_\ell)}$ , and output the commitment  $\mathsf{com} = (c_1, c_2)$ .

- 3. CheckCom(com, vp): Check whether com is well-formed, i.e., output 1 if  $e(c_1, g^{\alpha}) = e(c_2, g)$  and 0 otherwise.

- 4. Evaluate $(f, t, \mathsf{pp}_f)$ : On input  $t = (t_1, \ldots, t_\ell)$ , compute y = f(t). Next, using Lemma 1 compute the polynomials  $q_i(x_i, \ldots, x_\ell)$  for  $i = 1, \ldots, \ell$ , such that  $f(x_1, \ldots, x_\ell) f(t_1, \ldots, t_\ell) = \sum_{i=1}^{\ell} (x_i t_i) \cdot q_i(x_i, \ldots, x_\ell)$ . Output y and the proof  $\pi := \{g^{q_i(s_1, \ldots, s_\ell)}, g^{\alpha q_i(s_1, \ldots, s_\ell)}\}_{i=1}^{\ell}$ .

- 5. Ver(com,  $y, t, \pi, \mathsf{vp}$ ): Parse the proof  $\pi$  as  $(\pi_1, \pi'_1, \dots, \pi_\ell, \pi'_\ell)$ . If  $e(c_1/g^y, g) = \prod_{i=1}^\ell e(g^{s_i-t_i}, \pi_i)$  and  $e(c_1, g^\alpha) = e(c_2, g)$  and  $e(\pi_i, g^\alpha) = e(\pi'_i, g)$  for  $1 \le i \le \ell$  output 1. Otherwise, output 0.

We have the following theorem:

**Theorem 3.** Under Assumptions 1 and 2, Construction 2 is an extractable VPD scheme. For a variable-degree-d  $\ell$ -variate polynomial  $f \in \mathcal{F}$  containing m monomials, algorithm KeyGen runs in time  $O(\binom{\ell(d+1)-1}{\ell d})$ , Commit in time O(m), Evaluate

in time  $O(\ell dm)$ , Ver in time  $O(\ell)$  and CheckCom in time O(1). If d=1, Evaluate runs in time  $O(2^{\ell})$ . The commitment produced by Commit consists of O(1) group elements, and the proof produced by Evaluate consists of  $O(\ell)$  elements of  $\mathbb{G}$ .

*Proof.* The completeness requirement immediately follows from the construction of (KeyGen, Commit, Evaluate, Ver).

We now prove the extractability property. Let  $\mathsf{Adv}$  be a PPT adversary that on input  $(1^\lambda, \mathsf{pp})$ , where  $(\mathsf{pp}, \mathsf{vp})$  is the output of  $\mathsf{KeyGen}(1^\lambda, \ell, d)$ , outputs commitment  $\mathsf{com}^*$  such that  $\mathsf{CheckCom}(\mathsf{com}^*, \mathsf{vp})$  accepts. This implies that  $e(c_1, g^\alpha) = e(c_2, g)$  where  $\mathsf{com}^* \stackrel{\mathrm{def}}{=} (c_1, c_2)$ . By Assumption 2, there exists PPT extractor  $\mathcal{E}'$  for  $\mathsf{Adv}$  such that upon the same input as  $\mathsf{Adv}$ , and with access to the same random tape, outputs  $a_0, \ldots, a_{|\mathcal{W}_{\ell,d}|} \in \mathbb{F}$  such that  $\prod_{W \in \mathcal{W}_{\ell,d}} g^{a_W \prod_{i \in W} s_i} = c_1$ , except with negligible probability. Note that, the coefficients  $(a_0, \ldots, a_{|\mathcal{W}_{\ell,d}|})$  can be encoded as a variable-degree-d,  $\ell$ -variate polynomial that has  $a_i$  as its monomial coefficients. We now build extractor  $\mathcal{E}$ :

- 1. Upon input  $(1^{\lambda}, pp)$ ,  $\mathcal{E}$  runs  $\mathcal{E}'$  on the same input.

- 2.  $\mathcal{E}$  tries to parse the output of  $\mathcal{E}'$  as  $a_0, \ldots, a_{|\mathcal{W}_{\ell,d}|} \in \mathbb{F}$  and aborts if this fails.

- 3.  $\mathcal{E}$  outputs f', where  $f' \in \mathcal{F}$  is the polynomial with coefficients  $a_0, \ldots, a_{|\mathcal{W}_{\ell,d}|}$ .

Note that  $\mathcal{E}$  is PPT as  $\mathcal{E}'$  is PPT and it only performs polynomially many operations in  $\mathbb{F}$ . It remains to argue that f' is a valid pre-image of Commit except with negligible probability. Observe that, if  $\mathcal{E}$  does not abort, it follows from the construction of Commit that Commit(f', pp) = com, where com is the output commitment of Adv.

By assumption 2, the probability that the output  $\mathcal{E}'$  is not a valid set of coefficients is negligible which concludes the proof.

Next, we prove the soundness property. Let  $\mathsf{Adv}$  be a PPT adversary that wins the soundness game with non-negligible probability. For  $i=1,\ldots,\ell$  we define adversary  $\mathsf{Adv}_i$  that receives the same input as  $\mathsf{Adv}$  and executes the same code, but outputs only  $(\pi_i, \pi_i') \in \pi^*$  (where  $\pi^*$  is the proof output by  $\mathsf{Adv}$ ). Moreover, since  $\mathsf{Adv}$  is PPT, all these adversaries are also PPT. Thus, for  $i=1,\ldots,\ell$ , from Assumption 2 there exists PPT  $\mathcal{E}_i$  (running on the same random tape as  $\mathsf{Adv}_i$ ) which on input  $(1^\lambda,\mathsf{pp})$  outputs  $a_{0,i},\ldots,a_{|\mathcal{W}_{\ell,d}|,i}\in\mathbb{F}$  such that the following holds: If  $e(\pi_i,g^\alpha)=e(\pi_i',g)$  then  $\prod_{W\in\mathcal{W}_{\ell,d}}g^{a_{W,i}\prod_{j\in W}s_j}\neq\pi_i$ , except with negligible probability. Note that, the coefficients  $(a_{0,i},\ldots,a_{|\mathcal{W}_{\ell,d}|,i})$  for  $i=1,\ldots,\ell$  can always be encoded as a variable-degree-d,  $\ell$ -variate polynomial which we denote by  $q_i'(\mathbf{x})$  for undefined variable  $\mathbf{x}=(x_1,\ldots,x_\ell)$ .

We construct an adversary  $\mathcal{B}$  that breaks Assumption 1. On input  $(1^{\lambda}, p, \mathbb{G}, \mathbb{G}_T, e, g, g^s, g^{s^2}, \dots, g^{s^{\ell-d}})$ ,  $\mathcal{B}$  does the following:

Parameter generation.  $\mathcal{B}$  implicitly sets  $s_1 = s$  and for  $i = 1, \ldots, \ell$  he chooses  $r_i \in \mathbb{F}$  uniformly at random and sets (also implicitly)  $s_i = s \cdot r_i$ . Then he chooses uniformly at random a value  $\alpha \in \mathbb{F}$ . Next  $\mathcal{B}$  needs to generate the terms in  $\mathbb{P} = \{g^{\prod_{i \in W} s_i}, g^{\alpha \cdot \prod_{i \in W} s_i}\}_{W \in \mathcal{W}_{\ell,d}}$ . Since the exponent of each term is a product of at most  $\ell \cdot d$  factors where each factor is one of the values  $s_i = s \cdot r_i$ , it can be written as a polynomial in s with degree at most  $\ell \cdot d$ . Therefore,  $\mathcal{B}$  can compute these terms from the values  $g, g^s, g^{s^2}, \ldots, g^{s^{\ell \cdot d}}$  and  $\alpha$ . Finally,  $\mathcal{B}$  runs Adv on input  $(1^{\lambda}, \mathsf{pp})$ ,

where  $pp = (p, \mathbb{G}, \mathbb{G}_T, e, g, g^{\alpha}, \mathbb{P}).$

Query evaluation. Upon receiving  $(f^*, t^*, y^*, \pi^*)$  from Adv,  $\mathcal{B}$  first runs Commit  $(f^*, \mathsf{pp})$  to receive  $\mathsf{com} \stackrel{\mathrm{def}}{=} (c_1, c_2)$  and then runs  $\mathsf{Ver}(\mathsf{com}, t^*, y^*, \pi^*, \mathsf{vp})$  where  $\mathsf{vp} = (1^\lambda, p, \mathbb{G}, \mathbb{G}_T, e, g, g^s, g^{s^2}, \dots, g^{s^{\ell d}}, g^\alpha)$ . If  $\mathsf{Ver}$  rejects,  $\mathcal{B}$  aborts, else he runs extractors  $\mathcal{E}_1, \dots, \mathcal{E}_\ell$  (defined above) on the same input as Adv and receives polynomials  $q_1', \dots, q_\ell'$ . If for the output of any of the  $\mathcal{E}_i$  it holds that  $\prod_{W \in \mathcal{W}_{\ell,d}} g^{a_{W,i} \prod_{j \in W} s_j} \neq \pi_i$ ,  $\mathcal{B}$  aborts. Otherwise, let  $\delta = y^* - f^*(t^*)$  and let  $Q(\mathbf{x})$  be the polynomial over  $\mathbb{F}$  defined as  $Q(\mathbf{x}) \stackrel{\mathrm{def}}{=} f^*(\mathbf{x}) - f^*(t^*) - \sum_{i=1}^\ell (x_i - t_i) q_i'(\mathbf{x})$  where  $t^* \stackrel{\mathrm{def}}{=} (t_1, \dots, t_\ell)$ .  $\mathcal{B}$  picks  $\tau \in \mathbb{F}$  uniformly at random. If  $g^\tau = g^{-s}$ , he sets  $\tau \leftarrow \tau + 1$ . He then computes polynomial  $Q'(x) \stackrel{\mathrm{def}}{=} Q(\mathbf{x})/(\tau + x_1)$  and finally outputs  $(\tau, e(g, g)^{\delta^{-1} \cdot Q'(s_1, \dots, s_\ell)})$  as a challenge tuple for Assumption 1.

Since  $s_1 = s, s_2 = r_2 \cdot s, \ldots, s_\ell = r_\ell \cdot s$ , we have  $Q'(s_1, \ldots, s_\ell) = Q''(s)$  where Q'' is an efficiently computable univariate polynomial of degree  $\ell \cdot d$  hence  $e(g,g)^{-\delta \cdot Q'(s_1,\ldots,s_\ell)}$  is computable from  $(1^{\lambda},p,\mathbb{G},\mathbb{G}_T,e,g,g^s,g^{s^2},\ldots,g^{s^{\ell \cdot d}})$ .  $\mathcal{B}$  is clearly PPT since all of  $\mathcal{E}_i$  are PPT and he performs polynomially many operations in  $\mathbb{F},\mathbb{G},\mathbb{G}_T$ . Next, we analyze the success probability of  $\mathcal{B}$ . Recall that, by assumption Adv succeeds in violating soundness with probability  $\epsilon$ . We observe that, conditioned on not aborting,  $\mathcal{B}$ 's output is always a valid tuple for breaking Assumption 1. Let us argue why this is true. Since verification succeeds, it holds that

$e(c_1/g^{y^*},g) = \prod_{i=1}^{\ell} e(g^{s_i-t_i},\pi_i)$ ; since extraction succeeds, this can be replaced with

$$e(g,g)^{f^*(s_1,\dots,s_\ell)-\delta-f^*(t^*)} = \prod_{i=1}^{\ell} e(g^{s_i-t_i}, g^{q'_i(s_1,\dots,s_\ell)})$$

$$e(g,g)^{\delta} = e(g,g)^{f^*(s_1,\dots,s_\ell)-f^*(t^*)} \prod_{i=1}^{\ell} e(g^{s_i-t_i}, g^{-q'_i(s_1,\dots,s_\ell)})$$

$$e(g,g)^{\delta} = e(g,g)^{f^*(s_1,\dots,s_\ell)-f^*(t^*)-\sum_{i=1}^{\ell} (s_i-t_i)q'_i(s_1,\dots,s_\ell)}.$$

By the definition of Q' it follows that

$$e(g,g)^{\delta} = e(g,g)^{Q(s_1,\dots,s_{\ell})}$$

$$e(g,g)^{\frac{\delta}{\tau+s_1}} = e(g,g)^{\frac{Q(s_1,\dots,s_{\ell})}{\tau+s_1}} = e(g,g)^{Q'(s_1,\dots,s_{\ell})}$$

$$e(g,g)^{\frac{1}{\tau+s_1}} = e(g,g)^{\delta^{-1} \cdot Q'(s_1,\dots,s_{\ell})}.$$

Thus, the final piece in order to conclude the proof is to bound the probability that  $\mathcal{B}$  aborts. Note that, conditioned on Adv winning,  $\mathcal{B}$  will only abort if extraction fails which can only happen with negligible probability  $\operatorname{neg}(\lambda)$ . This holds since, if verification succeeds it must be that  $e(\pi'_i, g) = e(\pi_i, g^{\alpha})$  for  $i = 1, \ldots, \ell$  and in this case, by Assumption 2, extraction for any of  $\mathcal{E}_1, \ldots, \mathcal{E}_{\ell}$  fails with negligible probability. Since  $\ell$  is polynomial in  $\lambda$  it follows that the probability any of them fails (which by a union bound is at most equal to the sum of each individual failure probability) is also negligible.

Finally, let us argue that the polynomial division  $Q(\mathbf{x})/(\tau + x_1)$  is always possible. Recall, that for polynomials defined over finite fields division is always possible assuming that the dividend's degree is at least as large as that of the divisor's. Moreover, the degree of the quotient is at most that of the dividend's and that of the remainder is strictly smaller than that of the divisor. Let us assume for

contradiction that  $Q(\mathbf{x})$  is a constant polynomial. Since,  $e(g,g)^{\delta} = e(g,g)^{Q(s_1,\ldots,s_{\ell+1})}$ and e(g,g) is a generator or  $\mathbb{G}_T$ , it must be that  $Q(\mathbf{x}) \stackrel{\text{def}}{=} \delta$  therefore we can write

$$-\delta = \sum_{i=1}^{\ell} (x_i - t_i) q_i'(\mathbf{x}) - f^*(\mathbf{x}) + f^*(t^*)$$

$$f^*(\mathbf{x}) - \delta - f^*(t^*) = \sum_{i=1}^{\ell} (x_i - t_i) q_i'(\mathbf{x})$$

$$f^*(\mathbf{x}) - y^* = \sum_{i=1}^{\ell} (x_i - t_i) q_i'(\mathbf{x})$$

From the above relation it follows that  $t^*$  is a root of the polynomial  $f' \stackrel{\text{def}}{=} f^*(\mathbf{x}) - y^*$ , i.e.,  $f'(t^*) = 0$  which implies that  $f^*(t_1, \dots, t_\ell) = y^*$ . Thus, in this case,  $y^*$  is the correct evaluation of  $f^*$  on  $t^*$ , i.e.,  $\delta = 0$  and Adv did not cheat. In all other cases, the polynomial division is possible.

From the above analysis it follows that the probability that  $\mathcal{B}$  succeeds is at least  $(1-\text{neg}(\lambda))\epsilon$ . By assumption,  $\epsilon$  is the non-negligible probability that Adv wins the soundness game, therefore  $\mathcal{B}$ 's success probability is also non-negligible. This contradicts Assumption 1 and our proof is complete.

**Asymptotic analysis.** The claims for the general polynomial case follow directly from the analysis of [69]. For d = 1, i.e., for multi-linear polynomials, we prove the tighter bound for the runtime of Evaluate below.

Recall that during Evaluate the prover computes polynomials  $q_i(x_i, \ldots, x_\ell)$  for  $i=1,\ldots,\ell$ , such that  $f(x_1,\ldots,x_\ell)=\sum_{i=1}^\ell (x_i-t_i)\cdot q_i(x_i,\ldots,x_\ell)+f(t_1,\ldots,t_\ell)$  and proof  $\pi=\{g^{q_i(s_i,\ldots,s_\ell)},g^{\alpha q_i(s_i,\ldots,s_\ell)}\}_{i=1}^\ell$ . We start by computing  $q_1(x_1,\ldots,x_\ell)$ . Since the degree of every variable is at most 1, the multi-linear polynomial f can be written as  $f(x_1,\ldots,x_\ell)=g(x_2,\ldots,x_\ell)+x_1\cdot h(x_2,\ldots,x_\ell)$ , where  $g(x_2,\ldots,x_\ell)$  and

$h(x_2, \ldots, x_\ell)$  are multi-linear polynomials of variables  $x_2, \ldots, x_\ell$ . In this way, f can be decomposed as

$$f(x_1, \dots, x_\ell) = g(x_2, \dots, x_\ell) + x_1 \cdot h(x_2, \dots, x_\ell)$$

$$= (g(x_2, \dots, x_\ell) + t_1 \cdot h(x_2, \dots, x_\ell)) + (x_1 - t_1)h(x_2, \dots, x_\ell)$$

$$= R_1(x_2, \dots, x_\ell) + (x_1 - t_1)h(x_2, \dots, x_\ell).$$

We set  $q_1(x_1,\ldots,x_\ell)=h(x_2,\ldots,x_\ell)$  (which means  $q_1$  contains no monomial with  $x_1$ ), and proceed to decompose the multi-linear polynomial  $R_1(x_2,\ldots,x_\ell)$  with  $\ell-1$  variables in the same way as f to compute  $q_2(x_2,\ldots,x_\ell)$ . Regarding the complexity of this, note that both  $g(x_2,\ldots,x_\ell)$  and  $h(x_2,\ldots,x_\ell)$  contain at most  $2^{\ell-1}$  monomials. Therefore, it takes  $2^{\ell-1}$  additions and multiplications to compute  $q_1(x_1,\ldots,x_\ell)$  and  $R_1(x_2,\ldots,x_\ell)$ , and  $2^{\ell-1}$  exponentiations to generate  $g^{q_1(s_1,\ldots,s_\ell)}$  and  $g^{\alpha q_1(s_1,\ldots,s_\ell)}$  in the proof, respectively. The exact same reasoning applies for all of  $q_3,\ldots,q_\ell$ . At the last step after computing  $q_\ell(x_\ell)$ , the remaining constant term is equal to the answer  $f(t_1,\ldots,t_\ell)$ . In general, in the ith step, we are decomposing  $R_{i-1}(x_i,\ldots,x_\ell)$  with  $\ell-i+1$  variables in the same way above to compute  $q_i(x_i,\ldots,x_\ell)$  and  $R_i(x_{i+1},\ldots,x_\ell)$ , and the complexity is  $O(2^{\ell-i})$ . Thus, the total complexity of computing  $q_1,\ldots,q_\ell$  is  $O(2^{\ell-1})+O(2^{\ell-2})+\ldots=O(2^\ell)$ . The polynomial evaluation in order to get the answer takes the same time. Each pair  $\pi_i,\pi_i'$  is computed with two exponentiations, thus the overall running time is  $O(2^\ell)$ .

### 3.2 Improving the Expressiveness of the CMT Protocol

As presented in Theorem 2 and Remark 2, the prover complexity of the CMT protocol is in particular efficient if the circuit can be represented as many parallel copies of the same small sub-circuit. In this section, we show how to modify the CMT protocol to achieve the same prover efficiency for circuits that consist of multiple (different) sub-circuits.

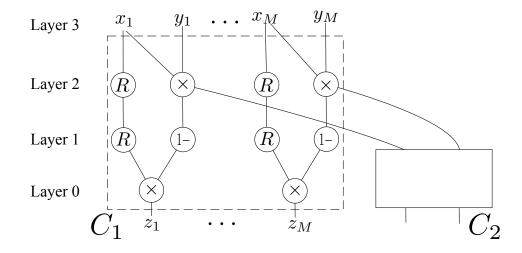

Let C be a depth-d, size-n, layered arithmetic circuit consisting of B independent ("parallel") sub-circuits  $C_1, \dots, C_B$ , each of depth at most d' and size at most n', where the outputs of  $C_1, \dots, C_n$  are fed into an aggregation circuit D of depth-d'' and size n''. In this section, we show how to modify the CMT protocol so as to prove statements about the output of C in time which is linear in the size of C. Our modified protocol proceeds as follows. We start by following the standard CMT protocol for the d'' layers of sub-circuit D. Next, for the remaining d - d'' = d' layers, we modify things in a similar way to [78] and [79]. Let  $S_i$  now denote the maximum number of gates in layer i across  $C_1, \dots, C_B$ , and let  $s_i = \lceil \log S_i \rceil$ . We let  $V_i$  again be a function mapping a gate at level i to its value, but we now specify a gate g by a pair  $g_1, g_2$ , where  $g_2 \in [B]$  indicates the sub-circuit in which g lies and  $g_1 \in [S_i]$  is the index of g (at level i) within that subcircuit. The prover and verifier then run a CMT-like protocol, but using the equation  $V_i(g_1, g_2) = \sum_{u_1, v_1 \in \{0,1\}^{s_{i+1}}} (\mathsf{add}_{i+1}(g_1, u_1, v_1, g_2) \cdot (V_{i+1}(u_1, g_2) + V_{i+1}(v_1, g_2)) + V_{i+1}(v_1, g_2) + V_{i+1}(v_1, g$  $\mathsf{mult}_{i+1}(g_1,u_1,v_1,g_2)\cdot (V_{i+1}(u_1,g_2)\cdot V_{i+1}(v_1,g_2))).$

The equation above still recursively defines  $V_i$  in terms of  $V_{i+1}$ , but takes

advantage of the fact that there is no interconnection between the different subcircuits. This has the effect of reducing the number of variables in  $\mathsf{add}_{i+1}$  and  $\mathsf{mult}_{i+1}$  from  $2s_{i+1} + s_i + 3\lceil \log B \rceil$  to  $2s_{i+1} + s_i + \lceil \log B \rceil$ . Next, we define the multilinear extension of  $V_i(g_1, g_2)$ .

$$\begin{split} \tilde{V}_{i}(z_{1}, z_{2}) &= \sum_{u_{1}, v_{1} \in \{0,1\}^{s_{i+1}}, g_{2} \in \{0,1\}^{\log\lceil B \rceil}} f_{i, z_{1}, z_{2}}(u_{1}, v_{1}, g_{2}) \\ &\stackrel{\text{def}}{=} \sum_{u_{1}, v_{1} \in \{0,1\}^{s_{i+1}}, g_{2} \in \{0,1\}^{\lceil \log B \rceil}} \tilde{\beta}_{i}(z_{2}, g_{2}) \cdot \left( \tilde{\operatorname{add}}_{i+1}(z_{1}, u_{1}, v_{1}, g_{2}) \cdot (\tilde{V}_{i+1}(u_{1}, g_{2}) + \tilde{V}_{i+1}(v_{1}, g_{2})) + \tilde{\operatorname{mult}}_{i+1}(z_{1}, u_{1}, v_{1}, g_{2}) \cdot (\tilde{V}_{i+1}(u_{1}, g_{2}) \cdot \tilde{V}_{i+1}(v_{1}, g_{2})) \right). \end{split}$$

The only difference between equation 3.1 and the equation used for dataparallel circuits with same sub-circuits in [78,79] is that  $\tilde{\mathsf{add}}_{i+1}$  and  $\tilde{\mathsf{mult}}_{i+1}$  take an

extra variable  $g_2$ , which denotes that the gates and wiring patterns can be different

in each sub-circuit. We further observe that running the same algorithm for the

sumcheck protocol as in [78,79] on equation 3.1 results in the same complexity on

the prover, which is  $O(BS_i \log S_{i+1})$ . To see this, for the first  $2s_{i+1}$  rounds, there

are at most  $BS_i$  monomials per round, as there are at most  $BS_i$  gates in the i-th

layer of the circuit and the number of non-zero monomials in  $\tilde{\mathsf{add}}_{i+1}$  and  $\tilde{\mathsf{mult}}_{i+1}$ is bounded by the number of gates. By Remark 1, this takes  $O(BS_i)$  arithmetic

operations per round, so the complexity for these rounds is  $O(BS_i \log S_{i+1})$ . For the

remaining rounds, by Remark 1,  $\mathcal{P}$ 's running time is  $O(2^{\lceil \log B \rceil - j})$  in round  $2s_{i+1} + j$   $(j = 1, \ldots, \lceil \log B \rceil)$  and the complexity is O(B). Thus, the complexity is dominated

by the first part, i.e.,  $O(BS_i \log S_{i+1})$ .

In this way, we extend the class of the circuit efficiently supported by the CMT protocol in [78,79] without any overhead on the prover time.<sup>1</sup> We present the following result.

**Theorem 4.** Let  $C : \mathbb{F}^n \to \mathbb{F}$  be a depth-d layered arithmetic circuit consisting of B parallel sub-circuits  $C_1, \ldots, C_B$  connected to an "aggregation" circuit D such that  $|D| = O(|C|/\log |C|)$ , and let  $S = \max_j \{ \text{width}(C_j) \}$ . Executing the CMT protocol from Construction 1 using Equation 3.1 and the above described modifications to the sum-check protocol, yields an interactive proof for C with soundness  $O(d \cdot \text{width}(C)/|\mathbb{F}|)$ . Moreover,  $\mathcal{P}$ 's running time is  $O(|C|\log S)$  and the protocol uses  $O(d\log(\text{width}(C)))$  rounds of interaction. If  $\tilde{\text{add}}_i$  and  $\tilde{\text{mult}}_i$  are computable in time  $O(\operatorname{polylog}(\text{width}(C)))$  for all the layers of C, then the running time of the verifier V is  $O(n+d \cdot \operatorname{polylog}(\text{width}(C)))$ .

# 3.3 The Construction of Our Argument System

Finally, we present our new argument system with circuit-independent preprocessing. Our construction combines the modified CMT protocol from Section 3.2 with the VPD scheme presented in Section 3.1. We refer to the prover and verifier of the CMT protocol as  $(\mathcal{P}_{cmt}, \mathcal{V}_{cmt})$ , respectively, and to the algorithms of the VPD scheme as (KeyGen, Commit, Evaluate, Ver). We construct an argument system  $(\mathcal{G}, \mathcal{P}, \mathcal{V})$  for the satisfiability of arithmetic circuits over finite fields, where the preprocessing done by  $\mathcal{G}$  depends on a bound on the size of the circuit, the size of its  $\overline{\phantom{a}}$  The complexity of the CMT protocol for circuits composed of identical sub-circuits has recently been improved to  $O(BS_i + S_i \log S_i)$  in [82]. input, and the field over which it is defined, but not the circuit itself.

Let  $\mathcal{V}_{cmt}^{1+2}$  be the restriction of the CMT verifier from Construction 1 which performs Steps 1 and 2 of  $\mathcal{V}_{cmt}$  and outputs  $(r_d, a_d)$  without performing Step 3. Construction 3 is a formal description of our argument system.

Construction 3. Let  $\mathbb{F}$  be a prime-order field with  $|\mathbb{F}|$  exponential in  $\lambda$ , and let n, t be input size and circuit size parameters. For simplicity of exposition we assume that n is a power of 2. Consider the algorithms  $\mathcal{G}, \mathcal{P}, \mathcal{V}$  described below.

**Preprocessing phase.**  $\mathcal{G}(1^{\lambda}, n, t)$  runs  $(pp, vp) \leftarrow \text{KeyGen}(1^{\lambda}, n, 1)$ . The proving key pk is set to be pp and the verification key vk is set to be vp.

**Evaluation phase.** Let  $C: \mathbb{F}^{n_x+n_w} \to \mathbb{F}$  be a depth-d layered arithmetic circuit over  $\mathbb{F}$  with at most t gates such that  $n_x+n_w \leq n$ . Moreover, let  $x \in \mathbb{F}^{n_x}$  and  $w \in \mathbb{F}^{n_w}$  be such that C(x;w)=1. Assume that  $n_w/n_x=2^m-1$  for some  $m \in \mathbb{N}$ . Consider the following protocol between  $\mathcal{P}$  and  $\mathcal{V}$ .

- 1.  $\mathcal{P}$  first commits to the multilinear extension  $\widetilde{V}_d$  of the input layer of C(x; w).

That is,  $\mathcal{P}$  runs  $c \leftarrow \mathsf{Commit}(\widetilde{V}_d, \mathsf{pp})$  and sends c to  $\mathcal{V}$ . Upon receiving c,  $\mathcal{V}$  runs  $\mathsf{CheckCom}(c, \mathsf{vp})$ . If the output is reject,  $\mathcal{V}$  rejects.

- 2. V computes the multilinear extension  $\tilde{x}$  of the input x, generates a random point  $r \in (\mathbb{F}^{\log(n_x)} \times 0^{\log(n_w)})$  and sends r to  $\mathcal{P}$ . Upon receiving r,  $\mathcal{P}$  executes  $(a,\pi) \leftarrow \mathsf{Evaluate}(\tilde{V}_d,r,\mathsf{pp})$  and sends  $(a,\pi)$  to  $\mathcal{V}$ . Upon receiving  $(a,\pi)$ ,  $\mathcal{V}$  executes  $\mathsf{Ver}(c,a,r,\pi,\mathsf{vp})$ . In case  $\mathsf{Ver}$  outputs  $\mathsf{0}$  or  $a \neq \tilde{x}(r)$ ,  $\mathcal{V}$  outputs  $\mathsf{0}$ .

- 3. V runs  $V_{cmt}^{1+2}$  and P runs  $P_{cmt}$  to verify C(x; w) = 1. If  $V_{cmt}^{1+2}$  rejects at any point,

$\mathcal{V}$  outputs 0. Otherwise, let  $r_d$ ,  $a_d$  be the final values returned by  $\mathcal{V}_{cmt}^{1+2}$ . At this point,  $\mathcal{V}$  must verify that  $\tilde{V}_d(r_d) = a_d$ .

- 4.  $\mathcal{V}$  sends  $r_d$  to  $\mathcal{P}$ . Upon receiving  $r_d$ ,  $\mathcal{P}$  executes  $\mathsf{Evaluate}(\tilde{V}_d, r_d, \mathsf{pp})$  and obtains  $(a'_d, \pi')$  which he sends to  $\mathcal{V}$ .

- 5.  $\mathcal{V}$  upon receiving  $(a'_d, \pi')$  executes  $Ver(c, a'_d, r_d, \pi', vp)$ . In case Ver outputs 0 or  $a'_d \neq a_d$ ,  $\mathcal{V}$  outputs 0. Otherwise,  $\mathcal{V}$  outputs 1.

We have the following theorem:

**Theorem 5.** If Construction 2 is an extractable VPD scheme, then Construction 3 is an argument system for arithmetic circuits, as defined by Definition 2. The running time of  $\mathcal{P}$  is  $O(|C|\log|C|)$ . When used for a depth-d, layered circuit C consisting of B parallel sub-circuits  $C_1, \ldots, C_B$  (the sub-circuits can be the same or different) whose outputs feed into a circuit D with  $|D| \leq |C|/\log|C|$ , the running time of  $\mathcal{P}$  is  $O(|C| \cdot \log \max_j \{ \operatorname{width}(C_j) \})$  and the protocol has  $O(d \log(\operatorname{width}(C)))$  rounds. If C has input length n and is log-space uniform then the running time of  $\mathcal{V}$  is  $O(n+d \cdot \operatorname{poylog}(|C|))$ . Finally, if d is  $\operatorname{polylog}(|C|)$ , the above construction is a succinct argument.

*Proof.* The completeness requirement immediately follows from the construction of  $(\mathcal{G}, \mathcal{P}, \mathcal{V})$ .

We now argue about the knowledge soundness property. Let Adv be an adversary which outputs a circuit C with  $|C| \le t$  and  $n_x + n_w \le n$ , where  $n_x$   $(n_w)$  is the size of the input (auxiliary input) of C) and an input  $x \in \mathbb{F}^{n_x}$  and is able to

make  $\mathcal{V}$  accept for (C, x). We will construct a corresponding extractor  $\mathcal{E}$  which is able to produce a witness  $w \in \mathbb{F}^{n_w}$  such that C(x; w) = 1, except with negligible probability.

We begin by observing that the prover parameters  $\mathsf{pk}$  of the argument, that are given as input to  $\mathsf{Adv}$ , are equivalent to  $\mathsf{pp}$  output by  $\mathsf{KeyGen}(1^\lambda, n, 1)$ . Therefore, since  $\mathsf{Adv}$  convinces  $\mathcal V$  which runs  $\mathsf{CheckCom}$  as a sub-routine, it holds that in Step 1  $\mathsf{Adv}$  outputs a  $c \stackrel{\mathrm{def}}{=} (c_1, c_2)$  for the input layer of the circuit C such that  $\mathsf{CheckCom}(c, \mathsf{vp})$  accepts.

Next, let Adv' be a simplified version of Adv that runs the same code of but halts right after Step 1, outputting only commitment c. Clearly, whenever CheckCom(c, vp) accepts when interacting with Adv, it will also accept upon receiving the output of Adv' since they produce the same output. Thus, from the extractability property of our VPD scheme, it follows that there exists extractor  $\mathcal{E}'$  that upon the same input as Adv' outputs f' such that c = Commit(f', pp) except with negligible probability. Note that Adv' is PPT as Adv' is PPT, therefore, by extractability,  $\mathcal{E}'$  is also PPT.

Now we are ready to define our main extractor  $\mathcal{E}$  for Adv. Upon input  $(1^{\lambda}, pk)$ ,  $\mathcal{E}$  operates as follows:

1. Run  $\mathcal{E}'(1^{\lambda}, \mathsf{pk})$  and receive polynomial f'. If f' is not a n-variate polynomial of variable-degree 1, abort.

2. Output  $w = (f'(n_x), \dots, f'(n_w - 1)).$

${\mathcal E}$  is PPT as  ${\mathcal E}'$  is PPT, and he performs only polynomially many operations in  ${\mathbb F}.$

It remains to show that in case  $\mathsf{Adv}$  convinces  $\mathcal{V}$ , then it holds that C(x;w)=1 where w is the output of  $\mathcal{E}$ , except with negligible probability. Assume for contradiction that  $\mathsf{Adv}$  convinces  $\mathcal{V}$  and  $C(x;w)\neq 1$  with some non-negligible probability  $\epsilon$ , where w is the output of  $\mathcal{E}$ . We will build an adversary  $\mathcal{B}$  that uses  $\mathsf{Adv}, \mathcal{E}$  in order to break the soundness of the CMT protocol or of our VPD construction, as follows:

- 1.  $\mathcal{B}$  receives as input (pp, vp) generated from  $\mathsf{KeyGen}(1^{\lambda}, n, 1)$  from a challenger for the VPD soundness game. He then runs  $\mathsf{Adv}(1^{\lambda}, \mathsf{pk} = \mathsf{pp})$ .

- Let C, x be the circuit and input chosen by Adv and let d be the depth of C.

Moreover, let c be the commitment output by Adv (claimed to be a commitment to the input layer of C).

- 3.  $\mathcal{B}$  runs  $\mathsf{CheckCom}(c, \mathsf{vp})$  and if it outputs reject he aborts. Else, he runs  $\mathcal{E}(1^\lambda, \mathsf{pk})$  and receives witness w. If  $w \notin \mathbb{F}^{n_w}$ ,  $\mathcal{B}$  aborts. Else, he sets polynomial  $f: \mathbb{F}^n \to \mathbb{F}$  to be the multilinear extension of the array x||w| (i.e. the multilinear extension of the entire input to C).

- 4.  $\mathcal{B}$  chooses  $r \in \mathbb{F}^{\log n_x} \times 0^{\log n_w}$  uniformly at random and forwards it to Adv. Upon receiving  $a, \pi$ , he runs  $\mathsf{Ver}(c, a, r, \pi, \mathsf{vp})$ . If it outputs reject he aborts. Else, if  $a \neq f(r)$ ,  $\mathcal{B}$  outputs  $(f, r, a, \pi)$  as a challenge for VPD and terminates.

- 5.  $\mathcal{B}$  initializes the interaction with  $\mathcal{V}_{cmt}$  for circuit C and input x, w. For all layers of C (from 0 to d)  $\mathcal{B}$  simply forwards the messages of  $\mathcal{V}_{cmt}$  to Adv and vice versa.

- 6. Let  $r_d$  be the random point established by  $\mathcal{V}_{cmt}$  for the d-th layer of C.  $\mathcal{B}$  forwards

$r_d$  to Adv and receives  $a'_d$ ,  $\pi'$ . He then runs  $\text{Ver}(c, a'_d, r_d, \pi', \text{vp})$ . If it outputs reject he aborts. Else, if  $a'_d \neq f(r_d)$ ,  $\mathcal{B}$  outputs  $(f, r_d, a'_d, \pi')$  as a challenge for VPD and terminates.

7.  $\mathcal{B}$  forwards  $a'_d$  to  $\mathcal{V}_{cmt}$  and terminates.

$\mathcal{B}$  is PPT since Adv,  $\mathcal{E}$  are PPT and he performs polynomially many operations in  $\mathbb{F}$ ,  $\mathbb{G}$ ,  $\mathbb{G}_T$ . Let us now argue about  $\mathcal{B}$ 's success probability.

We define the following events:

- $B_{wins}$  is the event that  $\mathcal{B}$  succeeds in breaking the VPD or the CMT soundness.

- $B_{aborts}$  is the event that  $\mathcal{B}$  aborts during his interaction with Adv.

- A is the event that Adv succeeds in convincing  $\mathcal{P}$  to accept and  $C(w, x) \neq 1$ , where w is the output of  $\mathcal{E}$ .

- R is the event that during the interaction of  $\mathcal{B}$  with Adv,  $a \neq f(r)$  or  $a'_d \neq f(r_d)$ .

- $E = A \cap \mathcal{B}^c_{aborts}$ .

For an event Y, let  $Y^c$  denote its complement. In general, by the law of total probability we can write

$$\Pr[B_{wins}] \ge \Pr[B_{wins}|E \cap R] \Pr[E \cap R] + \Pr[B_{wins}|E \cap R^c] \Pr[E \cap R^c].$$

Next, we turn our attention to evaluating the two summands.

For  $\Pr[B_{wins}|E \cap R]$  we argue as follows. Conditioning on  $E \cap R$  implies that: (i) Adv successfully convinces V, (ii)  $C(w,x) \neq 1$ , (iii)  $\mathcal{B}$  does not abort, and (iv)  $a \neq f(r)$  or  $a'_d \neq f(r_d)$ . Then, the view provided to Adv by  $\mathcal{B}$  is a perfect emulation of the interaction with  $\mathcal{V}$  and the view provided by  $\mathcal{B}$  to  $\mathcal{V}_{cmt}$  is a perfect emulation of the execution of CMT for C(x,w), up to the point where  $\mathcal{B}$  finds out that  $a \neq f(r)$  (during Step (4) above), or that  $a'_d \neq f(r_d)$  (during Step (7) above). Without loss of generality, we focus on the case where this occurs for  $a \neq f(r)$  and the exact same reasoning follows for the other case. Simply observe that  $(f, r, a, \pi)$  is indeed a valid challenge tuple for the VPD soundness game, since  $\operatorname{Ver}(c, a, r, \pi, \operatorname{vp})$  accepts and  $\operatorname{Commit}(f, \operatorname{pp}) = c$ , as  $\mathcal{B}$  did not abort. It follows that, under these conditions,  $\mathcal{B}$  always succeeds in winning therefore  $\operatorname{Pr}[B_{wins}|E\cap R] = 1$ .