Copyright and use of this thesis This thesis must be used in accordance with the provisions of the Copyright Act 1968.

Reproduction of material protected by copyright may be an infringement of copyright and copyright owners may be entitled to take legal action against persons who infringe their copyright.

Section 51 (2) of the Copyright Act permits an authorized officer of a university library or archives to provide a copy (by communication or otherwise) of an unpublished thesis kept in the library or archives, to a person who satisfies the authorized officer that he or she requires the thorized officer that he or she requires the reproduction for the purposes of research or study.

The Copyright Act grants the creator of a work a number of moral rights, specifically the right of attribution, the right against false attribution and the right of integrity.

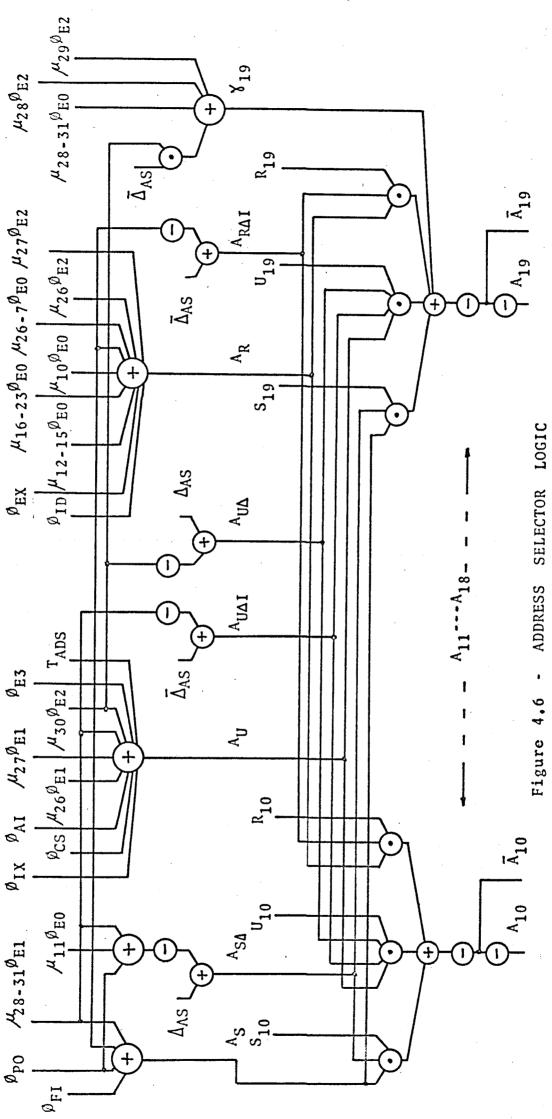

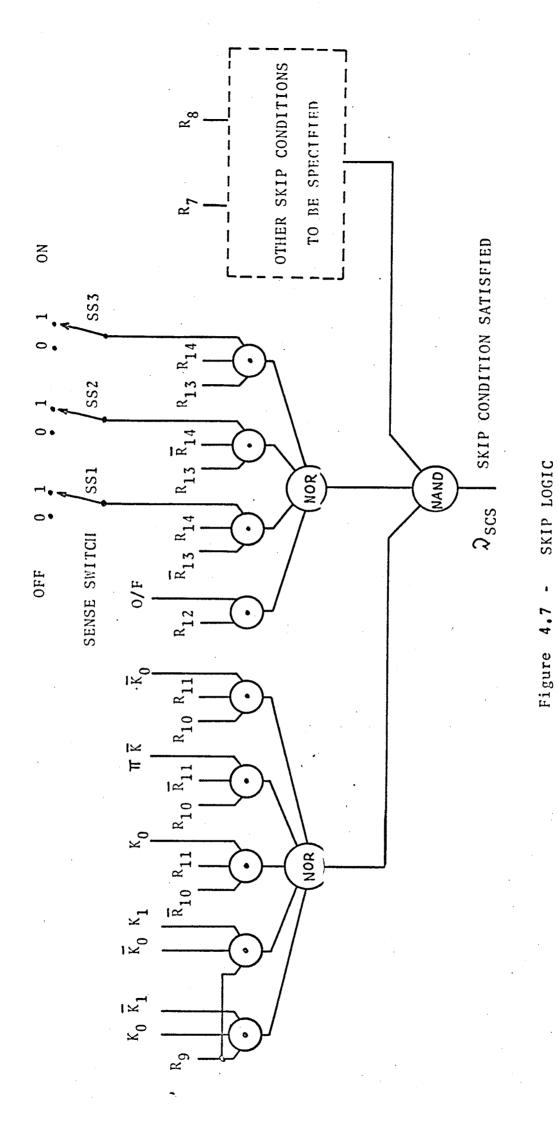

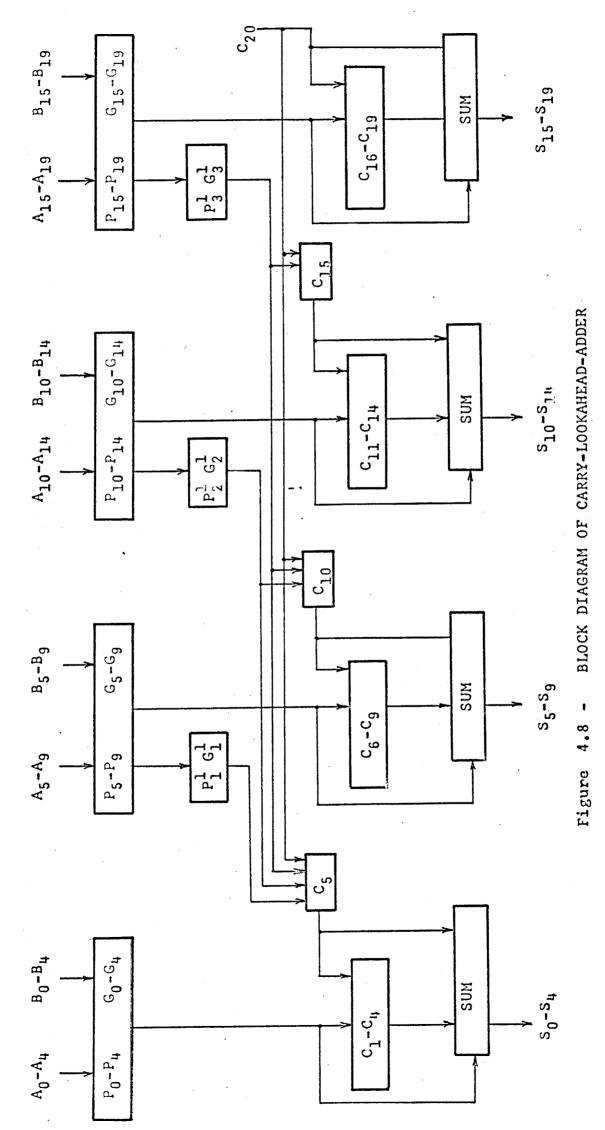

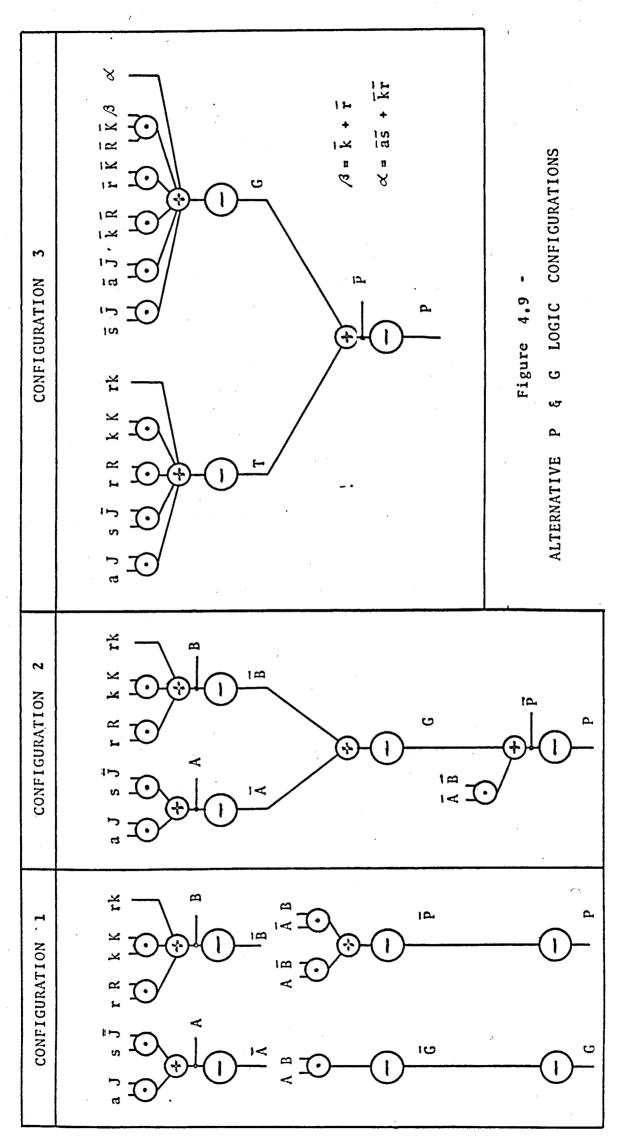

You may infringe the author's moral rights if you:

fail to acknowledge the author of this thesis if you quote sections from the work

- attribute this thesis to another author

-subject this thesis to derogatory treatment which may prejudice the author's reputation

For further information contact the University's Copyright Service. sydney.edu.au/copyright

### THE DESIGN AND CONSTRUCTION OF

### THE DIGITAL COMPUTERS SNOCOM, NIMBUS AND ARCTURUS

#### D.G. WONG

A thesis presented in support of an application for the degree of Doctor of Philosophy in the School of Electrical Engineering of the University of Sydney.

December, 1966.

#### PREFACE

This thesis contains an account of the development of the three digital computers SNOCOM, NIMBUS and ARCTURUS within the School of Electrical Engineering of the University of Sydney.

SNOCOM was the first semiconductor, general-purpose digital computer constructed and installed in Australia. It was built for the Snowy Mountains Hydro Electric Authority and was commissioned in August, 1960.

NIMBUS is the first educational digital computer of its kind to be built in Australia (and possibly in the world). It was commissioned in December, 1961.

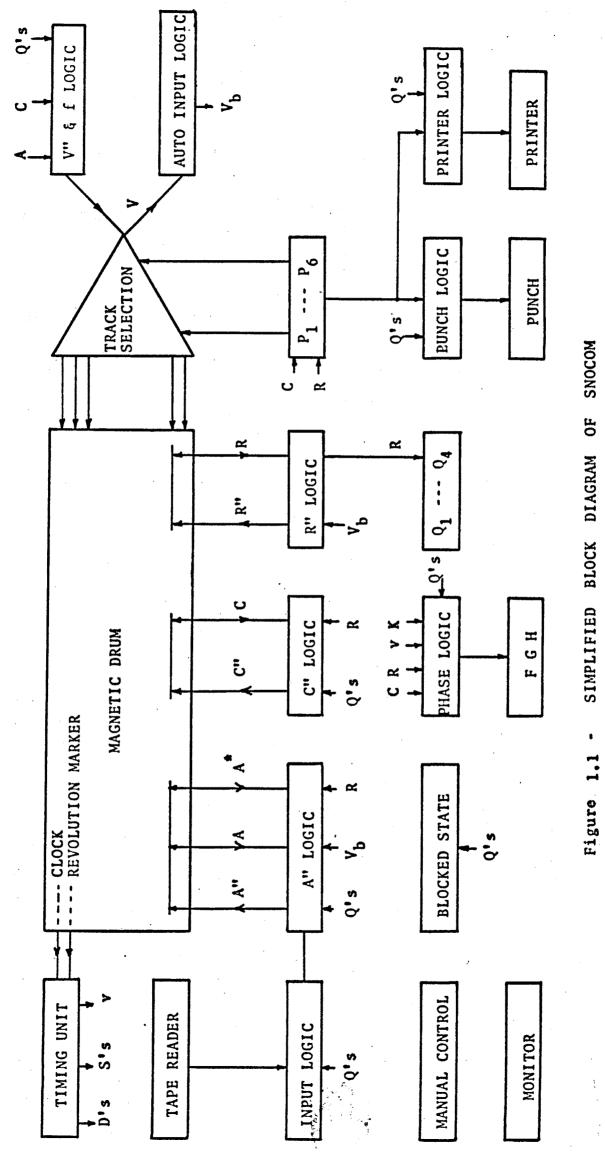

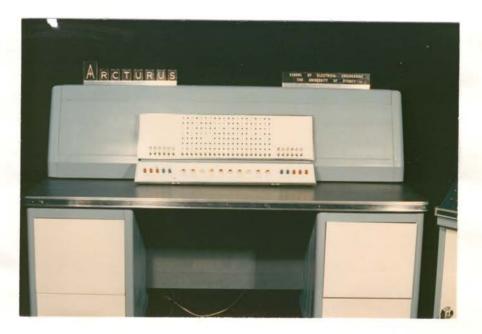

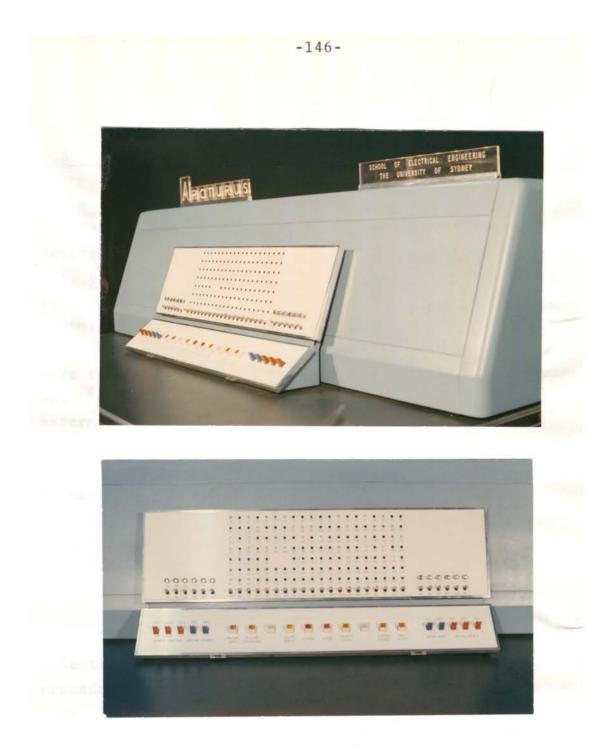

ARCTURUS is a parallel, general-purpose digital computer which utilises advanced techniques of design and construction, and which contains some novel and original features. Its internal processing speed is greater than that of other computers constructed in Australia. It was commissioned in May, 1966, and has been used for both teaching and research purposes.

Chapter 1 of this thesis deals with SNOCOM. A brief description of this computer is presented, and then the design of the "Auto-input" (an original feature due to the Author) is described in detail. Conclusions drawn from the SNOCOM project terminate the chapter.

Chapter 2 deals with NIMBUS, and contains a brief description, a summary of the design of a very simple computer and conclusions drawn from the NIMBUS project.

Chapters 3-7 deal with the various stages of the ARCTURUS project, viz :- system design (Chapter 3), functional and logical design (Chapter 4), circuit design (Chapter 5), constructional techniques and commissioning (Chapter 6) and programming (Chapter 7). Although many logical design considerations are not even mentioned, Chapter 4 is, by far, the longest chapter. The approach taken with this chapter was to describe designs for selected sections of the computer so that a reasonably accurate representation of the design techniques used in ARCTURUS is produced.

. (

Chapter 8 contains a review of computer developments and an appraisal of the SNOCOM, NIMBUS and ARCTURUS projects.

The ARCTURUS project was carried out with extremely limited man-power and financial support. By salvaging semiconductors and connectors from old equipment, and by constructing several peripheral units in the laboratory, this computer was produced with a component cost of less than \$A 10,000. This sum was obtained over a period of about five years.

#### -ii-

The Author's publications relating to the work described in this thesis are as follows :-

- (i) "The Logical Design of the General Purpose Digital Computer SNOCOM", Conference Papers, Annual Engineering Conference, The Institution of Engineers, Australia, Cooma, 1962, and Jour. I. E. Aust., June, 1962, pp125-136.

- (ii) "An Educational Digital Computer", Conference Papers, Australian Computer Conference, Melbourne, 1963

- (iii) "Laboratory Equipment for Teaching Digital Computer Fundamentals", Proc. I.R.E.E.Aust., Feb., 1965, Special Issue on Education, pp77-83.

- (iv) "The Design and Construction of the Digital Computer ARCTURUS", Proceedings of the Third Australian Computer Conference, Canberra, May, 1966.

Reformatted versions of Papers (i), (iii) and (iv) appear in the Appendix. Paper (ii) is not included as it is similar to Paper (iii).

Papers (i), (ii) and (iv) were read at Computer/ Engineering Conferences. The Author received the 1963 Award of the J. R. Bainton Prize from the Institution of Engineers, Australia for Paper (i).

The Author was in charge of the final stages of the development of SNOCOM and of all stages of the development of NIMBUS and ARCTURUS. Mr. K. R. Rosolen (the Author's Design Assistant) played a major role in all three projects, and was mainly responsible for circuit design and constructional techniques. System design, functional design, logical design and programming were the main responsibilities of the Author.

The merit of the work described in this thesis lies in (i) the novel and original features incorporated in the three computers SNOCOM, NIMBUS and ARCTURUS, (ii) the fact that, under the Author's direction, a small but effective research group capable of establishing advanced concepts and techniques has been formed and (iii) the fact that the SNOCOM, NIMBUS and ARCTURUS projects represent a significant contribution to the development of computers in Australia.

ARCTURUS

#### ACKNOWLEDGEMENTS

The construction of SNOCOM was made possible by the generous support given by the Snowy Mountains Hydro Electric Authority to computer development within the School of Electrical Engineering of the University of Sydney.

Dr. M.W. Allen, formerly of the Mathematical Instruments Section of the Commonwealth Scientific and Industrial Research Organization (now Professor of Electronic Computation at the University of New South Wales), was responsible for the circuit design and constructional techniques utilized in SNOCOM. The initial stages of development of SNOCOM were under his direct supervision, and he is to be given much of the credit for its success.

The assistance given by Messrs. W.S. Lamond, L.G. Bellamy, J.E. Todd, R.B. White, K.R. Rosolen, P.T. Brown and D. Linsten during various stages of the SNOCOM project is also gratefully acknowledged.

The author is particularly indebted to Mr. K.R. Rosolen who capably assisted in all stages of the NIMEUS and ARCTURUS projects. Mr. Rosolen is to be given much of the credit for the circuit design and constructional techniques used in these projects. He was directly responsible for the construction of the tape reader, the modifications to the printer, the wiring of a large number of packages, all the base wiring of ARCTURUS and all the mechanical construction.

The author would like to thank Mr. I.M. Cowell for wiring some of the packages for ARCTURUS and for his assistance during the latter stages of the project.

The author would particularly like to thank Professor W.N. Christiansen, Head of the School of Electrical Engineering of the University of Sydney for his encouragement and support of all the projects described in this thesis.

Finally, the author would like to thank his supervisor, Dr. H.K. Messerle,\* for his guidance and sound advice on numerous occasions during the running of the projects and also during the production of this thesis.

\* (now Professor of Electrical Engineering at the University of Sydney)

#### -v-

CONTENTS

.

-1-

# INTRODUCTION

.

.

| CHAPTER | 1 -  | THE DIGITAL COMPUTER SNOCOM             | - 3 - |

|---------|------|-----------------------------------------|-------|

|         |      | List of symbols used in this chapter    |       |

|         |      | Introduction                            |       |

|         | 1.2  | General description                     |       |

|         | 1.3  | Functional & logical design             |       |

|         |      | The auto-input                          |       |

|         | 1.5  | Conclusions                             | •     |

|         |      |                                         | •     |

| CHAPTER | 2 -  | THE EDUCATIONAL DIGITAL COMPUTER NIMBUS | -21-  |

|         | 2.0  | List of symbols used in this chapter    |       |

|         | 2.1  | Introduction                            |       |

|         | .2.2 | Brief description of NIMBUS             |       |

|         | 2.3  | The design of a simple computer         |       |

|         | 2.4  | Conclusions                             |       |

|         |      |                                         |       |

| CHAPTER |      | ARCTURUS - SYSTEM DESIGN                | -31-  |

|         |      | List of symbols                         |       |

|         | •    | Approach to system design               |       |

|         |      | General description of Arcturus         |       |

|         | 3.3  | Implementation of system design         |       |

| CHAPTER | 4 -  | ARCTURUS - FUNCTIONAL & LOGICAL DESIGN  | -47-  |

|         | 4.0  | List of symbols                         |       |

|         | 4.1  | Approach to functional & logical Design |       |

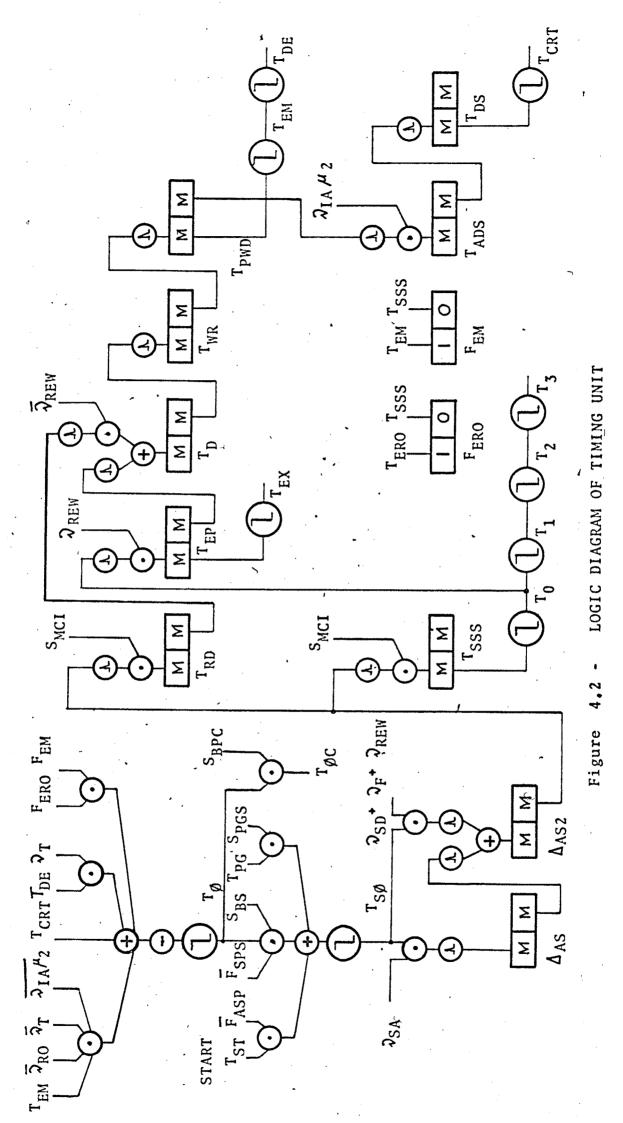

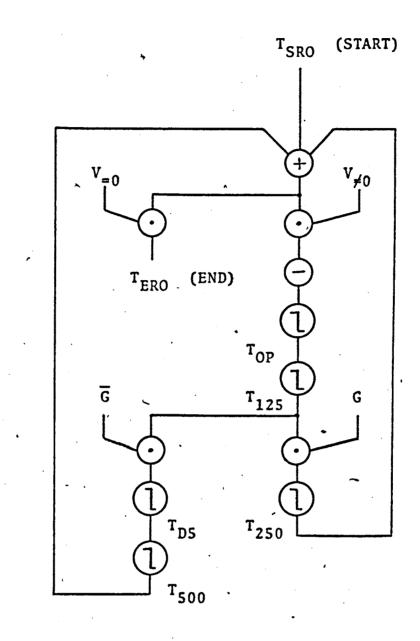

|         | 4.2  | Timing unit                             |       |

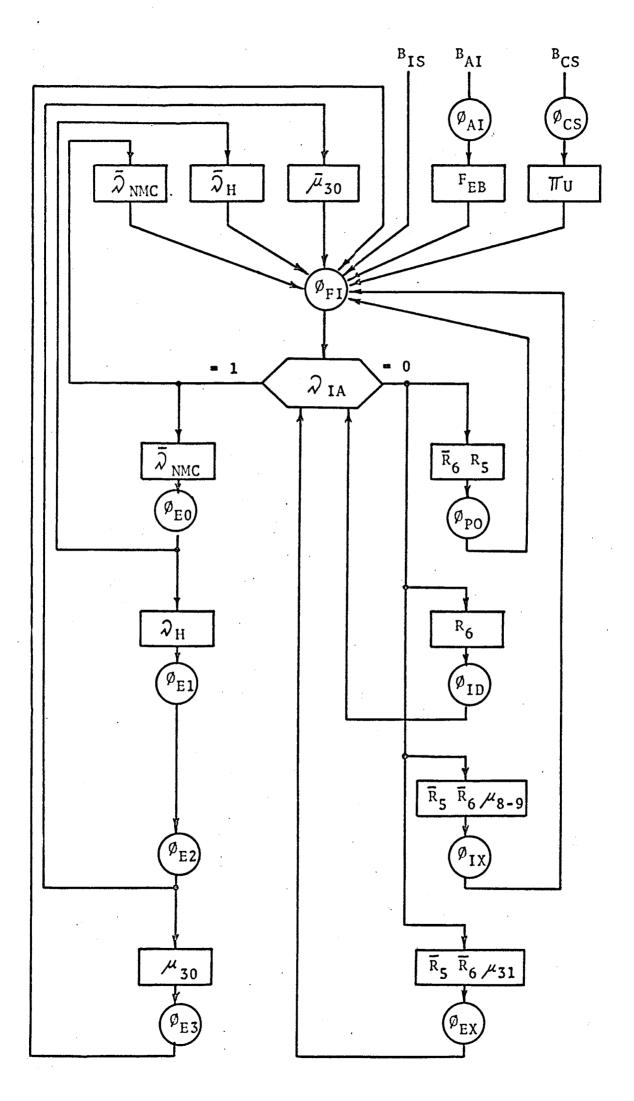

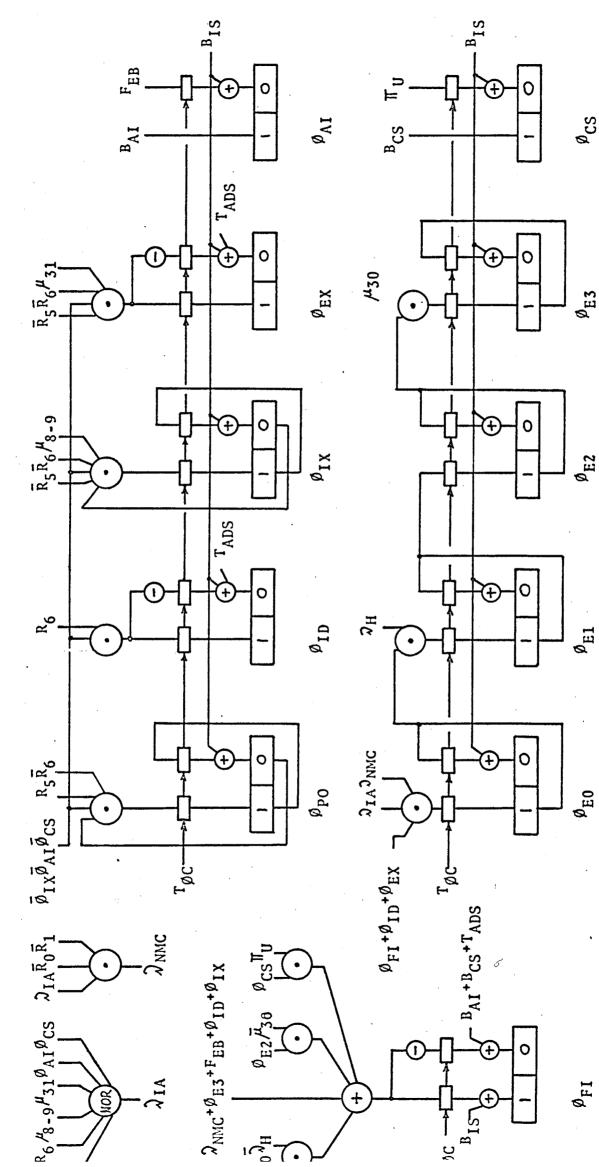

| •       | 4.3  | Machine phases                          |       |

|         | 4.4  | Control                                 |       |

|         | 4.5  | Carry lookahead adder                   |       |

|         | 4.6  | Machine registers                       |       |

|         | 4.7  | Multiplication procedure                |       |

|         | 4.8  | Division procedure                      |       |

|         | 4.9  | Programmed operators                    |       |

|         | 4.10 | Peripheral units                        |       |

|         | 4.11 | Comments on functional & logical design |       |

|         |      |                                         |       |

| CHAPTER |      | ARCTURUS - CIRCUIT DESIGN               | -117- |

|         |      | Design approach                         |       |

|         | 5.1  | Circuit types & characteristics         |       |

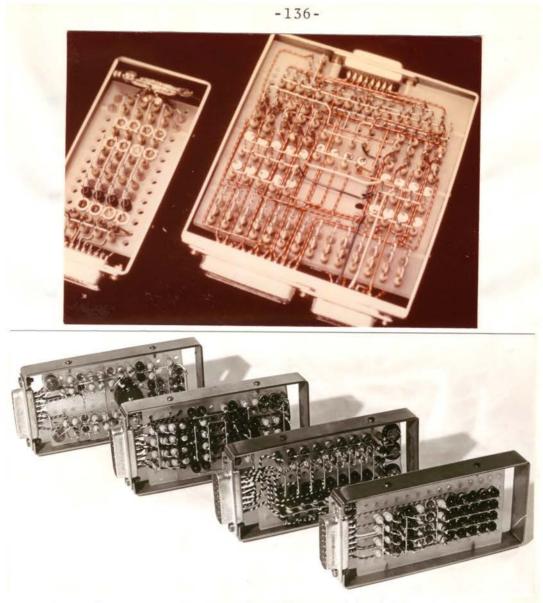

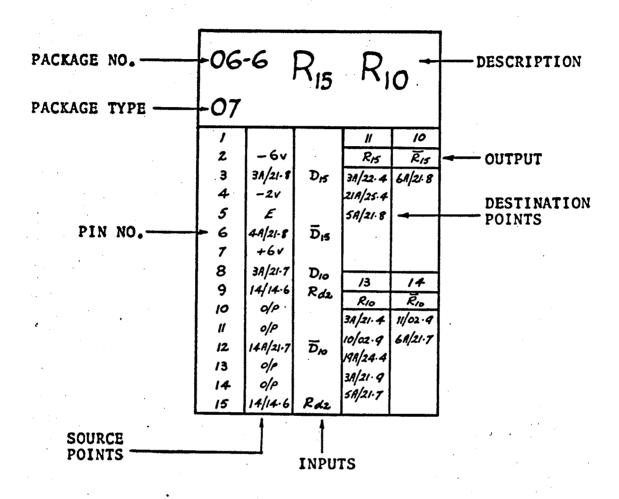

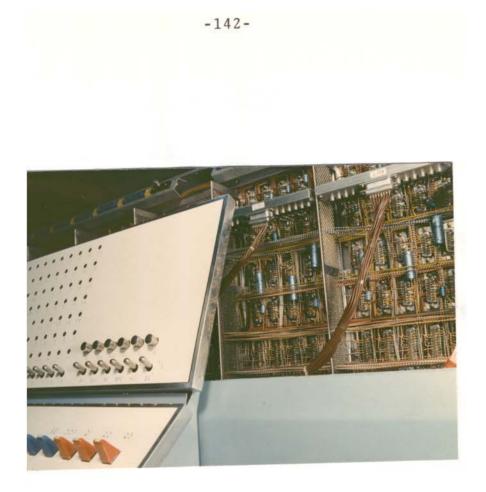

| CHAPTER 6  | -   | ARCTURUS - CONSTRUCTIONAL TECHNIQUES |       |

|------------|-----|--------------------------------------|-------|

|            |     | & COMMISSIONING                      | -134- |

| 6          | •0  | Packaging                            |       |

| 6          | .1  | Base-wiring                          |       |

| 6          | • 2 | Engineering construction             |       |

| 6          | • 3 | Commissioning procedure              |       |

| CHAPTER 7  | -   | ARCTURUS - PROGRAMMING               | -151- |

|            | .0  | The assembly program AP1             | -131- |

|            | -   | Programmed-operators                 |       |

| 7          |     | Subroutine hierarchy                 |       |

| 7.         | .3  | Software development                 |       |

| CHAPTER 8  | -   | REVIEW & APPRAISAL                   | -166- |

| 8.         | .0  | Preface to final chapter             |       |

| 8.         | .1  | Review of computer developments      |       |

| . 8.       | •2  | Appraisal of SNOCOM, NIMBUS          | •     |

|            |     | & ARCTURUS projects                  | •     |

| REFERENCES | s   | · · · · ·                            | -181- |

|            |     |                                      | ,     |

-vii-

-191-

#### INTRODUCTION

The development of the digital differential analyser ADA (Ref. 1) was carried out as a joint project of the School of Electrical Engineering of the University of Sydney and the Mathematical Instruments Section of the Commonwealth Scientific and Industrial Research Organization. As this project was supported by the Snowy Mountains Hydro Electric Authority, one of its aims was to produce a second computer for the Authority.

In 1957 investigations carried out by the author (Ref. 2) led to the conclusion that the Authority's computing requirements could be better met by a general-purpose digital computer than by a digital differential analyser.

After ADA was completed early in 1958, the development of the computer, which was to be known as SNOCOM, was commenced. The availability of Frankel's design of the LGP-30 (Ref. 3) and the realization that essentially the same circuit and constructional techniques developed for ADA could be used with the second machine were the main reasons for basing SNOCOM (Ref. 4) on the logical structure of the LGP-30. SNOCOM was commissioned in August, 1960, and has

given many years of good service.

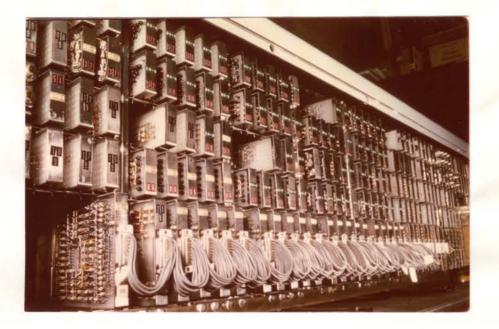

In 1961 the educational digital computer NIMBUS (Refs. 5 and 6) was constructed and since 1962 it has been used very effectively in final-year courses on computer design. NIMBUS consists essentially of a large number of logic and storage elements which may be readily patched together. The number, type and arrangement of these elements have been selected so that it is possible to synthesize a very simple computer.

NIMBUS has also been used to test logic circuit configurations for carrying out high-speed arithmetic and to bread-board equipment for testing computer peripherals.

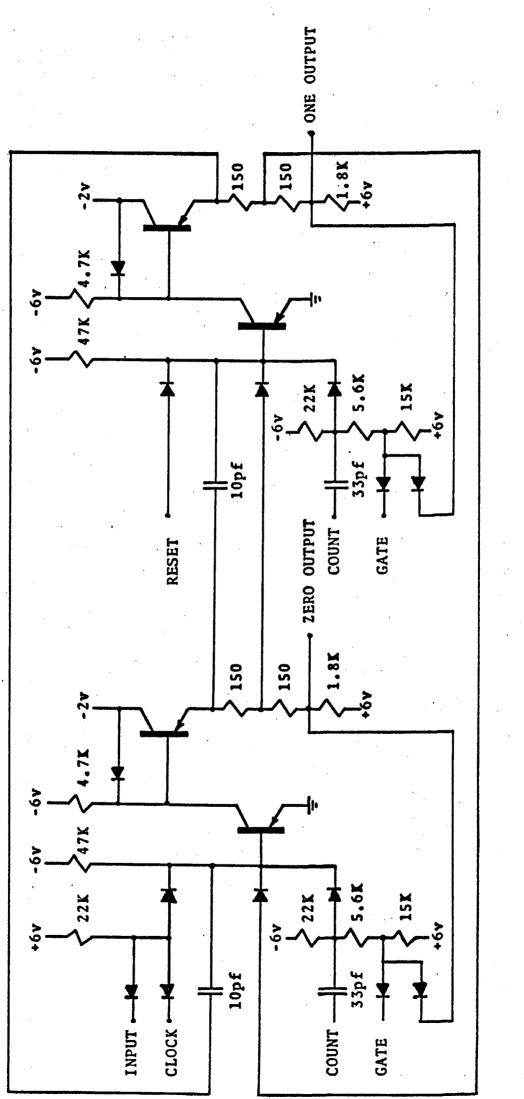

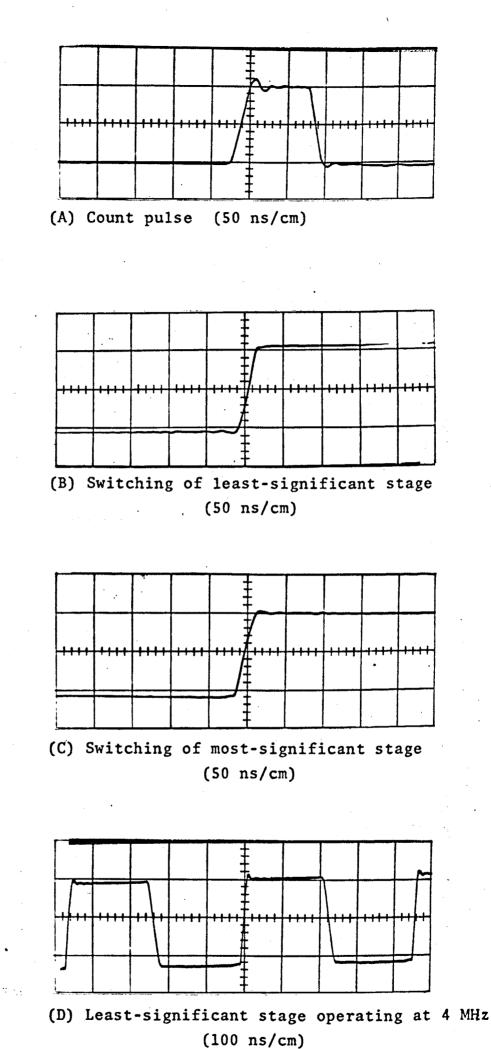

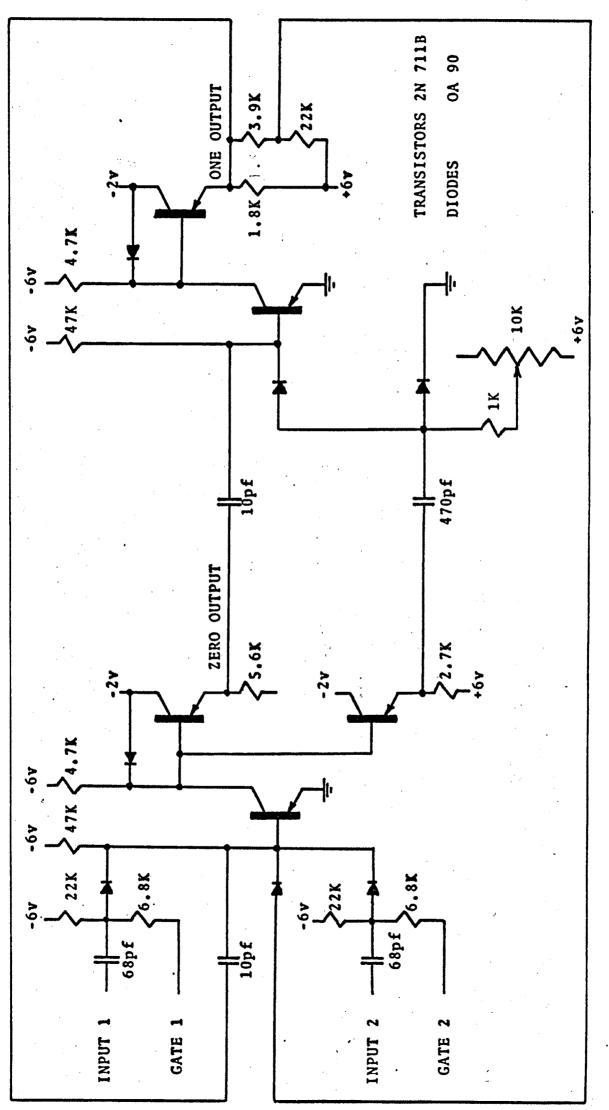

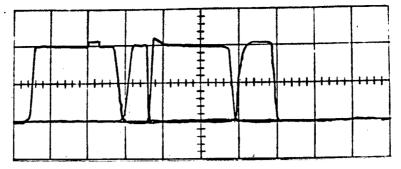

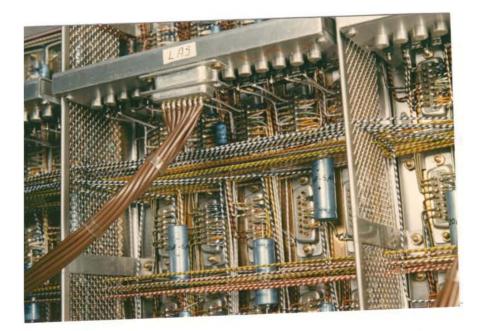

During the years 1961 to 1963 the peripheral units (Ref.21) for ARCTURUS including a paper tape reader of novel design (Ref. 7) were constructed; the circuitry associated with the ferrite-core memory was constructed and a new range of 4 MHz logical elements was developed.

The specification and design of the central processing unit for ARCTURUS were completed by mid-1964. Construction of this unit was carried out in the years 1964 to 1965. Commissioning of the computer commenced in late 1965, and by early 1966 the computer was in good operating order.

-1-

The development of ARCTURUS was carried out with very limited resources. This has meant that much time was spent in developing peripherals rather than purchasing commercial units, in salvaging transistors and diodes from old equipment and in manufacturing in the laboratory almost every logical package of the computer. Items of major expenditure include a Teletype punch, a 32x32x20 ferrite-core stack, about 2000 transistors and about 5000 diodes. The justification for the purchase of these units still had to include the usefulness of the final product for teaching purposes. Hence the specifications of ARCTURUS had to be made so that the computer could be constructed in a reasonable time with the available resources and so that the final product would be useful both for teaching and research.

In spite of the difficult conditions under which the ARCTURUS project was carried out, a reasonably fast computer with some novel and original features has been constructed and is now in good operating order.

Because ARCTURUS is significantly different from all computers previously constructed in Australia, a new approach to design had to be established. This has resulted in a powerful central processing unit which was relatively simple to implement.

No relaxation of the specifications of ARCTURUS was found to be necessary during commissioning. In fact, not only were the design and constructional techniques found to be quite adequate, but also they suggested methods which could be used in faster and more powerful computers.

# CHAPTER 1

- 3 -

## THE DIGITAL COMPUTER SNOCOM

1.0 LIST OF SYMBOLS USED IN THIS CHAPTER

. •

1.0.0 Symbols used in the text

1.0.1 Symbols appearing in the diagrams only

- 1.1 INTRODUCTION

- 1.2 GENERAL DESCRIPTION

- 1.3 FUNCTIONAL AND LOGICAL DESIGN

- 1.4 THE AUTO INPUT

| 1.4.0 | A bootstrap routine              |

|-------|----------------------------------|

| 1.4.1 | The Auto Input                   |

| 1.4.2 | Logical design of the Auto Input |

1.5 CONCLUSIONS

| 1.5.0 | Usefulness of the Auto Input feature   |

|-------|----------------------------------------|

| 1.5.1 | Design approach to minimize hardware   |

| 1.5.2 | Flexibility of a serial arithmetic and |

|       | control unit.                          |

| 1.0.0                                                                                         | Symbols used in the text                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                               |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

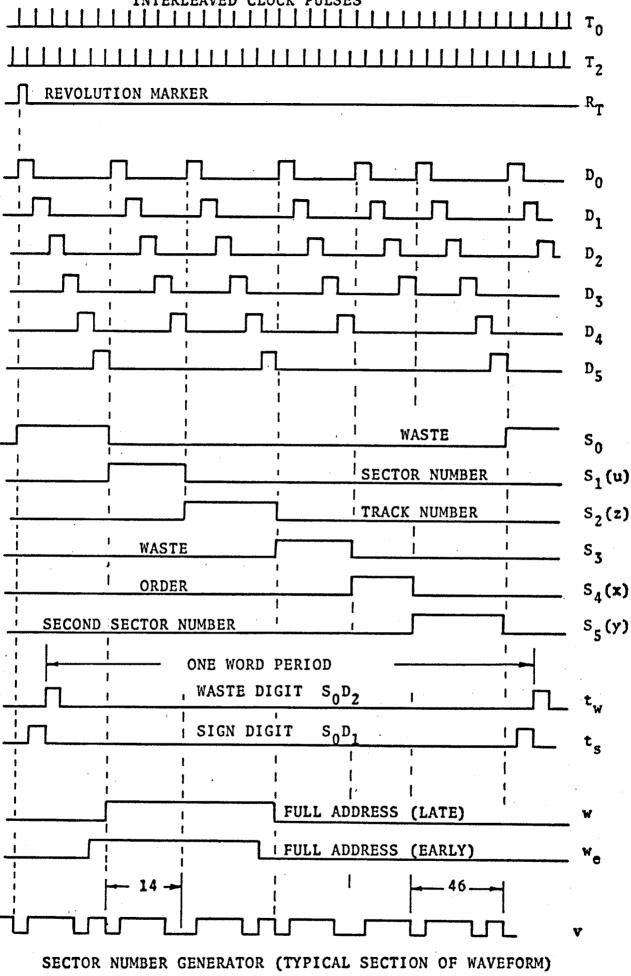

| s <sub>o</sub> - s <sub>5</sub>                                                               | Segment timing waveforms                                                                                                                                                                                                                                                                                                                                                                                            | (Fig. 1.3)                                                                                                    |

| $D_0 - D_5$                                                                                   | Digit timing waveforms                                                                                                                                                                                                                                                                                                                                                                                              | (Fig. 1.3)                                                                                                    |

| -                                                                                             | Interleaved clock pulses                                                                                                                                                                                                                                                                                                                                                                                            | (Fig. 1.3)                                                                                                    |

| R <sub>T</sub>                                                                                | Once-per-revolution marker                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                               |

| v                                                                                             | Store playback flip-flop                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                               |

| V <sub>b</sub>                                                                                | Auto input store playback si                                                                                                                                                                                                                                                                                                                                                                                        | Ignal                                                                                                         |

| c                                                                                             | Sequence counter                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                               |

| 0 - 9 +                                                                                       | - N J F L Sexadecimal cha                                                                                                                                                                                                                                                                                                                                                                                           | aracters                                                                                                      |

| / #                                                                                           | Control characters used in i                                                                                                                                                                                                                                                                                                                                                                                        | Input instruction                                                                                             |

| $w_1 - w_{16}$                                                                                | Binary counter outputs of th                                                                                                                                                                                                                                                                                                                                                                                        | ne sector number generator                                                                                    |

| B                                                                                             | Auto input flip-flop                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                               |

| Bt                                                                                            | Signal which sets B to ONE                                                                                                                                                                                                                                                                                                                                                                                          | E ,                                                                                                           |

| B                                                                                             | Signal which resets B to Z                                                                                                                                                                                                                                                                                                                                                                                          | ZERO                                                                                                          |

| <sup>ф</sup> 1                                                                                | Phase 1                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                               |

| tw                                                                                            | Waste digit                                                                                                                                                                                                                                                                                                                                                                                                         | (Fig. 1.3)                                                                                                    |

| A .                                                                                           | Accumulator playback flip-fl                                                                                                                                                                                                                                                                                                                                                                                        | Lop                                                                                                           |

| 1.0.1                                                                                         | Symbols appearing in the diagr                                                                                                                                                                                                                                                                                                                                                                                      | cams only                                                                                                     |

|                                                                                               | Symbols appearing in the diagr<br>Phase flip-flops                                                                                                                                                                                                                                                                                                                                                                  | rams only                                                                                                     |

| FGH                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                     | · · ·                                                                                                         |

| F G H<br>K                                                                                    | Phase flip-flops                                                                                                                                                                                                                                                                                                                                                                                                    | · · ·                                                                                                         |

| F G H<br>K<br>L                                                                               | Phase flip-flops<br>Sector search, lock-out and                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                               |

| F G H<br>K<br>L                                                                               | Phase flip-flops<br>Sector search, lock-out and<br>Carry-borrow flip-flop                                                                                                                                                                                                                                                                                                                                           |                                                                                                               |

| $F G H$ $K$ $L$ $Q_{1} - Q_{4}$ $P_{1} - P_{6}$                                               | Phase flip-flops<br>Sector search, lock-out and<br>Carry-borrow flip-flop<br>Order flip-flops                                                                                                                                                                                                                                                                                                                       | augmentation flip-flop                                                                                        |

| $F G H$ $K$ $L$ $Q_{1} - Q_{4}$ $P_{1} - P_{6}$                                               | Phase flip-flops<br>Sector search, lock-out and<br>Carry-borrow flip-flop<br>Order flip-flops<br>Track selection flip-flops                                                                                                                                                                                                                                                                                         | augmentation flip-flop                                                                                        |

| F G H<br>K<br>$Q_1 - Q_4$<br>$P_1 - P_6$<br>A''                                               | Phase flip-flops<br>Sector search, lock-out and<br>Carry-borrow flip-flop<br>Order flip-flops<br>Track selection flip-flops<br>Accumular input (i.e. signal                                                                                                                                                                                                                                                         | augmentation flip-flop<br>to accumulator record                                                               |

| $F G H$ $K$ $L$ $Q_{1} - Q_{4}$ $P_{1} - P_{6}$ $A''$                                         | Phase flip-flops<br>Sector search, lock-out and<br>Carry-borrow flip-flop<br>Order flip-flops<br>Track selection flip-flops<br>Accumular input (i.e. signal<br>amplifier)                                                                                                                                                                                                                                           | augmentation flip-flop<br>to accumulator record                                                               |

| $F G H$ $K$ $L$ $Q_{1} - Q_{4}$ $P_{1} - P_{6}$ $A''$ $A$                                     | Phase flip-flops<br>Sector search, lock-out and<br>Carry-borrow flip-flop<br>Order flip-flops<br>Track selection flip-flops<br>Accumular input (i.e. signal<br>amplifier)<br>Accumulator playback flip-fl                                                                                                                                                                                                           | augmentation flip-flop<br>to accumulator record                                                               |

| $F G H$ $K$ $L$ $Q_{1} - Q_{4}$ $P_{1} - P_{6}$ $A''$ $A$ $A$ $C$                             | Phase flip-flops<br>Sector search, lock-out and<br>Carry-borrow flip-flop<br>Order flip-flops<br>Track selection flip-flops<br>Accumular input (i.e. signal<br>amplifier)<br>Accumulator playback flip-fl<br>Double length accumulator pl                                                                                                                                                                           | augmentation flip-flop<br>to accumulator record                                                               |

| $F G H$ $K$ $L$ $Q_{1} - Q_{4}$ $P_{1} - P_{6}$ $A''$ $A$ $A^{*}$ $C$ $R''$                   | Phase flip-flops<br>Sector search, lock-out and<br>Carry-borrow flip-flop<br>Order flip-flops<br>Track selection flip-flops<br>Accumular input (i.e. signal<br>amplifier)<br>Accumulator playback flip-fl<br>Double length accumulator pl<br>Counter playback flip-flop                                                                                                                                             | augmentation flip-flop<br>to accumulator record<br>lop<br>layback flip-flop                                   |

| $F G H$ $K$ $Q_{1} - Q_{4}$ $P_{1} - P_{6}$ $A''$ $A$ $A''$ $R''$ $R$                         | Phase flip-flops<br>Sector search, lock-out and<br>Carry-borrow flip-flop<br>Order flip-flops<br>Track selection flip-flops<br>Accumular input (i.e. signal<br>amplifier)<br>Accumulator playback flip-fl<br>Double length accumulator pl<br>Counter playback flip-flop<br>Instruction register input                                                                                                               | augmentation flip-flop<br>to accumulator record<br>lop<br>layback flip-flop                                   |

| F G H<br>K<br>L<br>$Q_1 - Q_4$<br>$P_1 - P_6$<br>A"<br>A<br>A<br>C<br>R"<br>R<br>V"           | Phase flip-flops<br>Sector search, lock-out and<br>Carry-borrow flip-flop<br>Order flip-flops<br>Track selection flip-flops<br>Accumular input (i.e. signal<br>amplifier)<br>Accumulator playback flip-fl<br>Double length accumulator pl<br>Counter playback flip-flop<br>Instruction register input<br>Instruction register playbac                                                                               | augmentation flip-flop<br>to accumulator record<br>lop<br>layback flip-flop<br>ek flip-flop<br>he main store) |

| F G H<br>K<br>L<br>$Q_1 - Q_4$<br>$P_1 - P_6$<br>A''                                          | Phase flip-flops<br>Sector search, lock-out and<br>Carry-borrow flip-flop<br>Order flip-flops<br>Track selection flip-flops<br>Accumular input (i.e. signal<br>amplifier)<br>Accumulator playback flip-fl<br>Double length accumulator pl<br>Counter playback flip-flop<br>Instruction register input<br>Instruction register playbac<br>Digits to be recorded (in th                                               | augmentation flip-flop<br>to accumulator record<br>lop<br>layback flip-flop<br>ek flip-flop<br>he main store) |

| $F G H$ $K$ $L$ $Q_{1} - Q_{4}$ $P_{1} - P_{6}$ $A''$ $A$ $A$ $C$ $R''$ $R$ $V''$ $f$         | Phase flip-flops<br>Sector search, lock-out and<br>Carry-borrow flip-flop<br>Order flip-flops<br>Track selection flip-flops<br>Accumular input (i.e. signal<br>amplifier)<br>Accumulator playback flip-fl<br>Double length accumulator pl<br>Counter playback flip-flop<br>Instruction register input<br>Instruction register playbac<br>Digits to be recorded (in th<br>Duration of recording (in th               | augmentation flip-flop<br>to accumulator record<br>lop<br>layback flip-flop<br>ek flip-flop<br>he main store) |

| $F G H$ $K$ $L$ $Q_{1} - Q_{4}$ $P_{1} - P_{6}$ $A''$ $A$ $A$ $C$ $R''$ $R$ $V''$ $f$ $t_{s}$ | Phase flip-flops<br>Sector search, lock-out and<br>Carry-borrow flip-flop<br>Order flip-flops<br>Track selection flip-flops<br>Accumular input (i.e. signal<br>amplifier)<br>Accumulator playback flip-fl<br>Double length accumulator pl<br>Counter playback flip-flop<br>Instruction register input<br>Instruction register playbac<br>Digits to be recorded (in th<br>Duration of recording (in th<br>Sign digit | augmentation flip-flop<br>to accumulator record<br>lop<br>layback flip-flop<br>ek flip-flop<br>he main store) |

- 4 -

#### 1.1 INTRODUCTION

In the early 1950's engineers of the Snowy Mountains Hydro-Electric Authority had used the C.S.I.R.O. Mechanical Differential Analyser (Ref. 8) with some success for the solution of flood-routing problems (Ref. 9).

In the mid-1950's the development of the digital differential analyser ADA (Ref. 1) was commenced as a joint project of the School of Electrical Engineering of the University of Sydney and the Mathematical Instruments Section of the Commonwealth Scientific and Industrial Research Organization.

Because the digital differential analyser had been accredited with many of the outstanding advantages of both analogue and digital computers, and because of its previous success with a mechanical differential analyser, the Snowy Mountains Hydro-Electric Authority supported the ADA project with the understanding that a second computer would be built for its own use.

The Authority's computer was to be specifically designed for the solution of a system-operational problem which had previously taken many man-years of manual calculations for its solution. It was shown by the author that a digital differential analyser solution was possible, but about four hundred integrators would have been required and the computation time might have been prohibitively long (Ref.2). The main reason for this was that the problem had not been formulated as a set of ordinary non-linear differential equations, and although the differential analyser approach (e.g. for the generation of analytic functions and for the evaluation of integrals) could be applied to advantage in some sections of the problem, there were some sequences of arithmetic and logical operations on whole numbers which could not be avoided. As the digital differential analyser is an incremental computer, operations on whole numbers are extremely inefficient.

In 1957 a system-operational problem typical of those which the Authority wanted solved was programmed for its solution on SILLIAC, the general-purpose digital computer within the Basser Computing Department of the University of Sydney. The SILLIAC studies carried out by the author led to the conclusion that the Authority's computing requirements could be better met by a general-purpose digital computer than by a digital differential analyser.

- 5 -

After ADA was completed early in 1958, the development of the computer which was to be known as SNOCOM was commenced. The availability of Frankel's design of the LGP-30 (Ref. 3) and the realization that essentially the same circuit and constructional techniques developed for ADA could be used with the second machine were the main reasons for basing SNOCOM (Ref. 4) on the logical structure of the LGP-30.

-6-

SNOCOM was constructed within the School of Electrical Engineering of the University of Sydney, and was then installed in August, 1960 within the offices of the Snowy Mountains Hydro-Electric Authority in Cooma - about 260 miles from Sydney. Since 1960 SNOCOM has given many years of good service.

A paper on SNOCOM (Ref. 4) was presented at the Annual Conference of the Institution of Engineers, Australia in March, 1962 in Cooma. The author received the 1963 Award of the J.R. Bainton Prize for this paper. A reformatted version of this paper is presented in the appendix. A general description of SNOCOM will now be presented. This is followed by an outline of the functional and logical design and by details of the "Auto Input". Conclusions drawn from the SNOCOM project terminate the chapter.

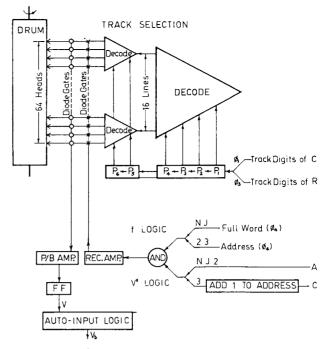

#### 1.2 GENERAL DESCRIPTION

SNOCOM is a fixed-point, binary, serial, storedprogram, single-address, general-purpose digital computer using transistor circuits and magnetic drum storage. The storage capacity of the computer is 2048 words, each of 32 binary digits. These are arranged on 64 tracks of the drum with 32 words per track. The Model 512-A Bryant magnetic drum (5" dia., 12" long) runs at 6,000 R.P.M., giving a clock rate of 102.4 kHz, a word time of 312 microseconds and a mean access time of 5 milliseconds. The accumulator, instruction register and instruction counter are in the form of recirculating registers, with the spacing between record and playback heads corresponding to one word period. The addition of a second playback head on the accumulator recirculating register enables double length numbers to be stored for use in the multiplication and division processes. The computer logic is synchronized by clock pulses derived from a clock track and a once-per-revolution marker permanently recorded on the drum.

An interlaced sector number system enables simple instructions to be obeyed within nine word periods. Another sixty-four word periods are required for the multiplication and division instructions. Hence the addition and multiplication times are 2.8 milliseconds and 22.8 milliseconds, respectively. The bench-mark time (i.e. the time to carry out ten additions and one multiplication) is about 51 milliseconds.

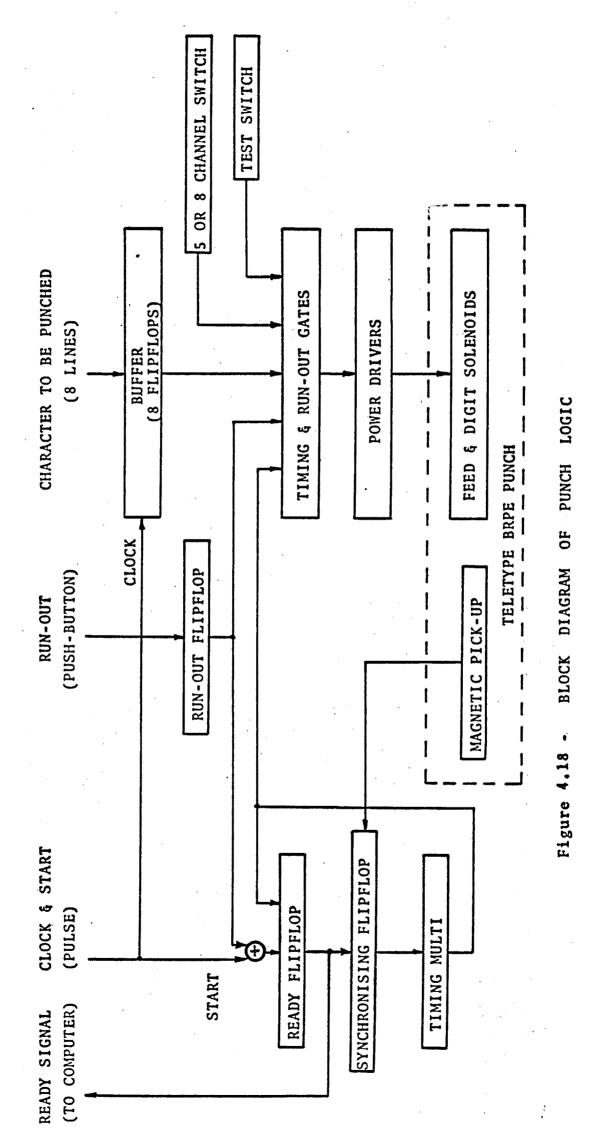

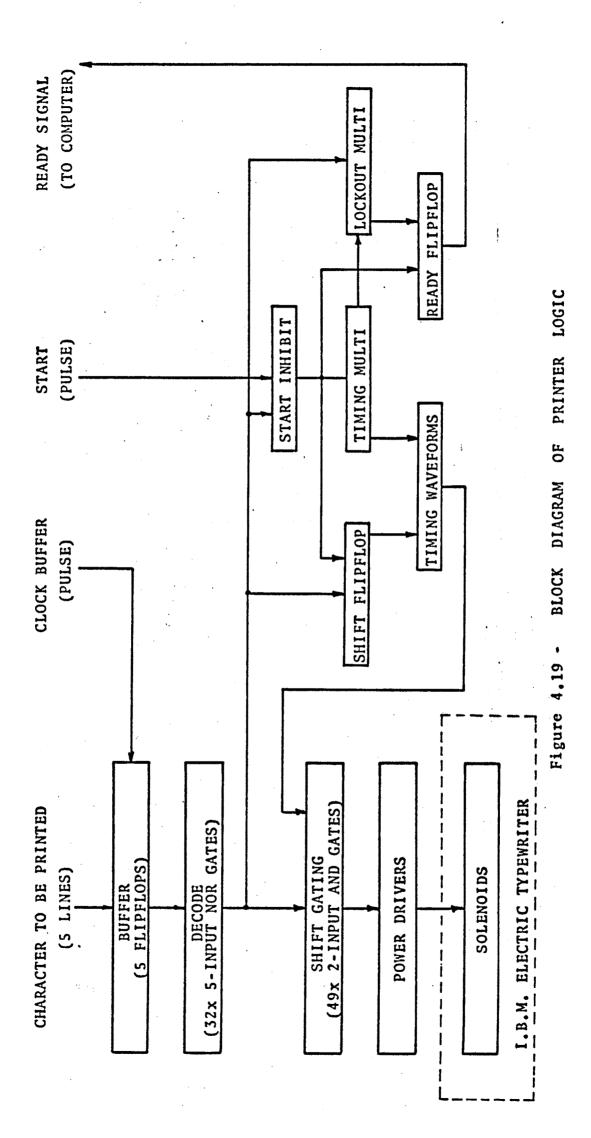

The peripheral units consist of (1) a Ferranti TR 5 paper tape reader which operates at 300 characters per second, (2) a Teletype BRPE paper tape punch which operates at 50 characters per second and (3) a modified IBM electric typewriter which operates at 10 characters per second. Both output units are computer controlled and all units may operate simultaneously.

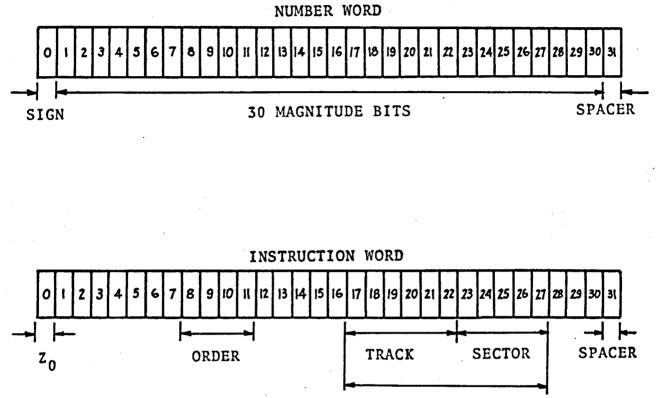

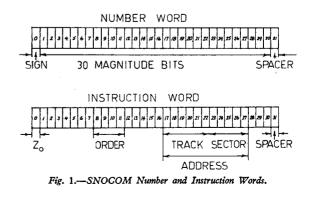

A SNOCOM number word consists of a sign bit, thirty magnitude bits and a spacer bit as shown in Figure 1.0. The binary point is assumed to be between bit 0 and bit 1, and the normal two's complement system for the representation of negative numbers is used.

A SNOCOM instruction word consists of four order bits, six track bits and five sector bits as shown also in Fig. 1.0. The track and sector bits together constitute the full address of the instruction. Apart from the sign bit which is used in conjunction with the conditional transfer of

- 7 -

control order for external program control, the remaining bits have no significance. Corresponding to the different combinations of the four order bits, there are sixteen basic instructions which SNOCOM is capable of executing.

The order code for SNOCOM's sixteen basic instructions is shown in Table 1.0. These instructions are defined in detail in the Appendix.

#### TABLE 1.0

# THE SNOCOM ORDER CODE\*

| CODE        |        |                        |  |

|-------------|--------|------------------------|--|

| Sexadecimal | Binary | ORDER                  |  |

| 1           | 0001   | Bring                  |  |

| F           | 1110   | Add                    |  |

| L           | 1111   | Subtract               |  |

| 7           | 0111   | Multiply fractions     |  |

| 6           | 0110   | Multiply integers      |  |

| 5           | 0101   | Divide                 |  |

| 9           | 1001   | Extract                |  |

| +           | 1010   | Unconditional transfer |  |

| -           | 1011 - | Conditional transfer   |  |

| N           | 1100   | Store                  |  |

| J           | 1101   | Store and clear        |  |

| 2           | 0010   | Store address          |  |

| 3           | 0011   | Return address         |  |

| 4           | 0100   | Input                  |  |

| 8           | 1000   | Output                 |  |

| 0           | 0000   | Stop                   |  |

|             |        |                        |  |

See Appendix J for details.

ADDRESS

#### 1.3 FUNCTIONAL AND LOGICAL DESIGN

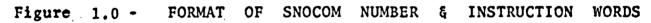

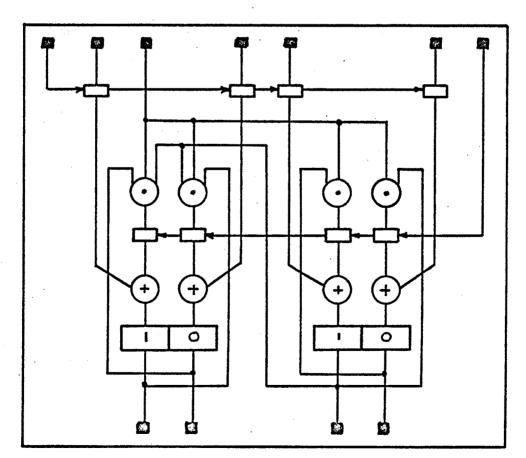

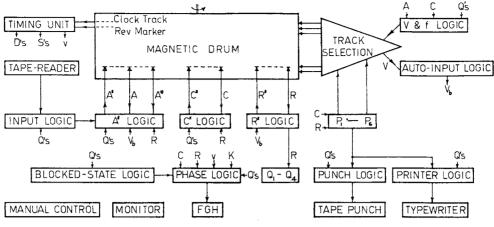

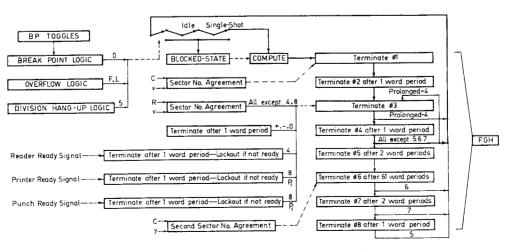

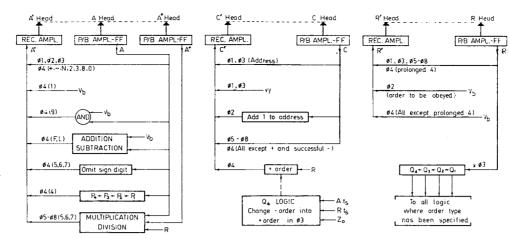

The following brief description refers to the simplified diagram of Fig. 1.1. More details appear in the SNOCOM paper.

The execution of each instruction stored on the magnetic drum takes place in four to eight phases with each phase consisting of one or more word periods. During computation information is held on the drum, in the recirculating registers and in flip-flops. The definition of the operations, which are to be executed in each phase, such as the transfer of information from drum to recirculating register or from recirculating register to flip-flop, constitutes the functional design of the computer.

Logical design consists of deriving Boolean equations from which logic circuits may be readily obtained to implement the functional design.

The logical design of the LGP-30 as described by Frankel (Ref. 3) consists primarily of (1) the specification of the conditions under which each of the main fifteen flipflops is set and reset, (2) the specification of the digits to be recorded in the recirculating registers in each digit period and (3) the specification of the exact location on the magnetic drum in which specified digits are to be recorded.

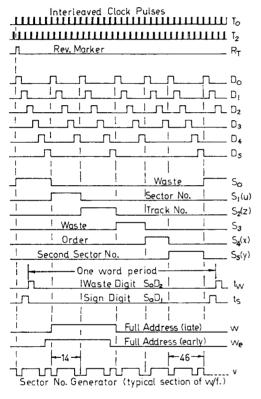

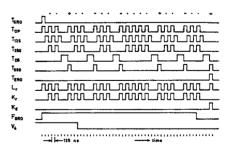

SNOCOM is a synchronous computer as all operations carried out in all possible machine phases are synchronized by timing waveforms generated from clock tracks on the drum. These timing waveforms are shown in Fig. 1.2.

To maintain complete flexibility so that any digit within a word may be specified, a word period has been divided into six segments with each segment containing either four, five or six digits. The segment waveforms  $S_0 - S_5$  and the digit waveforms  $D_0 - D_5$  of Fig.1.2are generated by two ring counters and interconnecting logic. Any digit within a word is specified in terms of these waveforms. For example, the waste digit and the sign digit are the first and last digits in the word and may be specified as  $S_0D_2$  and  $S_0D_1$ , respectively.

The interleaved clocks  $T_0$  and  $T_2$  are used in the two-phase logic arrangement. The once-per-revolution marker synchronizes the segment and digit rings.

In SNOCOM consecutive addresses do not correspond to consecutive locations on a track of the drum, but to locations which are spaced nine word periods apart. In this way an instruction, which refers to an operand which is appropriately

-10-

located between itself and the next instruction, is obeyed in nine word periods rather than the minimum time of thirty-two word periods (corresponding to one drum revolution) which would otherwise be required. To make the above interlaced system possible, a sector number must be formed by subtracting seven from the number of the preceding sector (modulo 32). The resulting sector number sequence is shown in the Appendix (in the SNOCOM paper).

Two three-stage binary counters are used in the generation of the sector number sequence. The first counter corresponds to the three least significant digits of the sector number and is pulsed to count forwards every word period. The second counter corresponds to the two most significant digits of the sector number plus an additional (more significant) digit which effectively counts odd and even drum revolutions. This second counter is pulsed to count backwards on every word period except every eighth when the first counter changes from the state 111 to 000. With the above arrangement one is added to the weight one position of the sector number and one is subtracted from the weight eight position; this results in a sector number being formed which is seven less than the preceding one. The second counter is inhibited from changing when the first has changed from 111 to 000 as this already represents a subtraction of seven.

The binary counters are pulsed early in the word period and their states are gated by the digit waveform  $(D_0 - D_5)$  so that their representation is converted into the serial form required by the machine logic.

In the LGP-30 the sector number pattern is recorded permanently on one track of the drum. This is not the case for SNOCOM, and the parallel representation of the sector which is next to be presented by the store playback amplifier is utilized in the auto input logic.

-12-

INTERLEAVED CLOCK PULSES

Figure 1.2 - SNOCOM TIMING WAVEFORMS

-13-

#### 1.4 THE AUTO INPUT

#### 1.4.0 A bootstrap routine

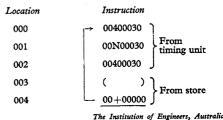

With SNOCOM's order code the minimum number of instructions required for a bootstrap or short input routine is three. In sexadecimal these instructions are as follows:-

| Location | Instruction |                     |

|----------|-------------|---------------------|

| 000      | 00400000    | Input               |

| 001      | 00N00030    | Store in location 3 |

| 002      | 00400000    | Input.              |

The first two words on the input tape must be :-

/00N00040# /00+00000#

where / and # are the control characters detected by the input logic to enable a complete word to be read into the accumulator by the input instruction.

The routine must be started at location 000 by pressing the "clear C" button on the control console. The latter word on the tape is stored in location 004 on the execution of the former (instruction) word which had previously been stored in location 003 by the three orders of the initial bootstrap routine. On the execution of the latter (instruction) word in location 004 control is transferred to location 000 , and the following program on the input tape is then effectively under the control of the following routine :-

| Location | Instruction     |                        |

|----------|-----------------|------------------------|

| 000      | ▶ 00400000      | Input                  |

| 001      | 0000030         | Store in location 3    |

| 002      | 0040000         | Input                  |

| 003      | ( )             |                        |

| 004      | <u>00+00000</u> | Transfer to location 0 |

This routine may be used to fill a program into the store when each word of the program is preceded by a "store" or "store and clear" instruction whose operand address corresponds to the location in which the word is to be stored.

The execution of the bootstrap routine can be terminated if the first order of an order pair is an unconditional transfer of control order.

#### 1.4.1 The Auto Input

After the auto input button has been pressed, the normal store playback (V) from sectors 0, 1 and 2 is inhibited and replaced by a pattern of digits generated from the timing unit. This pattern of digits is equivalent to the following three orders :-

| 00400030 | (fr | rom s | sector      | 0)  |

|----------|-----|-------|-------------|-----|

| 0000030  | (   | 11    | **          | 1)  |

| 00400030 | (   | 17    | <b>11</b> . | 2). |

If the first two words on a program tape are :-

/00N00040# /00+00000#

and the computer is started after pressing the "clear C" button, the word 00+00000 will be stored in 004 and the program will then be effectively under the control of the following bootstrap routine :-

| Location | Instruction                           |

|----------|---------------------------------------|

| 000      | $\rightarrow 00400030$ ] From         |

| 001      | 00N00030 timing unit                  |

| 002      | 00400030 J <u>Clanting direc</u>      |

|          |                                       |

| 003      | ( ) From store                        |

| 004      | L <u>00+00000</u> / <u>110m 01010</u> |

The normal store playback from sectors 0, 1 and 2 (track 0) is not inhibited permanently, conditions being returned to normal immediately a ONE is sensed in the waste digit position of the accumulator in phase 1.

It is to be noted that, because of a simplification of logical design, the normal store playback is inhibited whenever the sector number generator announces a number whose binary equivalent contains a ZERO in the weight 4 position, and this applies not only to track 0 but to all tracks. To eliminate these abnormal conditions as soon as possible, it is recommended that all program tapes should begin with the following eight words :-

| /00N00040# | /00+00000# |

|------------|------------|

| /00N00000# | /00400000# |

| /00N00010# | /00N00030# |

| /00N00020# | /00400001# |

When this is done, the bootstrap routine discussed above will be actually written into the store, and conditions will be returned to normal by the ONE in the waste digit position of the eighth word.

After the program tape has been placed in the tape reader, the normal procedure for entering a program using the auto input is as follows :-

- 1. Press the initial set button.

- 2. Press the clear C button.

- 3. Press the auto input button.

- 4. Press the operate button.

It is to be noted that without the auto input feature many times this number of operations would have been required for entering programs into the computer.

#### 1.4.2 Logical design of the Auto Input

The sector number generator announces the sector number of the next word to be presented to the read-write heads of the main memory. Hence, when sectors 0, 1 and 2 are being played back, the sector number announces 25, 26 and 27, respectively. If the binary counter outputs of the sector number generator are  $w_1$ ,  $w_2$ ,  $w_4$ ,  $w_8$  and  $w_{16}$ , the relevant sectors are represented by the following :-

| Sect | or played back | Sector number announcem                                            | ent  |

|------|----------------|--------------------------------------------------------------------|------|

|      | 0              | $w_1 \ \overline{w}_2 \ \overline{w}_4 \ w_8 \ w_{16}$ (sector     | 25)  |

|      | l              | $\overline{w}_1 w_2 \overline{w}_4 w_8 w_{16}$ ( "                 | 26)  |

| 4    | 2              | $w_1 w_2 \overline{w}_4 w_8 w_{16}$ ( "                            | 27)  |

|      | 3              | $\overline{w}_{1} \ \overline{w}_{2} \ w_{4} \ w_{8} \ w_{16}$ ( " | 28)  |

|      | 4              | $w_1 \overline{w}_2 w_4 w_8 w_{16}$ ( "                            | 29). |

It can readily be seen that  $w_{4}$  alone distinguishes sectors 0, 1 and 2 from sectors 3 and 4.

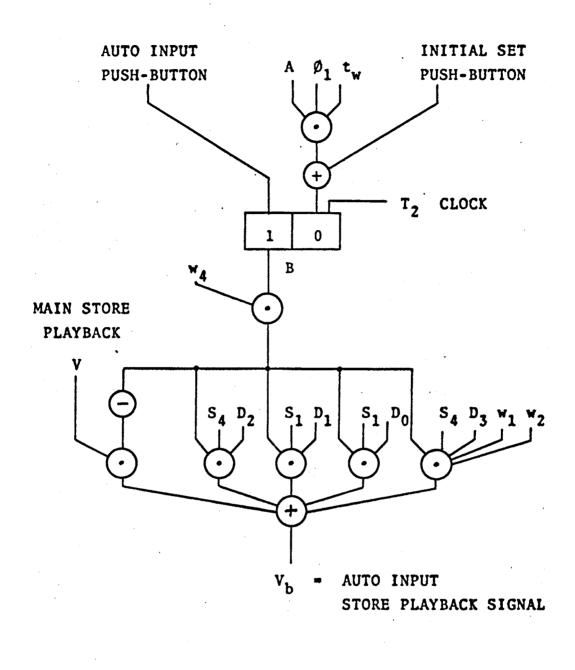

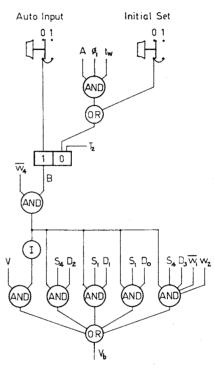

After the auto input button has been pressed, the B flip-flop is set to the ONE state, and while this flip-flop is in this state, the normal V playback from sectors 0, 1 and 2 (and other sectors but not sectors 3 and 4) is inhibited. The conditions to be satisfied while V is inhibited are therefore represented by  $\overline{w}_{\mu} \cdot B = 1$ .

The normal V playback is replaced by a pattern of digits generated from the timing unit. For example, an input order 00400000 is represented by a single digit  $S_4D_2$ , and the order 00N00030 is represented by the 4 digits :-

$S_4D_3 + S_4D_2 + S_1D_1 + S_1D_0$

Using  $w_1$  and  $w_2$  to distinguish between sectors 0, 1 and 2; and  $w_4$  to distinguish sectors 0, 1 and 2 from sectors 3 and 4, the pattern of digits to be generated from the timing unit may be represented by :-

$$S_{4}D_{2}w_{1}\overline{w}_{2}\overline{w}_{4}$$

+ (S\_{4}D\_{3} + S\_{4}D\_{2} + S\_{1}D\_{1} + S\_{1}D\_{0}) \overline{w}\_{1}w\_{2}\overline{w}\_{4}

+ S\_{4}D\_{2}w\_{1}w\_{2}\overline{w}\_{4} .

The digits from sectors 0, 1 and 2 have  $S_4D_2$  in common. Also, as the address portion of an input order has no significance, the digits  $S_1D_1$  and  $S_1D_0$  may be added to the input orders without harm. The pattern therefore may be simplified to :-

$$(S_{4}D_{2} + S_{1}D_{1} + S_{1}D_{0}) \overline{w}_{4} + S_{4}D_{3}\overline{w}_{1}w_{2}\overline{w}_{4}$$

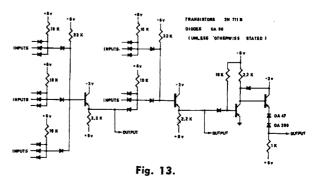

The auto input logic is introduced into the main machine logic by replacing the normal V playback by a new variable  $V_{\rm b}$  which is equal to V under normal conditions, but equal to the digits generated from the timing unit under the conditions of Auto Input (i.e. when  $\overline{w}_{\rm h} \cdot B = 1$ ). Hence

$$\tilde{v}_{b} = v \cdot \overline{\tilde{w}_{4}} \cdot B + \overline{w}_{4} \cdot B(S_{4}D_{2} + S_{1}D_{1} + S_{1}D_{0} + S_{4}D_{3}\overline{w}_{1}w_{2})$$

The B flip-flop is set to ONE when the auto input button is depressed, and is reset to ZERO when a ONE is detected in the waste digit of the accumulator in  $\phi_1$ . It is also reset to ZERO when the initial set button is depressed so that the computer may be used without the Auto Input operation. Hence

> B' = auto input button  $\overline{B}' = \phi_1 t_w A$  + initial set button.

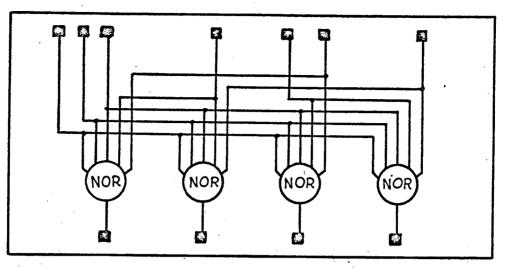

A logic diagram corresponding to the above equations is shown in Fig. 1.3.

Figure 1.3 - SNOCOM 's AUTO INPUT LOGIC

#### 1.5 CONCLUSIONS

#### 1.5.0 Usefulness of the Auto Input feature

Some simple magnetic drum computers (such as the LGP-30) require an undesirably long sequence of console operations to enter programs into the main store. One possible solution to this problem would be to have a bootstrap routine or an assembly routine permanently recorded on one track of the drum. As this track cannot be used for any other purpose, one track of the drum is the price paid for the simpler loading procedure. The most desirable arrangement would be one (like SNOCOM's Auto Input) which requires very little additional hardware and which does not in any way diminish the capabilities of the computer.

Since its installation the Auto Input feature of SNOCOM has been found to be an extremely useful feature and almost all programs are entered this way.

(

#### 1.5.1 Design approach to minimize hardware

The approach taken by Frankel (Ref. 3) in the design of the LGP-30 had as one of its main objectives the minimization of hardware. One design approach which significantly contributed to the attainment of this objective was the allocation, to computing elements (especially flip-flops), of active functions in as many of the machine phases as possible. For example, the K flip-flop is used to search for the correct sector in phases one and three, to increment the sequence counter in phase two and to lock out the computer when peripheral units are not ready. Another example is the use of the  $Q_2$  flip-flop as a means of stopping the computer as well as one of four order flip-flops which determine the type of instruction which is to be obeyed.

Another useful design approach was the appropriate grouping of instructions so that complete decoding of the order flip-flops would not be required as the flip-flop outputs themselves would provide effective control signals.

A close examination of the design of the LGP-30 and SNOCOM would reveal some of the subtleties which enabled the designers to produce remarkably economical designs.

For a commercial computer like the LGP-30 the economies gained by an ingenious design would be extremely desirable because of the saving of cost. For a custom-built computer like SNOCOM (of which only one was built) some of these economies may well prove to be false economies. A case in point is the multiple use of the  $Q_2$  flip-flop. When the computer stops (e.g. on single-shot operation), the Q indicators only reveal that the last instruction obeyed was one of two possible instructions. The additional complexity in interpreting the console indicators would provide a strong case for another flip-flop.

It appears that as computing elements become less expensive, the designer's objective should not be a minimal hardware design but rather an efficient (near minimal) design which considers simplicity of understanding and use as well. Other considerations, of course, include simplicity of construction, commissioning and maintenance procedures.

### 1.5.3 Flexibility of a serial arithmetic and control unit

Starting from the general framework of the LGP-30 design, it has been found relatively simple to introduce a number of desirable features into SNOCOM. These features include (i) the allowable selection of the number of characters entered by an input instruction, (ii) the auto input feature, (iii) the reduction of the operand search phase (phase three) to one word period for some instructions and (iv) the buffering of all peripheral units and the modification of the phase logic to enable simultaneous operation of all peripheral units and the central processing unit.

As SNOCOM is a serial computer, it would be expected that relatively small amounts of hardware would be necessary to introduce new features, as in many cases only a single signal line is affected. It would, for example, be relatively simple to extend the order code of the computer by providing a large number of variants of some of the instructions.

By making use of recent advances in semiconductor devices, it would be possible to construct a central processing unit similar to SNOCOM's which was significantly more powerful and several orders of magnitude faster. However, as SNOCOM is already "memory-limited", there would be little point in doing this without changing the organization of the computer and the form of the memory. These observations would suggest that a good design could be obtained by combining a parallel, ferrite-core store with a serial central processing unit. This approach has, in fact, been taken by designers of some commercial computers (Ref. 10).

-20-

# CHAPTER 2

## THE EDUCATIONAL DIGITAL COMPUTER NIMBUS

- 2.0 LIST OF SYMBOLS USED IN THIS CHAPTER

- 2.1 INTRODUCTION

- 2.2 BRIEF DESCRIPTION OF NIMBUS

•

- 2.3 THE DESIGN OF A SIMPLE COMPUTER

- 2.4 CONCLUSIONS

| 2.4.0 | Usefu                                      | lness o | f machi | nes like  | NIMBUS   | for  | teaching |

|-------|--------------------------------------------|---------|---------|-----------|----------|------|----------|

| 2.4.1 | Usefu                                      | lness o | f machi | nes like  | NIMBUS   | for  | research |

| 2.    | 4.1.0                                      | NOR co  | nfigura | itions    |          |      |          |

| 2.    | 2.4.1.1 High-speed circuit configurations. |         |         |           |          |      | S.       |

| 2.    | 4.1.2                                      | Multi-  | functic | on comput | er eleme | ents |          |

| 2.    | 4.1.3                                      | Testin  | g compu | iter peri | pherals  |      |          |

|       |                                            |         |         |           |          |      |          |

| 2.0 LIST OF SYMBOLS USED IN THIS CHAPTER |                                                             |  |  |  |  |  |  |

|------------------------------------------|-------------------------------------------------------------|--|--|--|--|--|--|

| T                                        | Clock pulse (Figs. 2.0 and 2.1)                             |  |  |  |  |  |  |

| •                                        | Binary counter drive pulse (Figs. 2.0 and 2.1)              |  |  |  |  |  |  |

| -2<br>B <sub>2</sub> - B <sub>2</sub>    | Binary counter outputs (Figs. 2.0 and 2.1)                  |  |  |  |  |  |  |

| $\Delta B_{4}$                           | $B_{\mu}$ waveform differentiated (Figs. 2.0 and 2.1)       |  |  |  |  |  |  |

|                                          | B <sub>16</sub> waveform differentiated (Figs. 2.0 and 2.1) |  |  |  |  |  |  |

|                                          | Initial set (Fig. 2.0)                                      |  |  |  |  |  |  |

|                                          | Signals which stop the timing unit (Fig. 2.0)               |  |  |  |  |  |  |

| $\Phi_{2} - \Phi_{2}$                    | Machine phases 0-3 (Fig. 2.1)                               |  |  |  |  |  |  |

|                                          | Function toggle outputs                                     |  |  |  |  |  |  |

| $C_{2} - C_{2}$                          | Sequence counter outputs                                    |  |  |  |  |  |  |

| 0 3<br>C"                                | Sequence counter input                                      |  |  |  |  |  |  |

| c <sub>d</sub>                           | Sequence counter drive input                                |  |  |  |  |  |  |

| $P_{a} - P_{a}$                          | Address register outputs                                    |  |  |  |  |  |  |

| P" .                                     | Address register input                                      |  |  |  |  |  |  |

| Pd                                       | Address register drive input                                |  |  |  |  |  |  |

|                                          | Fixed store output                                          |  |  |  |  |  |  |

| W <sub>15</sub>                          | Word 15 (= $P_3 P_2 P_1 P_0$ )                              |  |  |  |  |  |  |

| $R_{0} - R_{3}$                          | Instruction register (address) outputs                      |  |  |  |  |  |  |

| R"A                                      | Instruction register (address) input                        |  |  |  |  |  |  |

| RAd                                      | Instruction register (address) drive input                  |  |  |  |  |  |  |

| $R_4 - R_7$                              | Instruction register (order) outputs                        |  |  |  |  |  |  |

| R"o                                      | Instruction register (order) input                          |  |  |  |  |  |  |

| Rod                                      | Instruction register (order) drive input                    |  |  |  |  |  |  |

| $A_0 - A_7$                              | Accumulator outputs                                         |  |  |  |  |  |  |

| A''                                      | Accumulator input                                           |  |  |  |  |  |  |

| Ad                                       | Accumulator drive input                                     |  |  |  |  |  |  |

| s <sub>o</sub> - s <sub>7</sub>          | Store register outputs                                      |  |  |  |  |  |  |

| S                                        | Store register input                                        |  |  |  |  |  |  |

| Sd                                       | Store register drive input                                  |  |  |  |  |  |  |

| K'                                       | Signal which sets the K flip-flop (to 1)                    |  |  |  |  |  |  |

| K'                                       | Signal which resets the K flip-flop (to 0)                  |  |  |  |  |  |  |

| K                                        | Counter augmentation flip-flop output                       |  |  |  |  |  |  |

| L                                        | Carry/borrow flip-flop output                               |  |  |  |  |  |  |

| Ъ<br>                                    | Sum/difference digit                                        |  |  |  |  |  |  |

| V                                        | Store output                                                |  |  |  |  |  |  |

| J                                        | Counter augmentation and carry/borrow flip-flop             |  |  |  |  |  |  |

As a result of the rapidly increasing use of digital equipment both for research and industrial applications, there is great demand for personnel trained in digital systems engineering. Training in this field can be carried out quite effectively with the use of "educational digital computers" (Refs. 5 and 6). These are experimental units which have been specifically designed with the specification of a complete computer in mind. The number, type and arrangement of logical circuits provided in the experimental unit enable the synthesis not only of various combinational and sequential switching circuits, but also of a complete stored-program computer.

The first digital-logic training devices were marketed in 1960, and now a large range is commercially available (Refs. 11 and 12). The function of these devices is of course to provide training in the fundamentals of digital circuits. Educational digital computers must also be able to do this, but they go one step further. The synthesis of a complete digital computer would be extremely useful to teach engineers computer design techniques and to help programmers visualize the internal organization of a computer.

Some of the desirable features of a digital-logic training device or an educational digital computer are as follows:- the equipment should contain standard transistorized digital circuits (or integrated circuits) for good simulation of actual design problems; the circuit modules may be either fixed or removable, but the arrangement must be flexible so that many circuits may be synthesized; logic panels must be clearly engraved and extensive monitoring facilities must be provided to facilitate the understanding and testing of circuit configurations; the main control unit must enable the monitoring of memory states after each state-change (i.e. after each clock pulse); and finally the device must be "student-proof" so that any interconnection may be made without damage to the equipment.

Most of the above features have been incorporated into the educational digital computer NIMBUS. This machine has been used since 1962 by final-year students of electrical engineering of the University of Sydney. A brief description of NIMBUS is presented in section 2.2; an outline of the design of an extremely simple computer is presented in section 2.3; and finally conclusions concerning the usefulness of machines like NIMBUS for teaching and research are presented in section 2.4.

-23-

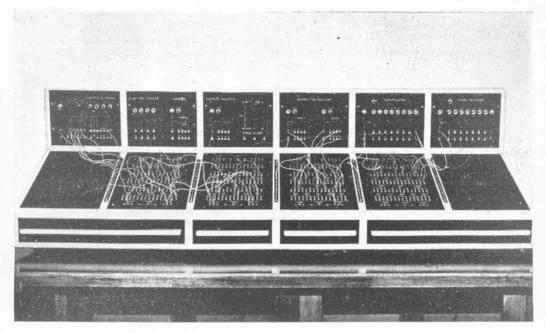

#### 2.2 BRIEF DESCRIPTION OF NIMBUS

A photograph of NIMBUS appears on page iv, and a reproduction of a paper (Ref. 6) containing a description of this machine appears in the Appendix.

In essence, the machine consists of several subassemblies and a large number of logical and storage elements which may be readily patched together. The sub-assemblies provided in NIMBUS enable experiments on serial, synchronous, digital systems to be carried out.

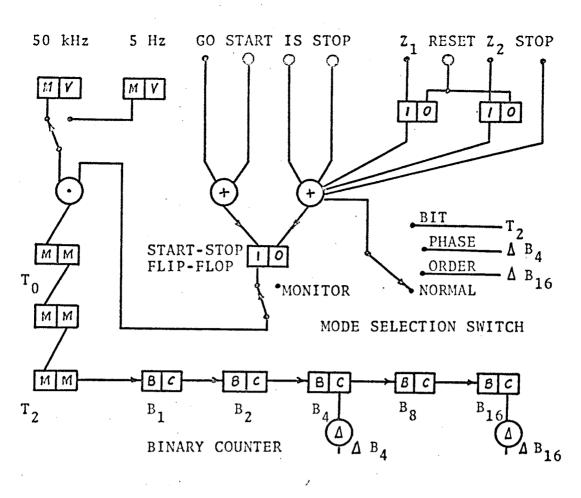

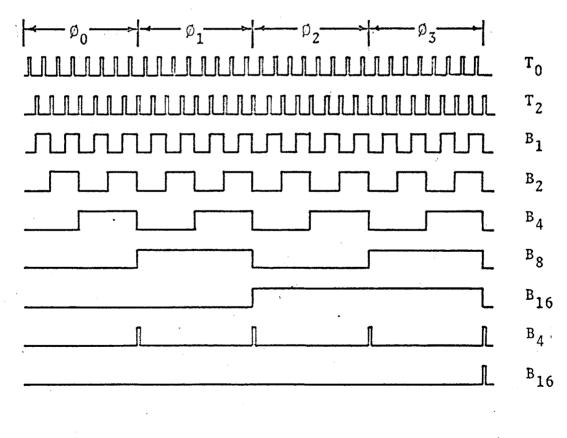

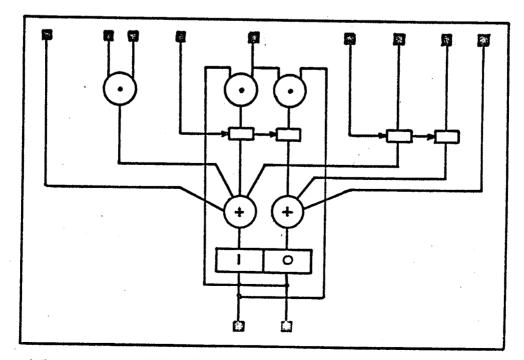

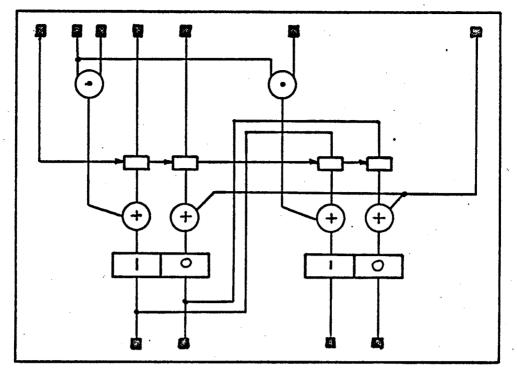

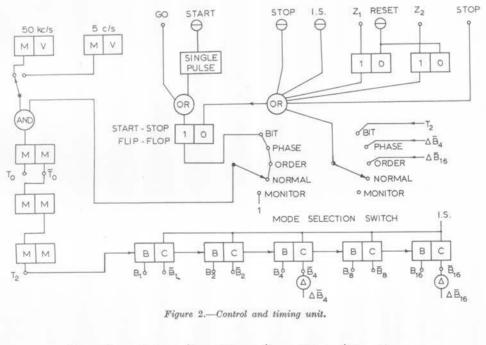

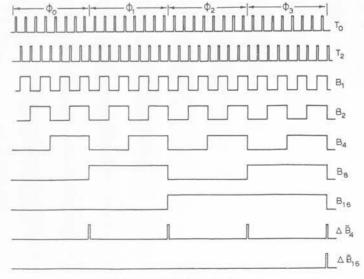

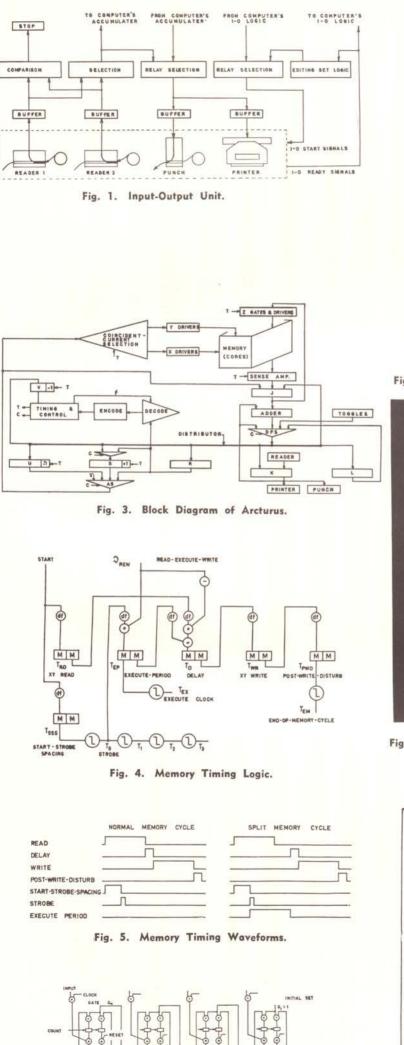

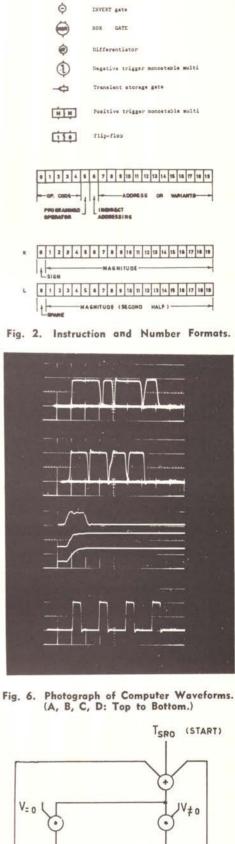

One of the main sub-assemblies is the control and timing unit. A logic diagram of this unit is shown in Figure 2.0, and timing waveforms are shown in Fig. 2.1. When the START button is depressed, the timing unit generates one pulse, eight pulses, thirty-two pulses or a train of pulses depending on whether the MODE-SELECTION switch is in the BIT, PHASE, ORDER or NORMAL positions, respectively. When this switch is in the MONITOR position, the unit runs continuously and all waveforms may be monitored. The ability to change the mode of operation in this way is an extremely useful and almost indispensable feature of a training device.

To demonstrate the principles of operation of a stored-program computer, some storage device must be provided in the educational machine.

In NIMBUS a sixteen word pinboard-store is provided, and this is supplemented by a very limited amount of erasable storage in the form of a one-word flip-flop register. The outputs of the four-stage address register are decoded into sixteen lines which drive the WORD-busses of the pinboard-store. Component plugs containing sub-miniature diodes may be inserted to bridge the WORD-busses with the eight BIT-busses at appropriate places. The pinboard, together with component plugs, forms a diode-matrix which produces (in parallel) the eight bits of the word specified by the contents of the address The diode-matrix outputs are combined with the timing register. waveforms  $B_1$ ,  $B_2$  and  $B_4$  in parallel-to-serial conversion circuits to produce the serial store output  $V_{o}$  . The selection of either the pinboard-store output or the flip-flop register output may be readily carried out using the outputs of the address register as the gating signals.

Other sub-assemblies take the form of self-contained shift registers. The arrangement of these sub-assemblies were chosen with the organization of a simple computer in mind; for example, a four-stage register for the (sequence) counter is provided and the panel for this sub-assembly is accordingly engraved with this function in mind. Other registers are provided for the address register, the instruction register and the accumulator.

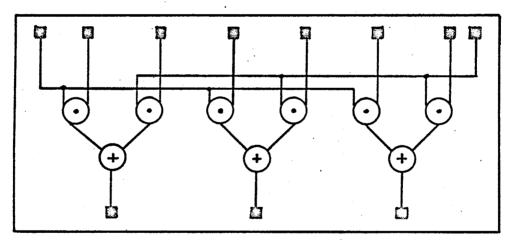

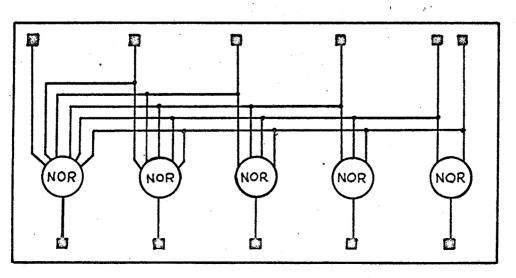

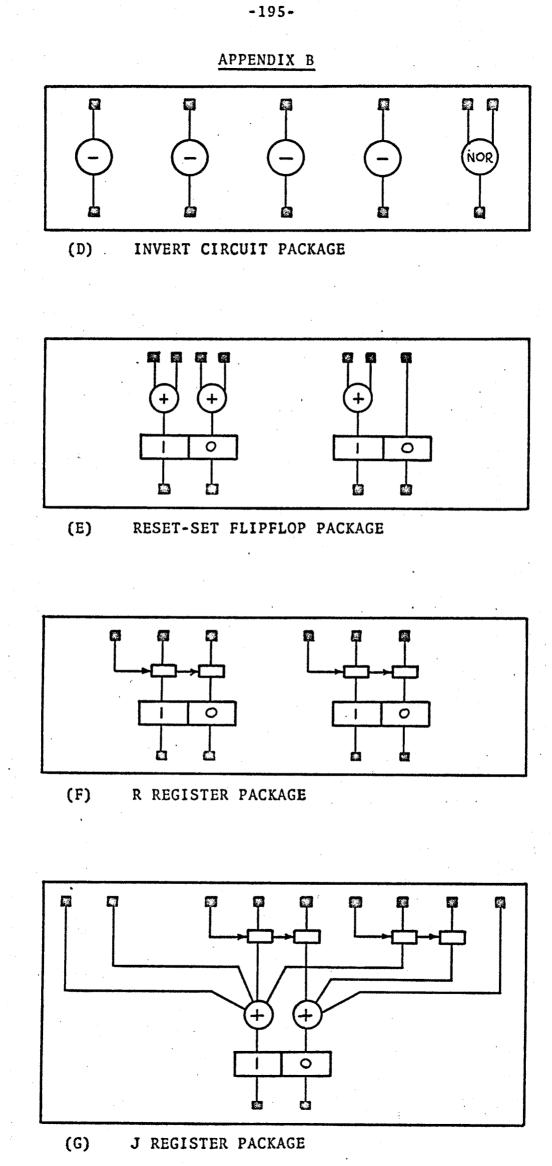

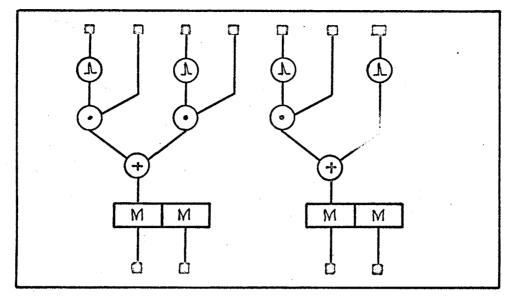

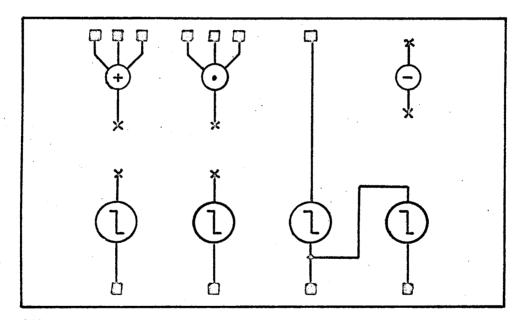

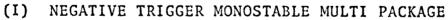

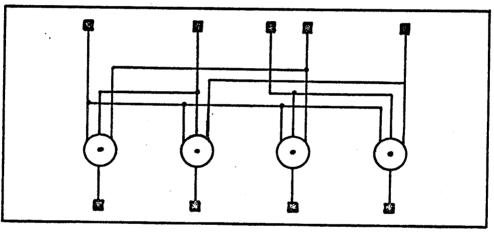

The sloping panels of the machine contain storage and logical elements. Each of the existing panels contains two flip-flops, three invert circuits and nineteen NOR circuits. Other circuits may be used as the panels are self-contained and readily interchangeable.

The inputs and outputs of all elements in the machine are brought to sockets on the panels so they may be interconnected with flexible leads.

Figure 2.0 :- NIMBUS CONTROL & TIMING UNIT

Figure 2.1 :- NIMBUS TIMING WAVEFORMS

-26-

### 2.3 THE DESIGN OF A SIMPLE DIGITAL COMPUTER

The sub-assemblies and logic circuits briefly described in the preceding section may be interconnected to form a simple digital computer. Computers with different order codes may be constructed, the only restriction being the amount of hardware which is necessary for their implementation. An example of a computer which may be constructed is a fixed-point, binary, serial, single-address digital computer with a storage capacity of sixteen eight-bit words of which fifteen are fixed and one is erasable. The computer is capable of carrying out only eleven basic instructions, although four stages in the order part of the instruction register make provision for six-The order code is shown in Table 2.0. A complete desteen. cription of the functional and logical design of this computer appears in the paper which is reproduced in Appendix K .

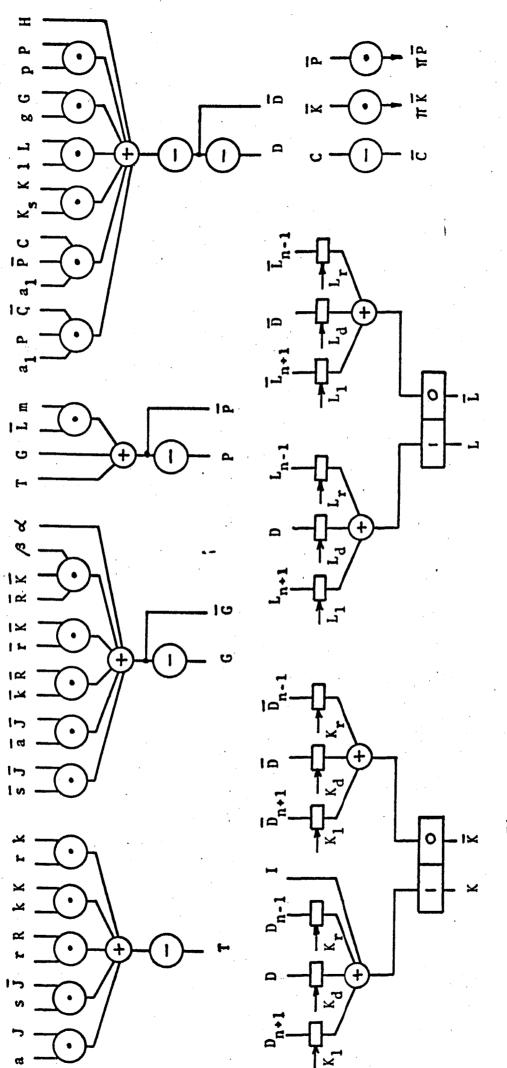

The Boolean equations of Table 2.1 represent a summary of this design. The symbols used in these equations are listed in section 2.0.

#### TABLE 2.0 : ORDER CODE OF A SIMPLE COMPUTER

| Code | Order                                                                                                                                                                           |  |  |  |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0000 | INPUT :Illuminate the Z, monitor light and stop the computer so that eight digits may be set into the accumulator.                                                              |  |  |  |  |

| 0001 | OUTPUT :Illuminate the Z, monitor light and stop the computer so that the accumulator may be monitored.                                                                         |  |  |  |  |

| 0010 | TRANSFER IF NEGATIVE : Transfer control to the address specified by the instruction if the accumulator is negative.                                                             |  |  |  |  |

| 0011 | UNCONDITIONAL TRANSFER : Transfer control to the address specified by the instruction.                                                                                          |  |  |  |  |

| 0100 | STORE :Store the contents of the accumulator into the store register (address 15).                                                                                              |  |  |  |  |

| 0101 | BRING :-Bring the word specified by the address of the instruction into the accumulator.                                                                                        |  |  |  |  |

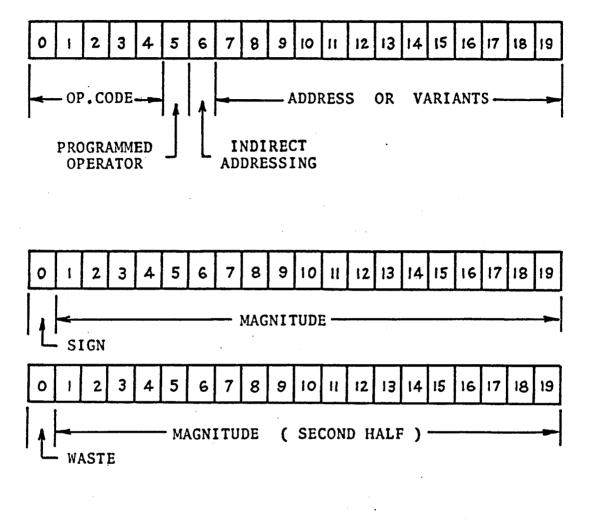

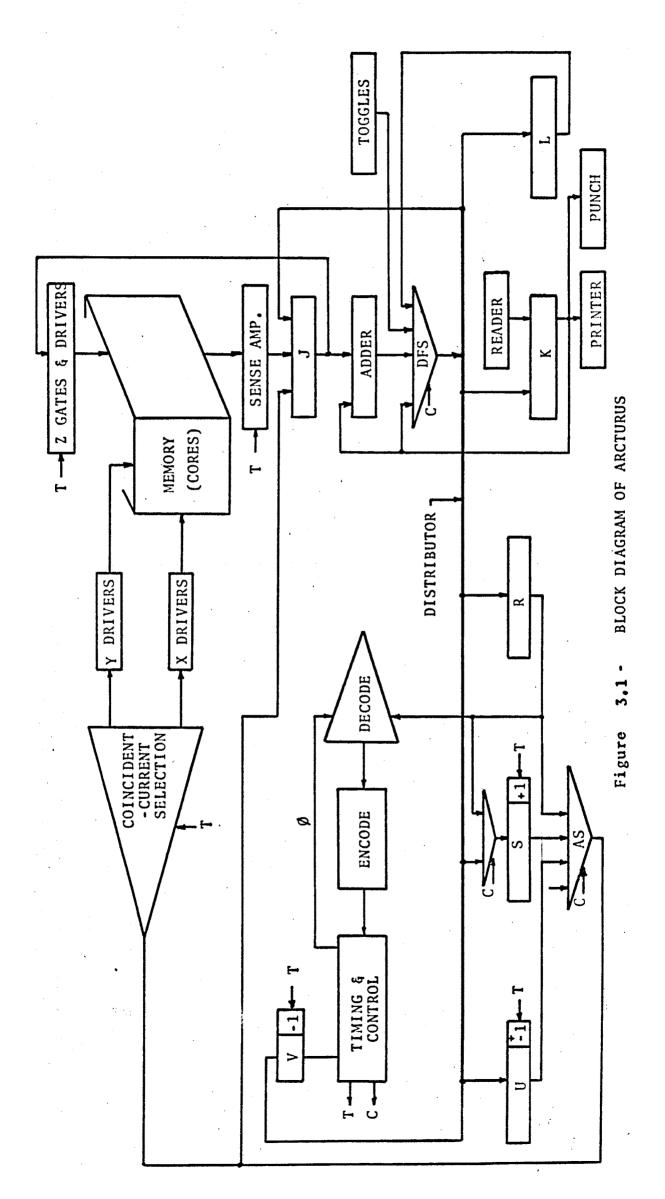

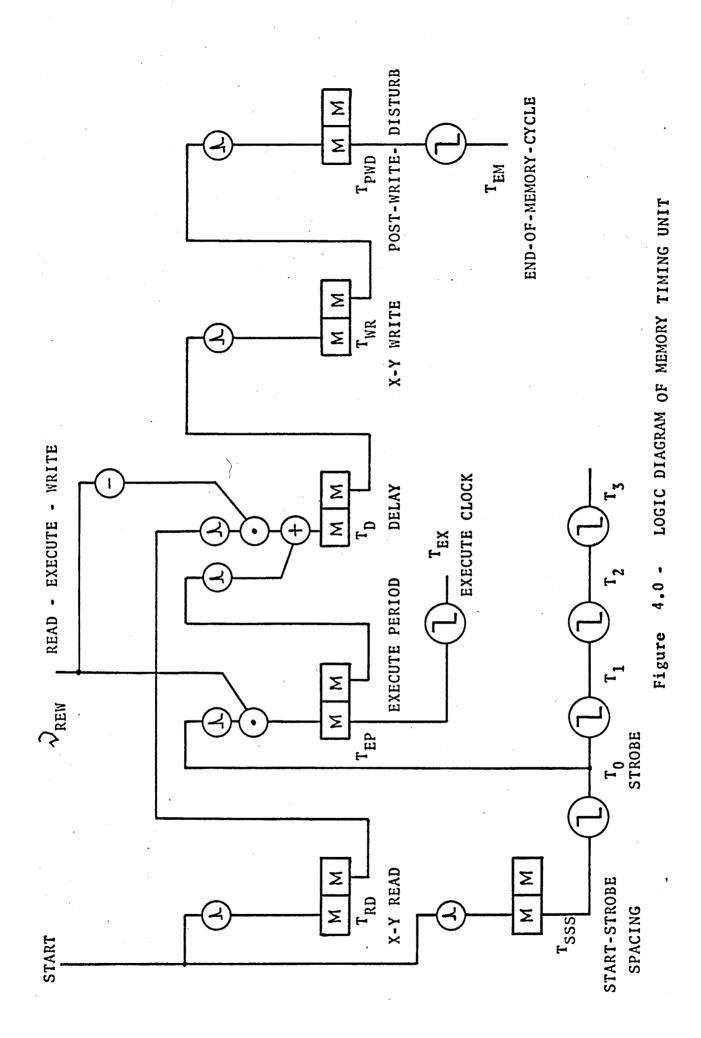

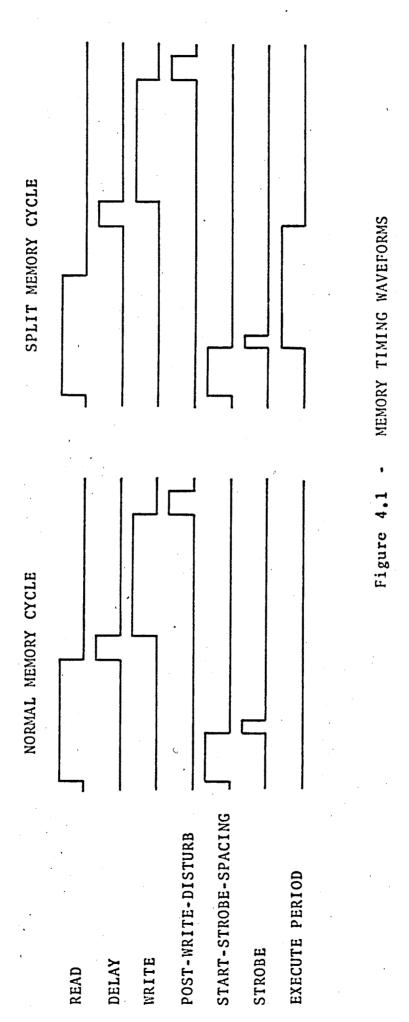

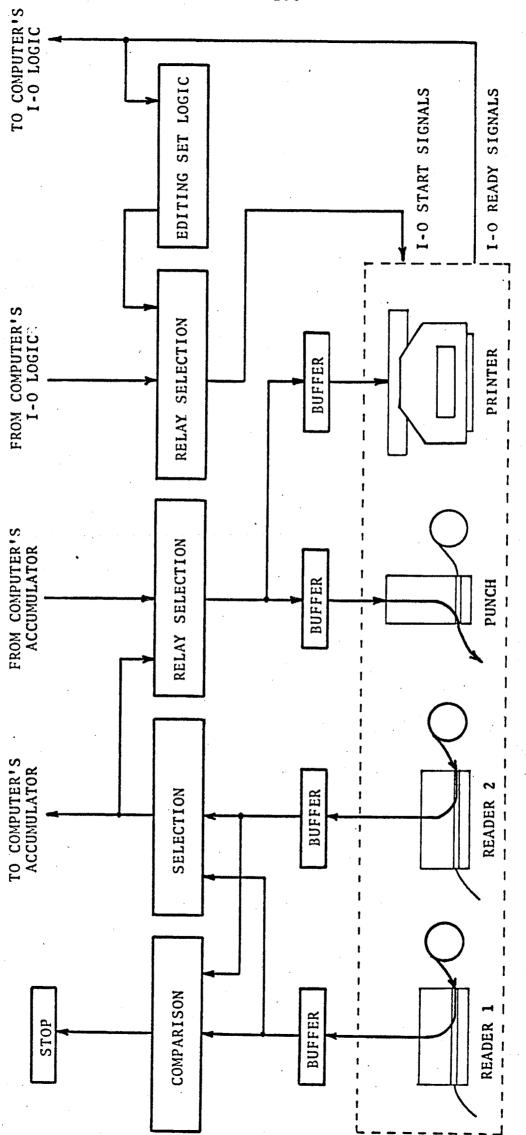

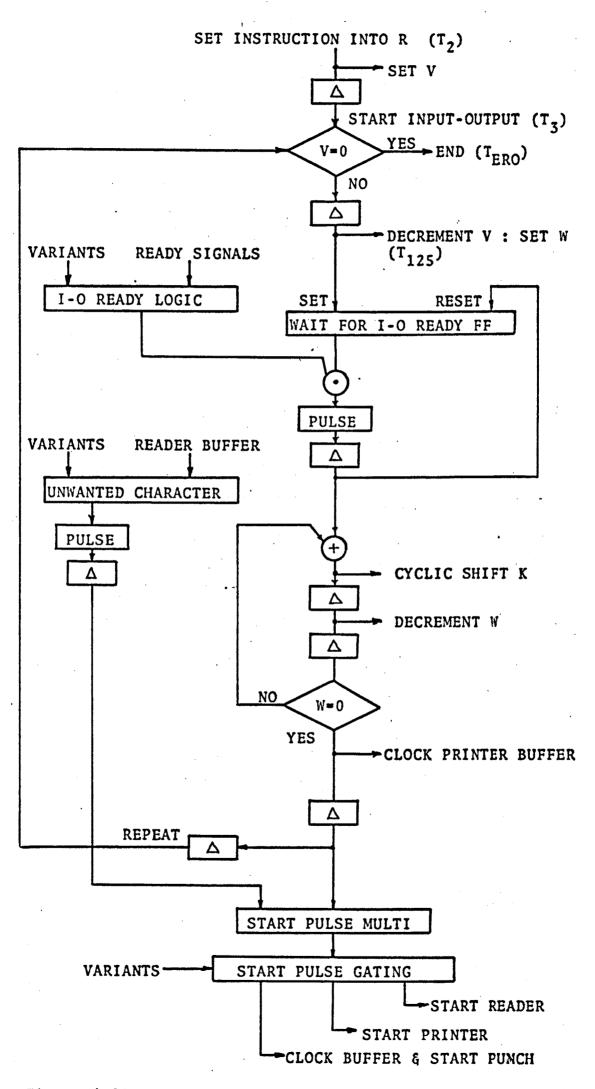

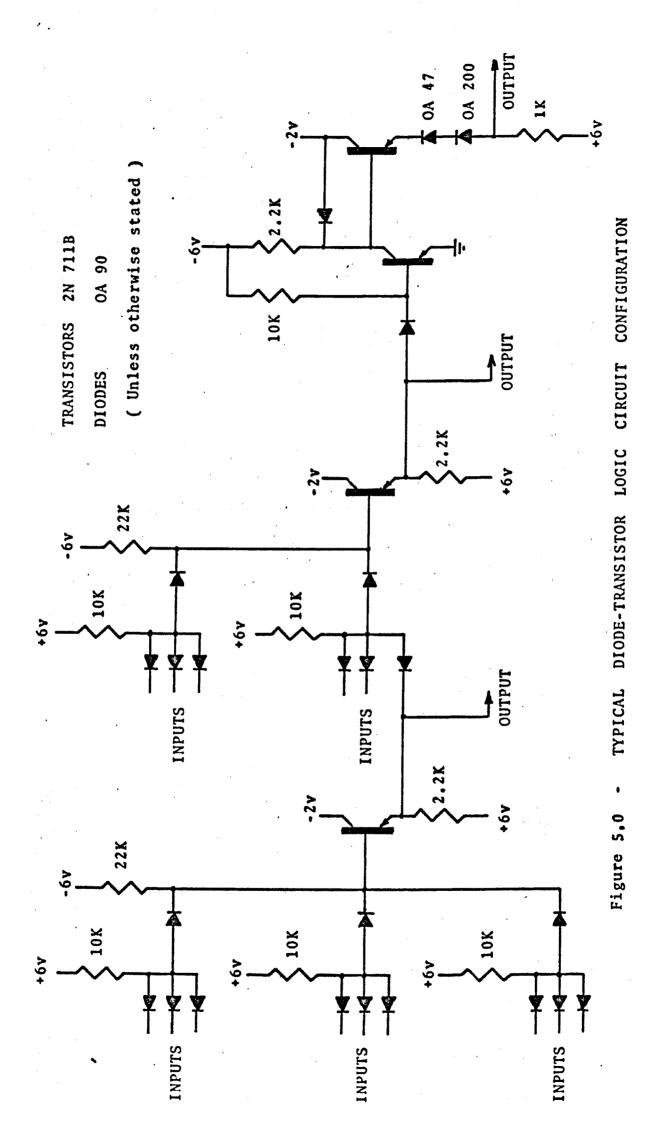

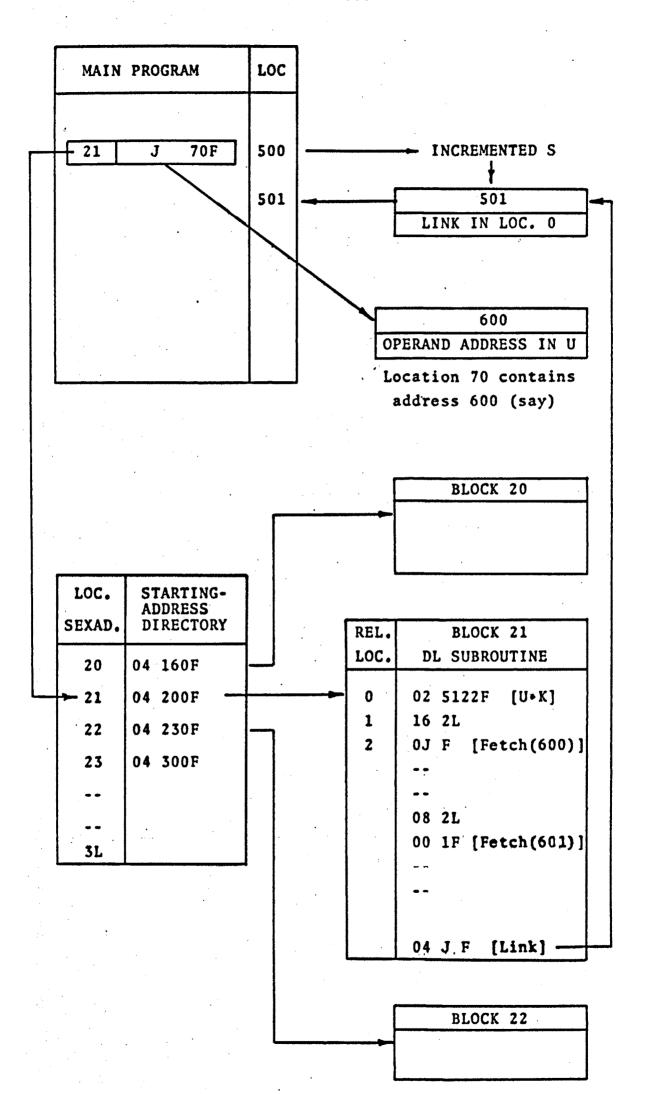

| 0110 | ADD :Add the word specified by the address of the instruction to the contents of the accumulator retaining the result in the accumulator.                                       |  |  |  |  |